## ALTERNATIVE GATE DIELECTRICS AND APPLICATION IN NANOCRYSTAL MEMORY

NG TSU HAU (B.Eng.(Hons.)and M.Eng., NUS)

## A THESIS SUBMITTED

## FOR THE DEGREE OF DOCTOR OF PHILOSOPHY IN ENGINEERING

## DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

## NATIONAL UNIVERSITY OF SINGAPORE

2005

### Acknowledgement

I would like to thank my thesis supervisor, Associate Professor Chim Wai Kin and Associate Professor Choi Wee Kiong, for giving me the opportunity to undertake this interesting research topic and I am also very grateful for their guidance throughout my candidature.

I would like to thank Yan Ny, Wei Yip and Mr. Joo Moon Sig for their assistance rendered during the fabrication of the devices in Silicon Nano Device Laboratory (SNDL). I am also thankful to Mr. Walter Lim, Lee Wee, Vincent Ho and Eric for their discussions and assistance while working in Microelectronics laboratory. I would like to thank Dr. Wang Shi Jie as well as Li Qin for some of the collaborative work.

In Center for Integrated Circuits Failure Analysis and Reliability (CICFAR), I would like to thank Mrs Ho Chiow Mooi and Thiam Peng for their prompt supply of equipment and Lei Yong for the occasional discussions. Appreciation also goes to Chee Keong, Zheng Jianxin, Dr. Wong Wai Kin, Yong Yu, Osterberg Mans Jhan Bertil, Tiet Eng, Xin Hua, Li Qi, Gu Hua, Soon Leng, Soon Huat, Kuan Song, Chow Khim as well as many others who have made my stay in NUS an enriching experience.

I would like to thank all my ex-colleagues in Advanced Micro Devices (AMD), especially Dr. Mai Zhi Hong, for the friendship as well as their strong encouragement for my embarkation on this challenge.

## Title: Alternative Gate Dielectrics and Application in Nanocrystal Memory

#### TABLE OF CONTENTS

|        |          | I                                                                              | Pages |

|--------|----------|--------------------------------------------------------------------------------|-------|

| Ackn   | owledge  | ement                                                                          | i     |

| Table  | e of Con | itents                                                                         | ii    |

| Sumi   | mary     |                                                                                | vii   |

| List o | of Table | S                                                                              | viii  |

| List ( | of Figur | es                                                                             | ix    |

| Chap   | oter 1   | Introduction                                                                   | 1     |

| 1.1    | Backg    | ground                                                                         | 1     |

| 1.2    | Motiv    | ation                                                                          | 2     |

| 1.3    | Resea    | rch Objectives                                                                 | 4     |

| 1.4    | Organ    | ization of Thesis                                                              | 5     |

| Refer  | rences   |                                                                                | 7     |

| Chap   | oter 2   | Literature Review on High Dielectric Constant                                  | 9     |

|        |          | Materials and Nanocrystal Memory                                               |       |

| 2.1    | Litera   | ture Review on High Dielectric Constant (high-κ) Materials                     | 9     |

|        | 2.1.1    | Limitations of Silicon Dioxide (SiO <sub>2</sub> ) as Gate Dielectric Material | 9     |

|        | 2.1.2    | Employment of High Dielectric Constant Material as a Solution                  | 12    |

|        |          | to Limitations of Silicon Dioxide (SiO <sub>2</sub> )                          |       |

|        | 2.1.3    | Criteria for Selection of Alternative Gate Dielectrics and                     | 14    |

|        |          | Potential Candidates                                                           |       |

| 2.2    | Introd   | uction to Current Nonvolatile Memory Devices and their                         | 17    |

|        | Limita   | ations                                                                         |       |

|      | 2.2.1  | Basic Programming Mechanisms in Non-Volatile Memory                  | 19 |

|------|--------|----------------------------------------------------------------------|----|

|      |        | Devices                                                              |    |

|      |        | 2.2.1.1 Programming by Fowler-Nordheim (F-N) Tunneling               | 19 |

|      |        | 2.2.1.2 Programming by Hot-carrier Injection (HCI)                   | 21 |

|      | 2.2.2  | Basic Erasing Mechanisms Non-Volatile Memory Devices                 | 23 |

|      |        | 2.1.2.1 Erasing by UV radiation                                      | 24 |

|      |        | 2.1.2.2 Erasing by F-N Tunneling                                     | 24 |

| 2.3  | Candi  | dates to Address the Limitations of FLOTOX/Flash Memory              | 26 |

|      | Devic  | es                                                                   |    |

|      | 2.3.1  | MNOS Memory                                                          | 26 |

|      | 2.3.2  | SONOS Memory                                                         | 27 |

|      | 2.3.3  | Nanocrystal Memory Devices                                           | 30 |

|      |        | 2.3.2.1 Methods to Fabricate Nanocrystal Memory Devices              | 31 |

|      | 2.3.4  | Other Emerging Memory Devices                                        | 35 |

| 2.4  | Appro  | paches to Improve the Performance of Nanocrystal Memory              | 37 |

|      | 2.4.1  | Tunnel Oxide Thickness Reduction and its Related Issues              | 37 |

|      |        | 2.4.1.1 Approach to Address Limitations of Thin Tunnel Oxide         | 38 |

|      | 2.4.2  | Electric Field Coupling Enhancement                                  | 39 |

|      |        | 2.4.2.1 Capping Layer Thickness Reduction                            | 39 |

|      |        | 2.4.2.2 High-κ Material as Alternative Capping Material              | 39 |

| 2.5  | Summ   | nary                                                                 | 40 |

|      | Refere | ences                                                                | 42 |

| Chap | ter 3  | Fabrication and Characterization of High-Dielectric                  | 51 |

|      |        | <b>Constant Materials for Potential Applications in</b>              |    |

|      |        | Nanocrystal Memory Devices                                           |    |

| 3.1  | Fabric | eation and Characterization of Zirconium Dioxide (ZrO <sub>2</sub> ) | 51 |

|      | 3.1.1  | Device Fabrication                                                   | 51 |

|      | 3.1.2  | Device Characterization                                              | 52 |

|      |        |                                                                      |    |

|                     |                                                                                  | 3.1.2.1 Structural Characterization                                                                                                                                                                                                                                                                                                                                                                                 | 52                                                                                             |

|---------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

|                     |                                                                                  | 3.1.2.2 Electrical Characterization                                                                                                                                                                                                                                                                                                                                                                                 | 54                                                                                             |

|                     |                                                                                  | 3.1.2.3 Quantum-Mechanical Simulation of C-V curves                                                                                                                                                                                                                                                                                                                                                                 | 57                                                                                             |

|                     | 3.1.3                                                                            | Charge Transport Mechanisms                                                                                                                                                                                                                                                                                                                                                                                         | 62                                                                                             |

| 3.2                 | Fabrio                                                                           | cation and Characterization of Hafnium Dioxide                                                                                                                                                                                                                                                                                                                                                                      | 68                                                                                             |

|                     | 3.2.1                                                                            | Fabrication of HfO <sub>2</sub> Film                                                                                                                                                                                                                                                                                                                                                                                | 68                                                                                             |

|                     | 3.2.2                                                                            | XPS Characterization of HfO <sub>2</sub> Film                                                                                                                                                                                                                                                                                                                                                                       | 69                                                                                             |

|                     | 3.2.3                                                                            | Electrical Characterization of the HfO <sub>2</sub> Film                                                                                                                                                                                                                                                                                                                                                            | 70                                                                                             |

| 3.3                 | Investi                                                                          | gation of Crystallization Temperature of Hafnium Dioxide and                                                                                                                                                                                                                                                                                                                                                        | 71                                                                                             |

|                     | Hafniu                                                                           | ım Aluminum Oxide                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                |

| 3.4                 | Summ                                                                             | ary                                                                                                                                                                                                                                                                                                                                                                                                                 | 74                                                                                             |

|                     | Refere                                                                           | nces                                                                                                                                                                                                                                                                                                                                                                                                                | 75                                                                                             |

|                     |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                |

|                     | 4                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                     | =0                                                                                             |

| Chapt               | er 4                                                                             | Nanocrystal Memory Devices with High Dielectric Constant                                                                                                                                                                                                                                                                                                                                                            | 79                                                                                             |

| Cnapt               | er 4                                                                             | Nanocrystal Memory Devices with High Dielectric Constant<br>Material as Tunnel Dielectric                                                                                                                                                                                                                                                                                                                           | 79                                                                                             |

| <b>Chapt</b><br>4.1 |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                     | 7 <b>9</b><br>79                                                                               |

| -                   | Fabric                                                                           | Material as Tunnel Dielectric                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                |

| -                   | Fabric                                                                           | Material as Tunnel Dielectric<br>ation and Characterization of Nanocrystal Memory with Hafnium                                                                                                                                                                                                                                                                                                                      |                                                                                                |

| -                   | Fabric<br>Dioxic                                                                 | <b>Material as Tunnel Dielectric</b><br>ation and Characterization of Nanocrystal Memory with Hafnium<br>le as Tunnel Dielectric (EOT = 4.8nm)                                                                                                                                                                                                                                                                      | 79                                                                                             |

| -                   | Fabric<br>Dioxic<br>4.1.1                                                        | Material as Tunnel Dielectric<br>ation and Characterization of Nanocrystal Memory with Hafnium<br>le as Tunnel Dielectric (EOT = 4.8nm)<br>Charge Storage Studies                                                                                                                                                                                                                                                   | 79<br>81                                                                                       |

| -                   | Fabric<br>Dioxic<br>4.1.1<br>4.1.2<br>4.1.3                                      | Material as Tunnel Dielectric<br>ation and Characterization of Nanocrystal Memory with Hafnium<br>le as Tunnel Dielectric (EOT = 4.8nm)<br>Charge Storage Studies<br>Charging and Discharging Time Studies                                                                                                                                                                                                          | 79<br>81<br>84                                                                                 |

| 4.1                 | Fabric<br>Dioxic<br>4.1.1<br>4.1.2<br>4.1.3<br>Furthe                            | Material as Tunnel Dielectric<br>ation and Characterization of Nanocrystal Memory with Hafnium<br>le as Tunnel Dielectric (EOT = 4.8nm)<br>Charge Storage Studies<br>Charging and Discharging Time Studies<br>Charge Retention Studies                                                                                                                                                                              | 79<br>81<br>84<br>85                                                                           |

| 4.1                 | Fabric<br>Dioxic<br>4.1.1<br>4.1.2<br>4.1.3<br>Furthe                            | Material as Tunnel Dielectric<br>ation and Characterization of Nanocrystal Memory with Hafnium<br>le as Tunnel Dielectric (EOT = 4.8nm)<br>Charge Storage Studies<br>Charging and Discharging Time Studies<br>Charge Retention Studies<br>r Scaling of Hafnium Dioxide Tunnel Dielectric to EOT of                                                                                                                  | 79<br>81<br>84<br>85                                                                           |

| 4.1                 | Fabric<br>Dioxic<br>4.1.1<br>4.1.2<br>4.1.3<br>Furthe<br>1.9nm                   | Material as Tunnel Dielectric<br>ation and Characterization of Nanocrystal Memory with Hafnium<br>le as Tunnel Dielectric (EOT = 4.8nm)<br>Charge Storage Studies<br>Charging and Discharging Time Studies<br>Charge Retention Studies<br>r Scaling of Hafnium Dioxide Tunnel Dielectric to EOT of<br>and Performance Characterization                                                                              | 79<br>81<br>84<br>85<br>87                                                                     |

| 4.1                 | Fabric<br>Dioxic<br>4.1.1<br>4.1.2<br>4.1.3<br>Furthe<br>1.9nm<br>4.2.1          | Material as Tunnel Dielectric<br>ation and Characterization of Nanocrystal Memory with Hafnium<br>le as Tunnel Dielectric (EOT = 4.8nm)<br>Charge Storage Studies<br>Charging and Discharging Time Studies<br>Charge Retention Studies<br>r Scaling of Hafnium Dioxide Tunnel Dielectric to EOT of<br>and Performance Characterization<br>Structural Characterization                                               | 79<br>81<br>84<br>85<br>87<br>88                                                               |

| 4.1                 | Fabric<br>Dioxic<br>4.1.1<br>4.1.2<br>4.1.3<br>Furthe<br>1.9nm<br>4.2.1<br>4.2.2 | Material as Tunnel Dielectric<br>ation and Characterization of Nanocrystal Memory with Hafnium<br>le as Tunnel Dielectric (EOT = 4.8nm)<br>Charge Storage Studies<br>Charging and Discharging Time Studies<br>Charge Retention Studies<br>r Scaling of Hafnium Dioxide Tunnel Dielectric to EOT of<br>and Performance Characterization<br>Structural Characterization<br>Charge Storage<br>Charge Retention Studies | <ul> <li>79</li> <li>81</li> <li>84</li> <li>85</li> <li>87</li> <li>88</li> <li>91</li> </ul> |

| Chapter 5 |        | High Dielectric Constant Material as Capping<br>Layer for Improved Electric Field Coupling in<br>Nanocrystal Memory Devices | 97  |

|-----------|--------|-----------------------------------------------------------------------------------------------------------------------------|-----|

| 5.1       | Exper  | imental Details                                                                                                             | 97  |

| 5.2       | Comp   | arison of Performance for Devices with Different Types of                                                                   | 98  |

|           | Cappi  | ng Layer                                                                                                                    |     |

|           | 5.2.1  | Charge Storage Analysis                                                                                                     | 98  |

|           | 5.2.2  | Charge Retention Capability Studies                                                                                         | 105 |

| 5.3       | Condu  | uctance Measurement                                                                                                         | 109 |

|           | 5.3.1  | Motivation for Applying Conductance Measurement to the                                                                      | 109 |

|           |        | Study of Nanocrystal Devices                                                                                                |     |

|           | 5.3.2  | Theory and Model of Conductance Measurement                                                                                 | 110 |

|           | 5.3.3  | Correlation between Conductance Peak Location and Flatband                                                                  | 117 |

|           |        | Voltage                                                                                                                     |     |

|           | 5.3.4  | Conductance Measurement on Nanocrystal Capacitor                                                                            | 120 |

|           |        | Devices with Different Types of Capping Layer                                                                               |     |

|           | 5.3.5  | Estimation of Nanocrystal Density Based on                                                                                  | 125 |

|           |        | Conductance-Voltage (G-V) Data                                                                                              |     |

| 5.4       | Summ   | nary                                                                                                                        | 129 |

|           | Refer  | ences                                                                                                                       | 131 |

| Chaj      | oter 6 | Investigation of Charge Storage Mechanism in Germanium                                                                      | 133 |

|           |        | Nanocrystals Using Nanocrystal Transistor Devices                                                                           |     |

| 6.1       | Fabric | cation Procedure of Nanocrystal Memory Transistor                                                                           | 134 |

| 6.2       | Electr | ical Characterization of Nanocrystal Memory Transistor                                                                      | 135 |

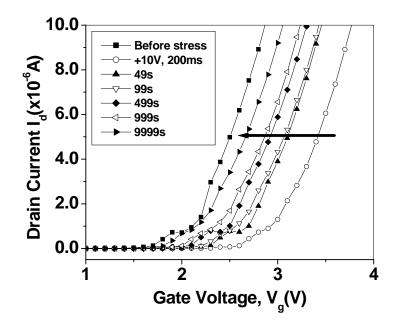

|           | 6.2.1  | Transient Characteristics of the Transistor Based Nanocrystal                                                               | 139 |

|           |        | Memory Structures                                                                                                           |     |

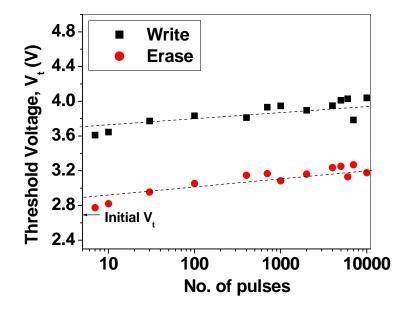

|           | 6.2.2  | Endurance Characteristics                                                                                                   | 141 |

|           |        | 6.2.2.1 Write/Erase Endurance Testing                                                                                       | 142 |

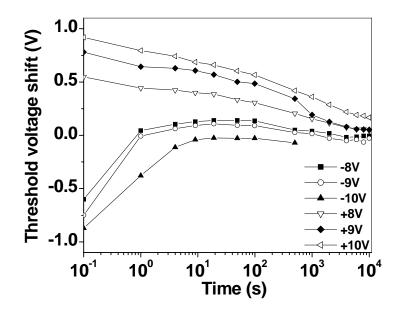

|           |        | 6.2.2.2 Charge Retention Testing                                                                                            | 143 |

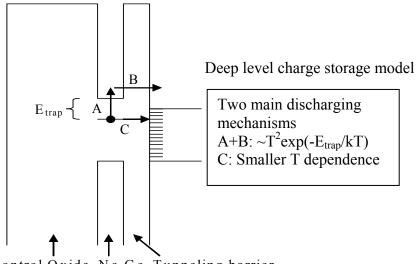

| 6.3       | Charg  | e Storage and Discharge Mechanisms in Nanocrystal Flash                                                                     | 145 |

## Memories

| List | of Publi  | cations                                                    | 181 |

|------|-----------|------------------------------------------------------------|-----|

|      | Refere    | ences                                                      | 176 |

| 7.3  | Recon     | nmendation for Future Work                                 | 171 |

| 7.2  | Techn     | ology Perspective                                          | 170 |

| 7.1  | Summ      | nary                                                       | 167 |

| Chap | oter 7: C | Conclusion                                                 | 167 |

|      | Refere    | ences                                                      | 164 |

| 6.6  | Summ      | •                                                          | 162 |

|      | -         |                                                            |     |

| 6.5  | Tran I    | Level Enginnering                                          | 160 |

| 6.4  | Altern    | native Method for Extraction of Trap Energy Level          | 156 |

|      | 6.3.3     | Possible Origin of the Extracted Trap Level                | 155 |

|      |           | Nanocrystal Transistors                                    |     |

|      | 6.3.2     | Extraction of Trap Energy Level from Germanium             | 152 |

|      | 6.3.1     | Review of Previous Work on Extraction of Trap Energy Level | 146 |

#### Summary

Nanocrystal memory has attracted much attention because it has better scalability than the conventional floating gate Flash memory. In this work, the performance of germanium (Ge) nanocrystal memory structures, employing high dielectric constant (high- $\kappa$ ) materials to replace the tunnel oxide and capping oxide (control oxide) layers, was investigated. It was found that faster charging rate and better charge retention performance could be obtained with a high- $\kappa$  tunnel dielectric layer of equivalent oxide thickness (EOT) to that of silicon dioxide. Even at an EOT of 1.9 nm, the high- $\kappa$  layer is still physically thick enough to prevent Ge penetration into the substrate during high temperature annealing. If Ge penetration were to occur, Ge nanocrystals will not be able to form and the device will not show any charge storage effect. The replacement of the capping oxide layer with a high- $\kappa$  material of similar physical thickness as that of a silicon dioxide capping layer will result in better gate electric field coupling. The effect of gate electric field coupling on the conductance-voltage (G-V) characteristics of different trilayer nanocrystal memory structures was also investigated. It was found that the distinctive G-V characteristics due to nanocrystals could be separated and identified from the interface traps provided the memory structure has sufficiently high electric field coupling from the gate applied voltage. A method for calculating the density of nanocrystals based on the G-V data was also discussed. Finally, investigation of trap energy levels in Ge nanocrystal memory structures and their effect on the device charging and discharging kinetics were also carried out by monitoring the transient drain current characteristics.

## List of Tables

| Table 2.1 | List of projected transistor parameter requirements for future devices.                                                                     | Pages<br>10 |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Table 2.2 | Characteristics and properties of some potential high- $\kappa$ dielectric material. SiO <sub>2</sub> is also listed for comparison         | 15          |

| Table 2.3 | A summary of the various nanocrystal fabrication techniques.                                                                                | 33          |

| Table 4.1 | The configurations of the trilayer structures used for comparison of device performance.                                                    | 80          |

| Table 4.2 | The configurations of the trilayer structures (with tunnel dielectric thickness further reduced) used for comparison of device performance. | 90          |

| Table 5.1 | The configurations of the trilayer structures (with different capping material/thickness) used for comparison of device performance.        | 98          |

| Table 5.2 | A summary of the structures of the fabricated devices and comparison of their charge storage capability.                                    | 102         |

| Table 5.3 | Description of the devices used for G-V study.                                                                                              | 121         |

## List of Figures

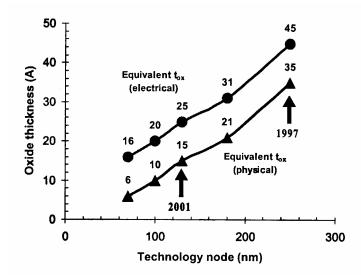

| Figure 2.1  | Extrapolated gate oxide scaling trend for recent CMOS technologies.                                                                                                                                                         | Pages<br>11 |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

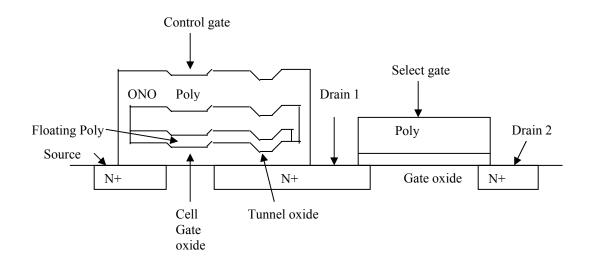

| Figure 2.2  | Schematic figure of a FLOTOX EEPROM cell.                                                                                                                                                                                   | 18          |

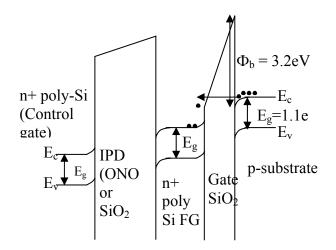

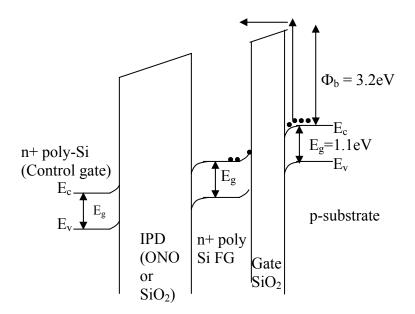

| Figure 2.3  | Energy band diagram of a floating gate memory during programming by F-N tunneling.                                                                                                                                          | 19          |

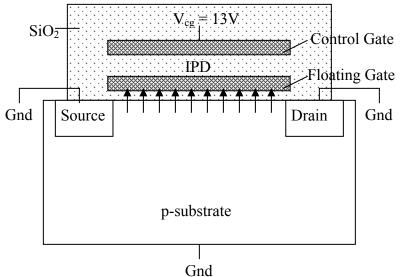

| Figure 2.4  | Schematic diagram showing uniform F-N tunneling of electrons from the substrate to the floating gate during programming of a Flash memory.                                                                                  | 20          |

| Figure 2.5  | Energy band diagram of a floating gate memory during programming by hot-electron injection.                                                                                                                                 | 22          |

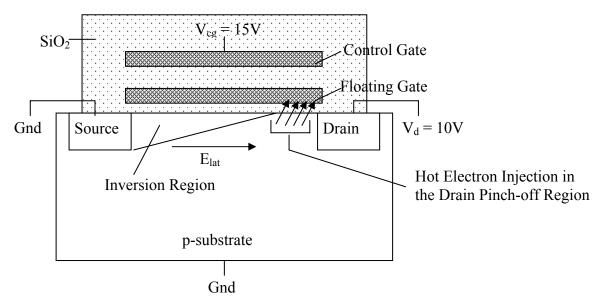

| Figure 2.6  | Schematic diagram showing hot-electron injection mechanism for programming in a NVM.                                                                                                                                        | 23          |

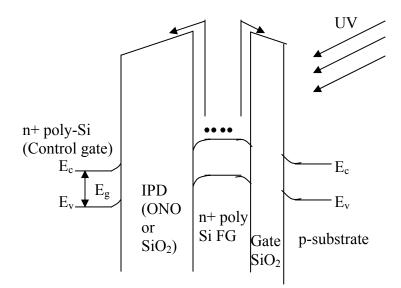

| Figure 2.7  | Band diagram describing the erasure of stored charge by UV radiation.                                                                                                                                                       | 24          |

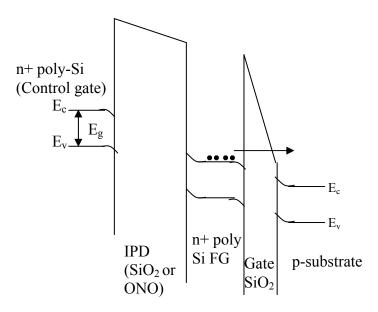

| Figure 2.8  | Energy band diagram of a floating gate memory during erasing by F-N tunneling.                                                                                                                                              | 25          |

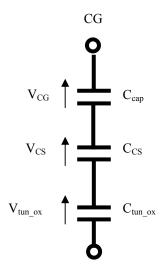

| Figure 2.9  | Schematic diagrams showing two methods to erase a Flash EEPROM: (a) uniform F-N tunneling erase and (b) drain-side tunneling erase.                                                                                         | 25          |

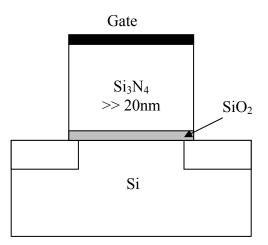

| Figure 2.10 | Schematic diagram of a MNOS memory structure                                                                                                                                                                                | 27          |

| Figure 2.11 | Schematic diagram of a SONOS memory structure.                                                                                                                                                                              | 28          |

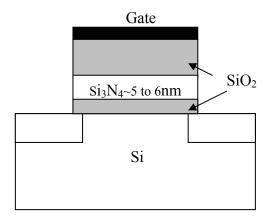

| Figure 2.12 | Capacitive model of the gate dielectric stack for SONOS-type device. CG denotes the control gate, "cap" denotes the capping (control) oxide layer, CS denotes the charge storage layer and tun_ox denotes the tunnel oxide. | 29          |

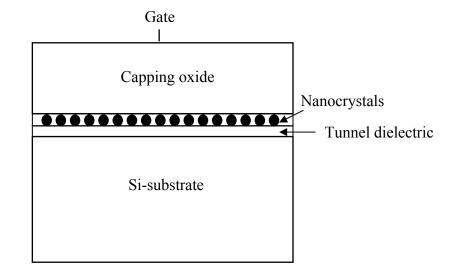

| Figure 2.13 | Schematic diagram of a nanocrystal memory structure.                                                                                                                                                                        | 30          |

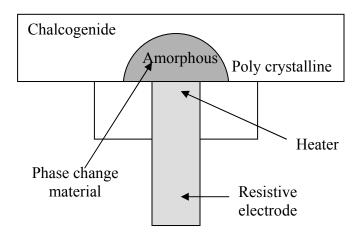

| Figure 2.14 | Schematic diagram of a Ovonic Unified Memory (OUM) device.                                                                                                                                                                                                                                                                                                                    | 35 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

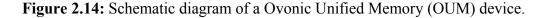

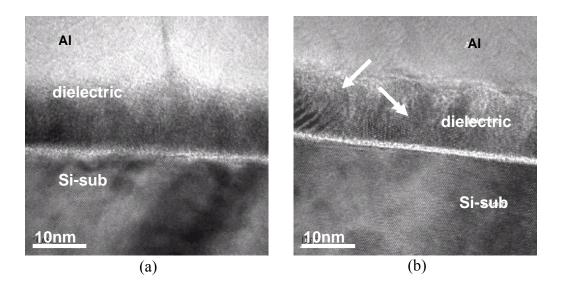

| Figure 3.1  | TEM images of the fabricated $Al/ZrO_2/n-Si$ MIS devices at (a) a low leakage site and (b) a high leakage site.                                                                                                                                                                                                                                                               | 53 |

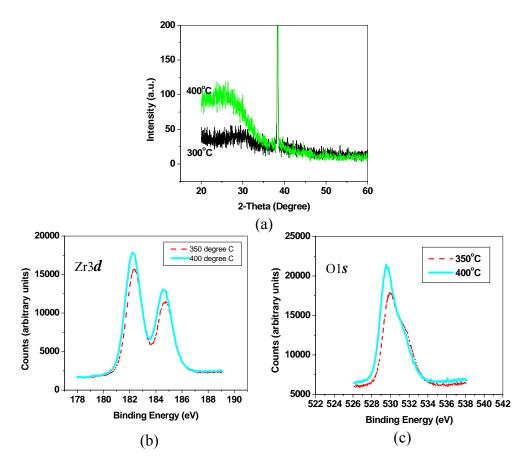

| Figure 3.2  | Structural characteristics of the fabricated Al/ZrO <sub>2</sub> /n-Si MIS devices: (a) The XRD spectra of the ZrO <sub>2</sub> film for wafer substrate temperatures of 300°C and 400°C during sputtering. The (b) Zr3 <i>d</i> and (c) O1 <i>s</i> XPS spectra of the ZrO <sub>2</sub> film for wafer substrate temperatures of 350°C and 400°C during reactive sputtering. | 54 |

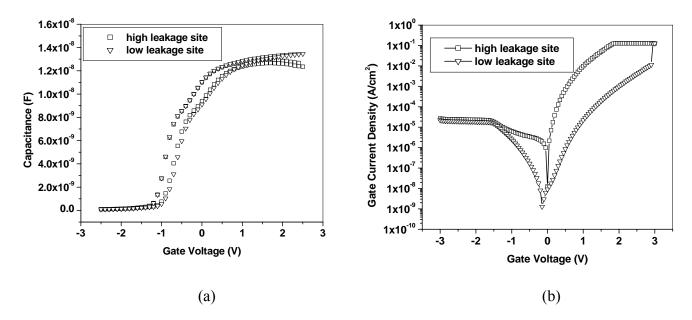

| Figure 3.3  | Electrical characteristics of the Al/ZrO <sub>2</sub> /n-Si MIS devices: (a) C-V and (b) I-V characteristics for high leakage and low leakage devices.                                                                                                                                                                                                                        | 55 |

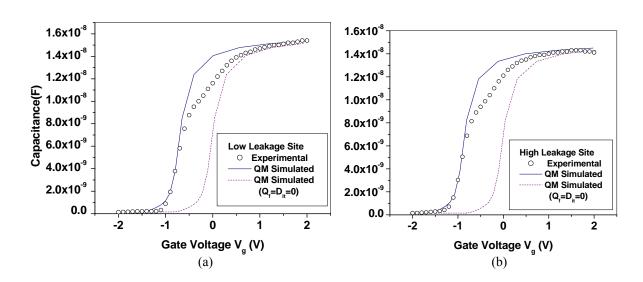

| Figure 3.4  | Quantum-mechanical C-V modeling (solid and dotted lines)<br>of typical (a) low leakage and (b) high leakage devices<br>compared with experimental measurements (open circles)                                                                                                                                                                                                 | 57 |

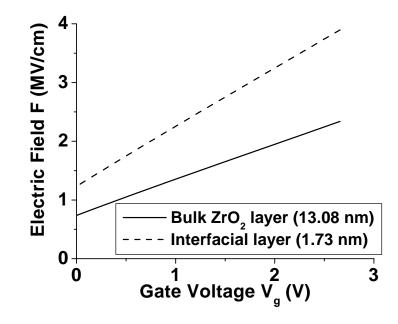

| Figure 3.5  | Plot showing the electric fields in both the bulk $ZrO_2$ and interfacial layer at the various gate voltages.                                                                                                                                                                                                                                                                 | 63 |

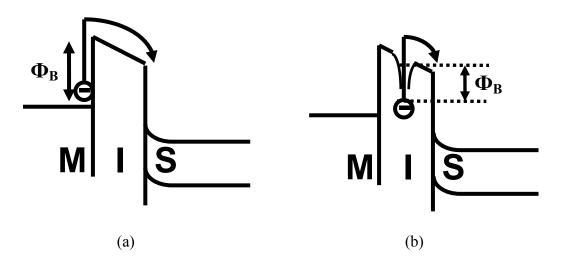

| Figure 3.6  | Band diagrams describing the current conduction processes in<br>Metal-Insulator-Semiconductor devices. (a) shows the<br>Schottky emission mechanism and (b) shows the F-P<br>emission mechanism.                                                                                                                                                                              | 65 |

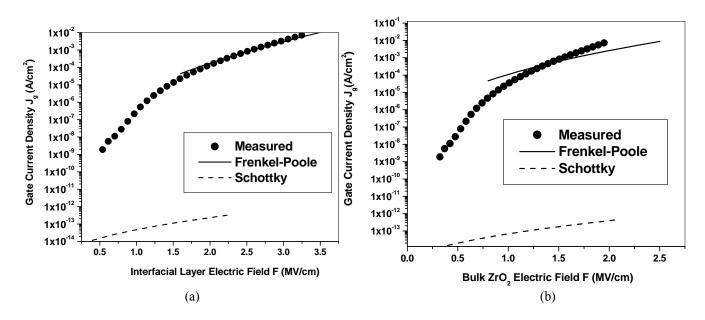

| Figure 3.7  | The measured and calculated (fitted) $J_g$ - $F$ characteristics, for values of $F$ in the (a) interfacial layer and (b) bulk ZrO <sub>2</sub> of a typical low leakage Al/ZrO <sub>2</sub> /n-Si MIS device in the low gate bias region.                                                                                                                                     | 66 |

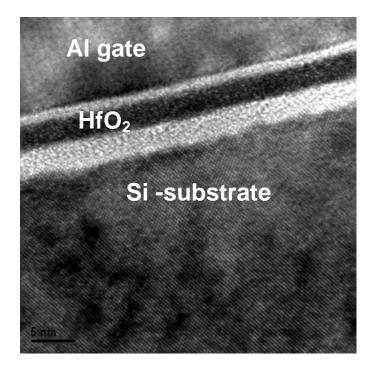

| Figure 3.8  | TEM picture of the high- $\kappa$ (HfO <sub>2</sub> ) film.                                                                                                                                                                                                                                                                                                                   | 69 |

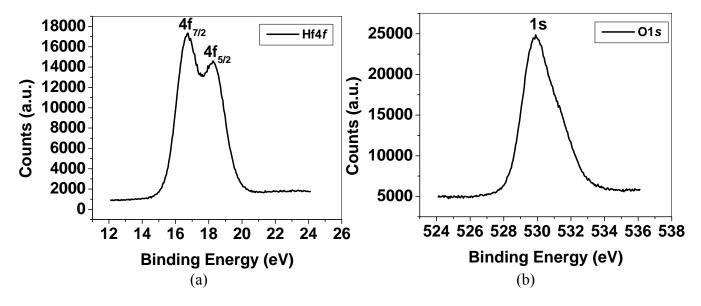

| Figure 3.9  | (a) Hf4 <i>f</i> and (b) O1 <i>s</i> XPS spectra of the deposited and annealed HfO <sub>2</sub> film.                                                                                                                                                                                                                                                                         | 70 |

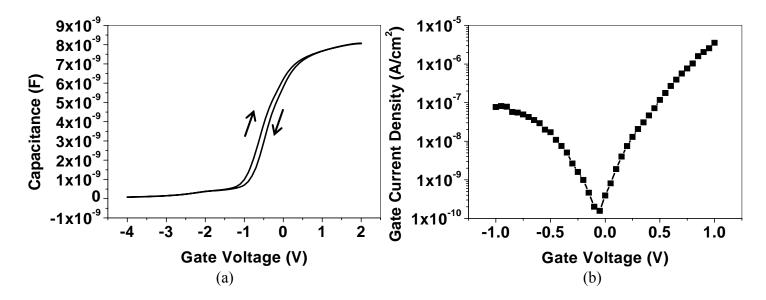

| Figure 3.10 | (a) C-V and (b) I-V characteristics of a typical MIS device with $HfO_2$ as the insulator layer.                                                                                                                                                                                                                                                                              | 71 |

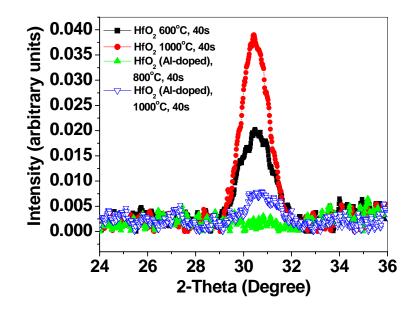

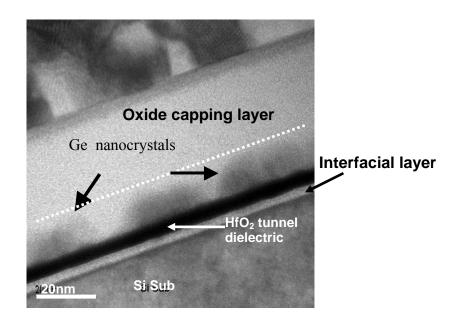

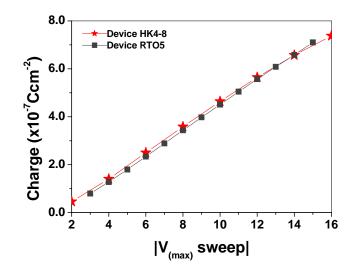

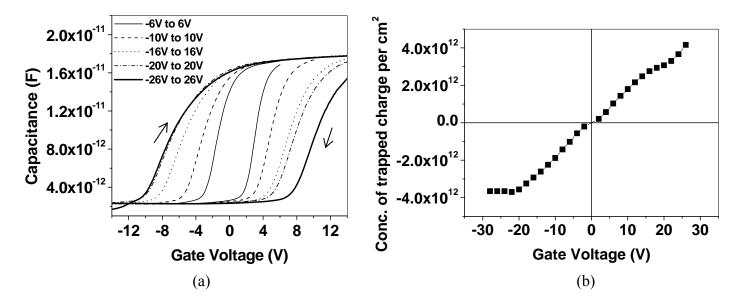

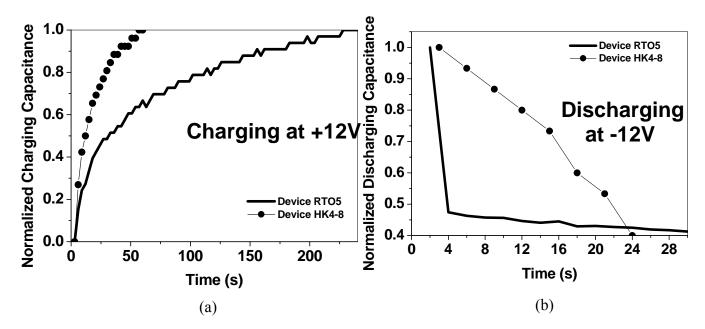

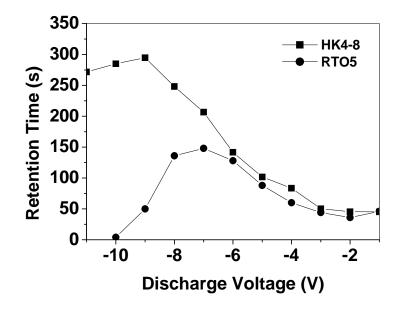

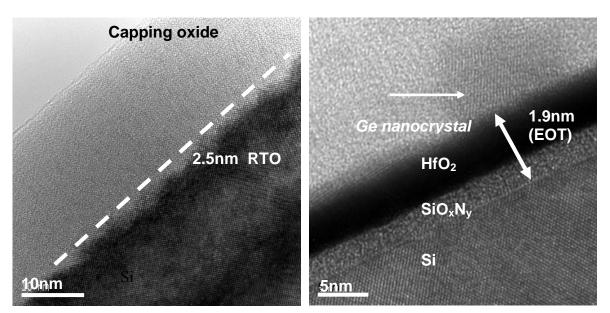

Figure 3.11 XRD spectra of pure HfO<sub>2</sub> after annealing at 600°C and 73 1000°C and HfO<sub>2</sub> doped with Al after annealing at 800°C and  $1000^{\circ}$ C. The crystallization temperature of HfO<sub>2</sub> could be raised to 1000°C when it is doped with Al. Figure 4.1 81 Cross-sectional HRTEM image of the nanocrystal memory device HK4-8. 82 Figure 4.2 C-V characteristics of (a) Device HK4-8 and (b) Device RTO5 showing clock-wise hysteresis. The gate voltage sweep range was gradually increased from -2V<V<sub>g</sub><2V to -16<Vg<16V. Figure 4.3 A plot summarizing the charge storage capability with respect 83 to the gate voltage sweep range for Device RTO5 and Device HK4 8. Figure 4.4 (a) C-V characteristics of device HK4-8. The gate voltage 84 sweep range was gradually increased till the occurrence of device breakdown (beyond the -26<Vg<26V sweep range). (b) Concentration of negative and positive trapped charges versus gate bias for device HK4-8. Figure 4.5 85 Study of Charging and discharging rate of the two devices. (a) shows the charging characteristics of the devices when a gate voltage of 12V is applied (b) shows the discharging characteristics when the gate voltage is abruptly switched to -12V after charging. Figure 4.6 87 Retention characteristics of trilayer insulator structure nanocrystal memory devices for different types of tunnel dielectric. Both HfO<sub>2</sub> and SiO<sub>2</sub> tunnel dielectric have the same equivalent-oxide-thickness of 5nm. The middle and cap layer thickness of both devices are the same. Figure 4.7 Cross-sectional TEM image of (a) device RTO2-5 and (b) 88 device HK1-9. Note the absence of Ge nanocrytals and the uneven RTO-Si interface caused by the Ge penetration in device RTO2-5.

Figure 4.8 SIMS result (of device HK1-9) showing that Ge does not penetrate and diffuse significantly into the silicon substrate. The HfO<sub>2</sub> layer provides a good blocking platform for the formation of Ge nanocrystals.

90

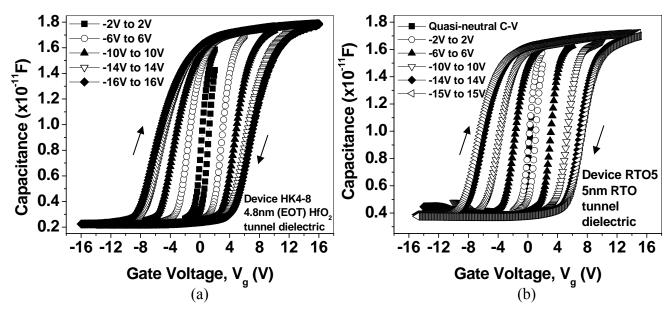

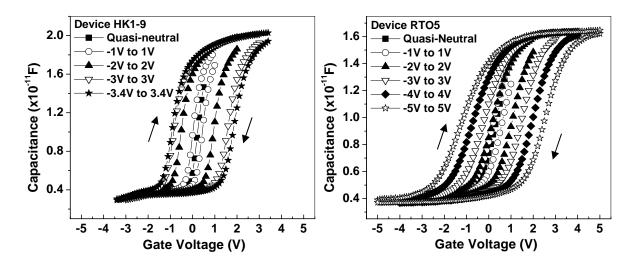

- Figure 4.9 High frequency *C-V* characteristics of (a) device HK1-9 and 91 (b) device RTO5. The quasi-neutral *C-V* curves for the respective devices were obtained by restricting the gate bias to a very narrow range to minimize charging up of the Ge nanocrystals.

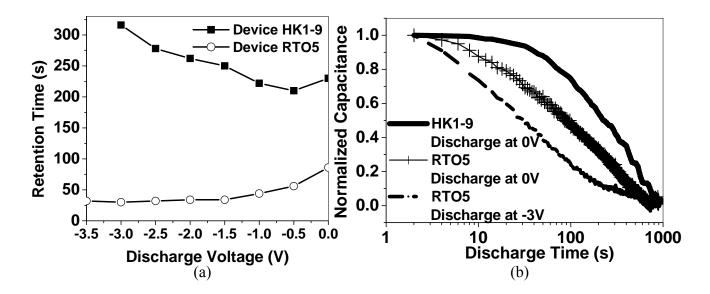

- Figure 4.10 Retention characteristics of devices RTO5 and HK1-9: (a) 93 Comparison of retention time versus discharge bias of both devices and (b) Some representative normalized *C-t* curves during discharge of devices RTO5 and HK1-9 at a constant discharge voltage of either 0 V or –3 V as indicated.

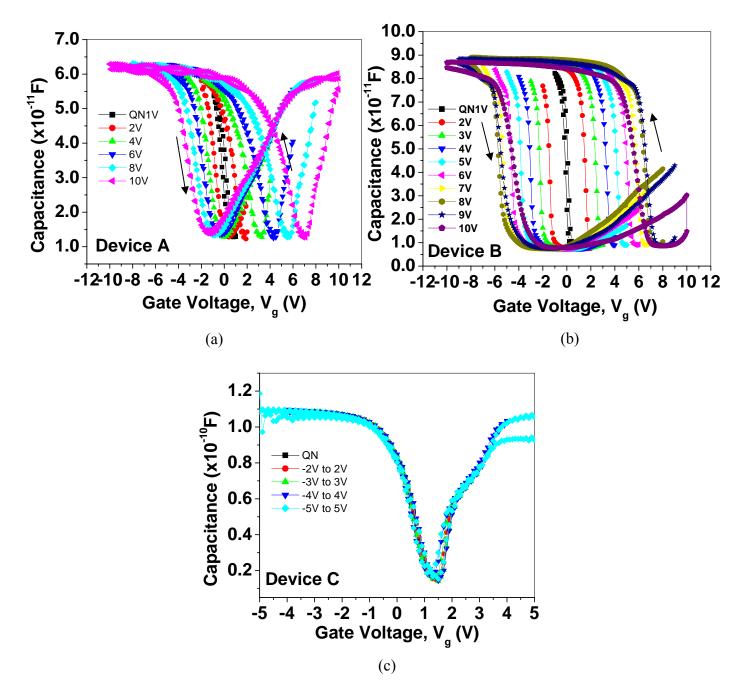

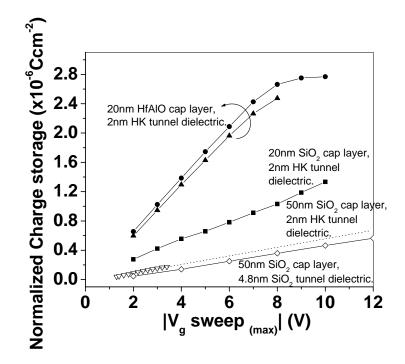

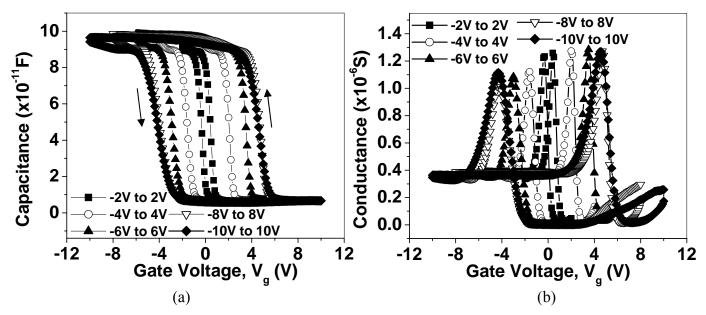

- Figure 5.1 Forward/reverse C-V characteristics of the three devices for 99 various sweep ranges. C-V Characteristics of (a) Device A (device with 20nm SiO<sub>2</sub> capping layer), (b) Device B (device with 20nm HfAlO capping layer) and (c) Device C (device with 10nm HfAlO capping layer). The capacitor area is  $4x10^{-4}$ cm<sup>2</sup> for the three devices. A holding time of 240s is applied before the commencement of each gate voltage sweep.

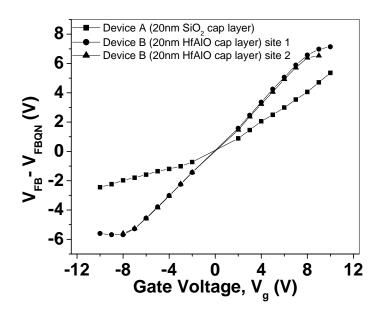

- Figure 5.2 Plot of flatband voltage shift with respect to the gate voltage 101 sweep range for Device A and Device B. The area of the device is  $4x10^{-4}$ cm<sup>2</sup>. V<sub>FB</sub> and V<sub>FBQN</sub> denote the flatband voltages of the charged and uncharged (quasi-neutral) device, respectively.

- Figure 5.3 Plot of charge storage with respect to the gate voltage sweep 102 range for Device A and Device B.

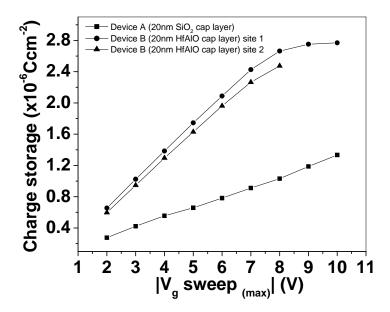

- Figure 5.4 Plot of charge storage with respect to the gate voltage sweep 104 range for Device A and Device B as well as devices fabricated in our earlier work (Device HK4-8 and Device HK1-9).

- xii

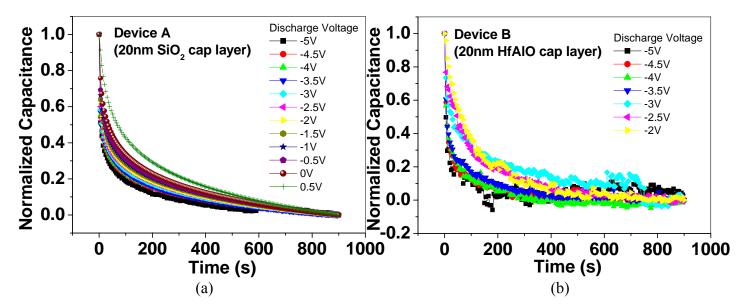

- Figure 5.5 Charge retention characteristics of Device A (device with 105 20nm SiO<sub>2</sub> capping layer) and Device B (device with 20nm HfAlO capping layer). Discharge characteristics of (a) Device A and (b) Device B.

- Figure 5.6 Plot of retention time over the discharge voltage range for 106 Device A and Device B.

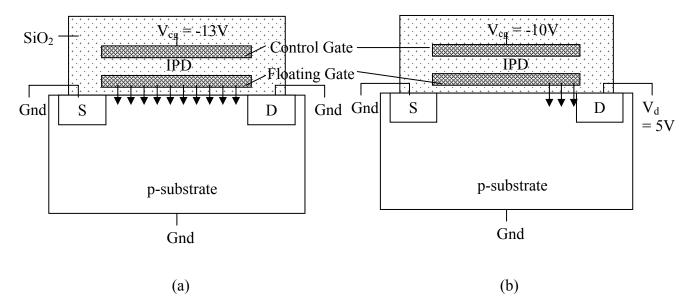

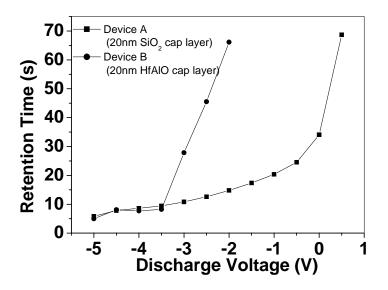

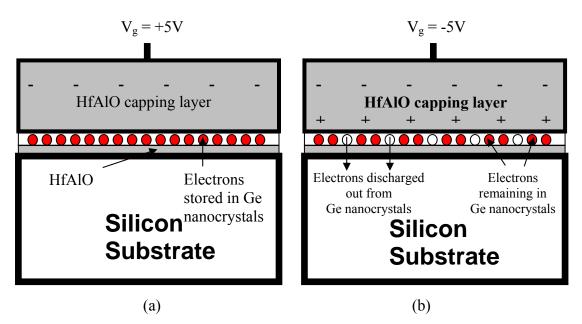

- Figure 5.7 Schematic diagram describing the polarization effect in the 108 high-κ capping layer during charging. (a) shows the polarization of the high-κ material when +5V is applied to the gate during charging. (b) shows the positive charge in the dipole of the polarized high-κ material preventing some electrons (stored in the nanocrystals) from tunneling back to the Si substrate easily, when the gate voltage is abruptly switched to -5V during discharging. The nanocrystals that are still stored with electrons are represented by the shaded nanocrystals in (b).

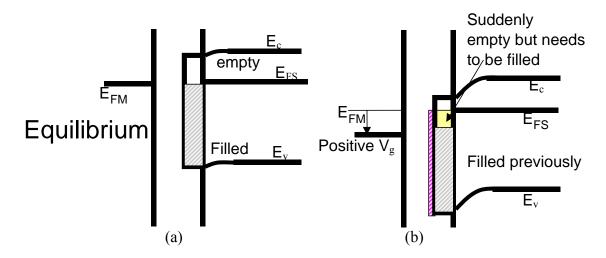

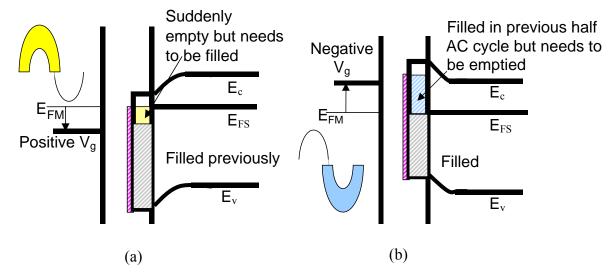

- Figure 5.8 Energy band diagram showing the interface traps (a) at 111 equilibrium and (b) in the positive half cycle of the AC signal applied at the gate electrode.

- Figure 5.9 Energy band diagram showing the interface traps (a) at the 112 positive half cycle of the AC signal and (b) immediately followed by negative half of the AC signal.

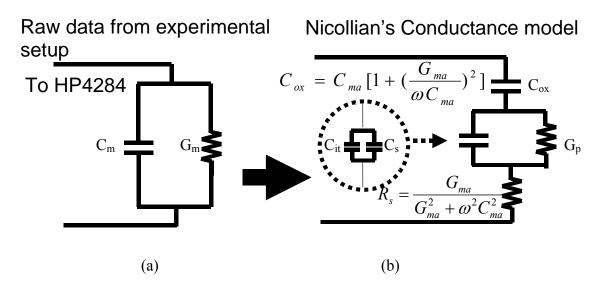

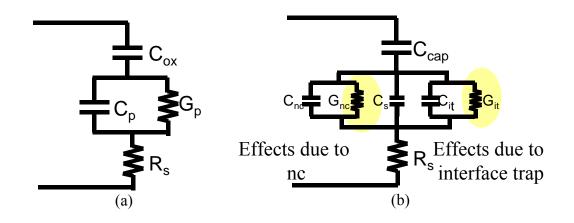

- Figure 5.10 Schematic diagram explaining the derivation of the 113 conductance parameters. (a) shows the experimental setup for a typical LCR meter to acquire the capacitance and conductance data and (b) shows the schematic for obtaining the parameters for Nicollian's conductance model.

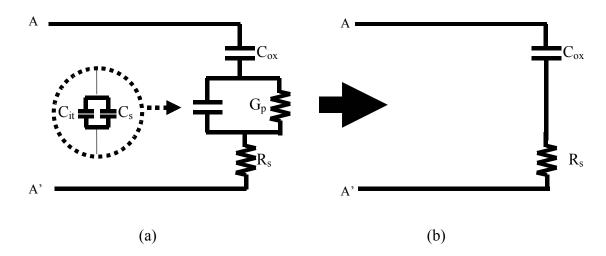

- Figure 5.11 Schematic diagrams illustrating the procedure for correction 114 of series resistance. (a) shows the original schematic representation whereas (b) shows the simplified diagram when the MOS capacitor is biased into the strong accumulation region.

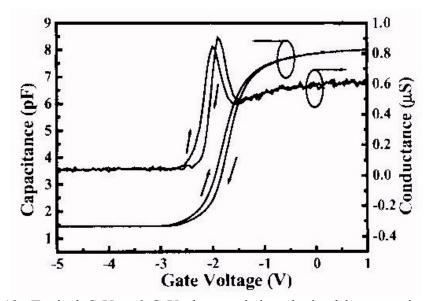

- Figure 5.12 Typical C-V and G-V characteristics obtained by sweeping 117 gate voltage back and forth between -5V and 1V. The peak position in the G-V characteristics is around the flatband condition [5].

- Figure 5.13 High frequency C-V and G-V characteristics of the trilayer 118 structure nanocrystal memory device B. (a) Forward and reverse sweeps C-V curves showing counter-clockwise hysteresis with the gate voltage ( $V_g$ ) sweep increasing from -2  $V < V_g < 2$  V to -10  $V < V_g < 10$  V. (b) The corresponding G-V characteristics during the respective gate voltage sweep.

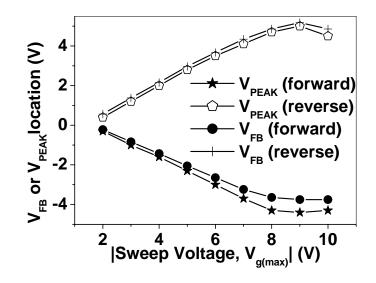

- Figure 5.14 Plot of the gate voltage corresponding to the conductance 119 peak ( $V_{\text{PEAK}}$ ) and flatband voltage  $V_{\text{FB}}$  (from C-V plot) versus the gate voltage sweep range.

- Figure 5.15 Schematic diagram showing the components for the extracted 120 parallel conductance. (a) shows the extracted parallel conductance,  $G_p$ , which is contributed by (b) the nanocrystal conductance  $G_{nc}$  branch, and the interface trap  $G_{it}$  branch.

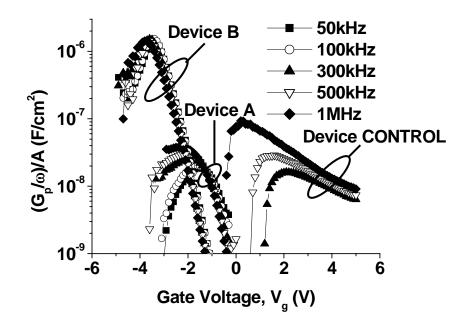

- Figure 5.16 Parallel conductance characteristics,  $(G_p/\omega)/A$  on a log scale 122 plotted against gate voltage during forward (increasing) gate voltage sweep after biasing at a gate voltage of -5 V for 240 s, for the three devices: Device Control (without nanocrystals), Nanocrystal memory device A (with 20-nm thick SiO<sub>2</sub> cap layer) and Nanocrystal memory device B (with 20-nm thick HfAlO cap layer). Note that the 50 kHz and 100 kHz  $(G_p/\omega)/A$  data for device A are smaller than 10<sup>-9</sup> F cm<sup>2</sup> and are not shown on the plot.

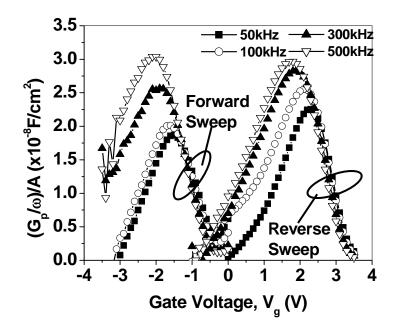

- Figure 5.17 Frequency dependent parallel conductance characteristics, 124  $(G_p/\omega)/A$  plotted on a linear scale against gate voltage, of nanocrystal memory device A (with 20-nm thick SiO<sub>2</sub> cap layer): (a) During forward (increasing) gate voltage sweep after biasing at a gate voltage of -5 V for 240 s, and (b) During reverse (decreasing) gate voltage sweep after biasing at a gate voltage of 5 V for 240 s.

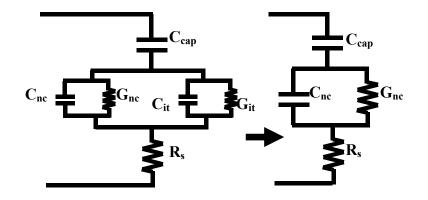

| Figure 5.18 | Schematic diagram of the conductance model for a typical<br>nanocrystal memory device structure. When the effect of<br>nanocrystals is more dominant than that of interface traps, the<br>model on the left could be further simplified to that on the<br>right.                                                                 | 126 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 5.19 | Schematic diagram illustrating the approach for the calculation of nanocrystal density.                                                                                                                                                                                                                                          | 127 |

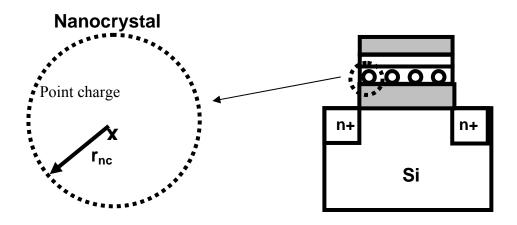

| Figure 6.1  | Schematic diagram of the process flow for Ge nanocrystal memory transistor device fabrication.                                                                                                                                                                                                                                   | 135 |

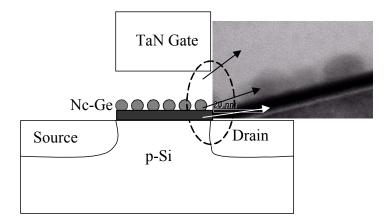

| Figure 6.2  | Schematic cross-sectional structure of fabricated device and HRTEM image of the HfAlO/nc-Ge/SiO <sub>2</sub> transistor memory structure.                                                                                                                                                                                        | 136 |

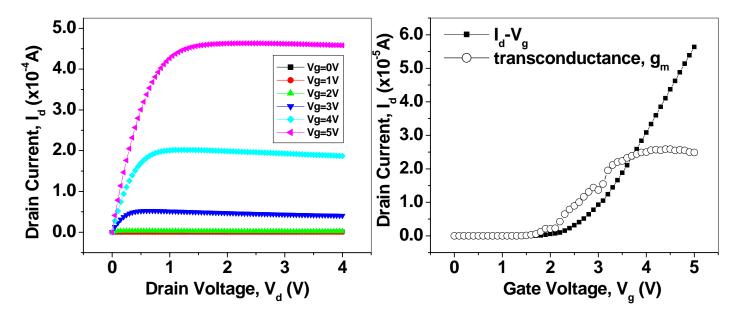

| Figure 6.3  | Electrical characteristics of the transistor memory device: (a) $I_d$ -V <sub>d</sub> and (b) $I_d$ -V <sub>g</sub> characteristics. The threshold voltage is about 2.7V.                                                                                                                                                        | 137 |

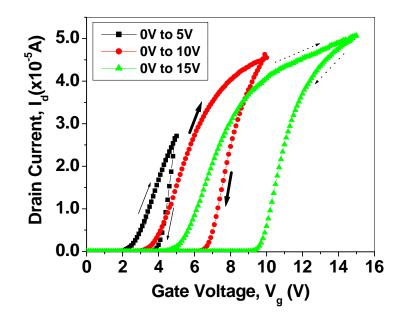

| Figure 6.4  | $I_d$ - $V_g$ characteristics of the nanocrystal transistor memory device obtained by first sweeping the gate voltage positively in the forward direction followed by a reverse sweep direction. The hysteresis loop formed by each pair of forward/reverse curves is indicative of the charge storage capability of the device. | 138 |

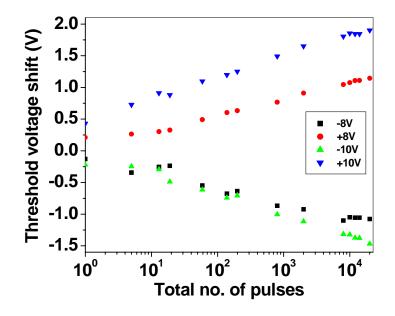

| Figure 6.5  | A plot of the threshold voltage shift with respect to the total time duration for accumulated number of pulses. It takes about 59 pulses of 10V to result in a threshold voltage shift of 1V.                                                                                                                                    | 141 |

| Figure 6.6  | Data endurance characteristics. $\pm 10V$ , 100ms pulses are applied for write/erase cycling of the nanocrystal transistor memory device. Write and erase conditions were (10V, 100ms) and (-10V, 100ms), respectively.                                                                                                          | 142 |

| Figure 6.7                                                                                                                                        | Various $I_d$ versus $V_g$ characteristics of the transistor memory device at the specified time durations after application of a write pulse of 10V for 200ms.                                                                                                                                                                                                                                          |     |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|

| Figure 6.8                                                                                                                                        | gure 6.8 Room temperature charge retention characteristics of the nanocrystal transistor memory after Write and Erase pulses of (8V, 9V and 10V for 200ms) and (-8V, -9V and -10V for 200ms), respectively.                                                                                                                                                                                              |     |  |  |  |

| Figure 6.9                                                                                                                                        | Model of deep level charge storage and discharging mechanisms.                                                                                                                                                                                                                                                                                                                                           | 147 |  |  |  |

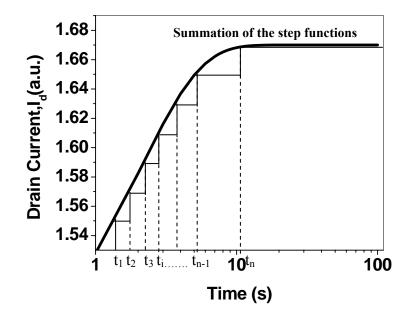

| Figure 6.10                                                                                                                                       | Pictorial explanation of the formation of the transient drain current during the discharging process. A step increase in the drain current is resulted when an electron is de-trapped from a nanocrystal into the Si substrate at time $t=t_i$ . The drain current transient curve could be represented by a summation of these step functions over the elapsed time throughout the discharging process. | 148 |  |  |  |

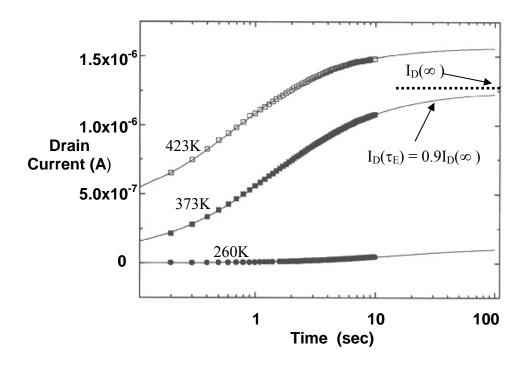

| Figure 6.11                                                                                                                                       | Drain current $(I_D)$ transient at the read voltage $(V_R)$ of 3 V after writing at 4V. Symbols represent measured data and the lines are fitted data.                                                                                                                                                                                                                                                   | 150 |  |  |  |

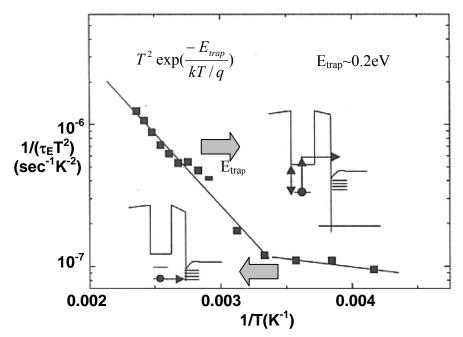

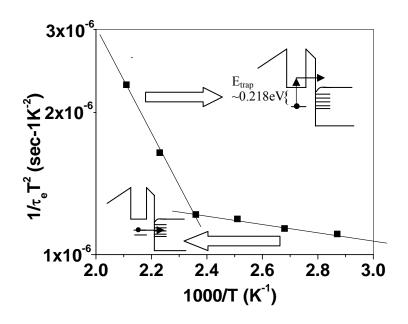

| Figure 6.12                                                                                                                                       | Inverse of the discharging time constant divided by squared temperature (T) at various read voltage and temperature T.                                                                                                                                                                                                                                                                                   | 151 |  |  |  |

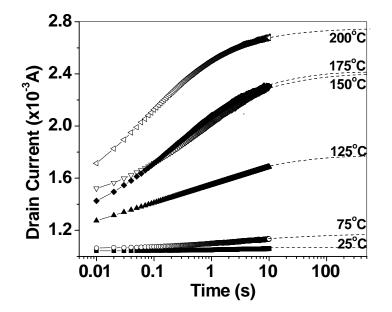

| Figure 6.13 The drain current transient during the application of the read voltage at 4V, after the application of a write voltage of 8V for 60s. |                                                                                                                                                                                                                                                                                                                                                                                                          |     |  |  |  |

| Figure 6.14                                                                                                                                       | Inverse of the discharging time constant divided by squared temperature (T) versus the inverse of T for germanium nanocrystal memory transistors.                                                                                                                                                                                                                                                        | 154 |  |  |  |

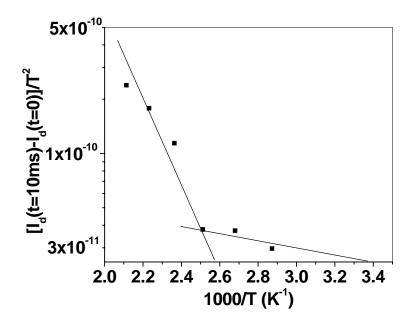

| Figure 6.15                                                                                                                                       | Drain current difference during discharging divided by squared temperature (T) versus the inverse of T.                                                                                                                                                                                                                                                                                                  | 159 |  |  |  |

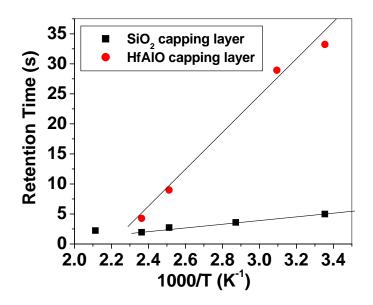

| Figure 6.16                                                                                                                                       | Temperature dependence of retention time for nc-Ge capacitors with $SiO_2$ capping layer and HfAlO capping layer.                                                                                                                                                                                                                                                                                        | 162 |  |  |  |

### **Chapter 1: Introduction**

#### 1.1 Background

The floating gate (FG) memory device is the most widely used design in nonvolatile semiconductor memory (NVSM) implementation. However, there are numerous difficulties in the scaling down of the FG NVSM device, especially decreasing the tunnel oxide thickness to meet conflicting operational requirements. On one hand, the tunnel oxide has to be thin to allow low-voltage, fast program and erase. On the other hand, the tunnel oxide has to be thick to provide superior isolation under charge retention condition in order to maintain information integrity of up to 10 years. As a result of these contradicting demands, Flash memory manufacturers have settled on a compromise for tunnel oxide thickness with values in the range 9 to 11 nm [1].

Storing charge on a single node (i.e. the FG node) makes the conventional Flash memory structure particularly prone to failure of the FG isolation (i.e., tunnel oxide). One weak spot in the tunnel oxide is sufficient to create a fatal discharge path, compromising long-term nonvolatility. One way to overcome this is to rely on distributed charge storage with charge storage nodes isolated from each other. The most popular types are polysilicon-oxide-nitride-oxide-silicon (SONOS) or nanocrystal memories. The main disadvantage for SONOS memory devices is that the traps are distributed randomly in the nitride charge storage layer [2]-[3]. Nanocrystal NVM offers greater control of the charge storage spatial location, especially if a templated self assembly method is used to order the nanocrystals [4].

In a nanocrystal NVM device, the charge is not stored on a continuous FG poly-Si layer, but instead on a layer of discrete, mutually isolated, crystalline nanocrystals or dots, typically made of semiconductor material [5]–[59]. Each dot will typically store only a single charge; collectively the charges stored in these dots control the channel-conductivity of the memory transistor. Compared to FG NVM, nanocrystal charge-storage offers several advantages; the main one being the potential to use a thinner tunnel oxide without sacrificing nonvolatility. Hence this will lead to lower operating voltages and higher program and erase speeds. Due to the distributed nature of charge storage, the charge storage device is more robust and fault tolerant to charge loss. This will also lead to improved endurance write/erase performance as compared to FG NVM.

#### **1.2** Motivation

A nanocrystal memory device typically consists of three layers of gate material deposited on the Si-substrate. These layers are namely, the tunnel oxide layer, the germanium (Ge) nanocrystal (charge storage) layer and the capping oxide layer. Although a thin tunnel oxide is highly-desirable for fast programming speed, one inherent issue would be the penetration of Ge through the thin tunnel oxide into the silicon (Si) substrate during high temperature annealing to form the Ge nanocrystals, resulting in a complete loss of charge storage capability [10]. This penetration issue imposes a lower bound (~5nm) to the scaling of the tunnel dielectric layer [11].

In this project, we intend to address the Ge penetration issue as well as to further reduce the tunnel dielectric electrical thickness by using an alternative material with a higher permittivity ( $\kappa$ ) value. The high- $\kappa$  material is able to provide a sufficiently thick physical layer to prevent the Ge from penetrating through the tunnel dielectric while at the same time, providing a much lower equivalent oxide thickness (EOT) for device operation.

In order to obtain a fast programming speed, the electric field across the tunnel oxide needs to be high so that charge carriers can tunnel rapidly from the Si substrate into the Ge nanocrystals. This high electric field could be achieved by simply applying a high voltage at the gate electrode but this approach is counter to low voltage operation. Application of a high gate voltage is also likely to induce unnecessary degradation on the tunnel oxide during Fowler-Nordheim tunneling of the charge carriers. Alternatively, the high electric field across the tunnel oxide could be achieved by decreasing the Ge layer thickness (i.e., nanocrystal size) or the capping oxide thickness. As there is a limit to decreasing the Ge layer thickness, a more viable approach would hence be to decrease the capping oxide thickness. Similar to the tunnel dielectric layer, there also exists a lower bound to the scaling of the capping oxide thickness as the Ge could out-diffuse from the middle Ge layer into the environment during the high temperature annealing to form the Ge nanocrystals if the capping oxide is too thin. It would be interesting to determine the lower bound limit for the SiO<sub>2</sub> cap layer thickness to ensure proper device functioning as well as to further reduce this layer electrically by replacing it with a high- $\kappa$  material. A high- $\kappa$  capping oxide layer would also result in better electric field coupling of the gate voltage to the tunnel oxide.

#### **1.3 Research Objectives**

The aim of this research is to explore the possibility of replacing the silicon dioxide (SiO<sub>2</sub>) components (tunnel oxide layer and capping layer) in a trilayer gate structure nanocrystal memory device with a high- $\kappa$  material. The performance of the device with the high- $\kappa$  layers will be compared with the control device with conventional SiO<sub>2</sub> layers. To obtain a better understanding of the role of each replaced layer and its effect on device performance, the individual layers will be changed one at a time and its characteristics studied.

During the initial phase of this project, the suitability of several high- $\kappa$  materials (e.g., zirconium dioxide (ZrO<sub>2</sub>), hafnium dioxide (HfO<sub>2</sub>) and hafnium aluminum oxide (HfAlO)) as a replacement material for SiO<sub>2</sub> will first be investigated before deciding on a suitable material. Charge storage capability, charging and discharging speeds as well as charge retention studies will be carried out and compared on nanocrystal capacitor memory devices with 5nm (EOT) of high- $\kappa$  tunnel dielectric and on device with the same thickness (5nm) of conventional RTO.

As the conventional RTO thickness has a lower limit at 5nm, below which Ge penetration would result in complete loss of charge storage capability, we attempt to address this penetration issue and also further reduce this 5nm EOT limit by replacing the conventional RTO with a suitable high- $\kappa$  material.

As the down-scaling of the capping layer (physical and electrical thickness) is beneficial to the programming/erasing speed of the device, the possibility of reducing the thickness of 50nm SiO<sub>2</sub> cap layer [8] -[11], as well as replacing this layer with a suitable high- $\kappa$  material would also be investigated. Electrical characterizations such as capacitance–voltage (C-V), current-voltage (I-V) and charge retention time studies will be performed on these devices. The more sensitive conductance-voltage (G-V) measurement method will also be used to characterize the devices to obtain further insights into the nanocrystal memory device operation. A methodology for extracting the nanocrystal density based on the G-V data will be discussed.

Upon the fabrication of the nanocrystal memory capacitors, a full-scale nanocrystal memory transistor with high- $\kappa$  as the tunnel dielectric material will be fabricated and characterized. An experiment for extraction of the nanocrystal trap energy level (E-trap) based on the study of drain current (during the discharging of trapped charge) with respect to temperature will be carried out [12]. An alternative method for extraction of E-trap levels will be proposed and discussed. Finally, the possibility of engineering the E-trap levels in the Ge nanocrystals by varying the surrounding matrix will be investigated.

#### **1.4 Organization of Thesis**

The thesis is arranged in a way to address the objectives set out for this research. Chapter 2 is devoted to cover the key findings in the literature survey on high- $\kappa$  materials as well as provide an overview of the theory of FG flash memory and nanocrystal memory structures. Chapter 3 describes the work carried out on fabrication and characterization of several high- $\kappa$  materials, namely ZrO<sub>2</sub>, HfO<sub>2</sub> and HfAlO, to identify suitable high- $\kappa$  materials for the nanocrystal memory. Chapter 4 examines the performance of the nanocrystal memory device with high- $\kappa$  HfO<sub>2</sub> and HfAlO materials as the tunnel dielectric material. Chapter 5 studies the possibility of employing the high- $\kappa$  HfAlO material as the capping layer for enhanced electric field coupling. The results of conductance-voltage (G-V) measurements performed on the nanocrystal memory capacitor devices will be shown in this chapter. A method for estimating the nanocrystal density based on the G-V data will also be discussed. Chapter 6 describes the electrical characterization of the transistor-based nanocrystal memory structures with high- $\kappa$  HfAlO material as the tunnel dielectric. The extraction of the nanocrystal trap energy level based on the study of drain current (during the discharging of trapped charge) with respect to temperature will be presented in this chapter. An alternative method to extract the energy trap level will be compared and discussed.

## References

- Jan De Blauwe, "Nanocrystal Nonvolatile Memory Devices", *IEEE Transactions* on Nanotechnology, vol. 1, no. 1, pp. 72-77, 2002.

- [2] F.R. Libsch and M.H. White, "Charge Transport and Storage of Low Programming Voltage SONOS/ MONOS Memory Devices", *Solid State Electronics*, vol. 33, no. 1, pp. 105-126, 1990.

- [3] H.E. Maes and R.J. Van Overstraeten, "Memory Loss in MNOS Capacitors", J. *Applied Physics*, vol. 47, no. 2, pp. 667-671, 1976.

- [4] Z. Chen, Y. Lei, H. G. Chew, L.W. Teo, W. K. Choi and W. K. Chim, "Synthesis of germanium nanodots on silicon using an anodic alumina membrane mask", *Journal of Crystal Growth*, vol. 268, pp. 560-563, 2004.

- [5] S. Tiwari, F. Rana, H. Hanafi, A. Hartstein, E. F. Crabbe and K. Chan, "Single charge and confinement effects in nano-crystal memories", *Applied Physics Letters*, vol. 68, no. 10, pp. 1377-1379, 1996.

- Y.C. King, T.J. King and C. Hu, "MOS memory using germanium nanocrystals formed by thermal oxidation of Si<sub>1-x</sub>Ge<sub>x</sub>", *IEDM Technical Digest*, pp. 115-118, 1998.

- Y.C. King, T. J. King and C. Hu, "Charge-trap memory device fabricated by oxidation of Si<sub>1-x</sub>Ge<sub>x</sub>", *IEEE Transactions on Electron Devices*, vol. 48, no. 4, pp. 696-700, 2001.

- [8] W. K. Choi, W. K. Chim, C. L. Heng, L. W. Teo, V. Ho, V. Ng, D. A. Antoniadis, and E. A. Fitzgerald, "Observation of memory effect in germanium nanocrystals embedded in an amorphous silicon oxide matrix of a

metal-insulator-semiconductor structure", *Applied Physics Letters*, vol. 80, no. 11, pp. 2014-2015, 2002.

- [9] L.W. Teo, W. K. Choi, W. K. Chim, V. Ho, C. M. Moey, M. S. Tay, C. L. Heng, Y. Lei, D. A. Antoniadis, and E. A. Fitzgerald, "Size control and charge storage mechanism of germanium nanocrystals in a metal-insulator-semiconductor structure", *Applied Physics Letters*, vol. 81, no. 19, pp. 3639-3641, 2002.

- [10] V. Ho, L. W. Teo, W. K. Choi, W. K. Chim, M. S. Tay, D. A. Antoniadis, E. A. Fitzgerald, A.Y. Du, C. H. Tung, R. Liu and A. T. S. Wee, "Effect of germanium concentration and tunnel oxide thickness on nanocrystal formation and charge storage/retention characteristics of a trilayer memory structure", *Applied Physics Letters*, vol. 83, pp. 3558-3560, 2003.

- [11] V. Ho, M. S. Tay, C. H. Moey, L. W. Teo, W. K. Choi, W. K. Chim, C. L. Heng, and Y. Lei, "Electrical characterization of a trilayer germanium nanocrystal memory device", *Microelectronic Engineering*, vol. 66, pp. 33-38, 2003.

- [12] S.J. Baik, S. Choi, U.-I. Chung, and J.T. Moon, "Engineering on tunnel barrier and dot surface in Si nanocrystal memories," *Solid-State Electronics*, vol. 48, pp. 1475-1481, 2004.

## Chapter 2: Literature Review on High Dielectric Constant (High-к) Materials and Nanocrystal Memory

In this chapter, the literature reviews on high dielectric constant (high- $\kappa$ ) materials will first be presented, followed by an overview of current memory devices and their limitations during device downscaling. From the literature reviews, the nanocrystal memory device seems to offer a promising solution to address the issues faced by current memory devices. To further enhance the performance of nanocrystal memory devices, the possibility of utilizing high- $\kappa$  materials to replace the conventional SiO<sub>2</sub> components in such a device will be discussed.

#### **2.1** Literature Review on High Dielectric Constant (high-κ) Materials

Silicon dioxide (SiO<sub>2</sub>) has been used as the main-stream gate dielectric material in Metal-Insulator-Silicon (MIS) devices for many years. However limitations start to arise with device downscaling. In this section, some of the issues experienced by SiO<sub>2</sub> during device downscaling will be mentioned and an explanation on how a high dielectric constant (high- $\kappa$ ) material could provide a solution to these issues will be provided. Some considerations to look into for the choice of an ideal alternative gate dielectric material will also be highlighted.

#### 2.1.1 Limitations of Silicon Dioxide (SiO<sub>2</sub>) as Gate Dielectric Material

In recent years, the gate oxide has been aggressively scaled as part of device miniaturization. In the very near future, the leakage current will increase to unacceptably high level and the boron penetration problem will be severely aggravated. In addition, it will be more difficult to control the uniformity and reproducibility of ultra-thin oxide growth processes. The extrapolated gate oxide scaling targets based on published data from recent Intel technologies [1] predicts that by the year 2008, the physical gate oxide thickness needs to be as thin as 8Å at the 60nm technology node and the solution to this problem is yet unknown. The technology node refers to the smallest polysilicon (poly-Si) gate length which can be defined by photolithography and roughly corresponds to the minimum channel length for a given process technology. A more complete list of projected transistor parameters is given in Table 2.1. The predictions are based on extrapolations of published state-of-the-art 180nm technologies assuming channel length, supply voltage, and gate oxide thickness scaling factors of 0.7, 0.8, and 0.8, respectively [2]-[4]. These projections, representative of the current targets for high-performance logic technology, aggressively outpace those compiled earlier in the year 2000 update of the International Technology Roadmap for Semiconductors (ITRS).

| Table 2.1: List of | projected transistor | parameter requirements | for future | devices [2]-[4]. |

|--------------------|----------------------|------------------------|------------|------------------|

|                    |                      |                        |            |                  |

| Generation (nm)                  | 180 | 130 | 100 | 70  | Scaling Factor |

|----------------------------------|-----|-----|-----|-----|----------------|

| L <sub>gate</sub> (nm)           | 100 | 70  | 50  | 35  | 0.7x           |

| $V_{dd}(V)$                      | 1.5 | 1.2 | 1.0 | 0.8 | 0.8x           |

| Tox, electrical (Å)              | 31  | 25  | 20  | 16  | 0.8x           |

| T <sub>ox</sub> , physical (Å)   | 21  | 15  | 10  | 6   | 0.8x           |

| I <sub>off</sub> at 25°C (nA/µm) | 20  | 40  | 80  | 160 | 2x             |

| Year                           | 1999             | 2001  | 2004  | 2008 | 2011 | 2014 |

|--------------------------------|------------------|-------|-------|------|------|------|

| Technology Node                | 180nm            | 130nm | 90nm  | 60nm | 40nm | 30nm |

| L <sub>gate</sub> (nm)         | 120              | 90    | 70    | 45   | 32   | 22   |

| T <sub>ox</sub> , physical (Å) | 19-25            | 15-19 | 12-15 | 8-12 | 6-8  | 5-6  |

| Gate leakage at 100°C (nA/µm)  | 7                | 10    | 16    | 40   | 80   | 160  |

|                                | No solutions yet |       |       |      |      |      |

Figure 2.1: Extrapolated gate oxide scaling trend for recent CMOS technologies [2]-[4].

The two data sets in Fig. 2.1 refer to the equivalent electrical and physical thickness of the gate oxide. The equivalent oxide thickness (EOT) refers to how thin a pure silicon dioxide (SiO<sub>2</sub>) layer would need to be in order to meet the gate capacitance requirements of a given technology. In a modern MOSFET device, the gate oxide could behave electrically as if it were 8-10Å thicker than its physical thickness due to polysilicon depletion and quantum mechanical effects. From Fig. 2.1, it is clear that the physical thickness of the gate oxide is rapidly approaching atomic dimensions. The 250nm technology, which entered volume production in 1997, used a SiO<sub>2</sub> layer with approximately 40Å physical t<sub>ox</sub>, corresponding to approximately 20 monolayers of SiO<sub>2</sub>. In contrast, the 100nm and 70nm technologies, scheduled for production in the next 5 to 10 years, will require gate capacitance values achievable only with SiO<sub>2</sub> layers as thin as 10Å and 7Å, respectively, to guarantee proper device operation. A 10Å film consists of only three to four monolayers of SiO<sub>2</sub>.

# 2.1.3 Employment of High Dielectric Constant Material as a Solution to Limitations of Silicon Dioxide (SiO<sub>2</sub>)

An approach to address the limitations of the conventional  $SiO_2$  gate insulator is to employ a physically thicker, higher permittivity gate dielectric in place of  $SiO_2$ , and/or silicon oxynitride, to meet the same gate capacitance requirements. In the following paragraphs, a brief explanation on the operation of the MOSFET followed by how the high dielectric constant material could be employed in such a device will be given.

A MOSFET ideally acts as a three-terminal switch, either connecting or isolating the drain (D) and source (S) terminals based on the voltage applied to the controlling gate (G) terminal. In practice, this switching action is achieved through the use of a gate capacitor. Depending on the polarity of the voltage applied to the gate terminal, either positive or negative charge is induced in the channel region. The channel charge either connects or isolates the drain and source nodes depending on the type of carriers contained in the channel region.

The operation of the MOSFET depends critically on several properties of the gate dielectric material SiO<sub>2</sub>. The wide insulating bandgap ( $E_g \sim 9eV$ ) of SiO<sub>2</sub> electrically isolates charges in the gate and channel regions, so that the controlling gate terminal does not interfere with the flow of the current in the channel regions. Also, the interface between SiO<sub>2</sub> and the underlying Si substrate is electrically of very high quality, allowing electric field originating at the gate electrode to penetrate into the channel region to accumulate or invert the surface charge. Prior to the development of the Si/SiO<sub>2</sub> system, attempts to realize a field-effect transistor (FET) were hampered by the abundance of electrically active defects at the dielectric/semiconductor interface.

The amount of charge (Q) induced in the channel region is given by the product of the gate oxide capacitance per unit area ( $C_{ox}$ ) and the voltage drop across the gate capacitor (V),

$$Q = C_{ox} V \tag{2.1}$$