## SAFA: Stack And Frame Architecture

BY Soo Yuen Jien (B.Sc (Hon) NUS, M.Sc NUS)

A THESIS SUBMITTED FOR THE DEGREE OF DOCTOR OF PHILOSOPHY AT DEPARTMENT OF COMPUTER SCIENCE SCHOOL OF COMPUTING NATIONAL UNIVERSITY OF SINGAPORE 2005

## Acknowledgment

First and foremost, I would like to thank my supervisor, Professor Yuen Chung Kwong, for suggesting such an interesting research topic. His knowledge and insight on the subject has guided me through many thorny issues. More importantly, his kind words have given me more confidence in the research direction.

I wish to express my gratitude to my research review committee members, Professor Teo Yong Ming and Associate Professor Wong Weng Fai. They have frequently pointed out blind spots in my research method, steering the research from potential pitfalls.

Last but not least, I would like to thank my wife, my parent and family members for their unfailing support and encouragement.

### Summary

Superscalar execution of computer instructions exists in many forms, which can be grouped roughly into two major camps: the hardware approach with examples like Alpha, PowerPC, x86 etc; the software approach with heavy reliance on compilers e.g. VLIW, EPIC etc. However, these approaches shares many characteristic and can be studied under a cohesive framework, which we termed as General Tagged Execution Framework. By exploiting the commonality of the approaches, it is possible to apply a combination of subsets of techniques under a different context.

Specifically, we investigated the feasibility of adapting some well studied techniques to a stack-oriented architecture. The research concentrates on two major areas of a stack architecture, namely high level language support and low level instruction execution. In the first area, improved control flow and data structure support are studied. For the low level instruction execution, superscalar and speculative execution techniques are incorporated. As a platform for experimenting with these mechanisms, we designed and implemented a simulator for a new stack architecture, named as SAFA (Stack And Frame Architecture).

# Contents

| 1        | Intr | oductio   | n                                               |    |   |   |   |     |   | 1  |

|----------|------|-----------|-------------------------------------------------|----|---|---|---|-----|---|----|

|          | 1.1  | General   | Tagged Execution Framework                      |    |   | • | • |     |   | 4  |

|          | 1.2  | The SA    | FA Architecture                                 |    |   | • | • |     |   | 6  |

|          | 1.3  | Objectiv  | ves of Our Work                                 |    |   | • | • |     | • | 8  |

|          | 1.4  | Overvie   | w of Thesis                                     |    |   | • | • |     |   | 9  |

| <b>2</b> | Lite | erature S | Survey                                          |    |   |   |   |     |   | 10 |

|          |      |           |                                                 |    |   |   |   |     |   | 10 |

|          | 2.1  | Introdu   | etion                                           |    | • | • | • | ••• | • | 10 |

|          | 2.2  | Objectiv  | 7es                                             |    |   | • | • |     | • | 10 |

|          | 2.3  | Stack B   | ased Architecture                               |    | • | • | • |     | • | 12 |

|          |      | 2.3.1 I   | Burroughs Family B5000-B6700                    |    | • | • | • |     | • | 12 |

|          |      | 2.3.2 I   | Hewlett-Packard HP3000                          |    | • | • | • |     | • | 13 |

|          |      | 2.3.3 I   | ntel iAPX432                                    |    |   | • | • |     |   | 14 |

|          |      | 2.3.4 I   | NMOS transputer                                 |    |   | • | • |     | • | 15 |

|          |      | 2.3.5     | ava Virtual Machine and picoJava implementation | on |   | • | • |     |   | 17 |

|          |      | 2.3.6     | Conclusion                                      |    |   | • | • |     |   | 18 |

|          | 2.4  | Register  | -Based Superscalar Architecture                 |    |   |   |   |     |   | 20 |

|   |     | 2.4.1   | Alpha Family                      | 20 |

|---|-----|---------|-----------------------------------|----|

|   |     | 2.4.2   | PowerPC Family                    | 23 |

|   |     | 2.4.3   | Conclusion                        | 25 |

|   | 2.5 | Summ    | nary                              | 26 |

| 3 | Hig | h Leve  | el Language Support               | 27 |

|   | 3.1 | Contro  | ol Flow                           | 28 |

|   |     | 3.1.1   | Procedure Activation              | 28 |

|   |     | 3.1.2   | Repetitive Execution with Counter | 33 |

|   | 3.2 | Data S  | Structure                         | 38 |

|   |     | 3.2.1   | Array                             | 38 |

|   |     | 3.2.2   | Linked List                       | 41 |

|   | 3.3 | Objec   | t Oriented Language               | 43 |

|   |     | 3.3.1   | Object Representation             | 44 |

|   |     | 3.3.2   | Dynamic Method Dispatching        | 46 |

|   | 3.4 | Additi  | ional Benefits of Frame Register  | 52 |

|   |     | 3.4.1   | Context Sensitivity               | 52 |

|   |     | 3.4.2   | Prefetching                       | 57 |

|   | 3.5 | Summ    | nary                              | 59 |

| 4 | Low | v Level | l Execution Support               | 60 |

|   | 4.1 | Overv   | iew of Instruction Dependencies   | 62 |

|   |     | 4.1.1   | Data Dependence                   | 62 |

|   |     | 4.1.2   | Name Dependence                   | 63 |

|   |     | 4.1.3   | Control Dependence                                                | 65  |

|---|-----|---------|-------------------------------------------------------------------|-----|

|   | 4.2 | Coping  | g with Data and Name Dependence                                   | 66  |

|   |     | 4.2.1   | Tomasulo's Scheme                                                 | 66  |

|   |     | 4.2.2   | Adaptation for SAFA                                               | 71  |

|   | 4.3 | Coping  | g with Control Dependence                                         | 85  |

|   |     | 4.3.1   | Branch Prediction and Speculative Execution in General            | 85  |

|   |     | 4.3.2   | Branch Prediction and Speculative Execution in SAFA $\ . \ . \ .$ | 88  |

|   |     | 4.3.3   | Limitation of Speculative Execution in SAFA                       | 95  |

|   | 4.4 | Coping  | g with Frequent Memory Movements                                  | 97  |

|   |     | 4.4.1   | Local Data Access in SAFA                                         | 100 |

|   | 4.5 | Advan   | aces in Java Technology                                           | 114 |

|   |     | 4.5.1   | Comparison: SAFA vs Java Processors                               | 118 |

|   | 4.6 | Influer | nce of General Tagged Execution Framework                         | 120 |

|   | 4.7 | Summ    | ary                                                               | 121 |

| 5 | Ben | chmar   | k Environment                                                     | 122 |

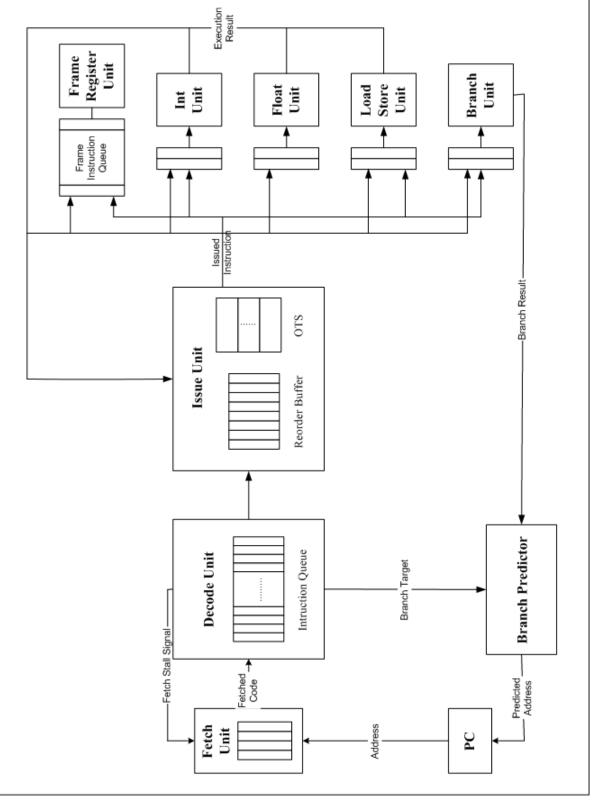

|   | 5.1 | Hardw   | vare - SAFA Simulator                                             | 122 |

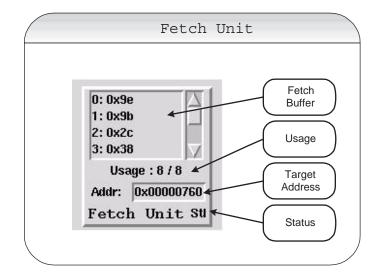

|   |     | 5.1.1   | Fetch Unit                                                        | 125 |

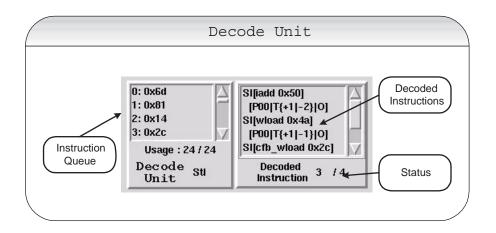

|   |     | 5.1.2   | Decode Unit                                                       | 125 |

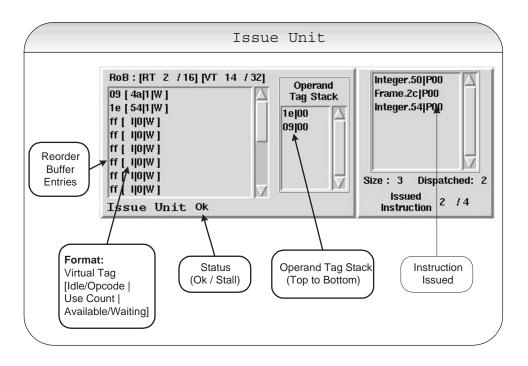

|   |     | 5.1.3   | Issue Unit                                                        | 126 |

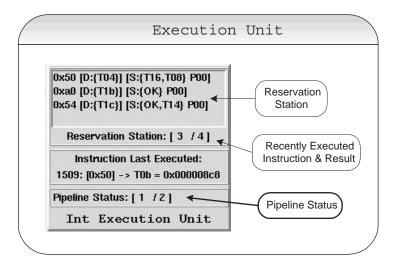

|   |     | 5.1.4   | Execution Units                                                   | 128 |

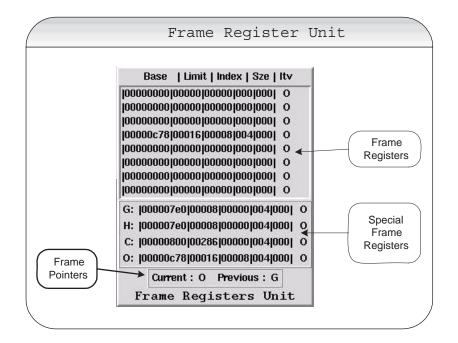

|   |     | 5.1.5   | Frame Registers Unit                                              | 128 |

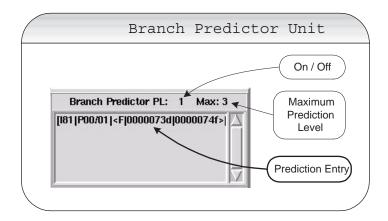

|   |     | 5.1.6   | Branch Predictor Unit                                             | 129 |

|   |     | 5.1.7 Overall System                                                                                                                          |

|---|-----|-----------------------------------------------------------------------------------------------------------------------------------------------|

|   |     | 5.1.8 Verification of SAFA Simulator                                                                                                          |

|   | 5.2 | Software - Assembler and Cross-Assembler                                                                                                      |

|   | 5.3 | Benchmark Programs                                                                                                                            |

|   |     | 5.3.1 Sieve of Erathosthense                                                                                                                  |

|   |     | 5.3.2 Bubble Sort                                                                                                                             |

|   |     | 5.3.3 Fibonacci Series                                                                                                                        |

|   |     | 5.3.4 Quick Sort $\ldots \ldots 140$ |

|   |     | 5.3.5 Test Score Accumulation: Array and List                                                                                                 |

|   |     | 5.3.6 Linpack - Gaussian Elimination                                                                                                          |

|   | 5.4 | Hardware Parameters                                                                                                                           |

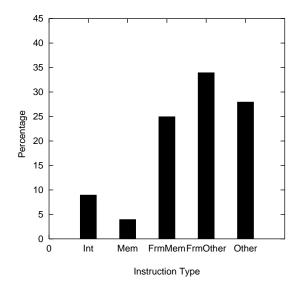

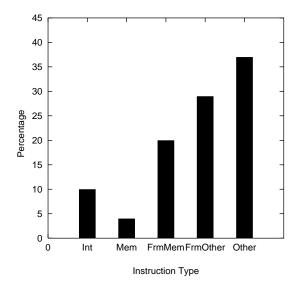

|   | 5.5 | Instruction Type and Execution Time                                                                                                           |

|   |     | 5.5.1 Derivation of Instruction Execution Time                                                                                                |

|   | 5.6 | Summary                                                                                                                                       |

| 6 | Ben | chmark Results 148                                                                                                                            |

|   | 6.1 | Benchmark Notation                                                                                                                            |

|   | 6.2 | High Level Language Support                                                                                                                   |

|   |     | 6.2.1 Data Structure Support: Array                                                                                                           |

|   |     | 6.2.2 Data Structure Support: Array of Records                                                                                                |

|   |     | 6.2.3 Data Structures Support: Linked List                                                                                                    |

|   | 6.3 | Low Level Instruction Support                                                                                                                 |

|   | 6.4 | Various Benchmarks: Single Execution Unit                                                                                                     |

|   |     | 6.4.1  | Fibonacci Series                              | 167 |

|---|-----|--------|-----------------------------------------------|-----|

|   |     | 6.4.2  | Sieve of Erathosthense                        | 171 |

|   |     | 6.4.3  | Bubble Sort                                   | 175 |

|   |     | 6.4.4  | Quick Sort                                    | 177 |

|   |     | 6.4.5  | Linpack: Gaussian Elimination                 | 180 |

|   | 6.5 | Variou | is Benchmarks: Multiple Execution Units       | 184 |

|   |     | 6.5.1  | Bubble Sort                                   | 184 |

|   |     | 6.5.2  | Linpack Benchmark                             | 187 |

|   | 6.6 | Variou | us Benchmarks: Local Data Access Optimization | 190 |

|   |     | 6.6.1  | Fibonacci Series                              | 191 |

|   |     | 6.6.2  | Sieve of Erathosthense                        | 195 |

|   |     | 6.6.3  | Quick Sort                                    | 199 |

|   |     | 6.6.4  | Bubble Sort                                   | 203 |

|   | 6.7 | Concl  | usion                                         | 207 |

| 7 | Top | ical B | enchmarks                                     | 208 |

| ' | тор |        |                                               | 200 |

|   | 7.1 | Large  | Application                                   | 209 |

|   |     | 7.1.1  | Benchmark Result                              | 212 |

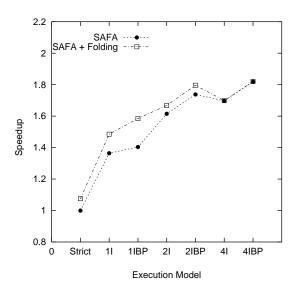

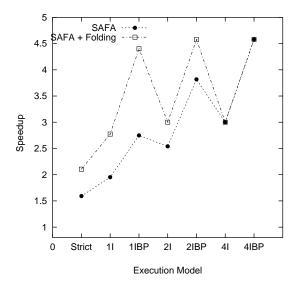

|   | 7.2 | Instru | ction Folding                                 | 215 |

|   |     | 7.2.1  | SAFA vs Instruction Folding                   | 219 |

|   |     | 7.2.2  | SAFA with Instruction Folding                 | 222 |

|   | 7.3 | Gener  | al Purpose Register Machine                   | 225 |

|   | 7.4 | Concl  | usion                                         | 230 |

| CONTENTS |  |

|----------|--|

|          |  |

| 8 | Con  | aclusion                          | 231   |

|---|------|-----------------------------------|-------|

|   | 8.1  | Contribution                      | . 231 |

|   | 8.2  | Future Work                       | . 233 |

| A | ppen | dices                             | 245   |

| A | SAI  | FA Assembly Code and Assembler    | 245   |

|   | A.1  | Frame Register Instructions       | . 247 |

|   | A.2  | Direct Memory Access Instructions | . 251 |

|   | A.3  | Integer Instructions              | . 252 |

|   | A.4  | Floating Point Instructions       | . 254 |

|   | A.5  | Branching Instructions            | . 257 |

|   | A.6  | Stack Manipulation Instructions   | . 261 |

|   | A.7  | SAFA Assembler Introduction       | . 264 |

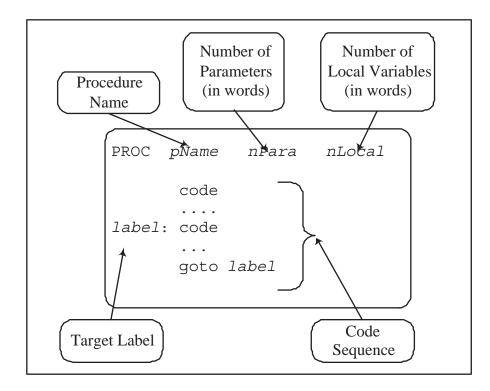

|   |      | A.7.1 Syntax for Procedure        | . 264 |

|   |      | A.7.2 Syntax for Data Values      | . 265 |

|   |      | A.7.3 Built in Assembly Macros    | . 268 |

|   |      | A.7.4 Sample Translation          | . 270 |

|   |      | A.7.5 Using the assembler         | . 271 |

| в | SAI  | FA Simulator                      | 272   |

|   | B.1  | Simulator in Plain Text           | . 272 |

|   |      | B.1.1 Configuration File          | . 274 |

|   |      | B.1.2 Statistic File              | . 274 |

|   |      | B.1.3 Memory Dump and CPU State                  | 279 |

|---|------|--------------------------------------------------|-----|

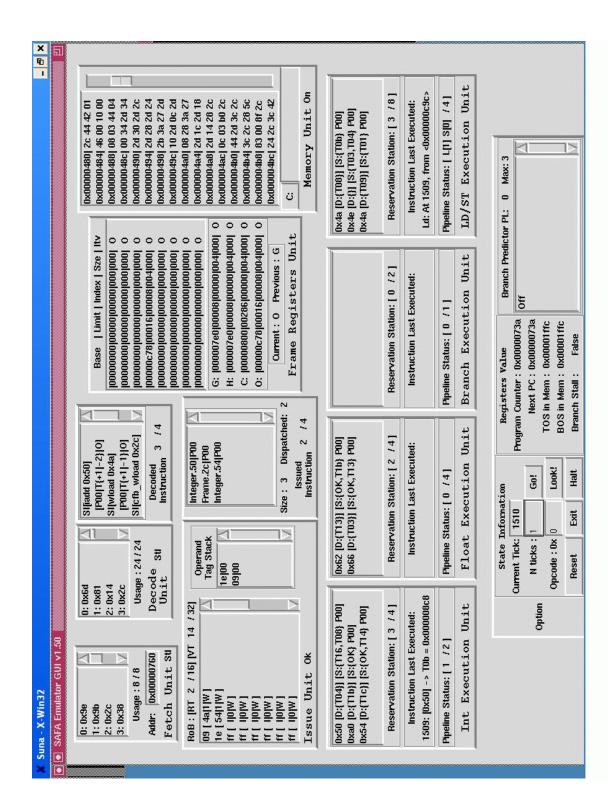

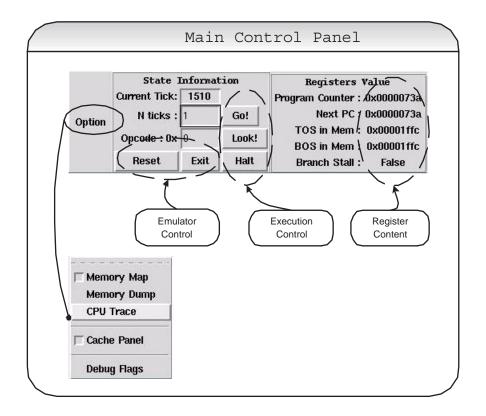

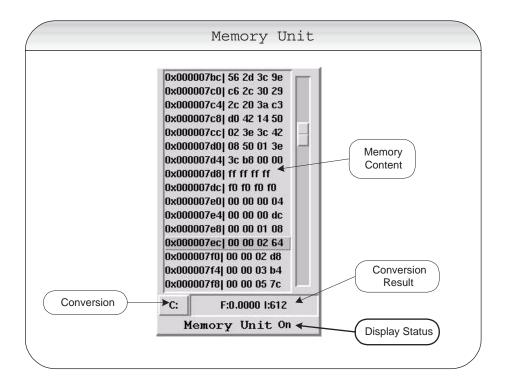

|   | B.2  | Simulator with GUI                               | 281 |

|   |      | B.2.1 Main Control Panel                         | 283 |

|   |      | B.2.2 Components Window                          | 286 |

| С | SAF  | FA Benchmark Programs 2                          | 97  |

|   | C.1  | Sieve of Erathosthense                           | 297 |

|   | C.2  | Bubble Sort                                      | 299 |

|   | C.3  | Bubble Sort: Frame Register Version              | 801 |

|   | C.4  | Fibonacci Series                                 | 803 |

|   | C.5  | Quick Sort                                       | 304 |

|   | C.6  | Student Array: Conventional Array Access         | 806 |

|   | C.7  | Student Array: Frame Register and Index          | 807 |

|   | C.8  | Student Array: Frame Register and Offset         | 808 |

|   | C.9  | Student List: Conventional Linked List Traversal | 809 |

|   | C.10 | Student List: Frame Register and Index           | 310 |

|   | C.11 | Student List: Frame Register and Offset          | 311 |

|   | C.12 | Linpack Benchmark                                | 312 |

# List of Figures

| 1.1  | Tagged Execution Framework.    4                |

|------|-------------------------------------------------|

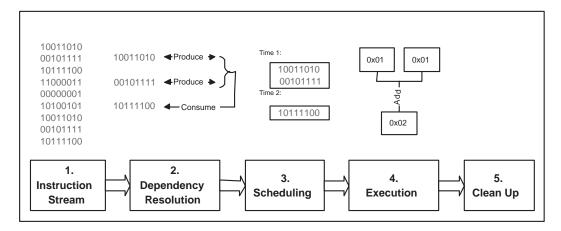

| 3.1  | Dynamic Dispatching in OOLs                     |

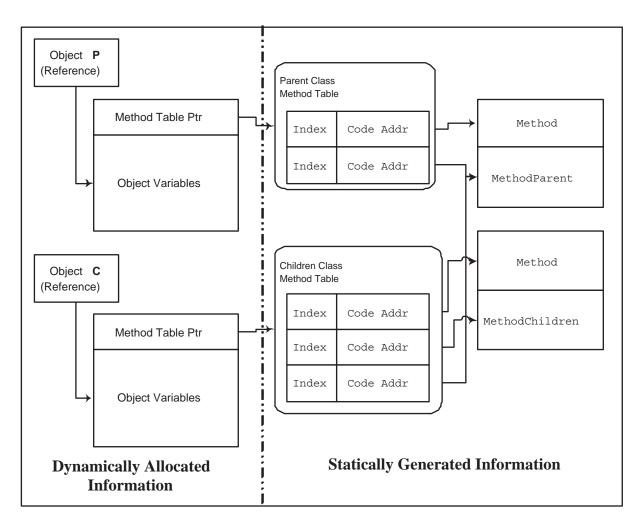

| 3.2  | Object Representation in SAFA                   |

| 4.1  | Simple Architecture without Tomasulo's Scheme   |

| 4.2  | Simple Architecture with Tomasulo's Scheme      |

| 4.3  | Control Dependence Example 1: <i>if-else</i>    |

| 4.4  | Control Dependence Example 2: <i>while</i> loop |

| 4.5  | Prediction Level Example                        |

| 4.6  | Single Level Prediction                         |

| 4.7  | Multiple Level Prediction                       |

| 4.8  | Machine State before Branch                     |

| 4.9  | Machine State at Point A                        |

| 4.10 | Sun Microsystems picoJava Block Diagram         |

| 5.1  | SAFA Components Diagram                         |

| 6.1  | Bubble Sort(50 Numbers): Comparison             |

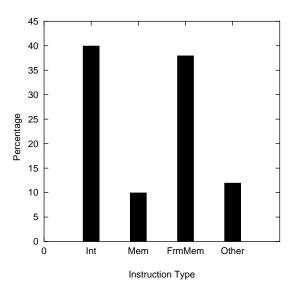

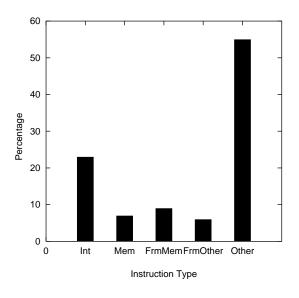

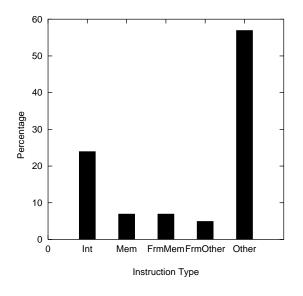

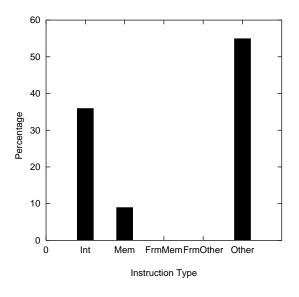

| 6.2  | Bubble Sort(50 Numbers): Conventional Array Access Instruction                                                                 |

|------|--------------------------------------------------------------------------------------------------------------------------------|

|      | Composition                                                                                                                    |

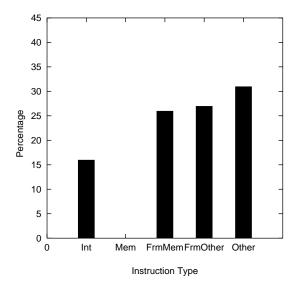

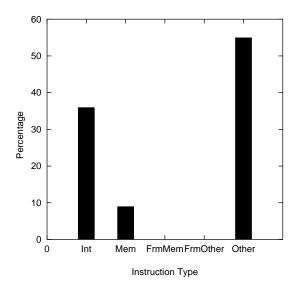

| 6.3  | Bubble Sort(50 Numbers): Frame Registers Version Instruction Com-                                                              |

|      | position                                                                                                                       |

| 6.4  | Student Array (100 Records): Comparison                                                                                        |

| 6.5  | Student Linked List (100 Records): Comparison                                                                                  |

| 6.6  | Fibonacci Series. Fib(10) : Speed Up $\ldots \ldots 170$ |

| 6.7  | Fibonacci Series: Composition                                                                                                  |

| 6.8  | Sieve of Erathosthense (100 Numbers) : Speed Up                                                                                |

| 6.9  | Sieve of Erathosthense: Composition                                                                                            |

| 6.10 | Bubble Sort (50 Numbers) : Speed Up                                                                                            |

| 6.11 | Quick Sort (50 Numbers) : Speed Up                                                                                             |

| 6.12 | Quick Sort: Composition                                                                                                        |

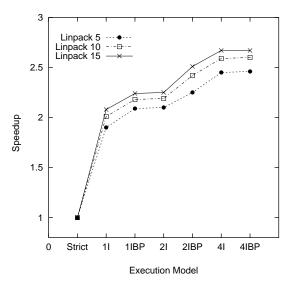

| 6.13 | Linpack Benchmarks : Speed Up                                                                                                  |

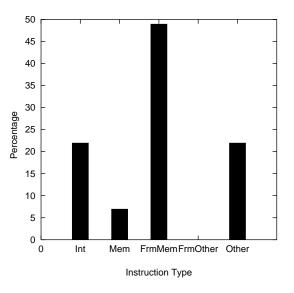

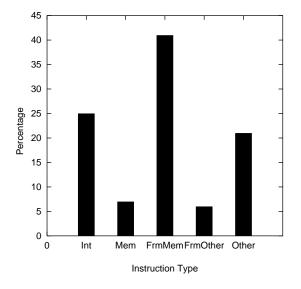

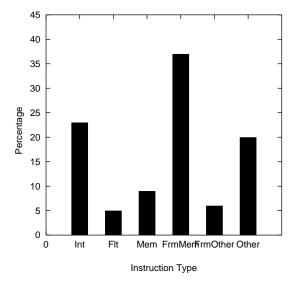

| 6.14 | Linpack Benchmarks: Composition                                                                                                |

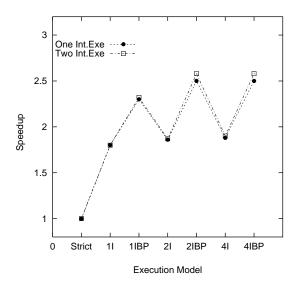

| 6.15 | Bubble Sort (50 Numbers) : Multiple Execution Units - Speed Up                                                                 |

|      | Comparison                                                                                                                     |

| 6.16 | Linpack Benchmark (15 x 15): Multiple Execution Units - Speed Up                                                               |

|      | Comparison                                                                                                                     |

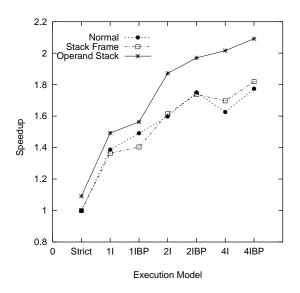

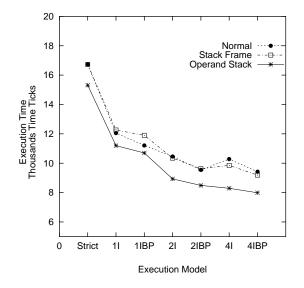

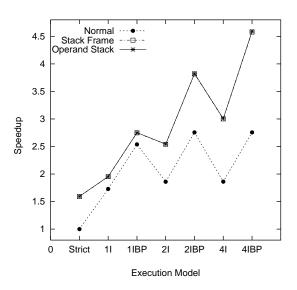

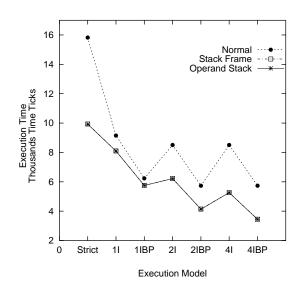

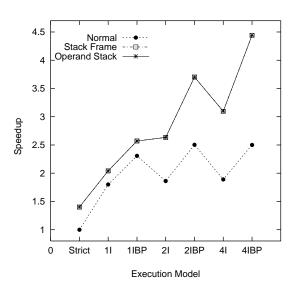

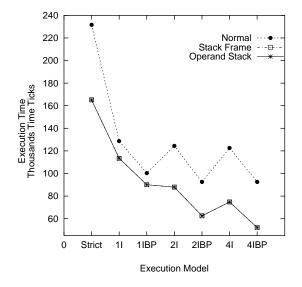

| 6.17 | Fibonacci Series: Local Variable Access - Speed Up Comparison $\ . \ . \ . \ 192$                                              |

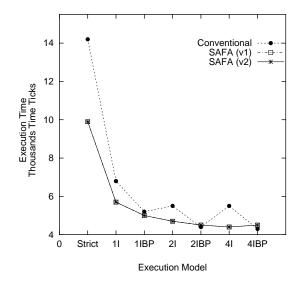

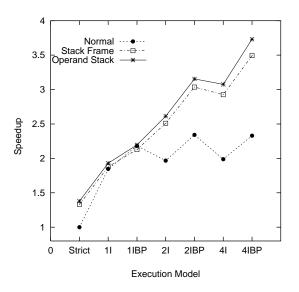

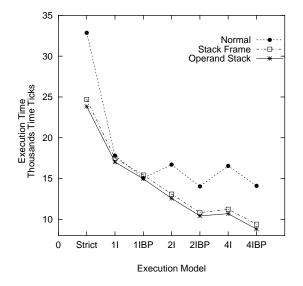

| 6.18 | Fibonacci Series: Local Variable Access - Execution Time Comparison 192                                                        |

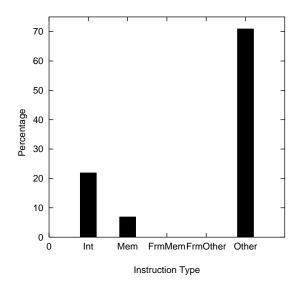

| 6.19 | Fibonacci Series: Local Variable Access (Stack Frame) Instruction                                                              |

|      | Composition                                                                                                                    |

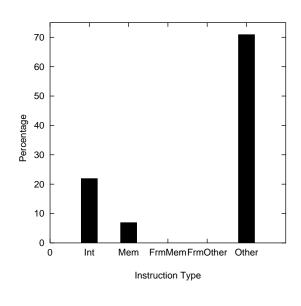

| 6.20 | Fibonacci Series: Local Variable Access (Operand Stack) Instruction     |

|------|-------------------------------------------------------------------------|

|      | Composition                                                             |

| 6.21 | Sieve of Erathosthense: Local Variable Access - Speed Up Comparison 195 |

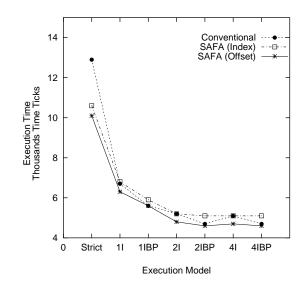

| 6.22 | Sieve of Erathosthense: Local Variable Access - Execution Time Com-     |

|      | parison                                                                 |

| 6.23 | Sieve of Erathosthense: Local Variable Access (Stack Frame) Instruc-    |

|      | tion Composition                                                        |

| 6.24 | Sieve of Erathosthense: Local Variable Access (Operand Stack) In-       |

|      | struction Composition                                                   |

| 6.25 | Quick Sort: Local Variable Access - Speed Up Comparison 200             |

| 6.26 | Quick Sort: Local Variable Access - Execution Time Comparison 200       |

| 6.27 | Quick Sort: Local Variable Access (Stack Frame) Instruction Com-        |

|      | position                                                                |

| 6.28 | Quick Sort: Local Variable Access (Operand Stack) Instruction Com-      |

|      | position                                                                |

| 6.29 | Bubble Sort: Local Variable Access - Speed Up Comparison 204            |

| 6.30 | Bubble Sort: Local Variable Access - Execution Time Comparison 204      |

| 6.31 | Bubble Sort: Local Variable Access (Stack Frame) Instruction Com-       |

|      | position                                                                |

| 6.32 | Bubble Sort: Local Variable Access (Operand Stack) Instruction          |

|      | Composition                                                             |

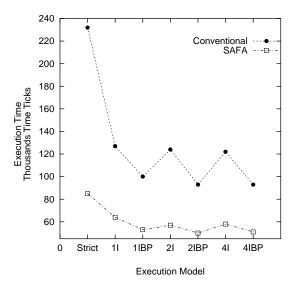

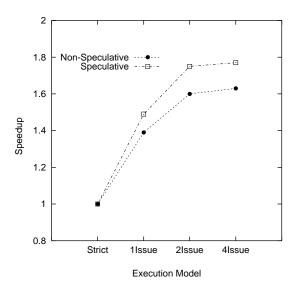

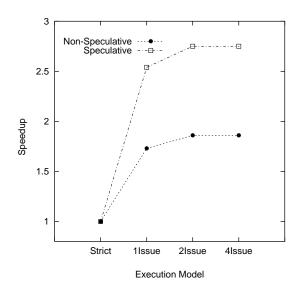

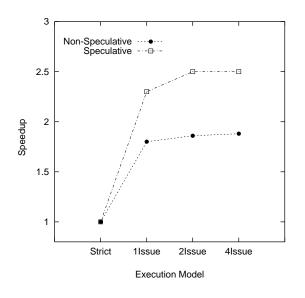

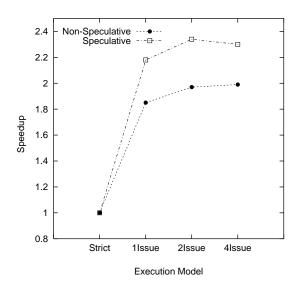

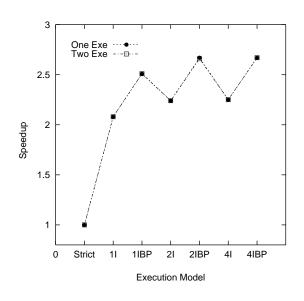

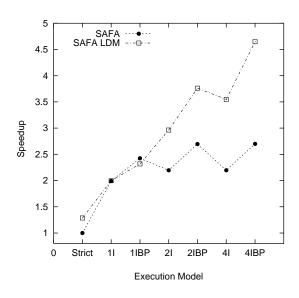

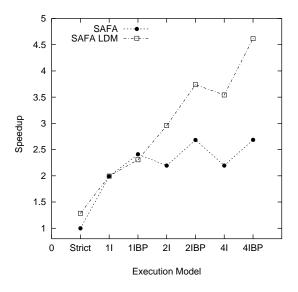

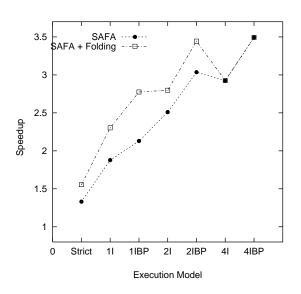

| 7.1  | Compress (4000 bytes Text) - Speed Up Comparison                        |

| 7.2  | Compress (8 kbytes Binary) - Speed Up Comparison                        |

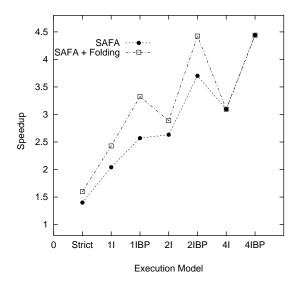

| 7.3  | Fibonacci Series : SAFA with Folding - Speed Up                         |

| 7.4  | Sieve of Erathosthense: SAFA with Folding - Speed Up |

|------|------------------------------------------------------|

| 7.5  | Quick Sort: SAFA with Folding - Speed Up             |

| 7.6  | Bubble Sort: SAFA with Folding - Speed Up            |

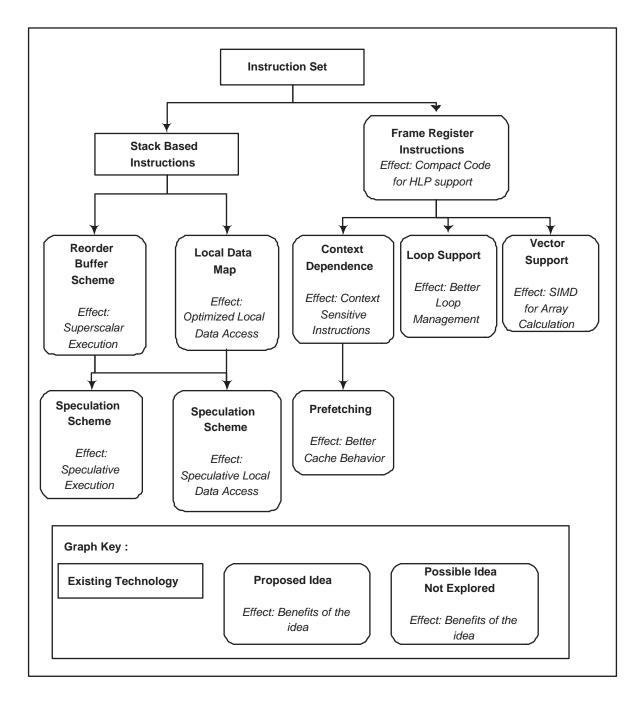

| 8.1  | Ideas Relationship in SAFA                           |

| A.1  | Syntax for a Procedure in SAFA Assembly Code         |

| A.2  | Layout of a Procedure Stack Frame                    |

| B.1  | Sample Configuration File                            |

| B.2  | Sample Statistic File (Part1)                        |

| B.3  | Sample Statistic File(Part2)                         |

| B.4  | Sample Statistic File (Part 3)                       |

| B.5  | Sample Memory Dump File (Partial)                    |

| B.6  | Sample CPU Trace File (Abridged)                     |

| B.7  | SAFA Simulator GUI v1.5 Screen Shot                  |

| B.8  | Main Control Panel GUI                               |

| B.9  | Fetch Unit GUI                                       |

| B.10 | Decode Unit GUI                                      |

| B.11 | Issue Unit GUI                                       |

| B.12 | Frame Register Unit GUI                              |

| B.13 | Branch Predictor Unit GUI                            |

| B.14 | Execution Unit GUI                                   |

| B.15 | Memory Unit GUI                                      |

# List of Tables

| 4.1  | Speculative Consumption of Result                                           |

|------|-----------------------------------------------------------------------------|

| 4.2  | Confirmation of Prediction PL $j$                                           |

| 4.3  | Handling Misprediction at PL $j$                                            |

| 6.1  | Bubble Sort 50 Numbers: Conventional Array Access                           |

| 6.2  | Bubble Sort 50 Numbers: Using Frame Register                                |

| 6.3  | Student Array (100 records) Benchmark: Conventional Array Access 157        |

| 6.4  | Student Array (100 records): Using Frame Register (version 1) 157           |

| 6.5  | Student Array (100 records): Using Frame Register (version 2) 158           |

| 6.6  | Student Linked List (100 records): Conventional Linked List Traversal 163   |

| 6.7  | Student Linked List (100 records): Using Frame Register and Index $$ . 163  |

| 6.8  | Student Linked List (100 records): Using Frame Register and Offset . 164 $$ |

| 6.9  | Fibonacci(10) = 55. Total Recursive Calls = $177 \dots 169$                 |

| 6.10 | Sieve of Erathosthense: 100 Numbers                                         |

| 6.11 | Quick Sort: 50 Numbers. Total Recursive Calls = $43  \dots  \dots  179$     |

| 6.12 | Linpack(5): Solve 5 x 5 floating point matrix using Gaussian Elimi-         |

|      | nation                                                                      |

| 6.13       | Linpack(10). Solve 10 x 10 floating point matrix using Gaussian<br>Elimination |

|------------|--------------------------------------------------------------------------------|

| 6.14       | Linpack(15). Solve 15 x 15 floating point matrix using Gaussian<br>Elimination |

| 6.15       | Bubble Sort (50 Numbers): Multiple Execution Units - Comparison . 186          |

| 6.16       | Linpack Benchmark (15 x 15): Multiple Execution Units - Comparison<br>189      |

| 6.17       | Fibonacci Series : Local Variable Access - Comparison                          |

| 6.18       | Sieve of Erathosthense: Local Variable Access - Comparison 197                 |

| 6.19       | Quick Sort: Local Variable Access - Comparison                                 |

| 6.20       | Bubble Sort: Local Variable Access - Comparison                                |

| 7.1        | Compress (4000bytes Text): Summary                                             |

| 7.2        | Compress (8kbytes Binary) - Summary                                            |

| 7.3        | Folding Benchmarks without LDM: Summary                                        |

| 7.4        | Folding Benchmarks with LDM: Summary                                           |

|            |                                                                                |

| 7.5        | SAFA vs Instruction Folding (without LDM): Summary                             |

| 7.5<br>7.6 | SAFA vs Instruction Folding (with LDM): Summary                                |

|            |                                                                                |

| 7.6        | SAFA vs Instruction Folding (with LDM): Summary                                |

## Chapter 1

## Introduction

"The number of transistors on an Integrated Chip will double every 18 months.", these are the words of the widely known *Moore's Law*<sup>1</sup> due to Gordon Moore in 1965. This observation, amid doubts and speculations, has held true for several decades, witnessing exponential growth of both component count and structural complexity of electronic chips. As an example, consider the first fully-electronic programmable computer *ENIAC* in 1940s, which had a mammoth foot print of 9 by 15 meters. Nowadays, even a handheld calculator of 9 by 15 *centimeters* has more computing power.

However, the ability to cramp more components into an ever decreasing space was only partially responsible for the increase in computing power. Transistors are just the raw building material that must must be harnessed into a meaningful design. Computer architecture completes the picture by imposing the structure on the raw components for better and more efficient computation, which usually takes the form of a set of machine instructions.

The execution of a machine instruction in a Von Neumann Machine<sup>2</sup> is frequently compared to a production line in the real world, for example, the automobile

<sup>&</sup>lt;sup>1</sup>One of the many formulations.

$<sup>^{2}</sup>$ Computer with independent but interconnected memory and execution unit

#### CHAPTER 1. INTRODUCTION

assembly line. Just as a car undergoes several assembly stages, an instruction goes through several well defined stages as well, generally:

- 1. Fetch: To bring an instruction from the memory store into the execution core.

- 2. **Decode:** Determine the operation(s) to be performed as indicated by the instruction.

- 3. **Execution:** Execute the operation(s) required.

- 4. Write Back: The result of the execution is recorded.

The similarity between the real world assembly line and the minute one in the Central Processing Unit allows many useful techniques to be shared. One good example would be the pipeline process. By splitting the procedure of car assembling into several stages, multiple cars at various stages can be worked on at the same time. Consider a simple scenario: a car assembly line with four stages where each stage takes one day can be expected to finish 12 cars in 15 days.

However, the pipelining in CPU does not yield such a speed up usually. There are two main reasons:

- Inter-Dependency between Instructions: Unlike individual cars on the assembly line, machine instructions are usually inter-related. For example, an instruction may depend on the previous one for producing the needed data. In this case, the latter instruction must wait until the former instruction is executed before proceeding. Such relations restrict the order of the execution as well as impose delays in execution, and prevent many parallelizing techniques from running at full steam.

- 2. Limited Resources: Because of resource limitations, a CPU may not be able to accommodate more instructions running at the same time. These resources include registers (or similar structures to hold data), execution units, etc.

A large number of techniques have been proposed to mitigate these restrictions. The famous Tomasulo's Scheme [38] was proposed to enable dynamic scheduling of instructions, thereby curbing the dependency problem mentioned. By renaming registers (also known as tagging), the operands and result of an instruction are associated with a tag (or virtual register number) instead of a real physical register. Since real physical registers now can be utilized more freely by having different tags as needed, resource dependency problems would be less frequent. With dynamic scheduling and register renaming, it is now possible to process (issue) more than one instruction in a clock cycle. This technique has been the backbone for quite a number *superscalar* (multi-issue) architectures. Although the Tomasulo's Scheme requires relatively complicated hardware implementation, little special attention is needed from compilers.

Reminiscent of the heated debate of  $RISC^3$  and  $CISC^4$  in the 80's, another approach that requires more sophisticated compilers but relatively simple hardware has been proposed. The Very Long Instruction Word (VLIW) architecture depends on the compiler to extricate (disentangle) inter-dependent instructions and group independent instructions into a parallel package (also known as an instruction word/bundle). Since there is no dependency between instructions in a package, they can be executed simultaneously without further checking. As succinctly put by the Online Byte Magazine, "VLIW is basically a software- or compiler- based superscalar architecture."

The two approaches mentioned spark off enthusiastic research into the respective areas with abundant results. At first glance, they seem quite different from each other, with distinct emphasis on separate part of the instruction execution. However, we feel that it would be beneficial to put them under a common cohesive framework. This conceptual framework is presented in the next section.

<sup>&</sup>lt;sup>3</sup>Reduced Instruction Set Computer

<sup>&</sup>lt;sup>4</sup>Complex Instruction Set Computer

## 1.1 General Tagged Execution Framework

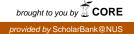

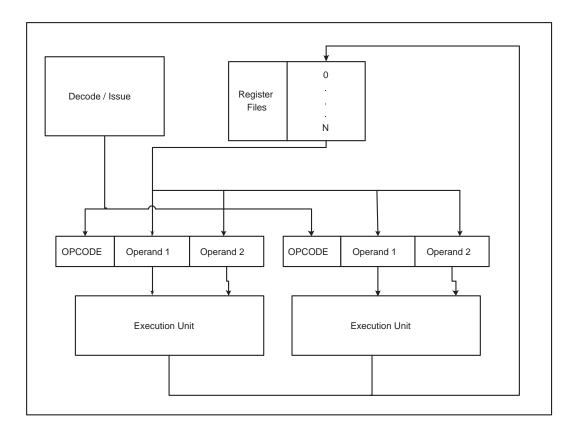

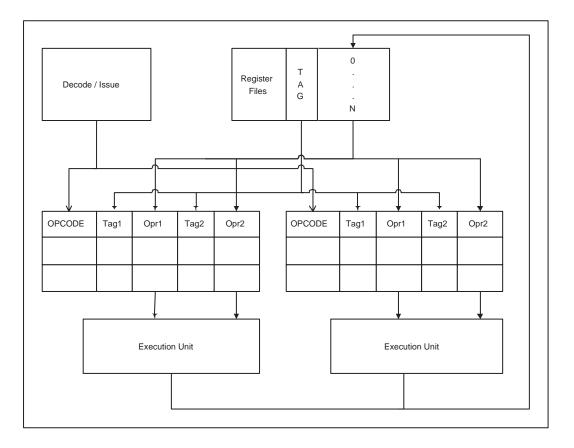

By extracting the commonality between the approaches, we find that there is a underlying common conceptual framework, as shown in the Figure 1.1.

Figure 1.1: Tagged Execution Framework.

As can be seen in the framework, we start with a stream of instructions in stage one going into the framework. Instruction dependency checking is performed in stage two. Producer instructions pick up a fresh tag to identify their future results, while consumers instructions collect operands (identified by tags). Instructions can be said to have lost their original form at this stage, and become a more general execution package, which describes a manipulation based on tags. In stage three, an execution package that is considered ready based on a set of criteria get scheduled. The readiness criteria can differs from system to system. The actual execution happens in stage four. Finally, in stage five, execution results will be stored, tags and other resources will be released.

This conceptual framework captures quite a number of existing computer architectures. Since one or more stages preceding the execution stage in the figure above can be implemented either in hardware or software, a number of interesting models arise. For example, for a superscalar (multi-issue) machine that employs Tomasulo's Scheme (e.g. PowerPC, Alpha), the second and third stage would be implemented by a Reorder Buffer and Common Data Bus in hardware and the fourth stage would be a superscalar pipelined execution engine.

For a VLIW architecture, (e.g. IA64 EPIC), the second and third stage would be performed in software (the compiler), with limited scheduling in hardware and the fourth stage would be a EPIC execution engine to process instruction bundles. A dynamically scheduled VLIW machine would have both 2nd and 3rd stage in hardware, with an EPIC-like execution engine.

Also, it is interesting to note that the type of instruction set *does not* matter in this framework. As instructions pass through the tagging stage and are transformed into an execution package as described previously, similar techniques at the later stages are equally valid. Traditionally, different types of instruction set (commonly known as 0-, 1- and 2- operands instructions) requires their own specialized hardware for execution. With this framework, however, it is possible to consider the possibility of utilizing previously used techniques on a wide range of instruction sets, all producing tagged instructions that produce/consume data via virtual registers.

Based on this observation, we decided to study the feasibility of applying tagging to the stack-oriented instruction set. The benefits for this choice are two fold:

- Traditionally, stack-oriented machines suffered the most under the problems mentioned. The fading of stack machines from the computer architecture scene can be largely attributed to the fact that stack machines fail to incorporate new parallelizing techniques devised for other platforms.

- 2. Recent popularity of the programming language Java and its underlying virtual machine (JVM), which is a stack based machine, have rekindled interest in this area.

With this in mind, we introduce the Stack And Frame Architecture, SAFA.

### 1.2 The SAFA Architecture

Traditionally, a pure stack-based instruction set is also known as the 0-address or 0operand instruction set. As opposed to the general-purpose register instruction set, where the operands of an operation (stored in registers) are stated explicitly in the instruction, or the accumulator instruction set, where one of the operands is stated explicitly and the other is assumed in the accumulator implicitly, the stack-based instruction set assume that the operands exist on a stack and consequently does not carry any explicit operand[1].

In the 70s, when main memory storage was a scarce and expensive resource, stack based machines enjoyed popular acceptance because of the compact binary code produced. Besides, the stack is also a natural data structure used frequently in high-level programming language (HLP) execution, e.g. activation records of procedural languages, simple variable scoping etc. However, the limitation of stack machines become apparent when better and more efficient instruction execution techniques, like superscalar execution, pipelining etc were found to be inapplicable. In [27], the limitation of the stack machine is summarized as:

The stack oriented architectures .... has passed from the scene because it is difficult to speed execution of such a processor because the stack pointer manipulations become a bottleneck.

The other major disadvantage of the stack instruction set is the poor execution support for data structure, for example array indexing. Since the array is one of the most frequently used data structures, inefficient support of these operations seriously handicaps the stack architecture.

However, recent development in the field shows that a stack architecture still has its attractiveness. For example, *Java*, one of the fastest growing programming languages, is implemented on top of a virtual machine, the *Java Virtual Machine (JVM)*[14]. The designers have chosen the stack architecture for the *JVM*  because of the simplicity in design as well as the compact binary size produced[13]. Hardware implementation of JVM, the *picoJava*[10][11] architecture, shows that it is possible to overcome some of the inherent disadvantages of a stack architecture.

For our project, we have devised a set of mechanisms that concentrate on the two following areas:

#### 1. High Level Language Support:

- Instructions with hardware support for HLP execution, especially subroutine entrance and exit, variable scoping and stack frame accesses.

- Improved data structure and control flow support for HLP.

#### 2. Low Level Instruction Support:

- Hardware stack structure that uses tagged execution to support Instruction Level Parallelism, ILP.

- Speculative execution of stack instructions.

- Retention of frequently accessed data in CPU core to minimize memory access.

Although these ideas/mechanisms are mostly self-contained and applicable to other suitable architectures, we need a flexible independent platform to introduce *all* of them for experimentation. The SAFA architecture is thus designed as a means to experiment with the ideas mentioned, as well as to study the interaction between them. Detailed explanations will be given in the relevant chapters, according to the categorization above: High Level Language support in Chapter 3, and Low Level Instruction execution in Chapter 4.

## 1.3 Objectives of Our Work

We shall see that the ideas in *SAFA* architecture are able to overcome the weaknesses of stack architectures, while strengthening the advantages. These mechanisms would be able to provide:

- 1. Good instruction level parallelism without the heavy compiler optimization usually needed in GPR machines.

- 2. Good support for high level programming languages, including procedure activation and array indexing.

- 3. More expressive instructions that allow compact binary code size.

- 4. Optimized local data access.

The SAFA architecture, as a complete package, has the following advantages:

- 1. General purpose yet providing hardware alternative to the Java Virtual Machine.

- 2. A possible choice as an embedded processor because of its good performance with simple hardware implementation and compact binary size.

Also, by showing that tagging stack-based instructions within a more general architecture, the usefulness of the general execution framework proposed in the last section could be established. With this framework in place, more cohesive studies of the topic can be made in the future.

## 1.4 Overview of Thesis

An overview of the remaining chapters in this thesis is given below:

- Chapter 2 Gives a short related literature survey.

- Chapter 3 Discusses the ideas we adapted in SAFA to improve high level language support.

- Chapter 4 Explains the ideas we adapted to improve low level execution of stackoriented instructions.

- Chapter 5 Lay out the setup of the benchmarking.

- Chapter 6 Presents the benchmark results of the SAFA simulator. Several representative programs are executed to exploit the various new hardware features.

- Chapter 7 Presents several topical benchmark studies to provide a broader perspective.

- Chapter 8 Concludes the thesis by summarizing the contribution of work done.

Possible future continuation work is also discussed.

## Chapter 2

## Literature Survey

## 2.1 Introduction

This chapter summarizes the literature survey we have done as related to our research proposal. The methodology as well as the objectives of the survey is given in the Section 2.2. Detailed information for each of the included machines is presented, along with comparison of our proposed alternative. A brief conclusion that summary of the survey is presented in Section 2.5.

## 2.2 Objectives

As mentioned in Chapter 1, in addition to studying the general applicability and potential of a tagged execution, our project also aims to research the possibility and feasibility of designing a stack machine that is efficient at the instruction set level and provides good support for executing high level programming languages. Hence, a survey on past machine architectures would serve as both guideline and comparative framework for our design. With this in mind, we have cast our net into the past few decades to study a few architectures that have one or more of the following features:

- **0-Address Instruction Set** As stated in [1], 0-address instruction set machine, which is usually considered as the pure stack machine, utilizes a stack for evaluating expressions. Most instructions assume the operands needed for carrying out the operations reside on a stack (whether in CPU hardware or memory). This makes stack machines very different from general purpose registers machines.

- High Level Language Support As early as the 1970s, designers of machine architecture have realized the importance of good support for executing high level language programs[6]. Efficient instruction level execution cannot guarantee good overall performance of a CPU, if the support for high level language construct likes variable scoping, method/function invocation, information hiding/protection etc is lacking or poorly implemented.

- Superscalar Register Based Machine If tagging can be applied to stack-oriented instructions, it is argued in Chapter 1 that normal execution mechanism and technique employed in register-based machines may be equally applicable to our design. It would be useful to study a few typical register-based superscalar machines to look for useful structure and/or technique.

The case studies will be grouped into:

- 1. Stack based machine, reported in Section 2.3.

- 2. Register based machine, reported in Section 2.4.

## 2.3 Stack Based Architecture

Information for stack machines proved to be scarce, mainly due to fact that stack machine has fallen out of the mainstream architectures for the past few decades. Four machines have been selected for our study.

#### 2.3.1 Burroughs Family B5000-B6700

#### History

Brief Information: Developed by Burroughs Corporation, starting in 1961 (for B5000)[8].

Design of Instruction Set: Pure stack instruction set which takes 0 operand for most of the instructions.

#### **Features of Processor Architecture**

- Display registers to keep track of the activation records to reflect the current lexical scope of executing program. Facilitates non-local variable accessing.

- 4 registers to store top of stack data.

- Top and base of stack tracked by registers.

#### High Level Programming Language Support

- Influenced by Algol60 and Cobol.

- Operating System support. E.g. Linked-list search instruction, for ease of memory management, interrupt handling mechanism.

- Tagged Memory words that describe type/meaning of a memory word, facilitate Memory Protection.

- Descriptors that can used for array access mechanism and hardware bound checking. Also simplifies dynamic array allocation.

- Activation records stored on stacks. Both static and dynamic links are kept as a linked list and maintained by hardware when procedure is entered/exited to facilitate access to parent/caller information.

- Virtual Memory Support.

- Multitasking support.

- Data Structure support.

- Allows efficient process splitting/spawning (B6500/B7500), by establishing and maintaining a tree structure that stores multiple stacks (the Saguaro Stack System). Two independent jobs/process can share part of same stack.

#### 2.3.2 Hewlett-Packard HP3000

#### History

Brief Information: Developed by Hewlett Packard, in 1976[27][9].

Design of Instruction Set:

- Takes in 1 operand and assume the other operands (if any) reside on stack. Can be considered a stack/accumulator hybrid.

- A number of addressing modes.

- A few instructions that does not conform to the stack paradigm (e.g. allowing execution results to be stored directly to memory etc).

- Does not give direct access to variables declared in enclosing blocks.

#### High Level Programming Language Support

- Influenced by Algol60 and Burroughs Family.

- Registers to keep track of stack (top of stack in memory, top of stack in registers etc).

- General linked list traversals instruction provided.

- Activation records kept as stack.

#### 2.3.3 Intel iAPX432

#### History

Brief Information: Developed by Intel Corporation, in Year 1981[7].

Design of Instruction Set:

- No user addressable registers.

- Instruction fetches its input operands offset from an object (in Memory).

- 0-3 operands, expressed in 2 parts: object selector + displacement.

- Expression evaluation carried out on operand stack.

#### High Level Programming Language Support

- Influenced heavily by Ada

- Based on the observation that HLP relies heavily on a particular data structure, the directed graph. E.g. Object is a node, and reference to object is an arc to this node. Implements directed graph (akin to linked list) in hardware design.

- Object-oriented representation for program execution. Several key types of object below.

- Compiled code information encapsulated by a Domain Object.

- Context of a executing procedure, includes information of addressing info (scoping), operand stack for expression evaluation, static link (enclosing block of scope), dynamic link (caller's context) etc.

- A doubly linked list of context objects is maintained, with functionality similar to activation records.

- Process Object to store information of execution state of a program, so as to facilitate suspension and resumption of process easily.

- CPU internal registers to hold the current process, context, domain object descriptor for efficient access.

- Access rights are embedded in object descriptor and enforced by hardware.

- Refinement Object that implements public/private property of object attributes.

- Caters mainly for the Ada programming language, which organize program into package (similar to class in OOP). Supports easy implementation of OOP languages.

#### 2.3.4 INMOS transputer

#### History

Brief Information: Developed by INMOS (now ST Microelectronics), starting from 1984[62][39]. A number of models were developed, which can be categorized into three groups:

1. 16-bit T2 series

- 2. 32-bit T4 series

- 3. 32-bit T8 series with 64-bit IEEE 754 floating-point support

#### Design of Instruction Set:

- 8 bits RISC instruction set with 4 bits opcode and 4 bits operand.

- Can be extended by interpreting the operand as extra opcode bits.

#### **Features of Processor Architecture**

- A single transputer consists of a RISC sequential processor, on chip memory and a 4-ways inter-processor communication system.

- Multiple transputer can be connected in different topology to form parallel system.

- Only 3 general registers A, B and C, which are treated as stack by the instruction set (A is the stack top). Arithmetic operations are performed using A and B implicitly.

- Other than general registers, there are also a workspace memory pointer, an instruction pointer and an operand pointer which refers to the on chip memory.

- High speed on chip memory helps to overcome the limited number of general registers in the INMOS transputers.

#### High Level Programming Language Support

- Intended to be programmed by the OCCAM programming language.

- Occam supported concurrency and channel-based inter-process or inter-processor communication as a fundamental part of the language.

• As such, the INMOS transputers are designed specifically with this language in mind [62].

#### 2.3.5 Java Virtual Machine and picoJava implementation

#### History

JVM is the virtual machine designed by Sun Microsystem to execute Java byte code programs independently across different platforms. So far, two hardware implementations have been produced by Sun Microsystem[10][11]. There are a number of hardware extensions in recent years, for example, the ARM Jazelle[63], which have moderate success in embedded devices.

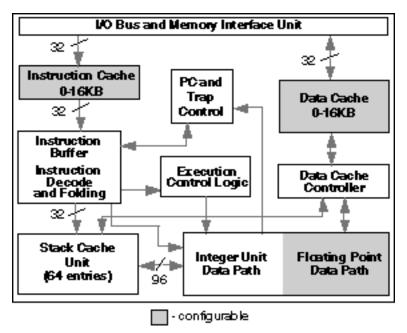

Brief Information: Developed by Sun Microsystem, in 1997 (picoJava I) and 1999 (picoJava II).

#### **Processor Architecture**

Design of Instruction Set:

- Pure 0-address instruction set.

- All instructions except memory load/store instructions take 0 data addresses and operate on top of stack.

- Specific set of instructions for different data types.

- Provides instructions that access local variables in a block directly.

- A few fairly high level instructions to facilitate method invocations.

- Byte size (8 bits).

Design of CPU:

- 6 stage pipeline with 64 entry stack cache

- Instruction folding for top of stack operations, to improve speed and efficiency.

- Hardware stack drizzle unit to load/store part of memory from/to memory automatically.

- Most common used instructions in hardware, complex instructions are microcoded. Only a few very complicated ones trapped and emulated in software.

#### High Level Programming Language Support

- Designed specifically for JAVA

- Thread synchronization, garbage collection support in hardware.

- Supports method invocation and hiding of loads from local variables.

- Utilizes stack frame to store information about executing threads, acts as activation record.

- Operand stack size is pre-calculated and space is allocated in stack frame to facilitate suspension/resumption of threads.

- Above items gives good support to OOP in general.

#### 2.3.6 Conclusion

Stack machines surveyed showed a few common trends:

- Stack structure is very good at supporting certain high level programming language constructs, e.g. variables scoping, function/procedure entrance/exit.

- Although receiving praise (especially from the academic field), stack machines generally perform poorly in actual sales. For example, the Intel iAPX432 was

considered as the "machine of the future" by many [7], but it failed badly to sell. This is mainly due to the fact that stack machines are much more complicated than other machines, which usually shows in slow product development, higher price and/or poorer performance.

Because of the complexity and difficulty in speeding the execution of stack instructions, most machine architecture designers prefer the alternative design (e.g. general purpose register architecture). In those architectures, dependency detection, pipelining, super scalar execution of instructions can be done much more easily[27].

## 2.4 Register-Based Superscalar Architecture

Since Register-Based Architectures has been the mainstream for almost as long as the history of computer architecture, a huge number of processor designs have been proposed and implemented. To narrow our search, we only concentrate on architectures that are:

- **RISC-Based** RISC-based architecture has the added advantage of simple and uncluttered design compared to CISC based architecture. This allows us to concentrate on the main features that are relevant.

- **Superscalar** We have chosen to implement a superscalar stack machine. Naturally, superscalar architecture will provide us with important ideas.

- **Speculative** Another well-developed idea on register based architecture, which would shed light on our design.

- Long Life Quite a number of architectures simply fade out of the main stream after a short period of time. Though not necessarily being the best designs, long lived processor families also allow us to compare each successive generation to see the evolution of certain ideas.

#### 2.4.1 Alpha Family

#### History

The **DEC Alpha** (also known as **Alpha AXP**) is a 64-bit RISC microprocessor originally developed and fabricated by Digital Equipment Corp (DEC). This architecture family is frequently touted as the proof of superiority of manual design as opposed to automated design. The Alpha chips consistently showed that manual design can lead to a simpler and cleaner architecture [39]. Besides, the **Alpha AXP** also posted excellent performance that is almost unrivaled in its generation [20]. A cluster of 4096 Alpha Processors currently (2004) powers the 6th fastest supercomputer in the world [26]. Sadly, the Alpha AXP family tree is finally ended at **EV7** in year 2004, where **HP** (who bought Compaq, which in turn bought DEC) officially announced the end of production line.

The DEC Alpha family includes the following chips (excluding chips that were never fabricated and minor variations):

- 1. Alpha 21064 (EV4) in Year 1992.

- 2. Alpha 21164 (EV5) in Year 1995.

- 3. Alpha 21264 (EV6) in Year 1998.

- 4. Alpha 21364 (EV7) in Year 2003.

This survey is mainly based on the older and simpler Alpha 21164.

#### **Processor Architecture**

The main features of the Alpha AXP Architecture is summarized in [17] as a scalable RISC architecture, supporting 64-bit addresses and data types, and deeply pipelined, superscalar designs that operate with a very high clock rate. The AXP designers strive for simplicity over functionality, such as eliminating branch delay slots, register windows etc, in exchange for efficient superscalar implementation.

#### Alpha 21164

The 21164 pipeline length varies from 7 stages for integer execution to 9 stages for floating point execution, up to 12 stages for on-chip memory access and a variable number of additional stages for off-chip memory access [18]. The first 4 stages (known as instruction pipeline in AXP architecture) which deals with instruction decoding and issuing, are the same for all instructions. Since we are interested in Superscalar technique, this would be the part that we concentrate on.

Stage S0 (the first stage in the instruction pipeline) fetches a blocks of four instructions from instruction cache and performs preliminary decoding. Stage S1 mainly checks for flow control instruction (branching, subroutine enter/exit), calculates the new fetch address and updates the instruction cache accordingly.

In stage S2, instructions are steered to an appropriate function unit, a process called *instruction slotting*[19]. The slotter process can slot all four instructions in a single cycle if the block contains a mix of integer and floating point instructions that can be issued together. In other word, this stage resolves all structural hazards and issues as many as possible instruction to Stage S3. The slotting appears to be similar to the VLIW packaging process, albeit the former is dynamic, the latter static.

Stage S3 performs dynamic conflict checks on the set of instructions advanced from S2. Basically, this stage contains a complex register scoreboard to check for read-after-write and write-after-write register conflicts. This stage also detects function-unit-busy conflicts.

#### Alpha 21264

According to [21], Alpha 21264 has similar stages to Alpha 21164. However, there are a few notable differences. First, register renaming is deployed to expose instruction parallelism. This is stated as the fundamental to the 21264's out-of-order techniques.

Also, advanced branch prediction is added. A number of branch predictions methods are known that work pretty well. However, the accuracy of prediction is not universal and different algorithms work well on different types of branches. Hence, instead of using a fixed prediction algorithm, the **21264** employs a hybrid approach that combine two different algorithms, picking the better one dynamically[20]. It is important to note that whenever prediction fails (the wrong path is taken), the **21264** enters a *mispredict trap*, which basically stops all in-flight instructions, flushes the instruction pipeline and restarts from the correct path.

## 2.4.2 PowerPC Family

#### History

The **PowerPC** (Power Computing) began life from the IBM's **POWER** (Power Optimization With Enhanced RISC) architecture, which was introduced with the RISC System/6000 in early1990 [39]. This architecture specification is the result of the three-way collaboration **AIM**, which involve three big names in the industry, **A**pple, **I**BM and **M**otorola. The first chip of the PowerPC family, **601** was released in Year 1994. A number of variations on the basic chip were later released as **PowerPC 602**, **603** and **604**. The first 64bit implementation, the **620**, was released in Year 1995. Later chips were used by the Apple Macintosh machine:

- 1. **750** (PowerPC G3) in Year 1997

- 2. **7400** (PowerPC G4) in Year 1999

- 3. 970 (PowerPC G5) in Year 2003

Besides from the Apple Macintosh machine, PowerPC chips are also a favorite choice for embedded computer designers, in particular the **PowerPC 620**.

#### **Processor Architecture**

The original **POWER** architecture incorporated common characteristics for RISC architectures: fixed length instructions, load/store only memory access, separate registers for integer and floating point operations. Also, the **POWER** architectures is functionally partitioned, which facilitated the implementation of superscalar designs[23].

When the **PowerPC** architecture was extended into the 64bits realm, there were several major changes:

- 1. The designers removed niche instructions that were deemed too complicated.

- 2. A set of simpler, single precision floating-point operations were added.

- 3. A more flexible memory model, allows software to specify how the system performs memory accesses.

#### PowerPC 620

The **620** pipeline has 5 stages for integer instruction: fetch, dispatch, execute, complete and write-back. For other type of instructions, a variable number of stages is needed, briefly Floating Point Instruction takes 8, Load Instruction takes 7, Store Instruction takes 9 and Branch Instruction takes 4. The main execution characteristic of the **620** is that Instructions are dispatched in program order, are executed out-of-order, and are completed in order [24]. As with the **Alpha AXP** architecture, we are concerned mainly with the fetch and dispatch stage.

The fetch stage access the instruction cache to bring up to 4 instructions into a 8-entry FIFO buffer. The first four (the older four) are referred to as dispatch buffer which is accessed by the dispatch stage directly, and the other four entries are the instruction buffer. The **620** also associates seven pre-decode bits with each instruction which contains executions information like GPR<sup>1</sup> file usage, execution unit needed etc. These pre-decode bits eliminates the need for a separate decode pipeline stage.

During each cycle, the dispatch stage examines the four instructions in the dispatch buffer and attempts to dispatch them to reservation stations in appropriate execution units. Inter-instruction dependencies are identified and an attempt is made to read the source operand from the architectural register files or from the

$<sup>^{1}</sup>$ General Purpose Register

rename buffers. Note that the **620** assigns rename buffer for results produced by an instruction. Subsequent instructions that depends on this result are given a tag to identify that particular rename buffer.

Since execution can occur out-of-order, a 16-entry reorder buffer is used to keep track of the instruction order (the program order) as well as the state of the instructions. A reorder buffer entry is associated with each dispatched instruction. A completion flag is recorded when the instruction finished its execution, which will be used to ensure program order.

The **620** employs a **Branch History Table** method for branch prediction. Prediction is made based on the past history of a particular branch instruction. Static branch prediction, where a bit in the instruction along with the direction of the branch determines the outcome of the prediction, can be turned on by software to take the place of the BHT method[24].

Speculative execution is made possible by maintaining the results in temporary storage, such as rename buffers, reorder buffers and shadow registers (registers that are invisible/unaccessible to programmer). When misprediction occurs, the completion logic kicks in and purges all speculative results.

## 2.4.3 Conclusion

The superscalar machines survey has taught us several important lessons:

- Multi-Issue (Superscalar) Execution depends on the architecture ability to disentangle the static and dynamic dependencies between instructions. Tagging or renaming is a widely employed solution.

- 2. Instruction Supply is important in Superscalar design. Because of the multiple instructions dispatched every clock cycle, a constant supply of of instructions from the fetching stage is vital.

3. **Branch Prediction** in a superscalar setting is viable. However, two problems must be solved efficiently for this technique to be worthwhile: keeping track of speculative results and cleaning up misprediction.

These considerations have considerably influence our design for SAFA.

# 2.5 Summary

The two surveys outlined in this chapter have given us much material to help design our architecture. Although the architectures surveyed comes from radically different design, we found that there are complementing traits between the two groups. The stack machines survey has shown very clearly the disadvantages of the stack oriented architecture, but at the same time points out the undeniable fact that stack structure is one of most utilized data structure in high level language. The register machines survey, on the other hand, showed that there are some very well studied techniques that can improve instruction level parallelism. However, these machines have little specialized support for high level language. Guided by these observations, we have laid out our design of a new stack machine **SAFA**, in search for a stack architecture that provides good high level language support and performs well at the machine level. The architectural details which will be covered in the next few chapters.

# Chapter 3

# High Level Language Support

The original purpose of computer programming languages is to provide a more human friendly interface leading to the lowest level of hardware instructions. In the beginning, Assembly Languages were basically thinly veiled human readable machine code. The close relationship between the language and the hardware reflects the need of maximum efficiency in execution since processing power comes at a premium. However, that also renders the language to be restricted, awkward to use and machine dependent.

As computing power increased, the possibility of allowing more flexible and expressive programming language emerged. Programming language design shifted from machine-centric to human-centric. These languages, usually termed as High Level Programming Languages to distinguish them from the low level counterparts, represent richer paradigms to organize the data and control of a program. The HLPs, being further away from the machine code conceptually, relies on compilers to translate them into machine executable code. This frees the HLPs from the restriction of any single machine and further enhances the flexibility of the language.

With the growing importance of HLPs, new design in computer architecture must take high level language support into consideration. Providing specialized hardware for high level construct has greatly influenced the design of some computer architectures. For example, from the older schools of architecture we have the Burrough architecture, which utilized the display registers (Section 2.3.1) for efficient procedure invocation. For the more recent architectures, the Intel Pentium x86 architecture provides the MMX (multimedia extension) for video, computer graphics processing. There are even attempts to based computer architecture on high level language paradigm, for example, the Intel AIX (Section 2.3.3) which actually embodies object oriented concepts.

For SAFA, we consider the HLP support in two main areas, control flow and data structure, which are discussed in the following sections.

# 3.1 Control Flow

There are two major forms of control flow in most HLPs, procedure<sup>1</sup> activation, and selective execution (branching and looping).

### 3.1.1 Procedure Activation

In HLPs, program code is usually organized into manageable modules e.g. *Procedures/Functions* in procedural imperative languages, *Methods* in object-oriented languages to allow better modularity and code re-usability. Hence, one of the most frequently used operations in HLPs is to transfer the thread of control from one module to another, e.g. function call, method invocation etc. According to [27], in a typical PASCAL program, the frequency of procedure activation (function call) can be as high as 15%, the third highest after assignment (45%) and branching (29%). Compared to function calls, assignment and *if-then-else* are relatively simpler operations. These operations can easily be mapped to a few low level instructions. By providing maximum efficiency in the instruction level, these operations can then be executed with satisfactory speed. On the other hand, function calls require more

<sup>&</sup>lt;sup>1</sup>also known as module, coroutine or function

complicated mechanism for efficient execution.

There are two major tasks during procedure activation. In addition to the mechanism of transferring and bookkeeping of threads of control, accessing scoped variable also requires attention. For procedural HLPs, there are at least two level of scoping, one for the so called *Global Variables* (accessible in the whole program), and *Local Variables* (specific to each module)<sup>2</sup>. For object oriented HLPs, there are at least two more scopes: the class variables (specific to each class) and the object variables (specific to each object, i.e. instances of each class). The extra scopes in object oriented HLPs can be taken as an extension from the procedural counterparts, where class variable is similar to global variable in a class, and object variable is similar to local variable specific to each object. We will first consider the scoped variables in procedural HLPs.

During the execution of a procedure, both type of variables may be accessed. However, a local variable in a procedure is not visible or accessible from the outside. Hence, an efficient mechanism for accessing variables in different scopes, and also access protection is needed.

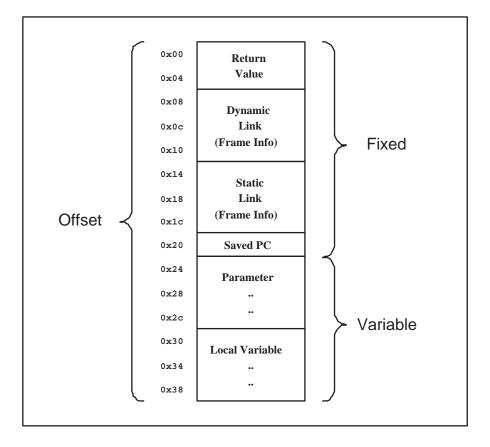

The information needed for the activation of a procedure is usually collected in a record called an *activation record* or *stack frame*[29]. This record is created at runtime when a procedure is about to be entered. Usually it is allocated on the memory stack or heap according to different designs. A number of the more important information items kept is listed as follows:

- **Control Link** Also known as dynamic link, points to the stack frame of the runtime caller.

- Access Link Also called as static link, points to the lexical host (parent) of the current procedure.

<sup>&</sup>lt;sup>2</sup>Languages that support nested procedures will have more scoping levels, like Pascal, Algol60 etc

Saved State any process state information of the caller procedure, used for resumption of the caller procedure.

**Parameters** Actual parameters for the activation of the current procedure.

Local Variables Storage space for local variables of the current procedure.

The two links: dynamic and static, play important role in procedure activation. By following the control link, the return address and information of the caller relevant to the procedure can be determined when the current procedure finishes. By using the access link(s), the non-local variables in parent or global scope can be accessed. Since these two links are utilized heavily during execution, it is natural for architecture designer to provide hardware support for them. For most general purpose register machines, only a single register is used to store the address of the activation record. This register is given different name in different architecture, for example, the frame pointer in the x86 architecture. The two links are then accessed via offsets from this register.

Although a single register is sufficient for bookkeeping purpose, accessing out of scope variables would require extra computation since the access links need to be traversed repeatedly to reach the required scope. Other architecture designers tried to provide more sophisticated support to cut down the execution time. For example, the Burroughs line provides an array of 32 Display Registers, which is used to store the addresses of activation records at each lexical scope level[37]. The content of each register is adjusted automatically upon entering/exiting to/from a procedure. Accessing scoped variable is then translated into a single access of the register array at the required lexical scope level<sup>3</sup>.

SAFA follows a similar scheme, but with the following differences:

1. Less registers. The total number of registers (named as *frame register*) used for bookkeeping the activation frames is only four. Each of the four frame

<sup>&</sup>lt;sup>3</sup>to be precise, an offset must also be added

registers has a specific role, which will be covered later.

2. More information is stored in each register. Most of the other architectures opt to store only the address of the starting (or ending) of the activation records in the registers. *SAFA* choose to encode more information, which includes the starting address, the total number of data elements and size of elements among others<sup>4</sup>.

In most high level programming languages, there are four activation frames are of greater interest during execution. These four frames are:

Global Frame describes global information (the outermost lexical scope).

- **Caller Frame** describes the caller of the current procedure. Also the destination of return when current procedure finishes.

- Host Frame describes the lexical parent of current procedure, mostly used for accessing non local variables.

**Own Frame** describes the current running procedure.

As for languages that allows nested procedure, the information stored in the host frame can be used to locate the predecessor frames for non-local variables in various lexical levels. However, this scheme would be slower than other implementations, for example, the display registers scheme, since multiple traversals are needed. More frequent access to a non-local frame can however be accommodated by utilizing additional frame registers, as will be discussed later.

The decision of limiting the frame registers to 4 for procedure activation can be viewed as a compromise between flexibility and hardware economy. By providing more frame registers, the CPU may give better performance *only* when dealing with nested procedure languages. However, the complexity and size of the frame registers will certainly take their toll on CPU space and circuitry complexity. On the other

<sup>&</sup>lt;sup>4</sup>other fields will be discussed in the next section

hand, the added information of each register provides added benefits like hardware detection of illegal access (by using the limit of each frame) and other checking with reasonable amount of register complexity.

To give a clearer picture of the scheme adopted by SAFA, consider the following *Pascal*-like program.

| Program P              |                              |

|------------------------|------------------------------|

| Procedure A()          |                              |

| Procedure B()          |                              |

| begin                  |                              |

|                        | // Point Beta                |

| end                    | // end of B                  |

| begin                  |                              |

| B()                    |                              |

| end                    | // end of A                  |

| Procedure C()<br>begin |                              |

|                        | // Point Alpha               |

| A()                    |                              |

| end                    | // end of C                  |

| begin<br>C()           | <pre>// main procedure</pre> |

| end                    | // end of P                  |

Upon the initiation of the program  $\mathbf{P}$ , the four frame registers have the following information:

| Frame Register | Pointing to |

|----------------|-------------|

| Global         | Р           |

| Caller         | nil         |

| Host           | nil         |

| Own            | Р           |

Since we are executing the main procedure, the current frame would point to  $\mathbf{P}$ , which is also the global frame. When we reach *Point Alpha* in procedure  $\mathbf{C}$ , the frame registers would now contain:

| Frame Register | Pointing to |

|----------------|-------------|

| Global         | Р           |

| Caller         | Р           |

| Host           | Р           |

| Own            | С           |

Since the main procedure called  $\mathbf{C}$ , the Caller Frame points to frame  $\mathbf{P}$ .  $\mathbf{P}$  also happens to be the lexical parent of  $\mathbf{C}$ . When the *Point Beta* in procedure  $\mathbf{B}$  is reached, we will now have:

| Frame Register | Pointing to |

|----------------|-------------|

| Global         | Р           |

| Caller         | А           |

| Host           | А           |

| Own            | В           |

The procedure  $\mathbf{A}$  is the caller as well as the host of procedure  $\mathbf{B}$ . By using the Global Frame Register and the Host Frame Register, the procedure  $\mathbf{B}$  can easily access global variables (defined in the program scope) or parent's variables (defined in procedure  $\mathbf{A}$ ).

Since the content of the frame registers is managed automatically by hardware upon procedure entry and exit, compiler writers can utilize the machine instructions provided to gives optimized access to variables in different scopes.

#### **3.1.2** Repetitive Execution with Counter

Repetitive execution, commonly known as looping, represents another kind of major control flow in HLPs. It is no exaggeration to say most programs spend most time looping. For this section, we concentrate on a particular subclass of repetitive execution: loops with counter. Most loops will ends the execution upon meeting some condition. For loops with counter, the ending condition is specified with numerical values, usually in the form of checking a variable against a fixed upperbound. For example:

| For $I = 1$ to $10$ | //Loop Header |

|---------------------|---------------|

| Do Something        | //Loop Body   |

The for-loop above terminates when the variable I exceeds 10. This particular form of loop enjoyed heated research about optimizing it mainly because of its frequent appearance, usually to do with array/matrix manipulation. By examining the example, we can see that there are two major components in a loop with counter. The loop header is basically to maintain bookkeeping information about the number of iterations. The loop body, on the other hand, contains the main computations. Various methods are proposed to optimize each of the components.

In this section, we concentrate on the possible optimization of the loop header. For stack-oriented machine, the updating and validating of the loop header can be performed as follows:

```

//Assume:

11

I is a local variable in stack frame

//

I = 1 initially

start:

Load I

Load 10

//terminates the loop

If_Greater done

. . .

//loop body

. . .

//load I again

Load I

Add

//Increment I