# EMBEDDED MACHINE VISION – A PARALLEL ARCHITECTURE APPROACH –

CHAN KIT WAI

NATIONAL UNIVERSITY OF SINGAPORE 2005

### EMBEDDED MACHINE VISION

### - A PARALLEL ARCHITECTURE APPROACH -

CHAN KIT WAI

(B. Tech. (Hons), NUS)

A THESIS SUBMITTED FOR THE DEGREE OF MASTER OF ENGINEERING DEPARTMENT OF ELECTRICAL & COMPUTER ENGINEERING NATIONAL UNIVERSITY OF SINGAPORE

2005

# Acknowledgements

First of all, I would like to thank my project supervisor, Dr Prahlad Vadakkepat for his help and guidance in writing this thesis. For that, he has spent his precious time guiding me for making this thesis readable. I would also like to express my gratitude for his advice and the freedom that he had given, to explore the areas of my interest.

I would also like to thank those who had gave their technical advice and time for answering numerous questions. In particular, Dr Tang Kok Zuea, Boon Kiat and Dr Wang.

Special thanks, goes to my wife for giving her unlimited support in many ways; especially working through late nights for the preparation of this thesis. Her understanding and encouragement are important during this demanding period of my career and studies.

Jason Chan Kit Wai Nov 2005

# Contents

| A  | cknov | wledge       | ements                                  | ii  |  |

|----|-------|--------------|-----------------------------------------|-----|--|

| C  | onter | nts          |                                         | iii |  |

| Sı | ımma  | ary          |                                         | vii |  |

| Li | st of | Table        | s                                       | ix  |  |

| Li | st of | Figur        | es                                      | x   |  |

| Li | st of | Abbre        | eviations                               | xiv |  |

| 1  | Intr  | Introduction |                                         |     |  |

|    | 1.1   | Vision       | System For Mobile Robots                | 1   |  |

|    | 1.2   | Differe      | ent Architectures for Image Processing  | 4   |  |

|    |       | 1.2.1        | Microprocessors                         | 5   |  |

|    |       | 1.2.2        | DSP Processors                          | 6   |  |

|    |       | 1.2.3        | Application Specific Integrated Circuit | 7   |  |

|    |       | 1.2.4        | Reconfigurable Architecture             | 7   |  |

|    | 1.3   | Data 1       | Processing at Different Level           | 9   |  |

|          | 1.4                         | Motivation and Contribution |                                            |    |  |  |  |

|----------|-----------------------------|-----------------------------|--------------------------------------------|----|--|--|--|

|          | 1.5                         | Thesis Outline              |                                            |    |  |  |  |

| <b>2</b> | $\mathbf{Sys}^{\mathbf{r}}$ | tem Le                      | evel Architecture Design                   | 13 |  |  |  |

|          | 2.1                         | Syster                      | n Components Studies                       | 13 |  |  |  |

|          |                             | 2.1.1                       | Image Sensors                              | 14 |  |  |  |

|          |                             | 2.1.2                       | Memories                                   | 17 |  |  |  |

|          |                             | 2.1.3                       | FPGA Development Board                     | 17 |  |  |  |

|          | 2.2                         | Simula                      | ation and Development Tools                | 18 |  |  |  |

|          |                             | 2.2.1                       | Programming Tools                          | 19 |  |  |  |

|          |                             | 2.2.2                       | FPGA Design Flow                           | 19 |  |  |  |

|          |                             | 2.2.3                       | Verilog vs VHDL                            | 22 |  |  |  |

|          | 2.3                         | Image                       | Representation                             | 24 |  |  |  |

| 3        | An                          | Analy                       | tic Model for Embedded Machine Vision      | 28 |  |  |  |

|          | 3.1                         | Introd                      | uction                                     | 28 |  |  |  |

|          | 3.2                         | Analy                       | tic Model to Determine Image Buffer Size   | 29 |  |  |  |

|          |                             | 3.2.1                       | Concept of Queuing Theory                  | 29 |  |  |  |

|          |                             | 3.2.2                       | Row buffering                              | 31 |  |  |  |

|          | 3.3                         | Analy                       | tic Model to Determine Computational Speed | 34 |  |  |  |

|          | 3.4                         | Analy                       | sis of Image Segmentation Algorithm        | 36 |  |  |  |

|          |                             | 3.4.1                       | Computation using microprocessor           | 37 |  |  |  |

|          |                             | 3.4.2                       | Computation using custom architecture      | 39 |  |  |  |

|   | 3.5                                                       | Analysis of Image Convolution Algorithm                                    |    |  |  |  |

|---|-----------------------------------------------------------|----------------------------------------------------------------------------|----|--|--|--|

|   | 3.6                                                       | Summary                                                                    |    |  |  |  |

| 4 | Image Acquisition, Compression, Buffering and Convolution |                                                                            |    |  |  |  |

|   | 4.1                                                       | Image Acquisition                                                          | 44 |  |  |  |

|   |                                                           | 4.1.1 Image sensor interface signals                                       | 44 |  |  |  |

|   |                                                           | 4.1.2 Image acquisition: implementation                                    | 46 |  |  |  |

|   | 4.2                                                       | Image Compression                                                          | 49 |  |  |  |

|   |                                                           | 4.2.1 Image compression: concept                                           | 49 |  |  |  |

|   |                                                           | 4.2.2 Image compression: implementation                                    | 52 |  |  |  |

|   | 4.3                                                       | B Image Buffering                                                          |    |  |  |  |

|   |                                                           | 4.3.1 Image buffering: theory                                              | 56 |  |  |  |

|   |                                                           | 4.3.2 Image buffering: implementation                                      | 60 |  |  |  |

|   | 4.4                                                       | Convolution Theory                                                         | 65 |  |  |  |

| 5 | FPO                                                       | GA Implementation of Parallel Architecture                                 | 67 |  |  |  |

|   | 5.1                                                       | Edge Detection Theory                                                      | 68 |  |  |  |

|   | 5.2                                                       | Proposed Parallel Architecture for Edge Detection                          | 71 |  |  |  |

|   | 5.3                                                       | Thresholding                                                               | 75 |  |  |  |

|   | 5.4                                                       | Edge Detection: Analysis and Results                                       | 76 |  |  |  |

|   |                                                           | 5.4.1 Experiment of edge detection with different scenes                   | 80 |  |  |  |

|   |                                                           | 5.4.2 Images with resolution $320 \ge 240 = \dots = \dots = \dots$         | 80 |  |  |  |

|   |                                                           | 5.4.3 Image with resolution of $1280 \ge 1024 \ldots \ldots \ldots \ldots$ | 81 |  |  |  |

|              | 5.5   | 5 Proposal Parallel Architecture for Low Pass Filter |                                       |     |  |  |

|--------------|-------|------------------------------------------------------|---------------------------------------|-----|--|--|

|              |       | 5.5.1                                                | Noise pixels in high resolution image | 83  |  |  |

|              |       | 5.5.2                                                | Low Pass Filter                       | 84  |  |  |

|              | 5.6   | Syster                                               | n Resource Utilization                | 88  |  |  |

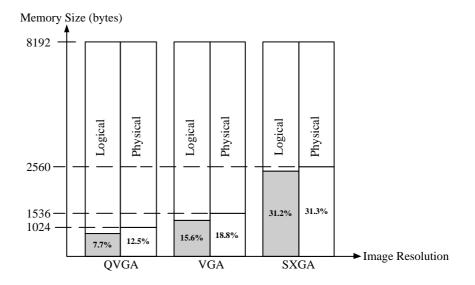

|              |       | 5.6.1                                                | On-Chip memory size requirements      | 88  |  |  |

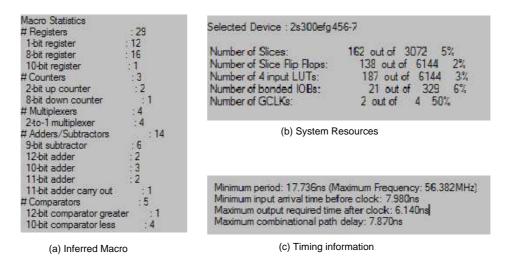

|              |       | 5.6.2                                                | Logic resources                       | 89  |  |  |

|              |       | 5.6.3                                                | System performance                    | 89  |  |  |

|              | 5.7   | Summ                                                 | ary of Results                        | 90  |  |  |

| 6            | Con   | clusio                                               | ns and Future Work                    | 92  |  |  |

|              | 6.1   | Conclu                                               | usions                                | 92  |  |  |

|              | 6.2   | Future                                               | e Work                                | 93  |  |  |

| Bi           | bliog | graphy                                               |                                       | 95  |  |  |

| $\mathbf{A}$ | uthoi | r's Pul                                              | olications                            | 101 |  |  |

### Summary

Machine vision is one of the essential sensory functions in mobile robotics. By applying vision processing techniques, certain features can be extracted from a given scene. However, there are certain limitations in implementing an on-board image processor. Limited computational power, low data transfer rate and tight memory budget, place constraints on the performance. As a result, image resolution and frame rate are often compromised.

To implement efficient solutions, algorithms and hardware architectures must be well matched. This can be achieved for algorithms with high degree of regularity that are identified to exploit its parallelism. The operations can be mapped into custom functional units to achieve higher performance compared to the fixed processing units. Such approaches can eliminate the necessity of employing high-end processors.

Reconfigurable architectures pose as a suitable platform for computationally demanding image processing algorithms. Custom logic can be designed to exploit parallelism at different areas and levels of an application.

Suitable image sensor, FPGA IC Chip and the suitable simulation and developmental tools are selected. An analytical mathematical model to estimate the various performance parameters associated real-time image processing is proposed. The model allows system designers to estimate the required memory size and processing frequency of a given microprocessor architecture. In one of the examples, the reduction in the number of instructions per pixel, resulted into processing a pixel in a single cycle. Next, the image acquisition, compression, buffering and image convolution are studied. Custom architectures are designed with the considerations of optimising the logic and memory resources. The image buffering is modelled as a producer-consumer problem. Techniques are employed to reuse memory locations. Data that reaches the end of its lifetime is automatically removed to free up the memory location for new data.

A parallel architecture is proposed to the perform 2D convolution operation with the aim of processing a pixel within a single clock cycle. The customized architecture allows direct computation instead of conventional load store operations. Specifically, the low pass filter, edge detection and thresholding algorithm are investigated. For edge detection, two separate 2D convolution processes and a thresholding process are computed within a single clock cycle. A study is conducted to evaluate the effects of adding a low pass filter to the design. After which, a threshold operation is performed to extract the desired edge features of an image. Two types of image processing, with and without low pass filter are compared.

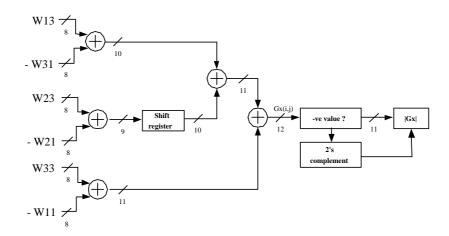

To achieve minimal usage of hardware resources, the redundant memory locations, logics and computations are removed. For instance, the multipliers are replaced by an equivalent bit-wise shifter and a 9 pixels convolution is reduced to a 6 pixels convolution.

The synthesis results obtained are very encouraging. The total number of slices occupied by the design is 5% of the total hardware resource available. Lastly, simulation and actual hardware implementation are provided to demonstrate the performance of the embedded machine vision using FPGA.

# List of Tables

| 1.1 | Specifications of various commercially available on-board vision pro- |    |  |  |  |

|-----|-----------------------------------------------------------------------|----|--|--|--|

|     | cessors                                                               | 3  |  |  |  |

| 2.1 | Comparison of available on-board vision processor                     | 15 |  |  |  |

| 2.2 | Development and analysis tools                                        | 19 |  |  |  |

| 2.3 | Comparsion of VHDL and Verilog                                        | 23 |  |  |  |

| 4.1 | Properties of exclusive OR operations                                 | 51 |  |  |  |

# List of Figures

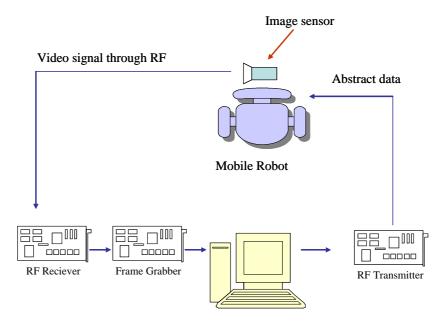

| 1.1  | Typical machine vision system                                                    | 2  |

|------|----------------------------------------------------------------------------------|----|

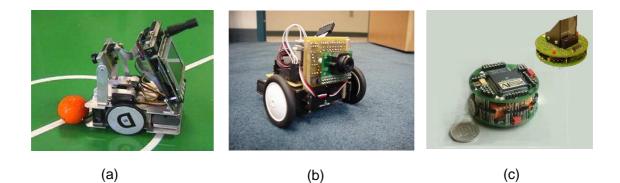

| 1.2  | (a) Eyebot (b) CMUCam (c) Khepera Camera Turret $[1][13][18]$                    | 3  |

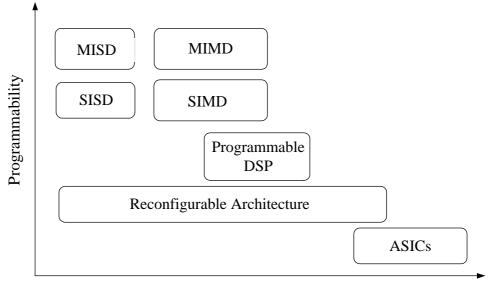

| 1.3  | Programmability vs parallelism                                                   | 5  |

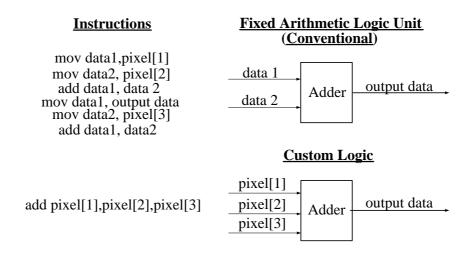

| 1.4  | Fixed Arithmetic Logic Unit (ALU) vs Custom ALU                                  | 8  |

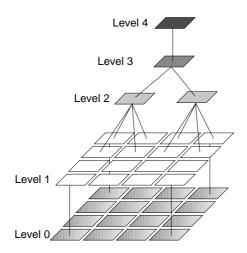

| 1.5  | Data processing at different level                                               | 9  |

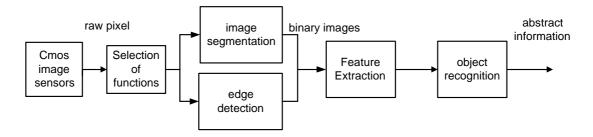

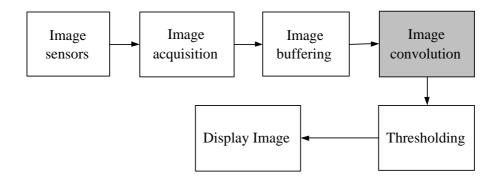

| 1.6  | Stages for image processing                                                      | 10 |

| 2.1  | MicroViz setup configuration                                                     | 14 |

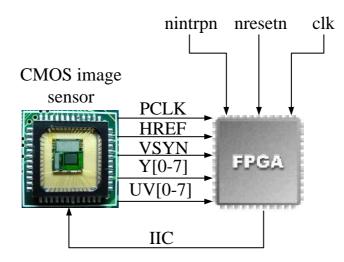

| 2.2  | OV7620 Image sensor and FPGA                                                     | 15 |

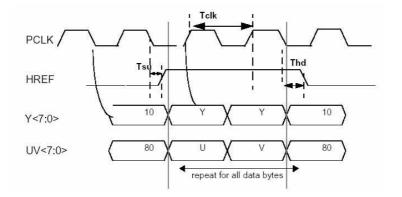

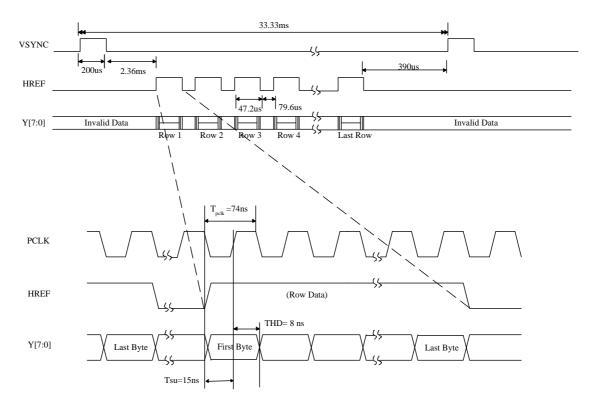

| 2.3  | Timing waveform of pixel data bus [36]                                           | 16 |

| 2.4  | MicroViz Prototype board                                                         | 18 |

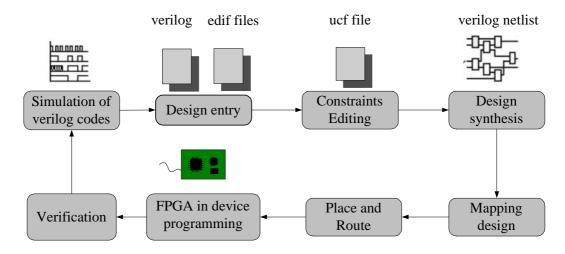

| 2.5  | FPGA design flow                                                                 | 20 |

| 2.6  | Gate level netlist                                                               | 21 |

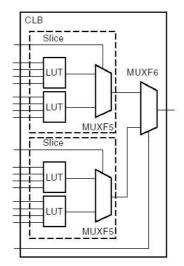

| 2.7  | Configuration Logic Block [30]                                                   | 22 |

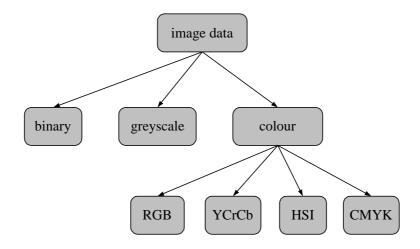

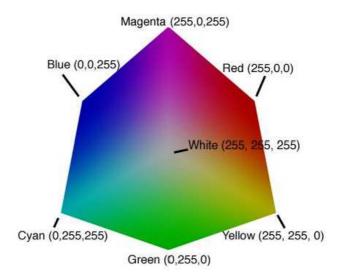

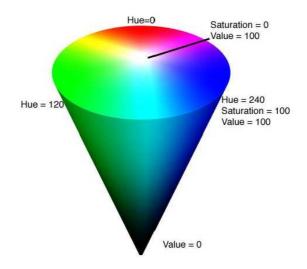

| 2.8  | Colour Space                                                                     | 24 |

| 2.9  | (a)<br>RGB colour image (b)<br>Greyscale image (c)<br>Binary image $\ . \ . \ .$ | 25 |

| 2.10 | RGB colour space [35]                                                            | 25 |

| 2.11 | HSI colour space $[35]$                            | 26 |

|------|----------------------------------------------------|----|

| 3.1  | Queue model of vision system                       | 30 |

| 3.2  | Burst time and emptying time                       | 31 |

| 3.3  | Thresholding                                       | 37 |

| 3.4  | Assembly code representation of C program          | 38 |

| 3.5  | Convolution algorithm in C                         | 41 |

| 4.1  | Image acquisition process                          | 44 |

| 4.2  | CMOS image sensor array                            | 44 |

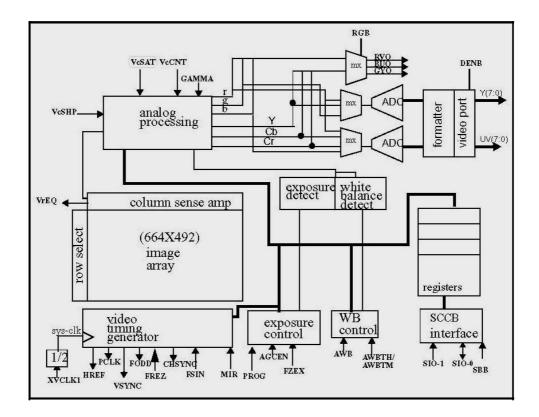

| 4.3  | CMOS image sensor architecture [36]                | 45 |

| 4.4  | Timing Diagram of the control signals              | 47 |

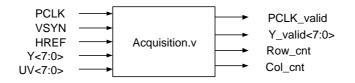

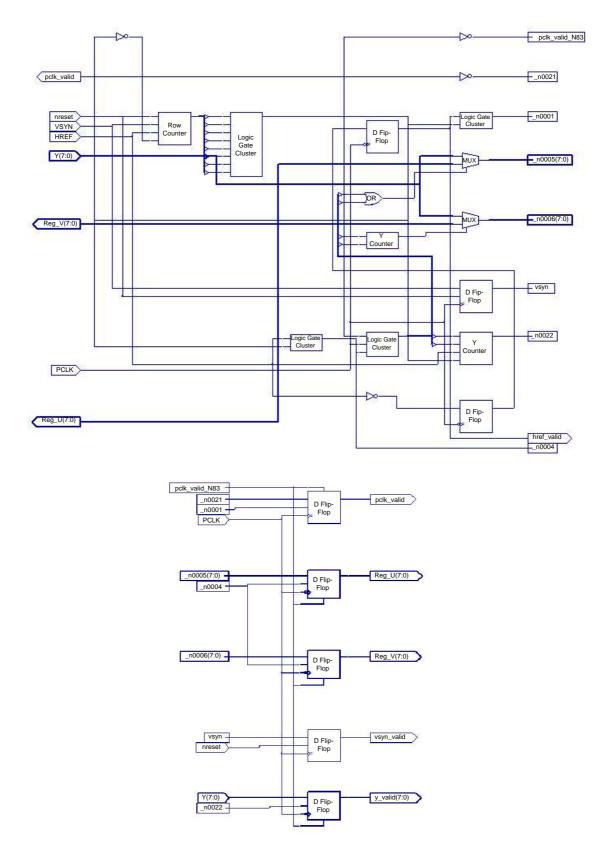

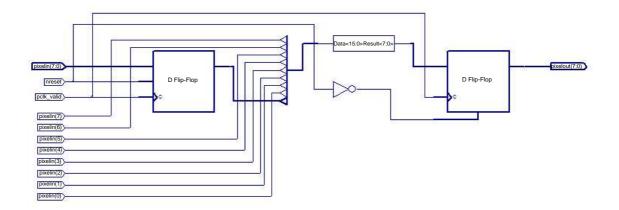

| 4.5  | Image acquisition block                            | 47 |

| 4.6  | Synthesized circuit of the image acquisition block | 48 |

| 4.7  | Simulation result of the image acquisition block   | 49 |

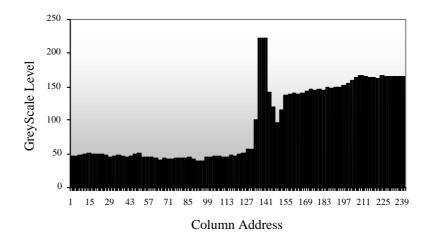

| 4.8  | Pixel amplitude of a single line                   | 50 |

| 4.9  | Number of bits to represent compressed pixel       | 50 |

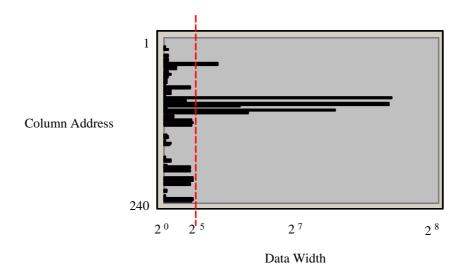

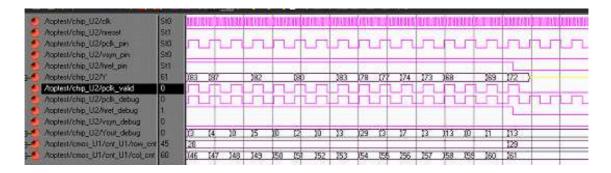

| 4.10 | Block diagram of Compression and Decompression     | 52 |

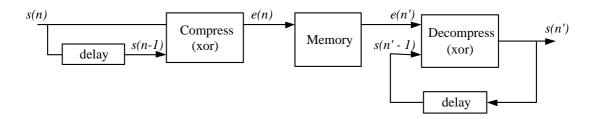

| 4.11 | Simulation results                                 | 53 |

| 4.12 | Synthesized circuit of XOR compression module      | 54 |

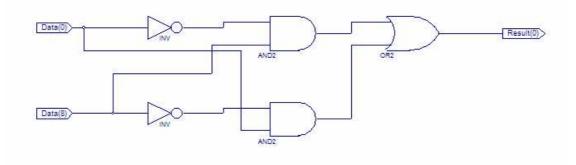

| 4.13 | XOR gate                                           | 54 |

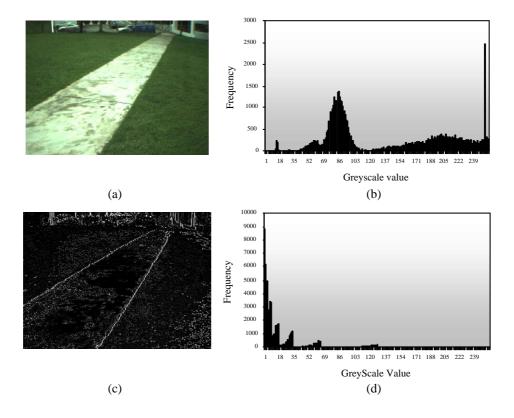

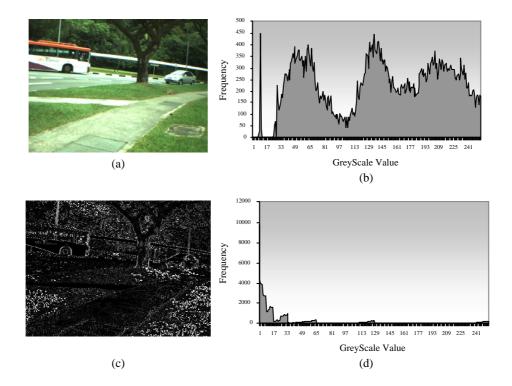

| 4.14 | Histogram of image with low frequency content      | 55 |

| 4.15 | Histogram of image with high frequency content     | 55 |

| 4.16 | Image buffering stage                                                        | 56 |

|------|------------------------------------------------------------------------------|----|

| 4.17 | A 3 x 3 convolution mask on a 5 x 4 image                                    | 57 |

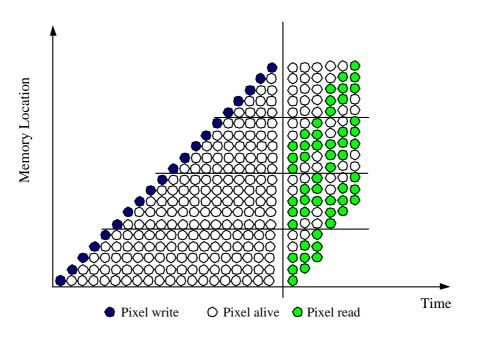

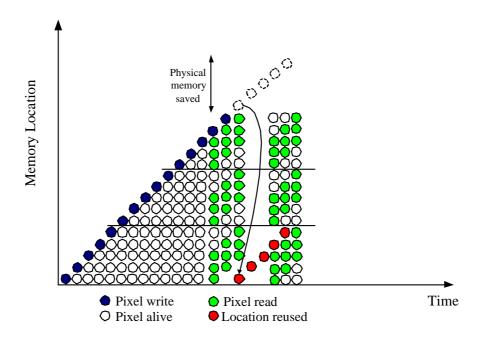

| 4.18 | Producer and consumer of pixels before transformation $\ldots \ldots \ldots$ | 58 |

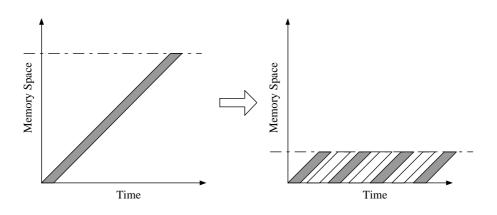

| 4.19 | Producer and consumer of pixels after transformation                         | 58 |

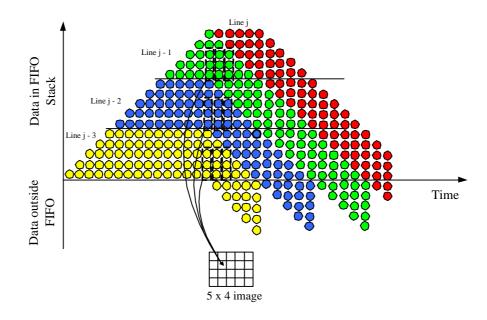

| 4.20 | Buffering using FIFO                                                         | 59 |

| 4.21 | Reduction of memory space after data reuse                                   | 59 |

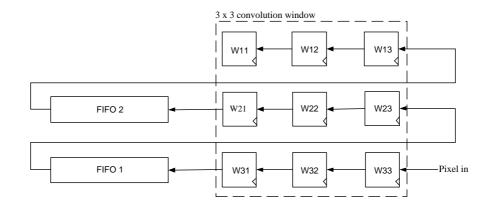

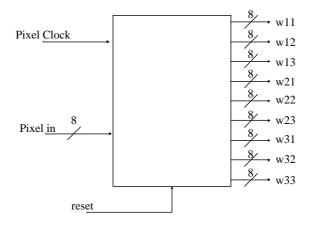

| 4.22 | Convolution window using registers                                           | 61 |

| 4.23 | Image buffer module                                                          | 61 |

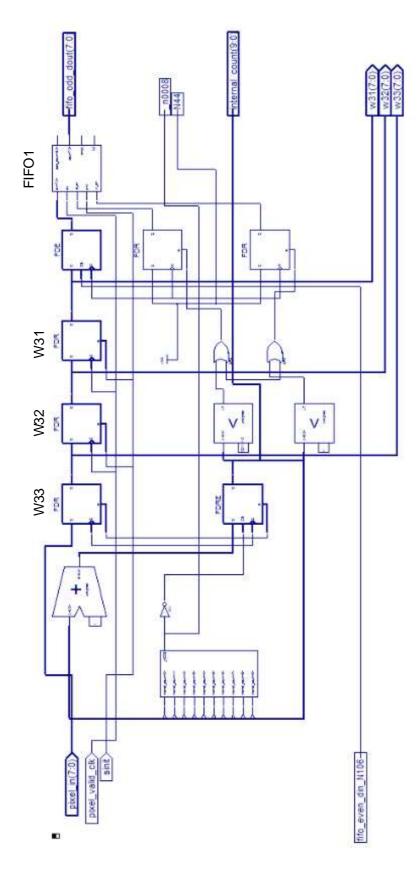

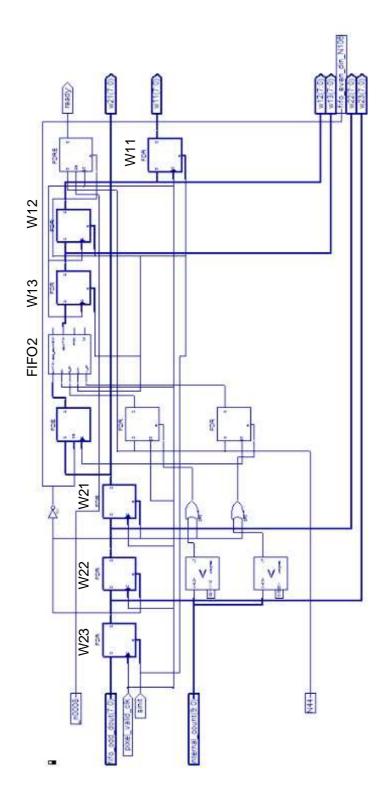

| 4.24 | Synthesize result of Image buffer (Part 1)                                   | 63 |

| 4.25 | Synthesize result of Image buffer (Part 2)                                   | 64 |

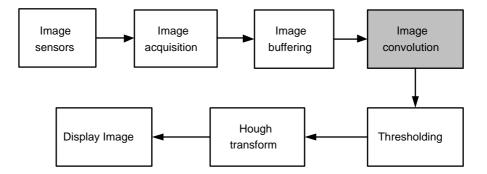

| 4.26 | Image convolution stage                                                      | 65 |

| 4.27 | Image convolution                                                            | 66 |

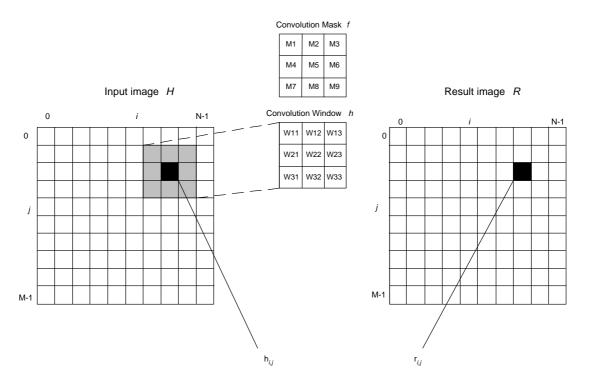

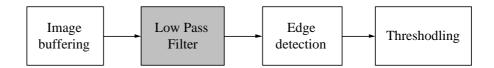

| 5.1  | Image processing stage                                                       | 67 |

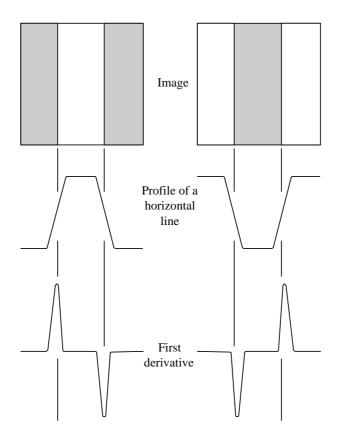

| 5.2  | Image intensity level derivatives                                            | 68 |

| 5.3  | Convolution window                                                           | 69 |

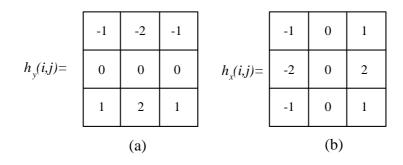

| 5.4  | Prewitt operator                                                             | 69 |

| 5.5  | Sobel operator                                                               | 70 |

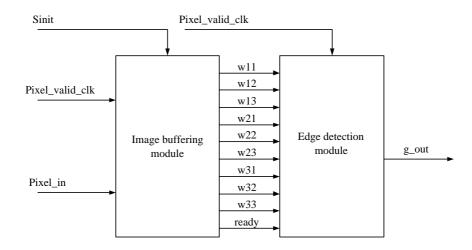

| 5.6  | Acquiring nine pixels from image buffering module                            | 71 |

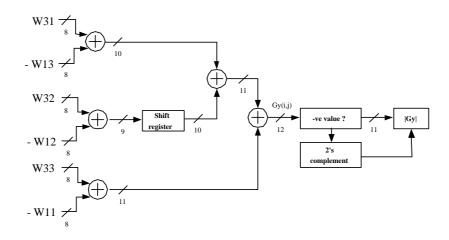

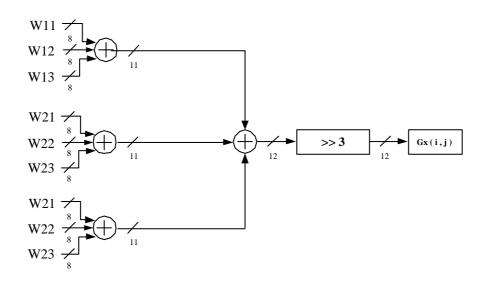

| 5.7  | Architecture of $G_x$                                                        | 72 |

| 5.8  | Architecture of $G_y$                                                        | 73 |

| 5.9  | Architecture for gradient magnitude and thresholding $\ldots$ .              | 73 |

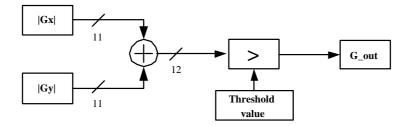

| 5.10 | Simulation of architecture using Visual C/C++ $\ldots$                       | 75 |

| 5.11 | Thresholding                                                                                                                                        | 76 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----|

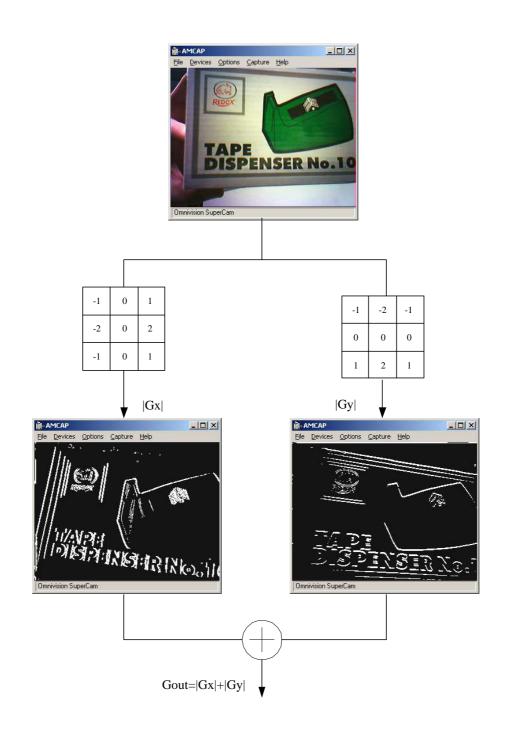

| 5.12 | Sum of $ Gx $ and $ Gy $ component                                                                                                                  | 77 |

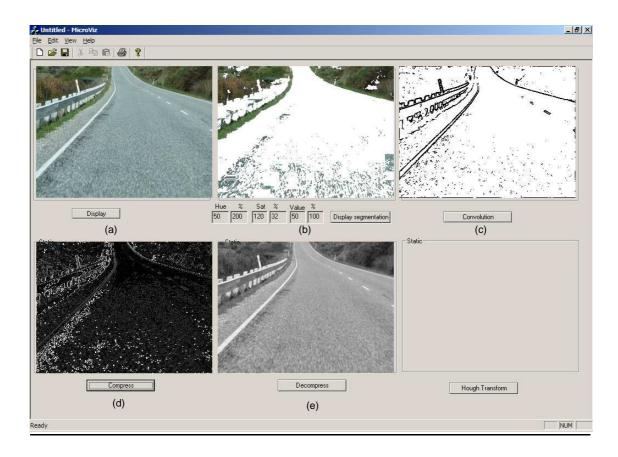

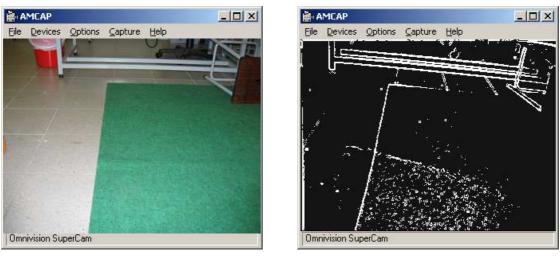

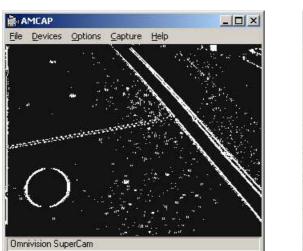

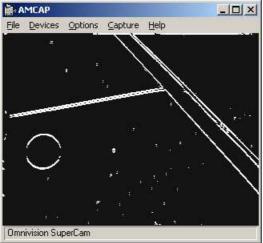

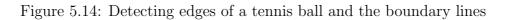

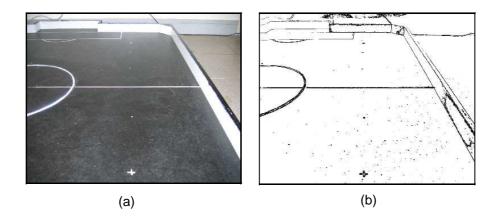

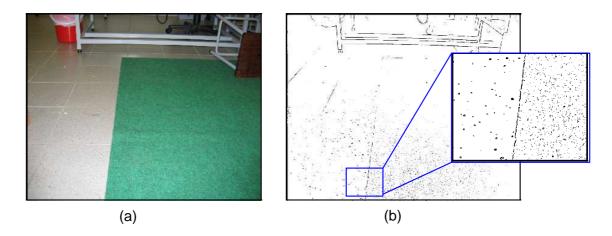

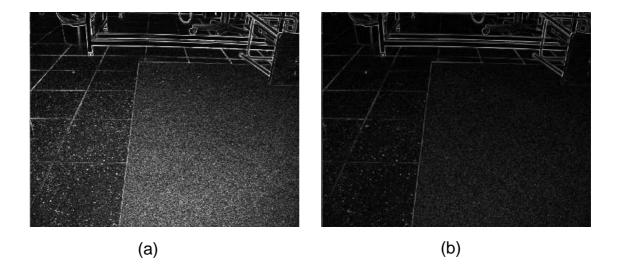

| 5.13 | Detecting edges of the green carpet                                                                                                                 | 78 |

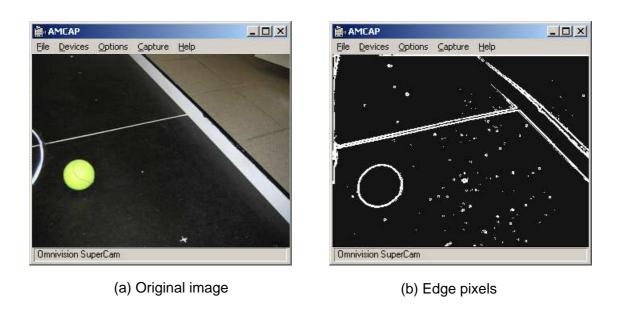

| 5.14 | Detecting edges of a tennis ball and the boundary lines $\ldots$ .                                                                                  | 79 |

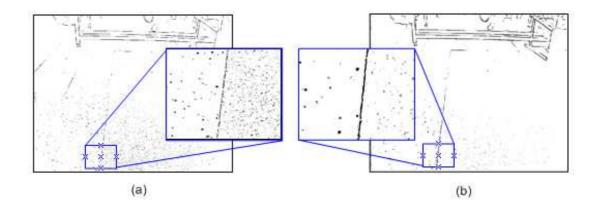

| 5.15 | Edge detection with image resolution of $320 \ge 240 \\ \ldots \\ $ | 80 |

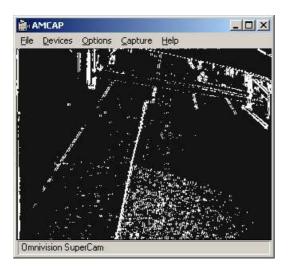

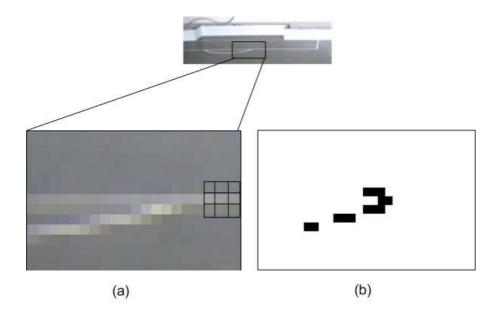

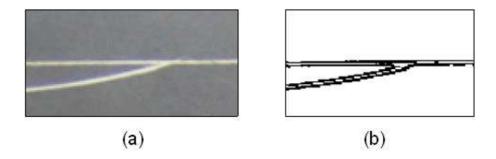

| 5.16 | Magnified image of Figure 13                                                                                                                        | 81 |

| 5.17 | (a) Original image of 1280 x 1024 produces (b) fine edge pixels                                                                                     | 82 |

| 5.18 | (a) Magnified image of Figure 15 and (b) Edge detection of fine lines                                                                               | 82 |

| 5.19 | Edge detection with different image resolution                                                                                                      | 83 |

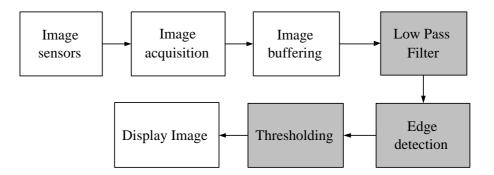

| 5.20 | Insertion of Low pass filter before edge detection                                                                                                  | 84 |

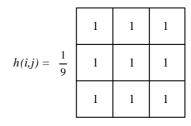

| 5.21 | Convolution coefficients of Low Pass Filter                                                                                                         | 84 |

| 5.22 | Architecture of Low Pass Filter                                                                                                                     | 85 |

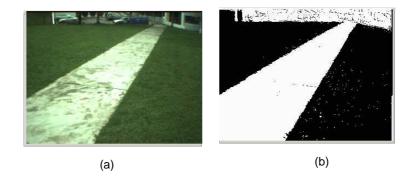

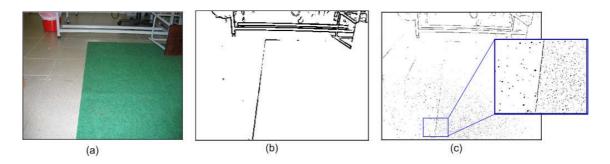

| 5.23 | (a) Orignal image (b) Edge detection without Low Pass filter                                                                                        | 86 |

| 5.24 | (a) Original 1280 x 1024 image (b) Resultant Image applied with<br>Low pass filter                                                                  | 86 |

| 5.25 | (a) Edge detection without Low Pass filter (b) Edge detection with<br>Low Pass filter                                                               | 87 |

| 5.26 | (a) Without Low pass filtering (b) With Low pass filtering $\ldots$ .                                                                               | 87 |

| 5.27 | Comparison of image buffer size required for different resolution                                                                                   | 88 |

| 5.28 | Synthesis report from Xilinx synthesis tool                                                                                                         | 89 |

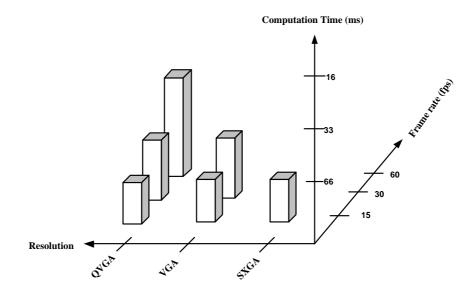

| 5.29 | Computation time with different resolution                                                                                                          | 90 |

# List of Abbreviations

| ALU   | Arithmetic Logic Unit                       |

|-------|---------------------------------------------|

| ASICs | $Application\ Specific\ Integrated-Circuit$ |

| CCD   | Charge Coupled Device                       |

| CLB   | $Configuration \ Logic \ Blocks$            |

| CMOS  | Complementary Metal-oxide Semiconductor     |

| CPU   | Central Processing Unit                     |

| DSP   | Digital Signal Processing                   |

| EDA   | Electronic Design Automation                |

| EDIF  | Electronic Design Interchange Format        |

| EE    | Electrical Engineering                      |

| FIFO  | First In First Out                          |

| FPGA  | Field Programmable GateArray                |

| FPS   | Frames per Second                           |

| HDL   | Hardware Description Language               |

| HREF  | Horizontal Reference                        |

| HSI   | Hue Saturation Intensity                    |

| I2C   | Inter – IC Connection                       |

| IIC   | Inter IC Connect                            |

| IOBs  | Input Output Blocks                         |

| ISE   | Integrated Software Environment             |

| JTAG  | Joint Test Access Group                     |

| LUT   | Look - upTables                             |

|       |                                             |

| MIMD  | $Multiple\ Instruction\ Multiple\ Data$ |

|-------|-----------------------------------------|

| MISD  | Multiple Instruction Single Data        |

| P&R   | Place and Route                         |

| PCLK  | Pixel Clock                             |

| RAM   | Random Access Memory                    |

| RGB   | Red Green Blue                          |

| SIMD  | Single Instruction Multiple Data        |

| SISD  | Single Instruction Single Data          |

| UCF   | User Constraints File                   |

| VHDL  | VHSIC HDL                               |

| VHSIC | Very High Speed Integrated Circuit      |

| VSYN  | Vertical Synchronization                |

# Chapter 1

# Introduction

Robot vision is one of the most essential development set by the robotic community at large. Research and development in robot vision has grown dramatically over the past decade. The interest and concerns of image processing for mobile robots can be seen from the vast amount of literature on this subject, including major projects spearheaded in the industry and research institutes. In particular much emphasis is placed on localization and navigation abilities of mobile robots [1][2][12][13].

Machine vision is one of the essential sensory functions for mobile robotics. By applying vision processing techniques, certain features can be extracted from a given scene. These are used to describe the environment. Collectively, such description is necessary for localization and navigation. This forms the basic behavior of any mobile robot and pave the way for the development of intelligence robot.

#### 1.1 Vision System For Mobile Robots

A typical machine vision system consists of a Charge Coupled Device (CCD) camera, a frame grabber and a host computer for the execution of the image processing algorithm.

Figure 1.1: Typical machine vision system

A typical image processing system is shown in Figure 1.1. A host computer receives images from a CCD camera, performs image recognition algorithms and transmits control signals to the mobile robot. Such configuration setup is shown in Figure 1.1 is often used in many mobile robotic systems [14][45][16].

A variety of standard image processing tools are supported on a general purpose computer. For instance, some of the commonly used programming libraries and tools are Intel Processing Library, Matlab, Visual C/C++ and Borland C/C++.

However, there are certain limitations that require the processing to be performed on board. The ability to perform on-board processing of real-time images sets many constraints. At many times, limited computational power, low data transfer rate and tight memory budget place constraints on the implementation and performance of the robots. As a result, image resolution and frame rate are often compromised.

A survey is performed to study some of the existing on-board vision systems. The EyeBot, CMUCam1, CMUCam2 and Khepera Camera Turret are reviewed (Figure 1.2). The EyeBot processes an image resolution of 80 x 60 pixels on a

Figure 1.2: (a) Eyebot (b) CMUCam (c) Khepera Camera Turret [1][13][18]

20MHz processor. The Khepera vision turret is a commercially available vision module exclusively targeted for Khepera miniature mobile robot [13]. It can process a relative high resolution image of up to 160 x 120 pixels. The Camera Turret uses a V6300 digital Complementary Metal-Oxide Semiconductor (CMOS) camera along with a dedicated 32bit Central Processing Unit (CPU) in the turret. Table 1.1 shows the comparison of the various on-board vision processors mentioned.

| Table $1.1$ : | Specifications | of various | commercially | available | on-board | vision | proces- |

|---------------|----------------|------------|--------------|-----------|----------|--------|---------|

| sors          |                |            |              |           |          |        |         |

| Descriptions   | CMUCam1        | CMUCam2        | Eyebot             | Khepera vision<br>Turret |

|----------------|----------------|----------------|--------------------|--------------------------|

| CPU            | Ubicom<br>sx28 | Ubicom<br>Sx52 | Motorola<br>32 bit | Motorola<br>32bit        |

| CPU speed      | 75 Mhz         | 75 Mhz         | 25 Mhz             | -                        |

| Max resolution | 143 x 80       | 288 x 160      | 60 x 80            | 160 x 120                |

| FPS @ max res  | 2 to 17 fps    | 50 fps         | 10 fps             | -                        |

| Min resolution | 80 x 143       | 80 x 143       | 60 x 80            | 160 x 120                |

| FPS @ min res  | 30 fps         | 50 fps         | 10 fps             | -                        |

| Memory size    | Int.           | Ext. FIFO      | -                  | SRAM                     |

|                | 138 bytes      | 384K x 8bit    |                    | 128K x 8bit              |

| Com port       | 115200bps      | 115200bps      | -                  | 57600bps                 |

On-board image processor poses certain challenges in the following areas:

**Speed:** Real-time images are to be computed at high frame rate for closed loop vision control.

**Power:** The power consumption should be reduced to the minimal for longer battery life. The power consumed by the processor depends on the algorithm, switching frequency (clock frequency) and the switching voltages.

Memory requirements: Vision algorithms often demands more memory compared to other embedded applications. Temporary storages are often used to store image buffers at different stages of the image transformation and analysis. Generally, First-In-First-Out (FIFO) or dual ported Random Access Memory (RAM) are used to buffer the input image for the subsequent processing.

**Size constraints:** The size of the embedded machine vision should be small enough to fit onto miniature mobile robot.

With the four major constraints specified, it is noted that there is a relationship between all the four constraints. The area of the IC chip is related to the clock speed, amount of memories and logic elements within the die. By lowering the clock speed of the processor, the energy consumption is also reduced accordingly. As a result, this research focuses on the reduction of clock speed and memory requirements for various image processing algorithms.

#### **1.2** Different Architectures for Image Processing

The computational demands associated with high performance image processing has led to several architectures being proposed. Namely, the Microprocessor Architecture, the dedicated Digital Signal Processing (DSP) Processor, Application Specific IC (ASIC) Architecture and the Reconfigurable Architecture. These mentioned architectures are targeted for different types of processing requirements. Figure 1.3 shows the relationship of the different architectures in programmability vs the data parallelism space [20][19].

Parallelism

Figure 1.3: Programmability vs parallelism

#### 1.2.1 Microprocessors

The Microprocessor can be further categorised into four different architectures. These have been named in Flynn's classification [20][4] as: Single Instruction Single Data (SISD), Single Instruction Multiple Data (SIMD), Multiple Instruction Single Data (MISD) and Multiple Instruction Multiple Data (MIMD). The latter two have generally been used for demanding image processing algorithms.

General purpose computer systems using microprocessor technology are commonly used in the industry. This popular platform provides well established tools and rapid implementation of image processing applications. In addition, the applications are portable to future variants of such system.

The microprocessor is also often used in industry applications. The keys factors for its popularity are: short time to market, low setup cost, backward compatibility, commercially available image processing tools and software modules. In addition, the doubling of the processor speed in every 18 months gives them the luxury of improving system performance with near zero development cost.

To a large extent, the performance of such systems greatly depend on the computing speed of the processor. This solution does not actually map the software with appropriate hardware functional units to exploit both data and computational parallelism. Rather, it is an interpreter and translator of algorithms being read from memory. The microprocessor architecture requires many load, store and branch operations. These operations are used to perform various data manipulations. Hence, most of the computing time is spent on "overhead" instructions rather than the actual processing of data. As a result, the silicon area to data processing ratio is low. Most of the silicon area is used for communication, control logic, functions and the management of the flow of computing instructions. As such, in microprocessor implementations, most computationally complex applications spend 90% of execution time on 10% of the codes [22]. Therefore, research has been carrying out in parallel processor architecture. It is a well-known fact that parallel processors always perform better than a microprocessor.

#### 1.2.2 DSP Processors

Signal processing applications, by their very definition, process signals which are generated in real time. Traditionally, much signal processing work has operated on one-dimensional signals, such as speech or audio. To obtain real time performance for these applications, processors with architectures and instruction set specially tailored to signal processing began to emerge [5]. Typical features included multiply and accumulate instructions, special control logic and instructions for tight loops, pipelining of arithmetic units and memory accessing, and Harvard architecture (with separate data and program memory spaces). More recent designs (such as some in the Texas range of DSP processors) have featured explicitly for (twodimensional) image processing, particularly with image compression in mind.

When carefully programmed to exploit the special architectural features, these

processors can yield very impressive performance rates. However, there is a cost. The programming model at the machine level is much more complex than for traditional microprocessors. Highly optimizing compilers are needed if the processor's potential is to be realized with a high level language.

#### 1.2.3 Application Specific Integrated Circuit

Application Specific Integrated Circuit (ASIC) has the highest degree of computational parallelism. This device is usually chosen in cases whereby sequential processors have reached the performance limits. Any further improvement in performance can only be obtained by adding more processors. For this reason, parallel processing techniques have been widely studied for image processing applications [21]. In some cases, techniques have been developed specifically for image processing; in other cases, standard parallel processing techniques have merely been applied.

#### **1.2.4** Reconfigurable Architecture

In the mid-1980s, a new technology for implementing digital logic was introduced: the Field Programmable Gate Array (FPGA). The introduction of FPGA provides the flexibility to configure the hardware. The FPGA consists of hardware logic that are unconnected. It can be programmed to interconnect the various available logic components to implement any desired digital function. For the advantages it offers, the reconfigurable devices open a new area of research in custom and parallel computing [29][6][11].

The rapid progress in microelectronics and FPGA provides an architectures that have higher speed and density. Hence, the FPGA architectures are potential candidates for computational intensive applications. They also provide customization of hardware without the risk and high setup cost involved with ASIC implementation. The main advantage of FPGA-based processors is that they offer near supercomputer performance at relatively low costs [59]. FPGAs provide the benefits of customized hardware architecture and at the same time allowing for dynamic reprogrammability. It is an important characteristic that meets the changing requirements of the wide range of applications.

Reconfigurable architectures can be designed to achieve different levels of performance for a given application. The custom logic are designed to exploit parallelism at different areas and levels of the application. Of particular importance and interest, is the use of these techniques to produce compact and fast circuit. Such mapping tends to be most successful for implementing algorithms with high degrees of parallelism [10].

Figure 1.4: Fixed Arithmetic Logic Unit (ALU) vs Custom ALU

To implement efficient solutions, the algorithm and hardware architecture must be well matched to improve overall computational efficiency and concurrency. This can be achieved for algorithms with high degree of regularity that are identified to exploit its parallelism. The operations are mapped into custom functional units to achieve higher performance compared to the fixed processing unit. Figure 1.4 demonstrates the example of computational efficiency of processing three pixels in a single cycle, as compared to multiple cycles for a fixed Arithmetic Logic Unit (ALU).

#### **1.3** Data Processing at Different Level

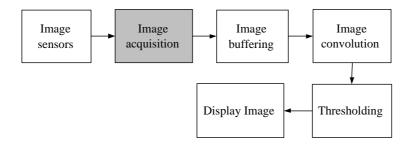

Image processing consists of several sub-system operations. They are generally categorized into pre-processing, segmentation, feature extraction and classification. The process is sequential with each step gradually transforming the image data to give a higher level of abstract image information.

Figure 1.5: Data processing at different level

The amount of data to be processed is modelled using a pyramid architecture as shown in Figure 1.5. The bottom level of the pyramid represents the data volume to be processed and similarly the top level of the pyramid represents abstract information derived from the image. The lowest level comprised of the raw pixels acquired from the source image. Intermediate level 1, 2, 3 are typically pre-processing, segmentation, feature extraction and classification. The final level produces abstract data as a feedback control signal in vision servo.

The vision task at the lowest level is often identified as the process that consumes the most computing resource. The Low level tasks consist of pixel-based transformation such as filtering and edge detection. These tasks are characterized by large amount of data pixels, small neighbourhood operators, and simple structured operations (e.g multiply and add functions) [31]. Computational intensive and yet repetitive algorithms fall in this category at the lowest level of the pyramid; convolution, thresholding and component labelling. On the other hand, higher level tasks are more dynamic in nature. These tasks are more decision oriented and do not have a repetitive execution of a set of algorithms. The intensive processing of image at each stage, requires efficient architectural support for frequently accessed functions. The first step to exploit parallelism is to identify the sub-system that demands heavy workload. Next, the critical section of the algorithm within the sub-system must be identified as well. With reference to Figure 2.2, performance improvement will be significant when exploiting parallelism in Level zero. The following sections discuss about the hardware architecture design for preprocessing, edge detection and boundary detection tasks. Figure 1.6 shows the different stages of image processing for object recognition.

Figure 1.6: Stages for image processing

Researchers have recognized that a new architecture is necessary for real-time image processing. Several optical sensors are developed, to perform on-chip preprocessing task at the pixel level. This dramatically simplify the extraction of the desired information [34][33]. Any image processing task that is performed within the sensor itself reduces the communication and processing workload of the host controller.

On-chip processing has an important role to play in the viability of visual servoing applications. With the increasing accessibility of custom logic design, this makes the development of smart image sensing architectures attractive.

#### **1.4** Motivation and Contribution

Mobile robots with size constraints generally have limitations on the kind of hardware that can be used for the vision system. As a result, most of the vision processing operations have to be performed off the board, i.e. on a host computer. To achieve a self-contained and fully autonomous robot, real-time vision processing is required. At many times, to achieve the desired performance, a high speed processor is required.

Machine-vision applications that demand computational expensive algorithms can be accelerated by custom computation units. With the emergence of reconfigurable devices, many of the on-going research efforts use FPGAs to increase the performance of computationally intensive image processing applications. Such approaches can reduce the necessity of employing high-end processors.

The aim of this research is to investigate the methods of achieving the desired performance, without utilizing high-end microprocessors. Techniques of exploring computationally efficient algorithms and exploring various hardware architectures are studied. Low-level tasks consisting of pixel-based transformations, such as filtering, image segmentation, image convolution and edge detection algorithms are implemented in this work.

With the aim of exploring custom hardware architectures, an analytic mathematical model is derived. The model is used to study the required processing speed of Digital Signal Processor and memory requirements. Additionally, the mathematical model helps to analyse the performance of custom architecture without the need for a simulation model.

Together with the mathematical model and the selected FPGA board, memory chip and CMOS image sensor, the custom architecture is tested in both simulation environment and actual hardware setup.

Using the available FPGA logic resources, the custom architecture is configured to exploit the computation parallelism. The limitations discussed in section 1.1 are addressed in the proposed design. Real-time VGA images is computed at a very high speed of 30 fps. Furthermore, the memory optimisation technique employed allows all image buffers to fit within the available on-chip memory. Collectively, this work addresses three main constraints of processing real-time images in embedded system. These are computational speed, memory size and physical size constraints.

#### 1.5 Thesis Outline

This thesis is organised as follows, Chapter 2 introduces and evaluates on the various type of image sensor, FPGA and development tools required for the experimental setup. It also includes the introduction to the different types of colour space.

Chapter 3 presents an analytical mathematical model to estimate the various performance parameters associated real-time image processing. The model allows system designers to estimate the required memory size and processing frequency of a given microprocessor architecture. In Chapter 4, the image acquisition, compression, buffering and image convolution are studied. Custom architecture are designed with the considerations of optimising for logic and memory resources.

Chapter 5 is devoted to the FPGA Implementation of Parallel Architecture. Specifically, the low pass filter, edge detection and thresholding algorithm are investigated. The parallel architecture is designed to accomplish high performance image processing task. Methods and techniques are investigated to implement the design with the minimal resources needed.

Finally the thesis is concluded in Chapter 6 with a brief on the major results and observations obtained and an outline of possible directions for future work.

# Chapter 2

# System Level Architecture Design

The chapter discusses about the various type of image sensor, FPGA and development tools required for the experimental setup. In additional, the different colour space that are suitable for image processing is also included.

#### 2.1 System Components Studies

Selecting the proper hardware components is one of the critical decisions that controls the success or failure of the project. There are many criteria to be considered in the process of selection. The few main considerations are component size, memories size, sensor resolution and frame rate.

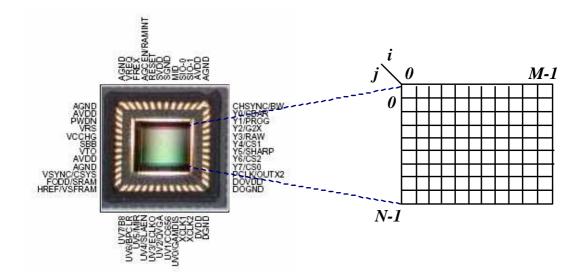

There are various types of image sensors available in the market. A comparison of CCD image sensors and CMOS image sensor is conducted. Furthermore, the various types of CMOS sensor are narrow down for selection. In this project, the selection of image sensor is very much focused on the resolution and the interface to the FPGA.

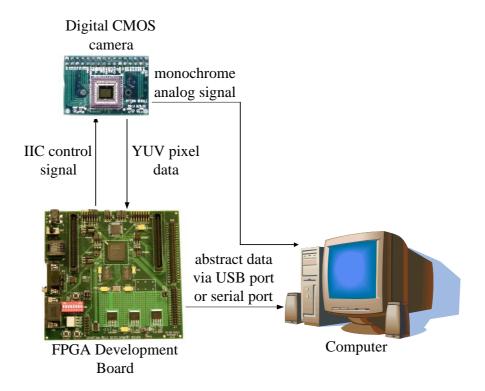

The following sections discuss about the various image sensor, memories and FPGA development board available in the market. Figure 2.1 shows the overview

Figure 2.1: MicroViz setup configuration

of the physical interface circuitry between the various components.

#### 2.1.1 Image Sensors

CMOS sensors rose to the top of the hype curve in the 1990s, promising to do away with their predecessors, the CCD sensor. CCDs traditionally use a process that consumes more power as compared to CMOS image sensors. It consumes as much as 100 times more power than an equivalent CMOS sensor [37]. As a result, CMOS sensor with low power dissipation at the chip level, coupled with its small form factor and the ability to deliver high frame rate, emerges as the suitable candidate for many low power mobile applications.

A major advantage of CMOS over CCD camera technology is its ability to integrate additional circuitry on the same die as the sensor itself. This makes it possible to integrate the Analog to Digital Converters (ADCs) and associated pixel grabbing circuitry. Thus a separate frame grabber is not needed [2].

A study is conducted to evaluate the suitability of various image sensors for this purpose. The six different sensors are shown in table 2.1.

| Supplier   | Model     | Resolution    | AD      | Output | Frame rate |

|------------|-----------|---------------|---------|--------|------------|

|            |           |               |         | format |            |

| VLSI       | VV6300    | $160 \ge 120$ | 8 bit   | Bayers | 60  fps    |

| Vision     |           |               |         | RGB    |            |

| Hynix      | HV7131GP  | $652 \ge 492$ | 10  bit | YCrCb, | 30  fps    |

|            |           |               |         | RGB    |            |

| Pictos     | MK00-D190 | $640 \ge 480$ | 10  bit | RGB,   | 30  fps    |

|            |           |               |         | YCrCB, |            |

|            |           |               |         | JPEG   |            |

| Kodak      | KAC-0311  | $640 \ge 480$ | 10  bit | Bayers | 60  fps    |

|            |           |               |         | RGB    |            |

| OmniVision | OV6620    | $356\ge 292$  | 10  bit | YCrCb, | 60  fps    |

|            |           |               |         | RGB    |            |

| OmniVision | OV7620    | $664 \ge 492$ | 10  bit | YCrCb, | 60  fps    |

|            |           |               |         | RGB    |            |

Table 2.1: Comparison of available on-board vision processor

The OV7620 CMOS image sensor from OmniVision is chosen since is offers the best configurations based on its resolution, frame rate and data format. The OV7620 is able to configure the data output in RGB bayers format or YCrCb format for different types of image processing requirements.

Figure 2.2: OV7620 Image sensor and FPGA

The OV7649 (Figure 2.2) is a 1/3" color camera module with digital output

ports. The digital video port supplies a continuous 8/16 bit-wide image data stream. All camera functions, such as exposure, gamma, gain, white balance, color matrix, windowing, are programmable through the Inter-IC Connection (IIC) interface.

Figure 2.3: Timing waveform of pixel data bus [36]

The OV7620 supports some flexible YCrCb 4:2:2 output format. For instance, for every Pixel Clock (pclk) cycle, the 16 bit pixel data is placed on the Y and UV data bus. Using the YUV 4:2:2 subsampling format, the sequence output is given as

Y (8 bit databus) : Y0 Y1 Y2 Y3 UV (8 bit databus): U0 V1 U2 V3

Hence, the respective Y,U and V is mapped to the following four pixels:

| Pixel 0    | Pixel 1    | Pixel 2    | Pixel 3    |

|------------|------------|------------|------------|

| [Y0 U0 V1] | [Y1 U0 V1] | [Y2 U2 V3] | [Y3 U2 V3] |

|            |            |            |            |

#### 2.1.2 Memories

In any image processing system, buffering the input image signal is necessary. The camera module produces 640 x 480 (VGA) colour pixels at a rate of 30 frame/sec. In order to process an entire image, the entire image is often buffered prior to any processing. For a given data output format of YCrCb 4:2:2, a pixel consists of 16 bits. Hence, from the calculations, the data to be stored is very large.

Number of pixel per frame: 640x480=30,7200 pixels Size per frame (RAM):  $30,7200 \ge 16$  bit= 4.9152 Mbit = 600 KBytes Buffer Memory for processed image: 614.4 KBytes

A memory storage space of 4.9152M bit is required to store an entire frame. These values exclude data buffers and other overheads. The significant huge amount of memory space seriously poses a problem in the embedded world, where memories are very expensive.

#### 2.1.3 FPGA Development Board

A survey is performed to evaluate the different types of FPGA available in the industry. There are various vendors that manufacture FPGAs. The more prominent ones are Xilinx, Altera, Cypress and Quicklogic.

Xilinx and Altera are the leading manufacturers of FPGAs. They provide extensive support for both industrial and academic developers. As a result, the Spartan-IIE from Xilinx is selected as a suitable platform for this research project. The Spartan-IIE system board connected together with the CMOS sensor board are shown in Figure 2.4.

The Spartan-IIE system board utilizes the 300,000-gate (XC2S300E- 6FG456C) with a 456 fine-pitch ball grid array package. The high gate density and large number of user I/Os allows complete system solutions to be implemented in the

Figure 2.4: MicroViz Prototype board

low-cost Spartan-IIE FPGA. The board also supports the Memec Design P160 expansion module standard, which allows application-specific expansion modules to be easily added.

The Spartan-IIE incorporates several large block RAM memories. These complement the distributed RAM LUTs that provide shallow memory structures implemented in CLBs. Block RAMs are organized in columns. Most Spartan-IIE devices contain two such columns, one along each vertical edge. The XC2S400E has four block RAM columns. The XC2S300E has a total of 16 RAM blocks [30].

#### 2.2 Simulation and Development Tools

The following section discussed about the programming and analysis tools used in this research project. The selection of Hardware Description Language (HDL) and the introduction to FPGA design flow is also covered in this section.

#### 2.2.1 Programming Tools

There are many development and analysis tools required for this research as shown in Table 2.2. Simulations necessary prior to actual implementation. The Visual C/C++ is used as a platform to test and evaluate any new algorithms. After which, the equivalent verilog codes are written according to those verified in C. The verilog codes are simulated using ModelSim, producing simulation waveform of data signals for verification purpose. The Xilinx Integrated Software Environment (ISE) translates verilog codes into hardware logic circuits. This process is often known as synthesis. After the FPGA is programmed, the data signals are verified using the oscilloscope, ANT16 logic analysis and the Chipscope Pro. The schematic design and PCB is designed using Protel 99SE.

Table 2.2: Development and analysis tools

Visual C/C++ 6.0: For simulation of algorithm in C

ModelSim: Simulation package for vhdl and verilog code

Xilinx ISE 6: Design Entry, design synthesis and device programming.

Xilinx EDK 6: Hardware specifications, MicroBlaze microcontroller

Chipscope Pro: Internal register Logic Analyzer

ANT16: External data bus Logic Analyzer

Irfanview: Portable Pixel Map file image viewer

Protel 99 SE: Schematic entry and PCB design

#### 2.2.2 FPGA Design Flow

The FPGA design flow is illustrated in Figure 2.5. An idea or concept is translated into Verilog HDL. This language is often used in the design at an entry stage.

Alternatively, Electronic Design interchange Format (EDIF) or schematic entry is used for design entry. Following that, the user constraints file (ucf) specify the timing and pin location constraints. A logic synthesis tool reads a HDL entry and produces a netlist consisting of a description of basic logic cells and their interconnections (Figure 2.6).

The implementation of a digital logic design with a FPGA involve a design flow similar to ASIC design flow [28].

Figure 2.5: FPGA design flow

The mapping function allocates Configuration Logic Blocks (CLB) and Input Output Blocks (IOBs) resource for all basic logic elements in the design. It considers the available resources together with the constraints specified and map the digital logic design into the targeted FPGA chip.

The Place and Route (P&R) process decides the location of the cells in a block and places the connections between the cells and blocks. The generated bit stream file is programmed into the FPGA via a Joint Test Access Group (JTAG) connection. The results are verified using Chipscope Pro, PC-USB Logic Analyser and oscilloscope. This process is often repeated for many iterations to yield satisfactory results.

The Xilinx RAM-based FPGA features a logic block that is based on LUTs. A

```

(cell LUT4 (cellType GENERIC)

(view view_1 (viewType NETLIST)

(interface

(port I0 (direction INPUT))

(port I1 (direction INPUT))

(port I2 (direction INPUT))

(port I3 (direction INPUT))

(port O (direction OUTPUT))

)

)

)

(cell MUXCY (cellType GENERIC)

(view view_1 (viewType NETLIST)

(interface

(port DI (direction INPUT))

(port CI (direction INPUT))

(port S (direction INPUT))

(port O (direction OUTPUT))

)

)

)

```

Figure 2.6: Gate level netlist

LUT is a small one bit wide memory array, the address lines for the memory are inputs from the logic block and the one bit output from the memory is the LUT output. A LUT with K inputs would then correspond to a  $2^k \ge 1$  bit memory. It can realize any logic functions of its K inputs by programming the logic function's truth table directly into the memory.

Each Spartan-IIE CLB contains four Logic Cells (LCs), organized in two similar slices; a single slice is shown in Figure 2.7. This arrangement allows the CLB to implement a wide range of logic functions. Furthermore, each LUT can provide a 16 x 1 bit synchronous RAM. The two LUTs within a slice can be combined to create a 16 x 2-bit or 32 x 1 bit synchronous RAM, or a 16 x 1 bit dual-port synchronous RAM [30] [29].

Figure 2.7: Configuration Logic Block [30]

### 2.2.3 Verilog vs VHDL

Schematic capture and hardware description language are used for design entry. The two industry standard hardware description languages are VHSIC HDL (VHDL) and Verilog.

VHDL was developed by committee intended for documenting digital hardware behaviour. It originated out of the Very High Speed Integrated Circuit (VHSIC) Program as a part of a US Department of Defense Project in 1981. Although it was adopted by many Electronic Design Automation (EDA) companies and carried strong support from the European electronics market, VHDL had significant deficiencies. There was no facility for handling timing information [25].

On the other hand, Verilog HDL came from the commercial world and was developed as part of a complete simulation system. It was also developed to describe digital based hardware systems. The Verilog HDL is used extensively, since launched in 1983 by Gateway. It became the IEEE standard 1364 in December 1995 [26].

A comparison is made between the two HDL lanaguages is shown in Table 2.3. It is also noted that there are increasing number of universities adopting to teach

|                                                 | VHDL                                                                                    | Verilog                                                           |  |  |  |  |

|-------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------|--|--|--|--|

| Learning curve                                  | A strongly typed language<br>with heavy syntax                                          | Easy to pick up for those with<br>C language background           |  |  |  |  |

| Design<br>reusability                           | Procedures and functions may<br>be placed in a package                                  | Define modules to reuse<br>design                                 |  |  |  |  |

| Datatypes                                       | Dedicated functions are<br>needed to convert objects<br>from one datatype to another    | Easy to use and geared<br>towards modelling hardware<br>structure |  |  |  |  |

| HDL modelling<br>capability                     | Good for modelling large<br>design structure, unable to<br>provide gate level modelling | Developed with gate level<br>modeling in mind                     |  |  |  |  |

| Usage in Digital<br>Design Market<br>world wide | 40% (mainly in europe,<br>military and academic<br>institutes)                          | 60% (mainly in US and Asia companies)                             |  |  |  |  |

#### Table 2.3: Comparison of VHDL and Verilog

this language as part of their advanced Electrical Engineering programs; and to dated more than 75 companies offer Verilog HDL products and services [25].

As a result, Verilog is chosen for this research project. The primary reasons are the ease of usage, which is similar to C and the popularity of its usage in the industry.

# 2.3 Image Representation

Images are represented in a form of analogue or digital signals. Analogue signals are traditionally used in many types of video equipment, and mainly used for television broadcasting.

However, in recent years, digital image and video are rapidly taking over many applications. The most common digital signals used are RGB and YCbCr. The RGB format is commonly used for display devices such as LCD display panels, while the YCrCb is often used for data transmission and data processing.

A digitised colour image is represented as an array of pixels, where each pixel contains numerical components that define a colour. The images captured from the camera will consist of these array of pixels.

After an image is captured, it is represented in various formats. Typically, the binary, greyscale, Red Green Blue (RGB), Hue Saturation Intensity (HSI) or the YCrCb format are used (Figure 2.8). The binary image format represents the simplest form of an image, with a one bit representing one pixel. Hence, for a given image of 640 x 480, is represented by 38400 bytes. Although a binary image offers a small file size, there is a significant loss in image quality.

Figure 2.8: Colour Space

In a typical 8 bit grey scale image, there are 256 shades of grey. Each pixel

(a) (b) (c)

represents different shade of grey according to its brightness.

Figure 2.9: (a)RGB colour image (b)Greyscale image (c)Binary image

Colour image can be represented in RGB, YCrCb or HSI colour format. RGB is typically used to display images, YCrCb for transmission of image data and HSI for image processing. Figure 2.9 shows the different data representation of image in binary, greyscale and RGB colour format.

#### **RGB** colour space

The RGB space is widely used throughout computer graphics. The individual component are added together to form a desired colour, it is represented using cartesian coordinate system as shown in Figure 2.10.

Figure 2.10: RGB colour space [35]

However, RGB colour space is not very efficient when dealing with real world images. Processing an image in the RGB colour space requires the modification of all three colour components [27]. For instance, to increase the intensity or colour of a given pixel, all three components must be read, calculate the new value and written back into the memory for each pixel. For this reason, other colour space is derived from the basic RGB colour space to ease date processing. The HSI and the YCrCb colour space is discussed in the following section.

#### HSI colour space

HSI is preferred in some systems as it separates apparent "colour" from "brightness". Colour in HSI space is relatively more robust to illumination, lights and noise as compared to RGB is more sensitive to highlights and shadow. The HSI colour space is shown in Figure 2.11.

Figure 2.11: HSI colour space [35]

#### YCrCb colour space

The image data represented in YCrCb color space is sampled in 4:2:2, 4:2:0 or 4:1:1 sampling format. In YCrCb 4:2:2 format, for every four samples of Y component, there are two Cb and Cr. Each sample is typically 8 bits. This positioning of YCrCb colour component sampling offers a reduction of bandwidth for transmission. This is due to the fact that YCrCb 4:2:2, 4:2:0 and 4:1:1 use a lower sampling rate for the chromatic components, hence require less storage space and transmission bandwidth.

The YCrCb colour space is also derived from the RGB colour space. The Y component is the luminance, Cr represents a colour value consisting of the luminance deducted from the color red (R-Y) and Cb represents the color value of the luminance deducted from the color blue (B-Y).

The next chapter presents an analytical mathematical model to estimate the various performance parameters associated real-time image processing. The model allows system designers to estimate the required memory size and processing frequency of a given microprocessor architecture.

# Chapter 3

# An Analytic Model for Embedded Machine Vision

# 3.1 Introduction

This chapter focuses on the performance of the embedded machine vision. A model is introduced to estimate the performance and memory resource requirements.

In literature, there are three basic techniques for performance evaluation; namely measurement, simulation and analytic modelling [40] [41].

An analytic model is often used to predict performance. It can evaluate the performance with minimal efforts and costs over a wide range of choices for system parameters and configurations [42]. For various processor architectures, the key resources and workload requirements can be analytically modelled with sufficient realism to provide insight into the bottlenecks and key parameters affecting the system performance [46]. However, such approach is impractical, if the vision system is modelled in great details [40].

An analytic model is derived to provide a mathematical description of the vision system. Such approach is considered being far less time consuming and more flexible compared to simulation based methods. A model is proposed to analyse the performance of processing real-time images in embedded systems. Last but not least, the limitations of general purpose processors are also discussed.

Section 3.2 presents a model to determine the optimal memory size for buffering real-time images. Section 3.3 presents another model to calculate the processing frequency required to perform certain algorithms. Specifically, image segmentation and convolution algorithms are analysed in Section 3.4 and 3.5 respectively.

# 3.2 Analytic Model to Determine Image Buffer Size

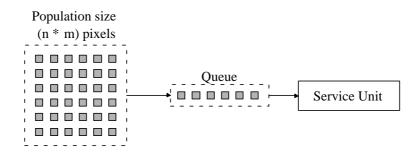

#### 3.2.1 Concept of Queuing Theory

The image acquisition process is modelled using a producer and consumer process. The CMOS image sensor produces image data and the image acquisition consumes image data. Due to the difference in arrival and consumption rate, the producer and consumer processes are buffered by a message queue. A message queue is a set of memory locations that provides temporary storages for data that are being passed from one process to other. In general, a producer places new message into the queue while the consumer acquires the message by removing it from the queue. For this approach, a First-In First-Out(FIFO) RAM is commonly used.

It many embedded systems, it is required to estimate the maximum number of messages that will queue in a system. Empirical methods to estimate the required capacity are not reliable [44], and these methods are often not able to determine the optimal memory size for different algorithm. Furthermore, empirical methods are often conducted using the actual experimental setups or simulation models. For these reasons, an analytic model is derived from queuing theory to compute the maximum message queue length. Queueing theory plays a very important role in analytical modelling [42]. The concept is used as the fundamental formulae to calculate the system requirements for real-time operations.

The system is modelled using the queueing analysis as illustrated in Figure 3.1. The definitions used in this model are as follows:

$n_q = no. \ of \ jobs \ in \ queue$   $\lambda_b = arrival \ rate \ of \ pixel \ during \ burst$   $\mu_b = service \ rate \ of \ pixel \ during \ burst$   $t_e = time \ require \ to \ empty \ buffer$   $t_b = burst \ time$   $t_o = time \ of \ occurence$   $t_s = service \ time \ per \ pixel$   $n_{ipp} = no. \ of \ instructions \ per \ pixel$   $n_{cpi} = no. \ of \ clock \ per \ instruction$   $t_{clk} = processor \ clock \ cycle$  $f_{clk} = clock \ frequency$

Figure 3.1: Queue model of vision system

The image sensor, or producer is said to have a population size of  $n^*m$  messages. If the messages arrive at a rate faster than the system can service, a queue is formed. The sudden arrival of messages for a period of time is call a burst. During the burst  $t_b$ , a buffer is required to absorb any excess of production of pixels over the consumption. At the beginning of each burst, the message queue should be empty. The pixels will be placed into the queue synchronous to the clock of the image sensor, which is also refer as the arrival rate  $\lambda_b$ . At the same time, some pixels are consumed by the image acquisition routine, at a consumption rate  $\mu_b$ . If  $\lambda_b \leq \mu_b$ , the queue will not grow, else the queue will grow. In the situation where the pixels arrive at a rate faster than it can handle for a long enough period of time, the messages continue to stack up in the queue, to a point overflow occurs.

$$n_q(t) = \lambda_b t - \mu_b t \tag{3.1}$$

Equation 3.1 is used to determine the number of messages  $n_q(t)$  in the queue at time t, where  $\lambda_b t$  is the number of messages arrived in the queue at time t and  $\mu_b t$  is the number of messages consumed from the queue at time t.

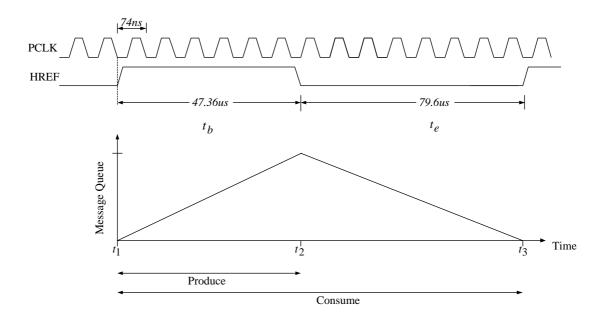

#### 3.2.2 Row buffering

A row buffer is proposed in this work to acquire a single row of pixels and process it before acquiring the next row of pixels.

Figure 3.2: Burst time and emptying time

Figure 3.2 illustrates the producer and consumer of pixels in the message queue. It shows that the burst  $t_b$  is 47.36 us and the maximum time allowed for the consumer to service all pixels is  $t_b + t_e$ . The required memory size can be determined by the maximum length of a queue. From Figure 3.2, it is noted that the queue length peaks after the last pixel is place in the queue, at t=t2.

At  $t_1$  (Figure 3.2), the first pixel is placed into the message queue. For every *PCLK*, a pixel arrives at the message queue when HREF is high. At the same time, some of these pixels are consumed in a First-In First-Out order. The message queue continues to grow as long as the arrival rate is greater than consumption rate (service time). At end of each burst, immediately after the last pixel is placed into the message queue at  $t_2$ , the message queue stop to grow. The production rate is equals to zero while the consumption rate remains the same. At this point, the total no. of messages remaining in queue is

$$n_q(t_b) = \lambda_b t_b - \mu_b t_b$$

=  $(\lambda_b - \mu_b) t_b$ , (3.2)

where

$$\lambda_b = \frac{w_i}{t_b} , \qquad (3.3)$$

$$\mu_b = \frac{w_i}{t_b + t_e} , \qquad (3.4)$$

The maximum time given to the consumer to empty the message queue before the arrival of the next pixel is  $t_e = t_2 - t_1$ . Hence, the worst case consumption rate  $\mu_b$  is given in (3.4), where  $w_i$  is the image width (number of pixels in a row).

If a new burst begins before the queue is totally emptied, the allocated message queue will not have the capacity to store all pixels for the next row. As a result, buffer overflow will occurs. Hence, it is important to note that the all message should be consumed within the allocated time.

If the  $\frac{\lambda_b}{\mu_b}$  ratio is large, the emptying time will be very much longer than the burst time. As a result, the maximum queue length increases accordingly.

With (3.3) and (3.4),  $n_q(t_b)$  is simplified to

$$n_q = (\lambda_b - \mu_b) t_b$$

$$= \left(\frac{w_i}{t_b} - \frac{w_i}{t_b + t_e}\right) t_b$$

$$= \frac{w_i t_b (t_b + t_e - t_b)}{t_b (t_b + t_e)} ,$$

$$n_q = \frac{w_i t_e}{t_b + t_e} \tag{3.5}$$

For instance, if  $t_e$  is equal to  $t_b$ , the messages are consumed at half the rate of the arrival rate. As a result, the maximum queue length is half of the image width as shown in (3.6).

$$n_q = \frac{w_i \ t_b}{2t_b} = \frac{1}{2} \ w_i \tag{3.6}$$

In this example (Figure 3.2), with  $t_b = 47.36 \ us$ ,  $t_e = 79.6 \ us$  and  $w_i = 640$ , the required buffer size calculated with (3.5) is found to be 402 pixels. With this model, the buffer size can be adjusted accordingly by reducing the  $t_e$  parameter. However, it should be noted that reducing  $t_e$  results in the reduction of service time. The next section will present a model to illustrates the effects of  $t_e$  on the processor clock frequency.

# 3.3 Analytic Model to Determine Computational Speed

In many embedded system design, the processor and its clocking frequency are generally determined either by simulation or empirical methods. Many at times, simulation models may not be available. As mentioned earlier, empirical methods are not reliable and do not address the issue of scalability. In this section, a model is derived to estimate the required processing speed.

With the consumption rate  $\mu_b$  and the no. of message in the queue  $n_q$ , the time required to empty the queue is

$$t_e = \frac{n_q}{\mu_b} \tag{3.7}$$

Together with the concept and equations derived in the previous section, the time required to service a pixel can be computed as follows:

$$n_q = (\lambda_b - \mu_b) t_b , \qquad (3.8)$$

$$\lambda_b = \frac{1}{t_{pclk}} , \qquad (3.9)$$

$$\mu_b = \frac{1}{t_s} , \qquad (3.10)$$

where  $t_{pclk}$  is the inter-arrival time of each pixel, and  $t_s$  is the time needed to service one pixel. By substituting (3.8),(3.9),(3.10) into (3.7),  $t_s$  is simplified as

$$t_{e} = t_{s} [(\lambda_{b} - \frac{1}{t_{s}}) t_{b}]$$

$$= t_{s} t_{b} \lambda_{b} - t_{b}$$

$$t_{s} = \frac{t_{e} + t_{b}}{t_{b} \lambda_{b}}$$

$$(3.12)$$

With reference to Figure 3.2, a pixel arrives at an interval of 74 ns. The burst time  $t_b$  is 47.36 us and the emptying time  $t_e$  is 79.6 us. Hence, the service time per pixel (3.12) is calculated to be 198.37 ns.

To estimate the processing speed required to compute one pixel, the number of instructions to process a single pixel must be known. An image algorithm may consist of several instructions to compute one pixel. In additional, a single instruction may require of more than one clock cycle to complete.

In general, the target processor is first identified and the instruction set architecture is studied. With the instruction set, the no. of instructions needed to compute a single pixel is estimated. Thus, the service time per pixel is expressed as

$$t_s = n_{ipp} \ n_{cpi} \ t_{clk} \ , \tag{3.13}$$

and together with (3.12) and (3.13), the required processing clock frequency is expressed as

$$f_{clk} = \frac{n_{ipp} n_{cpi}}{t_s} ,$$

$$= \frac{t_b \lambda_b n_{ipp} n_{cpi}}{t_e + t_b} ,$$

(3.14)

where  $n_{ipp}$  is the number of instructions per pixel and  $n_{cpi}$  is the number of cycles per instruction.

Lastly, the production rate and consumption rate ratio are found to be

$$\frac{\lambda_b}{\mu_b} = \frac{198.37}{74} = 2.68$$

The analytic model discussed in this section provides an estimation of the clock frequency required to perform certain image processing algorithm. With this model, an in-depth analysis of image segmentation and image convolution algorithm are discussed in the following sections. The clock frequency is calculated based on a selected processor architecture and image algorithm is written in C. As such, this will assist in the selection of processor architecture, instruction set and most importantly the optimal processing speed.

### 3.4 Analysis of Image Segmentation Algorithm

The segmentation process partitions an image into meaningful regions [24]. The nature of this process involves scanning of each pixels. Thresholding is one of the most important approaches in image segmentation. It is a process to convert greyscale images to binary images. Typically, a greyscale image is thresholded to obtain a binarised version of the image that consists of only foreground and background. To obtain a binary image which consists of only foreground and background pixel, a threshold value, T, is used to partition the image into two regions, such that

> If  $f(x, y) \ge T$  then g(x, y) = 1If f(x, y) < T then g(x, y) = 0

where the image g(x, y) denotes the binarised version of image f(x, y).

A simple experimental setup for image segmentation is simulated in Visual C/C++ and MicroChip MPLab. The program reads in the raw image data, converts the Red, Green, Blue (RGB) primaries to greyscale image and performs image

(a) (b)

thresholding. Finally, the program writes to an image file for viewing. The result is shown in Figure 3.3.

Figure 3.3: Thresholding

For instance, a real-time vision system with a resolution of 640 x 480 is required to be processed at a rate of 30 fps (frames per second). The analytical model is used to estimate the processing clock speed needed for handling real-time image thresholding process.

#### 3.4.1 Computation using microprocessor

Image thresholding can be performed using a Digital Signal Processor. Often, such architectures requires several load, store and branch operation to perform data manipulation.

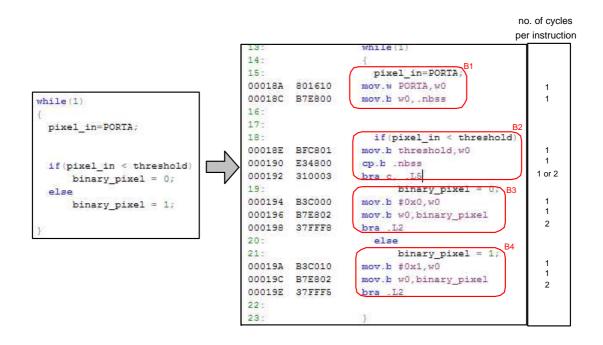

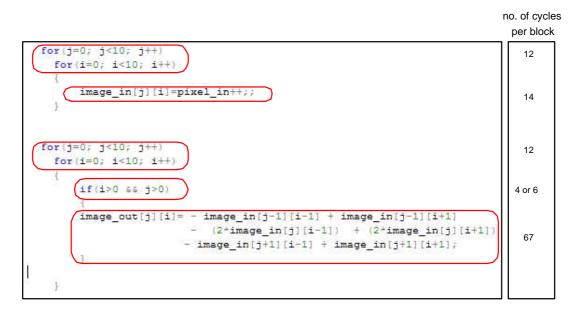

The dsPIC30F6012 DSP controller from Microchip Technology Inc. is used as a target chip in this work. It is a 16 bit Harvard RISC machine designed for embedded system. The processor can reach up to the speed of 30 MIPS. The simplified threshold algorithm written C is translated to assembly language as shown in Figure (3.4). In addition, the number of cycles to complete a specific instruction is also shown.

A further analysis of the program flow reveals that the computational time of each path is different. For instance, if  $pixel_in < threshold$ , the branch instruction is not taken and the program executes through B1, B2, B3. The total time to

Figure 3.4: Assembly code representation of C program

complete one iteration is 9 clock cycles. Otherwise, the flow of the program is taken in the sequence of B1, B2 and B4. As a result, 10 clock cycles are needed to process a pixel.

By taking the worst case condition,  $n_{ipp} n_{cpi} = 10$ , hence

$$f_{clk} = \frac{t_b \ \lambda_b \ n_{ipp} \ n_{cpi}}{t_e + t_b}$$

$$= \frac{47.36 \ us(\frac{1}{74 \ ns})10}{79.6 \ us + 47.36 \ us}$$

(3.15)

$$= 50.4 \ MHz$$