# ANALYSIS OF COLUMN INTERCONNECTS FOR WAFER LEVEL PACKAGES

SUN Wei

(B. Eng, Zhejiang University)

### **A THESIS SUBMITTED**

# FOR THE DEGREE OF MASTER OF ENGINEERING DEPARTMENT OF MECHANICAL ENGINEERING NATIONAL UNIVERSITY OF SINGAPORE

2005

### Acknowledgements

Firstly, I'd like to take this opportunity to express my deepest appreciation to my supervisors, Professor Andrew Tay and Dr. Srikanth Vedantam, for their valuable guidance and advice all the way. Also, I'd like to thank the Nano Wafer Level Packaging Program and National University of Singapore for the grant of research scholarship to support my study and research towards a master's degree.

Secondly, I hope to give my grateful thanks to my various colleagues, including Audrey, Zhao Bing, Aiping, Guojun, Manyi, Jidong, Srinivasarao, Gu Jie, Deng Chun and Ebin for their help during my stay in NWLP lab. Special thanks are given to Audrey for her many stimulating discussions and advice and Jeremy for his help with Surface Evolver simulation.

Lastly but not least, I'd like to thank my parents, grandparents and uncle, for their support and kind understanding, without which I would not be able to finish my study and research in Singapore.

### **Table of Contents**

| Acknowledgements                                     | i  |

|------------------------------------------------------|----|

| Table of Contentsi                                   | ii |

| Summaryv                                             | i  |

| List of Figuresiz                                    | X  |

| List of Tablesxii                                    | ii |

| CHAPTER 1: Introduction                              | 1  |

| 1.1 Background                                       | 1  |

| 1.2 Program Motivation                               | 3  |

| 1.3 Motivation and Scope of This Work                | 6  |

| 1.4 Organization of This Thesis                      | 8  |

| CHAPTER 2: Brief Literature Survey on Fatigue Models | 9  |

| 2.1 Introduction                                     | 9  |

| 2.2 Strain-Based Fatigue Models                      | 1  |

| 2.2.1 Models Based on Plastic Strain                 | 1  |

| Coffin-Manson Type1                                  | 1  |

| Modified Coffin-Manson Type14                        | 4  |

| 2.2.2 Models Based on Creep Strain10                 | 6  |

| 2.2.3 Combination of Plastic and Creep Strain        | 7  |

| Miner's Rule1                                        | 7  |

|                                                      |    |

| 2.3 Energy-Based Fatigue Models                               |    |

|---------------------------------------------------------------|----|

| 2.3.1 Non Crack-Propagation-Included Models                   | 18 |

| Energy Partitioning                                           | 18 |

| Models Based on Total Energy                                  | 19 |

| 2.3.2 Models Which Include Crack-Propagation                  | 20 |

| 2.4 Conclusion                                                | 21 |

| CHAPTER 3: Simulation-based Design Optimization on CuC        | 24 |

| 3.1 Introduction                                              | 24 |

| 3.2 Steps of Simulation-based Design Optimization             | 27 |

| 3.2.1 Problem Definition                                      | 27 |

| 3.2.2 Identification of Design Factors, Space and Constraints | 27 |

| 3.2.3 DoE Setup                                               |    |

| 3.2.4 Finite Element Analysis                                 |    |

| 3.2.5 Responses Extraction                                    |    |

| 3.2.6 Surrogate Model Construction                            |    |

| 3.2.7 Optimization                                            |    |

| 3.2.8 Conclusion                                              |    |

| 3.3 Optimization Study on the CuC Interconnect                |    |

| 3.3.1 A Brief Note on the CuC Interconnect                    |    |

| 3.3.2 Problem Definition                                      |    |

| 3.3.3 Identification of Design Factors and Space              |    |

| 3.3.4 DoE Study Setup                                  |    |

|--------------------------------------------------------|----|

| 3.3.5 Finite Element Analysis                          |    |

| Geometry and Mesh                                      |    |

| Loading and Boundary Conditions                        |    |

| Material Properties                                    | 40 |

| 3.3.6 Responses Extraction                             | 43 |

| 3.3.7 Surrogate Model Construction                     | 46 |

| 3.4 Summary and Conclusion                             | 55 |

| CHAPTER 4: Fatigue Life Estimation of CuC Interconnect | 56 |

| 4.1 Finite Element Modeling                            |    |

| 4.1.1 Introduction                                     | 56 |

| 4.1.2 Difficulty in FEA                                | 56 |

| 4.1.3 Shell-and-Beam Model                             |    |

| 4.1.4 Shell-to-Solid Submodeling and Coupling          | 62 |

| 4.2 Feasibility Analysis                               | 63 |

| 4.2.1 Modeling Methodologies                           | 63 |

| 4.2.2 The Dummy Package                                | 65 |

| Full 3D Model                                          | 65 |

| Shell-and-Beam-Submodeling                             | 66 |

| Shell-and-Beam-Coupling                                | 68 |

| Results and Discussion                                 | 69 |

| 4.2.3 Summary and Conclusion                               |

|------------------------------------------------------------|

| 4.3 Fatigue Life Estimation of CuC Interconnect            |

| 4.3.1 The CuC Interconnect and Package under Investigation |

| 4.3.2 Solder Joint Shape Prediction                        |

| 4.3.3 Equivalent Beam Representation                       |

| 4.3.4 Global shell-and-beam model                          |

| 4.3.5 Shell-to-solid submodeling94                         |

| 4.3.6 Discussion                                           |

| 4.3.7 Conclusions                                          |

| CHAPTER 5: Conclusions of the Current Thesis               |

| References103                                              |

#### Summary

Copper column (CuC) interconnect is proposed in the Nano Wafer Level Packaging (NWLP) program as a candidate chip-to-substrate interconnect solution and is the focus of investigation in this thesis.

In this thesis, a literature survey on fatigue life correlation models and two important tasks are completed. The two important tasks are:

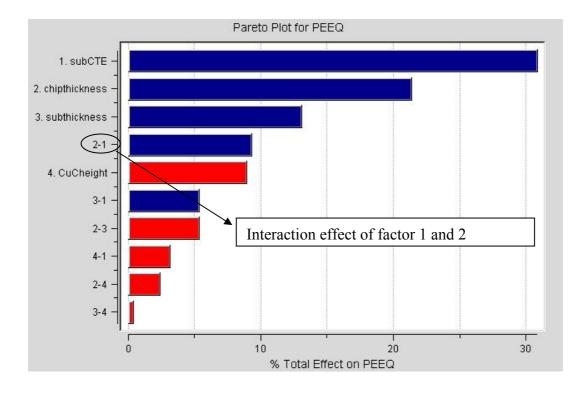

First, a simulation-based design optimization process is established based on our available software resources, ABAQUS and Minitab. This process integrates finite element analysis (FEA), design of experiment (DoE) technique and numerical optimization, generating a systematic and efficient method that can be used to study the effects of various design parameters on desired system response. The significance of this simulation-based design optimization process lies in its general applicability in various design scenarios where effect of each design parameter on the system response is of interest, investigation of interaction of design parameters is needed and an optimal design parameter setting is required. After the establishment of this optimization process, a case study on CuC interconnect in wafer level packages is detailed. It is found that the substrate coefficient of thermal expansion (CTE) has the largest influence on solder joint fatigue reliability. The chip thickness has the second largest influence with a smaller chip thickness leading to better solder joint reliability. The substrate thickness plays the third most important role with a thinner substrate thickness giving longer fatigue life. It is also found that increasing CuC height will result in better solder joint fatigue performance. Finally we find that the optimal design combination is: low-level substrate CTE, chip and substrate thickness, and high-level CuC height.

Secondly, two new and novel advanced finite element simulation methodologies, based on simplifying chip/substrate as shells and interconnects as beams, are developed to address the difficulty of modeling the large number of CuC interconnects in a 20mm by 20mm wafer level package with ultra-fine pitch. Although the idea of using shell and beam elements to model substrate/chip and interconnects is not new, previous researchers have not accurately translated the displacement results from the global shell-and-beam-based model to the local model. This thesis describes first-ever the application of the shell-to-solid submodeling and shell-to-solid coupling techniques available in ABAQUS to overcome the above-mentioned difficulty in the context of modeling solder joint fatigue of electronic packages. A feasibility demonstration of the two methodologies is firstly carried out. A great saving of computational resources is realized and results show that good accuracy is achieved. After this, as a case study, the shell-and-beam-submodeling approach is chosen for fatigue life prediction of three different CuC interconnects in 20mm by 20mm wafer level packages with 100µm pitch. By using the shell-to-solid submodeling technique, the stress/strain of the critical solder joint can be derived. Fatigue life prediction can then be

performed based on Solomon's fatigue correlation. It should be noted that the shell-and-beam-submodeling approach can be used not only in the thermomechanical but also in drop impact simulation of electronic packages.

## **List of Figures**

| Figure 1.1 Conventional packaging in comparison with WLP [2]                                      | 2       |

|---------------------------------------------------------------------------------------------------|---------|

| Figure 1.2 Proposed 100µm pitch interconnects                                                     | 5       |

| Figure 3.1 Typical flow chart for Simulation-based Design Optimization                            | 27      |

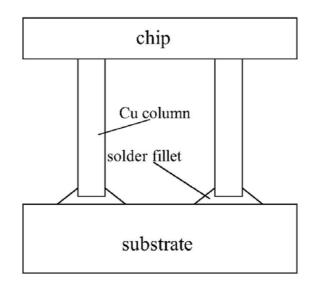

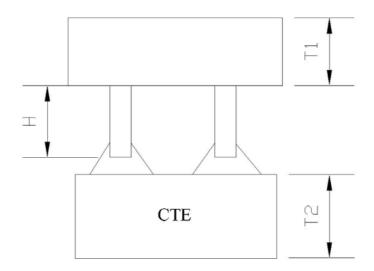

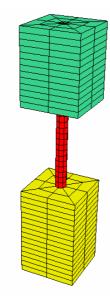

| Figure 3.2 Schematic picture of the CuC interconnect                                              | 33      |

| Figure 3.3 Illustrations of Design Factors                                                        | 34      |

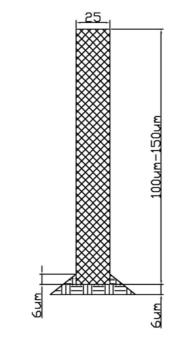

| Figure 3.4 Dimensions of the CuC interconnect                                                     | 38      |

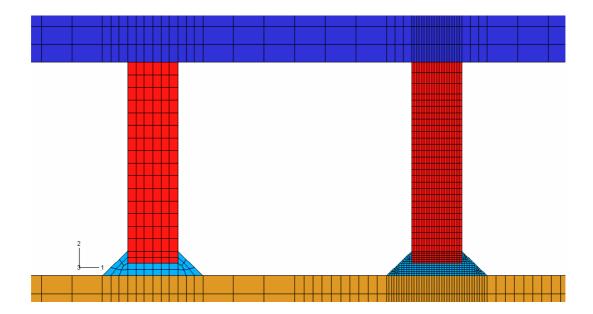

| Figure 3.5 2D mesh of the electronic package under investigation (a close-up                      | o view  |

| of the corner part)                                                                               | 38      |

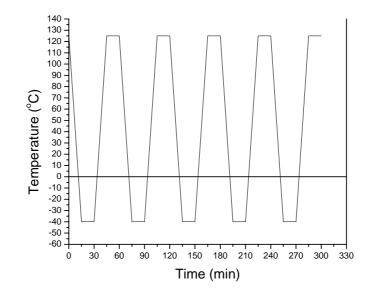

| Figure 3.6 Temperature cycling profile                                                            | 40      |

| Figure 3.7 Boundary conditions of the 2D finite element model                                     | 40      |

| Figure 3.8 Predicted values VS simulation results                                                 | 47      |

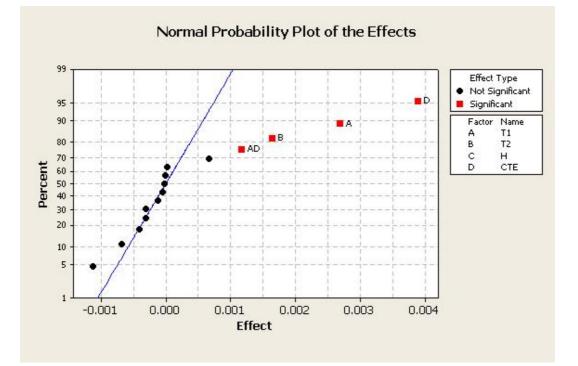

| Figure 3.9 Normal probability plot of factor effects                                              | 48      |

| Figure 3.10 Influences of design factors and interactions on $\Delta \varepsilon_{avg}$ value     | 51      |

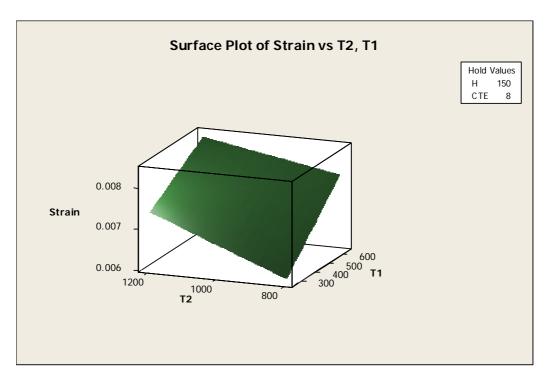

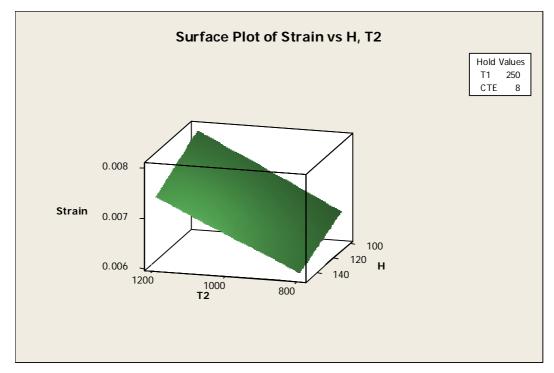

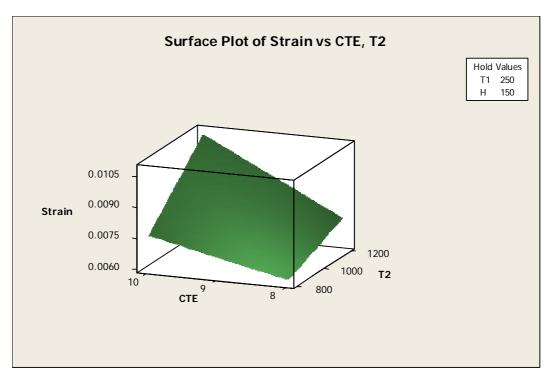

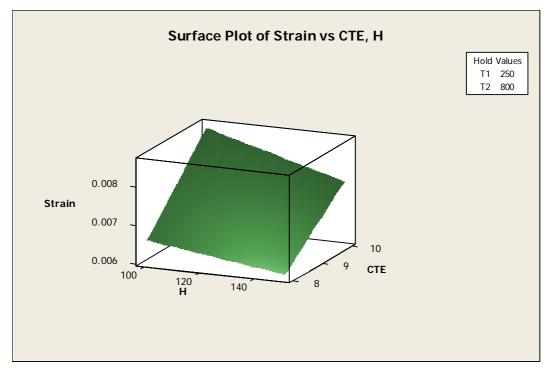

| Figure 3.11(a) Response surface plot of $\Delta \varepsilon_{avg}$ vs. chip thickness and su      | bstrate |

| thickness                                                                                         | 52      |

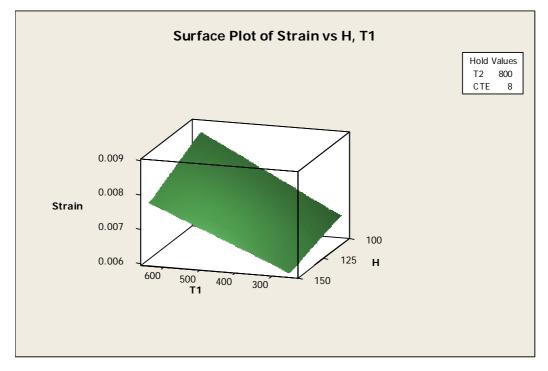

| Figure 3.11(b) Response surface plot of $\Delta \varepsilon_{avg}$ vs. chip thickness and CuC hei | ght 52  |

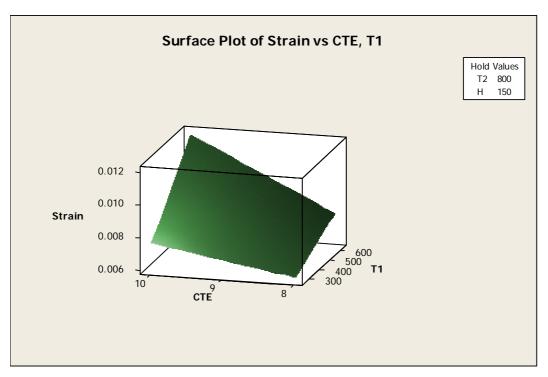

| Figure 3.11(c) Response surface plot of $\Delta \varepsilon_{avg}$ vs. chip thickness and substrate CTE |

|---------------------------------------------------------------------------------------------------------|

|                                                                                                         |

| Figure 3.11(d) Response surface plot of $\Delta \varepsilon_{avg}$ vs. substrate thickness and CuC      |

| height53                                                                                                |

| Figure 3.11(e) Response surface plot of $\Delta \varepsilon_{avg}$ vs. substrate CTE and substrate      |

| thickness                                                                                               |

| Figure 3.11(f) Response surface plot of $\Delta \varepsilon_{avg}$ vs. CuC height and substrate CTE.54  |

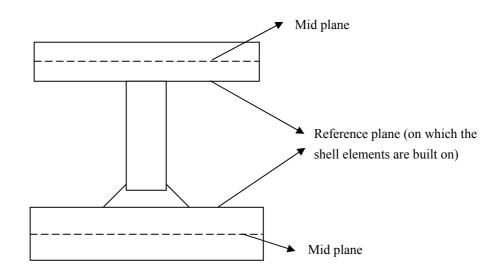

| Figure 4.1 Schematic picture of the reference plane of the shell elements                               |

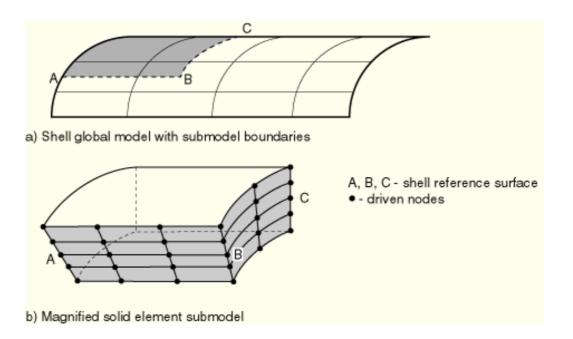

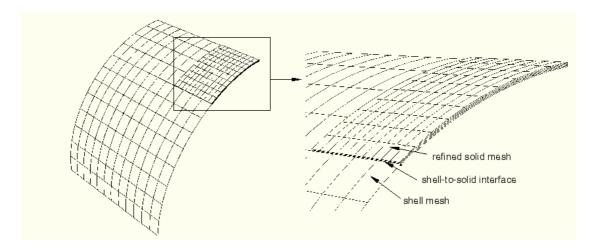

| Figure 4.2 Shell-to-solid submodeling [65]63                                                            |

| Figure 4.3 Shell-to-solid coupling [65]63                                                               |

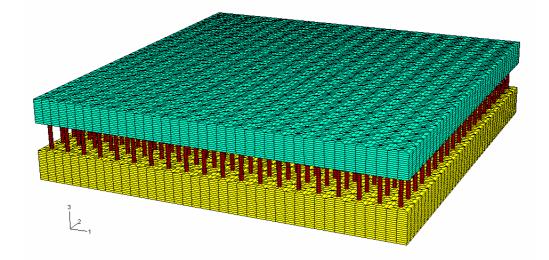

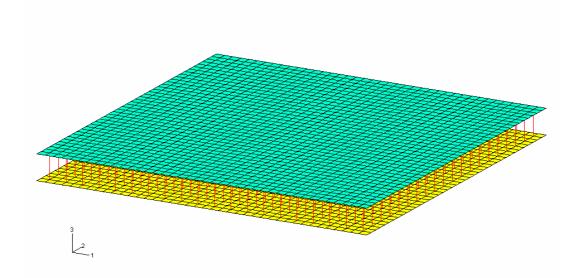

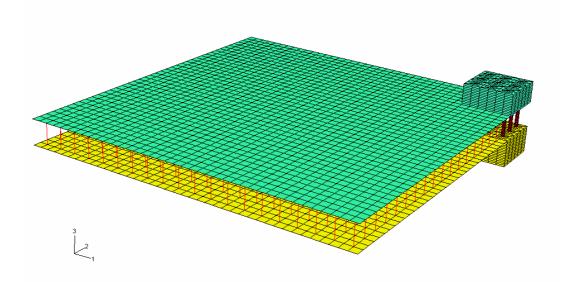

| Figure 4.4 Finite element mesh of the dummy package                                                     |

| Figure 4.5 Finite element mesh of the global shell-and-beam model                                       |

| Figure 4.6 Finite element mesh of the submodel of the critical interconnect                             |

| Figure 4.7 Finite element mesh of the shell-and-beam-coupling model69                                   |

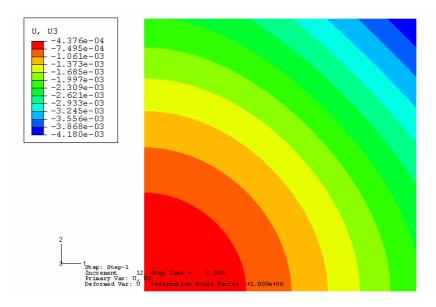

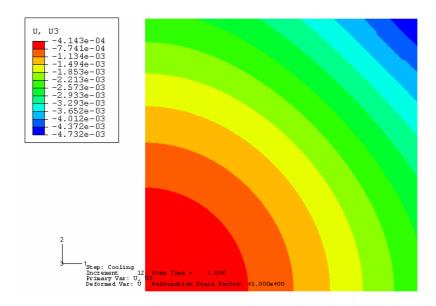

| Figure 4.8 Displacement (Z-direction) contour of the chip in full 3D model73                            |

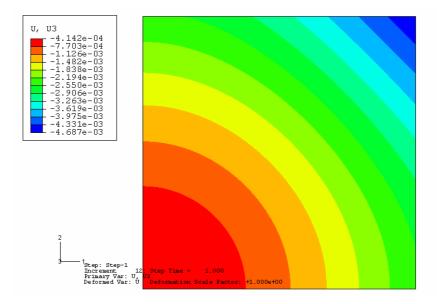

| Figure 4.9 Displacement (Z-direction) contour of the chip in global shell-and-beam model                |

| Figure 4.10 Displacement (Z-direction) contour of the chip in shell-to-solid-                           |

| coupling model74                                                                                        |

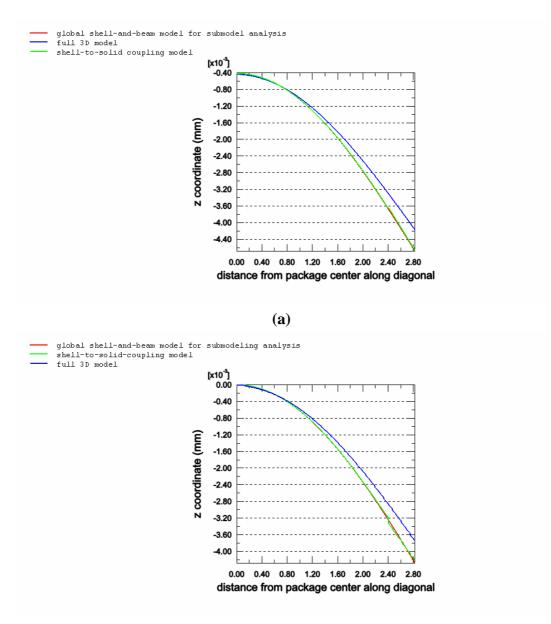

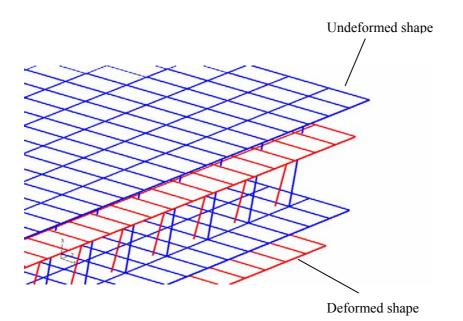

| Figure 4.11 Comparison of deformed shape of the 4mm by 4mm package after            |

|-------------------------------------------------------------------------------------|

| temperature drop from 125 °C to -40 °C. (a) Top of interconnect, and (b) bottom of  |

| interconnect                                                                        |

|                                                                                     |

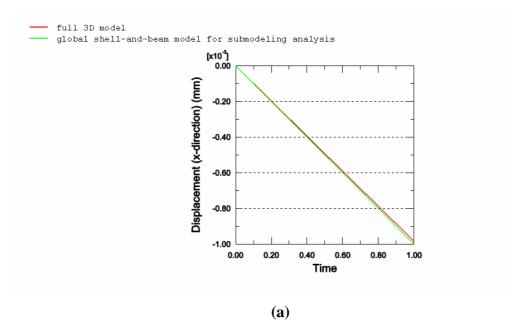

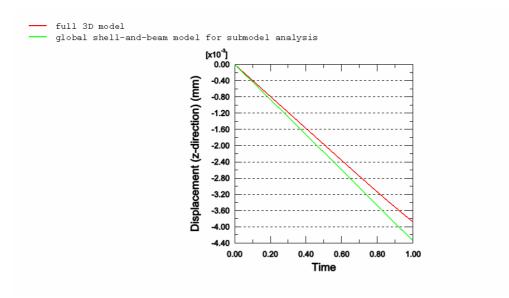

| Figure 4.12 Time history deformation of the global shell-and-beam model and full    |

| 3D model                                                                            |

|                                                                                     |

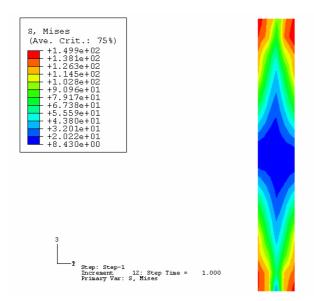

| Figure 4.13 Stress contour plot for the corner CuC interconnect in the full 3D      |

| model                                                                               |

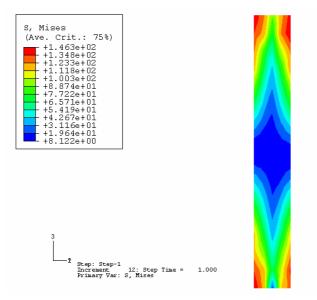

| Figure 4.14 Stress contour plot for the corner CuC interconnect using the shell-to- |

| solid-submodeling approach                                                          |

| sond-submodening approach                                                           |

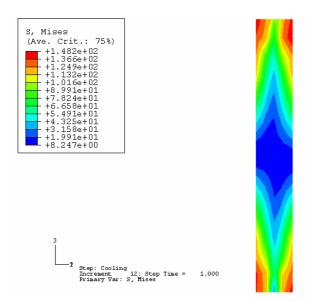

| Figure 4.15 Stress contour plot for the corner CuC interconnect using the shell-to- |

| solid-coupling approach                                                             |

|                                                                                     |

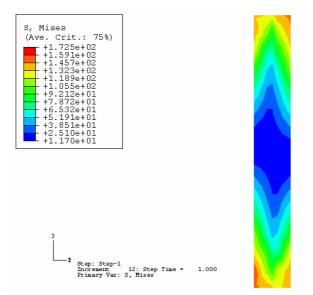

| Figure 4.16 Stress contour plot for the corner CuC interconnect using the original  |

| Chng's micro modeling approach (Chng, 2003)78                                       |

|                                                                                     |

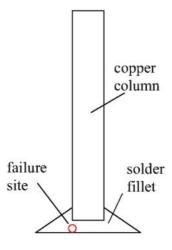

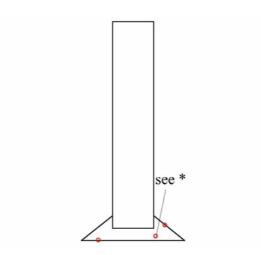

| Figure 4.17 Schematic picture of the CuC interconnect                               |

| Figure 4.18 Dimensions of CuC interconnect                                          |

|                                                                                     |

| Figure 4.19 Predicted solder joint shape by Surface Evolver                         |

| Figure 4.20 Micro model of CuC interconnect                                         |

| rigure 4.20 where model of ede interconnect                                         |

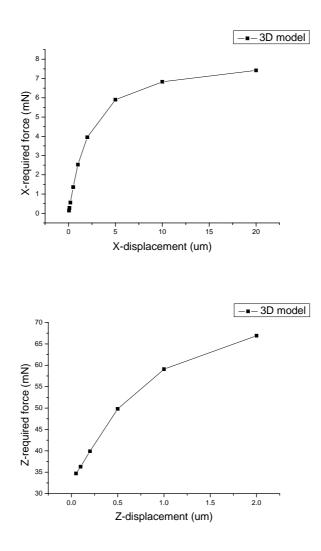

| Figure 4.21 Force-displacement characteristics of micro model                       |

|                                                                                     |

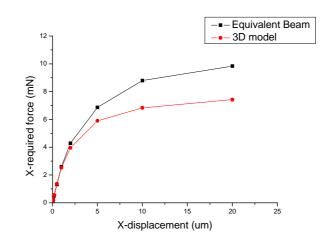

| Figure 4.22 Comparison of X-displacement of equivalent beam                         |

| Figure 4.23 Comparison of Z-displacement of equivalent beam                         |

|                                                                                     |

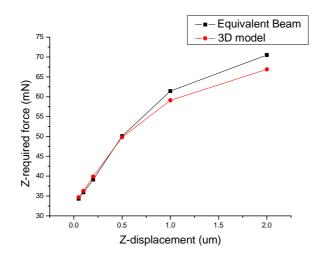

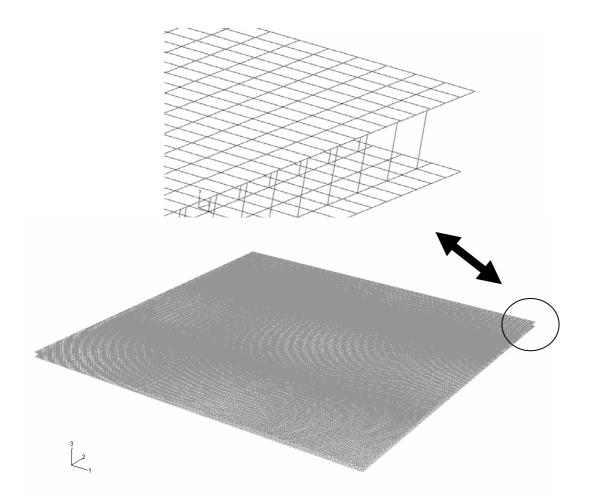

| Figure 4.24 Global shell-and-beam model and local zoom-in view                      |

| Figure 4.25 Deformation of global model at -40oC (first cycle)               | 94 |

|------------------------------------------------------------------------------|----|

| Figure 4.26 Submodel of critical CuC interconnect                            | 95 |

| Figure 4.27 Failure site identified using the modified macro-micro approach  | C  |

| Figure 4.28 Failure sites identified using the original macro-micro approach | -  |

### List of Tables

| Table 1.1 Main design parameters of the proposed interconnects                | 5  |

|-------------------------------------------------------------------------------|----|

| Table 2.1 Category of fatigue [6]                                             | 10 |

| Table 3.1 Design factors and their variations                                 | 35 |

| Table 3.2 DoE design table                                                    | 36 |

| Table 3.3 Details of modeling parameters                                      | 37 |

| Table 3.4 Material properties for chip and FR4 board                          | 41 |

| Table 3.5 Material properties for copper                                      | 42 |

| Table 3.6 Material properties for solder                                      | 43 |

| Table 3.7 Reponses of all the sixteen finite element models                   | 45 |

| Table 3.8 List of unscaled and scaled coefficients                            | 50 |

| Table 4.1 Geometrical parameters of the dummy package                         | 66 |

| Table 4.2 Displacement result comparison between the three models             | 74 |

| Table 4.3 Mises stress result comparison between the four models              | 79 |

| Table 4.4 Requirements of various models in analyzing a 4mm by 4mm du package | -  |

| Table 4.5 Details of modeling parameters                                      | 84 |

| Table 4.6 Parameters used for solder shape prediction by Surface Evolver      | 87 |

| Table 4.7 Equivalent beams (EBs) for CuC interconnects                        | 88 |

| Table 4.8 Fatigue lives of the three CuC interconnects                        | 96 |

#### **CHAPTER 1: Introduction**

#### **1.1 Background**

Since the emergence of Large Scale Integrated-circuit (LSI), the electronic packaging industry has gone through two revolutions [1]. The transition from Pin through Hole (PTH) technology to Surface Mount Technology (SMT) stands for the first revolution. After this revolution Quad Flat Package (QFP) became widely used by the industry to replace the traditional Dual in-line Package (DIP) for denser assembly on Printed Circuit Board (PCB).

The second revolution is typified by the invention of the Ball Grid Array (BGA). The emergence of BGA was driven by the need for integration of larger number of I/Os in the package and relatively coarser interconnect pitch. BGA meets the need for higher I/O number because it adopts an area array interconnect methodology instead of the peripheral array methodology used by QFP. Therefore, with the same I/O number BGA can realize a coarser pitch than QFP, making assembly of BGA much easier.

Currently electronic packaging industry is going through the third revolution. The need for high speed, high power, high number of I/Os, low cost and high performance IC packages calls for new advances in packaging technology. Among all the advances, Wafer Level Packaging (WLP) is the most promising one. In WLP, the package interconnects are fabricated directly on the wafers, the test and

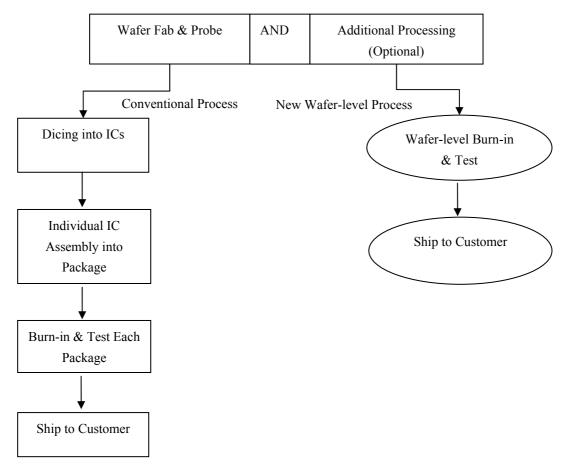

burn-in process are done at the wafer level, and the dies after dicing are directly ready for SMT assembly [2]. A typical WLP process flow is shown is Figure 1.1.

Figure 1.1 Conventional packaging in comparison with WLP [2]

As a result of the new process flow, WLP is expected to provide the following advantages [2]:

- Providing the smallest system size, because it is truly a chip size package

- Enabling interconnect continuum from IC to PCB because of thin film processing

- Reduced cost of packaging, because all the interconnects are fabricated at the wafer level

- Reduced cost of testing, because testing is done at the wafer level for all ICs

- Reduced cost of burn-in, because the burn-in is done at the wafer level once

- Elimination of underfill because of compliancy of the leads or other ways to achieve reliability

- Improved electrical performance because of short lead lengths

The two most important momentums driving WLP are size benefits for portable products and cost benefits for all products [2].

#### **1.2 Program Motivation**

The International Technology Roadmap for Semiconductors (ITRS) 2003 indicated that the IC feature size is expected to go down to 32 nm and the pitch to 20µm in the year 2013 [3]. Accordingly, in 2002, the NWLP program, an international collaboration among the National University of Singapore, Institute of Microelectronics, and the Packaging Research Center at Georgia Institute of Technology, USA, was initiated with the vision to develop nano-structured interconnect solutions for ultra-fine pitch WLP. The ultimate purpose of this collaboration is to develop interconnect solutions for high speed, high power IC packages with pitch size of  $100\mu m$  and explore possible solutions for  $20\mu m$  pitch using nano-structured materials [4] [5].

NWLP is actually an advanced version of the WLP because it extends the current WLP technology to ultra-fine interconnect pitch and explore the use of nanostructured materials to WLP for state-of-the-art package performance.

At the initial phase of this program our research focus is, however, to develop interconnect solutions for the next generation WLP with 100µm pitch [4].

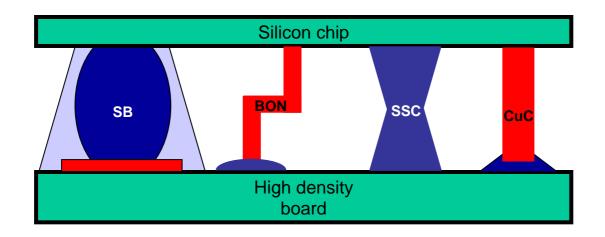

Four candidate solutions that extend the current state of the interconnect technology are proposed. They are [5]:

- Solder Ball with No-flow Underfill (SB)

- Bed of Nails (BON)

- Stretched Solder Column (SSC)

- Copper Column Interconnect (CuC)

Figure 1.2 is a schematic picture of the four interconnects and Table 1.1 lists the main design parameters.

Figure 1.2 Proposed 100µm pitch interconnects

| Table 1.1 Main | design | narameters | of the | proposed | interconnects |

|----------------|--------|------------|--------|----------|---------------|

| Table 1.1 Main | ucsign | parameters | or the | proposed | mucromicus    |

| Size of Chip               | 20mm by 20mm         |

|----------------------------|----------------------|

| Pitch of Interconnect      | 100µm                |

| Number of I/Os             | 10,000 per $cm^2$    |

| Temperature Cycling Range  | -40 °C to 125 °C     |

| Thermal Cycle Fatigue Life | 1000 cycles (target) |

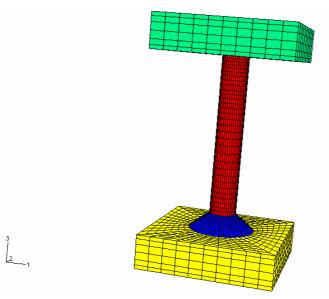

The SB interconnect is basically an extension of current technology down to 100µm pitch with no-flow underfill. It is a rigid interconnect. The BON interconnect consists of three segments of electroplated copper in a Z-shaped structure and is expected to be joined to the substrate using solder. It is a compliant interconnect. The SSC interconnect is fabricated by stretching molten high-lead solder bump to an hourglass shape. After that it is joined to the substrate with lead-free or eutectic solder. It is supposed to be a semi-compliant interconnect [4]. The CuC interconnect is actually a simplified version of the BON interconnect. In this interconnect technology a copper column with circular cross section is formed by

electroplating and joined to the substrate with solder. Therefore, the CuC interconnect is much easier to process than the BON interconnect. CuC interconnect is also a compliant interconnect.

CuC interconnect will be the focus of this thesis.

#### **1.3 Motivation and Scope of This Work**

As far as long-term reliability of IC packages is concerned, the integrity of solder joints under cyclic temperature changes, known as thermo-mechanical reliability, must be guaranteed. This thermo-mechanical reliability concern arises from the CTE mismatch between silicon chip and substrate. As IC packages experience cyclic temperature changes, i.e. power on and off, the chip and substrate expand or shrink differently due to CTE difference. This difference of expansion or shrinkage make the solder joints between the chip and substrate undergo cyclic load and eventually cause low cycle fatigue failure.

The solder joint thermo-mechanical reliability is already a major concern for current electronic packages and is expected to be critical in view of the proposed chip size of 20mm by 20mm and pitch of 100µm in the NWLP program. Before any physical prototypes are made and experiments carried out, it is often of interest to 1) do a design optimization study to find out the effects of various design parameters on solder joint reliability and find out an optimal set of design

parameters combination that leads to maximum solder joint fatigue life; 2) conduct FEA to estimate the solder joint fatigue life of the critical interconnect.

To do a design optimization analysis of CuC interconnect, a 2D plane strain finite element model is an adequate and efficient. However, when accurate modeling of solder joint fatigue is required, the 2D finite element model is not adequate due to its underlying inaccurate assumption. Full 3D finite element modeling is necessary. But in light of the large package size and ultra-fine interconnect pitch coupled with the requirement for full area array, modeling of solder joint fatigue is a challenge for the current computational resources. Therefore, one of the aims of this thesis is to develop efficient and accurate modeling method to address the challenge.

To sum up, the objectives of this work are to:

- Do a design optimization study to find out the effects of changes of various design parameters on solder joint reliability and determine an optimal parameter combination.

- Develop an efficient and accurate modeling method to address the challenge of modeling solder joint fatigue.

- Use the developed modeling methodology to estimate the solder joint fatigue life of the critical corner interconnect of some CuC packages.

### **1.4 Organization of This Thesis**

This thesis consists of four chapters. Chapter 1 serves as an introduction which describes the industry background, the motivation of the NWLP program, and the motivation and scope of the current work. Chapter 2 is a review of the popular fatigue models including both strain and energy-based models. Chapter 3 contains the simulation-based design optimization process establishment procedures and a case study. Chapter 4 provides the details the newly developed simulation methodologies that can be used to efficiently address the simulation difficulty of CuC interconnect in 20mm by 20mm wafer level package with 100µm pitch.

# CHAPTER 2: Brief Literature Survey on Fatigue Models 2.1 Introduction

The eutectic Pb-Sn solder is widely used in the electronic packaging industry because its low melting point allows solder joint to be formed at temperatures low enough to prevent device failure. As far as long-term reliability is concerned, the solder joint sustainability under cyclic temperature changes is vital. This is because during service life the package will experience power on and off as well as ambient temperature changes, causing the solder joints to experience cyclic loadings and eventually failures occur. The primary failure mechanism of eutectic Pb-Sn solder joint under thermal cycling is fatigue. Fatigue occurs when material undergoes repetitive loading. The repetitive loading causes damage to material. Unlike some biomaterials, this damage is cumulative and unrecoverable [6]. When this damage cumulates to a certain level, crack initiates and propagates across the material and failure occurs. There are two types of fatigue, namely high cycle fatigue and low cycle fatigue. The definitions and characteristics of these two types of fatigue are shown in Table 2.1 [6]. According to Table 2.1, solder joint fatigue in electronic packaging is categorized as low cycle fatigue. This is true because solder joints are often stressed beyond their yielding point during thermal cycling and the number of cycles to failure is much lower than  $10^4$ .

|                    | Significant plastic strain in each cycle                            |  |  |  |

|--------------------|---------------------------------------------------------------------|--|--|--|

| Low cycle fatigue  | • High load                                                         |  |  |  |

|                    | • Low number of cycles to failure, from 1 to $10^4$ or              |  |  |  |

|                    | $10^5$ cycles                                                       |  |  |  |

|                    | Largely confined to elastic range                                   |  |  |  |

| High cycle fatigue | • Low load                                                          |  |  |  |

|                    | • Long life, greater than 10 <sup>4</sup> or 10 <sup>5</sup> cycles |  |  |  |

|                    |                                                                     |  |  |  |

Table 2.1 Category of fatigue [6]

Since solder joints electrically and mechanically connect the chip and substrate, their integrities are important to ensure the package's long-term functionality. Therefore, there is a great interest in evaluating and predicting the solder joint fatigue life under thermal cycling. A cost-effective way for fatigue life prediction is to use finite element analysis coupled with fatigue models.

There are many fatigue models derived by different researchers using different methods. According to the different damage indicators used, the majority of those models can be categorized as strain-based and energy-based [7] [8]. Other less popular ones include crack-based, stress-based and entropy-based [9]. In current literature survey, only two most popular ones which are the strain-based and energy-based fatigue models will be reviewed. Since only eutectic Pb-Sn solder will be used in this work, emphasis will be put on eutectic and near-eutectic solders.

#### **2.2 Strain-Based Fatigue Models**

The most widely used fatigue models are strain based. Some of them are based on plastic strain, some on creep strain, and others on total strain.

#### 2.2.1 Models Based on Plastic Strain

Some of the fatigue models, based on plastic strain only account for plastic strain (i.e. the fatigue is only related to plastic strain range) and thus is categorized as Coffin-Manson type fatigue models. Others may also take into account the cyclic frequency, cyclic temperature range, mean temperature, dwell times, dwell temperatures and loading rates, and thus categorized as Modified Coffin-Manson type fatigue models [7] [8].

#### **Coffin-Manson Type**

Coffin [10] and Manson [11] reported that the total number of cycles to failure,  $N_f$ , is related to plastic strain range,  $\Delta \gamma_p$ . This relation is expressed in Equation (2.1).

$$\frac{\Delta \varepsilon_p}{2} = \varepsilon'_f \left(2N_f\right)^c \tag{2.1}$$

The fatigue ductility coefficient,  $\varepsilon'_{f}$ , is approximately equal to the true fracture ductility,  $\varepsilon_{f}$ . The fatigue ductility exponent, c, is a material constant that varies between -0.5 and -0.7 [12]. Either fatigue experiments or FEA modeling can be adopted to derive the plastic strain range,  $\Delta \varepsilon_{p}$ , for fatigue life prediction. This Coffin-Manson fatigue model is widely used due to its simplicity. However, the Coffin-Manson fatigue model assumes that the fatigue failure is strictly due to plastic deformation and that elastic strain plays a minor role in fatigue failure. When elastic strain is not negligible and must be taken into consideration, Basquin's fatigue model should be used in conjunction with Coffin-Manson model for fatigue prediction [6]. Basquin's equation relates the total number of cycles to failure,  $N_f$ , to the elastic strain range, and the relation is expressed as Equation (2.2) [7],

$$\frac{\Delta \varepsilon_{elastic}}{2} = \frac{\sigma_f}{E} (2N_f)^b \tag{2.2}$$

where  $\Delta \varepsilon_{elastic}$  is the elastic strain range,  $\sigma'_{f}$  is the fatigue strength coefficient, *E* is the elastic modulus and *b* is the fatigue strength exponent. When both elastic and plastic strains must be considered as contributors to fatigue failure, Equation (2.1) and Equation (2.2) should be combined for fatigue life prediction [6] [13].

$$\frac{\Delta\varepsilon}{2} = \frac{\sigma_f}{E} \left( 2N_f \right)^b + \varepsilon_f' \left( 2N_f \right)^c \tag{2.3}$$

$\Delta \varepsilon$  is the total strain or is the sum of  $\Delta \varepsilon_p$  and  $\Delta \varepsilon_{elastic}$ . From the above three equations, we can see that for large strains or short fatigue life, plastic strain component predominant and Equation (2.1) is adequate to describe fatigue behavior. For small strains or long fatigue life, elastic strain component predominant and Equation (2.2) is adequate to describe fatigue behavior. If both elastic and plastic strains have to be taken into account, Equation (2.3) should be used.

Another Coffin-Manson type fatigue model was proposed by Solomon [14]. In his research pure shear tests were performed and the following fatigue model was obtained.

$$\Delta \gamma_p N_f^{\alpha} = \theta \tag{2.4}$$

$\Delta \gamma_p$  is the plastic shear strain range,  $\theta$  is the inverse of the fatigue ductility coefficient, and  $\alpha$  is a material constant. If the strain state is much more complex than the state in a pure shear test, i.e. the strain is multi-dimensional, accumulated equivalent plastic strain should be used [15]. The definition of accumulated equivalent plastic strain is as follows:

$$\Delta \varepsilon_{eq}^{pl} = \frac{\sqrt{2}}{3} \sqrt{\left(\Delta \varepsilon_{xx}^{pl} - \Delta \varepsilon_{yy}^{pl}\right)^2 + \left(\Delta \varepsilon_{yy}^{pl} - \Delta \varepsilon_{zz}^{pl}\right)^2 + \left(\Delta \varepsilon_{xx}^{pl} - \Delta \varepsilon_{zz}^{pl}\right)^2 + \frac{3}{2} \left[\left(\Delta \gamma_{xy}^{pl}\right)^2 + \left(\Delta \gamma_{yz}^{pl}\right)^2 + \left(\Delta \gamma_{xz}^{pl}\right)^2\right]}$$

$$(2.5)$$

where  $\Delta \varepsilon_{xx}^{pl}$ ,  $\Delta \varepsilon_{yy}^{pl}$ ,  $\Delta \varepsilon_{zz}^{pl}$ ,  $\Delta \gamma_{xy}^{pl}$ ,  $\Delta \gamma_{yz}^{pl}$  and  $\Delta \gamma_{xz}^{pl}$  are the incremental plastic strain components acting on the solder. Equation (2.5) may also be expressed in terms of principal strain values:

$$\Delta \varepsilon_{eq}^{pl} = \frac{\sqrt{2}}{3} \sqrt{\left(\Delta \varepsilon_1^{pl} - \Delta \varepsilon_2^{pl}\right)^2 + \left(\Delta \varepsilon_1^{pl} - \Delta \varepsilon_3^{pl}\right)^2 + \left(\Delta \varepsilon_2^{pl} - \Delta \varepsilon_3^{pl}\right)^2} \tag{2.6}$$

The accumulated equivalent plastic strain may be defined as:

$$\mathcal{E}_{eq}^{pl} = \sum \Delta \mathcal{E}_{eq}^{pl} \tag{2.7}$$

In addition to the equivalent plastic strain, some other strain values may also be used for fatigue life prediction where multi-axial fatigue situations are expected. Cortez et al [15] [16] have investigated the use of maximum principal plastic strain and the maximum plastic shear strain as correlation parameters. Smith, Watsono and Tooper [17] relation extended by Sochie [18] for multi-axial fatigue uses maximum principal stress and the maximum principal strain amplitude. Other correlation parameters used are normal stress on the maximum shear planes and the maximum shear strain by Brown and Miller [19], Lohr and Ellison [20].

#### **Modified Coffin-Manson Type**

All the above Coffin-Manson type fatigue model equations are simple, so it may be reasonable to assume that their applications are likewise simple. Actually, the above Coffin-Manson type fatigue models are derived based on isothermal fatigue tests, i.e. they only define the fatigue behavior at the temperatures at which the tests were performed. Other factors that may affect the fatigue behavior of solders were not considered.

Coffin [21] [22] found that decreasing the cyclic frequency by increasing the cycle period generally reduces the number of cycles to failure. He described the effect of cyclic frequency on fatigue behavior using a frequency-modified version of the Coffin-Manson equation, i.e., by

$$\left(N_{f}\nu^{(K-1)}\right)^{\alpha}\Delta\gamma_{p}=\theta\tag{2.8}$$

where *K* is determined at different temperatures, which defines the effect of cyclic frequency. If K = 1, the cyclic frequency has no effect on fatigue behavior; if K = 0, the time to failure,  $t_f$ , is a constant for constant plastic strain  $(N_f / v = t_f)$ . Generally *K* is between 1 and 0.

The hold time and ramp rate also have effect on solder joint fatigue behavior. Vaynman and Fine [23] found that the number of cycles to failure  $N_f$  is given by

$$N_{f} = \left(C + D(t_{ht} + t_{hc})\right) / \left(2t_{r} + t_{ht} + t_{hc}\right)$$

(2.9)

where *C* and *D* are constants and  $t_{ht}$ ,  $t_{hc}$  and  $t_r$  are the tensile hold time, compressive hold time, and the ramp time, respectively. This approach requires experiments to determine *C* and *D*.

Engelmaier [24] proposed a fatigue model based on data from [25] that takes into account effects of both frequency and temperature. According to his fatigue model, the total number of cycles to failure is related to the total shear strain range  $\Delta \gamma_t$ . The relation is shown in Equation (2.10),

$$N_{f} = \frac{1}{2} \left( \frac{\Delta \gamma_{t}}{2\varepsilon_{f}} \right)^{1/c}$$

(2.10)

where  $c = -0.442 - 6 \times 10^{-4} \overline{T}_s + 1.74 \times 10^{-2} \ln(1+f)$ .  $\overline{T}_s$  is the mean cyclic solder joint temperature in  ${}^{\circ}C$ , and f is the cyclic frequency in cycles/day.

#### 2.2.2 Models Based on Creep Strain

As far as solder joints are concerned, their fatigue failure due to creep has been found to be related to two creep mechanisms, namely grain boundary sliding and matrix creep [7].

Knecht and Fox [26] have developed a fatigue life prediction model based on the amount of matrix creep generated during thermal cycling. This model uses a similar form as the Coffin-Manson fatigue model. This equation is:

$$N_f = \frac{C}{\gamma_{mc}} \tag{2.11}$$

The number of cycles to failure,  $N_f$ , is related to a constant *C*, which is independent on failure criteria and solder microstructure.  $\gamma_{mc}$  is the matrix creep strain and defined as:

$$\gamma_{mc} = \int C \left( \tau / \tau_0 \right)^{n_{mc}} dt \tag{2.12}$$

where  $n_{mc}$  and  $\tau_0$  is a constant, and  $\tau$  is the shear stress as a function of time.

Syed [27-29] proposed a fatigue model that includes the other creep mechanism, grain boundary sliding, with matrix creep. In this model, creep strain is partitioned into two parts as shown in Equation (2.13):

$$N_f = \left(0.022D_{gbs} + 0.063D_{mc}\right)^{-1} \tag{2.13}$$

where  $D_{gbs}$  and  $D_{mc}$  are the accumulated equivalent creep strain per cycle for grain boundary sliding and matrix creep, respectively.

#### 2.2.3 Combination of Plastic and Creep Strain

#### **Miner's Rule**

Miner's linear superposition rule can be used to combine the effects of both plastic and creep strains in a fatigue model. A typical application of this rule is the combination of Equation (2.1) and Equation (2.11) into Equation (2.14) [30],

$$\frac{1}{N_f} = \frac{1}{N_p} + \frac{1}{N_c}$$

(2.14)

where  $N_p$  is the number of cycles to failure due to plastic strain in Equation (2.1) and  $N_c$  is the number of cycles to failure due to creep strain in Equation (2.11).

#### **Strain Range Partitioning**

Manson [31-33] used strain range partitioning (SRP) to predict fatigue life. The underlying assumption of SRP is that a typical hysteresis loop may be partitioned into four components: the plastic strain in tension and compression (PP), the creep strain in tension and compression (CC), the creep strain in tension and plastic strain in compression (CP), as well as the plastic strain in tension and creep strain in tension (PC). The fatigue life is determined using Equation (2.15):

$$\frac{1}{N_f} = \frac{F_{pp}}{N_{pp}} + \frac{F_{cc}}{N_{cc}} + \frac{F_{cp}}{N_{cp}} + \frac{F_{pc}}{N_{pc}}$$

(2.15)

where  $F_{ij}$  the fraction of the total inelastic strain range of the hysteresis loop. The contribution from each part is determined from other fatigue models and from cyclic stress-strain tests.

#### **2.3 Energy-Based Fatigue Models**

The fatigue failure of materials normally goes through two stages, namely crack initiation and crack propagation. Among the energy based fatigue models, some of them only calculate the number of cycles to crack initiation while others predict the overall fatigue life from a combination of crack initiation and propagation.

#### 2.3.1 Non Crack-Propagation-Included Models

#### **Energy Partitioning**

Energy-based fatigue models were developed later than the strain-based ones, but they are becoming increasingly popular. These models use hysteresis energy or volume-weighted average stress-strain history to predict fatigue life.

Dasgupta [34] proposed the use of total strain energy derived from stress-strain history as an indicator of fatigue life. This strain energy includes both elastic strain energy and inelastic work dissipated during each thermal cycle. A detailed stressstrain analysis is required to determine the elastic strain energy density  $U_e$ , plastic energy dissipation  $W_p$ , and creep strain energy dissipation  $W_c$  within a typical thermal cycle. The relation between fatigue life and the above energy components is expressed in Equation (2.16),

$$U = U_e + W_p + W_c = U_{e0} N_{fe}^{b'} + W_{p0} N_{fp}^{c'} + W_{c0} N_{fc}^{d'}$$

(2.16)

where the coefficients  $U_{e0}$ ,  $W_{p0}$  and  $W_{c0}$  represent the intercepts of the elastic, plastic and creep energy density versus fatigue life curves on a log-log plot, while the exponents b', c', and d' are their corresponding slopes. The variables  $N_{fe}$ ,  $N_{fp}$ , and  $N_{fc}$  represent the cycles to failure due to elastic, plastic and creep deformations, respectively. Similar to Equation (2.14), the total damage is computed by summing the inverse of  $N_{fe}$ ,  $N_{fp}$ , and  $N_{fc}$ .

$$D_{total} = \frac{1}{N_{fe}} + \frac{1}{N_{fp}} + \frac{1}{N_{fc}}$$

(2.17)

It is obvious that the above fatigue model uses an energy partitioning approach. When multiple damage mechanisms need to be taken into account, Equation (2.17) is used to compute the total damage from each damage mechanism.

#### **Models Based on Total Energy**

Morrow [35] was one of the first modern fatigue researchers to show that fatigue life could be correlated with the mechanical energy of hysteresis loop. His energy based fatigue model is shown in Equation (2.18),

$$N_f^m W = \theta_E \tag{2.18}$$

where *m* and  $\theta_E$  are constants.

Akay [36] proposed that the volume-weighted average total strain energy dissipated in a stabilized response cycle can be related to the mean cycles to failure,  $N_f$ , using the following equation,

$$N_f = \left(\frac{\Delta W_{total}}{W_0}\right)^{1/k} \tag{2.19}$$

where  $\Delta W_{total}$  is the total strain energy calculated from the volume-weighted averages over a stabilized cycle,  $W_0$  and k are load-independent material constants. Successful applications of this fatigue model on LLCC leaded packages were reported by Akay [36]. Based on his studies the values of  $W_0$  and k were determined to be  $W_0 = 0.1573$  and k = -0.6342 for the leaded joints tested.

Liang et al [37] have developed a fatigue model that takes into account the geometry of solder joint based on elastic and creep analyses. This model is expressed in Equation (2.20),

$$N_f = C \left( W_{ss} \right)^{-m} \tag{2.20}$$

where  $W_{ss}$  is the stress-strain hysteresis energy density. *C* and *m* are temperaturedependent material constants determined from experiments. Successful application of this model was reported by Liang in BGA packages.

#### 2.3.2 Models Which Include Crack-Propagation

All the above energy-based fatigue models do not account for crack propagation, i.e. they only predict the number of cycles to crack initiation. Prediction of the overall time to failure needs to include crack propagation.

Gustafsson [38] has proposed a fatigue model that combines the crack initiation and propagation based on the findings from Darveaux. This fatigue model is shown in Equation (2.21).

$$N_{\alpha w} = N_{0s} + \frac{a - (N_{0s} - N_{0p}) \frac{da_p}{dN}}{\frac{da_s}{dN} + \frac{da_p}{dN}}$$

(2.21)

For either crack initiation or propagation, it is considered that there are primary and secondary cracks, denoted by the subscripts p and s, respectively. The primary and secondary cracks are considered to initiate and propagate towards each other at different rates.  $N_{\alpha w}$  is the total number of cycles to failure, and a is the total possible crack length.  $N_{0p}$  and  $N_{0s}$  are the primary and secondary crack initiation energy terms, respectively. They can be calculated by Equation (2.22) [38],

$$N_{0p}, N_{0s} = 54.2\Delta W^{-1.00} \tag{2.22}$$

where  $\Delta W$  is energy density calculated from the hysteresis curves in an analysis. Finite element results reported by Gustafsson were based on the leadless RF-transistor solder joints.

The crack propagation terms, da/dN, are dependent on the corresponding values of  $\Delta W$ , as shown in Equation (2.23) [38].

$$\frac{da}{dN} = 3.49 \times 10^{-7} \Delta W^{1.13} \tag{2.23}$$

#### **2.4 Conclusion**

Various fatigue models for solder joint fatigue life prediction are available in the literature. The damage indicators they use range from popular ones like strain range and energy density to less popular ones including stochastic crack, stress and entropy. Among all the solder joint fatigue models, the strain-based and energybased ones constitute the majority. This chapter has reviewed some of the most popular strain-based and energy-based fatigue models. For more details on each of the fatigue models described in this chapter, the readers are encouraged to read the corresponding reference papers.

It should be noticed that each of the fatigue models was developed for a certain type of electronic package. Therefore, when one wants to make accurate fatigue life prediction using a fatigue model he or she should always use the most relevant one, i.e. for a BGA package, use a fatigue model developed for BGA packages rather than another fatigue model developed for leaded packages.

One of the purposes of this work is to carry out solder joint fatigue life prediction for CuC interconnect in WLP. However, the CuC interconnect is a new type of interconnect and no available fatigue models in the literature have been developed specially for solder joint fatigue life prediction of this interconnect/package. Furthermore, this kind of interconnect is still in the development stage and no dummy packages or physical prototypes are readily available for experimentally determining the fatigue life prediction model.

To move forward, this thesis will used Solomon's fatigue correlation,

$$\Delta \gamma_p N_f^{0.51} = 1.14 \tag{2.24}$$

where  $\Delta \gamma_p$  is the cyclic shear strain range. This correlation is chosen based on its ease of use.

# **CHAPTER 3: Simulation-based Design Optimization on CuC 3.1 Introduction**

Traditionally, a product development process from conceptual design to final large-volume manufacturing usually contains the following two typical procedures. 1) The design engineers do the initial design to meet the functional requirements for the product. Some simple analytical calculations are needed to design against potential product failures. 2) After the design procedure, some physical prototypes must be made. Test engineers have those prototypes undergo actual service conditions or sometimes accelerated testing conditions to see whether reliability requirements are met. If, fortunately, those requirements are met, the product may be manufactured in large volume and put into the market. Unfortunately, however, in most cases, not all the reliability requirements are met and re-design, reprototyping and re-testing have to be carried out. The design, prototyping and testing procedures loop until all the reliability requirements are met. This approach for product design is called the trial-and-error method. It is clear that this design approach is quite time-consuming and the final product cost can be very high due to the fact that many loops may have been done until all the reliability requirements are met. Physical prototyping is also expensive.

Recently product development has been speeded up and cost is reduced by the extensive use of computer simulation techniques, which greatly reduce or even in some occasions eliminate the need for physical prototyping. This design approach using computer simulation is often called virtual prototyping. Virtual prototyping means that the prototype is modeled in computer simulations and potential reliability issues are foreseen and reduced as much as possible before physical prototypes are fabricated. By using the virtual prototyping approach, in many cases, physical prototyping and testing are only needed to verify the results of computer simulation. Another benefit that virtual prototyping provides is its ability to gain an insight into the effect that changes in design parameters (i.e. geometry or material properties) have on product reliability and hence give some indications on how to improve the design. The investigation of changes in design parameters on reliability is called parametric study.

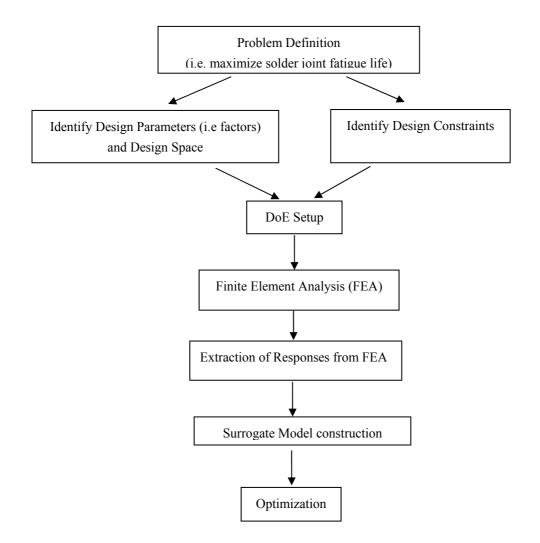

More recently engineers have found that although virtual prototyping combined with parametric study provides critical data and insight into the effects of changes in design parameters such approach can be very time-consuming because each simulation run may require a long time to complete with the presence of nonlinearities in geometry, material properties and boundary conditions. Also, the parametric study cannot investigate two parameters simultaneously and very important interaction effects are likely to be missed in such an analysis. Besides, this approach cannot give enough information on how to arrive at an optimal design within the design constraints. To overcome these drawbacks design of experiments (DoE) technique, Surrogate Modeling technique and numerical optimization technique, together with virtual prototyping have been integrated to form a new design approach called Simulation-based Design Optimization. This new approach not only has the capability to study the effects of changes of different design parameters but also provides a systematic method on how to combine different design parameters within various design constraints to arrive at an optimal parameter combination that leads to optimal reliability.

In the context of solder joint thermo-mechanical reliability design, many researchers have applied the Simulation-based Design Optimization approach to optimize the solder joint fatigue life by finding the optimal or near-optimal set of design parameters (Mertol [39-41]; Dasgupta et al [42]; Zhang [43]; Stoyanov [44]; Vandevelde et al [45-46]; Driel et al [47] [48]; Jagarkal et al [49]; Yang et al [50]; Lee et al [51]).

A typical flow chart for the solder joint thermo-mechanical reliability design using Simulation-based Design Optimization approach is show in Figure 3.1.

Those steps involved in the above flow chart will be explained in detail in the next section.

Figure 3.1 Typical flow chart for Simulation-based Design Optimization

# 3.2 Steps of Simulation-based Design Optimization

## **3.2.1 Problem Definition**

In the current context of solder joint thermo-mechanical reliability design, the problem is solder joint fatigue and the objective is to find an optimal set of design parameters to maximize solder joint fatigue life.

## 3.2.2 Identification of Design Factors, Space and Constraints

Design factors are independent design parameters, i.e. changing one factor will not involve changing the other factors. The design space is typically a multidimensional hypercube defined by the upper and lower bounds of each design factor over some region of interest. The upper and lower bounds of a factor are a special type of constraint. Another type of constraint is the one put on the system response (i.e. the output of an input of design factors combination). An example of this constraint is that while the solder joint fatigue life needs to be maximized, the stress in the chip should not exceed a certain value to avoid die cracking.

#### 3.2.3 DoE Setup

There are actually numerous design points across the design space. To find the optimal design point, obtaining the system responses at all the design points is definitely impractical. Design of experiments (DoE) method is a systematic sampling method used to optimize the selection of design points for subsequent surrogate modeling. There are many types of DoE methods, including the classical ones and new ones developed with the emergence of computer simulation. The classical DoE methods were originally developed for planning physical experiments where random variations cannot be eliminated. Those methods include full factorial design, central composite design (CCD), Box-Behnken design, and their variants [52]. Since the wide use of computer simulation, new data sampling methods known as design and analysis of computer experiments (DACE)

have been developed. These methods include Monte Carlo sampling, Latin Hypercube sampling, and orthogonal array sampling [52].

In the realm of electronic packaging, various researchers have used different DoE methods to sample the design space. Mertol [39-41] applied the orthogonal array sampling method in chip scale package design. Dasgupta et al [42] developed a generic computational optimization methodology based on orthogonal array sampling method. Zhang et al [43] reported Phlips' strategy of virtual thermomechanical prototyping developed based on Latin Hypercube sampling. Vandevelde et al [45] [46] and Driel et al [47] [48] also used the Latin Hypercube sampling method to do the optimization work for thermo-mechanical reliability optimization of chip scale package and nonlinear packaging stress, respectively. Stoyanov et al [44] did a design optimization study using the orthogonal array method for solder joint thermo-mechanical reliability in flip chip package with noflow underill. Jagakal and his colleagues [49] used ANSYS software and its integral optimization module to optimize the solder joint reliability in a board-level electronic package. They used sub-approximation method, full factorial method and CCD method to conduct the optimization study and found that the optimal solution derived based on the full factorial method is best among the three for that specific case. Yang et al [50] did an optimization study for solder joint reliability in a lead-free flip chip on board (FCOBO) package using CCD method. Lee et al [51] performed a full factorial study on the solder joint reliability of a double-layer wafer level package.

From the above literature survey, it seems that the full factorial, orthogonal array and Latin Hypercube methods are more popular than others.

## **3.2.4 Finite Element Analysis**

After the DoE method is chosen, many finite element models will be built according to the different factor combinations or design points sampled from the design space by the selected DoE method and sent to a finite element code for analysis. Usually a finite element analysis of one model is called a trial.

#### **3.2.5 Responses Extraction**

After all the trials are done, the desired system responses must be extracted for surrogate modeling in the next step.

#### **3.2.6 Surrogate Model Construction**

Surrogate model construction, also known as surface fitting, metamodeling or response surface approximation, is widely used in engineering design applications to provide an insight into the trends exhibited by system responses with respect to changes in values of design factors. Once all the system responses at the sampled design points are derived from finite element simulation, it is ready for us to set up a surrogate model. The purpose of surrogate model construction is to derive a closed-form mathematical model to approximate the relationship between design factors and the system response. If such a surrogate model is established, system responses for other design factor combinations or design points can be determined using this model and thus eliminate the need for further expensive and timeconsuming finite element simulations.

There are several types of surrogate model construction methods, including quadratic polynomial model, first-order Taylor series expansion, Kriging spatial interpolation model, stochastic layered perception artificial neural networks, and multivariate adaptive regression splines. All of these surrogate model construction methods can be used to design applications with arbitrary numbers of design factors.

Among all the surrogate model construction methods, the quadratic polynomial is most frequently used due to its computational simplicity and convenient algebraic form [52]. In the design optimization studies for electronic packaging, the popularity of quadratic polynomial can be seen in the works of Mertol [39-41], Dasgupta et al [42], Zhang et al [43], Stoyanov [44], Vandevelde et al [45] [46], Driel et al [47] [48], Jagarkal et al [49], Yang et al [50] and Lee et al [51]. However, surrogate model constructed using the quadratic polynomial method does not always meet the accuracy requirement. If intolerable discrepancy is found between the predicted system response from the surrogate model and true values from computational simulation, more reliable and complex methods, such as Kriging model may be used for surrogate model construction [47].

Typically, a surrogate model constructed using the quadratic polynomial method takes on the form of a fully quadratic polynomial with cross-terms [50] [52].

$$\hat{y} = C_0 + \sum_{i=1}^m C_i x_i + \sum_{i=1}^m \sum_{j=1}^m C_{ij} x_i x_j + \varepsilon$$

(3.1)

In Equation (3.1),  $\hat{y}$  is the response value of the system, *m* is the number of design factors,  $x_i(i=1-m)$  are the design factors,  $\varepsilon$  is the residual error term,  $C_0$  is the constant term of the approximation model,  $C_i(i=1-m)$  are the coefficients of linear terms and  $C_{ij}(i, j=1-m)$  are the coefficients of the quadratic terms.

## 3.2.7 Optimization

Once the response surface approximation model is derived and specified accuracy criteria satisfied, various types of design optimization can be carried out efficiently. If an optimal design parameters combination is derived and this combination is not a trial in the original DoE setup, an extra simulation run based on this optimal parameter setting should be performed as verification.

## 3.2.8 Conclusion

Some commercially available software packages, such as iSIGHT, Modelcenter, Modelfrontier, DAKOTA, Optimus, VisualDoC, can integrate the above design optimization procedures and run those procedures in an integrated and automated manner. But those software tools are not available in our program. To move forward, ABAQUS FEA software, together with statistical software, Minitab and S-Plus, will be used for the current design optimization study and the optimization procedures will be conducted manually.

# **3.3 Optimization Study on the CuC Interconnect**

## 3.3.1 A Brief Note on the CuC Interconnect

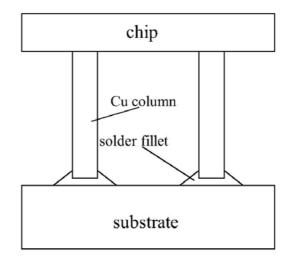

The CuC interconnect is actually a simplified version of the BON interconnect. In this interconnect a copper column with circular cross section is formed by electroplating and joined to the substrate using solder. Therefore, the CuC interconnect is much easier to process than the BON interconnect. The CuC interconnect is supposed to be a compliant interconnect. Figure 3.2 shows a schematic picture of the CuC interconnect.

Figure 3.2 Schematic picture of the CuC interconnect

## **3.3.2** Problem Definition

As far as long-term reliability of electronic package is concerned, solder joint integrity under temperature cycling is vital. The purpose of the current design optimization study on the CuC interconnect is to find an optimized set of design parameters that leads to optimized solder joint thermo-mechanical reliability. In this study, maximization of solder joint fatigue life, i.e. minimization of the fatigue damage indicator at the outermost (critical) interconnect, will serve as the optimization objective.

## 3.3.3 Identification of Design Factors and Space

Based on the inputs from process people, the design factors identified for the current design optimization study are illustrated in Figure 3.3 and listed in Table 3.1.

**Figure 3.3 Illustrations of Design Factors**

| Symbol | Design factors           | Variations     |

|--------|--------------------------|----------------|

| T1     | Chip thickness (µm)      | $250 \sim 640$ |

| T2     | Substrate thickness (µm) | 800 ~ 1200     |

| Н      | CuC height (µm)          | 100 ~ 150      |

| СТЕ    | Substrate CTE (ppm/K)    | 8 ~ 10         |

## Table 3.1 Design factors and their variations

## 3.3.4 DoE Study Setup

Given the design factors and design space, the next step would be the selection of an appropriate DoE method to sample the design space. For the current study, the 2-level full factorial DoE method will be adopted. Since there are four design factors, the number of simulation runs required would be:

$$k^n = 2^4 = 16 \tag{3.2}$$

where k is the number of levels for each design factor, and n is the total number of design factors.

After the DoE method is selected, the design table is built and shown in Table 3.2.

| Trial No. | T1 (µm) | T2 (μm) Η (μm) |     | CTE (ppm/K) |

|-----------|---------|----------------|-----|-------------|

| 1         | 250     | 800            | 100 | 8           |

| 2         | 640     | 800            | 100 | 8           |

| 3         | 250     | 1200           | 100 | 8           |

| 4         | 640     | 1200           | 100 | 8           |

| 5         | 250     | 800            | 150 | 8           |

| 6         | 640     | 800            | 150 | 8           |

| 7         | 250     | 1200           | 150 | 8           |

| 8         | 640     | 1200           | 150 | 8           |

| 9         | 250     | 800            | 100 | 10          |

| 10        | 640     | 800            | 100 | 10          |

| 11        | 250     | 1200           | 100 | 10          |

| 12        | 640     | 1200           | 100 | 10          |

| 13        | 250     | 800            | 150 | 10          |

| 14        | 640     | 800            | 150 | 10          |

| 15        | 250     | 1200 150       |     | 10          |

| 16        | 640     | 1200           | 150 | 10          |

# Table 3.2 DoE design table

# **3.3.5 Finite Element Analysis**

## **Geometry and Mesh**

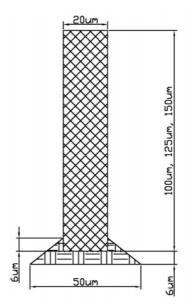

The detailed modeling parameters for the electronic package under investigation are shown in Table 3.3 and Figure 3.4. Those data are based on Table 3.1 and inputs from process group. Based on previous study in [9], the hysterisis loop of stress-strain will converge after five cycles. So five temperature cycles will be simulated in the current analyses.

| Chip thickness           | $250\sim 640 \mu m$   |  |  |

|--------------------------|-----------------------|--|--|

| Substrate thickness      | $800 \sim 1200 \mu m$ |  |  |

| Substrate CTE            | 8 ~ 10ppm/K           |  |  |

| Solder gap               | бµm                   |  |  |

| Column wetting height    | 6µт                   |  |  |

| Solder pad diameter      | 50µm                  |  |  |

| CuC radius               | 25µm                  |  |  |

| CuC height variation     | 100 ~ 150μm           |  |  |

| Interconnect pitch       | 100µm                 |  |  |

| Chip size                | 20mm by 20mm          |  |  |

| Temperature extremes     | 125°C to -40°C        |  |  |

| Number of cycles modeled | 5                     |  |  |

**Table 3.3 Details of modeling parameters**

Figure 3.4 Dimensions of the CuC interconnect

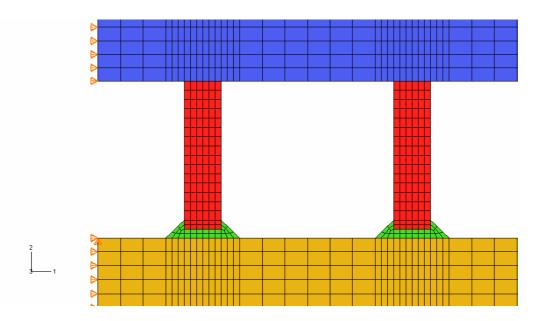

Figure 3.5 2D mesh of the electronic package under investigation (a close-up view of the corner part)

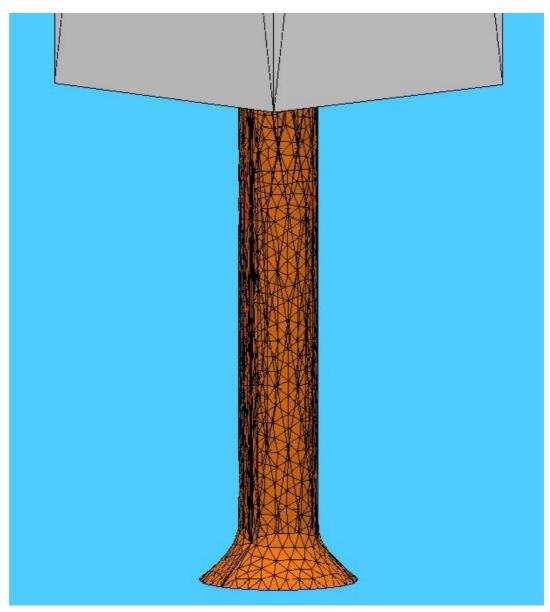

2D plane strain model is used for the finite element analysis in the current design optimization study. Although the 2D plane strain model adopts an inaccurate underlying assumption, it is well suitable for design optimization study where accurate prediction of solder joint fatigue life is not a necessity [53] and only the trend is of more importance. In the current analyses, CPE4 plane strain element in ABAQUS is adopted.

A typical mesh of the package under investigation is shown in Figure 3.5.

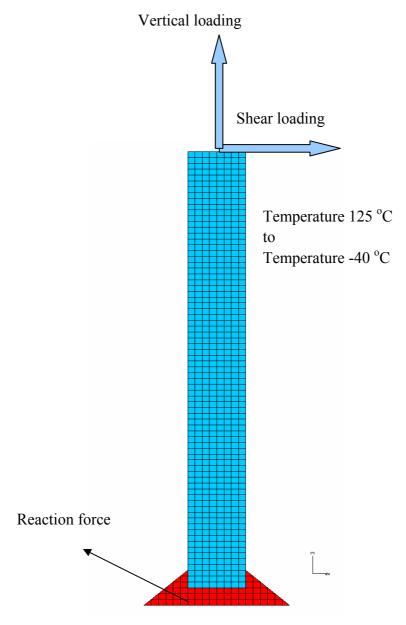

#### **Loading and Boundary Conditions**

When doing the analysis of solder joint thermo-mechanical reliability, we assume that the only loading acting on the electronic package is the cyclic temperature change. In the most rigorous way of solder joint fatigue modeling, initial temperatures are specified for all parts of the package and a thermal analysis is first conducted to obtain the temperature field within the package, then this temperature field is used as an input for subsequent stress analysis [53]. The above analysis is known as sequentially coupled temperature-displacement analysis. However, in most cases, the temperature field is assumed to be uniform in all the parts of the package as the temperature cycles between its extremes [53]. This assumption eliminates the need for a thermal analysis.

In this study, the above mentioned assumption is adopted. The temperature cycling profile is shown in Figure 3.6. The stress-free state is assumed to be at 125°C.

The boundary condition for the finite element model is shown in Figure 3.7. The package neutral line is required only to be able to move along y-direction and a point is fixed to prevent rigid body motion.

Figure 3.7 Boundary conditions of the 2D finite element model

# **Material Properties**

Modeling of solder joint fatigue requires accurate material properties for all the materials in the electronic package. Although such data is extensively available, they are derived from bulk specimens rather than very small-scaled ones. It should be noted that material properties derived from bulk material tests could be quite different from material properties when the characteristic size of the material is down to less than 100µm [54] [55]. Moreover, material properties are also known to be dependent on the preparation procedure of specimens [56]. Due to the lack of appropriate material properties, however, the current study will use the data available in the literature to move forward. Both chip and substrate are modeled as temperature-independent linear elastic materials whose properties are listed in Table 3.4. Copper is assumed to be a temperature-independent elastic-plastic material with properties stated in Table 3.5. Eutectic tin-lead solder is modeled as a temperature-dependent elastic-plastic material whose properties are detailed in Table 3.6 [9] [57]. Due to the prohibitive computational resources required, creep property of solder is not modeled [57].

|                         | Chip | Substrate |

|-------------------------|------|-----------|

| Young's modulus(GPa), E | 131  | 22        |

| Poisson's ratio, υ      | 0.23 | 0.28      |

| CTE(ppm/K)              | 2.8  | 8~10      |

Table 3.4 Material properties for chip and FR4 board

| Young's modulus(GPa), E            | 35.7   |

|------------------------------------|--------|

| Poisson's ratio, v                 | 0.34   |

| CTE(ppm/K)                         | 16.7   |

| Yield stress(GPa), $\sigma_y$      | 100    |

| Plastic strain at stress=125 MPa   | 0.0016 |

| Plastic strain at stress=150 MPa   | 0.0028 |

| Plastic strain at stress=175 MPa   | 0.0043 |

| Plastic strain at stress=200 MPa   | 0.0075 |

| Plastic strain at stress=212.5 MPa | 0.0099 |

| Plastic strain at stress=225 MPa   | 0.0139 |

| Plastic strain at stress=231.7 MPa | 0.0186 |

| Plastic strain at stress=238 MPa   | 0.0301 |

# Table 3.5 Material properties for copper

| Temperature(K)                              | 233    | 273    | 303    | 333    | 363    | 393    | 423    |  |

|---------------------------------------------|--------|--------|--------|--------|--------|--------|--------|--|

| Young's<br>modulus(GPa), E                  | 40.554 | 34.474 | 29.914 | 25,354 | 20.794 | 16.234 | 11.674 |  |

| Poisson's ratio, v                          | 0.35   |        |        |        |        |        |        |  |

| CTE(ppm/K)                                  |        |        |        | 22.4   |        |        |        |  |

| Yield stress(GPa), $\sigma_y$               | 38     | 31     | 25.6   | 20.3   | 14.9   | 9.6    | 4.2    |  |

| Stress(MPa) at<br>plastic<br>strain=0.002   | 46.4   | 39.1   | 32.2   | 25.5   | 17.9   | 10.1   | 4.5    |  |

| Stress( MPa ) at<br>plastic<br>strain=0.005 | 50.2   | 42.3   | 34.8   | 27.4   | 19.3   | 10.5   | 4.7    |  |

| Stress(MPa) at<br>plastic strain=0.01       | 53     | 44.5   | 36.4   | 28.4   | 20     | 10.8   | 4.8    |  |

| Stress(MPa) at<br>plastic strain=0.02       | 56.6   | 46.7   | 37.8   | 29.5   | 20.7   | 11.1   | 4.9    |  |

| Stress(MPa) at<br>plastic strain=0.05       | 60.3   | 49.6   | 40     | 30.9   | 21.4   | 11.5   | 5.0    |  |

| Stress(MPa) at<br>plastic strain=0.1        | 63.4   | 51.7   | 41.6   | 31.9   | 22.0   | 11.8   | 5.1    |  |

| Stress(MPa) at<br>plastic strain=0.2        | 66.8   | 53.9   | 43.2   | 33.1   | 22.7   | 12     | 5.2    |  |

| Stress(MPa) at<br>plastic strain=0.5        | 71.9   | 57.2   | 45.6   | 34.9   | 23.3   | 12.3   | 5.35   |  |

# Table 3.6 Material properties for solder

# **3.3.6 Responses Extraction**

In the current study, incremental equivalent plastic strain defined in Equation (2.5), (2.6) and (2.7) will be used as the indicator of fatigue life. It should be noted that the copper/solder and the solder/substrate interfaces usually involve abrupt geometrical changes which will cause singular stress/strain responses. Since

nonlinear material properties are taken into account, such stress/strain concentration is alleviated. Techniques are needed to characterize the strain response around the singularity point. It is also known that the strain value near the concentration area is very sensitive to mesh density. To solve all the above problems and to make fair comparisons among the results from different models, a volume-weighted technique is adopted to average the strain values derived. The volume-weighted technique is expressed in Equation (3.3) [58],

$$\Delta \varepsilon_{avg} = \frac{\sum_{e=1}^{n} \Delta \varepsilon_{e} \times V_{e}}{\sum_{e=1}^{n} V_{e}}$$

(3.3)

where  $\Delta \varepsilon_e$  is the incremental equivalent plastic strain of the e-th element and  $V_e$  is the volume of the e-th element. In the current study the incremental equivalent plastic strain is averaged over the entire solder volume.

According to the design table shown in Table 3.2, sixteen finite element models for all the sixteen design factors combinations are constructed. The responses for all the sixteen models are extracted and listed in Table 3.7.

| Trial<br>No. | T1<br>(μm) | T2<br>(μm) | H<br>(µm) | CTE<br>(ppm/K) | $\Delta \mathcal{E}_{avg}$ | Surrogate Model predictions |

|--------------|------------|------------|-----------|----------------|----------------------------|-----------------------------|

| 1            | 250        | 800        | 100       | 8              | 0.0066                     | 0.006388                    |

| 2            | 640        | 800        | 100       | 8              | 0.0087                     | 0.008888                    |

| 3            | 250        | 1200       | 100       | 8              | 0.0080                     | 0.008088                    |

| 4            | 640        | 1200       | 100       | 8              | 0.0093                     | 0.009238                    |

| 5            | 250        | 800        | 150       | 8              | 0.0061                     | 0.006013                    |

| 6            | 640        | 800        | 150       | 8              | 0.0078                     | 0.007913                    |

| 7            | 250        | 1200       | 150       | 8              | 0.0074                     | 0.007613                    |

| 8            | 640        | 1200       | 150       | 8              | 0.0084                     | 0.008163                    |

| 9            | 250        | 800        | 100       | 10             | 0.0086                     | 0.008837                    |

| 10           | 640        | 800        | 100       | 10             | 0.0139                     | 0.01369                     |

| 11           | 250        | 1200       | 100       | 10             | 0.0120                     | 0.01189                     |

| 12           | 640        | 1200       | 100       | 10             | 0.0153                     | 0.01539                     |

| 13           | 250        | 800        | 150       | 10             | 0.0076                     | 0.007662                    |

| 14           | 640        | 800        | 150       | 10             | 0.0120                     | 0.01191                     |

| 15           | 250        | 1200       | 150       | 10             | 0.0108                     | 0.01061                     |

| 16           | 640        | 1200       | 150       | 10             | 0.0133                     | 0.01351                     |

Table 3.7 Reponses of all the sixteen finite element models

#### **3.3.7 Surrogate Model Construction**

After all the responses for the sixteen design points are extracted, the next step is to construct a surrogate model to approximate the relationship between the system response and the design factors and interactions. In this study the system response is the volume-weighted incremental equivalent plastic strain.

Various surrogate models may be used for the approximation. In current study, quadratic polynomial model that takes on the form in Equation (3.1) will be adopted. The coefficients in the polynomial equation are determined by fitting the system response data using the least squares approach and is derived using Minitab software. The following quadratic polynomial shown in Equation (3.4) is found to be the approximation between the volume-weighted incremental equivalent plastic strain  $\Delta \varepsilon_{avg}$  and the four design parameter, T1, T2, H and CTE:

$$\begin{split} &\Delta \varepsilon_{avg} \left( \text{T1(mm),T2(mm),H(mm),CTE(ppm/K)} \right) \\ &= -0.000139423076922915 - 7.69230769230764e - 006 \times T1 \\ &- 6.5865385113284e - 006 \times T2 + 6.81923096999526e - 005 \times H \\ &- 7.82051283749752e - 005 \times \text{CTE} - 8.65384587086737e - 009 \times T1 \times T2 \\ &- 3.07692307978868e - 008 \times T1 \times H + 3.01282061263919e - 006 \times T1 \times \text{CTE} \\ &- 4.99999987368938e - 009 \times T2 \times H + 1.68750004377216e - 006 \times T2 \times \text{CTE} \\ &- 7.999999797903e - 006 \times H \times \text{CTE} \end{split}$$

After the above surrogate model is derived, its accuracy must be evaluated. Several statistical methods which are based on Residual Analysis, Analysis of Variance, and statistical efficiency measures, can be used to judge the quality of the

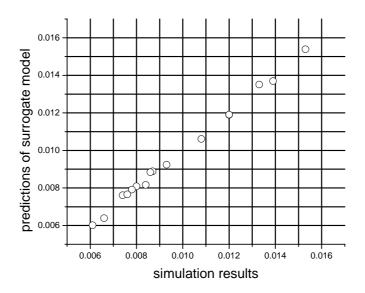

generated quadratic polynomial approximation. These methods have shown that the above polynomial approximation provides a good fit. In Figure 3.8 the volumeweighted incremental equivalent plastic strain values predicted by Equation (3.4) are plotted against the actual values from simulation results. Clearly we can see that the quadratic polynomial approximation gives acceptable accuracy. The coefficient of determination,  $R^2$ , is also a measure of the accuracy of the surrogate model fit. When the surrogate model is a perfect fit,  $R^2$  is equal to one. The  $R^2$  value for the above derived quadratic polynomial surrogate model is 0.989, showing a good fit between the surrogate model and the simulation results at all the design points.

Figure 3.8 Predicted values VS simulation results