# LOW NOISE AMPLIFIER DESIGN AND NOISE CANCELLATION FOR WIRELESS HEARING AIDS

ZHANG LIANG

NATIONAL UNIVERSITY OF SINGAPORE

2005

# LOW NOISE AMPLIFIER DESIGN AND NOISE CANCELLATION FOR WIRELESS HEARING AIDS

ZHANG LIANG

# A THESIS SUBMITTED

# FOR THE DEGREE OF MASTER OF ENGINEERING

### DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

### NATIONAL UNIVERSITY OF SINGAPORE

2005

# Acknowledgements

I would like to thank my supervisors, Dr. Ram Singh Rana and A/Prof. Hari Krishna Garg. They gave me opportunities to blossom my research ideas. Their research attitudes and inspirations are impressed deeply on me. During the two years study, they helped me open my mind and be an independent researcher. I learnt a lot from them not only how to think about problems but also how to do the research work. I hope they are proud of having me as research scholar as I am proud to have them as my supervisors.

Specifically thank to my colleague, TangBin who is pursuing his Graduate Program in Bioengineering. I really appreciate many valuable discussions held with him. Furthermore, I would like to thank the Institute of Microelectronics (IME) for providing the scholarship in the past two years. This work has been supported by IME and NUS (National University of Singapore). The infrastructure and the fabrication support provided by IME are greatly acknowledged.

Finally, I thank my families for their never-ending support who had patience while I was away from them during this research work.

# **Table of Contents**

| Acknow    | vledgements                                         |    |

|-----------|-----------------------------------------------------|----|

| Summa     | ry                                                  |    |

| Table o   | f Contents                                          |    |

| List of   | Tables                                              |    |

| List of ] | Figures                                             |    |

| Chapte    | r 1 Introduction                                    | 1  |

| 1.1       | Introduction                                        | 1  |

| 1.2       | Design Challenges of Hearing Aid Device             | 10 |

| 1.3       | Objective and Scope of Thesis                       | 17 |

| 1.4       | Organization of Thesis                              | 17 |

| Chapte    | r 2 Low Noise Amplifier Design and Optimization     | 19 |

| 2.1       | Introduction                                        | 19 |

| 2.2       | RF Models for LNA Design                            | 19 |

| 2.3       | LNA Design Topologies                               | 24 |

| 2.4       | Specification Freezing and Design Target            | 26 |

| 2.5       | Low Noise Amplifier Design                          |    |

| 2.6       | LNA Simulation Results                              | 35 |

| 2.7       | Conclusions                                         |    |

| Chapte    | r 3 Low Noise Amplifier Measurement and Discussions | 40 |

| 3.1       | Introduction                                        | 40 |

| 3.2       | LNA Chip Layout Development                         | 40 |

| 3.3       | LNA PCB Layouts                                     | 42 |

|    | 3.4    | LNA Measurement Setup and Testing                       | .47 |

|----|--------|---------------------------------------------------------|-----|

|    | 3.5    | LNA PCB Measurement Results and Discussion              | .51 |

|    | 3.6    | LNA Performance Comparison with Others Works            | .57 |

|    | 3.7    | Conclusions                                             | .58 |

| Cl | naptei | • 4 Noise Cancellation for Wireless Hearing Aid Devices | .60 |

|    | 4.1    | Introduction to Background Noise Cancellation           | .60 |

|    | 4.2    | Behavior Model Development                              | .67 |

|    | 4.3    | Behavioral Simulation and Model Validation              | .71 |

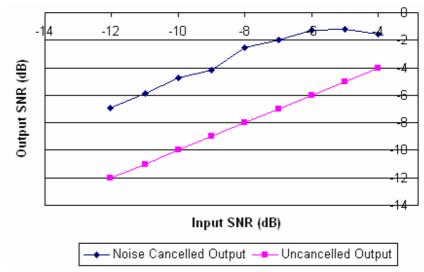

|    | 4.4    | Noise Cancellation Simulation in Wireless Hearing Aid   | .79 |

|    | 4.5    | Conclusions                                             | .82 |

| Cl | napter | 5 Conclusions and Future Works                          | .84 |

|    | 5.1    | New Development                                         | .84 |

|    | 5.2    | Main Conclusions                                        | .84 |

|    | 5.3    | Future Works                                            | .85 |

## References

# Appendices

| A. | LPLV LNA Design and Optimization Steps                      | 92   |

|----|-------------------------------------------------------------|------|

| B. | Proof of Two-element Microphone Array Beamformer Limitation | 95   |

| C. | MATLAB Simulation Program for Noise Cancellation            | 98   |

| D. | Author's Related Publications                               | .103 |

# **Summary**

Wireless technology is one of the most promising approaches for future hearing aids research. Compared to the conventional hearing aids, wireless hearing aids provide a clearer voice, longer operation time, easy communication with other audio devices, and so on. Although the advantages of the wireless hearing aids, noise cancellation and power consumption are still the key issues in research, which require more efficient noise cancellation method and lower power consumption circuit design.

Receiving the processed audio signal within the power budget of the wireless hearing aid earpiece is one of the inherent design challenges. Low noise amplifier (LNA) is the first stage to receive the signal, which is embedded in the earpiece of a wireless hearing aid. There has been not much attempts to implement a CMOS receiver for the earpiece of wireless hearing aid systems. As an attempt towards its CMOS implementation, an integrated single-ended CMOS LNA with inductive degeneration at the source is presented. The power consumption is the key issue to concern in this design. Because the earpiece and the body unit for hearing aid device are separated within about one meter, the noise figure and gain is not as important as power consumption. With the small power consumption, the LNA should have good linearity also. According to the normal hearing aid battery capacity, the total power consumption of an earpiece, where receiver is the most power hungry block, should be as low as possible but below 3.0 mW [1]. The recently reported 0.9 GHz CMOS receiver consumption will extend the battery life. A single ended low voltage and low power LNA was implemented in CSM 0.18 µm

CMOS technology. The LNA is powered at 1.0 V supply and drains only 0.95 mA. The LNA provides a forward gain of 11.91 dB with a noise figure of only 2.41 dB operating in the 0.9 GHz band. The IIP3 is 0.7 dBm and the P1dB is -12 dBm. The proposed design also meets requirements on noise, linearity and gain for 0.9 GHz low power applications, specifically suitable for CMOS wireless hearing aids.

Another consideration in this research work is about canceling the environmental noise. Normally, an input to hearing aids is often associated with the environmental noise. For instance, due to the environmental noise, a hearing-impaired person not only feels severe hearing loss but also is unable to perceive desired speech from the noisy environment. Thus, the noise cancellation is a primary concern, particularly for hearing impaired. In this thesis, a modified two-element beamforming method for noise cancellation is introduced, which helps reduce the surrounding environment noise. This method needs to be verified before physical implementation. So, the behavior model for this method is also presented, which shows a better noise cancellation performance. In addition, the whole wireless hearing aid system is simulated using the proposed noise canceling model. The simulation satisfies the proposed method.

# Nomenclatures

- ADC: Analog-to-Digital Converter

- ADS: Advance Design System

- BSIM: Berkeley Short-channel IGFET Model

- BSIM3: third generation BSIM

- CAD: Computer Aided Design

- CIC: Completely In Canal hearing aid

- CMOS: Complimentary Metal Oxide Semiconductor

- CSM: Charted Semiconductor Manufacturer

DC: Direct Current

- DAC: Digital-to-Analog Converter

- DRC: Design Rule Check

- DSP: Digital Signal Processing

- DUT: Device Under Test

- EDA: Electronics Design Automation

- HA: Hearing Aid

- IEEE: Institute of Electrical and Electronic Engineer

- IIP3: Input-referred third-order Intercept Point

- IME: Institute of Microelectronics, Singapore

- ITC: In The Canal hearing aid

- LNA: Low Noise Amplifier

- LPLV: Low Power consumption Low Voltage

- MIM: Metal Insulator Metal

MOSFET: Metal-Oxide-Semiconductor Field Effect Transistor

NF: Noise Figure

- NMOSFET: Negative Channel MOSFET

- NQS: Non-Quasi-Static

- PMOSFET: Positive Channel MOSFET

- P1dB: 1 dB compressor Point

- QPFSK: Quadrature Phase-Shift Keying

- RF: Radio Frequency

- SMA: SubMiniature version A

- SNR: Signal to Noise Ratio

- SPICE: Simulation Program for Integrated Circuits Emphasis

- SPL: Sound Pressure Level

# **List of Figures**

| Fig. 1.1  | Some conventional hearing aids                                                | 4  |

|-----------|-------------------------------------------------------------------------------|----|

| Fig. 1.2  | An analog hearing aid system                                                  | 5  |

| Fig. 1.3  | A digital hearing aid system                                                  | 6  |

| Fig. 1.4  | Typical wireless hearing aid principle                                        | 8  |

| Fig. 1.5  | Typical wireless hearing aids system construction                             | 9  |

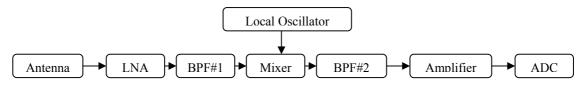

| Fig. 1.6  | Typical RF receiver architecture                                              | 13 |

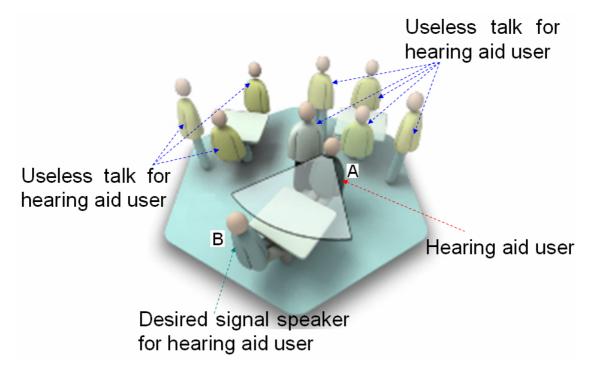

| Fig. 1.7  | Example for noise cancellation application situation in hearing aids design . | 16 |

| Fig. 2.1  | NMOSFET model for RF circuit design                                           | 21 |

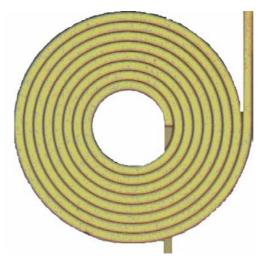

| Fig. 2.2  | Layout of circular spiral inductors                                           | 22 |

| Fig. 2.3  | Circular spiral inductor model                                                | 22 |

| Fig. 2.4  | Layout of MIM capacitors structure                                            | 23 |

| Fig. 2.5  | MIM capacitor model                                                           | 24 |

| Fig. 2.6  | Different LNA topologies                                                      | 25 |

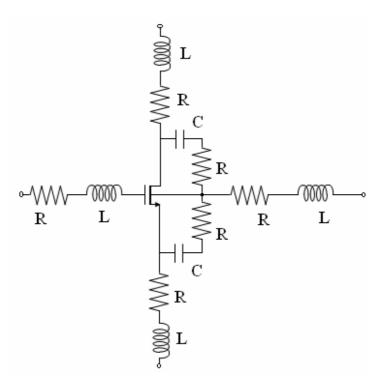

| Fig. 2.7  | LNA circuit schematic                                                         | 29 |

| Fig. 2.8  | Noisy two ports network driven by noisy source                                | 31 |

| Fig.2.9   | Small equivalent circuit for CMOS LNA                                         | 33 |

| Fig. 2.10 | S-parameter input and output matching simulation results                      | 36 |

| Fig. 2.11 | S-parameter noise figure simulation results                                   | 37 |

| Fig. 2.12 | S-parameter power gain simulation results                                     | 37 |

| Fig. 3.1  | LNA chip bounding diagram                                                     | 42 |

| Fig. 3.2  | PCB description for LNA testing                                               | 43 |

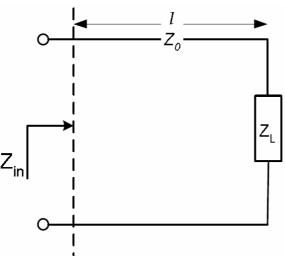

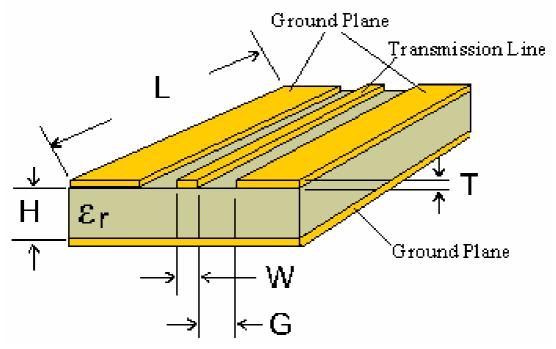

| Fig.3.3     | Transmission line $Z_0$ terminated with $Z_L$                                   | .44 |

|-------------|---------------------------------------------------------------------------------|-----|

| Fig. 3.4    | Cross-section of symmetric coplanar waveguide with ground plane                 | .45 |

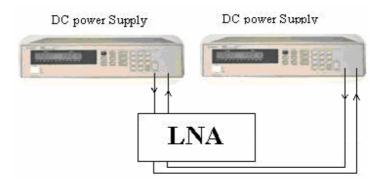

| Fig. 3.5    | DC measurement setup                                                            | .48 |

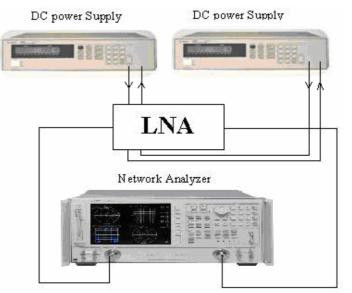

| Fig. 3.6    | S-parameters measurement setup                                                  | .48 |

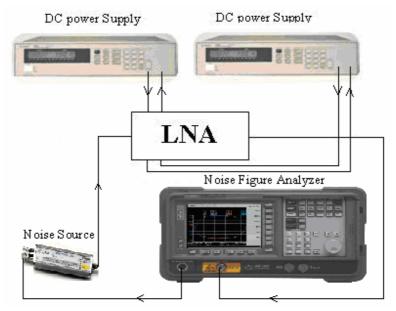

| Fig. 3.7    | Noise figure measurement setup                                                  | .49 |

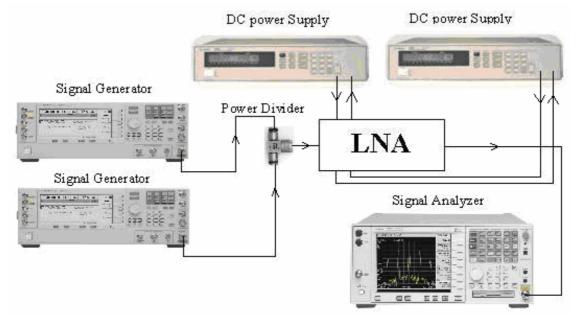

| Fig. 3.8    | Linearity measurement setup                                                     | .50 |

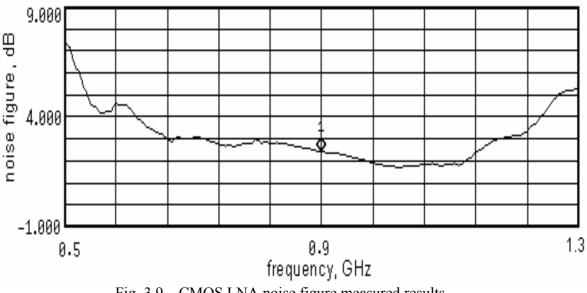

| Fig. 3.9    | CMOS LNA noise figure measured results                                          | .51 |

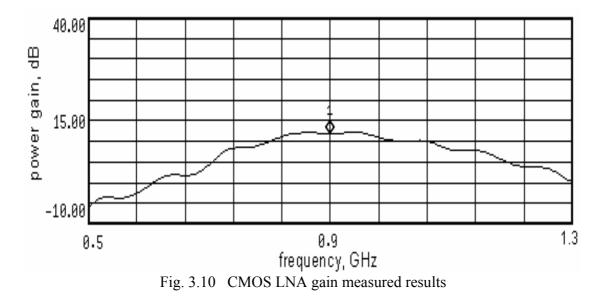

| Fig. 3.10   | CMOS LNA gain measured results                                                  | .52 |

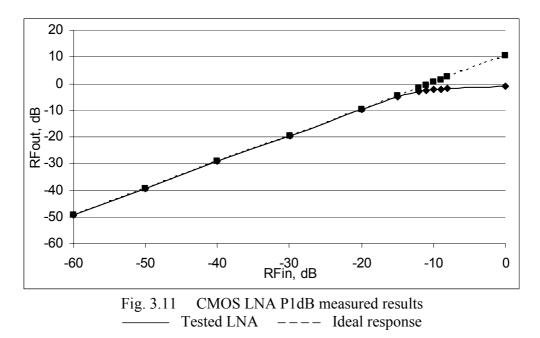

| Fig. 3.11   | CMOS LNA P1dB measured results                                                  | .52 |

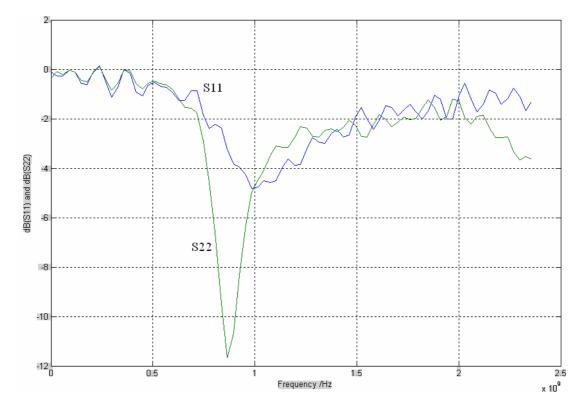

| Fig. 3.12   | CMOS LNA input and output matching measured results                             | .53 |

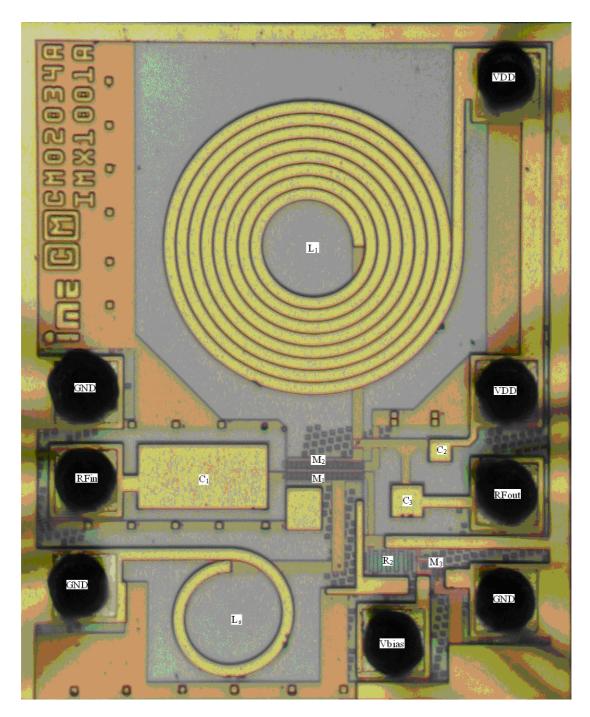

| Fig. 3.13   | LNA chip microphotograph                                                        | .54 |

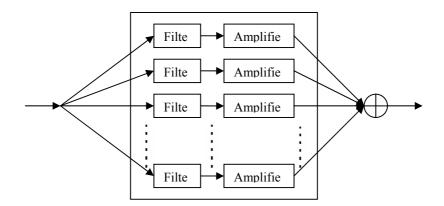

| Fig. 4.1    | Filter bank for noise cancellation                                              | .60 |

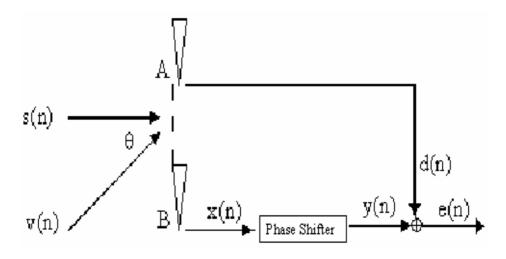

| Fig. 4.2    | Two-element beamformer                                                          | .63 |

| Fig. 4.3    | A two-element microphone array beamformer                                       | .63 |

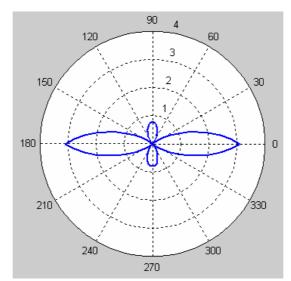

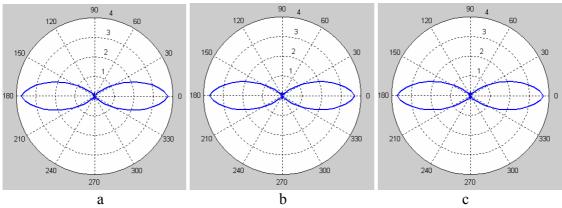

| Fig. 4.4    | Directivity pattern of two-element beamformer                                   | .65 |

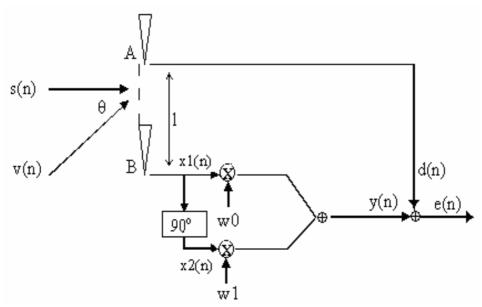

| Fig. 4.5    | A modified two-element beamformer                                               | .66 |

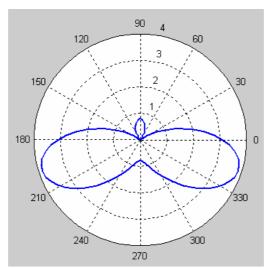

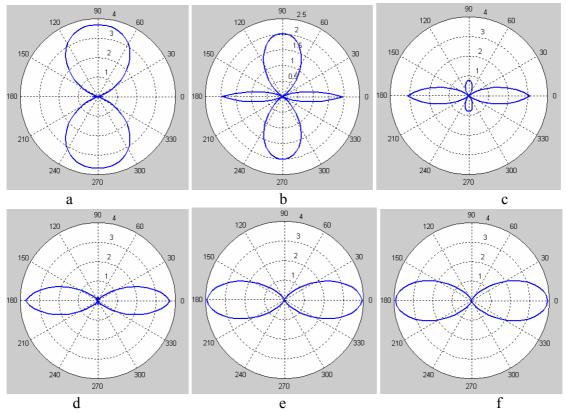

| Fig. 4.6    | Directivity pattern of modified two-element beamformer                          | .67 |

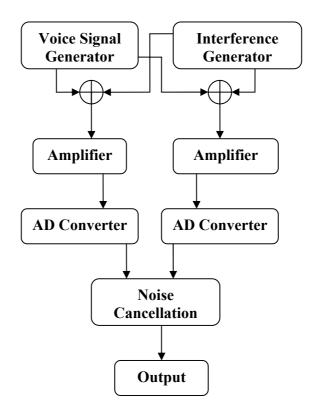

| Fig. 4.7    | A typical system using noise cancellation in an audio device                    | .68 |

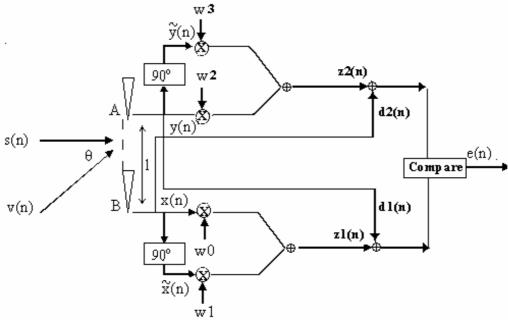

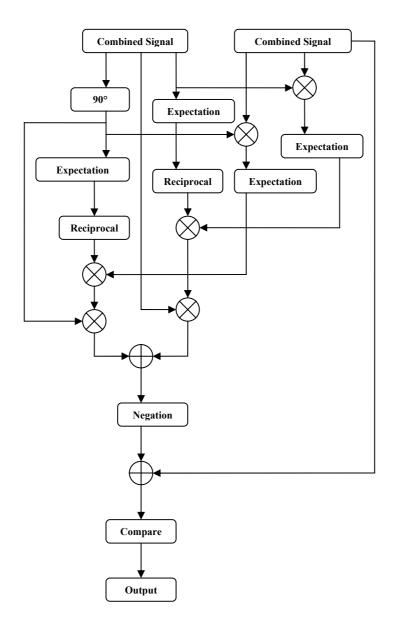

| Fig. 4.8    | Extended block diagram of single path beamforming                               | .70 |

| Fig.4.9     | Directivity pattern of modified two-element beamformer with differ              | ent |

| direction a | angle between noise and voice signal $\theta_0$ which is for constructing model | .72 |

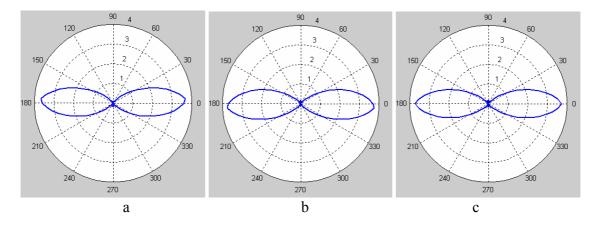

| Fig. 4.10   | Directivity pattern of modified two-element beamformer with different in        | put |

| SNR         |                                                                                 | .74 |

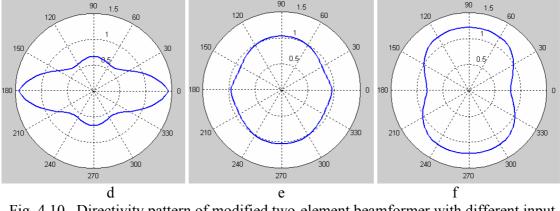

| Fig. 4.11    | Directivity pattern of modified two-element beamformer with different                                                           |

|--------------|---------------------------------------------------------------------------------------------------------------------------------|

| variances of | of signal $\sigma_{\alpha}$ and different variances of noise $\sigma_{\beta}$                                                   |

| Fig. 4.12    | Directivity pattern of modified two-element beamformer with different center                                                    |

| frequency    | of signal and noise76                                                                                                           |

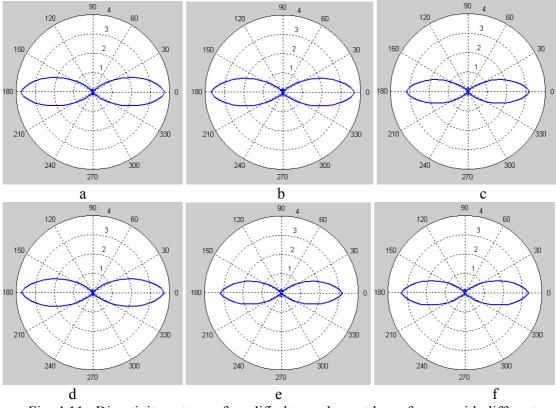

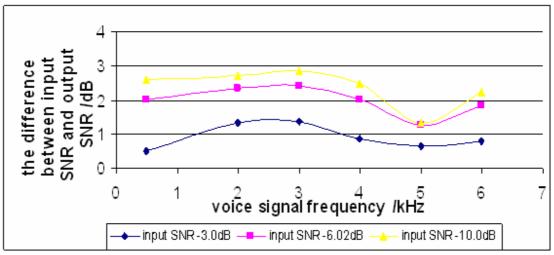

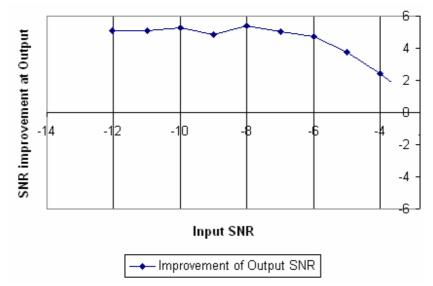

| Fig. 4.13    | Difference between input SNR and output SNR of modified two-element                                                             |

| beamform     | er for different frequency77                                                                                                    |

| Ei~ 111      |                                                                                                                                 |

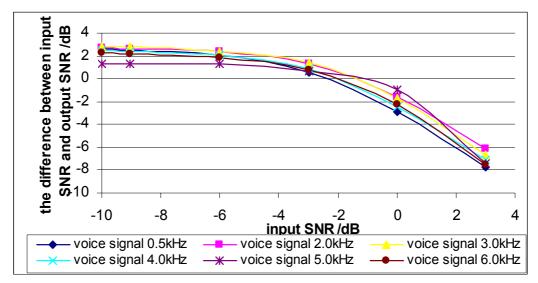

| FIg. 4.14    | Difference between input SNR and output SNR of modified two-element                                                             |

| e            | Difference between input SNR and output SNR of modified two-element<br>er for different input SNR (noise frequency is at 1 kHz) |

| beamforme    |                                                                                                                                 |

# List of Tables

| Table 1.1 | Hearing aid battery capacity in the market     | 11 |

|-----------|------------------------------------------------|----|

| Table 2.1 | Advantages and disadvantages of LNA topologies |    |

| Table 2.2 | LNA specifications design target               | 27 |

| Table 2.3 | Component values of LNA                        |    |

| Table 2.4 | Proposed LNA simulation performance summary    |    |

| Table 3.1 | Pin description of the LNA test chip           | 43 |

| Table 3.2 | Double-Sided FR-4 PCB parameters               | 46 |

| Table 3.3 | Component sizes in the LNA test PCB design     | 47 |

| Table 3.4 | DC measurement equipment list                  | 47 |

| Table 3.5 | S-parameters measurement equipment list        | 48 |

| Table 3.6 | Noise figure measurement equipment list        | 49 |

| Table 3.7 | Linearity measurement equipment list           | 50 |

| Table 3.8 | LNA measurement summary                        | 55 |

| Table 3.9 | A comparison of recent LVLP CMOS LNA designs   |    |

# **Chapter 1** Introduction

#### 1.1 Introduction

Keeping in view the global population of hearing impaired people in the world, there is a huge market demand on hearing aid devices. Thanks to the microelectronics development, it attracts more and more the interest of industries attempting to exploit the micro-technologies for hearing aids devices [3].

A hearing aid is an electronic, battery-operated device that amplifies and changes sound to allow for improved communication. Hearing aids receive sound through a microphone, which then converts the sound waves into electrical signals. The amplifier increases the loudness of the signals and then sends the sound to the ear through a speaker. Every conventional electrical hearing aid has mainly three parts [4] :

(1) A microphone used to collect the sound and convert into electrical impulses. Thus, reproduces the rise and fall of pitch of the sound (high or low) and the intensity (loudness measured in decibels).

(2) An amplifier, modulates the electrical impulses, makes sounds louder. It has an integrated circuit comprising of several transistors or a combination of integrated circuits.

(3) A speaker (earphone) converts the amplified signal into sounds and feeds them into the ear.

Hearing aids have been developed for a long time since the year 1800 [4], [5]. The Greeks used shells and Romans had bronze funnels, but it was only in the 1800's that the first ear horns or trumpets were developed. In 1800's London F C Rein company

established itself as the first company to manufacture hearing aids on a commercial basis. In 1892 the first hearing aid, a carbon hearing aid, was produced at the Pilitzer Clinic in Vienna. It consists of an earphone connected to a carbon microphone fastened onto a battery box. Alexander Graham Bell is also credited as the first to build an earphone which amplifies sound for the hearing impaired. In 1901 the first commercial aid was the Akoulallion 1899, but this carbon ball invented in 1901 led to an increase in the quality and reliability of electrical hearing aids. An electrical hearing aid was used by the English Queen Alexandra for her coronation of 1902. In 1934, the first vacuum tube aid was developed in England, consisting of a microphone, an earphone, an amplifier and two batteries. Vacuum tube technology rapidly became the hearing aid standard. However, the new vacuum aid requires two large batteries which usually last one day only. The transistor was invented by Bell laboratories in 1947 and in 1953 transistor hearing instruments were fabricated to make them smaller, cheaper and more effective. The transistors allow behind-the-ear aids to develop. Other head worn aids are often attached to hair with a clip. In 1970 hybrid hearing aids combined both digital and analog circuitry. These were the first to include a digital chip and were a fraction of the size of previous hearing aids. Leading up to the 70's, behind the ear aids (BTE) almost fit behind the ear. In-the-ear aids (ITE) became popular in the late 70's, which are more reliable and smaller. In the 1980's, the first programmable hearing aids were developed. First digital hearing aid circuits are similar to those in personal computers. Programmable aids allow user to control hearing in different situation. In 1990's the first automatic aids without volume control were made available. Moreover, the first fully digital hearing aid came out in 1997. The first completely digital CIC was also announced around the same time. The

CIC hearing aids now are smaller than ever before allowing truly "invisible" hearing for all. In 2001, with the RF technology and IC design development a kind of wireless hearing aid was invented [1]. At present, the wireless hearing aids are the research focus which would bring many advantages over the traditional hearing aids. The CMOS technology seems the most promising to provide high performance.

Hearing aid manufacturing is a highly technical and delicate task. Most of the hearing impaired persons' hearing losses are different from each other's hearing loss, so each hearing instrument has to be customized to match the user's exact needs. The elements which go into making a hearing aid should not be compared to a pair of spectacles, which have mass-produced frames and lenses, but are actually closer to that of a sophisticated piece of specialist hi-fi equipment. As every customer's hearing loss is unique, so every hearing aid is different. The type of hearing aid best suited to a customer depends largely on their type of hearing loss, in addition to the physical and cosmetic considerations [6]. In Fig. 1.1 a few sample of the range of styles and sizes of hearing instrument available in the market are depicted [7].

BEHIND THE EAR HEARING AID IN THE EAR HEARING AID

#### COCHLEAR IMPLANT HEARING AID

Fig. 1.1 Some conventional hearing aids

Behind the ear hearing aids (BTE) are usually cheaper, easier to adjust than other devices. It is fairly visible and usually more powerful, thus fewest number of problems with wax or infections. Completely in the canal hearing aid (CIC) cannot be seen and require tight fit. It is hard to adjust and remove. CIC aid is so small that it is invisible. However, the battery capacity is limited, so the user needs to change the battery more frequently. Behind the ear hearing aids are bigger in size than CIC aids. Hence more circuits can be built in with more functions, such as clearer voice. In the ear hearing aid (ITE) is less visible, harder to put in and adjust compared to the CIC aid. In the canal

hearing aid (ITC) is even less visible and consumes less power than ITE. As a result, hearing-impaired patients with tremor or poor eyesight are not good candidates for ITC/CIC aids. Cochlear implant hearing aids are more advanced, mostly recommended to patients with profound loss/deaf [7]. First, sound is picked up by a directional microphone and sent from the microphone to the speech processor. Then the speech processor analyzes and digitizes the sound into coded signals. Third, coded signals are sent to the transmitter via radio frequency. The transmitter sends the code across the skin to the internal implant. Fourth, the internal implant converts the code to electrical signals. The signals are sent to the electrodes to stimulate the corresponding hearing nerve fibers. Finally, the signals are recognized as sounds by the brain, thus produce a hearing sense.

Fig. 1.2 An analog hearing aid system

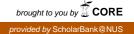

For simplicity, among the above mentioned hearing aids, from circuit point of view hearing aids can be categorized mainly of two kinds: (i) the conventional hearing aids and (ii) wireless hearing aids. Wireless hearing aids using wireless technology are under investigations [1]. From the circuit operation and signal processing point of view, the conventional hearing aids are generally of two types: (i) analog hearing aid (Fig. 1.2) and (ii) digital hearing aid (Fig. 1.3) [5], [7]. Analogue hearing aids use microphone to convert sounds into an electric signal which is modified in a miniature amplifier and converted back into sound by a receiver. That sound passes into the ear and is heard by

the patient. After 1996, with the rapid growth in digital communications, the first digital hearing aid was fabricated. The digital hearing aid uses the microphone to get the electrical signal. Then after A/D conversion, the digital signal processing (DSP) is performed to get rid of the noise and modulate the signal. Finally, the digital signal is converted to analog signal which is heard by the user. Hearing aids with digital technology contain a very advanced degree of signal processing that can provide better accuracy, sound quality, perception of loudness and environmental noise reduction [5], [8]. At the same time, digital hearing aids can have many separate amplifier channels. Most digital models are programmable using personal computers and can offer a high degree of flexibility and precision. Moreover, the digital hearing aid, which is so small as to be practically invisible out of canal, could be compared to a contact lens.

Fig. 1.3 A digital hearing aid system

Because of the advantages of the digital hearing aid, many researchers focus on the digital hearing aid. The major concerns in the hearing aid design are noise and echo cancellation by DSP and the whole system power consumption budget. However, taking into account the limited size and battery supply in hearing aid devices, putting DSP chip in the earpieces perhaps is intuitively not the best choice. For traditional hearing aids, the battery capacity is limited, such as one kind of 600 mAh battery in the market [9], because of the small size of hearing aids. It is difficult to build complex circuits for the hearing aids, because of the limited power supply, especially for the CIC. For example, some good noise cancellation performance method can not be built in the hearing aid

(HA), which needs more circuits to be implemented. Usually, conventional hearing aids use the filter banks to cancel the noise, so the noise cancellation performance is limited. To solve this problem, some manufactures use bipolar technology in their hearing products, because the bipolar technology consumes less power to get the similar performance compared to the CMOS technology. However, the hearing aids built with bipolar technology are more expensive than those with the CMOS technology.

The size of the hearing aid is small, such as CIC, so it is not practical to design a hearing aid in only one part with the trade off in size, power consumption, and efficiency. It faces challenges to improve the hearing aids performances further.

The integrated circuits design has been scaled down to deep submicron (DSM) technology. Analog, digital, mixed signals and radio frequency signals processing circuits can be built into one chip. Digital signal processing methods are more advanced than before, better noise canceling circuits can be implemented in a DSP chip. Considering recent evolutions, the wireless hearing aids having multi-microphones, analog, digital and mixed signals and radio frequency signals processing circuits, DSP and programmable unit seem to be promising to provide enhanced performance [1], [10].

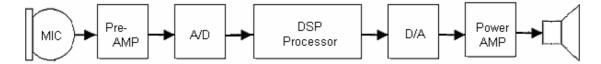

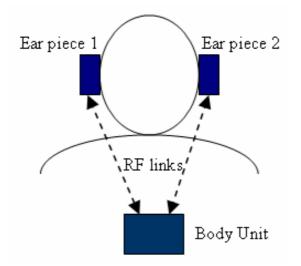

A typical wireless hearing aid scheme is shown in Fig. 1.4. It has a body unit and an earpiece [1]. The earpiece communicates with the body unit by a RF link. The earpiece receives the audio signal and converts it into an electrical signal. After A/D conversion, the signal processing is done in the body unit and transmits back into the earpiece using RF link. The earpiece converts the RF signal into audio signal and feeds it into the patient's ear. This kind of wireless hearing aid has several characteristics. It gives better noise cancellation, easy trade off in hearing aid earpiece power consumption and size etc.

Fig. 1.4 Typical wireless hearing aid principle

Based on the concept of RF link as shown in Fig. 1.5 [1], a typical wireless hearing aid can be configured as shown in Fig. 1.5. In this architecture, the wireless hearing aid has two separate parts, a body unit and an earpiece with RF wireless links connecting between them. The voice sound is received by the microphones in the earpiece. In order to get a clearer voice, only one microphone is not enough [5]. So, in the wireless hearing aids, there are two omni-directional microphones built in the body unit, which not only provide a good noise cancellation performance, but also help the users locate the sound. The microphone outputs are amplified to feed forward into the following AD converter. After AD conversion, the data are transmitted into a RF receiver in the body unit. The DSP block following the RF receiver lies in the body unit and functions to eliminate unwanted surrounding noise, reverberations and echo. Various DSP algorithms are implanted to realize complex functions [11], [12]. The noise cancellation output is transmitted between earpiece and body unit via RF wireless link. Modulation methods are optimized for a tradeoff between size, complexity and power. After the RF receiver receives the RF signal from RF transmitter in the body unit, the signal is down converted to low frequency signal. Then the digital signal is converted to analog signal by D/A converter to drive the earpiece speaker.

Fig. 1.5 Typical wireless hearing aids system construction

Some characteristics of a wireless hearing aid, compared to the conventional hearing aids, as discussed below:

(1) Wireless hearing aids primarily have two parts, body unit and earpiece, connected by a RF link. The body unit size is bigger than conventional hearing aid size. The bigger battery with higher capacity is used in the body unit. The power hungry circuits for hearing aids can be built in body unit. As a result, the earpiece can be built with less power consumption circuits and of the smaller size.

(2) Better noise cancellation method is implemented in DSP part in the body unit for clear voice. There are several good noise cancellation performance methods based on adaptive signal processing, which are built in the DSP block. Moreover, two microphone inputs and binaural configuration also help noise cancellation and sound localization.

(3) In order to be compatible with other audio device, these functions can be realized in DSP block inside body unit. As is a trend to be all-in-one, the features of the body unit can be embedded with other audio devices, such as mobile phone, MP3 player, FM receiver and other handheld audio devices.

(4) HA circuit noise is one of the most stringent problems for the HA users, if the circuit noise is so large that makes the useful signal distortion. It is possible to design more compensation circuits for less noise in body unit, because of more power capacity and larger size of body unit.

Keeping above in view, wireless hearing aids seem quite promising, which are currently under research and investigations.

#### **1.2 Design Challenges of Hearing Aid Device**

For a long time, hearing impairment has been an inevitable severe problem in the medical community. However with technological evolutions, attempts have been made to provide hearing aids. With the increase of IC technology development, currently available hearing aid devices, such as analog hearing aids, though help the patients up to certain extent, have the severe problems related with noise and echo. They do not satisfy users' need. With time, technology has been further advanced and it has opened a wider window to overcome such problems. More and more researchers [1], [3] show their interests in the study of advanced hearing aid devices which give more benefit to the hearing impaired. Many of them focused on the issue of digital signal processing (DSP) method for noise cancellation, speech quality improvement, ultra low power consumption and lower price, etc. However, there are a number of design challenges to bring the technology to the end user. It includes issues related with minimum power consumption, noise cancellation, size and portability, etc.

#### **1.2.1** Size and Power Consumption

A hearing aid system invisible to other people like CIC or ITC hearing device is more acceptable to the impaired nowadays. However, the limited size of hearing devices is not able to hold current complex functions, which needs more complicated circuits and power consumption.

The problem is how to realize a tiny hearing aid with complex function. While highly integrated circuit is needed to realize complex functions, separating redundant components from ear-piece to a body unit can be a choice [10].

Battery life is a crucial characteristic of hearing aid devices. Worn by the patients throughout the day, hearing devices are expected to maintain a longer working life. Some researches [13] focus on developing long-lasting batteries which are out of the scope of this thesis. Another way is using rechargeable battery that is recharged when it has no power. In the market, there are different kinds of batteries for hearing aids. Unfortunately, the power capacity of battery for hearing aid is limited, even for BTE hearing aids. In Table 1.1, some hearing aids battery capacities are shown [9]. At the one side, investigations are needed to enhance the battery capacity, at the other side, circuit design researches are focused on reducing power consumption of the hearing aid systems.

| Table 1.1            | Table 1.1 Hearing aid battery capacity in the market |                |  |

|----------------------|------------------------------------------------------|----------------|--|

| Battery model number | H.A. type                                            | Capacity / mAH |  |

| A675                 | BTE                                                  | 600            |  |

| A13                  | BTE/ITE                                              | 260            |  |

| A312                 | ITE/ITC                                              | 150            |  |

| A10                  | ITC/CIC                                              | 80             |  |

| A675P                | Cochlear                                             | 520            |  |

The present hearing aids are built using microchip and other electronic components. Obviously, the microchip power consumption should be reduced. In the conventional hearing aids, especially digital hearing aids, noise cancellation method is implemented in the chip. Since the complexity of noise cancellation algorithm should be increased for improved noise cancellation performance, so as the power consumption. With the development of semiconductor technology, especially submicron technology, the circuits can be built with much less power consumption to realize same function. To further reduce the circuit power consumption, the number of off-chip components should be reduced. The system power cost is greatly reduced to a much lower level by integrating components to one silicon chip. Current technique on semiconductor has been used in hearing aid device to reduce both its size and power consumption. However, even with these methods to reduce circuit power consumption, it is still difficult to get a better noise cancellation in with limited power budget.

Many researchers have shown their interests in monolithic hearing aid design with technology of 0.6  $\mu$ m CMOS [3] and 0.8  $\mu$ m BiCMOS [1] in the past 3 years. However, these have inherent limitations. Normally, the price for implementing circuits in BiCMOS technology is higher than implementing circuits in CMOS technology. Hence, wireless hearing aid implemented in CMOS technology may be a more economic solution.

Digital circuits are designed in CMOS technology, such as DSP chip, because of the higher speed and lower power consumption. At present, the CMOS technology has already reached the 0.18 µm. In some situations, the analog circuit and RF circuit can be implemented in CMOS technology with the similar performance compared to the one with bipolar technology. In the wireless hearing aid design, it includes not only digital circuit part but also analog circuit, RF circuit part. So when the chip, which includes

digital circuit, analog circuit and RF circuit, is designed using the BiCMOS technology, it faces the drawbacks of the BiCMOS technology. The CMOS technology is preferable in hearing aid devices since CMOS technology is more suitable for mix-signal IC design compared to other silicon techniques strongly backs up this preference. That means digital circuits and analog circuits can be fabricated in one chip with CMOS technology in order to be cheap enough. The complexity in digital circuits is increased to compensate the disadvantages in the analog circuits and RF circuits when built in CMOS technology. The recent improvement in the CMOS technology promises a more miniaturized and lower-power consuming circuit, which will benefit to hearing aid design.

The RF receiver is the main part of earpiece in wireless hearing aid. There are several fundamental topologies for RF receiver design. One of the typical RF receiver topologies is shown in Fig. 1.6.

Fig. 1.6 Typical RF receiver architecture

The receiver function is transferring RF signal to base band signal. There are some fundamental blocks in the receiver. LNA is the first block in the receiver. It amplifies the weak RF signal adding as less noise as possible. Band pass filter #1 rejects the imaginary RF signal and passes the desired RF signal. Mixers are used to down convert the high frequency signal to low frequency signal. Local oscillator provides high frequency signal for mixer to down convert the desired RF signal. Band pass filter #2 only passes the desired signal. Amplifier is working at base band frequency to provide suitable amplitude for the following AD converter. After AD conversion, the base band analog signal becomes to digital signal. The further digital signal processing can be implemented. LNA design is important in the whole receiver design. It should amplify the weak receiving signal to the level suitable for processing and provide gain to overcome the noise of subsequent stages while adding as little noise as possible, handle large (unwanted) signal along with some very weak signal. For example, noise figure is a very important parameter in receiver design, which is the ratio of input SNR to the output SNR. If the LNA noise figure is too high, the noise figure of the whole receiver is not acceptable, because normally the total noise figure is mainly determined by the LNA noise figure. That means the signal is affected by the noise, if the receiver noise figure is too high.

The literature search shows that by far there is no CMOS LNA design for wireless hearing aids, especially in very low voltage and low power operation. It is not easy to trade off among power gain, noise figure, linearity and matching in such low voltage and low power consumption. Designing LPLV LNA circuit is one of the major challenging problems involved in the design of CMOS wireless hearing aids.

#### **1.2.2 Background Noise and Echo Cancellation**

With the advancements in integrated circuits technology the performance improvements of audio device, such as hearing aid devices, has been more beneficial to the end users e.g. hearing impaired. However, an input to such device is often associated with the environmental noise. For instance, even for a hearing-impaired person with a HA, due to environmental noise, a hearing-impaired person not only feels severe hearing loss but is also unable to discern desired speech from the environment noise sometime. Environmental noise, also termed as reverberations, is the main noises that make a hearing-impaired person unable not discern desired speech.

When a hearing-impaired person is in a noisy environment, even with a HA, the surrounding noise may interfere the desired voice that makes the hearing-impaired person to have the difficulty in discerning the desired speech. So the hearing aid should only amplify what the hearing-impaired person need to hear and reduce what hearing-impaired person does not want to hear. Thus, even in the noisy environment, the HA should be able to cancel all surrounding noise and selects only desired speech.

The conventional hearing aids which are merely amplifying all inputs or doing simple filtering have been proved to be insufficient. The speech enhancement which includes noise cancellation and echo reduction is needed. With the help of DSP technique, today's hearing aid devices start to develop their ability on speech enhancement.

A simple design in many current commercial hearing devices is using a single directional microphone for voice pick-up. By inhibiting background noise, SNR is increased (Siemens Hearing, Unitron Hearing, etc). Many DSP algorithms are presented for such single microphone setup and most of them are based on frequency spectrum analysis [14] or wavelet transforms [15].

Due to the fact that interference often overlaps in the frequency domain with the desired speech, the single microphone setup is not sufficient [5]. Current researches are focusing on using more than one microphone, especially on dual-microphone setups. The principle is by using more than one microphone, the system obtains more information on both the desired speech and noise [16], [17]. Thus, it is possible to extract the desired signal from the inputs. Adaptive filtering [18], [19], [20] is used as the fundamental

method in these studies. Some researchers also use an estimator to estimate the noise then cancel the noise from the original signal [1]. However, the result seems not satisfactory enough. Currently, there are few commercial products implementing a mature multi-inputs signal processing technology.

As an example, Fig. 1.7 shows a noise cancellation application situation for hearing aids users.

Fig. 1.7 Example for noise cancellation application situation in hearing aids design

Person A, a hearing aid user, is in a noisy environment as some people are standing besides him and talking. However, person A does not care about other people's talking. The hearing aid user only wants to perceive the voice from the person B.

The noise, undesired voice, and the desired signal are both in audio frequency band. The normal filter bank method is difficult to get rid of the noise. Adaptive signal processing method can be used in this situation. However, the two-element beamforming method has some limitations.

Since noise cancellation is very important for users, further investigations are required to get a clear voice. Many researchers are focusing on further investigation for improving the noise cancellation schemes [12], [21].

#### **1.3 Objective and Scope of Thesis**

The research work reported in this thesis aims mainly for two aspects concerning wireless hearing aids:

(i) Low power low voltage design and development of CMOS low noise amplifier circuit. Under this, the scope of work includes design and test of a CMOS LNA operated at 1.0 V, keeping in view the wireless hearing requirements.

(ii) Background noise cancellation method with beamforming method for wireless hearing aids. Investigating the improved noise canceling method and its application in wireless hearing aids system simulation is included within the scope of the work.

#### **1.4 Organization of Thesis**

The thesis is divided into five chapters. It begins with the hearing aids introduction in Chapter 1. Chapter 2 provides the details of design and optimization techniques of the CMOS LNA circuit with low voltage and low power consumption for wireless hearing aids. Measurement results and discussion of CMOS LPLV LNA are presented in Chapter 3. Noise cancellation method, modified two-element beamforming, for wireless hearing aids is described in Chapter 4. Conclusions, together with some suggestions for future work, are included in Chapter 5.

# **Chapter 2** Low Noise Amplifier Design and Optimization

#### 2.1 Introduction

Receiving the processed audio signal within the power budget of an earpiece in wireless hearing aids is one of the inherent design challenges [1]. Low noise amplifier is the first stage to receive the RF signal, which is embedded in the earpiece of a wireless hearing aid. Literature survey shows that there has been not much attempts to implement a CMOS receiver for the earpiece of wireless hearing aid systems, especially on LVLP LNA design. Towards CMOS implementation, in this thesis, a low power consumption low voltage monolithic single-ended CMOS low noise amplifier with cascode source inductive degeneration at the source is presented. The LNA design targets, topology and optimization are also described.

#### 2.2 **RF Models for LNA Design**

Because MOSFETs, spiral inductors and capacitors are often used in LNA circuit, the accurate RF models are very important to predict the silicon performance of gigahertz circuits. The characteristic of transistor in low frequency is different from the one in high frequency. The parasitic effects of transistor should be considered in circuit design, which are not included in the low frequency circuit design. So the transistor model for low frequency design is quite different with the model for high frequency design. Moreover, in high frequency, the inductance and Q value varies with the operating frequency, and capacitor also has parasitic effects. So Inductor and capacitor models should also be studied carefully for correct design. Otherwise, the difference between simulation results and testing results are unacceptable.

#### 2.2.1 MOSFET RF Models

MOSFET models, especially the RF MOSFET models are required to predict the silicon performance accurately, such as sub-circuit short channel MOSFET models for RFIC designs. In the sub-circuit models, MOSFET is divided into two parts, an intrinsic part and an extrinsic part. The intrinsic part represents the main active part of the device, which can be any compact model, such as Berkeley Short-Channel IGFET Model (BSIM). BSIM3 Model is a physics-based, accurate, scalable, robotics and predictive MOSFET SPICE model for circuit simulation and CMOS technology development. It is developed by the BSIM Research Group in the Department of Electrical Engineering and Computer Sciences (EECS) at the University of California, Berkeley. This model has already been accepted and verified. However, the extrinsic part consists of most of the parasitic elements, including all the terminal access series resistance, gate resistance, overlap and junction capacitance, and substrate network. One of such NMOSFET model is shown in Fig. 2.1, which is used for RF circuit design. The transistor symbol in the figure is the BSIM3 model. The resistors, inductors and capacitors in the Fig. 2.1 are all ideal components. This charge-based model takes into account short channel effects and Non-Quasi-Static (NQS) effect. It is valid in all regions of operation, from strong inversion to weak inversion, and in all of DC, small-signal AC and large-signal analysis up to 10 GHz.

Fig. 2.1 NMOSFET model for RF circuit design

As the MOSFET models include main noise sources, i.e. channel thermal noise, flick noise, terminal resistances thermal noise, substrate resistances thermal noise and induced gate noise, they work well for the noise performance prediction of short channel devices, which is critical for low noise RFIC designs.

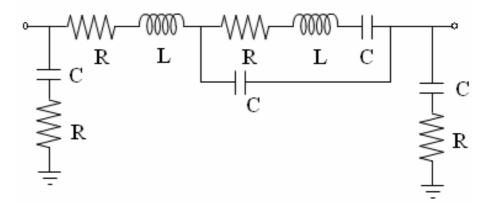

#### 2.2.2 Inductors RF Models

Spiral inductors with reasonable Q and self-resonant frequency are widely used in the RFIC designs, such as fully integrated LNA, oscillator and impedance matching network. They are proved to be most difficult passive components to be implemented on chip. Fig. 2.2 shows the layout of a circular spiral inductor, which is defined by their geometry sizes. For example, a circular square spiral inductor is defined by side length, wire width, wire space and number of turns.

Fig. 2.2 Layout of circular spiral inductors

A typical spiral inductor consists of several series or/and parallel metal segments. Each segment is modeled as two-port lumped components as shown in Fig. 2.3, which is used for RF circuits design. Therefore the spiral inductor becomes a finite-lumpedelement circuit of series and parallel connection of lumped segments. Solving the circuit equations in the model, we can compute the inductance matrix and capacitance matrix, then find the final characteristics of spiral inductors.

Fig. 2.3 Circular spiral inductor model

Although the model helps the designers to predict the silicon performance, the design of higher performance spiral inductors with smaller area remains a very challenge task due to the electrical coupling, relatively high metal resistance and substrate loss in

CMOS process. Some novel techniques compatible with standard CMOS process have been reported. They include higher conductivity metal layers or multi-shunted metal layers with increased effective thickness to reduce the metal loss [22], thick oxide, floating inductors or ground shields to reduce the substrate loss [22], tapered shape to optimized performance from energy point of view [23], miniature 3-D structure to reduce the area [24].

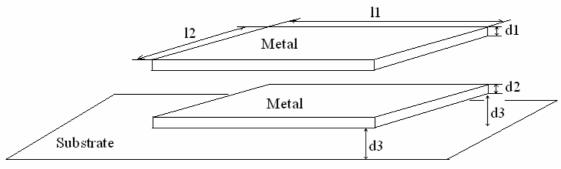

#### 2.2.3 Capacitors RF Models

Capacitors are another important passive components widely used in RF circuit design, such as impedance matching and DC block. Fig. 2.4 shows a typical MIM capacitor layout structure in RF circuit design, which uses two metal layers as their top and bottom plates. Normally, the metals used to constructed capacitor are the high layer metals. For example, sixth layer metal can be as top plate and first layer metal can be as bottom plate in 0.18 µm technology design. Thus, the capacitor parasitic effects are smaller.

Fig. 2.4 Layout of MIM capacitors

Similar with inductor models, the MIM capacitor models is made up of a finitelumped-element passive network by connection of ideal resistors, inductors and capacitors. Fig. 2.5 shows a typical MIM capacitor model used for RF circuits design. Solving the circuit equations in the model, the characteristics of MIM capacitors can be got.

Fig. 2.5 MIM capacitor model

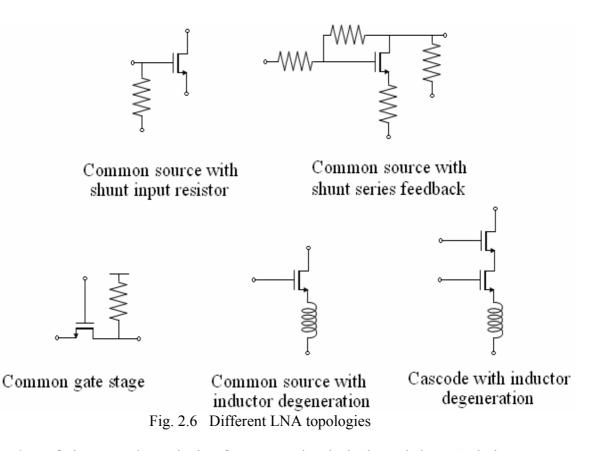

# 2.3 LNA Design Topologies

Low noise amplifier is the first stage in the receiver design. Because the operating frequency of LNA is in RF frequency band, the circuit should be as simplified as possible, especially for the RF path. Otherwise the circuit noise becomes too high. Moreover, if the circuit is complicated, the parasitic effects may distort the amplified signal.

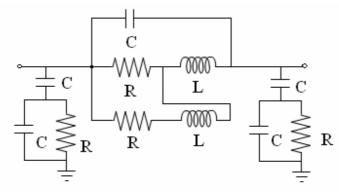

Hence, there are several fundamental low noise amplifier topologies for single ended narrow band low power low voltage design, such as resistive termination common source, common gate, shunt series feedback common source, inductive degeneration common source, cascode inductor source degeneration, which are shown in Fig. 2.6.

Out of the several topologies for narrow band single ended LNA design, an appropriate topology should be selected for low power and low voltage optimized LNA design. For common gate topology, the gain is less than 10.0 dB in very low power consumption. For shunt series feedback common source topology, it is difficult to trade off among gain, small noise figure and better input/output matching in very low power consumption. Resistor termination common source topology adds noise to the LNA because of the resistor thermal noise. Inductive degeneration common source topology satisfies the specification in very low power consumption, but the isolation is not good enough compared to the cascade inductor source degeneration topology, which can get the similar low noise amplifier performance in very low power consumption. Above all, the cascode inductor source degeneration topology is selected for this design. The

advantages and disadvantages of these different kinds of LNA topologies are shown as below Table 2.1.

| Туре                                       | Advantages                                                                                              | Disadvantages                                                      |

|--------------------------------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| Resistive<br>termination<br>common source  | Broad band amplifier                                                                                    | Adding the noise from the resistor                                 |

| Common gate                                | The input impendence is equal to $1/g_m$ . It is practical to get 50 $\Omega$ .                         | The impedance varies with the bias current.                        |

| Shunt series<br>feedback common<br>source  | Broad band amplifier                                                                                    | Adding the noise from resistor                                     |

| Inductive<br>degeneration<br>common source | The source and gate inductors<br>make the input impendence 50<br>Ω. Not adding noise from the<br>input. | The inductor is off chip at<br>low frequency and low<br>isolation. |

| Cascode inductor source degeneration       | Isolation of input and output is good, higher gain, lower noise figure.                                 | The inductor is off chip at low frequency.                         |

Table 2.1 Advantages and disadvantages of LNA topologies

## 2.4 Specification Freezing and Design Target

The LNA is the first stage of receiver in the earpiece, which is powered by a battery. So, the power consumption is the key issue to concern in this design. Reducing LNA consumption will improve the battery life. Because the earpiece and the body unit for hearing aid device are separated within about one meter, the noise figure and gain is not as important as power consumption.

According to normal hearing aid battery capacity, the total power consumption of an earpiece, where receiver is the most power hungry block, should be as low as possible but below 3 mW [1]. The recently reported 0.9 GHz CMOS receiver consumes only 2.2 mW, out of which LNA alone consumes 1.44 mW [2]. In this low noise amplifier design, the voltage is power by 1.0 V, and the aim for power consumption is less than 1.0 mW. With the small power consumption, the LNA should amply the weak receiving signal to the level suitable for processing and provide gain to overcome the noise of subsequent stages while adding as little noise as possible, handle large (unwanted) signal along with some very weak signal. LNA is the first stage in receiver design, and normally each block of receiver is matched. From noise figure equation [25], the receiver total noise figure is mainly determined by the LNA noise figure, if the gain of LNA is large enough. So the gain should large enough, at the same time the noise should be as less as possible. However, the gain of LNA should not be too high, otherwise the following stage, mixer, is saturated. Noise figure should be less than 3.0 dB and the gain should be more than 10 dB. Moreover, LNA should present specific impedance at the input, e.g. 50  $\Omega$ , especially interface with the filter or antenna. This is shown in S-parameter chart.

Keeping in view the wireless hearing aid design requirements, efforts were needed to freeze the specifications for LNA design application specific to these requirements. Based on the preliminary studies about hearing aids and the batteries, the low voltage and low power low noise amplifier design target are defined as shown in the Table 2.2.

| Table 2.2           | LNA specifications design target |

|---------------------|----------------------------------|

| noise figure        | <3.0 dB                          |

| power gain          | >10 dB                           |

| IIP3                | >-5.0 dBm                        |

| power supply        | 1.0 V                            |

| current             | <1 mA                            |

| S11                 | <-10 dB                          |

| S22                 | <-10 dB                          |

| P1dB                | >-15 dBm                         |

| <b>RF</b> frequency | 0.9 GHz                          |

| technology          | CMOS 0.18 µm                     |

## 2.5 Low Noise Amplifier Design

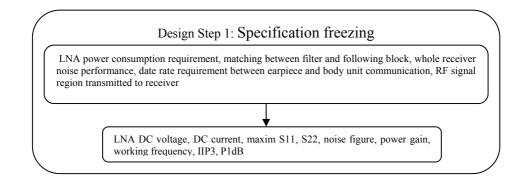

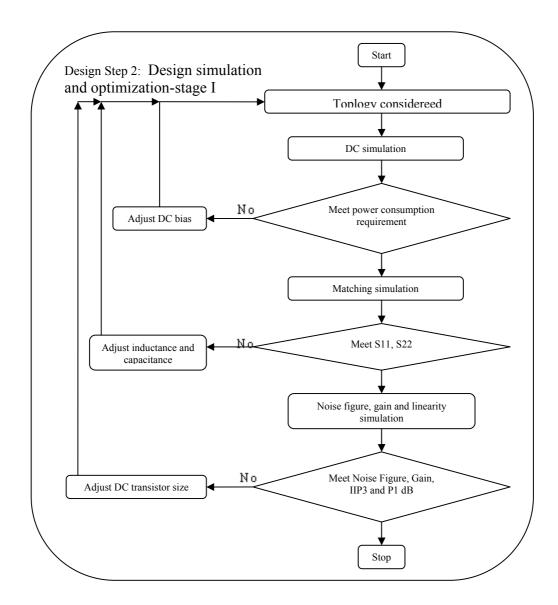

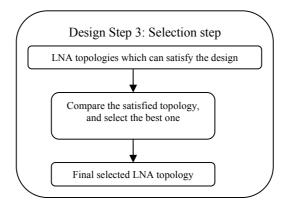

The design and optimization steps followed in the design of presented LNA are mentioned below. For each step, the design flow is given in Appendix A.

<u>Step1</u>. Specification freezing: The design specifications of the DC voltage, DC current, power gain, noise figure, S11, S22, isolation, IIP3 and P1dB are defined keeping in view the earpiece requirements for wireless hearing aids based on the literature search [1]. For example, the DC voltage is determined by the battery voltage in the earpiece. The receiver noise performance is determined by the LNA noise figure, so the LNA noise figure should be not too high, normally less than 3.0 dB.

<u>Step2</u>. Design simulation and optimization-stage I: the five kinds of low noise amplifiers, which are resistive termination common source topology, common gate topology, shunt series feedback common source topology, inductive degeneration common source topology and cascode inductor source degeneration topology, are considered and tried to satisfy the design requirements. If some specifications are not satisfied, the iterations are started till they are satisfied. That means that the transistor sizes, inductor values, capacitor values and resistor values are changed to match the design requirements. If the design requirements can not be satisfied no matter how to change the component sizes, the simulation for this specific low noise amplifier design should be paused. For those topologies that match the design requirements, the design specifications are further trade-off to get the best results for the design.

<u>Step3</u>. Topology selection step: each satisfied topology which can meet the design target in the previous design step is compared. The best LNA topology is selected for further design.

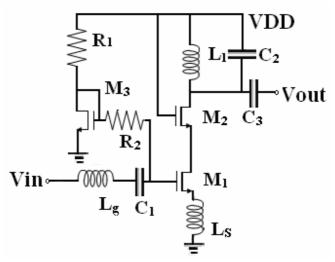

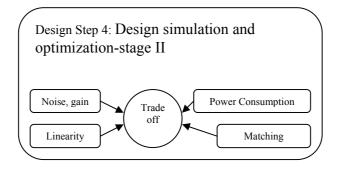

<u>Step4</u>. LNA design simulation and optimization–stage II: In this step, the design optimization is carried out on the selected topology to meet the design targets. The design step can be described as follows. From theoretical analysis and the preliminary simulation studies for various topologies, the CMOS LNA circuit shown in Fig. 2.7 is selected for the targeted specification. This topology seems the best suitable for a CMOS wireless hearing aid earpiece. It is based on the cascode inductor source degeneration topology.

Fig. 2.7 LNA circuit schematic

It is difficult to trade off between noise performance and power consumption at the same time. Classical noise matching only considers the noise performance, so the power consumption is quite high sometimes. That means one cannot obtain both input matching and minimum NF simultaneously. Low noise circuit design starts as follows [48]: firstly, select the transistor and operation point to meet the circuit noise requirements by the preliminary noise analysis; secondly, a circuit configuration or feedback can be determined to meet the gain, bandwidth and impedance requirements; thirdly, some modification should be done to meet all specifications, such as more stages, additional

feedback or increasing the bias current of the input transistor; finally, the noise can be recalculated to see if it is still within the specifications. This iterative procedure ensures satisfactory noise performance and prevents locking in on a high-noise condition at the very beginning of the design. However, this methodology does not consider more on power consumptions. Sometimes, this methodology uses more power to meet the noise performance requirements. In the earpiece blocks design for wireless HA, power consumption is more important than noise requirement, because of the limited HA battery capacity.

For cascode inductor source degeneration topology, power-constrained noise optimization method is provided in the reference [25] and [27] by Thomas H. Lee. It was found that, for the small amount of power dissipation, there exists an optimum transistor size that provides a minimum NF while satisfying input matching [25]. However, the achievable minimum NF is a little higher than of the common-source transistor. This power-constrained noise optimization method is suitable for this LNA design for wireless hearing aid.

The proposed CMOS LNA circuit can be matched to the 50  $\Omega$  output impedance of the antenna. Moreover, the input and output impedance matching of the amplifier can be done individually. By selecting the suitable inductance, the real part of the impedance can meet the matching requirements. The input impedance of the circuit at the resonance frequency  $\omega_0$  is  $R_{in} = g_m \times L_s / C_{gs}$ , where  $g_m$  is the transconductance of the transistor M<sub>1</sub>,  $C_{gs}$  is the gate source capacitance.  $L_s$  and  $L_g$  are selected to satisfy the resonant conditions for the input circuit. The value of  $L_s$  is optimized as 0.45 nH in this design according to this input matching requirement. A cascode transistor is used to isolate the local oscillator reverse leaking to the antenna from the LNA.

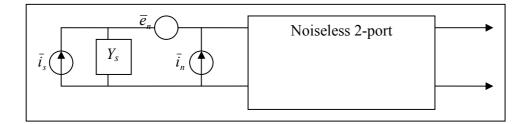

A useful measure of noise performance of a system is the noise factor, which is usually denoted *F*. Noise figure is the logarithm of noise factor [25]. In Fig. 2.8, a two port driven by a source that has an admittance  $Y_s$  and an equivalent shunt noise current  $\bar{i}_s$ . Symbol  $\bar{e}_n$  and  $\bar{i}_n$  are the total noises appearing as inputs to the noiseless network.

Fig. 2.8 Noisy two ports network driven by noisy source

The noise factor can be expressed as

$$F = \frac{\overline{i_{s}^{2}} + |\overline{i_{n} + Y_{s}e_{n}}|^{2}}{i_{s}^{2}}$$

(2.1)

In order to accommodate the possibility of correlations between  $e_n$  and  $i_n$ , express  $i_n$ as the sum of two components.  $i_c$  is correlated with  $e_n$ , and  $i_u$  is not correlated with  $e_n$ . The relation between  $i_c$  and  $e_n$  is  $i_c = Y_c e_n$ . The noise factor can be expressed as

$$F = 1 + \frac{\overline{i_u^2} + |Y_c + Y_s|^2 \overline{e_n^2}}{i_s^2}$$

(2.2)

In equation 2.2, the independent noise can be treated as an equivalent resistance or

conductance. Assuming

$$R_n = \frac{\overline{e_n^2}}{4KT\Delta f}$$

,  $G_u = \frac{\overline{i_u^2}}{4KT\Delta f}$  and  $G_s = \frac{i_s^2}{4KT\Delta f}$ , where K is

Boltzmann's constant, T is the absolute temperature in Kelvin, and  $\Delta f$  is the noise

bandwidth in hertz over which the measurement is made. Noise factor can be expressed as

$$F = 1 + \frac{G_u + [(G_c + G_s)^2 + (B_c + B_s)^2]R_n}{G_s}$$

(2.3)

In equation 2.3, the admittance  $Y_s$  can be expressed as  $Y_s=G_s+jB_s$ , and the admittance  $Y_c$  can be expressed as  $Y_c=G_c+jB_c$ .

The noise figure can be expressed as

$$NF = NF_{\min} + \frac{R_n}{G_s} (G_s - G_{opt})^2$$

(2.4)

where

$$G_{opt} = \sqrt{\frac{G_u}{R_n} + G_c^2}$$

,  $NF_{min} = 1 + 2R_n(G_{opt} + G_c)$

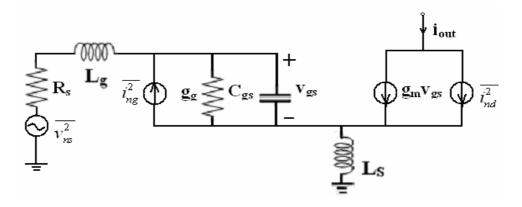

In this LNA topology, the small equivalent circuit for CMOS LNA is shown in Fig.

2.9.

$$R_n = \frac{\gamma g_{d0}}{g_m^2}$$

,  $G_u = \frac{\delta \omega^2 C_{gs}^2 (1 - |c|^2)}{5g_{d0}}$  and  $G_c \approx 0$ , where c is the correlation coefficient

defined as  $c = \frac{\overline{i_{ng} \times i_{nd}^*}}{\sqrt{i_{ng}^2} \times \sqrt{i_{nd}^2}}$ .  $i_{nd}$  is the drain current noise, and  $i_{ng}$  is the gate current noise;

$\gamma$  is the coefficient of channel thermal noise;  $g_{d0}$  is the drain-source conductance at zero drain source bias voltage;  $g_m$  is the transconductance of transistor;  $\delta$  is the gate noise coefficient;  $C_{gs}$  is the gate source capacitance;  $\omega$  can be expressed as  $\omega = 2\pi f$ , f is the frequency.

Fig.2.9 Small equivalent circuit for CMOS LNA

In this topology, combining low-noise operation with low power consumption requires the use of a low  $V_{gs}$ - $V_T$  value, allowing a high  $g_m$  at low current levels, where  $V_{gs}$  is the voltage between gate and source of the transistor and  $V_T$  is the transistor threshold voltage. Yet, as low  $V_{gs}$ - $V_T$  values mean wide transistors. Assuming  $Q_{opt} = \frac{G_{opt}}{\omega C_{gs}} = \alpha \sqrt{\frac{\delta}{5\gamma} (1 - |c|^2}$  and  $Q_s = \frac{1}{\omega C_{gs} R_s}$ , where  $\alpha = \frac{g_m}{g_{d0}}$ , and Rs is the

source resistance, the width of the optimum device width  $M_1$  is determined by the equation from [25]:

$$W_{opt} = \frac{1}{3 \sigma L C_{ox} R_s}$$

(2.5)

where *L* is the length of transistor,  $C_{ox}$  is the gate unit capacitance of transistor,. The width of the optimum device width M<sub>1</sub> is 300 µm in this design. This value expresses noise optimization in a way that takes power consumption explicitly into account. Moreover, the larger gate to source capacitor helps reducing current consumption [26]. In addition, the width of transistor M<sub>3</sub> and the value R<sub>1</sub> are optimized to control the gate voltage of transistor M<sub>1</sub>.

The LNA noise figure is primarily due to the transistor  $M_1$ . The noise figure relation is expressed as equation 2.4 [27].

With the width of  $W_{opt}$ , the noise figure obtained within the power constrained is

$$F_{\min} \approx 1 + 2.4 \frac{\gamma}{\alpha} \left[ \frac{\omega}{\omega_T} \right]$$

(2.6)

where  $\varpi_T = \frac{g_m}{C_{gs}}$ .

The thermal noise from the resistor  $R_2$  should also be considered, because it affects the input signal from the transistor  $M_1$  gate. The  $R_2$  value is selected large enough, such as 50 k $\Omega$ , to give as less noise as possible to the whole circuit noise figure. The transistor  $M_2$  contributes more on IIP3 of LNA than transistor M1 does. Increasing the DC bias of  $M_2$  improves IIP3. Since, the power consumption is the most critical for this design. The DC bias of  $M_2$  can be optimized in terms of its gate width, while keeping the DC bias voltage of  $M_1$  as low as possible to reduce the power consumption of the circuit. The width of transistor  $M_2$  is optimized to be 300 µm in this design.

From the analysis and iterative simulations, the components values of LNA are optimized and summarized in Table 2.3.

| Table 2.3    Component values of LNA |                   |                                             |  |  |

|--------------------------------------|-------------------|---------------------------------------------|--|--|

| Component                            | Values            | Functionality                               |  |  |

| M <sub>1</sub> , M <sub>2</sub>      | 60×(5 μm/0.18 μm) | Amplify the RF signal                       |  |  |

| $M_3$                                | 8×(5 μm/0.18 μm)  | DC bias current mirror                      |  |  |

| Lg                                   | 35 nH (off chip)  | Input matching                              |  |  |

| Ls                                   | 0.45 nH           | Input matching                              |  |  |

| $L_1$                                | 14.7 nH           | Output matching                             |  |  |

| $C_1$                                | 8 pF              | Input matching                              |  |  |

| $C_2$                                | 0.5 pF            | Output matching                             |  |  |

| $C_3$                                | 1.0 pF            | Output matching                             |  |  |

| $R_1$                                | 4.8 kΩ            | DC bias                                     |  |  |

| R <sub>2</sub>                       | 50 kΩ             | Reduce the input noise from DC bias circuit |  |  |

### 2.6 LNA Simulation Results

The simulation is done in the EDA software ADS [28]. The RF transistor models, inductor models, capacitor models and resistor models are provided by CSM in CMOS 0.18 µm technology, which are mentioned in the above section. The simulation also uses the package model and pad model available in IME in-house central library. The pad model and package model are both passive networks composed of ideal resistors, capacitors and inductors. All these resistors, capacitors and inductors values are extracted from the actual wafer and PCB testing results. When the simulation includes all these models, the simulation results are more similar with the testing results. However, some parasitic, such as PCB parasitic effect, can not be fully included in the simulation, because it is more difficult to build a model for these kinds of parasitic effects. The only way to deal with these parasitic is the careful layout on PCB, such as wire width, wire length, component location, etc. Thus, these parasitic can be reduced further.

The simulation includes DC simulation, S-parameter simulation and harmonic balance simulation in ADS. From DC simulation the power consumption is got. The transistors operation points are optimized from DC simulation. It is important to give the larger gain for LNA design with the optimum operation point. S-parameter simulation considers the microwave effects, such as wave reflection and gives parameters of S11, S22, S21 and S12. From these parameters, S-parameter simulation provides input/output matching, noise figure and power gain. Harmonic balance simulation provides linearity analysis, including P1 dB analysis and IIP3 analysis. HB is a powerful frequency domain analysis technique including simulations of inter-modulation frequencies, harmonics and frequency conversion between harmonics. It is well-suited for the predication of steadystate behavior in nonlinear circuits and systems, especially in the RF regions.

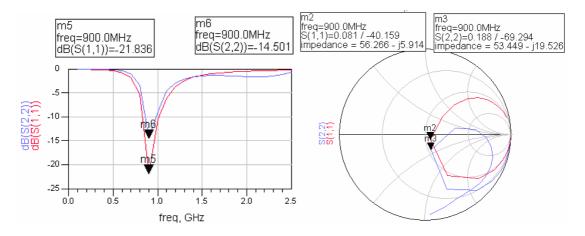

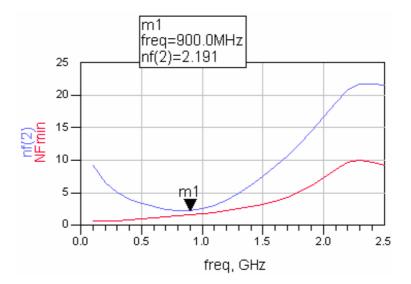

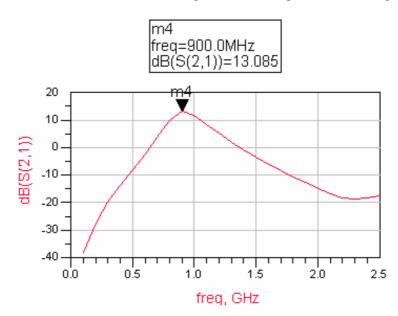

The simulation predicts a forward gain (S21) of 13.0 dB with a noise figure of 2.19 dB while drawing 0.95 mA from a 1.0 V power supply. The simulated curves of noise figure, input/output matching, and gain for S-parameters are shown in Fig. 2.10, Fig.2.11 and Fig. 2.12.

Fig. 2.10 S-parameter input and output matching simulation results

In the left figure of Fig. 2.10, S11 and S22 have the minim values at frequency 0.9 GHz. The minim values are less than -10 dB. That means the input and output power matching is good enough. The value of S11 and S22 is less than 0 dB from 0 Hz to 2.5 GHz. That means the input and output are quite sable from 0 dB to 2.5 GHz. And in the right figure of Fig 2.10, the impedances of S11 and S22 at 0.9 GHz frequency are close to 50  $\Omega$ , which is for the impedance matching.

Fig. 2.11 S-parameter noise figure simulation results

In Fig. 2.11 the noise figure is 2.19 dB at 0.9 GHz frequency. The noise figure is high in low frequency and high frequency. In low frequency, the flick noise dominates the noise performance, which characteristic is proportional to 1/f. However in high frequency, with the distortion of the circuit gain, the noise performance degrades.

Fig. 2.12 S-parameter power gain simulation results

In Fig. 2.12, the power gain of this low power consumption low voltage LNA is 13.08 dB at 0.9 GHz frequency, which is about the maxim value in the simulation frequency band.

The various simulation iterations are performed on the proposed LNA circuit to meet design requirements. It is simulated for the whole process variation from slow corner to the fast corner. The threshold voltages for the slow, typical and fast process corners are 0.49 V, 0.41 V and 0.32 V respectively. The simulation results achieved at the typical process are summarized in the Table 2.4.

| Table 2.4 Proposed LNA simulation performance summary |                                  |              |  |  |

|-------------------------------------------------------|----------------------------------|--------------|--|--|

|                                                       | Design Target Simulation Results |              |  |  |

| noise figure                                          | <3.0dB                           | 2.19 dB      |  |  |

| <b>RF</b> frequency                                   | 0.9 GHz                          | 0.9 GHz      |  |  |

| power gain                                            | >10dB                            | 13. 08dB     |  |  |

| IIP3                                                  | >-5dBm                           | 7.5dBm       |  |  |

| power supply                                          | 1.0V                             | 1.0V         |  |  |

| current                                               | <1mA                             | 0.95mA       |  |  |

| S11                                                   | <-10dB                           | -21.8dB      |  |  |

| S22                                                   | <-10dB                           | -14.5dB      |  |  |

| P1dB                                                  | >-15dBm                          | -14.0dBm     |  |  |

| technology                                            | CMOS 0.18 µm                     | CMOS 0.18 µm |  |  |

ad TNTA simulation

# **2.7 Conclusions**

LPLV LNA for wireless hearing aids was designed and described in this chapter according to the design target. In order to select the most suitable topology, five different LNA topologies are simulated and compared. The cascode inductor source degeneration topology was selected for the required design. The circuit was implemented using RF transistor, inductor and capacitor models. The simulation results show the satisfaction with the design target. The simulation predicts a forward gain (S21) of 13.08 dB with a noise figure of 2.19 dB while drawing 0.95 mW from a 1.0 V power supply. The simulated IIP3 and P1dB are 7.5 dBm and -14.0 dBm.

# **Chapter 3 Low Noise Amplifier Measurement and Discussions**

### **3.1 Introduction**

Normally, in RF circuit design, there are parasitic effects which are difficult to include in simulation. These parasitic effects reduce the whole circuit performance. Hence, the RF circuit measurement is very important. The RF circuit simulation results are verified by the measurement results. After the RF circuit simulation, the circuit layout development is done. Then the circuit design is converted into the GDS format file and sent to foundry for fabrication. When the wafer is back from foundry, it is covered with package for testing. To test this LNA, the chip is soldered on the PCB with other off-chip components, such as resistors, capacitors and inductors. The LNA test includes DC test, S-parameter test, noise figure test and linearity test. Form these measurements, the LNA performances, such as power consumption, noise figure, power gain, linearity, are gotten.

## 3.2 LNA Chip Layout Development

Layout of RF circuits is a critical issue to determine their final performance in silicon. Several key points in the RF layout design are discussed in this section.

All the circular spiral conductors have the optimized geometry of width, radius and spacing. They are made of two shunted top metal layers (Metal 5 and Metal 6 in CMOS 0.18  $\mu$ m technology) to reduce the metal loss and substrate loss. Moreover, the layout method of placing gate contacts on each end of the device can reduce the poly-gate resistance further, by half. In the transistors' layout, the multi-fingered folded structure is also used to improve the Q of parasitic capacitors  $C_{gs}$ ,  $C_{gd}$ ,  $C_{gb}$ ,  $C_{db}$ . The number of

fingers should be chosen properly to minimize the total parasitic capacitance. Proper floor plan and routing technique are required for reducing the parasitic inductance and capacitance.

General layout design rules and considerations are still valid in RF layout designs. Sufficient number of contacts for substrate/n-well diffusion and well-placed guard rings must be placed for the high IC reliability. Around the portions flowing radio frequency signals, some additional empirical RF design rules are applied to reduce the magnetic field effects upon these components. First, because of the interference of inductor is very strong, the distance between inductor and other components should big enough to reduce the interference, such as about 50µm minimum spacing between spiral inductors and other component. Second, this LNA is a single ended design, so the AC ground, including DC ground and voltage supply, is very important. It affects the whole performance badly if we do not consider it fully. More care should be given to the AC ground layout. Third, guard rings prevent the transistors from noise. Fourth, the RF path should be as short as possible, at the same time, use direct path as possible. Fifth, the metal for RF path should use high layer metal, such as sixth layer metal, to reduce the capacitance effect between the metal layer and the substrate.

According to these above rules, the LNA layout is developed in the Cadence design environment using CSM CMOS 0.18 um process design rules. The total silicon area required is 535  $\mu$ m × 653  $\mu$ m. The Design Rule Check (DRC) is made over the developed layout and the layout was ensured meeting all design rules provided by the foundry, before release for fabrication. The test chip has 8 total pads including 2 power supply pads, 2 RF signal pads, 1 bias voltage pad and 3 ground pads.

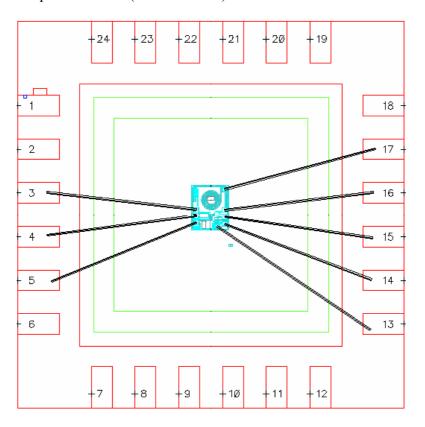

The LNA chip bonding diagram is shown in Fig. 3.1. The chip package is QPF24 model provided by IME, which has 24 pins. However, only 8 pins were used in this design, other left pins were NC (not connected).

Fig. 3.1 LNA chip bounding diagram

The bonding wire is made up of low resistance metal, which gives low parasitic effects on the whole circuit performance.

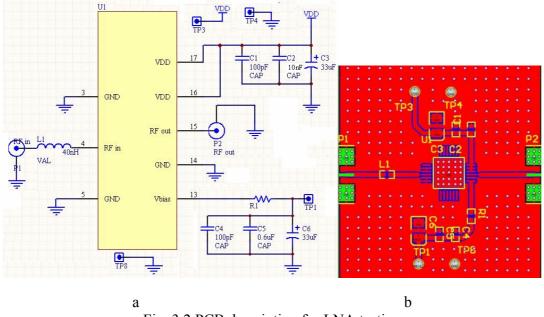

# **3.3 LNA PCB Layouts**

The PCB layout is developed using EDA tool Protel [29]. The PCB description for LNA testing is shown in Fig. 3.2. The PCB material is FR4, which is suitable for this