### SELECTED TOPICS ON ADVANCED ELECTRON DEVICES AND THEIR CIRCUIT APPLICATIONS

YANG TIAN

(B. Sc., Fudan University)

A THESIS SUBMETTED FOR THE DEGREE OF MASTER OF ENGINEERING DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING NATIONAL UNIVERSITY OF SINGAPORE July, 2005

### Acknowledgements

This thesis is a collection of my research work at National University of Singapore (NUS) and Institute of Microelectronics (IME). I would like to take this opportunity to express my great thanks to my principal supervisor, Prof. Li Ming-Fu, not only for his dedicated guidance, valuable advice and illuminating ideas, but also for his scientific research spirit and attitude, which has deeply inspired. I am also deeply indebted to my co-supervisors, Dr. Subhash C. Rustagi, Yu M. B. and Zhu C. X. for their constant direction and care.

I would also like to thank my peers and seniors in Silicon Nano Device Lab and IME, Mr. Shen C., Yu H. Y., Tian T. and Hu H., for their insightful advice and discussion. Without their investment of time and energy, I would never have been able to complete this work.

Lastly, and most importantly, I would like to thank my parents for their selfless love, care, support and belief. Without them, I would never have gotten to where I am today.

### **Table of content**

| Acknowledgements<br>Гable of content | i  |

|--------------------------------------|----|

| Table of content                     | ii |

| Summary                              | V  |

### Part I: A systematic study on Negative Bias Temperature Instability (NBTI) in p-MOSFETs with ultra-thin SiON gate dielectrics

#### Chapter One Introduction

| 1.1 MOSFET scaling and issues with gate dielectric scaling down                 | 2  |

|---------------------------------------------------------------------------------|----|

| 1.2 Oxide reliability and motivation                                            | 4  |

| 1.3 Review of previous studies on NBTI in p-MOSFETs                             | 6  |

| 1.4 Major contribution of this work                                             | 8  |

| Reference:                                                                      | 9  |

| Chapter Two Measurement methods for NBTI Characterizati                         | on |

| 2.1 Introduction of the conventional DC technique for $V_{th}$ characterization | 12 |

| 2.2 An advanced fast technique for V <sub>th</sub> characterization             | 13 |

| 2.3 Improved Charge Pumping and DCIV techniques for $N_{it}$ characterization   | on |

| thin gate dielectric                                                            | 18 |

| Reference:                                                                      | 22 |

#### Chapter Three A detailed analysis on conventional DC measurements

| 3.1 | Debate on the origin of NBTI recovery effect in p-MOSFET with SiON gate |      |

|-----|-------------------------------------------------------------------------|------|

|     | dielectric by DC method                                                 | . 24 |

| 3.2 | Experimental results and discussion                                     | . 25 |

| 3.3 | Impact of N <sub>it</sub> measurement on NBTI recovery                  | . 30 |

| Ref | erence:                                                                 | .35  |

|     |                                                                         |      |

### Chapter Four Fast NBTI components in p-MOSFET with SiON gate

#### dielectric and its impact on circuit applications

| 4.1 Introduction   |                                              | . 37 |

|--------------------|----------------------------------------------|------|

| 4.2 Experimental   | results and discussion                       | . 38 |

| 4.3 Modeling of fa | ast DNBTI component in SiON gate dielectric  | . 48 |

| 4.4 Impact of the  | fast NBTI components on circuit applications | . 49 |

| Reference:         |                                              | . 51 |

#### Part II: Advanced passive devices and their application in circuits

#### Chapter Five Proton implanted high-Q inductors

| 5.1 Introduction                                                | 54 |

|-----------------------------------------------------------------|----|

| 5.2 Experiments                                                 | 55 |

| 5.3 Results and discussion on the impact of proton implantation | 57 |

| Reference:                                                      | 60 |

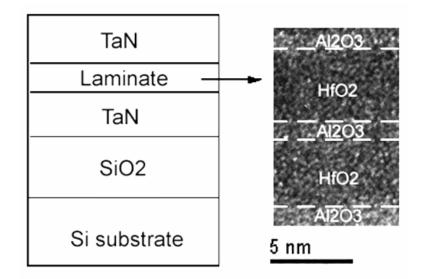

#### Chapter Six High-к dielectric MIM capacitors

| 6.1 | Introduction                                | 61 |  |

|-----|---------------------------------------------|----|--|

| 6.2 | Device fabrication and experimental results | 62 |  |

| 6.3 RF modeling on high-κ MIM capacitors                                     | 66        |

|------------------------------------------------------------------------------|-----------|

| Reference:                                                                   | 68        |

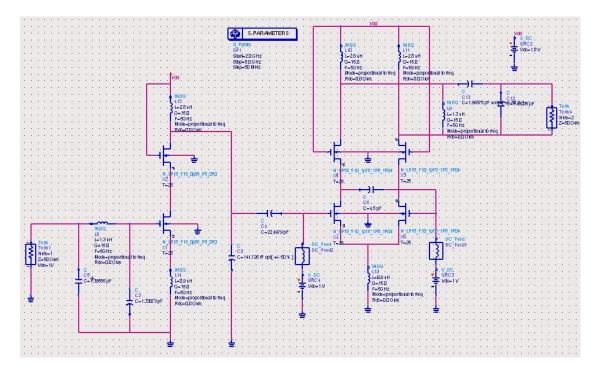

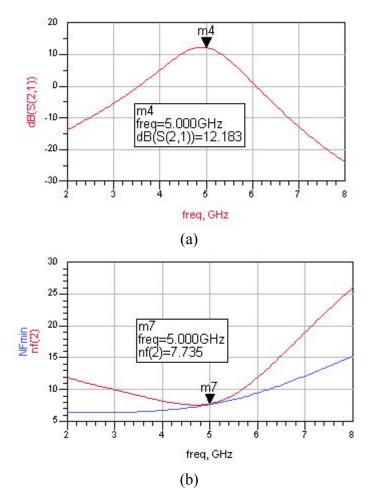

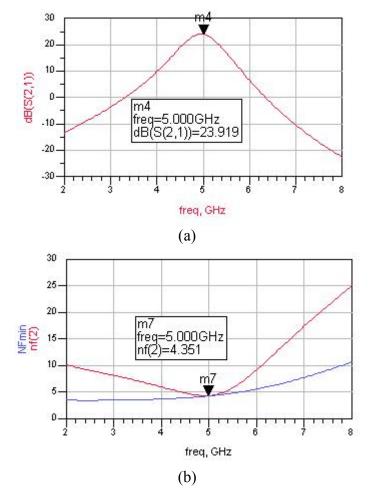

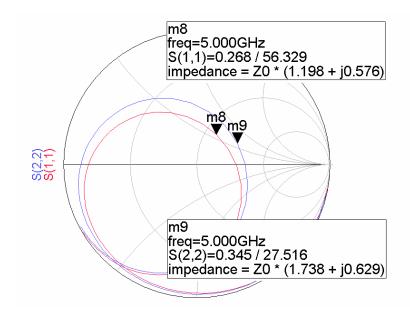

| Chapter Seven RF and analog circuits using advanced passiv                   | e devices |

| 7.1 5GHz low noise amplifier (LNA) using high-Q inductors                    | 69        |

| 7.1.1 One stage LNA design                                                   | 69        |

| 7.1.2 Two stage LNA design                                                   |           |

| 7.1.3 Conclusions                                                            | 75        |

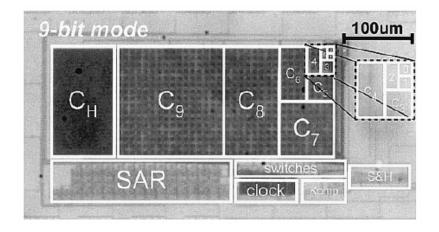

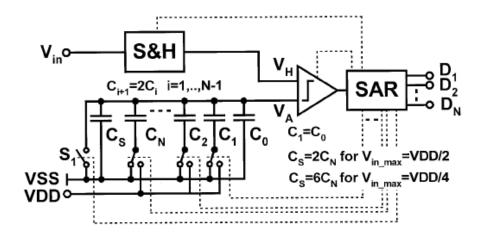

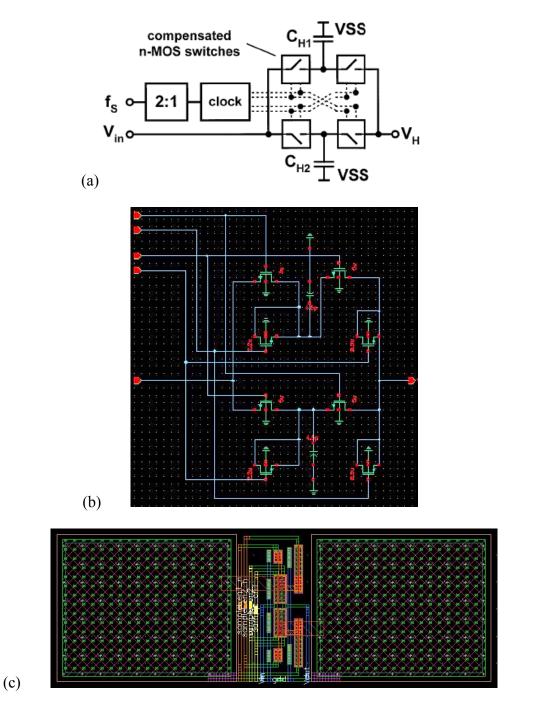

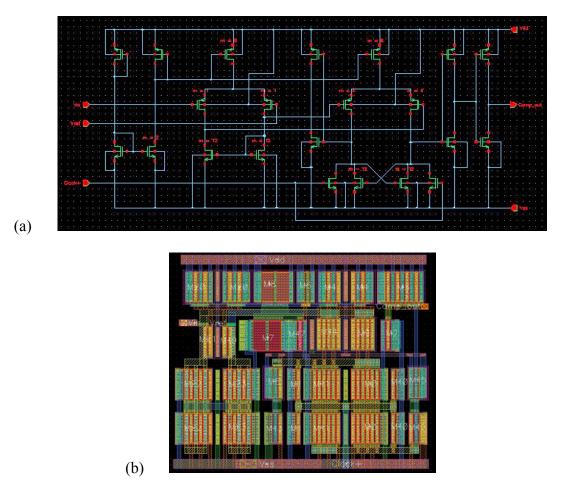

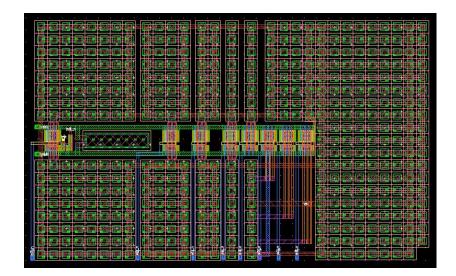

| 7.2 8-bit successive approximation ADC using high- $\kappa$ MIM capacitor ar | ray 75    |

| Reference:                                                                   | 79        |

| Chapter Eight Conclusions                                                    | 80        |

| List of publications                                                         |           |

#### Summary

In this thesis, selected topics on advanced modern electron devices have been studied, including both active devices and passive devices. Their applications in different kinds of circuit applications are also discussed.

In part I, a systematic study of Negative Bias Temperature Instability (NBTI) in p-MOSFETs with ultra-thin SiON gate dielectric is reported. The study shows that the conventional measurement methods which have been used over the past years seriously underestimate  $N_{it}$  due to passivation of  $N_{it}$  during measurement. By using the fast pulsed method, a fast Dynamic NBTI (DNBTI) component is distinguished from the conventional slow one for the first time. Evidence has been shown that this component is due to trapping and de-trapping of hole traps  $N_{ot}$  in SiON. The accumulative degradation increases with increasing stress frequency. A model describing the phenomenon has been developed and the model simulations are in excellent agreement with all the experiments. The impact of fast DNBTI on device lifetime and circuit applications has been re-evaluated in the light of this new finding.

In part II, researches have been done on proton implanted high quality inductor as well as high-κ MIM capacitor, showing promising characteristics for future ULSI application. RF and analog circuits using advanced passive devices are also designed and the simulation results show improved circuit performance.

## Part I

# A systematic study on Negative Bias Temperature Instability (NBTI) in p-MOSFETs

### with ultra-thin SiON gate dielectrics

#### **Chapter One**

#### Introduction

#### 1.1 MOSFET scaling and issues with gate dielectric scaling down

The modern Metal-Oxide-Semiconductor Field Effect Transistor (MOSFET) was successfully demonstrated in the 1960's, when the silicon technology was mature enough to realize MOS gate stacks based on the thermal SiO<sub>2</sub>-Si framework. Large-scaled commercialization of MOS technology took place from then on. In 1963, the complementary MOSFET (CMOS) was proposed [1]. It soon emerged ast the work-horse in the semiconductor industry due to its low power consumption and high packing density. It still prevails as the technology of choice for today's ultra-large-scale-integration (ULSI) applications.

For the goals of reducing gate delay, increasing operating frequency, increasing transistor density and reducing power dissipation, the modern MOSFETs has been continuously downsized based on a set of guidelines established over the past four decades. The basic scaling parameters include channel length *L*, power supply voltage  $V_{dd}$ , threshold voltage  $V_{th}$ , and gate oxide thickness  $t_{ox}$ . According to Moore's law [2], for every three years, the device dimension is reduced by approximately  $1/\sqrt{2}$ , the chip size is increased by about 1.5 times, and the number of transistors in a chip is increased by a factor of four. By reducing the device dimensions, in particular the

transistor gate length the amount of current supplied by a transistor is increased. Higher current allows the circuits to switch more quickly, leading to faster computations. In addition, the reduction in transistor size also allows more transistors to be integrated on a single chip. Consequently the complexity and functionality of ICs can be increased while keeping the cost of the circuit fabrication low. This in turn constantly expands the realm of possible applications of semiconductor products.

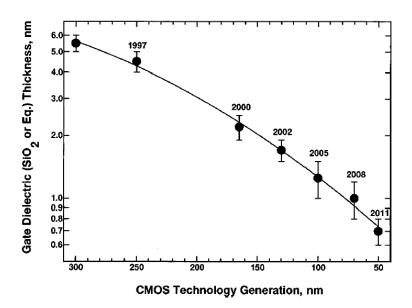

On the other hand, with the reduction in gate length, gate is losing its control over the channel because of a channel control competition from the drain side. To keep the pace with drive current demands and the better gate control over channel, the gate dielectric thickness must also be scaled down in accordance with the gate length. As can be seen from Fig. 1.1, gate dielectric thickness continues to shrink aggressively to offer higher drive current and gate capacitance required by scaled MOSFETs.

Fig.1-1 Decrease in gate EOT with device scaling. (Extracted from ITRS [3]).

Though promising for high performance MOSFETs, ultra-thin gate dielectric layer leads to critical issues in the following areas, namely: (i) Direct tunneling current (DT); (ii) Boron penetration and gate poly-silicon depletion; (iii) Quantum mechanical effects; (iv) Integration issue and manufacturability; and, (v) Oxide reliability. These issues pose serious challenges for device engineering and could become significant hurdles for further MOSFET scaling.

#### **1.2** Oxide reliability and motivation

Oxide reliability is one of the most important issues introduced by gate dielectric scaling down. It has received increasing attention since it causes degradation and failures in advanced ULSI devices, and therefore, is a serious challenge to the downscaling trend of oxide thickness and MOSFET size.

A critical reliability issue that is associated with dielectric scaling is negative bias temperature instability (NBTI). In recent years, it has been widely recognized that NBTI is the most serious reliability issue in the ultra-thin SiO<sub>2</sub> or SiON gate dielectric p-channel MOSFETs (p-MOSFETs) [4] [5]. It could increase the amplitude of the threshold voltage ( $\Delta V_{th}$ ) by as much as 50 – 100mV in a p-MOSFET over a period ranging from months to years, depending on the operating condition. As a result, it would be more difficult to turn on the p-MOSFET, causing a significant reduction in circuit speed and even logical mal-function. With these concerns, the reliability of ultra-thin gate dielectrics has become one of the limiting factors for future ULSI development.

As a result of the NBTI issue in the p-MOSFET, an evolutionary change in the lifetime limiting factor for CMOS technology has occurred in the past few years. Traditionally, for 0.35µm technology and above, hot-carrier injection (HCI) induced degradation of n-channel MOSFETs limits the lifetime of CMOS circuitry, and

therefore considerable work has been carried out to understand the mechanism responsible for defect generation in n-MOSFETs under HCI stress. However, with aggressive scaling of the thickness of gate oxide film into the direct-tunneling regime, NBTI degradation in p-MOSFETs, instead of the HCI degradation in n-MOSFETs, limits the CMOS lifetime [5]. Therefore, investigation into NBTI issue becomes paramount especially when the gate dielectric thickness is reduced to barely a few atomic layers.

Another challenge is that the NBTI reliability physics of ultra-thin gate dielectric becomes more complicated when continued scaling requires material-based modification like incorporation of nitrogen into the thin  $SiO_2$  film to form silicon oxynitride (SiON) or even totally change the  $SiO_2$  based dielectric material to high- $\kappa$  material, for instance, HfO<sub>2</sub>. Many existing NBTI models for thick pure SiO<sub>2</sub> might then be challenged [6]. Hence, it is essential that a systematic study on this topic could be carried out as soon as possible.

Significantly, G. Chen et al. [7] reported a recovery effect of NBTI stress which prolongs the device lifetime in real application. A debate on what is the origin of this recovery effect was then raised. G. Chen et al. [7] and also some other groups claimed that the  $V_{th}$  recovery in the passivation phase is due to the passivation of SiO<sub>2</sub>/Si interface traps [8]-[12]. On the contrary, V. Huard et al. [13] argued that the transient recovery of  $V_{th}$  in the passivation phase is due to de-trapping of hole traps in the dielectric. To clarify this conflict is demanded not only for physics study, but also has important implications for real IC application and further studies on high- $\kappa$  dielectric MOSFETs.

All the above factors form the major motivation of this research work, which addresses the issue of NBTI in the ultra-thin gate dielectric MOSFETs.

#### **1.3 Review of previous studies on NBTI in p-MOSFETs**

Researches on NBTI can be traced back to the very early days of MOS device development. In 1967, Deal et al. [14] found that both the interface trap density  $N_{it}$  and oxide charge density  $N_{ox}$  increased after negative bias stress. The rates of increase of both  $N_{it}$  and  $N_{ox}$  were very similar. In 1973, Goetzberger et al. reported the same observation using metal gate devices with 100 nm thick oxides, stressed at -106V/cm at 300°C [15]. Later on, many other research groups confirmed the observation that there is an equal growth of oxide charge (reflected by  $V_{th}$  shift) and surface trap density, which are independent of the NBTI stress field and temperature. Another common observation is that the generation of interface trap and positive oxide charge follow a power-law time dependence with the exponent having values in the range of  $0.20 \sim$ 0.25 [16]-[20]. To explain the interface trap generation, many researchers adopted the Si-H dissociation mechanism, which is a two-reaction model involving atomic hydrogen dimerization and hydrogen-interface reactions [21]. At that time, it is commonly acknowledged that the threshold voltage shift is only because of interface trap generation. Since the dielectric layer was so thick that no direct tunneling or FN tunneling could occur, no one took the bulk trap into consideration.

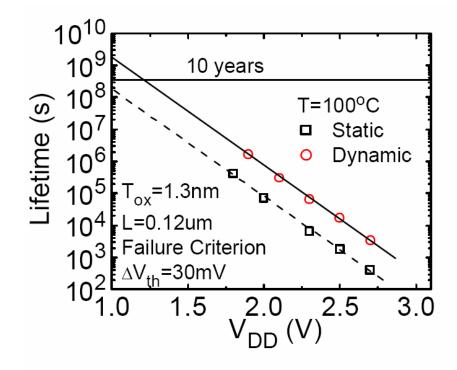

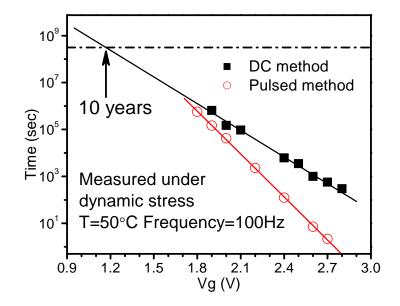

Recently, Dynamic NBTI stress test is widely used to predict the device lifetime and to study the physical mechanisms of BTI degradation since it is more similar to the real device operation conditions. In the year of 2002, G. Chen et al. applied an AC stress on the gate to simulate an inverter's operation conditions: switch on and off [22]. Consequently, they found that the Dynamic NBTI effect significantly prolongs the lifetime of p-MOSFETs operating in a digital circuit. As shown in Fig.1-2 [22], the projected 10-year lifetime operating voltage  $V_{10Y}$  is 1.2V for Dynamic NBTI stress, and is 0.9V for Static NBTI stress, which overestimates the degradation in real digital circuit operation.

Fig.1-2 SNBTI and DNBTI lifetime projections for p-MOSFETs. The SNBTI stress overestimates the degradation in real digital operation.

From then on, many groups started trying to do more researches on this DNBTI effect [23]-[26], not only on pure SiO<sub>2</sub> dielectrics, but also other materials such as  $HfO_2$  based high- $\kappa$  dielectric, Si<sub>3</sub>N<sub>4</sub> etc..

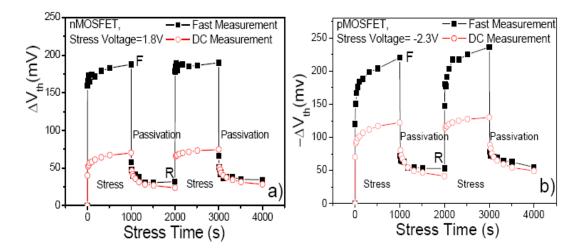

With the advent of high- $\kappa$  dielectric, more advanced measurement technologies [6] [27] are now being used in BTI research, especially for measuring the fast  $V_{th}$  shift. The  $V_{th}$  shift can no longer be ascribed to only the interface traps, but the charge trapping and de-trapping in the bulk dielectric layer [6], [27] also contributes to it. Fig.1-3 gives a comparison on  $\Delta V_{th}$  measured by fast and conventional DC methods on both n- and p-MOSFETs respectively, showing significant difference.

Fig.1-3 Comparison of measured  $\Delta V_{th}$  under DNBTI stress by fast and conventional DC methods on both n- and p-MOSFETs.

A new reaction-diffusion model was proposed by M. A. Alam [8] to study the physics of frequency-dependent shift in transistor parameters due to NBTI. C. Shen et al. also made a frequency dependent model and explained the BTI frequency dependence of the slow traps by the –U property of these traps [6].

However, there has been no research work using the fast measurement method to study on SiON dielectrics, which is widely be used in present day CMOS technology. Does SiON also have fast traps? If so, does it affect the circuit performance and device lifetime? These questions are to be discussed based on the experimental result.

#### **1.4 Major contribution of this work**

The followings are the major contributions of this work.

1. For the first time, a systematic study on the impact of  $N_{it}$  measurement on  $N_{it}$ and  $V_{th}$  recovery has been done.

- The recent debate in the slow DNBTI component measured by conventional DC method has been clarified.

- 3. The fast DNBTI component measured by fast measurement method has been demonstrated and analyzed for the first time. Device lifetime has been reevaluated based on the new results and its impact on circuit application has also been studied.

#### **Reference:**

- F. Wanlass and C. T. Sah, "Nanowatt logic using field-effect metal-oxidesemiconductor triodes," *IEEE Technical digest of Int. Solid-state circuit Conf.*, pp.32-33, 1963.

- [2] G. E. Moore, "Progress in digital integrated circuit," *IEEE IEDM Tech. Dig.*, pp.11-14, 1975.

- [3] International Technology Roadmap for Semiconductor 1999 and 2005.

- [4] J. H. Stathis and D. J. DiMaria, "Reliability projection for ultra-thin oxides at low voltage," *IEEE IEDM Tech. Dig*, pp. 167-170, 1998.

- [5] N. Kimizuka, T. Yamamoto, T. Mogami, K. Yamaguchi, K. Imai, and T. Horiuchi, "The impact of bias temperature instability for direct-tunneling ultrathin gate oxide on MOSFET scaling," *Symp. on VLSI Tech. Dig.*, pp. 73-74, 1999.

- [6] C. Shen, M. F. Li, X. P. Wang, H. Y. Yu, Y. P. Feng, A. T.-L. Lim, Y.-C. Yeo, D. S. H. Chan, and D. L. Kwong, "Negative-u traps in HfO<sub>2</sub> gate dielectrics and frequency dependence of dynamic BTI in MOSFETs," in *IEEE IEDM Tech. Dig*, 2004, pp. 733–736.

- [7] G. Chen, K. Y. Chuah, M. F. Li, Daniel SH Chan, C. H. Ang, J. Z. Zhong, Y. Jin and D.L. Kwong, "Dynamic NBTI of PMOS transistor and its impact on device lifetime," in *Proc. IEEE Reliab. Phys. Symp.*, 2003, pp.196-202.

- [8] M. A. Alam, "A critical examination of the mechanics of dynamic NBTI for PMOSFETs," in *IEEE IEDM Tech. Dig*, 2003, pp. 345-348.

- [9] S. Mahapatra, M. A. Alam, P. Bharath Kumar, T. R. Dalei and D. Saha, "Mechanism of negative bias temperature instability in CMOS devices: degradation, recovery and impact of nitrogen," in *IEEE IEDM Tech. Dig*, 2004, pp.105-108.

- [10] S. Chakravarthi, A.T. Krishnan, V. Reddy, C.F. Machala and S. Krishnan, "A comprehensive framework for predictive modeling of negative bias temperature instability," in *Proc. IEEE Reliab. Phys. Symp.*, 2004, pp.273-282.

- [11] S. Ogawa, M. Shimiya and N. Shionon, "Interface trap generation at ulthathin SiO<sub>2</sub>-Si interfaces during negative-bias temperature aging," *J. Appl. Phys.*, vol.77, 1995, pp.1137-1148.

- [12] N. Kimizuka, K. Yamaguchi, K. Imai, T. Lizuka, C. T. Liu, R. C. Keller, T. Horiuchi, "NBTI enhancement by nitrogen incorporation into ultrathin gate oxide for 0.10µm gate CMOS generation," *Symp. VLSI Tech.*, 2000, pp.91-92.

- [13] V. Huard, M. Denais, "Hole trapping effect on methodology for DC and AC negative bias temperature instability measurements in PMOS," in *Proc. IEEE Reliab. Phys. Symp.*, 2004, pp.40-45.

- [14] B.E. Deal, M. Sklar, A.S. Grove and E.H. Snow, "Characteristics of the Surface-State Charge (Q<sub>ss</sub>) of Thermally Oxidized Silicon," *J. Electrochem. Soc.*, vol. 114, pp. 266, 1967.

- [15] A. Goetzberger, A. D. Lopez, and R. J. Strain, "On the formation of surface states during stress aging of thermal Si-SiO<sub>2</sub> interfaces," *J. Electrochem. Soc.*, vol. 120, pp. 90, 1973.

- [16] K. O. Jeppson and C. M. Svensson, "Negative bias stress of MOS devices at high electric fields and degradation of MOS devices," J. Appl. Phys., vol. 48, pp 2004-2014, 1977.

- [17] G. Haller, M. Knoll, D. Braunig, F. Wulf, and W. R. Fahrner, "Bias-temperature stress on metal-oxide-semiconductor structures as compared to ionizing irradiation and tunnel injection," *J. Appl. Phys.*, vol.56, pp. 1844-1850, 1984.

- [18] C. E. Blat, E. H. Nicollian, and E. H. Poindexter, "Mechanism of negative-bias temperature instability," J. Appl. Phys., vol. 69, pp. 1712-1720, 1990.

- [19] S. Ogawa, M. Shimaya, and N. Shiono, "Interface-trap generation at ultrathin SiO2 (4-6 nm)-Si interface during negative-bias temperature aging," J. Appl. Phys., vol. 77, pp. 1137, 1995.

- [20] T. Yamamoto, K. Uwasawa, T. Mogami, "Bias temperature instability in scaled p+ polysilicon gate p-MOSFETs," *IEEE Trans. Electron. Devices*, vol. 46, pp. 921, 1999.

- [21] M. L. Reed and J. D. Plummber, "Chemistry of Si-SiO2 interface trap annealing," J. Appl. Phys., vol. 63, pp. 5776-5793, 1988.

- [22] G. Chen, M. F. Li, C. H. Ang, J. Z. Zheng and D. L. Kwong, "Dynamic NBTI of p-MOS transistors and its impact on MOSFET scaling," *Electron Device Letters*, *IEEE*, Vol. 23, pp. 734-736, Dec 2002.

- [23] W. Abadeer and W. Ellis, "Behavior of NBTI under AC dynamic circuit conditions," in *Proc. IEEE Reliab. Phys. Symp.*, pp. 17-22, Apr. 2003

- [24] S. S. Tan, T. P. Chen, C. H. Ang and L. Chan, "A new waveform-dependent lifetime model for dynamic NBTI in PMOS transistor," *in Proc. IEEE Reliab. Phys. Symp.*, 2004 pp. 35- 39

- [25] Y. J. Lee, Y. C. Tang, M. H. Wu, T. S. Chao, P. T. Ho, D. Lai, W. L. Yang, and T. Y. Huang, "NBTI effects of pMOSFETs with different nitrogen dose implantation," in *Reliability Physics Symposium Proceedings*, pp. 681-682, 2004.

- [26] Shiyang Zhu, A. Nakajima, T. Ohashi, H. Miyake, "Enhancement of BTI degradation in pMOSFETs under high-frequency bipolar gate bias," *IEEE Electron Device Letters*, Vol. 26, pp. 387-389, Jun. 2005

- [27] A. Kerber, E. Cartier, L.A. Ragnarsson, M. Rosmeulen, L. Pantisano, R. Degraeve, T. Kauerauf, G. Groeseneken, H.E. Maes and U. Schwalke, "Characterization of the VT-instability in SiO2/HfO2 gate dielectrics," *in Proc. IEEE Reliab. Phys. Symp.*, 2003, pp.41-45.

### **Chapter Two**

### **Measurement methods for NBTI**

#### Characterization

### 2.1 Introduction of the conventional DC technique for $V_{th}$ characterization

The NBTI degradation of CMOS devices with conventional gate dielectrics is commonly studied using static (DC) measurement techniques. The  $I_d-V_g$  curves are monitored by measure-stress-measure cycles with DC parametric measurement tools such as the HP4156 semiconductor parameter analyzer. The linear extrapolation (LE) method is widely used to extract threshold voltage ( $V_{th}$ ) from measured  $I_d-V_g$  curves. From the extracted  $\Delta V_{th}$  as stress time curves, the device stability degradation is investigated.

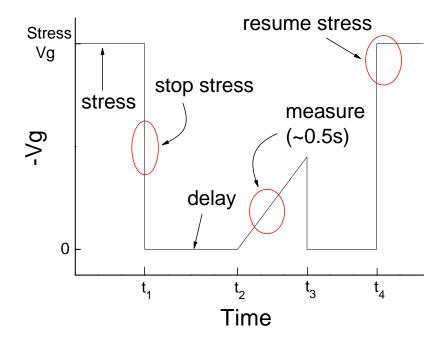

Fig.2-1 illustrates the typical DC measurement waveform applied to the gate when interrupting the stress for measurement. Stress is stopped at time t<sub>1</sub>. Since parameter analyzer needs time to set up the measurement parameters, the measurement is actually started after a delay (t<sub>2</sub>-t<sub>1</sub>). At time t<sub>2</sub>, the gate voltage starts to scan from 0V to the device operation voltage (usually smaller than the stress voltage) and at the same time, the analyzer captures the  $I_d-V_g$  information. This measurement period takes around 0.5sec or more. Then, also after a small delay, the stress is resumed at time  $t_4$ . The whole measurement cycle from stopping stress to resuming stress takes around 1~2sec.

Fig.2-1 Illustration of the conventional DC NBTI measurement cycle.

However, since there is always a time delay, which is typically in the order of 0.1–1 second, between the end of stress and the  $I_d-V_g$  measurement for  $V_{th}$  extraction, using this method to extract the  $\Delta V_{th}$  characteristic is only able to observe the slow component in NBTI degradation.

#### 2.2 An advanced fast technique for $V_{th}$ characterization

Since the aggressive scaling of CMOS devices, the pure  $SiO_2$  gate dielectric is being driven to its physical limits. Alternative gate dielectrics, such as SiON and HfO<sub>2</sub> based materials, are currently being investigated extensively as a replacement for  $SiO_2$ as a gate insulator. With the equivalent oxide thickness (EOT) scaling down, charge trapping / de-trapping in these alternative gate dielectrics makes degradation and recovery in  $V_{th}$  significant even within a 1ms delay [1]–[4]. The conventional measurement method greatly underestimates the real  $V_{th}$  NBTI degradation. Though the  $V_{th}$  recovery during the short delay in conventional DC measurement method has long been thought negligible in devices with SiO<sub>2</sub> as the gate dielectric, it must be taken into consideration in the investigation of SiON gate dielectric devices. Therefore, a fast technique is necessary to be developed in order to give more accurate analysis in SiON gate dielectric investigation.

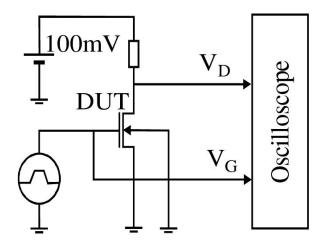

The measurement method developed by Kerber et al. has been widely used to evaluate the fast charging trapping in high- $\kappa$  dielectrics [1]. The method setup is shown in Fig.2-2.

Fig.2-2 Schematic drawing of measurement setup used for pulsed Id-Vg experiments in the µs range.

A pulse generator is used to apply the gate voltage to the MOSFET. The oscilloscope monitors the gate voltage, and measures the voltage drop across the sense resistor R at the drain, from which one is able to extract the drain current by the following equation:

$$I_{d} = \frac{100mV}{V_{d}} \cdot (\frac{100mV - V_{d}}{R_{L}}) , \qquad 2.1$$

where  $R_L$  is the load of the inverter circuit. The pulsed  $I_d$ - $V_g$  measurement technique enables drive current measurements down to less than millisecond. More importantly, the time delay between stressing and sensing is significantly shrunk.

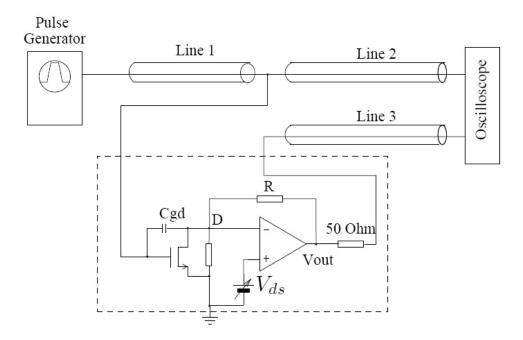

However, this method brings some constraints for ultra-fast measurement. In this method, the drain voltage of the MOSFET under test is not a constant, but changes with the change of drain current. The parasitic capacitor  $C_0$  and  $C_{gd}$  are charged or discharged since the change of gate or drain voltage during the measurement, and this charging current distorts the measured drain current. To circumvent this problem, an improved pulsed  $I_d-V_g$  measurement technique was developed by C. Shen et al [6], as shown in Fig.2-3.

Fig.2-3 Schematic diagram of the setup used for improved pulsed  $I_d$ - $V_g$  measurement technique

In this setup, an Op-Amp is inserted between the drain and source/substrate. Since the virtual short circuit property of Op-Amp (the two input terminals are forced to be equal), the drain voltage of the MOSFET is fixed at  $V_{ds}$  supplied by the voltage source. Therefore, there is no charging or discharging current flows through  $C_0$ . A high-speed Op-Amp (OPA655) with 400MHz unity gain bandwidth is used to achieve fast measurement.

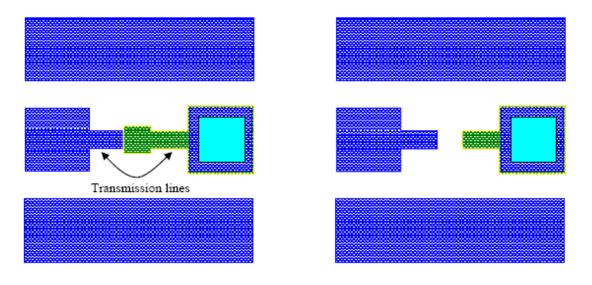

As samples are measured in probe station environment, the Op-Amp circuit (enclosed by the dashed line in Fig.2-3) is mounted immediately above the probe holder. Probe holders are modified to make the wire connection from voltage source to the transistor source and drain terminal less than 10cm, so that the parasitic effects are minimized. All the transmission lines are  $50\Omega$  co-axial cables, and cable 2 and 3 have the same length to minimize the difference in cable delay. The drain current is measured by the sense resistor R. Resistor  $R_0 = R$  is used to ensure circuit stability when the MOSFET is off. The output voltage measured at the oscilloscope is related to the MOSFET drain current by:

$$V_{out} = (I_d - I_{gd}) \cdot R + V_{ds}, \qquad 2.2$$

where R is the sense resistance,  $V_{ds}$  is the drain voltage, and  $I_{gd}$  is the current from gate to drain through the parasitic capacitor  $C_{gd}$ . The current  $I_{gd}$  is caused by the fast transient at the gate and is given by:

$$I_{gd} = C_{gd} \cdot \frac{dV_{gd}}{dt} = C_{gd} \cdot \frac{dV_{gs}}{dt}.$$

2.3

In the measurement, the MOSFET is biased in linear region in  $I_d - V_g$  measurements, and  $C_{gd}$  is given by:

$$C_{gd} = C_{overlap,d} + \frac{1}{2}C_{inv}, \qquad 2.4$$

where  $C_{overlap,d}$  and  $C_{inv}$  are the capacitance of the drain overlap region and the inversion capacitance, respectively.

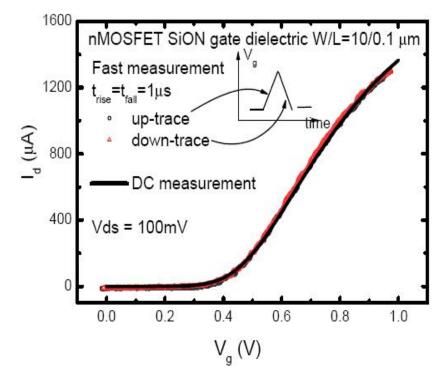

Fig.2-4  $I_d - V_g$  characteristics measured from a short-channel nMOSFET with SiON gate dielectric, with the  $V_g$  waveform shown in the inset.

For short-channel devices, since  $C_{gd}$  is small, the corresponding  $I_{gd}$  is much smaller than the drain current, and therefore the charging current through  $C_{gd}$  can be ignored. When a symmetric triangular pulse is applied at the gate as shown in the inset of Fig.2-4,  $Id-V_g$  curve can be measured at both the up-trace and down-trace of the pulse. In the two cases,  $dV_g/dt$  are of the same magnitude but of opposite polarity. For nMOSFET with short channel length L = 0.1µm, the  $Id-V_g$  curves measured in the up-trace and down-trace (1µs measurement time) of  $V_{gs}$  both coincide with that from DC measurement, as shown in Fig.2-4, which indicates that the effect of charging current through  $C_{gd}$  with a measurement time down to 1µs is negligible.

This improved pulsed  $I_d$ - $V_g$  measurement method is used to evaluate the charge trapping in ultra-thin SiON gate dielectric devices. It distinguishes the fast and slow NBTI component in SiON [4]. The 1µs measurement time is shown to be fast enough

for this particular application. Results of the fast measurement will be discussed in Chapter 4.

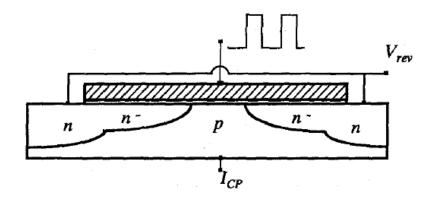

### 2.3 Improved Charge Pumping and DCIV techniques for $N_{it}$ characterization on thin gate dielectric

The charge-pumping (CP) technique is a well-known experimental approach for assessing the interface-state density of MOSFET's [5] [6]. Using this technique, it has been possible to measure the spatial variation of hot carrier induced  $D_{it}$  near the drain [7]-[9]. The pulses applied to the gate of the MOSFET can be square, triangular or sawtooth waves. The basic arrangement for the conventional CP measurements is presented in Fig.2-5.

Fig.2-5 Schematic diagram for Charge Pumping measurement setup

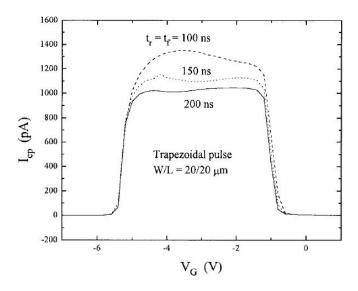

An HP8110 pulse generator is used to supply the gate pulses, and a small reverse bias is applied to the source and drain of the MOSFET. The substrate current of the device can be measured by an HP4156 parameter analyzer with varying pulse base level to drive the silicon surface from accumulation to inversion, while the amplitude of the pulses is kept constant. Fig.2-6 shows the measurement result on a long channel device with a thick EOT around 20nm [10]. The pulses added on gate were trapezoidal in shaped, and three different rise and fall times of the pulse were used in the measurements. As shown in this figure, the leakage gate current is very low during the measurement even when the amplitude of gate voltage exceeds 6V, hence it is generally thought to be accurate when measuring the devices with EOT>30Å.

Fig.2-6 Measured  $I_{cp}$  on a long channel thick dielectric device by the conventional Charge-Pumping measurement.

However, scaling of sub-l00nm device nowadays needs a  $t_{ox}$  in the range of 10-15Å, and as predicted from the roadmap, this thickness is even reaching the range of <10Å in the next couple of years. It is well known that two pronounced effects occur as a result of the gate oxide scaling below 30Å, i.e., direct tunneling gate leakage and the quantum mechanical effect [11] [12]. Since large gate leakage current occurs during the measurement, this conventional Charge-Pumping measurement becomes inaccurate for the  $t_{ox}$ <2nm. With the gate leakage current becoming dominant for  $t_{ox}$ <1.3nm, it is even impossible to observe the peak  $I_{cp}$  by the conventional ChargePumping method. Then one faces a severe problem on how to measure the oxide quality with thickness below 20Å, in particular the interface traps  $N_{it}$ .

An improved method – high-low frequency CP method, derived from the conventional charge pumping method was demonstrated by S. S. Chung et al. [13] for accurate determination of the interface traps in ultra-thin dielectric devices.

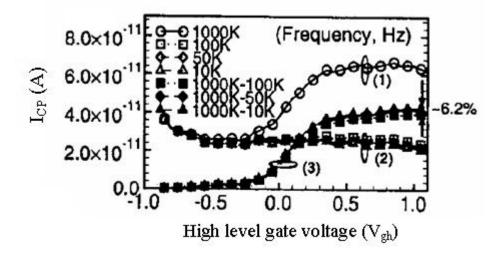

Fig.2-7 *I<sub>cp</sub>* measured by high-low frequency CP method.

High-low frequency CP method is shown in Fig.2-7. First, the  $I_{cp}$  for various frequencies was measured. Curve (1) was measured by a high frequency, while group (2) curves were measured by several low frequencies and are considered as the leakage current. Using curve (1) subtract group (2) curves can have the correct  $I_{cp}$  (group 3) without leakage component. Since the charge pumping current is proportional to the measurement frequency, one is now able to extract the  $N_{it}$  parameter from the  $I_{cp}$  curves after low frequency calibration.

Another method commonly used to characterize  $N_{it}$  is direct-current current–voltage (DCIV) technique [14].

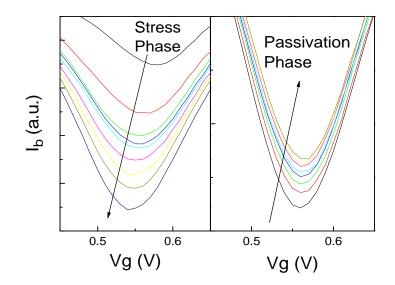

Fig.2-8 illustrates the DCIV measurement set-up for a p-MOSFET. The drain  $p^+$ , n<sup>-</sup> well and p<sup>-</sup> substrate form a vertical BJT transistor. Since the base current  $I_b$  comes from the recombination current at the interface traps generated during operation, it is directly proportional to  $N_{it}$ . Therefore, by measuring  $I_b$ , one is able to get the information of  $N_{it}$  in the channel. Adjust  $V_g$  until the interface trap energy in the middle of the Si energy gap becomes coincident with the Fermi energy; a peak value of  $I_{DCIV}$ can then be observed, and this peak amplitude is actually proportional to the effective number of interface traps  $N_{it}$ .

| HP 4145B Semiconductor Paremeter                           |      |                              |                                                    |                        |    |

|------------------------------------------------------------|------|------------------------------|----------------------------------------------------|------------------------|----|

| V <sub>s</sub> (I <sub>s</sub> = 0)<br>Source<br>(floated) |      | Vd(Id)<br>Drain<br>(Emitter) | V <sub>b</sub> (I <sub>b</sub> )<br>Bulk<br>(Base) | Vc<br>Substi<br>(Colle |    |

| Lt_                                                        | n-we | - <u>p-</u> p-               | +n                                                 | ± 55                   | p+ |

|                                                            |      | D -                          | substrat                                           | <u>e &gt;&gt;</u>      |    |

Fig.2-8 Cross-sectional schematic of a PMOS and the DCIV measurement set-up.

However, this method also suffers from the high leakage current with dielectric scaling down. G. Chen et al. [15] proposed an improved DCIV method to monitor the interface traps in MOSFETs with gate oxide thicknesses down to 1.3 nm by proper biasing and signal processing. By measuring  $I_b$  under bias  $V_e > 0$  and  $V_e = 0$ , respectively, one finds the difference  $(I_{b(Ve)} - I_{b(0)})$  is exactly the DCIV current combined with background recombination current (from drain to n-well) and thermal-trap-tunneling current at s/d extension, which are both independent of the  $N_{it}$ . Since BTI characterization usually only concentrates on the increase or recovery in  $N_{it}$  during stress or passivation, using the difference  $(I_{b(Ve)} - I_{b(0)})$ , one is able to eliminate the influence from the gate leakage current.

#### **Reference:**

- A. Kerber, E. Cartier, L. A. Ragnarsson, M. Rosmeulen, L. Pantisano, R. Degraeve, T. Kauerauf, G. Groeseneken, H. E. Maes, and U. Schwalke, "Characterization of the VT-instability in SiO2/HfO2 gate dielectrics," in *IEEE IRPS Tech. Digest*, 2003, pp. 41–45.

- [2] C. Shen, M. F. Li, X. P. Wang, H. Y. Yu, Y. P. Feng, A. T.-L. Lim, Y.-C. Yeo, D. S. H. Chan, and D. L. Kwong, "Negative-u traps in HfO2 gate dielectrics and frequency dependence of dynamic BTI in MOSFETs," in *IEDM Tech. Digest*, 2004, pp. 733–736.

- [3] M. Denais, A. Bravaix, V. Huard, C. Parthasarathy, G. Ribes, F. Perrier, Y. Rey-Tauriac, and N. Revil, "On-the-fly characterization of NBTI in ultra-thin gate oxide PMOSFET's," in *IEDM Tech. Digest*, 2004, pp. 109–112.

- [4] T. Yang, M. F. Li, C. Shen, C. H. Ang, C. Zhu, Y.-C. Yeo, G. Samudra, S. C. Rustagi, M. B. Yu, and D. L. Kwong, "Fast and slow dynamic NBTI components in p-MOSFET with SiON dielectric and their impact on device life-time and circuit application," in *VLSI Symp. Tech. Digest*, 2005, accepted.

- [5] J. S. Brugler and P. G. A. Jespers, "Charge pumping in MOS devices," *IEEE Trans. Electron Devices*, vol. ED-16, pp. 297–302, 1969.

- [6] G. Groeseneken, H. E. Maes, N. Beltran, and R. F. de Keersmaecker, "A reliable approach to charge-pumping measurements in MOS transistors," *IEEE Trans. Electron Devices*, vol. ED-31, pp. 42–53, 1984.

- [7] T. Poorter and P. Zoestbergen, "Hot carrier effects in MOS transistors," in *IEDM Tech. Dig.*, 1984, pp. 100–103.

- [8] M. G. Ancona, N. S. Saks, and D. McCarthy, "Lateral distribution of hot-carrierinduced interface traps in MOSFET's," *IEEE Trans. Electron Devices*, vol. 35, pp. 2221–2228, 1988.

- [9] W. Chen, A. Balasinski, and T. P. Ma, "Lateral profiling of oxide charge and interface traps near MOSFET junctions," *IEEE Trans. Electron Devices*, vol. 40, pp. 187–196, 1993.

- [10] P. T. Lai, J. P. Xu, C. K. Poek, and Y. C. Cheng, "Analysis on accuracy of Charge-Pumping measurement with gate sawtooth pulses," *IEEE Trans. Electron Devices*, vol. 45, No. 4, pp947-952, Apr., 1998.

- [11] C.-H. Choi, J.-S. Goo, T.-Y. Oh, Z. P. Yu, R. W. Dutton, A. Bayoumi, M. Cao, P. V. Voorde, and D. Vook, "C-V and gate tunneling current characterization of

ultra-thin gate oxide MOS (tox=1.3-1.8nm)," in *Symposium on VLSI Tech.*, pp. 63-64, 1999.

- [12] K. Yang, Y.-C. King, C. M. Hu, "Quantum effect in oxide thickness determination from capacitance measurement," in *Symposium on VLSI Tech.*, pp. 77-78, 1999.

- [13] Steve S. Chung, S.-J. Chen, C.-K. Yang, S.-M. Cheng, S.-H. Lin, Y.-C. Sheng, H.-S. Lin, K.-T. Hung, D.-Y. Wu, T.-R. Yew, S.-C. Chien, F.-T. Liou, and Frank Wen, "A novel and direct determination of the interface traps in sub-100nm CMOS devices with direct tunneling regime (12-16Å) gate oxide," in *Symp. VLSI Tech.*, 2002, pp.74-75.

- [14] B. B. Jie, M. F. Li, C. L. Lou, W. K. Chim, D. S. H. Chan, and K. F. Lo, "Investigation of Interface Traps in LDD pMOST's by the DCIV Method," *IEEE Electron Device Letter*, vol. 18, No. 12, pp.583-585, Dec. 1997.

- [15] G. Chen, K. Y. Chuah, M. F. Li, Daniel SH Chan, C. H. Ang, J. Z. Zheng, Y. Jin and D.L. Kwong, "Dynamic NBTI of PMOS transistor and its impact on device lifetime," in *Proc. IEEE Reliab. Phys. Symp.*, 2003, pp.196-202.

# Chapter Three A detailed analysis on conventional DC measurements

### 3.1 Debate on the origin of NBTI recovery effect in p-MOSFET with SiON gate dielectric by DC method

It is commonly known that under static NBTI stress, the p-MOSFET shows a significant negative threshold voltage shift. By adding a passivation phase (applying a positive or zero gate bias) after the NBTI stress, recovery of NBTI degradation can be observed. Recently, several studies on the origin of this NBTI recovery effect have been reported [1-7]. G. Chen et al. [1], by using DCIV method [8], found that the  $V_{th}$  recovery in the passivation phase is due to the passivation of SiO<sub>2</sub>/Si interface traps, which is consistent with some other works [2-4, 9, 10]. On the contrary, V. Huard et al. [5] using the charge pumping method (CP) [11], and inferred that the interface trap density remains as a constant during the passivation phase, and the transient recovery of  $V_{th}$  in the passivation phase is due to de-trapping of hole traps in the dielectric. In this chapter, the contradicting views on the  $V_{th}$  recovery mechanism in the passivation phase will be clarified. The NBTI degradation and recovery effects observed by the conventional DC measurement method is mainly due to the creation and dissipation of

interface traps at the SiON/Si interface by releasing and retracting hydrogen-related species, rather than trapping/de-trapping of the pre-existing hole traps in SiON bulk.

#### 3.2 Experimental results and discussion

Transistors were fabricated using CSM 0.11 $\mu$ m CMOS technology. The gate dielectric with two equivalent oxide thicknesses (EOT), 1.3nm and 4.5nm, were grown by thermal oxidation followed by decoupled plasma nitridation (DPN) and post-deposition thermal annealing. An HP4155C parameter analyzer was used to measure the device characteristics. CP pulse was generated by HP41501B pulse generator. For  $N_{it}$  measurement of p-MOSFET with EOT=1.3nm, the improved DCIV method and the improved CP method as illustrated in Chapter 2.3 were used.

For the NBTI characterization, devices with EOT=1.3nm were stressed under a constant negative gate voltage followed by a passivation phase ( $V_g$ =0V), while the source, drain and bulk were grounded. Stress in the stress phase was intermittently interrupted for  $V_{th}$  and  $N_{it}$  measurement. During each interruption, both  $V_{th}$  (extracted by  $I_d$ - $V_g$  measurement) and  $N_{it}$  (extracted by DCIV measurement) were measured by two characterization approaches: in the first approach,  $V_{th}$  was measured first, followed by  $N_{it}$  measurement; in the second one,  $N_{it}$  was measured first, followed by  $V_{th}$  measurement. NBTI stress was conducted under a wide range of gate voltage.

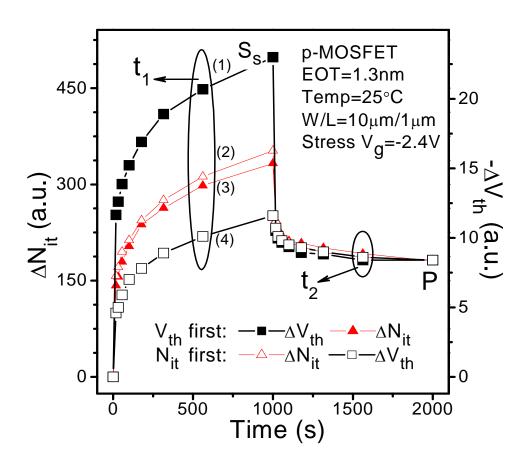

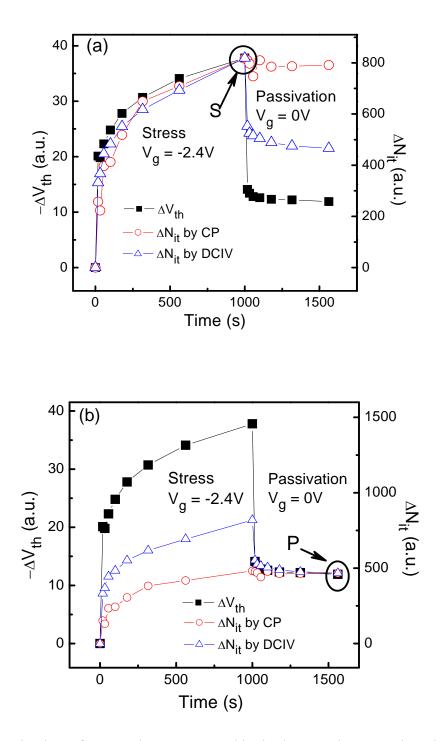

From the  $I_{DCIV}$  curves as shown in Fig.3-1, one can observe an unambiguous  $\Delta N_{it}$  generation and recovery. No doubt, interface traps do have recovery effect. Fig.3-2 plots both measured  $\Delta V_{th}$  and  $\Delta N_{it}$  data by two approaches.

Fig.3-1 Measured DCIV curves in both stress and passivation phases.

Fig.3-2 NBTI degradation of pMOSFET characterized by  $\Delta V_{th}$  and  $\Delta N_{it}$  under a stress phase (t=0 to 1000s) and a passivation phase (t=1000 to 2000s).

At a first glance, the four curves in Fig.3-2 do not look consistent. For further understanding the result, Fig.3-2 illustrates what really happens when measuring by two different approaches in both stress and passivation phases.

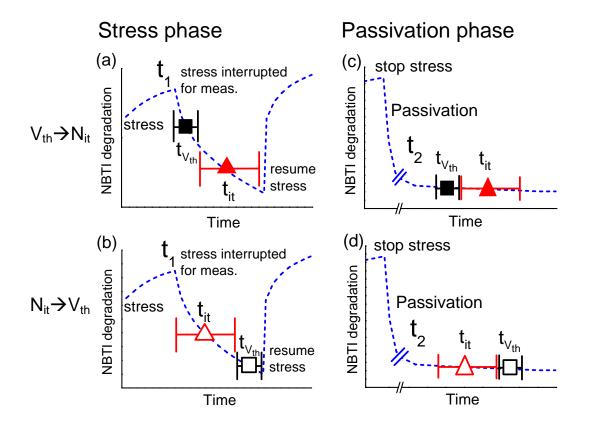

Fig.3-3 Illustration of the NBTI degradation in both stress and passivation phases using two approaches.

In the stress phase, as shown in Fig.3-3(a) and (b), once the stress is interrupted for measurement, the NBTI degradation starts to recover with a trend shown as the dash curves. After the measurement is finished, the stress is resumed, and the NBTI degradation goes up rapidly. If one measures  $V_{th}$  first, followed by  $N_{it}$ , the  $V_{th}$  value (square symbol) will be extracted at a higher NBTI degradation level, and  $N_{it}$  (triangle symbol) at a lower level; if measures  $N_{it}$  first followed by  $V_{th}$ , then the  $N_{it}$  value is extracted at a higher level, and  $V_{th}$  the lower. However, in the passivation phase, as shown in Fig.3-3(c) and (d), once the stress is stopped for passivation, the NBTI

degradation recovery starts. Until the time point to do the measurement, the recovery rate is already very slow. Therefore, no matter measuring  $V_{th}$  first or  $N_{it}$  first, the extracted data are taken at almost the same degradation level.

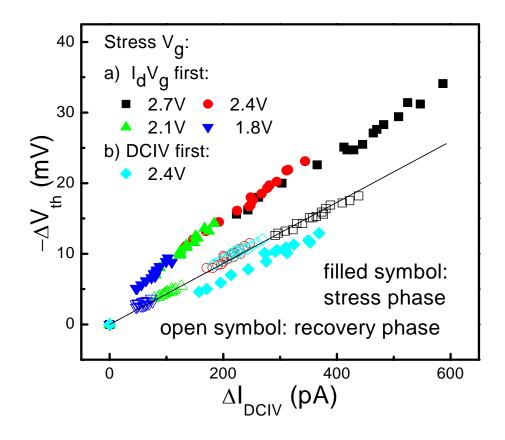

Fig.3-4 The correlation of  $\Delta V_{th}$  and  $\Delta N_{it}$  for NBTI stress under various stress voltage, in the stress and passivation phases, using both measurement approaches.

Fig.3-4 gives further proof on this explanation. It shows the correlation of  $\Delta V_{th}$  and  $\Delta N_{it}$  for NBTI stress under various stress voltage, in stress and passivation phases, using two measurement approaches. In the stress phase, the two measurement approaches ( $I_d$ - $V_g$  first or DCIV first) yield different correlation (different slopes in  $\Delta V_{th}$ - $\Delta N_{it}$  plot). However, in the passivation phase, two approaches yield the same correlation. The real correlation between  $\Delta V_{th}$  and  $\Delta N_{it}$  is shown in the passivation phase because of no interface traps passivation during measurement. Therefore, the

normalization of the four curves should be made at the end of passivation phase (point *P*).

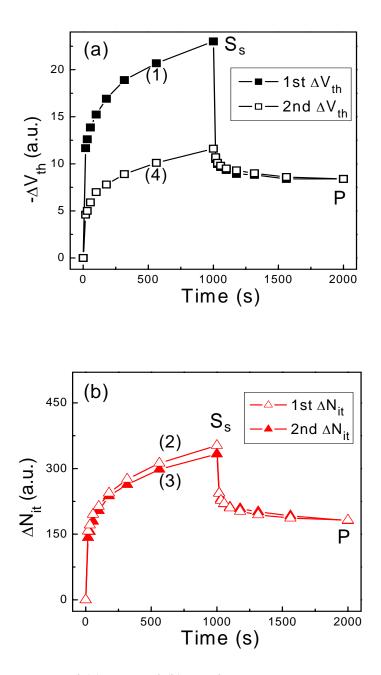

Before alignment of the four curves together,  $\Delta V_{th}$  curves and  $\Delta N_{it}$  curves were plotted separately first. Plotting first (solid squares) and second measured  $\Delta V_{th}$  (open squares) together in one figure gets Fig.3-5(a); and plotting first measured  $\Delta N_{it}$  (solid cycles) and second measured  $\Delta N_{it}$  (open cycles) together gets Fig.3-5(b).

Fig.3-5 Measured (a)  $\Delta V_{th}$  and (b)  $\Delta N_{it}$  by two measurement approaches.

Both figures show obvious bifurcation in the stress phase, which is because of  $N_{it}$  recovery during the other measurement, while both  $\Delta V_{th}$  and  $\Delta N_{it}$  overlap in the passivation phase, showing no influence of the measurement approaches. Normally, it takes different time for  $V_{th}$  and  $N_{it}$  measurements. Define the time for a  $V_{th}$  measurement as  $t_{Vth}$  and the time for a  $N_{it}$  measurement as  $t_{it}$ . Since the DCIV current is several orders smaller than the drain current, usually it takes longer time for  $N_{it}$  measurement than for  $V_{th}$ , and therefore,  $t_{it} > t_{Vth}$ , so the gap in the stress phase shown by the two  $\Delta V_{th}$  curves is much greater than that shown by  $\Delta N_{it}$  curves. Therefore, when plotting four curves together in one figure, it reasonably gets Fig.3-2.

#### 3.3 Impact of N<sub>it</sub> measurement on NBTI recovery

Further experiments are designed to illustrate the interface trap passivation effect and show a significant impact of  $N_{it}$  measurement on NBTI recovery.

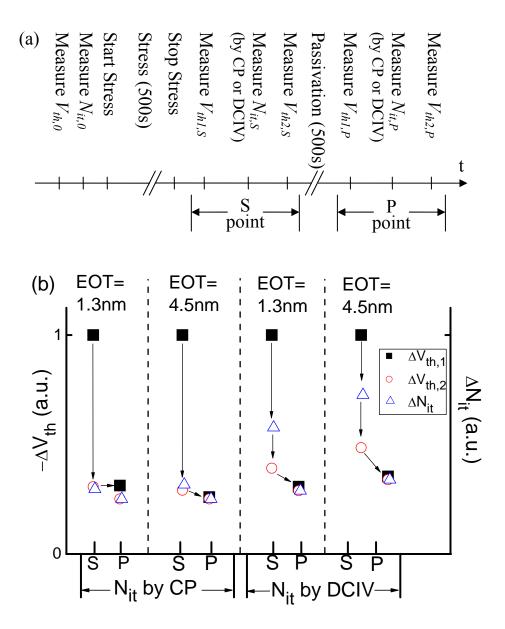

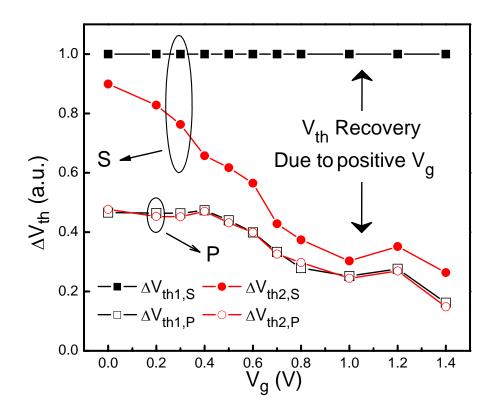

For each fresh device in Fig.3-6, the  $V_{th}$  and  $N_{it}$  were first measured, giving the initial threshold voltage  $V_{th,0}$  and the initial interface trap density  $N_{it,0}$ . A stress ( $V_g$  = - 2.4V for EOT=1.3nm devices, -4.5V for EOT=4.5nm devices) was then applied for 500sec. Threshold voltage shift  $\Delta V_{th1,S}$  was measured at the end of the stress (point  $S_S$  as indicated in Fig.3-2), followed by a measurement of the change in interface trap density  $\Delta N_{it,S}$  using CP or DCIV method, and another measurement of the threshold voltage shift  $\Delta V_{th2,S}$  was followed. After a 500ses lapse in the passivation phase ( $V_g$  = 0V),  $\Delta V_{th1,P}$ ,  $\Delta N_{it,P}$ , and  $\Delta V_{th2,P}$  were measured sequentially again at the end of passivation phase (point P as indicated in Fig.3-2). In Fig.3-6 (b),  $\Delta N_{it}$  and  $\Delta V_{th}$  data are normalized at point P because little passivation of  $N_{it}$  occurs at P.

Fig.3-6 (a): Measurement sequences at both *S* and *P* points (indicated in Fig.1) (b): Measured  $\Delta V_{th1}$ ,  $\Delta N_{it}$ , and  $\Delta V_{th2}$  data at points *S* and *P*.  $\Delta N_{it}$  and  $\Delta V_{th2}$  data are normalized at point *P*.

All data from devices with thin (EOT=1.3nm) and thick (EOT=4.5nm) gate dielectrics show the same trend: at point *S*,  $\Delta V_{th2}$  after the  $N_{it}$  measurement is much smaller than  $\Delta V_{th1}$  before the  $N_{it}$  measurement. For the thick dielectric with EOT=4.5nm, the measured FN tunneling current at gate rises significantly only when  $|V_g|$  is above 5V. Therefore at a stress voltage of -4.5V, the measured gate current is

negligible and no charge trapping/de-trapping in the dielectric. All variation of  $V_{th}$  is due to variation of  $N_{it}$  (generation and passivation). The reduction of  $\Delta V_{th}$  is due to the passivation of interface traps. The  $N_{it}$  measurement accelerates the reduction of  $\Delta V_{th}$ due to the positive gate bias applied to the device during  $N_{it}$  measurement. Fig.3-6 (b) also clearly shows that no obvious recovery of  $\Delta N_{it}$  can be observed in the passivation phase using CP measurement [5], because most of the interface traps have already been passivated during the CP measurement. Since the thin dielectric device has the same trend as the thick dielectric device, it is believed that the  $V_{th}$  recovery is dominated by  $N_{it}$  passivation [1] rather than  $N_{ot}$  de-trapping [5].

Fig.3-7 In the measurement sequence of Fig.3-6(a), the measurement of  $N_{it}$  is replaced by a 0.5 s positive gate bias stress  $V_g$  (for both points S and P). Plot  $\Delta V_{th,2}$  as a function of different  $V_g$ , normalized by  $\Delta V_{th,1}$  at point S.

Fig.3-7 illustrates the acceleration effect of interface trap passivation under a positive gate bias. The same measurement sequence as that in Fig.3-6 was used, however the measurement of  $N_{tl}$  was replaced by a 0.5s positive gate bias stress  $V_g$  (for both points S and P). Fig.3-7 plots  $\Delta V_{th,2}$  as a function of different positive  $V_g$ , normalized by  $\Delta V_{th,1}$  at point *S*. The results show clearly that the positive bias accelerates  $\Delta V_{th}$  passivation. This explains the different results obtained by DCIV and CP measurements in Fig.3-6 (b). In DCIV measurement, a recombination current  $I_{DCIV}$  through the interface traps shows a peak when the Fermi level coincides with the Si mid gap at surface [13]. In our measurement, the maximum  $V_g$  applied to the device to show the peak is around +0.5~0.6V. In the stress phase measurement, the interface traps have already passivated to some extend before reaching the  $I_{DCIV}$  peak gate voltage (Fig.3-7 data measured at point *S*), so the result is always underestimated. However after a time period of passivation in the passivation phase at point *P*, the passivation rate is almost zero (Fig.3-7 data measured at point *P*) and therefore DCIV method measures the real interface trap density.

The underestimation is more serious when using Charge Pumping (CP) technique. In CP measurement, the device changes from inversion to accumulation to pump the electrons between conduction/valence bands through the interface states [11]. Therefore, comparing to the DCIV measurement, a larger positive  $V_g$  should be applied. In our CP measurement, the maximum positive  $V_g$  applied to the device is +1.2V. In addition, CP measurement uses longer time than DCIV measurement. This explains why  $\Delta V_{th,2,s}$  and  $\Delta N_{it}$  measured by CP is smaller than that measured by DCIV as indicated in Fig.3-6(b), that is, more interface traps are passivated during the CP measurement.

Fig.3-8 The data of  $\Delta V_{th}$  and  $\Delta N_{it}$  measured by both CP and DCIV, plotted versus stress and passivation time: (a) all data aligned at point *S* [5]; (b) all data aligned at P point (this work).

According to the discussion in [5], all curves are aligned at point S in Fig.3-8(a). However, this alignment is misleading because the measured  $N_{it}$  is underestimated during the stress phase. Due to this incorrect alignment,  $N_{it}$  is lifted up at the passivation phase.  $N_{it}$  is lifted more by using CP measurement, consistent with Fig.1 of [5], even looks like no interface trap recovery. Thus, the contradiction between two different interpretations of the  $V_{th}$  recovery phenomena in the passivation phase is clarified.

### **Reference:**

- [1] G. Chen, M. F. Li, C. H. Ang, J. Z. Zheng, and D. L. Kwong, "Dynamic NBTI of PMOS transistors and its impact on MOSFET scaling," in *IEEE EDL* vol.23, pp.734-736 (2002), and *Proc. IEEE Reliab. Phys. Symp.*, 2003, pp.196-202.

- [2] M. A. Alam, "A critical examination of the mechanics of dynamic NBTI for pMOSFETs," in *IEDM Tech. Dig.*, 2003, pp. 345-348.

- [3] S. Mahapatra, M. A. Alam, P. Bharath Kumar, T. R. Dalei and D. Saha, "Mechanism of negative bias temperature instability in CMOS devices: degradation, recovery and impact of nitrogen," in *IEDM Tech. Dig.*, 2004, pp.105-108.

- [4] S. Chakravarthi, A. T. Krishnan, V. Reddy, C. F. Machala and S. Krishnan, "A comprehensive framework for predictive modeling of negative bias temperature instability," in *Proc. IEEE Reliab. Phys. Symp.*, 2004, pp.273-282.

- [5] V. Huard and M. Denais, "Hole trapping effect on methodology for DC and AC negative bias temperature instability measurements in PMOS," in *Proc. IEEE Reliab. Phys. Symp.*, 2004, pp.40-45.

- [6] W. Abadeer and W. Ellis, "Behavior of NBTI under AC dynamic circuit conditions," in *Proc. IEEE Reliab. Phys. Symp.*, 2003, pp.17-22.

- [7] S. Tsujikawa, T. Mone, K. Watanabe, Y. Shinamoto, R. Tsuchiya, K. Ohnishi, T. Onai, J. Yugami, and S. Kimura, "Negative bias temperature instability of p-MOSFETs with ultra-thin SiON gate dielectrics," in *Proc. IEEE Reliab. Phys. Symp.*, 2003, pp.183-187.

- [8] A. Neugroschel, C. T. Sah, K. M. Han, M. S. Caroll, T. Nishida, J. T. Kavalieros, and Y. Lu, "Direct-current measurement of oxide and interface traps on oxidized Silicon," *IEEE Trans Electron Devices*, vol.47, 1995, pp.1657-1662.

- [9] S. Ogawa, M. Shimiya and N. Shionon, "Interface trap generation at ulthathin SiO2-Si interfaces during negative-bias temperature aging," J. Appl. Phys., vol.77, 1995, pp.1137-1148.

- [10] N. Kimizuka, K. Yamaguchi, K. Imai, T. Lizuka, C. T. Liu, R. C. Keller, and T. Horiuchi, "NBTI enhancement by nitrogen incorporation into ultrathin gate oxide for 0.10µm gate CMOS generation," Symp. VLSI Tech., 2000, pp.91-92.

- [11] Guido Groeseneken, Herman E. Maes, Nicolas Beltran, and Roger F. De Keersmaecker, "A reliable approach to Charge-Pumping measurements in MOS transistors," *IEEE Trans. Electron Devices*, vol.ed-31, No.1, Jan, 1984, pp.42-53

- [12] Steve S. Chung, S.-J. Chen, C.-K. Yang, S.-M. Cheng, S.-H. Lin, Y.-C. Sheng, H.-S. Lin, K.-T. Hung, D.-Y. Wu, T.-R. Yew, S.-C. Chien, F.-T. Liou, and Frank Wen, "A novel and direct determination of the interface traps in sub-100nm CMOS devices with direct tunneling regime (12-16A) gate oxide," *Symp. VLSI Tech.*, 2002, pp.74-75.

- [13] J. Cai and C. T. Sah, "Interfacial electronic traps in surface controlled transistors," *IEEE Trans. Electron Devices*, vol.47, 2000, pp.576-583.

# Chapter Four Fast NBTI components in p-MOSFET with SiON gate dielectric and its impact on circuit applications

### 4.1 Introduction

As discussed in the previous chapters, using the conventional DC measurement method to characterize the NBTI degradation, time delay between the stopping of the stress and actual measurement is typically in the order of 1 second. Since the NBTI  $V_{th}$ degradation starts to recover as soon as the stress voltage is removed, this time delay leads to underestimation of  $V_{th}$  degradation which has already been found to be significant in thin high- $\kappa$  dielectrics [1][2]. Therefore a fast measurement method is necessary to minimize the  $V_{th}$  recovery effect prior to measurement. In this chapter, the fast pulsed measurement method as introduced in Chapter 2.4 is used for the DNBTI study of ultra-thin SiON gate dielectrics. By using the fast pulsed measurement method, a distinctive fast trapping / de-trapping transient component that is responsible for large  $V_{th}$  shifts has been found, in addition to the widely-reported slower DNBTI degradation component. The frequency and voltage dependencies of the fast DNBTI component are also investigated. A model for charge trapping is developed, and the impact of the fast DNBTI component is analyzed.

### 4.2 Experimental results and discussion

Transistors were fabricated using CSM 0.11  $\mu$ m CMOS technology. The gate dielectric has an equivalent oxide thickness (EOT) of 1.3 nm and was grown by thermal oxidation followed by decoupled plasma nitridation (DPN) and post-deposition thermal annealing. Both NBTI and DNBTI stress were performed using the fast pulsed  $I_d$ - $V_g$  measurement technique as described in Chapter 2.4 to examine the fast component of the de-trapping charge as stress progresses.

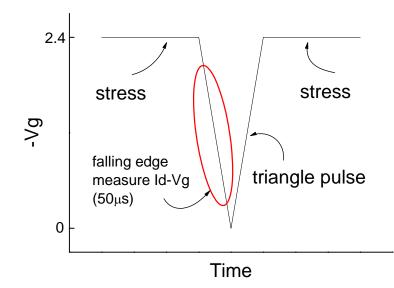

Fig.4-1 Pulsed waveform for NBTI characterization in static stress phase.

For NBTI stress, short triangular voltage pulses (from stress voltage to 0V and back to stress voltage) are inserted in the constant gate voltage stress to intermittently monitor the  $I_d$ - $V_g$  characteristics, as illustrated in Fig.4-1. The  $I_d$ - $V_g$  curves are derived

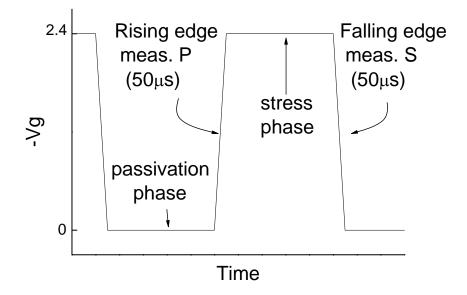

from the falling edge (from stress voltage to 0V) or rising edge (from 0V to stress voltage) of the triangular voltage pulses. For DNBTI stress, dynamic stress voltage with a square waveform is applied on the gate with different frequencies, and the  $I_d$ - $V_g$  characteristics are measured at both rising (R) and falling (F) edges of the square wave during stress, as illustrated in Fig.4-2. For both NBTI and DNBTI stresses, the measurement time  $t_m$  can be adjusted by changing the rising or falling time of the pulses, and therefore the delay between stress and measurement can be minimized. As long as  $t_m$  is short enough, the extracted transistor threshold voltage is negligibly affected by the  $V_{th}$  recovery effect.

Fig.4-2 Waveform for DNBTI characterization by the fast pulsed measurement.

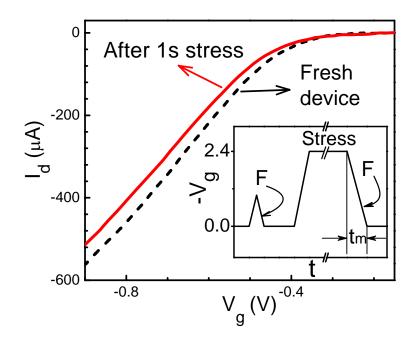

Fig.4-3 shows an example of measured  $I_d - V_g$  curves. The waveform applied on the gate is shown in the inset. First, a triangle pulse was applied on the gate, and the falling edge of the pulse was used to derive  $I_d - V_g$  curve of a fresh device; then after a 1 second stress, the falling edge of the stress was monitored to derive the  $I_d - V_g$  after stress. From the result, one can see an obvious  $V_{th}$  shift.

Fig.4-3  $I_d - V_g$  curves measured by fast pulsed measurement.

Fig.4-4  $\Delta V_{th}$  as measured using different measurement time  $t_m$  (Fig.4-3 inset), after 1sec stress.  $\Delta V$ th measured using a conventional DC method is also shown.

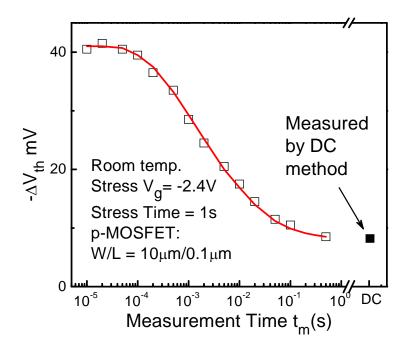

Since result shows the measured  $V_{th}$  shift depends on the measurement time, different  $t_m$  was used to repeat the above experiment. As shown in Fig.4-4, when  $t_m$  is increased above 100µs, the measured  $\Delta V_{th}$  decreases dramatically due to  $V_{th}$  recovery during the measurement. It is also seen from Fig.4-4 that the  $\Delta V_{th}$  measured by the fast pulsed method approaches the value obtained by the conventional DC method when  $t_m$ is longer than 0.5s, which means that the result of pulsed and DC methods are consistent with each other. On the other hand, when  $t_m$  is kept below 100µs, the measured  $\Delta V_{th}$  is almost independent of  $t_m$ , indicating that recovery of  $\Delta V_{th}$  during that time period is negligible.

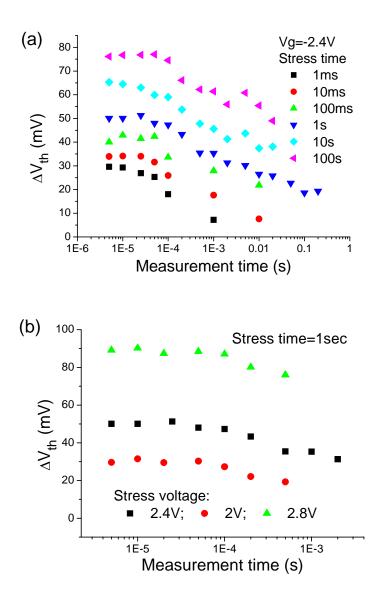

Fig.4-5  $\Delta V_{th}$  as measured using different measurement time  $t_m$  (Fig.4-3 inset), after: (a) different stress time with same stress voltage; (b) different stress voltage with fixed stress time.

In addition, different samples with different stress voltage  $V_g$  and different stress time ranging from 1ms to 100s were measured, and all the results (Fig.4-5) show a saturation  $\Delta V_{th}$  at  $t_m \sim 100 \mu$ s. Therefore  $t_m = 50 \mu$ s is fast enough for the specific devices used in this experiment, and it is employed for all the fast NBTI measurements in this work.

Fig.4-6 (a)  $\Delta V_{th}$  under dynamic stress as measured by fast pulsed and DC methods for frequency of 0.0005Hz; (b)  $\Delta V_{th}$  due to fast component.

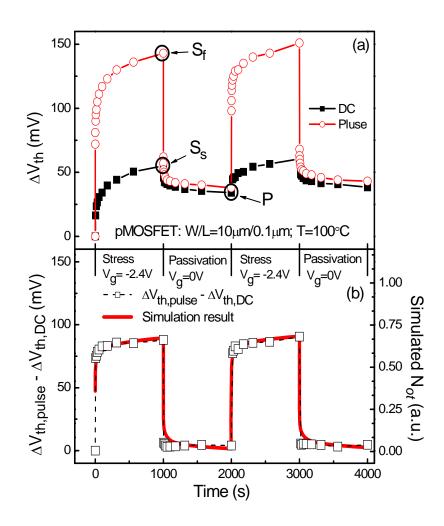

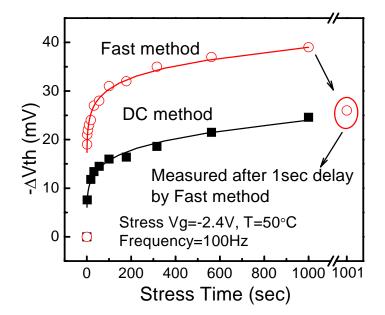

Fig.4-6 shows the  $\Delta V_{th}$  evolution measured on a p-MOSFET under DNBTI stress at a very low frequency (0.0005Hz), using both fast pulsed measurement described above and the conventional DC method.  $S_f$  and  $S_s$  are the points of the end of stress phase measured by fast pulsed and DC method respectively; P is the end of the passivation phase.

The result shows that during stress phase,  $\Delta V_{th}$  measured by fast pulsed measurement is much higher than that by DC method (about 100mV larger for -2.4V stress at 100°C for 1000s). On the other hand, during passivation phase, the difference in  $V_{th}$  shift between fast pulsed measurement and DC measurement diminishes quickly. This indicates that there is a distinctive fast component in the observed NBTI result. From Fig.4-4, one can estimate that the recovery time constant of this fast component is less than 0.1s. The pulsed measurement method captures both the fast and slow components, while the slow DC measurement measures only the slow component since its inevitable delay between stress and measurement, which is much greater than 0.1s. Therefore, the difference between  $V_{th}$  shift measured by fast pulsed method and DC method ( $\Delta V_{th,pulse}$ - $\Delta V_{th,DC}$ ) can be used as an estimation of the fast component, as shown in Fig.4-6(b).

Fig.4-7 Measured  $\Delta V_{th}$  due to DNBTI using DC method and fast pulsed method (using R edge to measure the accumulation degradation at P).

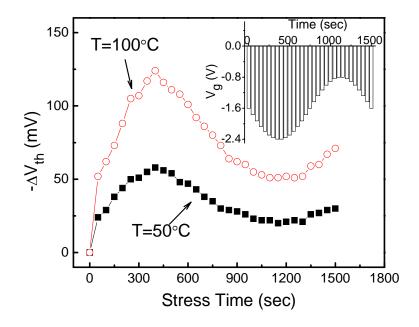

Using rising edge to measure the accumulation degradation at point P by a 100Hz DNBTI stress got Fig.4-7. The point in the circle is the result of fast pulsed measurement stop at 1000s and measured after 1s delay. The charge accumulated in  $N_{ot}$  in the stress phase is not completely de-trapped in the passivation phase. Hence, there is a net charge accumulation and  $N_{ot}$  contributes to an additional DNBTI degradation.

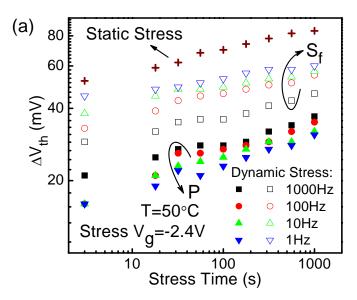

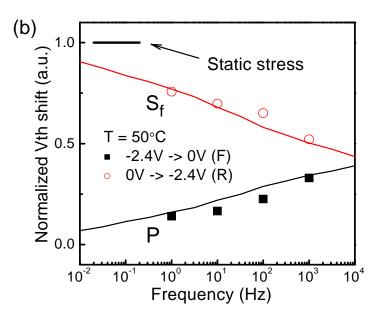

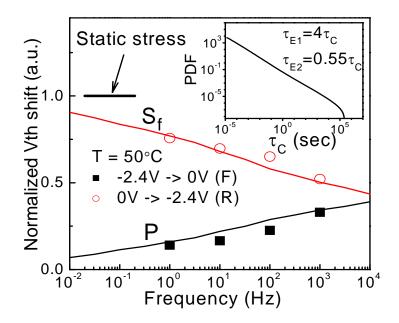

Fig.4-8 explores the frequency dependence of  $\Delta V_{th}$  as measured using the fast pulsed method at the end of the stress phase (point  $S_f$ ) and at the end of the passivation phase (point P). As shown in Fig.4-8(a),  $\Delta V_{th}$  at  $S_f$  (open symbols) and P (solid symbols) were measured at the falling and rising edges, respectively. Stresspassivation cycles determined by the frequencies are repeated so as to get total stress time of 1000s. At point P of each stress cycle, a net charge accumulation which increases with increasing stress time can be observed. This also proves that the charge cumulated in  $N_{ot}$  in the stress phase is not completely de-trapped in the passivation phase and  $N_{ot}$  contributes to an additional DNBTI. The  $V_{th}$  degradation due to the fast component is also a cumulative process.

Fig.4-8 (a) Stress pulse frequency dependence of  $\Delta V_{th}$  due to DNBTI as measured by fast pulsed method. (b) Stress pulse frequency dependence of the fast DNBTI component. The difference between  $S_f$  point and P point represents the transient amplitude of  $\Delta V_{th}$  indicated in Fig.4-6(a).

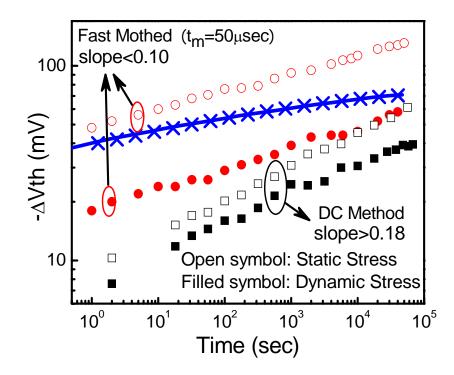

Fig.4-8(b) shows that the transient amplitude ( $\Delta V_{th, Sf}$ - $\Delta V_{th, P}$ ) under dynamic stress is reduced and approaches zero when the frequency is increased. This implies that if the device is working under a very high frequency, little transient effect is expected. On the other hand, DNBTI measured by DC method shows frequency independent behavior as reported in [3]. The same experiment was repeated in SiON samples in this experiment and same conclusion can be drawn from the result. This implies that the fast component and the slow component in NBTI or DNBTI have different origins. According to different results from this frequent dependence experiment, slow component can be attribute to the generation and passivation of interface traps as proposed in [6]-[8], which fits well with the reaction-diffusion model and shows frequency independent; while the fast DNBTI component can be attributed to the trapping and de-trapping at hole traps in SiON dielectric [4]. Measured  $\Delta V_{th}$  under dynamic and static stresses by fast pulsed and DC methods is shown in Fig.4-9. After 5x10<sup>5</sup>s stress, the measured  $V_{th}$  shift is around 130mV, still no degradation enhancement or saturation was observed. However, the experiment fit data of  $\Delta V_{th,pulse} - \Delta V_{th,slow}$ , shown as the "X" symbols, shows a saturation tendency at long stress time, implying the fast component might lose its dominance at very long stress time.

Fig.4-9 Measured  $\Delta V_{th}$  under dynamic and static stresses by fast pulsed and DC methods as stress time.

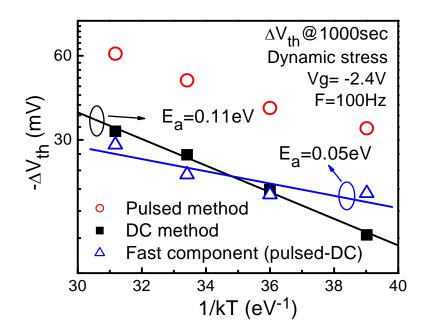

Temperature dependence measured by fast pulsed and DC methods under dynamic stress is shown in Fig.4-10. The slow component shows an activation energy ( $E_a$ ) of 0.11eV, while that of the fast component is only 0.05eV, much less temperature dependent. In addition, at very high temperature, the slow component can be even more significant than the fast component as shown in Fig.4-10.

Fig.4-10 Temperature dependence by fast pulsed and DC methods under dynamic stress (measured at P).

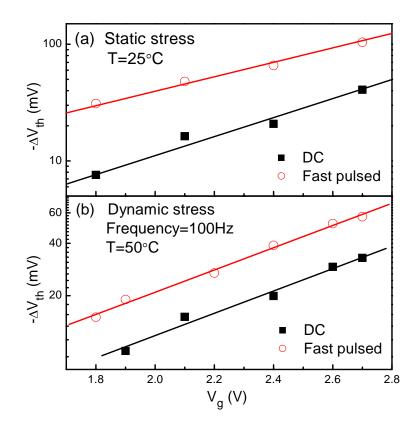

Fig.4-11  $\Delta V_{th}$  of p-MOSFET as different stress V<sub>g</sub> as measured by both fast pulsed method and DC method under: (a) static and (b) dynamic NBTI stress.

The stress voltage dependence is shown in Fig.4-11. Both static and dynamic NBTI stresses with different stress  $V_g$  were applied in the experiment.  $\Delta V_{th}$  measured by both DC and fast pulsed methods shows exponential dependence on stress  $V_g$ .

#### 4.3 Modeling of fast DNBTI component in SiON gate dielectric

The fast DNBTI component in SiON gate dielectric can be simulated using the following equations of trapping and de-trapping of the pre-existing hole traps  $N_{ot}$  [11] in bulk gate dielectric:

$$\frac{dp}{dt} = \frac{1}{\tau_C} (N_{ot} - p) - \frac{1}{\tau_{E1}} p$$

$$\frac{dp}{dt} = -\frac{1}{\tau_{E2}} p$$

(1)

(2)

where p is the trapped hole concentration;  $N_{ot}$  is the trap concentration, which has a wide distribution over trapping and de-trapping time constants  $\tau_C$  and  $\tau_E$  as shown in the inset of Fig.4-12.

Using (1) & (2), the simulated time evolutions of fast NBTI degradation are fitted to the experimental data. Fig.4-12 shows the frequency dependence of the fast DNBTI component ( $\Delta V_{th,pulse} - \Delta V_{th,DC}$  after 1000s stress) re-plotted on a normalized scale. Simulated results are plotted using solid lines, which are also in good agreement with the experimental data. The inset of Fig.4-12 shows the spectrum of trap concentration probability distribution function (PDF) over trapping and de-trapping time constants  $\tau_C$ and  $\tau_E$  employed in eq. (1) and (2). The continuous distribution of PDF is proposed to explain the power law of time evolution of NBTI degradation [9].

Fig.4-12  $\Delta V_{th}$  of p-MOSFET under static and dynamic NBTI stress (measured at *P*) as measured by both fast pulsed method and DC method.

The simulated time evolution of the fast components  $(\Delta V_{th,pulse} - \Delta V_{th,DC})$  is also plotted in Fig.4-8(b) and Fig.4-9 using solid lines. The measured  $\Delta V_{th}$  trend agrees well with simulated  $N_{ot}$ .

### 4.4 Impact of the fast NBTI components on circuit applications

Fig.4-8 shows that the transient amplitude of  $\Delta V_{th}$  under dynamic stress is reduced and approaches zero when the frequency is increased. Therefore no transient effect is expected in the fast digital circuit applications.

For analog applications, a good example is shown in Fig.4-13. Device was stressed under an ultra-low frequency sine wave signal, and  $\Delta V_{th}$  was measured using the fast pulsed method every few seconds. Since the exponential  $\Delta V_{th}$ - $V_g$  relationship, the measured  $\Delta V_{th}$  is no longer a sine function. This would induce a non-linear signal distortion in ultra-low frequency large signal analog applications.

Fig.4-13  $\Delta V_{th}$  under a sine wave  $V_g$  stress, measured  $\Delta V_{th}$  is not a sine function of time.

As for the device lifetime, if the charge accumulated in  $N_{ot}$  in the stress phase is completely de-trapped in the passivation phase, there is no net accumulation and no effect on the DNBTI device life time. Otherwise there is a net charge accumulation and  $N_{ot}$  will contribute to additional DNBTI degradation. Fig.4-7 clearly shows that the later case is true.

Choosing  $\Delta V_{th}$ =30mV as the failure criterion, the device lifetime is re-estimated under dynamic NBTI stress. Both fast pulsed method and conventional DC method were used, and the result is plotted in Fig.4-14. The DC method overestimates the device lifetime at high stress voltage  $V_g$ . However, with stress  $V_g$  decreasing and stress time increasing, the slow DNBTI component becomes more significant. Therefore, when doing the lifetime extrapolation to 10 years' time, the DC method is still valid to predict the device lifetime.

Fig.4-14 Device lifetime re-evaluated under dynamic stress. The fast DNBTI component affects the device lifetime at high voltage.

### **Reference:**

- [1] C. Shen, M. F. Li, X. P. Wang, H. Y. Yu, Y. P. Feng, A. T.-L. Lim, Y. C. Yeo, D. S. H. Chan, and D. L. Kwong, "Negative U traps in HfO<sub>2</sub> gate dielectrics and frequency dependence of dynamic BTI in MOSFETs," in *IEDM Tech. Dig.*, 2004, pp.733-736.

- [2] A. Kerber, E. Cartier, L.A. Ragnarsson, M. Rosmeulen, L. Pantisano, R. Degraeve, T. Kauerauf, G. Groeseneken, H.E. Maes and U. Schwalke, "Characterization of the V<sub>T</sub>-instability in SiO<sub>2</sub>/HfO<sub>2</sub> gate dielectrics," in *Proc. IEEE Reliab. Phys. Symp.*, 2003, pp.41-45.

- [3] G. Chen, M. F. Li, C. H. Ang, J. Z. Zheng, and D. L. Kwong, "Dynamic NBTI for p-MOS transistors and its impact on MOSFET scaling," *IEEE Electron Device Lett.*, Vol.23, pp.734-736, 2002.

- [4] V. Huard, M. Denais, "Hole trapping effect on methodology for DC and AC negative bias temperature instability measurements in PMOS," in *Proc. IEEE Reliab. Phys. Symp.*, 2004, pp.40-45.

- [5] G. Chen, K. Y. Chuah, M. F. Li, Daniel SH Chan, C. H. Ang, J. Z. heng, Y. Jin and D. L. Kwong, "Dynamic NBTI of PMOS transistor and its impact on device lifetime," in *Proc. IEEE Reliab. Phys. Symp.*, 2003, pp.196-202.

- [6] M. A. Alam, "A critical examination of the mechanics of dynamic NBTI for PMOSFETs," in *IEDM Tech. Dig.*, 2003, pp. 345-348.

- [7] S. Mahapatra, M. A. Alam, P. Bharath Kumar, T. R. Dalei and D. Saha, "Mechanism of negative bias temperature instability in CMOS devices: degradation, recovery and impact of nitrogen," in *IEDM Tech. Dig.*, 2004, pp.105-108.

- [8] S. Chakravarthi, A. T. Krishnan, V. Reddy, C. F. Machala and S. Krishnan, "A comprehensive framework for predictive modeling of negative bias temperature instability," in *Proc. IEEE Reliab. Phys. Symp.*, 2004, pp.273-282.

- [9] S. Zafar, A. Callegari, E. Gusev, M. V. Fischetti, "Charge trapping in high-κ gate dielectric stacks," in *IEDM Tech. Dig.*, 2002, pp.517-520.

## Part II

### Advanced passive devices and their application

### in circuits

### **Chapter Five**

### **Proton implanted high-Q inductors**

#### 5.1 Introduction

The on-chip inductors are one of the most important components for implementation of RF circuits in CMOS. Due to the lossy nature of Si substrate, the quality factor of CMOS on-chip inductors is low, which has become one of the fundamental barriers of Si VLSI [1]-[6]. There are many techniques reported in the literature to enhance the quality factor of the inductors. These include (i) use of high resistivity silicon substrate, (ii) removal of silicon substrate by micromachining techniques, (iii) use of very thick dielectric layers below the spiral inductors, and (iv) use of high energy proton implantations as a post processing add-on step[4]-[9].

In this chapter, the role of proton implantation in enhancing the Q-factor of inductors has been investigated. The DC resistance of the inductor spirals has been measured for the spirals without proton implantation as well those had undergone the proton implantation. Open pads have been modeled to investigate the influence of proton implantation on the bulk silicon resistivity. The inductors in two cases are both modeled. The improved inductor quality factor results are interpreted in terms of enhanced substrate resistivity by proton implantation.

#### 5.2 Experiments

Circular spiral inductors having turns from 1 to 8 and with two internal diameters of 75µm and 100µm were used in this study. The width of the spiral was 6µm and 10µm respectively in the two cases. A small piece of wafer with the inductors was implanted with high energy protons. The DC resistance of the inductors with and without proton implantation was measured.

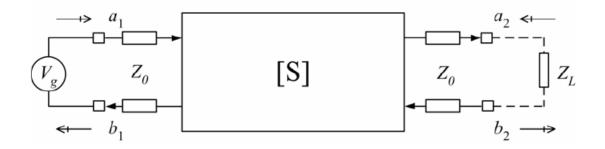

For RF characterization, Scattering Parameters (or S-parameters) are essential for practical system characterization in RF regime. S-parameters, which are the reflection and transmission coefficients between the incident and reflection waves, describe completely the behavior of a device under linear conditions at microwave frequency range. Each parameter is typically characterized by magnitude, decibel and phase. The wave functions used to define S-parameters are shown in Fig.5-1 [10] [11].

Fig.5-1 Wave functions used to define S-parameters for a two-port network.

Here  $\alpha_n$  and  $b_n$  (n = 1, 2) are the normalized incident and reflected power waves. The definition equations of S-parameter as shown below:

$$\begin{cases} b_1 \\ b_2 \end{cases} = \begin{bmatrix} S_{11} & S_{12} \\ S_{21} & S_{22} \end{bmatrix} \cdot \begin{cases} a_1 \\ a_2 \end{cases}$$

5.1

where,

$$\begin{cases} a_n = (1/2\sqrt{Z_0}) \times (V_n + Z_0 I_n) \\ b_n = (1/2\sqrt{Z_0}) \times (V_n - Z_0 I_n) \end{cases}$$

5.2

For a two port network using matched loads  $Z_0=Z_L=50\Omega$ ,  $S_{11}$  is the reflection coefficient of the input,  $S_{22}$  is the reflection coefficient of the output,  $S_{21}$  is the forward transmission gain, and  $S_{12}$  is the reverse transmission gain (from output to input).

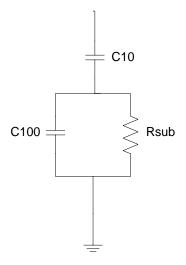

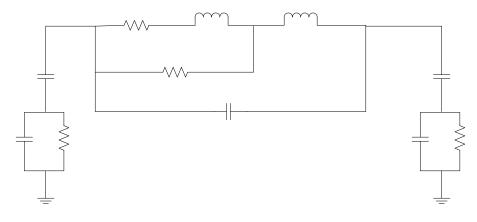

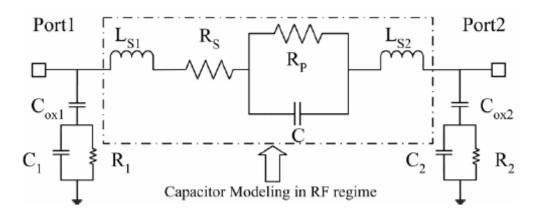

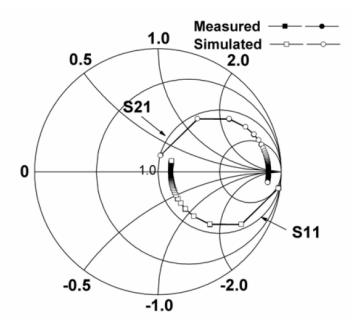

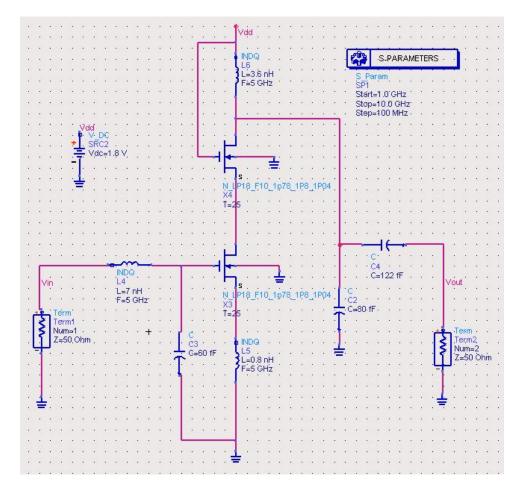

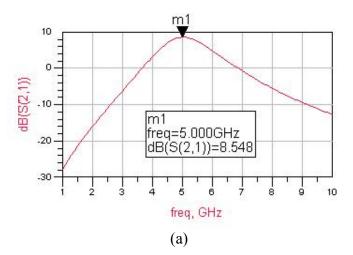

One-port S-parameters of open pads were modeled using the equivalent circuit shown in Fig.5-2. The equivalent circuit shown in Fig.5-3 was used to model the inductors. In this experiment, S-parameters of the inductors together with the open pads were measured from 50 MHz to 10 GHz using HP 8510C network analyzer with the GGB's air coplanar probes (ACP) for ground-signal-ground (GSG) configuration.

Fig.5-2 Equivalent RF modeling circuit of the open pad.

Fig.5-3 Equivalent RF modeling circuit of the inductor.

### 5.3 Results and discussion on the impact of proton implantation

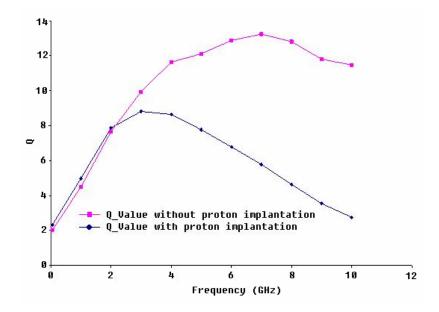

Fig.5-4 plots the Q values of the inductors as a function of frequency for a 5 and a half turns inductor for the two cases, namely, (i) without proton implantation and (ii) with proton implantation. There is significant improvement in the Q values in case (ii).

Fig.5-4 Q-Value w/ and w/o proton implantation over frequency (c75n5p5)

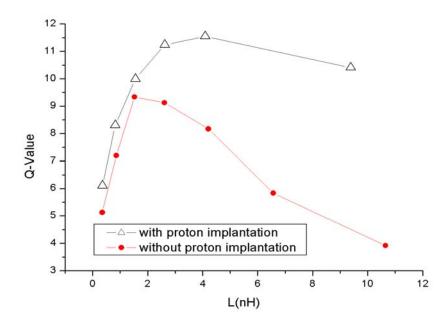

Fig.5-5 Q-Value w/ and w/o proton implantation @5GHz

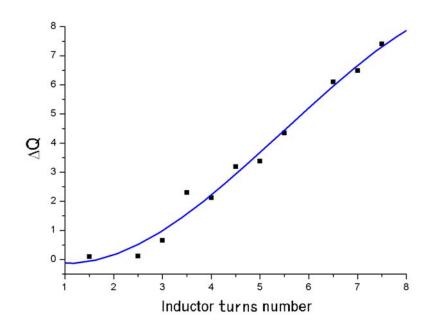

Fig.5-5 shows the Q-value with and without proton implantation as a function of inductance values. One observes more improvement in quality factor for larger inductance values. Fig.5-6 shows the improvement  $\Delta Q$  as a function of number of turns. More improvement was achieved with larger number of turns, or inductors with larger area.

Fig.5-6  $\Delta Q$  enhanced by post proton implantation on different scales @5GHz

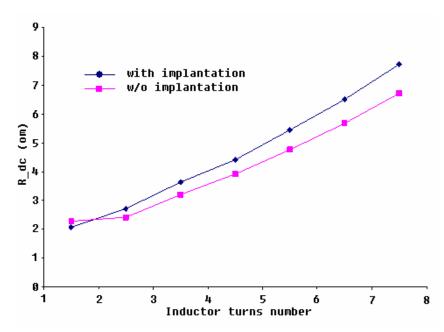

Fig.5-7 DC resistance of the metal spirals w/ and w/o post proton implantation

To investigate the influence of proton implantation on the resistance of metal spirals, the DC resistance of the coils was measured through IV characteristics. Fig.5-6 shows the results. There is no significant change in the DC resistance of the coils as a result of proton implantation.

To investigate the influence on the substrate, one-port S-parameters of open pads were modeled by the equivalent circuit shown in Fig.5-2. The extracted value of substrate resistance – before and after implantation – is indicative of the effect of proton implantation. The substrate resistivity appears to be improved by almost one order of magnitude after proton implantation, while the parasitic capacitors were remained almost the same (as shown in Table. 1-1).

|      | w/o Imp | w Imp |

|------|---------|-------|

| C10  | 110fF   | 100fF |

| C100 | 40fF    | 34fF  |

| Rsub | 210Ω    | 2310Ω |

Table.5-1 Substrate parameters of the inductors w/ and w/o post proton implantation

For inductors with small area, the increased substrate resistance does not have very large influence; however, for the larger inductors, this increment is very significant since the substrate loss plays a more significant role in quality factor degradation.

In conclusion, post fabricated proton implantation can increase the substrate resistance significantly, resulting in enhanced Q-value of inductor. This enhancement is significant for the inductors whose value is greater than 2nH and which occupies larger silicon area.

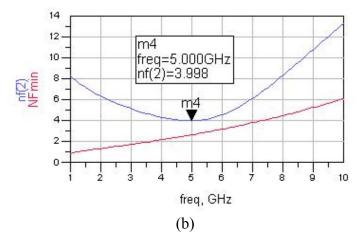

### **Reference:**