# BED OF NAILS (BON) – 100 MICRONS PITCH WAFER LEVEL OFF-CHIP INTERCONNECTS FOR MICROELECTRONIC PACKAGING APPLICATIONS

VEMPATI SRINIVASA RAO

NATIONAL UNIVERSITY OF SINGAPORE 2005

## **BED OF NAILS (BON) – 100 MICRONS PITCH WAFER LEVEL**

### **OFF-CHIP INTERCONNECTS FOR MICROELECTRONIC**

## PACKAGING APPLICATIONS

VEMPATI SRINIVASA RAO (B.TECH)

A THESIS SUBMITTED

FOR THE DEGREE OF MASTER OF ENGINEERING

DEPARTMENT OF MECHANICAL ENGINEERING

NATIONAL UNIVERSITY OF SINGAPORE

### ACKNOWLEDGEMENT

I would like to take this opportunity to express my heartfelt gratitude and appreciation to my project supervisors –Prof. Tay Andrew A. O., Assoc. Prof. Lim Chwee Teck and Dr. Vaidyanathan Kripesh for their guidance throughout my project. Special thanks to Dr. Vaidyanathan Kripesh for his invaluable advice, motivation and encouragement which enabled me to finish my project amidst all difficulties.

I am grateful to the IME Staff- Dr. Seung Wook Yoon, Mr. Ranganathan N, Mr. Kum Weng, Mr. Ranjan Rajoo, Mr. Chong Ser Choong, Mr. Samule, Miss. Hnin Wai Yin, Mr. Mark Lam T W and Mr. David for their kind support and assistance.

I would also like to thank my beloved parents and brothers for their love and affection and also my colleagues, M. Shanthi and others who have showered their love towards me during this needful time.

## TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                                                        | i    |

|-------------------------------------------------------------------------|------|

| TABLE OF CONTENTS                                                       | ii   |

| SUMMARY                                                                 | vi   |

| LIST OF FIGURES                                                         | viii |

| LIST OF TABLES                                                          | xii  |

| CHAPTER 1 INTRODUCTION                                                  | 1    |

| CHAPTER 2 LITERATURE REVIEW                                             | 5    |

| 2.1 Introduction to Microelectronics Packaging                          | 5    |

| 2.2 Hierarchies of IC packaging                                         | 7    |

| 2.3 Historical development of packaging technology                      | 8    |

| 2.4 Challenges to microelectronics packaging                            | 12   |

| 2.5 Wafer level packaging (WLP) technology                              | 15   |

| 2.6 Compliant wafer level interconnects                                 | 19   |

| 2.6.1 Tessera's $\mu$ BGA and WAVE <sup>TM</sup> packaging technologies | 20   |

| 2.6.2 FormFactor Microspring <sup>TM</sup> Contacts                     | 23   |

| 2.6.3 Sea-of-Leads (SoL) interconnects                                  | 24   |

| 2.6.4 Cantilevered spring interconnects                                 | 26   |

| 2.6.5 Helix-type interconnects                                          | 28   |

| 2.7 Challenges in wafer level packaging                                 | 29   |

| 2.8 Scope of the project                                                | 30   |

| CHAPTER 3 EXPERIMENTAL DETAILS                                           | 32 |

|--------------------------------------------------------------------------|----|

| 3.1 Materials                                                            | 32 |

| 3.2 Equipments                                                           | 33 |

| 3.2.1 Sputtering machine                                                 | 33 |

| 3.2.2 Spin coater track                                                  | 34 |

| 3.2.3 Mask aligner                                                       | 34 |

| 3.2.4 Copper electroplating tool                                         | 35 |

| 3.2.5 Solder plating tool                                                | 36 |

| 3.2.6 Scanning electron microscope (SEM)                                 | 37 |

| 3.2.7 Convection heating Oven                                            | 37 |

| 3.2.8 Wet bench                                                          | 38 |

| 3.2.9 Spin rinse dryer                                                   | 38 |

| 3.2.10 Plasma thermo etching system or Reactive Ion Etching system (RIE) | 38 |

| 3.2.11 Solder reflow oven                                                | 38 |

| 3.2.12 Dicing machine                                                    | 38 |

| 3.2.13 Flip-Chip bonder                                                  | 39 |

| 3.2.14 X-ray system                                                      | 40 |

| 3.2.15 Thermal cycling furnace                                           | 40 |

| 3.2.16 Bump shear tester                                                 | 40 |

| 3.2.17 Die shear tester                                                  | 41 |

iii

# CHAPTER 4 BED OF NAILS (BoN) INTERCONNECTS CONCEPTUAL42DESIGN AND FABRICATION PROCESS DEVELOPMENT42

| 4.1 Conceptual Design                                                           | 42 |

|---------------------------------------------------------------------------------|----|

| 4.2 Design Concerns                                                             | 42 |

| 4.2.1 Functional concerns                                                       | 42 |

| 4.2.2 Material concerns                                                         | 44 |

| 4.3 Design of BoN interconnect                                                  | 45 |

| 4.4 Fabrication process development                                             | 46 |

| 4.4.1 BoN Wafer Level Interconnects Fabrication Process                         | 48 |

| 4.4.1(a) Single layer BoN Wafer Level Interconnects Fabrication Process<br>Flow | 48 |

| 4.4.1 (b) Three layer BoN Wafer Level Interconnects Fabrication Process<br>Flow | 50 |

| 4.5 Selection criteria for interconnect design                                  | 52 |

| 4.5.1 Cost                                                                      | 52 |

| 4.5.2 Mechanical properties                                                     | 53 |

| 4.5.3 Electrical properties                                                     | 53 |

| 4.5.4 Processibility                                                            | 54 |

| 4.5.5 Yield                                                                     | 54 |

| 4.5.6 Environmental susceptibility                                              | 55 |

| 4.5.7 Reworkability                                                             | 55 |

| CHAPTER 5 TEST CHIP DEMONSTRATOR DESIGN AND FABRICATION                         | 57 |

| 5.1 BoN test chip and mask layout Design                                        | 57 |

| 5.2 Test chip fabrication                                                       | 60 |

| 5.2.1 Metal pads patterning and their passivation                               | 60 |

| 5.2.2 Thick resist process for single Column BoN interconnects fabrication | 64  |

|----------------------------------------------------------------------------|-----|

| 5.2.2 (a) SU-8 Photoresist                                                 | 65  |

| 5.2.2 (b) JSR Photoresist                                                  | 68  |

| 5.2.3 Copper and solder plating                                            | 73  |

| 5.2.4 Thick photoresist stripping                                          | 77  |

| 5.2.4 (a) SU-8 resist stripping                                            | 77  |

| 5.2.4 (b) JSR resist stripping                                             | 78  |

| 5.2.5 Solder reflow                                                        | 79  |

| 5.3 Solder bump fabrication                                                | 83  |

| 5.4 Bump shear test                                                        | 83  |

| CHAPTER 6 ASSEMBLY, RELIABILITY AND FAILURE ANALYSIS                       | 87  |

| 6.1 Introduction                                                           | 87  |

| 6.2 Test board design                                                      | 87  |

| 6.3 Assembly process                                                       | 89  |

| 6.3.1 Assembly process optimization for 10mmx10mm test chip                | 90  |

| 6.3.2 Assembly process optimization for 20mmx20mm test chip                | 97  |

| 6.4 Die shear test                                                         | 99  |

| 6.5 Reliability                                                            | 100 |

| 6.5.1 Failure analysis                                                     | 102 |

| CHAPTER 7 CONCLUSIONS                                                      | 106 |

| REFERENCES                                                                 | 108 |

### SUMMARY

The demand for interconnection density both on integrated circuit (IC) and packages increases tremendously as microsystems continue to move towards high speed and microminiaturization technologies. In order to meet the silicon device performance, number of I/Os needs to increase by 15% every year and the cost per pin needs to decrease by 10% every year to match the silicon productivity and cost. In the near future, the necessity for higher I/O count, 10,000 per IC chip requiring fine pitch of <100µm would increase as the IC technology shift towards the nano ICs with feature size of <90nm. In current approaches for chip-to-package interconnections at fine pitch solder interconnects number of limitations was observed. The main failure in these solder interconnects are due to the CTE mismatch between the Si chip and substrate. Especially in fine pitches, assembly yield and process costs are found to be higher due to the low stand off height and less solder volume. Thus, the present interconnection technologies cannot meet the essential requirements of reliability, cost, performance and manufacturability. Hence, in this present work, a new technology namely Bed of Nails (BoN) interconnections was conceived, designed, fabricated and tested to meet the above requirements. The fabrication uses conventional wafer level process, hence it is convenient to mass produce these interconnects. This work also highlights the challenges in high aspect ratio lithography process (50µm diameter and 100-130µm height) and electroplating of copper nails.

The test chips were designed and fabricated based on the optimized process developed. Two different test chips of 10 mm  $\times$  10 mm and 20 mm  $\times$  200 mm sizes were fabricated. The fabricated test chip with BoN interconnects was assembled on

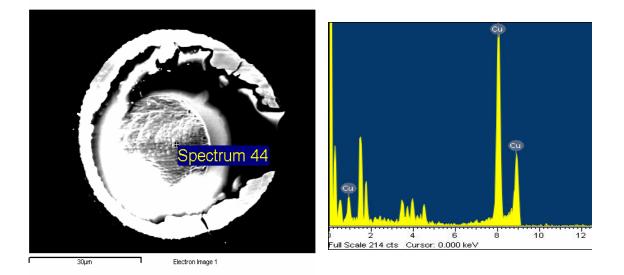

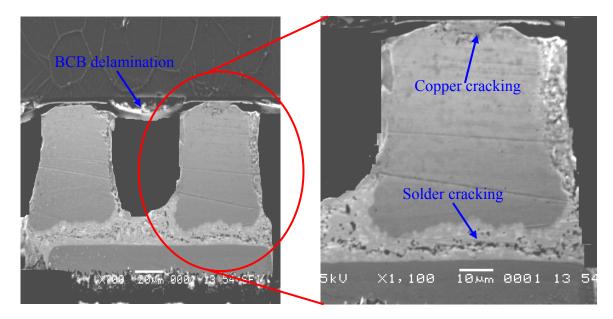

conventional test board using Karl-Suss flip chip bonder (FC-150). This interconnects were subjected to thermal cycle test as per the JEDEC standards. Results obtained clearly showed that BoN interconnects are at least better by a factor two compared to the conventional solder interconnects. Failure modes of the samples were analyzed using scanning electron microscopy and major failures were observed in the bulk solder. These failures can be further reduced by using solder of better properties. The wafer level interconnects Bed of Nails developed in this study can be implemented for fine pitch interconnect schemes between Si chip and substrate.

## LIST OF FIGURES

| Figure 2.1 Hierarchy of electronic packaging                                                                      | 8  |

|-------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.2 Packaging trends                                                                                       | 11 |

| Figure 2.3 Cross sectional view of Fujitsu's Super CSP                                                            | 16 |

| Figure 2.4 Cross sectional view of the Shellcase WL-CSP                                                           | 18 |

| Figure 2.5 Cross sectional view of Amkor ws-CSP package                                                           | 18 |

| Figure 2.6 Schematic representation of fundamental components of $\mu$ BGA package                                | 21 |

| Figure 2.7 Schematic representation of cross section and 3-D view of WAVE <sup>TM</sup> package                   | 22 |

| Figure 2.8 SEM micrograph showing Microspring contacts or interconnects (MOST <sup>TM</sup> ) array by FormFactor | 24 |

| Figure 2.9 SEM micrograph of SoL interconnects                                                                    | 25 |

| Figure 2.10 SEM micrograph of Ultra-fine pitch nanospring interconnects                                           | 27 |

| Figure 2.11 SEM micrographs of $\beta$ -Helix interconnects                                                       | 29 |

| Figure 3.1 (a) Schematic diagram of principle of electroplating                                                   | 36 |

| Figure 3.1 (b) Photograph of 8 inch wafer copper plating tool                                                     | 36 |

| Figure 3.2 (a) and (b) Photographs of rack type solder plating tool for 8inch wafer                               | 37 |

| Figure 3.3 Photograph of Karl-Suss flip chip bonder                                                               | 39 |

| Figure 3.4 Photograph of Dage X-ray system                                                                        | 40 |

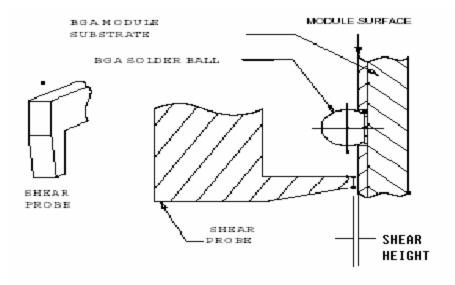

| Figure 3.5 Schematic diagram of bump shear test                                                                   | 41 |

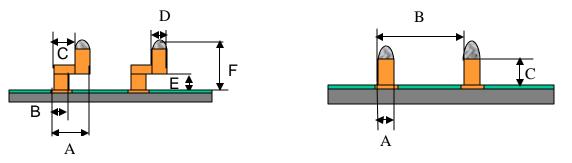

| Figure 4.1 Geometric representation of Bed of Nails interconnects                                                 | 46 |

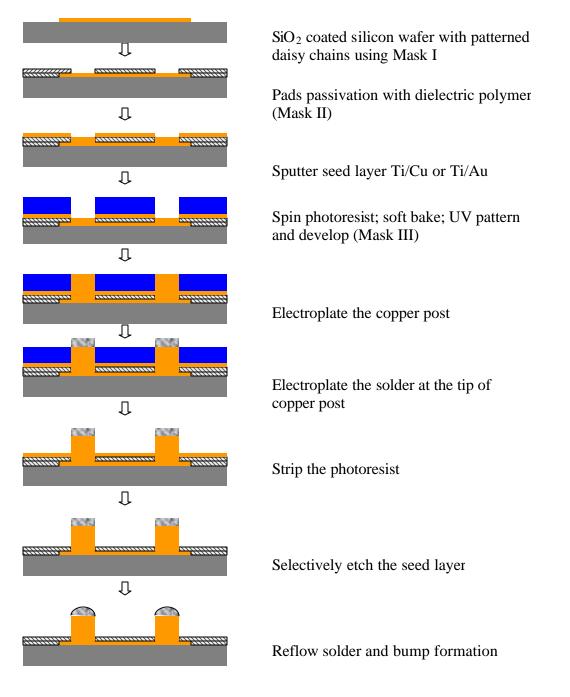

| Figure 4.2 Fabrication Process flow chart of Single Layer BoN Wafer Level<br>Interconnections                     | 49 |

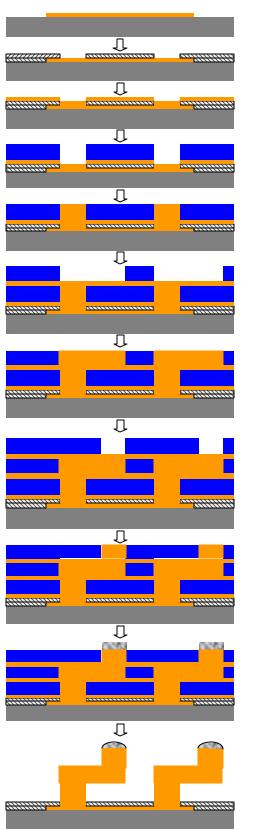

| Figure 4.3 Fabrication Process Flow chart Three Layer BoN Wafer Level<br>Interconnections                         | 51 |

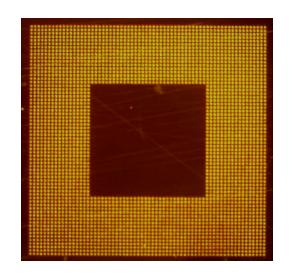

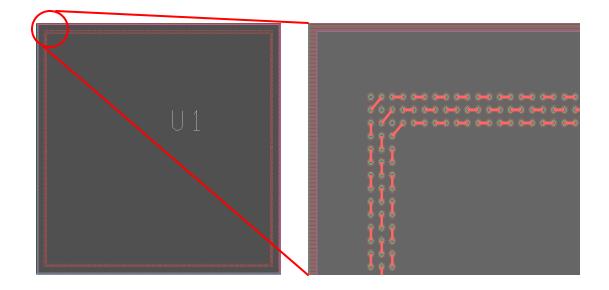

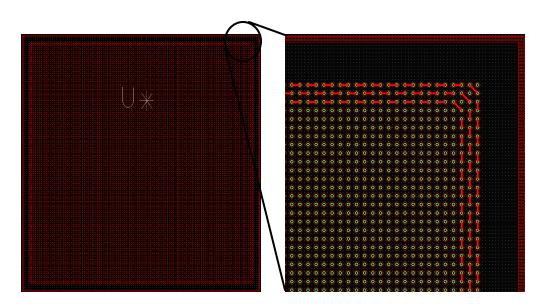

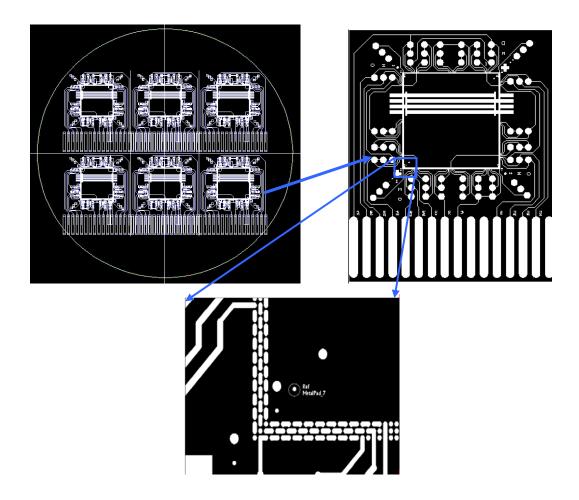

| Figure 5.1 Chip design of 10mm X 10mm size with 3332 I/Os in 17 depopulated rows                                                    | 58 |

|-------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 5.2 Chip design of 20mm X 20mm size with 2256 I/Os in 3 depopulated rows                                                     | 59 |

| Figure 5.3 Chip design of 20mm X 20mm size with 36481 I/Os as fully depopulated                                                     | 59 |

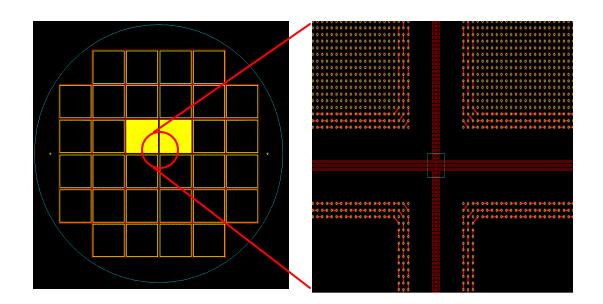

| Figure 5.4 Layout design of complete mask (7") with 20mm X 20mm chip design                                                         | 60 |

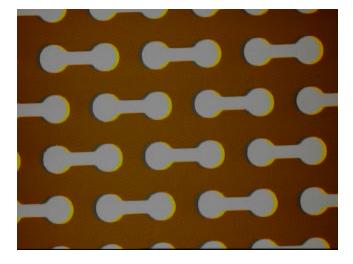

| Figure 5.5 Optical micrograph of the patterned metal pads with daisy chains                                                         | 61 |

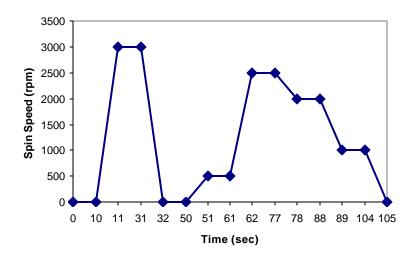

| Figure 5.6 AP3000 primer and BCB dielectric material coating cycle                                                                  | 62 |

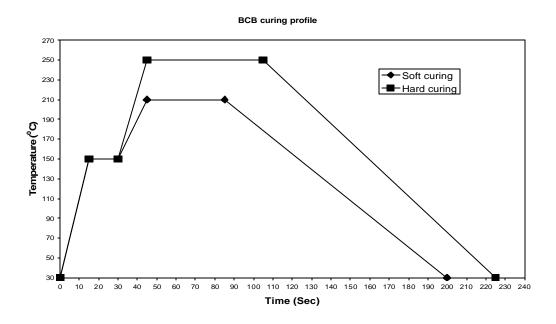

| Figure 5.7 BCB soft and hard curing profiles                                                                                        | 63 |

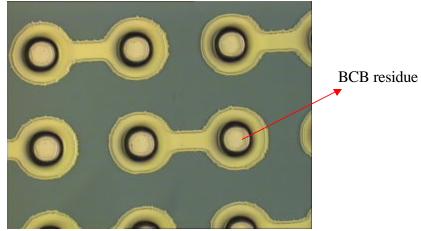

| Figure 5.8 Optical micrograph of patterned BCB before descum                                                                        | 64 |

| Figure 5.9 Optical micrograph of patterned BCB after descum                                                                         | 64 |

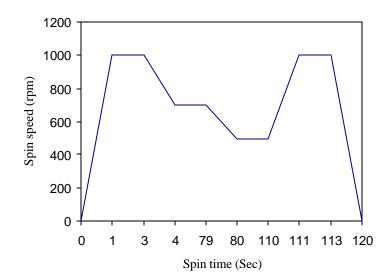

| Figure 5.10 Spin cycle for 50µm thick SU-8 resist coating                                                                           | 66 |

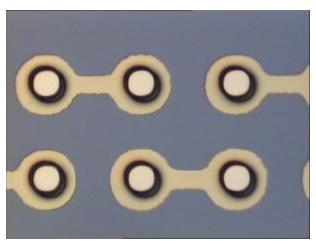

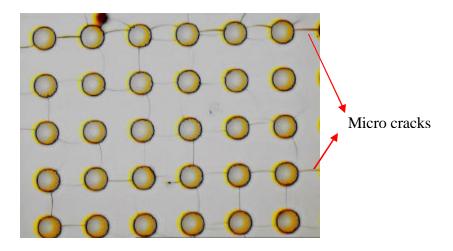

| Figure 5.11 SEM micrograph of planar view of 50µm thick patterned SU-8 photoresist with 50µm diameter holes (aspect ratio 1)        | 68 |

| Figure 5.12 Optical micrograph of patterned SU-8 resist with micro cracks                                                           | 68 |

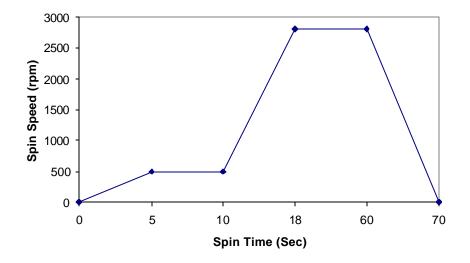

| Figure 5.13 Spin cycle for 65µm thick JSR resist coating on 8 inch wafer                                                            | 69 |

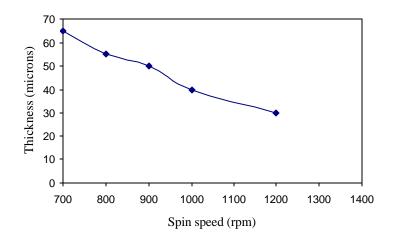

| Figure 5.14 Graph of Spin speed vs. thickness for JSR 151N resist on 8 inch wafer                                                   | 70 |

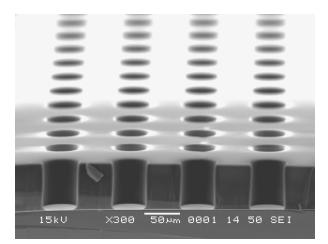

| Figure 5.15 SEM micrograph of planar view of 65µm thick pattrned JSR-151N photoresist with 50µm diameter holes (aspect ratio 1.3)   | 71 |

| Figure 5.16 SEM micrograph of planar view of 130µm thick patterned JSR-151N photoresist with 50µm diameter holes (aspect ratio 2.6) | 72 |

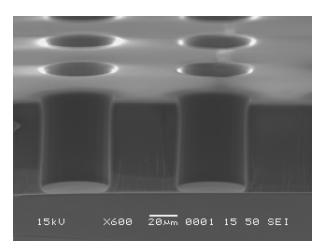

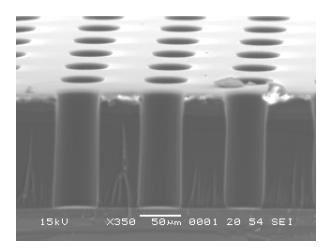

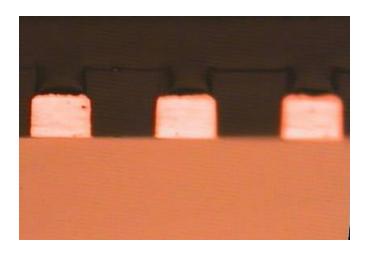

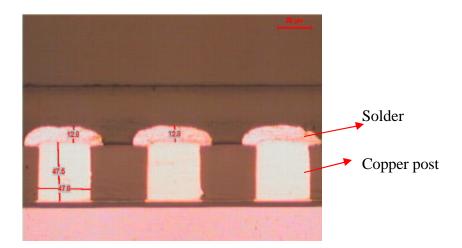

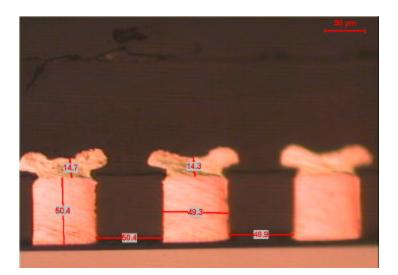

| Figure 5.17 Cross sectional view of copper filled vias in photoresist                                                               | 76 |

| Figure 5.18 Cross sectional view of 100µm pitch BoN interconnects in photoresist                                                    | 77 |

| Figure 5.19 Optical micrograph of SU-8 residues in between the BoN interconnects after stripping                                    | 78 |

| Figure 5.20 Optical micrograph of BoN interconnects after JSR resist stripping                                                      | 79 |

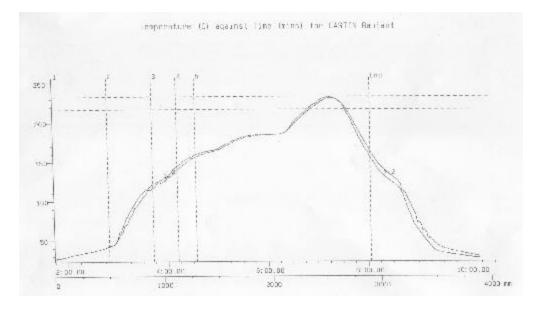

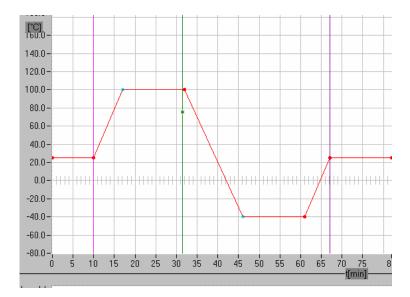

| Figure 5.21 Eutectic tin-lead solder reflow profile                                                                                 | 80 |

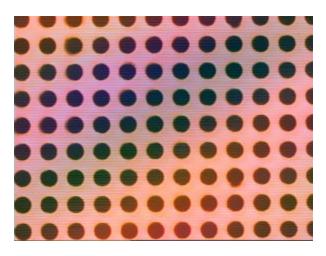

| Figure 5.22 Planar view of BoN interconnects before solder reflow                                        | 80 |

|----------------------------------------------------------------------------------------------------------|----|

| Figure 5.23 Cross-sectional view of BoN interconnects after one time solder reflow                       | 81 |

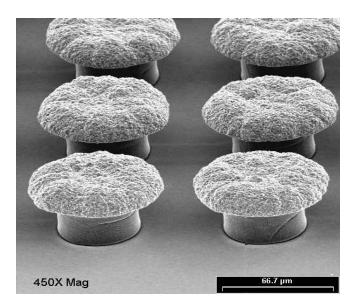

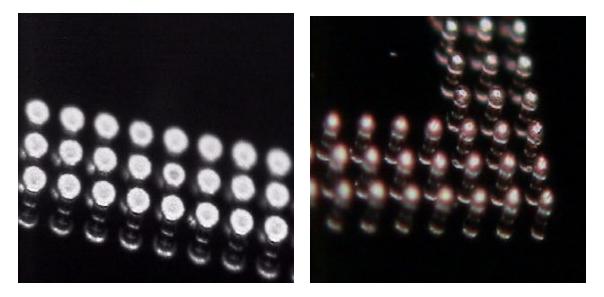

| Figure 5.24 Planar view of BoN interconnects after solder reflow using flux                              | 81 |

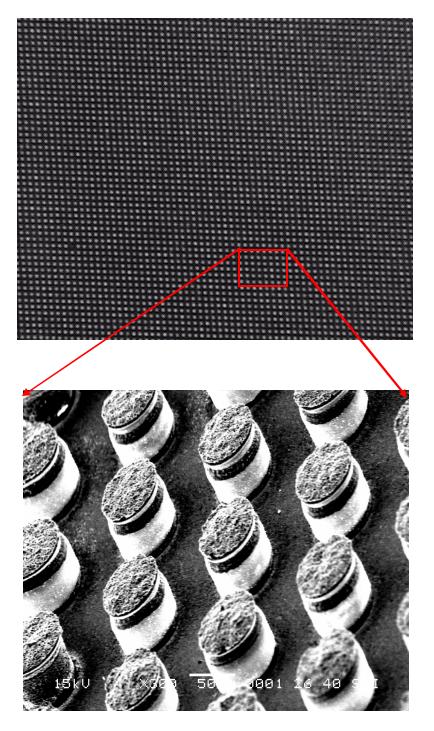

| Figure 5.25 SEM micrograph of area array of BoN interconnects on 20mmx20mm test chip                     | 82 |

| Figure 5.26 Electroplated eutectic tin-lead solder bumps before and after reflow                         | 83 |

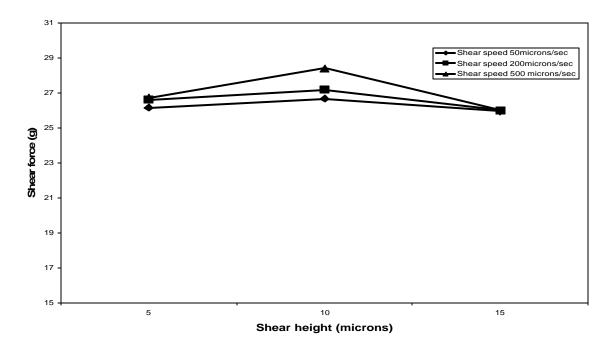

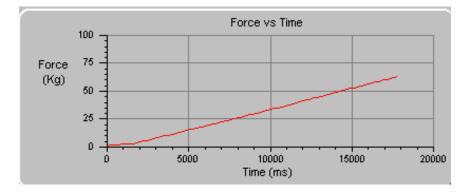

| Figure 5.27 Graph of Shear force vs. Shear height at constant shear speed                                | 85 |

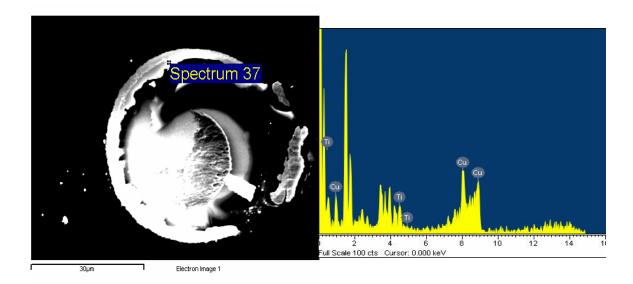

| Figure 5.28 SEM micrograph sheared bump pad and EDX graph at the center of sheared bump pad              | 85 |

| Figure 5.29 SEM micrograph sheared bump pad and EDX graph at the edge of sheared bump pad                | 86 |

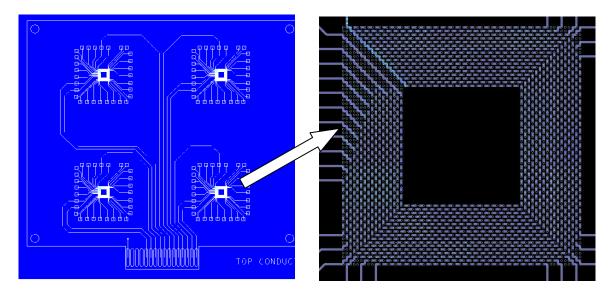

| Figure 6.1 Test board design for 10 mm X 10 mm test dies                                                 | 89 |

| Figure 6.2 Test board design for 20 mm X 20 mm test dies                                                 | 90 |

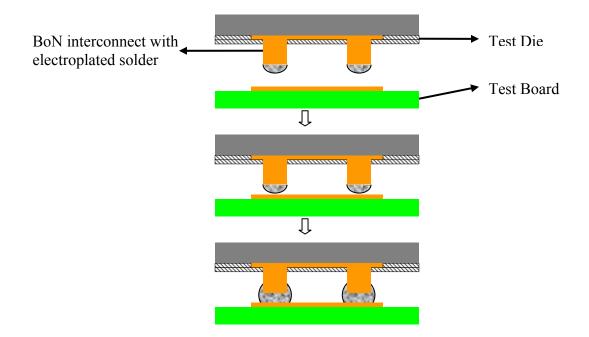

| Figure 6.3 Schematic Diagrame of BoN off-Chip interconnect assembly process                              | 91 |

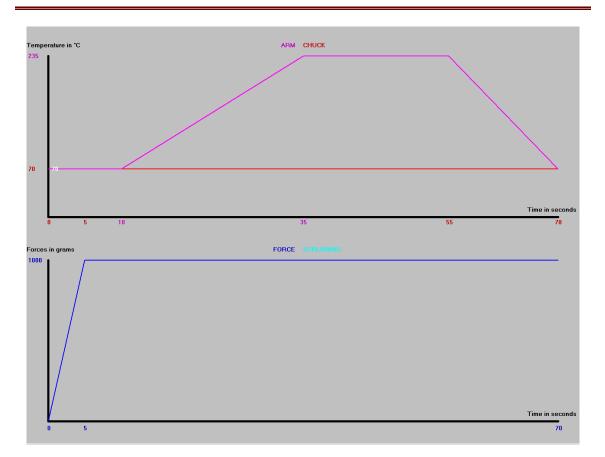

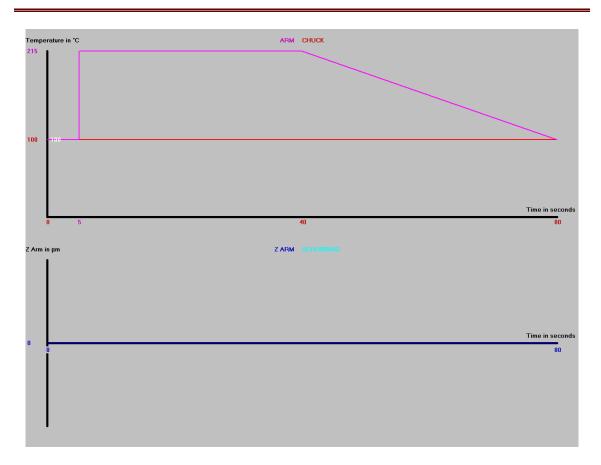

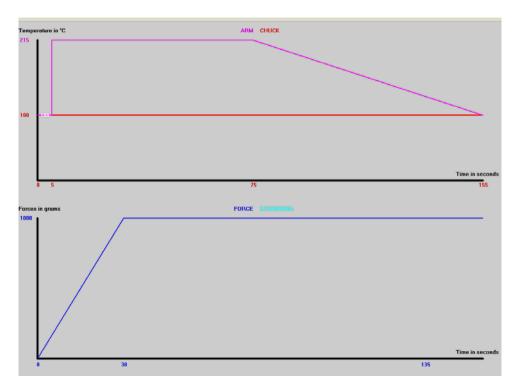

| Figure 6.4 Flip chip bonding profile with bonding force for 10mmx10mm test chip assembly                 | 92 |

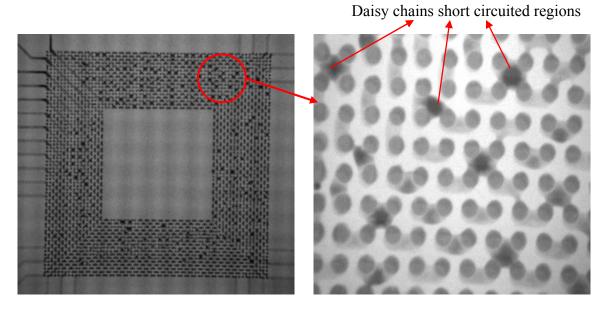

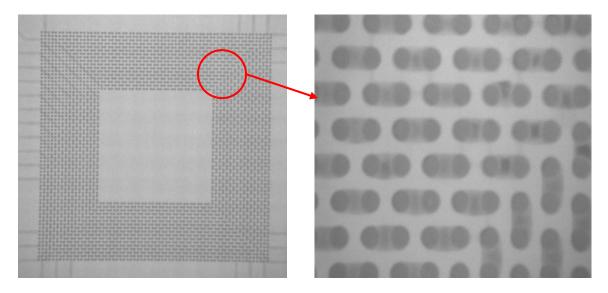

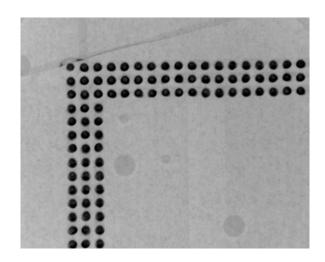

| Figure 6.5 X-ray scanning micrograph of assembled 10mmx10mm test chip<br>with daisy chain short circuits | 93 |

| Figure 6.6 X-ray scanning of assembled package in 3-D view                                               | 93 |

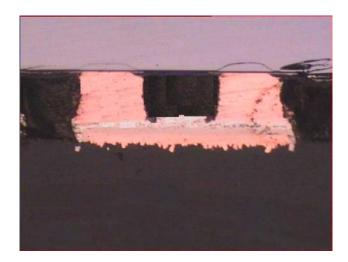

| Figure 6.7 Cross-sectional view of assembled 10mmx10mm test chip                                         | 94 |

| Figure 6.8 Flip chip bonding profile without bond force for 10mmx10mm test chip assembly                 | 95 |

| Figure 6.9 X-ray scanning micrograph of assembled 10mmx10mm test chip without daisy chain short circuits | 95 |

| Figure 6.10 Cross-sectional view of assembled 10mmx10mm test chip without bond force                     | 96 |

| Figure 6.11 Flip chip bonding profile with z-control for 10mmx10mm test chip assembly                    | 97 |

Х

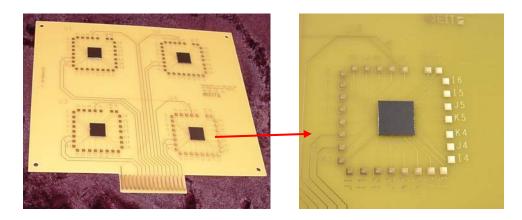

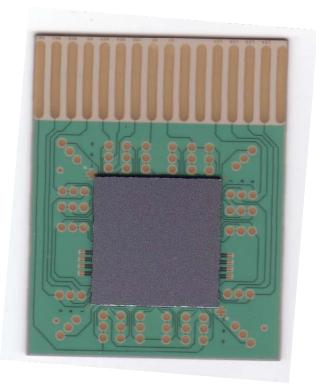

| Figure 6.12 Bed of Nails test demonstration on Conventional Board (CTE 18ppm/°C                                              | ) 97 |

|------------------------------------------------------------------------------------------------------------------------------|------|

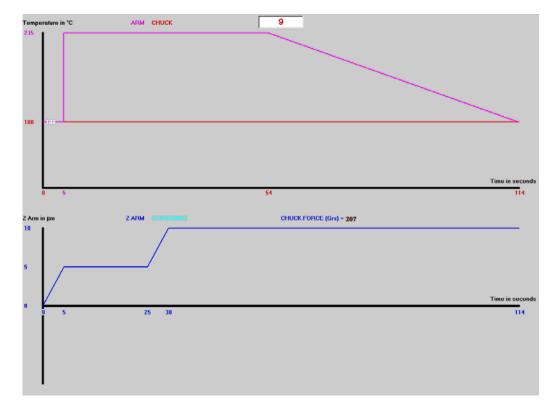

| Figure 6.13 Flip chip bonding profile with bonding force for 20mmx20mm test chip assembly                                    | 98   |

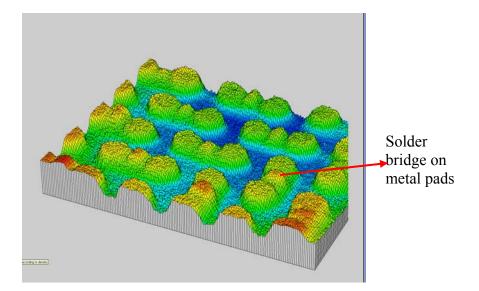

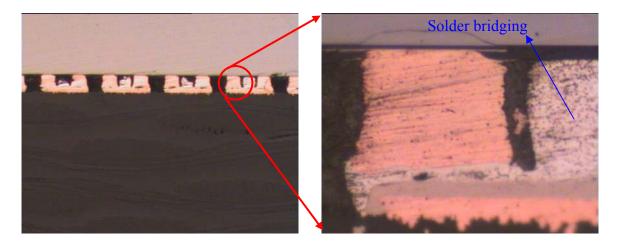

| Figure 6.14 X-ray scanning micrograph of assembled 20mmx20mm test chip withou daisy chain short circuits and solder bridging | t 99 |

| Figure6.15 20mmx20mm test chip demonstration on conventional board<br>(CTE 10ppm/°C)                                         | 99   |

| Figure 6.16 Die shear test result                                                                                            | 100  |

| Figure 6.17 Temperature profile for Thermal Cycle test                                                                       | 101  |

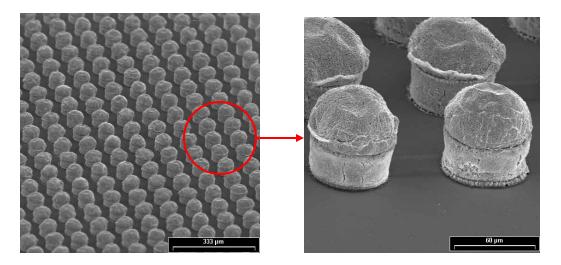

| Figure 6.18 SEM photograph of Cross section of failed interconnect after TC test                                             | 103  |

## LIST OF TABLES

| Table 1.1 | ITRS 2003 for Assembly and Packaging [ITRS 2003]                                          | 2   |

|-----------|-------------------------------------------------------------------------------------------|-----|

| Table 2.1 | Comparison of Commercial Wafer-Level package technologies                                 | 17  |

| Table 4.1 | Dimensions of Bed of Nails interconnect structures                                        | 46  |

| Table 4.2 | Simulated fatigue life data of the single and three layers BoN interconnects              | 53  |

| Table 4.3 | Simulated electrical properties of three layers BoN interconnect                          | 54  |

| Table 4.4 | Overall comparisons between Single layer and three layers BoN interconnects               | 55  |

| Table 5.1 | Lithography conditions for 2µm thick PFI 26A photoresist process                          | 60  |

| Table 5.2 | List of selective etchant chemicals and etching time for different metals                 | 61  |

| Table 5.3 | Lithography conditions for BCB dielectric patterning                                      | 62  |

| Table 5.4 | Lithography conditions for 50µm thick SU-8 photoresist process                            | 67  |

| Table 5.5 | Lithography conditions for 65µm thick JSR photoresist process                             | 70  |

| Table 5.6 | Lithography conditions for 130µm thick JSR photoresist using double coat process          | 72  |

| Table 5.7 | Comparison of JSR resist with other photoresist materials                                 | 73  |

| Table 5.8 | Plating conditions for copper and solder electroplating of 10mmx10mm size test chip wafer | 76  |

| Table 5.9 | Plating conditions for copper and solder electroplating of 20mmx20mm size test chip wafer | 76  |

| Table 5.1 | 0 Bump shear test parameters                                                              | 84  |

| Table 6.1 | Specifications of test dies                                                               | 88  |

| Table 6.2 | Test board specifications for test die                                                    | 88  |

| Table 6.3 | Die shear test parameters                                                                 | 100 |

| Table 6.4 | TC reliability test results                                                               | 102 |

\_\_\_\_\_ xii

## CHAPTER 1 INTRODUCTION

The rapid advances in IC design and fabrication continue to challenge electronic packaging technology, in terms of fine pitch, high performance, low cost and better reliability. In the near future, the demands for higher I/O count per integrated circuit (IC) chip increases as IC technology shifts towards the nano ICs with a feature size less than 90nm. According to Rent's rule the I/O counts will increase to around 10,000 by 2014 [1]. The demand for packages with increased I/O counts and decreased die size will result in the requirement for fine pitch I/Os.

The International Technology Roadmap for Semiconductors (ITRS) sponsored by the Semiconductors Industry Association (SIA) has given the future I/Os pitch requirements according to the IC technology advancements. Table 1.1 shows the ITRS 2003 I/O requirements for advanced IC assembly and packaging [2]. The minimum feature size in IC component will reach 45nm by 2010, requiring an area array chip-tosubstrate interconnect pitch of less than 100µm. As microsystems continue to move towards high speed and microminiaturization technologies, the stringent electrical and mechanical properties are required. Current chip-to-substrate interconnects cannot meet the above requirements. This bottleneck in the packaging industry will potentially limit the future progress in IC technology.

In the past four decades, various types of microelectronics packaging technologies have been developed to accommodate the decreasing feature size and increasing I/O density of ICs, which are discussed in the next chapter. It is very important for the chip-

to-next level substrate interconnect technology to accommodate to these trends in the development of microelectronic packaging. Thus the main focus of this research is on interconnects between chip-to-next level substrate for IC packaging which is also addressed as first-level or off-chip interconnect.

| Year of production                          |     | 2005 | 2007 | 2010 | 2013 | 2016 |

|---------------------------------------------|-----|------|------|------|------|------|

| DRAM <sup>1</sup> / <sub>2</sub> Pitch (nm) | 90  | 80   | 65   | 45   | 32   | 22   |

| MPU Physical Gate Length (nm)               | 37  | 32   | 25   | 18   | 13   | 9    |

| Chip Interconnect Pitch (µm)                |     |      |      |      |      |      |

| Flip Chip area array                        | 150 | 130  | 120  | 90   | 90   | 80   |

| Peripheral flip chip                        | 60  | 40   | 30   | 20   | 20   | 15   |

Table 1.1 ITRS 2003 for Assembly and Packaging [ITRS 2003]

The main criteria involved in the development of the first level interconnect technology are:

- High count I/Os

- Good electrical performance

- Better thermo-mechanical reliability

- Good manufacturability

- Low cost

In the current electronic packaging industry, the three most widely used off-chip interconnect technologies are wire bonding, tape automated bonding (TAB) and solder bump joints for flip chip (FC) packaging. Solder bump interconnects serve to meet the

requirements of high performance ICs due to the area array capabilities of solder bumps because it meets the requirements of increased I/O density and also provides shorter leads, lower inductance, higher frequency, small device footprint, and lower profile when compared to wire bonding and TAB.

As stated in Table 1.1 earlier, the pitch of area-array flip chip packages will reach 80µm by 2016. Electroplating solder balls could result in a pitch of 80µm, but this small pitch and the short standoff height of interconnects would decrease the thermo-mechanical reliability. The predominant failure mode in flip-chip technology was the thermo-mechanical fatigue of solder joints which eventually resulted in decreased reliability. The reason for this failure was attributed to the mismatch in the coefficient of thermal expansion (CTE) between IC and organic substrate, and the geometrical constraints of the package coupled with temperature excursions during assembly and operation [3].

To improve this reliability, the use of underfill material in the gap between the IC and substrate was suggested [1]. But the use of underfill added cost to the assembly and has moisture related reliability issues. Hence the packaging industry, particularly the consumer product industry prefers packages with no underfill, as one process step was eliminated with reworkability [4]. Moreover, as the pitch size between solder bumps reduces, the height of the solder bumps, and thus the gap between the chip and the substrate, is also reduced. Therefore the cost and the difficulties of underfill dispensing and solder reflow and attaching increases [5].

The potential solutions for the above problems can be summarized as follows

- develop flexible interconnect structure that can withstand the strain energy and thus reduce interconnect failures

- use low CTE boards

- underfill free interconnects

- increase the stand-off of the solder joints

In order to meet some of the above requirements, nano packaging is the only solution offered. Nano packaging comes at two levels namely wafer level and board level packaging. The nano wafer level packaging group, a collaboration project in Singapore, has proposed various wafer level interconnect schemes to develop  $100\mu m$  pitch interconnects at wafer level. The Bed of Nails (BoN) interconnect technology is one of the schemes proposed. The main objective of this research is to develop the fabrication process of the above off-chip interconnect at  $100\mu m$  pitch and to assess its reliability

In chapter 2, a literature survey of microelectronic packaging, wafer level packaging and compliant interconnects is presented followed by experimental details in chapter 3. BoN interconnects conceptual design and fabrication process development are discussed in chapter 4 followed by test chip demonstrator design and its fabrication process in chapter 5. Test board design, assembly process and reliability results of BoN interconnects are reported in chapter 6. Finally the thesis ends with main conclusions and a few recommendations for future work in chapter 7.

### CHAPTER 2

### LITERATURE SURVEY

### 2.1 Introduction to Microelectronics Packaging

Microelectronics is stated as the first and foremost important technology wave in microsystems technologies. It started with the invention of the transistor instead of vacuum tubes. Microelectronics typically, refers to those micro devices, such as integrated circuits (ICs), which are fabricated in sub-micron dimensions and which form the basis of all electronic products. Integrated circuits are defined as a miniature or microelectronic device that integrates elements such as transistors, resistors dielectrics and capacitors into an electrical circuit possessing a specific function [1]. Packaging can be defined as the bridge that interconnects the ICs and other components into a system-level board to form electronic products. Packaging of microelectronics (ICs) is referred to as microelectronics packaging.

Packaging is essential because IC devices cannot function without proper packaging, even though transistors act as brains of IC. The essential functions of the conventional IC packaging are listed as follows:

- To protect IC chips from the external environment.

- To facilitate the packaging and handling of IC chips.

- To dissipate heat generated by IC chips for proper operation of transistors and interconnects.

- To protect the electrical characteristics of the IC.

• To provide paths to distribute signals between chips and to supply voltage and current to the circuits within a chip, as well as to other ICs in a given system, for their operation.

Continuous advances in reducing the size of the transistors allowed the progressive integration of tens, hundreds, to thousands of transistors on a single IC in technologies called small, medium and large scale integration (SSI, MSI and LSI) which evolved into an era of very large or ultra scale integration (VLSI or ULSI) that consists of millions of transistors in a single IC.

In general, IC packages can be classified into two categories namely, Through-Hole and Surface Mount Packages. If the packages have pins that can be inserted into holes in the printed wiring board (PWB), they are called through-hole packaging. If the packages are not inserted into the PWB, but are mounted on the surface of the PWB, they are called surface mount packages. The three most important parameters for packaging ICs as listed in the IC roadmap are given as follows [1]:

- I/O which controls the pitch of the IC package and the wiring needs at system level.

- (2) Size of the IC which controls the reliability of the IC to package connection.

- (3) Power which controls heat dissipation properties of IC and system-level packaging.

Microelectronics packaging and interconnection technologies have undergone both evolutionary and revolutionary changes to serve the trend towards miniaturization in electronic equipment, which is presently evident in military, telecommunications, industrial and consumer applications. The trend has been driven by various forces

including specialist requirements for size and weight as well as cost and aesthetics, which have led to various innovative developments in packaging of integrated circuits and in connectivity on electronics substrates and circuit boards [6].

### **2.2 Hierarchies of IC packaging**

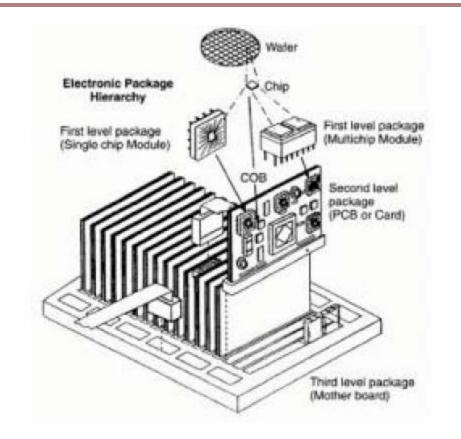

Packaging hierarchy can be divided into different levels in terms of its integration level as shown in Figure 2.1.

At the IC level, packaging involves interconnecting, powering, cooling and protecting ICs. A piece of IC die is generally attached to a chip carrier and the I/O pads on the IC connected to a lead frame by wire bonding. The assembly is then encapsulated. This is referred to as Level 1 in the packaging hierarchy.

Packaging a single IC does not generally lead to a complete system since a typical system requires a number of different active and passive devices. System-level packaging involves interconnection of all these packaged IC chips and components to be assembled on the system level board (PCB) by either through-hole or surface mount technology. The conductor traces on PCB works as communication paths between different IC chips and components by connecting every component so as to form one interconnected system. This is referred to as Level 2 in the packaging hierarchy.

A single system-level board may not carry all the components (ICs) necessary to form some total systems such as mainframes and supercomputers as they require a very large number of ICs. In this case, the several boards necessary to make up the entire system are typically connected through connectors, sockets and cables. This is referred to as Level 3 in the packaging hierarchy.

Figure 2.1 Hierarchy of electronic packaging <sup>[1]</sup>

### 2.3 Historical development of packaging technology

With increasing integration and higher speed ICs and with the miniaturization of electronic equipment, newer packaging systems have been requested by the industry which incorporates the following functions to the above stated functions [7]:

- Multi-pin I/O.

- Ultra-miniature packages.

- Packages suited for high density ICs.

- Improved heat resistance for use with reflow soldering techniques.

- High throughput speed.

- Improved heat dissipation.

• Lower cost per pin.

To resolve these requirements, a great number of packaging schemes are evolved in the market and used for various applications. These technologies have been developed which varies in their structure, materials, fabrication methodology, bonding technologies, package size and thickness, number of I/O connections, heat removal capability, electrical performance, reliability and cost.

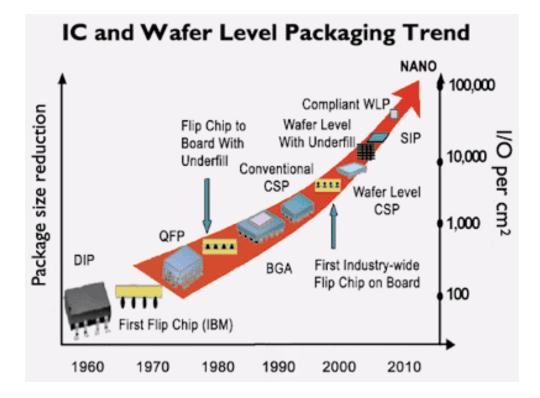

As shown in Figure 2.2, packages have been evolving into smaller size and higher pin count to be compatible with the ever increasing density and complexity demand of ICs. The first development in the packaging technology is the dual-in-line packages (DIP) which gained most popularity in 1970's and 1980's. DIP is through-hole package type, in which, I/Os, or the pins are distributed along the sides of the package. Though many packages have been developed, DIP is used for four decades (after its first introduction), because of its low cost and high reliability. Shrink DIP (SH-DIP), skinny DIP (SK-DIP), slim DIP (SL-DIP), ceramic DIP (CER-DIP) are the different types of DIPs with different number of pins. Since DIPs have upper limitation of the number of I/Os or pins as 64, to achieve higher I/O connections, DIPs have given way to pin grid arrays (PGA) which is also a through-hole package, where the pins are distributed in an area array fashion underneath the package surface.

Through-hole packages are inherently limited in some application due to their big size or inefficient use of the PCB estate, and thus the solution comes with the emergence of surface mount packages in 1980's. Surface mount packages occupy only one side of the PCB estate and thus significantly increase the second level packaging density compared with through-hole packages. Elimination of drilling holes for through-hole

packages also means that smaller pins with smaller pitches can be obtained. In the surface mount packages, the small outline package (SO or SOP) is the first package and most widely used package in modern memory for low I/O applications because of its extremely low cost. Another technology, the Quad flat package (QFP) is an extension of the SOP with larger I/O connections. Both the SOP and QFP have leads that can be attached to the PWB whereas further technology development has led to the evolution of leadless chip packages such as leadless chip carrier (LCC), plastic lead chip carrier (PLCC) and SOJ. In the late 1980's, packages with solder balls are developed as an alternative to packages with leads. The solder balls can be placed underneath the surface of the package in an array and can significantly increase the I/O count of the surface mount packages, for example, ball grid array (BGA) and flip chip packages. It should be noted that some packages, like flip chip packaging, are different from others such as SOP in the manner of connection between IC dies and carriers.

As the name implies, in flip chip technology the die is flipped upside down with the active side connected to the carriers by solder balls, which is in sharp contrast with DIP devices where the die is wire-bonded to the carrier. Flip chip devices are electrically superior to conventional dual-in-line (DIP) and pin grid array (PGA) packages since electrical parasitic associated with long bonding wires and lead frame pins are effectively eliminated. Although reliability concern and cost issues are still to be resolved before flip chip technology finally replaces wire bonding technology [8]. It is gradually accepted that flip chip technology is the right direction especially for high pin count devices. Furthermore, by properly applying underfill material between chip and carrier, reliability

of flip chip packages can be enhanced by a factor of ten [9]. Solder or gold bumps are used in flip chip technology, and the correct choice is application dependent [10-11].

Figure 2.2 Packaging trends <sup>[12]</sup>

The Chip scale package (CSP) has been developed to address the demands of modern electronics, like portable and hand held products, which require smaller, thinner and lighter packages. A CSP is defined as package whose area is less than 1.2 times the area of the IC package. Generally, CSP devices have solder ball interconnects with a diameter of 0.3mm and a pitch of 0.5mm and CSP package may come as small as 5x5mm<sup>2</sup> and 1 mm thick. Various CSP manufacturing methodologies have been developed by major semiconductor companies such as National semiconductor, Motorola and Fujitsu etc. Typical CSPs can be divided into lead frame, rigid and flexible substrate with flip chip and ceramics substrate with wire bond and flip chip types, but they still

follow the conventional packaging process, i.e., die singulation before packaging. On the other hand, wafer level packaging (WLP) technology such as wafer level CSP (WL-CSP) attracted greater interest from industry because it is cost effective, easy to test and has a small footprint and low profile. The unique feature of the wafer level approach is that the package is completed directly on the wafer then singulated by dicing for the assembly in a flip chip fashion. All WL-CSPs are real chip-size rather than chip-scale due to the wafer level processing. The industry may finally move to direct chip attach (DCA) technology that eliminates the first level package and thus further reduce cost, but the current infrastructure is still more suitable to CSPs and CSP devices which are easier to handle, assemble, test at higher speed and rework when compared to DCA.

With the decreasing feature size of ICs and packages, the RC delay and crosstalk effect might result in the serious problem that the signal integrity cannot be obtained with the packaging technologies mentioned above. Therefore, alternative packaging approaches have been proposed, including optical packaging, RF packaging and 3-D stack packaging [13-14]. Both on-chip and off-chip data transmissions are expected to improve with the enhancement in packaging density [15].

### 2.4 Challenges in microelectronics packaging

The microelectronics packaging industry continues to face technical challenges as long as market demands for modern electronics, like more portable and hand held, light weight, and high performance products. As a guide for research direction in the packaging field, the International Technology Roadmap for Semiconductors (ITRS) clearly indicates the technical challenges that could be roughly categorized as Printed Circuit Board (PCB) related, materials related, and design and simulation challenges [16]. With the increasing complexity and integration of semiconductor technology, PCB fabrication has become a bottle-neck for IC development. On-chip Input/Output pin (I/Os) numbers increases with increasing the number of transistors according to Rent's rule, while chip size keeps falling. As a result more stringent requirements are imposed on the corresponding metal pads on PCBs in terms of their size and pitch. To realize the fine-pitch board-level interconnects, micro via and soldering technologies need to be further improved for fabrication of reliable, multi-layer PCBs. PCB research is still focused on organic substrates due to their cost consideration. Advanced organic substrates must have higher glass transition temperature (Tg) to be compatible with the high temperature processing of Pb-free solder, increased wireability at low cost, improved planarity and low warpage at higher process temperatures, low moisture adsorption, low cost, increased via density in substrate core, low cost embedded passives. Electrically, the substrates must have improved impedance control and lower dielectric loss to support higher frequency applications.

Drastic improvements in materials properties will be required to support the technology nodes driven by projected semiconductor requirements in power, frequency and I/O, and as well as market requirements in cost, size, weight, and environment. Major material challenges are placed on underfill, copper/ low-k dielectrics, and Pb-free solders. Underfill is a liquid polymer-based composite that is dispensed and flowed between the flipped chip and underneath PCB to relieve the high strain in the chip-to-board interconnects. The current underfill materials must be improved in terms of their adhesion, lowering moisture absorption, and broadening the operating temperature range. Advanced underfill materials under development include pre-dispensed underfills,

reworkable underfills [17], and snap cure underfills. Underfill void and adhesion in the reduced solder bump gap and spacing between the bumps will pose additional difficult material challenges. Advanced underfills must easily dispense in narrowing solder bump gaps and in between higher density bumps. Low modulus underfill materials and molding compound materials may become needed for the chip dielectric and copper interconnects will be robust under thermo-mechanical stress.

Copper metallization and low-k dielectrics have been introduced into electronic packaging for the sake of lower signal delay and thus higher signal integrity required by next generation IC products. By the introduction of copper/low-k materials, the on-die dielectric stiffness will be approaching in stiffness to the materials on the package side such as the molding compound or underfill materials. However, mechanical problem results from higher mismatch in coefficient of temperature expansion (CTE) and poor interfacial strength between the low modulus (low-k) dielectric and metallization traces. Major efforts have been underway to address environmental concerns such as materials and surface finishes for lead-free solder assembly and development and implementation for halogen free materials. Pb-free solders are mandated not only to relieve the environmental concerns but also to reduce radiation-induced soft errors. The most significant emission of alpha particles comes from decay of <sup>210</sup>Pb, an unstable isotope of lead in the solder [18]. Tin-based alloys are the most promising lead-free solder candidates, including Sn-3.5Ag, CuSbAgSn and Sn-3.4Ag-4.8Bi etc.

Other material challenges are, due to the rapid reduction in wire bond pitch, the reduction in wire size, capillary, and solutions for wire sweep electrical signal integrity and bond pad designs, which will require significant materials improvement, and

materials process innovation than the currently used processes. Material properties such as dielectric constant, dielectric loss, and thermal conductivity will be very significant to meet higher frequency and higher power demands. Materials research and development will be needed to meet thermal management challenges such as for thermal interface materials, heat spreaders, and external solutions. Knowledge of packaging materials properties are critically needed for modelling and simulation of electrical, thermal and reliability performance for package design release and new package development. Methods for accurate characterization of materials properties and materials interface properties for packaging materials in their use environment will be needed.

### 2.5 Wafer level packaging technology

Wafer level packaging (WLP) entered the microelectronics industry's lexicon in the late 1990's. WLP is an advanced packaging technology in which the die interconnects bumping, assembly, packaging, test and burn-in all are processed at the wafer level prior to singulation for the system level assembly either as a flip chip or directly as a surface mount device. Compared with conventional packaging technologies where silicon wafers are first singulated into dies and then each die sequentially go through assembly, packaging, and test and burn-in steps, wherein WLP all these steps are done on IC dies when they are still in wafer form and thus it is a true chip-size package. WLP technology offered a number of advantages includes, size miniaturization, lowest cost, elimination of underfill materials and enhancement of electrical performance because of short interconnects [1].

All wafer level packages usually use area-array solder balls as chip-to-next level interconnection whereas WLP technologies differ according to the process steps for area-

array distribution of solder balls. WLP technologies can be classified as Redistribution WLP, Encapsulated WLP and Flex/tape WLP. Many commercial WLPs which have been introduced into the market by different companies are compared with respect to their process features in Table 2.1 [19].

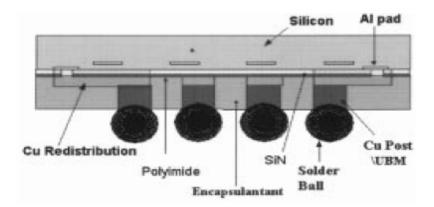

Redistribution WLP generally involves the deposition of thin-film polymer dielectrics, such as BCB or Polyimide, which acts as a secondary passivation layer and metallization Cu or Al to reroute the typical peripheral pads to an area-array configuration. Electroplated or electroless Ni/Au are used as under bump metallurgy (UBM). UBM is critical and necessary to minimize the metallurgical reactions like diffusion of Sn from solders into the redistribution layer and provide highly reliable interconnections. Finally solder balls are formed by solder past screen printing directly on the wafer and reflowed. Examples of redistribution WLPs include IZM-Berlin's S<sup>3</sup>-Diepack, FCT's Ultra CSP and Fujitsu's Super CSP etc. The cross section of Fujitsu's Super CSP is shown in Figure 2.3.

Figure 2.3 Cross sectional view of Fujitsu's Super CSP<sup>[19]</sup>

| Company    | Technology              | Feature                                   | UBM          | Dielectric  | Solder Bump<br>Ball dia/Pitch<br>(mm) |

|------------|-------------------------|-------------------------------------------|--------------|-------------|---------------------------------------|

| Amkor      | wsCSP <sup>TM</sup>     | WB connection<br>Cu/PI film               | N/A          | PI film     | 0.3-0.5/0.5-0.8                       |

| FCT        | UltraCSP <sup>™</sup>   | Redistribution                            | Al/NiV/Cu    | BCB         | 0.35-0.5/0.5-<br>0.8                  |

| FormFactor | MOST <sup>TM</sup>      | WB "Spring"                               | N/A          | N/A         | N/A                                   |

| Fujitsu    | SuperCSP <sup>™</sup>   | Encapsulated<br>0.1 mm Cu<br>posts        | Ti/Ni/Cu     | PI          | 0.35-0.5/0.5-<br>0.8                  |

| IZM Berlin | S <sup>3</sup> -diepack | Cu<br>redistribution                      | TiW/Cu/Ni/Au | BCB         | 0.3                                   |

| Intarsia   | MicroSMT <sup>TM</sup>  | Epoxy Si/glass<br>encapsulation           | Ti/Cu/Ni/Au  | Proprietary | 0.3                                   |

| Oki        | -                       | CMP<br>encapsulated<br>Cu posts           | -            | PI          | -                                     |

| Shellcase  | Shell BGA <sup>TM</sup> | Glass<br>encapsulation                    | Ni/Au        | BCB epoxy   | 0.3                                   |

| Tessera    | WAVE <sup>TM</sup>      | Cu/PI film, low<br>modulus<br>encapsulant |              | PI film     |                                       |

| Unitive    | -                       | Redistribution                            | Al/Ti/Cr-Cu  | BCB         | Plated bumps<br>0.125-0.25            |

Table 2.1 Comparison of Commercial Wafer-Level package technologies

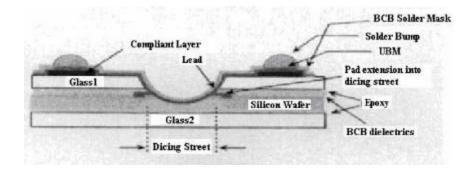

Encapsulated WLP technology seals the wafer which contains the active devices between the glass wafers. First, the peripheral pads on the die are extended into the dicing streets. The face of the wafer is then glued to a glass wafer and the back side of the wafer is thinned down to 100µm thickness. The backside of the wafer is sealed in glass and sawn to expose the extended pads. Metallization and UBM layers are deposited and patterned respectively. Finally, solder bumps are attached and reflowed. Examples of Encapsulated WLPs are Shellcase's Shell CSP and Intarsia- Micro SMT. The cross-section of a glass encapsulated Shell CSP WLP is shown in Figure 2.4.

Figure 2.4 Cross sectional view of the Shellcase WL-CSP<sup>[19]</sup>

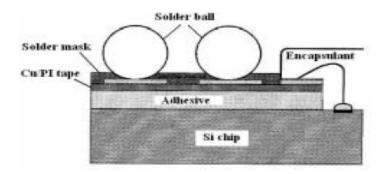

Flex tape WLP technologies redistribution structure is different from previous technologies. In this, a redistribution pattern is formed on the Cu/Polyimide flex tape and the patterned tape is attached to the wafer with adhesive. Then the chip is connected by wire bonds from the chip pads to the tape. Liquid encapsulant is used to protect the wire bonds and bond pads. Finally, eutectic solder bumps are attached and reflowed. The examples of Flex tape WLPs include Amkor Anam's wsCSP<sup>TM</sup>, Tessera's µBGA and FormFactor's MOST<sup>TM</sup> technology. The cross-section of the wsCSP<sup>TM</sup> flex tape WLP is shown in Figure 2.5.

Figure 2.5 Cross sectional view of Amkor ws -CSP package <sup>[19]</sup>

Inspite of many advantages when compared to conventional packaging, wafer level packaging technology has many challenges must still be solved, including reliability of larger die sizes and developing testing strategies. Other key challenges remaining include wafer-level burn- in and test, in addition to thermal management. Presently, wafer bumping and WLP technologies are relatively using 8inch or smaller wafers. But transistion is being made to 300mm, which challenges all the current technology in this scale-up migration. Major challenges include 300mm sputtering, full-field exposure and across-wafer resistance-drop for electroplating. While transistion from 200mm to 300mm has become a major project for the large IC manufacturers, it is even more challenging from bump foundries.

#### **2.6 Compliant wafer level interconnects**

Earlier investigations reported that flipped chips are bonded with PCBs using solder bumps or gold bumps. Solder bumps offers better advantages in terms of selfaligning property over gold during the solder reflow process with better planarity in bump height. However, problems arise when this solder ball interconnects are subjected to thermal loading; failure occurs due to thermal fatigue caused by the large CTE mismatch between the Si die (~2.3ppm/<sup>0</sup>C) and organic PCB substrate (18ppm/<sup>0</sup>C), inducing high strain in solder joints. In case of eutectic 63Sn/37Pb solder, which is preferred due to the low melting point of 183<sup>0</sup>C, creep deformation can occur even at room temperature. Thus, it is evident that solder joints are the most frequently observed failure sites in flip chip devices. The above problems can be overcome with the application of underfill material, which is a pre-dispensed liquid injected into the gap between the flipped chip and PCB substrate and is then cured. Due to this the solder joint reliability is substantially improved because the thermal deformation is evenly distributed through out the underfill material and solder joints. However, this improved reliability is obtained at the expense of cost and electrical performance degradation of the underfill material [20]. Apart from these drawbacks, cracking or interfacial delamination during thermal cycling can also occur in underfill materials. The other limitations of the solder bumps include the difficulty to reflow and attach solder and to dispense underfill as the pitch size is reduced [21]. Coupled with this, the reliability also drops down. Compliant interconnects with both vertical and horizontal compliance is found to offer better solutions to the above mentioned problems, especially for wafer level packaging, in which the vertical compliance facilitates wafer-level test and interconnection, and the lateral compliance has helped to reduce strain accumulated in solder joints. Few compliant interconnects for wafer-level packaging, which are either available in market or under development in laboratory are discussed as follows.

### 2.6.1 Tessera's $\mu$ BGA and WAVE<sup>TM</sup> packaging technologies

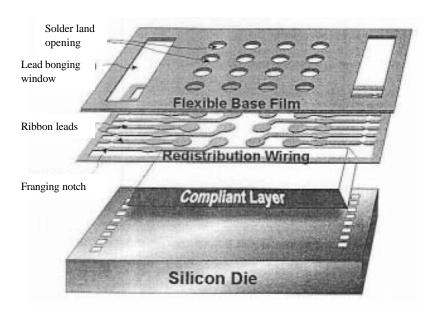

Tessera had developed  $\mu$ BGA technology in the early 1990's for a unique multiple chip module (MCM), with vertical compliance that facilitate reliable contact during electrical testing. Tessera  $\mu$ BGA technology is the first qualified CSP technology for Rambus memory (RDRAM) and flash memory devices [22]. Although some companies including Amkor and Hitachi, got licenses of the  $\mu$ BGA technology with many modifications, the fundamental elements are presented in Figure 2.6. The compliant layer or buffer layer, which is made of low modulus silicon elastomer with thickness of 75-150 $\mu$ m, enables to provide the required compliances. Since the compliant layer is in direct contact with the active side of IC, it must be free of alpha particle. The flexible links between IC pads and the chip to next level interconnects such as solder balls are provided by using redistribution layer. Another feature is that the notched leads remain attached to the carrier films until the moment of bonding. In Tessera  $\mu$ BGA packages, the structure incorporates compliancy that solves the reliability issues with thermal expansion mismatch between silicon die and PCB. Compliancy provides high on-board reliability that requires no underfill, allowing the device to be easily reworked. Other features of  $\mu$ BGA technology include its face-down structure enabling enhanced electrical and thermal performance, short signal paths resulting in reduced parasitics, and an exposed back surface of the die allowing for efficient heat dissipation.  $\mu$ BGA packages shows good electrical parasitics due to its short signal paths and excellent board level reliability, with a life of over 2876 cycles under thermal cycling between -60 to 150<sup>o</sup>C [23]. Tessera also demonstrated over 1200 cycles without failure under -40 to 125<sup>o</sup>C test condition with TV-46  $\mu$ BGA package [24].

Figure 2.6 Schematic representation of fundamental components of µBGA package

by Tessera <sup>[25]</sup>

Tessera's second generations of compliant packages are  $\mu Z^{TM}$  (Zinger<sup>TM</sup>) and WAVE<sup>TM</sup> (Wide Area Vertical Expansion) technologies. The WAVE package incorporates a compliant layer formation process that expands vertically along the surface of the die or the entire wafer as shown in Figure 2.7. In WAVE<sup>TM</sup> technology, more flexible interconnections between the die and package can integrate and the first level bonding of all die pads to substrate can be done simultaneously. The WAVE packages integrate the silicon die with a stress decouple layer made of low modulus encapsulate and a copper intrachip wiring layer with two metal/polyimide substrates. The gap between the die and the substrate is filled and expanded to a height of 100 to 150µm by injection of low modulus encapsulant. WAVE package has a much higher potential than  $\mu$ BGA package for high performance and high reliability package application. The board level reliable tests of WAVE package with a gap distance 150µm demonstrated over 1500 cycles between -40 and 125<sup>0</sup>C without fail and can be improved by optimization of lead type, lead orientation and gap distance [26-28].

Figure 2.7 Schematic representation of cross section and 3-D view of WAVE<sup>TM</sup>

package <sup>[26]</sup>

These packaging technologies which include  $\mu$ BGA, WAVE<sup>TM</sup> and  $\mu$ Z<sup>TM</sup> are engineered to enable the semiconductor industry to meet the growing demand for small form factor, high performance and cost effective electronics. These technologies are well suited for wireless and memory semiconductors devices including, DRAM (Dynamic Random Access Memory), ASIC (Application Specific Integrated Circuits) and RFIC (Radio Frequency Integrated Circuits) application which requires light weight, small foot print, thin profile and high performance [29].

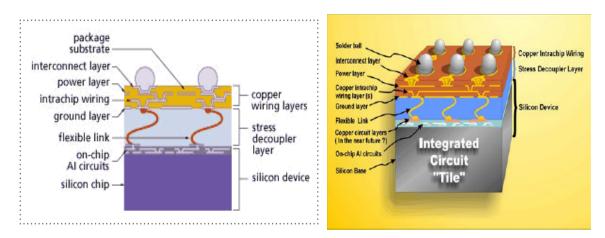

### 2.6.2 FormFactor Microspring<sup>TM</sup> Contacts

In 1998, FormFactor introduced the industry's first integrated wafer level backend process. This core technology involves the fabrication of Microspring<sup>TM</sup> contacts on the wafer using wire bonding technology. By using these microspring contacts as chip to next level interconnects, FormFactor introduced the industry's first integrated wafer level CSP (Chip Scale Package) called as Microspring<sup>TM</sup> Contact on Silicon Technology (MOST<sup>TM</sup>) package [30-32]. These Microspring contacts as shown in Figure 2.8, decouples the CTE mismatch between the Si IC chip and PCB substrate and thus improves reliability because of its controlled shape and inherent spring characteristics. Unlike, solder ball based CSP approaches, MOST<sup>TM</sup> process is unique in that the package leads (Microspring contacts) are also the compliant interface to the test and burn-in equipment and enables whole-wafer burn-in and test at the wafer level. Assembly methods to attach MOST leads to PCBs are conventional solder attach, self socketing die and using conductive epoxies developed by FormFactor and its partners. Advantages of MOST<sup>TM</sup> includes, low cost due to usage of conventional materials and equipment, elimination of underfill due to Microspring compliant leads structure and thus enables easy repair, and

soft errors rate also reduced due to the distance between the solder and the IC, compared to CSPs that apply solder balls directly on the die surface and this error is even totally removed in case of self-socketing die assembly and die attach using conductive epoxies where solder is not used for connection. Reliability test shows a life of over 1000 cycles under thermal cycling in the range of -55 to 125<sup>o</sup>C. MOST<sup>TM</sup> interconnects demonstrates low inductance and low stay capacitance compared to many solder-ball based interconnects. Despite having many advantages, MOST<sup>TM</sup> process has certain draw backs because they are fabricated one after other using wire bonding, which is an inefficient process which eventually leads to increased cost.

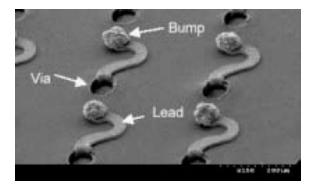

Figure 2.8 SEM micrograph showing microspring contacts or interconnects (MOST<sup>TM</sup>) array by FormFactor<sup>[33]</sup>

### 2.6.3 Sea-of-Leads (SoL) interconnects

Sea of Leads (SoL) is a novel ultra-high-density I/O interconnection technology developed at Georgia Institute of Technology to meet future chip-to-module interconnection needs, which includes giga scale off-chip communication in System on Chip (SoC) packages and electrical performance [34-36]. It is an extension of the concepts and processes that are developed by Patel et al. [37-38]. The important feature of SoL interconnection technology includes high density more than 10<sup>4</sup> leads per cm<sup>2</sup>, x-

y-z compliance, high power and high electrical band width, and low electrical parasitics [39]. SoL is fabricated at the wafer level to extend the economic benefits of semiconductor front-end and back-end wafer level batch fabrication to include chip I/O interconnects, packaging, and wafer level testing and burn-in [40]. The SoL processing steps starts with fabrication of die pads on the wafer using photolithography and metal etching followed by applying and patterning of polymer using photolithography to expose the die pads. Compliant metal interconnects extending from the die pad to the solder bump are fabricated by depositing a metal seed layer and electroplating with Cu to final interconnect thickness. The seed layer is then removed and the Cu interconnects are covered with second polymer layer followed by exposure of Cu interconnect end. Again a new seed layer is deposited and the solder bump is electroplated followed by finally removing the seed layer to form the complete SoL interconnects as shown in Figure 2.9. The advantages of SoL interconnects are that it enables high out-of-plane and in-plane compliances, low electrical parasitics and cross-talk by selecting the polymer with low Young's modulus and dielectric constant.

Figure 2.9 SEM micrograph of SoL interconnects <sup>[38]</sup>

The SoL packaging technology has made continuous improvements to enhance the electrical performance and mechanical compliance. Embedded air-gaps are introduced in SoL interconnects by processing a polynorbornene (PNB) sacrificial polymer (Unity<sup>TM</sup> 400) layer, which is thermally decomposed at 400-425<sup>o</sup>C, to increase the effective out-of-plane (Z-axis) compliance of the package for probe contact and other movements, to mitigate problems in thermal expansion between chip and printed wiring board, and also to reduce the dielectric constant of the interconnect dielectric materials [41]. Furthermore, optical waveguides are proposed to be incorporated within next generation SoL packages, in which the embedded air gaps are used as the upper cladding for optical waveguides. The SoL design is compatible with board-level optical signal distribution via waveguides and also the insertion loss of ground signal propagation into and out of SoL package is less than 1.2dB at 45GHz [42]. Advantages of the next-generation SoL packages includes enhanced predictability of global clock signals, higher heat removal and power supply capabilities that is especially important for hybrid electrical/optical systems packaging.

#### 2.6.4 Cantilevered spring interconnects

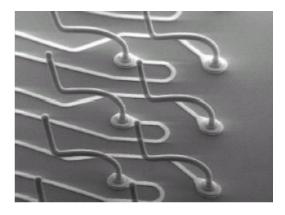

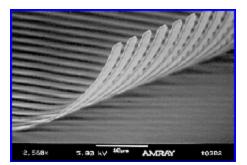

To address the compliant ultra fine pitch and high density I/O interconnects requirement for next generation packaging, micro-spring interconnects [43-46], J-Spring interconnects [47], and highly compliant cantilevered nanospring interconnects [48-50] have been introduced by Georgia Institute of Technology in collaboration with Xerox Palo Alto Research Center and Nanonexus Inc. All these technologies are based on stress induced sputtered metal thin film technology in which intrinsic stress in sputtered metal films leads to bending after the film is released from the substrate. The desired uniform bi-axial stress gradient across the film thickness, which determines the radius of curvature of the released compliant interconnect oriented in up or down directions to an expected extent, can be controlled by the manipulation of the argon pressure in the sputtering chamber. In nanospring technology, 80% Mo/20%Cr (by weight) alloy is chosen to make cantilever-type interconnects, in which the metal is first sputtered onto a substrate at low argon pressure to build compressive stress in thin metal layer. By gradually increasing the argon pressure in sputtering chamber, the film intrinsic stress is changed from compressive to tensile at the end of the sputtering deposition, which is required to bend up after the film is released from substrate. The stress-engineered thin film is patterned into springs and coated with a highly conductive metal layer such as gold to improve its electrical conductivity and the released layer under the thin film is etched away. The released springs curl up due to its intrinsic stress gradient to form spring interconnects as shown in Figure 2.10.

#### Figure 2.10 SEM micrograph of Ultra-fine pitch nanospring interconnects <sup>[50]</sup>

The advantage of these compliant spring interconnects is that it meets the requirements of ultra fine-pitch interconnects as small as 6µm. This technology is also found to be highly yielding and inexpensive. Compared to other compliant interconnects, spring interconnects posses very high compliance, i.e. tens of millimeters per Newton in X and Y directions, and over 10,000mm/N in Z direction. Another unique advantage of this technology is that it enables the no-soldering contact between the spring and the board pad. The drawback of this technology is that only some specific metals can be

used to fabricate the nanospring interconnects. Another coiled Microspring contact technology has been studied using thermal expansion coefficient of thin metal films [51].

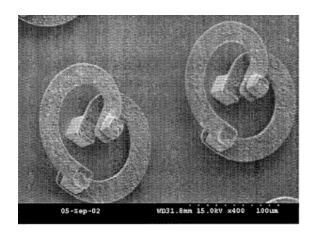

#### 2.6.5 Helix – type interconnects

Recently another novel compliant off-chip interconnects, namely one-turn Helix and ß-Helix have been developed as an underfill-free interconnects at Georgia Institute of Technology based on conventional photolithography and electroplating technologies [52-55]. The fabrication of Helix-type interconnects starts with the completion of die pads by using etching process on given wafer. A thick photoresist is initially spun, soft baked, UV patterned, post-exposure baked and developed. The bottom copper post is electroplated with seed layer. Again a new seed layer is sputtered and a thinner photoresist is applied, patterned and arc beam electroplated. This sequential process of photolithography and electroplating is repeated to fabricate the five-layer  $\beta$ -Helix structure. After completion of all these steps, the surrounding photoresist and the seed layers are etched sequentially layer by layer. Thus the free-standing wafer-level 200µm pitch B-Helix interconnects are fabricated as shown in Figure 2.11. Simulation results demonstrated that, the ß Helix interconnects had good mechanical compliance in the three orthogonal directions. Besides the good mechanical and thermo-mechanical performance, β-Helix interconnect also has comparative electrical parasitics with conventional solder bump interconnect. It is also a cost-effective process, especially when the I/O count is high because the fabrication of the above interconnects can be integrated into wafer-level processing as a batch process [55]. Research is still being carried at Georgia Institute of Technology, to develop an alternative geometry design like G-Helix to meet all of the electrical and the mechanical requirements without the need for relaxing for some of the values [56].

Figure 2.11 SEM micrographs of ß-Helix interconnects <sup>[55]</sup>

### 2.7 Challenges in wafer level packages

In the microelectronic packaging industry wire bond interconnections are still in use because of its low cost and easy processing method. Flip chip package interconnections fabrication process generally involved more number of process steps and costly photoresist and polymer materials hence found to be costly than wire bond interconnections. Apart from this, there are number of challenges faced by the existing interconnections technologies which are summarized in detail as follows:

- More number of processing steps are involved in interconnects fabrication thereby increasing the time of fabrication which resulted in reduced mass production.

- Usage of expensive proprietary polymers in processing techniques resulted in high cost. Hence the cost per I/O pin is increased.

- Most of the technologies fabricated interconnects at pitch size of 200-500µm.

which limits the interconnection density and the packaging technologies for next generation microelectronics.

- Due to difficult shapes involved, special assembly equipments are required. Apart from this assembly yield and quality are also biggest challenges faced.

- Process recipes should be compatible for mass production fabrication.

- Current technologies are using the polymers as encapsulates and underfill materials to obtain compliancy effect but these materials induces moisture issues in the package thereby degradation of their thermo-mechanical reliability.

### **2.8 Scope of the project**

The present packaging technologies are using solder balls as the interconnections between the chip and substrate, at the pitch size of 300-400µm. But the investigations found that these solder balls are the main failure sites in the package during the thermomechanical fatigue caused due to the CTE mismatch between the chip and organic substrate. Hence underfill material is dispensed around the solder bumps in between chip and substrate to improve the fatigue life. According to ITRS-2003, next generation packaging technologies will require interconnections technologies at lower pitch size, where solder balls cannot meet the reliability requirements because of its small size and short stand-off height at that fine pitch and underfill dispensing would also found to be a bottleneck issue at that fine pitch. Hence packaging industry needs cost effective underfill-free interconnections technologies to meet the reliability requirements at fine pitch. The present study was done on the fabrication of underfill-free Bed of Nails (BoN) interconnects. The fabrication of the BoN interconnects was based on photolithography and electroplating techniques. This fabrication was carried out at wafer level hence it enables mass manufacturing and realizes a cost effective package. The main tasks of this project includes optimization of thick photoresist process for mold fabrication, copper

and solder electroplating, solder reflow process and assembly process. Thermomechanical reliability of the above interconnects was done to test the feasibility and failure analysis to identify the possible failure modes.

### CHAPTER 3

### **EXPERIMENTAL DETAILS**

#### **3.1 Materials**

The future packaging demands on high I/O density and high mechanical and electrical reliability necessitate copper as a prominent material for interconnects. As an electrical off-chip connector, copper has lower electrical resistance that not only leads to improved power distribution and device performance but also helps to reduce cross-talk by providing a better control over the tight interconnect pitch. Furthermore, with good electromigration stability, copper can conduct high current density. From a cost point of view, copper is cheap and can be easily electroplated. Therefore, in the current study, copper was electroplated during the fabrication of the BoN interconnect. To fabricate the electroplated copper BoN interconnects the following materials were used in the process:

- 1. The p-type silicon (100) wafers of 200mm diameter with thin electrical insulating film of  $1000A^{\circ}$  SiO<sub>2</sub> were used for the fabrication of test chip demonstrator.

- Sputtered Ti/NiV/Au layers were used as pads and UBMs with daisy chains. It also was used as the seed layer for electrical contact during the electroplating of copper interconnects.

- 3. AD AP3000 primer solution for promoting adhesion of the BCB with the wafer.

- 4. BCB dielectric material was used to passivate the daisy chains and to define the pads for copper interconnects.

- 5. Wet etchant chemicals for selective etching of Ti, NiV, Au and Cu layers.

32

- 6. PFI 26A (+ve), PLA 900 (+ve), AZ P4620 (+ve), SU-8 (-ve) and JSR (ve) photoresist materials were used to get the patterned thick layer for selective plating of copper interconnects.

- 7. Electroplated eutectic Tin-Lead was used as a solder material.

- 8. Developer and stripper solutions for the above resist materials.

- Piranha solution (H<sub>2</sub>SO<sub>4</sub> + H<sub>2</sub>O<sub>2</sub>) for wafer cleaning. Ratio of H<sub>2</sub>SO<sub>4</sub> to H<sub>2</sub>O<sub>2</sub> was

5:1.

- 10. Acetone and PI for cleaning of wafers to reclaim the photoresist coated wafers.

### **3.2 Equipments**

#### 3.2.1 Sputtering machine

The seed layers for electroplating were deposited using Balzers LLS 502, load lock sputtering system. Ti layer was coated on the wafer prior to deposition of Cu or Au seed layer films to promote the adhesion. The Cu or Au target was used as the cathode with 99.9999 % purity. The sputtering conditions used were  $4 \times 10^{-6}$  base pressure;  $3 \times 10^{-1}$  working pressure; 4KW, 6KW and 1KW sputter power for Ti, Cu and Au respectively. The sputtering chamber was baked for about 20hrs by wiring with a couple of heaters to remove the moisture from the chamber wall very efficiently. High Purity Argon gas was used to maintain inert atmosphere. Seed layers were deposited by DC magnetron sputtering on the Si (100) substrate. The substrate was maintained at a distance of 70mm from the target. From thickness measurements of all the films, the deposition rate of the film was estimated to be 2.15nm/s.

#### 3.2.2 Spin coater track

SVG 90 series spin coater track was used to coat, soft bake, post exposure bake and to develop the photoresist material. This track accepted only 8inch diameter wafers and contained 18 stations, which included "2" wafer sender/receivers, "2" vapor primers at 150<sup>0</sup> C, coating, 4 hot plates, 6 chill plates, and 2 developing stations. In this spin coater, wafer flow could be defined according to the process flow, in such a way that wafer started from wafer sender to vapor primer at 150<sup>0</sup>C and then to chill plate to cool the wafer to room temperature. After cooling, the wafer is moved to the coating station where the resist spun onto the wafer according to the coating cycle which was already programmed. Finally the wafer was moved to the hot plate where a defined temperature was maintained for pre-defined time to soft bake the photoresist. All this process could be performed automatically for 25 wafers lot continuously by selecting automatic mode. Even the single step process such as coating or baking could be performed by selecting the manual mode. The thickness of the photoresist can be controlled by changing the spin speed and spin time.

#### 3.2.3 Mask aligner

EVG 640 mask aligner was used to expose the photo sensitive layers through soda lime or chrome masks and to align the subsequent masks in the lithography processes. This was a UV light (365-405nm) exposure aligner and was compatible with 5, 7 and 9 inch masks. The capabilities of the above aligner were as follows.

- Single and double side alignment

- Proximity, hard and soft contact modes

- $\pm 1 \mu m$  alignment accuracy

- Alignment for embossing and wafer bonding

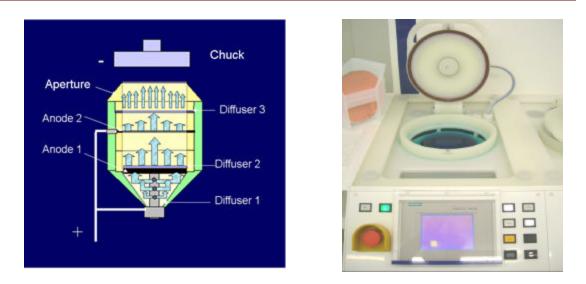

#### 3.2.4 Copper electroplating tool

Copper electroplating was carried out using RENA 8" wafer electroplating tool, which was fountain type (Cup type) in which Sperolyte  $CuSO_4$  based solution (Atotech Pte. Ltd) was used as electrolyte solution. The principle of this plating tool was that the wafer was loaded in chuck as cathode placed upside down at the top of the plating tool as shown in Figure 3.1 and the soluble copper anode was positioned at the bottom in cup shaped electrolyte chamber. The electrolyte was fountained from the bottom to the wafer surface through the diffusers. The concentration uniformity of the electrolyte solution also would be maintained due to this fountain type electrolyte flow and thereby improved the plating efficiency. The plating process was carried out in two steps. In first step, the chuck loaded with the wafer was rotated at high speed with high flow rate of electrolyte to improve the wettability of the wafer whereas in the second step, the flow rate was maintained constant with the rotating speed of the chuck being reduced to obtain uniform copper plating in the entire wafer. Hence the plating thickness could be controlled by optimizing the current density and platting time and uniformity could be controlled by optimizing the flow rate of electrolyte. The plating process was carried out at room temperature.

Figure 3.1 (a) Schematic diagram of principle of electroplating (b) photograph of 8 inch wafer fountain type for Cu plating tool

### 3.2.5 Solder plating tool

The eutectic tin-lead solder was plated at the tip of the copper interconnects using RENA 8" wafer electroplating tool, which was a rack type in which sperolyte solution (Atotech Pte. Ltd) was used as electrolyte solution and tin-lead pellets were used as anode. Here the principle of plating was that the wafer was loaded in the chuck and the chuck was positioned parallel to the anode as shown in the Figure 3.2. Solder thickness, uniformity and solder shape at the tip of the BoN interconnects were controlled by optimizing the current density, flow rate of electrolyte and plating time.

Figure 3.2 (a) and (b) Photographs of rack type solder plating tool for 8inch wafer