# DYNAMIC PERFORMANCE IMPROVEMENT IN BOOST AND BUCK-BOOST-DERIVED POWER ELECTRONIC CONVERTERS

# KANAKASABAI VISWANATHAN

(M.Eng., IISc, India)

# A THESIS SUBMITTED FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

# DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING NATIONAL UNIVERSITY OF SINGAPORE

2004

## Acknowledgements

I would like to express my sincere thanks to my research supervisors Dr. Dipti Srinivasan and Prof. Ramesh Oruganti, for their encouragement, guidance, support, and thought-provoking discussions during my doctoral research. I thank the Almighty for blessing me to work with such benevolent people, who were not only excellent supervisors, but also kind advisors helping and caring about me.

I am grateful to National University of Singapore for supporting this research project through the research grant R-263-000-190-112.

Lab officers Mr.Seow Hung Cheng, Mr. Teo Thiam Teck, Mrs. Jessica, Mr. Woo Ying Chee, and Mr. Chandra readily extended help whenever I needed. I am grateful to them, for without their help, the research project would have taken a longer time. I would like to extend my sincere appreciations to Mr. Abdul Jalil Bin Din for his prompt PCB fabrication services.

As a research scholar, my stay in the National University of Singapore was made pleasant by many of my friends. Foremost among them is Anshuman Tripathi and his family, who not only shared their apartment, but also their happiness with me. His child, little Avi had been a steady source of pleasure during my stay there. Among the other friends, I would like to thank Choy Min Chee, Deng Heng, Gary, Jin Jun, Kean Chong, Krishna Mainali, Lee Kai Mun, Marecar Hadja, Ng Poh Keong, Niu Peng Ying, Ravinder Pal Singh, Sahoo Sanjib Kumar, Shivanajay Marawaha, Siew Chong, Teo Keng Hon, Xu Xinyu, and Yin Bo.

My sincere thanks to B. Eng. student Agung Prasteya Susanto, for assisting me in building hardware and compile results associated to my research project.

Above all, I thank my parents Prof. E. V. Kanakasabai, and Mrs. Swarnalatha and my sister Mrs. Lalitha Maheshwaran for giving me enough confidence and support to successfully perform this 'yagna' of doctoral research. I dedicate this thesis to them and to Prof. Ramesh Oruganti.

## **Table of Contents**

| SUMN | IARY    |                                                              | xiv  |

|------|---------|--------------------------------------------------------------|------|

| LIST | OF FIGU | RES                                                          | xvii |

| LIST | OF TAB  | LES                                                          | xxix |

| Снар | TER 1   | INTRODUCTION                                                 | 1    |

| 1.0  | Backg   | ground                                                       | 1    |

| 1.1  | Impor   | tance and Requirements of DC-DC Converters                   | 2    |

| 1.2  | Boost   | and Buck-Boost-Derived DC-DC Converters                      | 5    |

|      | 1.2.1   | Small-signal Dynamic Response Problem due to Right-Half-Plar | ie   |

|      |         | (RHP) Zero                                                   | 6    |

|      | 1.2.2   | Large-Signal Dynamic Response Problem                        | 7    |

| 1.3  | Focus   | of the Thesis                                                | 9    |

|      | 1.3.1   | Issues Studied                                               | 9    |

|      | 1.3.2   | Thesis Contributions                                         | 11   |

| 1.4  | Thesis  | s Organization                                               | 12   |

|      |         |                                                              |      |

| Снар | TER 2   | LITERATURE SURVEY OF SOLUTIONS TO DYNAMIC RESPONSE           |      |

|      |         | PROBLEMS OF BOOST AND BUCK-BOOST-DERIVED DC-DC               |      |

|      |         | Power Converters                                             | 15   |

| 2.0  | Introd  | luction                                                      | 15   |

| 2.1  | Small   | -Signal Dynamic Response Problem due to RHP Zero             | 15   |

|      | 2.1.1   | Presence of RHP Zero and its Effect on Frequency and Time    |      |

|      |         | Domain Response of the Converter                             | 16   |

|      |         |                                                              |      |

|     | 2.1.2  | Solutions Available in Literature for RHP Zero Problem          | 19 |

|-----|--------|-----------------------------------------------------------------|----|

| 2.2 | Large- | Signal Dynamic Response Problem                                 | 20 |

|     | 2.2.1  | Problems with Classical Controllers in Handling Transient       |    |

|     |        | Disturbances                                                    | 21 |

|     | 2.2.2  | Solutions to Dynamic Response Problem on Account of Model-      |    |

|     |        | Dependent Nature of Controllers                                 | 23 |

|     | A.     | Adaptive Controllers                                            | 24 |

|     | B.     | Controllers that are Independent of Converter Model             | 25 |

|     | C.     | Controllers that do not Need an Accurate Model of the converter | 29 |

| 2.3 | Chapte | er Conclusions                                                  | 30 |

#### CHAPTER 3 DYNAMIC PERFORMANCE IMPROVEMENT BY ENHANCEMENT

|     |        | IN DESIGN AND CONTROL TECHNIQUES                           | 32  |

|-----|--------|------------------------------------------------------------|-----|

| 3.0 | Introd | uction                                                     | 32  |

| 3.1 | Mitiga | ation of RHP Zero Problem by Refining the Design Approach  | 34  |

| 3.2 | Invest | igation of Dynamic Performance Improvement by Enhanced Des | ign |

|     | of Co  | ntrollers                                                  | 37  |

|     | 3.2.1  | Gain-Scheduled-PI (GSPI)-Based Scheme                      | 37  |

|     | A.     | Development of GSPI Controller                             | 38  |

|     | B.     | Simulation Results and Discussions                         | 39  |

|     | 3.2.2  | Fuzzy Logic-Based Approach                                 | 42  |

|     | A.     | Re-design of Benchmark PI Controllers                      | 42  |

|     | B.     | Fuzzy Logic Controller- Implementation Details             | 45  |

|     |        |                                                            |     |

|       | C.      | Simulation and Experimental Results and Comparison of       |    |

|-------|---------|-------------------------------------------------------------|----|

|       |         | Performance with Linear-PI Controller                       | 48 |

| 3.3   | A N     | ote on Other Linear Compensators                            | 53 |

| 3.4   | Disc    | cussions and Conclusions                                    | 56 |

| Снарт | TER 4   | NON-LINEAR FUNCTION CONTROLLER: A SIMPLE AND COST-          |    |

|       |         | EFFECTIVE ALTERNATIVE TO FLC                                | 58 |

| 4.0   | Introdu | uction                                                      | 58 |

| 4.1   | Analys  | sis of FLC Structure in Power Converter Control             | 61 |

|       | 4.1.1.  | Shape of Input and output Membership Functions              | 61 |

|       | 4.1.2.  | Rule Base Structure                                         | 62 |

| 4.2   | Toepli  | tz Rule Tables and Reduction of Two-input FLC to NLFC       | 64 |

| 4.3   | NLFC    | - The Economical and Fast "FLC" and its Circuit Realization | 66 |

| 4.4   | Handli  | ing Asymmetrical Input Membership Functions                 | 68 |

| 4.5   | Verific | cation of Equivalence Between NLFC and FLC                  | 71 |

| 4.6   | NLFC    | : Performance Analysis                                      | 72 |

|       | 4.6.1   | NPIC/PI-FLCs Versus Linear-PI Controllers                   | 73 |

|       | 4.6.2   | Transient Performance Improvement in NPIC                   | 75 |

| 4.7   | Examp   | ble System and NPIC/PI-FLC Description                      | 76 |

|       | 4.7.1   | Boost Converter Specifications                              | 76 |

|       | 4.7.2   | NPIC/PI-FLC Description                                     | 77 |

| 4.8   | Derivi  | ng the Equivalent PI-FLC from NPIC                          | 79 |

|       | 4.8.1   | PI-FLC Equivalent to NPIC                                   | 79 |

|       | 4.8.2   | Performance comparison of PI-FLC and NPIC                   | 80 |

| 4.9  | Experi  | mental Results                                                            | 81     |

|------|---------|---------------------------------------------------------------------------|--------|

| 4.10 | Stabili | ty Analysis of NPIC                                                       | 87     |

|      | 4.10.1  | Gain-Margin without Considering System Non-linearities:                   | 88     |

|      | 4.10.2  | Describing Function Approach- Gain Margin Considering NPI                 | C's    |

|      |         | Non-linearity                                                             | 89     |

| 4.11 | Chapte  | er Conclusions                                                            | 91     |

|      |         |                                                                           |        |

| Снар | ter 5   | NOVEL TRI-STATE CLASS OF BOOST AND BUCK-BOOST-                            |        |

|      |         | DERIVED CONVERTERS WITH FAST DYNAMICS                                     | 93     |

| 5.0  | Backg   | round                                                                     | 93     |

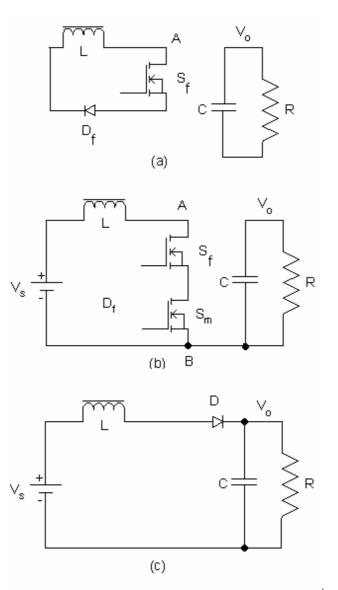

| 5.1  | Tri-Sta | ate Class of Converters- Motivation                                       | 94     |

| 5.2  | Tri-Sta | ate Boost Converter                                                       | 97     |

|      | 5.2.1   | DC Analysis                                                               | 101    |

|      | A.      | Boost Voltage Gain                                                        | 101    |

|      | B.      | Inductor Current Ripple (Iripple)                                         | 101    |

|      | C.      | Average Inductor Current (I <sub>L</sub> )                                | 102    |

|      | D.      | Peak Inductor Current (I <sub>p</sub> )                                   | 102    |

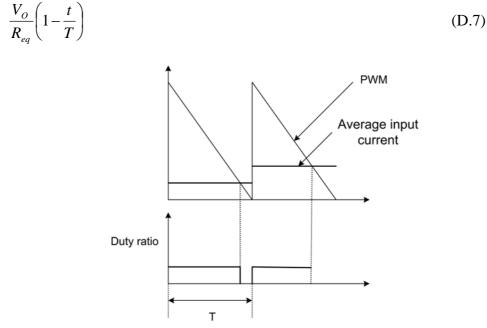

|      | E.      | Average Input Current                                                     | 102    |

|      | F.      | Output Voltage Ripple (V <sub>o_ripple</sub> )                            | 103    |

|      | 5.2.2   | Control Characteristics- A simple 'Constant-D <sub>o</sub> ' Control Meth | od 103 |

|      | 5.2.3   | Small-Signal Characteristics                                              | 103    |

|      | 5.2.4   | Simulation and Experimental Verification                                  | 105    |

|      | A.      | Open-Loop Performance                                                     | 107    |

|     | B.                                          | Closed-Loop Performance                                     | 110    |

|-----|---------------------------------------------|-------------------------------------------------------------|--------|

| 5.3 | Tri-St                                      | ate Flyback Converter                                       | 114    |

|     | 5.3.1                                       | Tri-State Flyback Converter - Switching Sequence and Theore | etical |

|     |                                             | Waveforms                                                   | 115    |

|     | 5.3.2                                       | Tri-State Flyback Converter- Small-Signal Characteristics   | 116    |

|     | 5.3.3                                       | Simulation and Experimental Results                         | 118    |

|     | 5.3.4                                       | Closed-Loop Performance                                     | 122    |

| 5.4 | Importance of Tri-state Class of Converters |                                                             | 123    |

| 5.5 | Chapt                                       | er Conclusions                                              | 124    |

## CHAPTER 6 DUAL-MODE CONTROL OF TRI-STATE CONVERTER FOR

|     |        | IMPROVED PERFORMANCE                                                     | 126 |

|-----|--------|--------------------------------------------------------------------------|-----|

| 6.0 | Backg  | round                                                                    | 126 |

| 6.1 | Dual-r | node control (DMC) scheme- Motivation                                    | 127 |

|     | 6.1.1  | 'Constant-D <sub>o</sub> ' Control Scheme- Limit on the Voltage Gain     | 128 |

|     | 6.1.2  | 'Constant-D <sub>o</sub> ' Control Scheme- Magnitude of Inductor Current | 128 |

| 6.2 | Dual N | Mode Control (DMC) Approach                                              | 130 |

|     | 6.2.1  | Tri-State Boost Converter- Small-Signal Model                            | 131 |

|     | 6.2.2  | Grouping of Control Inputs and Converter States                          | 131 |

|     | 6.2.3  | Control Method 1- Direct Dual-Mode Control (DDMC)                        | 133 |

|     | A.     | Significance of K-Factor                                                 | 135 |

|     | B.     | Design of Controllers for DDMC                                           | 135 |

|     | 6.2.4  | Control Method-II: Indirect Dual-mode Control (IDMC)                     | 136 |

|     |        |                                                                          |     |

| 6.3 | Simulation and Experimental Results |                                                              | 138  |

|-----|-------------------------------------|--------------------------------------------------------------|------|

|     | 6.3.1                               | Verification of Small-Signal Model                           | 138  |

|     | 6.3.2                               | Closed-Loop Performance- Controller Design                   | 144  |

|     | 6.3.3                               | Closed-Loop Performance- Simulation and Experimental Results | :145 |

|     | 6.3.4                               | Efficiency Comparison                                        | 151  |

| 6.4 | Chapte                              | er Conclusions                                               | 152  |

| CHAPTER 7 |        | DESIGN AND EVALUATION OF TRI-STATE BOOST CONVERTER                             | 154 |

|-----------|--------|--------------------------------------------------------------------------------|-----|

| 7.0       | Introd | uction                                                                         | 154 |

| 7.1       | Trade  | -Off in DMC of Tri-State Boost Converter                                       | 155 |

| 7.2       | Conve  | erter Disturbance Margins                                                      | 157 |

|           | 7.2.1  | Output Voltage Margin (V <sub>o_margin</sub> )                                 | 158 |

|           | 7.2.2  | Input Voltage Margin (V <sub>s_margin</sub> )                                  | 159 |

|           | 7.2.3  | Load Current/Power Margin ( $(\Delta I_o)_{max}$ [ or $(\Delta P_o)_{max}$ ] ) | 160 |

|           | 7.2.4  | Relationships between Disturbance Margins and K-factor                         | 162 |

|           | A.     | IDMC Scheme                                                                    | 162 |

|           | B.     | DDMC Scheme                                                                    | 163 |

| 7.3       | Desig  | n of Tri-state Boost Converter                                                 | 164 |

|           | 7.3.1  | Step 1: Disturbance Margins- Selection of K-Factor                             | 165 |

|           | 7.3.2  | Step 2: Selection of Boost Inductance                                          | 165 |

|           | 7.3.3  | Step 3: Correction of K-factor                                                 | 166 |

|           | 7.3.4  | Step 4: Design of Output Capacitor 'C'                                         | 166 |

|           | 7.3.5  | Step 5: Choice of Switches                                                     | 166 |

|     | 7.3.6  | Step 6: Design of controllers                                  | 167  |

|-----|--------|----------------------------------------------------------------|------|

| 7.4 | Design | n Example                                                      | 168  |

|     | 7.4.1  | Step 1: Disturbance Margin- Selection of K-Factor              | 169  |

|     | 7.4.2  | Step 2: Seletion of boost inductance                           | 169  |

|     | 7.4.3  | Step 3: Correction of K-factor                                 | 170  |

|     | 7.4.4  | Step 4: Selection of Output Capacitor C                        | 171  |

|     | 7.4.5  | Step 5: Design of Controllers                                  | 173  |

|     | А.     | Design of Current Controller $K_2(s)$ for DDMC                 | 173  |

|     | B.     | Design of $D_f$ Controller $K_3(s)$ for IDMC                   | 173  |

| 7.5 | Result | s and Discussions                                              | 174  |

|     | 7.5.1  | Investigation of Dynamic Performance of Tri-state Boost Conver | rter |

|     |        | under IDMC Scheme                                              | 175  |

|     | A.     | Step Changes in Reference Voltage (V <sub>ref</sub> )          | 175  |

|     | B.     | Step Changes in Load Conditions                                | 176  |

|     | C.     | Step Changes in Input Voltage                                  | 177  |

|     | 7.5.2  | Investigation of Dynamic Performance of Tri-state Boost Conver | rter |

|     |        | under DDMC Scheme                                              | 179  |

|     | A.     | Step Changes in Reference Voltage (V <sub>ref</sub> )          | 179  |

|     | B.     | Step Changes in Load Conditions                                | 182  |

|     | C.     | Step Changes in Input Voltage                                  | 183  |

|     | 7.6    | Chapter Conclusions                                            | 184  |

| Сна | PTER 8 | APPLICATION OF TRI-STATE CONTROL CONCEPT IN SINGLE-            |      |

### PHASE POWER FACTOR CORRECTION RECTIFIERS 186

ix

| 8.0  | Introd | luction                                                       | 186      |

|------|--------|---------------------------------------------------------------|----------|

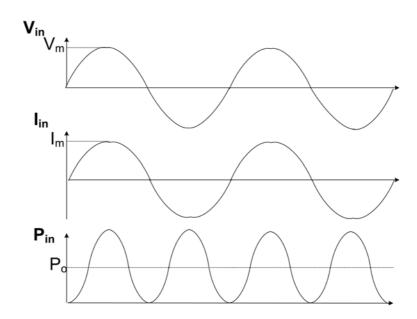

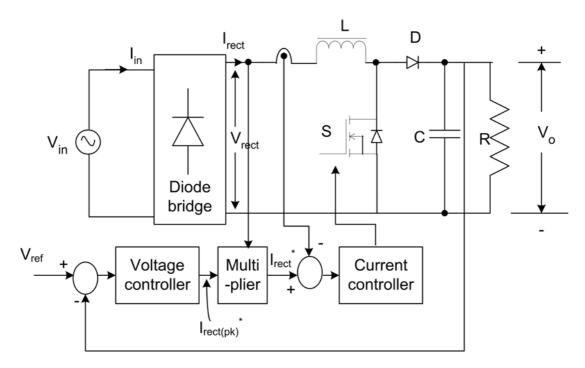

| 8.1  | Achie  | wing Steady-State Goals in a PFC Rectifier                    | 187      |

| 8.2  | Suitał | bility of 'Tri-state' Class of Converters in PFC Applications | 191      |

|      | 8.2.1  | Suitability of Tri-state Boost Converter                      | 191      |

|      | 8.2.2  | Suitability of Tri-state Buck-Boost-Based Converters          | 193      |

| 8.3  | Casca  | de-Buck-Boost PFC Converter (CBB-PFC)                         | 194      |

|      | 8.3.1  | CBB Converter- Degrees of Control-Freedom                     | 195      |

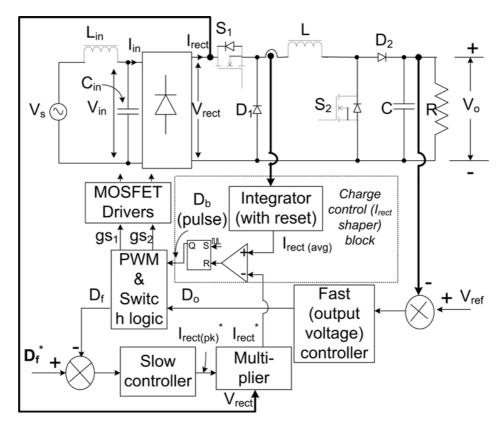

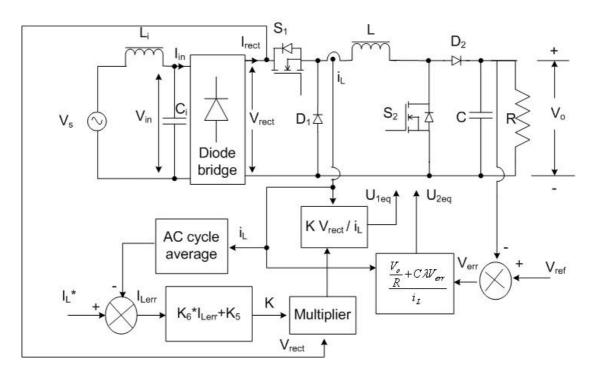

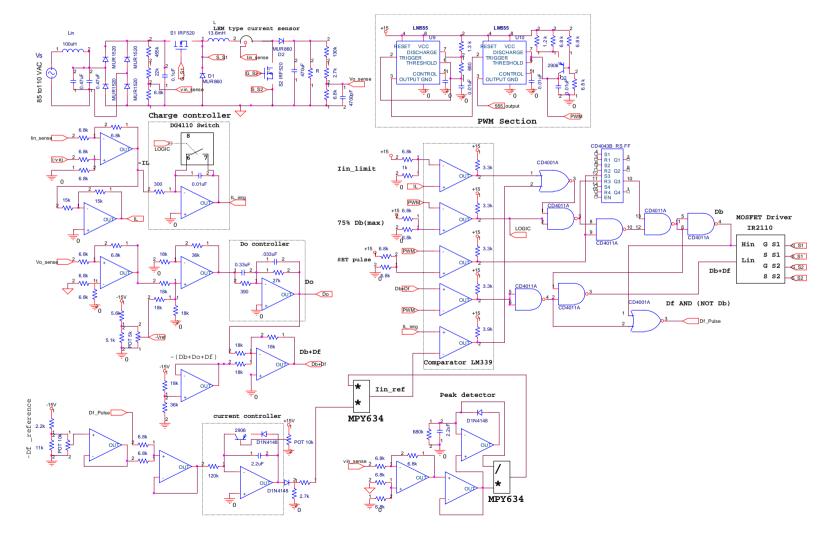

|      | 8.3.2  | Dual-Mode Control Scheme for CBB-PFC                          | 196      |

|      | A.     | Control Requirements and Grouping of Control Inputs of CBE    | 8-PFC196 |

|      | B.     | Dual-Mode Control (DMC) Scheme                                | 198      |

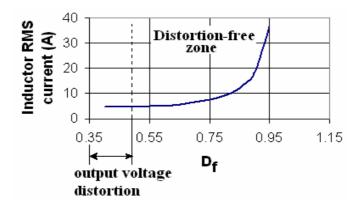

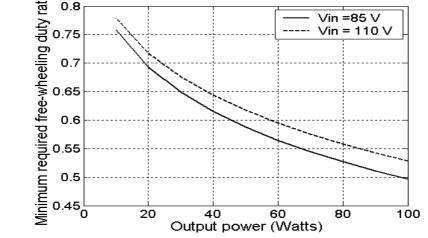

|      | C.     | DMC of CBB-PFC- Trade-Offs and Limitations                    | 199      |

|      | 8.3.3  | Selection of Power/Control Circuit Components                 | 202      |

|      | A.     | Selection of Inductance 'L'                                   | 202      |

|      | B.     | Selection of Output Capacitor 'C'                             | 204      |

|      | C.     | Selection of Diodes and Switches                              | 204      |

|      | D.     | Controllers and Hard-limits Set in the DMC Scheme             | 205      |

|      | 8.3.4  | Simulation and Experimental Results                           | 206      |

|      | 8.3.5  | Comparison of CBB-PFC with Popular PFC Rectifiers             | 215      |

|      | A.     | CBB-PFC Versus Stand-Alone Boost PFC Rectifier                | 215      |

|      | B.     | CBB-PFC Versus Cascaded Boost-Buck PFC Rectifier              | 216      |

|      | C.     | Dual-Mode Versus Other Control Techniques of CBB-PFC          | 218      |

| 8.4  | Chapt  | er Conclusions                                                | 223      |

| Снар | TER 9  | CONCLUSIONS AND FUTURE WORK                                   | 225      |

\_

| 9.0   | Background                                                           | 225 |

|-------|----------------------------------------------------------------------|-----|

| 9.1   | Mitigation of RHP Zero Problem by Refining the Design Approach       | 226 |

| 9.2   | Dynamic Performance Improvement by Modifications in the Employed     |     |

|       | Controller                                                           | 226 |

| 9.3   | Non-linear function controller                                       | 227 |

| 9.4   | Dynamic Performance Improvement by Modifications in the Converter    |     |

|       | Topology                                                             | 228 |

| 9.5   | Investigation of Tri-state Converters for Performance Improvement in |     |

|       | Single-Phase AC-DC PFC Applications                                  | 231 |

| 9.6   | Future work                                                          | 232 |

|       |                                                                      |     |

| Refer | RENCES                                                               | 233 |

| Appen | IDIX A TRI-STATE BOOST CONVERTER: DERIVATION OF COMPLETE             |     |

|       | SMALL-SIGNAL TRANSFER FUNCTION MODEL                                 | 240 |

| A.0   | Background                                                           | 240 |

| A.1   | Complete Transfer Function- Derivation                               | 240 |

| A.2   | Derivation of D <sub>b</sub> -to-State Transfer Functions            | 242 |

| A.3   | Derivation of $D_0$ -to-State Transfer Functions                     | 244 |

| A.4   | Control-to-State Transfer Functions in the Absence of Parasitics     | 245 |

|       |                                                                      |     |

| APPEN | IDIX B MATLAB-SIMULINK MODELS OF THE VARIOUS                         |     |

|       | <b>CONVERTER-CONTROLLER SCHEMES</b>                                  | 247 |

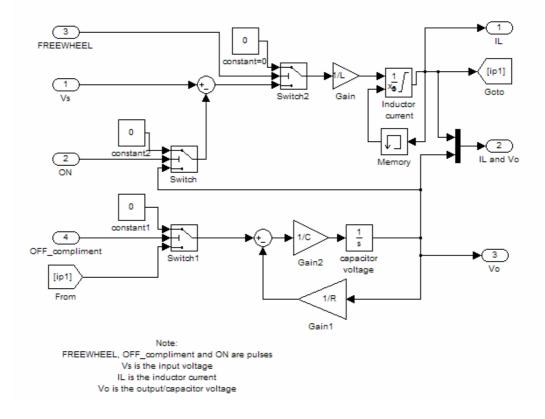

| B.0 | Tri-State Boost Converter | 247 |

|-----|---------------------------|-----|

|     |                           |     |

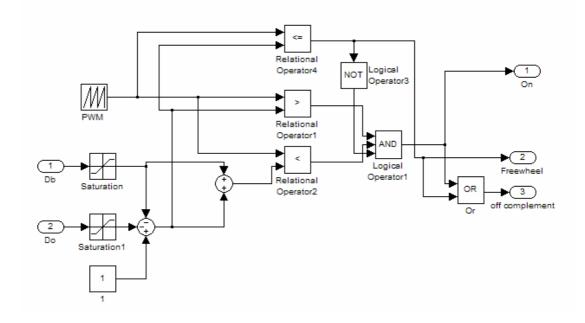

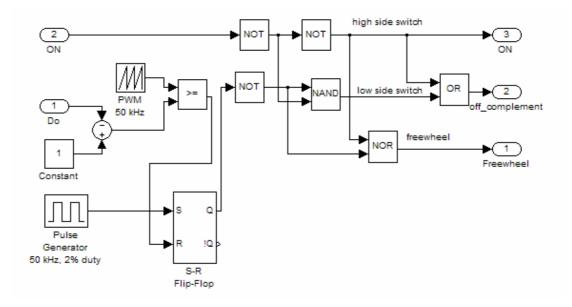

| B.1 | Switch   | Logic                                                        | 248   |

|-----|----------|--------------------------------------------------------------|-------|

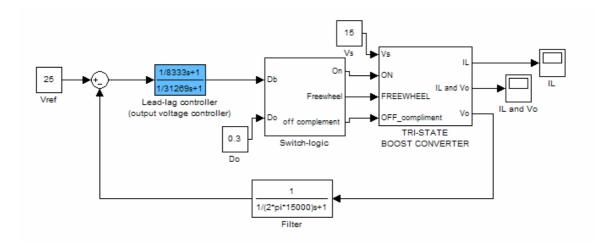

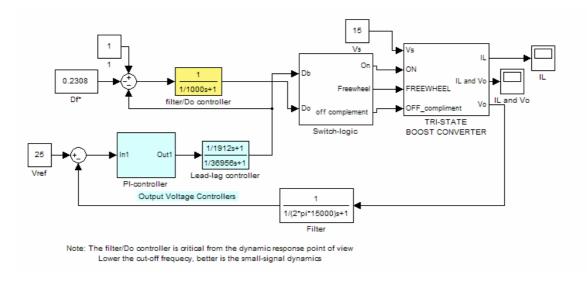

| B.2 | Tri-Stat | e Boost Converter- 'Constant-D <sub>o</sub> ' Control Scheme | 248   |

| B.3 | Tri-Stat | e Boost Converter- Direct Dual-Model Control (DDMC) Schem    | e249  |

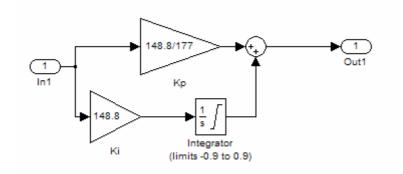

|     | B.3.1    | Subsystem 'PI Controller2'                                   | 249   |

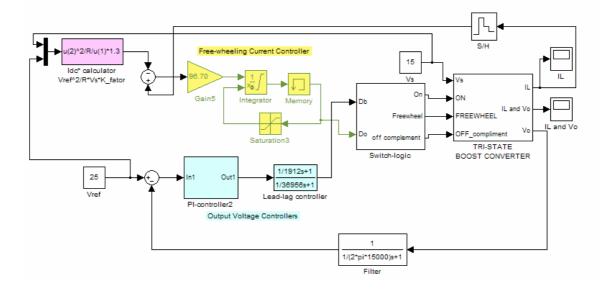

| B.4 | Tri-Stat | e Boost Converter- Indirect Dual-Model Control (IDMC) Schen  | ne250 |

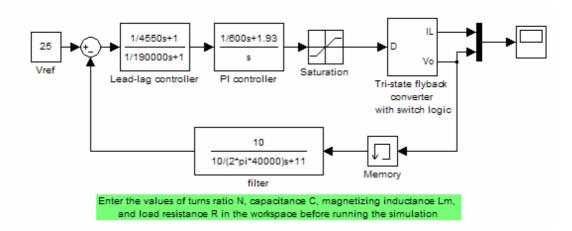

| B.5 | Tri-Stat | e Flyback Converter- 'Constant-Do' Control Scheme            | 250   |

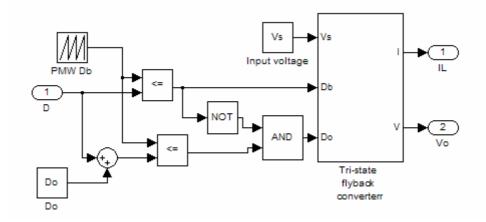

|     | B.5.1    | Subsystem 'Tri-state Flyback Converter with Switch Logic'    | 251   |

|     | B.5.2    | Subsystem 'Tri-state Flyback Converter'                      | 251   |

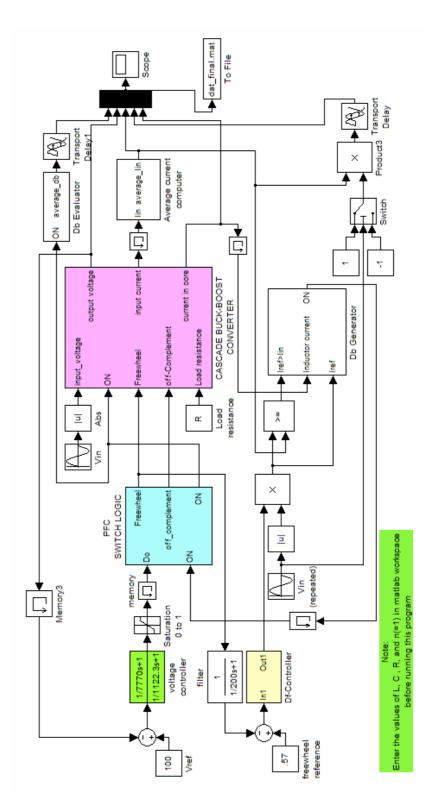

| B.6 | Dual-m   | ode Control of Cascade Buck-Boost Power Factor Correction (C | BB-   |

|     | PFC) C   | onverter                                                     | 252   |

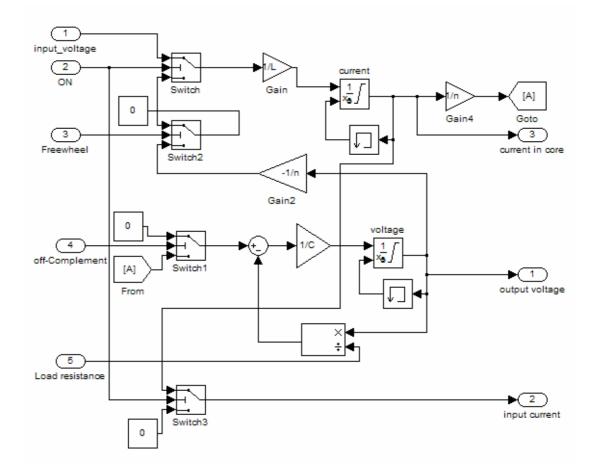

|     | B.6.1    | Subsystem 'CASCADE BUCK-BOOST CONVERTER'                     | 253   |

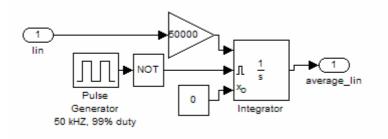

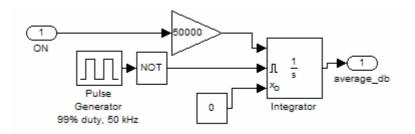

|     | B.6.2    | Subsystem 'AVERAGE CURRENT COMPUTER'                         | 253   |

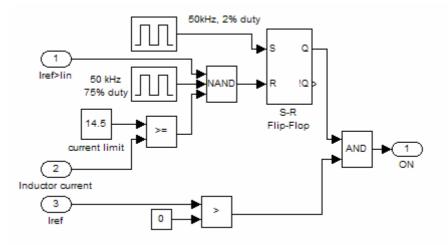

|     | B.6.3 St | ubsystem 'PFC SWITCH LOGIC'                                  | 254   |

|     | B.6.4    | Subsystem 'Db Evaluator'                                     | 254   |

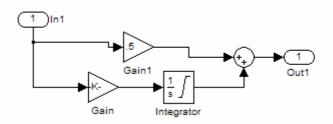

|     | B.6.5    | Subsystem 'Df Controller'                                    | 254   |

|     | B.6.6    | Subsystem 'Db Generator'                                     | 255   |

| B.7 | Classica | al Boost Converter (Averaged Model) Controlled by Gain-Sched | uled  |

|     | PI Cont  | roller                                                       | 255   |

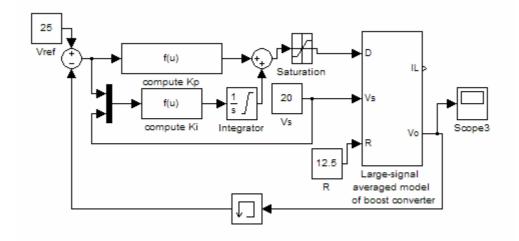

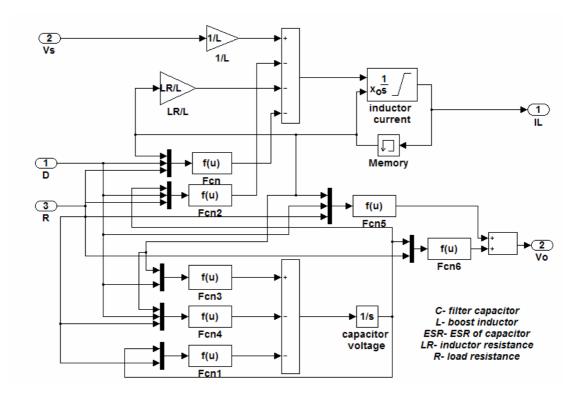

|     | B.7.1    | Subsystem ''Large-signal averaged model of boost converter'  | 256   |

| B.8 | Classica | al Boost Converter (Averaged Model) Controlled by Linear-PI  |       |

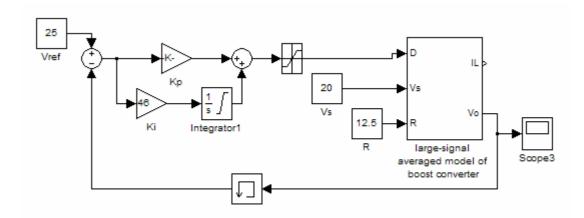

|     | Control  | ler                                                          | 257   |

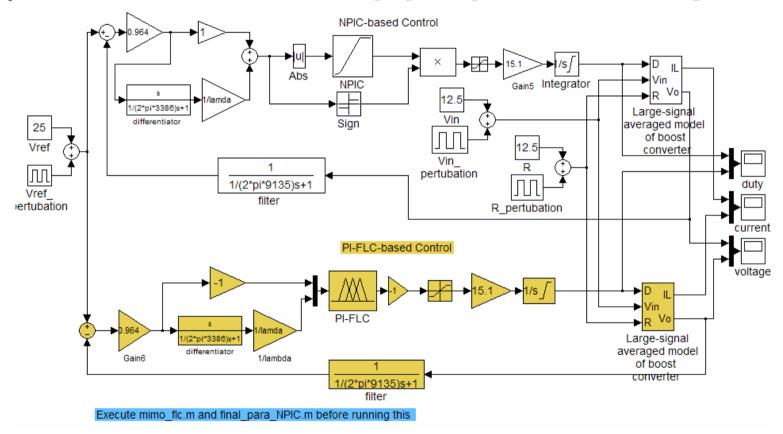

| B.9 | Classica | al Boost Converter (Averaged Model) Controlled by PI-FLC and | l     |

|     | NPIC C   | Controllers                                                  | 258   |

|     |          |                                                              |       |

|      |         | CONVERTER/CONTROL SCHEMES                                      | 259 |

|------|---------|----------------------------------------------------------------|-----|

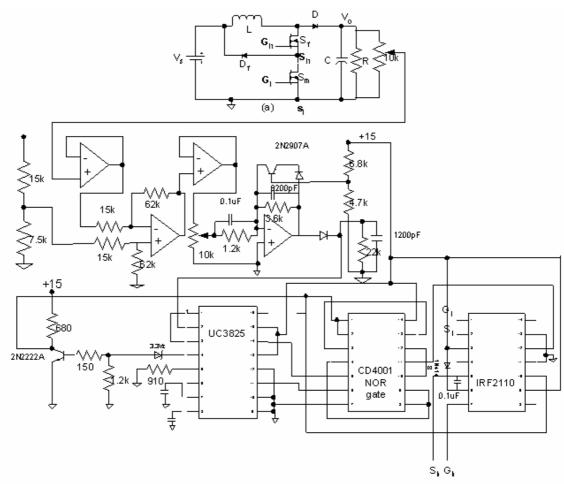

| C.0  | Tri-sta | te Boost Converter- 'Constant-D <sub>o</sub> ' Control Scheme  | 259 |

| C.1  | Classi  | cal Boost Converter- PI-based Control Scheme                   | 260 |

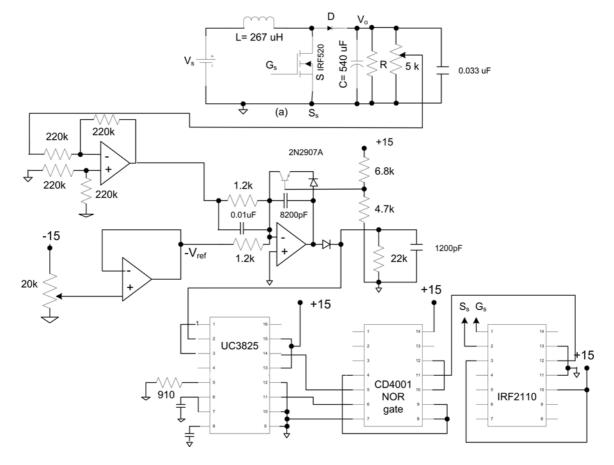

| C.2  | Tri-St  | ate Boost Converter- Direct Dual-Mode Control Scheme           | 261 |

| C.3  | Tri-St  | ate Boost Converter- Indirect Dual-Mode Control Scheme         | 262 |

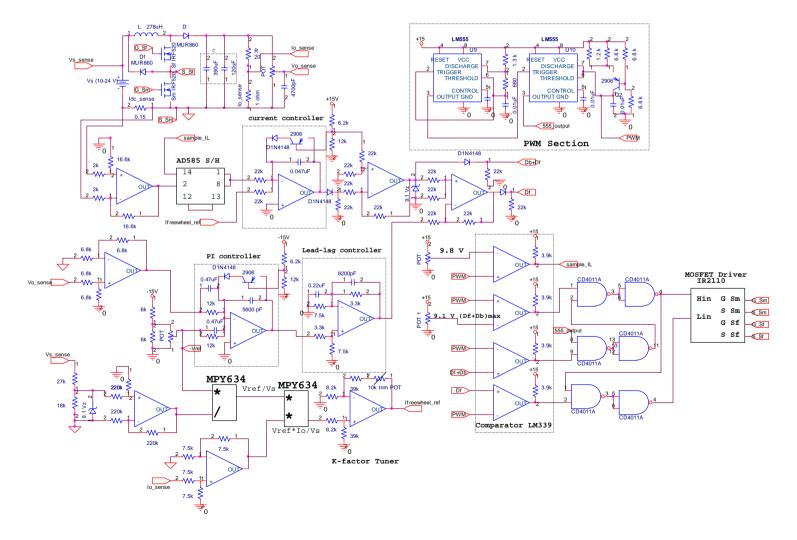

| C.4  | Tri-St  | ate Flyback Converter- 'Constant-Do' Control Scheme            | 263 |

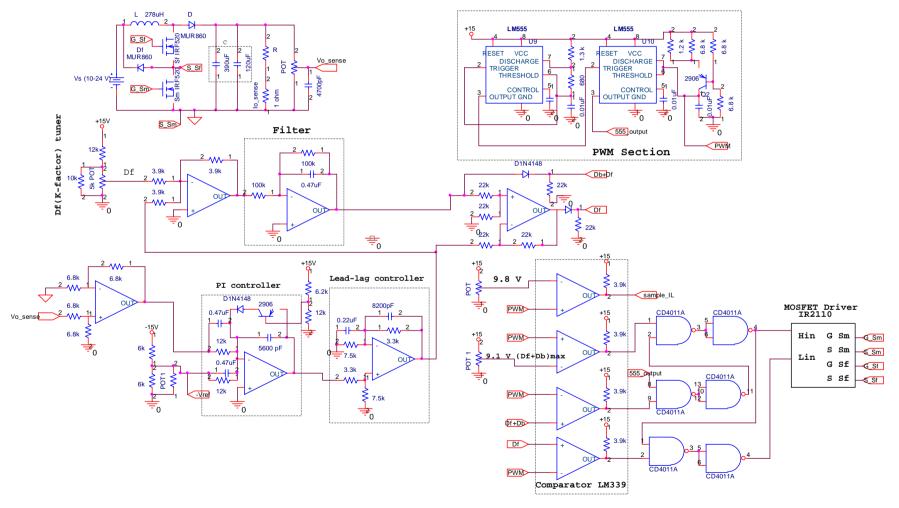

| C.5  | Dual-I  | Mode Control of Cascade-Buck-Boost PFC Converter- Circuit      |     |

|      | Schem   | natic                                                          | 264 |

|      |         |                                                                |     |

| APPE | NDIX D  | SINGLE-PHASE AC-DC POWER FACTOR CORRECTION                     |     |

|      |         | <b>Rectifiers: A Survey</b>                                    | 265 |

| D.0  | Introd  | uction                                                         | 265 |

| D.1  | Single  | -Phase AC-DC Rectifiers- Overview of Problems                  | 265 |

| D.2  | Applic  | cations of Boost and Buck-Boost converters in Single-Phase AC- | DC  |

|      | Power   | Factor Correction and Associated Problems                      | 268 |

|      | D.2.1   | Energy Storage on Load-side Capacitor                          | 268 |

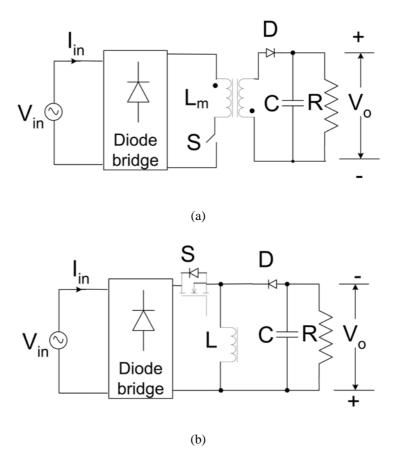

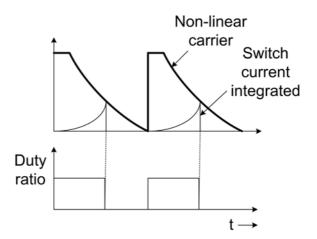

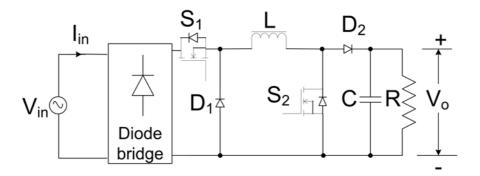

|      | A.      | Stand-Alone Boost PFC Rectifier                                | 268 |

|      | B.      | Single-Switch Buck-Boost/Flyback PFC Rectifier                 | 273 |

|      | D.2.2   | Energy Storage on the Intermediate Bus Capacitor               | 277 |

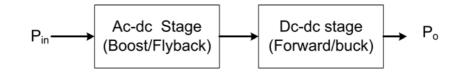

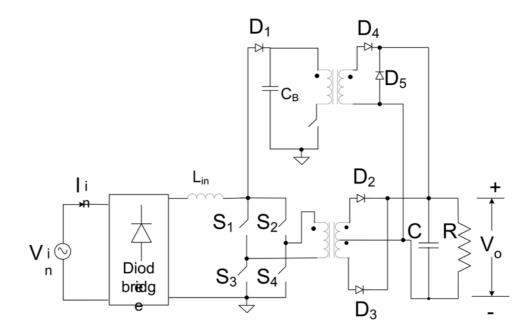

|      | A.      | Cascaded PFC Scheme                                            | 277 |

|      | B.      | Single-Stage PFC {S <sup>2</sup> PFC} Schemes                  | 278 |

|      | C.      | Parallel PFC Schemes (PPFC)                                    | 279 |

|      | D.2.3   | Energy Storage in Cascade Buck-Boost Converter                 | 280 |

### APPENDIX C HARDWARE IMPLEMENTATION DETAILS OF THE VARIOUS

### **Summary**

Classical boost and buck-boost converters and their derivatives are used in dcdc switch-mode power supplies and in single-phase ac-dc power factor correction (PFC) applications. In dc-dc applications, the small-signal dynamic performance of these converters operating in continuous-conduction mode is slow due to the presence of a right-half plane (RHP) zero in their control-to-output transfer function. Their large-signal dynamic performance is also sluggish, a prime reason being the linear nature of controllers commonly used with these converters. The focus of this thesis is to analyze and propose solutions for mitigating and overcoming these dynamic performance problems.

The proposed solutions are obtained in the following two ways.

- 1. By enhancing the converter design and by modifications in the employed controller

- 2. By modifying the converter topology.

Among the solutions related to the first approach, to begin with, it is shown that the small-signal dynamic performance problem of a boost converter is mitigated by appropriate selection of boost inductance. The pros and cons of the proposed design are discussed.

Following the first approach, the performance of boost converter is investigated with linear-PI controller, gain-scheduled PI controller (GSPI), and fuzzy logic controller (FLC). Linear-PI controller offers a better small-signal performance at the designed operating point than those offered by GSPI and FLC. For large-signal transients, FLC offers a dynamic performance better than that offered by the linear-PI controller. For explaining this transient response offered by FLC, the structure of several FLCs used in power-converter-control-applications (PCCA) in the past are analyzed. It is shown that most of these FLCs can be approximated by a single-inputsingle-output nonlinearity. The resulting 'Non-linear Function Controller' (NLFC) explains the rationale behind the good large-signal performance offered by FLCs. Besides, the design of NLFC (and indeed FLCs) to obtain good small-signal performance becomes logical. The proposed NLFC can replace FLCs in PCCA. A Non-Linear PI Controller (type of NLFC) is designed and tested with a boost converter to verify the advantages offered by NLFCs.

Another solution to dynamic response problem that falls under the second category relates to the novel 'tri-state' class of boost and buck-boost-derived converters proposed and analyzed in detail in this thesis. These converters have an extra-degree of control-freedom in the form of an 'inductor-free-wheeling' interval, using which the dynamic response problem due to RHP zero is avoided. Excellent improvement in dynamic performance over those of the classical counterparts is verified experimentally.

The additional control-freedom of tri-state boost converter is exploited by three novel control methods, namely,

- 1. 'Constant- $D_o$ ' control method

- 2. Direct dual-mode control (DDMC) method

- 3. Indirect dual-mode control (IDMC) method.

While the 'constant- $D_o$ ' control method focuses primarily on improving the dynamic performance, the multi-variable IDMC and DDMC schemes improve both the dynamic and steady-state (i.e. operating efficiency) performances of the converter.

A procedure for designing power and control components of a tri-state boost converter employing DMC scheme is also given.

Tri-state converters, due to their additional control-freedom constitute potential candidates for application as PFC rectifiers that have to meet multiple objectives, namely, drawing a sinusoidal input current at unity power factor, delivering a well-regulated dc voltage, and ensuring fast dynamic response. A study on the application of tri-state converters in PFC applications is presented. A simple 'dual-mode' control method for a PFC rectifier employing cascade buck-boost (CBB) converter (a tri-state converter) is proposed. This control method exploits the extra control-freedom in meeting the PFC goals. The anticipated good transient and steady-state performances are verified experimentally. A qualitative comparison of CBB-PFC with popular PFC converters is also given.

The report concludes with an identification of future work related to the tri-state class of power converters.

**Keywords:** boost, buck-boost, cascade buck-boost, controller, fuzzy logic controller non-linear function controller, non-linear PI-controller, power converter, Tri-state.

# List of Figures

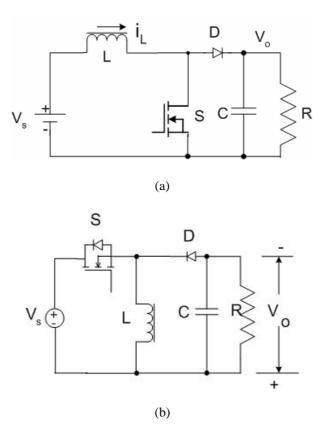

| Fig. 1.1  | Circuit diagrams (a) Classical single-switch boost converter (b)<br>Classical single-switch buck-boost converter.                                                                                                                                                                                                                                                                                                                                                           | 5  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

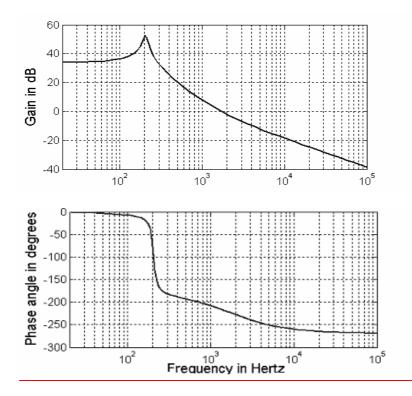

| Fig. 2.1. | Bode plot of Control-to-output transfer function of a classical boost converter at $V_s = 12.5$ V, $V_o = 25$ V, and $R = 12.5 \Omega$ .                                                                                                                                                                                                                                                                                                                                    | 17 |

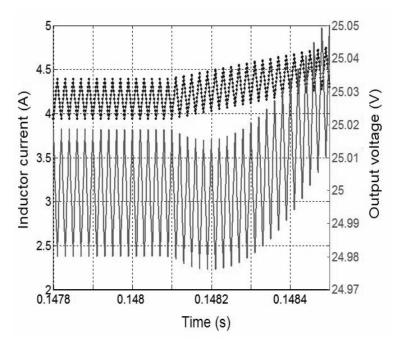

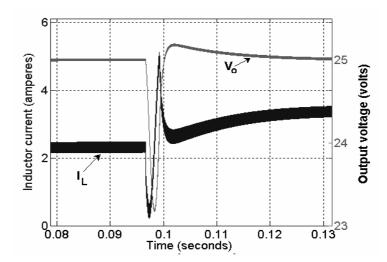

| Fig. 2.2. | Inductor current (upper) and output voltage (lower) waveforms of classical boost converter for a step increase in duty ratio from $D = 0.5$ to 0.51 at $V_s = 12.5$ V, $V_o = 25$ V, $I_o = 2$ A.                                                                                                                                                                                                                                                                           | 18 |

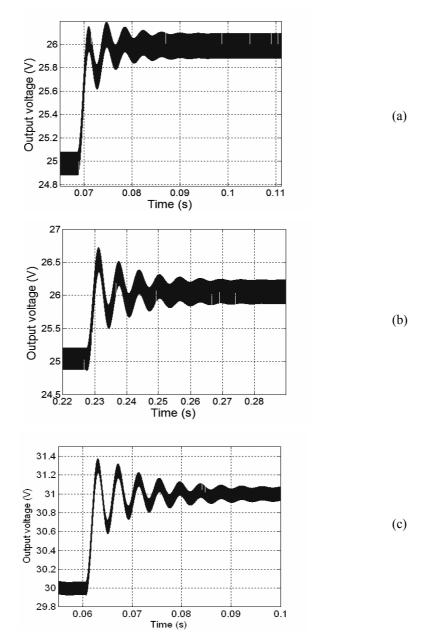

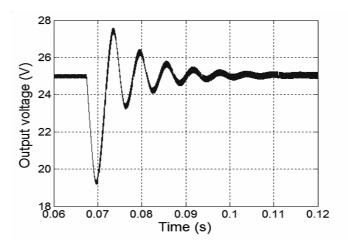

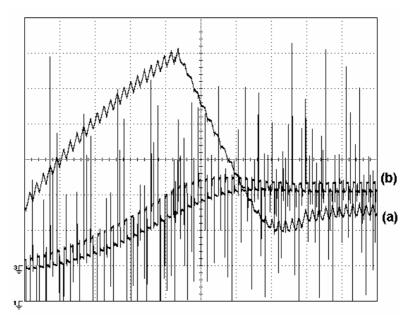

| Fig. 2.3. | Demonstration of model-dependent nature of linear controllers-<br>Simulation results (a) Transient response at deign operating point<br>$V_s=15 \ V$ , $R = 25 \ \Omega$ , $V_o$ transient from 25 V to 26 V(b) Transient<br>response at a different operating point $V_s=10 \ V$ , $R = 25 \ \Omega$ , $V_o$<br>transient from 25 V to 26 V (c) Transient response at a different<br>operating point $V_s=15 \ V$ , $R = 25 \ \Omega$ , $V_o$ transient from 30 V to 31 V. | 22 |

| Fig. 2.4. | Large-signal transient response offered by linear controller for a step change in $V_s$ (from 15 V to 10 V) at $V_o = 25$ V and $I_o = 1$ A.                                                                                                                                                                                                                                                                                                                                | 23 |

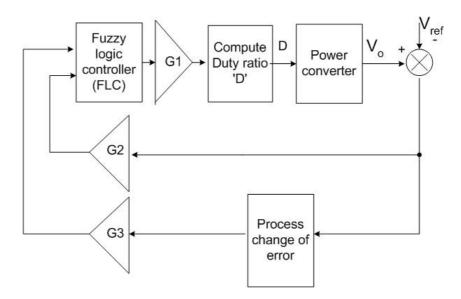

| Fig. 2.5. | Fuzzy logic controlled (FLC) power electronic converter.                                                                                                                                                                                                                                                                                                                                                                                                                    | 26 |

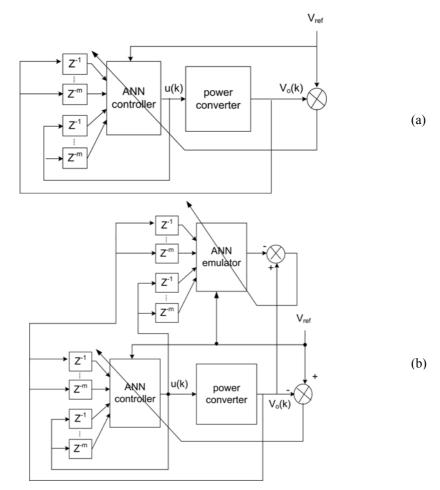

| Fig. 2.6. | ANN controllers for power converters (a) Direct control (b) Indirect control using emulator.                                                                                                                                                                                                                                                                                                                                                                                | 28 |

| Fig. 3.1. | Mitigation of RHP zero problem.                                                                                                                                                                                                                                                                                                                                                                                                                                             | 35 |

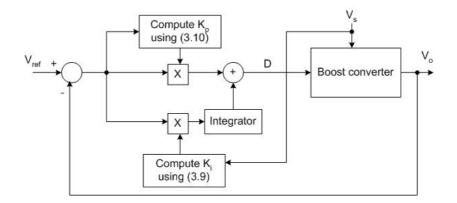

| Fig. 3.2. | Gain-scheduled-PI (GSPI) controller-boost converter: Schematic.                                                                                                                                                                                                                                                                                                                                                                                                             | 39 |

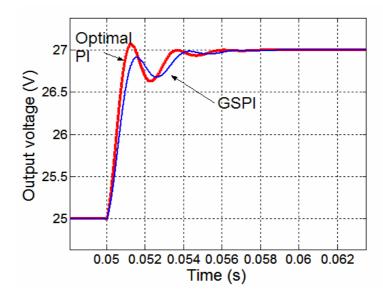

| Fig. 3.3. | Performance comparison of GSPI and PI for step change in reference voltage from 25 V to 27 V at 0.05 s at $V_s = 20$ V, $R = 50 \Omega$ .                                                                                                                                                                                                                                                                                                                                   | 40 |

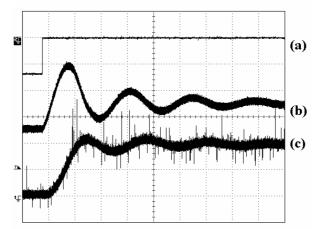

| Fig. 3.4. | Experimental step response of the boost converter with PI controller<br>for a step change in reference voltage from $V_{ref}=22$ V to $V_{ref}=24$ V,<br>at R = 12 $\Omega$ , $V_s = 10$ V (a) Step- marks the instant when the<br>reference voltage changes (b) Inductor current (c) Output voltage<br>(channel in ac coupling mode); Scale: voltage: 1 V/div, current: 1<br>A/div, time: 2ms/div.                                                                         | 44 |

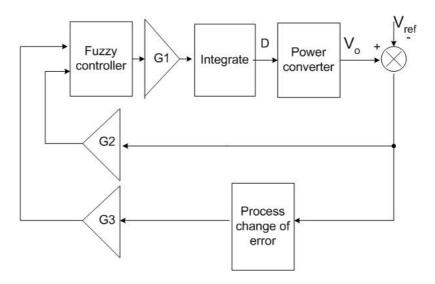

| Fig. 3.5. | FLC-based control of dc-dc boost power electronic converter.                                                                                                                                                                                                                                                                                                                                                                                                                | 46 |

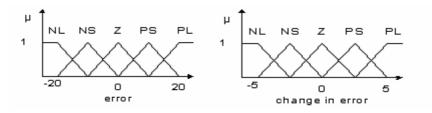

| Fig. 3.6  | Membership functions for inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                            | 46 |

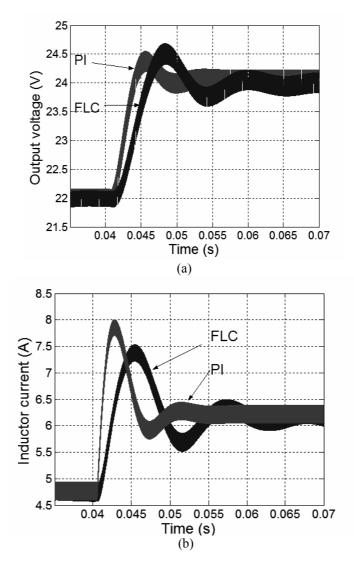

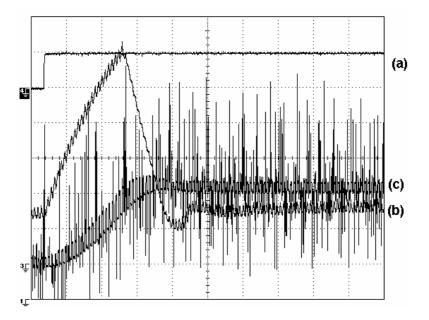

| Fig. 3.7. | Simulated reference-voltage-step-up transients offered by FLC and PI controllers at $V_s = 10$ V, $I_o = 2$ A, step of $V_{ref}$ from 22 V to 24 V (a) output voltage (b) inductor current.                                                                                                                                                                                                                                                                                 | 49 |

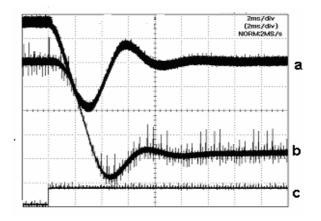

| Fig. 3.8.  | Experimental step response of the classical boost converter with FLC for a large step-change in reference voltage $V_{ref}$ at $V_s = 11$ V, $I_o = 2.1$ A (when $V_o = 24.9$ V) (a) Inductor current (b) $V_{ref}$ step change from 24.9 V to 20.9 V (c) Step $V_{ref}$ (inverted); Scale: voltage: 1 V/div, current: 1A/div, time: 2ms/div. | 50 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

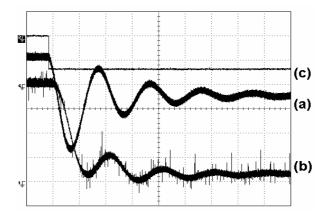

| Fig. 3.9.  | Experimental step response of the classical boost converter with PI controller for a large-step change in $V_{ref}$ at $V_s = 11$ V, $I_o = 2.0$ A (when $V_o = 24.9$ V) (a) Inductor current (b) $V_{ref}$ step from 24.69 V to 20.77 V (c) Step $V_{ref}$ ; Scale: voltage: 1 V/div, current: 1A/div, time: 2 ms/div.                       | 50 |

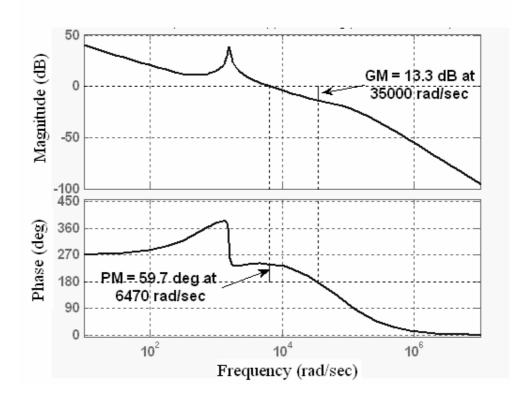

| Fig. 3.10. | Frequency response plot with re-designed controller.                                                                                                                                                                                                                                                                                          | 54 |

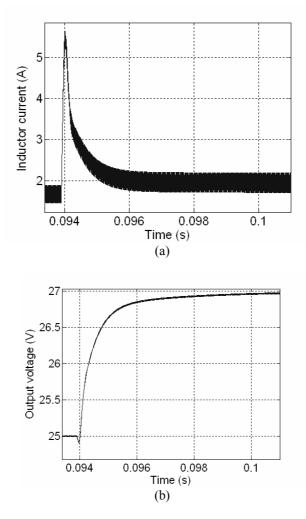

| Fig. 3.11. | Simulated reference-voltage-step-up transients offered by redesigned controller at $V_s = 15$ V, $I_o = 1$ A, step of $V_{ref}$ from 25 V to 27 V (a) output voltage (b) inductor current.                                                                                                                                                    | 55 |

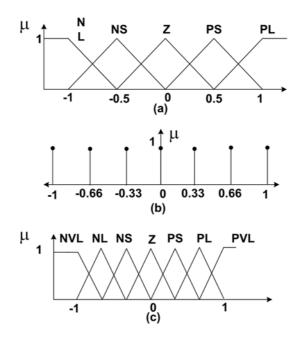

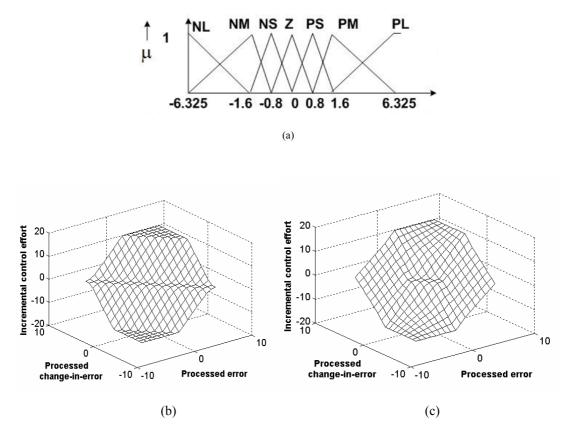

| Fig. 4.1.  | Membership functions- shapes (a) input (Sugeno and Mamdani) (b) output singletons (Sugeno) (c) output (Mamdani).                                                                                                                                                                                                                              | 61 |

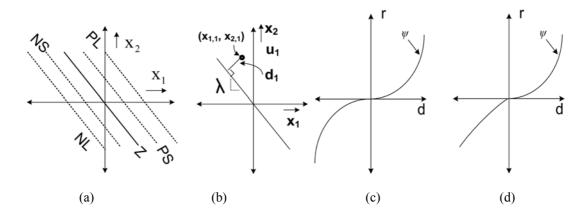

| Fig. 4.2.  | (a) Output membership functions in $x_1$ - $x_2$ plane (b) converting inputs from $x_1$ - $x_2$ plane to d-r plane (c) mapping a skew symmetric rule table in d-r plane (d) mapping of a non-skew symmetric rule table in d-r plane.                                                                                                          | 66 |

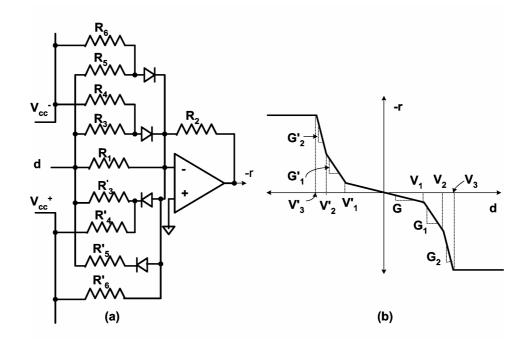

| Fig. 4.3.  | Cheap and Fast "FLC" (a) circuit realization (b) simulated non-linearity '- $\psi$ '.                                                                                                                                                                                                                                                         | 67 |

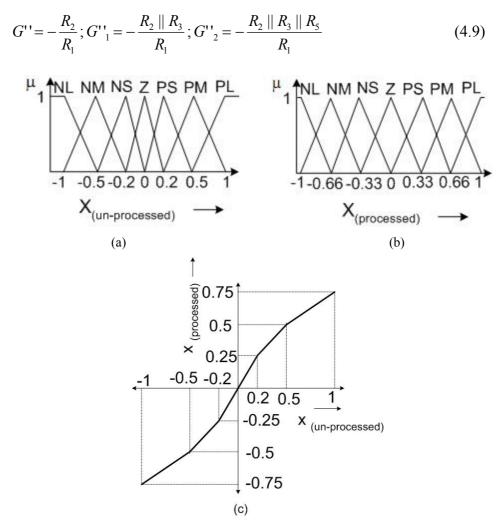

| Fig. 4.4.  | Membership functions (a) asymmetrical (b) symmetrical (c) mapping.                                                                                                                                                                                                                                                                            | 69 |

| Fig. 4.5.  | Preprocessing circuit (a) realization (b) mapping.                                                                                                                                                                                                                                                                                            | 69 |

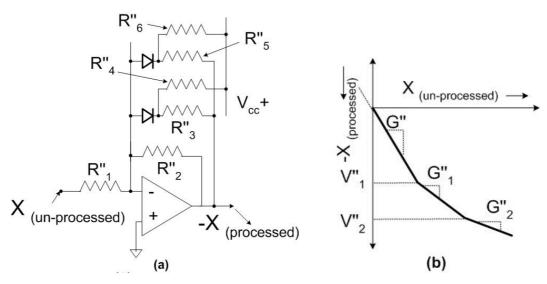

| Fig. 4.6.  | Comparison of FLC to NLFC (a) FLC (b) NLFC.                                                                                                                                                                                                                                                                                                   | 70 |

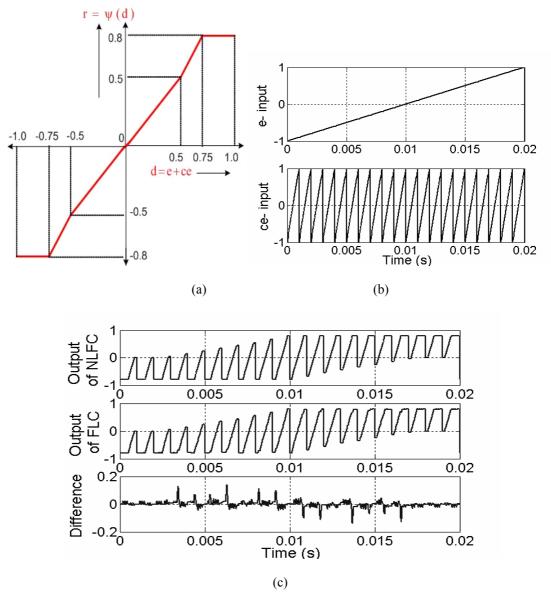

| Fig. 4.7.  | Equivalence of NFLC & FLC (a) NLFC- Function mapping (b)<br>Inputs to NLFC & FLC (c) Outputs of NLFC & FLC and their<br>difference.                                                                                                                                                                                                           | 72 |

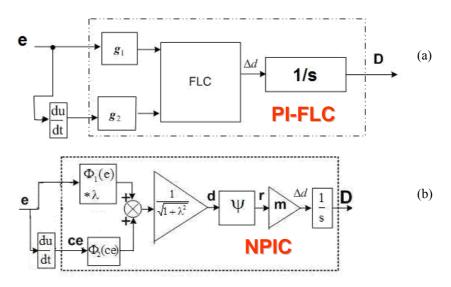

| Fig. 4.8.  | Schematic diagrams (a) PI-FLC (b) NPIC.                                                                                                                                                                                                                                                                                                       | 73 |

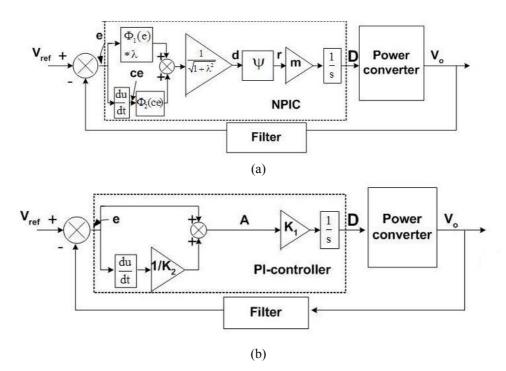

| Fig. 4.9.  | Power converter control schematic (a) with NPIC (b) with linear-PI controller.                                                                                                                                                                                                                                                                | 74 |

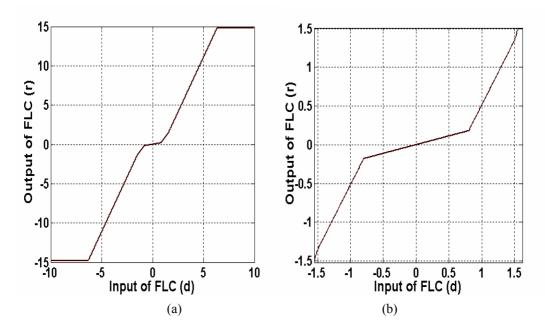

| Fig. 4.10. | Non-linear function $\psi$ mapping of SISO-FLC (a) the overall function with saturation (b) the mapping zoomed near the origin.                                                                                                                                                                                                               | 78 |

| Fig. 4.11. | (a) PI-FLC- Input membership functions (b) Input-output relation of NPIC (c) Input-output relation of PI-FLC.                                                                                                                                                                                                                                 | 80 |

|            |                                                                                                                                                                                                                                                                                                                                               |    |

81

82

83

83

84

84

85

86

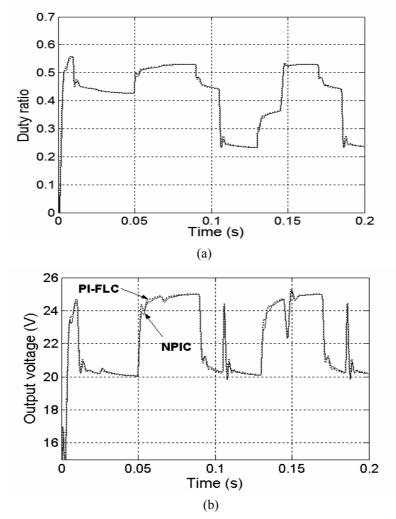

- Fig. 4.12. Performance comparison of NPIC and PI-FLC for random disturbances in the power converter; Input voltage transients at 0.025 s, 0.065 s, 0.105 s, 0.145 s, 0.185 s; reference voltage transients at 0.01 s, 0.05 s, 0.09 s, 0.13 s, 0.17 s; load resistance changes at 0.05 s, 0.09 s, 0.13 s, 0.17 s; load resistance changes at 0.05 s, 0.09 s, 0.13 s, 0.17 s (a) Duty ratio (b) Output voltage legend: '..' PI-FLC, solid line-NPIC.

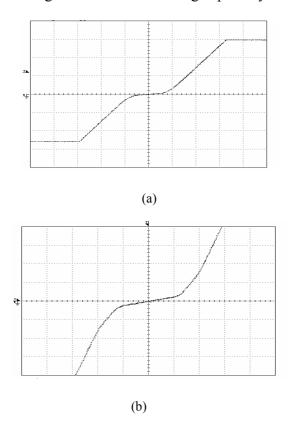

- Fig. 4.13. Non-linear function  $\psi$  hardware realization; Oscilloscope in xymode; (a) overall non-linearity; scale: x-axis (input 'd')= 2 V/div, yaxis (output 'r') = 5 V/div (b) non-linearity zoomed near the origin; scale: x-axis (input 'd')= 1 V/div, y-axis (output 'r') = 1 V/div.

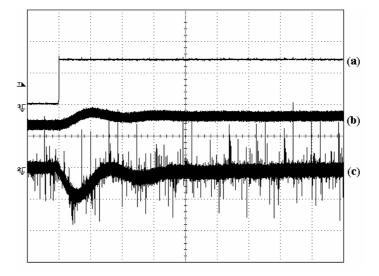

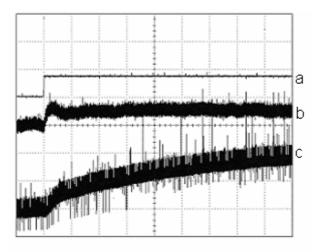

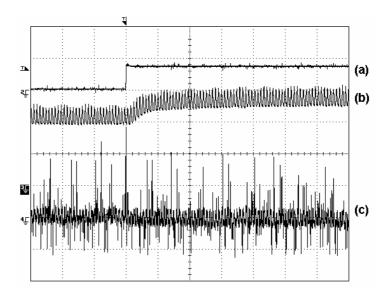

- Fig. 4.14. Experimental step response of the converter with NPIC for a step change in load from  $I_0=0.75$  A to  $I_0=0.9$  A, at  $V_s=15$  V,  $V_0=25$  V (a) Step- marks the instant when the load changes (b) Inductor current (c) Output voltage (oscilloscope channel in ac coupling mode); Scale: voltage: 0.2 V/div, current: 1 A/div, time: 2ms/div.

- Fig. 4.15. Experimental step response of the converter with PI controller for a step change in load from  $I_o$ = 0.75 A to  $I_o$ = 0.9 A, at  $V_s$  = 15 V,  $V_o$  = 25 V (a) Step- marks the instant when the load changes (b) Inductor current (c) Output voltage (channel in ac coupling mode); Scale: voltage: 0.2 V/div, current: 1 A/div, time: 2ms/div.

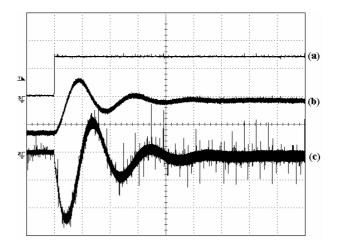

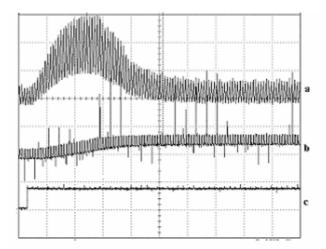

- Fig. 4.16. Experimental step response of the converter with NPIC for a step change in load from  $I_0=0.75$  A to  $I_0=2.0$  A, at  $V_s=15$  V,  $V_0=25$  V (a) Step- marks the instant when the load changes (b) Inductor current (c) Output voltage (oscilloscope channel in ac coupling mode); Scale: voltage: 0.5 V/div, current: 2 A/div, time: 2ms/div.

- Fig. 4.17. Experimental step response of the converter with PI controller for a step change in load from  $I_0 = 0.75$  A to  $I_0 = 2.0$  A, at  $V_s = 15$  V,  $V_0 = 25$  V (a) Step- marks the instant when the load changes (b) Inductor current (c) Output voltage (oscilloscope channel in ac coupling mode); Scale: voltage: 0.5 V/div, current: 2 A/div, time: 2ms/div.

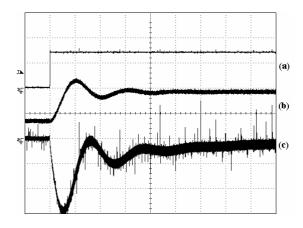

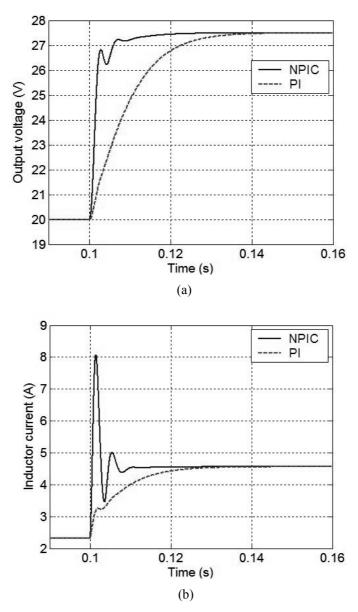

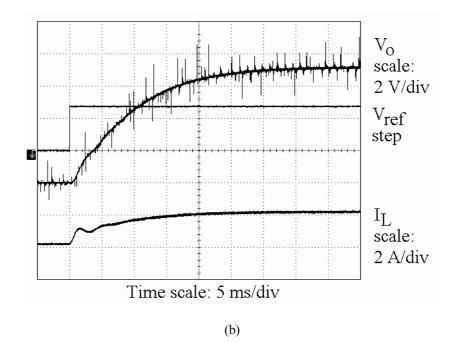

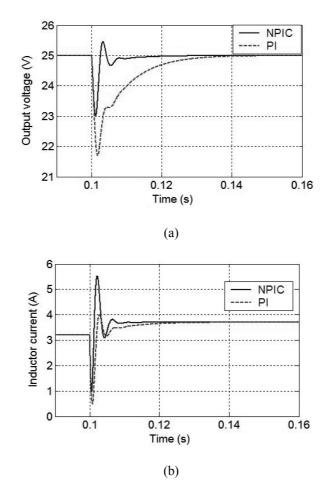

- Fig. 4.18. Simulated step response of the converter with NPIC and PI controllers for a step change in reference voltage from  $V_{ref} = 20$  V to  $V_{ref} = 27.5$  V, at  $V_s = 15$  V, load resistance R = 12.5  $\Omega$  (a) output voltage (b) inductor current.

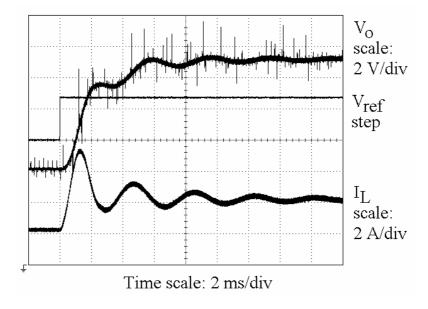

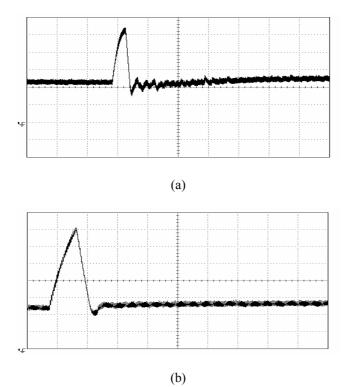

- Fig. 4.19. Experimental step response of the converter with (a) NPIC (b) PI for a step change in reference voltage from  $V_{ref} = 20$  V to 27.5 V, at  $V_s$ = 15 V, load resistance R = 12.5  $\Omega$ .

- Fig. 4.20. Simulated step response of the converter with NPIC and PI controllers for a step change in input voltage from  $V_s = 15$  V to  $V_s =$

xix

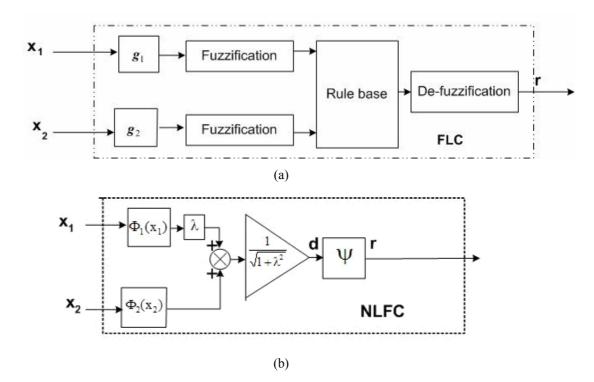

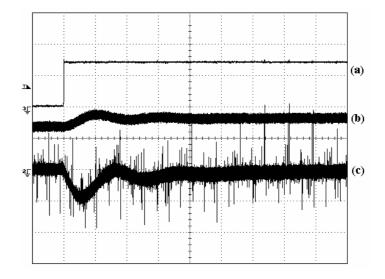

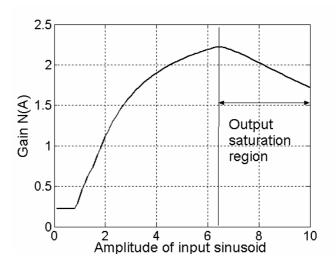

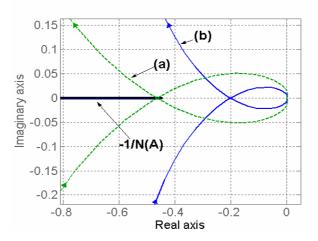

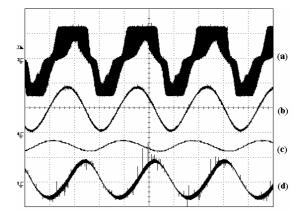

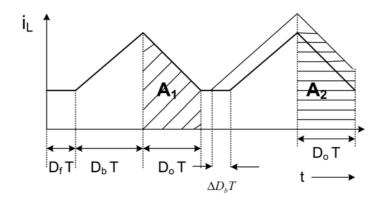

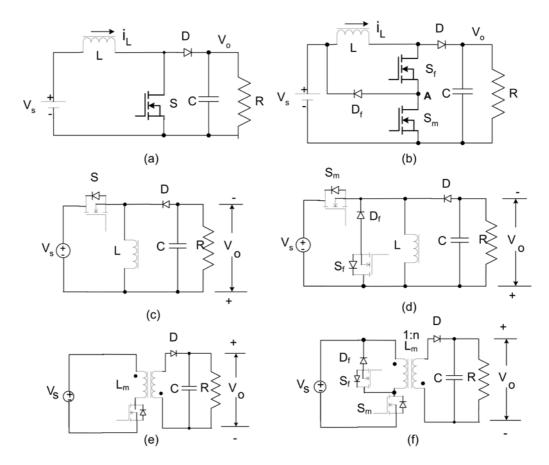

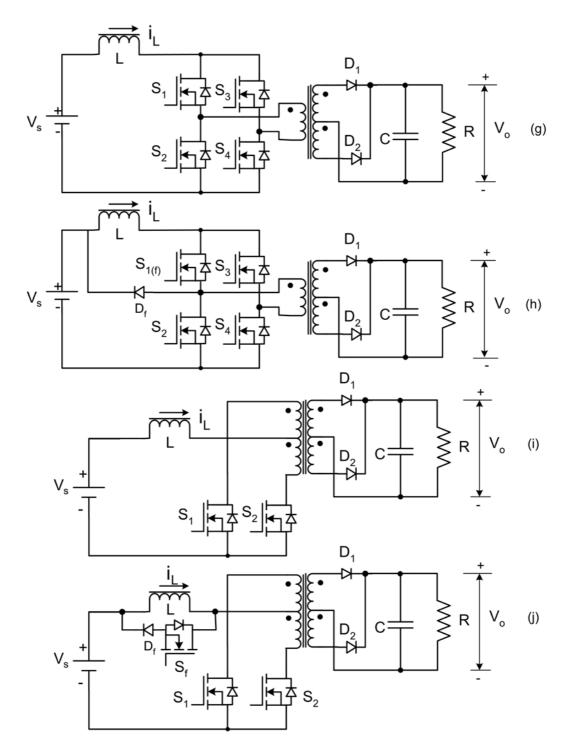

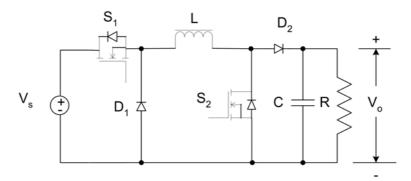

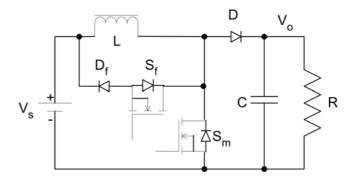

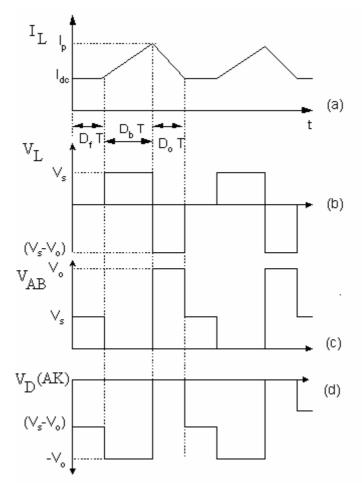

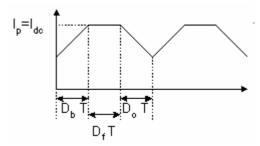

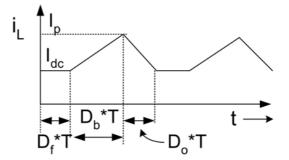

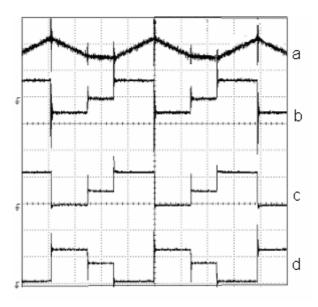

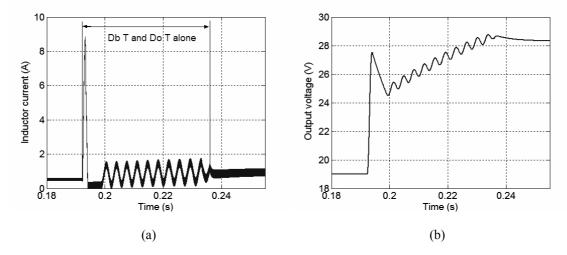

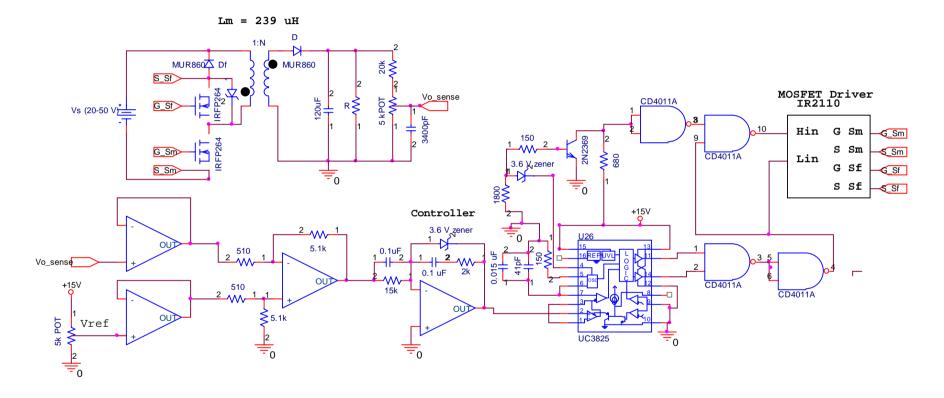

13 V, at  $V_{ref} = 25$  V, load resistance R = 12.5  $\Omega$  (a) output voltage (b) inductor current. 87 Fig. 4.21. Describing function of NPIC's non-linearity ' $\psi$ ' with output saturation. 89 Fig. 4.22. Onset of limit cycles predicted by describing function method; (a) Nyquist plot of G(s)\*K (system with the incremental gain 'K') at the verge of instability (b) Nyquist plot of G(s) alone with K=1 (stable). 90 Fig. 4.23. Experimental waveforms showing the converter exhibiting limit cycles at an extra gain of 3.3 (a) Output 'r' of ' $\psi$ ' (5 V/div) (b) Inductor current (5 A/div) (c) Duty ratio (0.5 units/div) (d) Output voltage (4 V/div) with channel in ac mode. 91 Tri-State class of converters- Motivation. 95 Fig. 5.1 Fig. 5.2 Circuit diagrams of classical and modified tri-state boost and buckboost-derived power converters (a) Classical boost converter (b) Tri-State boost converter (c) Classical buck-boost converter (d) Tri-state buck-boost converter (e) Classical flyback converter (f) Tri-state flyback converter (g) Classical full-bridge transformer-isolated boost converter (h) Full-bridge transformer-isolated tri-state boost converter (i) Classical push-pull isolated boost converter (i) Push-95 pull isolated tri-state boost converter. Fig. 5.3 An existing converter with possible tri-state operation- Cascadebuck-boost converter. 97 Fig. 5.4. Tri-state boost converter –another alternative (Circuit B). 98 Fig. 5.5. Equivalent circuits under different intervals of operation (a) 'Freewheeling' interval  $(D_f T)$  (b) 'Boost' interval  $(D_b T)$  (c) 99 Capacitor-charging interval  $(D_o T)$ . Fig. 5.6. Theoretical steady state waveforms of the tri-state boost converter (a) Boost-inductor current (b) Boost-inductor voltage (c) Voltage across A and B (d) Anode-cathode voltage of Diode D. 100 Fig. 5.7. 101 Alternative sequence for converter operation  $(D_b \rightarrow D_f \rightarrow D_o)$ . 102 Fig. 5.8. Inductor current waveform with  $(D_f \rightarrow D_b \rightarrow D_o)$  sequence. Fig. 5.9. Experimental waveforms of the tri-state boost converter at half load  $(V_s = 14V \text{ and } I_o = 1.2 \text{ A})$  (a) inductor current (b) voltage across inductor (c) cathode to anode voltage of diode D (d) voltage across A and B. Scale: current: 0. 5 A/div (ground not shown), voltage: 20 V/div, time: 5µs/div. 106

| Fig. 5.10. | Control-to-output Bode plots under minimum line (10 V) and maximum load (2 A) - Classical boost converter / open-loop operation.                                                                                                                                                                                                                                                             | 107 |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 5.11. | Control-to-output Bode plots under minimum line $(10 \text{ V})$ and maximum load $(2 \text{ A})$ –Tri-state boost converter / open-loop operation.                                                                                                                                                                                                                                          | 108 |

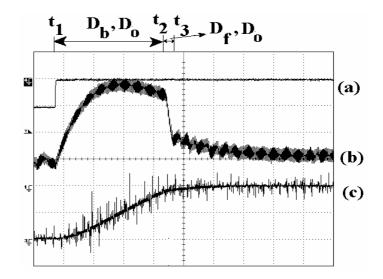

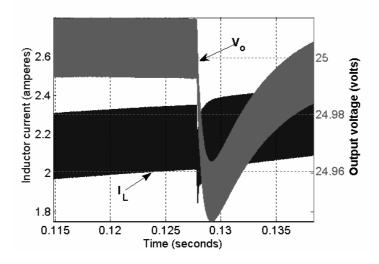

| Fig. 5.12. | Inductor current (upper) and output voltage (lower) waveforms of classical boost converter for a step increase in duty ratio from $D = 0.5$ to 0.51 at $V_s = 12.5$ V, $V_o = 25$ V, $I_o = 2$ A.                                                                                                                                                                                            | 109 |

| Fig. 5.13. | Inductor current (upper) and output voltage (lower) waveforms of tri-state boost converter for a step increase in duty ratio from $D = 0.3$ to 0.31 at $V_s = 12.5$ V, $V_o = 25$ V, $I_o = 2$ A.                                                                                                                                                                                            | 110 |

| Fig. 5.14. | Loop transfer-function Bode plots under minimum line (10 V) and maximum load (2 A)- Classical boost converter.                                                                                                                                                                                                                                                                               | 111 |

| Fig. 5.15. | Loop transfer-function Bode plots under minimum line (10 V) and maximum load (2 A)-Tri-state boost converter.                                                                                                                                                                                                                                                                                | 112 |

| Fig. 5.16. | Experimental step response of the classical boost converter for a step change in voltage reference (a) Step reference change (b) Inductor current (from 4.8 A to 5.1 A) (c) Output voltage (from 24.6 V to 25.5 V). Scale: voltage: 0.5 V/div, current: 0.5 A/div, time: 5ms/div.                                                                                                            | 113 |

| Fig. 5.17. | Experimental step response of the Tri-state boost converter for a step change in voltage reference (a) Inductor current (b) Output voltage (from 24.5 V to 25.4 V) (c) Step references change. Scale: voltage: 1 V/div, current: 0.5 A/div, time: $200\mu$ s/div.                                                                                                                            | 114 |

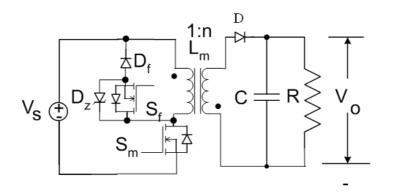

| Fig. 5.18. | Tri-state flyback converter- circuit diagram.                                                                                                                                                                                                                                                                                                                                                | 115 |

| Fig. 5.19. | Ideal theoretical steady state waveforms of the tri-state flyback converter (a) Gate-source voltage of switch $S_m$ (b) Gate-source voltage of $S_f$ (c) Magnetizing current in the equivalent inductor (d) Primary winding current (e) Secondary winding current (f) Voltage across the primary winding.                                                                                    | 116 |

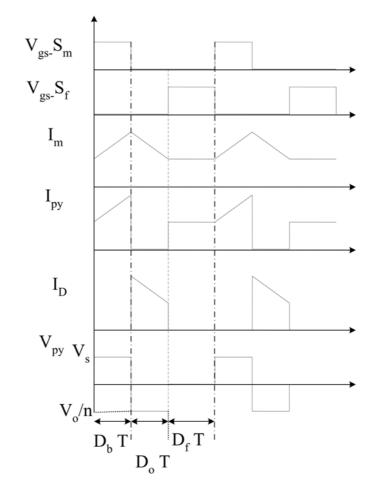

| Fig. 5.20. | Experimental waveforms of the tri-state flyback converter at half<br>load ( $V_s = 35$ V and $I_o = 1$ A) ( $I_{py}$ )- Primary current, scale: 5 A/div<br>( $V_{gs}$ - $S_m$ ) – Gate-source voltage of $S_m$ , scale: 10 V/div, ( $V_{py}$ )- Voltage<br>across the primary winding, scale : 50 V/div ( $V_{ds} S_m$ )- Drain-source<br>voltage of $S_m$ , scale: 50 V/div, time: 5µs/div. | 119 |

| Fig. 5.21. | Control-to-output ( $D_b$ -to- $V_o$ ) Bode plots under $V_s$ = 35 V and $I_o$ = 1 A –Tri-state flyback converter.                                                                                                                                                                                                                                                                           | 120 |

| Fig. 5.22. | Control-to-output ( <i>D-to-V<sub>o</sub></i> ) Bode plots under $V_s = 35$ V and $I_o = 1$ A –Classical flyback converter.                                                                                                                               | 121 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 5.23. | Loop transfer-function Bode plots at $V_s = 35$ V and $I_o = 1$ A -Tri-<br>state flyback converter.                                                                                                                                                       | 122 |

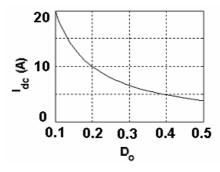

| Fig. 6.1.  | Theoretical variation of free-wheeling current versus $D_o$ at P = 50W, $V_s = 15 \text{ V}$ , $V_o = 25 \text{ V}$ , $f = 50 \text{ kHz}$ , and $L = 278 \mu\text{H}$ .                                                                                  | 129 |

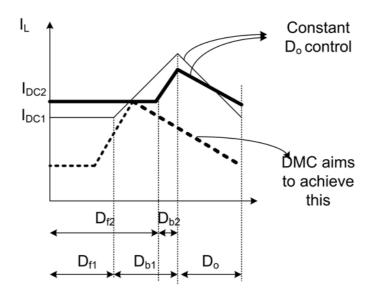

| Fig. 6.2.  | Comparison between inductor currents established by constant-D <sub>o</sub> and DMC schemes for an increase in input voltage from $V_o/2$ to $^{3}\!/_{4}$ $V_o$ .                                                                                        | 130 |

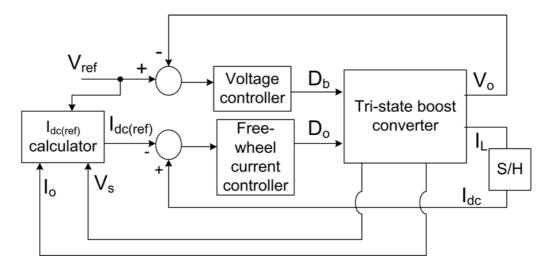

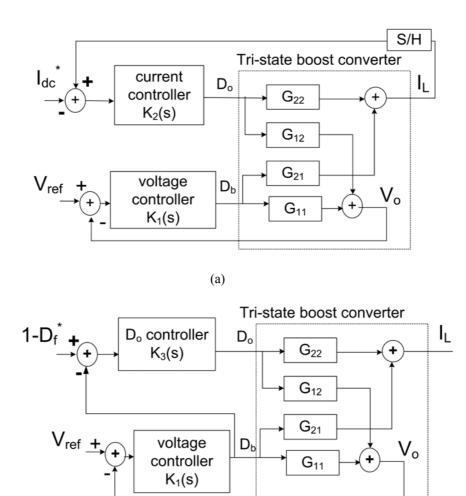

| Fig. 6.3.  | Direct Dual-mode control (DDMC) scheme.                                                                                                                                                                                                                   | 133 |

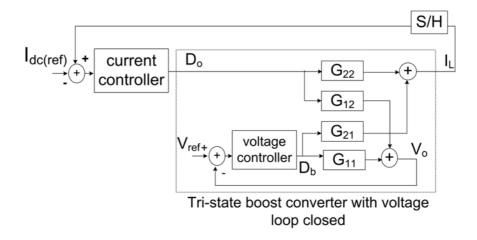

| Fig. 6.4.  | System model with cross-couplings for accurate current controller design (DDMC).                                                                                                                                                                          | 136 |

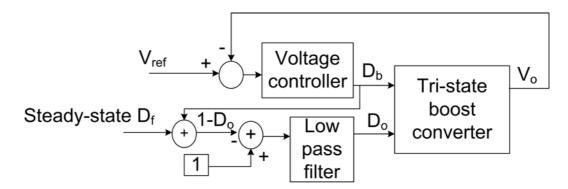

| Fig. 6.5.  | Indirect dual-mode control (IDMC) scheme.                                                                                                                                                                                                                 | 136 |

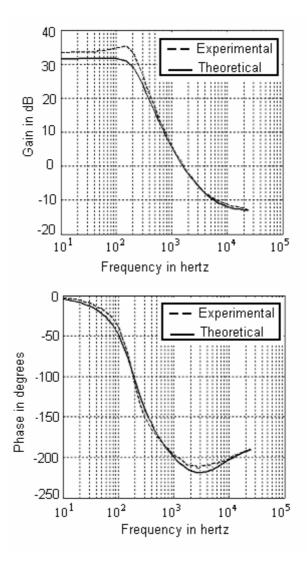

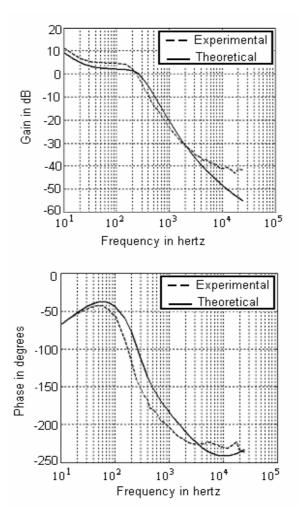

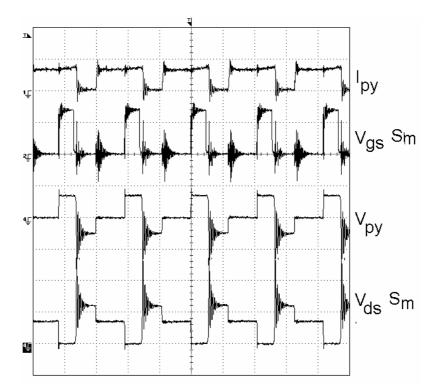

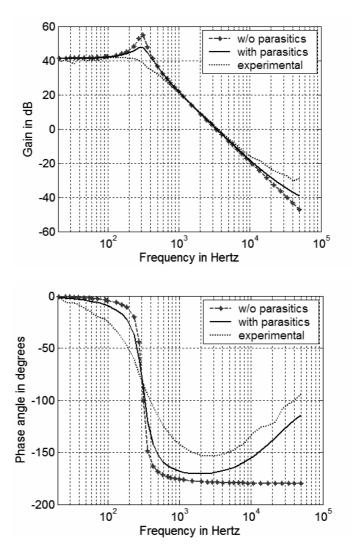

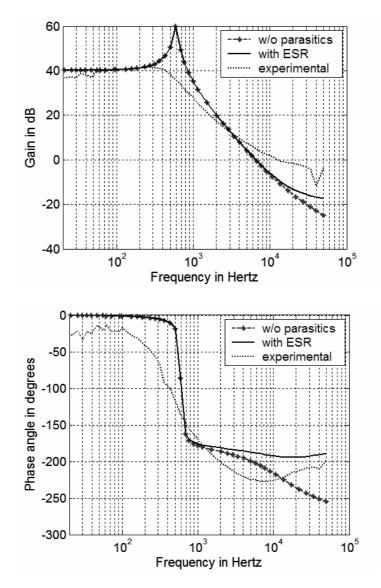

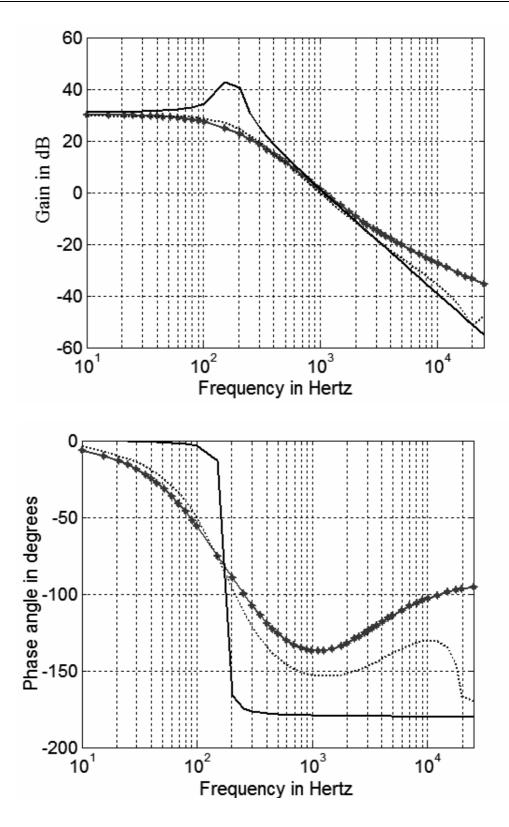

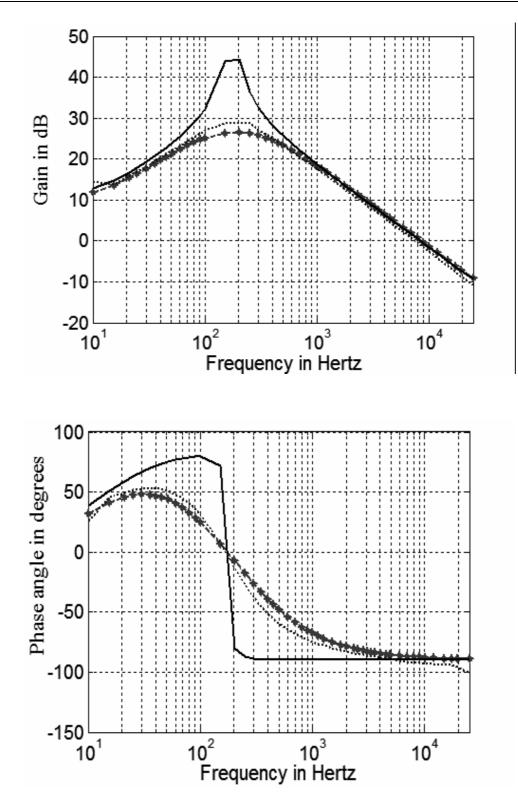

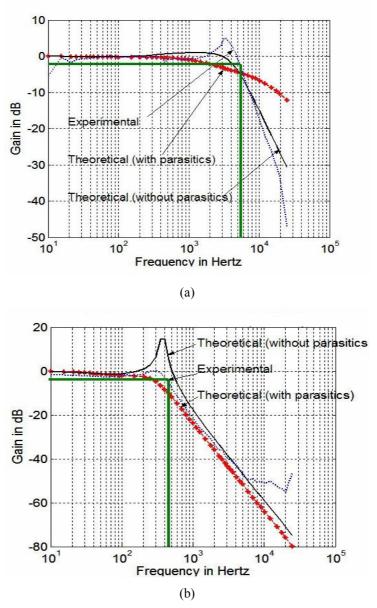

| Fig. 6.6.  | $D_b$ -to- $V_o$ Bode plots- Tri-state boost converter/ open-loop operation<br>at $V_s = 15$ V, $V_o = 25$ V, $I_o=1$ A, $D_b= 0.3586$ and $D_o=0.4188$ ; legends:<br>**-theoretical (with parasitics), experimental,theoretical<br>(without parasitics). | 140 |

| Fig. 6.7.  | $D_b$ -to- $I_L$ Bode plots- Tri-state boost converter/ open-loop operation<br>at $V_s = 15$ V, $V_o = 25$ V, $I_o=1$ A, $D_b= 0.3586$ and $D_o=0.4188$ ; legends:<br>**-theoretical (with parasitics), experimental,theoretical<br>(without parasitics). | 141 |

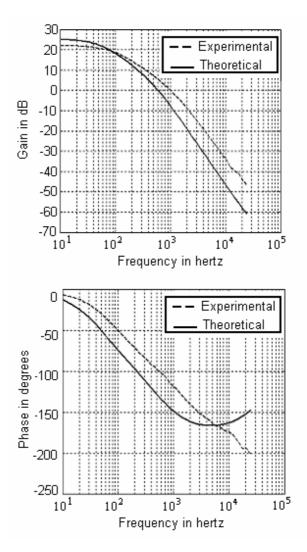

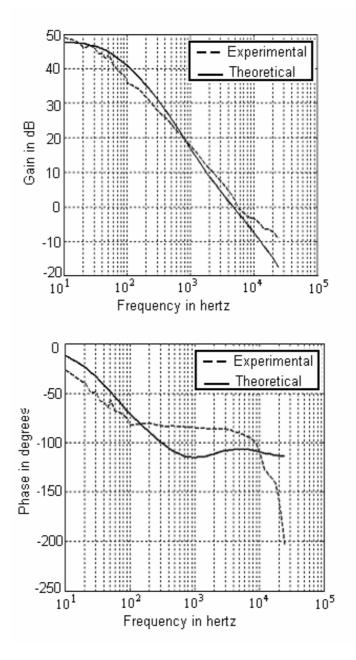

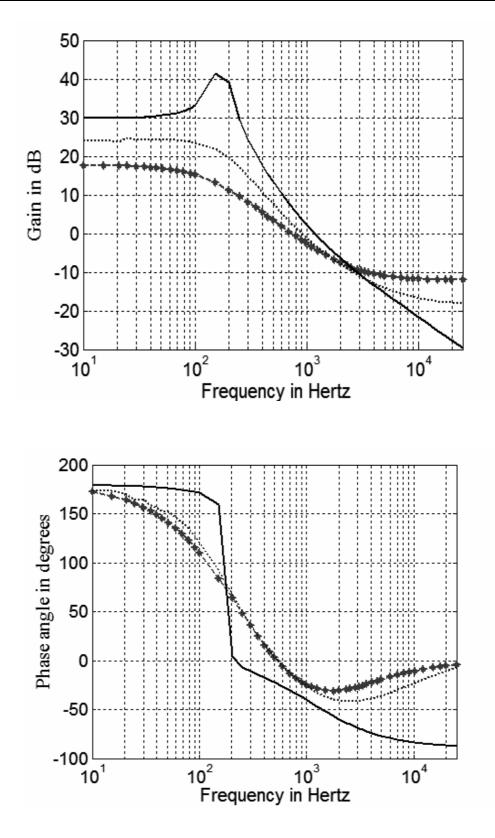

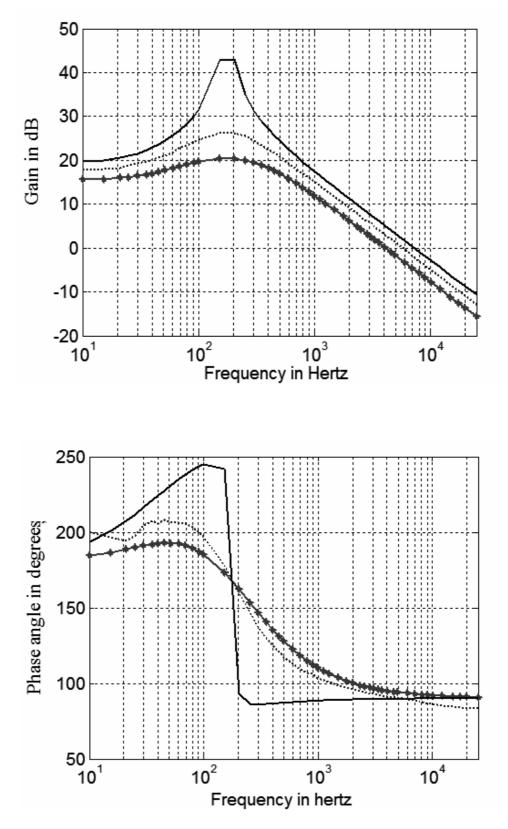

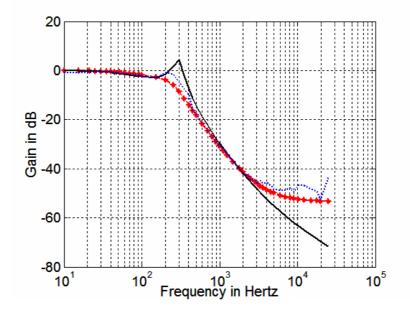

| Fig. 6.8.  | $D_o$ -to- $V_o$ Bode plots- Tri-state boost converter/ open-loop operation<br>at $V_s = 15$ V, $V_o = 25$ V, $I_o=1$ A, $D_b= 0.3586$ and $D_o=0.4188$ ; legends:<br>**-theoretical (with parasitics), experimental,theoretical<br>(without parasitics). | 142 |

| Fig. 6.9.  | $D_o$ -to- $I_L$ Bode plots- Tri-state boost converter/ open-loop operation<br>at $V_s = 15$ V, $V_o = 25$ V, $I_o=1$ A, $D_b= 0.3586$ and $D_o=0.4188$ ; legends:<br>**-theoretical (with parasitics), experimental,theoretical<br>(without parasitics). | 143 |

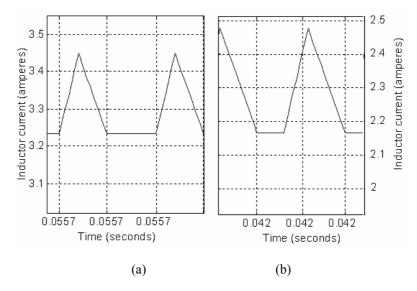

| Fig. 6.10. | Simulated steady-state inductor current waveforms of tri-state boost converter ( $V_s$ =15 V, $V_o$ = 25 V $I_o$ = 1 A) (a) 'constant- $D_o$ ' control scheme (b) DDMC scheme (K=1.3).                                                                    | 145 |

| Fig. 6.11. | Closed-loop Bode magnitude plot at $V_s = 15V$ , $V_o = 25V$ , $I_o=1A$ , $D_b= 0.3586$ and $D_o=0.4188$ ; (a) closed voltage loop (b) closed current loop.                                                                                               | 146 |

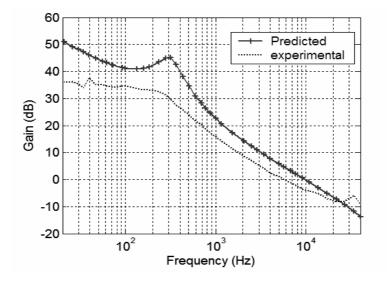

| Fig. 6.12. | Classical boost converter- closed-loop Bode magnitude plot at $V_s = 15V$ , $V_o = 25V$ , $I_o=1A$ , legends: **-theoretical (with parasitics), experimental,theoretical (without parasitics).                                                                                                                                                    | 147 |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

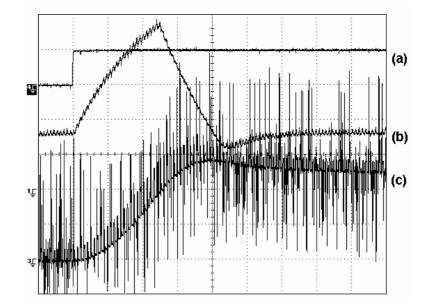

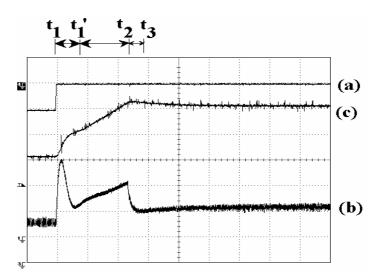

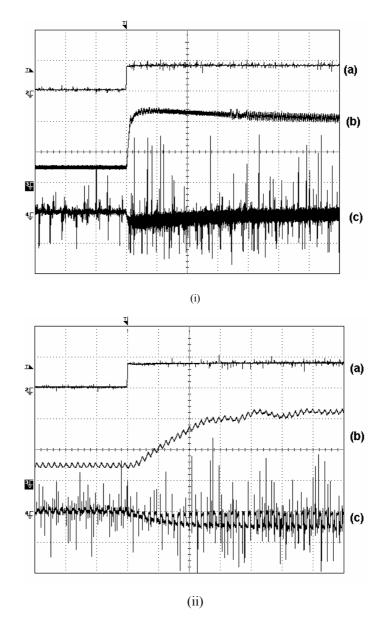

| Fig. 6.13. | Experimental reference voltage step response of a tri-state boost converter with 'constant- $D_o$ ' control scheme (a) step reference change (b) inductor current (ground at -1 div) (c) output voltage from 23.8 V to 25.1 V (oscilloscope in ac mode with ground at -3 div); Scale: voltage: 0.5 V/div, current: 2A/div, time: 200 $\mu$ s/div. | 148 |

| Fig. 6.14. | Experimental reference voltage step response of a tri-state boost converter under DDMC scheme; (a) step reference change (b) inductor current (ground at -2 div) (c) output voltage from 24.1 V to 25.1 V; Scale: voltage: 0.5 V/div, current: 1A/div, time: 200µs/div.                                                                           | 148 |

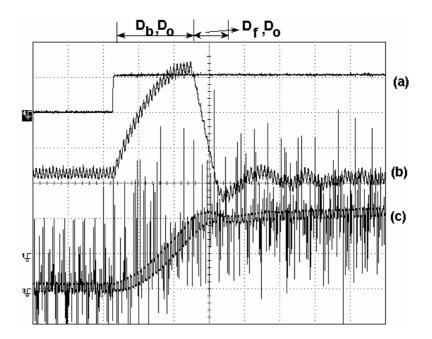

| Fig. 6.15. | DMC scheme- demonstration of vanishing free-wheeling interval for<br>a step change in reference voltage from 24.1 V to 25.1 V. (a)<br>inductor current (b) output voltage; scale: current: $1A/div$ , voltage:<br>$0.5 V/div$ , time: $100\mu s/div$ .                                                                                            | 149 |

| Fig. 6.16. | Experimental reference voltage step response of a tri-state boost converter with IDMC scheme; (a) step reference change (b) inductor current (ground at -4 div) (c) output voltage from 24.1 V to 25.1 V (oscilloscope in ac mode with ground at -3 div); Scale: voltage: 0.5 V/div, current: 1A/div, time: 200µs/div.                            | 149 |

| Fig. 6.17. | Slow current loop operation for a step change in reference voltage from 24.1 V to 25.1 V (a) DDMC scheme; scale: current: 1A/div, time: 1 ms/div (b) IDMC scheme; scale: current: 1A/div, time: 500 $\mu$ s/div.                                                                                                                                  | 150 |

| Fig. 6.18. | Experimental step response of the classical boost converter for a step change in voltage reference (a) step reference change (b) inductor current (ground at -1 div) (c) output voltage from 24.1 V to 25.1 V (oscilloscope in ac mode with ground at -3 div); Scale: voltage: 0.5V/div, current: 1A/div, time: 1ms/div.                          | 150 |

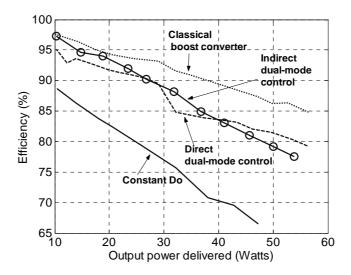

| Fig. 6.19. | Efficiency versus load power at $V_s=20$ V and $V_o=25$ V.                                                                                                                                                                                                                                                                                        | 151 |

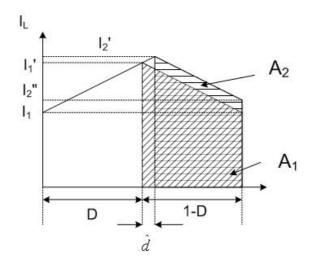

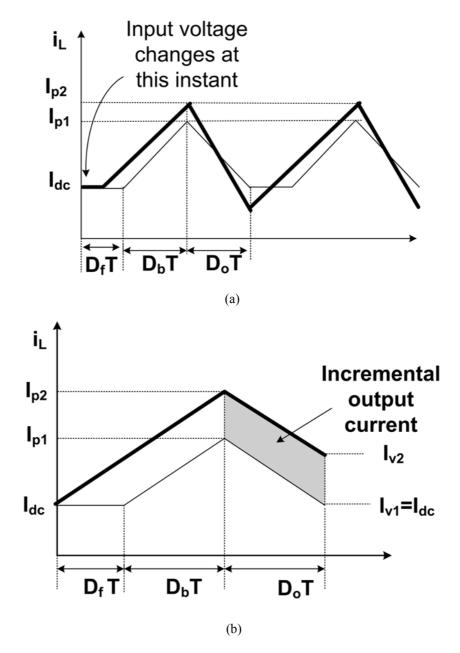

| Fig. 7.1.  | Inductor current waveforms (a) $V_s$ change (b) Load (or $V_{ref}$ ) change.                                                                                                                                                                                                                                                                      | 160 |

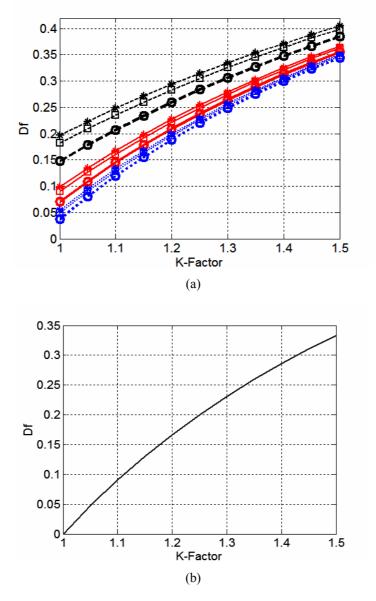

| Fig. 7.2.  | Variation of free-wheeling interval with <i>K-factor</i> (a) <i>DDMC</i> scheme<br>(b) IDMC scheme; Legend: square- $V_s=20$ V, starred- $V_s=15$ V, circled $V_s=10$ V, dashed line- $P_o=10$ W; continuous- $P_o=25$ W, dotted- $P_o=50$ W.                                                                                                     | 164 |

| Fig. 7.3.  | Small-signal model- (a) DDMC scheme (b) IDMC scheme.                                                                                                                                                                                                                                                                                              | 168 |

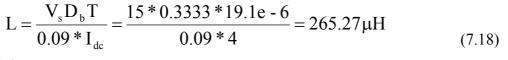

- Fig. 7.4. Variation of disturbance margins with *K-factor* at different load and line conditions (a)  $V_{o\_margin}$  (b)  $V_{s\_margin}$ ; Legend: square-  $V_s=20$  V, starred-  $V_s=15$  V, circled  $V_s=10$  V. 170

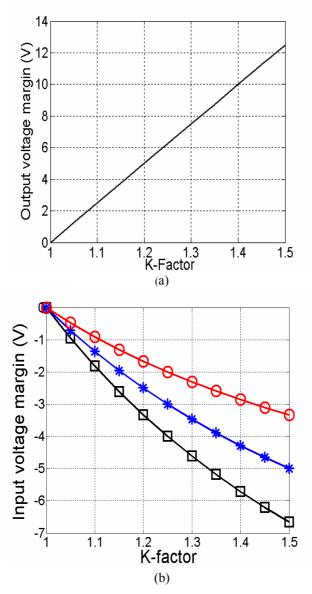

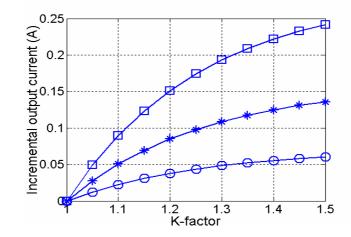

- Fig. 7.5.  $(\Delta I_o)_{\text{max}}$  versus *K*-factor- IDMC scheme (refer Fig. 7.4 for legend). 171

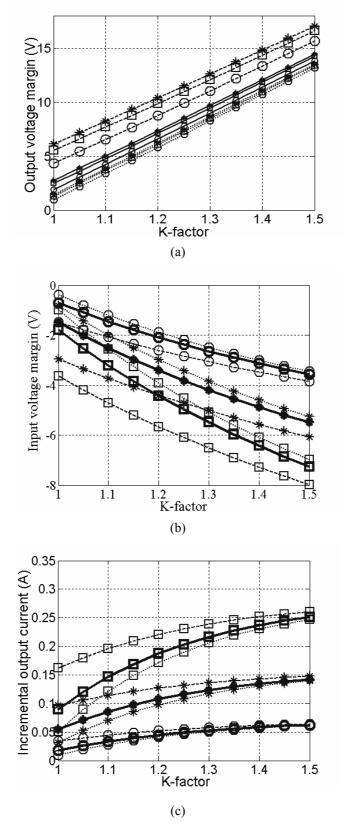

- Fig. 7.6. Variation of disturbance margins with *K*-factor (DDMC scheme) (a)  $V_{o\_margin}$  (b)  $V_{s\_margin}$  (c)  $(\Delta I_o)_{max}$ ; Legend: square-  $V_s=20$  V, starred-  $V_s=15$  V, circled  $V_s=10$  V, dashed line-P\_o=10 W; continuous-P\_o=25 W, dotted-P\_o=50 W. 172

- Fig. 7.7. Experimental small-V<sub>ref</sub> step response (IDMC) at  $V_s=15V$ ,  $R=62.5 \Omega$ ; (a)  $V_{ref}$  step (b)  $i_L$  (ground at -1 div) (c)  $V_o$  from 26 V to 30 V (oscilloscope in ac mode with ground at -3 div);  $V_{o\_margin}=7.8$  V scale: voltage: 2 V/div, current: 1A/div, time: 500 µs/div. 176

- Fig. 7.8. Experimental large-V<sub>ref</sub> step with IDMC scheme at  $V_s=15V$ , R=62.5 $\Omega$ ; (a)  $V_{ref}$  step (b) i<sub>L</sub> (ground -3 div) (c)  $V_o$  from 20.5 V to 30.5 V (oscilloscope in dc mode with ground at -3 div);  $V_{o\_margin}= 6.1$  V; scale: voltage: 5 V/div, current: 2A/div, time: 5 ms/div. 176

- Fig. 7.9. Experimental small-I<sub>o</sub>-step (0.4 A to 0.5 A) response at  $V_o=25$  V and  $V_s=15$  V with IDMC scheme (a) step load change (b)  $i_L$  (ground at -1 div) (c)  $V_o$  (oscilloscope in ac mode with ground at -2 div); ( $\Delta I_o$ )<sub>max</sub> = 0.11 A; scale: voltage: 0.25 V/div, current: 0.5 A/div, time: 200µs/div.

- Fig. 7.10. Experimental large-I<sub>o</sub>-step (0.4 A to 2 A) response at V<sub>o</sub>=25 V and V<sub>s</sub>=15 V with IDMC scheme (a) step load change (b)  $i_L$  (ground at 0 div) (c) V<sub>o</sub> (oscilloscope in ac coupling mode with ground at -1 div);  $(\Delta I_o)_{max} = 0.11$  A; scale: voltage: 0.5 V/div, current: 2 A/div, time: 500µs/div. 177

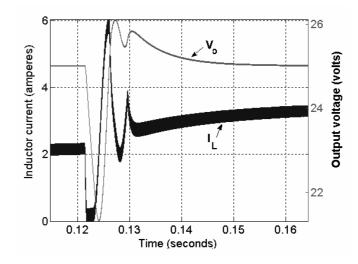

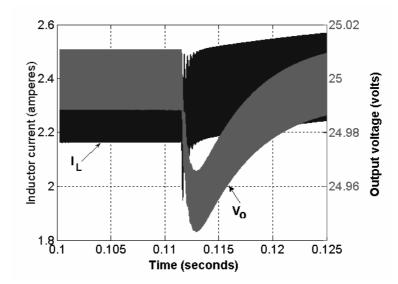

- Fig. 7.11. Simulated response (IDMC) for a small dip in input voltage from 15 V to 14 V at  $V_o=25 V$  and  $I_o=1 A$ ,  $V_{s margin} = -3.5 V$ . 178

- Fig. 7.12. Simulated response (IDMC) for a large dip in input voltage from 15 V to 10 V at  $V_o=25 V$  and  $I_o=1 A$ ,  $V_{s margin} = -3.5 V$ . 178

- Fig. 7.13. Experimental step response of a tri-state boost converter with DDMC scheme for a large step change in voltage reference at  $V_s=15V$ , R=62.5  $\Omega$ ; (a)  $V_{ref}$  step (b) inductor current (ground at -3 div) (c) output voltage from 26 V to 30 V (oscilloscope in ac mode with ground at +1 div);  $V_{o\_margin}= 13.06$  V; scale: voltage: 2.5 V/div, current: 2 A/div, time: 500 µs/div.

- Fig. 7.14. Experimental step response of a tri-state boost converter with DDMC scheme for a large step change in voltage reference at  $V_s=15V$ , R=62.5  $\Omega$ ; (a) step reference change (ground at +2.0 div) (b) inductor current (ground at -4 div) (c) output voltage from 19 V to

180

177

181

182

| 30.3 V (oscilloscope in dc mode with -20 V offset and with ground                    |

|--------------------------------------------------------------------------------------|

| at -3 div); V <sub>o margin</sub> = 9.2 V; scale: voltage: 2 V/div, current: 2A/div, |

| time: 1 ms/div.                                                                      |

| Fig. 7.15. | Simulated step response of a tri-state boost converter with DDMC            |     |

|------------|-----------------------------------------------------------------------------|-----|

|            | scheme for a large step change in voltage reference at $V_s=15V$ ,          |     |

|            | R=62.5 $\Omega$ ; (a) inductor current (b) output voltage from 19 V to 28.3 |     |

|            | V; $V_{o_margin} = 9.2$ V.                                                  | 181 |

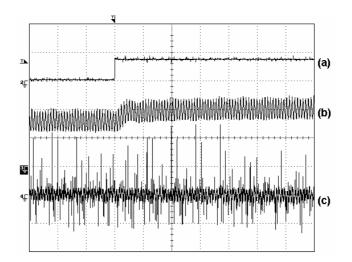

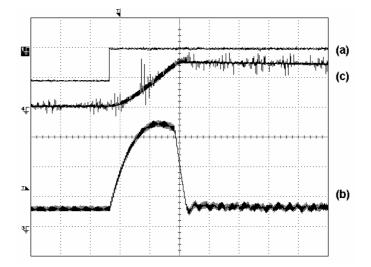

Fig. 7.16. Experimental response for a small step change in load current from 0.4 A to 0.5 A at  $V_0=25$  V and  $V_s=15$  V for DDMC (a) step load change (b) inductor current (ground at -3 div) (c) output voltage (oscilloscope in ac mode with ground at -2 div); scale: voltage: 0.25 V/div, current: 0.5 A/div, time: 200µs/div.

# Fig. 7.17. Experimental large- $I_o$ -step (0.4 A to 2 A) response at $V_o = 25$ V and $V_s = 15$ V with DDMC scheme (a) step load change (b) inductor current (ground at -1 div) (c) output voltage (oscilloscope in ac mode with ground at -3 div); scale: voltage: 0.5 V/div, current: 2 A/div, (i) time scale : 2 ms/div (ii) time scale: 100 µs/div. 183

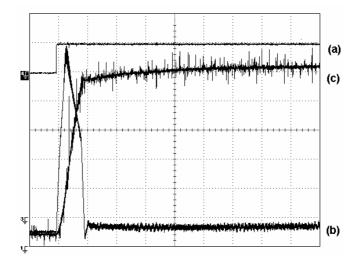

| Fig. 7.18. | Simulated response (DDMC) for a small dip in input voltage $V_s$ from   |     |

|------------|-------------------------------------------------------------------------|-----|

|            | 15 V to 14 V at $V_o = 25$ V and $I_o = 1$ A; $V_{s\_margin} = -4.2$ V. | 184 |

### Fig. 7.19. Simulated response (DDMC) for a large dip in input voltage $V_s$ from 15 V to 10 V at $V_o=25$ V and $I_o=1$ A. $V_{s\_margin}=-4.2$ V. 184

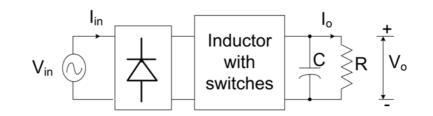

| Fig. 8.1. | A PFC rectifier with internal inductor energy storage.                                                                        | 188 |

|-----------|-------------------------------------------------------------------------------------------------------------------------------|-----|

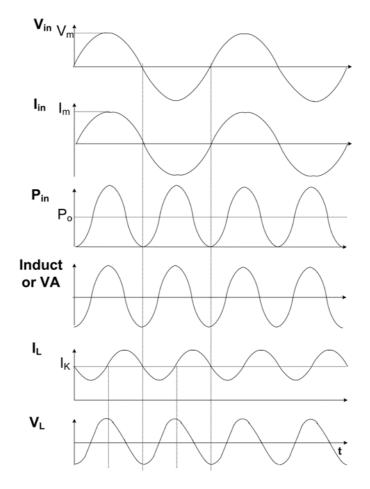

| Fig. 8.2. | Dual goal achievement- PFC rectifier, $V_L$ -voltage across inductor, $I_L$ -inductor current, $VA_L$ - inductor volt-ampere. | 191 |

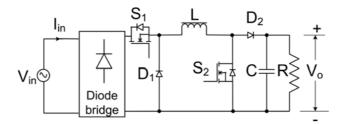

| Fig. 8.3. | Cascade buck-boost- PFC (CBB-PFC) converter.                                                                                  | 195 |

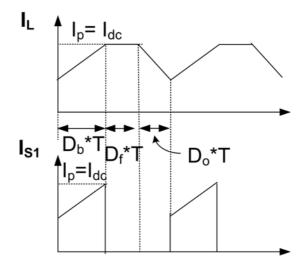

| Fig. 8.4. | Inductor $(I_L)$ and switch 'S <sub>1</sub> ' $(I_{SI})$ waveforms.                                                           | 196 |

- Fig. 8.5.Dual-mode Control scheme for CBB-PFC rectifier.199

- Fig. 8.6. Variation of inductor rms current with  $D_f^*$  at V<sub>s</sub>= 85 V, P<sub>o</sub>=100 W. 200

- Fig. 8.7. Variation of 'limiting'  $D_f^*$  with operating conditions, at  $V_o=100 V$ . 201

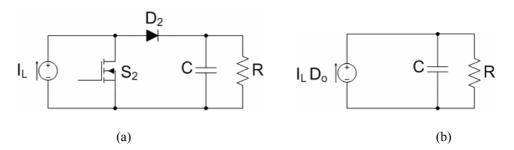

- Fig. 8.8.Simplified converter model for design of voltage-loop converter (a)<br/>current-fed converter model (b) averaged model with diode D2<br/>replaced by current source.205

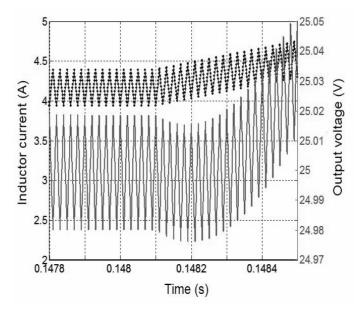

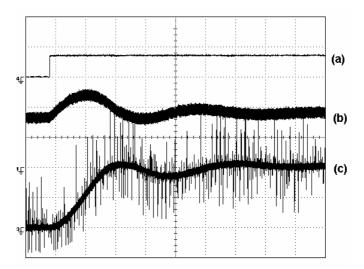

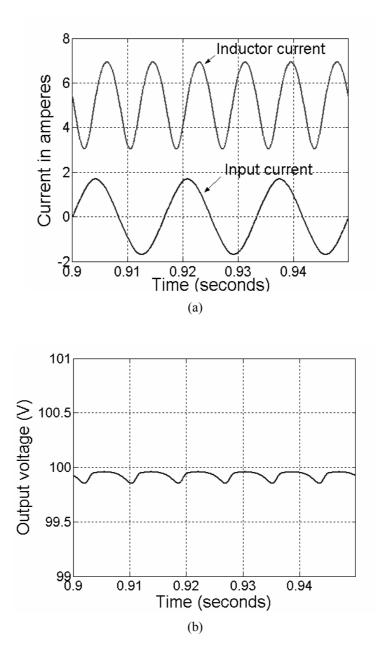

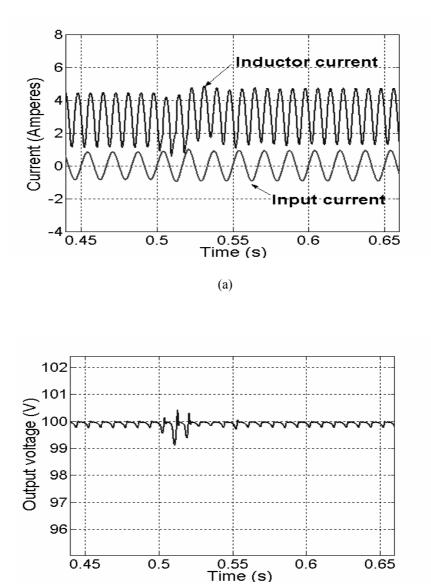

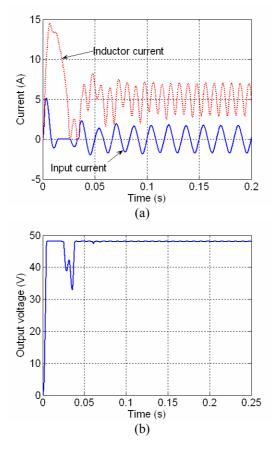

- Fig. 8.9. Steady-state waveforms of DMC based CBB-PFC rectifier at  $V_s$ =85 V,  $V_o$ =100 V,  $I_o$ =1 A,  $D_f^*$ =0.57 (a) Input and inductor currents (b) Output voltage. 207

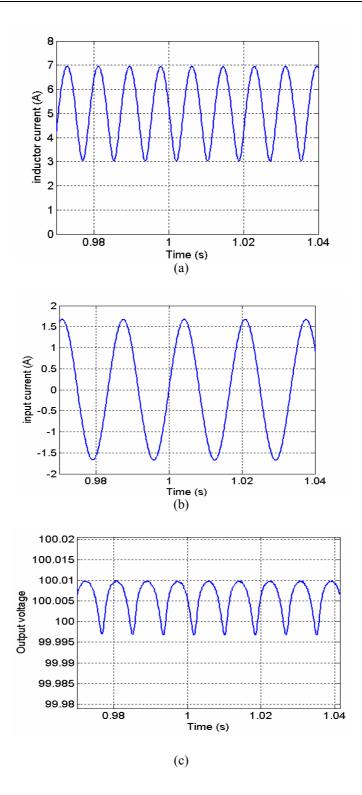

| Fig.8.10.  | Simulated steady-state waveforms of DMC based CBB-PFC rectifier<br>at $V_s=85 \text{ V}$ , $V_o=100 \text{ V}$ , $I_o=1 \text{ A}$ , $D_f^*=0.57$ - Investigation with<br>increased voltage-loop gain (a) Inductor current (b) input current (c)<br>output voltage.                                                                                                                                                                                                                                                                                                            | 208 |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

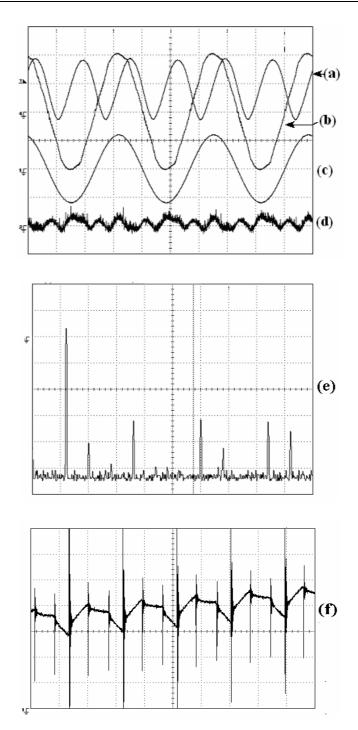

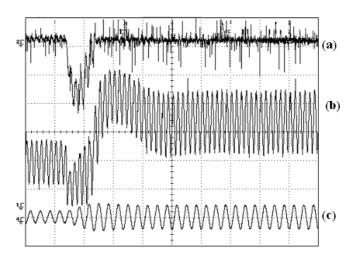

| Fig. 8.11. | Experimental steady-state waveforms at $V_s=85$ V, $V_o=100$ V, $I_o=1$ A.<br>(a) inductor current (ground at -1 div, scale: 2A/div) (b) input current<br>(scale: 1A/div) (c) input voltage (scale: 100 V/div) (d) output<br>voltage (oscilloscope in ac-coupling mode with ground at -3 div,<br>scale: 1V/div); time scale: 5ms/div (e) Harmonic spectrum of input<br>current; scale: x-axis:50 Hz/div, y-axis: 10dBA/div; GND at +2 div<br>(f) Inductor current (zoomed) showing tri-state operation (scale: 0.1<br>A/div, waveform has an offset of -2.7 A time: 10 µs/div. | 209 |

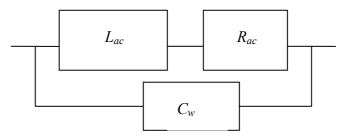

| Fig. 8.12. | Equivalent model of laminated iron-core inductor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 210 |

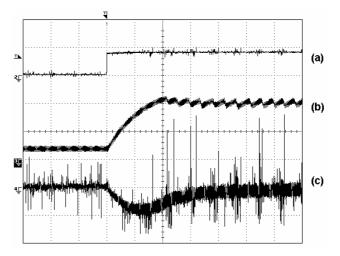

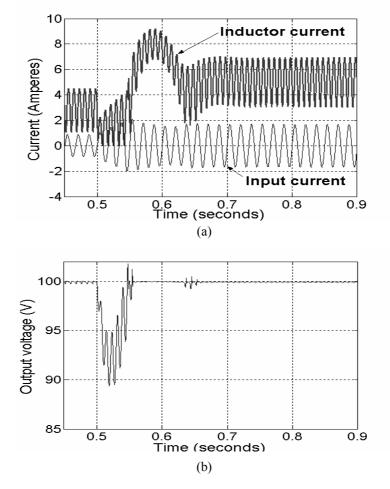

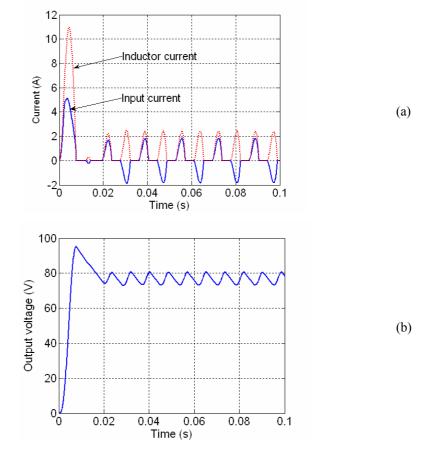

| Fig. 8.13. | Simulated step load transient response of the CBB PFC rectifier at $V_s$ =85 V, $V_o$ =100 V, $I_o$ =0.5 A to 0.55 A, $D_f^*$ =0.57. (a) Inductor and input current. (b) Output voltage.                                                                                                                                                                                                                                                                                                                                                                                       | 212 |

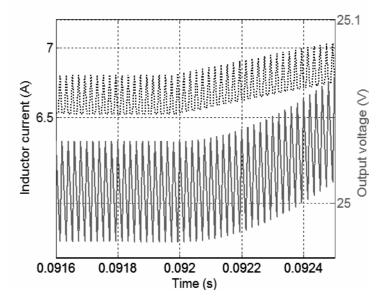

| Fig. 8.14. | Simulated step load transient response of the CBB-PFC rectifier at $V_s=85 \text{ V}$ , $V_o=100 \text{ V}$ , $I_o=0.5 \text{ A}$ to 1 A, $D_f^*=0.57$ . (a) Inductor and input current. (b) Output voltage.                                                                                                                                                                                                                                                                                                                                                                   | 213 |

| Fig. 8.15. | Experimental response for step load change at $V_s$ =85 V, $V_o$ =100 V, $I_o$ =0.5 A to 1 A, $D_f$ =0.57; (a) output voltage (scale: 5 V/div, oscilloscope in ac coupling mode with ground at 3.2 div) (b) inductor current (ground at -2.5 div, scale: 2A/div) (c) input current (scale: 5A/div; ground at -3 div) time scale: 50ms/div.                                                                                                                                                                                                                                     | 213 |

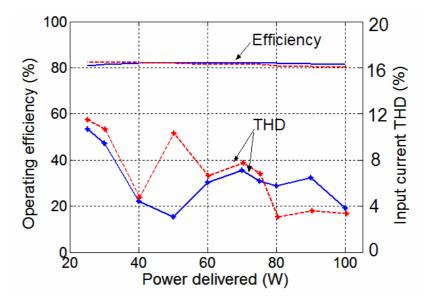

| Fig. 8.16. | Experimental variation of steady-state efficiency and input current THD (multiplied by 5) with delivered power at extreme line conditions; legends: dotted line $-V_s=110$ V, solid line $-V_s=85$ V.                                                                                                                                                                                                                                                                                                                                                                          | 215 |

| Fig. 8.17. | Block schematic diagram of sliding-mode control scheme for CBB-<br>PFC – based on the method in [48].                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 220 |

| Fig. 8.18. | Simulation results demonstrating the performance of control scheme employed in [48] at $V_s = 85$ V, $V_{ref} = 48$ V and $P_o = 100$ W (a) Inductor and input current (b) output voltage.                                                                                                                                                                                                                                                                                                                                                                                     | 221 |

| Fig. 8.19. | Simulation results demonstrating the drawback of sliding-mode control scheme employed in [48] (a) Inductor and input current (b) output voltage.                                                                                                                                                                                                                                                                                                                                                                                                                               | 222 |

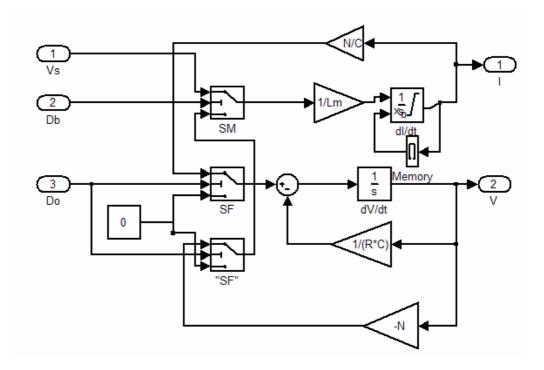

| Fig. B.1.  | Tri-state boost converter- Simulation (SIMULINK) model.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 247 |