# READOUT ELECTRONICS FOR MICROBOLOMETER INFRARED FOCAL PLANE ARRAY

QIAN XINBO

NATIONAL UNIVERSITY OF SINGAPORE

2004

# READOUT ELECTRONICS FOR MICROBOLOMETER INFRARED FOCAL PLANE ARRAY

QIAN XINBO (M. Sc., CAS)

A THESIS SUBMITTED FOR THE DEGREE OF DOCTOR OF PHILOSOPHY DEPARTMENT OF ELECTRICAL & COMPUTER ENGINEERING NATIONAL UNIVERSITY OF SINGAPORE

2004

### Acknowledgements

I wish to express my sincere gratitude to my supervisors, A/Prof. Yong Ping Xu and A/Prof. Gamani Karunasiri, for their interest, guidance and support throughout the course of this work. Their profound knowledge and rigorous scientific approach have greatly inspired me in the research. Their advices to me on all matters, not just the professional help, are greatly appreciated and are something I will ever benefit from.

My thankfulness also extends to my senior colleagues Mr. H.-J. Wu, Mr. X.-B. He and Mr. C. Y. Hui. They have greatly helped me in the research. Especially at the initial stages, I got a lot of support and helpful suggestions through the technical discussions with them. I would also thank Ms. Musni Hussain, Mr. Francis Boey and Mr S. M. Teo for their assistance in the experimental set-up. My appreciation also goes to Dr. V. Samper of Institute of Microelectronics (IME) for providing me the microbolometer samples and focal plane arrays.

Many thanks to graduate students in Center for Opto-electronics and VLSI Lab, in particular, Mr. L.-F. Zhou, Ms X.-W. Zhang, Ms. L.-C. Xu and Mr. Rama Krishna MVS for their kind help. I really enjoy and appreciate the time I have spent with them.

Finally, I would like to thank my family for their continuously support and encouragement.

# **Table of Contents**

| Acknowledgments                                      | i     |

|------------------------------------------------------|-------|

| Table of Contents                                    | ii    |

| Summary                                              | vii   |

| List of Figures                                      | ix    |

| List of Tables                                       | xv    |

| List of Symbols                                      | xvi   |

| List of Abbreviations                                | xviii |

| Chapter 1. Introduction                              | 1     |

| 1.1. Infrared detectors                              | 1     |

| 1.2 Microbolometer IR detector and focal plane array | 2     |

| 1.3 Detector characterization                        | 4     |

| 1.4. Structure of micromachined microbolometer       | 7     |

| 1.5. Readout circuits and self-heating effect        | 9     |

| 1.6. Scope and organisation of thesis                | 11    |

| Chapter 2. Literature Review                         | 14    |

| 2.1. Infrared detectors for thermal imaging          | 14    |

| 2.2. Microbolometer IR detector                      | 16    |

| 2.2.1. Microbolometer IR detector                    | 16    |

| 2.2.2. Microbolometer Focal plane array              | 18    |

| 2.3. Readout electronics for microbolometer FPAs                                        | 20 |

|-----------------------------------------------------------------------------------------|----|

| 2.3.1. Front-end signal conditioning circuits                                           | 21 |

| 2.3.1.1. Voltage-mode front-end readout circuits                                        | 22 |

| 2.3.1.2. Current-mode front-end readout circuits                                        | 25 |

| 2.3.1.3. Other front-end readout circuits                                               | 31 |

| 2.3.2. On-chip non-uniformity correction                                                | 31 |

| 2.3.3. Other on-chip functions                                                          | 33 |

| 2.4. Self-heating effect and cancellation techniques                                    | 36 |

| 2.5. Summary                                                                            | 39 |

| Chapter 3. Electro-thermal Characteristics of Microbolometer                            | 40 |

| 3.1. Thermal characteristics of microbolometer                                          | 41 |

| 3.2. Construction of SPICE electro-thermal model for microbolometer                     | 42 |

| 3.2.1. Elector-thermal model of microbolometer                                          | 43 |

| 3.2.2. Verification of the SPICE microbolometer model                                   | 45 |

| 3.3. Study of response of the microbolometer to the infrared and self-heating power     | 48 |

| 3.4. Summary                                                                            | 56 |

| Chapter 4. Readout IC for Microbolometer with Voltage-mode Self-heating<br>Cancellation | 57 |

|                                                                                         |    |

| 4.1. A new self-heating cancellation method                                             |    |

| 4.1.1. Self-heating cancellation circuit                                                |    |

| 4.1.2. Determination capacitor and current values                                       |    |

| 4.1.3. Function verification                                                            | 63 |

| 4.2. Self-heating cancellation circuit design                              | 64   |

|----------------------------------------------------------------------------|------|

| 4.2.1. Circuit design                                                      | 64   |

| 4.2.2. Charge injection and clock feed-through                             | 66   |

| 4.2.3. Final simulation results                                            | 69   |

| 4.3. Incorporation the voltage-mode self-heating cancellation circuit into |      |

| ROIC                                                                       | 70   |

| 4.3.1. Clock and control signals generation                                | 72   |

| 4.3.1.1. Clock generator for main_clk and $\phi_1$ , $\phi_2$              | 73   |

| 4.3.1.2. Clock generator for A/D converter                                 | 75   |

| 4.3.1.3. Pixel addressing signal generation                                | 77   |

| 4.3.2. Pre-amplifier design                                                | 79   |

| 4.3.2. Fixed pattern noise correction                                      | 83   |

| 4.4. Summary                                                               | 87   |

| Chapter 5. Readout IC for Microbolometer with Current-mode Self-hea        | ting |

| Cancellation                                                               | 88   |

| 5.1. Current-mode self-heating cancellation circuit                        | 88   |

| 5.1.1. Current-mode self-heating cancellation scheme                       | 88   |

| 5.1.2. Determination of the capacitor and current values                   | 91   |

| 5.1.3. Function verification                                               | 92   |

| 5.2. Current-mode ROIC with self-heating cancellation                      | 95   |

| 5.2.1. Digital circuitry of the current-mode ROIC                          | 97   |

| 5.2.2. Current subtraction circuit                                         | 98   |

| 5.2.3. Current steering DAC design                                         | 102  |

| 5.2.3.1. Selection of the current-steering DAC structure                   | 102  |

| 5.2.3.2. Current sources and mirrors                                         | 104 |

|------------------------------------------------------------------------------|-----|

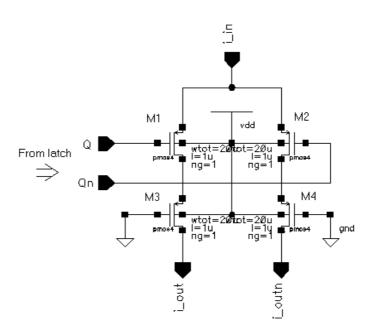

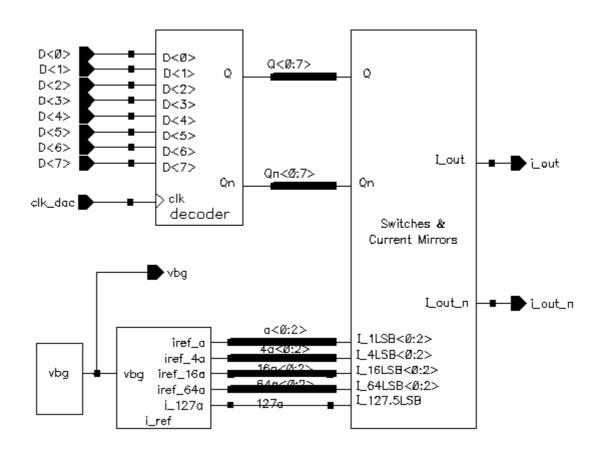

| 5.2.3.3. Decoder logic                                                       | 109 |

| 5.2.3.4. Differential switches and low-crossing latch                        | 111 |

| 5.2.3.5. Current-steering DAC circuit and performance                        | 113 |

| 5.2.4. Current-mode fixed pattern noise cancellation circuit                 | 117 |

| 5.3. Summary                                                                 | 121 |

| Chapter 6. Experimental Results                                              | 122 |

| 6.1. Microbolometers used in measurement                                     | 123 |

| 6.2. Test of the voltage-mode self-heating cancellation circuits with single |     |

| microbolometer                                                               | 125 |

| 6.3. Test of the current-mode self-heating cancellation circuits with single |     |

| microbolometer                                                               | 129 |

| 6.4. Test of the voltage-mode ROIC with an external microbolometer FPA       | 132 |

| 6.4.1. Test set-up of the voltage-mode ROIC                                  | 132 |

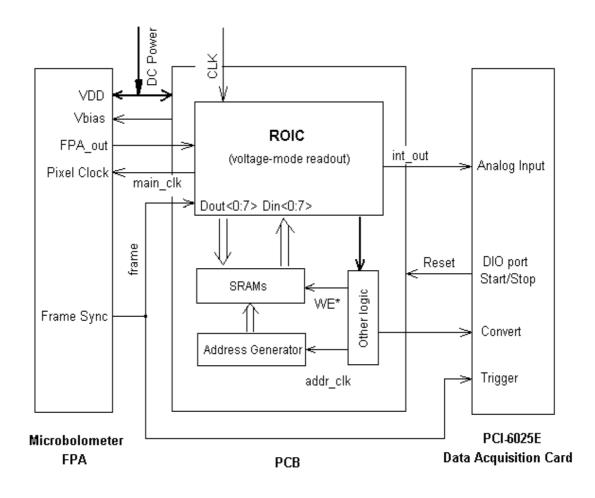

| 6.3.1.1. Hardware interface of the test system                               | 134 |

| 6.3.1.2. Image acquisition software                                          | 138 |

| 6.3.2. Test results of the voltage-mode ROIC                                 | 140 |

| 6.4. Test of the current-mode fixed pattern correction circuit on ROIC       | 147 |

| 6.5. Summary                                                                 | 151 |

| Chapter 7. Conclusion                                                        | 153 |

| 7.1. Conclusions                                                             | 153 |

| 7.2. Original contributions                                                  | 154 |

| 7.3. Future work                                                             | 154 |

| References                                                            | 156 |

|-----------------------------------------------------------------------|-----|

| Appendix A: List of Publications                                      | 174 |

| Appendix B: LabVIEW programs                                          | 175 |

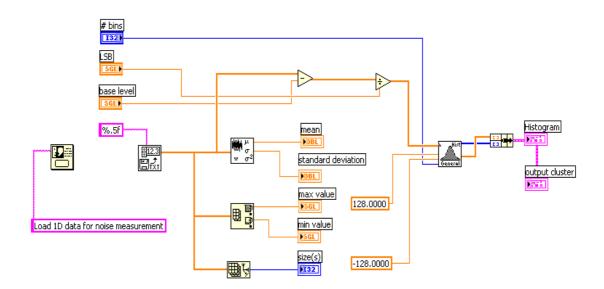

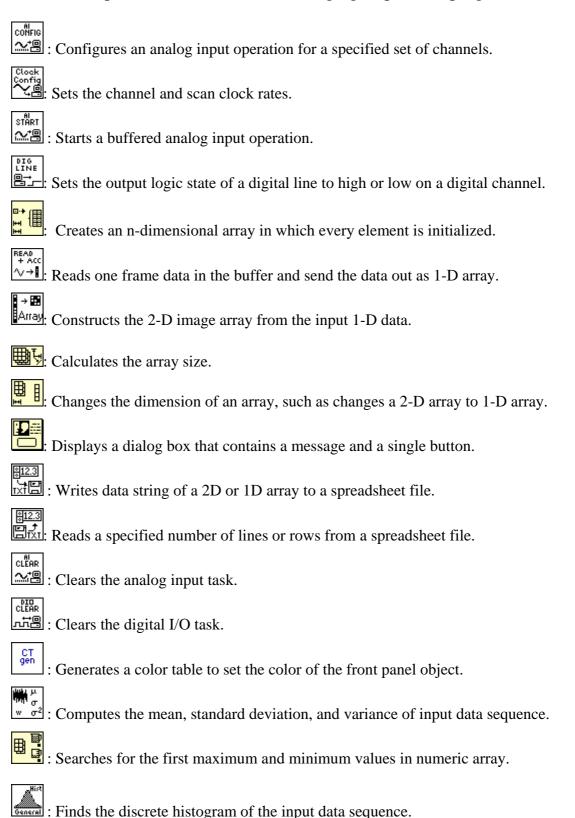

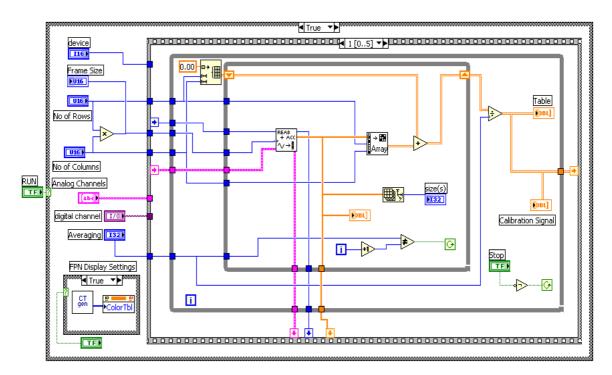

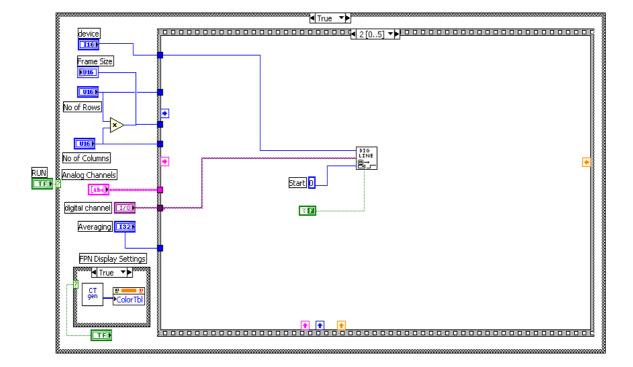

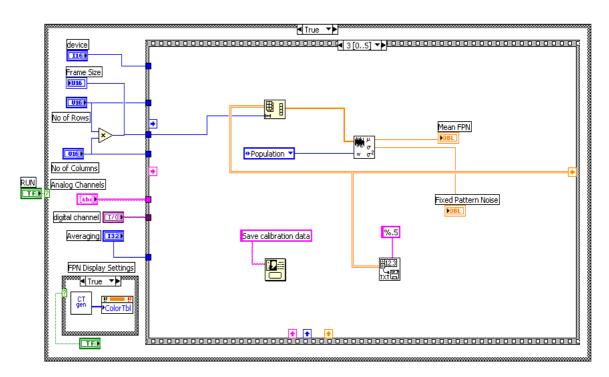

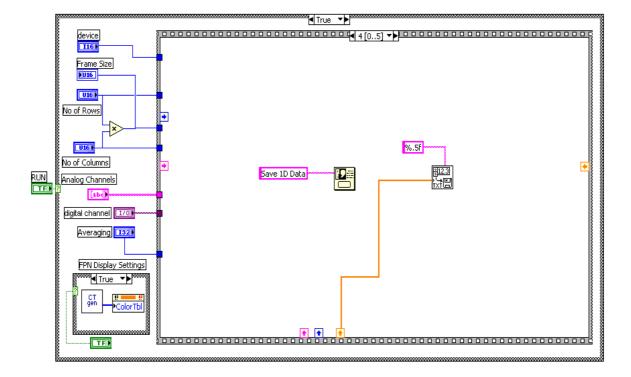

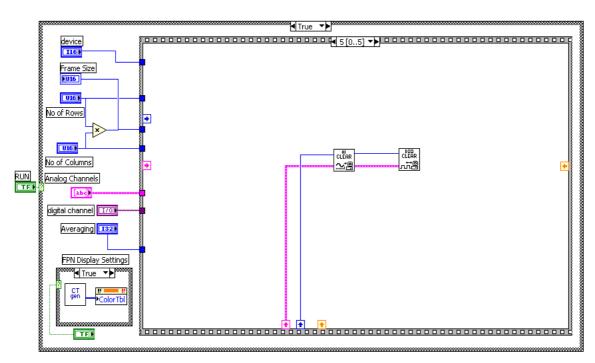

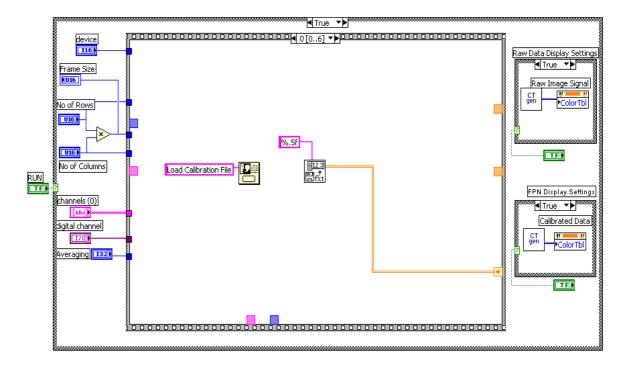

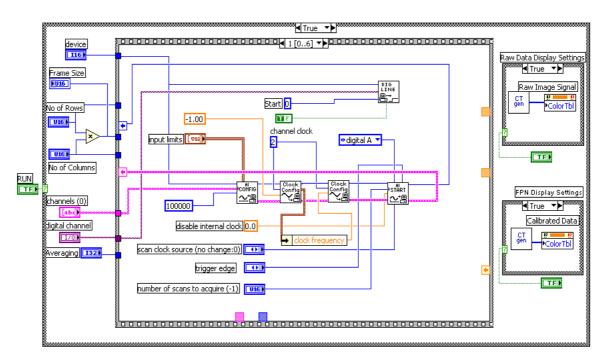

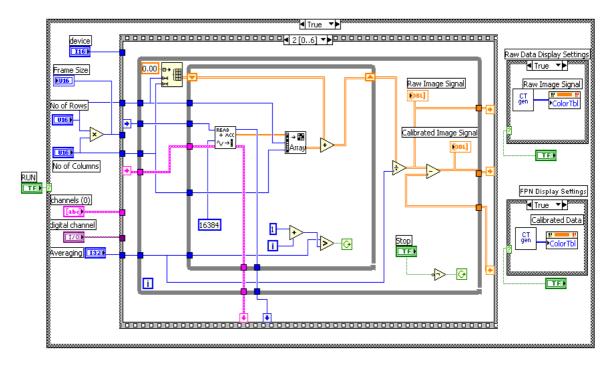

| B.1. Descriptions of the sub-VIs used in imaging acquisition programs | 175 |

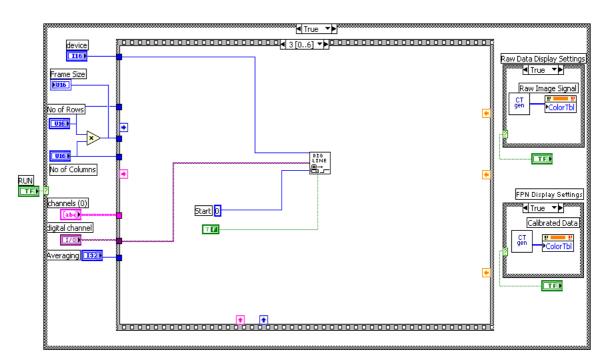

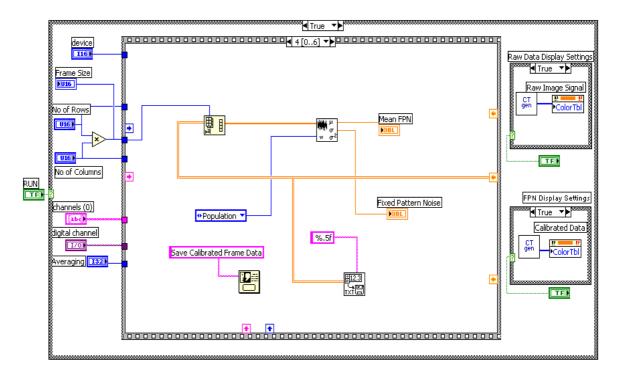

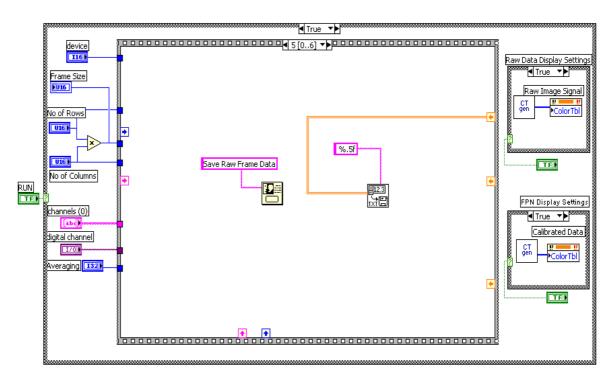

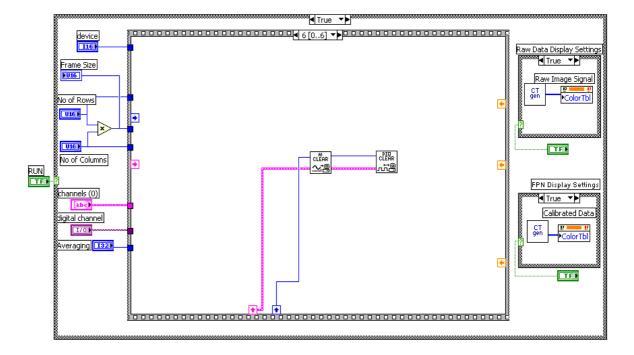

| B.2. LabVIEW program for calibration operation                        | 176 |

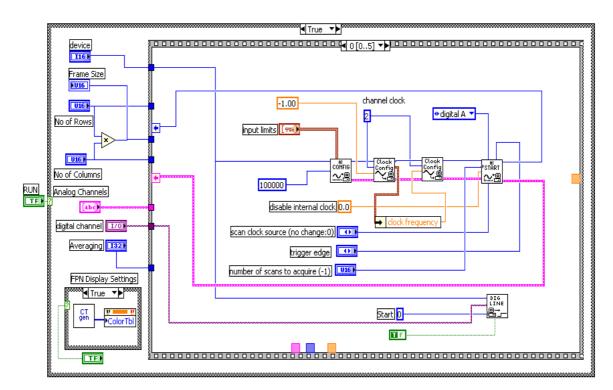

| B.3. LabVIEW program for real-time imaging                            | 179 |

| B.4. LabVIEW program for noise measurements                           | 182 |

### Summary

Uncooled microbolometer infrared detectors have a number of advantages over other types of detectors. They have showed their commercial potential to realize low-cost, high-performance infrared imagery systems. Microbolometer changes its resistance in response to the infrared radiation. In order to monitor the change of the resistance, microbolometers need to be electrically biased during the operation. Unfortunately, the bias current flowing through the microbolometer generates the heat on the sensor itself. This unavoidable self-heating effect will severely affect the readout circuits, such as the degradation of the dynamic range. The continuing improvement on the performance of the uncooled thermal imagers have driven the motive of developing an effective circuit for self-heating cancellation that can be applied to on-chip readout electronics for the microbolometer focal plane array.

This project looks into a novel technique of self-heating cancellation for microbolometer. Such a cancellation scheme is based on the equivalence between the electrical and thermal systems, and uses a capacitor to mimic the thermal capacitance of the microbolometer. A replica of the bias heating can generated on the capacitor and later used to cancel the self-heating of the bolometer. The concept of using the electrical equivalence of bolometer's thermal parameter to build the replica of self-heating is extended to current-mode readout circuits. A PMOS transistor working in the triode region is used to generate the ramp current to compensate the self-heating effect in a current subtraction circuit. Both voltage- and current-mode self-heating cancellation circuits are realized in silicon and the effectiveness is demonstrated with a single microbolometer.

vii

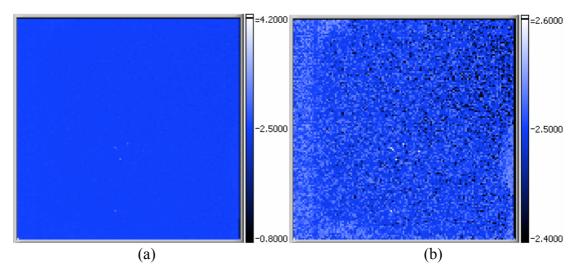

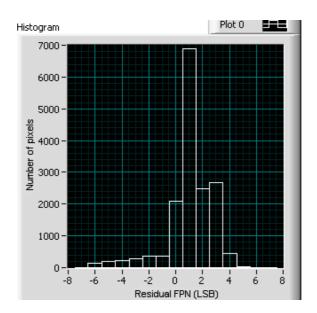

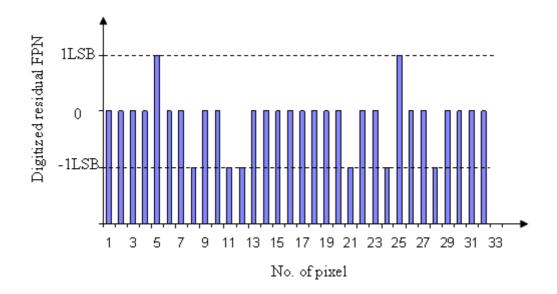

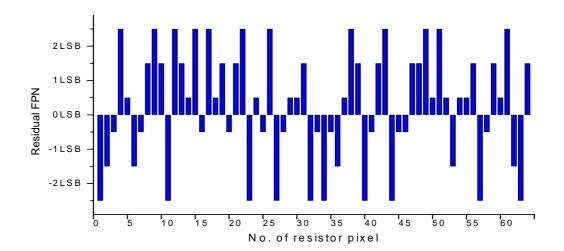

The voltage- and current-mode ROICs (readout integrated circuits) with the proposed self-heating cancellation circuit have been developed together with on-chip 8-bit fixed pattern noise (FPN) correction circuits. The ROICs were fabricated in a 0.6  $\mu$ m CMOS technology. The voltage-mode ROIC was evaluated with an external 128 × 128 microbolometer FPA. The test results have shown that the FPN can be corrected to a 7-bit resolution when exclude the pixels with unexpected large FPN from test, and an 8-bit resolution can be attained when tested with a built-in resistor array. The current-mode ROIC has been evaluated with a built-in 8 × 8 resistor array for the performance of FPN correction, since the microbolometer FPA for current-mode ROIC is not available. The measured residual FPN of less than ±2.5 LSB has been achieved. Due to the unavailability of proper microbolometer FPAs, the self-heating cancellation cannot be demonstrated with the on-chip FPN correction in the ROICs.

# List of Figures

| Fig. 1.1. Block diagram of a bolometer infrared detection system4                                                          |

|----------------------------------------------------------------------------------------------------------------------------|

| Fig. 1.2. Thermal image taken by the uncooled infrared camera LTC5504                                                      |

| Fig. 1.3. Structure of a bulk micromachined bolometer8                                                                     |

| Fig.1.4. Microstructure of the surface micomachined microbolometer9                                                        |

| Fig.1.5. Basic readout circuit of the microbolometer10                                                                     |

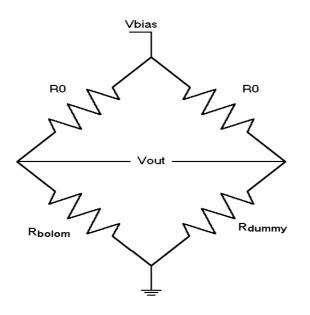

| Fig.1.6. Wheatstone bridge readout circuit of the microbolometer10                                                         |

| Fig. 2.1. Flip-chip-hybrid (a) and monolithic (b) structures of microbolometer<br>FPA19                                    |

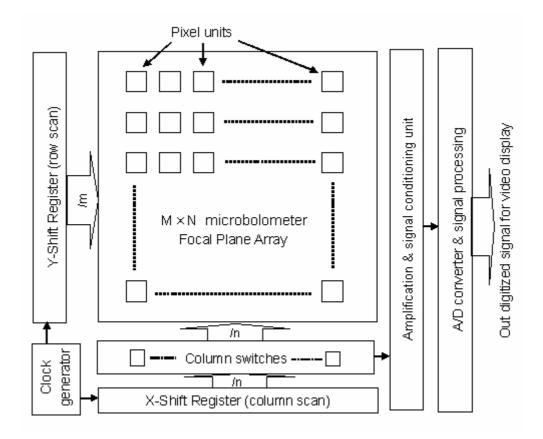

| Fig. 2.2. Block diagram of the ROIC for an M × N-pixel microbolometer focal plane array21                                  |

| Fig. 2.3. Two simplest voltage-mode readout circuits23                                                                     |

| Fig. 2.4. Chopper-amplifier voltage-mode circuit23                                                                         |

| Fig. 2.5. AC-bias bridge readout circuit for bolometer24                                                                   |

| Fig. 2.6. Bridge readout circuit with capacitive load25                                                                    |

| Fig. 2.7. A simple current-mode readout for microbolometer26                                                               |

| Fig. 2.8. Pixel amplifier and pulse current bias circuits27                                                                |

| Fig. 2.9. Direct injection circuit28                                                                                       |

| Fig. 2.10. Direct injection circuit with CTIA integrator28                                                                 |

| Fig. 2.11. The shared integration cell with current-mode background suppression29                                          |

| Fig. 2.12. CCBDI readout circuit30                                                                                         |

| Fig. 2.13. Pixel-wised A/D converter circuit31                                                                             |

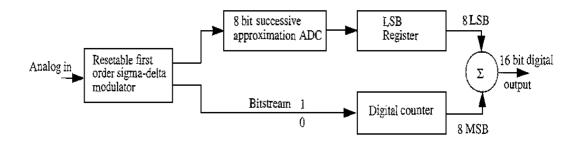

| Fig. 2.14. Block diagram of the two-mode 16-bit A/D converter33                                                            |

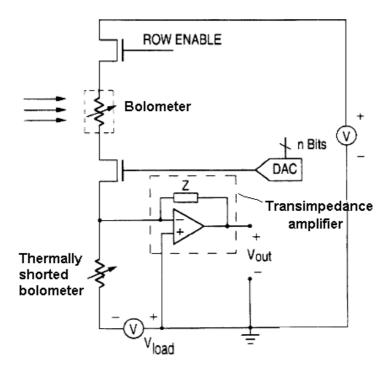

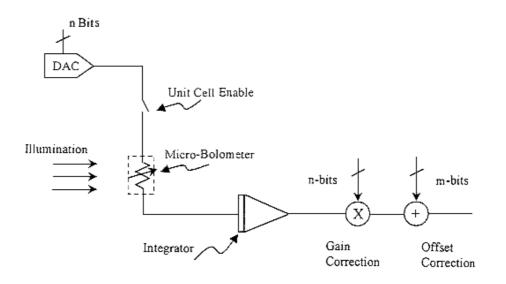

| Fig. 2.15. Method for correction for temperature-induced non-uniformities with thermally shorted microbolometer elements34 |

| Fig. 2.16. Block diagram of the three-point correction scheme3                                                                                                         | 35 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

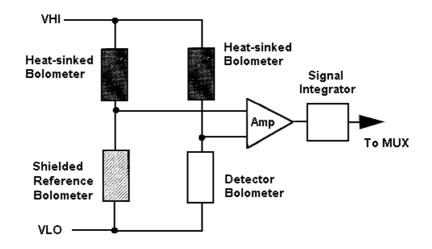

| Fig. 2.17. Front-end readout circuit with the self-heating cancellation using blind bolometer3                                                                         | 37 |

| Fig. 2.18. Self-heating compensation circuits in [131] [132]3                                                                                                          | 37 |

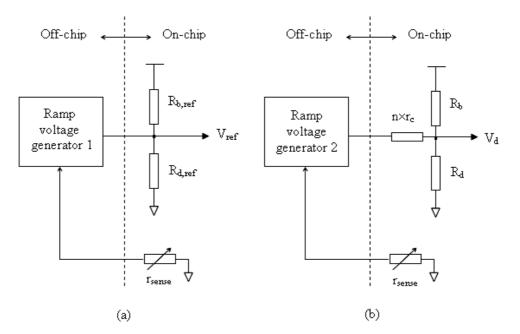

| Fig. 2.19. Off-chip self-heating compensation schemes: (a) Compensation of the difference of $V_{ref}$ and $V_d$ ; (b) Direct compensation of $V_d$ 3                  | 39 |

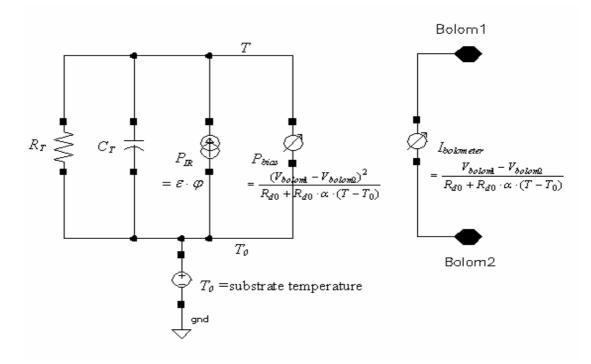

| Fig. 3.1. Electro-thermal model of microbolometer4                                                                                                                     | 14 |

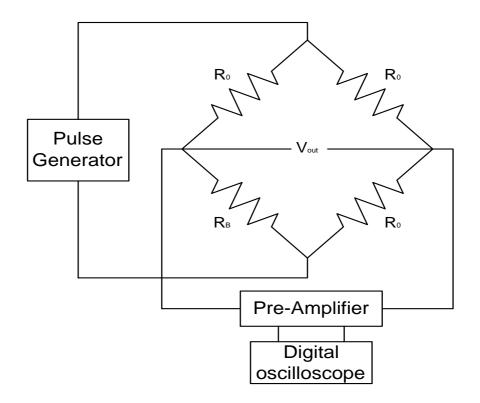

| Fig. 3.2. Experimental setup in Ref.[95], where $R_B$ is the microbolometer and $R_0$ s are the fixed reference resistors4                                             | 45 |

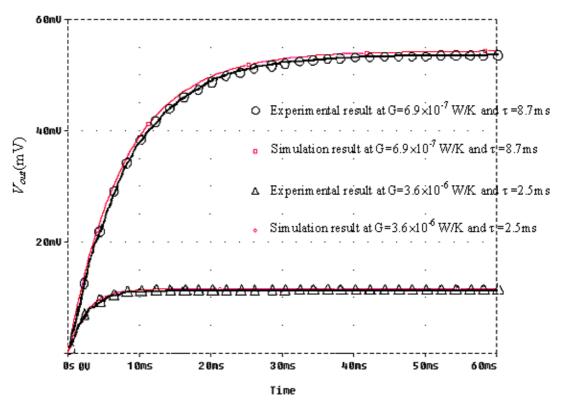

| Fig.3.3. Comparison of simulation results using the SPICE model with the experimental data4                                                                            | 47 |

| Fig. 3.4. Wheatstone bridge readout circuit5                                                                                                                           | 50 |

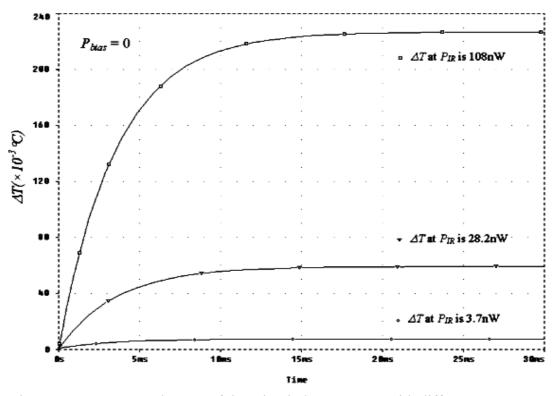

| Fig. 3.5. Temperature changes of the microbolometer, $\Delta T$ , with different IR powers5                                                                            | 51 |

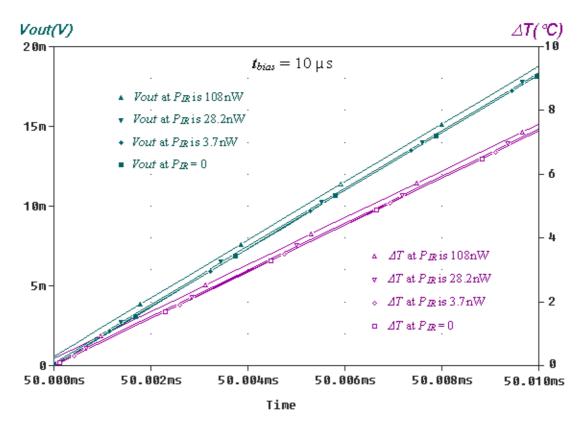

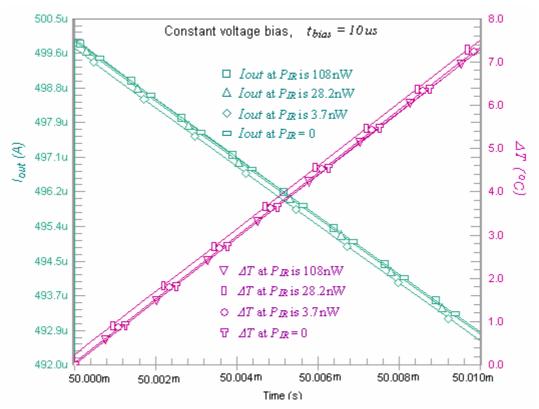

| Fig.3.6. Output voltage (green curves) and temperature change (pink curves) of the the microbolometer with different input IR powers5                                  | 52 |

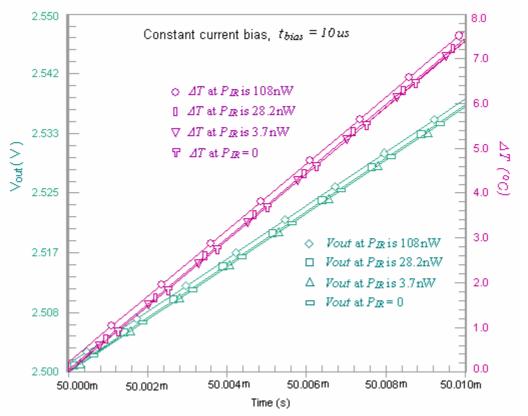

| Fig. 3.7. Output voltage (green curves) and temperature change (pink curves) of the microbolometer with different input IR powers, at constant current bias5.          | 5  |

| Fig. 3.8. Output current (green curves) and temperature change (pink curves) of the microbolometer with different input IR powers, at constant voltage bias5           | 55 |

| Fig. 4.1. Schematics of the self-heating canceling scheme5                                                                                                             | 59 |

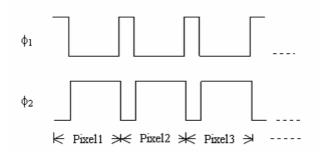

| Fig. 4.2. Waveforms of the clock signals5                                                                                                                              | 59 |

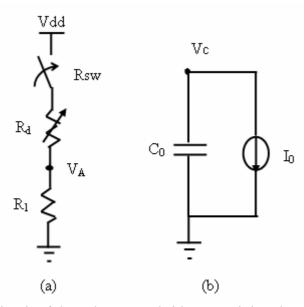

| Fig. 4.3. (a) Half circuit of the Wheatstone bridge containing the microbolometer<br>and (b) I-C pair that generates the replica of the self-heating6                  | 50 |

| Fig. 4.4. Mimic the self-heating effect using an I-C pair6                                                                                                             | 52 |

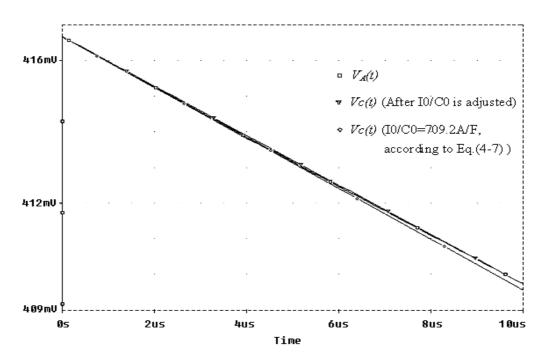

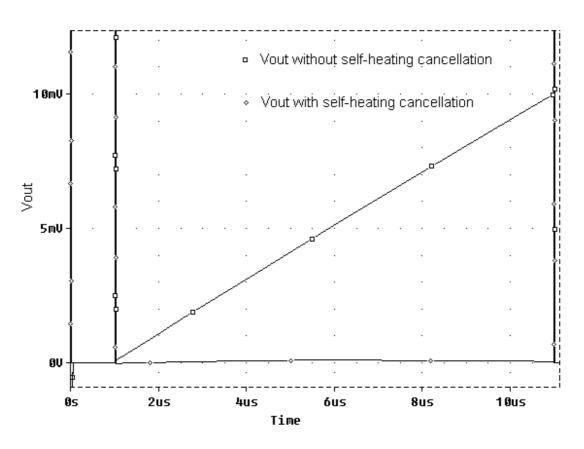

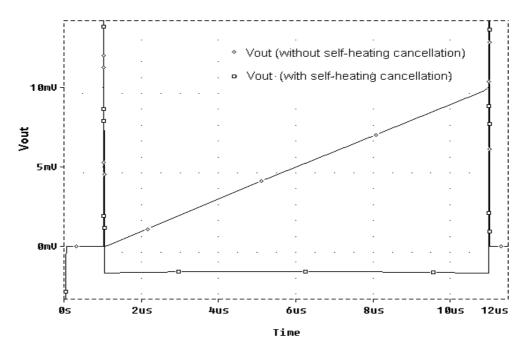

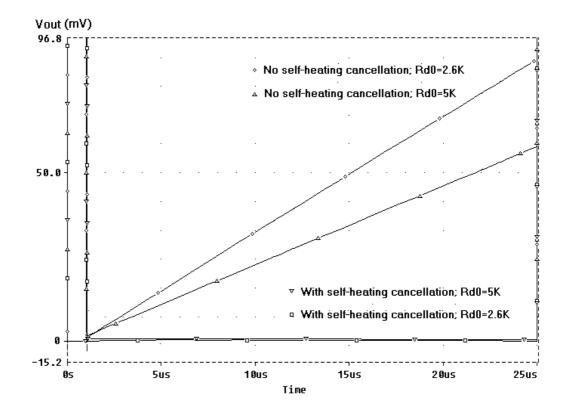

| Fig. 4.5. Simulation results for the self-heating cancellation circuit6                                                                                                | 54 |

| Fig. 4.6. The schematics of the tuneable self-heating cancellation circuit6                                                                                            | 55 |

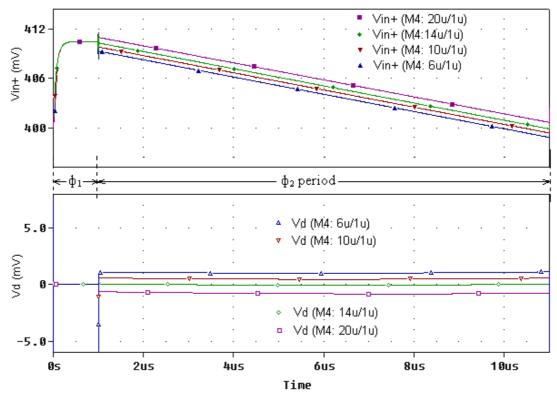

| Fig. 4.7. Output of the implemented self-heating cancellation circuit with non-<br>ideal switches6                                                                     | 56 |

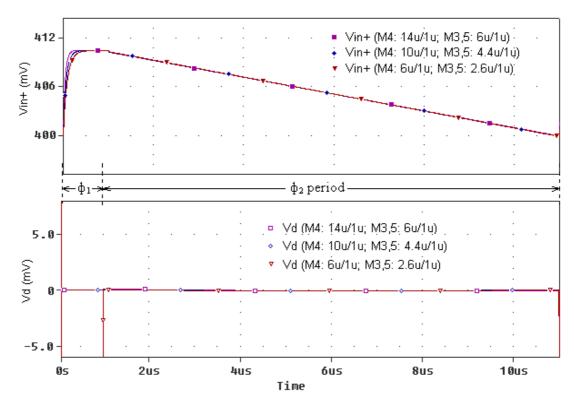

| Fig.4.8. Charge injection vs. different aspect ratio of M4. The upper plot shows non-<br>inverting inputs of the preamplifier, while the lower plot shows differential |    |

inverting inputs of the preamplifier, while the lower plot shows differential inputs of the preamplifier, at the different aspect ratio of M4-----68

| Fig.4.9. Charge injection after the size of M4 is optimized. The upper plot shows inverting inputs of the preamplifier, while the lower plot shows differenti inputs of the preamplifier, when size of M4 over M3,5 are around 2.3 | al |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig.4.10. Simulation results of optimized self-heating cancellation circuit                                                                                                                                                        | 70 |

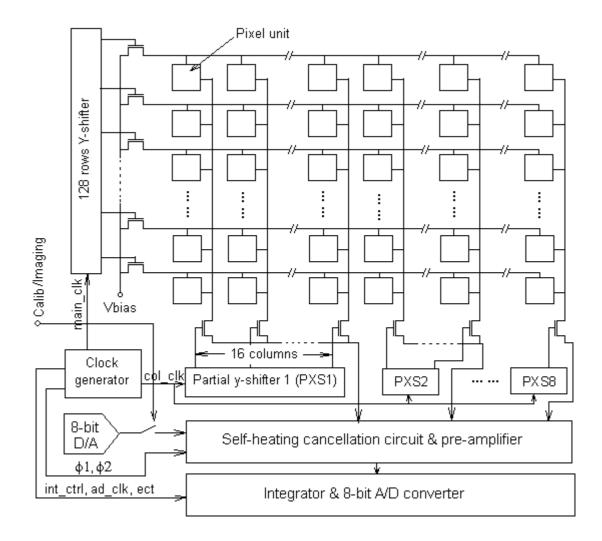

| Fig. 4.11. Partially parallel readout architecture of the voltage-mode ROIC                                                                                                                                                        | 71 |

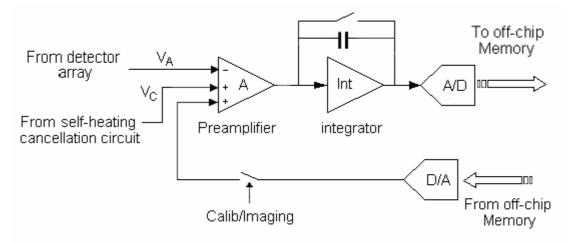

| Fig. 4.12. Block diagram of the fixed pattern noise correction circuit                                                                                                                                                             | 72 |

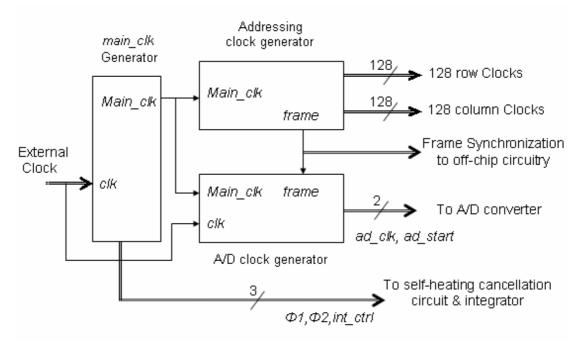

| Fig. 4.13. Block diagram of clock and control signal generator                                                                                                                                                                     | 73 |

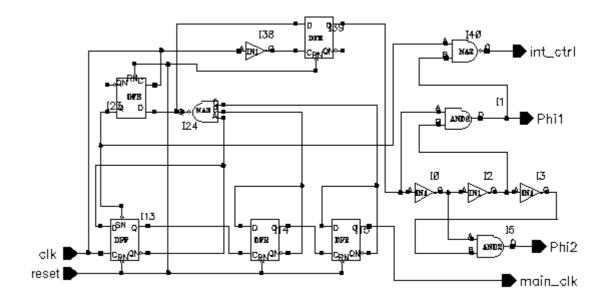

| Fig.4.14. Schematic of the pixel clock and control signal generator                                                                                                                                                                | 74 |

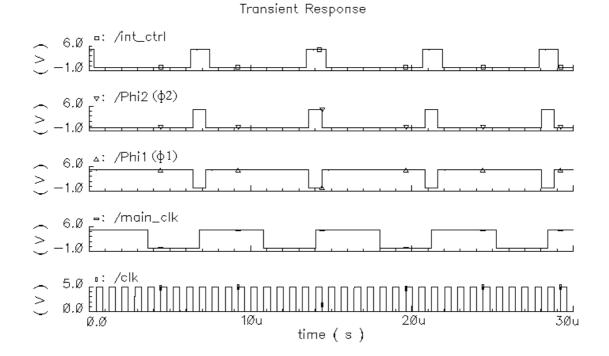

| Fig.4.15. Waveforms of <i>int_ctrl</i> , $\phi_2$ , $\phi_1$ <i>main_clk</i> and <i>clk</i>                                                                                                                                        | 75 |

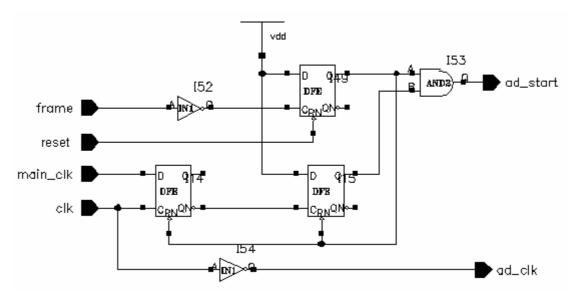

| Fig.4.16. Schematic of the <i>ad_clk</i> and <i>ad_start</i> signal generator                                                                                                                                                      | 76 |

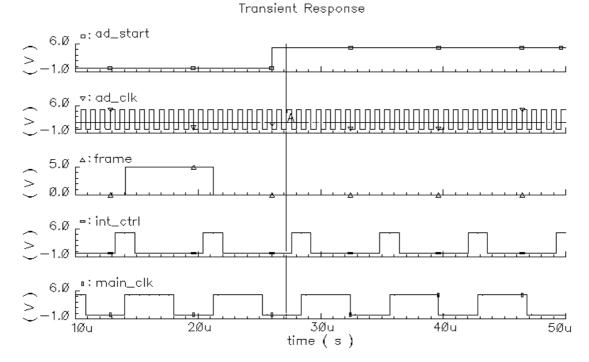

| Fig.4.17. Timing waveforms of ad_start, ad_clk, frame, int_ctrl and main_clk                                                                                                                                                       | 76 |

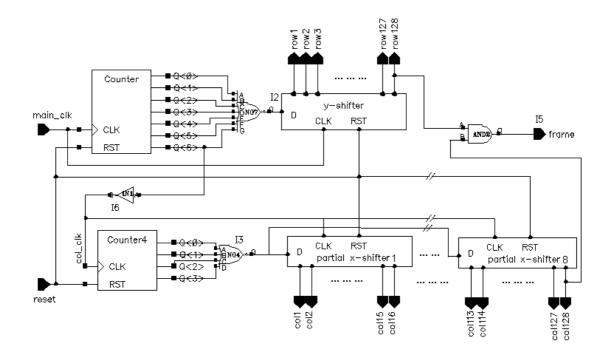

| Fig. 4.18. Block diagram of the X-Y scanning clock generator                                                                                                                                                                       | 78 |

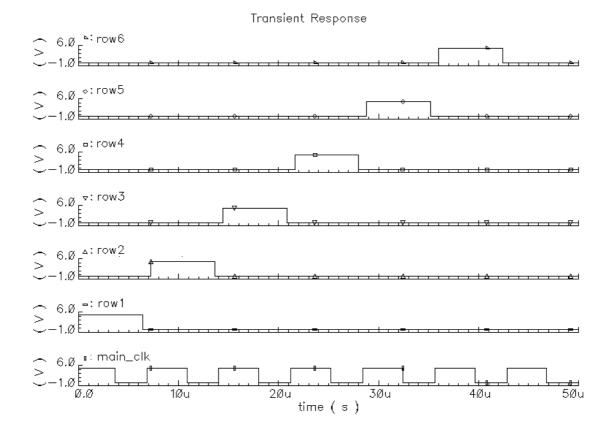

| Fig. 4.19. Waveforms of the scanning clocks of the first 6 rows and <i>main_clk</i>                                                                                                                                                | 78 |

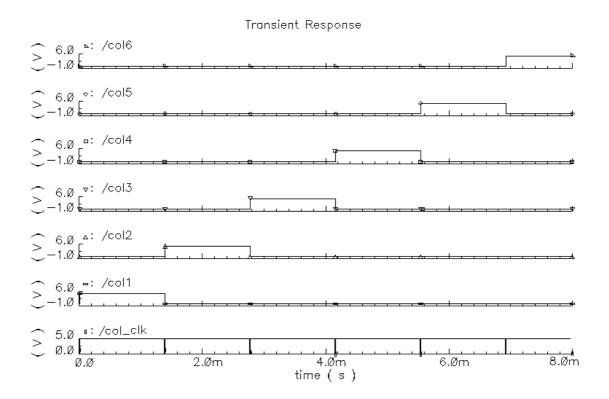

| Fig. 4.20. Waveforms of the scanning clocks of the first 6 columns and <i>col_clk</i> -                                                                                                                                            | 79 |

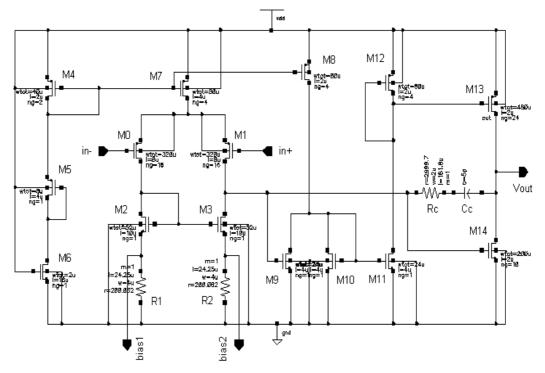

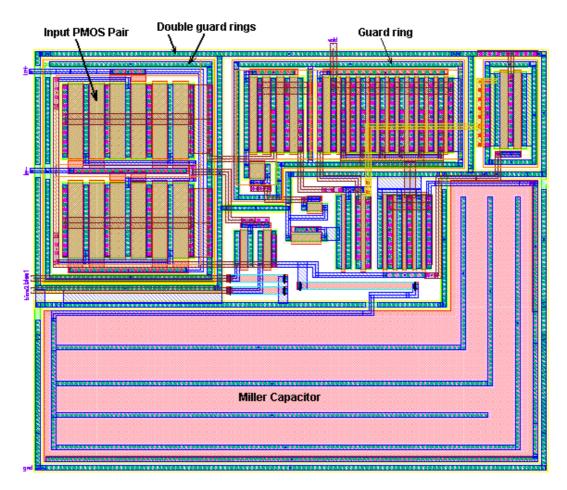

| Fig. 4.21. Schematic of the pre-amplifier                                                                                                                                                                                          | 82 |

| Fig. 4.22. Layout of the preamplifier                                                                                                                                                                                              | 82 |

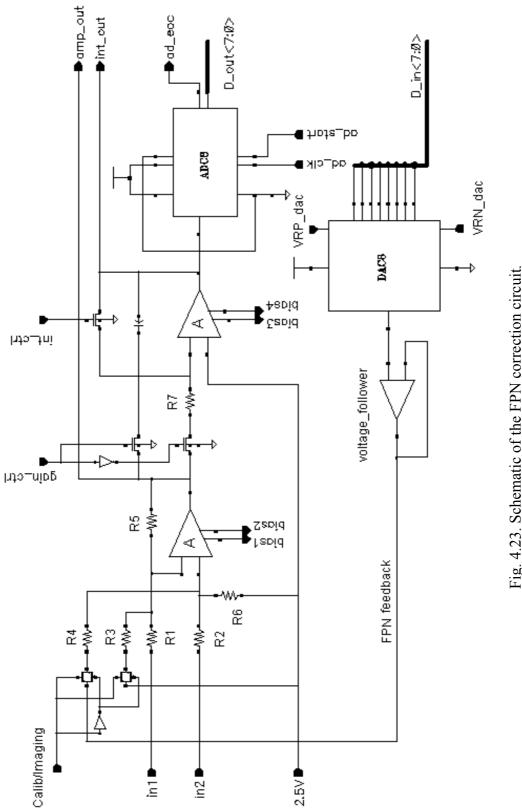

| Fig. 4.23. Schematic of the FPN correction circuit                                                                                                                                                                                 | 84 |

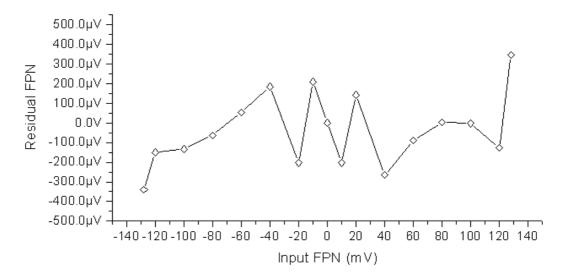

| Fig. 4.24. Simulation results of fixed pattern noise correction                                                                                                                                                                    | 87 |

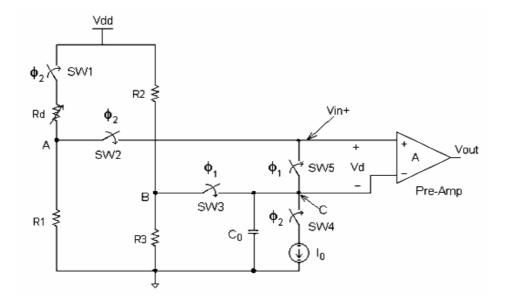

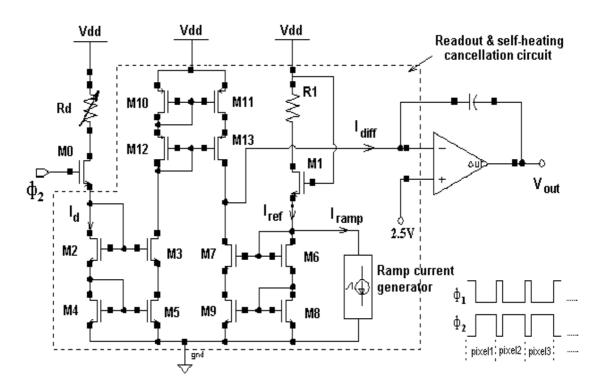

| Fig. 5.1. Schematic of the current-mode self-heating cancellation circuit                                                                                                                                                          | 90 |

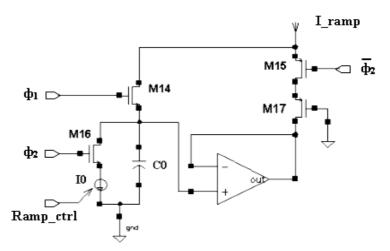

| Fig. 5.2. Schematic of the ramp current generator                                                                                                                                                                                  | 90 |

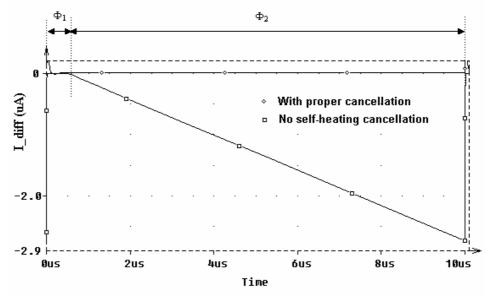

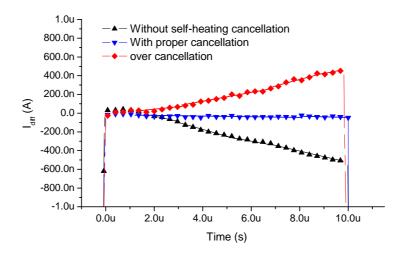

| Fig. 5.3. Simulation results for current-mode self-heating cancellation                                                                                                                                                            | 94 |

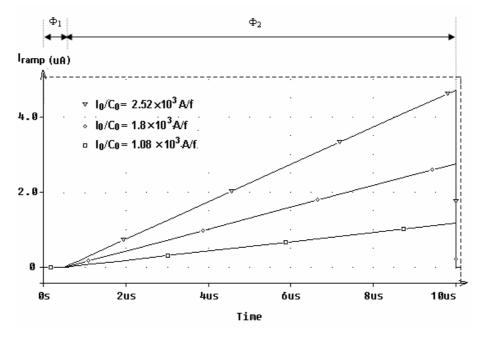

| Fig. 5.4. Tuneable feature of the ramp current generator                                                                                                                                                                           | 94 |

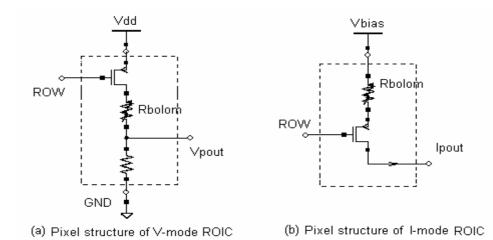

| Fig. 5.5. Pixel structure of the voltage-mode(a) and current-mode(b) readout circuit                                                                                                                                               | 95 |

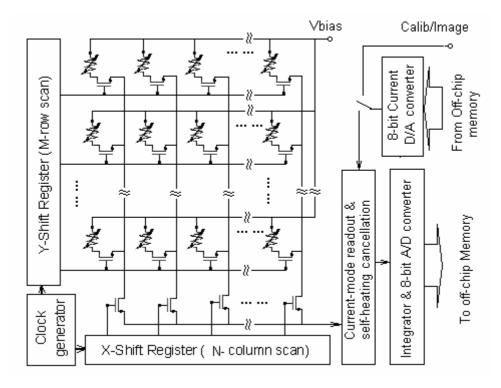

| Fig. 5.6. Readout circuit architecture of the current-mode ROIC for an $M \times N$ FPA                                                                                                                                            | 96 |

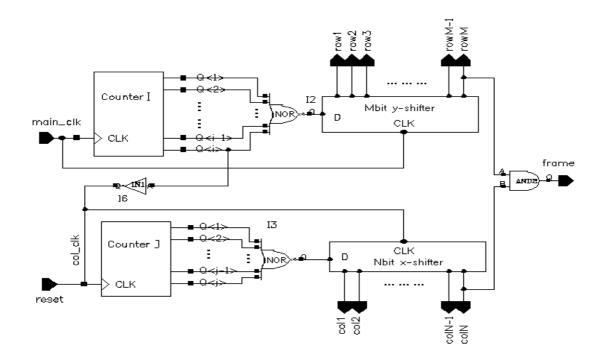

| Fig. 5.7. X-Y address clock generator for $M \times N$ FPA                                                                                                                                                                         | 97 |

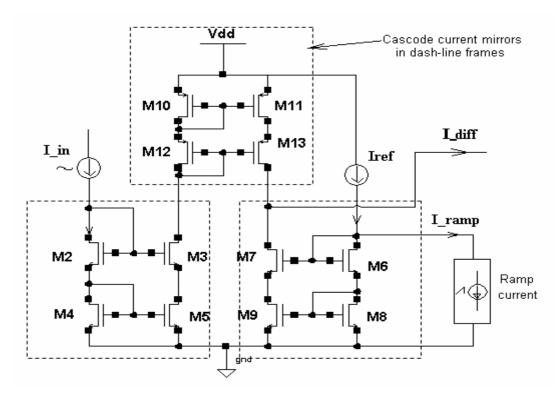

| Fig. 5.8. Current subtraction circuit                                                                                                                                                               | 98   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

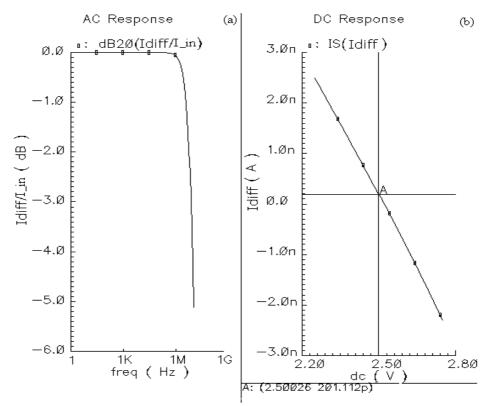

| Fig. 5.9. (a) AC sweep response and (b) DC sweep of the current subtraction circuit                                                                                                                 | -100 |

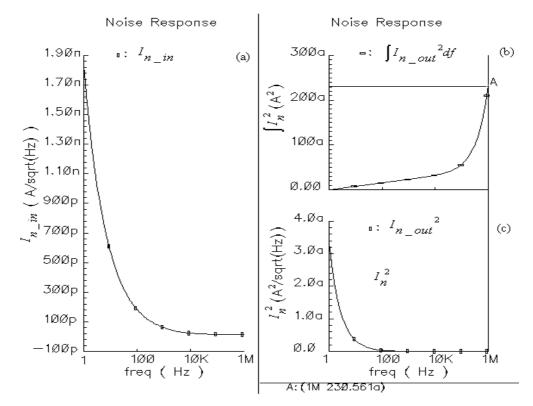

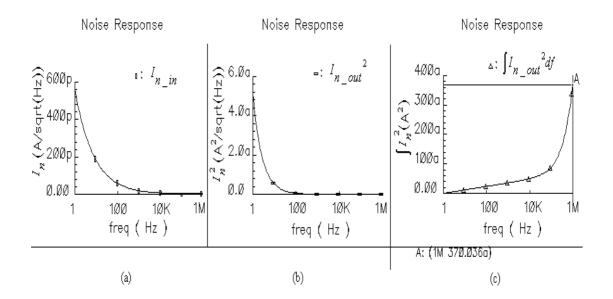

| Fig.5.10. Noise analysis of the current subtraction circuit: (a) Equivalent input current noise density, (b) output noise power density and (c) total noise power in the bandwidth from 1Hz to 1MHz | -100 |

| Fig.5.11.(a) Equivalent input current noise density; (b) output noise power density<br>and (c) total noise power in the bandwidth from 1 Hz to 1 MHz                                                |      |

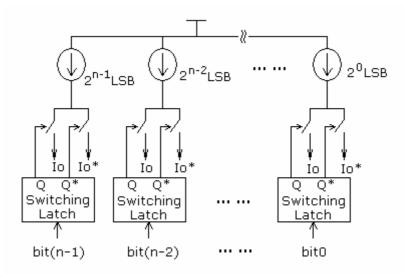

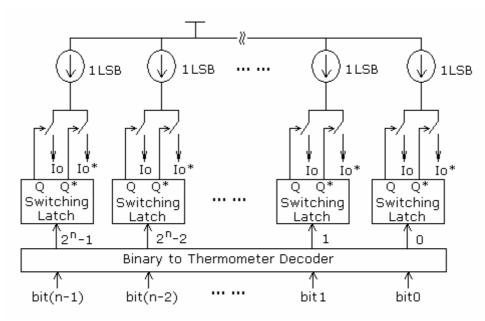

| Fig. 5.12. Binary weighted architecture of the current-steering DAC                                                                                                                                 | -103 |

| Fig. 5.13. Thermometer coded architecture of the current-steering DAC                                                                                                                               | -103 |

| Fig. 5.14. Segmented architecture of the 8-bit current-steering DAC                                                                                                                                 | -104 |

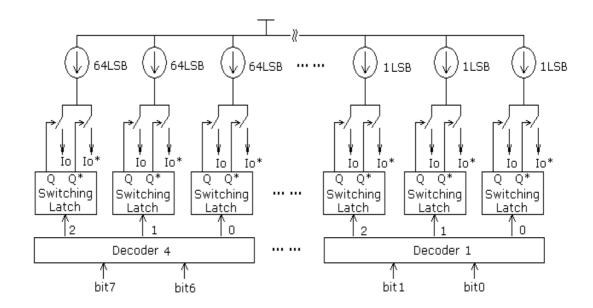

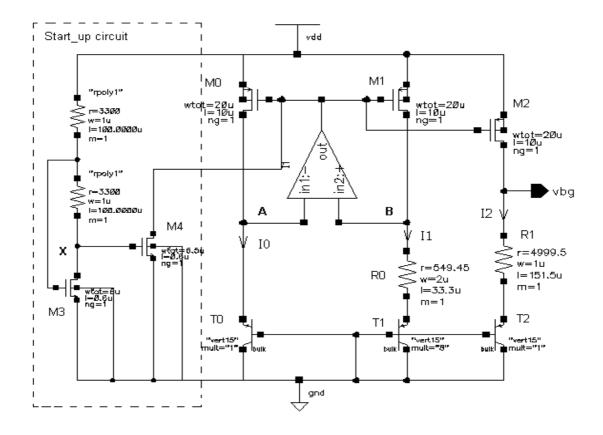

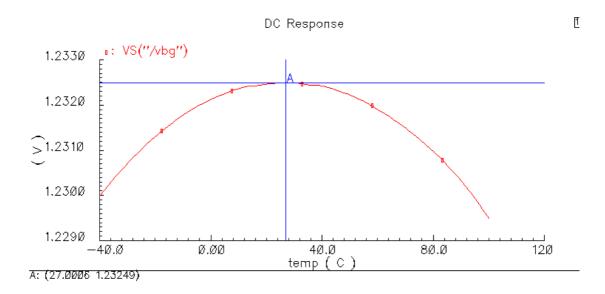

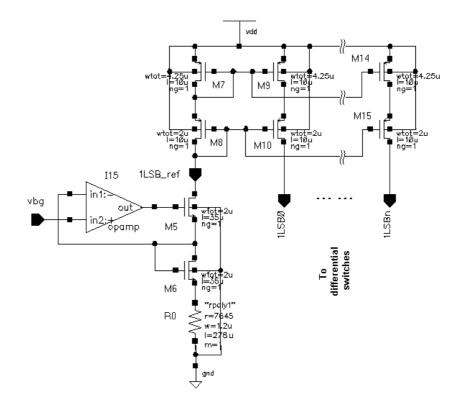

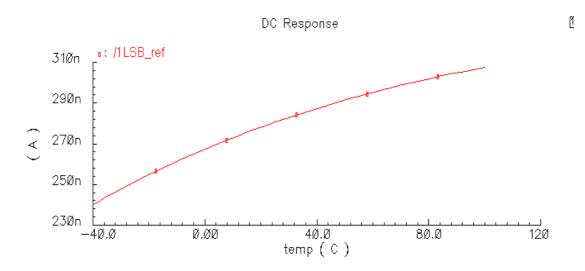

| Fig. 5.15. Schematic of the bandgap voltage reference circuit                                                                                                                                       | -107 |

| Fig. 5.16. Temperature dependence of the bandgap reference voltage output                                                                                                                           | -107 |

| Fig. 5.17. Schematic of the voltage-to-current converter                                                                                                                                            | -109 |

| Fig. 5.18. Simulation result of the 1 LSB basic current generator                                                                                                                                   | -109 |

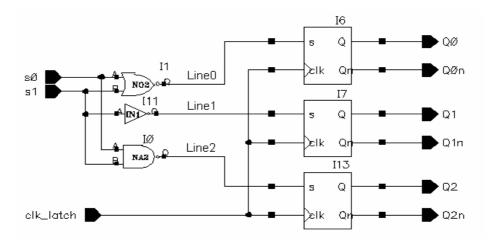

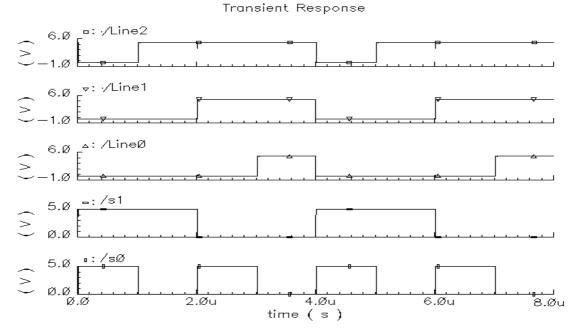

| Fig. 5.19. 2-bit binary-to-thermometer decoder circuit and latches                                                                                                                                  | -110 |

| Fig. 5.20. Waveforms of the decoder inputs, S0, S1 and outputs Line(0-3)                                                                                                                            | -111 |

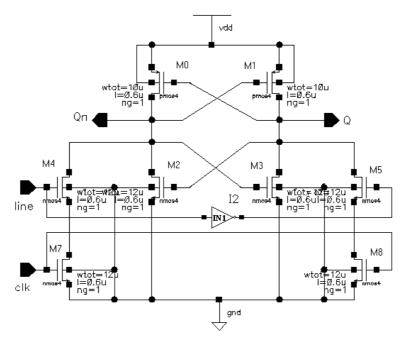

| Fig. 5.21. Schematic of the low-crossing latch                                                                                                                                                      | -111 |

| Fig. 5.22. Transient analysis results of the low-crossing latch                                                                                                                                     | -112 |

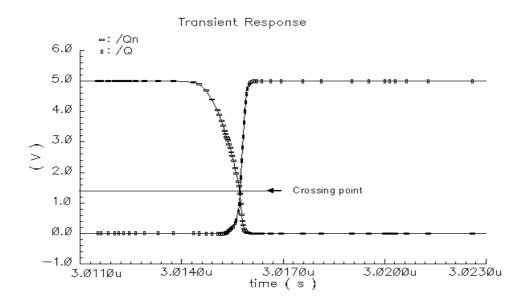

| Fig. 5.23. PMOS differential switches of the current outputs                                                                                                                                        | -113 |

| Fig. 5.24. Block diagram of the current-steering DAC                                                                                                                                                | -114 |

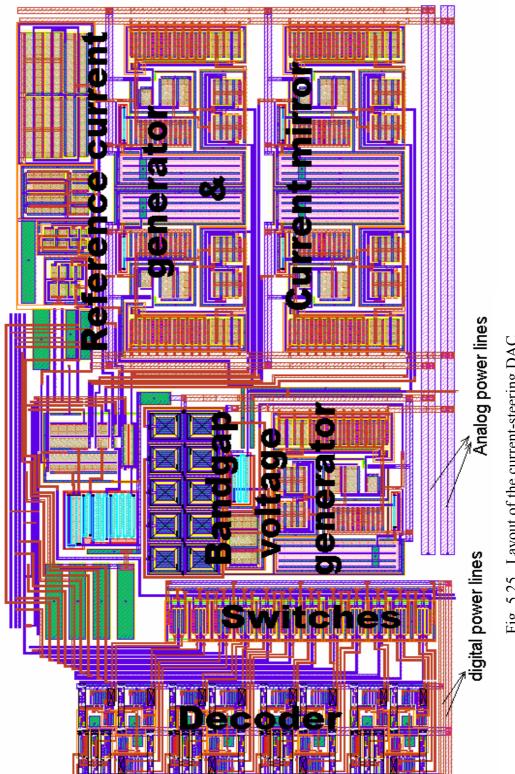

| Fig. 5.25. Layout of the current-steering DAC                                                                                                                                                       | -115 |

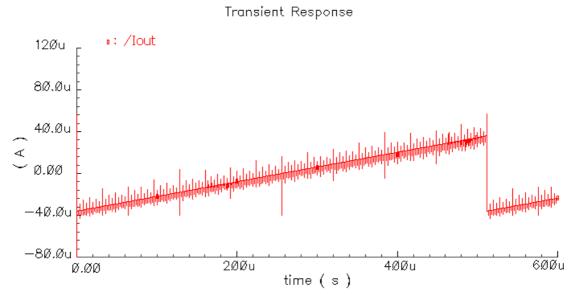

| Fig. 5.26. Transient analysis of the current-steering DAC                                                                                                                                           | -116 |

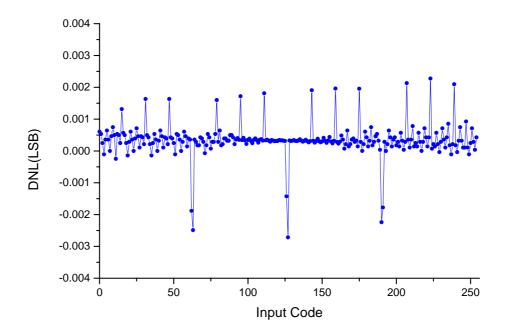

| Fig. 5.27. Simulated DNL of the current-steering DAC                                                                                                                                                | -116 |

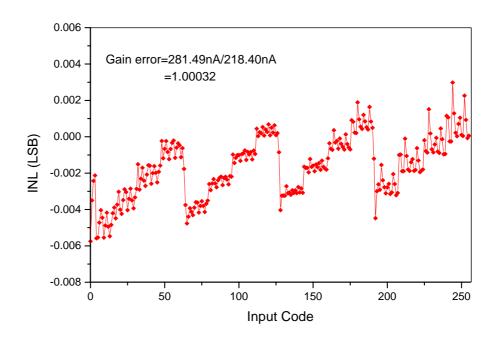

| Fig. 5.28. Simulated INL of the current-steering DAC                                                                                                                                                | -117 |

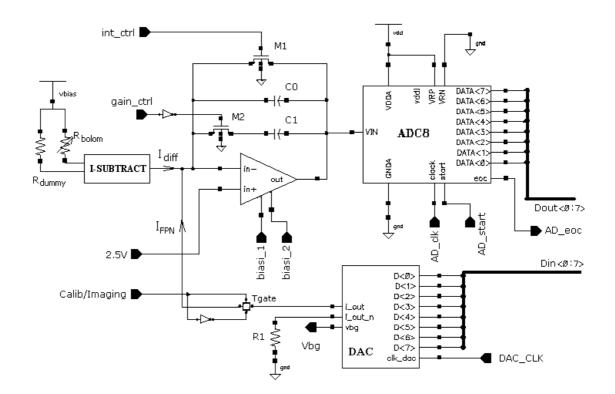

| Fig. 5.29. Schematic of the current-mode FPN correction circuit                                                                                                                                     | -118 |

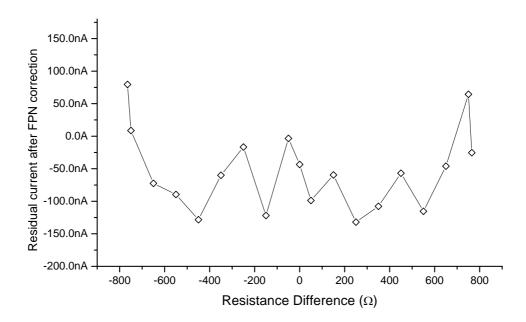

| Fig. 5.30. The residual FPN current after current-mode FPN correction                                                                                                                               | -121 |

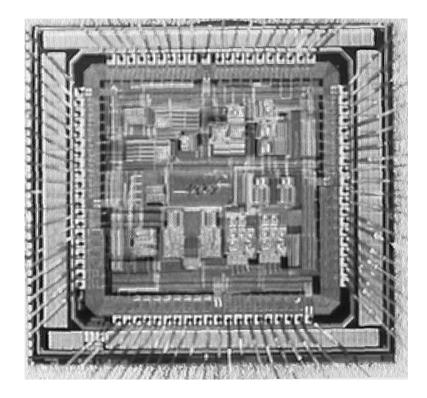

| Fig. 6.1. The microphoto of the ROIC12                                                                                                                                                      | 3 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

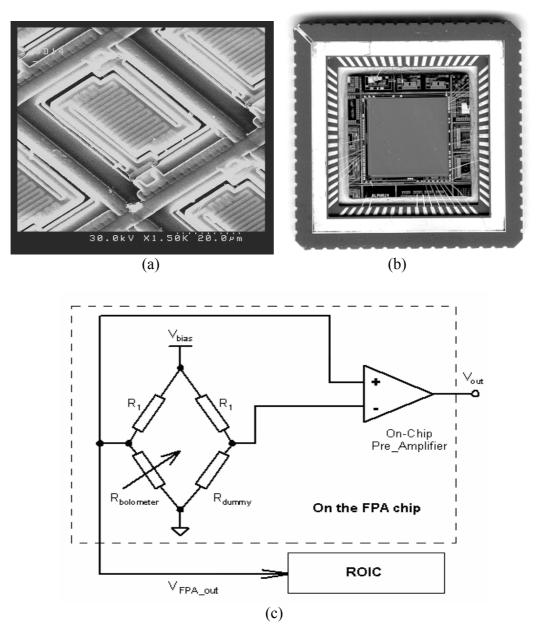

| Fig. 6.2. (a) SEM photo of the microbolometer on FPA; (b) The microphotograph of the microbolometer FPA chip; (c) On-FPA readout bridge and the output of FPA to our ROIC125                | 5 |

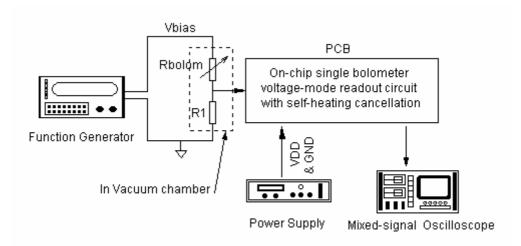

| Fig. 6.3. The test set-up of voltage-mode self-heating cancellation circuit for single bolometer12                                                                                          | 6 |

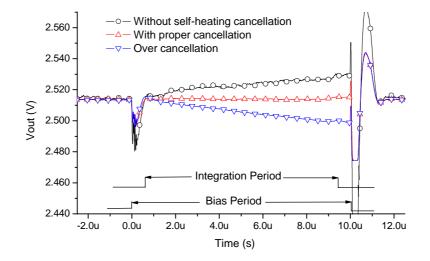

| Fig. 6.4. Measured output from preamplifier with different $I_0/C_0$ ratios12                                                                                                               | 8 |

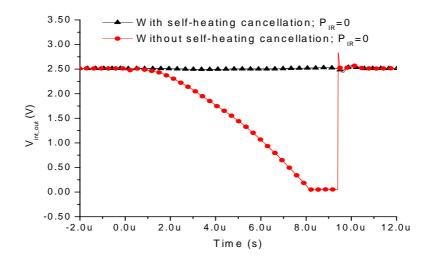

| Fig. 6.5. Measured output from integrator with and without self-heating cancellation                                                                                                        |   |

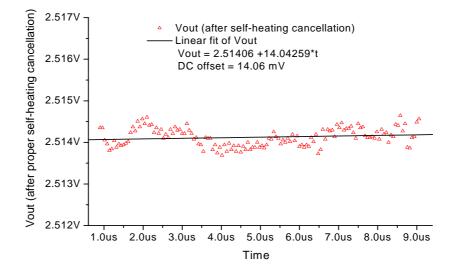

| Fig. 6.6. Measured residue error after self-heating cancellation12                                                                                                                          | 8 |

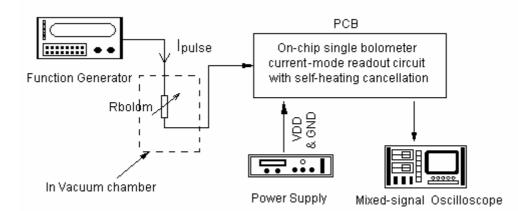

| Fig. 6.7. The test set-up of current-mode self-heat cancellation for single bolometer                                                                                                       |   |

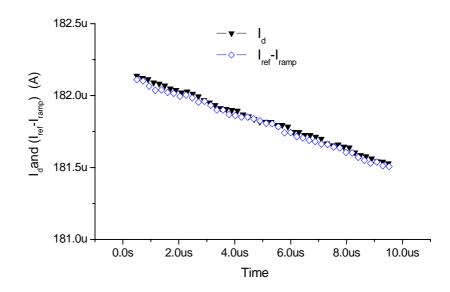

| Fig. 6.8. Measured $I_d$ and $I_{ref}$ - $I_{ramp}$ 130                                                                                                                                     | 0 |

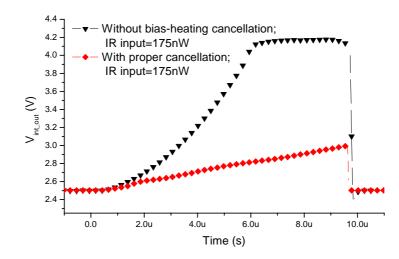

| Fig. 6.9. Integrator outputs with and without self-heating cancellation, at input IR power of 175nW13                                                                                       | 1 |

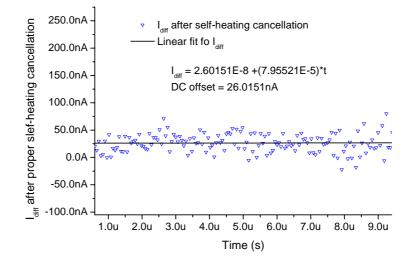

| Fig. 6.10. Measured residue error ( $I_{diff}$ ) after self-heating cancellation13                                                                                                          | 1 |

| Fig. 6.11. Tunable feature of the current-mode self-heating cancellation circuit13                                                                                                          | 1 |

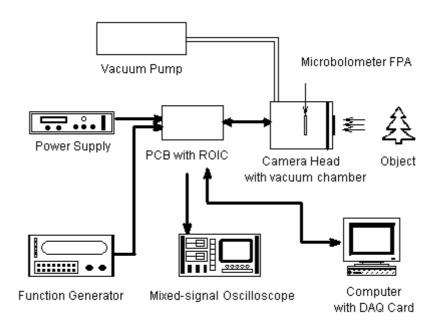

| Fig. 6.12. Test set-up for voltage-mode readout circuit13.                                                                                                                                  | 3 |

| Fig. 6.13. The signal flow diagram of the hardware interface of the test system13.                                                                                                          | 5 |

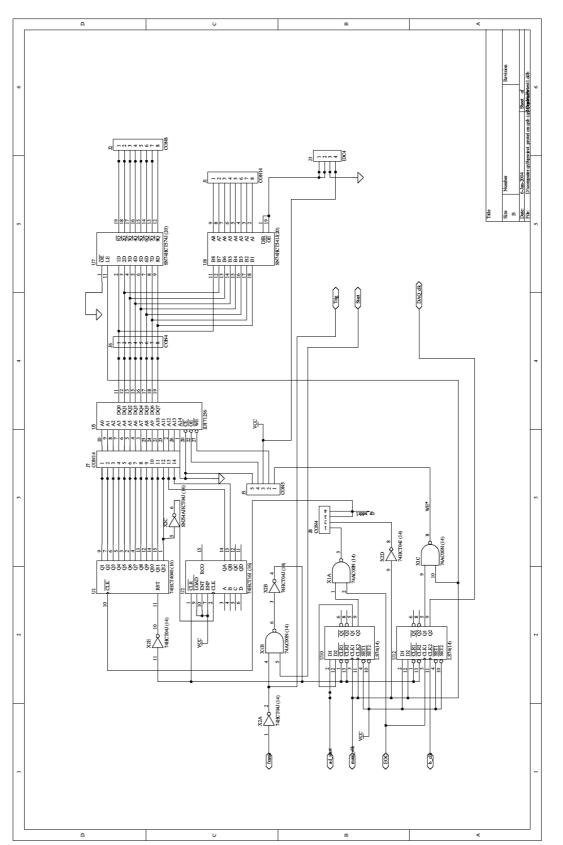

| Fig. 6.14. Schematic of the digital circuit on the PCB13'                                                                                                                                   | 7 |

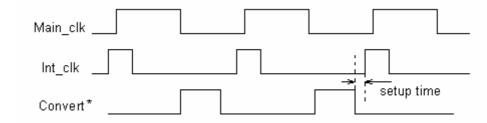

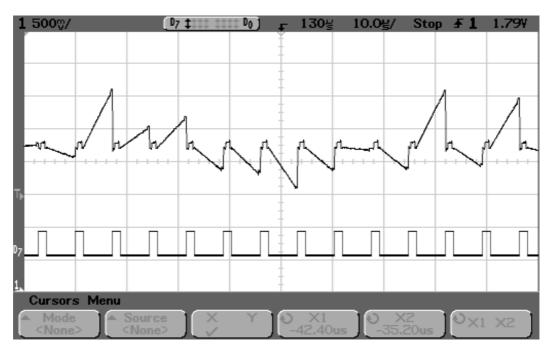

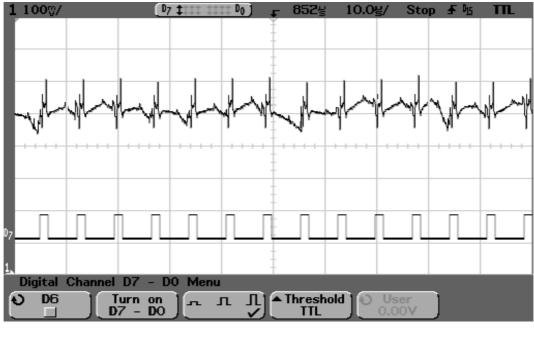

| Fig. 6.15. Relationship of <i>main_clk</i> , <i>int_clk</i> and <i>Convert*13</i>                                                                                                           | 8 |

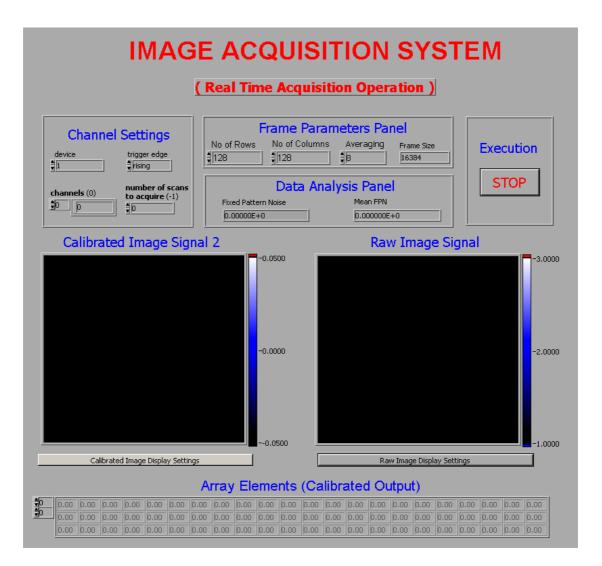

| Fig. 6.16. User interface of image acquisition13                                                                                                                                            | 9 |

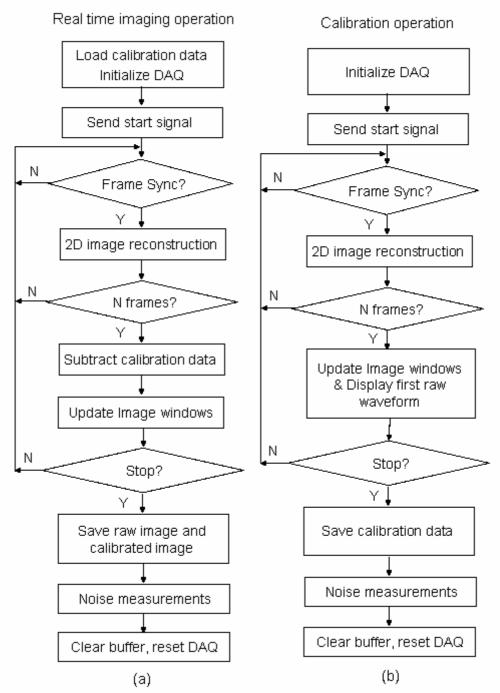

| Fig. 6.17. Flow chart of the Image Acquisition LabVIEW programs: (a) Real time imaging operation; (b) Calibration operation144                                                              | 0 |

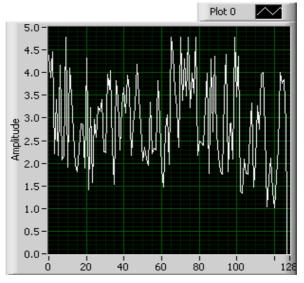

| Fig.6.18. Output waveform chart of the first row of FPA without FPN correction14                                                                                                            | 2 |

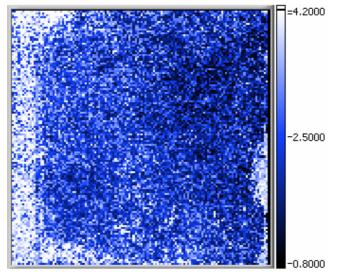

| Fig. 6.19. Measured 2-D Intensity graph of the FPA without coarse FPN correction                                                                                                            |   |

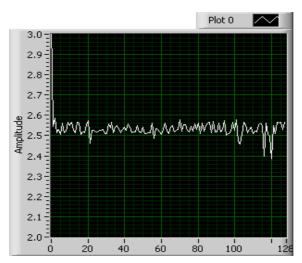

| Fig. 6.20. The residual FPN readings of the first raw of FPA14                                                                                                                              | 3 |

| <ul><li>Fig. 6.21. The residual fixed pattern of the FPA after on-chip correction:</li><li>(a) Intensity scale is same as that in Fig .6.19 and (b) Intensity scale is reduced144</li></ul> | 3 |

| Fig. | 6.22. | The histogram of the residual FPN                                                                 | 144 |

|------|-------|---------------------------------------------------------------------------------------------------|-----|

| Fig. | 6.23. | Residual error of FPN correction when tested with a resistor array                                | 145 |

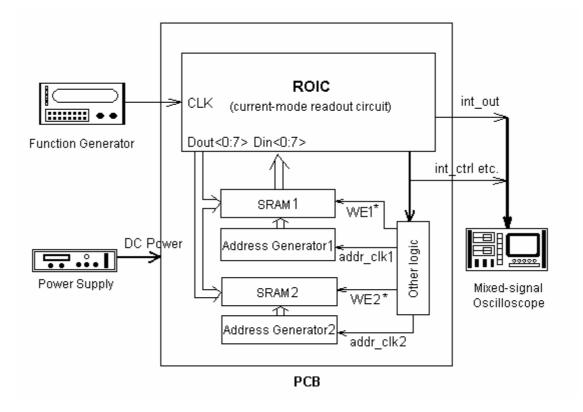

| Fig. | 6.24. | Test set-up for current-mode FPN correction circuit on ROIC                                       | 148 |

| Fig. | 6.25. | Measured residual error after coarse FPN correction                                               | 149 |

| Fig. | 6.26. | Output waveform of the on-chip current integrator. (a) before and (b) after coarse FPN correction | 150 |

# List of Tables

|            | Electrical equivalents of the thermal behaviour quantities of microbolometer | 42 |

|------------|------------------------------------------------------------------------------|----|

|            | Parameters of the two bolometers used in the experiments and simulation      | 47 |

| Table 3.3. | Parameters of the microbolometer used in the simulation                      | 50 |

| Table 4.1. | The circuit parameters after optimization                                    | 69 |

| Table 4.2. | Post-layout Simulated pre-amplifier parameters                               | 83 |

|            | Current-mode self-heating cancellation circuit parameters in simulation      | 93 |

| Table 5.2. | Truth table of the 2-bit binary-to-thermometer decoder1                      | 10 |

|            | Simulation results of the on-chip current-mode FPN correction circuit1       | 20 |

| List of | Symbols |

|---------|---------|

|---------|---------|

| Symbol           | Description                                                  | Unit                 | Page No.                     |

|------------------|--------------------------------------------------------------|----------------------|------------------------------|

| α                | Temperature coefficient of resistance                        | 1/K                  | 6,43,50,53,60<br>~ 63, 91,92 |

| ε                | Absorptivity coefficient                                     |                      | 41                           |

| $\phi_{e}$       | Spectral incident infrared power                             | W                    | 5                            |

| φ                | Input radiation power                                        | W                    | 41                           |

| η                | Emissivity of the detector material                          |                      | 6                            |

| $\mu_{p}$        | Hole mobility                                                | cm <sup>2</sup> /V.s | 92                           |

| τ                | Thermal time constant                                        | S                    | 41,46~48,58                  |

| ω                | Angular modulation frequency of incident radiation           | rad/s                | 5, 6                         |

| Δf               | Noise equivalent bandwidth                                   | Hz                   | 6                            |

| $\Delta T$       | Temperature difference of the detector                       | K                    | 48,50~53, 55,<br>60 ~ 63, 91 |

| $\Delta T_b$     | Temperature difference between the target and the background | K                    | 5                            |

| $\mathfrak{R}_v$ | Responsivity                                                 | V/W                  | 5,6                          |

| A                | Sensitive area of the detector                               | $cm^2$               | 6                            |

| В                | Bandwidth                                                    | Hz                   | 54                           |

| C <sub>ox</sub>  | Gate oxide capacitance per unit area                         | f/ cm <sup>2</sup>   | 92                           |

| $C_T$            | Electrical equivalent of thermal capacitance                 | f                    | 42,44,46,50                  |

| $D^{*}$          | Specific Detectivity                                         | cm√Hz/W              | 6                            |

| G                | Thermal conductance                                          | W/K                  | 6,42,41,46,48                |

| Н                | Thermal capacitance                                          | J/K                  | 6,41,42,48,<br>61,62,91,92   |

| Symbol              | Description                                                      | Unit | Page No.              |

|---------------------|------------------------------------------------------------------|------|-----------------------|

| $I_S$               | Saturation current of the bipolar device                         | А    | 105                   |

| k                   | Boltzmann's constant                                             | J/K  | 54,106                |

| P <sub>bias</sub>   | Bias heating power                                               | W    | 41~45,48,60~<br>62,91 |

| $P_{IR}$            | Infrared power absorbed by detector                              | W    | 41~45,52,55,<br>60    |

| q                   | Electron charge                                                  | С    | 106                   |

| $R_T$               | Electrical equivalent of Thermal resistance                      | Ω    | 42,44,46,50           |

| Т                   | Temperature                                                      | K    | 41,42,54,105,<br>106  |

| $V_{G0}$            | Bandgap voltage of the silicon at 0 °K                           | V    | 105,106               |

| $V_{GS}$ , $V_{DS}$ | Gate-source and drain-source voltage of transistor, respectively | V    | 92,98                 |

| $V_T$               | Thermal voltage                                                  | V    | 105,106               |

| $V_{TH}$            | Threshold voltage                                                | V    | 92                    |

| W, L                | Width and length of the transistor, respectively                 | μm   | 67,92                 |

| Abbreviation | Expansion                                  | Page No.                                                                                                                    |

|--------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| ADC, or A/D  | Analog to digital converter                | 31~33,72~74,77,85,87,<br>96,97,120,133,136,145<br>,146,148                                                                  |

| AMS          | AustriaMicroSystems                        | 72,92                                                                                                                       |

| CCBDI        | Constant current buffered direct injection | 30                                                                                                                          |

| CMOS         | Complementary Metal-Oxide Semiconductor    | 7,8,18,28,63,64,92,<br>105,122,123,151, 153                                                                                 |

| CTIA         | Capacitive transimpedance amplifier        | 28,29                                                                                                                       |

| DAC, or D/A  | Digital to analog converter                | 32,34,72,73,85~88,102<br>~105,107,113~117,119<br>,121,133, 148,149                                                          |

| DAQ          | Data acquisition                           | 132~136,141,146                                                                                                             |

| DI           | Direct injection                           | 27~30                                                                                                                       |

| DNL          | Differential Nonlinearity                  | 102,116,117                                                                                                                 |

| FPA          | Focal plane array                          | 3,9,11,12,14,17~21,<br>23,25,30~35,48,56,57,<br>70~73,76~79,85~<br>88,95~99,118,119,<br>122~125,132~136,<br>140~147,151~155 |

| FPN          | Fixed pattern noise                        | 31,32,36,57,66,72,79,<br>83~88,96~99,114,<br>117~122,133~136,<br>139,141~155                                                |

| GBW          | Gain bandwidth                             | 79,80,83                                                                                                                    |

| IC           | Integrated circuit                         | 14,35,58,63,70,88                                                                                                           |

| IME          | Institute of Microelectronics              | 132                                                                                                                         |

| INL          | Integral Nonlinearity                      | 102,117                                                                                                                     |

| IR           | Infrared                                   | 1~5,9,12,14~20,28,31<br>~39,48~57,60~63,77,<br>85,88,91,93~96,118,<br>119,122,129~134,140,<br>146,147,152~155               |

| JFET         | Junction field effect transistor           | 25                                                                                                                          |

# List of Abbreviations

| Abbreviation | Expansion                                           | Page No.                                                                                              |

|--------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| LSB          | Least significant bit                               | 104,107~109,113,119,<br>121,145,146,149,151,<br>154                                                   |

| NEP          | Noise Equivalent Power                              | 5,7                                                                                                   |

| NETD         | Noise Equivalent Temperature Difference             | 6,17,19,20,85                                                                                         |

| NMOS         | N-channel Metal-Oxide Semiconductor transistor      | 64,67,71,95,107                                                                                       |

| РСВ          | Printed circuit board                               | 129,132,134~138,147                                                                                   |

| PMOS         | P-channel Metal-Oxide Semiconductor transistor      | 22,64,80,90,92,105,<br>109~113,121                                                                    |

| PTAT         | Proportional to absolute temperature                | 106                                                                                                   |

| RMS          | Root mean square                                    | 5                                                                                                     |

| ROIC         | Readout integrated circuits                         | 9,12,14,19~22,31<br>~34,39,70,71,87,95~<br>98,122~125,129,<br>132~136,140~142,<br>144,146~148,151~155 |

| SEM          | Scanning electron microscope                        | 125                                                                                                   |

| SNR, or S/N  | Signal-to-noise ratio                               | 5,6,54,124,132,147                                                                                    |

| SPICE        | Simulation program with integrated circuit emphasis | 12,42,44~49,56,62,<br>92,153                                                                          |

| SRAM         | Static Random Access Memory                         | 135,138,141,147,148                                                                                   |

| TCR          | Temperature coefficient of resistance               | 6,7,17,43                                                                                             |

| VCVS         | Voltage control voltage source                      | 63                                                                                                    |

| VLSI         | Very large scale integration                        | 62,63                                                                                                 |

## Chapter 1. Introduction

#### 1.1. Infrared detector

Infrared (IR), or "beyond the red", is the electromagnetic radiation similar to visible light but with longer wavelengths. The infrared portion of the electromagnetic spectrum lies adjacent to the visible[1]. Its wavelength range extents from  $0.7\mu m$ , the red end of the visible light, to about 1000 $\mu m$ . While visible light is only emitted by objects at a very high temperature, infrared energy is radiated by all objects when the temperature of the object surface is above absolute zero. For example, at room temperature, the peak of the radiant emittance is about 10  $\mu m$  which lies in the infrared region[2][3]. Hotter the object, more energy is radiated.

Although infrared radiation is invisible to the naked human eyes, it can be "seen" by infrared detectors. It gives us the possibility of measuring the self-emitted radiant energy from objects. When the infrared radiation is effectively detected, we can see all objects regardless of the darkness of the environment.

An infrared detector is basically a radiation transducer. It senses the incident infrared radiation with the changes in some of its electrical parameters. The infrared detectors can be roughly classified into two groups: photon and thermal detectors. The former absorbs the incident photons, which interact with the charge carriers in the detector and generates a photo-current or voltage, which produce the electrical output directly proportional to the number of input photons. The thermal detector responds to the

infrared power with a change in its temperature, which can be converted to either a voltage or current signal through a temperature sensing device.

The photon detector needs to be cooled down with a cryogenic system for efficient operation. However, most of thermal detectors are "uncooled", which means that they can operate at room temperature. This enables uncooled detectors to have some advantages over the photon ones, such as affordability and reliability. These attractive characteristics encourage the development of the uncooled IR for a wide range of applications.

Since William Herschel first discovered the infrared energy beyond the visible region, the use of this portion of electromagnetic spectrum has aroused great interest among scientists. Modern infrared imaging system are lighter in weight and easier to use than those used decades ago[4][5]. They can sense the infrared radiant energy and generate useful electrical signal that is proportional to the temperature of the object surface. Therefore, clear thermal images can be produced for visual inspection. Nowadays, infrared technology is being widely adopted in many military, civilian, and scientific applications[6~8].

#### 1.2. Microbolometer IR detector and focal plane array

There have been several types of uncooled IR detectors reported to date. Among them, microbolometer IR detector has been widely adopted in commercial products owing to its low cost and compatible process with silicon integrated circuits.

Microbolometer is a temperature sensor whose resistance is dependent on its temperature. A microbolometer based infrared detector consists of a resistive elements built on a thermally isolated structure, which is also act as infrared absorption layer. The incident infrared radiation is absorbed by the detector, causing its temperature to rise. The temperature change of the detector is sensed by the change in resistance. With the readout circuit, the resistance change is converted to a voltage or current signal as the output of the detector.

When used in the thermal imaging applications, microbolometer detectors are commonly arranged in a two-dimensional detector array, which is called the focal plane array (FPA). A FPA is a detector array placed at the focal plane of an optical system such as a camera, spectrometer or telescope. This detector array is combined with readout circuits or multiplexer which allows the electronic access to each detector cell in the array. Each detector in FPA represents a pixel of the final thermal image.

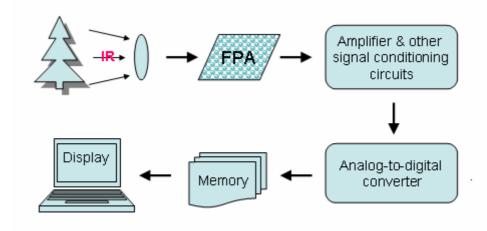

The operation of a microbolometer imaging system starts from the infrared incident absorption by the microbolometer FPA. Each detector cell senses the infrared energy radiated on it and changes its resistance accordingly. The readout electronics of the IR FPA sequentially addresses the detector cells (pixels) and convert the resistance change to an electrical signal, either in a voltage or a current. The signal from detectors is processed by the pre-amplifier and then analog-to-digital converter. After some imaging process programs such as filtering and enhancement, the digitized thermal image information can be obtained and stored in the video memory. Thus, a complete thermal image with the proper format and frame rate for TV display can be monitored. The block diagram of a microbolometer IR imaging system is illustrated in the Fig.1.1. An example of a thermal image taken by the microbolometer based infrared camera is shown in the Fig.1.2, where a bright spot corresponds to the high temperature and a dark spot corresponds to the low temperature.

Fig.1.1. Block diagram of a bolometer infrared detection system.

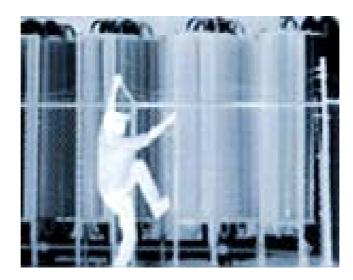

Fig.1.2. Thermal image taken by the uncooled infrared camera LTC550[9].

### 1.3. Detector characterization

In the study of thermal detector based systems, the following parameters are commonly used for characterizing the detectors.

• Responsivity:

The basic function of a detector is to convert input IR radiant power to an electrical output signal. The responsivity, as a measure of the conversion efficiency, is defined as the output signal per unit input IR power.

$$\Re_{v} = \frac{V_{s}}{\phi_{e}} \tag{1-1}$$

Where  $V_s$  is the detector output voltage and  $\phi_e$  is the spectral incident power, which can normally be decomposed into a set of sinusoidal components as

$$\phi_e = \phi_{e,0} e^{j\omega t} \tag{1-2}$$

Ideally, the responsivity of the microbolometer detector is broad and flat with respect to the wavelength of input radiation.

• Noise Equivalent Power (NEP):

NEP is defined as the root mean square (RMS) incident radiant power required to produce an output signal  $V_s$  that is equal to the detector noise level  $V_n$ .

$$NEP = \frac{\phi_e}{V_s / V_n}.$$

(1-3)

In other words, the NEP determines the incident power for the detector to produce a signal-to-noise ratio (SNR) of unity. It is a measure of the ultimate sensitivity of a detector.

• Specific Detectivity (D<sup>\*</sup>):

The specific detectivity,  $D^*$ , which is the sensitivity normalized to the area of  $1 \text{ cm}^2$  and the noise equivalent bandwidth of 1Hz, is defined as

$$D^* = \frac{\sqrt{A\Delta f}}{NEP},\tag{1-4}$$

where A is the sensitive area of the detector and  $\Delta f$  is the noise equivalent bandwidth.

• Noise Equivalent Temperature Difference (NETD):

NETD is defined as the smallest temperature difference between target and the background, which produces a signal to noise ratio (SNR) of unity.

$$NETD = \frac{\Delta T_b}{V_s / V_n} \tag{1-5}$$

$\Delta T_b$  is the temperature difference between the target and the background.

When a bridge readout circuit is used, the voltage responsivity of microbolometer can be expressed as

$$\Re_{v} = \frac{\alpha \eta \cdot V_{bias}}{4 \left( G^{2} + \omega^{2} H^{2} \right)^{1/2}}$$

(1-6)

where  $\alpha$  is the temperature coefficient of resistance (TCR),  $\eta$  is the emissivity of the detector material, G is the thermal conductance, H is the thermal capacitance of the microbolometer,  $\omega$  is angular frequency of incident radiation. The TCR is defined as

$$\alpha = \frac{1}{R_d} \frac{dR_d}{dT_d} \tag{1-7}$$

where  $R_d$  and  $T_d$  are the resistance and temperature of the detector, respectively.

It can be seen from Eq.(1-6) that, to achieve high responsivity, a microbolometer with high TCR, high absorption coefficient and low thermal conductance is desirable. This is also true for obtaining low noise equivalent power (NEP) and high detectivity (D\*).

Moreover, the responsivity of the bolometer has a low-pass feature. Although low thermal conductance can increase the responsivity, it reduces the bandwidth of the detector, and hence slows down the response of the microbolometer. Thus, compromise needs to be made in the detector design.

#### 1.4. Structure of micromachined microbolometer

According to the Eq.(1-6) and Eq.(1-7), the thermal isolation between the microbolometer and the substrate is one of the important factors that contributes to high performance of the detector. With the development of silicon micromachining technology, structure with good thermal isolation can be easily realized. The compatibility of silicon micromachining technology with the standard CMOS process offers the possibility of combining the conventional CMOS readout integrated circuits with the microbolometer focal plane array.

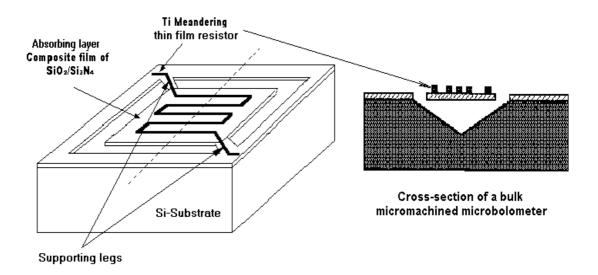

There are two main types of micromachining (bulk and surface) commonly used for fabricating microbolometers. The structure of a microbolometer made by bulk micromachining is schematically shown in Fig. 1.3. An infrared absorber layer is formed by the dielectric layers, normally the composite of silicon oxide and silicon nitride. A meandering thin film resistor material is then deposited on the dielectric layer. The silicon under the dielectric membrane is etched away later in the process to form the gap between the microbolometer and substrate in order to reduce the thermal mass and the thermal conductance. The resulting micromembrane is suspended above the silicon substrate and supported by the two legs connecting the detector to the readout circuits. The absorbed heat can only be dissipated through these two legs to the substrate that acts as a heat-sink.

Fig. 1.3. Structure of a bulk micromachined bolometer.

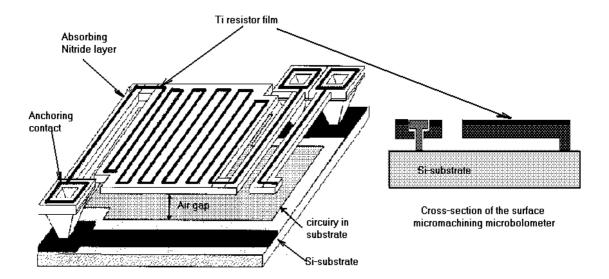

In surface micromachining technology, a sacrificial silicon dioxide layer is deposited at the early stage of the processing. Then the microbolometer thin film is fabricated on the top of the sacrificial layer. The infrared absorbing layer, similar to that of the bulk micromachined structure, is made of  $Si_3N_4$  during the CMOS process. Finally, the oxide sacrificial layer is removed with either wet or dry etching techniques. The free-standing microbolometer structure is then formed, as shown in Fig.1.4. After the sacrificial layer is removed, an air gap of 0.5 µm separates the micromembrane from the silicon substrate. The absorbed heat is dissipated to the substrate through the anchoring contacts.

Fig.1.4. Microstructure of the surface micomachined microbolometer.

#### 1.5. Readout circuits and self-heating effect

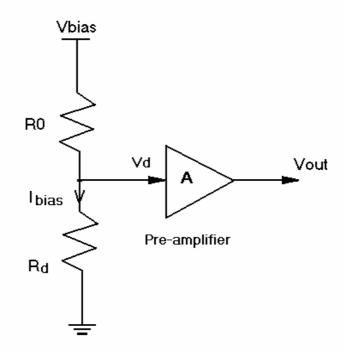

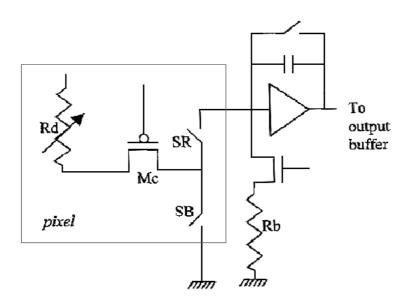

Besides the microbolometer detector itself, the readout integrated circuit (ROIC) is the next crucial part of the IR imaging system. It is an interface between the IR detector array and the thermal image display, where the signal and imaging process are carried out. The basic configuration of the readout circuit for microbolometer FPA is shown in Fig.1.5, where  $R_d$  is the microbolometer which is biased with a constant voltage  $V_{bias}$  through a load resistor,  $R_0$ . The IR radiation is sensed by  $R_d$ and a small voltage change  $\Delta V_d$  is produced, and subsequently amplified by the preamplifier. The main shortcoming of this configuration is the large pedestal voltage  $V_d$  is also amplified such that it overrides the IR signal.

Fig.1.5. Basic readout circuit of the microbolometer.

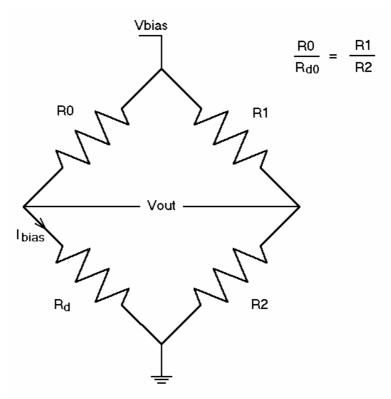

Fig.1.6. Wheatstone bridge readout circuit of the microbolometer.

Most practical readout circuits employ the Wheatstone bridge structure[10], as shown in Fig.1.6. When the ratio of the resistor  $R_0$  over the room temperature resistance of the microbolometer,  $R_{d0}$ , is equal to that of resistor  $R_1$  over  $R_2$ , the bridge is balanced. Such a bridge structure not only removes the pedestal bias voltage, but also rejects the fluctuation and other noise introduced by the power supply.

However, the Wheatstone readout circuit also has its shortcomings, such as selfheating effect. During the readout, in order to monitor the amount of the resistance change, the microbolometer element must be electrically biased. When there is a current flowing through the bolometer, it generates the Joule heating. As a result, the microbolometer is not only heated by the infrared radiant energy, but also the bias current flowing through. This heating effect due to the bias current is referred to as the self-heating of the microbolometer. Because of the micromachined structure, thermal conductance of the bolometer is greatly reduced. Hence the heat generated by the self-heating effect cannot be quickly dissipated through the thermal conduction to the substrate. This makes the temperature change of the microbolometer due to the selfheating effect much greater than that due to the input infrared radiation. Thus, the self-heating effect must be compensated in the readout circuits.

#### 1.6. Scope and organization of thesis

Several microbolometer based IR focal plane detector arrays have been reported. However, very little information is available on their readout electronics, especially on self-heating cancellation. An in-house microbolometer focal plane array was developed by previous students. However, its performance suffers from the problems in its ROIC, in particular, the self-heating effect, as it was not dealt with in the ROIC. The scope of this project is to develop a simple and yet effective method or circuit for the self-heating cancellation and employ it in the ROIC for the microbolometer focal plane array made in house. The overall objective was to develop a prototype ROIC for the above mentioned microbolometer focal plane array that can compensate both self-heating and fixed pattern noise.

The organization of the thesis is as follows:

Chapter 2 presents the literature review of the infrared imaging system and readout electronics for microbolometer focal plane array.

In chapter 3, a SPICE Electro-thermal model of the bolometer is introduced. The effectiveness of this model is demonstrated by the comparison between the simulation and the experimental results. The analysis of the thermal behaviours of the microbolometer is studied based on the proposed SPICE model.

In chapter 4, the design of the voltage-mode readout integrated circuits for microbolometer FPA is presented. A new self-heating cancellation scheme is proposed and the detailed description of the circuit operation is given. The proposed self-heating cancellation scheme is employed in a voltage-mode ROIC, in which the fixed pattern noise cancellation circuit is also included. Finally, the simulation results are presented.

Chapter 5 focuses on the design of the current-mode readout electronics for the microbolometer IR focal plane array readout circuit. The self-heating cancellation

scheme described in chapter 4 is extended to the current-mode realization. The design and simulation results are presented.

Chapter 6 deals with test and evaluation of the voltage- and current-mode readout circuits. Finally, chapter 7 gives the conclusions of this research and suggestions for the future work.

## **Chapter 2.** Literature Review

Over a century after the infrared is discovered, the first IR imaging system circa-1930 Evaporagraph [11] was produced. It was a rather insensitive non-scanning system which could not satisfied most tasks. Since then, rapid advances have been made in thermal imaging systems. Today, the sophisticated thermal imaging systems are used in many commercial, industrial and military applications [12][13]. The ever-expanding field of applications of IR imaging systems is a primary motivation for the worldwide efforts in the research and development of infrared technology.

Infrared detectors and readout integrated circuits (ROIC) are the two important aspects of thermal imaging systems. In late 1970s, the first generation IR focal plane arrays incorporating the IC technology were developed [14][15]. The readout integrated circuits for these IR FPA were simple multiplexers and consist of little, if any, signal conditioning circuits. Due to the significant system performance enhancements allowed by the integrated circuits, ROICs for IR imaging systems become more and more complex. The available on-ROIC or on-FPA functionality has increased dramatically. The advance in modern microelectronic technologies has provided the potential to realize cost-effective and high performance IR imaging systems.

#### 2.1. Infrared detectors for thermal imaging

IR detectors are generally classified into two categories, namely, photon and thermal IR detectors. Photon detectors absorb the IR radiation by interaction with electrons within the material. When an electron gains enough energy from the incident IR radiation (or photons), it overcomes the energy gap and becomes a free electron that alters the electrical parameters of the material, such as conductivity. Thus, the responsivity of the photon detector depends on the wavelength of the IR radiation, as the incident photon energy is a function of the wavelength. For a detector material with a fixed energy gap, when the wavelength of the incident IR radiation is beyond certain value, the photon energy will not be high enough to excite the electrons to over the energy band gap. The detector will fail to response. This is often referred to as "long wavelength limit" of the IR photon detectors. The major advantages of the photon detector are its good sensitivity and fast response[16][17]. However, in order to achieve this, the cryogenic cooling operation is required, which makes the semiconductor photon detectors bulky, heavy and inconvenient to use, as well as costly. Thus the applications of the photon IR detectors are mainly in the highperformance thermal imaging system or cameras [18~23].

Thermal IR detectors, on the other hand, absorb the IR radiant power resulting in the change of its temperature. This temperature change is converted to an electrical output through a temperature sensing device. Thermal effects are generally wavelength independent. The spectral band of thermal detectors is normally determined by optics and windows. Thus, a broad or flat spectral response can be expected. Since the room temperature object emits the highest radiant power in 8-14 $\mu$ m range, thermal detectors are generally used as long wavelength IR detector.

In comparison with photon detectors, thermal detectors are characterized by modest sensitivity and slow response. However, the thermal detectors are typically operated at the room temperature, making them low-cost and convenient to use. The thermal IR detectors are often referred to as uncooled IR detectors. Uncooled IR detector technology has advanced rapidly in the past decade and results dramatic improvement in the performance of uncooled thermal imaging systems [24][25]. The crucial technology to fabricate uncooled detectors is the micromachining technology. It enables the realization of miniaturized thermal isolated structure and increases the detector sensitivity and response speed[26~29]. The most common uncooled thermal detectors are microbolometer[30~33] and ferroelectric IR detectors[34~39].

As the microbolometer IR detector will be used in this study, the remaining of this chapter briefly reviews microbolometer IR detectors and its readout electronics.

## 2.2. Microbolometer

Microbolometer detector is one of the promising thermal IR detectors. When exposed to IR energy, the microbolometer detector heats up and its electrical resistance changes in response to the absorbed IR energy. The resistance change can be measured by applying an electrical bias to the detector and readout the changes in voltage or current.

#### 2.2.1. Microbolometer IR detectors

One of the successful commercialized microbolometer materials is vanadium oxide[40~42], VOx, which was developed originally at Honeywell. It usually has the

high temperature coefficient of resistance (TCR) of above - 2%/K[43]. The measured thermal capacitance of VO<sub>2</sub> detectors is about  $10^{-9}$  J/K corresponding to a thermal time constant of 10 ms. The responsivity of 250 kV/W has been observed with a 50µm-square pixel (detector) in response to 300K blackbody radiation[44][45]. One of the drawbacks of VOx microbolometer is its non-crystalline structure which results in large 1/f noises. Low NETD of 30 mK and D\* of about  $10^8$  cmHz<sup>1/2</sup>/W have been achieved for micromachined VOx microbolometers[46][47].

Metal film microbolometers, used in this study, have a positive TCR of about 0.3%/K. Such devices normally have the detectivities in the order of  $1 \times 10^8$  cmHz<sup>1/2</sup>/W under room temperature operation [14]. They have comparatively low temperature coefficient, but low noise and high lone-term stability in comparison with vanadium oxide detectors[16]. Titanium is one of the metal materials used for microbolometers, and reported to have the NETD of around 0.07K with f/1 optics and the TCR of about 0.25%/K to 0.35%/K [48][49]. Double sacrificial layer surface micromachining technology used to fabricate Ti microbolometer further improves the fill-factor of the FPA to around 92%[50][51]. The thermal isolation effect can also be enhanced by the technique of supporting the absorbent membrane with a lower layer, which is anchored to the substrate. The detectivity of  $2.43 \times 10^9$  cmHz<sup>1/2</sup>/W was reported with Ti microbolometer [50]. In spite of its low TCR, titanium has been successfully employed in commercial IR FPAs.

Amorphous silicon (a-Si) is another high TCR microbolometer material. With resistivity of up to  $10^5 \Omega$ cm, the TCR of a-Si:N can be as high as 6%/K. However, high noise is observed. While at low resistivity ( $10^3 \Omega$ cm), TCR reduces to around

2.5%/K[52]. High performance of the amorphous silicon microbolometer have been achieved in many investigations that show a-Si is becoming an advantageous choice for uncooled IR detector material[53~57].

YBaCuO is a well kown material for superconducting bolometers[58][59]. However, its possible operation at room temperature has been widely studied recently[60][61]. YBaCuO bolometers also demonstrate a low 1/f noise and low power-normalized corner frequency,  $f_c/I^2R$ , where  $f_c$  corresponds to the point of the frequency spectrum at which the voltage of the current noise equals the voltage of the Johnson noise[60][62]. The detectivity of 1×10<sup>8</sup> cmHz<sup>1/2</sup>/W was obtained with a thermal time constant of 5 ms.

There are several other bolometer materials that have been studied, such as the polycrystalline Si-Ge[63~65], P-N junction diode[66~68] and single crystal silicon N-well in the standard CMOS process[69][70]. The reported detectivities for these materials are  $2.3 \times 10^8$  cmHz<sup>1/2</sup>/W[63],  $1.2 \times 10^{10}$  cmHz<sup>1/2</sup>/W[68] and  $1.2 \times 10^9$  cmHz<sup>1/2</sup>/W[69] respectively.

#### 2.2.2. Microbolometer focal plane array

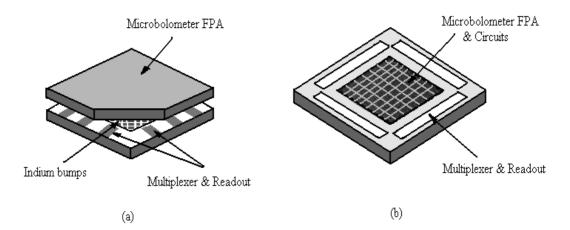

There are two main architectures used for developing IR focal plane arrays, namely, the hybrid and monolithic, as shown in the Fig.2.1. Hybrid microbolometer FPAs compound the detector arrays with the silicon readout chip via some chip-to-chip bonding techniques, such as indium bumps or loopholes, while in monolithic structure, detector arrays are fabricated on-chip with the readout circuits.

Fig. 2.1. Flip-chip-hybrid (a) and monolithic (b) structures of microbolometer FPA[71]

In the hybrid design, the microbolometer detector FPA and readout circuits are fabricated on different substrates, and bonded together through indium bump or loophole interconnection. The indium columns form both the electrical connection between detector and signal processor, and a thermal conduction path to the silicon. The thermal conduction must be minimized to maximize the temperature differential across the detector and achieve high sensitivity[72][73]. Since the detector array is on a separate chip from the one for the circuits, it can be optimized independently of the readout circuit. A high fill factor near 100% can be achieved[17]. Hybrid structure is used primarily when the processes of detector and ROIC are not compatible or there are some cost issues if fabricated both together. Hybrid uncooled microbolometer FPAs with NETD in the range of 300mK have been reported[74][75].

Modern two-dimenstional microbolometer FPAs employed in IR imaging system usually have large number of pixels so that individual lead-outs from each pixel are impractical. Thus, a monolithic structure with the control circuit fabricated in the underlying silicon has been developed. In the monolithic design, the detectors are fabricated on a thermally isolation structure on the same silicon substrate where the ROIC is. The monolithic thermal isolation structure typically provides a lower thermal conduction than that of the indium columns in the hybrid FPAs. Monolithic FPAs with the readout circuits on the same chip is the preferred choice for microbolometer infrared FPAs as the direct on-chip electrical connection results in the simplified package, improved performance and high reliability[76~78].

One of early studies of the fully monolithic micromachined bolometer FPA, with simple on-chip readout circuits and preamplifier, was reported in 1993[44]. No signal processing circuit was integrated on this chip. However, because of the improvement of the filling factor and the reliability in the monolithic IR FPA, the monolithic FPA technique has been widely employed and studied in the last decade [79~81]. IR imaging FPAs with various dimensions from  $128 \times 128$  to  $640 \times 480$  pixels have been reported[82~91]. The NETD for most of these FPAs have attained around 100mK, with the best performance being less than 20 mK[84].

### 2.3. Readout electronics for microbolometer FPAs

The basic functions of the readout electronics for microbolometer FPAs typically include the bias for the microbolometer, front-end amplification and signal conditioning, pixel addressing, digitization, and error correction circuits. The block diagram of a ROIC operated in serial pixel addressing mode is shown in Fig.2.2. The pixels in the array are read out serially through the pixel addressing circuits that consists of the column switches, x (column) and y (row) shifter registers. Clock generator generates all the control and clock signal needed in multiplexer circuits and signal processing circuits. The signal is amplified and further processed by signal

conditioning circuits. The output from the signal conditioning circuit is digitized and sent to the off-chip circuitry for further processing and producing the standard video display.

Fig. 2.2. Block diagram of the ROIC for an  $M \times N$ -pixel microbolometer FPA.

#### 2.3.1. Front-end signal conditioning circuits

The microbolometer is in essence a temperature sensing resistor whose resistance changes with its temperature. The change of the resistance can be read out as a voltage or a current. Thus the front-end signal conditioning circuit can be classified as voltage- or current-mode. Since the signal from the bolometer is normally very weak, the front-end signal conditioning circuit is critical to the performance of the ROIC.

#### 2.3.1.1. Voltage-mode front-end readout circuits

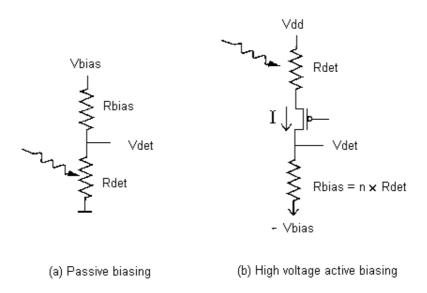

The simplest voltage-mode readout method is to connect the microbolometer to a bias resistor serially, as shown in Fig. 2.3(a). The problem in this solution is that the bias resistor damps the signal. To avoid this, an active bias scheme with high bias voltage was proposed in [92], as given in Fig. 2.3(b), where the bolometer is connected to the source of a PMOS transistor and the output signal is taken from its drain with the bias resistor as a load. Large PMOS transistor should be used to avoid the significant 1/f noise.

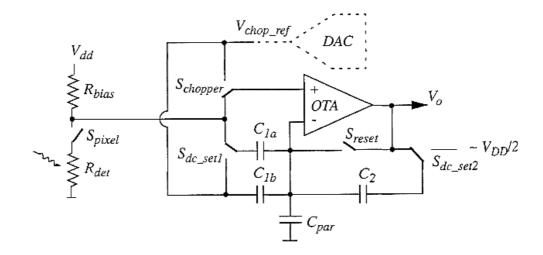

To overcome the problem of high 1/f noise from the active device, a modified the passive biasing circuit with a non-overlapping chopper amplifier was reported in [93], which is shown in the Fig.2.4. The chopping amplifier is worked as modulation circuit, which modulate the signal to a higher frequency band so that the DC and low frequency measurements can be avoided. Hence, the matching requirement between bolometer resistances is eliminated and greatly reduces the 1/f noise. The offset caused by the mismatch among the pixels (also referred to as the fixed pattern noise) can be pre-corrected by providing a suitable chopper reference to each pixel with a digital-to-analog converter, as indicated in the dash line.

Fig. 2.3. Two simplest voltage-mode readout circuits

Fig. 2.4. Chopper-amplifier voltage-mode circuit

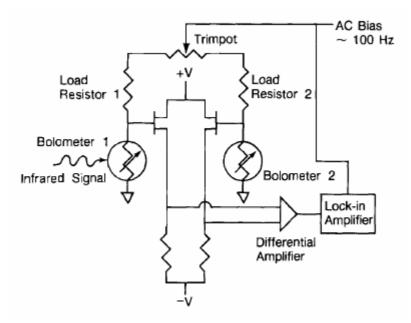

The Wheatstone bridge structure is the most commonly used voltage-mode readout scheme for microbolometer FPAs[94][95]. The advantage of this readout circuit is that the common-mode signal can be removed by a differential amplifier. Either a constant or pulse bias can be employed.

Fig.2.5 shows a Wheatstone bridge circuit with an AC bias voltage[96][97]. The AC bias can be either a sinusoidal or a square wave voltage with zero DC level. The frequency of the bias voltage is much higher than the thermal rolling-off frequency of the bolometer,  $1/2\tau$ , to provide a modulated signal for amplification. A lock-in amplifier provides the phase sensitive detection after the output of the bridge circuit is amplified, producing a DC output voltage proportional to the resistance difference between bolometer 1 and 2. If the two bolometers in the bridge are perfectly matched, the 1/f noise from the amplifiers and source-followers are eliminated by the phase sensitive detection.

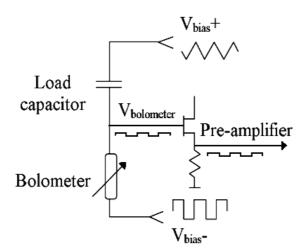

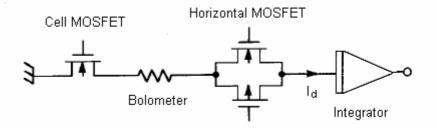

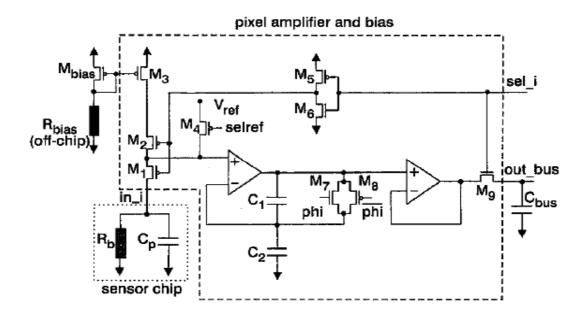

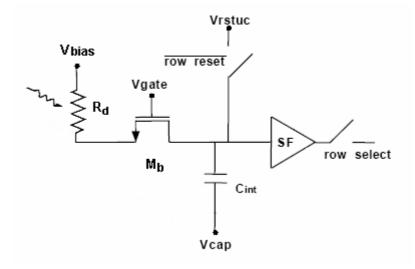

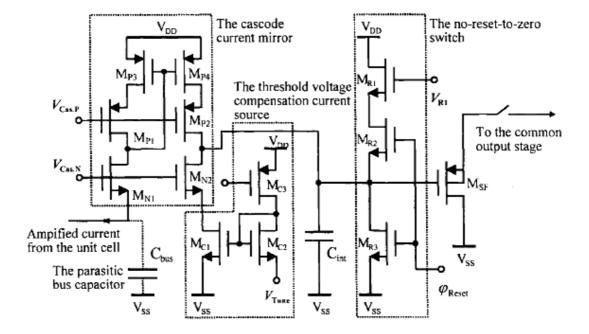

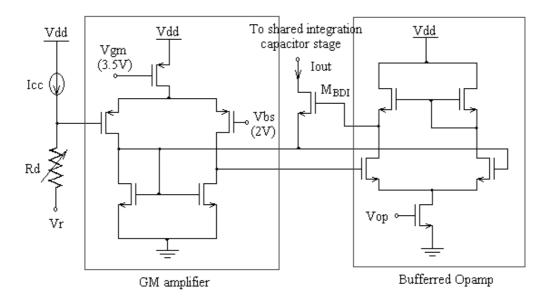

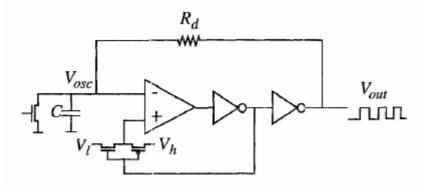

Fig. 2.5. AC-bias bridge readout circuit for bolometer