# DESIGN OF A FULLY DIGITAL MULTI-LEVEL DECISION FEEDBACK EQUALIZATION CHIP

XIE JIANG

(B.Eng(Hons.), BUPT)

### A THESIS SUBMITTED

### FOR THE DEGREE OF MASTER OF ENGINEERING

### DEPARTMENT OF ELECTRICAL & COMPUTER ENGINEERING

NATIONAL UNIVERSITY OF SINGAPORE

2004

## ACKNOWLEDGMENT

I would like to express my deepest appreciation to Prof. Xu Yong Ping for providing the continual guidance and support to me, which were essential in completing this project. I would also like to thank Chan Suet Yin for her contribution to the design of the Feed-Forward Equalizer. My gratitude also reaches out to Bi Lei for his contribution on the architecture investigation before this project. Finally, I appreciate the sponsor of this project – National University of Singapore -- for providing all the necessary funding and the EDA tools.

# **TABLE OF CONTENTS**

| Chapte | er 1 Introduction1                           |

|--------|----------------------------------------------|

| 1.1    | Overview1                                    |

| 1.2    | Objective of the Thesis2                     |

| 1.3    | Organization of the Thesis                   |

| Chapte | er 2 Introduction to MDFE4                   |

| 2.1    | Fixed-delay Tree Search (FDTS/DF)4           |

| 2.2    | RAM Decision Feedback Equalization7          |

| 2.2    | Linear DFE7                                  |

| 2.2    | .2 RAM-DFE9                                  |

| 2.3    | Multi-level Decision Feedback Equalization10 |

| 2.4    | Implementations of the MDFE13                |

| Chapte | er 3 Design and Implementation of FBE15      |

| 3.1    | Design Considerations for FBE15              |

| 3.2    | Simple RAM-FBE (Structure-I)16               |

| 3.3    | Look-ahead RAM-FBE (Structure-II)            |

| 3.4    | Improved Look-ahead FBE (Structure III)20    |

| 3.5 Op    | otimized Look-ahead FBE (Structure IV)         | 22 |

|-----------|------------------------------------------------|----|

| 3.6 Su    | mmary of Structure-I, II, III and IV           | 24 |

| 3.7 Be    | havior Simulation                              | 25 |

| 3.8 Fu    | nctional Verification                          | 29 |

| 3.8.1     | Data Analysis of Group-A                       | 31 |

| 3.8.2     | Data Analysis of Group-B                       | 34 |

| 3.9 IC    | Structure                                      | 35 |

| 3.9.1     | SFT_11                                         | 35 |

| 3.9.2     | LOOKUP                                         | 36 |

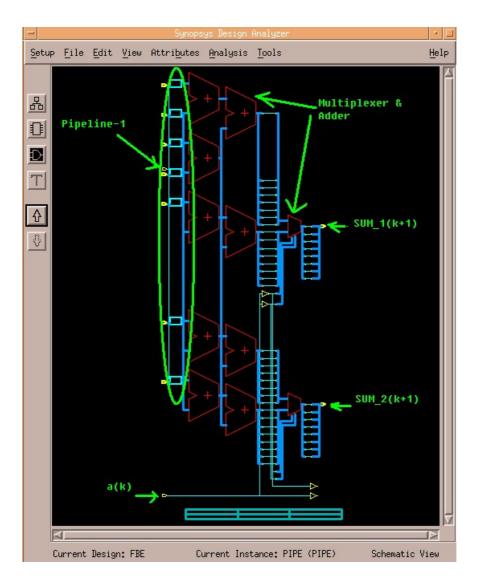

| 3.9.3     | PIPE                                           | 37 |

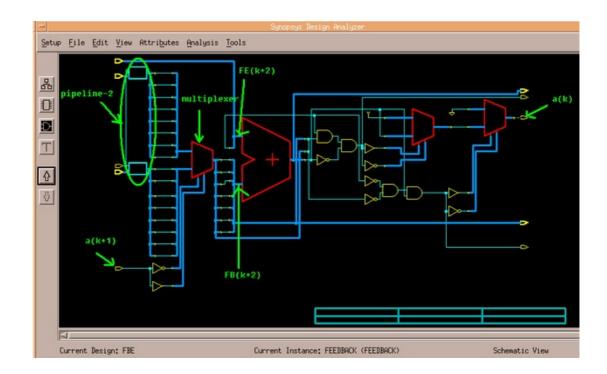

| 3.9.4     | FEEDBACK                                       | 38 |

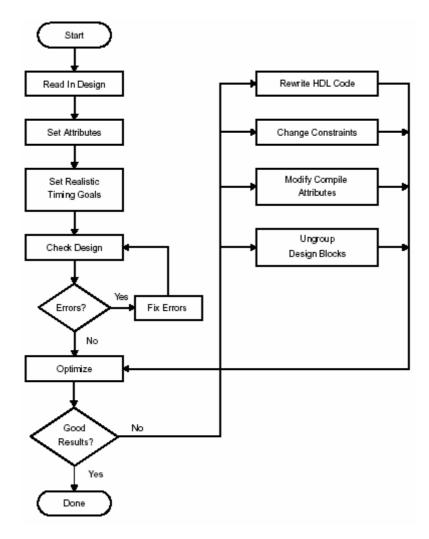

| 3.10 Sy   | nthesis and Optimization                       | 39 |

| 3.10.1    | Design Constraints                             | 40 |

| 3.11 Op   | otimization                                    | 45 |

| 3.12 Sta  | atic Time Analysis                             | 47 |

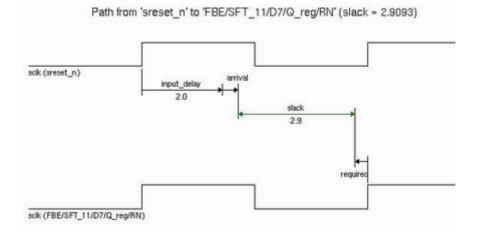

| 3.12.1    | PrimeTime Timing Analysis Flow and Methodology | 48 |

| 3.12.2    | Analysis and Reports.                          | 49 |

| Chapter 4 | Implementation of FFE                          | 54 |

| 4.1 Int   | roduction to the Feed-forward Equalizer        | 54 |

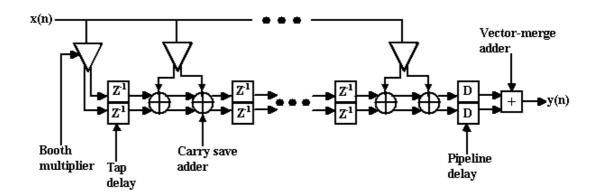

| 4.2 Th    | e Transpose Structure                          | 54 |

| 4.2.1     | Booth Multipliers                                   | 55 |

|-----------|-----------------------------------------------------|----|

| 4.2.2     | Addition Implementation                             | 56 |

| 4.2.3     | Sign Extensions                                     | 57 |

| 4.3 In    | nplementation                                       | 58 |

| 4.3.1     | Functional Verification of FFE                      | 59 |

| 4.3.2     | Synthesis and Timing Analysis of FFE                | 60 |

| Chapter 5 | System Integration of the MDFE Chip                 | 64 |

| 5.1 S     | ystem-Level Considerations                          | 64 |

| 5.2 B     | ehavior Simulation of the MDFE Chip                 | 66 |

| 5.3 Sy    | ystem on Chip (SOC) Implementation of the MDFE Chip | 69 |

| 5.3.1     | I/O Pins/Pads in the MDFE Chip                      | 69 |

| 5.3.2     | Constraints for the Synthesis                       | 73 |

| 5.3.3     | Place and Route (LAYOUT)                            | 74 |

| 5.4 Po    | ost–Layout Timing Analysis                          | 76 |

| Chapter 6 | Conclusion                                          | 80 |

| REFERE    | NCES                                                | 83 |

| APPEND    | IX.A HDL Codes of the Design                        | 87 |

| APPEND    | IX.B Scripts and Reports                            | 98 |

| <b>B</b> .1 | Script of the Constraints for Synthesis         | <del>)</del> 8 |

|-------------|-------------------------------------------------|----------------|

| B.2         | Script of the Constraints for Pre-layout STA:   | <del>)</del> 9 |

| B.3         | Script of the Constraints for Post-Layout STA10 | )0             |

| B.4         | Area Reports10                                  | )1             |

| B.5         | Dynamic Power Reports10                         | )3             |

| B.6         | Timing Reports10                                | )5             |

## **SUMMARY**

The design and implementation of a Multi-level Decision Feedback Equalization (MDFE) chip for magnetic recording channel is described. The architecture of the single-chip MDFE incorporates an 8-tap feed-forward equalizer and a 10-tap feedback equalizer. The feed-forward section (FFE) is a linear transposed filter that removes the linear precursor inter-symbol interference (ISI) by a sufficient length to delay the channel response to make it causal. The feedback section (FBE) uses the decision feedback technique to eliminate non-linear postcursor ISI by a look-up table based structure with the past decisions being the addresses, provided that the past decisions are correct. The main idea of MDFE is to eliminate all the ISI and shape the recoding channel with only impulse response plus some noise components remain.

The design is targeted at a 0.35µm CMOS technology. The minimum clock rate of the chip is projected to be 150MHz with minimal sacrifice in the core area and the dynamic power consumption. The final design shows that at post-layout level, the MDFE chip can operate at a clock rate of 170MHz in *TYPICAL* condition, 230MHz in *BEST* case, and 125MHz in *WORST* case. The speed can be further improved by removing the bottleneck at the FFE, which only runs up to 185 MHz as opposed to 200 MHz for the FBE. The chip, which is composed of 73,386 gates and 54 I/O pads, has the chip area of 4.4mm<sup>2</sup>, and consumes dynamic power of 143.03mW under a 3.3-V supply.

# LIST OF TABLES

| Table.2-1 | Comparison of MDFE architectures14                  |

|-----------|-----------------------------------------------------|

| Table.3-1 | Data path delay of Structure-I                      |

| Table.3-2 | Data path delay of Structure-II20                   |

| Table.3-3 | Core Area and Speed of Structure-III & II           |

| Table.3-4 | Comparison between Structure-IV & III               |

| Table.3-5 | Comparison between Structure-IV & III               |

| Table.3-6 | Summary of Structure-I, II, III & IV24              |

| Table.3-7 | Performance summary of FBE (Structure-IV)53         |

| Table.4-1 | Signal Description of FFE59                         |

| Table.4-2 | Performance of FFE                                  |

| Table.5-1 | Signal Description of the MDFE chip65               |

| Table.5-2 | Data analysis for the MDFE chip68                   |

| Table.5-3 | I/O Ports and Pads Description of the MDFE chip72   |

| Table.5-4 | Performance of the MDFE chip at post-layout level79 |

| Table.6-1 | Published DFE/MDFE filters/detectors                |

# **LIST OF FIGURES**

| Figure.2-1  | Fixed-delay tree search (FDTS/DF) detector     | 4  |

|-------------|------------------------------------------------|----|

| Figure.2-2  | FDTS/DF search algorithm                       | 5  |

| Figure.2-3  | Principle of FDTS/DF detection                 | 6  |

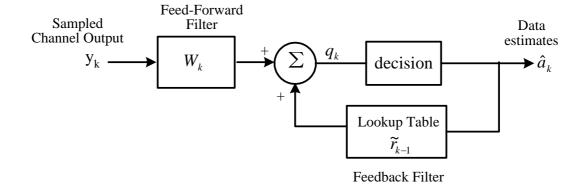

| Figure.2-4  | Block diagram of the linear DFE                | 7  |

| Figure.2-5  | Block diagram of RAM-DFE                       | 9  |

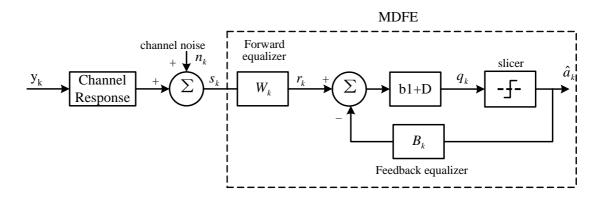

| Figure.2-6  | Digital communication channel with MDFE1       | .1 |

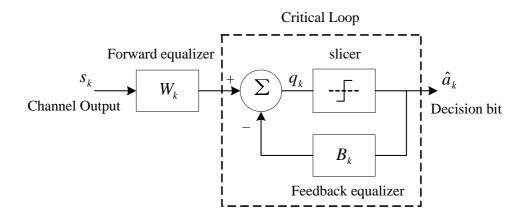

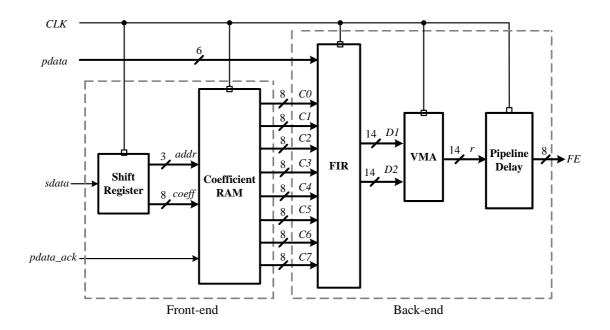

| Figure.3-1  | System diagram of FFE and FBE1                 | 5  |

| Figure.3-2  | Block diagram of FBE (Structure-I)1            | 7  |

| Figure.3-3  | Segmentation of complicated combination logic1 | 8  |

| Figure.3-4  | Block diagram of FBE (Structure-II)1           | 9  |

| Figure.3-5  | Block diagram of FBE (Structure III)2          | 21 |

| Figure.3-7  | Block diagram of FBE (Structure IV)2           | 2  |

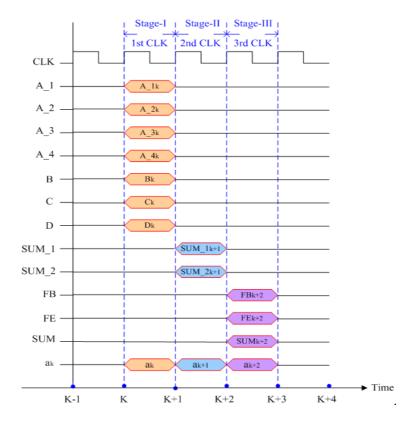

| Figure.3-8  | Operation diagram of FBE2                      | :6 |

| Figure.3-9  | Clock waveform of FBE (Structure-IV)           | 28 |

| Figure.3-10 | FBE functional simulation data (for Group-A)3  | 0  |

| Figure.3-11 | FBE functional simulation data (for Group-B)3  | 3  |

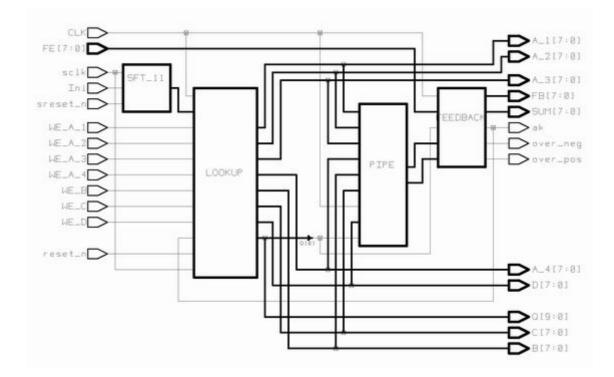

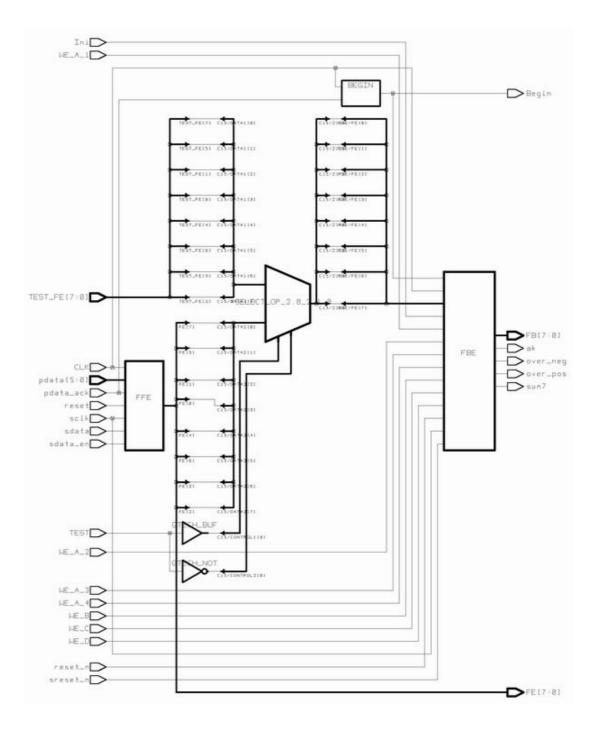

| Figure.3-12 | Schematic view of FBE                          | 5  |

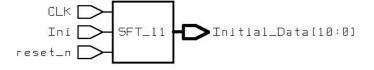

| Figure.3-13 | I/O description of module SFT_11               | 6  |

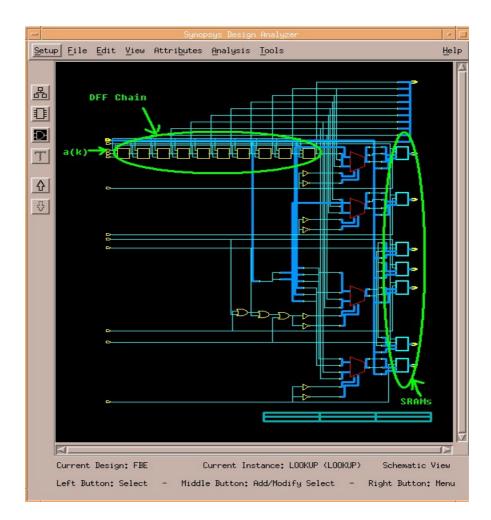

| Figure.3-14 | Schematic view of the module LOOKUP            | 7  |

| Figure.3-15 | Schematic view of the module PIPE              | 8  |

| Figure.3-16 | Schematic view of the module FEEDBACK                  | 39  |

|-------------|--------------------------------------------------------|-----|

| Figure.3-17 | Logic synthesis flow chart                             | 40  |

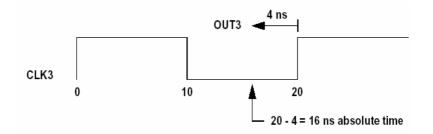

| Figure.3-18 | Waveform of input delay                                | 43  |

| Figure.3-19 | Waveform of output delay                               | .44 |

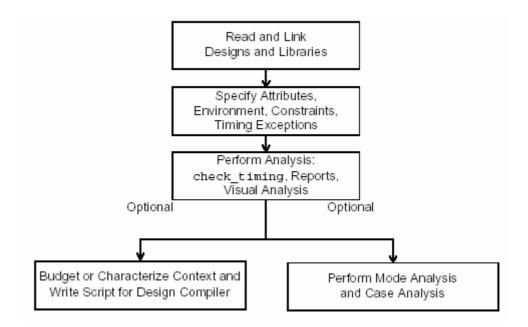

| Figure.3-20 | User flow of PrimeTime                                 | 48  |

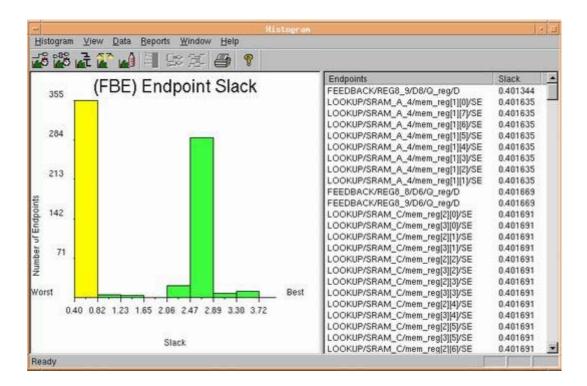

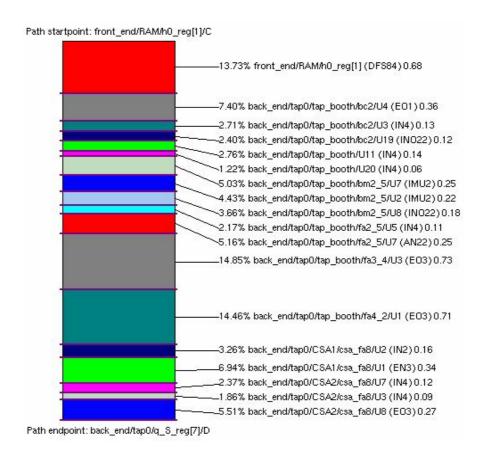

| Figure.3-21 | Histogramof path timing analysis                       | 52  |

| Figure.4-1  | FIR filter architecture used for FFE                   | 55  |

| Figure.4-2  | Block diagram of the feed-forward equalizer (FFE)      | 58  |

| Figure.4-3  | Functional simulation for FFE                          | 60  |

| Figure.4-4  | Leaf diagram of critical path in FFE                   | 62  |

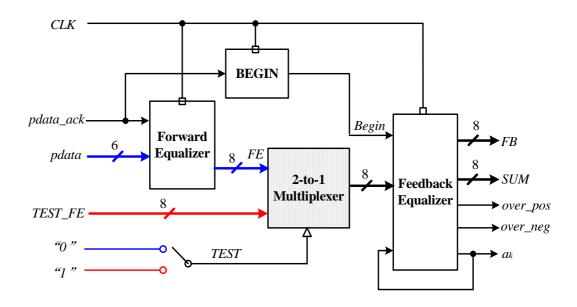

| Figure.5-1  | Block diagram of the MDFE chip                         | 65  |

| Figure.5-2  | Functional verification of the MDFE chip               | 67  |

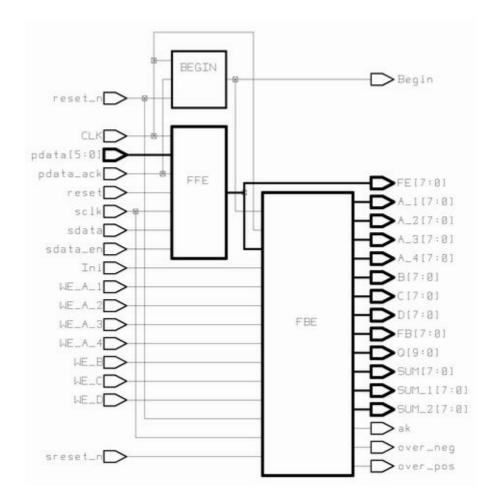

| Figure.5-3  | Schematic view of the combined system (full ports)     | 70  |

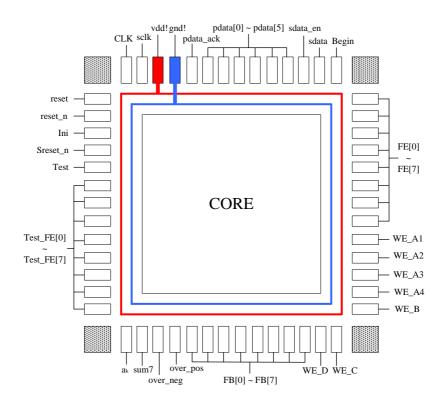

| Figure.5-4  | Schematic view of the combined system (partial ports)  | 71  |

| Figure.5-5  | Diagram of the I/O pads of the chip                    | 73  |

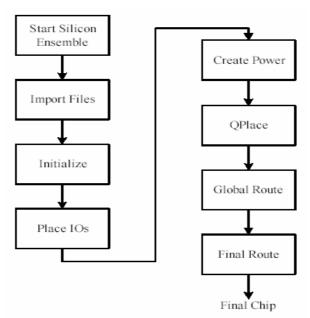

| Figure.5-6  | Flow chart of the layout process                       | 74  |

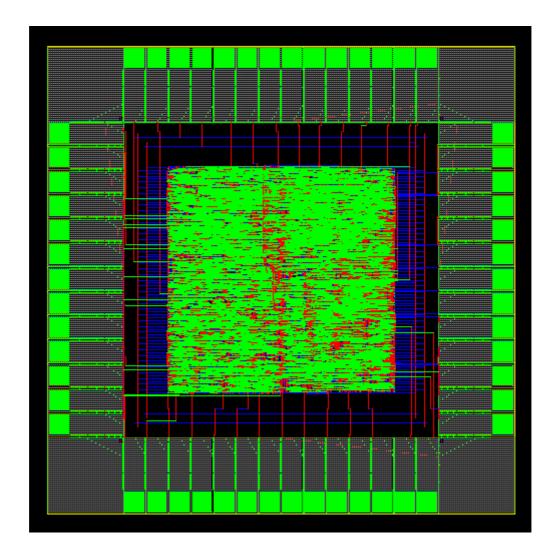

| Figure.5-7  | Layout view of the MDFE chip                           | 75  |

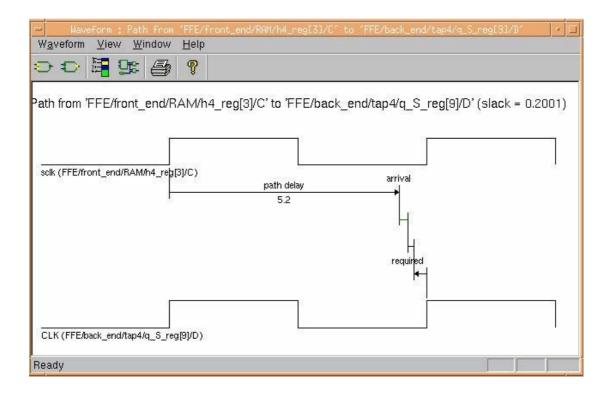

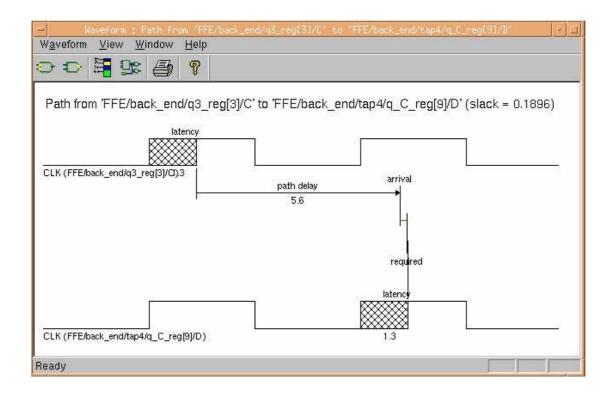

| Figure.5-8  | Time waveform of the critical path (Pre-Layout level)  | 77  |

| Figure.5-9  | Time waveform of the critical path (Post-Layout level) | .77 |

### **Chapter 1 Introduction**

#### **1.1 Overview**

As the magnetic recording industry strives toward high recording densities, the design of equalizers becomes one of the most crucial issues. Inter symbol interference (ISI) is severe at high recording densities and causes degradation in the detection performance because of the difficulty to achieve accurate equalization or because of the excessive noise enhancement. Conventional read-back processing involves the use of run-length limited (RLL) [1][2] codes with peak detection and some read-back equalization. At recording densities in the range of 2-2.5, this turns out to be highly inadequate. Several more sophisticated detection schemes which give improved detection performance at high recording densities are now being pursued.

These schemes can be broadly classified into two categories: one is based on the principle of partial-response signaling coupled with the maximum-likelihood sequence detection (PRML) and the other is based on the principle of decision feedback equalization (DFE). Class-IV PRML [3][4], and extended PRML [5][6] are examples of the first category. Fixed-delay tree search with decision feedback (FDTS/DF) [7], adaptive RAM-DFE [8][14] and multilevel DFE (MDFE) [9] are examples of the second category.

The main idea of decision feedback is to cancel all the precursor and postcursor ISI of the channel impulse response using a 2-tap filter. The feed-forward section (FFE) is a linear filter that removes the linear precursor ISI by averaging and distributing the energy to the postcursor ISI. The feedback equalizer (FBE) is a technique used to eliminate non-linear postcursor ISI by the decision-feedback, provided that the past decisions are correct, so that the output only consists of the impulse response plus some noise components.

#### **1.2 Objective of the Thesis**

The objective of this thesis is to design and implement an integrated multilevel decision feedback equalization chip for magnetic recoding channel. The MDFE chip consists of a feed-forward and a feedback equalizer. The two sections could either run together as a whole system or be tested independently. This design aims to attain a minimum clock rate of **150MHz** (typical-case) using 0.35µm CMOS technology with minimal sacrifice in the core area and the dynamic power consumption.

#### **1.3 Organization of the Thesis**

The thesis is organized as follows. Chapter 2 introduces some background knowledge about FDTS/DF, RAM-DFE and MDFE. Chapter 3 deals with the design and implementation of the feedback equalizer (FBE). Several different architectures are

first investigated and compared, from which the final architecture of FBE is decided. The functional simulation and static time analysis results are presented. Chapter 4 mainly concerns the implementation of the feed-forward equalizer (FFE). Chapter 5 presents the integration of FBE and FFE. The overall design is verified and further synthesized to physical level. The post-layout analysis is carried out and the result is presented. Finally, Chapter 6 concludes this research. Some future work is also suggested.

## **Chapter 2 Introduction to MDFE**

#### 2.1 Fixed-delay Tree Search (FDTS/DF)

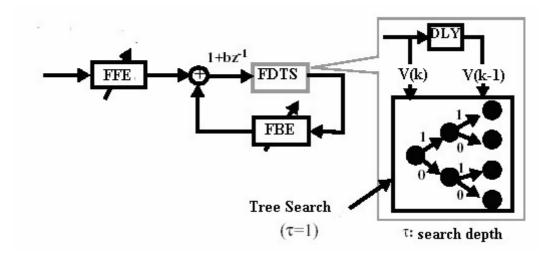

Fixed delay tree search with decision feedback (FDTS/DF) detector [7][10] is an architecture which has been explored extensively in the magnetic recording channels. Figure.2-1 shows the architecture of FDTS/DF with search depth ( $\tau$ ) equal to 1. The feed-forward equalizer (FFE) and feedback equalizer (FBE) are both adaptive, according to the raw channel read-back impulse response.

Figure.2-1 Fixed-delay tree search (FDTS/DF) detector

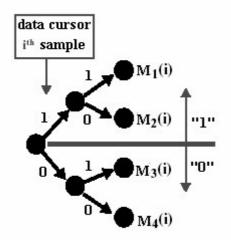

The core is a tree-search detector, which computes the accumulated path metrics for each paths, compares them and selects the path direction at the data cursor. The state diagram of  $\tau = 1$  tree search is shown on Figure.2-2:  $M_k$  is the accumulated path metrics for path *k*, defined as:

$$M_{k} = \sum^{\tau} (y_{j} - \overline{y}_{j,k})^{2}$$

(2.1)

where  $y_j$  is the received read-back samples, and  $\overline{y}_{j,k}$  is the ideal read-back samples if path *k* is selected. Instead of selecting exact one out of the four possible paths, FDTS/DF algorithm only selects the upper-half or lower-half which the detection should proceed at the data cursor, and the decoding window moves along to the next data cursor. Complete analysis can be found in [10][11]. When the search depth is equal to zero, the decision only depends on the current sample, which corresponds to the well-known decision feedback equalization (DFE).

Figure.2-2 FDTS/DF search algorithm

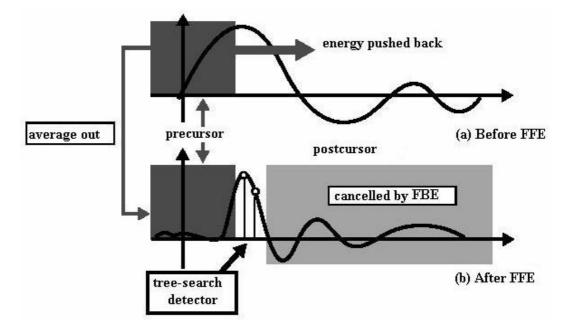

In FDTS/DF, FFE and FBE are designed to remove the precursor ISI and postcursor ISI of the channel impulse response, as shown in Figure.2-3. In digital communication channels where the response of the channel to a symbol to be transmitted is much longer than the symbol itself, a common source of signal distortion is inter-symbol interference (ISI). This means that the responses of the transmitted symbols overlap each other in time. The resulting superposition of signals causes shifts in the location of signal peaks and variances in signal amplitude. When signal distortion is too large, erroneous detections are made at the output. Therefore, as transmission rates increase,

symbols are packed more closely together, increasing ISI and the likelihood of erroneous detections. But if the effects of ISI can somehow be reduced, the achievable transmission rate for a given error probability can be increased.

Figure.2-3 Principle of FDTS/DF detection

FFE and DFE coefficients are usually adaptive according to the MMSE algorithm, to maximize the detector performance. However, the filter coefficients can be also analytically decided given the known input signal spectrum. Linear models for the optimization of  $\tau = 1$  tree-search detector and the relative definitions could denote the statistical expectation. Therefore, we can determine the optimal FFE and FBE filter coefficients without using adaptive algorithms, given that the channel impulse response, input sequence power spectrum, and noise power spectrum are known.

#### **2.2 RAM Decision Feedback Equalization**

Decision Feedback Equalization (DFE) [12] is another technique used to eliminate all ISI so that the output consists only of the impulse response, plus some noise component. The magnetic recording channel at high density exhibits significant non-linear inter-symbol interference, which degrades the performance of linear equalization techniques. The RAM-DFE is proposed as a solution to this problem, in which a digital random access memory (RAM) is used in the feedback path of a feedback equalizer (FBE). It is capable of canceling the non-linear post-cursor inter-symbol interference (ISI).

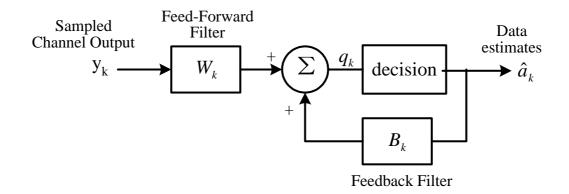

#### 2.2.1 Linear DFE

The linear DFE shown in Figure.2-4 uses an FIR filter in its decision feedback section and is capable of eliminating linear ISI only.

Figure.2-4 Block diagram of the linear DFE

The linear DFE is described by (with L feed-forward coefficients and M feedback coefficients is described by:

$$q_{k} = \sum_{l=0}^{L-1} w_{l} y_{k+1} + \sum_{m=1}^{M} b_{m} \hat{a}_{k-m}$$

(2.2)

$$=^{W'}y_{k+L-1:k} + b'\hat{a}_{k-1:k-M}$$

(2.3)

with  $y_{k+L-1:k} = [y_{k+L-1}...y_k]'$  as the vector of channel outputs, and **w** and **b** as the corresponding coefficient vectors of the linear DFE,  $w = [w_0,...w_{L-1}]'$  and  $b = [b_1,...b_M]'$ . For notational convenience, we assume the feed-forward section to be noncausal (realized with L units of delay). A good setting for the coefficient vectors in the linear DFE minimizes the mean square error  $E[\varepsilon_k^2]$ , where

$$\mathcal{E}_k = a_k - q_k \tag{2.4}$$

The corresponding settings for the linear DFE are well known to be computed as  $[w'b'] = p'R^{-1}$ , where  $p' = E\{[y'_{k+L-1:k}a'_{k-1:k-M}]a_k\}$  is the cross-correlation vector between the current estimated data symbol  $a_k$  and the vector of combined channel outputs and previous decisions; and

$$R = E\{[y'_{k+L-1:k}a'_{k-1:k-M}][y'_{k+L-1:k}a'_{k-1:k-M}]\}$$

(2.5)

is the autocorrelation matrix of the combined channel outputs and precious decisions. Assuming correct output decisions, the minimum mean-square error (MMSE) is

$$\sigma_{mmse}^2 = E\{a_k^2\} - p'R^{-1}p$$

(2.6)

#### 2.2.2 **RAM-DFE**

The RAM-DFE is shown in Figure.2-5, with linear feedback replaced by a lookup table. We define the RAM-DFE parameters using a new notation. If M past decision bits are arranged in a vector and used as a lookup table address, then we can interpret the content of the addressed location as the corresponding table output.

Figure.2-5 Block diagram of RAM-DFE

Let us denote an index for the address vector as  $\tilde{i}_{k-1}$ , where can write

$$0 \le \widetilde{i}_{k-1} = \sum_{m=0}^{M-1} \frac{1}{2} (a_{k-1-m} + 1) 2^m \le 2^M - 1$$

(2.7)

If we further define a 2<sup>M</sup>-dimensional vector

$$s(\tilde{i}_{k-1}) = [s_0(\tilde{i}_{k-1})s1(\tilde{i}_{k-1})...s_{2^{M}-1}(\tilde{i}_{k-1})]'$$

(2.8)

then we can write the RAM output as

$$r(\tilde{i}_{k-1}) = \tilde{b}'s(\tilde{i}_{k-1})$$

(2.9)

where  $\tilde{b} = [\tilde{b}_0 ... \tilde{b}_{2^{M}-1}]'$  is a vector with the contents of the corresponding ram locations. Since the feedback path is linear in the 2<sup>M</sup> newly defined inputs, the analysis is then the same as the linear DFE with  $\hat{a}_{k-1:k-M}$  replaced by  $s(\tilde{i}_{k-1})$ , and b replaced by  $\tilde{b}$ . The MMSE for the RAM-DFE is quadratic in the parameters  $[w'\tilde{b}']$ and has a unique global MMSE, because the autocorrelation matrix is nonsingular. The 2<sup>M</sup> elements of  $\tilde{b}$  are then the contents of the lookup table.

The MMSE for both the linear DFE and the RAM-DFE can be computed and compared. The quantities  $\tilde{p}$  and  $\tilde{R}$  are not trivially computed in terms of the given finite-state machine model for the channel. We show how to compute these quantities in term of  $f(i_k)$ . The DFE output SNR in either case is computed as

$$SNR = \frac{E(a_k^2) - \sigma_{mmse}^2}{\sigma_{mmse}^2}$$

(2.10)

In summary, RAM-DFE can very closely achieve the MMSE solution for the measured read signal. Furthermore, by using signed-LMS, all explicit multiplications may be eliminated from the adaptation procedure, making the RAM-DFE well suited to high-speed applications such as magnetic recording.

#### **2.3 Multi-level Decision Feedback Equalization**

A simplified version of FDTS/DF [13] is called Multi-Level Decision Feedback Equalization (MDFE) [9][15] because it is architecturally identical to DFE. The only difference is that the algorithm for determining the coefficients of the forward and backward equalizers is changed so that the output becomes multi-level. A digital communication channel incorporating MDFE is shown in Figure2-6.

Figure.2-6 Digital Communication Channel with MDFE

In this channel, a digital data stream,  $y_k$ , consisting of positive and negative impulses, enters the channel response block. The channel response block includes the response of the transmission media, plus that of filters that are used to shape the signal before and after its transmission. White noise is then factored in with the addition of the  $n_k$  term. After sampling, the transformed signal,  $s_k$ , enters the MDFE through a linear transversal filter - the forward FIR filter with coefficients  $W_k$ . This filter is of sufficient length to delay the response to make it causal. It is designed to remove pre-cursor ISI from the response - the ISI due to future symbols.

The output of the forward filter,  $r_k$ , is summed with the output of the feedback section. The  $B_k$  coefficients of the feedback section, or backward filter, are chosen

to match the combined response of the channel block and the forward filter to a unit impulse. In other words, when the output of the backward filter is subtracted from  $r_k$ , all of the channel responses except for the unit impulse response of a single  $y_k$  input are removed.

The coefficients in MDFE are determined in the same way as in DFE. One difference is the error signal,  $(\varepsilon_k = q_k - \hat{q}_k)$ , due to the changed target,  $\hat{q}_k$ , and actual,  $q_k$ , outputs in MDFE. Also, the b<sub>1</sub> term is removed from its normal position in the backward filter and is now calculated by a separate algorithm for its use in the linear discriminant. Its equation is:

$$b_{1,k+1} = b_{1,k} - 2\mu_{b1}(\hat{a}_{k+1} + \hat{a}_{k-1} + 2b_{1,k}\hat{a}_{k})\varepsilon_{k}$$

(2.11)

where  $\mu_{b1}$  is the rate of adaptation for  $b_{1,k}$ .

Because the error signal,  $\varepsilon_k$ , now uses a future detected symbol,  $\hat{a}_{k+1}$ , a delay must be added to the coefficient update equations for the forward and backward equalizers. The update equation for the forward equalizer coefficients,  $W_k = [w_{0,k}, w_{1,k}, ..., w_{M,k}]$ , becomes:

$$W_{k+1} = W_k + 2\mu_w S_{k-1} \varepsilon_{k-1}$$

(2.12)

The update equation for the backward equalizer coefficients,  $B_k^1 = [b_{2,k}, ..., b_{N,k}]$ , becomes:

$$B_{k+1}^{1} = B_{k}^{1} + 2\mu_{b}\hat{A}_{k-1}\varepsilon_{k-1}$$

(2.13)

Once the values for  $b_1$ ,  $W_k$ , and  $B_k^1$  are calculated,  $W_k$  and  $B_k^1$  must be multiplied through by the linear discriminant,  $(b_1 + D)$ , to obtain the actual coefficients to be loaded into the equalizers. Thus, the target response of MDFE is multiplied by  $(b_1 + D)$ , yielding:

$$\hat{q}_{k} = b_{1}\hat{a}_{k+1} + (1+b_{1}^{2})\hat{a}_{k} + b_{1}\hat{a}_{k-1}$$

(2.14)

MDFE provides superior performance to the other disk data detection methods, such as peak detection and Partial Response (PR) Equalization, while offering a simple, low-cost, low-power implementation. Thus, MDFE is a promise solution for the increasing disk drive storage density.

#### 2.4 Implementations of the MDFE

The most significant differences between analog and digital implementation are the non-idealities such as offset and nonlinearity that are associated with analog circuits. Table.2-1 briefly compares the three architectures. If offset proves to be a surmountable problem, the mostly analog MDFE will be the smallest of the three implementations. It is reasonable to assume, with the design of the counters in the mostly digital MDFE, the comparators will be the speed-limiting factor for all three implementations. In this case the most efficient in terms of size and power will be the mostly analog MDFE. For a completely digital implementation, the transposed FFE and the RAM-DFE are worthy of consideration.

| Architecture | Programming<br>Coefficients | Estimated Area | Design Challenge           |

|--------------|-----------------------------|----------------|----------------------------|

| Analog       | Hard, ADC-DAC               | Smallest       | Integrator DC gain,offset  |

| Digital      | Easy                        | Medium         | Fast digital circuits      |

| Mixed-Signal | Easy                        | Largest        | Fast digital circuits, DAC |

Table.2-1 Comparison of MDFE architectures

## **Chapter 3 Design and Implementation of FBE**

#### **3.1 Design Considerations for FBE**

The block diagram of MDFE to be implemented is given in Figure 3-1. As described before, the feed-forward section (FFE) is a linear filter that shapes the read-channel pulse response, and the feedback section (FBE) is used to eliminate the non-linear post-cursor ISI, provided that the past decisions are correct. An impulse response plus some noise components will therefore be obtained at the output.

Figure.3-1 System Diagram of FFE and FBE

being the addresses. A key specification for the FBE is the speed. When the current decision is available, the feedback coefficient must be ready before next clock arrives. Thus, the operation of the FBE must be completed within one clock cycle. This imposed some difficulties on the FBE design. In this chapter, a number of

architectures for FBE are investigated and compared, from which the final architecture is chosen. The number of taps and coefficients are determined from the system-level simulation done elsewhere. The full digital implementation is a prerequisite for this work. This design aims to attain a minimum clock rate of 150 MHz with minimal sacrifice in the core area and the dynamic power consumption.

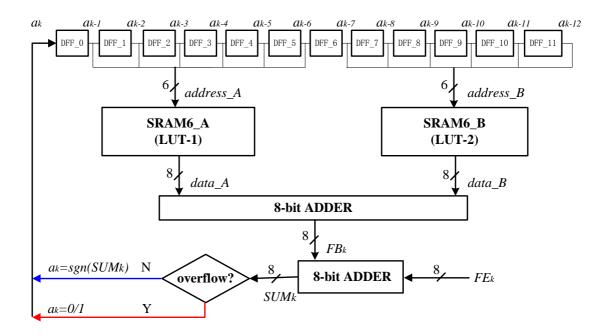

#### **3.2 Simple RAM-FBE (Structure-I)**

A simple structure of the RAM-FBE, as shown in Figure.3-2, is first investigated It is composed of a 12-tap D-Flip-Flop chain together with two SRAMs as the two look-up tables. Each SRAM has the size of  $2^6 \times 8$  bits. To achieve the goal of performing a broad range of recording densities, minimizing the noise enhancement and a good post-cursor ISI cancellation, the length of FBE must be long enough. The choice of 12-tap FBE is based on the work done in [17] where it showed that the satisfactory performance can be achieved the minimum number of feedback taps of 12.

All the feedback coefficients are pre-calculated and loaded into the look-up tables (LUT) through a series interface prior to the read operation of the channel. At the rising clock edge of time k, for example, the past decisions stored in the D-Flip-Flop chain are used to address the look-up tables. Two outputs from the lookup tables, *data\_A* and *data\_B* are summed to produce the final feedback value  $FB_k$ . This feedback data is then added to the 8-bit output data,  $FE_k$ , from the FFE. The slice

takes the sum as its input and produces the current decision-bit  $a_k$ , which is based on the sign of the summation.

Figure.3-2 Block diagram of FBE (Structure-I)

Though this structure is quite simple to be implemented, it has a disadvantage of its long critical path. For each data path which may start from  $a_{k-1}, a_{k-2}, ..., a_{k-12}$ , it will go through a  $2^6 \times 8$  bits SRAM and two 8-bit adder together with some combination logic gates, and then go back to the D-Flip-Flop chain.

Table.3-1 gives the path delay report after optimization. The highest clock rate that can be achieved for this structure is only about 75 MHz, far below the spec of **150MHz**. The critical path in this structure is 13.07ns, which is mainly caused by the SRAMs and the adders.

|                            | Path Through | Path Delay |

|----------------------------|--------------|------------|

| a <sub>k-1</sub> to data_A | SRAM6_A      | 4.91 ns    |

| data_A to $FB_k$           | 8-bit adder  | 3.78 ns    |

| $FB_k$ to $SUM_k$          | 8-bit adder  | 3.82 ns    |

| $SUM_k$ to $a_k$           | logic gates  | 0.56 ns    |

Table.3-1 Data path delay of Structure-I

#### 3.3 Look-ahead RAM-FBE (Structure-II)

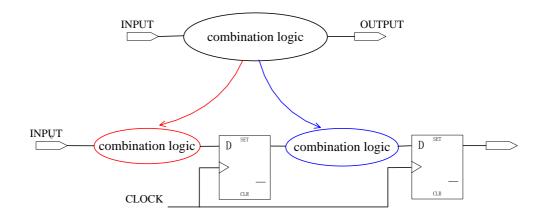

To reduce the delay caused by the SRAM and adders as in the Stucture I, the pipeline technique can be employed. In the synchronous logic design, shorting the path delay of the combination logic between the sequential logic is the most effective way to increase the system speed. As shown in Figure.3-3, the large combinational logic block can be segmented into several small ones that are divided by flip-flops. This is so called PIPELINE principle [18].

Figure.3-3 Segmentation of complicated combination logic

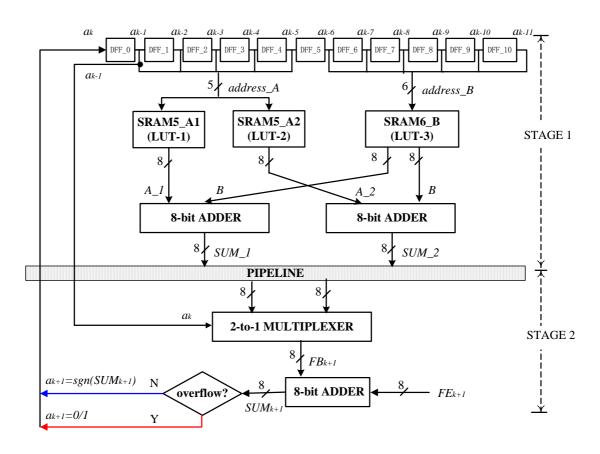

According to this method, a new design is explored with the pipeline insertion and the Look-Ahead operation. As shown in Figure.3-4, Structure-II has 2 combinational

logic stages. This design is composed of an 11-tap D-Flip-Flop chain where the first bit is taken as the look-ahead bit compared to Structure-I. Therefore, the first 6-bit SRAMs in Structure-I is split into two 5-bit SRAMs which store the coefficients for the current decision of "1" and "0", respectively. Thus, in this structure, three lookup tables are needed. Two sets of coefficients are pre-calculated and later selected by the multiplexer that is controlled by the current decision bit.

Figure.3-4 Block diagram of FBE (Structure-II)

Table.3-2 is the path delay report for Structure-II. The critical path (in stage-1) is reduced to 7.99ns and the speed is increased to 125MHz. This is attributed to the removal of one adder and some logic gates from the whole data path. However, it still

PathPath ThroughPath DelayStage-1 $a_{k-1}$  to SUM\_1SRAM5\_A1 & 18-bit adder7.99 nsStage-2FBk to  $a_k$ 18-bit adder & logic gates3.76 ns

Table.3-2 Data path delay of Structure-II

#### 3.4 Improved Look-ahead FBE (Structure III)

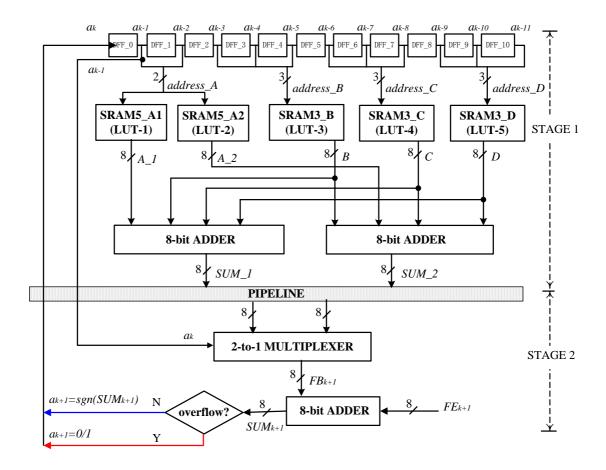

Though the system speed has been increased by the improvements made in Structure-II, the size of each lookup table is rather big  $(2^5 \times 8 \text{ or } 2^6 \times 8)$ . As the time taken by the FBE to generate the output to some extent is affected by the read access time of the SRAM, large size will possibly cause more delays and large silicon area. Therefore, we will split the big lookup table in to small ones [16].

Structure-III, as shown in Figure.3-5, is an improved version of Structure-II with a special focus on the chip area. This structure also has two pipeline stages and one 11-tap D-Flip-Flop chain, but it uses several small SRAMs ( $2^2 \times 8$  or  $2^3 \times 8$ ) to reduce the core area and the dynamic power. In this structure, 5 lookup tables are employed.

Figure.3-5 Block diagram of FBE (Structure III)

Synthesis and simulation results show that there is a significant improvement on the chip area in Structure II, while maintaining the same speed. The critical path is still in Stage-1. Table.3-3 shows the performance comparison between Structure II and III. The speed of the FBE needs to be further improved.

Table.3-3 Core Area and Speed of Structure-III & II

|               | <b>Critical Path</b> | <b>Clock Rate</b> | Core Area           |

|---------------|----------------------|-------------------|---------------------|

| Structure-II  | 7.99 ns              | 125 MHz           | $0.82 \text{ mm}^2$ |

| Structure-III | 7.70 ns              | 130 MHz           | $0.26 \text{ mm}^2$ |

#### **3.5 Optimized Look-ahead FBE (Structure IV)**

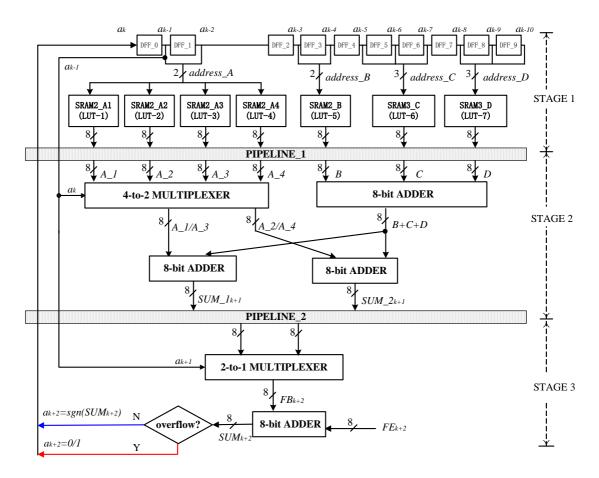

It has been found that the bottleneck for the speed in the previous structure is due to the SRAM and the adder in Stage-1. Thus, the SRAMs can be further split to small sizes and more pipelines can be employed. This leads to the Structure IV as shown in Figure.3-7.

Figure.3-7 Block diagram of FBE (Structure IV)

Structure IV has three pipeline stages and one 10-tap D-Flip-Flop chain. It looks ahead for **2** bits, instead of just one as in the two previous structures. The first two 2-bit SRAM, which is in structure-III, are split into four 2-bit SRAMs which store the coefficients for the current decision of "1" and "0" and the next decision of "1" and

"0" respectively. Thus, in this structure, seven lookup tables are needed. Four sets of coefficients are pre-calculated and later selected by the multiplexer that is controlled by the current decision bit and the next decision in different pipeline stages.

The three pipeline stages relax the timing constraint, while the 2-bit look ahead avoids the problem of latency introduced by the pipeline stages. In this structure, although seven lookup tables are needed, the size of each lookup table or RAM, which is  $2^2 \times 8$ or  $2^3 \times 8$ , is still quite small.

Table.3-4 shows the path delay report of Structure IV. As the 2 pipeline stages in Structure-II and III are split into 3 stages, here the critical path is no longer in Stage-1 but in Stage-2 only caused by the adders. It can be seen that evaluation the critical path is reduced to **4.60ns** and the speed of **200MHz** is attained.

Table.3-4 Comparison between Structure-IV & III

| Path Path Through |                 | Path Delay                  |         |

|-------------------|-----------------|-----------------------------|---------|

| Stage-1           | $a_{k-12}$ to D | SRAM3_D                     | 3.91 ns |

| Stage-2           | D to SUM_1      | 2 8-bit adders              | 4.60 ns |

| Stage-3           | $FB_k$ to $a_k$ | 1 8-bit adder & logic gates | 3.47 ns |

Table.3-5 shows the comparison with the Structure III. The chip area is  $0.33 \text{ mm}^2$ , only slightly larger than that of Structure-III ( $0.26 \text{ mm}^2$ ).

Table.3-5Comparison between Structure-IV & III

|               | <b>Critical Path</b> | Speed   | Core Area |

|---------------|----------------------|---------|-----------|

| Structure-III | 7.70 ns              | 130 MHz | 0.26 mm2  |

| Structure-IV  | 4.60 ns              | 200 MHz | 0.33 mm2  |

#### 3.6 Summary of Structure-I, II, III and IV

The performances of the four structures are summarized in Table.3-6. Structure-I is a direct implementation based on the operation of the MDFE. Although it is simple, it has the worst performance. The speed improvement of both Structure-II and Structure-III are benefited from the pipeline technique. Structure-III has the smallest core area which is achieved by replacing the big SRAMs with small ones. However, both of them are limited at the frequency of no more than 130MHz. Structure IV shows superior speed performance to the other three structures with slightly larger core area and high power consumption than those of Structure III. Its speed performance is attributed to its 3 pipeline and the use of small SRAMs. The Structure IV is finally chosen for the implementation of FBE.

| Structure                       | Ι                        | II                                                   | III                                                  | IV                                                   |

|---------------------------------|--------------------------|------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|

| Taps                            | 12                       | 11                                                   | 11                                                   | 10                                                   |

| Pipeline Stages                 | No pipeline              | 2                                                    | 2                                                    | 3                                                    |

| SRAM                            | $2^6 \times 8$ bits (×2) | $2^5 \times 8$ bits (×2)<br>$2^6 \times 8$ bits (×1) | $2^2 \times 8$ bits (×2)<br>$2^3 \times 8$ bits (×3) | $2^2 \times 8$ bits (×5)<br>$2^3 \times 8$ bits (×2) |

| Clock Rate<br>(MHz)             | 75                       | 125                                                  | 130                                                  | 200                                                  |

| Core Area<br>(mm <sup>2</sup> ) | /                        | 0.82                                                 | 0.26                                                 | 0.33                                                 |

| Dynamic Power<br>(mW)           | /                        | 1091.7                                               | 18.39                                                | 43.86                                                |

Table.3-6Summary of Structure-I, II, III & IV

#### **3.7 Behavior Simulation**

Behavior simulation is quite necessary when the system-level design is done. There are several ways to create an imaginary simulation model of a system. The behavioral simulation gives out the verification that if a logical system works correctly. The simulation tool used here is Verilog-XL.3.0 [24][25] by CADENCE. In the next subsections, the verification result and the data analysis of FBE and the whole system will be given.

As was described before, all the feedback coefficients are pre-calculated and loaded (written) into the lookup tables prior to the read operation of the channel. One of the simulation results is shown in Figure 3-8. In stage-1, the outputs ( $A_1$ ,  $A_2$ ,  $A_3$ ,  $A_4$ , B, C, D) of the SRAMs are determined by the previous decisions captured in the DFF chain ( $a_{k-1}$ ,  $a_{k-2}$ ,  $a_{k-3}$ ,  $a_{k-4}$ ,  $a_{k-5}$ ,  $a_{k-6}$ ,  $a_{k-7}$ ,  $a_{k-8}$ ,  $a_{k-9}$ ,  $a_{k-10}$ ). SUM\_1 and SUM\_2 are the outputs generated in stage-2. FB, SUM, over-pos, over-neg, and  $a_k$  are outputs generated in stage-3. CLK is the system clock, and FE is an external signal from the feed-forward equalizer.

As shown in Figure 3-7, with the look-ahead, the FBE is allowed to complete its operation in three clock cycles, thus the timing constraints on the critical path is relaxed.

| 1                                      |                                        |                      | Signalscan Wavefo                    | rn:1           |

|----------------------------------------|----------------------------------------|----------------------|--------------------------------------|----------------|

| <u>File Edit Control</u>               | <u>View Format Options</u>             | Windows <u>H</u> elp |                                      |                |

| Undo (at                               | Copy Parte                             | lalato Zo            | oomInX ZoomOutX                      | ZnOutXF        |

| TimeA = 5000 s                         | Cursor1 = 4305                         | 8                    | Cursor2 = 440                        | 5 s            |

| Sim End = 5000 s<br>Cur2-Cur1 = 100 s  | 4285 4300                              | <b>4</b> 350         | 4400                                 | A450           |

| Group: A                               |                                        |                      |                                      |                |

| CLK = 1                                | mmm                                    |                      | mmm                                  |                |

| - ak = 1                               |                                        |                      |                                      | •              |

| ak_1 = 0                               |                                        |                      |                                      |                |

| $ak_2 = 1$                             |                                        |                      |                                      |                |

| ak_3 = 0<br>ak_4 = 0                   |                                        |                      |                                      |                |

| ak_5 = 0                               |                                        |                      |                                      |                |

| alc_6 = 0                              | التحصير                                |                      |                                      |                |

| ak_7 = 0                               |                                        |                      |                                      |                |

| ak_8 = 0                               |                                        |                      |                                      |                |

| ak_9 = 1                               |                                        |                      |                                      |                |

| ak_10 = 0                              |                                        |                      |                                      |                |

| $A_1[7:0] = h 03$<br>$A_2[7:0] = h 07$ | 01 02 03 02 03 01<br>05 06 07 06 07 05 |                      |                                      | 02 03          |

| $A_3[7:0] = 'h OB$                     | 09 OA OB OA OB 09                      | OA OC OB 00          |                                      | 0A 0E          |

| $A_4[7:0] = 'h OF$                     | OD OF OF OF OF OD                      | OE 10 OF 01          |                                      | OE OE          |

| B[7:0] = 'h 11                         | 11 12 13 12                            | 13 11 12 14          | 4 13 12 13 11                        |                |

| C[7:0] = 'h 15                         | 19 15 16                               | 17 1A 17 19 19       | 5 16 18 1B 1A 17                     | 19 15          |

| D[7:0] = 'h 1F                         | 9D 1E 1F 21 9D                         | 1E 1F 22             | 2 1F 21 9D 1E 20                     | 23 22          |

| $SUM_1[7:0] = 'h 46$                   | 4A D0 46 50 4A C8                      | C6 D0 D2 4A 55       | 5 4D 4B 4C CC 4A                     | 51 41          |

| SUM_2[7:0] = 'h 4A<br>FB[7:0] = 'h D0  | 4E D4 4A 54 4E CC<br>47 4E D0 4A 50 4A | CA D4 D6 4E 59       | 9 51 4F 50 D0 4E<br>E 55 4D 4B 4C CC | 55 53<br>4E 51 |

| FE[7:0] = h B0<br>FE[7:0] = 'h 80      | 9B 00 80 00 35 07                      | 09 2A 43 00 01       | 8 E9 34 BB 6D 00                     | 63 102         |

| SUM[7:0] = 'h 50                       |                                        | D1 4F4 417 4D2 450   |                                      |                |

| over_pos = 0                           |                                        | •                    |                                      |                |

| over_neg = 1                           |                                        |                      |                                      |                |

Figure.3-8 Operation diagram of FBE

At the first rising clock edge, the previous decisions stored in the shift register are used to address the look-up table, or the SRAM. The shift register is simply implemented as a chain of 10 D-flip-flops with asynchronous reset and responds to input data at the rising clock edge. The six earliest decision bits,  $\{a_{k-5}, a_{k-6}, a_{k-7}\}$  and  $\{a_{k-8}, a_{k-9}, a_{k-10}\}\$  are used to address SRAM\_C and SRAM\_D, respectively. The two second recent decision bits,  $\{a_{k-3}, a_{k-4}\}\$ , are used to address SRAM\_B and the two most recent decision bits,  $\{a_{k-1}, a_{k-2}\}\$ , address four look-up tables, SRAM2\_A1(for the case of  $a_k=0, a_{k+1}=0$ ), SRAM2\_A2(for the case of  $a_k=0, a_{k+1}=1$ ), SRAM2\_A3(for the case of  $a_k=1, a_{k+1}=0$ ), and SRAM2\_A4(for the case of  $a_k=1, a_{k+1}=1$ ).

At the second rising clock edge, 4 possible values of *FB* are summed up by the previous 7 output data from the 7 look-up tables. At the same time, the current decision bit  $a_k$  is clocked into the first bit in the shift register, and this value is used as the select signal for the 4 to 2 multiplexer to choose the corresponding *SUM\_1* and *SUM\_2* from the 4 sum values. The computation of the 2<sup>nd</sup> stage outputs are shown in the following 2 equations.

$$\begin{cases} SUM \_1_{k+1} | (a_k = 0, a_{k+1} = 0) = A\_1 + B + C + D \\ SUM \_2_{k+1} | (a_k = 0, a_{k+1} = 1) = A\_2 + B + C + D \end{cases}$$

(3.1)

or,

$$\begin{cases} SUM_{-1_{k+1}} \mid (a_k = 1, a_{k+1} = 0) = A_{-3} + B + C + D \\ SUM_{-2_{k+1}} \mid (a_k = 1, a_{k+1} = 1) = A_{-4} + B + C + D \end{cases}$$

(3.2)

At the third rising clock edge, the current decision bit  $a_{k+1}$  is clocked into the first bit in the shift register. This value is used as the select signal for the 2 to 1 multiplexer to choose the corresponding  $FB_{k+2}$  from the two pre-calculated feedback values like following:

$$\begin{cases} FB_{k+2} \mid (a_{k+1} = 0) = SUM \_1_{k+1} \\ FB_{k+2} \mid (a_{k+1} = 1) = SUM \_2_{k+1} \end{cases}$$

(3.3)

The final feedback value  $FB_{k+2}$  will then be summed with the 8-bit input from the feed-forward filter.  $FE_{k+2}$  at the main adder to produce  $a_{k+2}$ , which is based on the sign of the summation. The computation of the 3<sup>rd</sup> stage outputs are:

$$SUM_{k+2} = FE_{k+2} + FB_{k+2}$$

(3.4)

In the case of no overflow:

$$a_{k+2} = \operatorname{sgn}(SUM_{k+2}) \tag{3.5}$$

In the case of positive or negative overflow:

$$\begin{cases} a_{k+2} = 0; (pos - overflow) \\ a_{k+2} = 1; (pos - overflow) \end{cases}$$

(3.6)

Figure.3-9 Clock waveform of FBE (Structure-IV)

The above operation is illustrated in Figure.3-9, in which it shows that the operation of the FBE is completed in three clock cycles.

#### **3.8 Functional Verification**

To do the functional verification, hundreds of vectors are fed into FBE as the simulated input data *FE* (8-bit). Therefore, the outputs of FBE could be verified, such as *FB*, *SUM*, and  $a_k$ . Figure.3-10 and Figure.3-11 shows the behavioral simulation result of FBE by vectors. Each data line presents for the variables in FBE system and they are listed by time. From the data, we could have an analysis that if this system is running just as correctly as predicted.

As the system is a feedback loop and the only factors which could influence the whole operation are  $a_k$  and *FE*, especially  $a_k$  the analysis could be taken out by **Typical Cases**. Totally such kinds of cases are 6 and they could be classified by 2 groups. Group-A includes 4 cases which mainly concern with the operation with different  $a_k/a_{k+1}$ , for  $a_k$  is to verify the logic in stage-2 and  $a_{k+1}$  is to verify the logic in Stage-3. Group-B includes the other 2 cases which concern with the data overflow. For these two cases,  $a_k/a_{k+1}$  are not relevant.

- Typical Case.1:  $a_k = 0$ ,  $a_{k+1} = 0$ ;

- Typical Case.2:  $a_k = 1$ ,  $a_{k+1} = 0$ ;

- Typical Case.3:  $a_k = 0, a_{k+1} = 1;$

- Typical Case.4:  $a_k = 1$ ,  $a_{k+1} = 1$ ;

- Typical Case.5: positive overflow;

- ♦ Typical Case.6: negative overflow;

Figure.3-10 and Figure.3-11 have exactly the same simulation data, and the only difference is they have different markers to show the case analysis of Group-A and Group-B respectively.

| 100           | ΞI              |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------|-----------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |                 |                                       | <pre></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|               |                 |                                       | p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p       p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|               |                 |                                       | SUM= 206<br>SUM= 206<br>SUM= 206<br>SUM= 208<br>SUM= 85<br>SUM= 85<br>SUM= 85<br>SUM= 210<br>SUM= 78<br>SUM= 78<br>SUM= 78<br>SUM= 78<br>SUM= 78<br>SUM= 129<br>SUM= 78<br>SUM= 23<br>SUM= 23<br>SUM= 23<br>SUM= 23<br>SUM= 23<br>SUM= 129<br>SUM= 129                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|               |                 |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|               |                 |                                       | FB= 206<br>FB= 206<br>FB= 2014<br>FB= 2014<br>FB= 2014<br>FB= 2014<br>FB= 2014<br>FB= 2014<br>FB= 2014<br>FB= 2014<br>FB= 714<br>FB= 714<br>FB= 714<br>FB= 714<br>FB= 2012<br>FB= 2012<br>FB= 2012<br>FB= 2012<br>FB= 2012<br>FB= 714<br>FB= 2012<br>FB= 714<br>FB= 714FB= 714<br>FB= 714<br>FB= 714<br>FB= 714 |

|               |                 |                                       | 212<br>2115<br>2115<br>2115<br>2115<br>2125<br>2125<br>2125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|               |                 |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|               |                 |                                       | 210 SUM<br>2211 SUM<br>79 SUM<br>882 SUM<br>883 SUM<br>883 SUM<br>883 SUM<br>712 SUM<br>712 SUM<br>800 SUM<br>713 SUM<br>714 SUM<br>715 SUM<br>715 SUM<br>715 SUM<br>715 SUM<br>715 SUM<br>715 SUM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|               |                 | 2222                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |