# A LOW POWER DESIGN FOR ARITHMETIC AND LOGIC UNIT

NG KAR SIN (B.Tech. (Hons.), NUS)

## **A THESIS SUBMITTED**

## FOR THE DEGREE OF MASTER OF ENGINEERING

# **DEPARTMENT OF**

## **ELECTRICAL AND COMPUTER ENGINEERING**

## NATIONAL UNIVERSITY OF SINGAPORE

2004

# ACKNOWLEDGEMENTS

I would like to express my deepest gratitude to all those who have directly or indirectly provided advice and assistance during the course of my research in the NUS.

Assoc. Prof. Tay Teng Tiow (NUS), who has led me to the proposal of this project. He has provided invaluable guidance, suggestions and support throughout the course of research. During times of difficulties, he has also shown much understanding and patience, which makes this course a memorable part of my life.

Mr Zhu Xiao Ping and Mr Pan Yan, for their times in several constructive discussions over technical and academic problems. These discussions often helped to clarify questions that are related to the research interest.

Miss Rose Seah and Mr Teo King Hock, for their prompt logistic support in the lab, which provided me a conducive environment to work in the lab.

# **TABLE OF CONTENTS**

#### ACKNOWLEDGEMENTS

| TABLE OF CONTENTS | ii   |

|-------------------|------|

| SUMMARY           | v    |

| LIST OF TABLES    | vii  |

| LIST OF FIGURES   | viii |

| LIST OF SYMBOLS   | х    |

#### CHAPTER 1 INTRODUCTION

| 1.1 | Background          | 1  |

|-----|---------------------|----|

| 1.2 | Related Work        | 2  |

| 1.3 | Project Proposal    | 5  |

| 1.4 | Project Overview    | 6  |

| 1.5 | Scope of Project    | 9  |

| 1.6 | Thesis Organization | 10 |

#### CHAPTER 2 THE ARITHMETIC AND LOGIC UNIT DESIGN

| 2.1 | ALU Design                     | 12 |

|-----|--------------------------------|----|

| 2.2 | Hardware Components            | 15 |

|     | 2.2.1 Decode and Control Unit  | 15 |

|     | 2.2.2 Functional Units         | 16 |

|     | 2.2.3 Register File            | 17 |

| 2.3 | Software Instruction Scheduler | 20 |

i

|           | 2.3.1  | Avoiding Hazards with Wait States                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 21 |  |  |  |  |  |

|-----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|--|--|

| 2.4       | Chapt  | Summary<br>RITHMETIC AND LOGIC UNIT HARDWARE<br>Circuits<br>Circuit Design<br>3.1.1.1 CMOS Logics<br>3.1.1.2 Circuit Size<br>3.1.1.3 Simulation<br>Power Consumption<br>3.1.2.1 Dynamic Switching Power<br>3.1.2.2 Short Circuit Current Power<br>3.1.2.3 Leakage Current Power<br>al Units<br>Circuit Models<br>Circuit Synthesis<br>Logic and Bit Operation Circuits<br>Addition Circuits                                                                                                         |    |  |  |  |  |  |

|           |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |  |  |  |  |  |

| CHAPTER 3 | THE A  | ARITHMETIC AND LOGIC UNIT HARDWARE                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |  |  |  |  |  |

| 3.1       | CMOS   | 5 Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 24 |  |  |  |  |  |

|           | 3.1.1  | Circuit Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 24 |  |  |  |  |  |

|           |        | 3.1.1.1 CMOS Logics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 24 |  |  |  |  |  |

|           |        | 3.1.1.2 Circuit Size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 26 |  |  |  |  |  |

|           |        | 3.1.1.3 Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 26 |  |  |  |  |  |

|           | 3.1.2  | Power Consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 26 |  |  |  |  |  |

|           |        | 3.1.2.1 Dynamic Switching Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 28 |  |  |  |  |  |

|           |        | 3.1.2.2 Short Circuit Current Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 29 |  |  |  |  |  |

|           |        | 3.1.2.3 Leakage Current Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 31 |  |  |  |  |  |

| 3.2       | Functi | onal Units                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 33 |  |  |  |  |  |

|           | 3.2.1  | Circuit Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 33 |  |  |  |  |  |

|           | 3.2.2  | Circuit Synthesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 34 |  |  |  |  |  |

|           | 3.2.3  | Logic and Bit Operation Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 37 |  |  |  |  |  |

|           | 3.2.4  | Addition Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 38 |  |  |  |  |  |

|           | 3.2.5  | Subtraction Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 42 |  |  |  |  |  |

|           | 3.2.6  | Multiplication Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 44 |  |  |  |  |  |

|           | 3.2.7  | Division Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 47 |  |  |  |  |  |

| 3.3       | Analy  | sis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 51 |  |  |  |  |  |

|           | 3.3.1  | Power Saving                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 51 |  |  |  |  |  |

|           | 3.3.2  | Appeter Summary22E ARITHMETIC AND LOGIC UNIT HARDWARE24IOS Circuits241 Circuit Design243.1.1.1 CMOS Logics243.1.1.2 Circuit Size263.1.1.3 Simulation262 Power Consumption263.1.2.1 Dynamic Switching Power283.1.2.2 Short Circuit Current Power293.1.2.3 Leakage Current Power31actional Units331 Circuit Models332 Circuit Synthesis343 Logic and Bit Operation Circuits374 Addition Circuits385 Subtraction Circuits426 Multiplication Circuits47atysis511 Power Saving512 Optimal Clock Period52 |    |  |  |  |  |  |

|           | 3.3.3  | Area Penalty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 55 |  |  |  |  |  |

| 3.4 | Chapter Summary |

|-----|-----------------|

|     |                 |

#### CHAPTER 4 THE SOFTWARE INSTRUCTION SCHEDULER

| 4.1 | Instru | ction Scheduling             | 57 |

|-----|--------|------------------------------|----|

|     | 4.1.1  | Background                   | 57 |

|     | 4.1.2  | Scheduling Algorithms        | 58 |

|     | 4.1.3  | Performance Optimality       | 59 |

| 4.2 | Softwa | are Instruction Scheduler    | 61 |

|     | 4.2.1  | Introduction                 | 61 |

|     | 4.2.2  | Scheduling Process           | 62 |

|     |        | 4.2.2.1 Initialization Phase | 63 |

|     |        | 4.2.2.2 Scheduling Phase     | 66 |

| 4.3 | Analy  | sis                          | 75 |

|     | 4.3.1  | Good and Bad cases           | 75 |

|     | 4.3.2  | Statistics and Power Savings | 78 |

| 4.4 | Chapt  | er Summary                   | 80 |

|     |        |                              |    |

#### CHAPTER 5 CONCLUSIONS

| 5.1 | Conclusions | 81 |

|-----|-------------|----|

| 5.2 | Future Work | 84 |

APPENDIX 87

#### BIBLIOGRAPHY 97

55

# SUMMARY

The rise of portable devices with wireless network connections has lead to demands on microprocessors to deliver high performance and yet consume low power. This project works on a design for a single-issue 32-bit integer pipelined ALU that comprises two kinds of functional units: one with fast performance and high power consumption and another with slow performance and low power consumption. Both are used to execute instructions, but slow functional units are used whenever possible, for the reason of reducing power consumption.

The ALU architecture comprises a Control Unit, Register File and the mentioned functional units. To make use of this architecture effectively, an offline software instruction scheduler is used to identify and create specific situations for the slow functional unit to be used. The specific situations occur when:

- 1. there are no subsequent instructions depending on the current instruction;

- 2. the current instruction has been scheduled for advanced execution;

- 3. the dependent subsequent instructions are scheduled for a later execution.

When the above situations are identified, slow functional units are used to execute instructions.

However, using two functional units with different levels of performance can cause instruction execution to be in-orderly issued but out-of-orderly executed. As such, instruction execution and retirement have to be properly synchronized to ensure that registers write-backs are performed correctly. This can be achieved by using the Control Unit to synchronize all instruction issues and executions, and updating the Register File at appropriate timings.

The software instruction scheduler mentioned earlier analyzes and rearranges PIns in the programs, resulting in specific situations being identified or created so that slow functional units are used. After analyzing and rearranging the PIns, the scheduler generates two types of directives for the assembler to work with. The first type of directives indicates selected PIns that can be executed with slow functional units. The assembler uses these directives to compile selected PIns with MIns that are executed with the specified slow functional units. The second type of directives indicates stalls in the pipeline caused by unresolvable instruction dependencies. The assembler uses these directives to embed stall information into opcodes, so that the ALU can delay instruction issue appropriately. In this way, delay instructions such as "NOP" are avoided and the power consumed by fetching and executing such instructions is saved.

Therefore, our proposed ALU consumes power for instruction executions only at run time, since there is no other real time activity happening during operation. Hence, it is therefore capable of attaining low power.

# LIST OF TABLES

| Table 3.1  | Synthesis process for behavioural model adder               | 35 |

|------------|-------------------------------------------------------------|----|

| Table 3.2  | Behavioural model adder circuit synthesis                   | 42 |

| Table 3.3  | Behavioural model subtractor circuit synthesis              | 43 |

| Table 3.4  | Behavioural model multiplication circuit synthesis          | 44 |

| Table 3.5  | Multiplication circuits synthesis                           | 46 |

| Table 3.6  | Behavioural model division circuit synthesis                | 48 |

| Table 3.7  | Division circuit synthesis performance                      | 51 |

| Table 3.8  | Functional unit implementation                              | 52 |

| Table 3.9  | Slack computations                                          | 54 |

| Table 3.10 | Average Normalized Slacks                                   | 54 |

| Table 3.11 | Area of ALU                                                 | 55 |

| Table 3.12 | Ratio of circuit area                                       | 55 |

| Table 4.1  | GIn mnemonic descriptions                                   | 65 |

| Table 4.2  | GIn segment for Case 1                                      | 76 |

| Table 4.3  | Program segment for Case 1                                  | 76 |

| Table 4.4  | GIn segment for Case 2                                      | 77 |

| Table 4.5  | Program segment for Case 2                                  | 77 |

| Table 4.6  | GIn segment for Case 3                                      | 78 |

| Table 4.7  | Program segment for Case 3                                  | 78 |

| Table 4.8  | Statistics on tested programs                               | 79 |

| Table 4.9  | Number of instructions assigned to use slow functional unit | 79 |

| Table 4.10 | Estimated power consumption savings                         | 79 |

# LIST OF FIGURES

| Fig. 1    | Instruction execution with slow functional unit             | 8  |

|-----------|-------------------------------------------------------------|----|

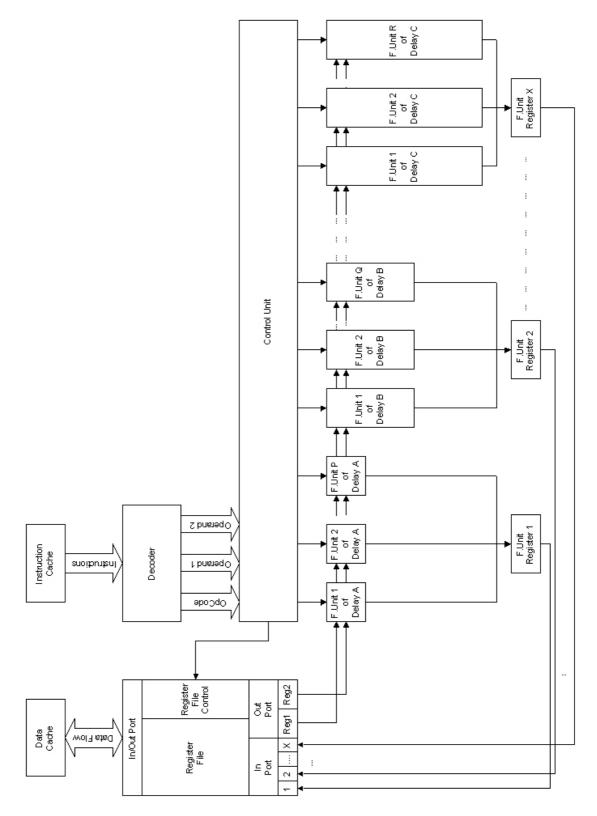

| Fig. 2.1  | ALU Architecture                                            | 13 |

| Fig. 2.2  | MIns concurrent retirement                                  | 19 |

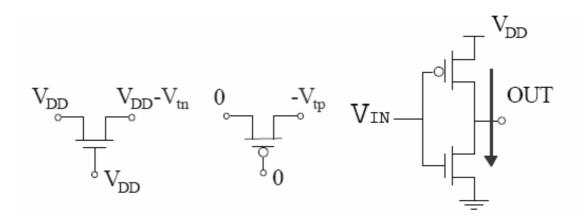

| Fig. 3.1  | Pass transistor (Left and Center) and CMOS circuit (Right)  | 25 |

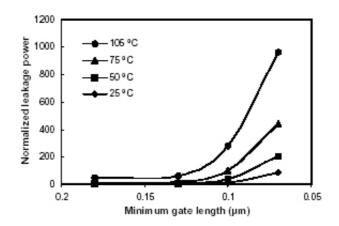

| Fig. 3.2  | Static (leakage) power against channel (gate) length        | 27 |

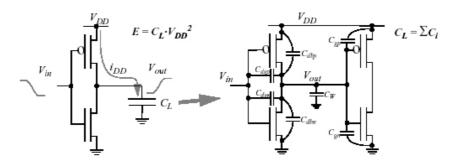

| Fig. 3.3  | Dynamic switching power consumption; sources of capacitance | 28 |

| Fig. 3.4  | Two transistor inverter circuit                             | 30 |

| Fig. 3.5  | Inverter circuit electrical signals                         | 31 |

| Fig. 3.6  | Reverse-bias diodes in CMOS inverter circuit                | 32 |

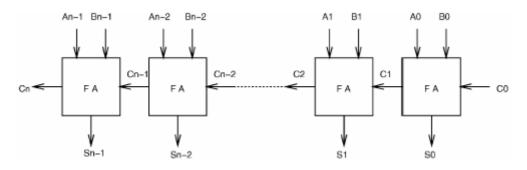

| Fig. 3.7  | Full Adder cell                                             | 39 |

| Fig. 3.8  | Carry Ripple adder design                                   | 39 |

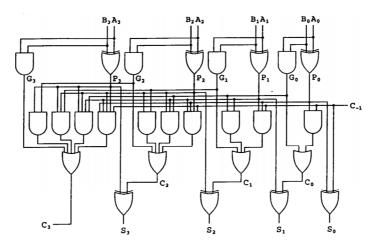

| Fig. 3.9  | 4-bit Carry Look Ahead adder                                | 40 |

| Fig. 3.10 | Behavioral model Carry Ripple adder schematic               | 41 |

| Fig. 3.11 | Behavioral model CLA adder schematic                        | 42 |

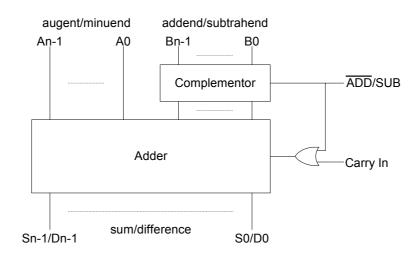

| Fig. 3.12 | Subtraction circuit implementation                          | 43 |

| Fig. 3.13 | Behavioural model multiplier schematic                      | 44 |

| Fig. 3.14 | Simple paper and pencil multiplication algorithm            | 45 |

| Fig. 3.15 | Modified multiplication algorithm                           | 46 |

| Fig. 3.16 | Modified multiplication circuit schematic                   | 46 |

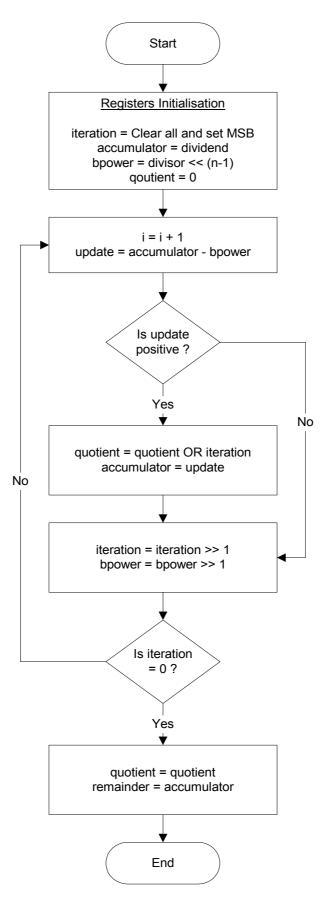

| Fig. 3.17 | Behavioral model division circuit schematic                 | 47 |

| Fig. 3.18 | Non-performing division algorithm                           | 49 |

| Fig. 3.19 | 5-bit non-performing division process                       | 50 |

| Fig. 3.20 | Non-performing division circuit schematic                   | 50 |

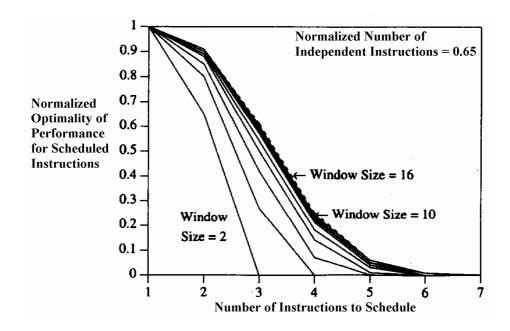

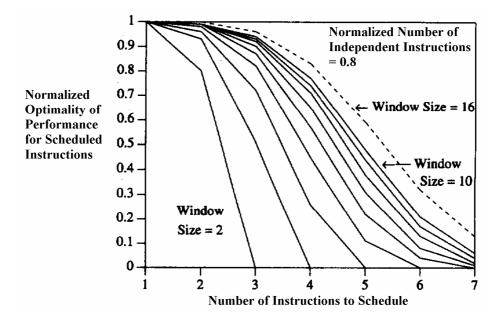

| Fig. 4.1 | Performance optimality with normalized number of independent instruction of 0.65 | 60 |

|----------|----------------------------------------------------------------------------------|----|

| Fig. 4.2 | Performance optimality with normalized number of independent instruction of 0.8  | 61 |

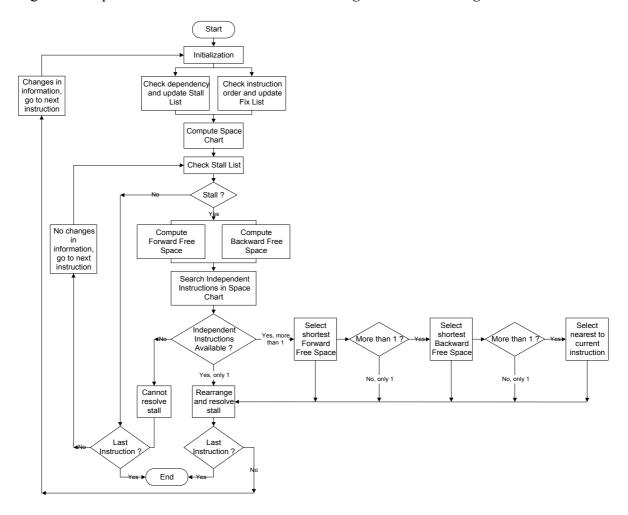

| Fig. 4.3 | Scheduling Phase Interim Algorithm Flow Chart                                    | 69 |

| Fig. 4.4 | Scheduling Phase Final Algorithm Flow Chart                                      | 74 |

# LIST OF SYMBOLS

| $C_{L}$                    | Load Capacitance          |

|----------------------------|---------------------------|

| $\Delta V$                 | Voltage Change            |

| V <sub>DD</sub>            | Supply Voltage            |

| $f_{clk}$                  | Clock Frequency           |

| α                          | Activity Factor           |

| F <sub>0-1</sub>           | Low-to-High Transitions   |

| $V_{Tn}$                   | Threshold Voltage of NMOS |

| $\mathbf{V}_{\mathrm{Tp}}$ | Threshold Voltage of PMOS |

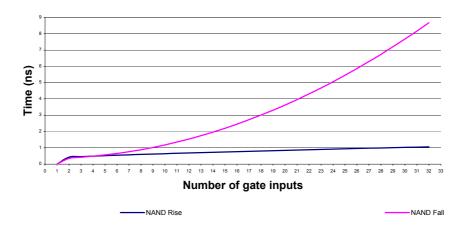

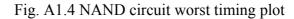

| $T_{WorstRise}$            | Worst Rise Time           |

| T <sub>Worst Fall</sub>    | Worst Fall Time           |

## **CHAPTER 1**

#### **INTRODUCTION**

This chapter is divided into four sections: 1.1 Background, 1.2 Related Work, 1.3 Project Proposal, 1.4 Project Overview and 1.5 Project Scope.

#### 1.1 Background

Portable devices with wireless network connections such as Personal Digital Assistants (PDA), cellular phones and Global Positioning System (GPS) navigators have become increasing popular and widely-used over the past few years. One reason for the widespread adoption is their usability such as a transformation to a graphical interface. The ability for such a transformation has much to do with the high performance microprocessors embedded in them. Not only are the microprocessors expected to execute complicated functions, but they also should sustain reasonably long usage times giving rise to a need for low power consumption. This explains why a lot of research effort and technological developments centre on building microprocessors that can deliver high performance and yet consume minimal power.

In this preceding chapter, we will explore briefly some techniques that have been developed to reduce power consumption in microprocessors. A general understanding of the technological development on this front will foster a clearer understanding of the project's objectives and where our ALU design stands in comparison with the techniques of reducing power consumption in microprocessors.

#### **1.2 Related Work**

Research on low power microprocessors has mainly been concerned with reducing power consumption while maintaining optimum performance levels. There are different techniques of reducing power consumption in microprocessors. Primarily, it is done either by lowering the supply voltage through hardware in conjunction with software support (e.g. Dynamic Voltage Scaling), or by reducing switching activities during runtime operations with an offline software support (e.g. offline intelligent compiler).

The power consumption of a microprocessor is directly proportional to the level of its performance, so the higher its level of performance, the more power the microprocessor consumes and vice versa (full details of microprocessor power consumption are described in Section 3.1). The technology that has been developed to reduce power consumption in a microprocessor works mainly around this relationship.

One problem arises when supply voltage is lowered to reduce power consumption in the microprocessor; the digital circuits in the microprocessor become more susceptible to noise. In order to ensure the proper function of circuits, the decrease of supply voltage has to be concurrent with lowering the clock frequency [1]. However, performance must not be compromised when clock frequency is reduced.

2

The Dynamic Voltage Scaling (DVS), is an example of a previously developed technique which meets this requirement. The DVS technique enables optimum performance in a microprocessor, even when supply voltage is lowered to reduce its power consumption [2, 3]. With this technique, a hardware voltage scheduler controls the supply voltage based on data from a feedback register, while clock frequency is regulated with a voltage-controlled oscillator that tunes the frequency as the supply voltage varies. It is this aspect of the technique that ensures the digital circuits function accurately and performance maintain optimally.

Software support for DVS is in the form of a real time process running on the Operating System, which updates data stored in the feedback register. This real time process monitors the microprocessor performance and computational load based on slack analysis [4, 5, 6, 7]. Depending on the rise or fall of values recorded on the feedback register, the level of computational demand is adjusted accordingly.

An alternative to a real time process is an offline intelligent compiler, which is another form of software support [8, 9, 10]. It is used to identify program regions where application of voltage scaling is required during compilation. The compiler embeds directives into instructions to update the feedback register during runtime operation. Data stored in the feedback register in turn communicates the level of performance required to meet computation demands to the microprocessor. As with the DVS technique, supply voltage and clock frequency is tuned as data is updated, so the microprocessor's optimum performance is maintained while reducing power consumption. Microprocessors designed for portable devices are capable of decreasing supply voltage to reduce power consumption. Some examples of these microprocessors are the ARM11 series and IBM 405LP for portable handheld devices and the Intel Centrino and TransMeta Crusoe series for laptops and notebook personal computers.

In these microprocessors, power consumption reduction also lies in the design of their functional circuits. The functional circuits built into these microprocessors have been specially designed for performance while consuming minimal power. This is evident in the analysis of the circuits' datapath, which reveals how switching activities in these functional circuits have been optimized for low power consumption [11]. Intentionally designed for frequently-used functions like addition [12, 13, 14, 15] and multiplication [16, 17, 18], the circuits are implemented with CMOS logic due to its low power consumption. These two design features of the functional circuits thereby result in switching activities with low power consumption. *More on CMOS logic is described in Section 3.1*.

Software also has a key role in reducing the power consumption of microprocessors. An offline software that is able to analyze programs and rearrange instructions can cut down microprocessor activities like memory accesses and signal switching within circuits to maintain low power consumption [19]. In the case of VLIW based microprocessors, software is commonly used to perform loop unrolling, software cache prefetch and software pipelining on instructions, which reduces pipeline stalls and improves performance of the microprocessor. Drawing on the same approach, software can reduce power consumption by expressly reducing the amount of memory accesses for data fetch [20]. The use of software can also reduce switching activities by rearranging instructions based on Hamming distance [8] and power consumed between instruction transitions [21, 22].

#### **1.3 Project Proposal**

While lowering supply voltage and decreasing the frequency of switching activities are prevalent techniques of reducing power consumption in microprocessors, they also have several disadvantages.

First, while supply voltage reduction effectively lowers power consumption, its application is limited to the functional units in the microprocessor circuits. Moreover, the voltage-reduced circuits require additional interfacing circuits to connect them to other circuits that work with different supply voltages.

Second, with voltage reduction during real time operation, the Operating System is required to update the voltage reduction mechanism frequently. Not only does this eat into overheads required by the microprocessor to compute the real time slacks during runtime, it also consumes extra energy to deliver the computations. On the other hand, offline optimization software activities are performed only during the compilation stage on development machines, and no overheads are incurred during runtime.

The project proposes a design for low power consumption ALU that exploits the benefits of offline software, which can work alone in delivering minimum power consumption or work alongside supply voltage reduction technology to deliver even lower power consumption. Our ALU architecture consists of a set of fast and slow functional units. Fast functional units deliver high performance, but consume a considerable amount of power as they use parallel circuits to carry out computations. Slow functional units on the other hand use simpler circuits to perform computations and consume less energy, but take a longer time to complete the computations.

An instruction scheduler was developed to analyze and rearrange instructions to execute with slow functional units before opcode assembly. The instruction scheduler generates directives for the assembler to assemble opcodes executed with slow functional units during runtime, a feature not available in other microprocessors in the market.

There are many advantages and plus points to the design of our ALU. Not only does it consume minimal power during runtime, it does not require real time process to monitor performance. Neither is a hardware circuit needed to tune the supply voltage. Compared with other models operating on the supply voltage reduction principle, the ALU we have designed is far simpler. This is another boon, because the simplicity in design means voltage reduction techniques can be additionally incorporated into the ALU to further reduce power consumption of the microprocessor.

An overview of the ALU design is described in Section 1.4, with full details on the ALU design is described in Chapter 2.

### 1.4 **Project Overview**

This project works on a design for a single-issue 32-bit integer pipelined ALU that comprises two kinds of functional units: one with fast performance and high power consumption and another with slow performance and low power consumption. Both are used to execute instructions, but slow functional units are used whenever possible, for the reason of reducing power consumption. An instruction scheduler is used to identify and create specific situations for the slow functional unit to be used.

It has been observed that in a conventional pipeline, instructions are usually executed with fast functional units. Data is processed as quickly as possible and instructions are passed down without stalling the pipeline. However, there are situations where fast functional units are not required to execute instructions. These situations occur when:

- 1. there are no subsequent instructions depending on the current instruction;

- 2. the current instruction has been scheduled for advanced execution;

- 3. the dependent subsequent instructions are scheduled for a later execution.

When instructions do not require immediate execution, slow functional units can be used to reduce power consumption without incurring loss in performance. This applies to the ALU design, when the above situations are identified.

However, using two functional units with different levels of performance can cause instruction execution to be in orderly issued but out of orderly executed [23, 24]. As such, instruction execution and retirement have to be properly synchronized to ensure that registers write-backs are performed correctly. Figure 1 shows an example of a situation when slow functional units are used to execute instructions with the following code sample. The pipeline stages used in Figure 1 are "F" for fetch, "D" for decode, "E" for execute and "W" for write-back. For instructions that require more than one execution stage, "En" is used to indicate execution and *n* is an integer that indicates the number of executing stage.

|            | Insti | ructio | ns | Cycles | 0 | 1 | 2 | 3  | 4  | 5  | 6  | 7 | 8 | 9 |

|------------|-------|--------|----|--------|---|---|---|----|----|----|----|---|---|---|

| <b>D</b> ( | Mov   | ax,    | bx | 1      | F | D | Е | W  |    |    |    |   |   |   |

|            | Add   | ax,    | bx | 1      |   | F | D | Е  | W  |    |    |   |   |   |

| Part<br>A  | Push  | bx     |    | 1      |   |   | F | D  | Е  | W  |    |   |   |   |

| A          | And   | bx,    | dx | 1      |   |   |   | F  | D  | Е  | W  |   |   |   |

|            | Mov   | si,    | bx | 1      |   |   |   |    | F  | D  | Е  | W |   |   |

|            | Рор   | bx     |    | 1      |   |   |   |    |    | F  | D  | Е | W |   |

|            |       |        |    |        |   |   |   |    |    |    |    |   |   |   |

|            | Insti | ructio | ns | Cycles | 0 | 1 | 2 | 3  | 4  | 5  | 6  | 7 | 8 | 9 |

|            | Mov   | ax,    | bx | 1      | F | D | Е | W  |    |    |    |   |   |   |

| Dant       | Add   | ax,    | bx | 4      |   | F | D | E1 | E2 | E3 | E4 | W |   |   |

| Part<br>B  | Push  | bx     |    | 1      |   |   | F | D  | E  | W  |    |   |   |   |

| D          | And   | bx,    | dx | 1      |   |   |   | F  | D  | Е  | W  |   |   |   |

|            | Mov   | si,    | bx | 1      |   |   |   |    | F  | D  | Е  | W |   |   |

|            | Рор   | bx     |    | 1      |   |   |   |    |    | F  | D  | Е | W |   |

Fig. 1 Instruction execution with slow functional unit

From Figure 1, Part A shows a conventional pipeline with regular stages for all instruction executions. In Part B, since the "add" instruction is not depended subsequently, it can be executed with slow functional units without affecting the performance or correctness of the program execution. Hence, arithmetic instructions like "add" in the above example can now be implemented with two functional units of different performance. To the programmer, the instructions appear the same since there is no need to know about the underlying instruction execution process. To the ALU, however, all instructions must be unique so the required functional unit is correctly selected for execution. To distinguish instructions for programmer and ALU, the instructions programmers use will be defined as "Programmer's Instructions" or "PIns". Instructions that the ALU executes will be defined as "Machine Instructions" or "MIns".

The software instruction scheduler mentioned earlier analyzes and rearranges PIns in the programs, resulting in specific situations being identified or created so that slow functional units are used. After analyzing and rearranging the PIns, selected PIns that can be executed with slow functional units are marked with directives. The directives inform the assembler to compile these PIns with MIns that are executed with the specified slow functional units.

Our ALU design is therefore capable of attaining low power consumption during runtime with a software instruction scheduler, with the exclusion of real time activities supporting the operation.

### **1.5 Scope of Project**

The scope of this project is to develop a low power ALU, both hardware and software. The ALU hardware development would focus on the fast and slow functional units, and the software development would focus on the development of algorithms to rearrange instructions to execute with slow functional units to achieve low power consumption.

The performance and power consumption of our ALU depends on the functional unit operations. The main focus of this project would be on hardware research and development. The study of power consumption of arithmetic circuit and behavior is carried out through simulation works. Details of the power consumption of the circuits are described in Appendix I. Different arithmetic circuits are modeled and synthesized with different performance levels to study on the variation in performance and power consumption. With which, the appropriate circuit would be selected to implement the functional unit. Details on the hardware development of the functional circuits and a summary on the selected circuits are described in Chapter 3.

The other section of this project would focus on the development of the software algorithm to achieve lower power consumption on the ALU, which would include the rearrangement of the instructions. Research on software scheduling is also carried out prior to the development work. Using the developed software, several programs are analyzed and reduction on power consumption is estimated. Details of the development work and a summary on the program analysis and power consumption estimation are described in Chapter 4.

## 1.6 Thesis Organization

The thesis would be organized in the following order.

Chapter 2 describes the runtime operation, hardware design and software instruction scheduler of our low power 32-bit integer ALU. The runtime operation would describe the method used to achieve lower power with the ALU. Components of the ALU would be presented in the hardware design section. The rearrangement of the instructions for the execution in slow functional units would also be described. A novel method to implement the wait state through rearrangement of software instructions would also be included.

Chapter 3 describes the characteristics of CMOS circuits and the implementation of the 32-bit integer ALU functional units. The power consumption and performance of the circuits will be described in this chapter. Results from the simulation would also be presented and discussed.

Chapter 4 presents the instruction scheduling algorithms used to enhance the performance and reduce power consumption during the ALU runtime. The algorithms at each functional stage would be discussed in detail. Results from the program analysis and power consumption estimation would also be presented and discussed.

Chapter 5 summarizes the research and development work and concludes the project. Possible future work and development would also be recommended.

## CHAPTER 2

## THE ARITHMETIC AND LOGIC UNIT DESIGN

In this chapter, we describe the runtime operation, hardware design and software instruction scheduler of our low power 32-bit integer ALU, explaining how lower power consumption is achieved during the runtime operation. In addition, we will illustrate how instructions are rearranged for the execution in slow functional units and how to implement wait state using embedded information in instructions.

Components of the ALU will be presented in the hardware design section.

## 2.1 ALU Design

Unlike a typical ALU which uses only one type of functional unit to execute a particular PIn, this ALU is capable of using either a fast or a slow functional unit to execute the PIn, depending on the situation. Figure 2.1 shows the ALU hardware architecture.

Given the same clock frequency in performing similar functions, the fast functional unit completes the operation in a shorter time than the slow functional circuit, because it has more logic circuits. However, while it is faster, the fast functional unit also consumes more power during the operation compared with the slow functional unit, which takes a longer time for the same operation, but consumes less power.

Fig. 2.1 ALU Architecture

The amount of time a functional unit takes to perform an operation is specified in term of number of clock cycles. Different functional units require a different number of clock cycles to perform their operations. As such, the PIns are issued in order from the Control Unit but may be completed in a different order.

With our ALU design structure, a software instruction scheduler analyses an input program and selects a suitable functional unit to perform the PIns. This differentiating feature in the structure of our ALU ensures power-efficient runtime without causing loss in performance.

In processors that use the conventional ALU, PIns are compiled into MIns by an assembler, with one MIn mapped to one PIn. When the proposed ALU is employed in processors, PIns may be realized with different MIns, which in turn trigger different functional units to perform the PIns.

The task of mapping of MIns to PIns for this proposed ALU is achieved with a software instruction scheduler. The scheduler analyzes the independence of PIns in the program and performs the mapping based on performance or power consumption criteria. The ultimate objective is to sustain optimal performance in the microprocessor while consuming minimal power. Optimal performance in achieved when there are no stalls in the pipeline during runtime while low power consumption is attained when slow functional units are used to execute PIns for most of the operations.

Before the scheduler performs its task, the PIns are analyzed and divided into segments, based on the control flow of the programs. Control PIns are used to mark the start and end points of segments. Within the segments, the PIns are reordered to ensure that the control flow of the PIns is correct after reordering. The objective of reordering the PIns is to work around constraints due to dependencies in PIns to enhance performance and reduce power consumption at runtime. After the scheduler has worked on the PIns, a list of directives is generated for the assembler to map MIns to PIns with the appropriate functional units.

The function of the hardware components and software scheduler are described in the following sections.

#### 2.2 Hardware Components

The hardware architecture is designed to be lean and simple. It consists of a Decode and Control Unit, Register File and several functional units of different performance levels. With this architecture, power is consumed during the operation of the Decode and Control Unit for MIns issue, Register File write-backs and when functional units are enabled by the Control Unit for MIns execution. The components and their functions are described as follows.

#### 2.2.1 Decode and Control Unit

The Decode Unit is responsible for fetching and interpreting MIns from the memory system before passing them on to the Control Unit. The Control Unit is designed to be a simple state machine that synchronizes the ALU activities like any other Control Unit in conventional microprocessors. It is responsible for issuing the MIns for execution and synchronizing register write-back for MIns that are orderly issued, but are executed out of order, because functional units of different performance levels are used.

At every clock cycle during runtime, the Decode Unit reads the MIns and relays relevant information like register operands and the functional unit required to the Control Unit. The Control Unit in turn triggers the appropriate functional unit, selects the required registers in the Register File and places the register contents on the input bus of the functional units. When MIns are executed with functional units requiring more than one clock cycle, the following happens: the Control Unit synchronizes MIns executions and register write-backs between the functional units and Register File. It does this by deferring write-backs for the number of clock cycles that the functional units require to run.

For the unused functional units, the clock signal is gated off. These functional units are thus in static state. However, because CMOS circuits are used in the functional units, static power consumption is negligible. An analysis of CMOS circuit power consumption is described in Appendix I.

#### 2.2.2 Functional Units

The functional units are circuit blocks that operated on integer data stored in the Register File. The Control Unit selects the registers and the stored data for the functional units to perform the operations for a particular MIn.

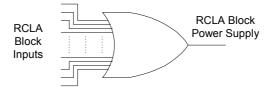

As shown in Figure 2.1, the functional units are organized such that units requiring the same amount of time (in terms of number of clock cycles) to perform their operations are grouped together. In a conventional ALU, each functional unit has a register to store the processed data. However, with the proposed ALU, each group of functional units shares a register to store processed data. Therefore, there are fewer registers required in the ALU to support the functional units. Registers used to store processed data for a group of functional units are called the Common Output Registers.

Even though there is only one Common Output Register available to several functional units within a group, conflicts would not arise when the functional units attempt to write to this register, as the Control Unit issues only one instruction every clock cycle. The workings of the functional unit circuits are described in Chapter 3.

#### 2.2.3 Register File

The Register File control reads selected registers and places the contents on the functional units' input bus. The Control Unit in turn issues instructions and updates selected registers with the content in the Common Output Registers.

The Register File comprises these components:

- 1. Registers that are available to the programmers,

- 2. An in-port for updating the registers,

- An out-port for placing selected register contents on the functional units' input bus,

4. And control circuits that select registers for reading or writing via control signals from the Control Unit.

The Register File is designed to perform multiple register writes within a clock cycle. Because functional units of different performance levels are used, MIns may be orderly issued but may be completed out of order. And when MIns are completed out of order, this allows for several MIns to be concurrently executed within a clock cycle. As such, the Register File must be able to perform multiple register write-backs within a clock cycle, so that the executed MIns are properly retired.

Figure 2.2 illustrates an example of such situations in a pipeline:

Part A shows a regular 4-stage pipeline where only one instruction retires in every clock cycle.

Part B and C show pipeline cases with functional units with operation time that is longer than 1 clock cycle. In Part B, the pipeline has execution stages that vary between 1 to 2 clock cycles. It is observed that for the worst case, there were 2 instructions retiring within a clock cycle. In Part C, the pipeline has execution stages that vary between 1 to 3 clock cycles. In the worst case scenario observed, 3 instructions retired within a clock cycle.

In general, we observed that in functional units requiring different lengths of operation time (measured in number of clock cycles), the maximum number of instructions that retire simultaneously within a clock cycle, n, is equal to the operation time (measured in number of clock cycles) of the slowest functional unit.

When a worst-case situation like this occurs, all the Common Output Registers in the ALU will be updated with the processed data from the functional units. The Register File must also update *n* registers respectively within that clock cycle.

|        | Cycles | 0 | 1 | 2 | 3 | 4  | 5  | 6  | 7  | 8  | 9 | 10 |

|--------|--------|---|---|---|---|----|----|----|----|----|---|----|

| Part A | 1      | F | D | Ε | W |    |    |    |    |    |   |    |

|        | 1      |   | F | D | Е | W  |    |    |    |    |   |    |

|        | 1      |   |   | F | D | Е  | W  |    |    |    |   |    |

|        | 1      |   |   |   | F | D  | Е  | W  |    |    |   |    |

|        | 1      |   |   |   |   | F  | D  | Е  | W  |    |   |    |

|        |        |   |   |   |   |    |    |    |    |    |   |    |

| Part B | 1      | F | D | Е | W |    |    |    |    |    |   |    |

|        | 1      |   | F | D | Е | W  |    |    |    |    |   |    |

|        | 2      |   |   | F | D | E1 | E2 | W  |    |    |   |    |

|        | 2      |   |   |   | F | D  | E1 | E2 | W  |    |   |    |

|        | 1      |   |   |   |   | F  | D  | Е  | W  |    |   |    |

|        | 1      |   |   |   |   |    | F  | D  | Е  | W  |   |    |

|        | 1      |   |   |   |   |    |    | F  | D  | Е  | W |    |

|        | 1      |   |   |   |   |    |    |    | F  | D  | Е | W  |

|        |        |   |   |   |   |    |    |    |    |    |   |    |

| Part C | 1      | F | D | Е | W |    |    |    |    |    |   |    |

|        | 1      |   | F | D | Е | W  |    |    |    |    |   |    |

|        | 2      |   |   | F | D | E1 | E2 | W  |    |    |   |    |

|        | 3      |   |   |   | F | D  | E1 | E2 | E3 | W  |   |    |

|        | 3      |   |   |   |   | F  | D  | E1 | E2 | E3 | W |    |

|        | 2      |   |   |   |   |    | F  | D  | E1 | E2 | W |    |

|        | 1      |   |   |   |   |    |    | F  | D  | Е  | W |    |

|        | 1      |   |   |   |   |    |    |    | F  | D  | Е | W  |

Fig. 2.2 MIns concurrent retirement

Multiple writes within the Register File may be implemented using multiple ports for the registers [26] or multiple banks of registers [27]. However, multiple writes within the Register File can be simpler using one port and bus for the registers, by implementing very fast writes in sequence.

For example, if one register-to-register write operation requires 3ns to perform, then a maximum of three registers can be updated sequentially within a clock cycle of 10ns

with a bus in the Register File. If the registers are implemented with two ports, six registers can be updated within the same write operation time and clock cycle.

#### 2.3 Software Instruction Scheduler

In conventional ALU, hardware circuits like Reservation Stations and Scoreboard Logics [28] are used during runtime to maintain peak performance, while the Dynamic Voltage Scaling [29] system is used to reduce power consumption. The proposed ALU system, however, does not employ these complicated hardware circuits. In place of these, is an offline software instruction scheduler.

The scheduler's objective is to ensure that PIns are rearranged offline to use the slow functional units that consume low power, without suffering any penalty in performance. A list of directives is generated by the scheduler to map PIns with appropriate MIns, as seen in the scheduling results.

Before the scheduler works on the PIns, the PIns pass through a conditioning phase in preparation for the scheduling. During this phase, empty lines and comments are removed from the PIns and they are segmented based on the control flow of the programs. Control PIns mark the start and end points of the segments. Within segments, the PIns are reordered to ensure that the control flow of the PIns is correct after reordering. After segmentation, the PIns are translated into a generic form that the scheduler recognizes.

The scheduler works on the PIns in two phases. In the first phase, the scheduler removes data hazards among the PIns that may stall the pipeline. It does this by

analyzing data dependencies among the PIns. When data dependencies are found, the PIns are reordered with the assumption that all functional units require only one clock cycle to execute. This ensures that the PIns are pre-scheduled for optimal performance, before the scheduler proceeds to work, under power-efficient conditions.

In the second phase, the scheduler reanalyzes the pre-scheduled PIns to correct the assumption in first phase. The pre-scheduled PIns are reordered again using the correct number of clock cycles that the functional units required. With this step – analyzing dependencies and reordering the PIns – in place, the scheduler creates or identifies the situations mentioned in Section 1.3, to ensure that slow functional units are used.

When any of the mentioned situations are either found or created, directives will be generated with the scheduling results to provide information for the assembler. The implementation of the software instruction scheduler is described in Chapter 4.

#### 2.3.1 Avoiding Hazards with Wait States

Wait states are still required on occasion to resolve pipeline hazards – even though the scheduler is mainly responsible for this task, which it achieves by reordering the PIns. These exceptions occur when the PIns happen to depend closely on each other, or when there are insufficient independent instructions available for reordering to avoid pipeline hazards. An example of a PIn commonly used in such situations, is the "NOP", which is found in Intel processors.

The "NOP" is technically an empty instruction as nothing is accomplished with its execution. But like other instructions, it is processed as per normal – fetched from memory, decoded and issued by the Control Unit and executed as "XCHG AX, AX", as in the case of Intel processors. As such, power [30] is still consumed in the process of fetch, decode, issue and execution of the "NOP" PIn.

An alternative method of resolving pipeline hazards, without incurring power consumption, is to implement the delay without explicitly using the "NOP" instruction.

Under the assumption that there are available unused bits in the MIns, the scheduler will generate delay directives for the assembler – when the scheduler detects unresolvable pipeline hazards in the PIns. Upon receiving the delay directives, the assembler embeds delay information [31] into MIns for the stalled PIns.

After the Decode Unit deciphers this delay information, it relays signals to the Control Unit to cease issuing MIns for the required number of clock cycles as indicated by the delay information.

This achieves the effect of using the "NOP" instruction in the implementation of wait states, without incurring power for fetching, decoding and executing it.

#### 2.4 Chapter Summary

The components used in the design of the proposed ALU differentiate it from conventional ALU. Conventional ALU use hardware circuits like Reservation Stations and Scoreboard Logics [28] to sustain peak performance during runtime and Dynamic Voltage Scaling to reduce power consumption.

With the proposed ALU design, both fast and slow functional units are used to execute MIns, along with a Control Unit and a Register File to support simultaneous retirement of instructions during runtime operation.

To achieve low power consumption, PIns are arranged to use slow functional units for execution of PIns, without affecting performance. In place of hardware circuits, a software instruction scheduler is developed to analyze and rearrange PIns to be executed with slow functional units.

The analysis by the software instruction scheduler will reveal how closely dependent the PIns are on each other, and whether wait states are necessary to resolve dependencies. Should delays be required, the necessary information will be embedded in the MIns, and subsequently be decoded by the Control Unit. As such, delay PIns like "NOP" that consume unnecessary power are avoided.

These components in the proposed ALU design differentiate it from conventional ALU, enabling it to sustain optimal performance at low power consumption.

## CHAPTER 3

## THE ARITHMETIC AND LOGIC UNIT HARDWARE

In this chapter, we will describe the characteristics of CMOS circuits and the implementation of the 32-bit integer ALU functional units. We will also discuss the results of the simulations conducted. Specifically, we will talk about the power consumption and performance of the circuits

### **3.1 CMOS Circuits**

The functional units used in the ALU are implemented with CMOS circuits, which are widely used in low power consumption designs [32]. In the following sections, we will briefly describe the characteristics of CMOS circuits as well as their power consumption behaviour.

#### 3.1.1 Circuit Design

#### 3.1.1.1 CMOS Logic

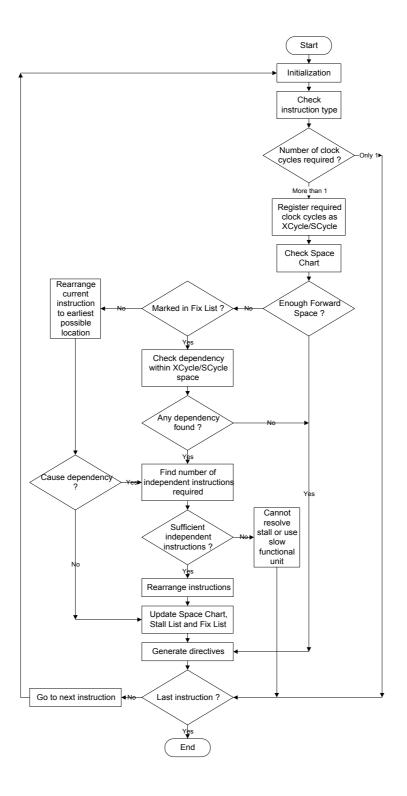

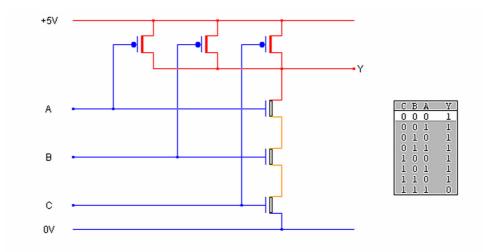

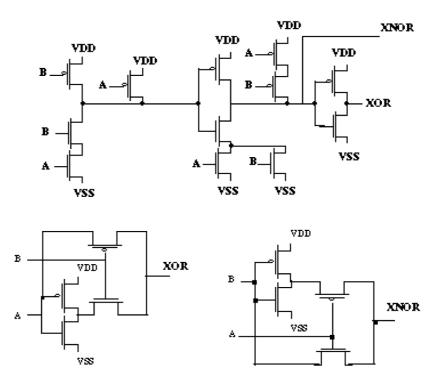

CMOS circuits use both N-type and P-type MOSFETs (Metal Oxide Semiconductor Field Effect Transistors) to realize logic functions. Figure 3.1 shows some basic circuits for CMOS and Pass transistor logic.

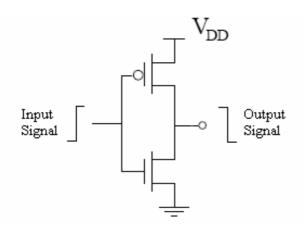

Fig. 3.1 Pass transistor (left and center) and CMOS circuit (right)

Pass transistor logic uses either a NMOS or PMOS (see Figure 3.1, left and center circuit) as a switch to gate electrical signals. Input signal is connected to the transistor gate to create a conductive channel to pass the signal that is connected to the source. This caused a threshold voltage drop across the conducted signal and the output logic signal is degraded [33]. Degraded logic signals may cause the subsequent connected circuits to consume static power due to subthreshold conduction (more details is covered in Appendix Section A1.2).

Contrary to pass transistor logic circuits, CMOS circuits (see Figure 3.1, right circuit) generate rail-to-rail output signals. CMOS circuits use NMOS as pull-down and PMOS as pull-up devices in the logic network. With appropriate input signals connected to the transistor gate, the PMOS transistor charge up output load to the supply voltage level and the NMOS transistor discharge the output load to the ground. As such, CMOS circuits do not incur static power consumption as much as the pass transistor logic circuits. This makes CMOS circuits more suitable for low power circuit designs.

## 3.1.1.2 Circuit Size

Due to both PMOS and NMOS transistors are used to realize digital logic functions, there are usually a large number of transistors in CMOS circuits. In particular, when many transistors are connected serially in the circuit the parasitic capacitance in the signal path increases. In turn, this increases delay the of the output signal. To counter this problem, buffers or inverters are added along the signal path to increase output drive and reduce the delay. However, this further increases the transistor count in the circuits and the circuit size becomes larger.

## 3.1.1.3 Simulation

Signal delays in CMOS circuits can be accurately simulated with various delay models and equations. The output signal delay of CMOS circuits may be expressed as a function of the intrinsic delay, parasitic capacitance and load capacitance. The intrinsic delay is determined by parameters in the transistor fabrication process as well as operating conditions. The load capacitance is dependent on the circuit design, while the parasitic capacitance is the sum of the gate capacitance of other connected transistors. In addition to signal delays, power consumption can also be accurately simulated with models and equations.

#### **3.1.2 Power Consumption**

There are three types of power consumption in CMOS circuits: dynamic switching power, short circuit power and leakage current power.

Dynamic switching power occurs when load and parasitic capacitances in the circuit are changed or delayed as a result of changes in states. It is the dominant component in CMOS circuit power consumption. Short-circuit current power is energy consumed as a result of the finite turnover time between the rise and fall of input signals. In the third aspect of CMOS circuit power consumption, power is consumed when current leaks through reverse-biased diodes or via sub-threshold conductions.

CMOS circuits have lower power consumption compared with NMOS or bipolar transistor circuits. While NMOS and bipolar junction transistor circuits consume power even when signals are not switching, static (leakage) power consumption for CMOS circuits can be negligible, depending on the channel length of the MOSFETs.

For channel length larger than 0.15um, static power consumption is negligible. For channel length smaller than 0.15um, static power consumption increase exponentially with decreasing channel length. Figure 3.2 shows a simulated plot for static power through an inverter circuit against decreasing channel (gate) length [34].

Fig. 3.2 Static (leakage) power against channel (gate) length

Extracted from [34], Figure 1 of "Drowsy caches: simple techniques for reducing leakage power" by Krisztian Flautner et al

When channel length is below 0.15um, the leakage current consists of subthreshold leakage, reverse-bias diode leakage, gate leakage and other smaller leakage components. With such a short channel length, the subthreshold (source/drain)

leakage and reverse-bias diode (drain/substrate) leakage current are amplified by the short channel effects and lower threshold voltage respectively [35].

In general cases, the leakage current is dominated by the subthreshold leakage because the depletion layers at the source and drain could be very close to each other due to short gate channel length. However, for advanced technology devices, where gate oxide thickness is very thin (1.8nm or below), gate leakage can dominate the leakage current.

We describe in greater details the three aspects of CMOS circuit power consumption in the following sub sections:

## 3.1.2.1 Dynamic Switching Power

For every low-to-high output signal transition in the circuits, a voltage change of  $\Delta V$  occurs across the output load capacitance  $C_L$ . To effect this change, energy equivalent to  $C_L \Delta V V_{DD}$  joules needs to be drawn from the supply voltage  $V_{DD}$ . On the other hand, a high-to-low output signal transition results in the energy stored on  $C_L$  to be dissipated into the NMOS transistors and pulls the output low. Figure 3.3 shows the various sources of capacitance seen in an inverter circuit.

Fig. 3.3 Dynamic switching power consumption; sources of capacitance Extracted from [1], Figure 2.3 of "Energy-Efficient Processor System Design" by Thomas D. Burd

The basic capacitor elements of  $C_L$  shown in Figure 3.3, consists of the gate capacitance of subsequent inputs attached to the inverter output ( $C_{gp}$ ,  $C_{gn}$ ), interconnect capacitance ( $C_W$ ), and the diffusion capacitance on the drains of the inverter transistors ( $C_{dbp}$ ,  $C_{dbn}$ ,  $C_{dgp}$ ,  $C_{dgn}$ ) [1].

The dynamic switching power consumption is the product of the energy consumed per transition at the rate of low-to-high transitions,  $F_{0-1}$ . The value of  $F_{0-1}$  is usually difficult to quantify as it is dependent on the state of the system and the input test vectors. In the absence of a transistor-level circuit simulation,  $F_{0-1}$  can be calculated via statistical analysis of the circuit, or by using a high-level behavioural model with benchmark software to determine a mean value.

Since most digital CMOS circuits are synchronous with a clock frequency  $f_{clk}$ ; an activity factor,  $0 < \alpha < 1$ , is used to denote the average fraction of clock cycles in which a low-to-high transition occurs, such that  $F_{0-1} = \alpha f_{clk}$ . For a circuit with N switching nodes, the dynamic switching power can generally be expressed as,

Dynamic Switching Power =  $V_{DD} f_{clk} \sum_{i=1}^{N} \alpha_i C_{Li} \Delta V_i$  .....(Eq. 1) From the equation, dynamic switching power may be lowered by reducing  $V_{DD}$ . As mentioned in Chapter 1, if  $V_{DD}$  is reduced, the operating  $f_{clk}$  must be proportionally reduced, as signals in the circuits become more susceptible to noise interference.

#### 3.1.2.2 Short-Circuit Current Power

Short-circuit current power consumption occurs when the output signal of the CMOS circuit is transitioning, while the input signal is still in the middle of transition.

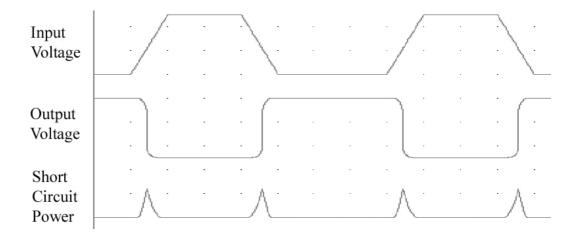

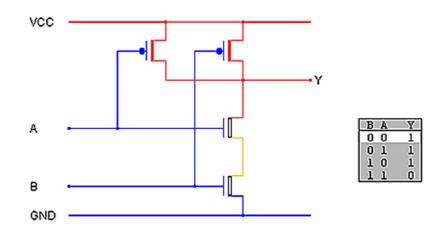

Figure 3.4 Two transistor inverter circuit

In an ideal inverter circuit shown in Figure 3.4, when a step input is given, the PMOS and NMOS transistors should switch states immediately with one turned on and the other turned off. This inhibits the conduction of power from  $V_{DD}$  to the ground through the transistors and eliminates short circuit power consumption.

However, in real circuits, parasitic capacitance exists along the signal path. This causes the input signals to have a finite rise and fall time. As long as the conditions  $V_{Tn} < V_{in} < V_{DD}$  -  $|V_{Tp}|$  and  $0 < V_{out} < V_{DD}$  remain in place for the input and output signals, a conductive path will connect  $V_{DD}$  to the ground as both PMOS and NMOS transistors are turned on. The slower the rise and fall times of the input signal, the longer the short-circuit current will continue to flow.

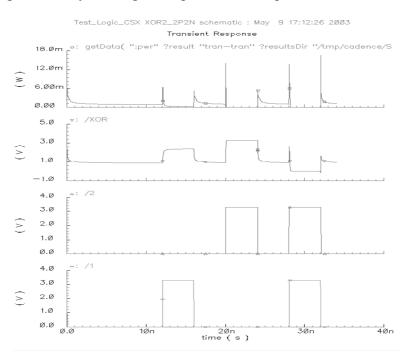

Figure 3.5 shows a plot for following signals from a switching inverter circuit shown in Figure 3.4. From the plot, the horizontal axis indicates time and the vertical axis indicate the magnitude of voltage or power for the respective signals.

Fig. 3.5 Inverter circuit electrical signals

From Figure 3.5, we can observe short circuit power occurring around every signal transitions.

Short-circuit power consumption scales along with  $V_{DD}$ . Theoretically, it can be eliminated if  $V_{DD}$  is lowered to the point below the sum of the thresholds of the transistors,  $V_{DD} < V_{Tn} + |V_{Tp}|$  because both PMOS and NMOS cannot be turned on at the same time.

## 3.1.2.3 Leakage Current Power

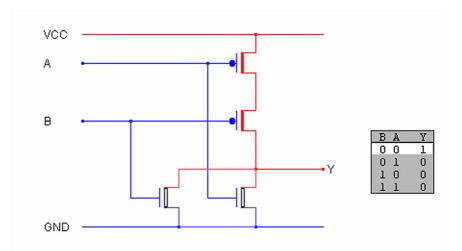

The current leakages in CMOS circuits are due to the reverse-bias diode leakage and sub-threshold leakage through the channel of a MOSFET that is turned off. The magnitude of these currents is set predominantly by the processing technology and total number of transistors.

#### Reverse-bias diode leakage

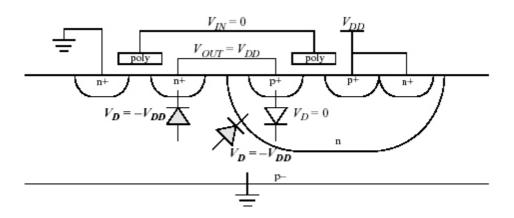

Diode leakage occurs when one transistor is turned off, and another active transistor charges up, or down, the drain with respect to the former's bulk potential. For a static CMOS inverter cross-section shown in Figure 3.6, with a low input voltage, the

output voltage will be high because the PMOS transistor is on. The NMOS transistor will be turned off, but its bulk-to-drain voltage will be equal to the supply voltage, *-VDD*. The resulting diode leakage current will be approximately  $I_{LD} = A_D J_{SD}$ , where  $A_D$  is the area of the drain diffusion, and  $J_{SD}$  is the leakage current density of the diffusion, set by the fabrication process technology.

Fig. 3.6 Reverse-bias diodes in CMOS inverter circuit

Extracted from [1], Figure 2.5 of "Energy-Efficient Processor System Design" by Thomas D. Burd

Since the diode reaches maximum reverse-bias current for relatively small reversebias potential (< 100mV), the leakage current is roughly independent of supply voltage.

In an nwell process, such as that depicted in Figure 3.6, the nwell-substrate reversebiased diode also has leakage current. Since a diode leakage current is primarily determined by the more lightly doped side of the junction, which is the p- substrate, the leakage current density is similar to that of the NMOS drain-substrate diode [36]. Because the well area,  $A_W$ , is an order of magnitude larger than the diffusion area, this current will dominate reverse-biased diode leakage in an n-well process. The current is  $I_{LW} = A_W.J_{SW}$ , where  $J_{SW}$  is the leakage current density of the well, also set by the technology. Subthreshold leakage

Subthreshold leakage occurs under similar conditions as the diode leakage. In Figure 3.6, the NMOS was turned off, but even for  $V_{GS} = 0$ V, there is still current flowing in the channel due to the  $V_{DS}$  potential of  $V_{DD}$ .

The magnitude of the subthreshold current is both a function of process, device sizing (W/L), and supply voltage [37]. The process parameter that predominantly affects the current value is  $V_T$ . Reducing  $V_T$  exponentially increases the subthreshold current, which to first order, is proportional to  $V_{DS}$ , or equivalently,  $V_{DD}$ .

## **3.2 Functional Units**

## 3.2.1 Circuit Models

The proposed ALU consists of functional units that perform logic, bit and arithmetic operations. Depending on the design, these functional units are either implemented with either high-performance complex logic that has high-power consumption circuits or simpler low-performance that has low-power consumption circuits.

The circuit design for the functional units may be described with behavioural, structural or hybrid models in Register Transfer Language (RTL) style using Verilog [38]. Behavioural models describe the functions of circuits using synthesizable Verilog function operators, while structural models describe the logical structure of the circuits using logic functions. In another words, the behavioural model can be seen as a high level description of the circuit model, while the structural model is a low level description.

Behavioural model is useful when designs can be described with synthesizable Verilog operators, instead of expressing the designs using primitive logic operators like AND, OR and XOR. In some cases, different parts of the design can be described with behavioural and structural model. Such circuit modelling approach is termed as the hybrid model.

Structural models are used to describe the logic operation circuits, since their design is simple and consists only of logic gates and registers. Behavioural models are used to describe bit operation circuits using the bit operators in Verilog as they are more complicated. The design of arithmetic circuits range from simple circuits to highly complicated logic networks. As such, the behavioural, structural and hybrid models are all used to describe different types of arithmetic circuits.

The performance and power consumption of the synthesized circuits depends on both the circuit design and the technology of the standard cell library. The circuit design determines the complexity of the circuit and in turn the number of logic components (from the standard cell library) required to realize the design. Each logic component has its own performance and power consumption. As such, the performance and power consumption of the synthesized circuit is computed based on the logic components used in the circuit.

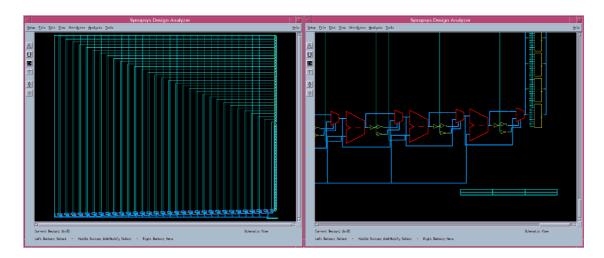

## 3.2.2 Circuit Synthesis

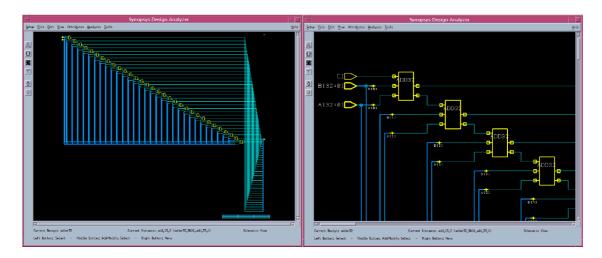

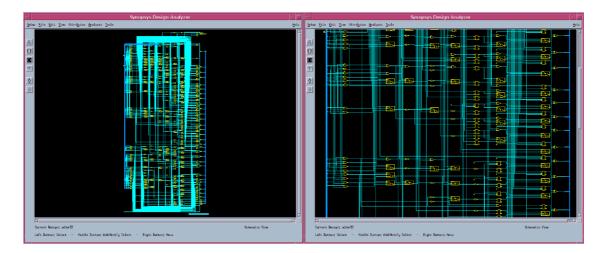

The circuits for the functional units are synthesized with the Synopsis Design Analyzer using the C35 0.35um CMOS standard cell library – the technology available at the time of development. The Synopsis Design Analyzer has different circuit-optimizing options to fulfil different requirements of performance or power consumption. These options are used along with a set of clock constraints to synthesize the circuit models to obtain circuits of different performance and power consumption level. The set of clock constraints ranged from 100ns up to the maximum performance limit of each model.

Clock constraint defines the amount of time in which the circuit is bound to deliver computation results. The inverse of the clock constraint is the operating clock frequency for the circuit. Thus, as clock constraint is shortened, the synthesized circuits run on a faster operating clock frequency. Depending on the level at which it is set, the circuits are synthesized to a performance point that is sufficient to meet the clock constraint.

Table 3.1 shows a summary on the circuit information obtained from synthesizing the behavioural addition circuit model with a range of clock constraints.

| <b>Clock Constraints</b> | 100ns | 50ns  | 25ns  | 10ns    | 5ns     |

|--------------------------|-------|-------|-------|---------|---------|

| Area (um <sup>2</sup> )  | 24156 | 24156 | 24156 | 51541.4 | 63654.6 |

| Dynamic Power (mW)       | 0.23  | 0.46  | 0.92  | 4.45    | 11.21   |

| Normalized Power (mW)    | 0.23  | 0.23  | 0.23  | 0.44    | 0.56    |

| Data Arrival (ns)        | 12    | 12    | 12    | 4.87    | 3.77    |

Table 3.1 Synthesis process for behavioural model adder

In Table 3.1, Area indicates the required circuit size on the silicon die. Performance is reflected in the Data Arrival measurements – it indicates the time the circuit takes to deliver computations. Dynamic Power indicates the circuit's power consumption.

From the observations on Table 3.1, circuits synthesized with clock constraints at 100ns, 50ns and 25ns have equal circuit areas and performance levels. This implies that the same circuit is synthesized for all three clock constraints, since this circuit performance meets the requirements. On the other hand, power consumption is observed to increase proportionally as the clock constraints get shorter. For example, the power consumption for 50ns is twice the power consumption for 100ns, while for 25ns it is four times the power consumption for 100ns.

From the datasheets of the logic components [39], power consumption is provided as micro Watts per MHz. This implies that power consumption is proportional to operating clock frequency. Thus, it explains the proportional difference in power consumption between circuits synthesized with clock constraints at 25ns and 100ns.

For clock constraints at 10n and 5ns, different circuits are synthesized to meet the requirement. In general, these circuits have larger size as there are more components used to execute parallel functions to speed up performance, but consume more power during operation.

The power consumption recorded in Table 3.1 is obtained from synthesizing circuits at different clock constraints. In order to provide a fair comparison among different circuits, it should be normalized based on a common clock constraint. Normalized power can be computed as follow,

divide the 100ns (common clock constraint) by the applied clock constraint to obtain a power factor,  then divide the Dynamic Power by the power factor to obtain the normalized power.

In another words, the normalized power indicates the power consumption for operating the circuit with the common clock constraint at 100ns. The reason for using 100ns as the common clock constraint is the ease of computation and also it is the lowest clock constraint in the range used to synthesize the circuit models.

Although the circuits are being compared based on the common clock constraint, the performance figure for the circuits are still valid. This can be proven from the performance of circuits synthesized with clock constraint at 100ns, 50ns and 25ns - which the performance of the circuits does not change regardless of the clock constraint applied. Hence, we can compare the synthesized circuits based on normalized power and performance, for selecting appropriate circuits to implement the functional units.

## 3.2.3 Logic and Bit Operation Circuits