# RELIABILITY MODELING OF ULTRA-THIN GATE OXIDE AND HIGH-K DIELECTRICS FOR NANO-SCALE CMOS DEVICES

LOH WEI YIP

B. Eng (Hons), NUS

# A THESIS SUBMITTED FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

NATIONAL UNIVERSITY OF SINGAPORE

2004

# Acknowledgments

First and foremost, my deepest gratitude to my supervisors, Associate Professor Cho Byung Jin and Professor Li Ming Fu, who have given me guidance throughout my study in NUS. In particular, it is Assoc. Prof. Cho who have aspired me to reach for the highest standard in my researches and who have tirelessly reviewed and guided me in all my publications. It is with his help that I am able to produce credible results in the area of oxide and high-*K* reliability. Gratitude also goes to Prof. Li, who because of his insight and theoretical expertise is able to guide me to seek for a more theoretical understanding in all my researches. Without Assoc. Prof. Cho and Prof. Li's kind and patient guidance, it would be difficult for me to have completed this thesis.

The advices and guidance of other teaching staffs are also gratefully acknowledged. In particular, Prof. Kwong DL, Assoc. Prof. Yoo WJ, Dr. Zhu CX, Dr Lee SJ, Dr. Yeo YC and Mr. Joo MS, have all given me tremendous help, advices and encouragements. I also wish to express my sincere gratitude to my fellow students in Silicon Nano Device Lab. (SNDL) and Center for Integrated Circuits Failure Analysis and Reliability (CICFAR) who have make my stay in NUS a joyful and meaningful experience. In particular, it is most gratifying to have the support and friendship of Mr. Kim Sun Jung who has so willing lend a helpful hand in all my experiments and Dr. Lim Peng Soon who has joined me in many fruitful discussions in both work and social matters. Thanks also go to all my friends including Wu Nan, Ren Chi, Tony Low, Chee Keong, Ng TH, Zerlinda, Tan KM, Chen JH, Wang YQ, Yu HY, Whang SJ, Park CS, and many others who have went out of their way to teach and assist me in this thesis.

The support and assistance from all the staffs of SNDL and NUS is also gratefully acknowledged. In particular, Mr. Patrick Tang, Mr. Yong Yu Foo, Mr. Goh Thiam Pheng, Mrs. Ho Chiow Mooi, and Mr. Walter Lim have greatly assisted me in all manners of my administrative duties and experiments. Their kind assistances are greatly appreciated.

Last but not least, I wish to dedicate this thesis to my parents, sister, Sook Fen and Gabriel and my dearest Tze Chieg. Without their emotional support, care and concerns, and continuous support and love, I would not have the privilege to even embark on this journey of my life.

# Summary

As complementary metal-oxide semiconductor (CMOS) technology advances, the dimensions of its various key device components are scaled downward, from its present day micrometer range and eventually, to its ultimate limit - the nanometer regime. In this aspect, silicon dioxide (SiO<sub>2</sub>), which forms the gate insulator for the transistor, is progressively reduced from thick to thin oxide (< 20 Å), ultra-thin (<15 Å) and eventually to high-K dielectrics. For high performance logic applications, gate oxide thickness scaling is driven by the need for higher switching speed, transistor drive current and minimization of short channel effects. However, as gate oxide scales to sub-5 nm regime, various reliability phenomena have become increasing prevalent and critical. Quasi-breakdown (QB), which is prevalent in sub-5 nm gate oxides, has become an increasing concern due to its significant impact at low gate voltage and signal noise increases. In the ultra-thin (< 15 Å) regime, gate oxide does not exhibit discrete occurrences of gate leakage current but shows progressive breakdown instead. Moreover, as gate oxide scales even further till sub-nanometer regime, there are increasing evidences that this scaling will be limited by gate dielectric leakage and reliability. At one nanometer, conventional silicon dioxide leakage current at operating voltage, is in the regime of  $10 \sim 100 \text{ A/cm}^2$  which may be too high for low power application. As a result, high-K dielectrics will be needed by the year 2007 for 65 nm technology node. The breakdown mechanisms, pertaining to different thicknesses of gate dielectrics, have to be well characterized and understood. In the long term, reliability studies for high-K will be even more challenging due to its differences in material and electrical properties compared to conventional SiO<sub>2</sub>.

For thin gate oxide, in the  $30 \sim 45$  Å thickness regime, the formation, conduction, and evolution of quasi-breakdown are investigated. Using carrier separation measurements, the electron and hole components of the gate leakage current at onset of QB, are measured and analyzed. Subsequently, bias and thermal annealing are performed on post-QB oxides and disparate responses are observed. By carefully analyzing all the experimental evidences, a unifying defect-induced

breakdown model is presented and verified. As gate oxide scales into ultra-thin regime (< 15 Å), QB becomes masked by the high gate leakage current and subsequent multiple QB spots can be observed and tolerated. A statistical study is conducted on ultra-thin silicon dioxides and a physical model based on multiple quasi-breakdowns is proposed and experimentally verified.

Eventually, high-*K* dielectrics are required for continual gate dielectric scaling. The reliability for high-*K* stacks is examined and a novel technique for stack reliability is presented. Polarity dependent charge trapping in  $HfAl_xO_y$  (Hafnium-Aluminum-Oxide) stack is observed and this is correlated to preferential breakdown in the high-*K* and interfacial layer (IL) stack. Using carrier separation measurements, breakdowns in high-*K* stack are attributed to an interface-initiated or bulk layer breakdown in the high-*K* dielectric stacks.

# Contents

| Acknowledgements  | i    |

|-------------------|------|

| Summary           | ii   |

| Table of Contents | iv   |

| List of Symbols   | viii |

| List of Figures   | x    |

| List of Tables    | XX   |

### 1. Introduction

| 1.1  | Dimension Scaling and Future Trends of Microelectronics | 1 |

|------|---------------------------------------------------------|---|

| 1.2  | Summary and Motivation of Thesis                        | 5 |

| 1.3  | Thesis Outline and Original Contributions               | 6 |

| Refe | rences                                                  | 9 |

### 2. Literature Review: Gate Dielectric Degradation

| 2.1   | Impact   | of device scaling on gate dielectric degradation | 11 |

|-------|----------|--------------------------------------------------|----|

| 2.2   | Electric | al Stress-Induced Degradation and Breakdown      | 14 |

| 2.3   | Quasi-b  | reakdown Mechanism                               | 16 |

|       | 2.3.1    | Direct Tunneling Model [2.10][2.26]-[2.30]       | 19 |

|       | 2.3.2    | Percolation Model [2.40]-[2.43]                  | 21 |

| 2.4   | Device   | Scaling and Dielectric Performance               | 23 |

| 2.5   | Ultra-th | in oxide Reliability                             | 24 |

| 2.6   | High-K   | Dielectrics Reliability                          | 27 |

|       | 2.6.1    | High-K charge trapping                           | 28 |

|       | 2.6.2    | Stack Reliability                                | 28 |

| 2.7   | Summa    | ry                                               | 30 |

| Refer | rences   |                                                  | 32 |

#### 3. Measurement Setup and Techniques

| 3.1  | Measurement Techniques |                                                   | 41 |

|------|------------------------|---------------------------------------------------|----|

|      | 3.1.1                  | Direct Current Current-Voltage (DCIV) Technique   | 41 |

|      | 3.1.2                  | Charge Pumping (CP) Measurement Technique [3.14]. | 44 |

|      | 3.1.3                  | Comparison between DCIV and CP Technique          | 46 |

|      | 3.1.4                  | Carrier Separation                                | 48 |

| 3.2  | Summar                 | ry                                                | 50 |

| Refe | rences                 |                                                   | 51 |

#### 4. Bipolar Stressing, Trap Generations and QB Mechanism Study

| 4.1 | Introduction                                                 | 53 |

|-----|--------------------------------------------------------------|----|

|     | 4.1.1 Bipolar and Unipolar Current Stressing                 | 55 |

| 4.2 | Devices and Experimental Setup                               | 56 |

| 4.3 | Complete Evolution of Oxide Degradation Stages               | 57 |

|     | 4.3.1 Trap generation in thin gate oxides                    | 59 |

| 4.4 | Trap Generation and Fluence dependency                       | 59 |

| 4.5 | Critical level of trap density at onset of QB                | 62 |

| 4.6 | Field and Area Dependency at QB                              | 64 |

| 4.7 | Comparison of QQB for bipolar and unipolar current stressing | 66 |

| 4.8 | Carrier Separation Results                                   | 69 |

| 4.9 | F-N and Direct Tunneling Modeling Equations                  | 73 |

|     | 4.9.1Electron Leakage Current                                | 73 |

|     | 4.9.2Hole dominance leakage current after QB                 | 76 |

| 4.1 | 0 Proposed Model for QB Mechanism                            | 77 |

| 4.1 | 1 Summary                                                    | 81 |

| Ref | erences                                                      | 82 |

### 5. Effect of Bias and Thermal Annealing on QB and its Mechanism Study

| 5.1  | Introdu | ction                                                  | 85 |

|------|---------|--------------------------------------------------------|----|

| 5.2  | Device  | and Experimental Setup                                 | 86 |

| 5.3  | Charact | eristics of Electrical Recovery under Bias and Thermal |    |

| Anne | aling   |                                                        | 87 |

|      | 5.3.1   | Bias Annealing of post-QB oxides                       | 88 |

|       | 5.3.2   | Reverse Bias Annealing after QB                     | 90  |

|-------|---------|-----------------------------------------------------|-----|

|       | 5.3.3   | Thermal Annealing after QB                          | 94  |

|       | 5.3.4   | Recoverable and Unrecoverable QB states             | 99  |

|       | 5.3.5   | Combined Annealing Results: Bias and Thermal Anneal |     |

|       |         |                                                     | 101 |

| 5.4   | Discuss | ions for bias and thermal annealing                 | 104 |

| 5.4.1 | Mechan  | ism of thermal and bias anneal                      | 105 |

| 5.5   | Summa   | ry                                                  | 109 |

| Refer | ences   |                                                     | 110 |

| 6. | Degrada | tion and | Breakdown Mechanism in Ultra-thin Oxides                   |     |

|----|---------|----------|------------------------------------------------------------|-----|

|    | 6.1     | Introduc | ction                                                      | 112 |

|    | 6.2     | Device   | Fabrication and Experimental Setup                         | 115 |

|    | 6.3     | Thin Ox  | xide (20 Å) QB Degradation Characteristics                 | 116 |

|    |         | 6.3.1    | Comparison between Thick and Thin oxide: Interface Tra     | ıp  |

|    |         | Enhand   | ced Tunneling (ITET)                                       | 116 |

|    |         | 6.3.2    | Direct Correlation between interfacial traps and gate leak | age |

|    |         |          |                                                            | 121 |

|    |         | 6.3.3    | Distinction between ITT and ITET                           | 124 |

|    |         | 6.3.4    | Area dependency of ITET                                    | 126 |

|    | 6.4     | Ultra-th | in (<14 Å) oxide Degradation Mechanism                     | 128 |

|    |         | 6.4.1    | Area Dependency of Progressive Breakdown in Ultra-thin     | 1   |

|    |         | Oxides   |                                                            | 134 |

|    | 6.5     | Modelir  | ng of Gate Leakage Current in Ultra-thin Oxides            | 138 |

|    |         | 6.5.1    | Empirical Experimental Fitting                             | 139 |

|    |         | 6.5.2    | Modeling of Multiples Breakdown Spots                      | 139 |

|    | 6.6     | Summa    | ry                                                         | 143 |

|    | Refer   | rences   |                                                            | 144 |

# 7. High-K Dielectrics Reliability: Charge Trapping and Breakdown characteristics

| 7.1 | Introduction                                  | 148 |

|-----|-----------------------------------------------|-----|

| 7.2 | Device Fabrication                            | 150 |

| 7.3 | Carrier Separation and Leakage Path Mechanism | 150 |

| 7.4  | Polarity | Dependent Charge Trapping                           | 153 |

|------|----------|-----------------------------------------------------|-----|

| 7.5  | Experin  | nental Results                                      | 154 |

|      | 7.5.1    | Charge Trapping in High-K stacks                    | 154 |

|      | 7.5.2    | Polarity dependent breakdown characteristics in MOS |     |

|      | capaci   | tors                                                | 158 |

|      | 7.5.3    | Negative CVS : p-MOSFET                             | 161 |

|      | 7.5.4    | Positive CVS : n-MOSFET                             | 166 |

|      | 7.5.5    | Statistical Breakdown Results                       | 168 |

| 7.6  | Propose  | ed Charge Induced Breakdown Model                   | 173 |

| 7.7  | Summa    | ry                                                  | 175 |

| Refe | rences   |                                                     | 176 |

### 8. Conclusion and Recommendations

| 8.1   | Conclusions                     | 181 |

|-------|---------------------------------|-----|

| 8.2   | Recommendations for Future Work | 183 |

| Refer | ences                           | 186 |

| А | List of Publications | 187 |

|---|----------------------|-----|

|---|----------------------|-----|

# List of Symbols

| $c_e^t$ Electron capture coefficient $C_{ox}$ Oxide Capacitance per unit areaDInterface state density |      |

|-------------------------------------------------------------------------------------------------------|------|

|                                                                                                       |      |

| D Interfere state densite                                                                             |      |

| D <sub>IT</sub> Interface-state density                                                               |      |

| E <sub>c</sub> Silicon conduction band edge                                                           |      |

| E <sub>F</sub> Fermi level                                                                            |      |

| E <sub>g</sub> Silicon bandgap                                                                        |      |

| E <sub>i</sub> Silicon intrinsic energy level                                                         |      |

| E <sub>ox</sub> Oxide electric field                                                                  |      |

| E <sub>S, max</sub> Surface electric field at maximum base recombination current                      | tion |

| E <sub>v</sub> Silicon valence band edge                                                              |      |

| F(t) Cumulative probability function                                                                  |      |

| g <sub>m</sub> Transconductance                                                                       |      |

| I <sub>B</sub> Base recombination current                                                             |      |

| I <sub>B,max</sub> Maximum base recombination current                                                 |      |

| I <sub>off</sub> Off-state transistor leakage current                                                 |      |

| I <sub>s</sub> Source current                                                                         |      |

| I <sub>s/d</sub> Current collected from source/drain terminals                                        |      |

| I <sub>w</sub> Substrate well current                                                                 |      |

| J <sub>DT</sub> Direct tunneling gate current density                                                 |      |

| J <sub>FN</sub> Fowler-Nordheim gate current density                                                  |      |

| J <sub>g</sub> Gate leakage current density                                                           |      |

| k Boltzmann constant                                                                                  |      |

| K Kelvin                                                                                              |      |

| K Dielectric permittivity constant                                                                    |      |

| L Channel length                                                                                      |      |

| m <sub>e</sub>             | Rest mass of electron                                                |

|----------------------------|----------------------------------------------------------------------|

| n <sub>i</sub>             | Intrinsic density of state                                           |

| N <sub>IT</sub>            | Interface-state density                                              |

| q                          | Electronic charge of electron                                        |

| Q                          | Charge fluence                                                       |

| QB                         | Quasi-breakdown                                                      |

| Q <sub>BD</sub>            | Charge-to-breakdown                                                  |

| $Q_{\mathrm{f}}$           | Oxide fixed charge density                                           |

| Q <sub>inj</sub>           | Injected electron fluence                                            |

| Q <sub>IT</sub>            | Interface trap charge density                                        |

| Q <sub>OT</sub>            | Oxide trapped charge density                                         |

| $Q_{QB}$                   | Charge-to-quasibreakdown                                             |

| R <sub>J</sub>             | Ratio of current density of degraded spot over fresh current density |

| Т                          | Temperature (in Kelvin)                                              |

| $T_{100\%Ig}$              | Time-to-100% increment in gate leakage current                       |

| T <sub>BD</sub>            | Time-to-breakdown                                                    |

| T <sub>ox</sub>            | Gate oxide thickness                                                 |

| T <sub>QB</sub>            | Time-to-Quasi-breakdown                                              |

| $\mathbf{V}_{\mathrm{BE}}$ | Forward voltage bias for base-emitter                                |

| $V_d$                      | Drain voltage                                                        |

| V <sub>dd</sub>            | Supply voltage                                                       |

| $V_{FB}$                   | Flatband voltage                                                     |

| $V_g, V_G$                 | Gate voltage                                                         |

| $V_{GB}$                   | Gate voltage corresponding to maximum base recombination current     |

| V <sub>ox</sub>            | Voltage drop across oxide/dielectric layer                           |

| Vs                         | Source voltage                                                       |

| V <sub>th</sub>            | Threshold voltage                                                    |

| W                          | Channel Width                                                        |

| γ                          | Quantum yield factor                                                 |

| ε <sub>r</sub>             | Relative permittivity to air                                         |

| $\frac{1}{x}$              | Charge Centroid                                                      |

|                            |                                                                      |

# List of Figures

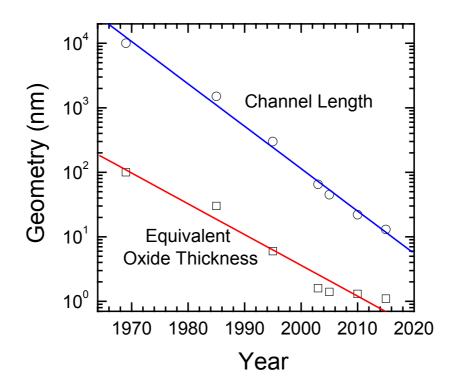

| Fig. 1.1  | Geometry scaling for MOSFET device channel length and equivalent oxide thickness for low power application MOSFETs. Equivalent oxide thickness (EOT) is used instead of physical oxide thickness due to the potential change in dielectrics to high-K material for 65 nm technology node                      |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

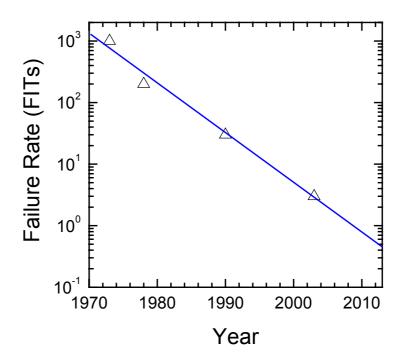

| Fig. 1.2  | Trend in long term reliability requirement for MOSFETs. 1 FITs = 1 failure per $10^9$ device hours                                                                                                                                                                                                            |

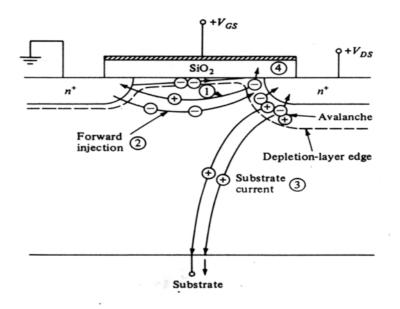

| Fig. 2.1  | Hot carrier generation and various current components in n-MOSFET. (After [2.1])11                                                                                                                                                                                                                            |

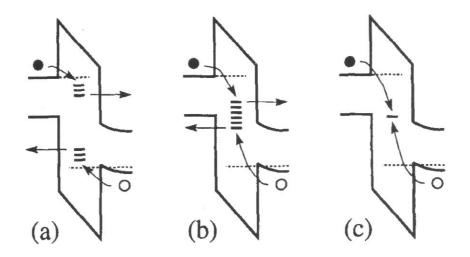

| Fig. 2.2  | Schematics of three possible conduction mechanisms leading to SILC leakage current. (a) Trap-assisted tunneling (TAT) at distinct defect locations with energy relaxation (b) Trap-assisted tunneling at same defect distribution (c) Tunneling and recombination at oxide defect sites (RTAT). (After [2.8]) |

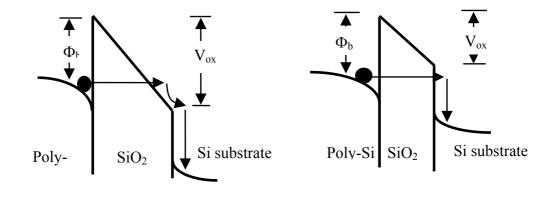

| Fig. 2.3  | Illustration of differences between (a) Fowler-Nordheim (FN) and (b) direct tunneling (DT). FN tunneling occurs when $V_{ox} > \Phi_b$ while DT occurs when $V_{ox} < \Phi_b$                                                                                                                                 |

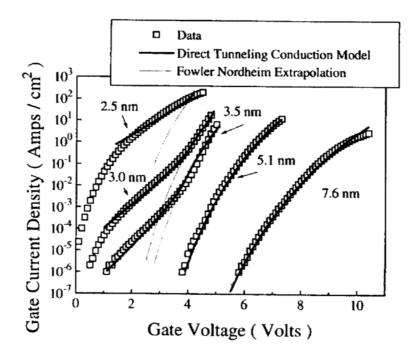

| Fig. 2.4  | Low-voltage conduction mechanism for thin oxide of various oxide thicknesses.<br>(After [2.11])                                                                                                                                                                                                               |

| Fig. 2.5  | Anode Hole Injection model with an incident electrons arriving at the anode and transferring its energy to a deep level valence electron and in the process, creating a hole which is then injected back into the oxide. (After [2.15])                                                                       |

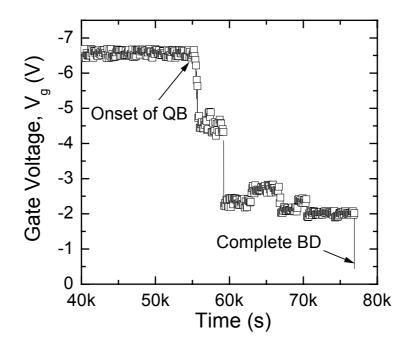

| Fig. 2.6  | Evolution of gate voltage under constant current stress till complete breakdown. At quasi-breakdown (QB), gate voltage drops due to enhanced leakage path with gate voltage magnitude still significantly higher than at complete breakdown                                                                   |

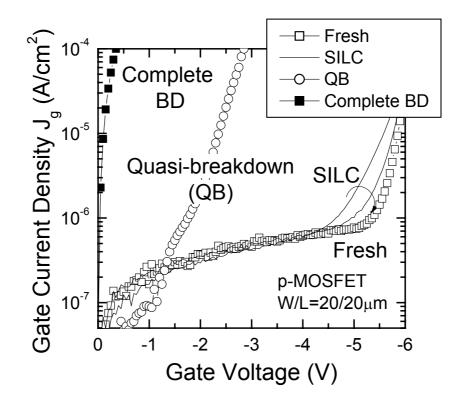

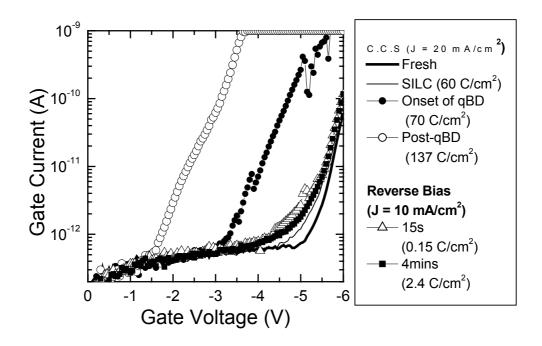

| Fig. 2.7  | I-V characteristics of gate oxide at various stages of stressing – Fresh, SILC, quasi-<br>breakdown (QB) and complete breakdown                                                                                                                                                                               |

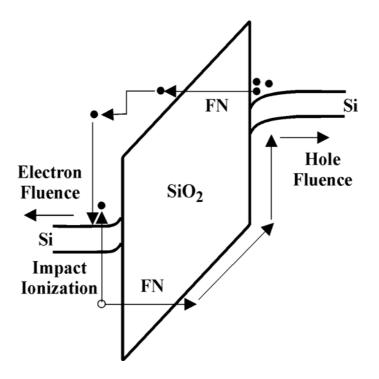

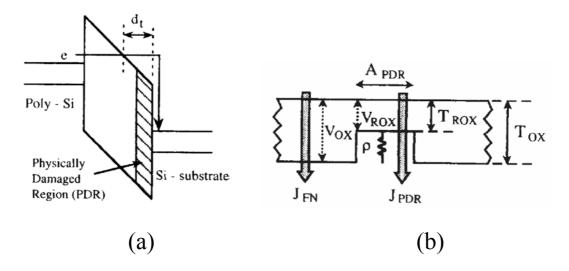

| Fig. 2.8  | Schematic drawing for (a) electron transport in the ultra thin gate oxide under high field stress (b) Current path in the oxide after quasi-breakdown. (After [2.10])                                                                                                                                         |

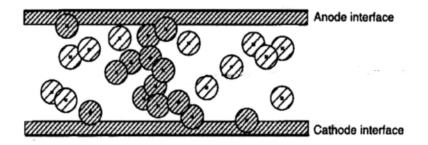

| Fig. 2.9  | Schematic illustration of percolation model for intrinsic oxide breakdown based on electrons trap generation. Conduction path is indicated by the shaded spheres. (After [2.33])                                                                                                                              |

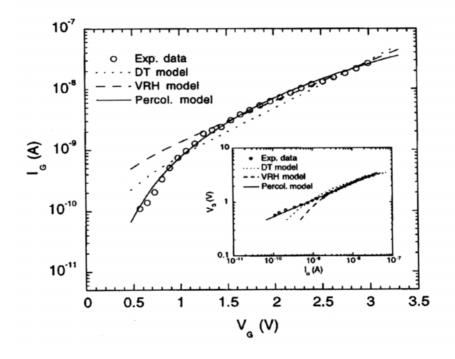

| Fig. 2.10 | Current-voltage characteristics of a MOS capacitor with a 4.2 nm gate oxide. Solid line is fit obtained with a percolation model. (After [2.43])                                                                                                                                                              |

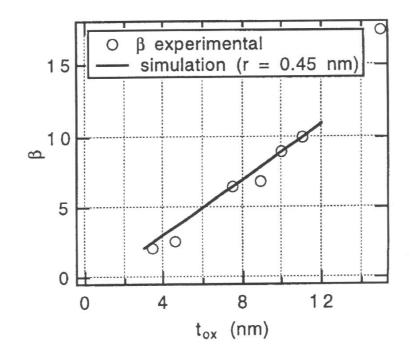

| Fig. 2.11 | Simulated and measured Weibull slope $\beta$ for charge-to-breakdown QBD as a function of oxide thickness. (After [2.40])                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

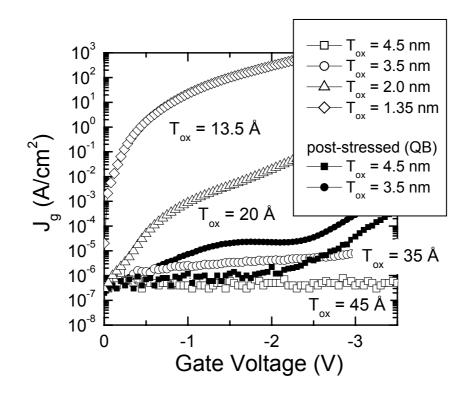

| Fig. 2.12 | Gate leakage current for different oxide thickness at fresh unstressed state and after post-QB. It can be observed that post-QB leakage current for 35 - 45 Å oxides are actually lower than that of the direct tunneling leakage current of 13 - 20 Å at its initial unstressed state                                                                                                                                                                                                                            |

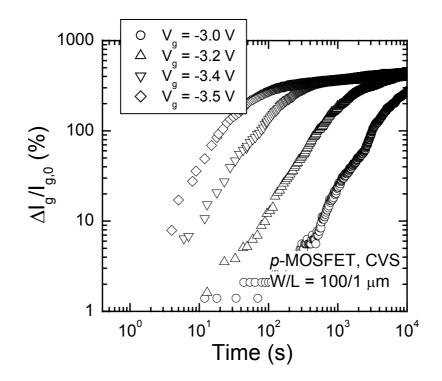

| Fig. 2.13 | Time evolution of gate current before and after onset of QB for ultra-thin oxides (13.5 Å) under various gate bias CVS                                                                                                                                                                                                                                                                                                                                                                                            |

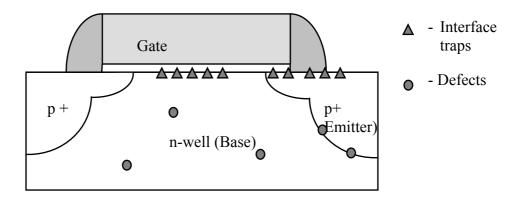

| Fig. 3.1  | p-MOSFET in top emitter-base configuration with spatial distribution of interface<br>traps and recombination traps centers as shown                                                                                                                                                                                                                                                                                                                                                                               |

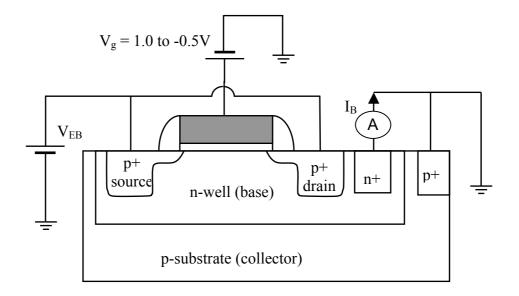

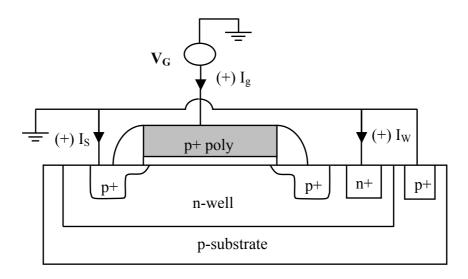

| Fig. 3.2  | Basic experimental setup for DCIV measurement using p-MOSFET. A vertical parasitic p/n/p-BJT is used with p+ source as emitter, n-well as base, and p-substrate as collector. Forward bias condition of $V_{EB} = +0.3$ V and $V_{BC} = 0$ V is applied and base recombination current $I_B$ is monitored as a function of gate voltage $V_g$ sweep. Drain can be connected together with source as shown or floated44                                                                                            |

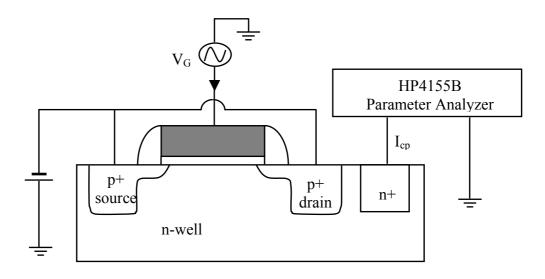

| Fig. 3.3  | Basic experimental setup for conventional charge-pumping measurements on p-MOSFETs. Source and drain are shorted and lightly reversed biased. An ac signal is applied to gate to alternately drive electrons and holes into the interface traps located at the SiO <sub>2</sub> -Si interface. During channel accumulation, recombination of free carrier with the trapped charges cause a net DC substrate current – charge pumping current $I_{cp}$ which is proportional to the areal interface trap density45 |

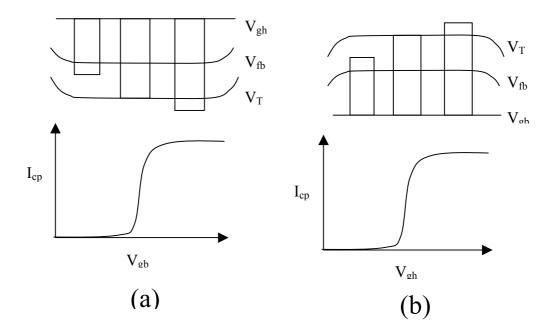

| Fig. 3.4  | Schematic illustration of CP technique applied to p-channel MOSFETs. (a) Fixed top level $V_{gh}$ with variable $V_{gb}$ and (b) fixed base level $V_{gb}$ and variable $V_{gh}$ . Both configuration shown with the associated charge pumping current versus the variable gate voltage as shown in the lower figures                                                                                                                                                                                             |

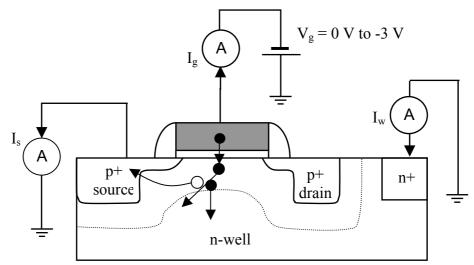

| Fig. 3.5  | Basic experimental setup for carrier separation measurement on p-channel MOSFETs under inversion mode. Drain is floated while source and n-well are grounded. Gate voltage is swept from 0 V to negative 3 V                                                                                                                                                                                                                                                                                                      |

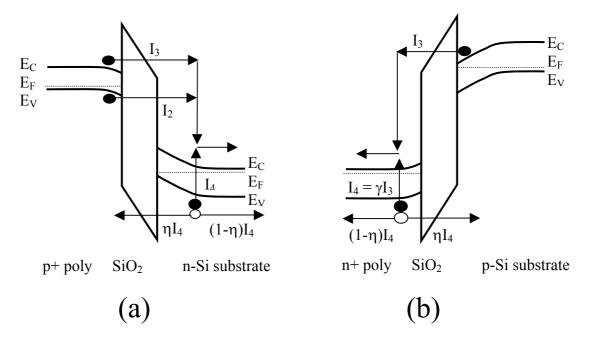

| Fig. 3.6  | Schematic band diagram (a) of p-channel MOSFET in inversion mode and (b) n-<br>channel MOSFET measured in inversion mode. [After [3.1]]49                                                                                                                                                                                                                                                                                                                                                                         |

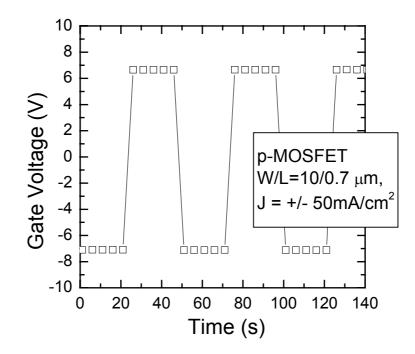

| Fig. 4.1  | Measured gate voltage due to application of constant bipolar current pulse of current density $J = +/-50 \text{ mA/cm}^2$                                                                                                                                                                                                                                                                                                                                                                                         |

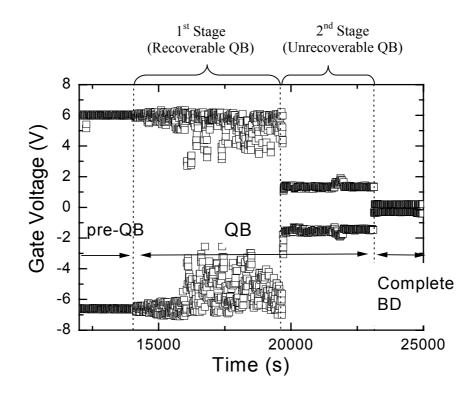

| Fig. 4.2  | Complete evolution of oxide degradation for thin oxide ( $T_{OX} = 45$ Å) under bipolar constant current stress ( $J_{stress} = +/- 10 \text{ mA/cm}^2$ ). It can be observed that within QB there are 2 stages – recoverable and unrecoverable QB. (n-MOSFET, W/L = 10/0.2 $\mu$ m)                                                                                                                                                                                                                              |

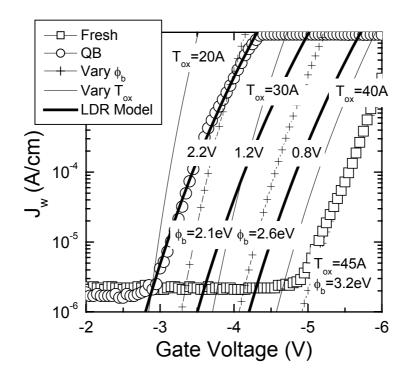

Fig. 4.3

Fig. 4.4

Fig. 4.5

Fig. 4.6

Fig. 4.7

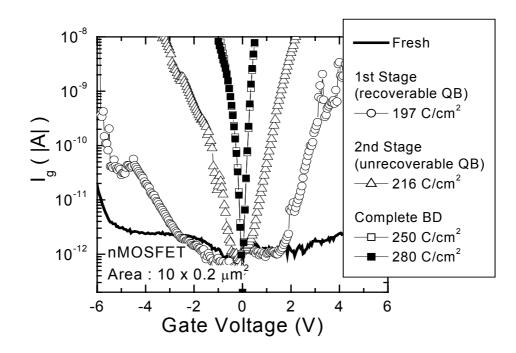

| I-V characteristics of oxides at various stages of stressing conditions – fresh, recoverable QB, unrecoverable QB and complete breakdown. (n-MOSFET, $W/L = 10/0.2 \ \mu m$ )                   | 58 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                                                                                                                                                                                                 |    |

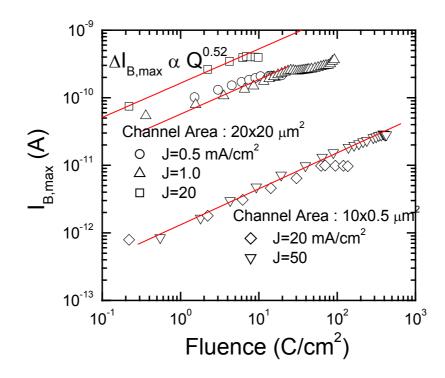

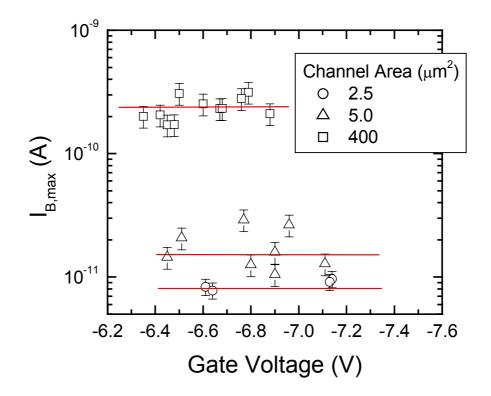

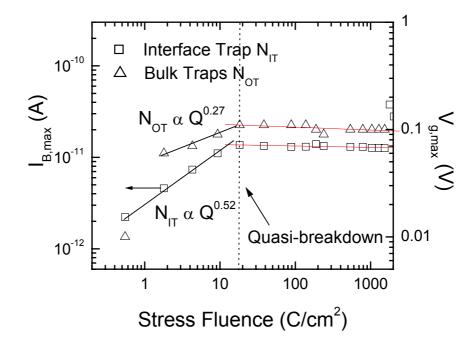

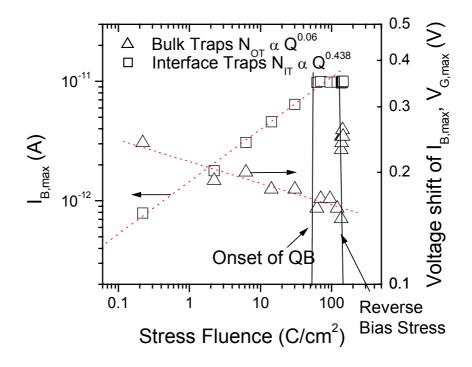

| Peak recombination current $I_{B,max}$ versus charge fluence for stressing till quasi-                                                                                                          |    |

| breakdown. Since peak $I_{B,max}$ is proportional to interface trap, it can be observed that                                                                                                    |    |

| interface trap density is proportional to charge fluence Q <sup>0.52</sup> independent of channel                                                                                               |    |

| area and stressing current density.                                                                                                                                                             | 60 |

|                                                                                                                                                                                                 |    |

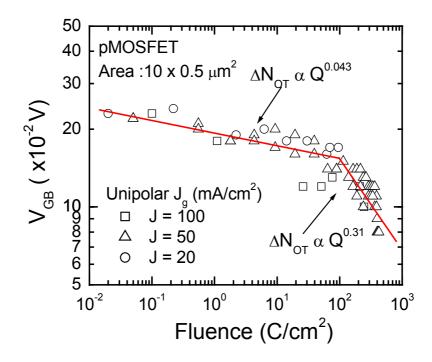

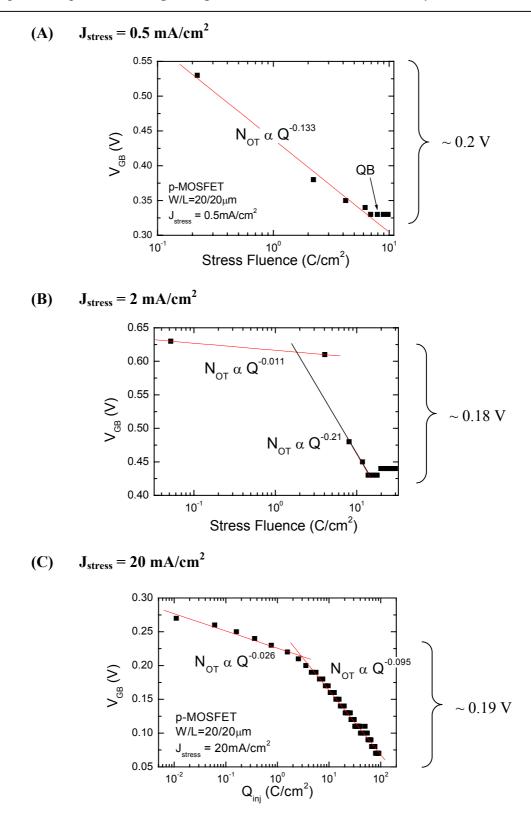

| Voltage shift of peak $I_{B,max}$ , $V_{GB}$ versus charge fluence. Since oxide trap density is                                                                                                 |    |

| proportional to $V_{GB}$ , it can be observed that oxide trap density can be divided into 2 region. At charge fluence < 100 C/cm <sup>2</sup> , oxide trap is proportional to $Q^{0.043}$ while |    |

| beyond, oxide trap is proportional to Q <sup>0.31</sup>                                                                                                                                         | 61 |

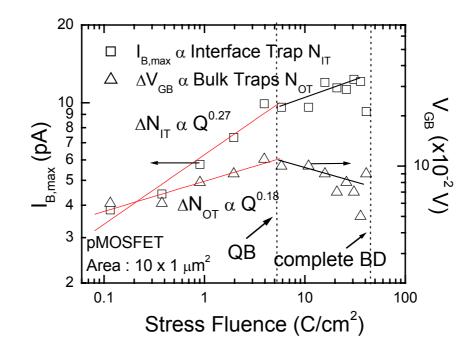

| Trap generation under constant voltage stressing. Oxide trap N <sub>OT</sub> is proportional to                                                                                                 |    |

| $Q^{0.18}$ while interface trap N <sub>IT</sub> is proportional to $Q^{0.27}$ . (p-MOSFET, W/L=10/1 $\mu$ m,                                                                                    |    |

| $V_{\text{stress}} = 6.8 \text{ V}$                                                                                                                                                             | 62 |

| stress 0.0 ()                                                                                                                                                                                   | 02 |

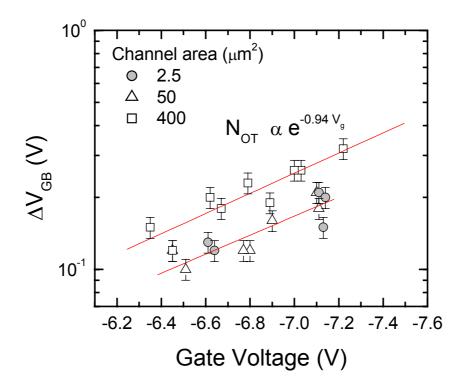

| Critical level of oxide trap at onset of quasi-breakdown for different channel area as                                                                                                          |    |

| shown. Oxides are stressed till QB using CVS at different gate bias. It can be                                                                                                                  |    |

| observed that bulk traps as reflected by $\Delta V_{GB}$ at onset of QB increase with gate bias,                                                                                                |    |

| without a single constant level expected for critical bulk defects for percolation                                                                                                              |    |

Fig. 4.8 Critical level of interface traps at onset of quasi-breakdown for different channel area. Oxides are stressed to QB using CVS at different gate bias. It can be observed that a constant level of interfacial traps is obtained irrespective of stressing gate

- Voltage shift of peak I<sub>B</sub> versus stress fluence for different stressing current density Fig. 4.9 (a)  $J_{stress} = 0.5 \text{ mA/cm}^2$  (b)  $J_{stress} = 2 \text{ mA/cm}^2$  (c)  $J_{stress} = 20 \text{ mA/cm}^2$ . It can be observed that 2 stages exist for bulk trap generation under CCS. The crossover point is highly dependent on the magnitude of the constant current stress. In the initial stage, bulk trap generation is much slower and highly dependent on gate bias. In the second stage, trap generation is much faster and total traps generated as reflected by

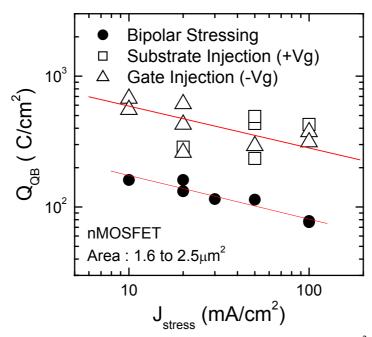

- Charge to quasi-breakdown for small channel area ( $< 3 \mu m^2$ ) using various mode of Fig. 4.10 constant current stress with different polarity injection, including unipolar and bipolar CCS. It can be observed that bipolar stressing results in much lower QQB for the same fluence as compared to unipolar stressing. Each point (differentiated by sample area) is obtained from 5-10 samples with Q<sub>OB</sub> (63% values) corresponding

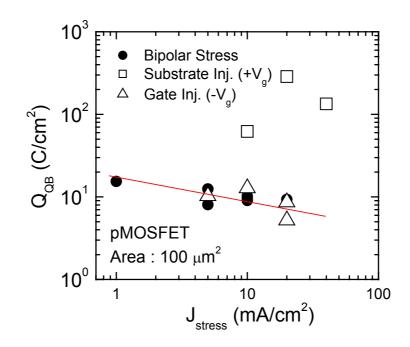

- Charge to quasi-breakdown for big channel area ( $\sim 100 \ \mu m^2$ ) using various mode of Fig. 4.11 constant current injection. For large area samples, gate injection unipolar stress

|           | results in significantly lower $Q_{QB}$ compared to substrate injection. Bipolar stressing<br>for large samples also has low $Q_{QB}$ and appears to be limited by the low $Q_{QB}$ for gate<br>injection under negative gate bias. Results are similar to [4.13]. Each point is<br>obtained from 5-10 samples with $Q_{QB}$ (63% values) corresponding to the zero level<br>in the Weibull distribution                                             |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

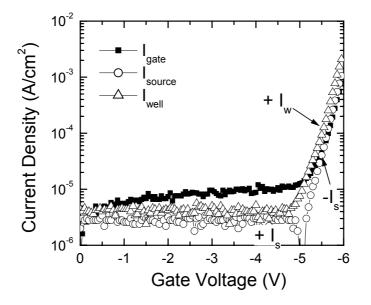

| Fig. 4.12 | Carrier separation measurement showing gate, source and substrate current component at fresh, unstressed state. (p-MSOFET, $T_{ox} = 45$ Å, W/L = 10/0.5 µm)70                                                                                                                                                                                                                                                                                       |

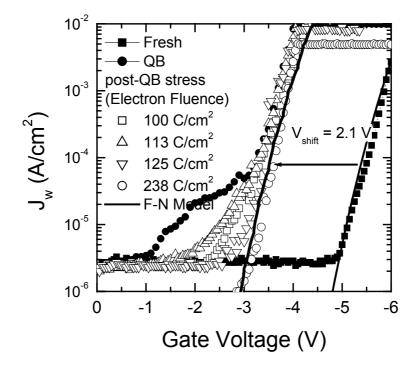

| Fig. 4.13 | Carrier separation measurement at onset of QB, which is attained after 222C/cm <sup>2</sup> of electron fluency. Sample is still in recoverable QB stage and is the same one used in Fig. 4.12.                                                                                                                                                                                                                                                      |

| Fig. 4.14 | Carrier separation measurement after post-QB stress (additional electron fluency of 38 C/cm <sup>2</sup> ) within recoverable QB stage. Sample used is the same as Fig. 4.12                                                                                                                                                                                                                                                                         |

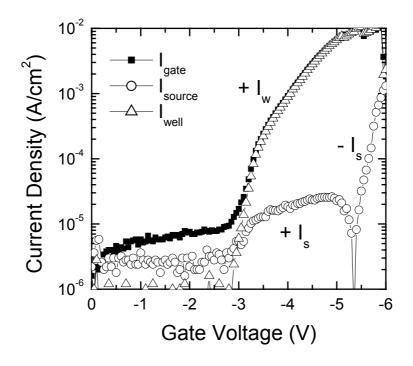

| Fig. 4.15 | Carrier separation measurement after post-QB stress but stressed to unrecoverable QB (p-MOSFET, $T_{ox} = 45$ Å, W/L = 10/1 $\mu$ m, $J_{stress} = 10$ mA/cm <sup>2</sup> )72                                                                                                                                                                                                                                                                        |

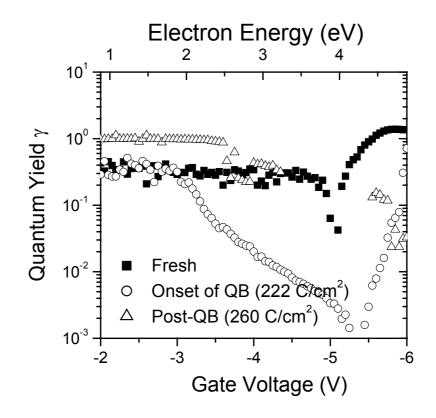

| Fig. 4.16 | Experimental quantum yield as a function of gate voltage and resulting electron energy for unstressed gate oxides and post-QB oxides as shown inset                                                                                                                                                                                                                                                                                                  |

| Fig. 4.17 | Carrier separation for well current component at fresh and onset of QB state. F-N current is simulated using (3.5) with varying energy barrier, oxide thickness and electric field shift. Good fit observed for experimental $I_{well}$ and F-N current using electric field shift $V_{shift} = 2.2 V$                                                                                                                                               |

| Fig. 4.18 | Evolution of well current component for post-QB stage under continual stressing.<br>Good fit observed for well current component with simulated F-N tunneling current.<br>$(T_{ox} = 45\text{\AA}, \text{W/L} = 10/0.7 \ \mu\text{m}, \text{p-MOSFET})$                                                                                                                                                                                              |

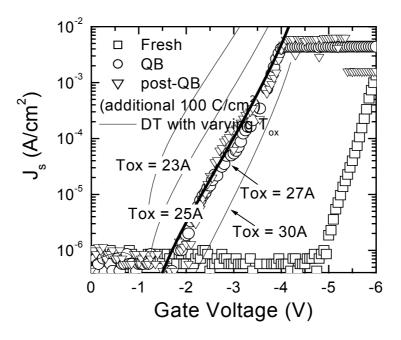

| Fig. 4.19 | Evolution of source current component after QB in hole dominant regime.<br>Relatively good fit observed between experimental data at QB and direct tunneling current modeling using (3.6). ( $T_{ox} = 45$ Å, W/L = 10/0.7µm, p-MOSFET)77                                                                                                                                                                                                            |

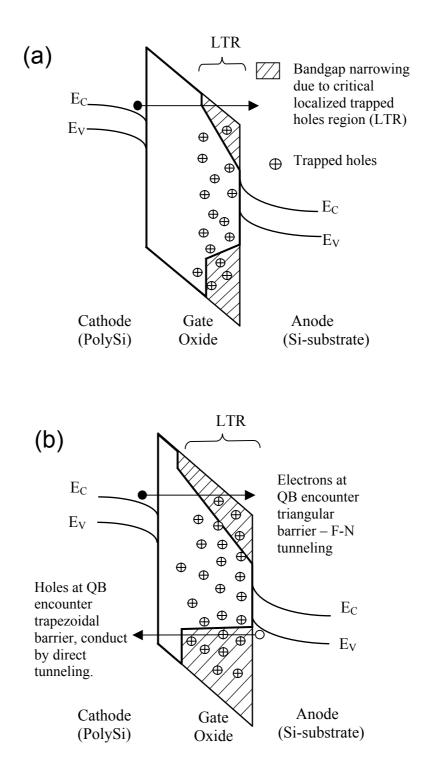

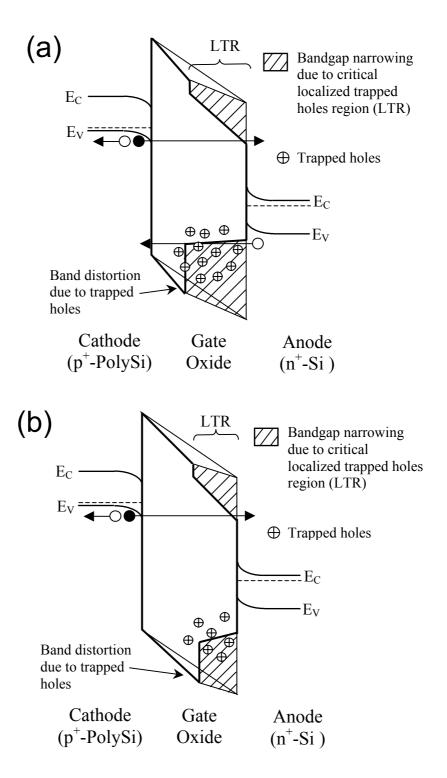

| Fig. 4.20 | A schematic drawing of energy band diagram for localized trap region (LTR) model. Hole trapping at anode results in distortion of energy band and formation of localized trap region (LTR) causing bandgap narrowing near the anode. (a) In initial stage, electron conduction by F-N tunneling. (b) Further stressing extends the LTR, resulting in hole direct tunneling. Electrons and holes are indicted by solid and open circles, respectively |

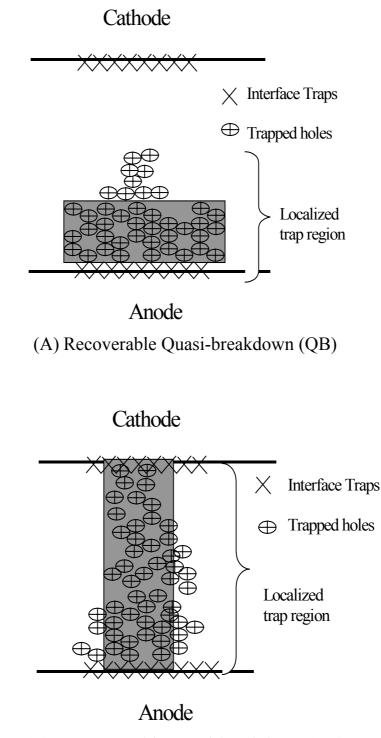

| Fig. 4.21 | Schematic illustration of evolution of the localized trap region (LTR) formed by deep level trapped holes at various stages of QB (A) at onset of QB, within recoverable QB, LTR is mainly localized at the anode and conduction proceed by direct tunneling of both holes and electrons. (B) at unrecoverable QB, LTR has                                                                                                                           |

| Fig. 5.1  | Schematic illustration of carrier separation measurement setup for electrical bias annealing experiment                                                                                                                                                                                                                                                                                                                           |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

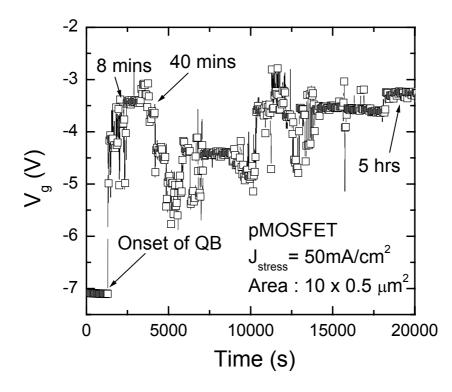

| Fig. 5.2  | Evolution of gate voltage under constant current stress till QB and post –QB positive bias annealing. (p-MSOFET, $T_{ox} = 45$ Å, W/L = 10/0.5 $\mu$ m, $J_{stress} = 50$ mA/cm <sup>2</sup> )                                                                                                                                                                                                                                    |

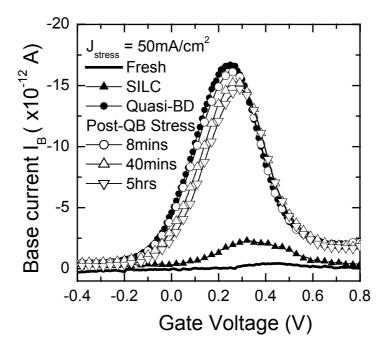

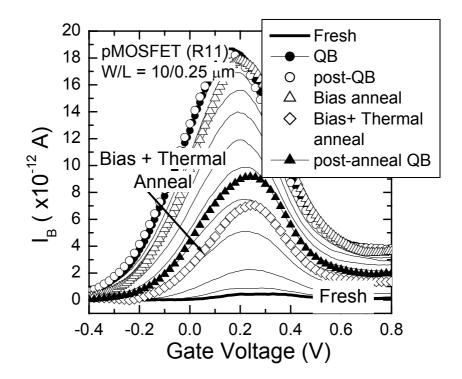

| Fig. 5.3  | DCIV spectra of p-MOSFET for Fig. 5.2, with stressing till QB and post-QB. After onset of QB, it can be observed that the recombination current, $I_B$ spectra overlaps with subsequent decrease in the peak amplitude of $I_B$ accompanied by a slight shift of VGB for peak IB to the right. (p-MSOFET, $T_{ox} = 45$ Å, W/L = 10/0.5 $\mu$ m, $J_{stress} = 50 \text{ mA/cm}^2$ )                                              |

| Fig. 5.4  | Quantitative DCIV spectra measurement showing IB, max and $\Delta VGB$ versus injected fluencies. Bulk and interface trap after QB show no further increment. (p-MOSFET, $T_{ox} = 45$ Å, W/L = 10/0.7 $\mu$ m, J <sub>stress</sub> = 50 mA/cm <sup>2</sup> )                                                                                                                                                                     |

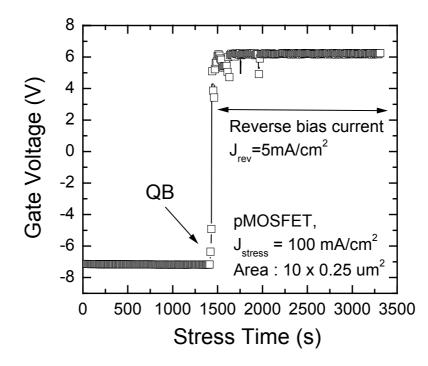

| Fig. 5.5  | Evolution of gate voltage under constant current stressing. At QB, reverse bias current $J_{rev} = 5 \text{ mA/cm}^2$ is applied. (pMOSFET, Tox = 45 Å, W/L = 10/0.25 µm, $J_{stress} = 100 \text{ mA/cm}^2$ )                                                                                                                                                                                                                    |

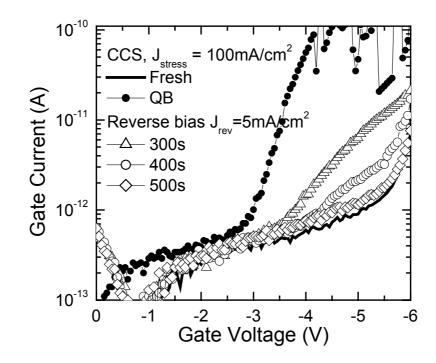

| Fig. 5.6  | Associated I-V characteristics of oxide at various stages of electrical stressing as shown inset. Reverse bias anneal applied after onset of QB. It can be seen that gate leakage recovers back to fresh after 500 s of reverse bias anneal. Sample used is the same as Fig. 5.5                                                                                                                                                  |

| Fig. 5.7  | DCIV spectra for p-MOSFET oxide at various stages of electrical stressing. The sample used is the same as Fig. 5.8                                                                                                                                                                                                                                                                                                                |

| Fig. 5.8  | Associated I-V characteristics at various stages of constant current stressing. After quasi-breakdown is attained, same polarity stressing is continued before application of a reverse bias stress. Gate leakage current after application of reverse bias shows reduction till SILC level. ( $T_{ox} = 45$ Å, W/L = 10/0.5 µm, p-MOSFET)93                                                                                      |

| Fig. 5.9  | Quantitative DCIV spectra measurement at various stages of current stressing. Peak recombination current $I_B$ is related to interface traps while the lateral shift of peak $I_B$ is related to oxide bulk traps. At reverse bias anneal, oxide bulk traps recover to initial values at fresh state while interface traps remains unchanged                                                                                      |

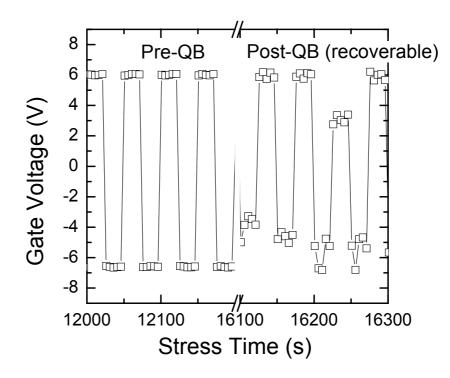

| Fig. 5.10 | Variation of gate voltage under bipolar constant current density $J_{stress} = +/-10$ mA/cm <sup>2</sup> at pre-QB and post-QB with successive alternating stressing and bias annealing. ( $T_{ox} = 45$ Å, W/L = 10/0.2 µm, n-MOSFET)                                                                                                                                                                                            |

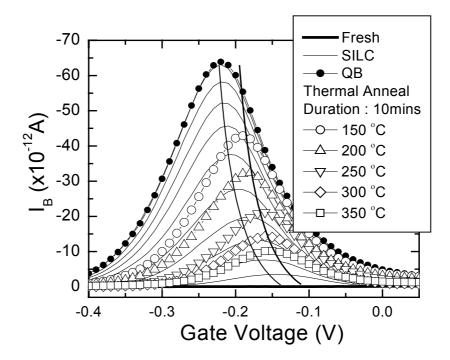

| Fig. 5.11 | DCIV spectra of p-MOSFET stressed to QB. Post-QB thermal annealing performed at various temperatures as shown inset. The thin line linking up the maxima of the $I_B$ spectra reflects the level of oxide bulk traps during SILC while the thick line reflect bulk trap level due to the thermal annealing. It can be observed that thermal anneal results in both a positive shift in the spectra and reduction in the maxima of |

|           | $I_B$ showing reduction in interface traps and bulk traps.( $T_{ox} = 45$ Å, $J_{stress} = 50$ mA/cm <sup>2</sup> , W/L = 10/1.0 $\mu$ m, p-MOSFET)95                                                                                                                                                                                         |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

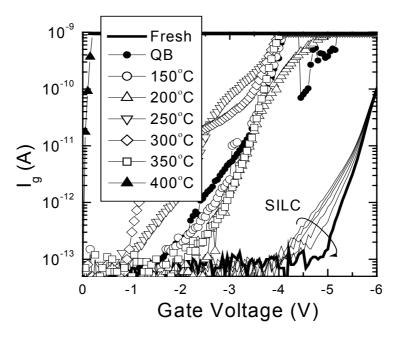

| Fig. 5.12 | Gate current leakage current after QB and with post-QB thermal annealing at successively higher temperature for 10mins each. ( $T_{ox} = 45$ Å, $J_{stress} = 50$ mA/cm <sup>2</sup> , W/L = 10/1.0 $\mu$ m, p-MOSFET)                                                                                                                        |

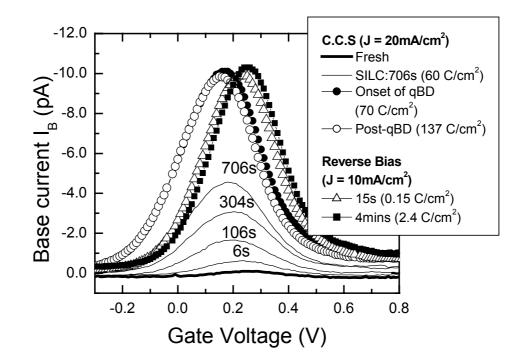

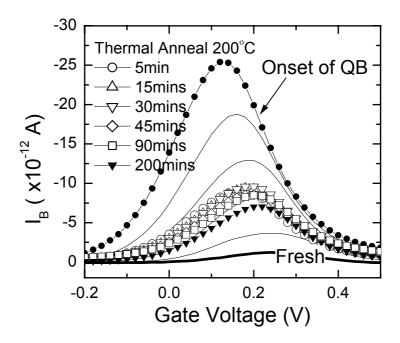

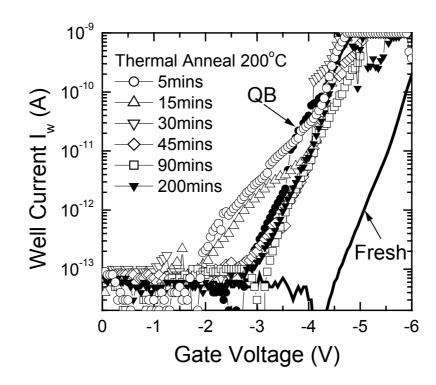

| Fig. 5.13 | DCIV spectra of p-MOSFET stressed to QB. Post-QB thermal annealing carried out at 200°C for varying period of annealing durations from 5 mins to 200 mins. ( $T_{ox} = 45 \text{ Å}$ , $J_{stress} = 20 \text{ mA/cm}^2$ , $W/L = 10/1.0 \mu\text{m}$ , p-MOSFET)                                                                             |

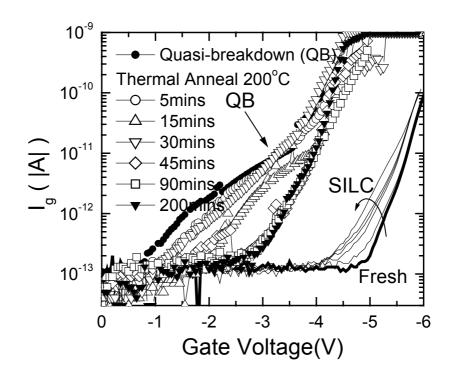

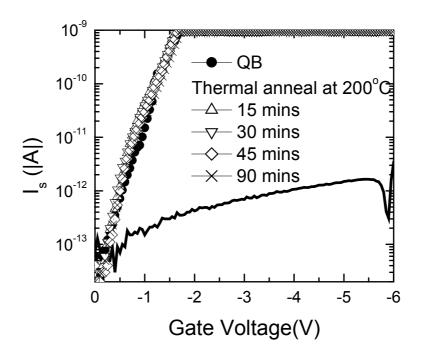

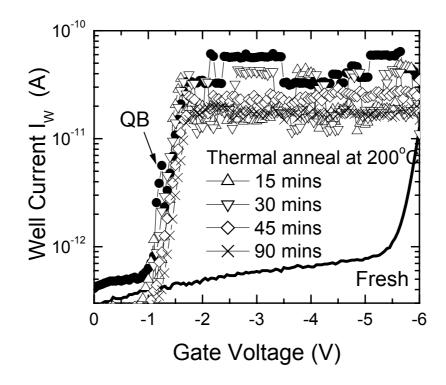

| Fig. 5.14 | Gate leakage current at QB and after post-QB thermal annealing treatment at 200°C for varying period of time as shown inset                                                                                                                                                                                                                   |

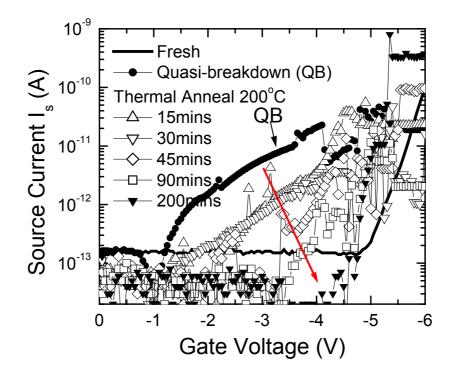

| Fig. 5.15 | Carrier separation measurement of source current component (holes current ) for p-<br>MOSFET under successive thermal anneal. Sample used is the same as Fig. 5.1498                                                                                                                                                                          |

| Fig. 5.16 | Carrier separation measurement of well current component (electron current) for p-<br>MOSFET under inversion conditions after successive thermal anneal. Sample used<br>is the same as Fig. 5.14                                                                                                                                              |

| Fig. 5.17 | Gate I-V characteristics for p-MSOFET stressed till unrecoverable QB with post-<br>QB thermal annealing at 200°C for varying period of durations as shown inset. ( $T_{ox}$ = 45 Å, $J_{stress}$ = 50 mA/cm <sup>2</sup> , W/L = 10/1 µm, p-MOSFET)100                                                                                        |

| Fig. 5.18 | Carrier separation for source I-V characteristics on the same p-MSOFET used in<br>Fig. 5.17 with post-QB thermal annealing treatment100                                                                                                                                                                                                       |

| Fig. 5.19 | Carrier separation measurement showing substrate I-V characteristics for p-<br>MOSFET used in Fig. 5.17 with post-QB thermal annealing treatment101                                                                                                                                                                                           |

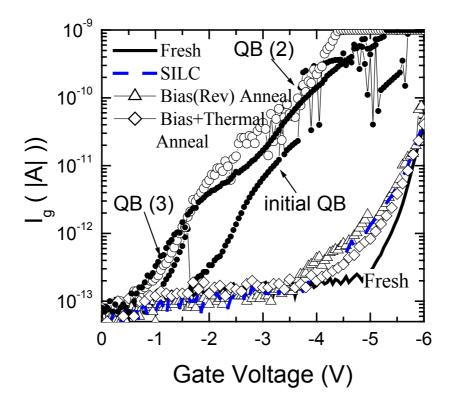

| Fig. 5.20 | Gate leakage current at fresh stage and after electrical stresses. Oxide was stressed till onset of QB as shown by initial QB and continual stressing result in QB(2) before being subjected to reverse bias and thermal anneal. The 'recovered' oxide was then subjected to additional electrical stress till second QB as shown by QB(3)102 |

| Fig. 5.21 | Associated DCIV spectra of oxide stressed till QB and subjected to bias and thermal anneal. It can be observed that the combined effects of bias and thermal anneal results mainly in a positive shift in the DCIV spectra of the post-QB oxide and reduces I <sub>B</sub> to a lower level respectively                                      |

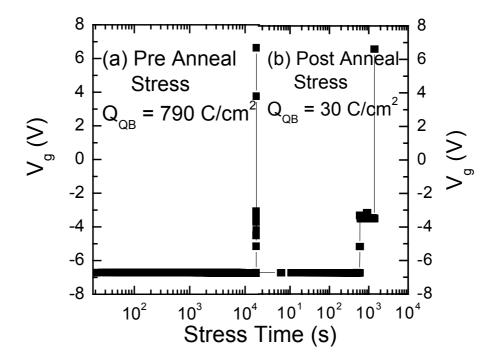

| Fig. 5.22 | Evolution of the gate voltage of oxide subjected to CCS till QB as shown in (a) and subsequently subjected to bias and thermal anneal. (b) shows the subsequent evolution of the gate voltage when the 'recovered' oxide is re-subjected to CCS till a second QB.                                                                             |

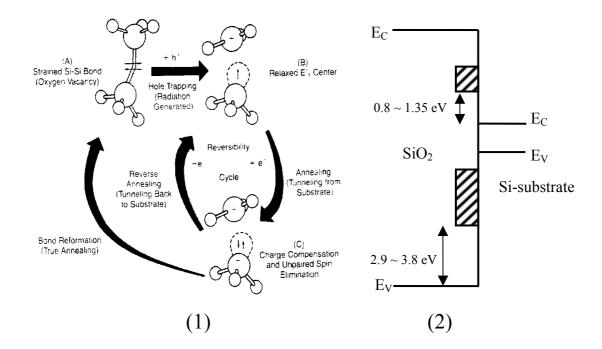

| Fig. 5.23 | (1) Microscopic model of hole trapping (A)-(B) forming an E' center and                                                                                                                                                                                                                                                                       |

1g. 5.23 (1) Microscopic model of hole trapping (A)-(B) forming an E' center and detrapping (C) along with charge compensation and bond reformation as proposed

|           | by Lelis <i>et al.</i> [5.13] (2) Two spatial equivalent trap levels that electrons can tunnel to, corresponding to the ground and excited state of the E' center. (After [5.13])105                                                                                                                                                                                                                                                                                                                                                                               |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

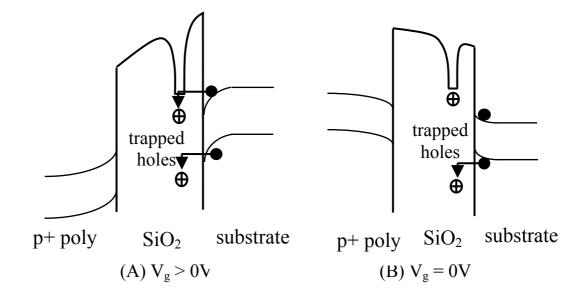

| Fig. 5.24 | Schematic diagram illustrating (A) Reverse bias annealing (B) Thermal annealing without bias. With bias anneal, both levels of trapped holes can be annealed while in thermal annealing, hole trap with energy level above Si conduction band requires electrons with energy above conduction band to be deactivated                                                                                                                                                                                                                                               |

| Fig. 5.25 | <ul> <li>(a) Proposed localized trap region (LTR) model: hole trapping predominantly at anode causes an energy band distortion and results in F-N conduction for electrons and direct tunneling for holes at the recoverable QB. (b) Thermal annealing results in electron-hole pair compensation and the reduction of localized trap region (LTR). The shaded regions represent bandgap narrowing due to formation of LTR while the thick lines show the resultant oxide energy band</li></ul>                                                                    |

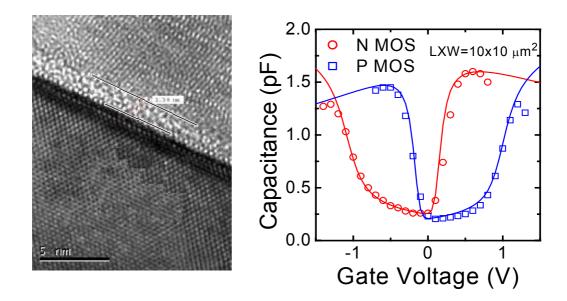

| Fig. 6.1  | HRTEM cross section of 13 Å gate oxide (left) and C-V measurements and simulation results (solid lines) fitting to 13 Å oxide thickness by Berkeley QMCV modeling (right)                                                                                                                                                                                                                                                                                                                                                                                          |

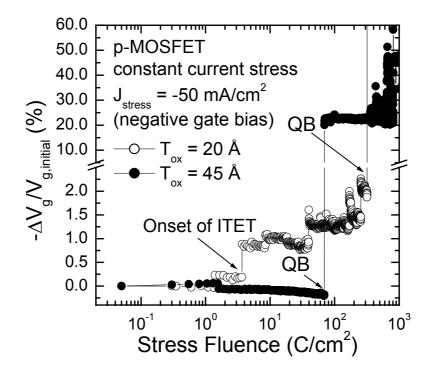

| Fig. 6.2  | Evolution of gate voltage under constant current stressing ( $J_{stress} = -50 \text{ mA/cm}^2$ ) with gate injection for thick (45 Å) and thin (20 Å) gate oxide. ( $T_{ox} = 45 \text{ Å } \& 20 \text{ Å}$ , Channel Area = 10 µm <sup>2</sup> , p-MOSFET)                                                                                                                                                                                                                                                                                                      |

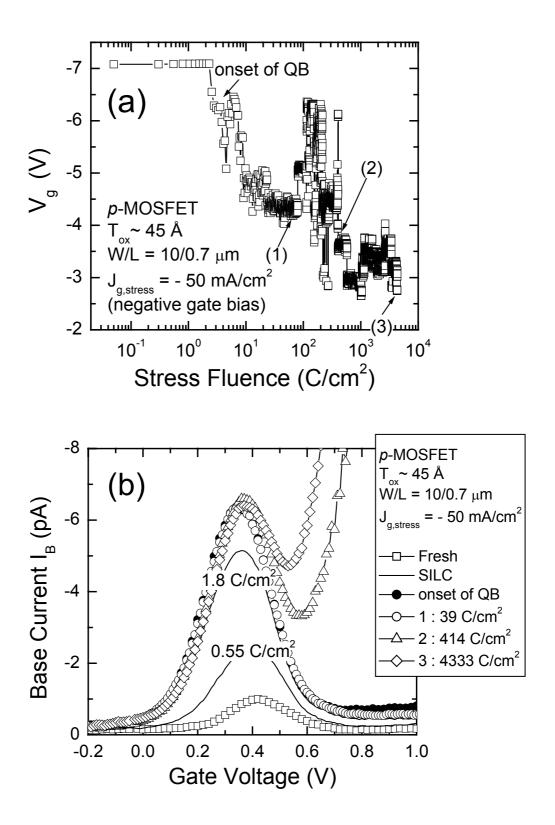

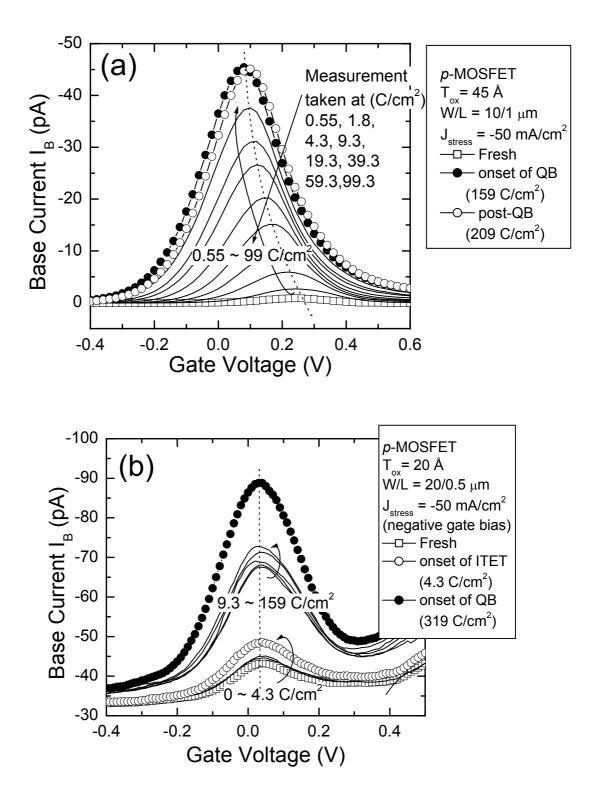

| Fig. 6.3  | (a) Evolution of gate voltage under CCS for thick (45 Å) p-MOSFET oxide after<br>onset of QB. (b) Associated DCIV spectra measured at interval specified in (a).<br>Base recombination current increases continuously under stressing till QB. At QB,<br>DCIV spectra observed to overlap with no further increases. (Channel Area = 10<br>$\mu$ m <sup>2</sup> , p-MOSFET)                                                                                                                                                                                        |

| Fig. 6.4  | Comparison of DCIV spectra for (a) thick (45 Å)and (b) thin oxide (20 Å) p-MOSFET under constant current stressing till QBs. (a) For thick oxide (45 Å), base recombination current increases continuously under stressing till QB. At QB, DCIV spectra observed to overlap with no further increases. (b) For thin oxide (20 Å), DCIV spectra increases even after QB with step-like increases in correlation with gate leakage current. (Locus of $I_{B,max}$ and $V_{g,max}$ is shown by the dotted lines). (Channel Area = 10 $\mu$ m <sup>2</sup> , p-MOSFET) |

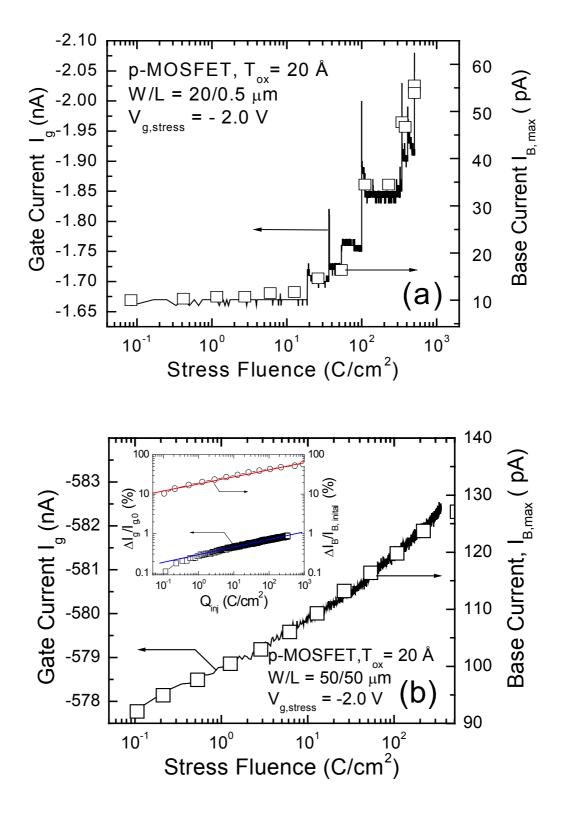

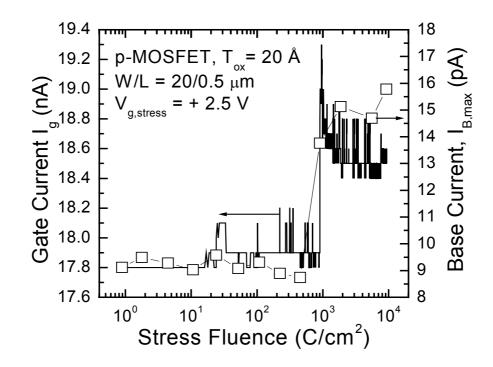

| Fig. 6.5  | Correlation of gate leakage current $I_g$ and base recombination current $I_B$ , which directly reflect interface trap density $N_{IT}$ under constant voltage stressing for (a) small area samples (W/L = 20/0.5 µm) and (b) large area samples (W/L = 50/50 µm). Inset figure shows the percentage change in $I_g$ and $I_B$ . (Tox = 20 Å, p-channel MOSFET)                                                                                                                                                                                                    |

| Fig. 6.6  | Correlation of gate leakage current $I_g$ and peak base recombination current $I_{B,max}$ under constant voltage stressing for substrate injection. Similar to negative gate bias (gate injection), gate leakage current observed to bear one-to-one correspondence to                                                                                                                                                                                                                                                                                             |

|           | base recombination current which is directly correlated to interface traps. ( $T_{ox} = 20$<br>Å, W/L = 20/0.5 µm, p-MOSFET)                                                                                                                                                                                                                                                                                                           |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

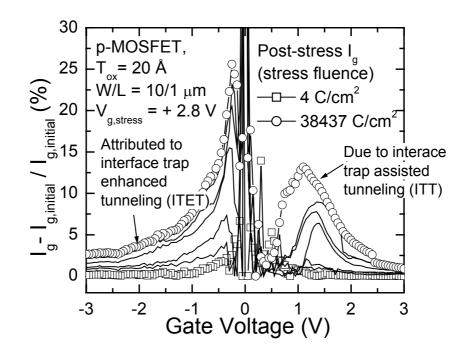

| Fig. 6.7  | Percentage change of gate leakage current $(I_g-I_{g,initial}/I_{g,initial})$ for different gate voltage under constant voltage stressing. The spike for $\Delta I_g$ at gate voltage near to zero volts is due to background noise. Unlike ITT, ITET occurs throughout the entire voltage measurement range. ( $T_{ox} = 20$ Å, Area = 10 $\mu$ m <sup>2</sup> , p-channel MOSFET).                                                   |

| Fig. 6.8  | Carrier separation showing holes (shown by source current $I_s$ ) and electrons current (shown by well current $I_w$ ) for small channel area p-MOSFET stressed under negative constant gate voltage. ( $T_{ox} = 20$ Å, Area = 10 $\mu m^2$ , p-channel MOSFET)125                                                                                                                                                                    |

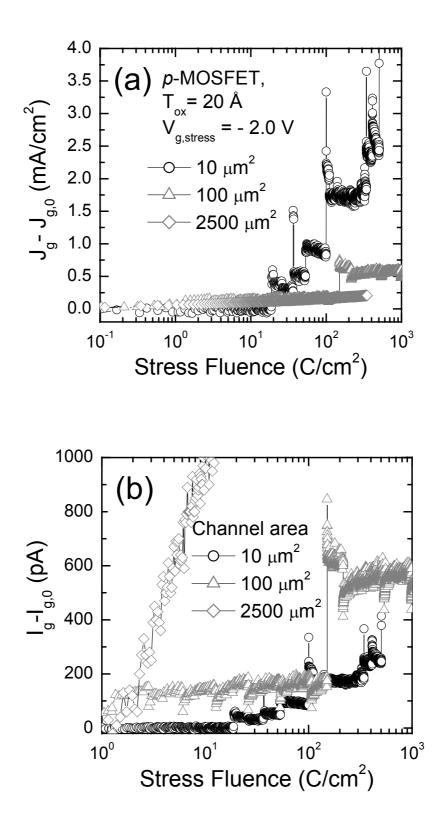

| Fig. 6.9  | (a) Discrete gate current density increase for different channel areas (b) normalized gate current increase under constant voltage stress for different channel area ranging from 10 to 2500 $\mu$ m <sup>2</sup> . (T <sub>ox</sub> = 20 Å, p-MOSFET)                                                                                                                                                                                 |

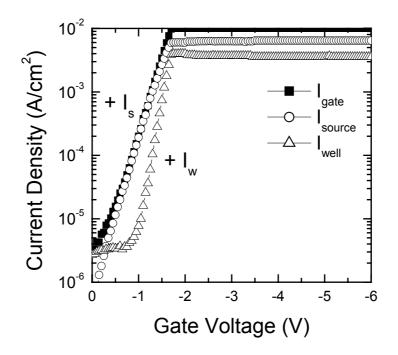

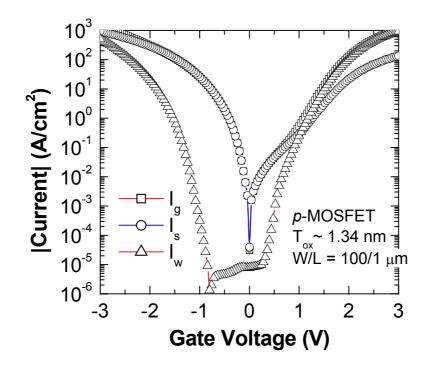

| Fig. 6.10 | Carrier separation characteristics for 13 Å gate oxide in both depletion and accumulation. Source, n-well and gate current indicated by $I_s$ , $I_w$ and $I_g$ respectively.<br>Drain electrode is not connected. (Channel Area = 100 $\mu$ m <sup>2</sup> , p-MOSFET)                                                                                                                                                                |

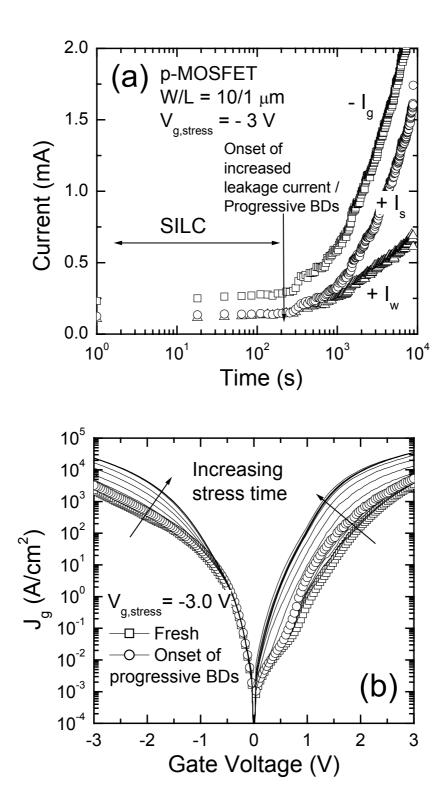

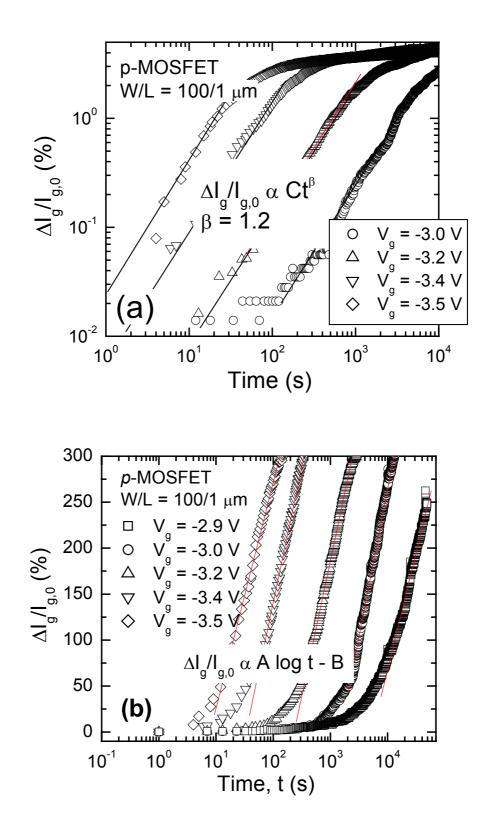

| Fig. 6.11 | (a) Evolution of current-voltage characteristics at fresh and after constant voltage stressing ( $V_{stress} = -3.0$ V). (b) Associated I-V characteristics at onset of progressive BD and post PBDs. ( $T_{ox} = 13.4$ Å, Channel Area = 10 $\mu$ m <sup>2</sup> , p-MOSFET)                                                                                                                                                          |

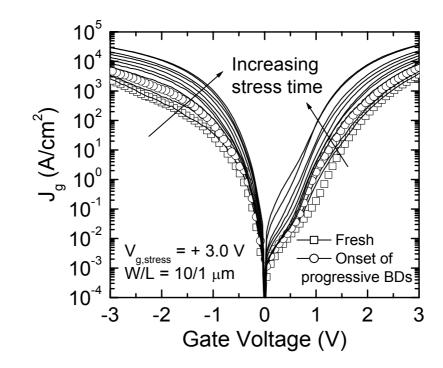

| Fig. 6.12 | Evolution of current-voltage characteristics at fresh and after constant voltage stressing ( $V_{stress} = + 3.0 \text{ V}$ ). ( $T_{ox} = 13.4 \text{ Å}$ , Channel Area = 10 $\mu$ m <sup>2</sup> , p-MOSFET)131                                                                                                                                                                                                                     |

| Fig. 6.13 | (a) Percentage change in gate leakage current under different stressing gate voltage<br>in the initial stage of PBDs. (b) In the subsequent PBDs stages, leakage current<br>proportional to logarithmic of stressing time. It can be observed that gate leakage<br>current follow a power relation with stressing time in the initial stage (a) and a<br>linear logarithmic time dependence as shown inset in the subsequent stage (b) |

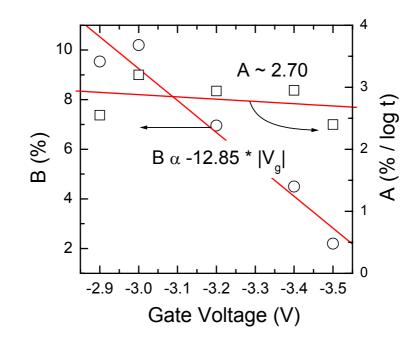

| Fig. 6.14 | Graph showing gate leakage current time dependence parameters A and voltage dependence parameter, B as defined in (1) for 2nd stage of PBDs versus stressing gate voltage. (Channel Area = $100 \ \mu m^2$ , p-MOSFET)                                                                                                                                                                                                                 |

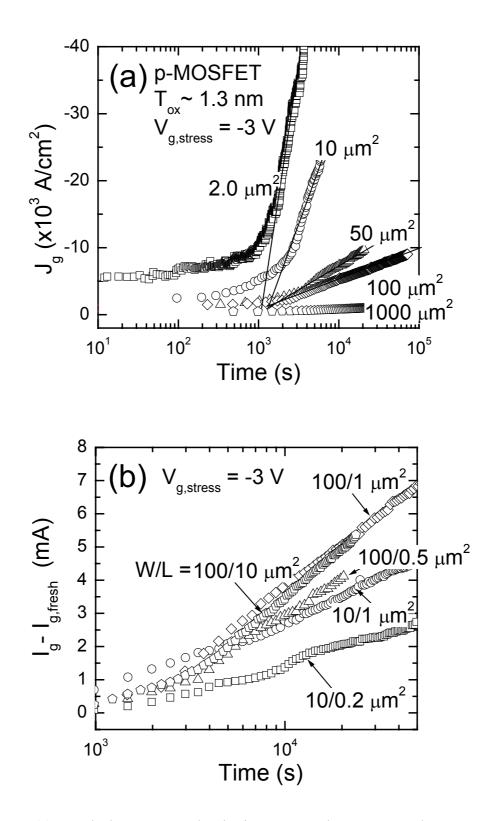

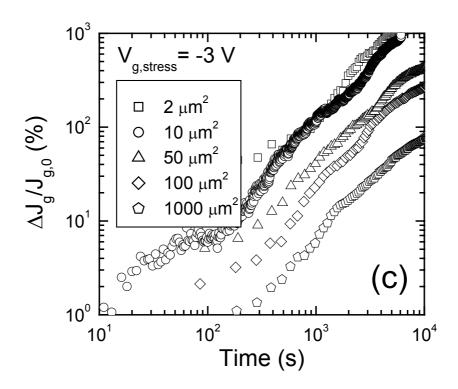

| Fig. 6.15 | (c) Percentage increase in gate leakage current after onset of 2nd stage PBDs for different sample areas                                                                                                                                                                                                                                                                                                                               |

| Fig. 6.16 | Degradation rate or defect generation rate defined by $Jg = Pg * Qinj$ where Pg is<br>the defect generation / gate degradation rate as shown for second stage of PBDs. It<br>can be observed that gate degradation increase as sample area decreases with<br>eventual saturation at very small area                                                                                                                                    |

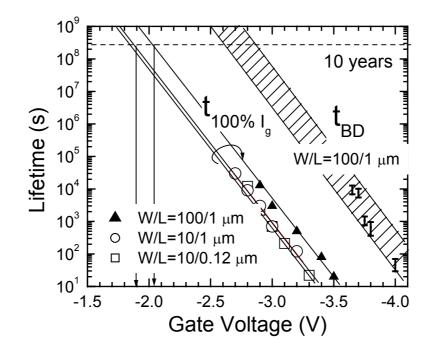

| Fig. 6.17 | Lifetime projection versus stressing gate voltage using 100% increase in gate leakage current as failure criterion. Lifetime for 100% increase in gate leakage $t_{100\%}$                                                                                                                                                                                                                                                             |

|           | $_{Ig}$ is much shorter than the conventional time-to-complete breakdown $t_{BD}$ . ( $T_{ox} = 13.4 \text{ Å}$ , p-MOSFET)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

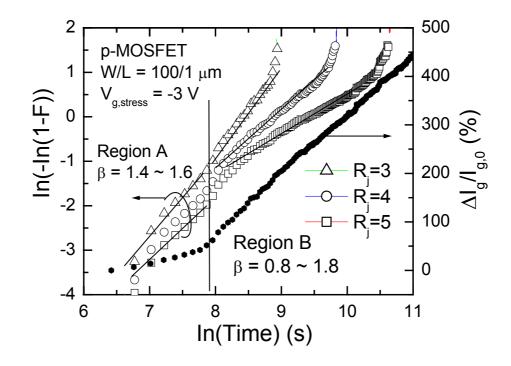

| Fig. 6.18 | Evolution of normalized gate leakage current $(I_g - I_{g,0})/I_{g,0}$ on a 13.4 Å gate oxide<br>when stressed under constant voltage stress (as shown by the solid symbol). Using<br>(5.6), the cumulative frequency of localized spots occurrence F(t) can be determined<br>and it's associated Weibull plot (with various values of Rj) versus logarithmic of<br>stressing time is as shown ( shown by the various open symbols). It can be observed<br>that the derived Weibull plots can be separated into 2 regions, A & B. The derived<br>Weibull shows a good linearity when $Rj = 3$ for both region A and B, deviating only<br>at the extreme short and long stressing time due to censoring effects |

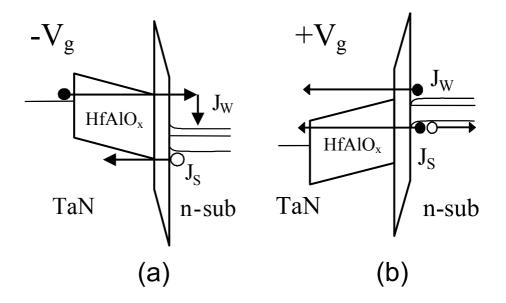

| Fig. 7.1  | Energy band diagram and tunneling current components for p-MOSFET with metal gate under (a) inversion (negative gate bias) and (b) accumulation (positive gate bias) conditions. The dominant components of gate currents under both polarities are the ones which tunnel through the IL: Js under $-V_g$ and Jw under $+V_g$ 151                                                                                                                                                                                                                                                                                                                                                                              |

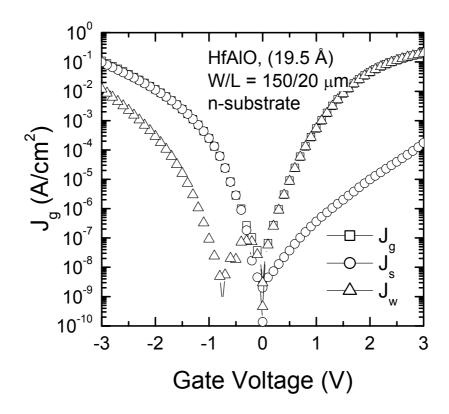

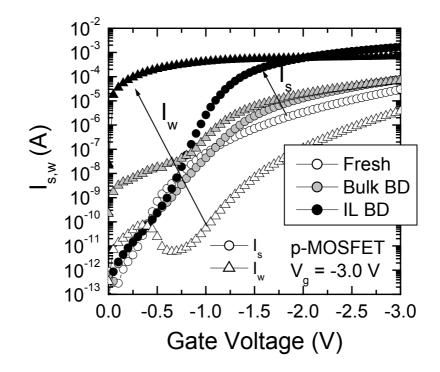

| Fig. 7.2  | $J_g$ - $V_g$ characteristics of p-MOSFETs with HfAlO dielectrics. Source and n-well are grounded. The dominant components of gate currents under both polarities are the ones which tunnel through the IL: $J_s$ under – $V_g$ and $J_w$ under + $V_g$                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

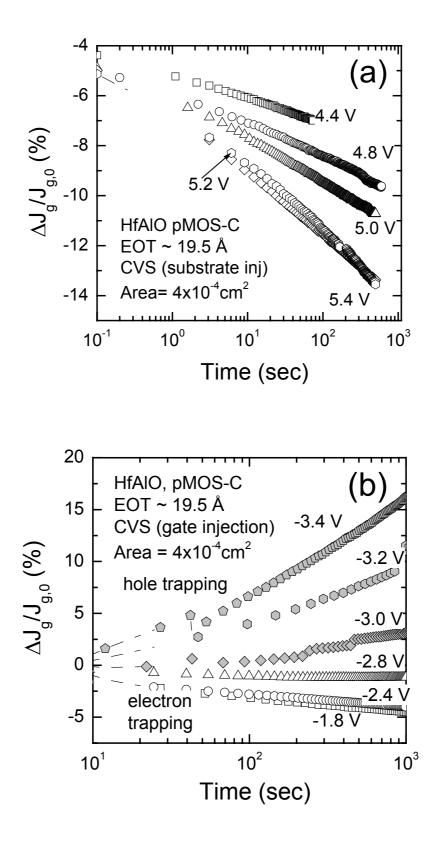

| Fig. 7.3  | Charge trapping characteristics (a) under positive V <sub>g</sub> , and (b) negative V <sub>g</sub> . Positive bias stress causes electron trapping, while negative bias stress results in hole trapping for $ V_g  > -3$ V. Sample area is 100 x 100 $\mu$ m <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                     |

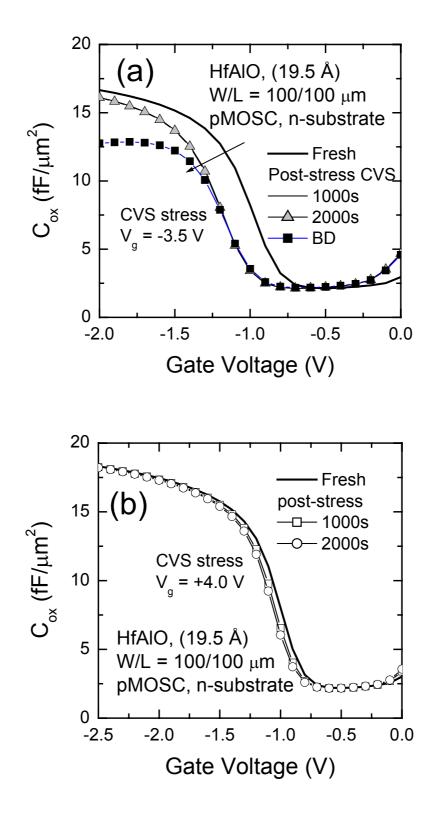

| Fig. 7.4  | Inversion capacitance-voltage curves of p-MOSFETs before and after stress under<br>(a) negative gate bias and (b) positive gate bias for a period of 1000 s and 2000 s. A<br>flatband voltage shift to the left after negative bias stress shows positive charge<br>trapping within the dielectric and IL                                                                                                                                                                                                                                                                                                                                                                                                      |

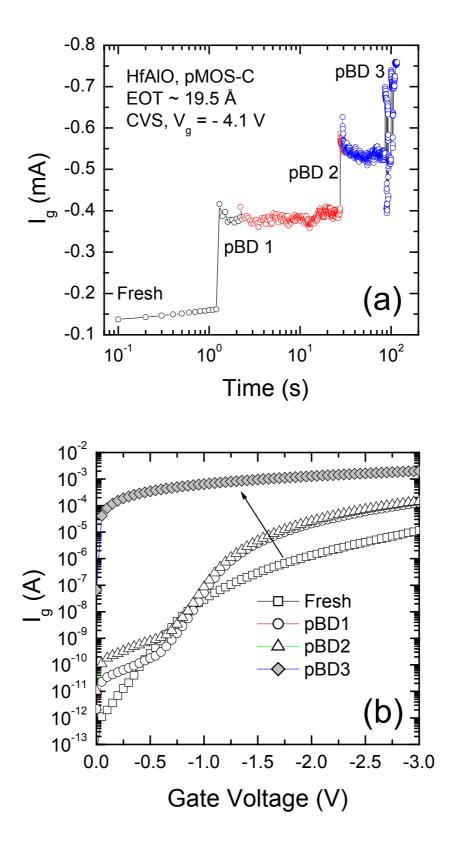

| Fig. 7.5  | (a) Evolution of gate leakage current in p-MOSC and (b) evolution of current-voltage characteristics under negative constant voltage stress. It can be observed that there are at least 2 distinct stages of breakdown as shown by pBD1, pBD2 and pBD3. Area of sample used is $100 \times 100 \mu m^2$                                                                                                                                                                                                                                                                                                                                                                                                        |

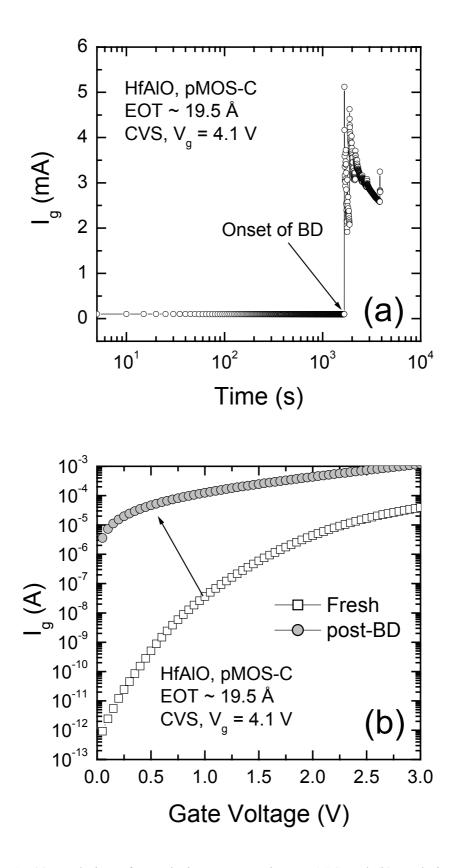

| Fig. 7.6  | (a) Evolution of gate leakage current in p-MOSC and (b) evolution of current-voltage characteristics under positive constant voltage stress. It can be observed that there are only 1 distinct stages of breakdown. Area of sample used is 100 x 100 $\mu m^2$                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

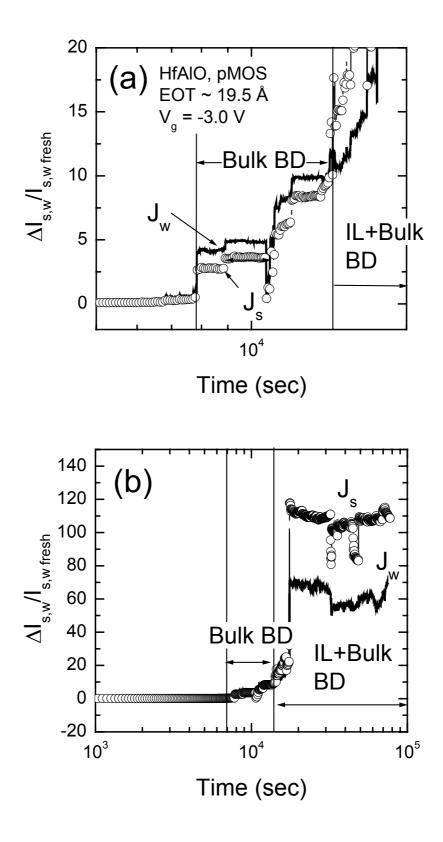

| Fig. 7.7  | (a) Relative changes of Js and Jw currents during negative CVS ( $V_g = -3.0$ V) on p-MOSFET. (b) Identical data with (a) but plotted in wider scale. The high-K bulk breakdown happens first at the initial stage of breakdown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Fig. 7.8  | Associated (J-V characteristics) carrier separation measurement of Fig. 6.8, showing both source and well current component before and after bulk BD and IL BD. It can be observed that at the first onset of Bulk BD (shown by shaded symbols), J <sub>w</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           | increases significantly throughout the entire range of gate voltage while $J_s$ , which reflect the IL condition, increases only marginally. Subsequent occurrence of IL BD (shown by solid symbols), result in significant increase in both $J_s$ and $J_w$                                                                                                                                                                                                                                                                                                                                                    | 3 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

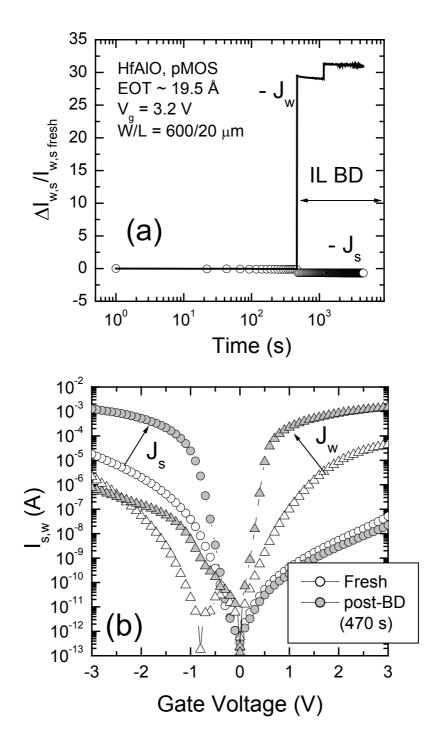

| Fig. 7.9  | (a) Relative changes of $J_s$ and $J_w$ currents during positive CVS ( $V_g = +3.2$ V) on p-MOSFET. Only interfacial layer breakdown observed after about 470s of stressing, shown by the larger increase in $J_w$ . (b) Associated I-V characteristics after positive CVS but measured under both negative and positive gate voltage regime. The IL leakage currents have increased by orders of magnitude, while the bulk leakage current did not increase significantly due to the intact high- <i>K</i> bulk layer                                                                                          | 5 |

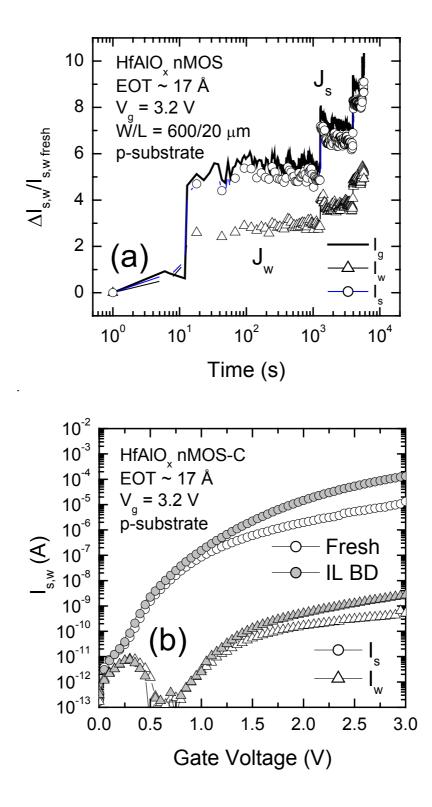

| Fig. 7.10 | (a) Relative changes of Js and Jw currents during positive CVS (Vg = $3.2$ V) on n-<br>channel MOSFET and (b) its associated J-V characteristics. The dominant electron<br>current, J <sub>s</sub> , increase faster than that of the subservient well current, J <sub>w</sub> , which reflect<br>the valence electron current. At onset of breakdown after stressing for 15 s,<br>interfacial layer breaks down, which translate to much higher leakage current for Js<br>while the well leakage current J <sub>w</sub> which tunnel through a thicker portion of the high-<br><i>K</i> layer is less affected | 7 |

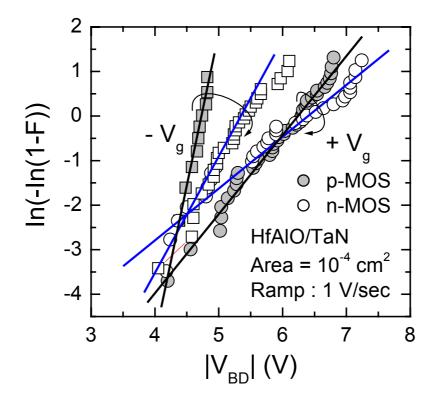

| Fig. 7.11 | Weibull distributions for $V_{BD}$ under ramped gate voltage sweep for p-channel MOS capacitors (shown by shaded symbols) and n-channel MOS capacitors (shown by open symbols) with source/drain implant. The Weibull slope for breakdown voltage $V_{BD}$ under $-V_g$ sweep is much steeper than that for $+V_g$ sweep for both n-channel and p-channel MOS.                                                                                                                                                                                                                                                  | 9 |

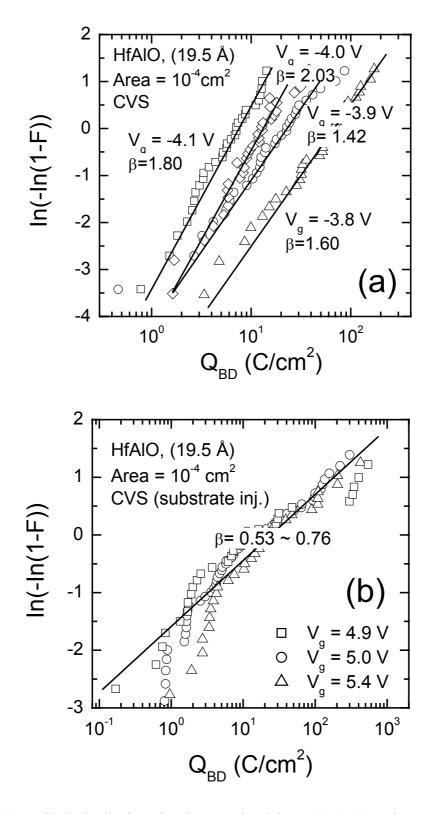

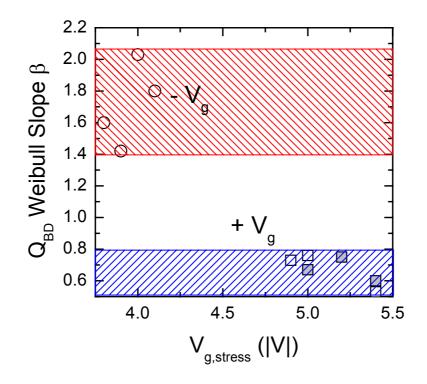

| Fig. 7.12 | Weibull distributions for charge-to-breakdown (QBD) (a) under negative constant voltage stresses and (b) under positive constant voltage stresses. It is observed that Weibull distribution for $+V_g$ CVS deviates from the linear line at low QBD for higher gate bias stressing due to temporal resolution of measurement setup, especially for early failure devices with low time-to-breakdown. High $\beta$ (Weibull slope) value under $-V_g$ and low $\beta$ value under $+V_g$ are observed. Sample area is 100 x 100 $\mu$ m <sup>2</sup>                                                             | 2 |

| Fig. 7.13 | Weibull distributions for charge-to-breakdown ( $Q_{BD}$ ) on p-channel MOS capacitors<br>under (a) negative constant voltage stresses and (b) under positive constant voltage<br>stresses. Reasonably high $\beta$ (Weibull slope) value under $-V_g$ CVS and low $\beta$ value<br>under $+V_g$ CVS are observed. Sample area is $10^{-4}$ cm <sup>2</sup>                                                                                                                                                                                                                                                     | 3 |

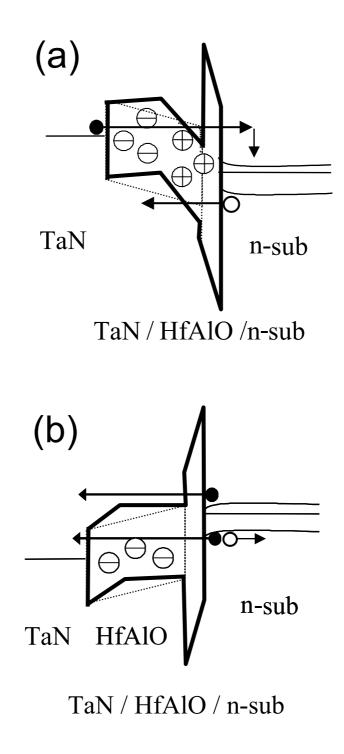

| Fig. 7.14 | A schematic drawing for a breakdown model using charge trappings at different spatial locations in high- <i>K</i> /IL stack dielectric with a metal gate structure. (a) For - $V_g$ , electron trapping occurs mainly in the bulk while hole trapping occurs near to the IL. The columbic force of the trapped charges distorts the energy band diagram, leading to a preferential breakdown in the bulk. (b) For + $V_g$ , only electron trapping occurs. The band distortion in the high-K bulk would be smaller, leading to higher possibilities of interfacial layer breakdown                              | 4 |

# List of Tables

| Table 1.1 | Selected data from latest ITRS 2003 update (After [1.2])                       | 3   |

|-----------|--------------------------------------------------------------------------------|-----|

| Table 2.2 | Summary of quasi-breakdown conduction mechanism                                | 19  |

| Table 6.1 | A summary of criteria for determining the dominant breakdown mechanism for all |     |

|           | the possible combinations of gate bias in both n- and p- MOSFETs               | 166 |

# Introduction

# 1.1 Dimension Scaling and Future Trends of Microelectronics

Microelectronics is becoming an important and integral part of modern living. It is interesting to note that in almost every part of our lives, including medical, transport, entertainment, communication and military defense, electronics is invariably present. The increasing miniaturization of electronics to even smaller sizes, through device scaling, novel process fabrication and device structures to its ultimate limit - nano dimensions, introduces changes, which were previously unimaginable. Nanoscience engineering provides new knowledge and capability to design and build materials at atomic scale. Yet these changes require tremendous engineering ingenuity, and researches into such new materials and its underlying science, are imperative.