## STRESS-INDUCED LEAKAGE CURRENT IN DUAL-GATE CMOSFETS WITH THIN NITRIDED GATE OXIDES

HUANG JINSHENG (B. Sc, PKU)

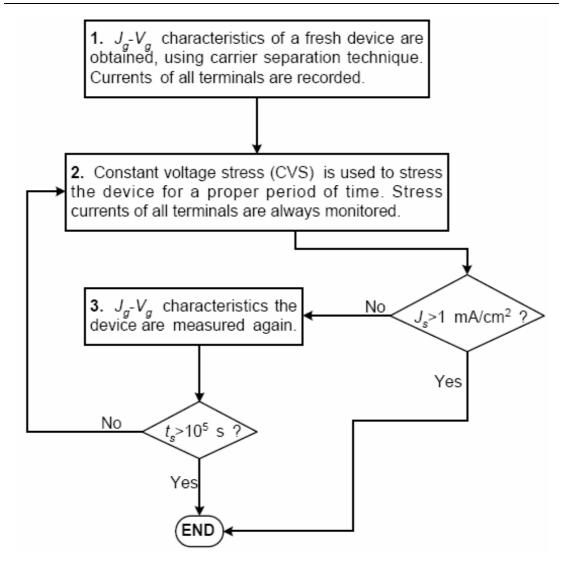

A THESIS SUBMITTED FOR THE DEGREE OF MASTER OF ENGINEERING DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING NATIONAL UNIVERSITY OF SINGAPORE 2004

## ACKNOWLEDGEMENTS

I would like to express my deepest thanks to my supervisors, Professor Ling Chung Ho and Dr Ang Diing Shemp, for their guidance, support and trust in the past three years, without which it would be impossible for me to complete this thesis.

My gratitude must also go to Madam Ah Lian Kiat, my ex-colleague in the MOS Device Lab. Her knowledge and experience in the facilities as well as her kindness made the lab an excellent place to work in. Sincerely, I would like to extend my gratitude to Mr. Lun Zhao, Xia Jinghua, Tan Swee Tian and Timothy Phua and others, for all the help in one way or another during the days in MOS Device Lab.

I would like to say "thank you" to all the friends I met in Singapore in the past three years, without whom the life here would have never been such a wonderful one.

Last but not least, my gratitude goes to the most important persons in my life, my parents, my sisters, my brother and my wife, Yanping. Their understanding, patience, and support have carried me through all the difficult times. I feel so blessed to live in this family.

Huang Jinsheng

## **Table of Contents**

| Acknowledgements  | i   |

|-------------------|-----|

| Table of Contents | ii  |

| Summary           | v   |

| List of Figures   | vii |

| List of Symbols   | xii |

| Nomenclatures     | xiv |

| Char | pter One. Introduction and Literature Survey     |    |

|------|--------------------------------------------------|----|

| 1.1  | Gate Oxide Scaling and Reliability               | 1  |

| 1.2  | Intrinsic Leakage Currents in Gate Oxides        | 3  |

| 1.3  | Stress-Induced Leakage Currents in Gate Oxides   | 5  |

|      | 1.3.1 General Physical Characteristics of SILC   | 6  |

|      | 1.3.2 Major Physical Models of SILC              | 9  |

|      | 1.3.3 Stress-Induced Traps in Oxides             | 15 |

|      | 1.3.4 Recent Advances of SILC                    | 17 |

| 1.4  | SILC and Oxide Degradation in Scaled Gate Oxides | 19 |

| 1.5  | Motivation of This Work                          | 21 |

| 1.6  | Organization of Thesis                           | 22 |

| Refe | rences                                           | 23 |

ii

### Chapter Two. Experiment Techniques

| 2.1    | Device Preparation 3                  |    |

|--------|---------------------------------------|----|

| 2.2    | .2 Major Experimental Procedures      |    |

|        | 2.2.1 Carrier Separation Technique    | 37 |

|        | 2.2.2 Constant Voltage Stress         | 42 |

|        | 2.2.3 Substrate Hot Carrier Injection | 43 |

| 2.3    | Summary                               | 44 |

| Refere | ences                                 | 45 |

### Chapter Three. SILC in p+/pMOSFET with Ultrathin Nitrided Gate Oxides

| 3.1        | Introduction                                    | 46 |

|------------|-------------------------------------------------|----|

| 3.2        | Electrons and Holes in the Gate Leakage Current | 47 |

| 3.3        | Gate SILC in p+/pMOSFETs                        | 51 |

| 3.4        | Hole SILC                                       | 55 |

| 3.5        | Hole SILC vs. Electron SILC                     | 58 |

| 3.6        | Physical Model of Hole-Dominant SILC            | 62 |

| 3.7        | Summary                                         | 69 |

| References |                                                 | 70 |

### Chapter Four. SILC in n+/nMOSFET with Ultrathin Nitrided Gate Oxides

| 4.1 | Introduction                                | 72 |

|-----|---------------------------------------------|----|

| 4.2 | Gate Leakage Currents in Virgin n+/nMOSFETs | 73 |

| 4.3 | SILC in n+/nMOSFETs                         | 73 |

| 4.4    | Summary | 81 |

|--------|---------|----|

| Refere | nces    | 82 |

## Chapter Five. Degradation of Ultrathin Nitrided Gate Oxides

| 5.1        | Introduction                               | 83 |

|------------|--------------------------------------------|----|

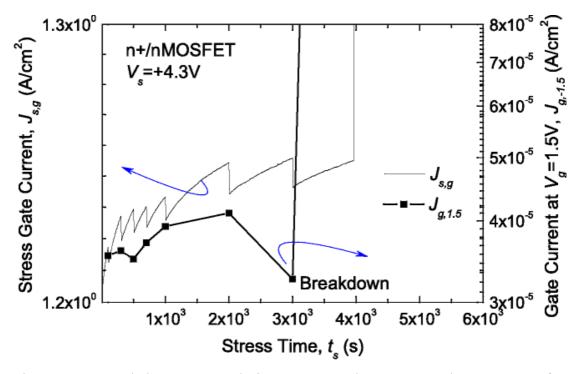

| 5.2        | Gate Stress Current and Gate Sense Current | 83 |

| 5.3        | SILC Generation and Oxide Degradation      | 85 |

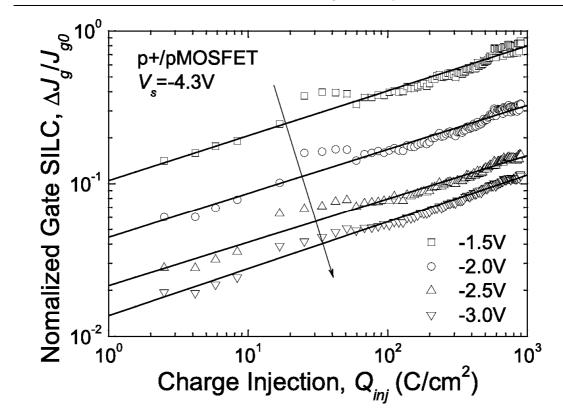

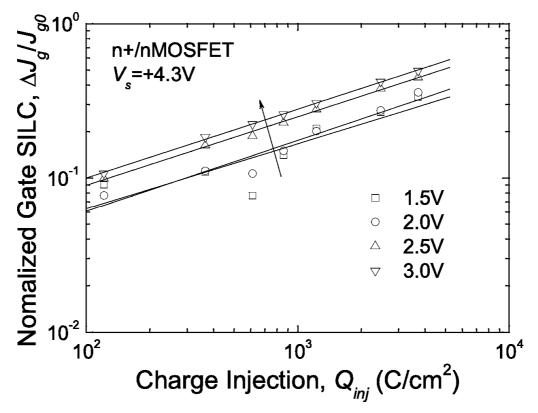

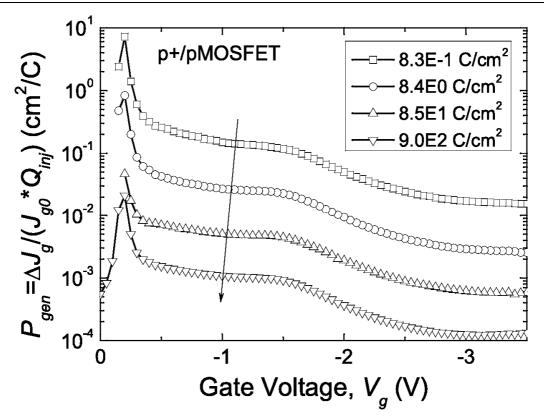

| 5.4        | Driving Force of Oxide Degradation         | 90 |

| 5.5        | Summary                                    | 91 |

| References |                                            | 92 |

## Chapter Six. Conclusions and Future Work

| 6.1 | Conclusions | 93 |

|-----|-------------|----|

| 6.2 | Future Work | 94 |

## SUMMARY

Beginning with a brief review of the literature about stress-induced leakage current (SILC), a study of the SILC in the dual-gate CMOSFET with 2.2 nm nitrided gate oxide has been presented, from the observation of the evolution of hole and electron current components.

In the p+/pMOSFET, the hole component of the SILC dominates over the electron component, and such dominance is enhanced continuously during stress. A physical model, featuring two separate energy distributions of oxide traps and favoring hole tunneling in the p+/pMOSFET, is proposed to explain the observed evolution of hole current and electron current components. Oxide trap localization near the substrate valence band is probably responsible for the dominance of hole current. Such a localized trap distribution could be generated by hole injection into the gate oxide. The proposed physical model is consistent with the established TAT framework for SILC

In the n+/nMOSFET, SILC is found to be dominated by the conduction-band electron tunneling, which is attributed to the trap-assisted tunneling (TAT) mechanism facilitated by a heavily one-sided stress-induced trap distribution, localized near the substrate conduction band edge.

Degradation of the ultrathin gate oxide process can be well visualized by the generation and increase of SILC. Before oxide breakdown happens, both p+/pMOS and n+/nMOS demonstrated the partial recovery of degradation after the withdrawal of stress voltage but before the oxide breakdown. A solid correlation exists between degradation rate of the gate oxide and charge injection. The sharp decrease of SILC generation

probability at high charge injection indicates that neutral oxide trap generation tends to saturate at high stress level.

## LIST OF FIGURES

- Figure 1.1 Illustration of two major tunneling mechanisms: (left) Fowler-Nordeim Tunneling and (right) Direct Tunneling.

- Figure 1.2 Intrinsic gate leakage current in dual-gate CMOSFETs with different oxide thickness. Measurement was done under inversion mode. The characteristics for both p+/pMOS (solid lines) and n+/nMOS (dashed lines) are shown.

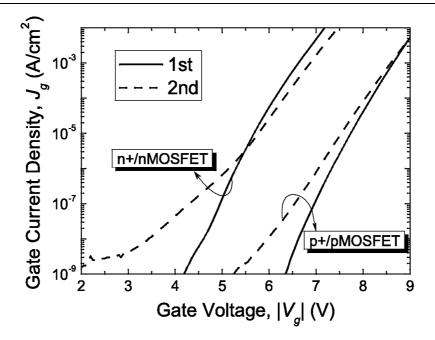

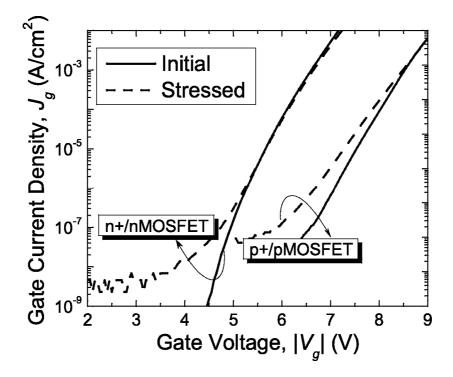

- Figure 1.3 SILCs in dual-gate CMOSFETs with 5.9 nm oxide. For each type of device, two  $J_g$ - $V_g$  measurements are taken successively, and the excess leakage current appears in the second curve (dashed line). The gate voltage was gradually increased from 0 to as high as 9.0 V (-9.0 V) for n+/nMOSFET (p+/pMOSFET).

- Figure 1.4 SILCs in dual-gate CMOSFETs with 5.9 nm oxide.  $J_g$ - $V_g$  measurements are taken before (solid lines) and after (dashed lines) constant voltage stress. The devices are the same as those of Figures 1. The n+/nMOSFET and p+/pMOSFET were stressed at +7 V and -8.5 V respectively, for 100 s.

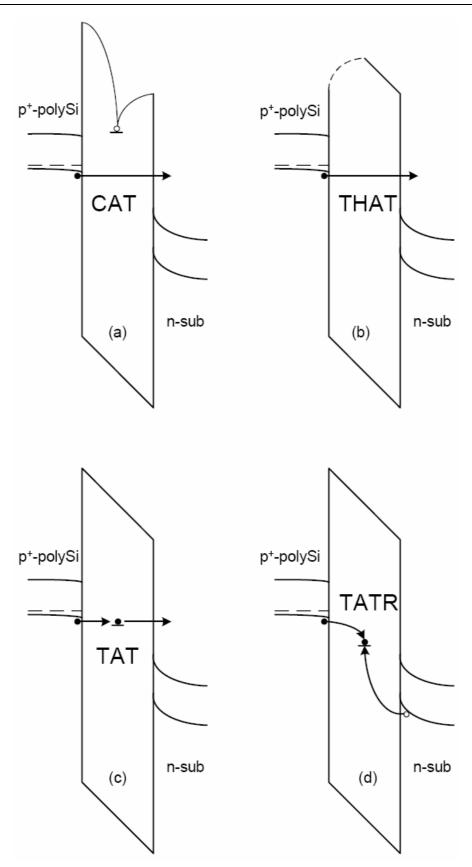

- Figure 1.5 Schematic diagrams illustrating four typical tunneling mechanisms that have proposed to explain the SILC.

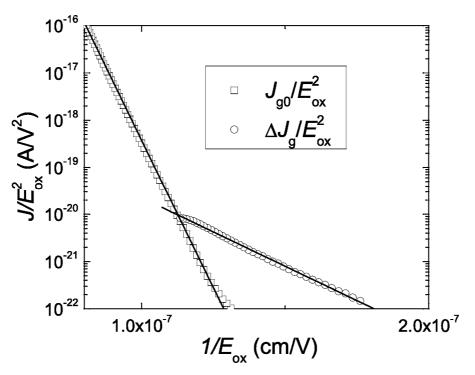

- Figure 1.6 FN plots of virgin FNT current and SILC, for an n+/nMOSFET with  $T_{ox} = 5.9$  nm. Device dimensions: W = 20  $\mu$ m, L = 20  $\mu$ m, T<sub>ox</sub> = 5.9 nm.

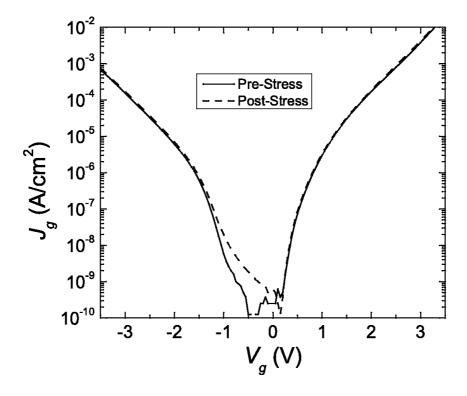

- Figure 1.7  $J_g$ - $V_g$  characteristics of an n+/nMOSFET. The solid and dashed lines denote the pre-stress and post-stress characteristics respectively. The gate voltage was swept from negative to positive during measurement. Device dimensions:  $T_{ox} = 2.2$  nm, W = 40 µm, L = 20 µm.

- Figure 2.1 A CVS/measurement procedure for characterizing the SILC in ultrathin gate oxides. Note that  $t_s$  stands for cumulative stress time and  $J_s$  stands for the gate current measured during the stress.

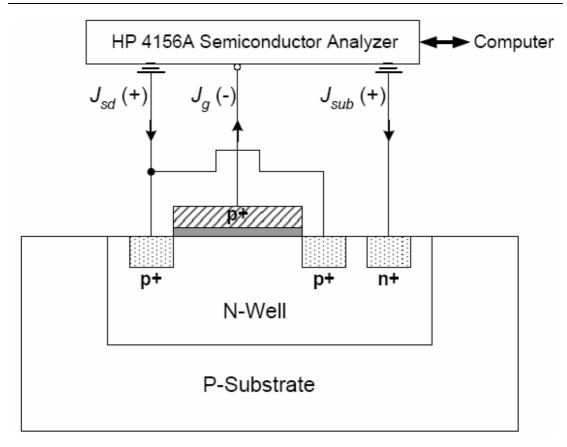

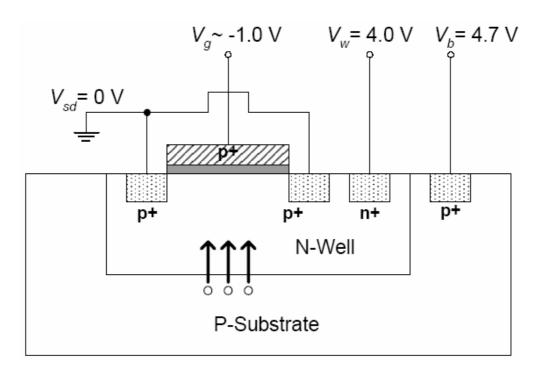

- Figure 2.2 A schematic diagram of the experimental configuration used for both constant voltage stress and carrier separation measurement, for a p+/pMOSFET. The cycling procedure is controlled by a computer. In this thesis, currents following into the transistor are always defined as positive, while those flowing out of the transistor are defined as negative.

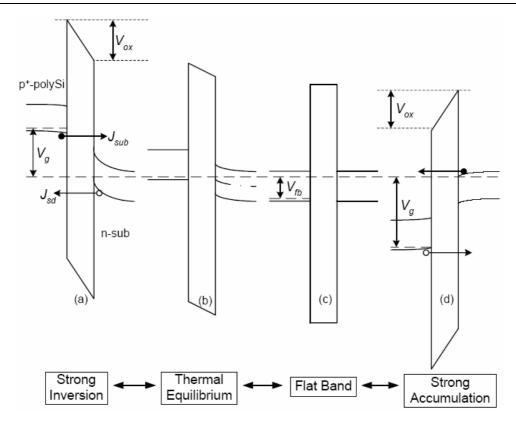

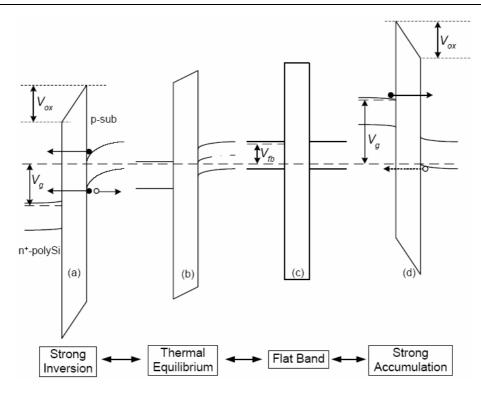

- Figure 2.3 Energy band diagrams illustrating the p+/pMOSFET transiting from strong inversion to thermal equilibrium, to flat-band, and to strong accumulation.

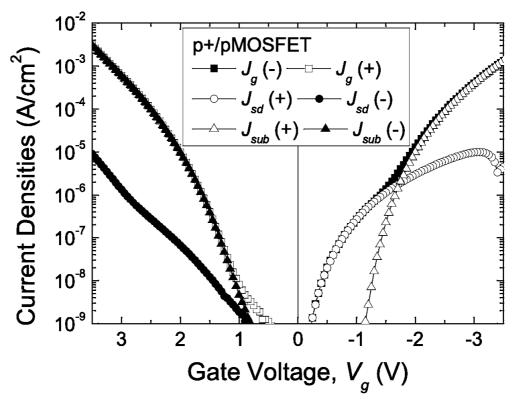

- Figure 2.4 Carrier separation measurement results of a p+/pMOSFET. Solid and open symbols denote positive and negative current, respectively. Device dimensions:  $T_{ox} = 2.2$  nm,  $W = 40 \mu m$ ,  $L = 20 \mu m$ .

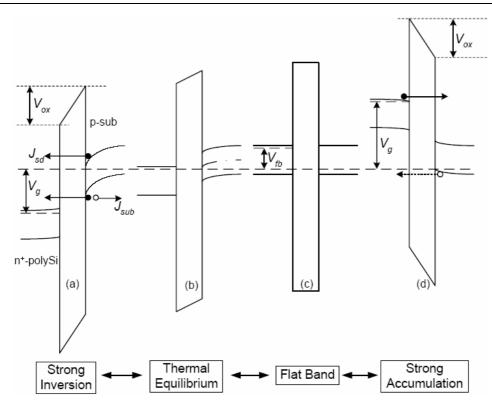

- Figure 2.5 Energy diagrams illustrating the n+/nMOSFET transiting from strong inversion to thermal equilibrium, to flat-band, and to strong accumulation.

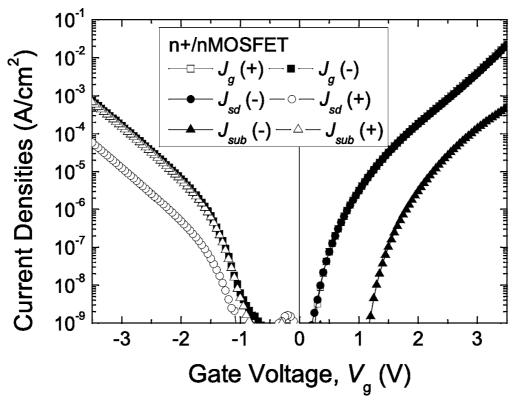

- Figure 2.6 Carrier separation measurement results of an n+/nMOSFET. Solid and open symbols denote positive and negative current, respectively. Device dimensions:  $T_{ox} = 2.2$  nm,  $W = 40 \mu m$ ,  $L = 20 \mu m$ .

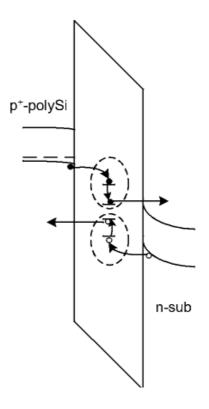

- Figure 2.7 Schematic illustration of substrate hot-hole injection. The source and drain are grounded. Both n-well and p-substrate are biased at high positive voltage ( $V_w$  and  $V_b$  respectively), with the latter 0.7 V higher than the former.

- Figure 3.1 Energy band diagrams illustrating the transition from strong inversion to strong accumulation of a p+/pMOS structure.

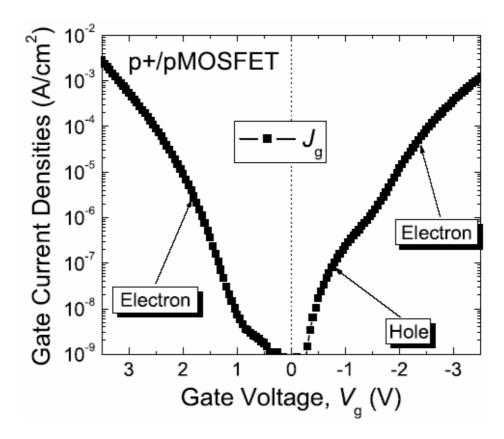

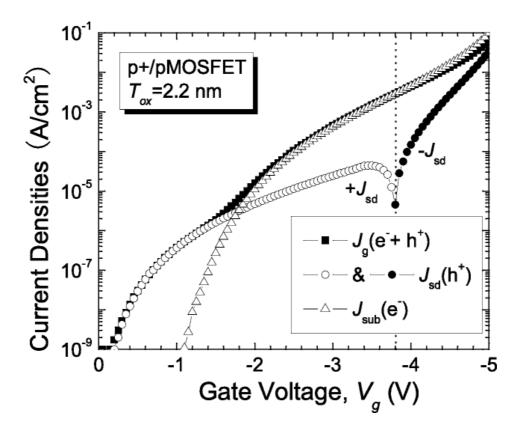

- Figure 3.2 Gate tunneling leakage current of a p+/pMOSFET with ultrathin gate oxide as the function of gate voltage, from strong accumulation to strong inversion. Device dimension: W= 40  $\mu$ m, L = 20  $\mu$ m, T<sub>ox</sub> = 2.2 nm.

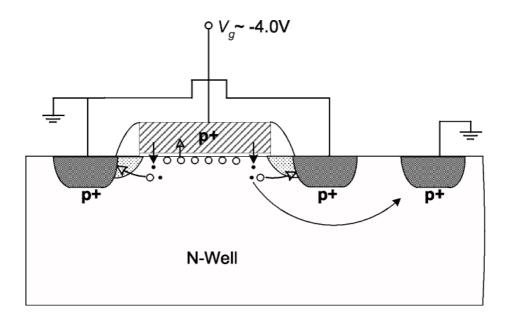

- Figure 3.3 Schematic diagrams showing the transition of gate bias from low-negative voltage to impact-ionization region in a p+/pMOS.

- Figure 3.4 Carrier separation curves of a p+/pMOSFET with the gate voltage swept from zero bias to the strong impact ionization regime (in inversion region). Solid and open circles denote positive and negative currents, respectively.

- Figure 3.5 Impact ionization in the substrate surface induced by highly energetic electrons, which originated from the valence band of the p+ gate.

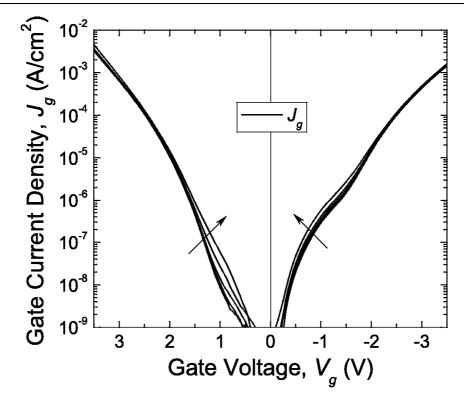

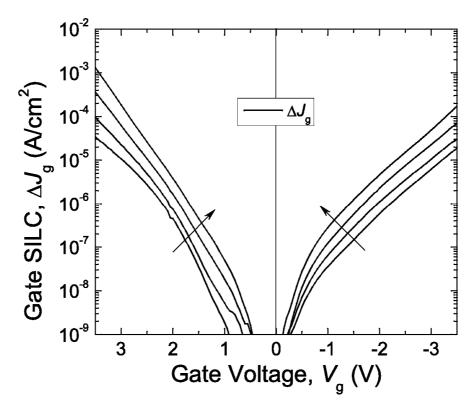

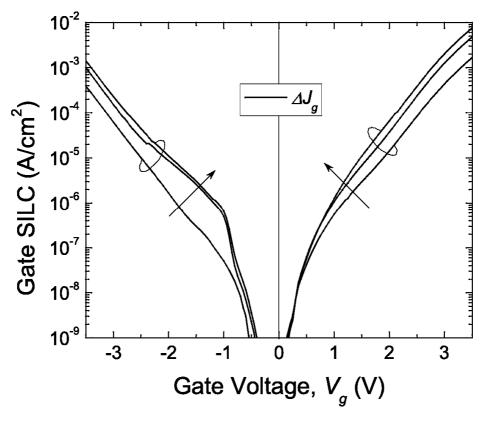

- Figure 3.6 Shift in the gate leakage characteristics of a p+/pMOSFET after 4 cumulative stress intervals:  $10^2$ ,  $10^3$ ,  $10^4$  and  $10^5$  seconds (along the direction of the arrows).

- Figure 3.7 Gate SILC of a p+/pMOSFET as a function of the sense voltage, with stress time as the parameter. The SILC is obtained from the  $J_g$ - $V_g$  characteristics in Figure 3.6.

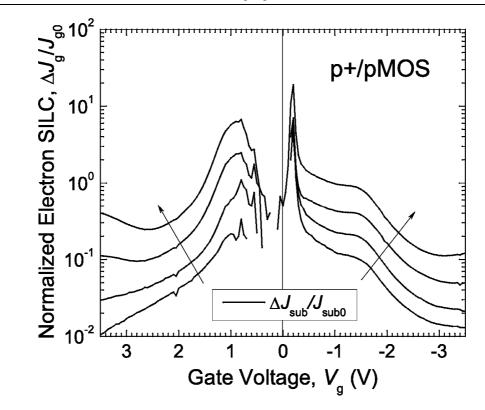

- Figure 3.8 Normalized gate SILC of a p+/pMOSFET as a function of the sense voltage, with stress time as the parameter. The normalized SILC is obtained from the  $J_g$ - $V_g$  characteristics in Figure 3.6.

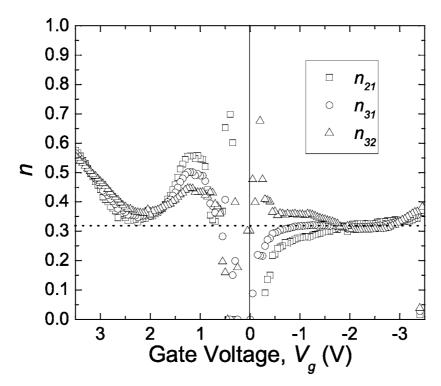

- Figure 3.9 Power-law exponent *n*, where *n* is as defined in the relation  $\Delta J_g = f(V_g) \cdot t^n$ , as a function of the sense voltage. Note that  $n_{21} = n(t_2, t_1)$ ,  $n_{31} = n(t_3, t_1)$ ,  $n_{32} = n(t_3, t_2)$ , with  $t_1 = 10^3$  s,  $t_2 = 10^4$  s,  $t_3 = 10^5$  s.

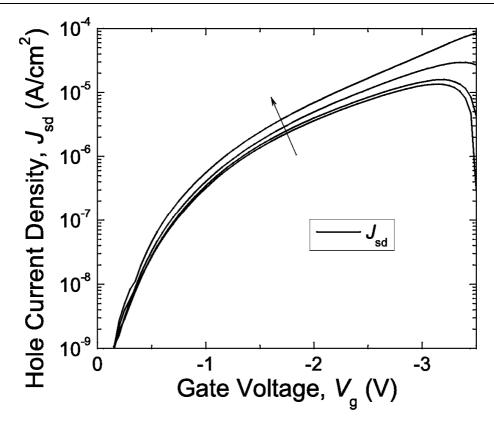

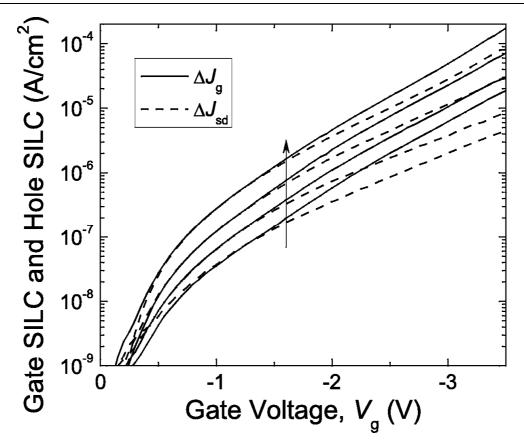

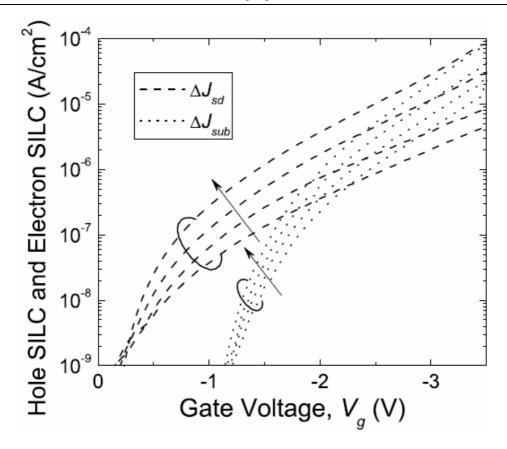

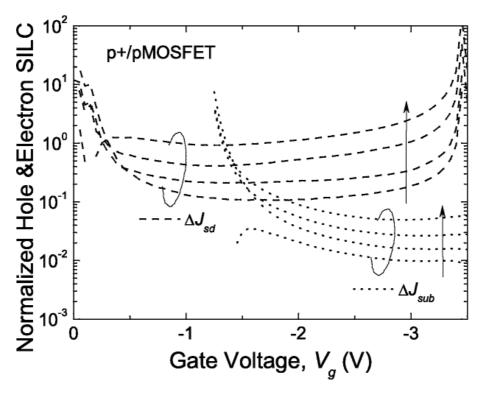

- Figure 3.10 Increase in the hole tunneling current in a p+/pMOSFET subjected to constant voltage stress, in respect to the gate SILC shown in Figure 3.7. The stress time increases in the direction of the arrow.

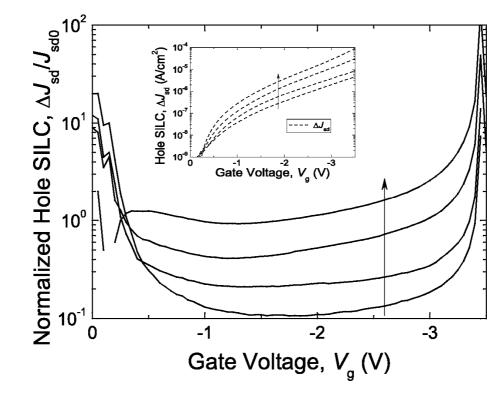

- Figure 3.11 Normalized hole SILC in p+/pMOSFET as a function of the gate sense voltage, after different stress intervals. The normalized SILC curves are obtained based on the data in Figure 3.10.

- Figure 3.12 Gate and hole SILC as a function of the gate sense voltage with stress time as the parameter.

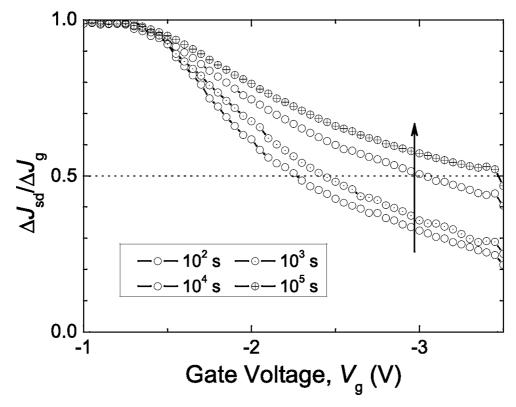

- Figure 3.13 The fraction of hole current component in the overall gate SILC  $(\Delta J_{sd}/\Delta J_g)$  as a function of the gate sense voltage, with stress time as the parameter.

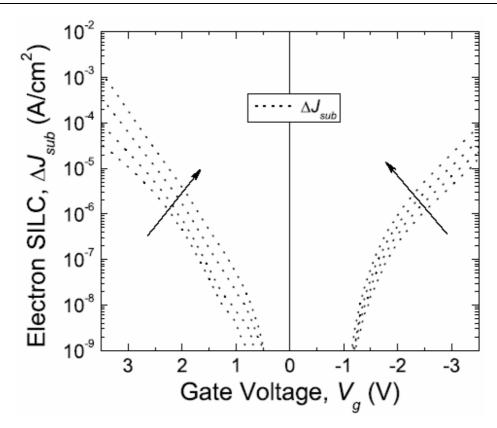

- Figure 3.14 Electron SILC as a function of gate sense voltage, for the accumulation and inversion regions. Stress time increases in the direction of the arrow.

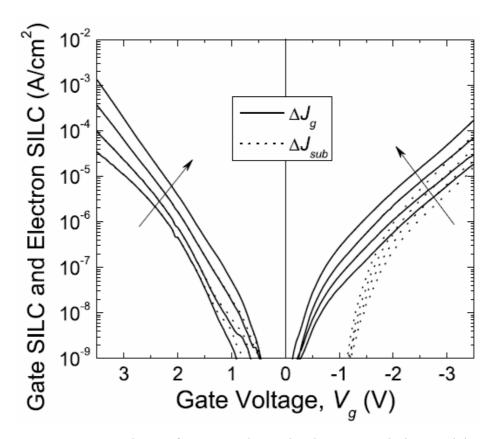

- Figure 3.15 A comparison of  $\Delta J_{sub}$  and  $\Delta J_g$  in the accumulation and inversion regions.

- Figure 3.16 A comparison of hole SILC  $\Delta J_{sd}$  and electron SILC  $\Delta J_{sub}$  in the inversion region, for different stress time.

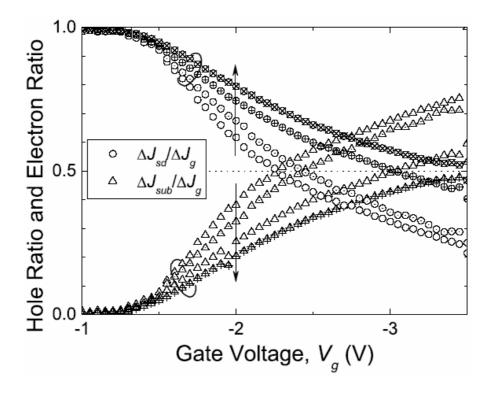

- Figure 3.17 Normalized hole SILC (circles) and electron SILC (triangles) characteristics, with the stress time as the parameter.

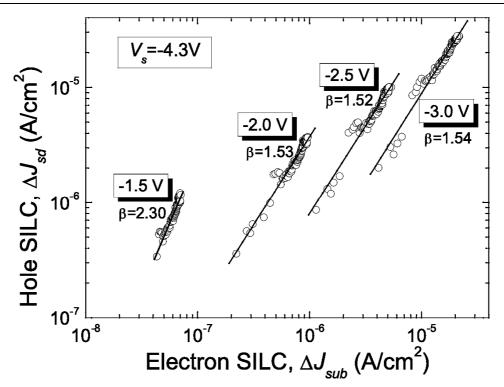

- Figure 3.18 The correlation between hole SILC and electron SILC for different gate sense voltages. The relation between these two components can be well described by a power-law expression. The gate sense voltages and the power-law exponents are given in the figure accordingly. Stress voltage  $V_s = -4.3$  V.

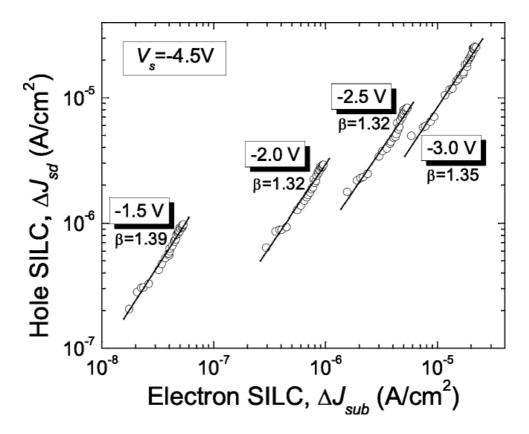

- Figure 3.19 Similar to Figure 3.18, except that stress voltage is higher at -4.5 V.

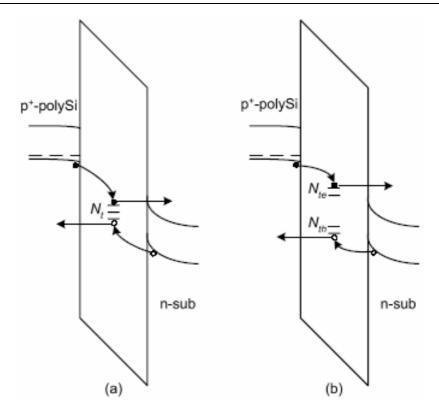

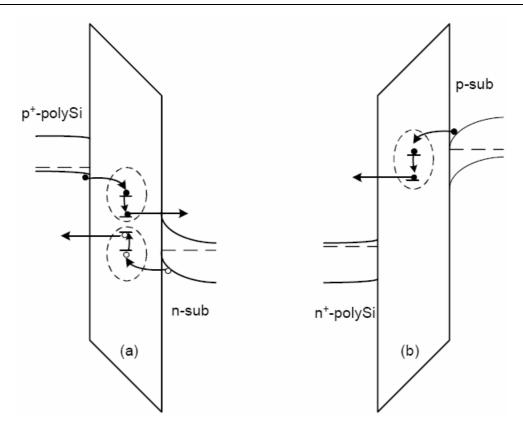

- Figure 3.20 Schematic illustration of two TAT conduction mechanisms: electron tunneling and hole tunneling via: (a). a common oxide trap distribution [13]; (b) two separate oxide trap distribution.

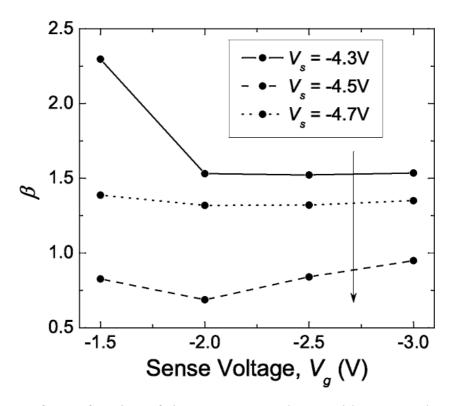

- Figure 3.21  $\beta$  as a function of the gate sense voltage, with stress voltage as the parameter.

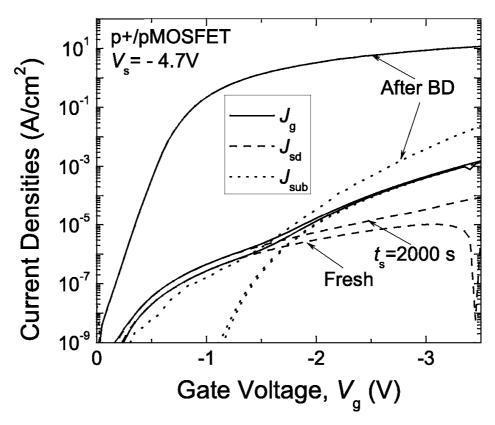

- Figure 3.22 Carrier separation curves for p+/pMOSFET after three stress intervals:  $t_s = 0$  (fresh device),  $t_s = 2000$  s and  $t_s = 2900$  s. The stress voltage is at -4.7 V.

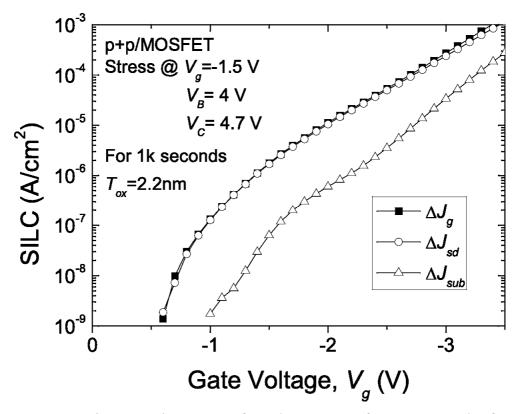

- Figure 3.23 Carrier separation curves of a p+/pMOSFET after 1000 seconds of SHH injection. Stress parameters are indicated in this figure.

- Figure 3.24 TAT process involving multiple steps. An electron (hole) tunnel from a shallow trap to a deep trap before it tunnels out to the conduction (valence) band.

- Figure 4.1 Energy band diagrams illustrating the transition from strong inversion to strong accumulation mode of an n+/nMOS device.

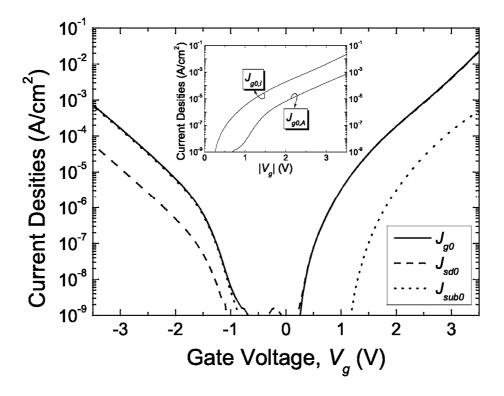

- Figure 4.2 Gate leakage current of an n+/nMOSFET with ultrathin gate oxide as a function of gate voltage, from strong accumulation to strong inversion.. In the inset,  $J_{g0,I}$  and  $J_{g0,A}$  denote gate leakage current in the inversion and accumulation region, respectively. Device dimensions: W = 40  $\mu$ m, L = 20  $\mu$ m, T<sub>ox</sub>= 2.2 nm.

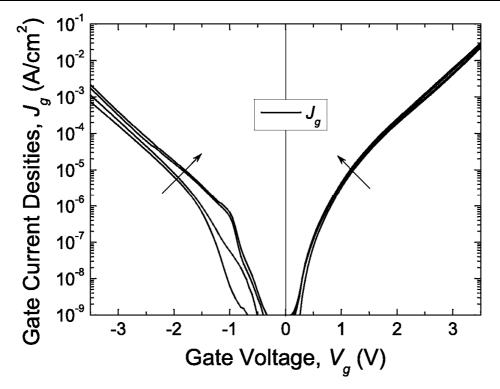

- Figure 4.3 Evolution of the gate leakage current in an n+/nMOSFET, after constant voltage stress at  $V_s = +4.3$ V. The stress time increases in the direction of the arrow: 0 s (pre-stress), 100 s, 1000 s, and 3000 s.

- Figure 4.4 Gate SILC of the n+/nMOSFET shown in Figure 4.3, for the accumulation and inversion modes. The stress voltage was +4.3 V. The stress time is 100 s, 1000 s, and 3000 s (same as Figure 4.3) along the direction of the arrow.

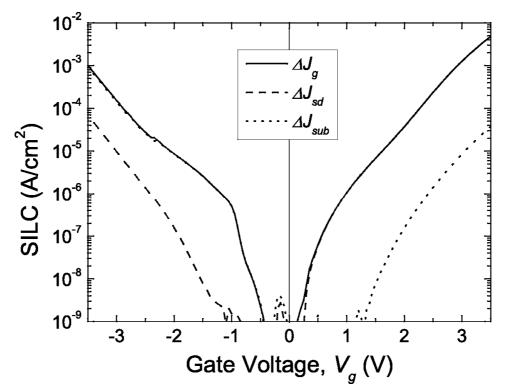

- Figure 4.5 Electron and hole SILC characteristics for the accumulation and inversion modes after t = 1000 s stress. The curves are obtained by sweeping the gate voltage from negative to positive.

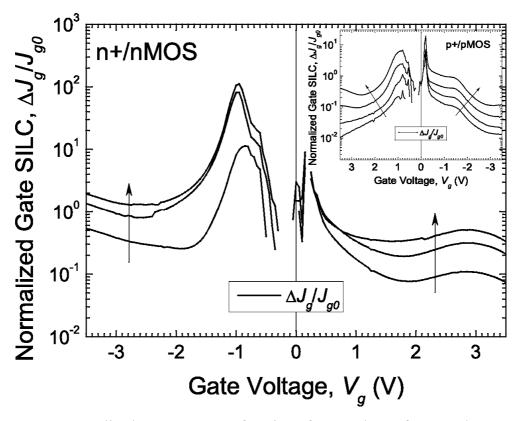

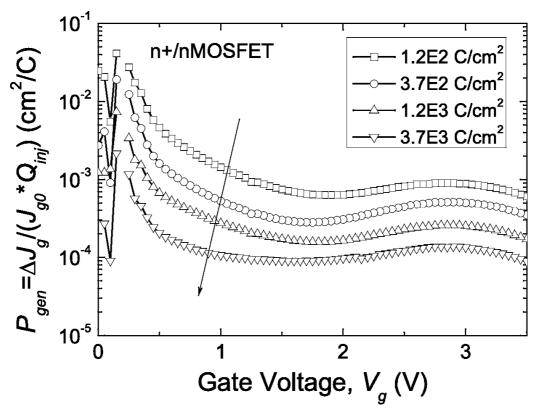

- Figure 4.6 Normalized gate SILC as a function of gate voltage, for an n+/nMOSFET following different stress times.  $J_{g0}$  denotes the pre-stress gate leakage current, and  $\Delta J_g$  denotes the gate SILC. A similar plot for a p+/pMOSFET is also shown in the inset. The stress time increases along the direction of the arrow.

- Figure 4.7 Electron and hole TAT process via stress-induced oxide trap (under strong inversion), for (a) p+/pMOS and (b) n+/nMOS, respectively.

- Figure 4.8 Normalized hole SILC and electron SILC in a p+/pMOSFET, for different stress times. The electron SILC in the low gate sense voltage ( $|V_g| < 1.2$  V)

regime is not shown, for the electron current in this voltage range is negligible. The Cumulative stress time increases along the direction of the arrow.

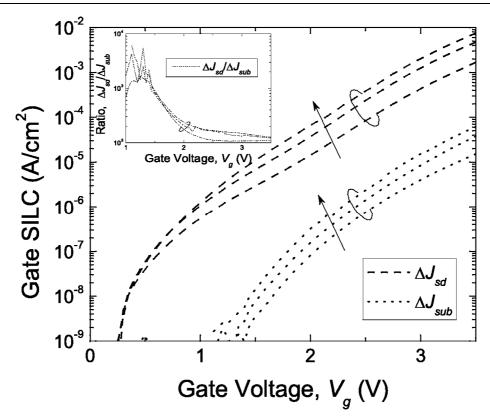

- Figure 4.9 Increase in the CBE tunneling current ( $\Delta J_{sd}$ , dashed lines) and VBE tunneling ( $\Delta J_{sub}$ , doted lines) in of an n+/nMOSFET with 2.2 nm gate oxide.

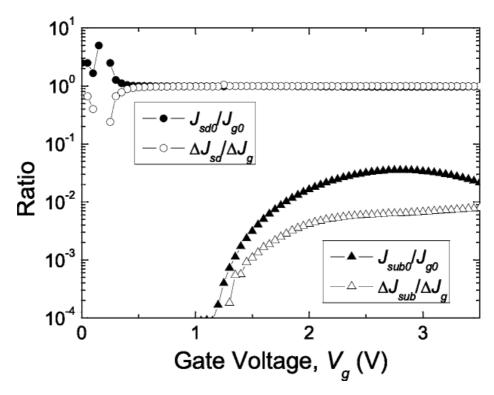

- Figure 4.10 The ratio of CBE tunneling current to the gate leakage current of a fresh device (solid circle), and to the in gate SILC of a stressed device (open circle). The corresponding ratios for the VBE tunneling current are also shown. Stress time t = 1000 s.

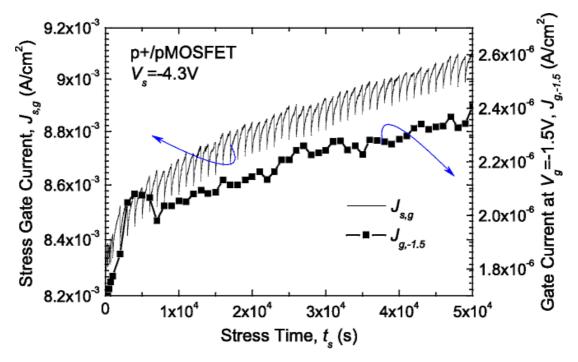

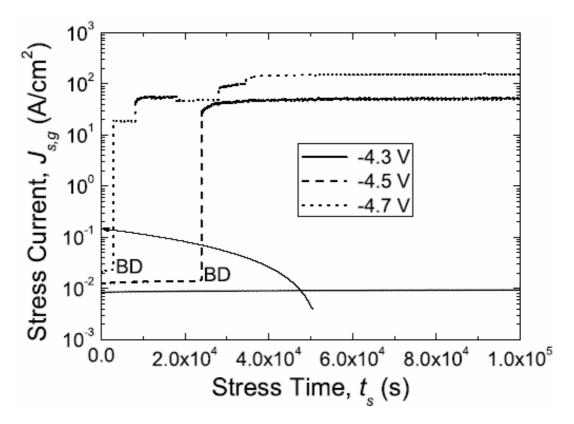

- Figure 5.1 Recorded gate current during constant voltage stress and gate sense current after each cycle of stress, for a p+/pMOSFET. Gate area is  $40 \times 20$   $\mu$ m<sup>2</sup>, and the gate oxide thickness is 2.2 nm.

- Figure 5.2 Recorded gate current during constant voltage stress and gate current after each cycle of stress, for an n+/nMOSFET. Gate area is  $40 \times 20 \ \mu\text{m}^2$ , and the gate oxide thickness is 2.2 nm.

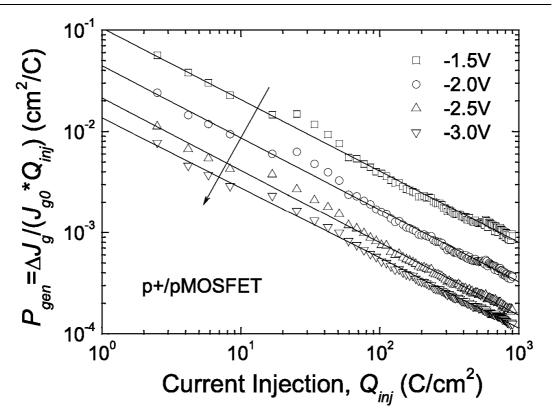

- Figure 5.3 Normalized gate SILC as a function of charge injection, with the gate sense voltage as the parameter. The p+pMOSFET was stressed -4.3 V.

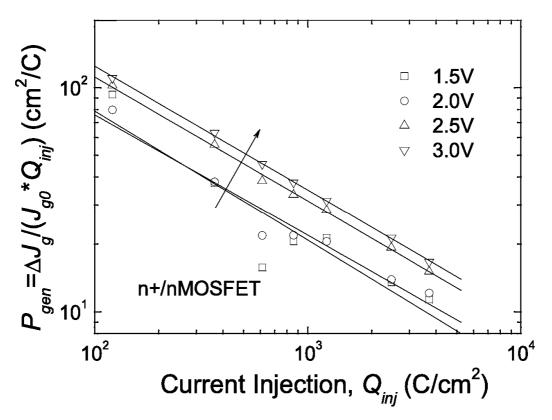

- Figure 5.4 Normalized gate SILC as a function of charge injection, with the gate sense voltage as the parameter. The n+/nMOSFET was stressed +4.3 V.

- Figure 5.5 SILC generation probability as a function of gate sense voltage, for different charge injection levels. The p+/pMOSFET was stressed at -4.3 V.

- Figure 5.6 SILC generation probability as a function of the gate sense voltage for different charge injection levels. The n+/nMOSFET was stressed at as +4.3 V.

- Figure 5.7 SILC generation probability as a function of charge injection, for different gate sense voltages. The p+/pMOSFET was stressed at -4.3 V.

- Figure 5.8 SILC generation probability as a function of charge injection, for different gate sense voltages. The n+/nMOSFET was stressed at +4.3 V.

- Figure 5.9 Evolution of stress gate current under different stress voltages: -4.3 V (solid line), -4.5 V (dashed line) and -4.7 V (dotted line). Stress is periodically stopped for SILC measurement.

## LIST OF SYMBOLS

- *E*c Energy level of conduction band edge of silicon

- *Ev* Energy level of valence band edge of silicon

- $J_{\rm g}$  Gate leakage current density of a MOSFET

- $J_{\rm sd}$  Source-drain current density of a MOSFET in carrier separation measurement

- *J*<sub>sub</sub> Substrate current density of a MOSFET in carrier separation measurement

- $J_{g0}$  Initial gate leakage current density

- $J_{\rm sd0}$  Initial source-drain current density

- $J_{\text{sub0}}$  Initial substrate current density

- $\Delta J_{\rm g}$  Gate SILC

- $\Delta J_{sd}$  Change of source-drain current sensed by carrier separation measurement

- $\Delta J_{sub}$  Change of substrate current sensed by carrier separation measurement

- L Channel length of a MOSFET

- $\Delta N_{\text{te}}$  Change of neutral oxide trap density responsible for electron tunneling

- $\Delta N_{\rm th}$  Change of neutral oxide trap density responsible for hole tunneling

- *N*<sub>te</sub> Neutral oxide trap density responsible for electron tunneling

- *N*<sub>th</sub> Neutral oxide trap density responsible for hole tunneling

- $P_{\text{gen}}$  Trap generation probability

- $Q_{\rm bd}$  Charge-to-breakdown

- $Q_{\rm inj}$  Charge injection fluence

- T<sub>ox</sub> Gate oxide thickness

- *T*<sub>bd</sub> Time-to-breakdown

- $t_{\rm s}$  Cumulative stress time

- $V_{\rm b}$  Voltage applied the body substrate during substrate hot carrier injection

- $V_{\rm g}$  Gate voltage of a MOSFET

- $V_{\rm ox}$  Voltage drop across the gate oxide

- *V*<sub>oe</sub> Gate voltage at which hole SILC is half of gate SILC

- $V_{\rm sd}$  Source-drain voltage of a MOSFET

- $V_{\rm s}$  Stress voltage during constant-voltage stress applied to the gate

- $V_{sub}$  Substrate voltage of a MOSFET

- $V_{\rm w}$  Voltage applied the well during substrate hot carrier injection

- W Channel width of a MOSFET

- $\beta$  Slope the correlation of hole SILC with electron SILC in double-log scale

# NOMENCLATURES

| A 111   | Anoda hala injection                                            |

|---------|-----------------------------------------------------------------|

| AHI     | Anode hole injection                                            |

| AHR     | Anode hydrogen release                                          |

| CAT     | Charge-assisted tunneling                                       |

| CBE     | Conduction-band electron                                        |

| CHE     | Channel hot electron                                            |

| CMOS    | Complementary metal-oxide-semiconductor                         |

| CMOSFET | Complementary metal-oxide-semiconductor field-effect transistor |

| CVS     | Constant voltage stress                                         |

| DT      | Direct-tunneling                                                |

| FNT     | Fowler-nordheim tunneling                                       |

| HBD     | Hard-breakdown                                                  |

| HV-SILC | High-voltage SILC                                               |

| LV-SILC | Low-voltage SILC                                                |

| MOS     | Metal-oxide-semiconductor                                       |

| MOSFET  | Metal-oxide-semiconductor field-effect transistor               |

| RTAT    | Recombination and trap-assisted tunneling                       |

| RTO     | Rapid thermal oxidation                                         |

| SBD     | Soft-breakdown                                                  |

| SHCI    | Substrate hot carrier injection                                 |

| SHEI    | Substrate hot electron injection                                |

| SHHI    | Substrate hot hole injection                                    |

| SILC    | Stress-induced leakage current                                  |

| TAT     | Trap-assisted tunneling                                         |

| TDDB    | Time-dependent dielectric breakdown                             |

| TDDW    | Time-dependent dielectric wearout                               |

| THAT    | Thermal-assisted tunneling                                      |

|         |                                                                 |

- ULSI Ultra large scale integration

- VBE Valence-band electron

## Chapter 1

# Introduction and Literature

## 1.1 Gate Oxide Scaling and Reliability

The quest for higher packaging density, faster circuit speed and lower power dissipation has been relentlessly driving complementary metal-oxide-semiconductor (CMOS) devices to ever smaller dimensions in the past three decades. For current ultra large scale integration (ULSI) applications, the state-of-art technology is 0.11  $\mu$ m. It will soon advance to 90 nm or even 65 nm in the very near future. CMOS devices with even smaller channel lengths (50 nm and sub-50 nm) have been successfully fabricated in research laboratories [1] - [7]. According to the International Technology Roadmap for Semiconductor (ITRS), gate length scaling will continue in a two-year cycle until 2007 [8], when the minimum feature size reaches 25 nm.

The scaling of the gate length must be accompanied by a corresponding reduction in the gate oxide thickness [9] [10], in order for the gate voltage to maintain enough control over the channel, thus suppressing the 2-D short channel effects and maintaining a good subthreshold slope. During the past two decades, MOSFET scaling has been primarily, but not exactly, following the constant-field scaling scheme, proposed by Dennard *et al.* [11] [12]. For CMOS logic technology, gate oxide thickness decreases from 20 nm to 1.5 nm, when the gate length reduces from 1  $\mu$ m to 100 nm, corresponding to a reduction in supply voltages from 5 V to 1.0 V. On the other hand, a reduced oxide thickness is also desirable for non-volatile memory devices, as the programming voltage could then be significantly reduced.

One of the key factors for the success of the MOS technology is the long list of extraordinary thermal and electrical properties of SiO<sub>2</sub> and its excellent scaling and process integration capabilities. However, SiO<sub>2</sub> is not perfect and suffers from some reliability problems. In the conventional MOS devices, the thin oxide layer is subjected to a gate voltage of several volts, resulting in a high oxide field. Continuous scaling of the CMOS technology gradually increases this oxide field, since the operating voltage has been scaled down less aggressively. In state-of-art logic CMOS devices, the oxide field is about 6 MV/cm [13]. At such a high field, the oxide properties gradually degrade, constituting the much-studied time-dependent dielectric breakdown (TDDB) phenomenon. Even though it has been the subject of numerous studies in the past three decades [13] - [15], a complete understanding of oxide degradation is still lacking and its implications on the reliability of devices and circuits remain unclear. Among the many models presented to explain the degradation and breakdown of silicon dioxides under electrical stress, two were widely accepted. They are the Anode Hole Injection (AHI) model [16] and Anode Hydrogen Release (AHR) model [17]. Another widely cited model is the thermochemical model (or *E*-model) [18] [19]. Despite continuing controversy, at least the following agreements have been reached. First, there is a force, such as the voltage, electric field or and/or tunneling current that drives the degradation and breakdown of the silicon dioxide film. Second, defects, including interface traps, bulk oxide traps and trapped charges, are generated, resulting in additional increase in the leakage current. Third, there exists a vital criterion that characterizes the final oxide breakdown, e.g. the hole fluence in the AHI model and the critical defect density in the percolation model.

When oxide thickness is scaled down to the nanometer regime, several new phenomena related to oxide reliability occur: Ballistic and direct tunneling [20], polarity-dependent oxide breakdown (including both time-to-breakdown ( $T_{bd}$ ) and charge-to-breakdown ( $Q_{bd}$ )) [21] - [23], decrease in the Weibull slope of the breakdown distribution [24] [25] and soft breakdown (SBD) [26] - [31]. These new phenomena add to the complexity of gate oxide reliability.

For thick oxides ( $T_{ox} > 5$  nm), oxide breakdown is characterized by a sudden change in current or voltage during electrical stress, due to the formation of a highly conductive ohmic short between anode and cathode by the propagation of thermal damage (hard breakdown, HBD). This conductive path has been verified to be localized. Usually, the HBD is followed by immediate device and circuit failure. However, for ultrathin oxides, another mode of oxide failure exists. This failure mode has been termed as soft, quasi, early, nondestructive, electric breakdown, or B-mode SILC, characterized by the creation of a more resistive breakdown path. The latter had been proposed as the dominant mode of failure for ultrathin gate oxides. However, the so-called soft breakdown (SBD) models have been challenged in recent years. Weir et al. [32] convincingly showed that devices remained functional even after soft breakdown of ultrathin gate dielectrics. Cheung reported that soft breakdown of the ultrathin gate oxide could probably be an experimental artifact induced by the inability of the device to eliminate the current surge at the moment of the formation of a percolation path [33]. Recently, a novel argument was proposed to account for a unique phenomenon: progressive degradation of ultrathin gate oxides. It was argued that ultrathin gate oxides actually would not breakdown (at least not in the manner of HBD or SBD), but will progressively degrade, as revealed by the progressive increase in the leakage current and/or current noise under constant voltage stress [34] - [36]. Wu et al. proposed a new Time-Dependent Dielectric Wearout (TDDW) technique to measure and characterize the degradation of ultrathin gate oxides [37].

Above all, downscaling of gate oxide thickness, has complicated, rather than simplified the gate oxide reliability issues. Established models are continuously challenged. A further understanding of the degradation process and mechanism of ultrathin gate oxides is greatly needed.

## 1.2 Intrinsic Leakage Currents in Gate Oxides

Current conduction in high-field-stressed oxides consists of two parts: Intrinsic part and stress-induced part. Depending on the oxide thickness and the magnitude of the electric field, one of these two mechanisms, Fowler-Nordheim Tunneling (FNT) and Direct Tunneling (DT), is responsible for the intrinsic leakage current. For oxides thicker than 30 Å, the intrinsic current can be well modeled as FNT. For thinner oxides, DT current dominates the intrinsic current. The difference of these two tunneling

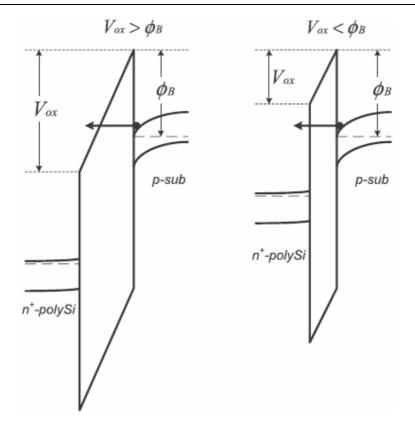

Figure 1.1: Illustration of two major tunneling mechanisms: (left) Fowler-Nordeim Tunneling and (right) Direct Tunneling.

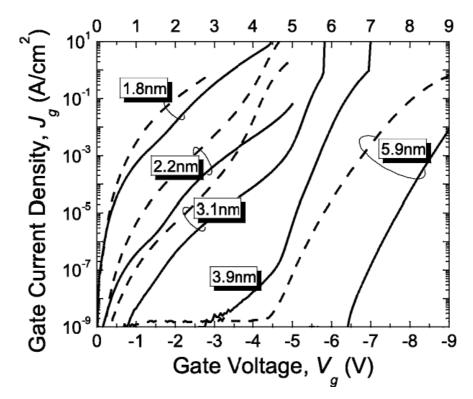

Figure 1.2: Intrinsic gate leakage current in dual-gate CMOSFETs with different oxide thickness. Measurement was done under inversion mode. The characteristics for both p+pMOS (solid lines) and n+nMOS (dashed lines) are shown.

mechanisms lies in the tunneling barriers involved, as shown in Figure 1.1. In FNT, the voltage across the oxide  $(V_{ox})$  is larger than the barrier height  $(\phi_{B})$ , and electrons tunnel through a triangular energy barrier. The current density can be written as

$$J_{\rm FN} \cong A \cdot E_{\rm ox}^2 \cdot \exp(-B / E_{\rm ox}). \tag{1.1}$$

where A and B are constants. The former is related to the doping density and oxide thickness, and the latter is related to the tunneling barrier height.  $E_{ox}$  is the oxide electric field.

For DT, however,  $V_{ox} < \phi_{B}$  and the energy barrier is trapezoidal. One representative model for DT taking into consideration of quantum mechanical effects is given as,

$$J_{\rm DT} \cong J_{\rm FN} \cdot 2\left(1 - \frac{V_{\rm ox}}{2\phi_{\rm B}}\right) \cdot \left(\frac{\phi_{\rm B}}{V_{\rm ox}}\right) \cdot \exp\left(\frac{\beta\left(\frac{\phi_{\rm B} - V_{\rm ox}}{\phi_{\rm B}}\right)^{3/2}}{E_{\rm ox}}\right).$$

(1.2)

The intrinsic gate leakage currents in dual-gate CMOSFETs with oxides of five different thicknesses are plotted in Figure 1.2. The transition from FNT current to DT current is clearly shown. For  $T_{ox} = 3.1$  nm and below, the gate leakage is primarily a DT current, while for  $T_{ox} = 3.9$  nm and  $T_{ox} = 5.9$  nm, the gate leakage is mainly FNT current. As the oxide thickness scales down, the leakage current increases dramatically; at the same time the gate current difference between n+/nMOSFET and p+/pMOSFET becomes smaller. The DT leakage thus imposes a critical limit on the further downscaling of silicon-dioxide-based ULSI devices.

## 1.3 Stress-Induced Leakage Currents in Gate Oxides

When a high electrical field is applied to the gate oxide, a number of phenomena related to the degradation of oxide properties occur: charge trapping, bulk trap generation, interface state generation and stress-induced leakage current (SILC) increase. These phenomena occur concurrently and may interact with one another. SILC is of

great importance among them. SILC was first reported by Maserjian and Zamani [38] [39]. Initially, it was defined as the excess low field leakage current induced by high-field stress. Physically speaking, SILC is the additional leakage current originating from stress-induced damage in the oxide and/or interfaces. Electrical stress induces charges and traps in the oxide and at the interface, and these defects modify the tunneling leakage current through the oxide. In practice, SILC is directly related to two important reliability issues: stand-by power dissipation of CMOS circuits and data retention time of non-volatile memory devices. Increased leakage current means more stand-by power dissipation for the former, while shorter data retention time for the latter [40]. Following the pioneering work of Maserjian and Zamani, an extensive research on SILC has been done. It has been widely accepted that carrier conduction in SILC is inelastic and defect-assisted. However, two major issues have been under debate for over two decades. First, what kinds of defects are involved (trap charges, bulk oxide traps, or interface states)? Second, how do they facilitate carrier conduction through the gate oxide?

### 1.3.1. General Physical Characteristics of SILC

#### A Classical Illustration of SILC

A classical illustration of SILC is given in Figure 1.3 and Figure 1.4. The SILC characteristics are obtained from dual-gate CMOSFET devices with 5.9 nm oxide. In Figure 1.3, the two  $J_g$ - $V_g$  curves are measured consecutively. In the first measurement, the voltage ramp was stopped at a high value. The SILC shows itself at low gate voltage in the second curve. This is due to oxide damage induced by the first measurement. A more common way to obtain SILC is to subject the device to a certain type of stress (such as constant current stress, constant voltage stress, ac stress, etc.) and to compare the pre- and post-stress  $J_g$ - $V_g$  characteristics. Shown in Figure 1.4 is a group of  $J_g$ - $V_g$  curves similar to those in Figure 1.3, but in the former, the devices were subjected to a constant voltage stress (CVS). Note that in both figures, the post-stress gate current at high measurement voltage is actually lower than the

Figure 1.3: SILCs in dual-gate CMOSFETs with 5.9 nm oxide. For each type of device, two  $J_g$ - $V_g$  measurements are taken successively, and the excess leakage current appears in the second curve (dashed line). The gate voltage was gradually increased from 0 to as high as 9.0 V (-9.0 V) for n+/nMOSFET (p+/pMOSFET).

Figure 1.4: SILCs in dual-gate CMOSFETs with 5.9 nm oxide.  $J_{g}V_{g}$  measurements are taken before (solid lines) and after (dashed lines) constant voltage stress. The devices are the same as those of Figures 1. The n+/nMOSFET and p+/pMOSFET were stressed at +7 V and -8.5 V respectively, for 100 s.

pre-stress one. This is due to the fact that charge trapped in the oxide lowers the transmission coefficient of tunneling electrons at high voltage [41].

#### Transient SILCs vs. Steady-state SILCs

SILC is strongly dependent on gate oxide thickness but is rather insensitive to process details. Basically, the components of SILC can be separated into two groups: Transient and steady-state. For oxides thicker than 7.5 nm, transient components tend to dominate the SILC, while steady-state components dominate in thinner oxides [42]. The transient SILC components have been shown to be composed of different sub-components with complex stress/measurement voltage dependence and polarity dependence [43] - [45]. Furthermore, one component can be revealed or concealed by different stress and measurement sequences, and is sensitive to voltage ramp rate [42] [46]. After stress, the current was observed to decay exponentially with time ( $J \propto t^{-n}$ , with  $n \approx 1$ ) [43], [47] - [49]. This transient behavior originates from charge trapping and detrapping in the oxide [50]. Several models have been proposed to characterize the transient SILCs [51] - [53]. In ultrathin gate oxides, since charge trapping is significantly reduced, transient SILC is practically absent.

#### Stress Time, Stress Fluence, Temperature and Oxide Thickness Dependence

It has been frequently reported that stress-induced leakage current increases exponentially with stress time, i.e.  $J_{SILC} \propto t_s^{-n}$ . The tendency of saturation has been observed at long stress time or large injection fluence at low stress voltages, as well as in small-area devices [54] [55]. In the case of thin oxides, the stress fluence dependence of SILC is similar to the stress time dependence, since the injection charge can be well approximated by an initial injection current multiplied by stress time, i.e.  $Q_{ini} \sim J_0 \cdot t_s$ .

The temperature dependence of SILC has been shown to be similar to that for trap creation [56] [57]. SILC, as well as the SILC generation efficiency, increases as the temperature increases.

The oxide thickness dependence of SILC shows a "turn-around" effect. For a fixed stress fluence, SILC increases as oxide thickness decreases and peaks at  $T_{ox} \sim 50$  Å. Thereafter, SILC decreases as oxide thickness decreases below 50 Å [58] [59]. This "turnaround" effect can be explained by the trap-assisted tunneling (TAT) framework [59] [60]. The turn-around effect may be attributed to the increasing significance of direct tunneling current over TAT current in thinner oxides.

#### **Impact of Nitridation on SILC**

By virtue of its ability to suppress boron penetration from the p+ gate, and to improve the hot-carrier reliability, the nitrided gate oxide is widely used in state-of-the-art CMOS technologies. The most popular nitridation method for high-quality gate oxide growth is Rapid Thermal Oxidation in an N<sub>2</sub>O ambient [61]. Apart from the well-known advantages that make nitrided oxide a more superior gate dielectric, it has also been reported that nitrided oxide exhibits a greater immunity to SILC generation, as compared to traditional silicon dioxide [62] - [64]. It is believed that the incorporated nitrogen decreases the trap generation rate and density of weak spots [63].

### 1.3.2. Major Physical Models of SILC

As indicated in the previous sections, SILC is far more than a simple physical phenomenon. In the past two decades, a lot of experimental and theoretical research works have been carried out. Generally, four groups of SILC models can be found in the literature: Charge-Assisted Tunneling (CAT) model [39] [65] [66], Thermally-Assisted Tunneling (THAT) model [56], Trap-Assisted Tunneling (TAT) model [42] [47] [57] [67], and Trap-Assisted Tunneling and Recombination model (TATR) [68] - [70]. The schematic diagrams in Figure 1.5 qualitatively illustrate these four mechanisms. In the CAT model, trapped holes modify the tunneling barrier profile, making it more favorable for electron tunneling. In the THAT model, excess leakage current originates from localized weak spots generated by high-field stress.

Figure 1.5: Schematic diagrams illustrating four typical tunneling mechanisms that have proposed to explain the SILC.

In the TAT model, oxide traps act as the stepping-stones for excess carrier tunneling. While in the RAT model, the traps act as recombination centers. In this model, it is proposed that a surface channel p+/pMOS structure, holes in the inversion layer actually do not tunnel through the gate oxide; instead, they are captured by the traps in the gate oxide and subsequently recombine with electrons that tunnel from the gate.

#### **Charge-Assisted Tunneling**

The increase of leakage current at low voltage was initially attributed to the generation of positive charges in the oxide. This forms the basis of the charge-assisted tunneling (CAT) model, proposed by Maserjian and Zamani [38]. It is proposed that during FN stress, positive oxide charges are generated near the anode, due to the breaking of strained Si-O-Si bonds by hot electrons in the oxide. The trapped holes modify the tunneling barrier profile, thus increasing the electron tunneling efficiency. This model has not gained much support in the literature, even though it is compatible with the AHI model [65] [66]. Recently, the role of positive trapped charge in the stress-induced leakage current is reinvestigated by some groups [53] [71] [72]. It is claimed that the dominant SILC mechanism is Positive Charge-Assisted Tunneling (PCAT), and the transient effect of SILC can be successfully explained by reduction of PCAT current via positive charge detrapping. Furthermore, it has been found that when oxide thickness reduces from 100 Å to 53 Å, the dominant mechanism changes from PCAT to TAT, which will be discussed in detail later in this section.

#### **Thermal-Assisted Tunneling**

Olivo *et al.* [56] investigated the dependence of SILC on stress polarity, oxide thickness and measurement temperatures. The excess leakage is modeled as thermal activated electron tunneling through *localized defect-related weak spots*. This constitutes the so-called Thermally-Assisted Tunneling (THAT) model. Furthermore, it is shown that the observed excess leakage can be well described by an FNT-like tunneling current through a heavily reduced barrier height (~0.9 eV) over a wide range of temperatures. Their work has great impact on those of other groups, even though the so-called THAT model for SILC has been abandoned by most groups nowadays. Further research found that the heavily reduced tunneling barrier height is characteristic of

SILC [58]. One example is shown in Figure 1.6, where both virgin gate current and SILC are replotted based on the FNT model, i.e.  $\log(J/E_{ox}^2)$  vs. $1/E_{ox}$ . Both virgin gate leakage and SILC characteristics can fit the FNT model well. However, it was shown in [63] that for ultrathin gate oxides the low field SILC does not support the FNT model.

Figure 1.6: FN plots of virgin FNT current and SILC, for an n+/nMOSFET with  $T_{ox} = 5.9$  nm. Device dimensions: W = 20  $\mu$ m, L = 20  $\mu$ m, T<sub>ox</sub> = 5.9 nm.

#### **Trap-Assisted Tunneling**

The trap-assisted-tunneling (TAT) model became widely accepted in the early 1990s. Actually, the significance of oxide traps in SILC conduction was suggested in late 1980's. Naruke *et al.* [73] investigated the low field excess leakage induced by w/e cycles in FLOTOX EEPROM tunnel oxides with thickness ranging from 40 Å to 100 Å. Consistent with the argument of [56], it was shown that the conduction mechanism of SILC was different from positive charge accumulation in the oxide, since SILC and hole trapping have very different (actually opposite) oxide thickness dependence. However, it seems that the Frenkel-Poole type defect hopping mechanism [74], with a current-field dependence of the form  $\log(J/E_{ox}) \propto \sqrt{E_{ox}}$ , fits the observed SILC characteristics quite well. A similar behavior was observed by Ann *et al.* [63]. It

should be noted that Frenkel-Poole emission actually can be treated as field-enhanced electron emission from trapping sites [75]. Thus, FP hopping conduction and the TAT mechanism may be largely similar: Low-field conduction in the gate oxides is facilitated by traps, via the formation of intermediate states in the oxide.

Dumin *et al.* [47] quantitatively investigated the relationship between excess leakage current and trap density ( $N_t$ ). A one-to-one relationship exists between them, strongly suggesting that the conduction of SILC is trap-assisted. Furthermore, the trap density is found to be proportional to the cube root of the injection charge fluence ( $N_t \propto Q^{1/3}$ ) and is independent of the stress polarity. It was observed in [47] that Schottky emission ( $\log J \propto \sqrt{V}$ ), other than Frenkel-Poole emission, also fits the experimental SILC. Patel *et al.* [58] found that there existed a threshold electron energy (~1.7 eV) for the stress voltage, below which no SILC could be observed. It was noted that this threshold value was very close to the trap creation energy in SiO<sub>2</sub> [76].

DiMaria [57] carried out a comprehensive investigation of the dependence of SILC on injected charge fluence, stressing voltage, sensing voltage, oxide thickness, Si-substrate doping, and temperature. SILC was found to exhibit a "universal" dependence on the hot-electron energy. Furthermore, oxide defect generation (trapped holes, trapped electrons, interface states, positive charge trapped near the anode) was investigated as a function of hot-electron energy. By comparing the latter results to the electron energy dependence of SILC, it was concluded that the major cause of SILC was neutral electron traps generated during hot-electron stress.

Other important reports related to the TAT model include [59] [77] - [79]. In [78], and with more detail in [80], experimental evidence is provided showing that trap-assisted tunneling is involved in SILC conduction. During SILC conduction, a "constant energy loss" ( $\sim$ 1.5 eV) is verified for electrons injected through the gate oxide into the Si substrate. This is also supported by the simulation results reported by Ghetti *et al.* [81] [82]. Furthermore, it is concluded that process-induced oxide traps and stress-induced oxide traps are essentially different, since tunneling through process-induced oxide traps appears to be elastic [82].

Assuming that the density of process-induced oxide traps is negligible, which is reasonable for state-of-the-art CMOS process, the principles behind the TAT model for

SILC can be summarized below:

- In post-stress oxide, the leakage current is made up of two parts: Native tunneling leakage current and excess leakage induced by stress. The native leakage can be FNT or DT, while the excess leakage is dominated by TAT.

- 2. The oxide traps act as stepping-stones for carrier tunneling. Tunneling is facilitated by oxide traps, because their presence substantially lowers the tunneling barrier.

- 3. TAT is at least a two-step process: A tunneling-in followed by a tunneling-out process.

- 4. Carriers lose energy when they tunnel through the gate oxide via TAT, i.e. the tunneling is inelastic.

- 5. Traps involved in TAT are believed to change their states after the TAT process, to compensate the energy loss stated above. The exact mechanism of this change is still not clear.

Based the TAT framework, many successful SILC models have been proposed [51], [83] - [88]. However, there are still uncertainties. The most controversial ones are those concerning the spatial and energy profile of stress-induced oxide traps. For example, it is still not clear whether interface traps or bulk traps, or both, are involved in the TAT process. As early as 1991, Rofan and Hu [67] proposed that SILC was a result of trap-assisted tunneling via interface traps, and this argument was supported by the fact that there was a close correlation between SILC and interface traps sensed by charge pumping current measurement for three cases: Pre-stress, post-stress, and post-stress anneal. This argument was also supported and developed by other groups [64] [89].

It has been reported that high-field generated interface states and oxide traps are actually correlated. From this point of view, the observation that SILC is well correlated to interface trap density is therefore not enough to prove that SILC conduction is dominated by interface-trap assisted tunneling. A similar conclusion applies to bulk oxide traps. Practically, it is sometimes difficult to clearly distinguish interface traps from oxide traps, especially for ultra-thin gate oxides. As gate oxide thickness approaches the critical dimension of a single electron trap, the debate on interface- or bulk-trap assisted tunneling may not be meaningful.

#### **Recombination and Trap-Assisted Tunneling**

Although the TAT model has gained great success and wide support in the past years, it has been challenged recently. The lack of direct evidence or detailed knowledge on the TAT process that happens at the oxide traps is the major short-coming for TAT-based models.

Ielmini *et al.* presented a novel model for SILC, which incorporated recombination into the TAT process, namely the recombination and trap-assisted tunneling (RTAT) model [68] - [70]. In this model, the simultaneous observation of hole current and electron current in SILC is attributed to electron-hole recombination at defect states in the oxide (Figure 1.5-d). It was shown that these two components in SILC are highly (almost one-to-one) correlated, in that they share the same stress dose dependence and relaxation time dependence [69]. Specifically, plotting hole SILC vs. electron SILC at different stress levels or relaxation time (after the stress) on log-log scale results in a straight line with slope very close to 1; wherever electron SILC is suppressed, e.g. in p+/pMOS devices, hole SILC is also suppressed.

#### 1.3.3. Stress-Induced Traps in Oxides

The strong correlation between SILC and trap generation has been demonstrated by many SILC models. The properties of the stress-induced oxide traps, the density of the traps, and the energy distribution of the traps are the factors that would most significantly influence SILC. But, how exactly an oxide trap facilitates carrier tunneling is still not clear till these days. The traditional methods for extracting trap density have their limitations. A good understanding on the energy distribution of the traps is lacking either. Specifically, a detailed knowledge of the energy distribution of stress-induced oxide traps is not available.

In the literature, several techniques have been used to measure the trap density. For example, the density of interface states was often measured by the charge pumping technique [64] [67]. The density of bulk oxide traps can be obtained from the discharge current characteristic after removal of high voltage pulse [47] or from the C-V and I-t characteristics [17]. More recently, a novel method, termed Direct-Current Current-Voltage (DCIV), was used to monitor both the bulk oxide traps and SiO<sub>2</sub>/Si interface states [89] [90]. However, it should be noted that all these methods can only sense a portion of the interface/bulk oxide traps. In other words, only the relative change in the trap density can be monitored, not the absolute change.

In order to characterize SILC accurately, the oxide trap distribution must also be known precisely. This includes the spatial and energy profiles of the traps. However, due to lack of insight into the microstructure, a detailed knowledge of the energy profile of the stress-induced oxide traps has never been obtained. A common practice in the literature of SILC modeling is to first introduce the energy level of the traps as a parameter, and later extract an improved value by fitting the SILC model to experimental data [91]. Spinelli *et al.* reported an experimental method to extract the energy distribution of oxide traps [92]. However, this method is not applicable to ultrathin gate oxides, since it makes use of the transient current as the monitor of trap density. In ultrathin gate oxides, the transient current is too small to be a sensitive monitor.

It is still not clear whether the electrical stress-induced oxide damage is localized or is uniformly distributed throughout the gate oxide. In the literature, some group adopted the concept that stress-induced damage is localized [93] on the basis that oxide breakdown (SBD or HBD) is highly localized [13]. However, in using the TAT model, the assumption of a uniform oxide trap distribution is found to fit the experimental SILC data very well [50] [86], indicating that oxide traps responsible for SILC may not be necessarily localized. This challenges the argument that SILC and oxide breakdown are well correlated. Furthermore, some groups postulated that the traps responsible for SILC are different from those responsible for oxide breakdown [94]. In recent years, new experimental findings have shown that there are at least two types of oxide traps created during electrical stress [95] [96]. This casts more doubts on the proposed strong correlation between SILC and oxide breakdown. However, as suggested in [94], and also in [97], the correlation between SILC and oxide breakdown could be indirect. Further research work is needed to clarify their relationship.

### 1.3.4. Recent Advances in Research

The number of publications on SILC is huge, and recent research work has become more detailed. Chetti *et al.* [82] investigated the physical characteristics of electrical stress-induced traps by quantum yield measurement and simulation [82], and they showed that electron tunneling via stress-induced traps is inelastic, consistent with [80]. Furthermore, it has been shown that electron tunneling via pre-existing traps is elastic. This indicates that pre-existing traps and stress-induced traps are different in nature, which is also shown recently in [98].

Ang *et al.* [99] found that SILC could be annealed out partially by applying a low voltage after high voltage stress, and proposed that the reduction in SILC was linked to annealing of trapped holes. The mechanism of SILC and dielectric breakdown was examined by Alers *et al.* [100] through 1/f noise in the tunneling current of 1.7 - 5 nm oxides. Before breakdown, a linear relationship between SILC and 1/f noise was observed. This behavior was successfully described using the TAT model. A new quantitative model was developed for the 1/f noise, on the basis of TAT current fluctuations. It was shown that the traditional charge-state fluctuation model is inconsistent with the voltage-scaling of the noise. These results also strongly suggest that the conduction mechanisms in the stressed and unstressed oxide<del>s</del> are fundamentally different.

Irrera proposed a kinetic model for trap creation in thermal oxides during electrical stress [101]. In this model, creation of additional traps is believed to be controlled by electron scattering by existing defects. The model predicts a square-root dependence of SILC on the stress time. Defect concentrations calculated by this model were used in a TAT model and excellent agreement with low-field conductivity was observed.

Ielmini *et al.* presented a detailed investigation based on Quantum Yield (QY) experiments [102]. Experimental data show that no correlation exists between QY and SILC, and that QY is determined by high-energy oxide traps. Numerical simulation was used, based on a detailed calculation of the oxide defect distribution. It is shown that the leakage current and the excess impact ionization component are due to TAT of electrons through different sets of traps: Deep level traps are responsible for SILC,

while high-energy states determine the impact ionization current. Simulation results were in good agreement with experiments, showing that QY results could not be used to extract the energy loss of the SILC electrons.

Wu *et al.* investigated the validity of SILC as a measure for the critical defect density ( $N_{BD}$ ) that triggered breakdown [103]. Their finding shows that SILC may not serve as a reliable measure for  $N_{BD}$ . This work suggests that a re-evaluation of the breakdown models constructed from SILC-based experiments is required, in particular, their validity in comparison to the statistically accurate breakdown data.

The relation between SILC and hydrogen release (HR) was analyzed by Esseni *et al.* for both channel hot electron (CHE) [104] and FN [105] stress. From the fact that no deuterium isotope effect was observed for SILC, they concluded that there was no causal relation between SILC generation and HR, regardless of whether the SILC was generated by CHE stress or FN stress. In contrast, it was shown that the AHI mechanism is operative even at low gate voltage [106].

Chim *et al.* investigated the SILC generated by impulse stress [107]. An abnormally high density of positive trapped charges was observed in oxides as thin as 4.3 nm. Furthermore, it was found that the transient SILC is larger than steady-state SILC, contrary to observations in DC-stressed thin oxides [42]. These two observations, i.e. abnormally high density of positive trapped charges and large transient SILC, were found to be correlated. Another article by the same team [108] presents a detailed investigation on the SILC conduction mechanism via Conduction Band Electron (CBE) and Valence-Band Electron (VBE) tunneling in thin oxides. An improved SILC model is proposed, which enables reproduction of the experimental SILC over a wide range of oxide field, and extraction of a realistic neutral trap concentration. This improved model also confirms the concept that SILC conduction via neutral traps is accompanied by energy loss. Furthermore, the energy loss is found to be dependent on the origin of tunneling species: ~1.5 eV for CBE, and ~0.8 eV for VBE.

Research on the impact of SILC on Flash memories has been greatly advanced by Ielmini *et al.* In [109], they reported a new experimental technique to evaluate the position of oxide weak spots responsible for SILC in Flash memories. In their report, the position of the leakage spot is determined by the shift in the gate current-voltage (I-V) characteristics, when the oxide field along the channel is modified by varying the

drain bias. Results reveal a strong localization of SILC near the drain junction, as a result of program/erase operations. A statistical model of SILC in Flash arrays is presented in [110], featuring that tunneling assisted by two traps (2TAT) [111] [112], rather than the traditional single-defect TAT, dominates the steady-state SILC in Flash arrays with oxide thickness in the range of 6.5 nm to 9.7 nm. Some recent progress on SILC in nonvolatile memory devices can also be found in [113] [114].

A good understanding of SILC has led to several applications in the characterization of gate oxide reliability and lifetime. SILC increase has been successfully used to predict the lifetime of ultrathin gate oxides by Nigam *et al.* in [115], and the method is found to be fast and simple. However, it should be noted that the measured oxide lifetime is not necessarily associated with breakdown. In some cases, the increase in gate leakage could already limit circuit functionality.

## 1.4 SILC and Oxide Degradation in Scaled Oxides

As gate oxide thickness scales down, the gate leakage current increases exponentially. The large direct tunneling leakage current has become a major reliability problem for ULSI, and it is believed to be the "show-stopper" of ULSI applications based on the silicon dioxide. Due to the predominance of direct tunneling current, SILC in ultrathin gate oxides is significantly different from that in thick oxides. For thick oxides, at very low voltage regime where initial leakage current is usually not detectable, SILC shows up as obvious increase in the leakage current after high-voltage stress. Instead, the increase in the leakage current is gradual and progressive in the case of ultrathin gate oxides, because the high DT current usually concealed SILC. An example is shown in Figure 1.7. In this figure, the data are obtained for an n+ poly-gated nMOSFET with 2.2 nm gate oxide. The currents have been normalized to the gate area. The pre-stress and post-stress  $J_g$ - $V_g$  characteristics are shown for both gate voltage polarities. We can see that the direct tunneling current constitutes a major part of the overall post-stress leakage current.

The dominant direct-tunneling current in ultrathin gate oxide at low voltage implies that different current conduction and degradation mechanism may exist. Takagi

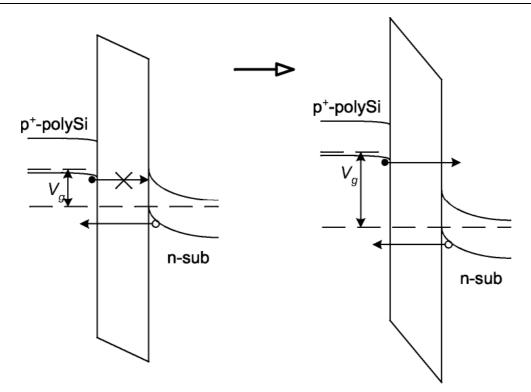

*et al.* [116] experimentally examined the DT current in unstressed and stressed ultrathin oxides in n+-poly/pMOS devices, and found that a leakage path allowing the flow of holes dominates SILC and overall leakage current after oxide soft-breakdown. This is also confirmed later by H. Guan *et al.* [117]. In [116], it is suggested that leakage paths different from those responsible for TAT are formed inside the SiO<sub>2</sub> layer after stress, and these paths lead to a dominant hole current and SB of the oxide. This implies the possibility that for direct-tunneling oxides, SILC is dominated by hole current, even though it has never been explicitly pointed out yet.

Figure 1.7:  $J_g$ - $V_g$  characteristics of an n+/nMOSFET. The solid and dashed lines denote the pre-stress and post-stress characteristics respectively. The gate voltage was swept from negative to positive during measurement. Device dimensions:  $T_{ox} = 2.2$  nm, W = 40  $\mu$ m, L = 20  $\mu$ m.

Recently, research on low-voltage SILC (LV-SILC) in ultrathin gate oxides reveals a scenario that is rather different from high-voltage SILC (HV-SILC). This includes the possible sense-voltage dependent SILC mechanism [122] and possible interfacial trap-rated tunneling [122] - [124]. Even though controversy remains [125] [126], these reports demonstrate the possibility that LV-SILC can be an alternative degradation monitor of ultrathin gate oxides, when traditional methods, such as C-V and

charge-pumping, are no longer applicable.

### 1.5 Motivation of This Work

As has been shown previously, SILC in thick oxides (>3 nm) has been comprehensively investigated, and it has generally been accepted that TAT dominates the SILC conduction. For ultrathin gate oxides, SILC usually is not quantitatively significant compared to the initial DT current. However, this does not mean that SILC in ultrathin gate oxides is not important. It is to be noted that even after more than 30 years of research, the degradation of oxide films under electrical stress is still not completely understood. SILC in ultrathin gate oxides, even though usually concealed by large DT current, may still be a very good indicator of oxide degradation. As a piece of evidence, LV-SILC has been used as monitor of oxide degradation in [125] and [126].

For ultrathin gate oxide case, probably TAT is still the most possible mechanism responsible for SILC [122] - [126]. However, several pieces of information are still missing for better understanding of SILC in ultrathin gate oxides, especially for dual-gate CMOS devices.

- In p+/pMOSFETs, it is known that the low voltage DT leakage is dominated by hole current. However, it is not clear the significance of hole current in SILC, and how it evolutes during electrical stress. This can be of great importance because it is possible to figure out the distribution of oxide traps responsible for SILC from the evolution of hole SILC and electron SILC [68] - [70].

- As indicated in the polarity dependence of oxide breakdown [21] [23], the manner of current injection has different oxide degradation rate. However, it is not clear how the manner of current injection will impact the evolution of hole SILC and electron SILC.

- 3. It is still not clear whether there is a common scheme, in terms of stress-induced trap generation and distribution, to explain the evolution of hole SILC and electron SILC in both p+/pMOSFET and n+/nMOSFET.

This work demonstrates an attempt to give an illustration of the evolution of hole SILC and electron SILC in dual-gate CMOSFETs with ultrathin gate oxides. Both type of devices (n+/nMOS and p+/pMOS), both stress polarities (inversion and accumulation), and both types of sense voltages (positive and negative) will be considered, to obtain better understanding of the SILC in different type of devices and generated/measured by different conditions.

## 1.6 Organization of the Thesis

This thesis consists of 6 chapters. Chapter 1 is the introduction chapter, which gives a comprehensive literature survey research on SILC. Chapter 2 provides detailed information about the test vehicles and experimental setup used in this work, as well as the data analysis technique. In Chapter 3, the SILC characteristics of ultrathin gate p+/pMOSFETs, subjected to different stress conditions, are discussed. Chapter 4 presents the SILC characteristics of the n+/nMOSFETs. In Chapter 5, we correlate our experimental SILC data to the defect generation mechanisms proposed for ultrathin gate oxides. Finally, Chapter 6 summarizes the major findings of this research project and makes suitable recommendations for future work.

# References

- M. Ono, M. Saito, T. Yoshitomi, C. Fiegna, T. Ohguro, and H. Iwai, "A 40-nm gate length nMOSFET," *IEEE Trans. Electron Devices*, vol. 42, pp. 1822–1830, 1995.

- Y. Taur, C. H. Wann, and D. J. Frank, "25 nm CMOS design considerations," *IEDM Tech. Dig.*, pp. 789–792, 1998.

- [3] A. Hori and B. Mizuno, "CMOS device technology toward 50 nm region -performance and drain avalanche," *IEDM Tech. Dig.*, pp. 641–644, 1999.

- B. Yu, H. H. Wang, O. Milic, Q. Xiang, W. Z. Wang, J. Z. An, and M. R. Lin,

"50 nm gate length CMOS transistor with super-halo: design, process and reliability," *IEDM Tech. Dig.*, pp. 653–656, 1999.

- [5] H. Kawaura, T. Sakamoto, T. Baba, Y. Ochiaia, J. Fujita, and J. Sone, "Transistor characteristics of 14 nm-gate-length EJ-MOSFET's," *IEEE Trans. Electron Devices*, vol. 47, pp. 856–860, 2000.

- [6] B. E. Weir, P. J. Silverman, M. A. Alam, F. Baumann, D. Monroe, A. Ghetti, J. D. Bude, G. L. Timp, A. Hamad, T. M. Oberdick, N. X. Zhao, Y. Ma, and M. M. Brown, "Gate oxides in 50 nm devices: thickness uniformity improves projected reliability," *IEDM Tech. Dig.*, pp. 437–440, 1999.

- [7] E. Murakami, T. Yoshimura, and S. Kimura, "Gate length scalability of n-MOSFET's down to 30 nm: comparison between LDD and non-LDD structures," *IEEE Trans. Electron Devices*, vol. 47, pp. 835–840, 2000.

- [8] (2001) International technology roadmap for semiconductor (ITRS). [Online].

Available: <u>http://pubic.itrs.net</u>.

- [9] C. Hu, "Gate oxide scaling limits and projection limits," *IEDM Tech. Dig.*, pp. 319–322, 1996.

- [10] Y. Taur, D. A. Buchanan, W. Chen, D. J. Frank, K. E. Ismail, S. H. Lo, G. A. Halasz, R. G. Viswanathan, H. Jen, C. Wann, S. J. Wind, and H. S. Wong,

"CMOS scaling into nanometer regime," Proc. IEEE, vol. 85, pp. 486–504, 1997.

- [11] R. H. Dennard, F. H. Gaenssien, H. N. Yu, L. Rideout, E. Bassous, and A. R. LeBlanc, "Design of ion-implanted MOSFET's with very small physical dimension," *IEEE J. Solid-State Circuits*, vol. 9, pp. 256–268, 1974.

- [12] D. L. Critchlow, "MOSFET scaling the driver of VLSI technology," *Proc. IEEE*, vol. 87, pp. 659–667, 1999.

- [13] R. Degraeve, B. Kaczer, and G. Groeseneken, "Degradation and breakdown in thin oxide layers: mechanisms, models and reliability prediction," *Microelectronics Reliability*, vol. 39, pp. 1445–1460, 1999.

- [14] J. H. Stathis, "Physical and predictive models of ultrathin oxide reliability in CMOS devices and circuits," *IEEE Trans. Device Mat. Rel.*, vol. 1, pp. 43–58, 2001.

- [15] J. S. Suehle, "Ultrathin gate oxide reliability: physical models, statistics, and characterization," *IEEE Trans. Electron Devices*, vol. 49, pp. 958–971, 2002.

- [16] K. F. Schuegraf, C. C. King, and C. Hu, "Ultra-thin silicon dioxide leakage current and scaling limit," *Proc. Symp. VLSI Tech.*, pp. 18–19, 1992.

- [17] D. J. DiMaria, E. Cartier, and D. Arnolda, "Impact ionization, trap creation, degradation, and breakdown in silicon dioxide films on silicon," *J. Appl. Phys.*, vol. 73, pp. 3367–3385, 1993.

- [18] J. W. McPherson and H. C. Mogul, "Underlying physics of the thermochemical *E* model in describing low-field time-dependent breakdown in SiO<sub>2</sub> thin films," *J. Appl. Phys.*, vol. 84, pp. 1513–1523, 1998.

- [19] J. W. McPherson and R. B. Khamankar, "Molecular model for intrinsic time-dependent dielectric breakdown in SiO<sub>2</sub> dielectrics and the reliability implications for hyper-thin gate oxide," *Semicond. Sci. Technol*, vol. 15, pp. 462–470, 2000.

- [20] J. Lee, G. Bosman, K. R. Green, and D. Ladwig, "Model and analysis of gate leakage current in ultrathin nitrided oxide MOSFETs," *IEEE Trans. Electron*

Devices, vol. 49, pp. 1232–1241, 2002.

- [21] T. Mastuoka, S. Kakimoto, M. Nakano, H. Kotaki, S. Hayashida, K. Sugimoto, K. Adachi, S. Morishita, K. Uda, Y. Sato, M. Yamanaka, T. Ogura, and J. Takagi, "Direct tunneling N<sub>2</sub>O gate oxynitrides for low-voltage operation of dual gate CMOSFETs," *IEDM Tech. Dig.*, pp. 851–854, 1995.

- [22] Y. Shi, T. P. Ma, S. Prasad, and S. Dhanda, "Polarity-dependent tunneling current and oxide breakdown in dual-gate CMOSFETs," *IEEE Electron Device Lett.*, vol. 19, pp. 391–393, 1998.

- [23] Y. Shi, T. P. Ma, S. Prasad, and S. Dhanda, "Polarity dependent gate tunneling currents in dual-gate CMOSFETs," *IEEE Trans. Electron Devices*, vol. 45, pp. 2355–2360, 1998.

- [24] R. Degraeve, G. Groesenken, R. Bellens, M. Depas, and H. E. Maes, "A consistent model for the thickness dependence of intrinsic breakdown in ultrathin oxides," *IEDM Tech. Dig.*, pp. 863–866, 1995.

- [25] R. Degraeve, G. Groeseneken, R. Bellens, J. Ogier, M. Depas, P. Roussel, and H. E. Maes, "New insights in the relation between electron trap generation and the statistical properties of oxide breakdown," *IEEE Trans. Electron Devices*, vol. 45, pp. 904–911, 1998.

- [26] S. H. Lee, B. J. Cho, J. C. Kim, and S. H. Choi, "Quasi-breakdown of ultrathin gate oxide under high field stress," *IEDM Tech. Dig.*, pp. 605–608, 1994.

- [27] M. Depas, T. Nigam, and M. Heyns, "Soft breakdown of ultra-thin gate oxide layers," *IEEE Trans. Electron Devices*, vol. 43, pp. 1499–1504, 1996.

- [28] T. Sakura, H. Utsunomiya, Y. Kamakura, and K. Taniguchi, "A detailed study of soft- and pre-soft-breakdowns in small geometry MOS structures," *IEDM Tech. Dig.*, pp. 183–186, 1998.

- [29] E. Wu, E. Nowak, J. Aitken, W. Abadeer, L. K. Han, and S. Lo, "Structural dependence of dielectric breakdown in ultra-thin gate oxides and its relationship to soft breakdown modes and device failure," *IEDM*, pp. 187–190, 1998.

- [30] M. Alam, B. Weir, J. Bude, P. Silverman, and D. Monroe, "Explanation of soft

and hard breakdown and its consequences for area scaling," *IEDM Tech. Dig.*, pp. 449–452, 1999.

- [31] S. Bruyere, E. Vincent, and G. Ghibaudo, "Quasi-breakdown in ultra-thin SiO<sub>2</sub> films: occurrence characterization and reliability assessment methodology," *Proc. Int. Reliab. Phys. Symp.*, pp. 48–54, 2000.

- [32] B. Weir, P. Silverman, D. Monroe, K. Krisch, M. Alam, G. Alers, T. Sorsch, G. Timp, F.Baumann, C. Liu, Y. Ma, and D. Hwang, "Ultra-thin gate dielectrics: they break down, but do they fail?" *IEDM Tech. Dig.*, pp. 73–76, 1997.

- [33] K. P. Cheung, "Soft breakdown in thin gate oxide: a measurement artifact," *Proc. Int. Reliab. Phys. Symp.*, pp. 432–436, 2003.

- [34] K. Farmer, R. Saletti, and R. Buhrman, "Current fluctuations and silicon dioxide wear-out in metal-oxide-semiconductor tunnel diodes," *Appl. Phys. Lett.*, vol. 52, pp. 1749–1751, 1988.

- [35] F. Monsieur, E. Vincent, D. Roy, S. Bruyere, J. C. Vildeuil, G. Pananakakis, and G. Ghibaudo, "A thorough investigation of progressive breakdown in ultra-thin oxides: Physical understanding and application for industrial reliability assessment," *Proc. Int. Reliab. Phys. Symp.*, pp. 45–54, 2002.

- [36] W. Y. Loh, B. J. Cho, M. F. Li, D. S. H. Chan, C. H. Ang, J. Z. Zheng, and D. L. Kwong, "Localized oxide degradation in ultrathin gate dielectric and its statistical analysis," *IEEE Trans. Electron Devices*, vol. 50, pp. 967–972, 2003.

- [37] Y. Wu, Q. Xiang, D. Bang, G. Lucovsky, and M.-R. Lin, "Time dependent dielectric wearout (TDDW) technique for reliability of ultrathin gate oxides," *IEEE Electron Device Lett.*, vol. 20, pp. 262–264, 1999.

- [38] J. Maserjian and N. Zamani, "Behavior of the Si/SiO<sub>2</sub> interface observed by fowler-nordheim tunneling," J. Appl. Phys., vol. 53, pp. 559–567, 1982.

- [39] J. Maserjian and N. Zamani, "Observation of positive charged state generation near the Si/SiO<sub>2</sub> interface during Fowler-Nordheim tunneling," *J. Vacc. Sci. Tech.*, vol. 20, pp. 743–746, 1982.

- [40] S. Aritome, R. Shirota, G. Hemink, T. Endoh, and F. Masuoka, "Reliability

issues of flash memory cells," Proc. IEEE, vol. 81, pp. 776–778, 1993.

- [41] P. Olivo, B. Ricc'o, and E. Sangiorgi, "High-field-induced voltage-dependent oxide charge," *Appl. Phys. Lett.*, vol. 48, pp. 1135–1137, 1986.

- [42] R. Moazzami and C. Hu, "Stress-induced current in silicon dioxide films," *IEDM Tech. Dig.*, pp. 139–142, 1992.

- [43] D. J. Dumin, S. Mopuri, S. Vanchinathan, R. S. Scott, and R. Suhramoniam,

"High field emission related oxide wearout and breakdown," *Proc. Int. Reliab. Phys. Symp.*, pp. 143–153, 1994.

- [44] D. J. Dumin, J. R. Cooper, J. R. Maddux, R. S. Scott, and D.-P. Wang,

"Low-level leakage currents in thin silicon oxide films," *J. Appl. Phys.*, vol. 76, pp. 319–327, 1994.

- [45] K. Sakakibara, N. Ajika, K. Eikyu, K. Ishikawa, and H. Miyoshi, "A quantitative analysis of time-decay reproducible stress-induced leakage current in SiO<sub>2</sub> films," *IEEE Trans. Electron Devices*, vol. 44, pp. 1002–1008, 1997.

- [46] K. Sakakibara, N. Ajika, M. Hatanaka, and H. Miyoshi, "A quantitative analysis of stress induced excess current (SIEC) in SiO<sub>2</sub> films," *Proc. Int. Reliab. Phys. Symp.*, pp. 100–107, 1996.

- [47] D. J. Dumin and J. R. Maddux, "Correlation of stress-induced leakage current in thin oxides with trap generation inside the oxides," *IEEE Trans. Electron Devices*, vol. 40, pp. 986–993, 1993.

- [48] D. Ielmini, A. S. Spinelli, A. L. Lacaita, D. J. DiMaria, and G. Ghidini, "Experimental and numerical analysis of the quantum yield," *IEDM Tech. Dig.*, pp. 331–334, 2000.

- [49] R. S. Scott, N. A. Dumin, T. W. Hughes, and D. J. Dumin, "Properties of high voltage stress generated traps in thin silicon oxides," *Proc. Int. Reliab. Phys. Symp.*, pp. 131–141, 1995.

- [50] R. S. Scott, N. A. Dumin, T. W. Hughes, D. J. Dumin, and B. T. Moore, "Properties of high-voltage stress generated traps in thin silicon oxide," *IEEE Trans. Electron Devices*, vol. 43, pp. 1133–1143, 1996.

- [51] J. D. Blauwe, J. V. Houdt, D. Wellekens, G. Groeseneken, and H. E. Maes, "SILC-related effects in flash E<sup>2</sup>PROM's — part II: prediction of steadystate SILC-related disturb characteristics," *IEEE Trans. Electron Devices*, vol. 45, pp. 1751–1760, 1998.

- [52] D. Ielmini, A. S. Spinelli, M. A. Rigamonti, and A. L. Lacaita, "Modeling of SILC based on electron and hole tunneling—part I: transient effects," *IEEE Trans. Electron Devices*, vol. 47, pp. 1258–1265, 2000.

- [53] T. Wang, N.-K. Zous, and C.-C. Yeh, "Role of positive trapped charge in stress-induced leakage current for Flash EEPROM devices," *IEEE Trans. Electron Devices*, vol. 49, pp. 1910–1916, 2002.

- [54] J. H. Stathis, A. Vayshenker, P. R. Varekamp, E. Y. Wu, C. Montrose, J. McKenna, D. J. DiMaria, L.-K. Han, E. Cartier, R. A. Wachnik, and B. P. Linder, "Breakdown measurements of ultrathin SiO<sub>2</sub> at low voltage," *Proc. Symp. VLSI Tech.*, pp. 94–95, 2000.

- [55] Q. Lu, K. P. Cheung, N. A. Ciampa, C. T. Liu, C.-P. Chang, J. I. Colonell, W.-Y.-C. Lai, R. Kiu, J. F. Miner, H. Vaidya, C.-S. Pai, and J. T. Celmens, "A model of the stress time dependence of SILC," *Proc. Int. Reliab. Phys. Symp.*, pp. 396–399, 1999.

- [56] P. Olivo, T. N. Nguyen, and B. Ricc'o, "High-field-induced degradation in ultra-thin SiO<sub>2</sub> films," *IEEE Trans. Electron Devices*, vol. 35, pp. 2259–2267, 1988.

- [57] D. J. DiMaria and E. Cartier, "Mechanism for stress-induced leakage currents in thin silicon dioxide films," J. Appl. Phys., vol. 78, pp. 3883–3894, 1995.

- [58] N. K. Patel and A. Toriumi, "Stress-induced leakage current in ultrathin SiO<sub>2</sub> films," *Appl. Phys. Lett.*, vol. 64, pp. 1809–1811, 1994.

- [59] K. Lai, W.-M. Chen, M.-Y. Hao, J. Lee, M. Gardner, and J. Fulford, "'Turnaround' effects of stress-induced leakage current of ultrathin N<sub>2</sub>O-annealed oxides," *Appl. Phys. Lett.*, vol. 67, pp. 673–675, 1995.

- [60] J. Wu, L. F. Register, and E. Rosenbaum, "Trap-assisted tunneling current

through ultra-thin oxide," Proc. Int. Reliab. Phys. Symp., pp. 389-395, 1999.

- [61] H. Hwang, W. Ting, B. Main, D. L. Kwong, and J. Lee, "Electrical characteristics of ultrathin oxynitride gate dielectric prepared by rapid thermal oxidation of Si in N<sub>2</sub>O,"*Appl. Phys. Lett.*, vol. 57, pp. 1010–1011, 1990.

- [62] W. Ting, G. Q. Lo, J. Ahn, T. Y. Chu, and D.-L. Kwong, "Comparison of dielectric wear-out between oxides grown in O<sub>2</sub> and N<sub>2</sub>O," *Proc. Int. Reliab. Phys. Symp.*, pp. 323–326, 1991.

- [63] J. Ahn, J. Kim, G. G. Lo, and D. L. Kwong, "Suppression of stress-induced leakage current in ultrathin N<sub>2</sub>O oxides," *Appl. Phys. Lett.*, vol. 60, pp. 2809–2811, 1992.

- [64] G. W. Yoon, A. B. Joshi, J. Kim, and D.-L. Kwong, "High-field-induced ultrahin N<sub>2</sub>O oxide," *IEEE Electron Device Lett.*, vol. 14, pp. 231–233, 1993.

- [65] G. Hemink, T. Endoh, and R. Shirota, "Modeling of the hole current caused by fowler-nordheim tunneling through thin oxides," *Jpn. J. Appl. Phys.*, vol. 33, pp. 546–549, 1989.

- [66] K. F. Schuegraf and C. Hu, "Hole injection SiO<sub>2</sub> breakdown model for very low voltage lifetime extrapolation," *IEEE Trans. Electron Devices*, vol. 41, pp. 761–767, 1994.

- [67] R. Rofan and C. Hu, "Stress-induced oxide leakage," *IEEE Electron Device Lett.*, vol. 12, pp. 632–634, 1991.

- [68] D. Ielmini, A. S. Spinelli, and A. L. Lacaita, "Experimental evidence of recombination-assisted leakage in thin oxides," *Appl. Phys. Lett.*, vol. 76, pp. 1719–1721,2000.

- [69] D. Ielmini, A. S. Spinelli, A. L. Lacaita, and G. Ghidini, "Evidence of recombination at oxide defects and new SILC model," *Proc. Int. Reliab. Phys. Symp.*, pp. 48–54, 2000.

- [70] D. Ielmini, A. S. Spinelli, M. A. Rigamonti, and A. L. Lacaita, "Modeling of SILC based on electron and hole tunneling—part I: steady-state," *IEEE Trans. Electron Devices*, vol. 47, pp. 1266–1272, 2000.

- [71] T. Wang, N.-K. Zous, J.-L. Lai, and C. Huang, "Hot hole stress induced leakage current (SILC) transient in tunnel oxides," *IEEE Electron Device Lett.*, vol. 19, pp. 411–413, 1998.

- [72] N.-K. Zous, T. Wang, C.-C. Yeh, C.-W. Tsai, and C. Huang, "A comparative study of SILC transient characteristics and mechanisms in FN stressed and hot hole stressed tunnel oxides," *Proc. Int. Reliab. Phys. Symp.*, pp. 405–409, 1999.