### DESIGN AND IMPLEMENTATION OF MULTIPLE ADDRESS PARALLEL TRANSMISSION ARCHITECTURE FOR STORAGE AREA NETWORK

# MENG BIN (M.Eng., Xi'an Jiaotong Univ.)

A THESIS SUBMITTED

FOR THE DEGREE OF MASTER OF ENGINEERING

DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

NATIONAL UNIVERSITY OF SINGAPORE

2004

#### Acknowledgements

I am sincerely grateful to my supervisor Prof. Chong Tow Chong for giving me the privilege and honor to work with him over the last two years. Without Prof. Chong's constant support, insightful advice, excellent judgment, and, more importantly, his demand for top-quality research, this thesis would not be possible. I am continuously amazed and humbled by his infinite knowledge and unmatched wisdom.

I would also like to thank Yong Khai Leong and Patrick B. T. Khoo for introducing me to the subject of network storage, giving a necessary direction to my research, providing continuous encouragement throughout my M.Eng.

This work would not be possible without a long-lasting support and infinite patience of DSI MCSA group. I would like to thank Core Technology members, Don Lee, Alvin Koy, Wei Minglong, Li Zhixiang and Implementation members, Wilson Wang, Jimmy Jiang, Law Sie Yong, Ng Tiong King, Wang Haichen, Huang Xiaogang, Yeo Heng Ngi. Since a large part of my work was experimental, I am further indebted to MCSA Application team for their extreme generosity in providing the abundant resources needed for completing this M.Eng. Many thanks to Vincent Leo, Wang Donghong, Daniel Khoo, Premalathe Naidu and Han Binhua.

Furthermore, I would like to thank my friends and fellow students at the National University of Singapore. I am especially grateful to Wu Daowei, Lin Song, Shen Yatao and Chen Li for being absolutely awesome friends and treating me to frequent philosophical discussions.

I am thankful to 20<sup>th</sup> *IEEE Symposium on Mass Storage Systems* reviewers for providing their helpful comments on earlier versions of this work.

Last, but not least, I would like to thank my parents. Without their continuous support this work would be simply impossible.

## **Contents**

| Ack  | nowled  | gements                                                       | i  |

|------|---------|---------------------------------------------------------------|----|

| Sum  | mary    |                                                               | iv |

| List | of Figu | ıres                                                          | vi |

| 1    | Ü       | oduction                                                      |    |

| 1    | 1.1     | Background and Motivations                                    |    |

|      | 1.2     | An Introduction to HyperSCSI Protocol                         |    |

|      | 1.3     | Contribution and Organization of Thesis                       |    |

| 2    | The     | oretical Models                                               | 12 |

|      | 2.1     | Network Topology - Ethernet and IP Packet Switching Network   |    |

|      | 2.2     | Multiple Address Parallel Transmission                        |    |

|      |         | 2.2.1 Case One: Single Data Flow on Asymmetrical Networks     |    |

|      |         | 2.2.2 Case Two: Multiple Data Flows on Asymmetrical Network.  |    |

|      | 2.3     | Load Balancing Algorithms for Two Stage Schedulers            |    |

|      |         | 2.3.1 Reverse Generalized Processor Sharing (RGPS)            | 21 |

|      |         | 2.3.2 Reverse Weighted Round Robin (RWRR)                     |    |

|      |         | 2.3.3 Reverse Weighted Fair Queuing (RWFQ)                    | 23 |

|      |         | 2.3.4 Reverse Deficit Round Robin (RDRR)                      |    |

|      | 2.4     | Data Flow Priority                                            | 27 |

|      |         | 2.4.1 One Virtual Channel vs. Multiple Sub Channels           |    |

|      |         | 2.4.2 Multiple Data Flows' Priorities with Service Discipline |    |

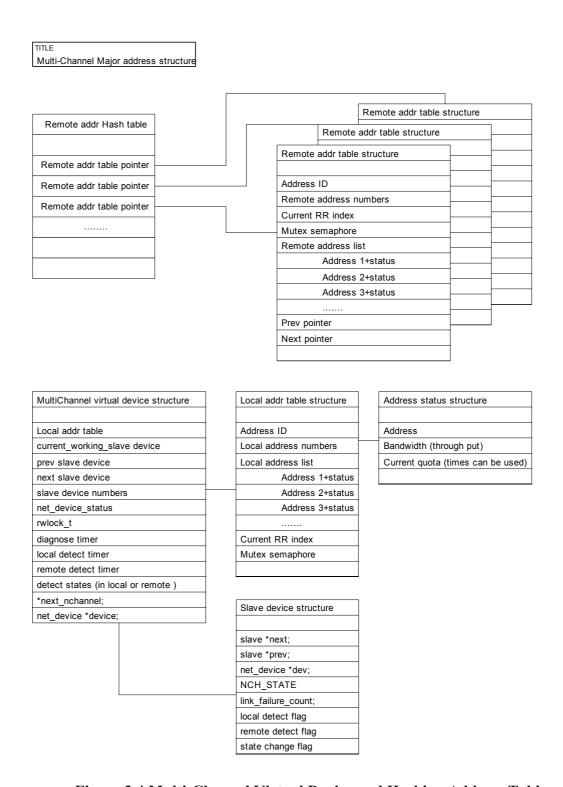

|      | 2.5     | Data Flow Restore Hashing Address Table and Reordering        |    |

|      |         | 2.5.1 Hash Chaining Structure for Address Restoring           |    |

|      |         | 2.5.2 Out-of-order Analysis                                   |    |

|      |         | 2.5.3 Retransmission Threshold and Reorder Buffer             |    |

|      | 2.6     | Fault Detection and Cost Estimation                           |    |

|      |         | 2.6.1 Three Fault Detection algorithms                        |    |

|      |         | 2.6.2 Cost Estimation for Local and Remote Fault Detection    | 40 |

| 3    | Imp     | lementation                                                   |    |

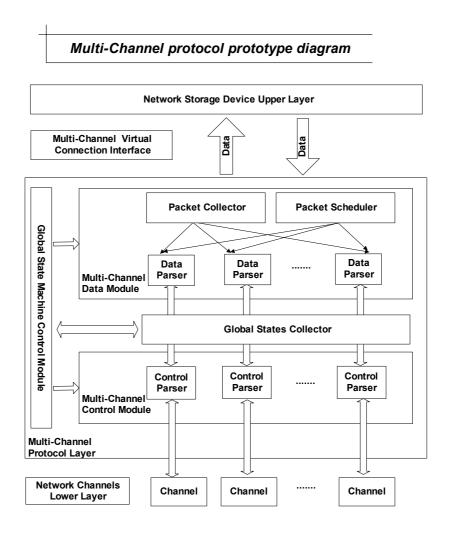

|      | 3.1     | Multiple Address Parallel Transmission Protocol               | 44 |

|      |         | 3.1.1 Multi-Channel Data Module                               |    |

|      |         | 3.1.2 Multi-Channel Control Module                            |    |

|      |         | 3.1.3 Global State Machine Module                             |    |

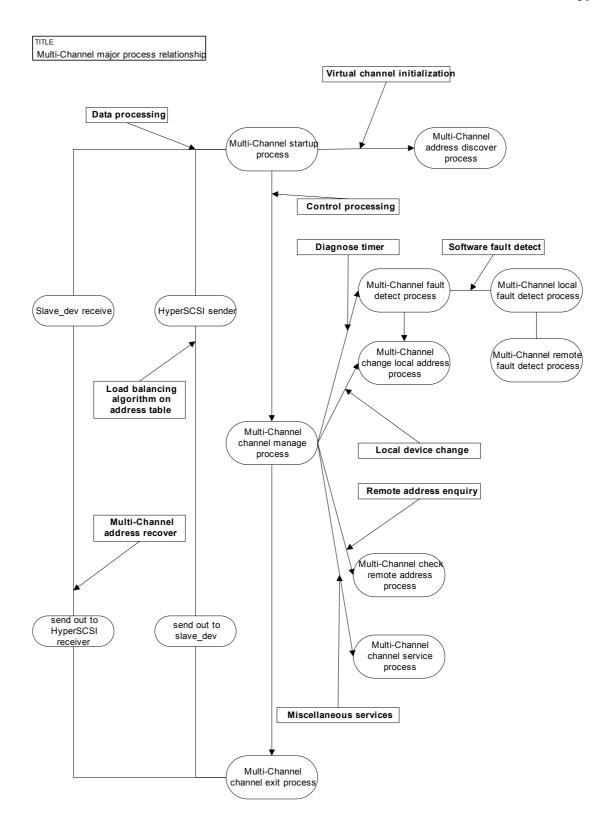

|      | 3.2     | Multi-Channel Protocol Processes Software Flow Charts         |    |

|      |         | 3.2.1 Major Flow Charts, Key Data Structures and Events List  |    |

|      |         | 3.2.2 Multi-Channel Packets Flow and Packet Types             |    |

|      |         | 3.2.3 Multi-Channel Address Discover                          |    |

|      |         | 3.2.4 Multi-Channel Address Table Change and Rebuild          |    |

|      |         | 3.2.5 Multi-Channel Fault Detection Flow Chart                |    |

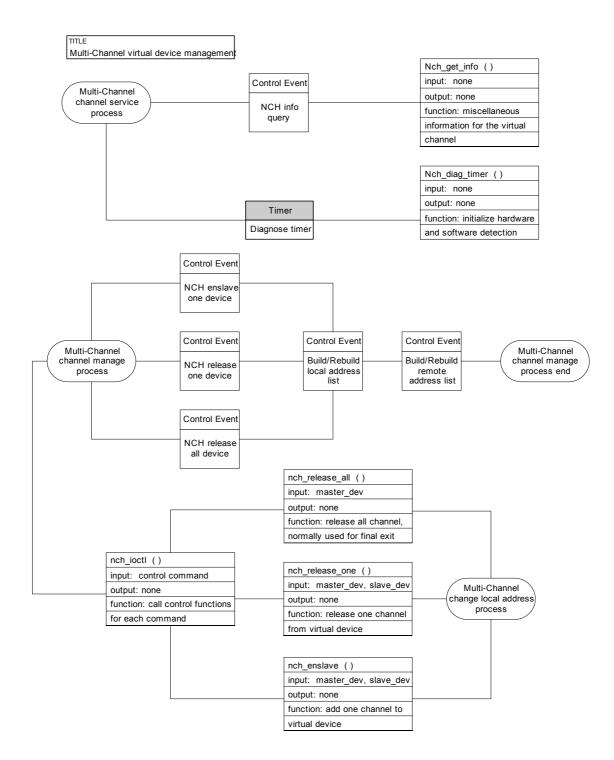

|      |         | 3.2.6 Virtual Device Management Flow Chart                    | 59 |

| 4    | Resi    | ults and Discussion                                           | 62 |

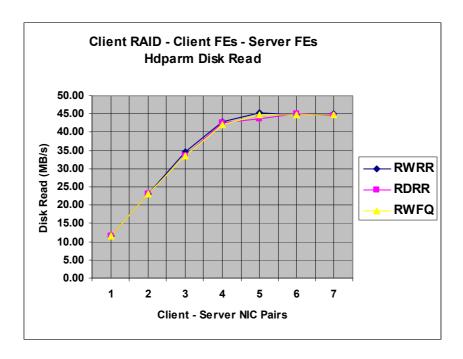

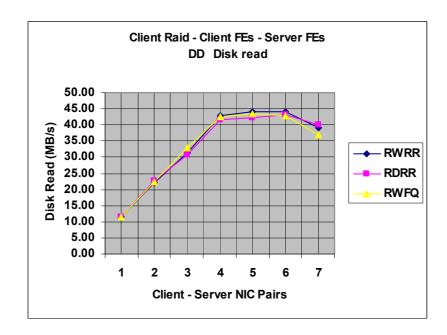

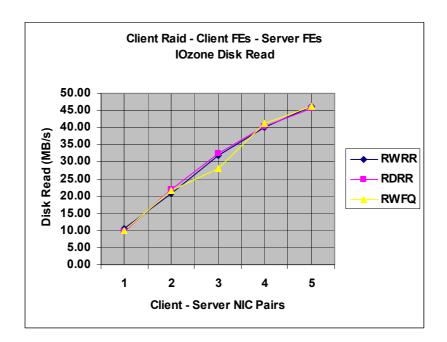

|            | 4.1 | Disk Read Performance                                        | 63 |  |

|------------|-----|--------------------------------------------------------------|----|--|

|            |     | 4.1.1 Multi-Channel with Symmetrical Parallel Network        | 63 |  |

|            |     | 4.1.2 Multi-Channel with Asymmetrical Parallel Network       | 65 |  |

|            |     | 4.1.3 Influence of System Resources on Disk Read Performance | 66 |  |

|            | 4.2 | Out-of-order Rate Analysis                                   | 69 |  |

|            | 4.3 | Packet Size's Affect on Out-of-order and Performance         | 72 |  |

|            | 4.4 | Multiple Clients - Multiple Channels Load Balancing          | 75 |  |

| 5          | Con | clusions and Future Work                                     | 78 |  |

|            |     | Extensions                                                   |    |  |

| References |     |                                                              |    |  |

| Appendices |     |                                                              |    |  |

| 11         |     | endix A Fault Tolerance Cost Estimation                      |    |  |

#### **Summary**

The demand for high availability and high performance in Storage Area Network (SAN) drives more and more effort on network architecture design. To build such a Storage Area Network, the use of parallel channels is attractive. At present, most parallel solutions heavily depend on hardware components and do not provide end-to-end parallel connection. This thesis provides a theoretical model and an implementation demonstrating the multiple address parallel transmission architecture. This architecture provides end-to-end parallel connections between network storage devices without any addition of components.

At first, the theories of the network topology and parallel data transmission model are studied. This parallel data transmission architecture is based on packet switching network. SAN topology using this structure will have good scalability and fault tolerance but without much additional complexity. The model of this transmission architecture is composed of two stage load balancing algorithms, data flow priority algorithms, data flow restoring, reordering and fault tolerance algorithms.

Three load balancing algorithms, Reverse Weight Round Robin (RWRR), Reverse Deficit Round Robin (RDRR) and Reverse Weighted Fair Queuing (RWFQ), are proposed and implemented with small computation overhead. The mechanism of out-of-order in parallel architecture is analyzed in detail. An efficient out-of-order estimation algorithm is used to setup retransmission threshold and allocate reordering buffer. Furthermore, since this transmission architecture uses redundant channels, the scheduler can provide fault tolerance by using either hardware-based, software local loop back andor remote acknowledge detection methods.

To demonstrate the multiple address parallel transmission protocol (MAP-TP) in SAN, we implement the protocol as network layer in the Linux kernel module of the HyperSCSI and measure the performance by testing the disk read speed of the virtual SCSI device with three popular benchmark tools of HDPARM, DD and IOZONE.

The result shows that HyperSCSI bandwidth can be increased above 380% when 4 links are used, which is acceptable for high speed transmission. Interestingly, we also found that out-of-order rate does not affect the disk read performance very much, which can be explained by the theory of schedule delay and out-of-order distance.

In addition, by supporting Ethernet MAC and IP packets, the network storage devices can work in both LAN and WAN environments. This architecture can be a key factor in deploying SANs, which can provide a highly scalable bandwidth with full redundancy over switched and parallel data paths.

# List of Figures

| Figure 1.1 Traditional Multi-channel Local Area Network                     | 2    |

|-----------------------------------------------------------------------------|------|

| Figure 1.2 Asymmetrical Parallel Architecture in Packet Switching Network   | 3    |

| Figure 1.3 Multi-Channel Network Architecture for HyperSCSI Protocol        | 9    |

| Figure 2.1 Model for Multiple Address Parallel Transmission Architecture    | 15   |

| Figure 2.2 Single Data Flow Scheduling on Two Stage Address Table Scheduler | 16   |

| Figure 2.3 Load Balancing of Multiple Data Flows and Multiple Nodes         | 18   |

| Figure 2.4 Reverse Deficit Round Robin Scheduler                            | 26   |

| Figure 2.5 Single Virtual Channel and Multiple Channels                     | 28   |

| Figure 2.6 Hashing Algorithm for Data Flow Restoring                        |      |

| Figure 2.7 Out-of-order Caused by Different Packet Sizes                    |      |

| Figure 2.8 Schedule Delay in Each Schedule Round                            | . 34 |

| Figure 2.9 Local Loop Back and Remote Acknowledge Detection Cost Estimation | . 42 |

| Figure 2.10 Probability Distribution of the Working NICs                    |      |

| Figure 3.1 Multi-Channel Protocol Layer Diagram.                            | . 45 |

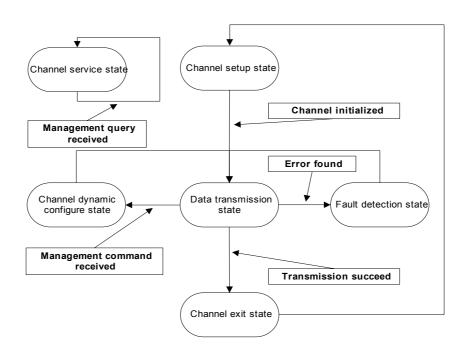

| Figure 3.2 Multi-Channel Data Transmission State Transition Diagram         |      |

| Figure 3.3 Data and Control Processes' Flow Chart                           |      |

| Figure 3.4 Multi-Channel Virtual Device and Hashing Address Table           |      |

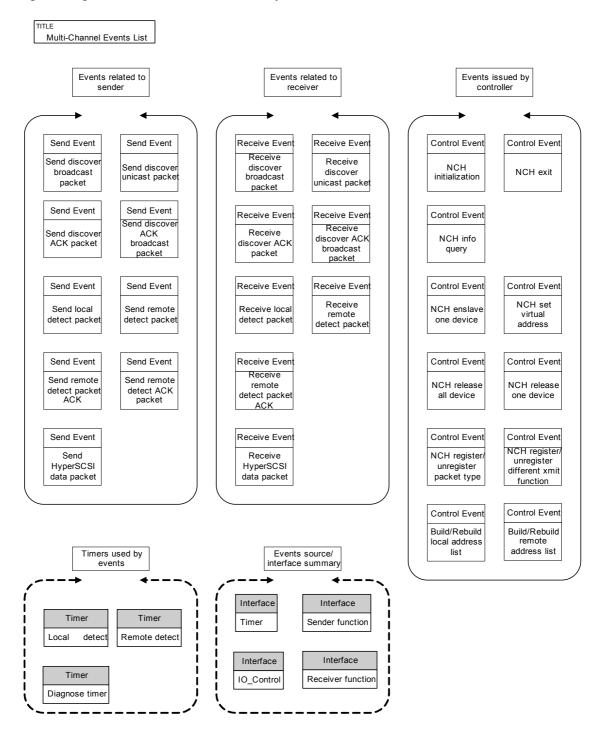

| Figure 3.5 Events List for Sender, Receiver and Controller                  |      |

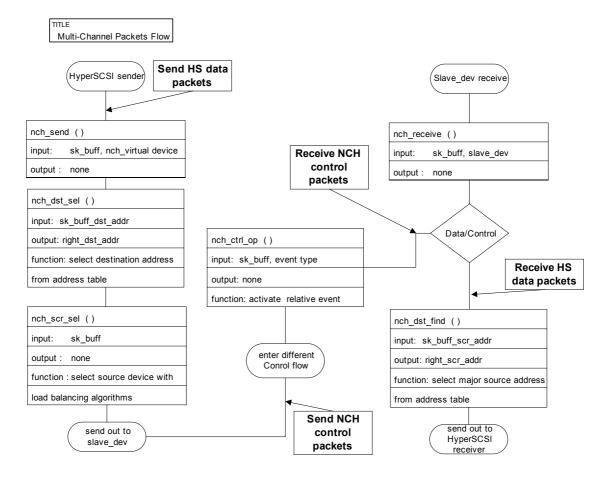

| Figure 3.6 Multi-Channel Packet Flow.                                       |      |

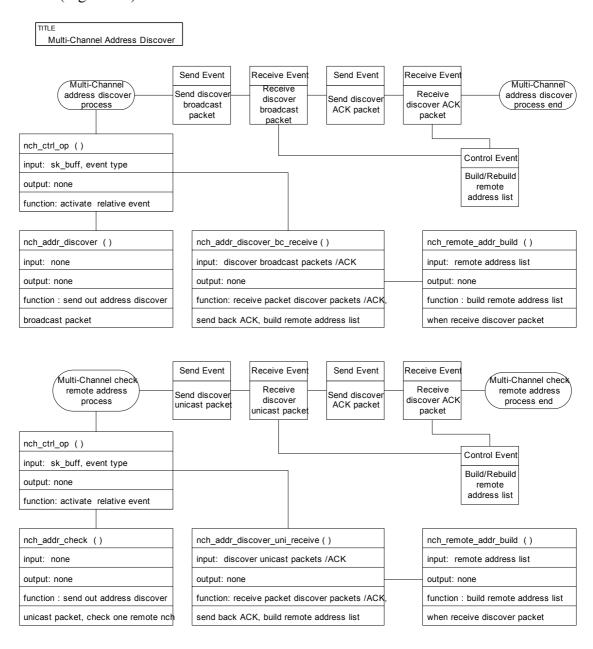

| Figure 3.7 Multi-Channel Address Discover                                   |      |

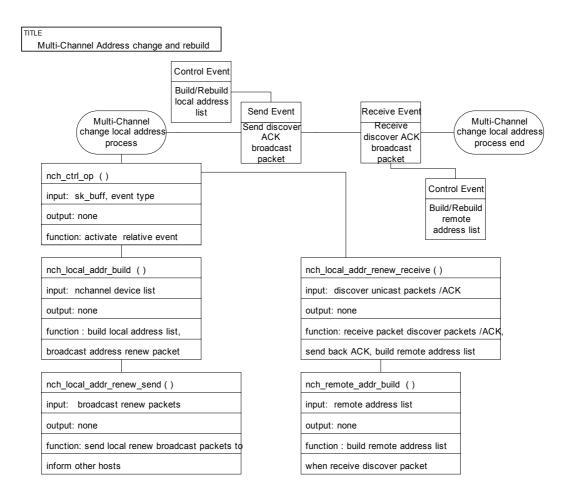

| Figure 3.8 Multi-Channel Address Change and Address Table Rebuild           |      |

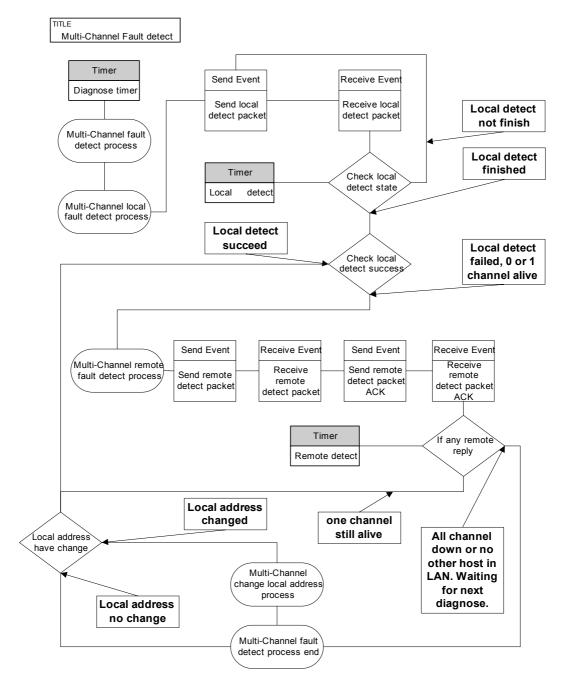

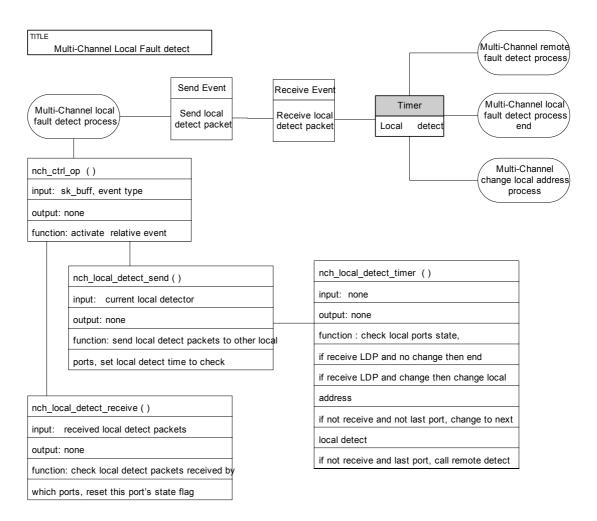

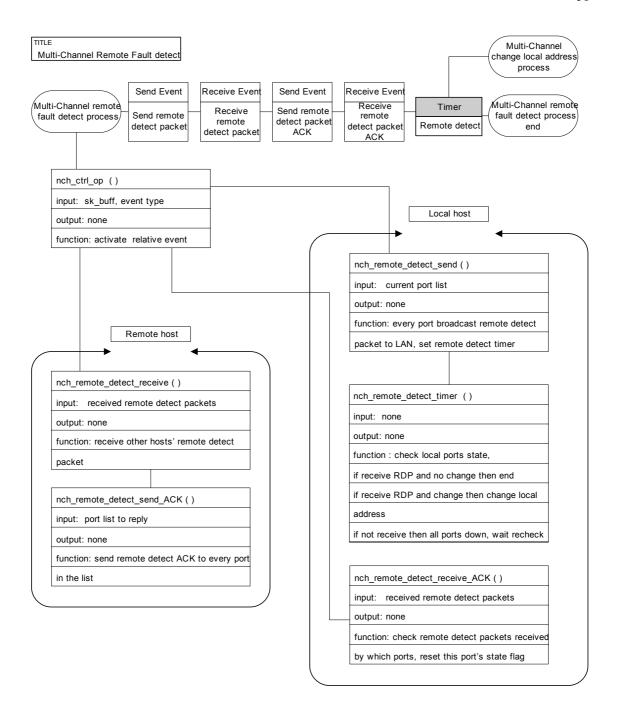

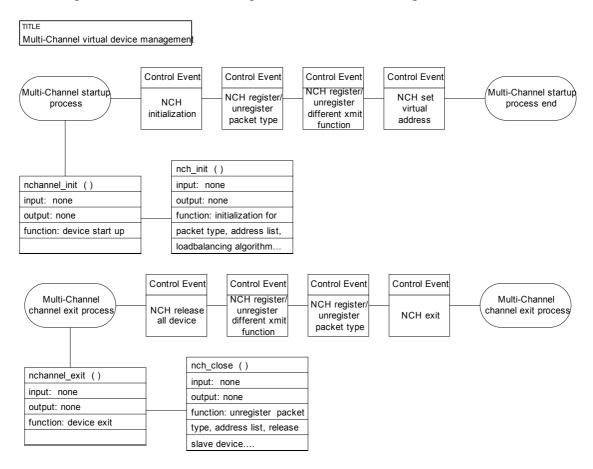

| Figure 3.9 Flow Chart of Multi-Channel Fault Detect                         |      |

| Figure 3.10 Multi-Channel Local Loop Back Detect                            |      |

| Figure 3.11 Multi-Channel Remote Acknowledge Fault Detect                   |      |

| Figure 3.12 Multi-Channel Virtual Device Startup and Exit                   |      |

| Figure 3.13 Channel Management and Channel Service                          |      |

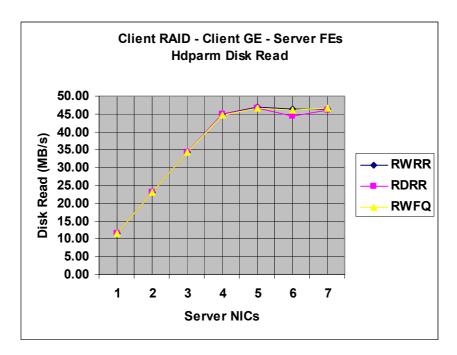

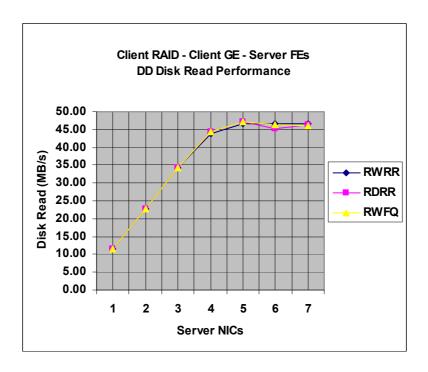

| Figure 4.1 Client RAID Symmetrical FE Pairs HDPARM Read                     |      |

| Figure 4.2 Client RAID Symmetrical FE Pairs DD Read                         |      |

| Figure 4.3 Client RAID Symmetrical FE Pairs IOZONE Read                     | . 64 |

| Figure 4.4 Client RAID Asymmetrical GE-FE Pairs HDPARM Read                 |      |

| Figure 4.5 Client RAID Asymmetrical GE-FE Pairs DD Read.                    |      |

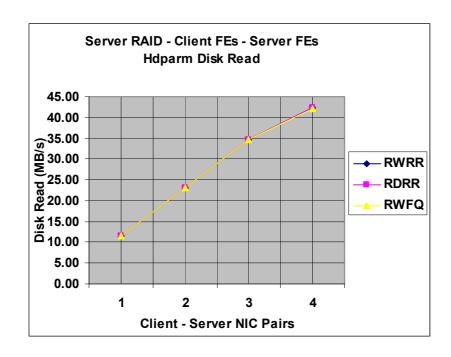

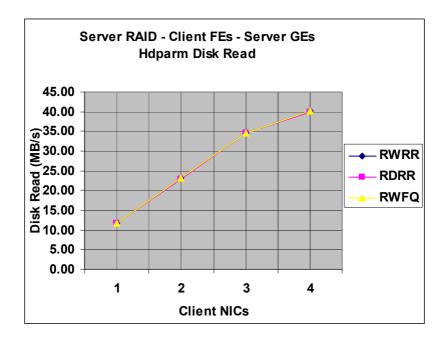

| Figure 4.6 Server RAID Symmetrical FE Pairs HDPARM Read                     |      |

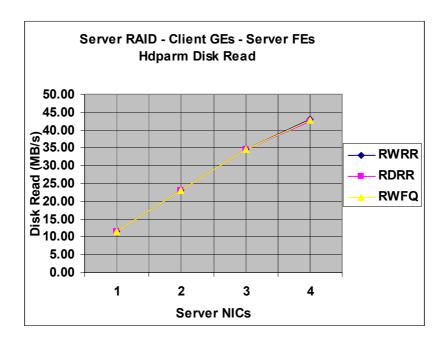

| Figure 4.7 Server RAID Asymmetrical GE-FE Pairs HDPARM Read                 |      |

| Figure 4.8 Server RAID Asymmetrical FE-GE Pairs HDPARM Read                 |      |

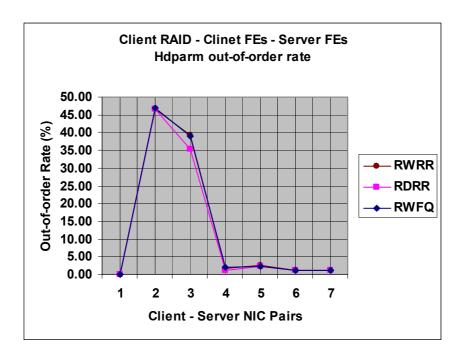

| Figure 4.9 Client RAID Symmetrical FE Pairs HDPARM Out-of-order Rate        |      |

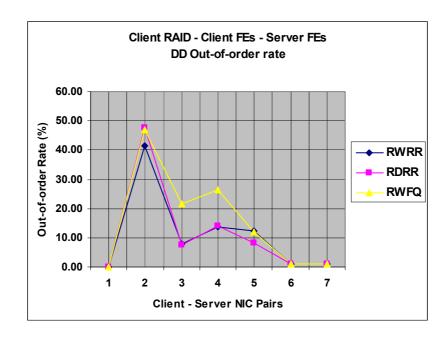

| Figure 4.10 Client RAID Symmetrical FE Pairs DD Out-of-order Rate           |      |

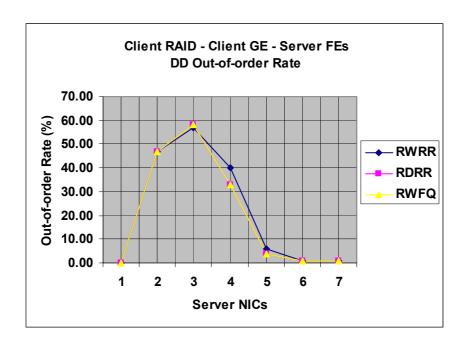

| Figure 4.11 Asymmetrical GE-FE Pairs DD Out-of-order Rate                   |      |

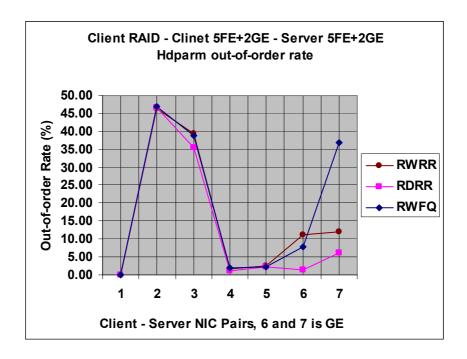

| Figure 4.12 Asymmetrical GE-FE Mixed Pairs, HDPARM Out-of-order Rate        |      |

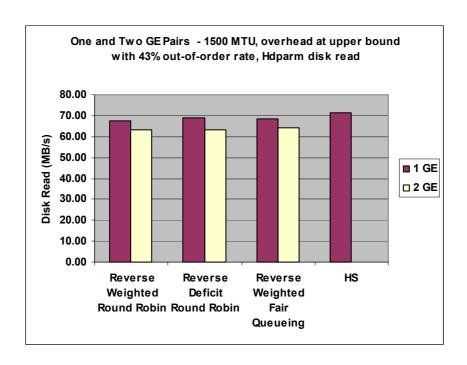

| Figure 4.13 GE Pairs HDPARM Read, MTU = 1500, Out-of-order Rate = 43%       |      |

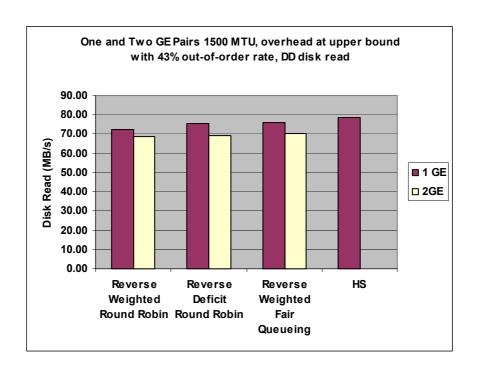

| Figure 4.14 GE Pairs DD Read, MTU = 1500, Out-of-order Rate = 43%           |      |

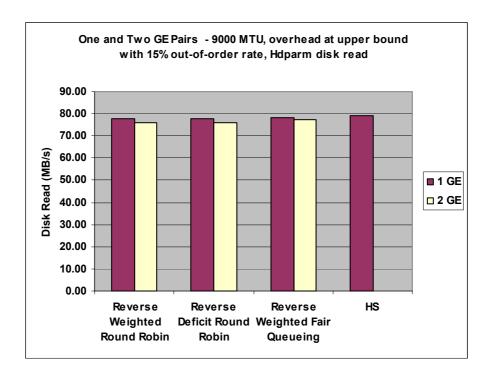

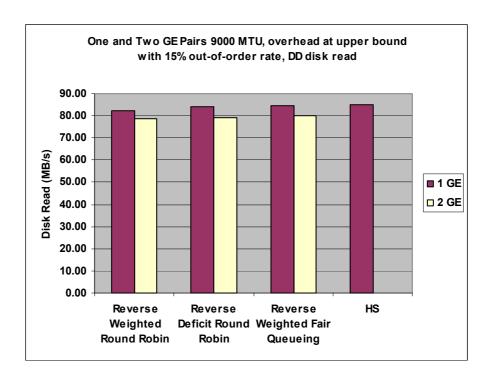

| Figure 4.15 GE Pairs HDPARM Read, MTU = 9000, Out-of-order Rate = 15%       |      |

| Figure 4.16 GE Pairs DD Read, MTU = 9000, Out-of-order Rate = 15%           |      |

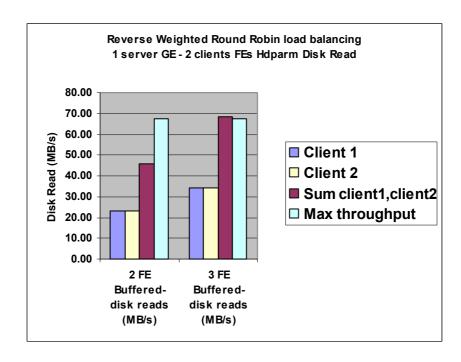

| Figure 4.17 RWRR Load Balancing on Two Clients with GE-FE Pairs             |      |

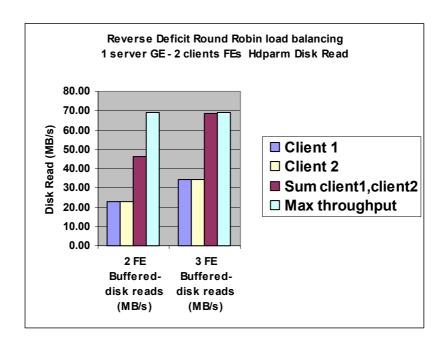

| Figure 4.18 RDRR Load Balancing on Two Clients with GE-FE Pairs             |      |

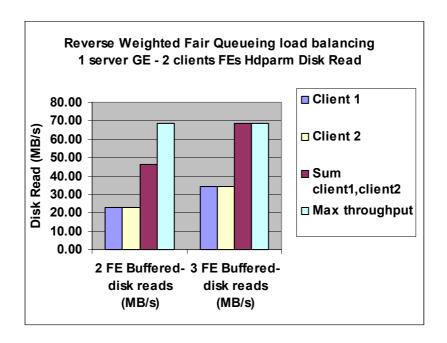

| Figure 4.19 RWFO Load Balancing on Two Clients with GE-FE Pairs             | . 77 |

#### **Chapter One**

#### 1 Introduction

#### 1.1 Background and Motivations

A Storage Area Network (SAN) is a specialized, high-speed network attaching servers and storage devices. It is sometimes called "the network behind the servers". A SAN allows "any to any" connection across the network, using interconnect elements such as routers, gateways, hubs and switches.

A Storage Area Network (SAN) is any high-performance network whose primary purpose is to enable storage devices to communicate with computer systems and with each other

The demand for high availability and high performance in Storage Area Network (SAN) drives more and more effort on network architecture design. The SAN's performance must be able to grow as the organization's information storage and processing needs grow. A successful SAN should provide an extra performance for the high-volume data and message traffic of client and server. Thus, the scalability of SAN is quite important, because it is not practical to replace a SAN very often for enterprise applications. To build a scalable Storage Area Network, the use of parallel data path network architecture is attractive.

Current parallel network architectures can be classified into two categories: non packet switching based and packet switching based architectures. The non packet switching parallel network architectures emerged at 1980s'. First, two popular non packet switching architectures are demonstrated below.

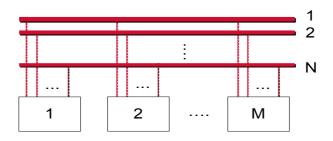

One traditional research on parallel network architecture concentrates on Multichannel Local Area Network (MLAN) architecture [1]. The MLAN is based on a bus sharing architecture (Figure 1.1). Although no middle gateways or switches are required, this bus sharing architecture has the disadvantage that only two devices can communicate at one time.

Figure 1.1 Traditional Multi-channel Local Area Network

The other architecture is Direct Attached Storage (DAS) network, where storage area network uses directly connected parallel SCSI network [2]. The current maximum data transmission performance of DAS is 200MB/s. However, faster speed means shorter distance, normally no more than 30 meters. Limited by the distance, DAS is not a good solution for parallel SAN architecture.

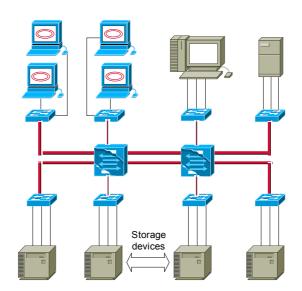

With the rapid evolution of the switching technology in 1990s', research in parallel network gradually focus on packet switching network (as showed in Figure 1.2). The algorithms which schedule data streams to parallel paths are also studied as inverse multiplexing [3]. The parallel packet switching network is more scalable and flexible than the MLAN and DAS. Additionally, two packet switched storage devices can communicate without affecting other devices' performance.

The parallel packet switching network architecture can be built on one particular link or end-to-end communication [4]. The aggregate bandwidth built on one

particular link is commonly used to increase local area network performance. These scheduling algorithms are relatively simple because of the symmetrical parallel architecture. However, it is highly dependent on switches to provide load balancing services. Most contemporary parallel implementations work on one particular link, for instance:

Link Aggregation Control Protocol (LACP) [5] is a sub layer for CSMA/CD MAC. Designed for IEEE 802.3 MAC, it can not adapt to the load balancing based on IP layer address; and LACP can not operate across multiple data rates, which means all network interface are restricted to the same transfer speed. Furthermore, LACP transfer one conversation on one physical network interface to avoid packets disorder, bandwidths on other interfaces are wasted.

Figure 1.2 Asymmetrical Parallel Architecture in Packet Switching Network

Linux Bonding, Cisco EtherChannel and Sun Trunking [6]: All these technologies refer to using multiple network interfaces to compose a virtual link, which use one pair of MAC address. This technology is similar to the LACP except that it heavily relies on switch's ability to provide traffic load balancing (known as

virtual LAN technology). This will increases the cost and complexity of the SAN topology.

The parallel packet switching architecture based on end-to-end parallel transmission routes different packets belonging to a single end-to-end application along multiple distinct network paths [7]. This end-to-end parallel technology can provide a highly scalable bandwidth over long distances, and with the ability to provide full redundancy and parallel data paths. However, there are several significant challenges to end-to-end protocol, which must be responsible for managing the multiple flows and resequencing packets with large skew. Due to these challenges, there is no available end-to-end parallel protocol at present.

On the storage area network application side, many contemporary SAN solutions such as, HyperSCSI, FCIP, iSCSI, iFCP and iSNS [8], are working on packet switching network. For these solutions, parallel packet switching technology is in great need to meet the new requirements for high scalability and reliability over long distance. Recently, GridFTP claims that it provides end-to-end parallel TCP streams to improve performance [9,10]. However, it actually provides multiple data flows on the same path. This only increases the channel utilization not the physical channel bandwidth.

As we discussed here, the end-to-end parallel transmission architecture will be a key factor in SAN solutions. Thus, we start a study on multiple address parallel transmission protocol (MAP-TP) for SAN to meet the new requirement of high scalability and reliability over long distances. This protocol is also referred as "Multichannel" technology throughout the thesis. The aim of the study is to design and implement an end-to-end parallel architecture that can increase the network I/O performance between network storage modules by employing more communication

channels in packet switching network. Moreover, a built-in fault tolerance strategy for surviving and restoring from network interface and network failures should be developed.

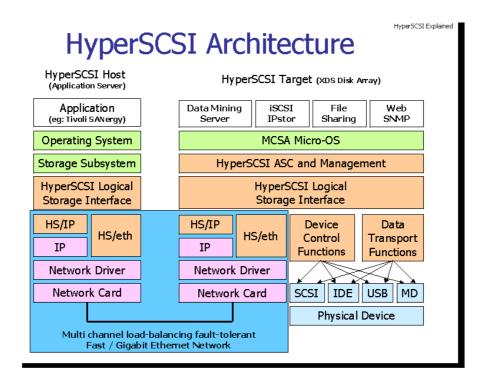

#### 1.2 An Introduction to HyperSCSI Protocol

To demonstrate the multiple address parallel transmission protocol in SAN, MAP-TP protocol is developed and combined with the HyperSCSI network storage protocol. In this section, we will outline some of the key features and basic technical details of HyperSCSI. The architecture relationship between MAP-TP and HyperSCSI is also demonstrated.

Small Computer Systems Interface (SCSI) is the predominant mechanism for various storage and even non-storage devices. To make SCSI "network-enabled", the HyperSCSI is invented for the transmission of SCSI family of protocols across a network.

Since the requirements of local network storage (SAN) and wide-area network storage (SWAN) are quite different, HyperSCSI protocol supports multiple modes of operation. Two such modes are currently being developed, one for local access, Local HyperSCSI over Ethernet (HS/eth), and the other for wide-area connectivity, Wide-Area HyperSCSI over IP (HS/IP). The basic protocol structure is essentially the same, thus allowing devices to speak local or wide-area storage seamlessly.

Many advanced functions and capabilities were built into the HyperSCSI protocol to support other requirements like dynamic management, dynamic flow control and in-band management capabilities. HyperSCSI can provide a minimum level of connectivity for interoperability operations and while supporting advanced vendor-specific or implementation-specific functions. Other possible device specific options include read-only access, removable media locking and data compression.

The HyperSCSI connection setup is a three-step handshaking procedure between a HyperSCSI client and server pair. Typically, in a storage network, the host machine (HyperSCSI client) is responsible for locating and initiating connections to storage devices (HyperSCSI servers). During this process, the HyperSCSI client issues a HCC\_DEVICE\_DISCOVERY via Ethernet broadcast or IP packet, to locate devices on the network. For IP-based situations, a client must specify an IP address (or DNS name) and a HCC\_DEVICE\_DISCOVERY packet is sent over IP directly to the server. Once the HyperSCSI server receives this packet, it checks the client address for authentication purposes and transmits the HCC\_ADN\_REQUEST packet back to the HyperSCSI client. In order for the HyperSCSI client to establish a connection with the HyperSCSI server, it must then send the correct response through a HCC\_ADN\_REPLY command and add the ID numbers of the devices that it has access to into its own registry. If the server successfully authenticates the HCC\_ADN\_REPLY, the connection is accepted and the HyperSCSI client can now send commands to the server.

An ACK mechanism has been adopted to support flow control of data between a HyperSCSI client and server pair. The ACK window size refers to the number of packets that the transmitter may continuously send before waiting for an acknowledgement. This window size must be negotiated and agreed upon before data flow can take place and is set by the requestor through an FC\_ACK\_SNR command. This packet is issued as a separate message and typically, the server will be the one to issue this command so that the server has the ability to balance loads or priorities across multiple clients, although this does not mean that the client may not issue one either. The ACK window size can be set based on traffic loads, or buffer capacities and can be set at start-up or changed dynamically during run time.

When there is a SCSI request from the local OS SCSI upper layer of the host machine, the HyperSCSI client software is responsible for converting the OS-specific SCSI command block together with any relevant data (as in a write command) into a platform independent HyperSCSI Command Block (HCB). The client then encapsulates and fragments the HCB into one or more HCBE\_REQUEST packets that it sends to the HyperSCSI server. SCSI command blocks and user data will therefore be transmitted together in the same packet. The HyperSCSI server receives the data stream, re-assembles the HyperSCSI command block and relevant user data, converts it back to an OS-specific SCSI command block and passes it to the relevant hardware for execution. When the result of this SCSI request is ready, the HyperSCSI server will send the result together with the requested data back to HyperSCSI client by issuing the HCBE\_REPLY packet stream in a similar manner as the request. The HyperSCSI client reassembles the HyperSCSI command block and converts it back to a OS-specific SCSI command block before passing it on to the local OS SCSI upper layer.

During a HyperSCSI connection, the HyperSCSI server will regularly (timerbased) issue a HCC\_ADN\_REQUEST command for three purposes, re-authentication of clients and key-exchange for security, re-negotiation of device options (if permitted), and as a form of "keep-alive". Through this method, servers not only poll the client's status, but also check its identity. Furthermore, if HyperSCSI encryption options are turned on for data transmission, the HCC\_ADN\_REQUEST and HCC\_ADN\_REPLY use an authenticated exchange mechanism to update and change encryption keys. This scheme also allows a device's options to be modified dynamically.

The HyperSCSI client can close a connection by sending an HCC\_DISCONNECT command to the HyperSCSI server. The server will then remove

this client from its connection list and close the connection. Servers do not need to acknowledge disconnect requests from clients because SCSI connections are host-target based.

Feature-wise, the HyperSCSI reference implementation already supports standard SCSI hard drives, IDE hard drives, software RAID / virtualized drives, optical disks (like DVDROM and CDRW), USB devices (like Iomega Zip Disk) and SCSI tape drives (like HP DAT40). We have even successfully used HyperSCSI to write CDs remotely over DSI live corporate LAN. File systems like Microsoft's FAT16/FAT32, SGI's XFS, IBM's JFS and Linux Ext2/Ext3 have all been successfully tested on HyperSCSI drives. HyperSCSI clients and servers have been successfully implemented on Linux, while client versions on Windows 2000 and Solaris 8 are currently in development. Encryption schemes that have already been implemented include 64-bit Blowfish and 128-bit Rijndael. HyperSCSI has been assigned its own IEEE Ethertype Number, and will soon receive a registered IP port for HS/IP implementations.

HyperSCSI provides an opportunity to address various concerns and open up new possibilities for network storage. The Local HS/eth protocol allows the construction of high-speed Ethernet based SANs while the use of Wide-Area HS/IP permits mobile devices like laptops to access the corporate SAN directly (bypassing servers if needed). However, storage devices that only use single network path are not efficient enough. In the HyperSCSI performance testing, it is found that the storage devices have low utilization rate when working on Fast Ethernet network. In this application, the network bandwidth becomes the bottleneck of the whole SAN system.

Figure 1.3 Multi-Channel Network Architecture for HyperSCSI Protocol

To improve the scalability and reliability of HyperSCSI, the MAP-TP protocol is combined with HyperSCSI protocol (Figure 1.3). Multiple network interfaces and network paths are used to enhance the performance and balance the traffic load. Furthermore, the packetisation and virtualization options of HyperSCSI allow us to implement Multi-channel communications with fault tolerance and reliability.

#### 1.3 Contribution and Organization of Thesis

In this thesis, our research emphasis is on the end-to-end multiple address parallel transmission architecture for SAN application. This architecture provides not only scalability, but also the simplicity and reliability. The contributions of this thesis can be summarized as:

1. A theoretical multiple address parallel transmission model is studied. This model provides end-to-end parallel connections between network storage devices without extra hardware.

- 2. Three load balancing algorithms, Reverse Weight Round Robin (RWRR), Reverse Deficit Round Robin (RDRR) and Reverse Weighted Fair Queuing (RWFQ), are proposed and implemented with small computation overhead.

- 3. The mechanism of the out-of-order in parallel architecture is analyzed in detail. An efficient out-of-order estimation algorithm is deduced to setup retransmission threshold and allocate reordering buffer.

- 4. Fault tolerance methods of hardware-based, software local loop back and/or remote acknowledge are studied on parallel redundant channels.

- 5. The multiple address parallel transmission protocol (MAP-TP) is implemented as network layer in the Linux kernel module of the HyperSCSI. The performance is measured by testing the disk read speed of the virtual SCSI device with three popular benchmark tools of HDPARM, DD and IOZONE.

Organization of this thesis is as follows:

In Chapter 2, we will discuss the theoretical model of the end-to-end multiple address parallel transmission architecture. First the parallel network topology is studied, and then an asymmetrical parallel data transmission model is demonstrated. This transmission model is composed of two-stage load balancing algorithm, data flow priority algorithm, data flow restoring, reordering and fault tolerance algorithm. Three load balancing algorithms, Reverse Weight Round Robin (RWRR), Reverse Deficit Round Robin (RDRR) and Reverse Weighted Fair Queuing (RWFQ) are proposed. The mechanism of the out-of-order in parallel architecture is analyzed in detail. An efficient out-of-order estimation algorithm is used to setup retransmission threshold and allocate reordering buffer. Furthermore, since this transmission architecture uses

redundant channels, three fault detection methods of hardware-based, software local loop back and/or remote acknowledge are studied.

In Chapter 3, the multiple address parallel transmission protocol (MAP-TP) will be implemented as network layer in the Linux kernel module of the HyperSCSI. Three major modules: data module, control module and global state machine module are demonstrated. The data module is responsible for sending and receiving data flow packets through multiple network channels. The control module is used to manage multiple channels and selecting load balancing algorithm. The fault tolerance is also considered in the control module. The global state machine inspects global parameters and synchronizes the control and data transmission states transition. Additionally, detail functions of the modules are presented in software design flow charts.

In Chapter 4, we will measure the parallel transmission performance and outof-order delivery by testing the disk read speed of the virtual SCSI device with three popular benchmark tools of HDPARM, DD and IOZONE. Different parallel symmetrical and asymmetrical architectures are studied under all three scheduling algorithms, RWRR, RDRR and RWFQ. All experiments are based on parameters of channel numbers, channel bandwidth, packet size and system resource. By discussing the experimental results, suggestions for MAP-TP design will be provided.

#### **Chapter Two**

#### 2 Theoretical Models

Research on parallel resource modeling is emerging in recent years. Several papers have proposed theoretical models [11, 12, 13, 14, 15, 16, 17] for multiple resources scheduling in parallel architecture network. These theories are quite helpful for designing and evaluating the throughput, delay, and load-balancing algorithm of multiple address parallel transmission architecture. In this chapter we first discuss the theories of the network topology, and then demonstrate an asymmetrical parallel data transmission model in the following sections. This transmission model is composed of two-stage load balancing algorithm, data flow priority algorithm, data flow restoring, reordering and fault tolerance algorithm.

#### 2.1 Network Topology - Ethernet and IP Packet Switching Network

In a SAN, the topology is arbitrary. The storage devices are expected to have variable bandwidths and packets can have variable sizes. To meet these requirements, we will design a model which can provide asymmetrical parallel channels between the sender and the receiver.

This multiple address parallel transmission architecture, which is called Multi-Channel, is designed to work on both symmetrical and asymmetrical packet switching network. In the switching network, storage devices are connected with links and switches, where links are assumed to have bound delay and switches are assumed to be "non-blocking". With these topologies, a connection in such a network can be modeled as traversing a number of queuing servers, while each server modeling the output link of a switch. Each communication component of the network has a bounded delay.

Between a node and a switch, multiple links can be used and these links can have different bandwidth. A general structure is shown in Figure 1.2. Each storage device (one node) can have any number of network interface cards (NIC). Every network interface can access any other network interface. To build a connection between two end-to-end nodes, the number of the network interfaces of two nodes need not to be equal. For the implementation, two most popular protocols, Ethernet and IP protocol are chosen as the network channels sub layer. The NIC interfaces can be Fast Ethernet or Gigabit Ethernet.

Unlike other NIC aggregation solutions, this design does not demand for special hardware in storage devices or switches. Each NIC uses their original address naming system, i.e., each NIC card is bonded with unique MAC address or IP address. The parallel communication channels between two nodes are built up by scheduling network packets based on these addresses. Many other parallel transmission solutions assign the same address to multiple NIC interfaces, which cannot build an end-to-end parallel channel. This requires that both nodes and switches install special load balancing and address translating service, which is complicated to setup. Normally, the switch components must support VLAN function to support such parallel transmission. In our architecture, only the sender and receiver nodes schedule the data flows, the required network in between is a normal network.

So far we have a multiple paths architecture built by normal packet switching network. Next, multiple communication channels are built on these paths. Some designs use part of the communication channels as backup channels [18], which preserve spare resource in case of failure. This is actually a resource waste. All the available channels should be utilized on communication simultaneously. Additionally, some design keep one data flow on one channel [19] to avoid packet out-of-order, this

also does not fully utilize the resource. Because information is required to maintain a data flow on a particular channel, it may cost more effort than out-of-order handling. In our design, one data flow or multiple data flows are distributed on all channels. By employing multiple channels, not only load balancing and fault tolerance are provided, the security feature is also enhanced in some distance because of the information dispersal [20].

With the improvement of the computation power, traffic load scheduling can be implemented based on software [21]. The whole multiple address parallel transmission protocol can be implemented as a software layer, where the sender can do all the scheduling. Multiple data flows are dispersed into packets at sender, and then the traffic load is sent to channels evenly by schedulers.

#### 2.2 Multiple Address Parallel Transmission

The communication model of Multi-Channel is different from a normal parallel transmission model. In SAN, network storage devices are expected to have variable capacity and bandwidth. At present, only the storage capacity has good scalability, while the bandwidth cannot be scaled easily. One purpose of Multi-Channel model is to efficiently increase the end-to-end bandwidth scalability of the network storage devices. To apply the algorithms more precisely to a real SAN environment, channel numbers are not necessarily symmetrical at sender and receiver nodes. For instance, if the storage server needs more bandwidth to serve multiple client stations, the server will be installed more NIC interfaces.

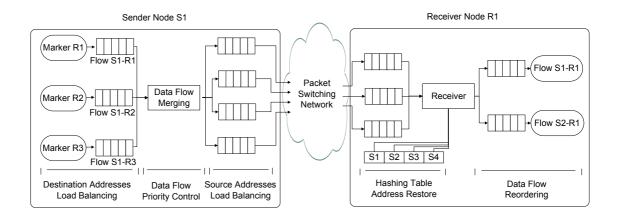

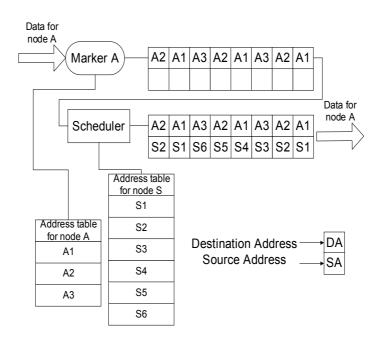

The theoretical model of a connection between a sender and a receiver is composed of five sequential components as shown in Figure 2.1: (1) the first stage load balancing scheduler, (2) data flow priority controller, (3) the second stage load balancing scheduler, (4) hashing table for address restoration and (5) data flow reorder.

With this architecture, the bandwidth of each network storage device can be easily increased or decreased independently. Such model can work in a normal packet switching network without the use of special hardware.

In the sender node, two schedulers are used to balance the traffic load on sender and receiver respectively. To distinguish the two schedulers, we call the first stage scheduler "Marker". Each data flow has a Marker, however all data flows share one global second stage scheduler. Between first and second scheduler, a service algorithm is used to grant different priorities for each data flow.

In the receiver node, data flows are restored and reordered when packets arrive at different network interface. A hashing selection and an out-of-order estimation algorithm are used to maintain the data flow.

Figure 2.1 Model for Multiple Address Parallel Transmission Architecture

The following parts will demonstrate each component in detail. First, two cases are studied to reveal the distribution of traffic flows in the network.

#### 2.2.1 Case One: Single Data Flow on Asymmetrical Networks

To demonstrate how the architecture can balance the traffic load of asymmetrical network, first a case of single data flow between sender node S and

receiver node A is considered. To simplify the illustration, both schedulers use Weighted Round Robin load balancing algorithm, other load balancing algorithms will be discussed later. Since there is only one data flow, no data flow priority selection algorithm is needed between two stage schedulers. In Figure 2.2, the data flow on sender node S is shown to explain how the packets are scheduled.

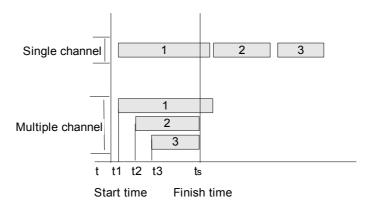

Figure 2.2 Single Data Flow Scheduling on Two Stage Address Table Scheduler

In this case, the sender node S has six network addresses (or network interfaces) from S1 to S6, and the receiver node A has three network addresses A1, A2 and A3. In the connection setup process, two nodes exchange their address table, so each node holds the address table of both sides. For data flow from node S to node A, the destination address of out going packets are first marked. Here Weighted Round Robin algorithm is used on destination address table of node A. This marking insures that the arrival traffic load at A will be balanced. Each network interface at A will receive 1/3 of the data flow. The middle switches will route packets evenly to three network interfaces on node A, and the traffic load is automatically balanced by ordinary switches. Then the second stage scheduler evenly distributes data flow to the

network interface on S. The source address of the packets is also marked with Weighted Round Robin algorithm, and the data flow will be sent out from six NIC interfaces on sender S evenly.

On the receiver node A, the in-coming data flow will be evenly received. No matter what routing algorithms are used in the packet switching networks, each NIC interface will receive same number of packets, because the destination address of the packets is predetermined by the sender node S. The major jobs on the receiver are to convert these packets into original data flow. Furthermore, since the packets go through different network path, the out-of-order is unavoidable. The receiver must reorder the packets to restore the data flow.

From the description above we show that the sender node S controls wholly the traffic load. The receiver only needs to restore the data flow. At both sender and receiver sides, the traffic load is evenly going out and going in no matter what middle network is used. Additionally, the load is balanced when the NIC interfaces on sender and receiver are asymmetrical.

There is one issue required to be mentioned that even we settle the load balancing problem, the data transmission rate is still determined by certain conditions. Because the bandwidth of the sender and receiver are different; the maximum transmission performance between two nodes is determined by the lower bandwidth side (suppose the packet switching networks provide enough bandwidth). This transmission rate is also constrained by the capability of the packet switching network.

#### 2.2.2 Case Two: Multiple Data Flows on Asymmetrical Network

In this section a case of multiple data flows and multiple nodes is considered. Figure 2.3 shows a data flow structure on the sender node S. Three receiver nodes A, B, C build connections with node S. Where node A has 3 addresses A1, A2 and A3,

node B has 2 addresses B1 and B2, node C has 1 address C1 and sender node S has 6 addresses S1 to S6. All the schedulers use Weighted Round Robin algorithm.

In Section 2.2.1, the destination address of a data flow must be marked by scheduler to make sure the load is balanced at the receiver node. In the case of multiple data flows, each data flow has its own first stage scheduler. This scheduler will mark the destination addresses of each data flow. Here Weighted Round Robin algorithm is employed on A, B, C's address table. This insures that three data flows will evenly arrive at NIC interfaces at receiver nodes A, B, C respectively. For the multiple data flows to the same receiver node, each data flow is also assigned a first stage marker. After this first stage scheduling, we can confirm that no matter how many data flows and receiver node exist, the NIC interfaces on the same receiver will receive balanced traffic load.

Figure 2.3 Load Balancing of Multiple Data Flows and Multiple Nodes

From first stage to second stage, three data flows will be merged into one queue and scheduled by the second stage scheduler. The mergence will provide a virtual data channel for all data flows. This design not only balances the load with simple algorithm, but also makes data flows independent of physical NIC interfaces. Thus, the data flows can migrate among the NIC interfaces freely. Whenever there is an error on

NIC interfaces, the scheduler can reschedule the data flows without affecting address marking and load balancing. Different merging algorithms can be used to provide service priorities for data flows of multiple nodes. In this case, three data flows are supposed to have the same priority and simply use a Round Robin algorithm.

After the data flows been merged into one queue, the second global scheduler uses Weighted Round Robin algorithm to distribute packets to the NIC interfaces on sender node S. Thus the packets from different data flows are evenly sent out to the network. The fact that all data flows share one global second stage scheduler insures that the out going traffic load is finely balanced.

On the receiver nodes A, B and C, the traffic load evenly arrives at specified NIC interfaces. The receiver only needs to distinguish different data flows and reorder them

So far two cases are discussed to make clear that the traffic can be balanced at both sender and receiver side. With multiple data flows and multiple nodes with multiple NIC interfaces, the load is balanced on an end-to-end asymmetrical architecture. Furthermore, the design is very flexible that NIC interfaces on both sender and receiver can be added and removed without affecting other nodes. Multiple nodes with different bandwidth (or network interface numbers) can work together and the load balancing is maintained without any hardware support in either device or packet switching networks. In next section, we will discuss scheduling algorithms used on sender and receiver in detail.

#### 2.3 Load Balancing Algorithms for Two Stage Schedulers

In previous section it has been shown that load balancing is controlled by two kinds of schedulers on the sender node. Each data flow has one first stage scheduler, and there is only one global second stage scheduler for all data flows. The first stage

scheduler (the marker) is used to balance the traffic load at multiple network interfaces of receiver node. The second stage scheduler is used to balance the out going traffic at the sender node. In the two demonstration cases, all schedulers use Weighted Round Robin algorithm to balance the load. Here a serial load balancing algorithms will be studied systematically.

Load balancing algorithm is used to balance traffic load to multiple channels in packet switching networks. While fair queuing algorithms are designed to fairly serve the packets form multiple queues. The load balancing algorithm could be acquired from a reverse of the fair queuing algorithm. A theorem of transformation from fair queuing to load balancing algorithm [22] has been proven. Consider a backlogged execution of a fair queuing algorithm. First a function f(s) is applied to select a queue. The packet p at the head of the selected queue is transmitted and then the state is updated using a function g(s, p). We can obtain a fair load sharing algorithm by using the same function f to pick a channel to transmit the next packet on, and update the state using the same function g.

Here, we intend to distribute variable sized packets to multiple channels. Each channel is backlogged and no channel is used as backup channel. Four reverse fair queuing algorithms are discussed and compared, namely Reverse Generalized Processor Sharing (RGPS), Reverse Weighted Round Robin (RWRR), Reverse Weighted Fair Queuing (RWFQ) and Reverse Deficit Round Robin (RDRR). The purpose is to determine the most suitable load balancing algorithms for the schedulers. The last three RWRR, RDRR and RWFQ can be implemented on two stage schedulers for source and destination load balancing. All these algorithms have small computation overhead.

#### 2.3.1 Reverse Generalized Processor Sharing (RGPS)

The Generalized Processor Sharing (GPS) algorithm is used to provide a fair scheduling for best-effort connections. The GPS visits each non-empty queue in turn and serves infinitesimally small amount from each. Connections can have service weights and will receive service in proportion to these weights when they have data in the queue. If there is no data at a queue, scheduler skips to the next non-empty queue. The description of GPS is as such:

The GPS is work conserving and operates at a fixed rate r. If the N connections being served by GPS server have positive real weights  $\phi(1),\phi(2)$ , ...,  $\phi(N)$ , then the server serves  $S(i,\tau,t)$  amount of data from the ith connection in the interval  $[\tau,t]$ , so that for any connection i backlogged (A connection is backlogged whenever it has data in its queue.) in  $[\tau,t]$ , and for any other connection j, we have  $\frac{S(i,\tau,t)}{S(j,\tau,t)} \geq \frac{\phi(i)}{\phi(j)}$ . Summing all connection j,  $S(i,\tau,t)\sum_j \phi_j \geq (t-\tau)r\phi_i$ , and connection i is guaranteed a rate of  $g_i = \frac{\phi_i}{\sum_j \phi_j} r$ . GPS ensures that backlogged connections share the remaining

bandwidth in proportion to their weights. GPS has many advantages. A connection can be guaranteed a throughput independent of the demands of other connections. Furthermore, by varying the  $\phi_i$ , we have the flexibility of treating each connection in different manners.

The Reverse Generalized Processor Sharing (RGPS) algorithm is a reversal algorithm of GPS in a special condition. The RGPS is used to schedule one queue to multiple connections with service weights. The RGPS send infinitesimally small amount to each connection. In a finite time interval it will visit every connection once. In RGPS, every connection is backlogged, because we intend to use all connection

resources. For the same GPS definition, we have  $\frac{S(i,\tau,t)}{S(j,\tau,t)} = \frac{\phi(i)}{\phi(j)}$ , which means all connections strictly share the service in proportion to their weights. Each connection receives rate  $g_i = \frac{\phi_i}{\sum_i \phi_j} r$  data flow.

RGPS is a perfect load balancing algorithm in theory, but it is unimplementable when the packets, not infinitesimal are scheduled. In the packet switching network, schedulers must approximate RGPS by scheduling packets with variable sizes. So, the concept of RGPS can help to evaluate other algorithms. Next, three simple algorithms are discussed, which are implementable and approximate to RGPS.

#### 2.3.2 Reverse Weighted Round Robin (RWRR)

The Weighted Round Robin (WRR) algorithm [23, 24, 25, 26, 27] is widely used to serve a packet instead of infinitesimal from each backlogged queue in turn. The packet sizes should be equivalent, otherwise the schedule algorithm is unfair. To demonstrate this FQ algorithm, first, consider fixed packet size and different weights. The computation is simple that the scheduler serves more than one packet per round after normalizing weights to integers. Secondly, consider variable sized packets and different weight. The scheduler should normalize weights by mean packet size to acquire fair queuing. Since the mean packet size is usually unavailable, the WRR for variable packet size is hard to implement. Many modifications [28, 29, 30] are proposed to improve WRR algorithm.

The WRR works well for a network with fixed packet size, because the work complexity of WRR is o(1) [31]. It is widely used in schedulers in ATM [32, 33, 34, 35] and IP switches and routers[36].

The Reverse Weighted Round Robin (RWRR) algorithm is the time reversal of the WRR on the condition that each connection of the WRR is backlogged. The RWRR sends packets to connections in turn. For fixed packet size and different weights, the number of served packets in one round is computed by normalized integer weights. When the RWRR is implemented on variable packet size, the fairness of RWRR is defined by FairIndex = (Max/Min), where Max is the maximum packet size and Min is the minimum packet size.

The RWRR algorithm is a practical solution because of its less computation overhead. The traffic load is balanced when the packet size is fixed. In SAN, when mass data flows are transmitted, most of the data packet will use fixed maximum protocol data unit (MPDU) for efficiency. The proportion of the similar sized packets is high. Thus we can use RWRR algorithm to approximate a perfect load balancing algorithm. In Chapter 4 we will show that RWRR works well for remote disk reading in a normal packet switching environment.

#### 2.3.3 Reverse Weighted Fair Queuing (RWFQ)

The Weighted Fair Queuing (WFQ) algorithm, also known as Packet-by-packet Generalized Processor Sharing (PGPS) [37, 38, 39], is designed for variable sized packets and weights. The WFQ algorithm serves packets in order of their finish number (or finish time), where the finish number of each packet is computed by a GPS algorithm. The finish number is given by

$$F(i,k,t) = \max\{F(i,k-1,t), R(t)\} + T(i,k,t), \qquad (2.1)$$

where,

$$T(i,k,t) = L(i,k,t)/r$$

, (2.2)

where R(t) is the round number computed by GPS algorithm, T(i,k,t) is the service time of k th packet on connection i, L(i,k,t) is the length of k th packet that arrives on connection i at time t, and r is the link service rate.

The fairness of WFQ algorithm is *FairIndex* = 1, which means the traffic load is perfectly balanced. Based on WFQ, research on implementation and performance [40, 41, 42, 43] has been conducted widely. Many network applications currently use modified WFQ algorithms in switches and routers [44, 45, 46, 47], voice on IP [48, 49], and wireless LAN [50].

However, since the work complexity of WFQ is  $o(\log n)$ , research efforts are conducted to simplify WFQ [51, 52] and improve its adaptability [53]. The best solution not only balances the load, but also keeps the work complexity at o(1). We will discuss a solution of work complexity o(1) in the next section.

The Reverse Weighted Fair Queuing (RWFQ) algorithm is a reverse of WFQ algorithm without empty channel. The finish number is assigned to each channel and computed by RGPS algorithm. The channel with the minimum finish number is selected to send the next packet in queue. The finish number is given by

$$F(i,k,t) = F(i,k-1,t) + T(i,k,t),$$

(2.3)

with

$$T(i,k,t) = L(i,k,t)/r$$

, (2.4)

where T(i,k,t) is the service time of k-th packet on channel i. L(i,k,t) is the length of k th packet that arrives on connection i at time t, r is the link service rate. Unlike WFQ, since no channel is empty in the procedure of data transmission, round number are not needed when computing the F(i,k,t). The weighted equation of RWFQ is

$$F(i,k,t) = F(i,k-1,t) + T(i,k,t) \div \phi(i)$$

, (2.5)

where  $\phi(i)$  is the weight of the connection *i*.

The RWFQ algorithm is better than RWRR when packet sizes are not fixed. However, the computation overhead of RWFQ is greater than the RWRR algorithm. For each packet, all the channels need to be checked in turn and the growing finish number F(i,k,t) also needs iterated deletion. If the channel numbers are huge, the computation overhead will degrade the performance. So, more efficient algorithms are required to handle the work complexity problem.

#### 2.3.4 Reverse Deficit Round Robin (RDRR)

The Deficit Round Robin (DRR) [54] algorithm is a modification of Weighted Round Robin. To serve multiple queues, the scheduler assigns each queue a service quantum. If a queue was not able to send a packet in the previous schedule round because its packet size was too large, the remainder from the previous quantum is added to the quantum for the next round. The weight of each connection can be converted to quantum.

DDR is a low complexity version of Fair Queueing. It can be implemented at work complexity of o(1) and has FairIndex = 1. Several modified DRR [55, 56, 57, 58] have been proposed to achieve both simplicity and fairness. They are widely used in Internet software and hardware applications. For instance, DRR is used to provide bandwidth guarantee to competing TCP flows [59]. When combined with Random Early Detection [60], it can improve the fairness for different bandwidth capacity. In [61], DRR is used to schedule the traffic by links not by data flows, which can decrease the schedule cost. For the hardware applications, many switches and routers also use DRR algorithms [62, 63, 64].

We have more interest on a modified DRR called Surplus Round Robin (SRR) [65], which provide link striping for variable sized packets. The Deficit Counter (DC) of SRR is initialized to 0, and incremented by the quantum for the served queue. As

long as the DC is positive, packets are sent form that queue, and the DC is decremented by the size of the transmitted packet. If the DC is non-positive, the current queue will be skipped.

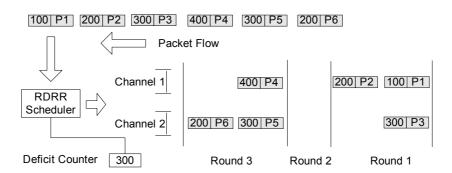

The Reverse Deficit Round Robin (RDRR) algorithm is a reverse DRR or SRR algorithm without empty queue. A detailed proof of transforming from FQ to load balancing algorithm can be found in [65]. The RDRR also use a Deficit Counter (DC) and quantum of service. Quantum is assigned by measuring the weight of the channels. The DC is initialized as 0 and served in turn. Each time a channel is selected, the DC is incremented by the quantum for that channel. Packets are sent to the channel and its DC is decremented by the packet size, till the DC becomes non-positive, then the next channel is selected.

Figure 2.4 Reverse Deficit Round Robin Scheduler

In Figure 2.4, a RDRR scheduler with two channels is demonstrated. Packets of different sizes are scheduled by checking the Deficit Counter of each channel. If the packet size is less than DC, it will be sent to this channel and the DC is decreased by the packet size. If the packet size is bigger than DC, the scheduler will check next channel. If the packet size is bigger than all channel's DC, the scheduler will wait next round until the DCs are incremented. Suppose that the maximum quantum among all the channels is Quantum and the maximum packet size is Max. After K round, the difference between the bytes that should have been sent to channel i,

*i.e.*,  $Max + 2 \times Quantum$ , and the bytes actually sent to channel i is bounded by  $K \times Quantum_i$ .

The computation overhead of the RDRR is slightly greater than the RWRR because of the quantum service. The actual value of the quantum should be cautiously selected. If the quantum is much less than the packet size, the scheduler will wait many rounds to accumulate the quantum to send out one packet. If the quantum is much greater than packet size, many packets will be sent to one channel in one round, which may increase out-of-order rate.

The RWRR algorithm is simple and efficient for scheduling large number of channels with fixed packet size. The RWFQ algorithm conducts a perfect load balancing and data flow ordering, it can be used when storage system has excellent computation power. The RDRR algorithm is a better solution when many channels with various packet sizes are used and computation resource is constrained. For different network environment and data transmission models, proper algorithm can be selected for specific requirements.

#### 2.4 Data Flow Priority

In this section we will explain why one data flow (or one conversation) is scheduled on all the addresses and how to assign priorities to multiple data flows on one device. Between first and second scheduler, we build one virtual data channel between nodes instead of multiple smaller data channels and use service disciplines algorithm to provide different priorities and rate-control for each data flow.

#### 2.4.1 One Virtual Channel vs. Multiple Sub Channels

We use a structure of two stage schedulers to build one virtual data channel between nodes in stead of multiple smaller data channels, which means that each data flow is scheduled on all workable sub channels for the efficiency and fault tolerance. Other protocols, for instance Link Aggregation Control Protocol (LACP), use a different method. It transfers one conversation on one physical network interface to avoid packets disorder. That will increase the delay, and can not handle load balancing problem for asymmetrical architecture.

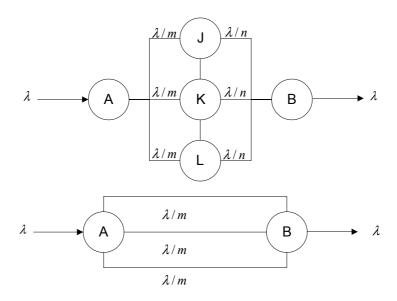

Figure 2.5 Single Virtual Channel and Multiple Channels

To compare the performance when multiple physical channels are used as one big data channel or multiple smaller data channels, consider a communication link serving m independent Poisson traffic streams with overall rate  $\lambda$  [66]. Suppose that the link is divided into m separate channels with one channel assigned to each traffic stream. However, if a traffic stream has no packet awaiting transmission, its corresponding channel is used to transmit a packet of another traffic stream. The transmission times of packet on each of the channels are exponentially distributed with mean  $1/\mu$ . The system can be modeled by the same Markov chain as the M/M/m queue. In the case of multiple sub channels, the average delay per packet is given by the M/M/m average delay expression

$$T = \frac{1}{\mu} + \frac{P_Q}{m\mu - \lambda} \,. \tag{2.6}$$

While in the case of one virtual channel, the model is an M/M/1 system with the same arrival rate  $\lambda$  and service rate  $m\mu$ . The average delay per packet is

$$\hat{T} = \frac{1}{m\mu} + \frac{\hat{P}_Q}{m\mu - \lambda} , \qquad (2.7)$$

where  $P_{\mathcal{Q}}$  and  $\hat{P}_{\mathcal{Q}}$  denote the queuing probability in each case  $(P_{\mathcal{Q}} = \frac{p0(m\rho)^m}{m!(1-\rho)})$ ,  $\lambda$  denotes the arrival rate (the inverse of average inter-arrival time),  $\mu$  denotes the service rate (the inverse of average service time). When  $\rho <<1$  (lightly loaded system) we have  $P_{\mathcal{Q}} \cong 0$ ,  $\hat{P}_{\mathcal{Q}} \cong 0$  and  $\frac{T}{\hat{T}} \cong m$ . When  $\rho$  is only slightly less than 1, we have  $P_{\mathcal{Q}} \cong 1$ ,  $\hat{P}_{\mathcal{Q}} \cong 1$ ,  $1/\mu <<1/(m\mu-\lambda)$  and  $1/\hat{T} \cong 1$ .

Therefore, for a light load, multiple sub channels produce a delay almost *m* times greater than the delay of one virtual channel. For a heavy load, the ratio of the two delays is close to 1. On average, keeping multiple conversations on one virtual channel is more efficient for packet transmission. This gives evidence that when implementing multiple address parallel transmission protocol, one conversation should view multiple network interfaces as one virtual channel. This also implies that packets of the conversation can migrate among the network interface without applications' awareness.

In our design, data flows are not constrained to specific channel. Packets of the data flows can be marked with any workable source and destination address pairs. Scheduled by the two stage scheduler, one conversation between two nodes takes multiple paths as one virtual channel.

## 2.4.2 Multiple Data Flows' Priorities with Service Discipline

The two stage schedulers can handle the end-to-end load balancing with multiple data flows. However the end-to-end performance guarantee is still need to considered, which requires various QoS service discipline algorithms.

One of the targets is to categorize the data flows. Since multiple data flows can be transmitted simultaneously in the architecture, service disciplines must be provided to determine the priorities of the data flows. For instance, the real-time data flows should have higher priority than non-real-time data flow.

The other target is to control the rate of each data flow to avoid the congestion. Since the best-effort data flow might cause unnecessary congestion and retransmission in the asymmetrical parallel architecture, a rate-controlled data flow can have better performance. Traditional congestion control methods [67, 68, 69] did not consider about the parallel architecture, thus an end-to-end congestion control method for parallel path is urgently needed.

In current packet switching network, the service disciplines which can provide per-connection end-to-end performance guarantee are still unavailable in most of the routers and switches. So the data flow rate and congestion can not be fully controlled before all the routers and switches along the path support QoS services. However, we can simply utilize service discipline algorithms on the source node to achieve the priority target. The target of rate control and congestion avoidance can be fulfilled when the whole packet switching network can support QoS service.

In recent years, QoS service disciplines have been widely studied. Two categories of service disciplines, the work-conserving disciplines and the non-work-conserving disciplines, can be found in [70, 71]. With the work-conserving disciplines such as, virtual clock, delay-EDD, WFQ, WF<sup>2</sup>Q, and SCFQ, a sorted priority queue

mechanism can be used to provide priority service for the data flows. With non-work-conserving disciplines such as, jitter-EDD, Stop-and-Go, HRR and RCSP, a rate-controlled service can be employed to reduce the possibility of the congestion.

The best place for in this service discipline is between two stage schedulers. The choice of this priority algorithm highly depends on the applications. In our implementation, all data flows are assigned the same priority; and the transmission rate is controlled by the minimum bandwidth side of an asymmetrical parallel architecture. Other algorithms can also be adopted to meet the QoS requirement of different applications.

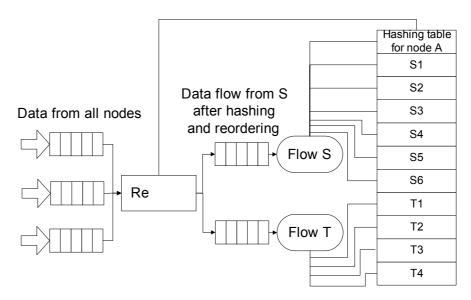

# 2.5 Data Flow Restore -- Hashing Address Table and Reordering

In the receiver node, data flows are restored and reordered when packets arrive at different network interfaces. Here, a chaining hashing algorithm is used to search senders' address table and an out-of-order estimation algorithm is used to setup retransmission threshold and allocate reordering buffer. Since the mechanism of the out-of-order differs from a normal network, several closely related parameters are studied in detail.

### 2.5.1 Hash Chaining Structure for Address Restoring

In the parallel transmission architecture, the packets of a data flow arrive at different network interfaces. The receiver must reorganize these packets into their original data flows quickly. Indexed by their source addresses, packets are differentiated by using a hash chaining searching on senders' addresses table.

The search time of normal hashing table is o(1), but this may waste too much memory resource when the address range is large. Here a hash chaining structure is used to balance the memory space and searching time. The searching time of a

chaining with separate lists is o(n/l), where n is the number of addresses and l is the number of lists. The addresses with the same hash key are organized in one list to avoid collision. By adjusting the list number l, the search time can be controlled in a definite range.

Figure 2.6 Hashing Algorithm for Data Flow Restoring

After the hash chaining searching, data flows from the same sender node are differentiated. Since every packet contains the unique ID of data flow on the same sender, the receiver will further classify different data flow by data flow ID. This procedure is quite simple and straightforward, thus, the major burden is the address table searching. To restore the data flow by searching sender's address table, the hash chaining address table structure is an efficient algorithm.

## 2.5.2 Out-of-order Analysis

In this section, we will discuss the reason of the out-of-order in parallel architecture. The out-of-order problem is quite prevalent in parallel transmission structure, the most reliable method is to mark sequence number on each packet. In our design, each packet in data flow is numbered and reordered with this sequence number.

The receiver reorders data flows by using a TCP-like algorithm. However, different parameters are used for the retransmission algorithm when out-of-order occurs. These parameters will be discussed in next section.

In normal network, out-of-order rate is not significant and hard to predict. The out-of-order is mainly caused by route changing. It rarely has a big impact on performance of a TCP similar protocol, because the scale of the out-of-order delivery is just a few packets.

In parallel transmission architecture, out-of-order is hard to avoid but can be predicted. In a theoretical parallel path transmission model, different channel bandwidths and packet sizes might cause out-of-order delivery. In a practical environment, the schedule delay and other system structure also influence the probability of out-of-order delivery.

First suppose that two nodes communicate through three sub channels with the same bandwidth (Figure 2.7). Three packets are sent to each channel at the time sequences t1, t2, t3. Since the sizes of the three packets are different, the packet 2 and 3 will arrive before the packet 1 (the arrival time of the last bit of a packet determines the arrival time of this whole packet). This will cause the receiver node to reorder the packets. While in a single channel case, the second packet will not be sent until the last bit of the first packet are sent out.

Figure 2.7 Out-of-order Caused by Different Packet Sizes

Different channel bandwidth can also cause out-of-order delivery with the similar mechanism. Consider packets with same size are sent into channels with different bandwidth. The arrival time sequence of each packet will not follow the sending sequence. In a channel with larger bandwidth packets can arrive early. To decrease the out-of-order delivery, the packet sizes should be constrained to fixed value and channels should be allocated with the same bandwidth.

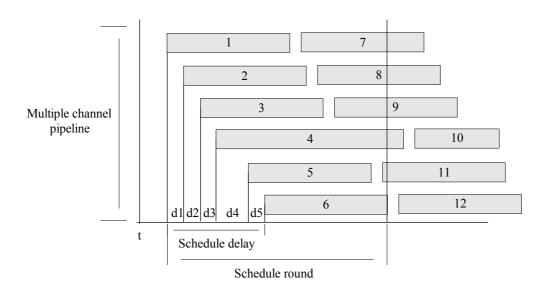

It is worth mentioning that other system parameters may also cause out-of-order. Small schedule delay (Figure 2.8) can cause out-of-order delivery even when packet size and channel bandwidth are fixed. The schedule delay is the schedule time interval between two packets in the same schedule round. Since packets are transmitted at different network paths, if the schedule delay between two packets is small, the possibility that these two packets reach the receiver at same time is high, which denotes a high out-of-order rate.

Figure 2.8 Schedule Delay in Each Schedule Round

The schedule delay can be affected by channel numbers, packet sizes. With more channels added, more packets need to be scheduled in one round. Thus the schedule delay extends (Figure 2.8) and decreases the possibility of the out-of-order delivery. Similar result can also be observed when the packet size is increased, schedule delay also increases. With larger packet size, the out-of-order rate drops. Different system workload may also change the schedule delay. Thus, a stable system environment is required to test the out-of-order delivery caused by schedule delay.

The out-of-order delivery can be a function of the schedule delay, the variance of packet size and the variance of channel bandwidth. Define the out-of-order rate  $\gamma_o$  as the frequency that the system observes out-of-order delivery. We can have:

$$\gamma_0 = f[Var(packet\_size), Var(bandwidth), 1/T(schedule\_delay)], \qquad \qquad \textbf{(2.8)}$$

$$T(schedule\_delay) = f[channel\_No., packet\_size],$$

(2.9)

The out-of-order rate  $\gamma_o$  will increase when the variance of packet size or channel bandwidth increases. The  $\gamma_o$  decreases when schedule delay increases, where the schedule delay can be increased by channel numbers and packet size.

Nevertheless, network storage device may use a multiple processor operating system. In such a system, different packet processing times on multiple processors can also cause out-of-order delivery. These problems should also be considered in the design when such operating systems are used.

The out-of-order delivery in parallel transmission architecture may affect many other network characteristics, such as, retransmission, window size, drop rate estimation, and buffer size. It also has an impact on the queuing delay analysis, since most of the queuing models are first-in-first-out (FIFO).

#### 2.5.3 Retransmission Threshold and Reorder Buffer

In this section, we will deduce the retransmission threshold and reorder buffer by estimating out-of-order rate in parallel transmission architecture. The transmission performance and out-of-order distance are also discussed.

The relation between out-of-order and the retransmission is a key architectural consideration in protocol design [72]. Previous out-of-order and retransmission research focuses on Internet and TCP performance [73, 74, 75]. In such network environment, the scale of out-of-order is a few packets and the packet drop rate is relatively large (mainly caused by network congestion or data error). When there is either out-of-order or packet drop in a packet flow, the receiver will observe sequence broken and this may cause a retransmission. Thus, it is important for a fast retransmit mechanism to disambiguate packet drop from out-of-order delivery. The TCP uses a duplicate ACK threshold to infer that a packet requires retransmission. This threshold is selected by estimating how long a receiver needs to wait to disambiguate out-of-order from packet drop [76]. Normally the threshold is been given a small value to improve the fast retransmit mechanism. This suggests that a short wait time is preferred, since most of the sequence broken is caused by packet drop.

In SAN with parallel transmission structure, the selection of duplicate ACK threshold depends more on out-of-order rate estimation to avoid unnecessary retransmission. Since SAN is more stable than Internet, the packet drop is relatively rare, while out-of-order delivery is more prevalent [77].

The out-of-order delivery can be estimated and used to select a proper retransmitting waiting time and reorder buffer threshold. The waiting time has an upper bound  $\tau$ , where  $\tau$  can be deduced from the maximum Round Trip Time (RTT) of the data packet. Since the bandwidth and packet size can be variable, the maximum

RTT is the time that a maximum sized packet used to pass through the minimum bandwidth channel. The buffer bound for reordering is the integration of maximum RTT multiplying the individual channel bandwidth.

Consider that the receiver observes a missing packet at sequence number N by receiving packet N-1 and N+ 1. Suppose that the missing packet is caused by out-oforder and all sub channels are using a FIFO queue, the N-th packet must have been sent out but still not arrive. The worst case is that the N-th packet has maximum size minimum bandwidth and is passing through the channel. So we have  $\tau = Max(RTT)/2$ , if the waiting time exceeds  $\tau$ , the possibility of packet drop increases. Thus the retransmission threshold must be larger than au . The minimum buffer used to reorder one out-of-order packet can also be deduced by

$$W = \sum_{i=1}^{N} \tau * \boldsymbol{\sigma}_{i} = \sum_{i=1}^{N} Max(RTT) * \boldsymbol{\sigma}_{i} / 2,$$

(2.10)

where W is the buffer size, N is the numbers of the channel,  $\varpi_i$  is bandwidth of each channel. This equation shows that in a worst case out-of-order, the data waiting in a reordering buffer equals all the received traffic within this waiting period.

Let out-of-order distance  $D_o$  be the number of packets that have arrived between the period of time in which that the system observes a missing packet and this missing packet arrives. Since each packet will arrive within time  $\tau$ , the  $D_o$  or the number of packets arrived before the out-of-order one can be estimated by:

$$D_o = \frac{W}{Average\_Pakcet\_Size} = \frac{\sum_{i=1}^{M} Max(RTT) * w_i / 2}{Average\_Pakcet\_Size}$$

(2.11)

This shows that the out-of-order distance can be controlled in finite range.

Theoretically, the small out-of-order distance will not affect the transmission performance, it only increases the delay bound by waiting and reordering packets. The

estimation of the retransmission waiting time and reordering buffer produces a slightly loose bound for the queuing delay model while the transmission performance is unchanged.

The estimations are based on maximum Round Trip Time, which can be easily acquired and computed. Estimation algorithms based on out-of-order rate requires more knowledge about network topology and scheduling algorithm. For different applications, the out-of-order rate might have different values. Our estimation also provides a general delay bound and all the other parameters can be efficiently computed.

#### 2.6 Fault Detection and Cost Estimation

The multiple addresses parallel transmission uses redundant channels to provide built-in fault tolerance feature. Whenever a fault channel is detected, data flows will be scheduled to other available channels.

To achieve fault tolerance, the protocol must be able to detect the error. It must recover from that error and eventually reaches a legal state and resumes its normal execution [78,79]. Several detection algorithms can be found in [80]. Most fault tolerance algorithms use spare resources to provide fault tolerance feature [81, 82, 83], which may be resource waste [84]. In our architecture, all the available resources are utilized to improve performance and achieve fault tolerance at the same time.

#### 2.6.1 Three Fault Detection algorithms

Since NIC failure, cable failure and switch failure can all contribute to channel failure, we propose three fault detection methods to diagnose different levels of failures. The three fault detection algorithms can be hardware detection, software local

loop back and remote acknowledge detection. All these algorithms can be implemented jointly or independently.

The hardware fault detection depends on the link failure register of the network interface cards. Currently most of the network interface cards support a link failure register. By checking the register periodically, the status of the first hop link can be collected. The computation overhead of checking a register is very small and the detection frequency could be a few seconds. The limitation of the hardware fault detection is that node can only check the first hop link in the packet-switching network.

The second algorithm is local loop back fault detection. We can build loop back channels by using the multiple addresses on the same node (the channel number should be greater than or equal to 2). The merit of the local loop back detection is that if the hardware detection is unavailable, a node can send detection packets to itself to detect the status of the first hop link and the nearest switch. The draw back of this algorithm is that the working addresses must be greater than or equal to 2. The procedure of the loop back detection can be described by:

- (A.) Select first network interface card (NIC) to be sender, send local detect packet to other NICs on the same node

- (B.) If at least one of these NICs received a local detect packet, it is suggests that the sender NIC and the nearest switch is working well. Those who have not received local detect packet can be regarded is faulty. The fault might be on the cable or the card. The detection process can be finished.

- (C.) If none of the other NICs received the local detect packet, we mark the sender NIC with "unknown", because we cannot assure if the sender NIC has fault. So we choose next NIC as sender, send local detect packet to remaining NICs and continue the B, C process.

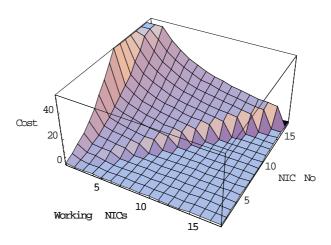

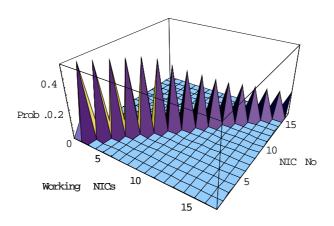

(D.) If no channel can be built on the local node, there are only two possible results. Either only one NIC is working or no NIC is working. To identify the only one working port (if existed), we must use remote detection algorithm.