# ADVANCED GATE STACK FOR SUB - 0.1 μm CMOS TECHNOLOGY

**YU HONGYU**

(M. ASc. University of Toronto; B. Eng. TsingHua University)

# A THESIS SUBMITTED

# FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

# **DEPARTMENT OF ELECTRICAL AND COMPUTER**

# ENGINEERING

# NATIONAL UNIVERSITY OF SINGAPORE

2004

# ACKNOWLEGEMENTS

I would like to take this chance to express my sincere thanks to my thesis advisors, Prof. Li Ming-Fu and Prof. Kwong Dim-Lee, for their instruction, guidance, wisdom, and kindness in teaching and encouraging me, not only professionally, but also personally, during my graduate study at NUS. Especially I greatly appreciate Prof. Li's help, who provides me the opportunity to join his group. Without the theoretical foresight, experimental intuition, and firm expertise in the field of semiconductor devices and physics from both Prof. Li and Prof. Kwong, all the projects I have undertaken can not be conducted smoothly. Throughout my life, I will definitely benefit from the experience and knowledge I have gained from them.

I would also like to greatly acknowledge Dr. Hou YongTian, Dr. Kang Jin-Feng, Dr. Yeo Yee-Chia, Dr. Chen Gang, Dr. Jin Ying, and Dr. Lee SJ for the many useful technical discussions. Many thanks to my colleagues in Prof. Li's group, including Wang XinPeng, Ren Chi, Tony Low, Shen Chen, Dr. Zhu ShiYang, and Dr. Ding SJ. I wish to thank Mr. Yong YF, Mr. Tang Patrick, Mrs. Ho CM, Dr. Bera KL for their technical support. I would also like to extend my appreciation to all other SNDL teaching staff, fellow graduate students, and technical staff.

My deepest love and gratitude go to my family, especially to my wife, Chi HaiYing, for their love, patience, and enduring support.

# **Table of Contents**

| Acknowledgements  | i    |

|-------------------|------|

| Table of Contents | ii   |

| Summary           | viii |

| List of Tables    | xi   |

| List of Figures   | xii  |

| Chapter 1. Introduction |  | .1 |

|-------------------------|--|----|

|-------------------------|--|----|

| 1.1 Introduction of the MOSFETs Scaling                                                     |

|---------------------------------------------------------------------------------------------|

| 1.1.1 Overview                                                                              |

| 1.1.2 MOSFET Device Scaling – Approaches                                                    |

| 1.1.3 Gate Dielectric Thickness Scaling                                                     |

| 1.2 Limitation of SiO <sub>2</sub> as the Gate Dielectric for Nano-Scale CMOS Devices5      |

| 1.2.1 Gate Leakage7                                                                         |

| 1.2.2 Reliability                                                                           |

| 1.2.3 Boron Penetration                                                                     |

| 1.3 Oxynitride and Oxynitride/Oxide Stack Dielectrics as Alternatives to SiO <sub>2</sub> 9 |

| 1.4 Alternative Higher-K Materials                                                          |

| 1.4.1 Selection Guidelines for High-K Gate Dielectrics11                                    |

| 1.4.1.1 Electron/Hole Barrier Height and Dielectric Constant        | 11 |

|---------------------------------------------------------------------|----|

| 1.4.1.2 Film Microstructures                                        | 13 |

| 1.4.1.3 Thermal Stability and Channel Interface Quality             | 14 |

| 1.4.1.4 Mobility Issues                                             | 15 |

| 1.4.1.5 Threshold Voltage Related Issues                            | 17 |

| 1.4.2 Research Status of Some Potential High-K Gate Dielectrics     | 18 |

| 1.4.3 Process Issues for High-K Gate Stack Fabrication              | 21 |

| 1.5. Metal Gate Technology                                          | 21 |

| 1.5.1. Limitation of Poly-Si Electrodes for Nano-Meter CMOS Devices | 21 |

| 1.5.1.1 Poly Silicon Depletion Effect                               | 22 |

| 1.5.1.2 Gate Electrode Resistivity and Dopant Penetration Effect    | 23 |

| 1.5.1.3 Work Function Requirement for Novel MOS Devices             | 24 |

| 1.5.2. Metal Gate Technology                                        | 24 |

| 1.6. Major Achievements in This Thesis                              | 26 |

| Reference                                                           | 29 |

#

| 2.1 Introduction                                               | 34 |

|----------------------------------------------------------------|----|

| 2.2 Theoretical Background on X-ray Photoelectron Spectroscopy | 35 |

| 2.2.1 Principles of XPS                                        | 36 |

| 2.2.2 Applications of XPS                                      |    |

| 2.2.2.1 Elemental Analysis                                     |    |

| 2.2.2.2 Chemical Bonding Information                                                                                                  | 39 |

|---------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2.2.3 Energy Gap Measurement for Dielectrics4                                                                                       | 10 |

| 2.2.2.4 Determination of the Valence (Conduction) Band Offset between a                                                               |    |

| Dielectric and the Si Substrate                                                                                                       | 12 |

| 2.3 Experimental4                                                                                                                     | 13 |

| 2.4. Energy Gap and Band Alignment for (HfO <sub>2</sub> ) <sub>x</sub> (Al <sub>2</sub> O <sub>3</sub> ) <sub>1-x</sub> on (100) Si4 | 17 |

| 2.4.1 Hf 4 <i>f</i> , Al 2 <i>p</i> , and O 1 <i>s</i> Core Level Spectra                                                             | 17 |

| 2.4.2. Gap Energy, Valence Band Offset, and Conduction Band Offset to (100)                                                           |    |

| Si Substrate                                                                                                                          | 50 |

| 2.5. Thermal Stability of $(HfO_2)_x(Al_2O_3)_{1-x}$ on (100) Si                                                                      | 55 |

| 2.5.1. XPS Study                                                                                                                      | 55 |

| 2.5.2. XTEM Study                                                                                                                     | 50 |

| 2.5.3. XRD Study                                                                                                                      | 51 |

| 2.6 Conclusion                                                                                                                        | 53 |

| References                                                                                                                            | 5  |

#

| 3.1 Introduction                                                     | 68 |

|----------------------------------------------------------------------|----|

| 3.2 Experimental                                                     | 69 |

| 3.3 Results and Discussion                                           | 71 |

| 3.3.1 Material Characterization of HfN                               | 71 |

| 3.3.2 Electrical Characterization of HfN-SiO <sub>2</sub> Gate Stack | 76 |

| 3.3.3 Electrical Characterization of HfN-HfO <sub>2</sub> Gate Stack | 84 |

| 3.3.3.1 MOS Capacitors with HfN-HfO <sub>2</sub> Gate Stack |     |

|-------------------------------------------------------------|-----|

| 3.3.3.2 MOSFETs with HfN-HfO <sub>2</sub> Gate Stack        | 94  |

| 3.4 Conclusion                                              |     |

| Reference                                                   | 102 |

# Chapter 4. Fermi Pinning Induced Thermal Instability of Metal Gate Work Functions 104 4.1 Introduction 104 4.2 Theoretical Background of Metal-Semiconductor (or Metal-Dielectrics) Interface 105 4.2.1 The Work Function of a Solid 105 4.2.2 Schottky Model and Bardeen Model 106 4.2.3 Interface Dipole Induced by Metal Induced Gap States (MIGS) 107 4.3 Experimental 109 4.4 Results and Discussion 110 4.4.1 Metal Gate on SiO<sub>2</sub> Gate Dielectric 110 4.4.2 Fermi Level Pinning Induced by Localized Extrinsic States – Model 115 4.4.3 Metal Gate on HfO<sub>2</sub> Gate Dielectric 118 4.5 Conclusion 120 Reference 121

| Chapter 5. Investigation of Hole Tunneling Current through |     |

|------------------------------------------------------------|-----|

| Ultrathin Oxynitride/Oxide Gate Dielectrics                | 123 |

| 5.1 Introduction1                                                            | 123 |

|------------------------------------------------------------------------------|-----|

| 5.2 Theoretical Background1                                                  | 124 |

| 5.2.1 Direct Tunneling                                                       | 125 |

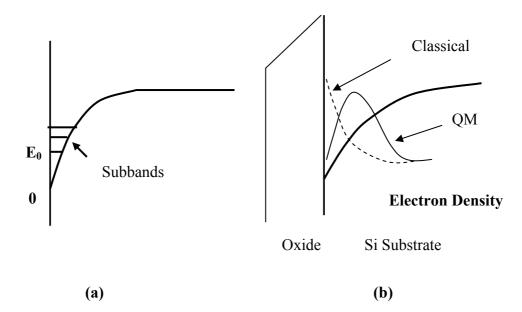

| 5.2.2 Basic Quantum Mechanical Effect in MOS Devices1                        | 126 |

| 5.2.3 Conduction Mechanism1                                                  | 127 |

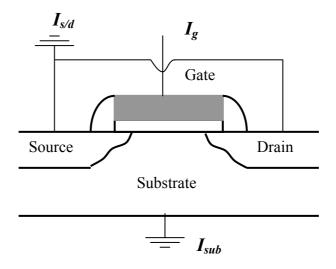

| 5.2.3.1 Carrier Separation Measurement                                       | 127 |

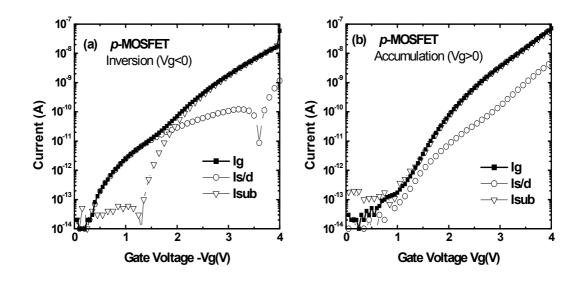

| 5.2.3.2 Conduction Mechanism in P <sup>+</sup> Poly-Silicon Gate P-MOSFET's1 | 128 |

| 5.2.3.3 Conduction Mechanism in N <sup>+</sup> Poly-Silicon Gate N-MOSFET's1 | 131 |

| 5.2.4 Modeling of Hole Current for p-MOSFET's Under Inversion                | 133 |

| 5.3 Experiments1                                                             | 136 |

| 5.4 Results and Discussion1                                                  | 138 |

| 5.4.1 Simulation of Hole Tunneling Through Silicon Oxide and N/O Stack in p  | p-  |

| MOSFET's1                                                                    | 138 |

| 5.4.2 Prediction of Optimum Nitrogen Concentration for Minimum Hole          |     |

| Tunneling Current for p-MOSFET's1                                            | 145 |

| 5.4.3 Projection of Scaling Limits of N/O Stack Gate Dielectrics Used in     |     |

| MOSFET's1                                                                    | 147 |

| 5.5 Conclusions1                                                             | 149 |

| Reference                                                                    | 51  |

| Chapter 6. | Conclusion | and | Recommendations | .154 |

|------------|------------|-----|-----------------|------|

|------------|------------|-----|-----------------|------|

| 6.1 Conclusion Remarks |

|------------------------|

|------------------------|

|   | 6.1.1 Material Characterization of ALD (HfO <sub>2</sub> ) <sub>x</sub> (Al <sub>2</sub> O <sub>3</sub> ) <sub>1-x</sub> Dielectrics | 154 |

|---|--------------------------------------------------------------------------------------------------------------------------------------|-----|

|   | 6.1.2 Thermally Robust HfN Metal Gate Electrode                                                                                      | 155 |

|   | 6.1.3 Metal Gate Work Function Thermal Stability                                                                                     | 157 |

|   | 6.1.4 Direct Hole Tunneling Current Study through Ultrathin Oxynitride/Oxid                                                          | e   |

|   | Stack Gate Dielectrics                                                                                                               | 158 |

| 6 | .2 Recommendations for Future Work                                                                                                   | 159 |

# Appendix

| List of Publications |  | 162 |

|----------------------|--|-----|

|----------------------|--|-----|

### SUMMARY

With the continuous scaling of the CMOS devices, the conventional poly- $Si/SiO_2$  gate stack shall be phased out, and advanced gate stack have to be developed to adapt to this change. The scope of this thesis emphasizes on studies of advanced gate stack for future nano-meter CMOS device application.

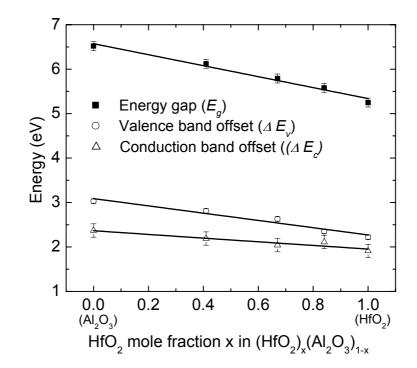

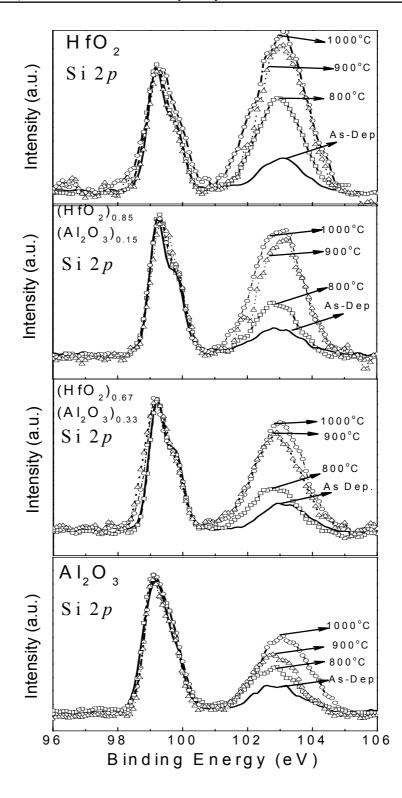

For ALD (HfO<sub>2</sub>)<sub>x</sub>(Al<sub>2</sub>O<sub>3</sub>)<sub>1-x</sub> high-K dielectrics, the materials properties including the energy band alignment to (100) Si substrate and the thermal stability have been studied. The energy gap  $E_g$  for (HfO<sub>2</sub>)<sub>x</sub>(Al<sub>2</sub>O<sub>3</sub>)<sub>1-x</sub>, the valence band offset  $\Delta E_{\nu}$ , and the conduction band offset  $\Delta E_c$  between (HfO<sub>2</sub>)<sub>x</sub>(Al<sub>2</sub>O<sub>3</sub>)<sub>1-x</sub> and the (100) Si substrate were studied based on high-resolution XPS measurement. It is also found that both the thermal stability and the resistance to oxygen diffusion of HfO<sub>2</sub> are improved by adding Al to form Hf aluminates, and the improvement is closely correlated with the Al percentage in the films. This observation is explained by (i) Al<sub>2</sub>O<sub>3</sub> has much lower oxygen diffusion coefficient than HfO<sub>2</sub> at high temperature; (ii) doping HfO<sub>2</sub> by Al raises the film crystallization temperature of HfO<sub>2</sub> and thus drastically reduces the oxygen diffusion along the grain boundaries during annealing.

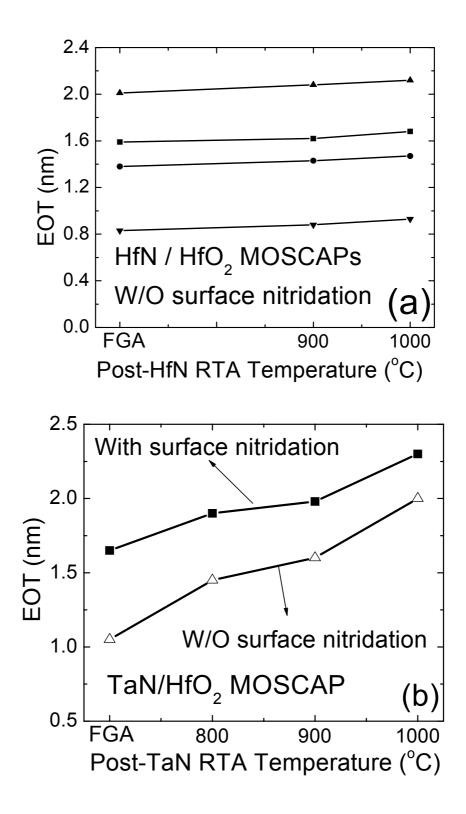

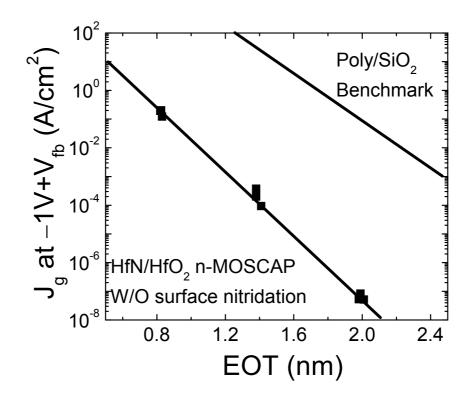

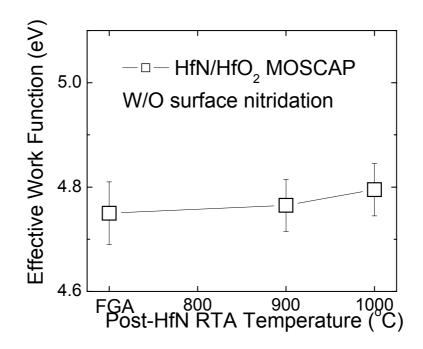

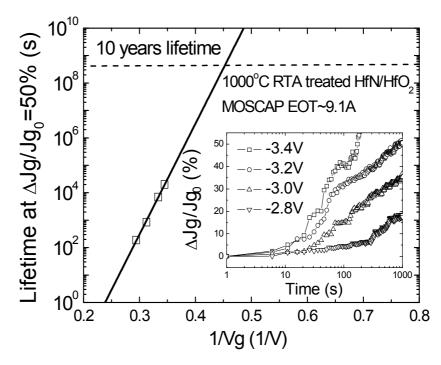

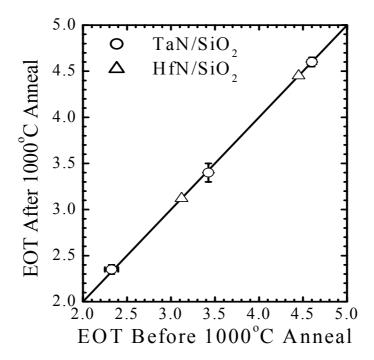

In this thesis, it is firstly reported a systematic study on novel HfN metal gate electrode for advanced CMOS devices applications. By using HfN metal gates, the devices with either SiO<sub>2</sub> or HfO<sub>2</sub> gate dielectrics demonstrate the robust resistance against high temperature RTA treatments (up to 1000°C), in terms of EOT, work function, and leakage current stability. It is also found that HfN metal possesses a mid-gap work function value. This superior electrical stability is attributed to the excellent oxygen diffusion barrier of HfN as well as the thermal stability of HfN/HfO<sub>2</sub> and HfN/SiO<sub>2</sub> interface. Further, the high quality HfN/HfO<sub>2</sub> gate stack's EOT has been successfully scaled down to less than 10Å with excellent leakage, boron penetration immunity, and long-term reliability even after 1000°C annealing, without using surface nitridation prior to HfO<sub>2</sub> deposition. The mobility is improved without surface nitridation for HfN/HfO<sub>2</sub> n-MOSFETs while achieving excellent EOT.

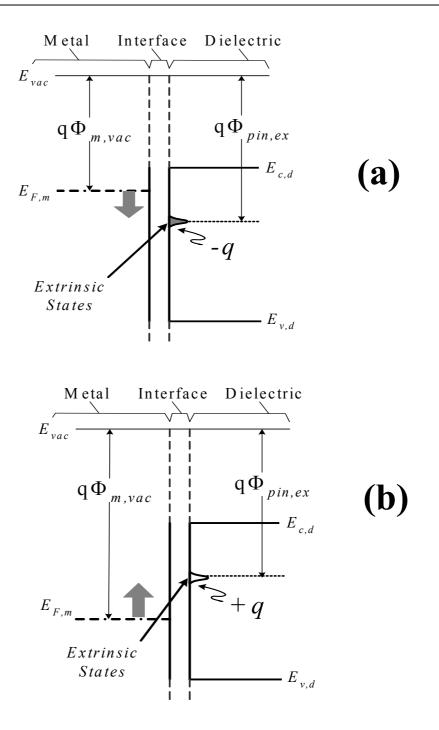

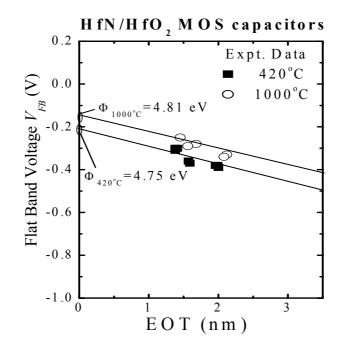

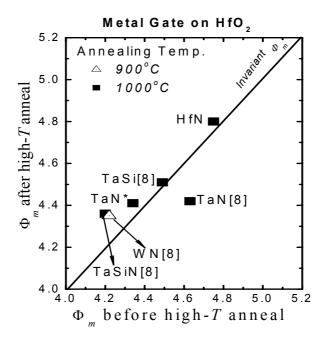

This thesis includes a study on metal gate work function thermal stability. A metal-dielectric interface model that takes the role of extrinsic states into account was proposed to qualitatively explain the dependence of metal work function on annealing process. The creation of extrinsic states and the resulting Fermi level pinning of the metal gate work function is observed for several combinations of metal gate and gate dielectric materials, particularly when the gate dielectric is SiO<sub>2</sub>. The effect appears to be thermodynamically driven, becoming more pronounced when the annealing temperature is higher. In general, the generation of extrinsic states upon annealing is less significant for metal gates on  $HfO_2$  compared to metal gates on  $SiO_2$ .

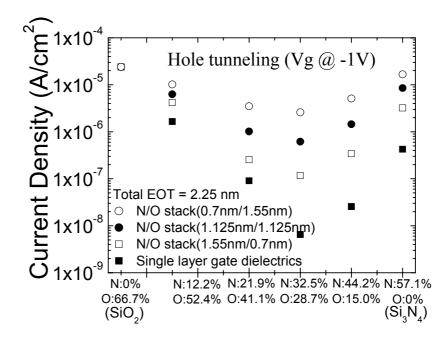

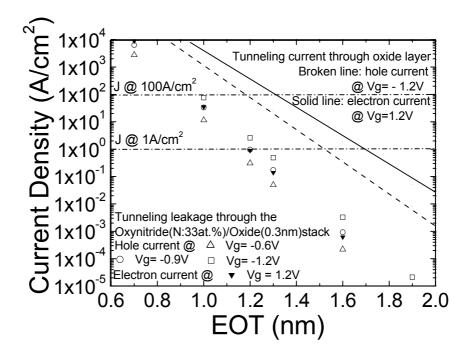

This thesis also presents a systematic study of hole tunneling current through ultrathin oxide and oxynitride gate dielectrics in *p*-MOSFET's devices. It is found that under typical inversion biases ( $|V_g| < 2$  V), hole tunneling current is lower through oxynitride and oxynitride/oxide with about 33 at. % N than through pure oxide and pure nitride gate dielectrics. This is attributed to the competitive effects of the increase in the dielectric constant and decrease in the hole barrier height at the dielectric/Si interface with increasing with N concentration for a given EOT. For minimum gate leakage current and maintaining an acceptable dielectric/Si interfacial

quality, an N/O stack structure consisting of an oxynitride layer with 33 at. % N and a 3 Å oxide layer is proposed. For a *p*-MOSFET at an operating voltage of -0.9 V, which is applicable to the 0.7 µm technology node, this structure could be scaled to EOT = 12 Å if the maximum allowed gate leakage current is 1 A/cm<sup>2</sup> and EOT = 9 Å if the maximum allowed gate leakage current is 100 A/cm<sup>2</sup>.

# List of Tables

| Table 1.1 | The scaling parameters for <i>CES</i> , <i>CVS</i> and generalized scaling guidelines                                                                                                                                                 | 3  |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 1.2 | Technology roadmap characteristics for the scaling of dielectrics thickness with time                                                                                                                                                 | 6  |

| Table 1.3 | Band offsets and dielectric constants for different high-K gate dielectric candidates (including $SiO_2$ and $Si_3N_4$ )                                                                                                              | 19 |

| Table 1.4 | Scaling parameters on gate electrode from ITRS-2001                                                                                                                                                                                   | 23 |

| Table 2.1 | Elemental composition of various $(HfO_2)_x(Al_2O_3)_{1-x}$ samples (labeled as from HAO-1 ~ HAO-5) estimated by XPS. The HfO <sub>2</sub> mole fraction value <i>x</i> as in $(HfO_2)_x(Al_2O_3)_{1-x}$ are also given in the table. | 45 |

| Table 3.1 | Material properties of some refractory metal nitrides                                                                                                                                                                                 | 69 |

# **List of Figures**

- Fig. 1.1 Oxygen bonding profiles for poly-Si/SiO<sub>2</sub>/Si structure measured by STEM-EELS. The Si substrate is at the left side and the gate polycrystalline Si is at the right side. (a) 1.0 nm (ellipsometric) oxide, annealed at 1050°C/10 s. The bulk-like O signal (y axis, arbitrary scale) yields a FWHM of 0.85 nm, whereas the total O signal yields a FWHM of 1.3 nm. The overlap of the two interfacial regions has been correlated with the observation of a very high gate leakage current, 10<sup>2</sup>A/cm<sup>2</sup>. (b) A thicker (~1.8 nm ellipsometric) oxide, also annealed. The interfacial regions no longer overlap and the gate leakage current is 10<sup>-5</sup>A/cm<sup>2</sup>.

- Fig. 1.2 For simple dielectrics, a relationship exists between the gap 12 energy and the permittivity

- Fig. 1.3 Crystallization temperature increases with decreasing film 13 thickness

- Fig. 1.4 Maximum mobility increases with the interfacial oxide 16 thickness

- Fig. 1.5 (a) The energy band diagram of a N-MOS device showing the 22 poly-Si gate depletion effect; (b)  $C_p$ ,  $C_{ox}$ , and  $C_{inv}$  represent the capacitance from the poly depletion layer, gate oxide and substrate inversion layer, respectively.

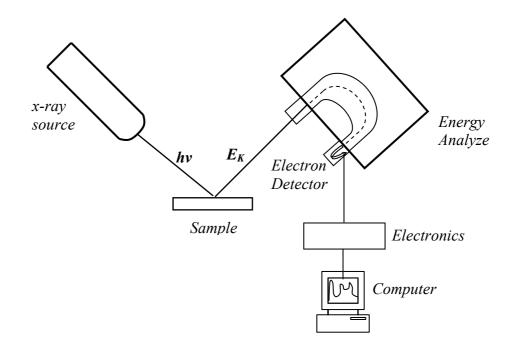

- Fig. 2.1 Schematic diagram of an X-ray photoelectron spectroscopy 37 experiment

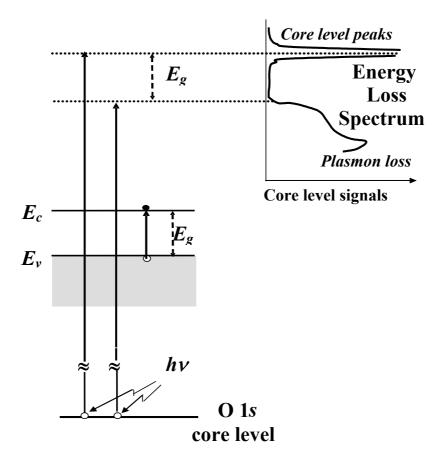

- Fig. 2.2 Schematic diagram showing the formation of O 1s energy loss 41 spectrum

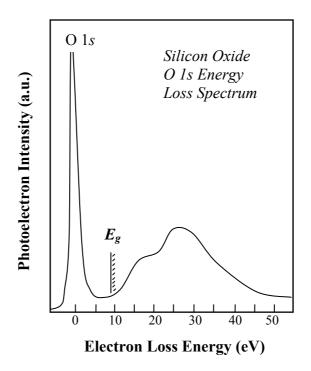

- Fig. 2.3 An example showing energy gap measurement of SiO<sub>2</sub> by 42 means of XPS O 1*s* energy loss spectrum

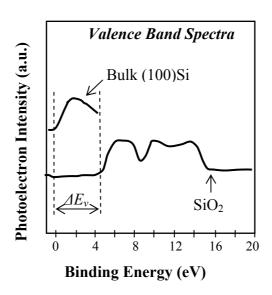

- Fig. 2.4 Valence band offset for SiO<sub>2</sub> on (100)Si determined by XPS 42

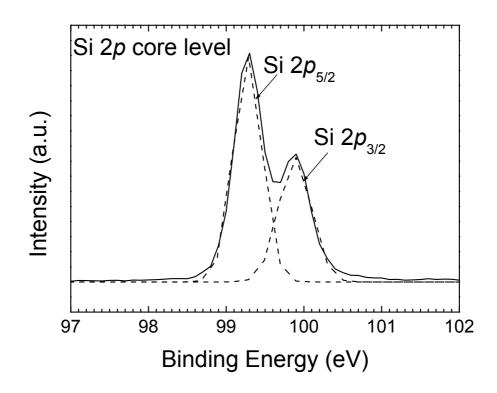

- Fig. 2.5 Si 2p core level spectrum recorded from hydrogen terminated 44 p-Si surface (Na ~  $10^{15}$  /cm<sup>3</sup>) and the FWHM of Si  $2p_{5/2}$  is measured as ~ 0.45 eV.

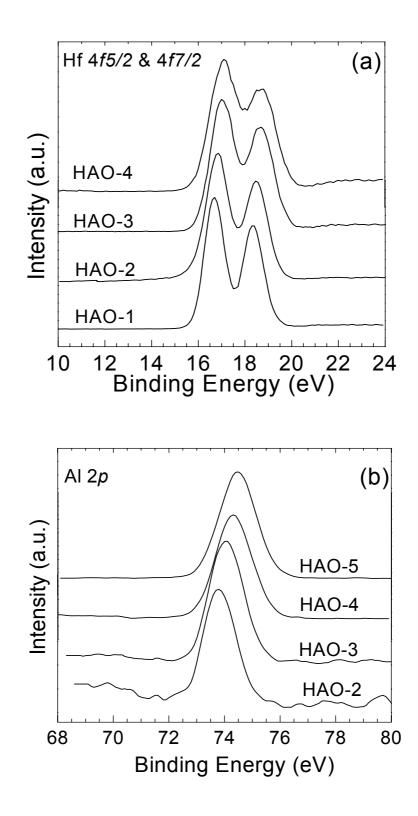

- Fig. 2.6 XPS spectra for (a) Hf 4*f* and (b) Al 2*p* core levels taken from 48 various  $(HfO_2)_x(Al_2O_3)_{1-x}$  samples. The core level peak positions of both Hf 4*f* and Al 2*p* shift continuously towards greater binding energy with increasing of Al components. The intensities for all the XPS spectra reported have been normalized for comparison.

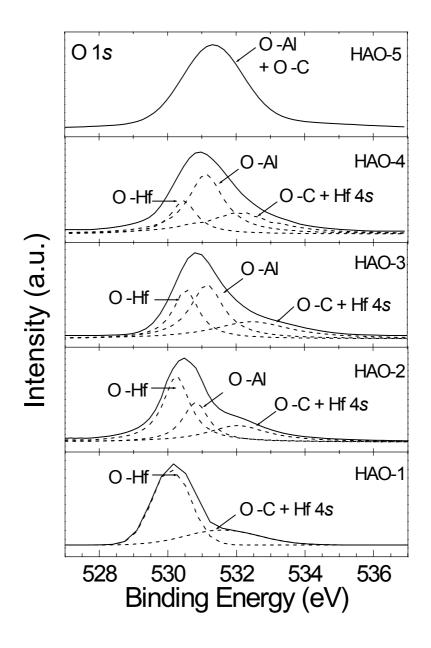

- Fig. 2.7 XPS spectra for O 1s core level taken from various 49 (HfO<sub>2</sub>)<sub>x</sub>(Al<sub>2</sub>O<sub>3</sub>)<sub>1-x</sub> samples. The core level peak positions shift continuously towards greater binding energy with increasing of Al components. Solid lines are experimental data and dashed lines are the curve fitting results.

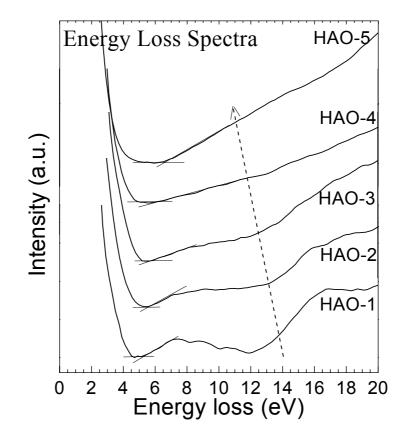

- Fig. 2.8 O 1*s* energy-loss spectra for various  $(HfO_2)_x(Al_2O_3)_{1-x}$  samples. 51 The cross points (obtained by linearly extrapolating the segment of maximum negative slope to the base line) denote the energy gap  $E_g$  values. Dashed arrow shows the continuous change in the energy loss spectra contour from sample HAO-1 to HAO-5.

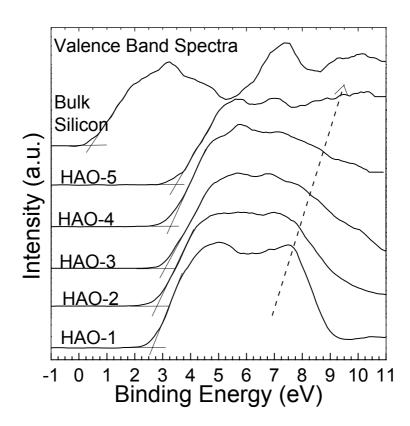

- Fig. 2.9 XPS valence band spectra taken from various (HfO<sub>2</sub>)<sub>x</sub>(Al<sub>2</sub>O<sub>3</sub>)<sub>1-x</sub> 52 grown on (100) Si substrate samples and H-terminated (100) Si substrate sample. The dashed arrow indicates the gradual change in the valence band density of states from sample HAO-1 to HAO-5.

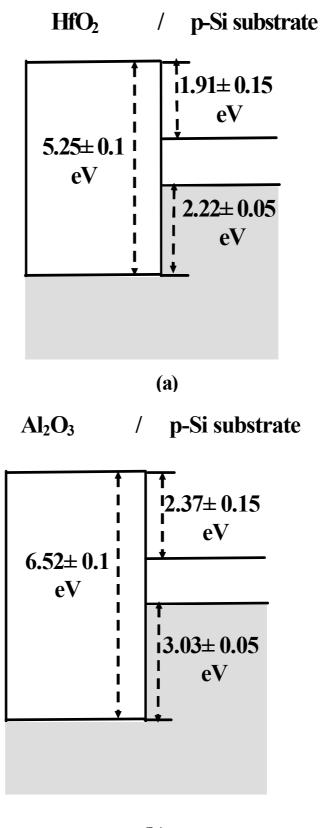

- Fig. 2.10 Schematic energy band alignment of (a) HfO<sub>2</sub> and (b) Al<sub>2</sub>O<sub>3</sub> on 53 (100) Si substrate based on XPS measurements.

- Fig. 2.11 Dependence of  $E_g$ ,  $\Delta E_v$ , and  $\Delta E_c$  for  $(HfO_2)_x(Al_2O_3)_{1-x}$  on  $HfO_2$  55 mole fraction x. The  $E_g$  and  $\Delta E_v$  data are obtained by XPS measurements. The  $\Delta E_c$  data are calculated by eq (2-3). The solid lines are obtained by linear least square fits of the data points.

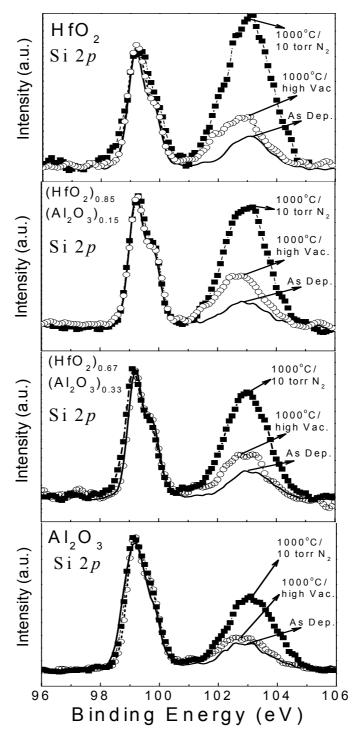

- Fig. 2.12 XPS Si 2p core level spectra recorded from various  $(HfO_2)_x(Al_2O_3)_{1-x}$  samples of as-deposited, after 10 torr of N<sub>2</sub> rapid thermal annealing at 800°C, 900°C, 1000°C respectively. The peak located at ~99.3 eV is assigned to Si-Si bonds from the substrates, and the one at ~103.0 eV to Si-O bonds from IL. The intensities for XPS peaks of Si-Si bonds have been normalized for comparison.

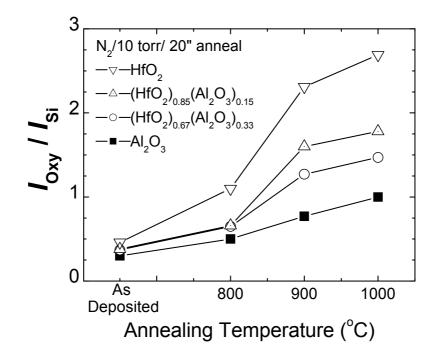

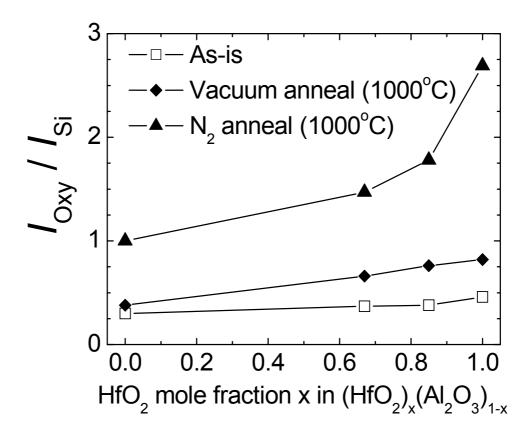

- Fig. 2.13 The ratio of  $I_{Oxy}/I_{Si}$  for various  $(HfO_2)_x(Al_2O_3)_{1-x}$  samples 57 versus the different annealing conditions based on XPS spectra in Fig. 2.12. The change in this ratio directly correlates with the variation of the IL growth.

- Fig. 2.14 XPS Si 2p core level spectra recorded from various 58  $(HfO_2)_x(Al_2O_3)_{1-x}$  samples of as-deposited, after 1000°C RTA in 10 torr of N<sub>2</sub> and in ~ 2 × 10<sup>-5</sup> torr of high vacuum respectively. The intensities for XPS peaks of Si-Si bonds have been normalized.

- Fig. 2.15 The ratio of  $I_{Oxy}/I_{Si}$  for various  $(HfO_2)_x(Al_2O_3)_{1-x}$  samples 59 versus the different annealing conditions based on XPS spectra in Fig. 2.14.

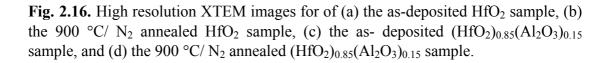

- Fig. 2.16 High resolution XTEM images for of (a) the as-deposited HfO<sub>2</sub> 60 sample, (b) the 900 °C/ N<sub>2</sub> annealed HfO<sub>2</sub> sample, (c) the as-deposited (HfO<sub>2</sub>)<sub>0.85</sub>(Al<sub>2</sub>O<sub>3</sub>)<sub>0.15</sub> sample, and (d) the 900 °C/ N<sub>2</sub> annealed (HfO<sub>2</sub>)<sub>0.85</sub>(Al<sub>2</sub>O<sub>3</sub>)<sub>0.15</sub> sample.

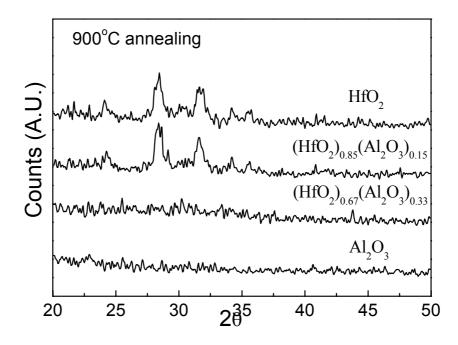

- Fig. 2.17 XRD characteristics of various  $(HfO_2)_x(Al_2O_3)_{1-x}$  samples (~ 62 20nm) after 900 °C/ N<sub>2</sub> annealing.

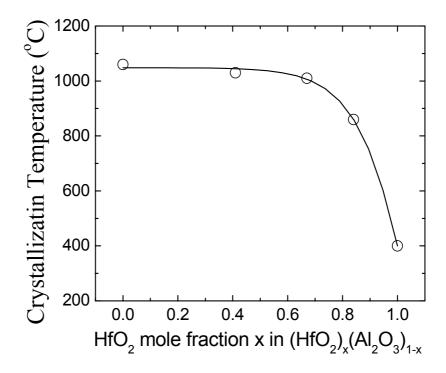

- Fig. 2.18 Crystallization temperature of  $(HfO_2)_x(Al_2O_3)_{1-x}$  variation with 62 its composition.

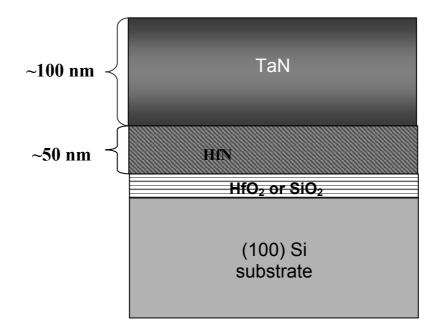

- Fig. 3.1 Schematic structure of the MOS devices with the HfN/TaN 71 metal gate stack

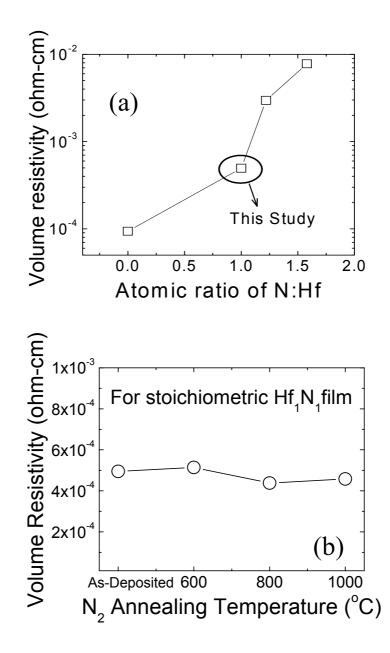

- Fig. 3.2 (a) Dependence of volume resistivity (Rv) of HfN on HfN 72 composition. Rv of pure Hf film is also shown (N:Hf = 0); (b) Dependence of volume resistivity of HfN on N<sub>2</sub> RTA temperature.

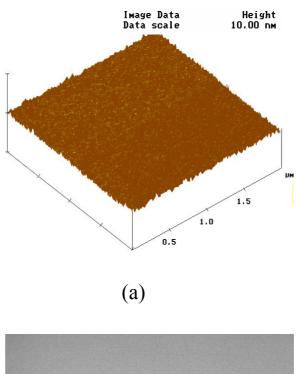

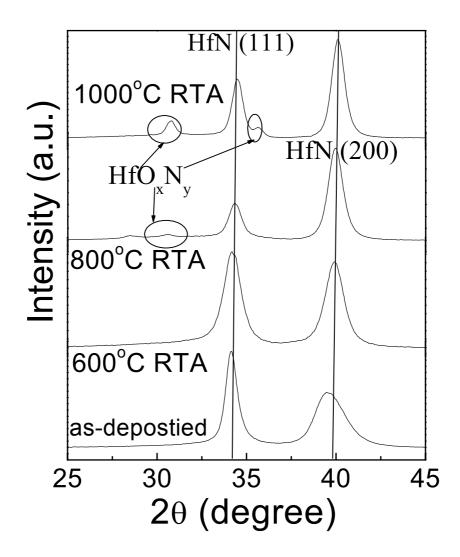

- Fig. 3.3 (a) AFM images of the PVD HfN film surface, with a RMS = 73 1.481nm; (b) SEM images of the PVD HfN film surface

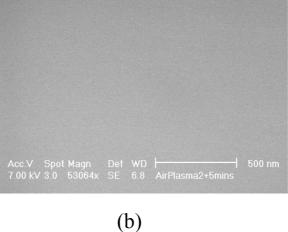

- Fig. 3.4 AES depth profiles for as-deposited and 1000°C RTA treated 74 HfN films

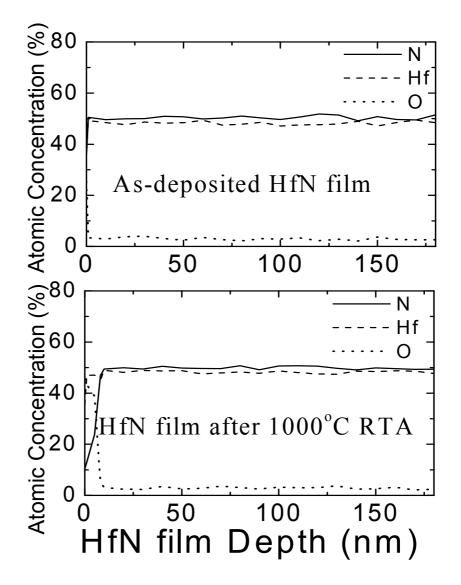

- Fig. 3.5 XRD characteristics of HfN film before and after various RTA 75 treatments. HfN crystalline planes (111) and (200) are indicated in the figure.

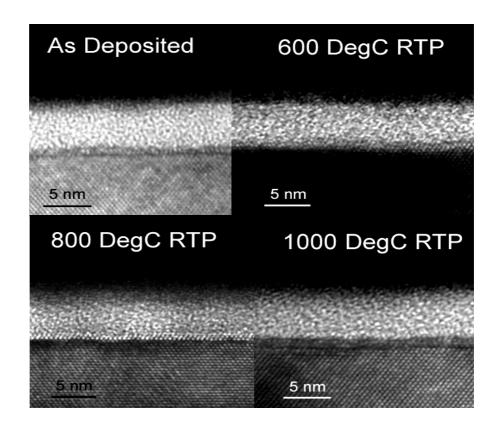

- Fig. 3.6 The high-resolution cross-sectional TEM micrographs of the 76 HfN/SiO<sub>2</sub>/Si MOS structure before and after different RTA in  $N_2$ .

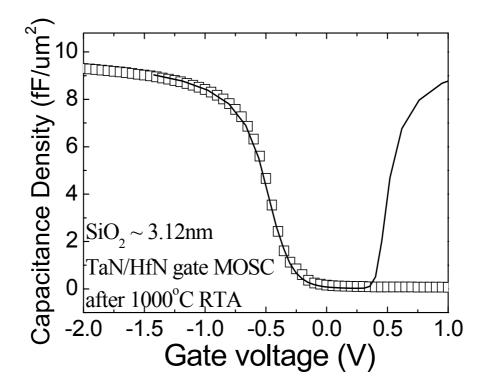

- Fig. 3.7 HFCV measurement (open squares) and LFCV simulation 77 (solid line) for a TaN/HfN gated MOS capacitor

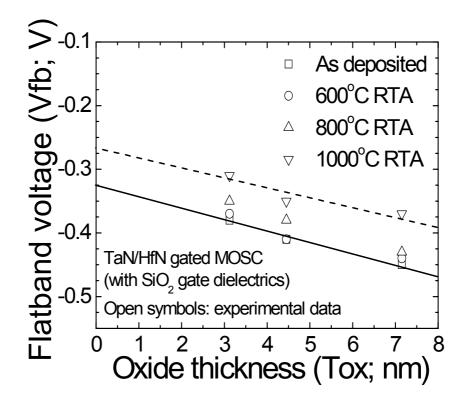

- Fig. 3.8 The plot of  $V_{fb}$  versus  $T_{ox}$  (or EOT) for TaN/HfN gated 78 MOSCAPs devices before and after various RTA treatments, with both  $V_{fb}$  and EOT extracting from CV measurements on these devices (three gate oxide thickness).

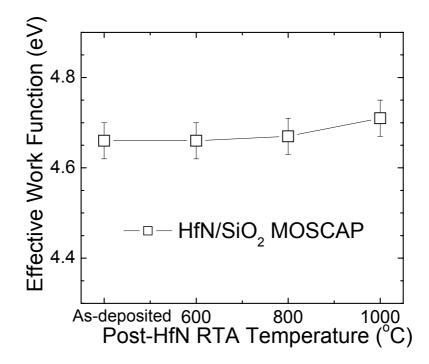

- Fig. 3.9 The dependence HfN  $\Phi_M$  on the N<sub>2</sub> RTA temperature for 78 HfN/SiO<sub>2</sub> devices.

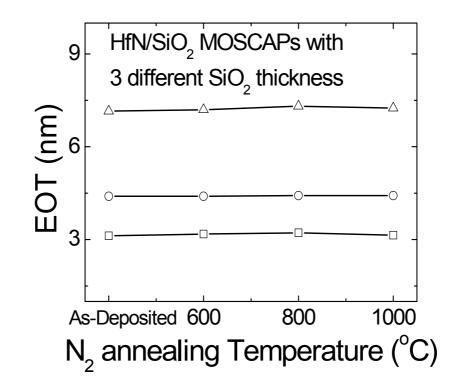

- Fig. 3.10 Dependence of EOT for HfN/SiO<sub>2</sub> MOSCAPs on the N<sub>2</sub> RTA 80 temperature.

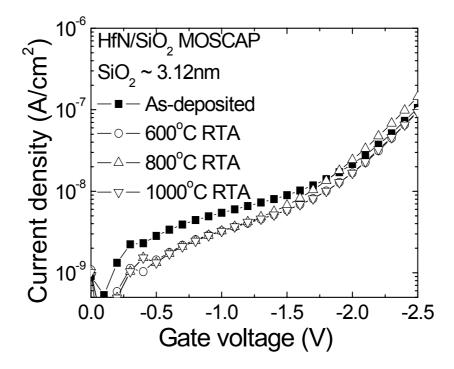

- Fig. 3.11 Measured gate leakage comparison from the HfN/SiO<sub>2</sub> 80 MOSCAPs (EOT=3.12nm) after various post metal annealing (PMA).

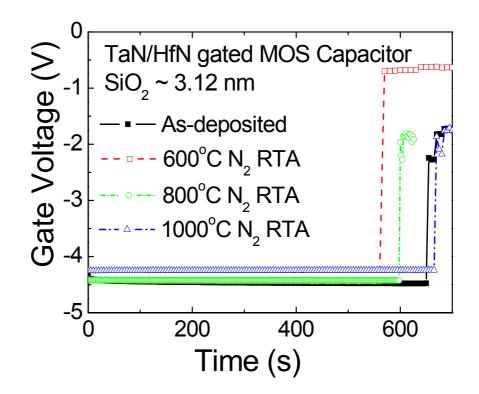

- Fig. 3.12 Typical voltage-time characteristics of MOS capacitors with 81 HfN/SiO<sub>2</sub> gate stack after various RTA under CCS.

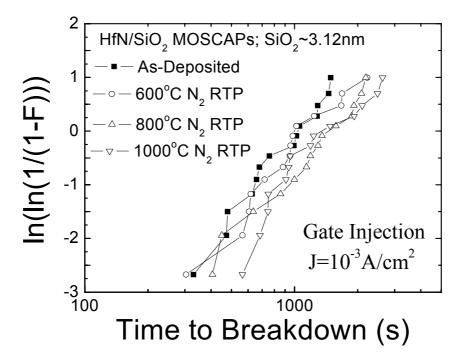

- Fig. 3.13 Comparison on TDDB characteristics of HfN/SiO<sub>2</sub> MOSCAP 81 (EOT=3.12nm) after various PMA.

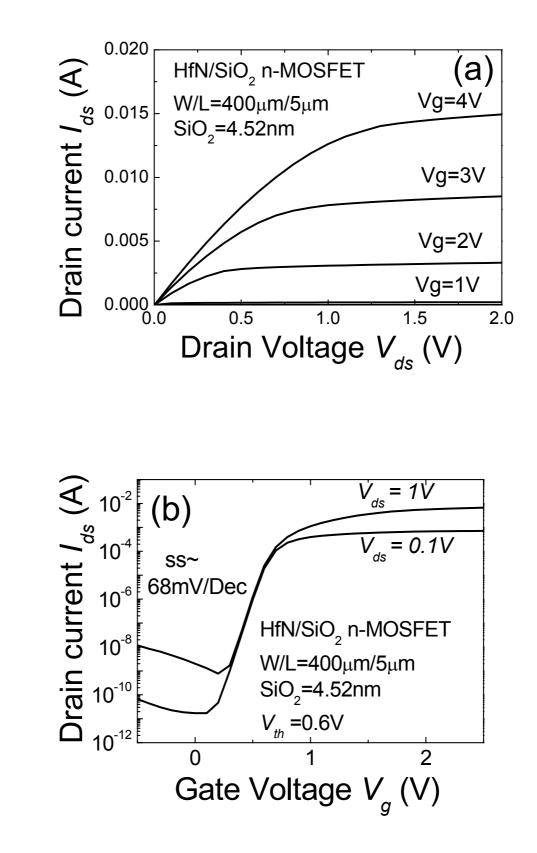

- Fig. 3.14 (a)  $I_{ds}$ - $V_{ds}$ ; (b)  $I_{ds}$ - $V_{g}$  characteristics of a HfN/SiO<sub>2</sub> n-MOSFET. 83

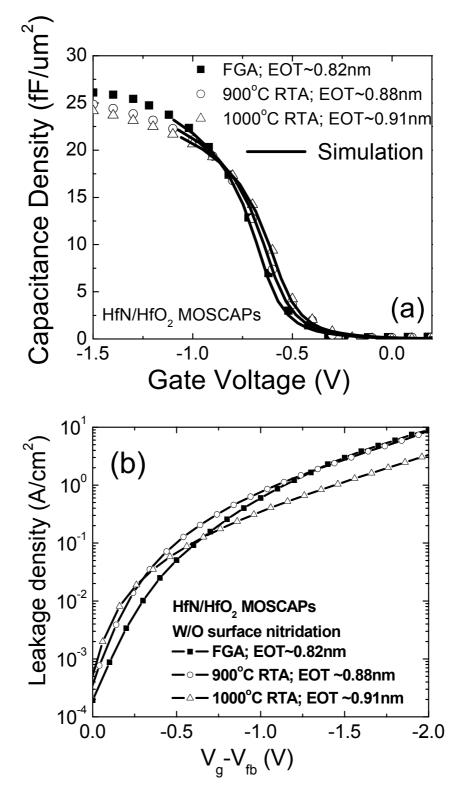

- Fig. 3.15 (a) HFCV measurement (symbols) and LFCV simulation (solid lines) of HfN/HfO<sub>2</sub> n-MOSCAPs after different thermal treatment; (b) The corresponding leakage current measured from the HfN/HfO<sub>2</sub> NMOSCAPs after various thermal treatments. No surface nitridation was performed before HfO<sub>2</sub> deposition.

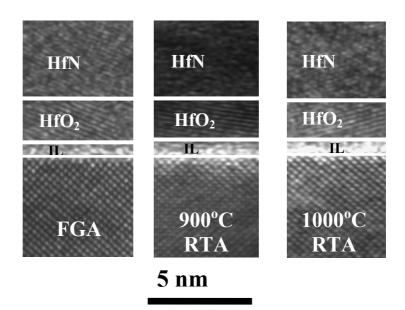

- Fig. 3.16 XTEM of these HfN/HfO<sub>2</sub> devices with different thermal treatments (corresponding to devices shown in Fig. 3.15).

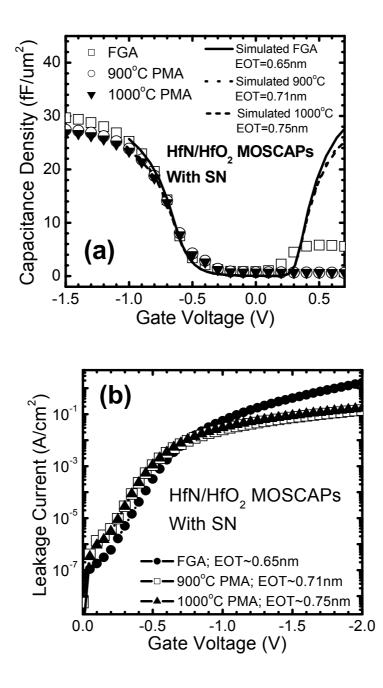

- Fig. 3.17 (a) Measured CV (symbols) and simulated CV (lines) 87 HfN/HfO<sub>2</sub> MOSCAP with surface nitridation after various thermal treatments; (b) The inset shows leakage comparison measured from these HfN/HfO<sub>2</sub> MOSCAP after various PMA.

- Fig. 3.18 Dependence of EOT for (a)  $HfN/HfO_2$  MOSCAPs (b) 88  $TaN/HfO_2$  MOSCAPs on the N<sub>2</sub> RTA temperature.

- Fig. 3.19 Leakage vs. EOT relationship for MOSCAP devices with 89 HfN/HfO<sub>2</sub> gate stack.

- Fig. 3.20 Work function of HfN metal gate on HfO<sub>2</sub> dielectrics after 90 various thermal treatments.

- Fig. 3.21 Lifetime projection based on SILC for the HfN/HfO<sub>2</sub> MOSCAP 90 (W/O SN) after 1000°C RTA with EOT=9.1Å. Inset shows typical SILC time evolutions at four gate voltages. Failure criterion is set at 50% increment of J<sub>g0</sub>.

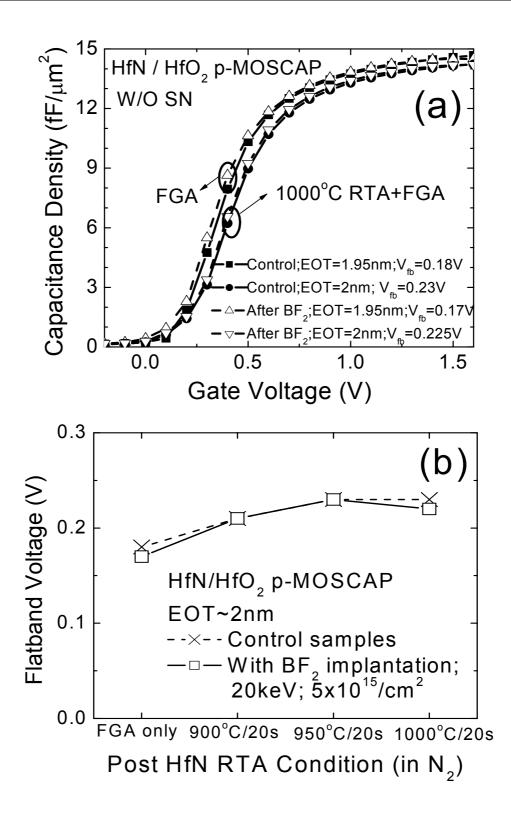

- Fig. 3.22 (a) Boron implantation effect on CV characteristics of 92 HfN/HfO<sub>2</sub> pMOSCAP. Solid symbols: control samples; empty symbols: BF<sub>2</sub> implanted samples. Measured CV after FGA and 1000°C RTA dopant activation are shown for both kinds of samples. (b) The comparison of the V<sub>fb</sub> variation after different RTA between control samples and the BF<sub>2</sub> implanted samples.

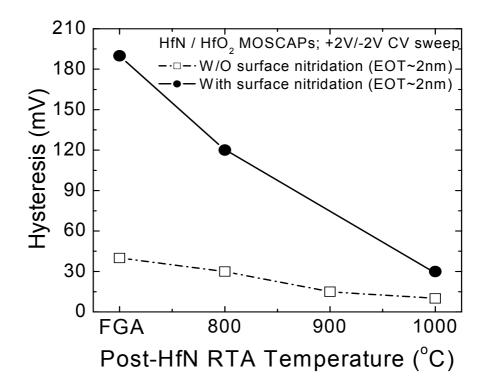

- Fig. 3.23 Hysteresis vs. post-HfN RTA temperature for HfN/HfO<sub>2</sub> 93 devices with and without surface nitridation prior to HfO<sub>2</sub> deposition.

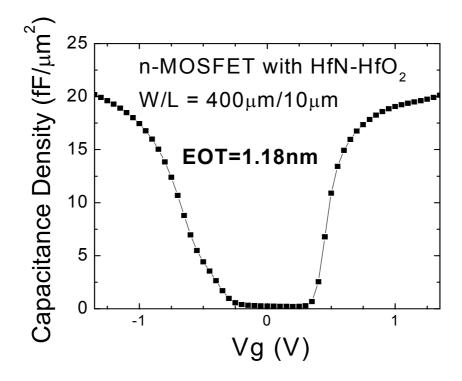

- Fig. 3.24 HFCV characteristics of the n-MOSFET with HfN/HfO<sub>2</sub> gate 94 stack; EOT of 1.18nm is obtained considering the quantum mechanical effect. No surface nitridation was performed before CVD HfO<sub>2</sub> deposition.

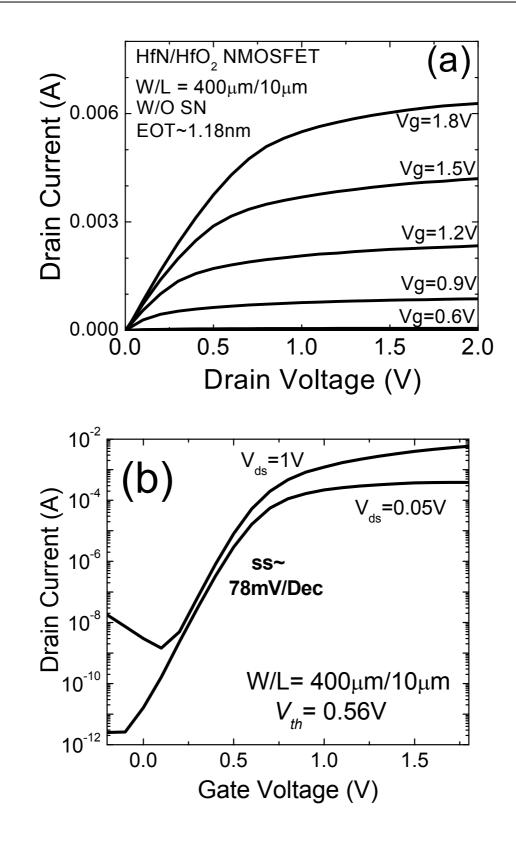

- Fig. 3.25 (a)  $I_{ds}$ -V<sub>ds</sub> (b)  $I_{ds}$ -V<sub>g</sub> characteristics of HfN/HfO<sub>2</sub> n-MOSFETs 95 without using SN and with EOT=1.18nm.

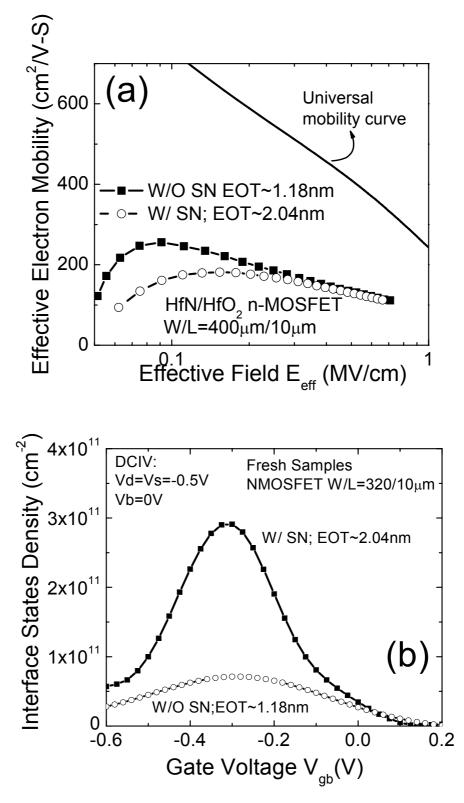

- Fig. 3.26 (a) The effect of SN treatment on effective electron mobility for 96 HfN/HfO<sub>2</sub> n-MOSFETs; (b) DCIV measurement show that interface trap density  $D_{it}$  is  $\sim 3x10^{11}/cm^2$  for fresh nMOSFETs after SN treatment (EOT~2.04nm), and  $D_{it} \sim 7x10^{10}/cm^2$  for fresh device W/O SN with EOT~1.18nm.

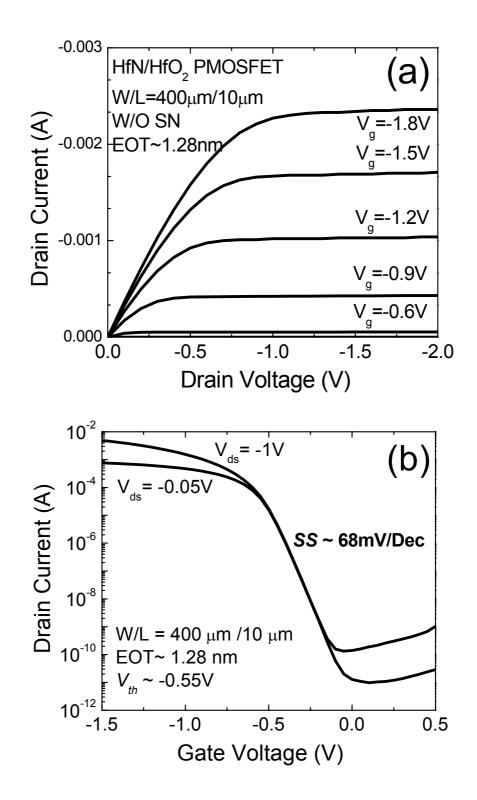

- Fig. 3.27 (a)  $I_{ds}$ - $V_{ds}$  and (b)  $I_{ds}$ - $V_{g}$  characteristics of HfN/HfO<sub>2</sub> p- 98 MOSFETs without using SN and with EOT=1.28nm.

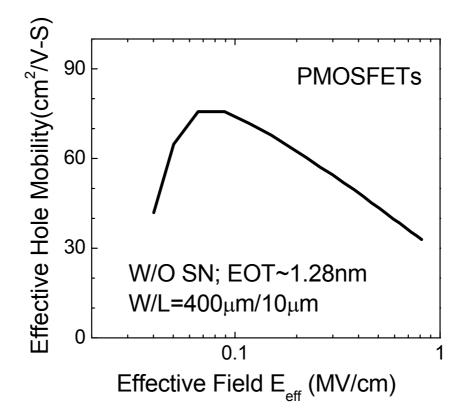

- Fig. 3.28 Effective hole mobility measured by split CV for the p-MOSFETs shown in Fig. 3.27.

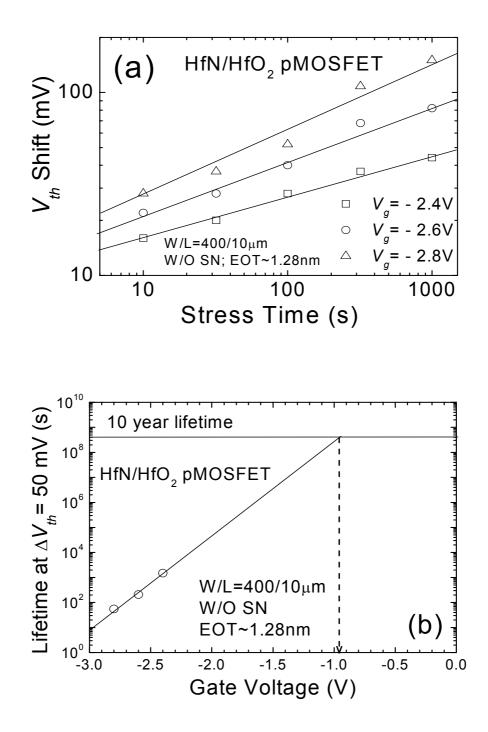

- Fig. 3.29 (a) For HfN/HfO<sub>2</sub> p-MOSFETs without using SN & with EOT=1.28nm, the V<sub>th</sub> variation as a function of stress time during NBTI under three different negative gate biases at 100°C. (b) Lifetime projection based on NBTI. Failure criterion is set as  $\Delta$ Vth=50mV. The devices can satisfy the 10-year lifetime at an operation voltage of ~1V.

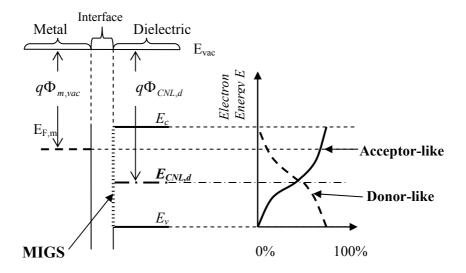

- Fig. 4.1 Schematic energy band diagram (left) and the characteristics of 108 the gap states (right) for metal gate on dielectrics. The character of MIGS becomes more acceptor- (donor-) like toward the  $E_c$  ( $E_v$ ), as indicated by the solid (dashed) line.

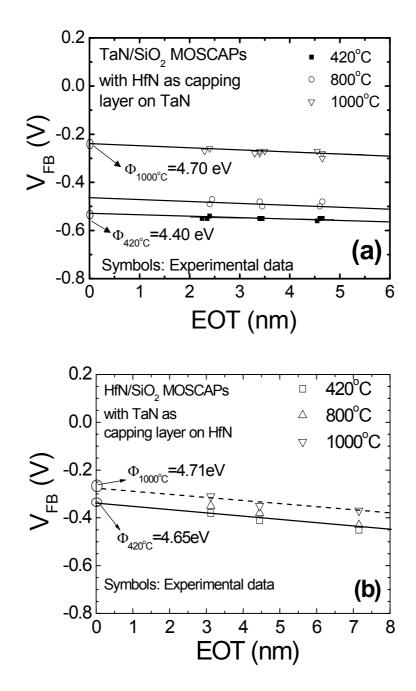

- Fig. 4.2 Flat band voltage  $V_{FB}$  versus SiO<sub>2</sub> dielectric thickness after 111 annealing at various temperatures for (a) HfN/TaN/SiO<sub>2</sub>/Si, and (b) HfN/SiO<sub>2</sub>/Si MOS capacitors.

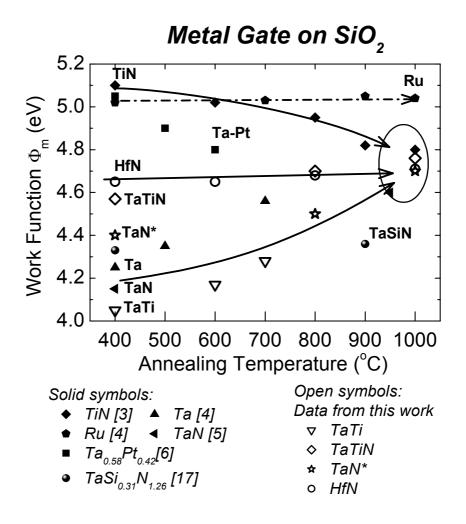

- Fig. 4.3 The variation of metal gate work function  $\Phi_m$  with the 112 annealing temperature. The gate dielectric is SiO<sub>2</sub>. Intrinsic states at the interface of metals and SiO<sub>2</sub> do not play a very significant role in modifying the vacuum metal work function. Therefore, the change of  $\Phi_m$  with increasing temperature is predominantly due to extrinsic states.

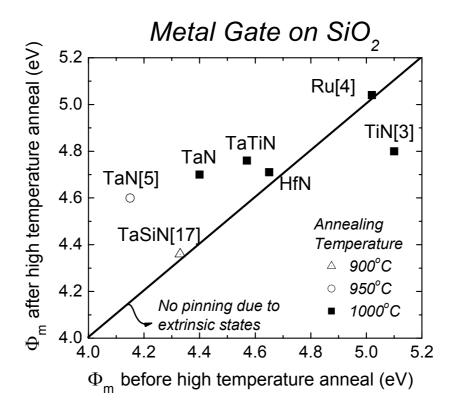

- Fig. 4.4 Work function of metal gates on (a) SiO<sub>2</sub> and (b) HfO<sub>2</sub> before 113 and after annealing at high temperatures. A 400°C anneal was performed prior to the high temperature anneal.

- Fig. 4.5 Gate dielectric EOT of HfN/TaN/SiO<sub>2</sub> or HfN/SiO<sub>2</sub> devices 114 does not change significantly after 1000°C anneal.

- Fig. 4.6 Schematic energy band diagram for a metal gate on a dielectric, 116 showing extrinsic states that pin the metal Fermi level. (a) When  $E_{F,m}$  is above the pinning level, (b) When the  $E_{F,m}$  is below the extrinsic pinning level. The conduction band edge and the valence band edge of the dielectric are denoted by  $E_{c,d}$  and  $E_{v,d}$ , respectively.

- Fig. 4.7 Plot of  $V_{fb}$  versus EOT of HfN/HfO<sub>2</sub>/Si MOS capacitors before 119 and after 1000°C anneal.

- Fig. 4.8 Impact of high temperature anneal on metal work function on 119 HfO<sub>2</sub>. (data TaN\* is from this work)

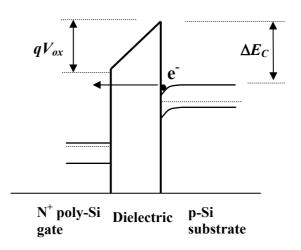

- Fig. 5.1 Schematic sketch of electron direct tunneling in an n-MOS 125 device under inversion.

- Fig. 5.2 Schematic illustration of the quantum mechanical effect (a) 126 energy quantization, (b) carrier density distribution in the Si substrate.

- Fig. 5.3 The cross-sectional schematics of the carrier separation 127 measurement

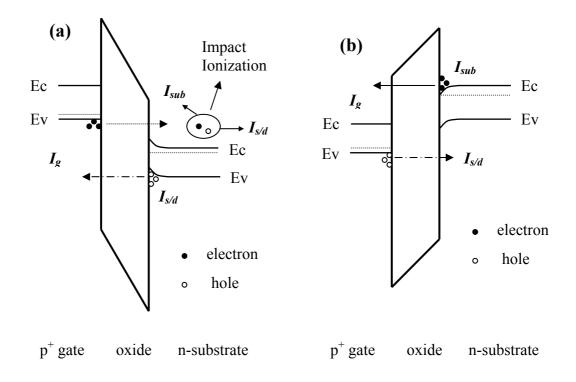

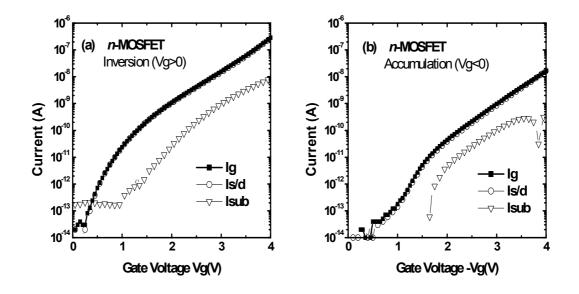

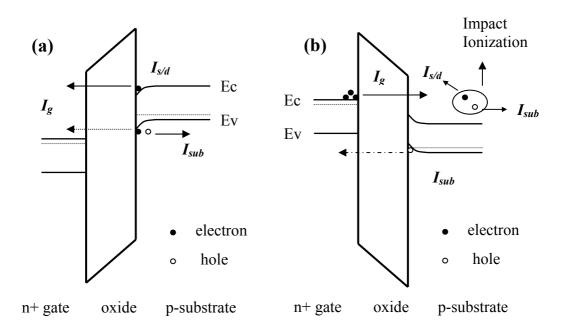

- Fig. 5.4 I-V characteristics (carrier separation) of a typical  $p^+$  polysilicon gate p-MOSFET (SiO<sub>2</sub> as gate dielectrics) under (a) the inversion, and (b) the accumulation biases.

- Fig. 5.5 Schematic band diagram of a p-MOSFET under (a) the 130 inversion, and (b) the accumulation biases.

- Fig. 5.6 I-V characteristics (carrier separation) of a typical  $n^+$  132 polysilicon gate n-MOSFET (SiO<sub>2</sub> as gate dielectrics) under (a) the inversion, and (b) the accumulation biases.

- Fig. 5.7 Schematic band diagram of a n-MOSFET under (a) the 132 inversion, and (b) the accumulation biases.

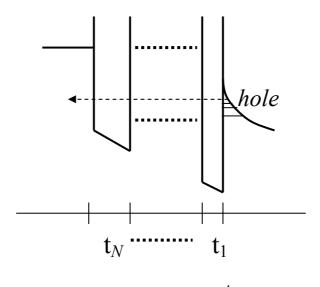

- Fig. 5.8 Energy band diagram of a p-MOSFET in inversion, assuming 134 the gate stack dielectrics contain N different layers (from  $t_1$  to  $t_N$ ). The inverted holes are confined in the inversion layer and form discrete 2-D subbands.

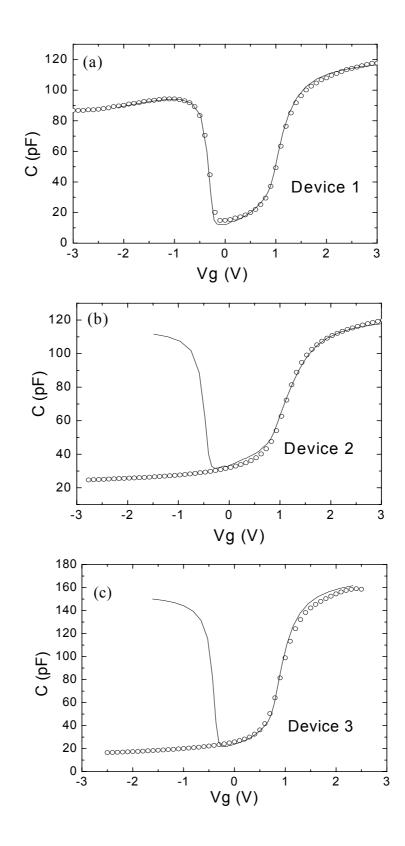

- Fig. 5.9 High frequency C-V experimental data (open circles) and 137 simulation results (solids lines) for (a) Device 1, (b) Device 2, and (c) Device 3. The device area is 10000 μm<sup>2</sup>.

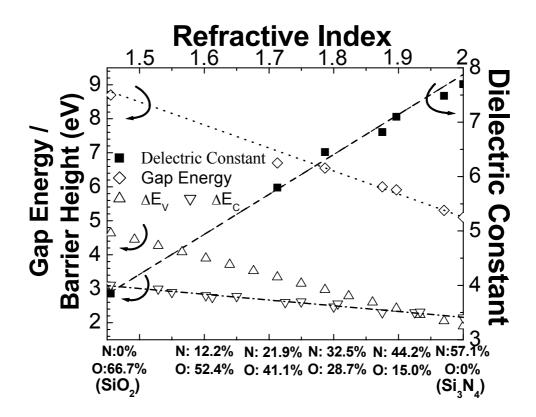

- Fig. 5.10 Variation of the electron and hole barrier height at the 139 oxynitride/Si interface ( $\Delta E_C$  and  $\Delta E_V$ ), oxynitride gap energy (*Eg*), as well as dielectric constant with the oxynitride composition.

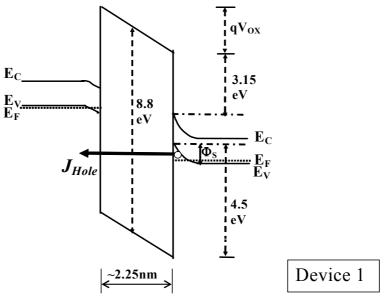

- Fig. 5.11 Energy band diagram of a *p*-MOSFET with oxide gate 140 dielectric (Device 1). Oxide thickness is determined as 2.25 nm from *C*-*V* measurements.

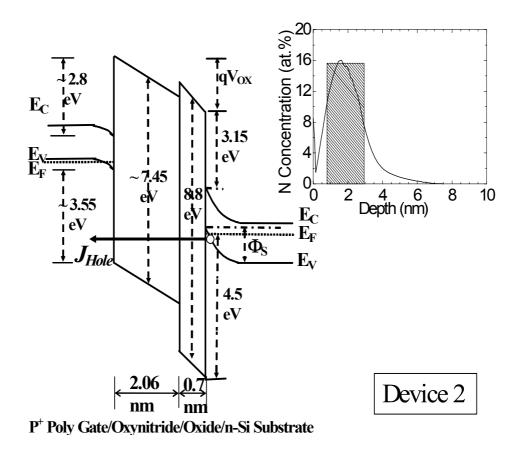

- Fig. 5.12 Energy band diagram of a *p*-MOSFET with oxynitride/oxide 140 stack gate dielectric (Device 2). Inset shows the SIMS depth profile of N in the oxynitride layer.

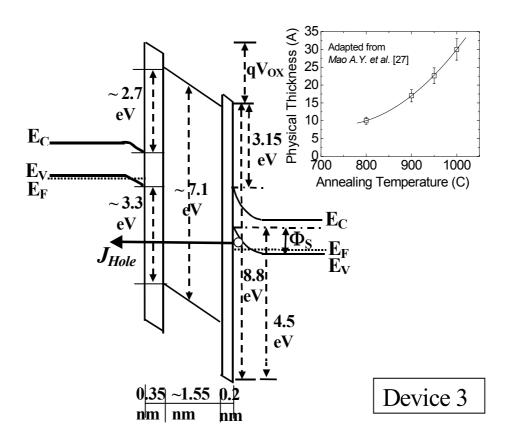

- Fig. 5.13 Energy band diagram of а p-MOSFET with 141 oxide/oxynitride/oxide stack gate dielectric (Device 3). Inset shows the variation of the physical thickness of the dielectric with annealing temperature. The 950 °C annealed gate stack in device 3 has a physical thickness of  $\sim 2.25$  nm [27]. The N concentration in the Oxynitride in this device 3 is estimated to be around 21 at. % according to the XPS measurement. EOT of the oxynitride is  $1.55 \times 3.9 / 5.7 = 1.05$  nm (3.9 and 5.7 are the dielectric constants obtained from Fig. 1 for the oxide and the oxynitride in device 3 respectively). EOT of the ONO stack is then 0.2+1.05+0.35=1.6 nm, in corresponding to the EOT measurement based on C-V simulation.

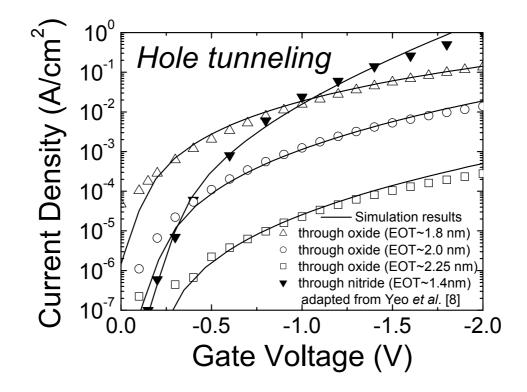

- Fig. 5.14 Comparison of simulated (line) and measured (symbol) hole 142 tunneling current through oxide and nitride gate dielectrics in *p*-MOSFETs at various dielectric thicknesses. In the simulation,  $0.41m_0$  is used for the hole effective mass in both nitride and oxide

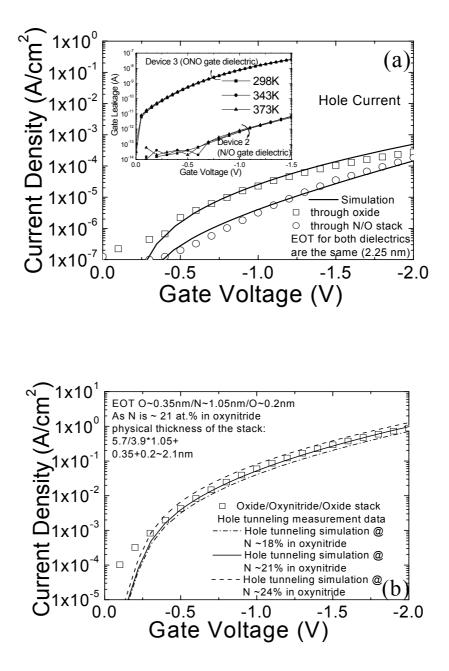

- Fig. 5.15 Comparison of simulated (line) and measured (symbol) hole 144 tunneling current through (a) oxide and oxynitride/oxide stack gate dielectrics in *p*-MOSFETs at EOT = 2.25 nm. Inset of Fig. 5.15a: negligible change of gate leakage through N/O (device 2) and ONO (device 3) with temperature up to 100 °C, indicating that the trap assisted tunneling mechanism such as Frenkel-Poole hopping can be neglected in hole leakage current in our oxynitride samples. (b) oxide/oxynitride/oxide stack gate dielectric in a p-MOSFET at EOT = 1.6 nm for various N concentrations in the oxynitride layer. In the simulation,  $0.41m_0$  is used as the hole effective mass in both oxide and oxynitride

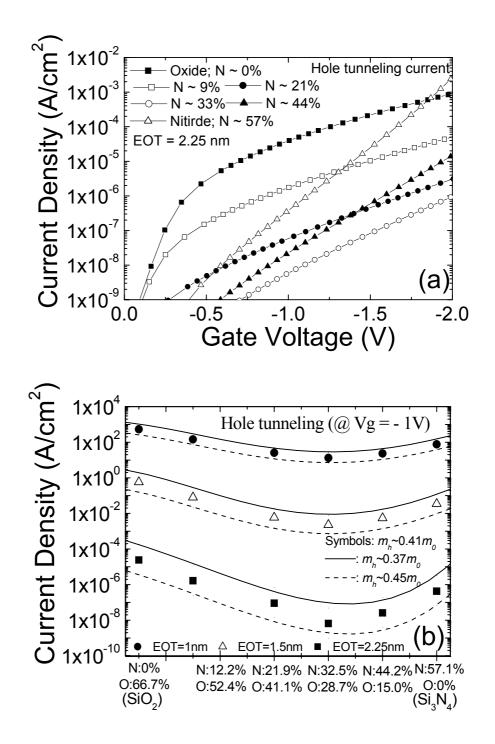

- Fig. 5.16 (a) Simulated hole tunneling current through oxynitride gate 146 dielectric in a p-MOSFET at EOT = 2.25 nm for various N concentrations in the dielectric. (b) Simulated hole tunneling current through oxynitride gate dielectric in a p-MOSFET at  $V_g = -1$  V for various EOT and N concentrations in the dielectric. The effect of +/- 10% variation of oxynitride hole effective mass value (0.41 $m_0$ ) [8] on hole tunneling current is demonstrated in this figure (solid and dashed lines). Hole tunneling current is lowest through the oxynitride with ~33 at. % of N for all of the cases.

- Fig. 5.17 Simulated hole tunneling current through oxynitride/oxide stack 147 gate dielectric in a *p*-MOSFET at  $V_G = -1.0$  V and EOT = 2.25 nm for various combinations of oxynitride and oxide thicknesses, and N concentrations in the oxynitride layer. (EOT of oxynitride /EOT of oxide data are given in the brackets.)

- Relationship between gate leakage currents (hole tunneling for 149 Fig. 5.18 *p*-MOSFET @ – 0.6V [open triangles], – 0.9V [open circles], – 1.2V [open squares] and electron tunneling for *n*-MOSFET @ 1.2V [solid triangles]) and total EOT of the optimized N/O stack. For same EOT and same absolute value of gate voltage (1.2 V), the electron current in n-MOSFET is lower than the hole current in p-MOSFET, which indicates that the EOT scaling for this optimized N/O stack is determined by the hole tunneling current in *p*-MOSFET, not by electron tunneling current in n-MOSFET. Also shown are the gate leakage currents through pure oxide layer (hole tunneling in *p*-MOSFET (a) - 1.2V [dashed line], and electron tunneling in *n*-MOSFET @ 1.2V [solid line] for different EOT. The critical dashed line (a) J = 1 A/cm<sup>2</sup> [14,15] suggests that the minimum EOT of this N/O stack structure used in MOSFET's is around 1.2 nm at a projected gate voltage of -0.9V.

# **Chapter 1**

# Introduction

# 1.1 Introduction of the MOSFETs Scaling

# 1.1.1 Overview

During the past several decades, silicon-based microelectronics devices have infiltrated practically every aspect of our daily life. This has been accomplished by continuously achieving the characteristics of higher speed, greater density, and lower power for the individual devices (the Metal Oxide Semiconductor Field Effect Transistors – MOSFET's). Therefore, "scaling", which is the reduction in individual device size, became the focus of engineers over the past 30+ years. The scaling behavior has followed the well known Moore's law, which predicts that the number of transistors per integrated circuit would double every ~ 18 months [1]. During the silicon industry's history and for most of the time, line features of the MOS devices (or <u>Dynamic Random Access Memory – DRAM half pitch</u>) have decreased at the rate of ~ 70% every two or three years. The design rules have been scaled from about 8  $\mu$ m in the year of 1972 to the 90 nm (0.09  $\mu$ m) DRAM half pitch of today's leading-edge technology. In the meantime, cost per function has decreased at an average rate

of ~ 25-30% per year per function [2]. Based on the predication of International Technology Roadmap for Semiconductors (ITRS), in the year of 2016, the MOSFET's with  $L_g$  ( $L_g$  is the final, etched length at the bottom of the gate electrode) of ~ 10 nm would be required for the mass production [2].

# 1.1.2 MOSFET Device Scaling – Approaches

There are various sets of scaling rules aimed at reducing the device size while keeping device function [3-5], such as constant-field scaling (*CES*), constant-voltage scaling (*CVS*), and the generalized scaling rules.

In *CES*, it was proposed to keep the electric field unchanged in a short-channel device in order to maintain comparable characteristics and reliability relative to a long channel device. The idea behind *CES* is to scale the device voltages ad the device dimensions (both horizontal ad vertical) by the same factor, so that the electric field remains unchanged. However, the requirement to reduce the supply voltage by the same factor as the physical dimension reduction in *CES* is difficult to meet since the threshold voltage and sub-threshold slope are not easily controlled for scaling [6]. If the threshold voltage scales slower than other factors, the drive current will be reduced. Thus, a constant voltage scaling rule (*CVS*) was proposed to address this issue, where the voltages remain unchanged while device dimensions are scaled. However, *CVS* will result in an extremely high electric field, which causes unacceptable leakage current, power consumption, and dielectric breakdown as well as hot-carrier effects [6]. To avoid the extreme cases of CFS and CVS, a generalized

scaling approach has been developed, where the electric field is scaled by a factor of  $\kappa$  while the device dimensions are scaled by a factor of  $\alpha$  [4]. In Table 1.1, the scaling parameters for CES, CVS and generalized scaling schemes are compared. In reality, the CMOS technology evolution has followed mixed steps of CES, CVS, and generalized scaling.

| MOSFET Device and Circuit                   | Multiplicative Factor for MOSFET's |              |                     |  |

|---------------------------------------------|------------------------------------|--------------|---------------------|--|

| parameters                                  | Constant E                         | Constant V   | Generalized         |  |

| Device Dimensions $(T_{ox}, L_g, W, X_j)$   | $1/\alpha$                         | $1/\alpha$   | $1/\alpha$          |  |

| Voltage (V)                                 | $1/\alpha$                         | 1            | к/α                 |  |

| Electric Field (E)                          | 1                                  | α            | К                   |  |

| Capacitance ( $C = \epsilon A/t$ )          | $1/\alpha$                         | $1/\alpha$   | $1/\alpha$          |  |

| Inversion Layer Charge Density $(Q_i)$      | 1                                  | α            | К                   |  |

| Circuit Delay Time ( $\tau \sim CV/I$ )     | $1/\alpha$                         | $1/\alpha^2$ | 1/κα                |  |

| Power per Circuit (P~VI)                    | $1/\alpha^2$                       | α            | $\kappa^3/\alpha^2$ |  |

| Power-Delay Product per Circuit ( $P\tau$ ) | $1/\alpha^3$                       | $1/\alpha$   | $\kappa^2/\alpha^3$ |  |

| Circuit Density ( $\propto l/A$ )           | $\alpha^2$                         | $\alpha^2$   | $\alpha^2$          |  |

| Power Density (P/A)                         | 1                                  | $\alpha^3$   | K <sup>3</sup>      |  |

Table 1.1. The scaling parameters for CES, CVS and generalized scaling guidelines

(α: Dimensional Scaling Factor; κ: Voltage Scaling Factor)

# 1.1.3 Gate Dielectric Thickness Scaling

One of the purposes of MOSFET device scaling is to decrease the switching time  $\tau$  of the MOSFET gate.

$$\tau = (CV/I_{dsat})^{-1} \tag{1-1}$$

Eq. 1-1 gives the definition of the  $\tau$  [7], in which *C* is the MOSFET gate's capacitance, *V* is the applied voltage, *I* is the current, taken as  $I_{dsat}$ . For the MOSFET with a high-K gate dielectric,  $I_{dsat}$  is given by the following equation [6]:

$$I_{dsat} = (w/2L_g) \left[ (\varepsilon_{SiO2}\varepsilon_0 A) / CET_{high-K} \right] \mu \left( V_{DD} - V_{th} \right)^2$$

(1-2)

$V_{DD}$  is the power supply bias,  $V_{th}$  is the threshold voltage,  $CET_{high-k}$  is the total electrically measured dielectric thickness in inversion, and  $L_g$  and w are the transistor's physical length and width, respectively. Note that *CET* extends the EOT to include the poly-depletion and quantum confinement effects. It can be seen that high drive current can be achieved by reducing  $L_g$ , decreasing the gate dielectric electrical thickness  $CET_{high-k}$ , or improving the channel carrier mobility  $\mu$ . Reducing the *EOT* of the dielectric has been a most efficient method to obtain a higher  $I_{dsat}$ . In addition, *EOT* reduction enhances the gate control over the channel, ensuring good short-channel behavior. On the other hand, it is essential to maintain the off-state leakage current (including gate leakage currents) as low as possible. From this viewpoint, SiO<sub>2</sub> gate dielectric will be eventually phased out as the dielectric thickness is scaled down to sub-1 nm region, and this will be discussed in detail in the next session. By using high-K gate dielectric as the replacement of the conventional SiO<sub>2</sub> dielectric, the physical thickness,  $T_{physical}$  of the gate dielectric could be increased with the decrease of the EOT (described by equations 1-3):

$$EOT_{high-K} = (\varepsilon_{SiO2} / \varepsilon_{high-K}) \times T_{physical}$$

(1-3)

where  $\varepsilon_{SiO2}$  and  $\varepsilon_{high-K}$  are the dielectric constant of SiO<sub>2</sub> and the high-K dielectric respectively.

# **1.2 Limitation of SiO<sub>2</sub> as the Gate Dielectric for Nano-**Scale CMOS Devices

The outstanding properties of SiO<sub>2</sub> have been the key element enabling the scaling of Si-based MOSFET's. The amorphous, high resistivity, stable (both thermodynamically and electrically) thin SiO<sub>2</sub> layer with a band gap of ~ 9 eV acts as an excellent insulator, separating two electrical signals. One traveling between the source and drain in the channel region underneath the SiO<sub>2</sub> and the other one flows in the semi-metallic layer (the gate) above the SiO<sub>2</sub>. These two signals are coupled in a capacitive fashion by SiO<sub>2</sub> film. Presently, defect charge density of  $< 5x10^{10}$ /cm<sup>2</sup>, mid-gap interface state densities of  $< 5x10^{10}$ /cm<sup>2</sup>-eV, dielectric strength of ~ 15 MV/cm, minimal low-frequency CV hysterisis and frequency dispersion (< 10 mV), minimal dielectric charging and interface degradation, and the sufficiently high carrier mobility (both electrons and holes) can be usually obtained for the MOSFET's with Si/SiO<sub>2</sub> system [2].

The rapid shrinking of transistor feature size must be accompanied by the corresponding reduction in the gate dielectric thickness. The gate dielectrics thickness of SiO<sub>2</sub> has decreased from the range of  $\sim$  50-100nm from the 4K

NMOSFET DRAM to  $\sim 1.2$  nm EOT for the today's leading edge high performance logics, and Table 1.2 summarizes such a trend.

**Table 1.2.** Technology roadmap characteristics for the scaling of dielectrics thickness with time [2]

| Year                                                                   | 2004    | 2007    | 2010    | 2013    | 2016    |

|------------------------------------------------------------------------|---------|---------|---------|---------|---------|

| Technology node                                                        | 90      | 65      | 45      | 32      | 22      |

| Physical gate length for MPU (nm)                                      | 37      | 25      | 18      | 13      | 9       |

| Physical gate length for low power logic (nm)                          | 53      | 32      | 22      | 16      | 11      |

| EOT for high-performance (nm)                                          | 0.9-1.4 | 0.6-1.1 | 0.5-0.8 | 0.4-0.6 | 0.4-0.5 |

| EOT for low-operating-power (nm)                                       | 1.4-1.8 | 1-1.4   | 0.8-1.2 | 0.7-1.1 | 0.6-1   |

| EOT for low-standby-power (nm)                                         | 1.8-2.2 | 1.2-1.6 | 0.9-1.3 | 0.8-1.2 | 0.7-1.1 |

| Gate leakage at 100°C for high performance (A/cm <sup>2</sup> )        | 270     | 4,000   | 17,000  | 54,000  | 110,000 |

| Gate leakage at 100°C for low-<br>operating-power (A/cm <sup>2</sup> ) | 0.57    | 2.19    | 4.55    | 18.75   | 90.9    |

| Gate leakage at 100°C for low-<br>standby-power (A/cm <sup>2</sup> )   | 0.0019  | 0.0031  | 0.014   | 0.044   | 0.091   |

With the rapid downscaling of  $SiO_2$  gate insulators, several limits will become inevitable, such as interfacial structure, boron penetration, reliability, and gate leakage issues. The direct tunneling, reliability, and boron penetration concerns associated with ultrathin  $SiO_2$  will be described below.

### 1.2.1 Gate Leakage

When the physical thickness of SiO<sub>2</sub> becomes thinner than ~ 3 nm, the gate leakage current will be dominated by the direct tunneling through the dielectric. As the SiO<sub>2</sub> thickness is decreased, the gate leakage current through the film increases exponentially according to the fundamental quantum mechanical rules [8]. The rapid increase in leakage current with the decrease of the gate dielectric thickness will pose serious concerns regarding to the operation of CMOS devices, especially with respect to standby power dissipation. The high gate leakage also causes the inversion charge loss, resulting in no further gains in transistor drive current when scaling the SiO<sub>2</sub> thickness thinner than about 10-12 Å [9].

**Fig. 1.1.** Oxygen bonding profiles for poly-Si/SiO<sub>2</sub>/Si structure measured by STEM-EELS. The Si substrate is at the left side and the gate polycrystalline Si is at the right side. (a) 1.0 nm (ellipsometric) oxide, annealed at  $1050^{\circ}$ C/10 s. The bulk-like O signal (y axis, arbitrary scale) yields a FWHM of 0.85 nm, whereas the total O signal yields a FWHM of 1.3 nm. The overlap of the two interfacial regions has been correlated with the observation of a very high gate leakage current,  $10^{2}$ A/cm<sup>2</sup>. (b) A thicker (~1.8 nm ellipsometric) oxide, also annealed. The interfacial regions no longer overlap and the gate leakage current is  $10^{-5}$ A/cm<sup>2</sup>. Courtesy from ref [10].

The study on SiO<sub>2</sub> electronic structure by electron energy loss spectroscopy (EELS) [10] indicates that the bulk SiO<sub>2</sub> energy band gap or the energy band offset to Si substrate cannot be maintained when the thickness of SiO<sub>2</sub> becomes less than two monolayers (~ 0.7 nm). As shown in Fig. 1.1, the EELS profiles consist of bulk-like regions and interfacial regions, and the interfacial regions are believed to be due to the interfacial states. Electrically, this 'interface' material would be unsuitable for low-leakage, high-mobility device operation, implying that a capacitor structure with two interfaces must be at least ~1.2 nm thick if considering the contribution from interfacial roughness (~0.5 nm). Therefore, SiO<sub>2</sub> ~ 10-12 Å is believed to be the practical limit, corresponding to the gate dielectric target in the 65 nm technology node [2].

# 1.2.2 Reliability

Reliability of ultrathin SiO<sub>2</sub> is another major concern for oxide scaling into the sub-2 nm range [11-13]. The carriers traveling through the SiO<sub>2</sub> layer may generate defects including carrier traps and interface states, and upon accumulation to the critical density, the dielectrics properties will be degraded. The accumulated charge to breakdown values ( $Q_{bd}$ ) for the dielectrics decreases with the thickness [11]. Recently, it was predicted that oxide films thinner than ~ 1.4 nm would not achieve the reliability required by the industry roadmap [12]. Nevertheless, the real impact of oxide breakdown on circuit performance, which ultimately is the critical issue, should be further investigated.

### **1.2.3 Boron Penetration**

As the  $SiO_2$  film decreases in thickness, boron penetration from p+ polysilicon gate to the channel region becomes significant especially upon thermal annealing [14,15]. This will result in a change in the doping concentration of the channel region, which in turn, leads to the poor threshold voltage control, the fluctuations in flat band voltage accompanied by increasing PMOSFETs subthreshold slope, and decreased the low field carrier mobility [14].

# **1.3 Oxynitride and Oxynitride/Oxide Stack Dielectrics** as Alternatives to SiO<sub>2</sub>

Oxynitride and oxynitride/oxide stack structures as the near-term gate dielectric alternatives have been proposed to address the high leakage, boron penetration and reliability concerns of ultrathin  $SiO_2$  [2]. It is noted that the hole and electron barrier height at the Oxynitride/Si interface, the oxynitride gap energy, as well as the dielectric constant vary linearly with the N concentration of the oxynitride film [16,17].

The addition of N to  $SiO_2$  could greatly reduce the impurity (especially for boron) diffusion through the dielectric, and was suggested to be due to the particular Si–O–N bonding lattice formed in silicon nitride and oxynitride [15]. Small amounts of N (~ 0.1 at. %) at or near the Si channel interface provide the ability of controlling channel hot-electron degradation effects [17]. However, larger amounts of N near this interface will degrade device performance. A work for depositing Si-nitride directly on the Si channel by remote plasma chemical vapor deposition (RPCVD), claimed the poor pMOS performance, with significant degradation of channel mobility and drive current [18]. This degradation mechanism is mainly attributed to excess charge of pentavalent N atoms, and hence a high defect density arising from bonding constraints imposed at the interface, which causes increased channel carrier scattering. In addition, the defect levels in the Si-nitride layer which reside near the valence band of Si also contribute the degradation. Oxynitride/oxide stack structure with the oxide as interfacial buffer layer is thus proposed in order to obtain the improved electrical properties [19,20].

Due to the ultimate limitation of the dielectric constant values of oxynitride (for  $Si_3N_4$ , the K value is ~ 7.8) and its smaller gap energy compared to  $SiO_2$ , the scaling limits for thickness of oxynitride (oxynitride/oxide stack) would be ~ 1.2 nm [20]. Further scaling of gate dielectrics requires other materials with higher K values.

# **1.4 Alternative Higher-K Materials**

The metric of the high-K gate dielectrics rather than  $SiO_2$  is to provide a physically thicker film for reduced leakage current and improved gate capacitance. In this section, the selection procedure for the alternative high-K gate dielectric is first discussed, followed by an overview of the research status on some potential high-K

gate dielectrics. Process issues for high-K gate stack fabrication and the pressing concerns associated with high-K transistors will also be briefed.

### 1.4.1 Selection Guidlines for High-K Gate Dielectrics

Several most important factors being considered for gate dielectric selection process are described as followings:

# 1.4.1.1 Electron/Hole Barrier Height and Dielectric Constant

First, the dielectrics should have barrier height for both electrons and holes  $(\Delta E_c \text{ and } \Delta E_v)$  more than 1.0 eV to avoid unacceptable gate leakage either by thermal emission or tunneling [21]. A large gap energy value generally corresponds to a large  $\Delta E_c$ , but the band structure for some materials has a large valence band offset  $\Delta E_v$  which constitutes most of the band gap of the dielectric (such as Ta<sub>2</sub>O<sub>5</sub>).

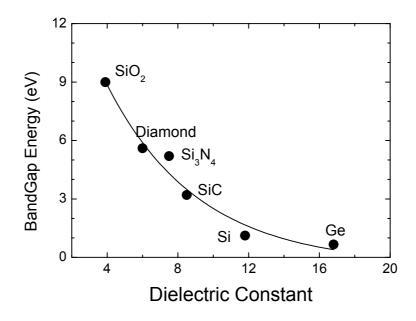

The gap energy of the dielectric should be balanced against its dielectric constant. Permittivity generally increases with increasing atomic number for a given cation in a metal oxide. However, the band gap of the metal oxides tends to decrease with increasing atomic number [22]. Fig. 1.3 shows that for simple dielectrics, the gap energy will decrease with the increase of the dielectric constant [23].

**Fig. 1.2.** For simple dielectrics, a relationship exists between the gap energy and the permittivity [23].

Attention is paid to such effect as the Fringing-Induced Barrier Lowering (*FIBL*) for high-K materials [24]. *FIBL* effect predicts that the device off-state leakage current increases as K value increases (become significant especially when K>25), which is due to that a significant fringing field at the edge of a high-K dielectric could lower the barrier for carriers transport into the drain, and hence seriously degrade the on/off characteristics of the device. It is therefore appropriate to find a dielectric which provides a moderate increase in K, but which also produces a large tunneling barrier and high quality interface to Si. A single dielectric layer with  $k \sim 12-25$  could allow a physical dielectric thickness of 35–50 Å to obtain the *EOT* values required for 65 nm CMOS and beyond.

### **1.4.1.2 Film Microstructures**

It is desirable that the gate dielectric remains amorphous throughout the necessary processing treatments [22]. The limitation of polycrystalline dielectrics could be the defects induced by grain boundaries, and the interfacial roughness arising from potentially faceted interfaces. Grain size and/or orientation changes inside a polycrystalline film can cause the variations in K value, leading to irreproducible properties for the dielectrics. In addition, the defects throughout the high-K films and interfacial roughness can cause the increase of gate leakage and the reduction of carrier mobility. The application of the single-crystalline dielectrics could be limited by its fabrication methods, although the grain boundaries and the interface issues could be addressed. These single-crystalline materials grown on Si substrate require sub-monolayer deposition control, which may only be obtainable by epitaxial approaches, which is not a cost-effective and manufacturable technique for mass production.

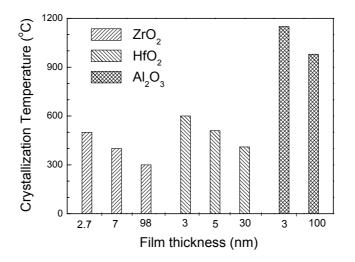

Fig. 1.3. Crystallization temperature increases with decreasing film thickness [25]

Fig. 1.3 shows the crystallization temperature for  $Al_2O_3$ ,  $ZrO_2$ , and  $HfO_2$  high-K dielectrics [25].  $Al_2O_3$  remains amorphous upon annealing till 1100 °C, while  $ZrO_2$ and  $HfO_2$  become crystallized below 600 °C. It is interesting to note that for all of three dielectrics, crystallization temperature increases with the decrease of the film thickness.

### 1.4.1.3 Thermal Stability and Channel Interface Quality

The interface with Si channel plays a key role for the realization of the high-K gate dielectrics in the IC. Most of the high-K materials reported up to date show the interface states density  $(D_{it})$  of ~  $10^{11} - 10^{12}$  states/eV-cm<sup>2</sup>, and a fixed charge density ~  $10^{11} - 10^{12}$  /cm<sup>2</sup> at the interface. It is proposed that the Si-dielectric interface quality depends on the bonding constraints [26]. The interface defect density will increase proportionally if the average number of bonds per atom is higher/lower compared to that of Si, leading to an over-/under- constrained interface with Si. These metal oxide (either over- or under- constrained with respect to SiO<sub>2</sub>) result in the formation of a high density of electrical defects near the Si-dielectric interface.

In addition, for most of the high-K materials, during their deposition on Si substrate under equilibrium conditions, there would be an undesirable and uncontrollable interfacial layer [22]. Therefore an interfacial reaction barrier should be required for a better channel interface quality. The chemical stability of gate oxides on silicon in the subsequent process conditions also has a critical impact on the Si/dielectric interface quality. One step from a typical CMOS process flow is the source/drain (S/D) activation annealing, which the gate stack must undergo. The

typical S/D anneal is done by rapid thermal anneal technique (up to 1000°C). If the cations from the gate dielectric diffuse into the channel region, the device electrical properties (especially the channel mobility induced by the impurity scatter) will be degraded. To control and improve the channel interface quality, the knowledge of the following for the gate dielectric is required during subsequent process: reaction with silicon, oxygen diffusion kinetics, oxygen stoichiometry, film crystallization and component segregation.

For the high-K dielectrics with high oxygen diffusivities at high temperature, such as  $ZrO_2$  and  $HfO_2$  [17, 27], during the annealing treatments where an excess of oxygen present, rapid oxygen diffusion through the oxides could be expected. And hence, the SiO<sub>2</sub> or SiO<sub>2</sub>-containing low-K interface layers would be formed, posing a serious concern regarding to *EOT* scalability of the high-K dielectric.

### 1.4.1.4 Mobility Issues

Mobility is a critical parameter to evaluate a high-K dielectric as the replacement to  $SiO_2$ . It is a key parameter determining a number of transistor metrics, such as saturation current, speed, threshold voltage, transconductance, and sub-threshold swing. It is desired to maintain the mobility of the high-K transistors close to that of the  $SiO_2$  system.

Three scattering mechanisms determine the inversion carrier mobility: the Coulomb charge scattering, the phonon scattering, and the surface roughness scattering [42]. Surface roughness scattering dominates only when the effective field

15

is high enough so that channel carriers are close to the Si substrate surface. It has been shown that at a high effective field ( $\geq 1$  MV/cm), the mobility of high-K transistors becomes close to the universal mobility curve.

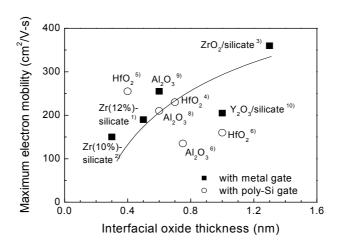

Coulomb scattering may originate from different scattering centers. Coulomb scattering centers was traditionally known to be due to the substrate impurities. However, remote Coulomb scattering (*RCS*) has been identified to play an important role for the mobility degradation phenomena in high-K transistors. These remote scattering centers are away from the inversion layer, and might be due to fixed charge, oxide trap, interface trap and micro-crystallization related to the high-K dielectric. Ref. [43] concludes that a thicker interfacial layer between high-K dielectric and Si substrate would lead to a higher carrier mobility [Fig. 1.4], based on the results summarized from various research groups. This suggests that the remote Coulomb scattering centers centroid is nearby the interfacial layer. A research group at *International Sematech* observes that the mobility increases with decreasing high-K physical thickness, which is attributed to the reduced total Coulomb scattering due to charges in the high-K [44].

Fig. 1.4. Maximum mobility increases with the interfacial oxide thickness.

At low temperature, it is known that only Coulomb scattering and surface roughness scattering dominate for transistors with the SiO<sub>2</sub> dielectric [42], as the phonon scattering is suppressed. However, it is interesting to note that a recent study [45] suggests that soft phonons scattering in high-K dielectrics is a source of mobility degradation, by investigating the low temperature mobility of the HfO<sub>2</sub> transistor, and comparing it with the SiO<sub>2</sub> counterpart at the medium high effective electric field (when inversion charge >  $5x10^{12}$  cm<sup>-2</sup>). On the other hand, another study on the low temperature mobility measurement [46] shows that electron mobility of HfO<sub>2</sub> transistor is much lower than the SiO<sub>2</sub> control at the relatively low effective field, indicating the RCS is at least partly responsible for the mobility degradation in HfO<sub>2</sub> device.

#### 1.4.1.5 Threshold Voltage Related Issues

Threshold voltage control is another key issue to be addressed in order to realize the high-K transistors in the IC. For the transistors with the poly-Si/HfO<sub>2</sub> gate stack and the poly-Si/Al<sub>2</sub>O<sub>3</sub> gate stack, significant threshold voltage shift has been observed as compared to poly-Si/SiO<sub>2</sub> control devices [47]. It was found the respective positive and negative shifts in *n*- and *p*- MOSFETs with high-K gate dielectrics, and this has been interpreted as the Fermi pinning occurring at the interface of poly-Si/HfO<sub>2</sub> and poly-Si/Al<sub>2</sub>O<sub>3</sub> [47]. Recently, the high threshold voltage is also reported in the transistors with high-K gate dielectrics using metal gate electrode [48], and again the Fermi pinning was suggested to play a determining role for such an observation [48, 49].

The dopant penetration through dielectrics leads to the uncontrolled threshold voltage shift of the transistors. This issue might be more significant for high-K transistors compared to the device with  $SiO_2$ , as most of the high-K become crystalline during the S/D annealing process. N-incorporation in high-K dielectrics is expected to suppress the dopant penetration [50], similar as the current  $SiO_xN_y$  technology.

It was observed that charge trapping phenomena occurs in the HfO<sub>2</sub> gate dielectric for MOSFETs under DC uniform ( $V_{ds} = 0$ ) static stress [51,52], leading to severe bias temperature instability (BTI). BTI is important as it caused the device threshold voltage shift and saturation drive current decreases with electrical stressing. However, under AC ( $V_{ds} \neq 0$ ) stressing, improvement of BTI degradation for MOSFETs with HfO<sub>2</sub> dielectric has been observed, and this improvement increases with increasing stress frequency [52]. It was thus concluded that the BTI should not be the "show-stopper" in realizing HfO<sub>2</sub> transistors for digital IC applications [52]. A model accounting for carrier trapping/de-trapping process and generation of new traps in HfO<sub>2</sub> dielectric under stress has been proposed to explain the frequency-dependant BTI degradation phenomena.

### 1.4.2 Research Status of Some Potential High-K Gate Dielectrics

Most of the high-K gate dielectric candidates studied up to date are the metal oxide, and Table 1.3 complies the materials properties for several potential high-k gate dielectric candidates.

| Dielectric                     | Dielectric<br>constant (K) | Gap energy<br>(eV) | Electron barrier<br>to Si (eV) |

|--------------------------------|----------------------------|--------------------|--------------------------------|

| SiO <sub>2</sub>               | 3.9                        | 8.8                | 3.15                           |

| Si <sub>3</sub> N <sub>4</sub> | 7.8                        | 5.1                | 2.1                            |

| $Al_2O_3$                      | 8 - 11.5                   | ~6.5 - 8.7         | ~2.4 - 2.8                     |

| ZrO <sub>2</sub>               | 22 - 28                    | ~5.5 - 5.8         | ~1.4 - 2                       |

| ZrSiO <sub>4</sub>             | 10 – 12                    | ~6                 | 1.5                            |

| HfO <sub>2</sub>               | 25 - 30                    | ~5.25 - 5.7        | ~1.5 - 1.9                     |

| HfSiO <sub>4</sub>             | ~10                        | ~6                 | 1.5                            |

| TiO <sub>2</sub>               | ~80                        | 3.5                | ~1.2                           |

| Ta <sub>2</sub> O <sub>5</sub> | ~25                        | ~5                 | ~0.3 - 0.5                     |

**Table 1.3**. Band offsets and dielectric constants for different high-K gate dielectric candidates (including  $SiO_2$  and  $Si_3N_4$ ) [17, 22, 28]

High-K dielectric properties and quality is critically determined by the method it is deposited [29]. For sputter physical vapor deposition (PVD), surface damages and hence the interface states will be the inherent concerns. On the other hand, chemical vapor deposition (CVD) is proven to be a reliable technique for obtaining the uniform coverage over complicated device topologies. Several most promising CVD metal oxide high-K gate dielectrics will be discussed below.

Alumina  $(Al_2O_3)$  belongs to group IIIA metal oxide, and its characteristics are very similar to SiO<sub>2</sub>. It has many favorable properties such as high gap energy value, thermodynamic stability on Si up to high temperature annealing, and remains amorphous under the conditions of interest. However, due to its relatively low k values (only  $8\sim11$ ), alumina is only considered as the short-term solution for industry's needs. For Al<sub>2</sub>O<sub>3</sub> deposited via atomic layer chemical vapor deposition (ALCVD) [30], severe dopant diffusion and the significant negative fixed charges have been demonstrated, therefore the carrier mobility at the dielectric/Si interface was significantly reduced.

TiO<sub>2</sub>, ZrO<sub>2</sub> and HfO<sub>2</sub> belong to group IVB metal oxides. TiO<sub>2</sub> has a high dielectric constant (80~110) and has been studied for both the memory and gate dielectric application. CVD TiO<sub>2</sub> is not stable on Si during deposition, and it will crystallize at ~ 400 °C [31]. These properties rule out TiO<sub>2</sub> application as the gate dielectric. Zirconium oxide, hafnium oxide and their silicates and aluminates also received considerable attention [32-36]. Degradation of the chemical properties for  $ZrO_2$  as compared to HfO<sub>2</sub> might be due to the interaction of the polysilicon gate electrode with the  $ZrO_2$  [37], as well as the interaction of  $ZrO_2$  with the lower silicon interface leading to silicide formation. For CVD ZrO<sub>2</sub> deposited on Si substrate, during annealing in UHV ambient, interfacial SiO<sub>x</sub> triggers the ZrSi<sub>2</sub> and Zr formation at the channel interface, which are decomposed from ZrO<sub>2</sub> [38]. HfO<sub>2</sub> film has emerged as one of the most promising gate dielectric candidates due to its high dielectric constant, large energy gap, superior thermal stability with poly-Si and its compatibility with conventional CMOS process [32-34]. On the other hand, the zirconium or hafnium silicates and aluminates have been demonstrated to have better thermal stability (higher crystallization temperature, and lower oxygen diffusivity) compared to that of the pure oxide. Despite of their lower dielectric constants compared to the value of the pure oxide, (see table 1.3), they seem to be adequate to meet the transistor performance goals [22].

#### 1.4.3 Process Issues for High-K Gate Stack Fabrication

Not only the specific deposition process, but the pre-deposition surface cleans and the post-deposition treatment, are critical in controlling the high-K films structure (crystallinity, micro-structure, and stoichiometry etc.) and, in turn, their electrical properties such as the EOT, gate leakage current and the reliability characteristics.

The study on pre- high-K deposition clean include standard RCA clean (SC1/SC2), HF last, ozone (O<sub>3</sub>), etc. A high quality chemical oxide at Si surface would be grown with the aid of O<sub>3</sub> clean. It was found that the O<sub>3</sub> clean led to a smoother high-K film subsequently deposited by ALD compared to RCA or HF last pre-gate clean [7], though the interfacial chemical oxide would cause the EOT increase. It is observed that a post high-K deposition anneal (PDA) in N<sub>2</sub> at mild temperature (600°C-700°C) is helpful to improve the high-K quality and reduce the leakage current for a given film physical thickness [32-33]. However, the trace amount of oxygen in an inert ambient anneal during high-K PDA can be sufficient to cause the low-K interfacial layer growth at the high-K/Si interface [39-40]. An NH<sub>3</sub> anneal prior to high-K PDA [41]. However, the interface defects caused by the N effect might degrade the device electrical properties [41].

### 1.5. Metal Gate Technology

### 1.5.1. Limitation of Poly-Si Electrodes for Nano-Meter CMOS Devices

#### **1.5.1.1 Poly-Silicon Depletion Effect**

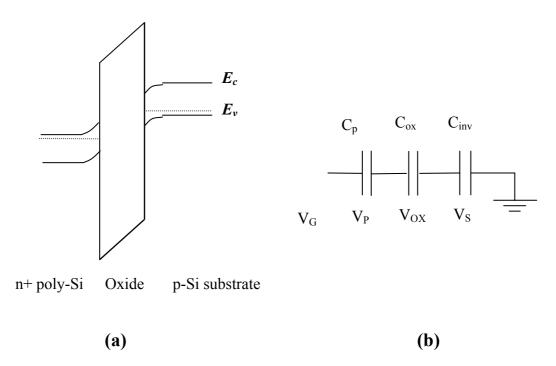

The poly-Si depletion effect occurs when a MOS device with a poly-Si gate electrode is biased into depletion or inversion region. Fig. 1.5 illustrates poly-Si depletion effect for a n+ poly-Si n-MOS device. When a positive bias is applied at the gate, a depletion layer with a finite thickness is formed at the poly-Si gate side at the poly-Si/oxide interface, associating with the non-negligible band bending in the poly-Si gate.

**Fig. 1.5.** (a) The energy band diagram of a N-MOS device showing the poly-Si gate depletion effect; (b)  $C_p$ ,  $C_{ox}$ , and  $C_{inv}$  represent the capacitance from the poly depletion layer, gate oxide and substrate inversion layer, respectively.

From an equivalent circuit diagram shown in Fig. 1.5(b), the poly-Si depletion capacitance  $C_P$  is series with the gate oxide capacitance, leading to a reduction of the gate oxide capacitance in inversion. This is equivalent to an increase of the effective

oxide thickness. As a result, a smaller inversion charge density is expected, and hence a reduction of the drive current for the MOSFET device. With the aggressive scaling of the gate dielectric thickness, the poly-Si depletion effect becomes much more significant [2]. An increase of gate dielectric EOT of 5-6 Å due to poly-Si depletion effect is expected, as compared to EOT requirement (< 1 nm) in nanometer scale CMOS.

### 1.5.1.2 Gate Electrode Resistivity and Dopant Penetration Effect

| Table 1.4. Scaling parameters on | gate electrode from ITRS-2001 [ | [2] |  |

|----------------------------------|---------------------------------|-----|--|

|                                  |                                 |     |  |

| Year                                                    | 2004  | 2007  | 2010  | 2013  | 2016 |

|---------------------------------------------------------|-------|-------|-------|-------|------|

| Technology node                                         | 90    | 65    | 45    | 32    | 22   |

| Gate electrode thickness (nm)                           | 37-74 | 25-50 | 18-36 | 13-26 | 9-18 |

| Average gate electrode sheet resistance $(\Omega/\Box)$ | 5     | 5     | 5     | 6     | 7    |

Tale 1.4 summarizes that scaling parameters on gate electrode, based on ITRS-2002. It is seen that the gate electrode resistivity is required to be scaled with the technology node. This is particularly important for MOS devices in RF application. One way to minimize the high gate resistance, as well as the poly depletion effect associated with poly-Si gate, the active dopant density in the poly-Si gate should be increased. However, it is difficult to get electrically active doping densities above  $10^{20}$  cm<sup>-3</sup> due to the limitation of the dopants solubility in the poly-Si films, especially for p+ poly-Si doped with boron [49]. Besides, for p-MOSFETs, the boron

penetration p+ poly-Si to the channel region induces threshold voltage shift and other reliability concerns for the transistors, as addressed in section 1.2.3 of this chapter.

#### **1.5.1.3 Work Function Requirement for Novel MOS Devices**

Work function of the conventional n+ poly-Si / p+ poly-Si is close to the conduction band / valence band edges of Si, and this is preferred for the optimal design of bulk n- / p-MOSFETs, respectively [53] because of the requirements on the threshold voltages and the need to use heavy dopants to control short-channel effects. However, the fixed work function value for n+ (p+) poly-Si might be adequate for some novel MOS devices. For examples, metal gate with a midgap work function is highly desired for ultra thin body FD-SOI devices to make low channel doping viable, so as to eliminate channel mobility degradation and minimize the V<sub>th</sub> variation [54].

#### 1.5.2. Metal Gate Technology

Metal gate electrodes not only eliminate the gate depletion and dopant penetration issues in CMOS devices, but also greatly reduce the gate sheet resistance. Moreover, the use of a metal gate material makes it possible to choose the work function of the gate and redesign the device for the optimum combination of work function and channel doping. Though metal gates promise superior performance, they pose significant technological challenges. The major challenge for metal gate technology is to identify the appropriate metals with suitable work functions and with sufficient chemical stability, and find a way to integrate the metal into CMOS process. To maintain the acceptable performance advantage, metal gates with work functions near the conduction band and valence band edges of Si are desired for the optimal design of bulk n- and p-MOSFETs, respectively [55]. A simple and direct way is to use two metal gate electrodes (one replaces p+ poly-Si, and the other one replaces n+ poly-Si) with distinct work functions. However, the metal gate electrodes must be thermally and chemically compatible with the underlying gate dielectrics. They must have good adhesion, and they should be controllably patterned. Presently, active research is in progress to identity the suitable metals. The possible candidates include pure metal with high melting temperature  $(T_m)$ , metal alloy, conductive metal oxides, metal silicide, and metal nitride. It is worth noting that by using one material system for the metal electrodes, it is possible to tune the metal work function for either n-MOS or p-MOS by varying the alloy composition or by doping. Such an approach is aimed to reduce the process complexity and cost. RuTa alloy is demonstrated to be able to meet both the requirement of p-MOSFETs (when Ta < 20%) and that of n-MOSFETs (when 40% < Ta < 54%) [56]. By doping nitrogen into the Mo, which is for the p-MOSFET metal electrode, Mo work function could be tuned toward the n-MOSFET required value [57].

Another promising solution is the fully silicidation of poly-Si gates (FUSI process) [58]. The metal silicide work function can be tuned by the doping the poly-Si before silicidation. In addition, FUSI process requires no new etch step, no high temperature post-gate step. The "gate-last" process for metal gate integration (by using replacement gate and damascene process) could avoid the high-temperature annealing of gate stack, however, it significantly increases the process complexity and cost.

### 1.6. Major Achievements in This Thesis

The focus of this thesis is the study of advanced gate stack for future nanometer CMOS device application. In chapter 2, the materials properties of  $(HfO_2)_x(Al_2O_3)_{1-x}$  high-K dielectrics grown by ALD are to be presented, including the energy band alignment to (100) Si substrate and the thermal stability. It is shown that Al 2p, Hf 4f, O 1s core levels high resolution XPS spectra, valence band spectra, and O 1s energy loss spectra all show continuous changes with  $HfO_2$  mole fraction x in  $(HfO_2)_x(Al_2O_3)_{1-x}$ . These data are used to estimate the energy gap  $E_g$  for  $(HfO_2)_x(Al_2O_3)_{1-x}$ , the valence band offset  $\Delta E_v$ , and the conduction band offset  $\Delta E_c$ between  $(HfO_2)_x(Al_2O_3)_{1-x}$  and the (100) Si substrate. Further it will be reported that both the thermal stability and the resistance to oxygen diffusion of HfO<sub>2</sub> are improved by adding Al to form Hf aluminates, and the improvement is closely correlated with the Al percentage in the films. This observation is explained by (i) Al<sub>2</sub>O<sub>3</sub> has much lower oxygen diffusion coefficient than  $HfO_2$  at high temperature; (ii) doping  $HfO_2$  by Al raises the film crystallization temperature of HfO<sub>2</sub> and thus drastically reduces the oxygen diffusion along the grain boundaries during annealing. The difference of IL growth between N<sub>2</sub> (10 torr) and high vacuum (~ 2  $\times$  10<sup>-5</sup> torr) 1000 °C annealing indicates that the active oxygen species from the annealing ambient is the main cause for the IL growth during RTA in N<sub>2</sub>.