# MICROMECHANICAL RESONATOR BASED BANDPASS SIGMA- DELTA MODULATOR

## WANG XIAOFENG

(B. of Eng., Northwestern Polytechnical University)

A THESIS SUBMITTED

FOR THE DEGREE OF MASTER OF ENGINEERING

DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

NATIONAL UNIVERSITY OF SINGAPORE

2003

## Abstract

In modern RF receivers, high-speed and high-resolution ADCs are needed for IF or RF digitization. Bandpass  $\Sigma\Delta$  modulator is seen as a potential candidate to fulfill this requirement. However, the speed of discrete-time bandpass  $\Sigma\Delta$  modulator implemented with switched-capacitor circuit is limited by the settling time of the opamps, while the continuous-time bandpass modulator can operate at much high sampling frequency, but suffers from the degradation of dynamic range due to the low-Q LC or G<sub>m</sub>C resonators.

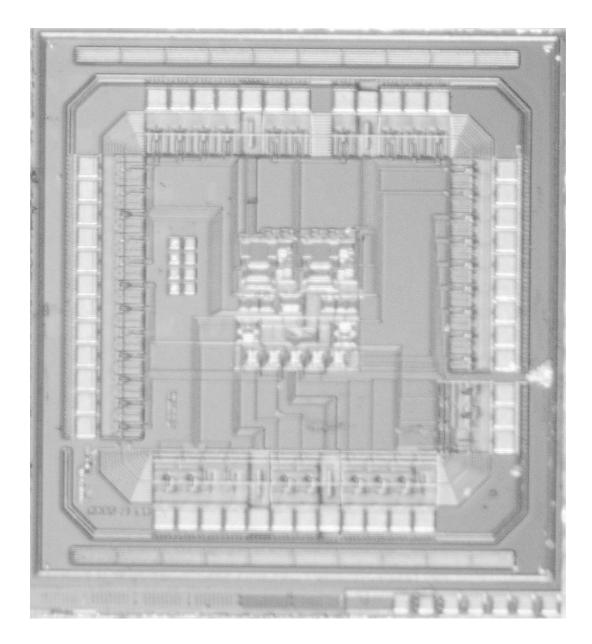

This work is to investigate the possibility of employing micromechanical resonators in bandpass  $\Sigma\Delta$  modulator design. The design of a newly proposed  $2^{nd}$ -order bandpass  $\Sigma\Delta$  modulator based on micromechanical resonator is presented. The micromechanical resonator is used to replace its electronic counterpart for its high Q value. The design is based on pulse-invariant transform and multi-feedback technique. A compensation circuit is proposed to cancel the anti-resonance in the micromechanical resonator in order to obtain the desired transfer function. The proposed modulator is implemented in a 0.6-µm CMOS process with an external clamped-clamped beam micromechanical resonator.

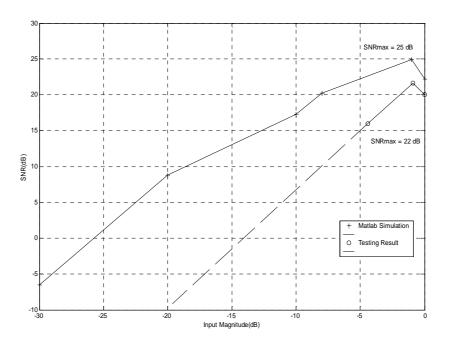

Due to the lack of qualified micromechanical resonator, the testing with the only micromechanical resonator did not give expected results. The test was subsequently carried out with crystal resonators and successfully demonstrated a 2<sup>nd</sup>-order

bandpass  $\Sigma\Delta$  modulator, which proves that the proposed idea is feasible. The test results have shown that when sampled at 4MHz the peak SNR in 200-kHz signal bandwidth is measured to be 22dB while the Matlab simulated value is 25dB. The modulator is also functional at the sampling frequency of 32MHz.

## Acknowledgements

I would like to express my sincere appreciation to my supervisor Professor Xu Yong Ping for his guidance and support of my research in the past two years. I would also like to thank my co-supervisor Professor Tan Leng Seow for admitting me into NUS which makes my research possible. Many thanks go to my co-supervisor Dr. Wang Zhe of the Institute of Microelectronics (IME) for providing me the micromechanical resonators and the opportunity to access the equipment at IME.

I would like to thank Mr. Sun Wai Hoong. He generously shared his S-function programs with me. A numerous discussions with him are also very valuable.

I would also like to thank Mr. Saxon Liw of IME for his generous assistance and support in testing the resonator. He also helped me solve many practical problems.

I would like to express my gratitude to Miss Qian Xinbo, Mr. Su Zhenjiang, and Ms. Xu Lianchun for their help on circuit design and using Cadence. Xinbo also helped me a lot in using test equipment.

I would like to thank Miss Yu Yajun for providing me her past designs as reference. Thanks also go to Mr. Luo Zhenying, Mr. Liang Yunfeng, and Mr. Zhou Xiangdong for their advices on circuit design, and Mr. Francis Boey for his support on equipment and electronic components.

Very special thanks go to all my friends at the Laboratory of Signal Processing and VLSI Design for making my years in NUS a wonderful experience.

I would like to thank the National University of Singapore for providing me with the financial support.

Finally, I would like to thank my parents and my grandparents for their consistent support.

## **Table of Contents**

| ABSTRACT                                                       | II     |

|----------------------------------------------------------------|--------|

| ACKNOWLEDGEMENTS                                               | IV     |

| TABLE OF CONTENTS                                              | VI     |

| LIST OF FIGURES                                                | VIII   |

| LIST OF TABLES                                                 | XI     |

| CHAPTER 1 INTRODUCTION                                         | 1      |

| 1.1 MOTIVATION                                                 |        |

| 1.2 THESIS OUTLINE                                             |        |

| CHAPTER 2 SIGMA-DELTA MODULATION                               | 6      |

| 2.1 NYQUIST-RATE A/D CONVERTER                                 | 6      |

| 2.1.1 Anti-aliasing                                            |        |

| 2.1.2 Sampling                                                 | 7      |

| 2.1.3 Quantization                                             | 7      |

| 2.2 OVERSAMPLING A/D CONVERTER                                 | 10     |

| 2.3 SIGMA-DELTA MODULATION                                     | 11     |

| 2.3.1 The Noise-shaping Technique                              | 12     |

| 2.3.2 High-order Sigma-Delta Modulation                        | 17     |

| 2.3.3 Multi-bit Quantization                                   |        |

| 2.4 CONTINUOUS-TIME BANDPASS SIGMA-DELTA MODULATOR             | 19     |

| 2.4.1 Discrete-time and Continuous-time Sigma-Delta Modulators | 19     |

| 2.4.2 Design Methodology of Continuous-time Bandpass Sigma-De  |        |

| Modulator                                                      |        |

| 2.4.3 Review of Continuous-time Bandpass Sigma-Delta Modulator |        |

| 2.4.4 Micromechanical Resonators                               | 24     |

| CHAPTER 3 MICROMECHANICAL RESONATORS                           | 27     |

| 3.1 MEMS TECHNOLOGY                                            | 27     |

| 3.2 STRUCTURES OF MICROMECHANICAL RESONATORS                   |        |

| 3.3 RESONATOR MODEL                                            | 32     |

| 3.4 Sensing Circuits                                           | 35     |

| 3.5 MICROMECHANICAL RESONATOR VERSUS LC AND $G_MC$ Resonat     | 'ORS36 |

| CHAPTER 4 BANDPASS SIGMA-DELTA MODULATOR BASE                  |        |

| MICROMECHANICAL RESONATOR                                      |        |

| 4.1 Design Methodology                                         | 37     |

| 4.2 ANTI-RESONANCE AND ITS CANCELLATION                        | 40     |

| 4.3 MODULATOR ARCHITECTURE                                     | 43     |

| 4.4         | 4 PERFORMANCE OF THE PROPOSED SIGMA-DELTA MODULATOR |                                              |    |  |

|-------------|-----------------------------------------------------|----------------------------------------------|----|--|

| 4.5         | CIRCU                                               | IT IMPLEMENTATION                            | 47 |  |

| CHAP        | TER 5                                               | CIRCUIT LEVEL DESIGN                         | 49 |  |

| 5.1         | FUNC                                                | fion Blocks                                  | 49 |  |

| 5.2         | <b>OPER</b>                                         | ATIONAL AMPLIFIER                            | 50 |  |

| 5.3         | COMP                                                | ARATOR                                       | 53 |  |

| 5.4         | ONE-E                                               | BIT DACS                                     | 55 |  |

| 5.5         | VOLTA                                               | AGE LEVEL SHIFTER                            | 56 |  |

| 5.6         | RESON                                               | NATOR INTERFACE CIRCUITS                     | 58 |  |

| 5.7         | PERFC                                               | RMANCE OF THE BANDPASS SIGMA-DELTA MODULATOR | 60 |  |

| 5.8         | LAYO                                                | UT DESIGN AND POST-LAYOUT SIMULATION         | 62 |  |

| СНАР        | TER 6                                               | TESTING                                      | 65 |  |

| 6.1         | TESTI                                               | NG SETUP                                     | 65 |  |

| 6.2         | TESTI                                               | NG RESULT                                    | 67 |  |

| 6.          | 2.1 Mo                                              | dulator with Micromechanical Resonator       | 67 |  |

| 6.          | 2.2 Mo                                              | dulator with Crystal Resonators              | 67 |  |

| 6.          | 2.3 Sign                                            | nal-to-Noise Ratio                           | 72 |  |

| 6.3         | DISCU                                               | SSION                                        | 73 |  |

| СНАР        | TER 7                                               | CONCLUSIONS AND FUTURE WORK                  | 75 |  |

| 7.1         | CONC                                                | LUSION                                       | 75 |  |

| 7.2         | Futui                                               | RE WORK                                      | 76 |  |

| REFE        | RENCES                                              |                                              | 77 |  |

| APPE        | NDIX A                                              | MATLAB PROGRAMS                              | 82 |  |

| A.1         | Progi                                               | ram for Pulse-invariant Transform            |    |  |

| A.2         | Progi                                               | RAM FOR POWER SPECTRUM ESTIMATION            |    |  |

| A.3         | Progi                                               | RAM FOR SNR CALCULATION                      | 86 |  |

| APPE        | NDIX B                                              | SIMULINK MODELS                              |    |  |

| <b>B</b> .1 | Simul                                               | INK MODEL FOR RETURN-TO-ZERO DAC             |    |  |

| B.2         |                                                     | INK MODEL FOR HALF-RETURN-TO-ZERO DAC        |    |  |

| APPE        | NDIX C                                              | CHIP LAYOUT                                  | 92 |  |

| APPE        | NDIX D                                              | CHIP PHOTOGRAPH                              |    |  |

## **List of Figures**

| Figure 1.    | Superheterodyne receiver with dual IF and baseband ADC.                            | .2 |

|--------------|------------------------------------------------------------------------------------|----|

| Figure 2.    | Direct-conversion receiver.                                                        | .2 |

| Figure 3.    | Direct-IF conversion receiver                                                      | .3 |

| Figure 4.    | The operation of Nyquist-rate A/D converter.                                       | .6 |

| Figure 5.    | A/D conversion process.                                                            | .8 |

| Figure 6.    | Linear model for quantization.                                                     | .8 |

| Figure 7.    | $\Sigma\Delta$ modulator                                                           | 1  |

| Figure 8.    | Linear model of $\Sigma\Delta$ modulator                                           | 2  |

| Figure 9.    | Lowpass $\Sigma\Delta$ modulator.                                                  | 3  |

| Figure 10.   | Gain of NTF and STF of the lowpass $\Sigma\Delta$ modulator                        | 3  |

| Figure 11.   | Simulated output spectrum.                                                         | 4  |

| Figure 12.   | Structure of baseband $\Sigma\Delta$ A/D converter                                 | 5  |

| Figure 13.   | Bandpass $\Sigma\Delta$ modulator.                                                 | 5  |

| Figure 14.   | Magnitude responses of NTF and STF of a $2^{nd}$ -order bandpass $\Sigma$          | Δ  |

| modulator.   | 16                                                                                 |    |

| Figure 15.   | Output power spectrum of a $2^{nd}$ -order bandpass $\Sigma\Delta$ modulator       | 6  |

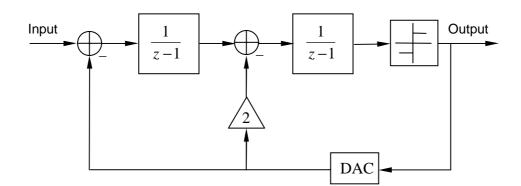

| Figure 16.   | $2^{nd}$ -order single-stage lowpass $\Sigma\Delta$ modulator                      | 8  |

| Figure 17.   | $2^{nd}$ -order lowpass MASH $\Sigma\Delta$ modulator                              |    |

| Figure 18.   | Equivalence between continuous and discrete-time modulators                        |    |

| Figure 19.   | Forward loops of (a) continuous-time and (b) discrete-time $\Sigma$                | Δ  |

| modulators.  | 21                                                                                 |    |

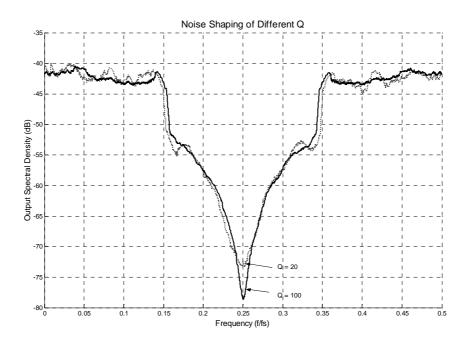

| Figure 20.   | Noise shapes of the resonators of different Q.                                     | 25 |

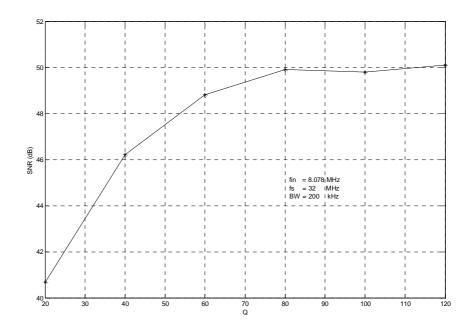

| Figure 21.   | SNR degradation due to Q.                                                          | 25 |

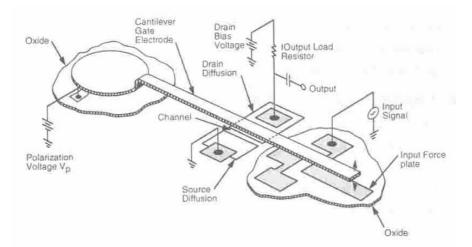

| Figure 22.   | Cantilever-beam resonator.                                                         | 29 |

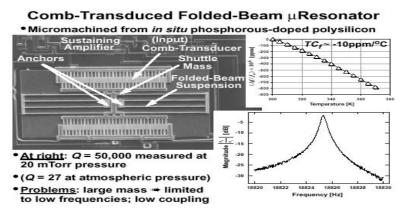

| Figure 23.   | Comb-transduced resonator                                                          | 30 |

| Figure 24.   | Clamped-clamped beam resonator                                                     | 30 |

| Figure 25.   | Free-free beam resonator                                                           | 31 |

| Figure 26.   | Disk resonator                                                                     | 31 |

| Figure 27.   | Equivalent circuit of the micromechanical resonator.                               | 32 |

| Figure 28.   | Equivalent circuit with resistive load                                             | 32 |

| Figure 29.   | Simulated frequency response of the resonator (With 10 tim                         | es |

| amplificatio | n). 34                                                                             |    |

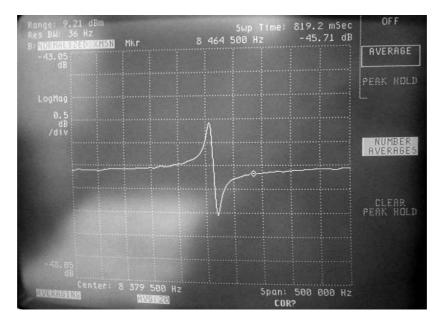

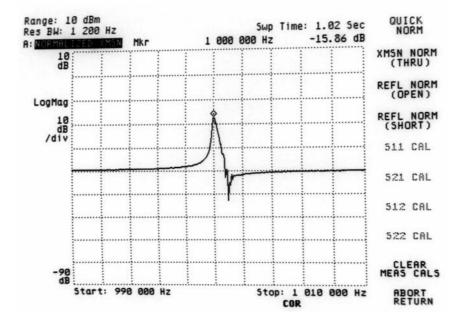

| Figure 30.   | Measured frequency response of the micromechanical resonator                       | 34 |

| Figure 31.   | Resistive sensing circuit.                                                         | 35 |

| Figure 32.   | Trans-impedance sensing circuit.                                                   | 35 |

| Figure 33.   | Equivalence between discrete-time and continuous-time modulators3                  | 38 |

| Figure 34.   | Broken loops of (a) continuous-time and (b) discrete-time $\Sigma\Delta$ modulator |    |

|              | 38                                                                                 |    |

| Figure 35.   | Continuous-time modulator with two feedbacks                                       | 39 |

| Figure 36.   | DAC waveforms                                                                |

|--------------|------------------------------------------------------------------------------|

| Figure 37.   | Linear model of $\Sigma\Delta$ modulator                                     |

| Figure 38.   | Anti-resonance cancellation scheme                                           |

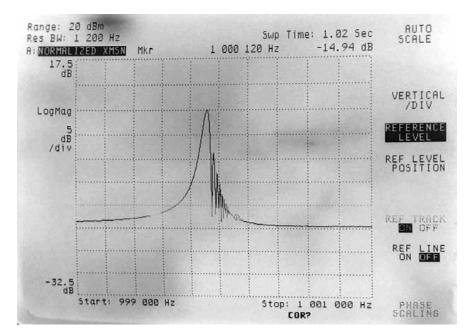

| Figure 39    | Frequency response of the resonator with anti-resonance cancellation42       |

| Figure 40.   | Frequency response of the micromechanical resonator with                     |

| anti-resonar | ace cancellation                                                             |

| Figure 41.   | Frequency response of the micromechanical resonator with imperfect           |

| anti-resonar | ace cancellation                                                             |

| Figure 42.   | Proposed micromechanical resonator based bandpass $\Sigma\Delta$ modulator44 |

| Figure 43.   | Simulink model of the continuous-time modulator45                            |

| Figure 44.   | Output power spectrum (Matlab simulation)45                                  |

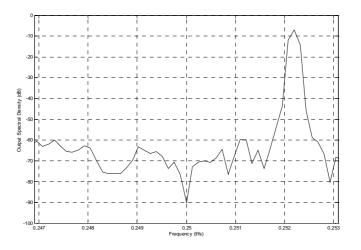

| Figure 45.   | In-band power spectrum (OSR = 80, Matlab simulation)46                       |

| Figure 46.   | SNR against Input magnitude (Matlab simulation)47                            |

| Figure 47.   | Circuit structure of the modulator47                                         |

| Figure 48.   | Modulator circuit structure                                                  |

| Figure 49.   | OTA schematic                                                                |

| Figure 50.   | Basing circuit schematic                                                     |

| Figure 51.   | Frequency response of the OTA                                                |

| Figure 52.   | Schematic of the differential comparator                                     |

| Figure 53.   | Transient response of the differential comparator                            |

| Figure 54.   | Schematic of the DAC                                                         |

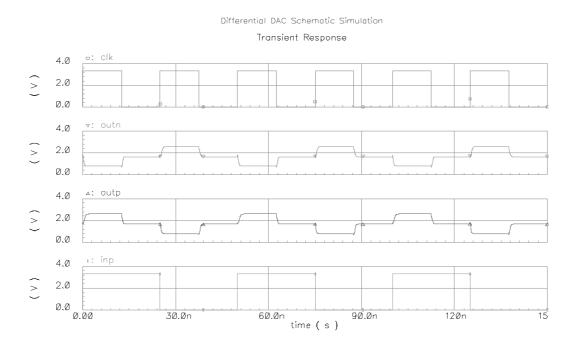

| Figure 55.   | Transient simulation results of the return-to-zero DAC                       |

| Figure 56.   | Schematic of the differential voltage level shifter                          |

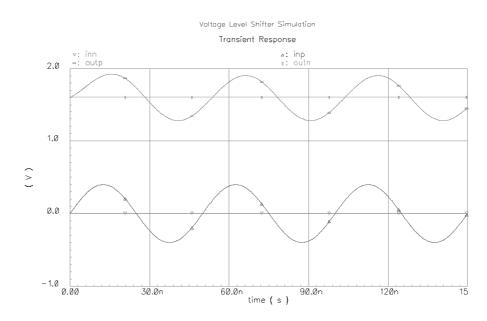

| Figure 57.   | VLS transient response                                                       |

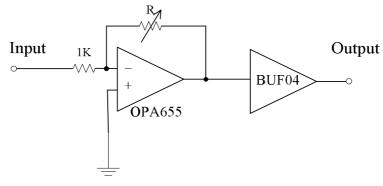

| Figure 58.   | Amplification circuit                                                        |

| Figure 59.   | Cancellation circuit                                                         |

| Figure 60.   | Frequency response of the micromechanical resonator                          |

| Figure 61.   | Frequency response of the resonator with anti-resonance cancellation59       |

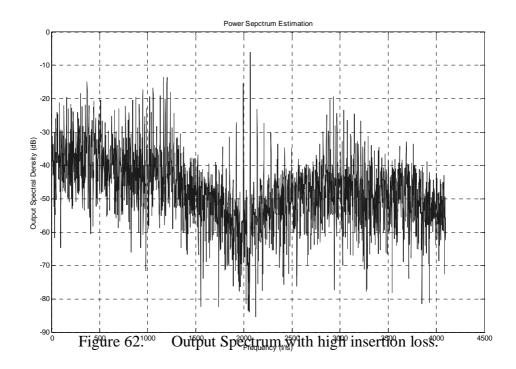

| Figure 62.   | Output Spectrum with high insertion loss                                     |

| Figure 63.   | Output power spectrum at $fs = 32$ MHz61                                     |

| Figure 64.   | In-band output spectrum at $fs = 32MHz$ 61                                   |

| Figure 65.   | SNR against input magnitude at $fs = 32MHz$                                  |

| Figure 66.   | Layout floor plan                                                            |

| Figure 67.   | Output power spectrum at $fs = 32$ MHz from post-layout simulation64         |

| Figure 68.   | In-band output power spectrum at $fs = 32$ MHz from post-layout              |

| simulation.  | 64                                                                           |

| Figure 69.   | Test setup                                                                   |

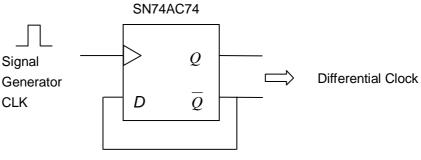

| Figure 70.   | Differential clock generation circuit                                        |

| Figure 71.   | Off-chip bias circuit                                                        |

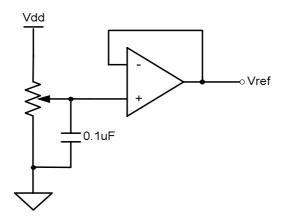

| Figure 72.   | Reference voltage generation circuit                                         |

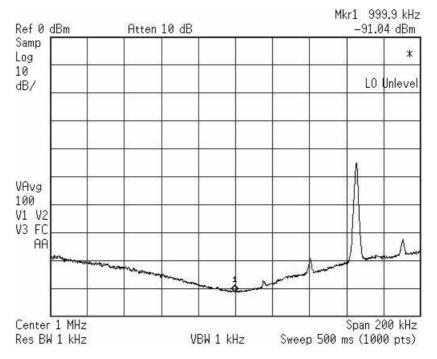

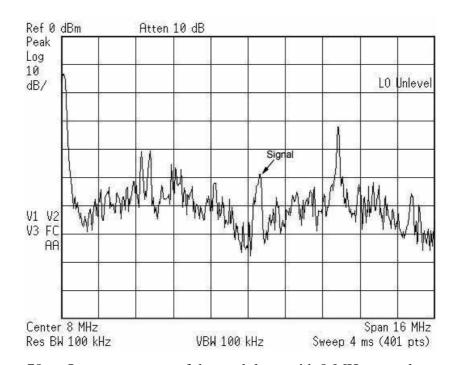

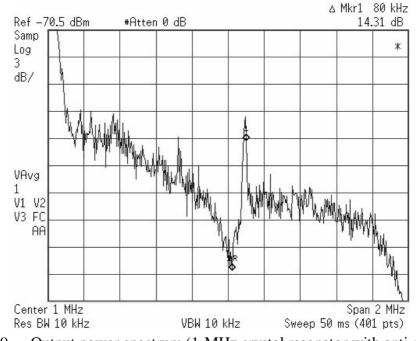

| Figure 73.   | Frequency response of the crystal resonator with resonant frequency of       |

| 1MHz.        | 68                                                                           |

| Figure 74.   | Frequency response of the crystal resonator with resonant frequency of       |

| 8MHz.        | 68                                                                           |

## **List of Tables**

| Table 1. | Continuous-time bandpass $\Sigma\Delta$ modulators published | 24 |

|----------|--------------------------------------------------------------|----|

| Table 2. | Design specifications.                                       | 49 |

| Table 3. | OTA transistor sizes                                         | 51 |

| Table 4. | Transistor sizes of the biasing circuit                      | 52 |

| Table 5. | Bias voltages                                                |    |

| Table 6. | Transistor sizes of the differential comparator              | 54 |

| Table 7. | Transistor sizes of the DAC.                                 | 55 |

| Table 8. | VLS transistor sizes.                                        | 57 |

## **Chapter 1 Introduction**

One of the major technical successes in the 20<sup>th</sup> century is the development of wireless communication systems which origins in 1980s. It is estimated there are 440 million wireless subscribers worldwide by the end of year 2002. The wireless equipment industry worldwide is estimated at \$45 billion annually. The number of subscribers is expected to double in several years. Driven by the great demand of personal communication systems, the wireless communication technology has developed rapidly to provide more and better services. As a key part in wireless communication system, the Radio Frequency (RF) receiver has attracted great research attention.

### **1.1 Motivation**

In the RF receiver design, most of the efforts are made to improve the integration and flexibility. High-level integration will increase the system reliability and reduce its cost, size and power consumption. More flexibility, on the other hand, will make the receiver compatible to multiple standards.

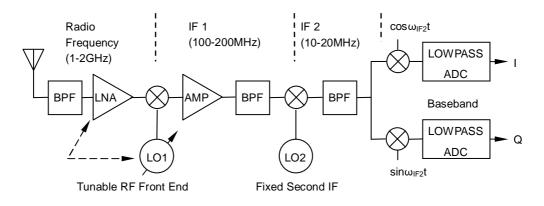

Currently, most of the RF receivers are implemented in the super-heterodyne architecture with baseband ADC (Analog-to-Digital Converter). The block diagram of a dual-IF super-heterodyne receiver with baseband ADC is shown in Figure 1 [Carl86].

The RF signal is filtered and mixed through two IF stages, then demodulated and converted into digital domain with baseband ADC. The superheterodyne architecture

has good sensitivity and selectivity, but it is complex, requires precise analog components and has many off-chip filters, so it is difficult to realize high integration and good flexibility.

Figure 1. Superheterodyne receiver with dual IF and baseband ADC.

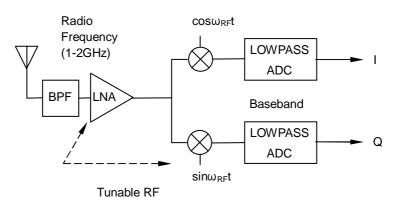

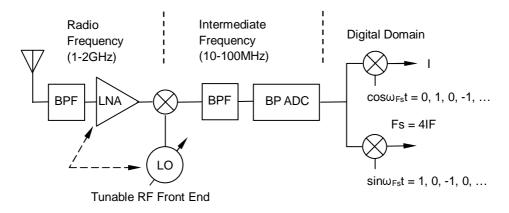

The research on new receiver architectures is carried out in two directions [Galt02]: one is to convert the RF signal directly to baseband or low-IF and use baseband ADC to convert the signal into digital domain. Such architectures are called zero-IF or low-IF direct conversion. Another direction is to use bandpass ADC to convert the signal into digital domain at IF, or even at RF frequency, such architectures are called superheterodyne receiver with bandpass ADC or direct-IF receiver [Galt02]. The block diagrams of direct-conversion receiver and bandpass ADC based direct-IF conversion receiver are shown in Figure 2 [Galt02] and Figure 3 [Galt02], respectively.

Figure 2. Direct-conversion receiver.

Figure 3. Direct-IF conversion receiver.

In the direct-conversion receiver, the RF signal is directly translated down to the baseband, where demodulation and A/D conversion are done. The direct-conversion relaxes the selectivity requirements on RF filters and eliminates all IF analog components, allows a highly integrated, low-cost and low-power realization of RF receivers [Abid95]. However, direct-conversion receivers have a severe DC offset problem that will affect the circuit biasing conditions. 1/f noise also degrades the dynamic range of the receiver.

In the bandpass ADC based superheterodyne receiver, the signal is converted to digital domain at IF. Compared with conventional superheterodyne receiver, the demodulation and channel selection in this architecture are done in digital domain, which alleviates the precision requirements on analog components. The channel selection is programmable so the flexibility is increased. The integration is also improved since the system structure is simplified. Moreover, compared with direct-conversion, the problems of 1/f noise and DC offset are avoided with the technique of direct IF digitization. The architecture is suitable for many RF receiver applications, such as, software-controlled digital radios. However, this architecture

requires high-frequency and high-resolution bandpass A/D converters. Bandpass Sigma-Delta ( $\Sigma\Delta$ ) ADC is seen as a good candidate in this application, since it can be realized in high resolution with coarse analog circuitry.

Currently, most of the bandpass  $\Sigma\Delta$  ADCs reported are implemented using switched-capacitor circuits [Sing95] [Baza98]. Such converters have robust performance, but only at low frequencies. When their sampling frequency increases, the non-idealities of the circuit (such as the finite gain and settling error of the op-amp) degrade the performance. Continuous-time bandpass  $\Sigma\Delta$  ADCs, on the other hand, can operate at high frequencies. But their performance is limited by the low Q factor and nonlinearity of the on-chip resonators [Shoa95] [Gao98].

In the past decades, the rapid development in silicon micromachining technology has led to the realization of micromechanical resonators (also called as µresonator) on silicon. Micromachining process can be made compatible with CMOS technology [Bust98] [Nguy01]. Therefore, it is possible to integrate micromechanical devices with CMOS circuit on a single chip. Different types of micromechanical resonators have been reported [Nguy01]. The major advantage of the micromechanical resonator is its high Q value (typically greater than 1000), which cannot be matched by its electronic counterpart, especially at high frequencies. In bandpass  $\Sigma\Delta$  modulators, high-Q resonator provides better noise shaping and hence better performance. Therefore micromechanical resonator is a good candidate to replace conventional LC and G<sub>m</sub>C resonators in high-speed bandpass  $\Sigma\Delta$  ADC design.

The research carried out in this thesis is to investigate the possibility of realizing

bandpass  $\Sigma\Delta$  modulator using micromechanical resonator. The intended application is IF digitization in modern RF receivers.

## **1.2Thesis Outline**

Chapter 2 of the thesis introduces the fundamentals of  $\Sigma\Delta$  modulation and reviews the previous work on continuous-time bandpass  $\Sigma\Delta$  modulator. Chapter 3 introduces micromechanical resonators. Chapter 4 describes system-level design of the proposed modulator. Chapter 5 deals with circuit-level implementation. Chapter 6 presents the testing results and Chapter 7 summarizes this research and suggests the future work.

## **Chapter 2 Sigma-Delta Modulation**

According to the relationship between sampling frequency and signal bandwidth, A/D converters can be categorized into Nyquist-rate and Oversampling A/D converters.  $\Sigma\Delta$  A/D converters belong to oversampling A/D converter.

This chapter reviews the fundamentals of Nyquist-rate A/D converter. The theory of oversampling A/D conversion and different modulator structures are then introduced. The previous work on continuous-time bandpass  $\Sigma\Delta$  modulator is reviewed and their limitations are analyzed. Finally the idea of micromechanical resonator based continuous-time bandpass  $\Sigma\Delta$  modulator is proposed.

### 2.1Nyquist-rate A/D Converter

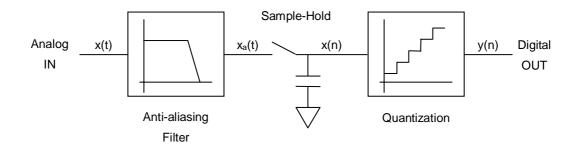

A/D conversion is a process of sampling in time and quantization in magnitude on an analog signal. The process of conversion can be divided into anti-aliasing filtering, sampling and holding, and quantization. The operation is shown in Figure 4.

Figure 4. The operation of Nyquist-rate A/D converter.

#### 2.1.1 Anti-aliasing

The analog signal must pass through a lowpass anti-aliasing filter to remove the signal components which are above 1/2 of the sampling frequency. Otherwise, high frequency components will alias into the baseband upon sampling and will corrupt the signal of interest.

#### 2.1.2 Sampling

From the Nyquist sampling theorem [Oppe89], if the sampling frequency is higher than two times of the signal bandwidth, there is no loss of information or aliasing upon sampling. The sampling frequency which is two times of the signal bandwidth is called Nyquist sampling rate. Generally, in real applications, to alleviate the constraints on anti-aliasing filters, sampling frequency is chosen to be higher than the Nyquist sampling rate. If the sampling-rate is chosen at or slightly higher than the Nyquist rate (1.5 to 10 times [John97]) and the digital output rate equals the sampling rate, the A/D converter is called Nyquist-rate A/D converter. Otherwise, if the sampling rate is much higher than the Nyquist rate (typically 20 to 512 times [John97]) and digital filter is used to decimate the high-rate bit stream to Nyquist rate and remove the out-of-band quantization noise, the A/D converter is called oversampling A/D converter.

#### 2.1.3 Quantization

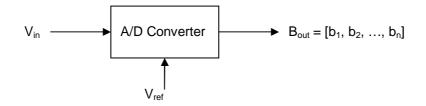

When the data is sampled and held, it is converted to digital value by a quantizer. This process is called quantization. Consider the block diagram of an N-bit A/D converter shown in Figure 5 [John97], where  $B_{out}$  is the digital output word, while  $V_{in}$  is the analog input signal and  $V_{ref}$  is the reference signal.  $b_1$  and  $b_n$  represent the most significant bit (MSB) and least significant bit (LSB), respectively.

Figure 5. A/D conversion process.

$$V_{ref}(b_1 2^{-1} + b_2 2^{-2} + \dots + b_n 2^{-n}) = V_{in} + e$$

(1)

where  $-\frac{1}{2}V_{LSB} \le e \le \frac{1}{2}V_{LSB}$ , *e* is quantization error. Because the quantization error is non-linear and signal dependent, it's difficult to analyze it. To simplify the analysis, the quantization error is often approximated to an additive white noise and is analyzed with statistical methods. Such an assumption is valid if the following conditions are satisfied [Benn48] [Widr56]:

- 1) The input signal never overloads the quantizer.

- 2) The quantizer has a large number of quantization levels.

- 3) The input signal is active over many quantization levels, and

- 4) The joint probability density of any two quantizer input samples is smooth.

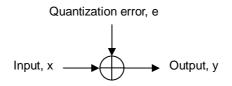

With the white noise assumption, the non-linear quantizer can be modeled as a linear system shown in Figure 6.

Figure 6. Linear model for quantization.

The output y is a combination of the input x and uncorrelated white quantization noise e:

$$y = x + e. \tag{2}$$

Since the quantization error is correlated with input signal, this white noise assumption is never exact, although the correlation is often too complex to be expressed analytically. Nevertheless, this model can be used to analyze the performance of a quantizer and it gives reasonable predictions in most cases.

With the above assumption, if the quantization step is defined as  $\Delta$ , the power of quantization error can be expressed as [John97]:

$$e^{2} = \frac{1}{\Delta} \int_{-\frac{\Delta}{2}}^{\frac{\Delta}{2}} e^{2} de = \frac{\Delta^{2}}{12}.$$

(3)

With a sampling frequency of  $f_s$ , the quantization noise will fold into the band of  $[0, f_s/2]$ . The spectral density of the quantization noise sampled is given by

$$E(f) = \sqrt{\frac{e^2}{f_s/2}} = e\sqrt{\frac{2}{f_s}}.$$

(4)

For a sinusoidal input signal with a full-scale magnitude of  $V_{ref}$ , the ac power of the input signal is  $V_{ref}^2/8$ . For  $2^N >> 1$ ,

$$1LSB = \frac{V_{ref}}{2^N - 1} \approx \frac{V_{ref}}{2^N} = \Delta$$

(5)

The SNR (Signal-to-Noise Ratio), which is defined as the ratio of signal power against the power of in-band noise can be obtained:

$$SNR = 10\log_{10}\left(\frac{V_{ref}^{2}/8}{\Delta^{2}/12}\right) = 6.02N + 1.76dB$$

(6)

where, N is the bit number of the quantizer.

### 2.2Oversampling A/D Converter

Oversampling A/D converters are sampled at a frequency much higher than the Nyquist rate. Compared with Nyquist-rate A/D converter, oversampling A/D converter can achieve high resolution with relatively coarse analog circuits. Since the sampling frequency is much higher than Nyquist rate, the constraints on anti-aliasing filter is alleviated. The sharp cut-off filter is not necessary which makes it possible to implement the filter on-chip. Another advantage of oversampling A/D converter is that the sample-hold stage is generally not required.

We define the Oversampling Ratio (OSR) as the sampling frequency over the Nyquist-rate. If the input signal bandwidth is  $[0, f_B]$ ,

$$OSR = f_s / 2f_B.$$

<sup>(7)</sup>

For bandpass oversampling ADC, OSR is defined as the sampling frequency over two times of the bandwidth,

$$OSR = f_s / 2BW . \tag{8}$$

The spectral density of the quantization noise after sampling is shown in Eq. (4) and the in-band noise can be calculated:

$$n_{ib} = \int_0^{f_B} E^2(f) df = e^2 \frac{2f_B}{f_s}.$$

(9)

For a Nyquist-rate ADC,  $f_s=2f_B$ , thus  $n_{ib}=e^2$ .

For an oversampling ADC,

$$n_{ib} = e^2 \frac{2f_B}{f_s} = \frac{e^2}{OSR} = \frac{\Delta^2}{12OSR}.$$

(10)

From the Eq. (10), it can be seen that the in-band noise can be reduced if OSR is increased. For every doubling of OSR, the in-band noise can be reduced by 3dB, which is equivalent to a half bit.

However, this SNR improvement is very limited. To further improve the in-band SNR, another technique called noise-shaping can be applied, which shapes the quantization noise out of the band of interest. The oversampling A/D converter that uses the noise-shaping technique is called  $\Sigma\Delta$  A/D converter.

### 2.3Sigma-Delta Modulation

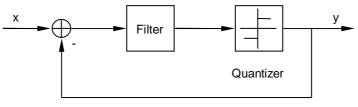

The basic concept of  $\Sigma\Delta$  modulation is the use of feedback to improve the effective resolution of a coarse quantizer.  $\Sigma\Delta$  modulation was first proposed by Inose, and Yasuda in 1962 [Inos62]. The block diagram of a  $\Sigma\Delta$  modulator is shown in Figure 7.

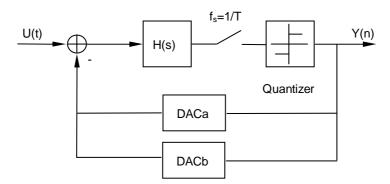

Figure 7.  $\Sigma\Delta$  modulator.

A  $\Sigma\Delta$  modulator is composed of a loop filter, a quantizer and a DAC in the feedback loop. The  $\Sigma\Delta$  modulator is to modulate the analog input signal into a digital sequence which, in the frequency domain, approximates the input very well at certain frequencies. The feedback structure also shapes the quantization noise out of the signal band, thus high in-band resolution can be realized.

#### 2.3.1 The Noise-shaping Technique

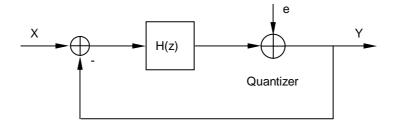

By applying the linear model of the quantizer discussed in Section 2.1, a linear model of the  $\Sigma\Delta$  modulator can be obtained as shown in Figure 8. H(z) is the Z-domain transfer function of the loop filter.

Figure 8. Linear model of  $\Sigma\Delta$  modulator.

The linear model assumes that the quantization noise is white, additive and independent of input X. Under this assumption, the output of the modulator can be expressed as

$$y(z) = \frac{H(z)}{1 + H(z)} x(z) + \frac{1}{1 + H(z)} e(z).$$

(11)

where the signal transfer function is

$$STF = \frac{H(z)}{1+H(z)};$$

(12)

and the noise transfer function is

$$NTF = \frac{1}{1 + H(z)}.$$

(13)

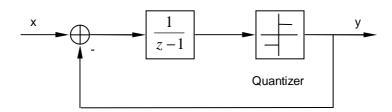

It can be seen from Eq. (11) that the poles of H(z) become the zeros of *NTF*. At the frequencies which satisfy H(z) >> 1,  $y(z) \approx x(z)$ , that is, at these frequencies the signal is transferred while noise is attenuated. The concept can be demonstrated with the lowpass  $\Sigma\Delta$  modulator shown in Figure 9.

Figure 9. Lowpass  $\Sigma\Delta$  modulator.

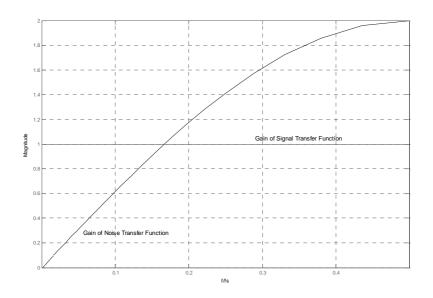

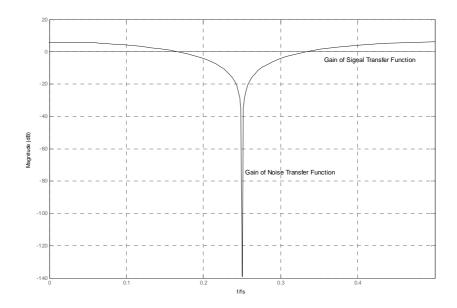

The forward loop filter for a 1<sup>st</sup>-order lowpass  $\Sigma\Delta$  modulator is simply an integrator with a pole at DC. From Eq. (11), the signal transfer function can be calculated to be  $Z^{-1}$ , which is merely a unit delay; while the noise transfer function is (Z-1)/Z. The signal and noise transfer functions obtained in Matlab are shown in Figure 10. The output spectrum of the modulator is shown in Figure 11. At the frequencies close to DC, H(z) >> 1, the gain of the quantization noise is close to zero, so the quantization noise is shaped away from these frequencies. Such a technique that shapes the spectrum of the noise is called noise shaping.

Figure 10. Gain of NTF and STF of the lowpass  $\Sigma\Delta$  modulator.

Figure 11. Simulated output spectrum.

For the 1<sup>st</sup>-order lowpass  $\Sigma\Delta$  modulator, the in-band noise can be calculated as

follows:

$$e_{ib}^{2} = \int_{0}^{f_{b}} e^{2}(f) \left| \frac{z - 1}{z} \right|^{2} df$$

$$= \int_{0}^{f_{b}} \frac{e^{2}}{f_{s}/2} \left| 1 - z^{-1} \right|^{2} df$$

$$= \int_{0}^{f_{b}} \frac{\Delta^{2}/12}{f_{s}/2} \left| 1 - e^{-j\omega T_{s}} \right|^{2} df$$

$$= \int_{0}^{f_{b}} \frac{\Delta^{2}/6}{f_{s}} (2 - 2\cos\frac{2\pi f}{f_{s}}) df$$

$$= \frac{\Delta^{2}}{12} \frac{\pi^{2}}{3} \frac{1}{OSR^{3}}$$

(14)

where  $f_B$  is the signal bandwidth.

It can be seen that doubling of OSR will lead to 9dB, equivalent to 1.5bit, increase in SNR. The increase is much higher than that of the oversampling converter without noise-shaping as indicated in Eq. (10). Eq. (14) also shows that high OSR is desired in  $\Sigma\Delta$  modulation.

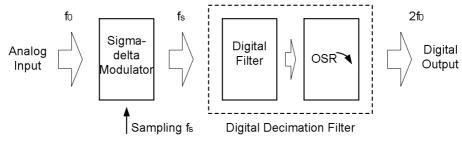

A complete block diagram of baseband  $\Sigma\Delta$  A/D converter is shown in Figure 12.

The converter is composed of a  $\Sigma\Delta$  modulator and a digital decimator. The decimator filters out the out-of-band noise and decimates the high-rate bit stream into Nyquist rate.

Figure 12. Structure of baseband  $\Sigma \Delta$  A/D converter.

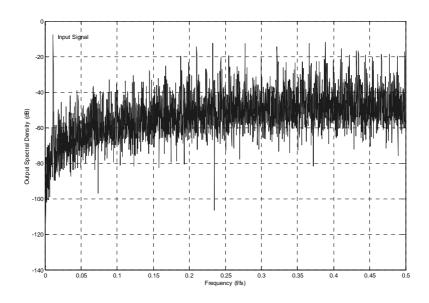

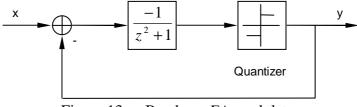

The  $\Sigma\Delta$  modulation can also be extended to bandpass applications. If a resonator is used to replace the lowpass filter in the forward loop, the quantization noise will be shaped away from the resonant frequency instead of DC. Bandpass decimation circuit is used after the bandpass modulator to remove the out-of-band noise, so that high SNR can be obtained in the band of interest. In bandpass  $\Sigma\Delta$  modulator, the sampling frequency is generally selected to be four times of the resonant frequency to simplify the design [Sing95]. A bandpass  $\Sigma\Delta$  modulator is shown in Figure 13.

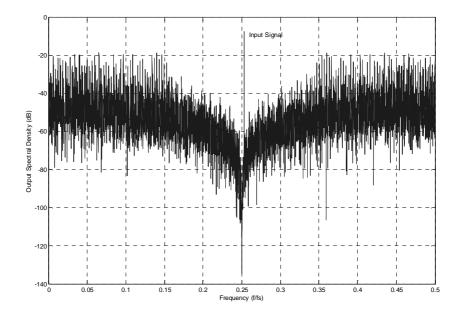

Figure 13. Bandpass  $\Sigma\Delta$  modulator.

The output of the modulator can be written as:

$$y(z) = -x(z)z^{-2} + e(z)\frac{z^2 + 1}{z^2}.$$

(15)

The input signal is just delayed by two clocks cycles, but the quantization noise is shaped. The frequency responses of the signal transfer function and noise transfer function for a  $2^{nd}$ -order bandpass  $\Sigma\Delta$  modulator are shown in Figure 14. It can be seen

at the resonant frequency, that is, one fourth of the sampling frequency, the quantization noise is close to zero. The output power spectrum obtained with Matlab simulation is shown in Figure 15. It is evident that the quantization noise is shaped away from the resonant frequency.

Figure 14. Magnitude responses of NTF and STF of a  $2^{nd}$ -order bandpass  $\Sigma\Delta$  modulator.

Figure 15. Output power spectrum of a  $2^{nd}$ -order bandpass  $\Sigma\Delta$  modulator.

The in-band noise can be calculated as below:

$$e_{ib}^{2} = \int_{f_{o}-BW/2}^{f_{o}+BW/2} e^{2}(f) \left| \frac{z^{2}+1}{z^{2}} \right|^{2} df$$

$$= \int_{f_{o}-BW/2}^{f_{o}+BW/2} \frac{e^{2}}{f_{s}/2} \left| 1+z^{-2} \right|^{2} df$$

$$= \int_{f_{o}-BW/2}^{f_{o}+BW/2} \frac{\Delta^{2}/12}{f_{s}/2} \left| 1+e^{-j2\omega T_{s}} \right|^{2} df$$

$$= \int_{f_{o}-BW/2}^{f_{o}+BW/2} \frac{\Delta^{2}}{f_{s}} \left( 2+2\cos\frac{4\pi f}{f_{s}} \right) df \qquad , \quad (16)$$

$$= \frac{\Delta^{2}}{3f_{s}} \left[ BW - \frac{f_{s}}{2\pi} \sin\frac{2\pi BW}{f_{s}} \right] \qquad (f_{s} = 4f_{0})$$

$$\approx \frac{\Delta^{2}}{3f_{s}} \left\{ BW - \frac{f_{s}}{2\pi} \left[ \frac{2\pi BW}{f_{s}} - \frac{1}{3!} \left( \frac{2\pi BW}{f_{s}} \right)^{3} \right] \right\} \qquad (f_{s} >> 2\pi BW)$$

$$= \frac{\Delta^{2}}{12} \frac{\pi^{2}}{3} \frac{1}{OSR^{3}}$$

where the band of interest is  $[f_0-BW, f_0+BW]$  and signal frequency is  $f_s$ .

Compared Eq. (14) and Eq. (16), it is noticed that the in-band noise power of the  $2^{nd}$ -order bandpass modulator is the same as the  $1^{st}$ -order low-pass modulator.

#### 2.3.2 High-order Sigma-Delta Modulation

In the last section, the noise transfer function has been introduced. Generally, the order of the modulator is defined according to the order of its noise transfer function. High-order modulators will lead to better noise-shaping. It has been proven that, for an Lth-order lowpass modulator, (6L+3) dB SNR increase can be obtained when doubling the OSR [Cand92].

One method to realize high order  $\Sigma\Delta$  modulator is to directly cascade filters in the forward path of the modulator loop while employing only one quantizer. This architecture is called single-stage or multi-loop  $\Sigma\Delta$  modulator. A 2<sup>nd</sup>-order single-stage

lowpass  $\Sigma\Delta$  modulator is shown in Figure 16 [Cher00]. Care should be taken in designing a single-stage  $\Sigma\Delta$  modulator when its order is higher than two, as it may not be stable.

Figure 16.  $2^{nd}$ -order single-stage lowpass  $\Sigma\Delta$  modulator.

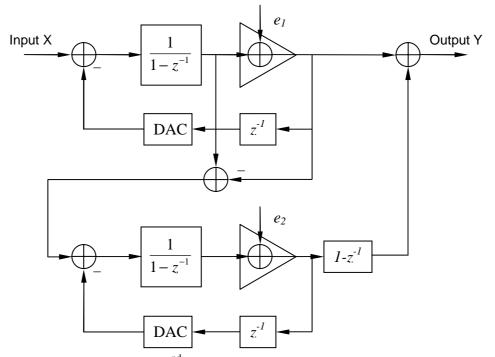

Another method is to use multi-stage structure (typically called MASH, for multi-stage noise-shaping [Hay86]). A second-order lowpass MASH  $\Sigma\Delta$  modulator is shown in Figure 17 [Cher00]. The output can be expressed as

$$Y = X + (1 - z^{-1})^2 e_2.$$

(17)

The  $1^{st}$ -order shaped quantization noise from the first stage is cancelled by the second stage and  $2^{nd}$ -order noise-shaping is achieved. Theoretically, the structure can be extended to high-order noise-shaping with unconditional stability since each  $1^{st}$ -order stage is unconditional stable. However mismatches between components in the stages result in imperfect noise cancellation [Mats87].

Figure 17.  $2^{nd}$ -order lowpass MASH  $\Sigma\Delta$  modulator.

#### 2.3.3 Multi-bit Quantization

Most of the  $\Sigma\Delta$  modulators use single-bit quantizer to take advantage of its good linearity. But the  $\Sigma\Delta$  modulator with one-bit quantizer is prone to idle tones and stability problem. In some designs, multi-bit quantizer is used to increase the resolution and improve the stability, especially for the high-order modulators. The drawbacks of multi-bit quantizer are the complexity of circuit and SNR degradation due to the nonlinearity of the multi-bit DAC. To compensate the circuit imperfection, additional calibration circuits are often required in multi-bit quantizer modulators [Galt96].

### 2.4 Continuous-time Bandpass Sigma-Delta Modulator

#### 2.4.1 Discrete-time and Continuous-time Sigma-Delta Modulators

Discrete-time  $\Sigma\Delta$  modulators refer to the  $\Sigma\Delta$  modulators which are implemented

with discrete-time switched-capacitor circuits [Sing95] [Baza98]. If the loop filter is realized with continuous-time circuit, such as LC or  $G_mC$  form, the modulator is called continuous-time  $\Sigma\Delta$  modulator.

Discrete-time bandpass  $\Sigma\Delta$  modulators have robust performance and can be easily analyzed in Z-domain [Schr89]. But their operating frequency is limited by the settling time of the circuit. This makes the discrete-time bandpass  $\Sigma\Delta$  modulator unable to process high-frequency signals and also limits the maximum OSR that can be achieved. The sampling frequency of most reported discrete-time  $\Sigma\Delta$  modulators are below 100MHz.

Continuous-time bandpass  $\Sigma\Delta$  modulators are not constrained by the settling time problem and suitable for high-speed applications. The continuous-time modulators also have the advantage of inherent anti-aliasing [Shoa94], which alleviates the constraints on the anti-aliasing filter.

## 2.4.2 Design Methodology of Continuous-time Bandpass Sigma-Delta Modulator

Lowpass continuous-time  $\Sigma\Delta$  modulators can be easily designed from the discrete lowpass modulators by simply replacing the discrete-time integrator with continuous-time one. But for bandpass continuous-time modulators, such a replacement of discrete-time resonator with continuous-time one does not yield a stable system [Nors97] [Cher00].

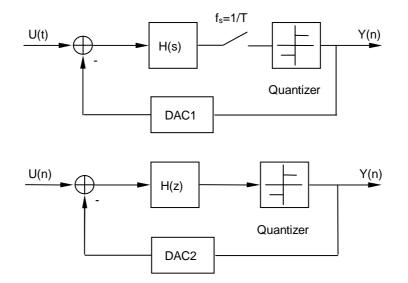

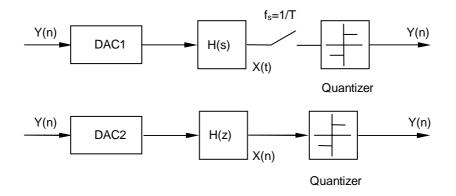

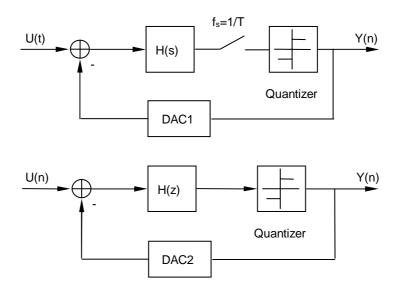

Due to the presence of a clocked sampler within the forward loop, one way to design the continuous-time bandpass  $\Sigma\Delta$  modulator is to explore the equivalence

between discrete-time and continuous-time bandpass  $\Sigma\Delta$  modulators [Shoa94]. A continuous-time and a discrete-time  $\Sigma\Delta$  modulators are shown in Figure 18. If the two inputs to the quantizers are made the same at the sampling instants, then the same output bit streams Y(n) can be obtained from the modulators. This is illustrated in Figure 19.

Figure 18. Equivalence between continuous and discrete-time modulators.

Since both modulators have the same input, the input can be ignored and the loop can be broken after the quantizers as shown in Figure 19.

Figure 19. Forward loops of (a) continuous-time and (b) discrete-time  $\Sigma\Delta$  modulators.

The equivalence can be expressed as:

$$X(t)|_{t=nT} = X(n) \tag{18}$$

or

$$H(z)D(z) = Z\{L^{-1}[H(s)D(s)]|_{t=nT}\}.$$

(19)

where, D(s) is the transfer function of DAC2, while D(z) is the transfer function of DAC1. Such a transformation between continuous-time and discrete-time is based on Pulse-Invariant Transform [Gard86] [Thur91].

The most commonly used continuous-time resonators are of LC and  $G_mC$  types. Since the transfer function of the resonators are generally fixed, other technologies, such as multiple feedback loops, have to be used to realize the equivalence. The detailed design methodology for continuous-time bandpass  $\Sigma\Delta$  modulators will be discussed in Chapter 4.

#### 2.4.3 Review of Continuous-time Bandpass Sigma-Delta Modulators

The idea of bandpass  $\Sigma\Delta$  modulator was first proposed by R. Schreier and M. Snelgrove [Schr89]. The bandpass  $\Sigma\Delta$  modulator was realized by putting the zeros of the noise transfer function at a certain frequency instead of DC. The modulator was implemented using switched-capacitor circuits.

Since then, many discrete-time bandpass  $\Sigma\Delta$  modulators have been reported [Jant92] [Long93] [Sing95] [Hair96] [Ong97] [Cusi01]. With the increase of sampling frequency, the nonlinearities of the switched-capacitor circuits become obstacles in the high-speed bandpass  $\Sigma\Delta$  modulator design. Continuous-time bandpass  $\Sigma\Delta$  modulators, which have the advantages of high operating frequency and inherent anti-aliasing, began to attract more attentions. But unlike discrete-time modulators, the continuous-time modulators lacked a systematic design methodology to predict the performance and stability. One effort to solve this problem was reported in [Thur91]. The pulse-invariant transform was introduced to explore the equivalence between the continuous and discrete-time modulators. But their method was still not an optimal solution since the equivalence was not fully realized due to limited controllability.

The problem was solved by Shoaei and Snelgrove [Shoa94]. In this paper, an idea that combines the multi-feedback technique together with the pulse-invariant transform was proposed. For the first time, a complete design methodology for continuous-time bandpass  $\Sigma\Delta$  modulator design was presented. It was also pointed out in the paper that the low Q of resonators would affect the performance of the modulator. Low Q will lead to a SNR loss. A continuous-time bandpass  $\Sigma\Delta$  modulator was designed and implemented with GmC resonator.

A LC resonator based continuous-time bandpass  $\Sigma\Delta$  modulator was later reported in [Shoa95]. Due to the substrate loss, the on-chip LC resonator suffers from low Q factor. A Q-enhancement technique has to be used to improve the Q factor.

Many continuous-time bandpass  $\Sigma\Delta$  modulators with different structures and technologies were reported later. The resonators used in the modulators were either LC or G<sub>m</sub>C resonators. Table 1 lists the details of some reported continuous-time bandpass  $\Sigma\Delta$  modulators.

| Reference                 | [Shoa97]         | [Gao98]  | [Gao98a]        | [Cher00a]       | [Hsu00]          | [Maur00]         |

|---------------------------|------------------|----------|-----------------|-----------------|------------------|------------------|

| F <sub>sampling</sub>     | 200              | 3,800    | 4,000           | 4,000           | 280              | 800              |

| OSR                       | 500              | 10,000   | 500             | 100             | 700              | 2,000            |

| Order                     | $2^{nd}$         | $2^{nd}$ | $4^{\text{th}}$ | $4^{\text{th}}$ | $2^{nd}$         | $4^{\text{th}}$  |

| <b>SNR</b> <sub>max</sub> | 46               | 57       | 53              | 37              | 42               | 68               |

| (dB)                      |                  |          |                 |                 |                  |                  |

| DR (dB)                   | 50               | N/A      | 62              | 40              | N/A              | 60               |

| Resonator                 | G <sub>m</sub> C | LC       | LC              | LC              | G <sub>m</sub> C | G <sub>m</sub> C |

| Process                   | 0.8-µm           | 0.5-µm   | 0.5-µm          | 0.5-µm          | 0.5-µm           | SiGe BJT         |

|                           | BiCMOS           | BJT      | SiGe            | SiGe HBT        | CMOS             |                  |

|                           |                  |          | HBT             |                 |                  |                  |

Table 1. Continuous-time bandpass  $\Sigma\Delta$  modulators published.

It can be seen from the table that the resolution of the modulator is limited to 10 bits or lower. One of the major reasons that limit the resolution is the low Q of the LC and  $G_mC$  types of resonators. The low Q of LC resonator is mainly due to the losses from series resistance of the conductor and magnetically induced eddy current in the substrate. The Q degradation in the  $G_mC$  resonator, on the other hand, is because of its finite output impedance. Both are more severe at high frequencies.

#### 2.4.4 Micromechanical Resonators

As it can be seen from the previous section, one of the limiting factors in high-speed continuous-time bandpass  $\Sigma\Delta$  modulators is the low Q of the resonators. Both LC and G<sub>m</sub>C resonators suffer from the poor Q factor. Although Q enhancement techniques are used in most of the designs [Shoa97] [Gao98] [Chee00a], they only have limited improvement. Besides, the Q-enhancement circuit degrades the linearity of the resonator.

Low Q will result in degradation of noise-shaping and SNR in  $\Sigma\Delta$  modulators. Figure 20 illustrates the noise-shaping degradation due to low Q, while Figure 21 shows the SNR degradation. Similar analysis was done in [Shoa94] and [Gao98].

Figure 20. Noise shapes of the resonators of different Q.

Figure 21. SNR degradation due to Q.

It can be seen that the SNR is highly dependent on the Q, especially when Q is less than 70. This can be easily understood as high-Q resonator gives a deeper notch at

the resonant frequency and have less quantization noise in the band of interest, as indicated in Figure 20.

Micromechanical resonators with resonant frequency as high as several hundreds of megahertz have been demonstrated [Bust98] [Nguy01]. Compared with LC and  $G_mC$  resonators, micromechanical resonators have the advantages of high Q (typically higher than 1000), good temperature stability, low power and high resonant frequency. The micromachining technology can be made compatible with CMOS process [Nguy01], which makes it possible to integrate with the circuits. The aim of the thesis is to investigate the feasibility of a micromechanical resonator based continuous-time bandpass  $\Sigma\Delta$  modulator.

# **Chapter 3 Micromechanical Resonators**

This Chapter introduces the various silicon micromechanical resonators. The MEMS (MicroElectroMechanical Systems) technology is briefly discussed. Comparison between the micromechanical resonator and other continuous-time resonators is presented. Finally, the clamped-clamped beam micromechanical resonator used in this project is introduced. The equivalent circuit is proposed to model the resonator and the resonator interface circuit is also presented.

#### **3.1MEMS Technology**

MEMS is the acronym of MicroElectroMechanical Systems. They are micro-structures created on silicon or other materials.

The idea of MEMS was first proposed by the Nobel Prize-winning physicist R. R. Feynman in his famous talk "there is plenty of room at the bottom" given in Caltech in 1959. Since then, many researchers have developed various fabrication technologies and numerous MEMS devices and systems on silicon or other materials. Some commercial products, such as accelerometers, microphone, and pressure sensors, have been widely used in many applications [Gabr98].

The basic processes of MEMS, such as photolithography and chemical etching are borrowed from IC fabrication. But the IC fabrication is mostly based on surface processes, while the fabrication processes of MEMS are rather diverse. The bulk micromachining technique [Gabr98] is a major technique in MEMS fabrication. It is based on etching (especially wet etching), and uses the anisotropic etchants to shape the structure.

Another important fabrication technique is surface micromachining [Bust98]. Like conventional IC fabrication, surface micromachining utilizes deposition, lithography and etching to realize microstructures. Surface micromachining can realize complex structures and is compatible with conventional IC processing. But it is inherently two-dimensional planar process and unable to realize structures with high aspect ratio.

LIGA [Bach95] is a new process proposed to realize the high-aspect-ratio structures. It is, in essence, a molding technique based on high-energy lithography source. But it has limited accessibility since it requires a synchrotron radiation source. Besides, it is not compatible with standard IC processing.

Many efforts have been made to integrate MEMS devices with integrated circuits so that the entire system can be realized on a single chip [Bust98] [Nguy01]. Although the integration is possible, it has not become the main stream technology due to the issues, such as cost and yield.

#### **3.2Structures of Micromechanical Resonators**

Micromechanical resonator is a device, which generally utilizes the mechanical resonance driven by static electric force to work as a resonant component. The earliest version of the Micromechanical resonator as I know was the cantilever-beam resonator in [Nath67], shown in Figure 22. A bias voltage is applied to pull the beam close to the

substrate. The beam and the input force plate work as the two electrodes of a capacitor. The AC signal can be applied to the input force plate. When the frequency equals the inherent resonant frequency of the structure, the beam will have the largest movement. So, largest current output can be measured at the output port.

Figure 22. Cantilever-beam resonator.

Although the micromechanical resonator was reported decades ago, they didn't get much attention until recent years. Micromechanical resonators have the advantages of high Q and the potential to be integrated with circuits on single silicon, which makes them very attractive in the communication systems design. To date, many different structures of micromechanical resonators have been proposed, which are detailed as below.

Comb-transduced Resonator - Figure 23 [Nguy99] shows a comb-transduced resonator, together with its frequency response. Compared with cantilever-beam resonator, the vertical structure is replaced with two parallel inter-digit combs. The two combs act as the two electrodes of a capacitor. They move laterally when the electric force exists between them. The resonant frequency is determined by their mechanical

dimension, material, and bias voltage. Comb-transduced resonator has good linearity, but their working frequency is low (typically less than 1MHz) due to the bulky structure.

Figure 23. Comb-transduced resonator.

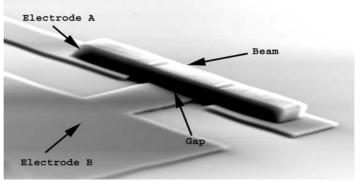

Figure 24. Clamped-clamped beam resonator.

Clamped-clamped Beam Resonator - The structure of the clamped-clamped beam micromechanical resonator is shown in Figure 24. Compared with cantilever-beam resonator, the beam has two stubs instead of one. The resonator consists of a polysilicon beam (connected to electrode A), and an electrode B, which lies under the beam. A bias voltage is applied to electrode A to pull the beam close to electrode B with electric force. The input signal is applied to electrode B to activate the resonator and the output signal is current. The output can be sensed with a resistive load or trans-impedance circuit. When the input signal frequency equals the resonant frequency, the signal will have the least loss in the transmission.

Free-free Beam Resonator - Free-free beam resonator is devised from the clamped-clamped beam resonator. It uses a membrane suspended with four beams as the resonant component. The beam length is designed at the one-fourth of the wavelength of the resonant frequency, so that the beam-introduced damping can be cancelled. With such a modification, free-free beam resonator can operate at higher resonant frequency than the clamped-clamped beam resonator. Figure 25 [Nguy99] shows a 92MHz free-free beam micromechanical resonator.

Figure 26. Disk resonator.

Disk Resonator – Disk resonator uses extensional, instead of flexural vibration mode to realize very high frequency resonance. Figure 26 [Nguy01] shows a radial contour-mode disk resonator. The resonator vibrates via uniform, well-balanced, radial expansion and contraction along its perimeter.

# **3.3 Resonator Model**

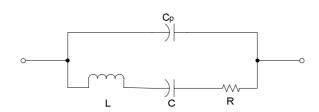

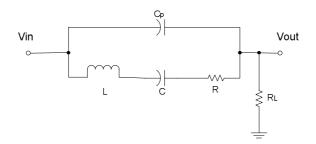

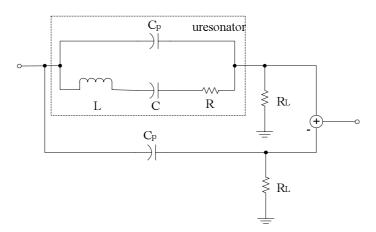

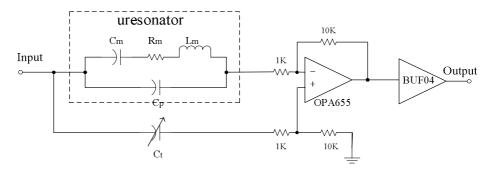

A commonly used equivalent circuit for one-port micromechanical resonator is shown in Figure 27 [Sant99], where  $L_m$ ,  $C_m$  and  $R_m$  are the motion elements and  $C_p$  is the static capacitor between the input and output of the micromechanical resonator.

Figure 27. Equivalent circuit of the micromechanical resonator.

Figure 28. Equivalent circuit with resistive load.

The transfer function of the micromechanical resonator can be obtained based on the equivalent circuit in Figure 27. The transfer function with resistive load  $R_{L}$ , as shown in Figure 28, is given by

$$M_{R}(s) = \frac{Vout}{Vin} = \frac{s(s^{2} + as + b)}{s^{3} + cs^{2} + ds + e}$$

(20)

where a = R/L,  $b = (C+C_P)/(LCC_P)$ ,

$$c = (R_L R C_P + L)/(R_L L C_P), d = (R_L C_P + R_L C + RC)/(R_L L C C_P)$$

$$e = 1/(R_L L C C_P).$$

The resonator used in our project is designed and fabricated by the Institute of Microelectronics (IME), Singapore. It is a one-port clamped-clamped beam resonator shown in Figure 24. The model parameters are given as below:

$$R = 350K\Omega, C = 100aF, L = 3.6H, C_p = 200 fF$$

.

Due to the bonding pads, there is a 5.5pF parasitic capacitor shunt at both the input and output.

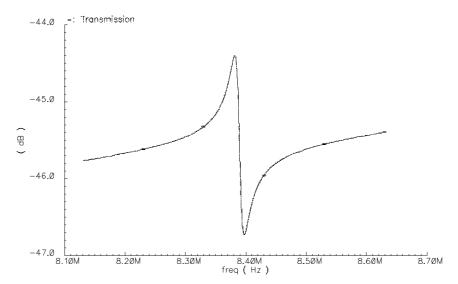

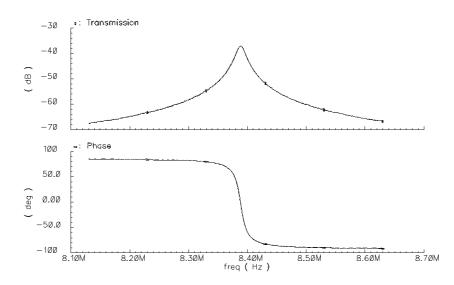

Based on the parameters of this resonator and the equivalent circuit in Figure 27, the resultant frequency response with 50- $\Omega$  load and 50- $\Omega$  source impedance and 10 times amplification is shown in Figure 29, which closely matches the measured response shown in Figure 30 at a pressure of 20mTorrs. The loaded Q is measured to be around 200. When pressure is lower, the Q can be further improved. Considering the OSR of our design is expected to be 80, from Figure 21, it can been that a Q higher than 80 is adequate to ensure that the SNR loss due to non-ideal Q is negligible. So the Q of the micromechanical resonator is high enough.

The model is considered as accurate as far as the resonant frequency, anti-resonant frequency, insertion loss and Q are concerned.

Figure 29. Simulated frequency response of the resonator (With 10 times amplification).

Figure 30. Measured frequency response of the micromechanical resonator (With 10 times of amplification).

Apart from the resonant peak, a notch also appears in the frequency response. The additional notch is referred as anti-resonance, which is caused by the existence of static capacitance  $C_P$ . Such a phenomenon is not a concern in the existing applications, as the resonators are mostly used as bandpass filters. However, it will be shown later that the anti-resonance is not desirable when the resonator is used to realize the  $\Sigma\Delta$  modulator. The details will be discussed Chapter 4.

# **3.4Sensing Circuits**

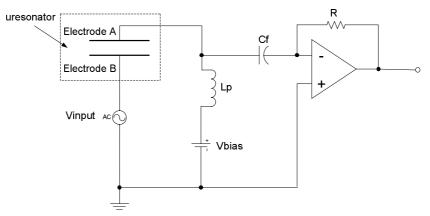

When a voltage signal is applied at the input of the micromechanical resonator, a resistive load or trans-impedance circuit is generally used to sense the resonator output.

A sensing scheme based on resistive load is shown in Figure 31 [Wang00], where  $L_P$  is used to block the AC signal, while  $C_f$  blocks the DC. Generally,  $L_P=1mH$ ,  $C=0.1\mu F$  are used.

Figure 31. Resistive sensing circuit.

Another sensing scheme is based on trans-impedance circuit as shown in Figure 32

[Bili01].

Figure 32. Trans-impedance sensing circuit.

Both circuits have the same function, that is, to convert the current output from the resonator to a voltage. Note that a coupling capacitor is needed to isolate the DC bias voltage.

# 3.5 Micromechanical Resonator versus LC and $G_mC$ Resonators

Compared with LC and  $G_mC$  resonators, micromechanical resonators have the advantages of high Q, high resonant frequency, and good temperature stability. Their disadvantages lie in the insertion loss (inherent for passive elements), and the existence of anti-resonance.

All the continuous-time bandpass  $\Sigma\Delta$  modulators published so far used LC or G<sub>m</sub>C resonators. They suffered from low quality factor Q and poor linearity, which degraded the performance of the  $\Sigma\Delta$  modulators. This is especially true at high frequencies. Q-enhancement circuits were generally needed [Shoa97] [Gao98] [Cher00a]. Micromechanical resonators have high Q and relatively high resonant frequency and the micromachining processing can be made compatible with IC processing [Bust98] [Nguy01]. Therefore, micromechanical resonator is a good candidate to replace LC and G<sub>m</sub>C resonators in continuous-time bandpass  $\Sigma\Delta$  modulators.

# Chapter 4 Bandpass Sigma-Delta Modulator Based on Micromechanical Resonator

In Chapter 2, it was pointed out that the poor Q factor was one of the obstacles in realizing high-speed bandpass  $\Sigma\Delta$  modulators. High Q micromechanical resonator is proposed to replace the LC and G<sub>m</sub>C resonators in an attempt to overcome this problem. This chapter deals with the design of the micromechanical resonator based continuous-time bandpass  $\Sigma\Delta$  modulator. The design methodology is first introduced. The effect of anti-resonance is then discussed and an anti-resonance cancellation circuit is proposed. Finally, the modulator architecture and its simulation results are presented. The circuit-level implementation is also recommended.

#### **4.1 Design Methodology**

The design methodology for continuous-time bandpass  $\Sigma\Delta$  modulators was proposed by Shoaei and Snelgrove in 1994 [Shoa94]. It is based on the equivalence between the discrete-time and continuous-time  $\Sigma\Delta$  modulators. Such equivalence can be achieved by pulse-invariant transform and multi-feedback technique.

For the continuous-time and discrete-time  $\Sigma\Delta$  modulators shown in Figure 33, if the two quantizers produce the same output Y(n), the quantizers inputs at the sampling instants must be the same. This is illustrated in Figure 34 and can be described mathematically by the following equation:

$$X(t)|_{t=nT} = X(n) \tag{21}$$

Figure 33. Equivalence between discrete-time and continuous-time modulators.

Figure 34. Broken loops of (a) continuous-time and (b) discrete-time  $\Sigma\Delta$  modulators.

Thus, the loop transfer function of the continuous-time modulator should satisfy

$$H(z)D(z) = Z\{L^{-1}[H(s)D(s)]\Big|_{t=nT}\}.$$

(22)

where, D(s) is the transfer function of DAC2 and D(z) is transfer function of DAC1. Depending on the transfer function of the resonator, the above equation may not have a solution. In such a case, more degrees of freedom are needed. Thus, multi-feedback technique is used by adding an additional feedback loop, as shown in Figure 35.

Figure 35. Continuous-time modulator with two feedbacks.

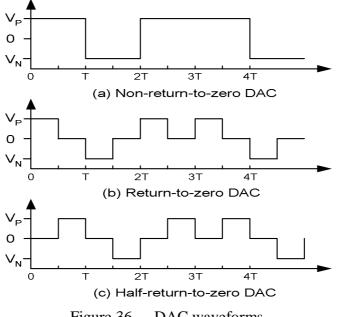

The DACs used in continuous-time modulator can be categorized into two types: non-return-to-zero DAC and return-to-zero DAC. Assume  $V_P$ ,  $V_N$  are the positive and negative outputs of the DAC, respectively. Non-return-to-zero DAC outputs either  $V_P$ or  $V_N$  in each clock cycle. But for return-to-zero DACs, there is a period in a clock cycle, in which the DAC output will be zero. According to location of the return-to-zero period, return-to-zero DACs can be divided into return-to-zero, half-return-to-zero, and other types.

The waveforms of non-return-to-zero, return-to-zero, and half-return-to-zero DACs are shown in Figure 36.

Figure 36. DAC waveforms.

The S domain transfer functions of the DACs are as below:

Non-return-to-zero DAC:

$$DAC_N(s) = \frac{1 - e^{-sT}}{s}$$

(23)

Return-to-zero DAC:

$$DAC_R(s) = \frac{1 - e^{-sT/2}}{s}$$

(24)

Half-return-to-zero DAC:

$$DAC_{H}(s) = \frac{e^{-sT/2} - e^{-sT}}{s}$$

(25)

In multi-feedback technique, the linear combination of the DACs' transfer functions makes it possible to satisfy Eq. (22) and to realize the equivalence between the discrete-time and continuous-time  $\Sigma\Delta$  modulators.

#### 4.2Anti-resonance and Its Cancellation

The idea to use micromechanical resonator in  $\Sigma\Delta$  modulation is to take advantage of its high Q. However, the micromechanical resonator has the drawbacks of anti-resonance and insertion loss. While the insertion loss can be compensated with amplification, the effect of anti-resonance has to be analyzed.

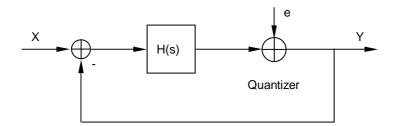

Figure 37. Linear model of  $\Sigma\Delta$  modulator.

Consider the linear model of  $\Sigma\Delta$  modulator shown in Figure 37, the signal and noise transfer functions are given below:

Signal Transfer Function:

$$STF = \frac{H(s)}{1 + H(s)}$$

(26)

*Noise* Transfer Function:

$$NTF = \frac{1}{1+H(s)}$$

. (27)

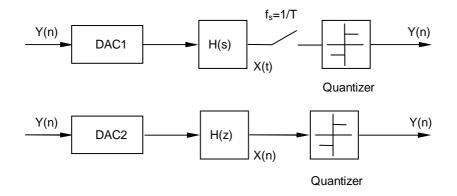

At the anti-resonant frequency, |H(s)| << 1, thus the signal is attenuated and the noise shaping cannot be attained. Matlab simulation also shows that the continuous-to-discrete equivalence cannot be achieved if the anti-resonance exists. Therefore, in order to realize the bandpass  $\Sigma\Delta$  modulator, the anti-resonance must be removed. The proposed cancellation scheme is shown in Figure 38.

Figure 38. Anti-resonance cancellation scheme.

The existence of anti-resonance is due to the feed-through static capacitance  $C_P$ . In this scheme, the effect of  $C_P$  is generated in an additional branch and subsequently subtracted from the resonator output. The resultant transfer function normalized to the sampling frequency can be approximated to

$$H(s) = g \frac{s}{s^2 + (\pi/2)^2}.$$

(28)

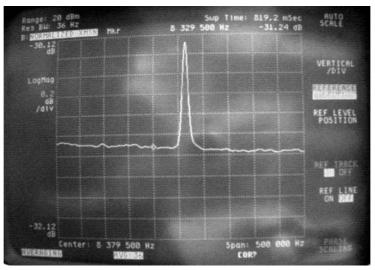

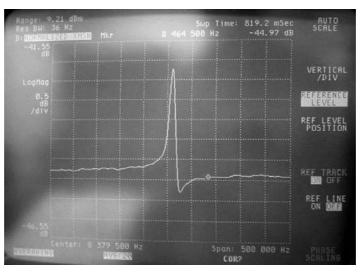

The simulated frequency response of the micromechanical resonator with anti-resonance cancellation is shown in Figure 39, while the measured result is shown in Figure 40. When the two paths are not matched, the cancellation may be incomplete, as shown in Figure 41.

Figure 39 Frequency response of the resonator with anti-resonance cancellation.

Figure 40. Frequency response of the micromechanical resonator with anti-resonance cancellation.

Figure 41. Frequency response of the micromechanical resonator with imperfect anti-resonance cancellation.

#### **4.3 Modulator Architecture**

The prototype discrete-time bandpass modulator is shown in Figure 13. With the design methodology discussed in Section 4.1, if only one non-return-to-zero DAC feedback is used, the loop transfer function after pulse-invariant transform will be

$$H(z) = Z\{L^{-1}[H(s)D(s)]|_{t=nT}\}$$

(29)

where H(s) is the resonator transfer function, and D(s) is the transfer function of the non-return-to-zero DAC.

With the anti-resonance cancellation, the transfer function of the micromechanical resonator can be written as

$$H(s) = \frac{s}{s^2 + (\pi/2)^2}$$

(30)

which is normalized to the sampling frequency  $f_s$ .

So Eq.(29) can be calculated to be

$$H(z) = Z\{L^{-1}[H(s)D(s)]|_{t=nT}\} = \frac{0.6366z - 0.6366}{z^2 + 1}$$

(31)

The calculation is done with the Matlab program in Appendix A1. The result doesn't equal to the loop transfer function of the second-order discrete-time bandpass  $\Sigma\Delta$  modulator  $\frac{-1}{z^2+1}$ . The reason is that there is no enough controllability to make the continuous-time to discrete-time equivalence [Cher00]. Comparing the numerators of the two equations, it can be seen that two feedback loops are needed to realize the equivalence. They can be any combination of the three DACs proposed in Section 4.1. The two return-to-zero DACs are used in the design because they are immune to the asymmetric pulse waveform [Cherr00].

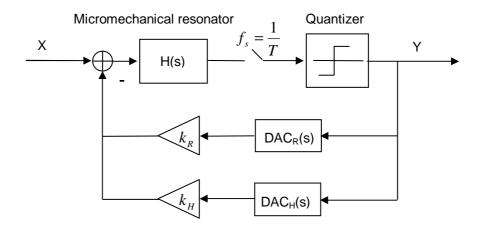

The proposed architecture for the micromechanical resonator based bandpass  $\Sigma\Delta$  modulator is shown in Figure 42.

Figure 42. Proposed micromechanical resonator based bandpass  $\Sigma\Delta$  modulator.

By applying pulse-invariant transform, an equivalent Z-domain transfer function can be obtained from that of the continuous-time bandpass  $\Sigma\Delta$  modulator:

$$H(z) = Z\{L^{-1}[k_{R}H(s)DAC_{R}(s) + k_{H}H(s)DAC_{H}(s)]\}$$

=  $k_{R}\frac{0.1865z - 0.4502}{z^{2} + 1} + k_{H}\frac{0.4502z - 0.1865}{z^{2} + 1}$  (32)

The two coefficients  $k_R$  and  $k_H$  can be determined by equating Eq.(32) to the desired Z-domain transfer function of second-order sigma-delta modulator, that is,

$$H(z) = k_R \frac{0.1865z - 0.4502}{z^2 + 1} + k_H \frac{0.4502z - 0.1865}{z^2 + 1} = \frac{-1}{z^2 + 1}$$

(33)

The coefficients obtained from Eq. (33) are

$$k_R = 2.6815, \qquad k_H = -1.1107.$$

### 4.4Performance of the Proposed Sigma-Delta Modulator

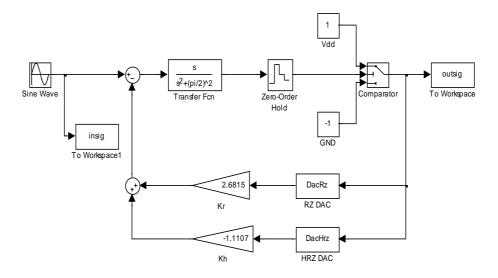

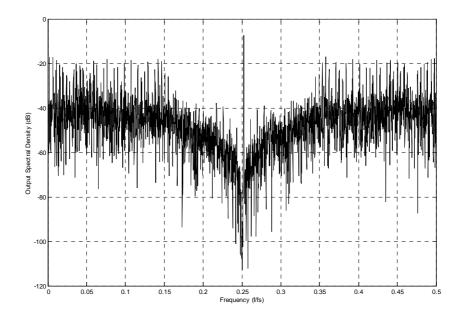

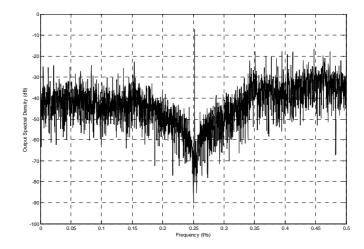

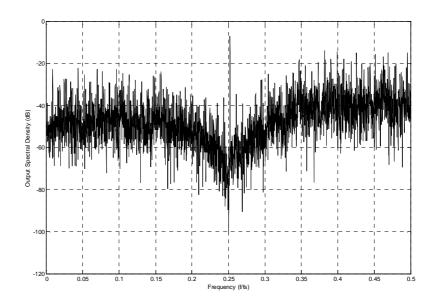

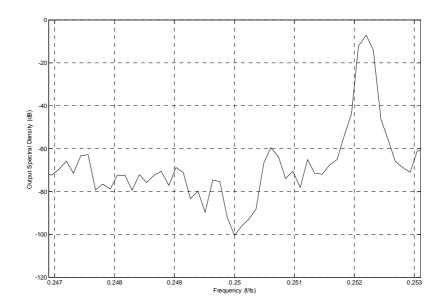

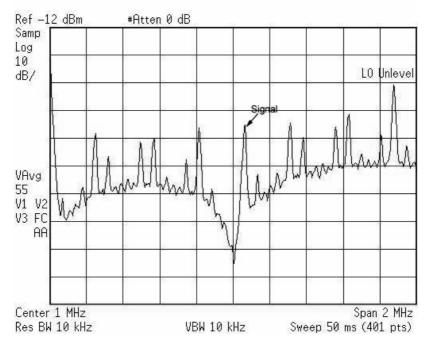

The Simulink model shown in Figure 43 is used to evaluate the performance of the proposed  $\Sigma\Delta$  modulator. Figure 44 shows the power spectrum of the output bit stream

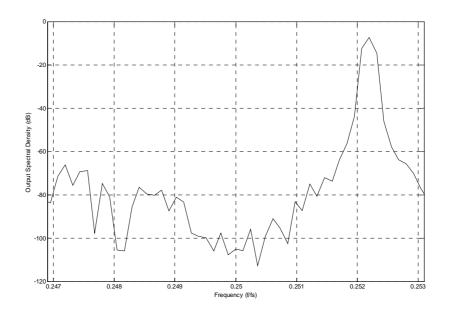

when the input signal is at 8.07 MHz with a magnitude of -4.4dB, the sampling frequency is 32 MHz. Figure 45 is the in-band spectrum within the 200-KHz bandwidth. 8192 samples are used in the FFT calculation.

Figure 43. Simulink model of the continuous-time modulator.

Figure 44. Output power spectrum (Matlab simulation).

Figure 45. In-band power spectrum (OSR = 80, Matlab simulation).

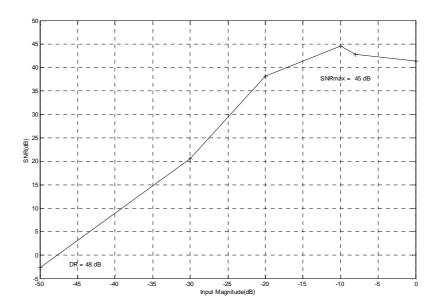

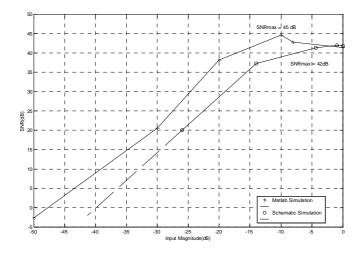

Figure 46 shows the SNR again input magnitude for the bandwidth of 200 KHz and sampling frequency of 32 MHz. The calculated dynamic range is 48dB and peak SNR is 45dB.

The simulation result shows a similar noise shaping as obtained in the discrete-time 2<sup>nd</sup>-order bandpass Sigma-delta modulator, which proves that the design methodology is correct. The SNR degradation when input approaches full scale is due to the increased spectral harmonic content. Here the full scale input is defined to be the one whose magnitude equals the maximum magnitude of the quantizer feedback [Cher00].

The dynamic range is determined by the noise floor, which is also the ideal peak SNR. Due to the SNR degradation at full scale, the peak SNR is slightly lower than the dynamic range.

Figure 46. SNR against Input magnitude (Matlab simulation).

# **4.5 Circuit Implementation**

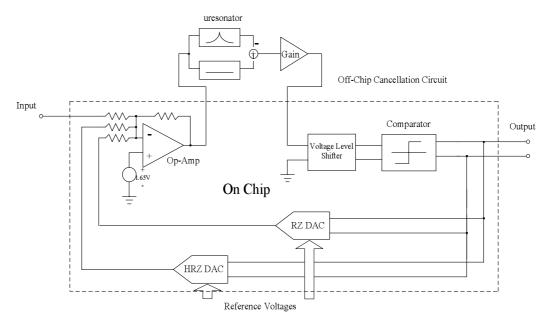

The circuit implementation of the proposed modulator is depicted in Figure 47, where the micromechanical resonator and its anti-resonance cancellation circuit is off-chip.

Figure 47. Circuit structure of the modulator.

The operational amplifier is used to realize the signal addition. The output from

the opamp is fed to the micromechanical resonator and the cancellation circuit. The gain stage is used to compensate the insertion loss of the micromechanical resonator.

# **Chapter 5 Circuit Level Design**

This chapter describes the circuit-level design of the proposed modulator and presents the simulation results. The design is based on a triple-metal, double-poly 0.6-µm CMOS process from AMS (Austria MikroSystems). The design specifications are summarized in Table 2.

| Process            | 0.6-µm CMOS        |

|--------------------|--------------------|

| Supply Voltage     | 3.3V Single Supply |

| Sampling Frequency | 32MHz              |

| Signal Frequency   | 8MHz               |

| Bandwidth          | 200kHz             |

| OSR                | 80                 |

| Dynamic Range      | 48dB               |

Table 2. Design specifications.

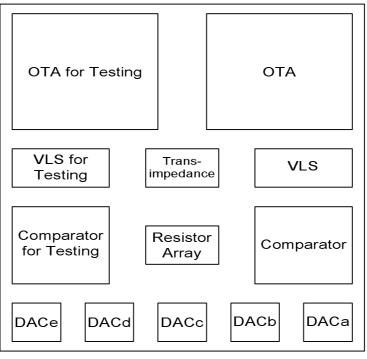

#### **5.1 Function Blocks**

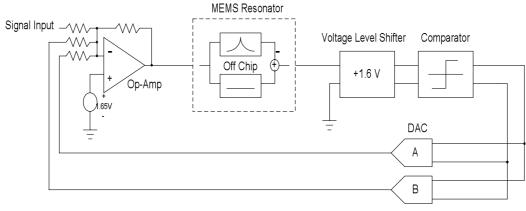

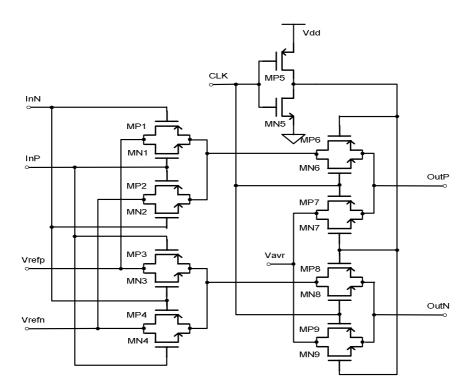

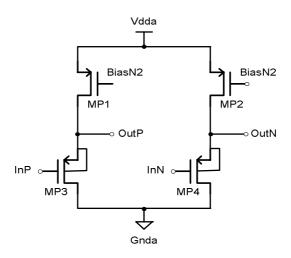

Figure 48 shows the circuit-level block diagram of the proposed modulator. The micromechanical resonator part is realized off-chip. The on-chip circuits include the operational amplifier, voltage shifter, comparator, and DACs. The operational amplifier is used to realize the sum amplifier. The voltage shifter shifts the signal with a proper DC level required by the comparator. The voltage shifter, comparator and DAC are designed in differential form to reduce noise and interference. The operational amplifier is single-ended, since the micromechanical resonator cannot handle the differential signal.

Figure 48. Modulator circuit structure.

# **5.2Operational Amplifier**

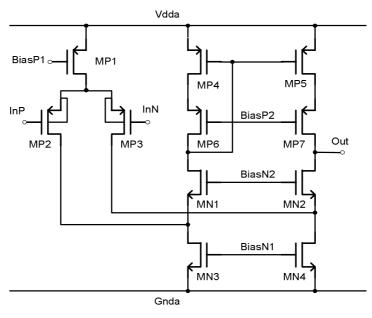

Since the opamp is used to realize a sum amplifier, considering the signal from DACs has a frequency of 32MHz, high bandwidth and a modest DC gain is needed. A folded cascode structure is chosen for the opamp. The circuit of the opamp is shown in Figure 49.

Figure 49. OTA schematic.

Both the input and output DC levels are set to 1.65V. MP4 to MP7 are the active load with differential-to-single ended conversion, so the long channel length is used to

alleviate the channel length modulation effect. MP2 and MP3 are designed in minimum length to achieve high  $g_m$  with a reasonable transistor width. The size of MN1, MN2 and MP6 and MP7 are determined based on the trade-off between gain and frequency response through simulation. The bias current of the input stage is 1.5mA and the currents of MP4 and MP5 are both designed as 0.75mA. The sizes of the transistors are listed in Table 3.

| Transistor | W/L (micron) | Transistor | W/L (micron) |

|------------|--------------|------------|--------------|

| MP1        | 1107.6/4.8   | MN1/2      | 134.6/0.9    |

| MP2/3      | 684.95/0.6   | MN3/4      | 335.25/2.1   |

| MP4/5      | 383.4/4.8    |            |              |

| MP6/7      | 292/0.9      |            |              |

Table 3. OTA transistor sizes.

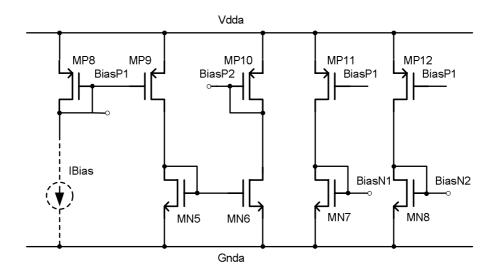

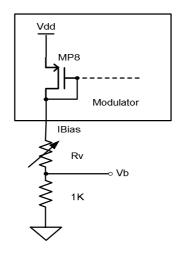

Biasing circuit for the opamp is shown in Figure 50. The input reference current  $I_{Bias}$  is set to be 0.2mA and is generated off-chip. Large transistor length is used to reduce the channel length modulation effect. The transistor sizes are listed in Table 4 and the bias voltages in Table 5.

Figure 50. Basing circuit schematic.

| Transistor | W/L (micron) | Transistor | W/L (micron) |

|------------|--------------|------------|--------------|

| MP8        | 147.75/4.8   | MN5        | 160.5/4.8    |

| MP9        | 73.65/4.8    | MN6        | 161.4/4.8    |

| MP10       | 19.55/4.8    | MN7        | 54.3/4.8     |

| MP11       | 73.3/4.8     | MN8        | 16.4/4.8     |

| MP12       | 75.5/4.8     |            |              |

Table 4. Transistor sizes of the biasing circuit.

Table 5. Bias voltages.

| Net Name    | BiasP1 | BiasP2 | BiasN1 | BiasN2 |

|-------------|--------|--------|--------|--------|

| Voltage (V) | 1.8    | 1.1    | 1.3    | 1.7    |

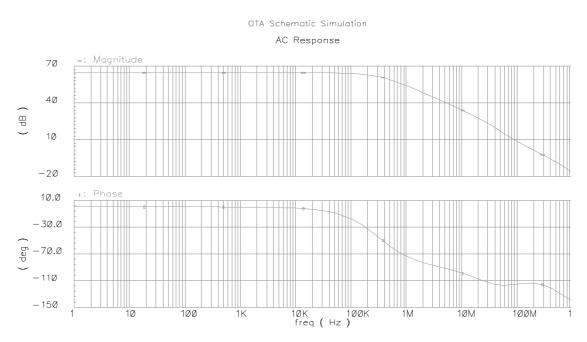

The simulation result is shown in Figure 51. The unity gain frequency is approximately 229MHz for a capacitive load of 2pF. The phase margin is 63°. The power consumption of the OTA and basing circuit is measured to be 12mW.

Figure 51. Frequency response of the OTA.

### 5.3 Comparator

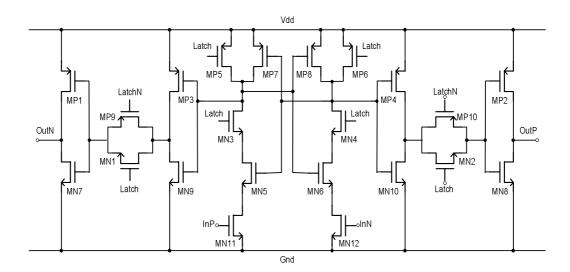

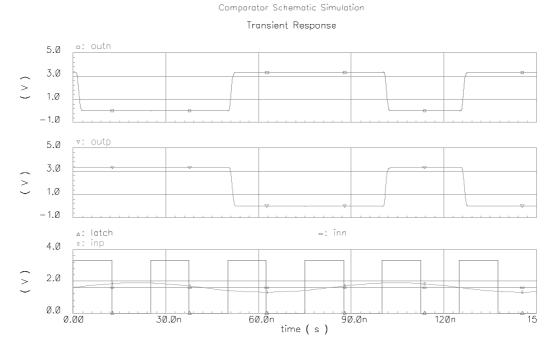

The schematic of the high-speed latched comparator [John97] is shown in Figure 52. The comparator circuit can be divided into track-and-latch stage and the buffer. The latch-and-track stage is implemented with two back-to-back connected inverters and a buffer. The positive feedback regenerates the analog input into a full-scale digital output.

Latch and LatchN are two differential clocks. The comparator operates in two phases: the compare and reset phases. When Latch is high, MP5 and MP6 are off. The comparator does comparison, and the output appears at OutP and OutN. When Latch is low and LatchN is high, MP5 and MP6 are on, which resets the outputs of the track-and-latch stage. In the meantime, the two transmission gates are off, so that the previous result is stored at the buffer stage until next clock cycle. The reset phase is used to ensure that no memory is transferred from one decision cycle to the next. The transistor sizes are given in Table 6.

Figure 52. Schematic of the differential comparator.

| Transistor | W/L (micron) | Transistor | W/L (micron) |

|------------|--------------|------------|--------------|

| MP1/2      | 45/0.6       | MN1/2      | 2/0.6        |

| MP3/4      | 6/0.6        | MN3/4      | 40/0.6       |

| MP5/6      | 28/0.6       | MN5/6      | 60/0.6       |

| MP7/8      | 60/0.6       | MN7/8      | 15/0.6       |

| MP9/10     | 6/0.6        | MN9/10     | 2/0.6        |

|            |              | MN11/12    | 120/1.2      |

Table 6. Transistor sizes of the differential comparator.