# A STUDY OF SIMULATION PERFORMANCE BASED ON EVENT ORDERINGS

HU YANJUN

# NATIONAL UNIVERSITY OF SINGAPORE

# A STUDY OF SIMULATION PERFORMANCE BASED ON EVENT ORDERINGS

HU YANJUN

(B. Sci., Peking University, China)

# A THESIS SUBMITTED FOR THE DEGREE OF MASTER OF SCIENCE DEPARTMENT OF COMPUTER SCIENCE NATIONAL UNIVERSITY OF SINGAPORE

ABSTRACT

### Abstract

A simulation protocol must adhere to a certain event ordering to produce correct simulation results. However, different event orderings exploit various degrees of parallelism and may require different amounts of memory. We have developed a formal methodology to predict the event parallelism and memory requirement of parallel simulation before implementation based on event orderings. This methodology was previously validated using limited queuing network benchmarks.

This thesis focuses on the study and validation of this methodology using a larger and more realistic application. We modeled and implemented an Ethernet network simulator and used it to study the effects of event orderings on simulation performance. The simulator is instrumented to obtain its event sequence and causal relationships, and various event orderings are analyzed using a time space analyzer that we have developed. The experimental results reveal that in a closed system, a weaker event ordering exploits more parallelism without increasing memory usage. We observed that in the Ethernet network simulator the upper bound on memory due to event orderings is 6n-8, where *n* is the number of stations. Apart from assessing the cost of event orderings, the methodology can also analyze the performance of a simulation problem and the overhead of implementation. To study the cost of implementation, we analyzed the conservative null message simulation protocol and observed that much more memory is required to support synchronization than for maintaining event orderings.

ACKNOWLEDGEMENT

### Acknowledgement

First, I would like to express my heartfelt thanks to my supervisor, Associate Professor TEO Yong Meng, for his supervision through this project. He has conscientiously provided me with careful guidance at every stage of my research, offered various ideas whenever I ran into difficulties, and constructively corrected some of my mistakes in the course of my work. I appreciate the fact that participating in his projects has granted me many paths to develop my research and analytical abilities greatly. His support enabled me to both learn and write what is presented in this thesis. In addition, he has given me constructive suggestions on my attitude to work, which is helpful to my career development.

Another person who has made many contributions to this thesis is Bhakti Stephen Onggo, a PhD student who is currently working on time and space analysis of parallel simulation. Every time when I had some problems in my research he would kindly offer his help to me. He explained certain difficult concepts and definitions concisely to me.

I would also say thanks to Dr. Gary S. H. TAN for he inspired my research interest in parallel and distributed systems in course CS5223 – distributed system. Hand-on experience gained in the course project gave me an advantage in this study.

Others that I would like to thank include Ng Yew Kwong, Hu Yu, Gozali Johan Prawira and Dr. Li Ming, whom I enjoyed sharing discussions on parallel simulation

ii

ACKNOWLEDGEMENT

and programming questions with.

In addition my sincere appreciation is given to my lab fellows, Ameya Virkar, Zhao Na, Zhang Gong, Liu Ming and Liu Peng for their generous help both in my research and in my life, and for the pleasant and friendly environment of the computer system lab.

Last but not least, I would like to convey my gratitude to the thesis examiners for taking time from their busy schedules to assess my research work.

# **Table of Contents**

| Abstract                                       | i    |

|------------------------------------------------|------|

| Acknowledgement                                | ii   |

| Table of Contents                              | iv   |

| List of Figures                                | vi   |

| List of Tables                                 | viii |

| Chapter 1 Introduction                         | 1    |

| 1.1 Parallel Discrete-Event Simulation         | 2    |

| 1.2 Related Works                              | 4    |

| 1.3 Event Ordering Based Approach              | 9    |

| 1.4 Research Contribution                      |      |

| 1.5 Thesis Overview                            |      |

| Chapter 2 Methodology                          | 20   |

| 2.1 Research Methodology                       | 20   |

| 2.2 Tools                                      | 24   |

| 2.2.1 CSIM                                     |      |

| 2.2.2 SPaDES/Java                              |      |

| 2.2.3 TSA                                      |      |

| 2.3 TSA Validation                             |      |

| 2.4 Summary                                    |      |

| Chapter 3 Ethernet Modeling and Implementation |      |

| 3.1 Problem                                    |      |

| 3.2 Simulation Model                           |      |

| 3.3 Simulation and Implementation              | 42   |

| 3.3.1 Sequential                               |      |

| 3.3.2 Parallel                                 | 51   |

| 3.4 Verification                               | 54   |

| 3.5 Validation                                 |      |

| 3.5.1 Sequential Simulation                                   | 57 |

|---------------------------------------------------------------|----|

| 3.5.2 Parallel Simulation                                     | 60 |

| 3.6 Events Instrumentation                                    | 60 |

| 3.7 Summary                                                   | 68 |

| Chapter 4 Experimental Results and Analysis                   | 69 |

| 4.1 Event Parallelism                                         | 69 |

| 4.1.1 Problem                                                 | 69 |

| 4.1.2 Event Orderings                                         | 72 |

| 4.1.3 Implementation                                          | 76 |

| 4.1.4 Relationship between Different Parallelisms             | 79 |

| 4.2 Memory Requirement                                        | 81 |

| 4.2.1 Problem                                                 | 82 |

| 4.2.2 Event Orderings                                         | 82 |

| 4.2.3 Implementation                                          | 87 |

| 4.3 Performance Tradeoff                                      | 90 |

| 4.4 Summary                                                   | 92 |

| Chapter 5 Conclusion                                          | 93 |

| References                                                    | 97 |

| Appendix A: Run-time Report of Pipeline Simulation            |    |

| Appendix B: Events in Pipeline Simulation                     |    |

| Appendix C: Pseudo Code of Ethernet Simulation in SPaDES/Java |    |

# **List of Figures**

| Figure 1.1: A typical simulation process13                                   |

|------------------------------------------------------------------------------|

| Figure 2.1: Research approach21                                              |

| Figure 2.2: Simulation executive main loop with TSA instrumentation29        |

| Figure 2.3: TSA validation methodology                                       |

| Figure 3.1: State transit diagram of an Ethernet station40                   |

| Figure 3.2: Processes and resources in simulation model of Ethernet          |

| Figure 3.3: Kernel class of Ethernet network simulation                      |

| Figure 3.4: A station class45                                                |

| Figure 3.5: Retransmission mechanism47                                       |

| Figure 3.6: A frame class49                                                  |

| Figure 3.7: Collision handler50                                              |

| Figure 3.8: Links in a 3-station Ethernet network                            |

| Figure 3.9: Sequential and parallel implementation of frame passing53        |

| Figure 3.10: Five types of events in Ethernet network simulator              |

| Figure 3.11: Control flow graph (CFG) of Ethernet simulator                  |

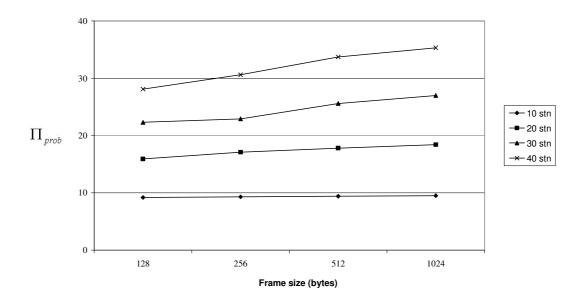

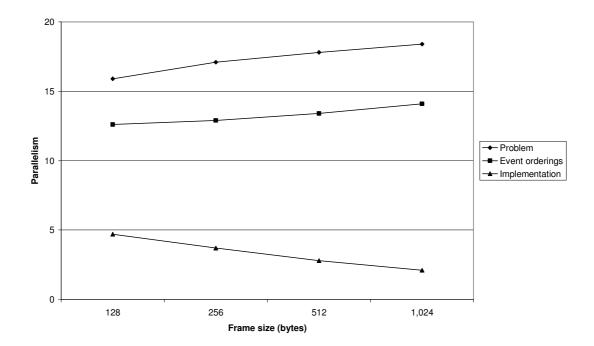

| Figure 4.1: $\Pi_{prob}$ for Ethernet                                        |

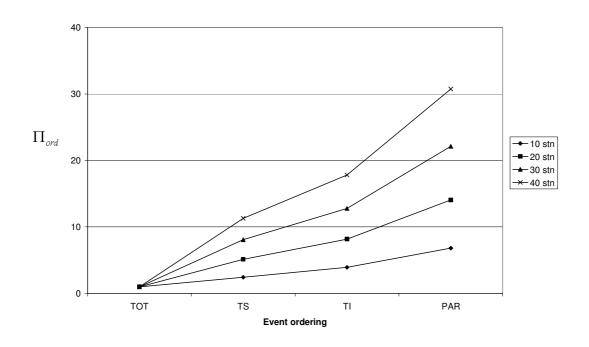

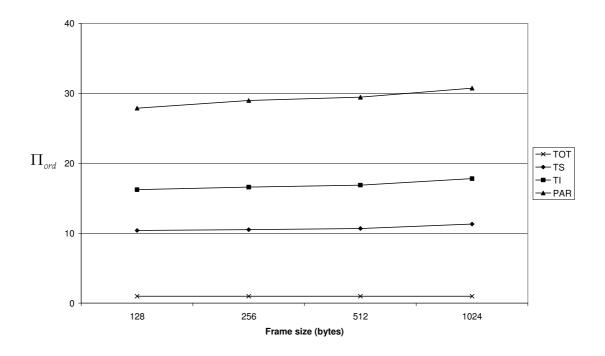

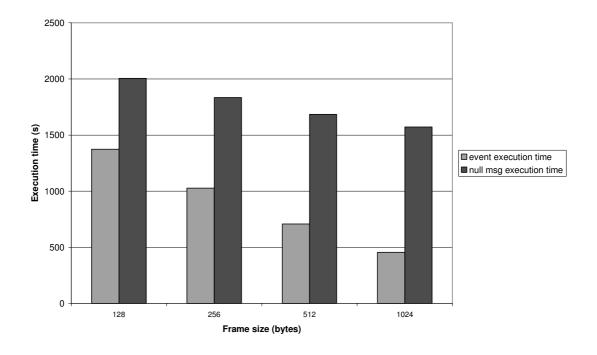

| Figure 4.2: $\Pi_{ord}$ changes with event orderings (frame size 1024 bytes) |

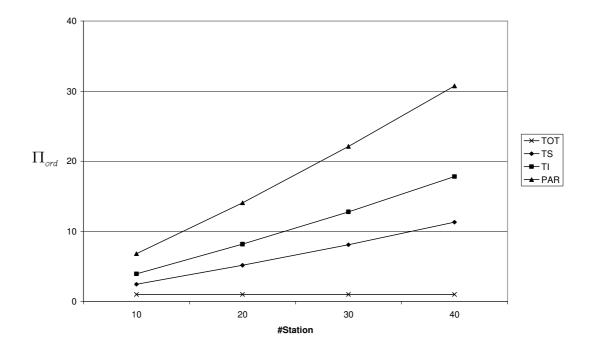

| Figure 4.3: $\Pi_{ord}$ changes with problem size (frame size 1024 bytes)74  |

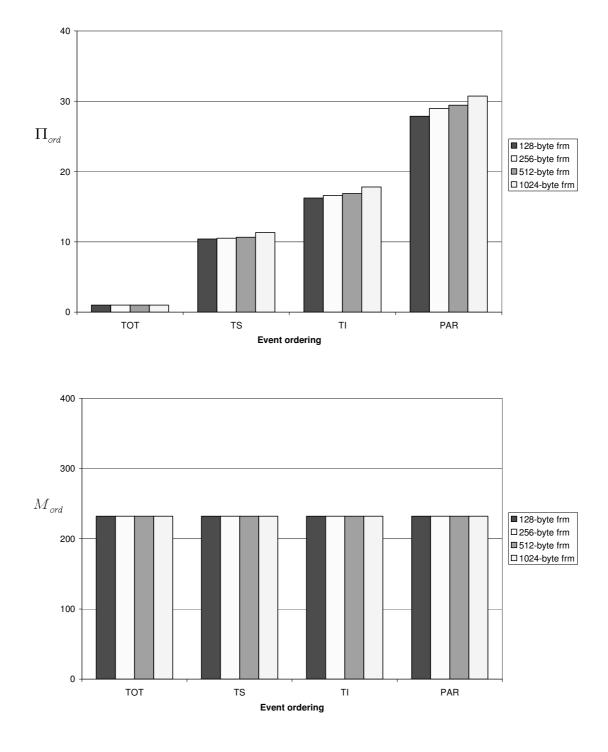

| Figure 4.4: $\Pi_{ord}$ changes with frame size (n=40)                       |

| Figure 4.5: $\Pi_{ord}$ changes with frame size (partial event order)        |

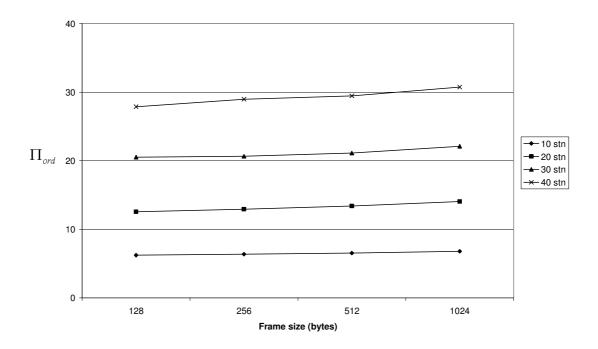

| Figure 4.6: $\Pi_{sync}$ for Ethernet                                        |

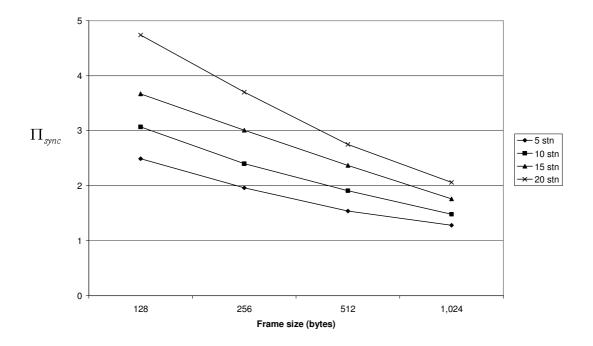

| Figure 4.7: Event and null message execution time changes with frame size | 79 |

|---------------------------------------------------------------------------|----|

| Figure 4.8: Relationships of different parallelisms (#station is 20)      | 80 |

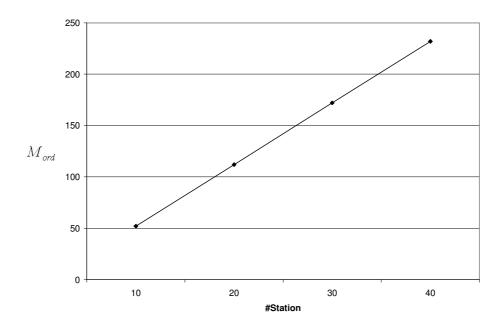

| Figure 4.9: $M_{ord}$ increases linearly with problem size                | 83 |

| Figure 4.10: Worst case scenario for total event ordering                 | 84 |

| Figure 4.11: Ethernet memory profile for partial event ordering           | 86 |

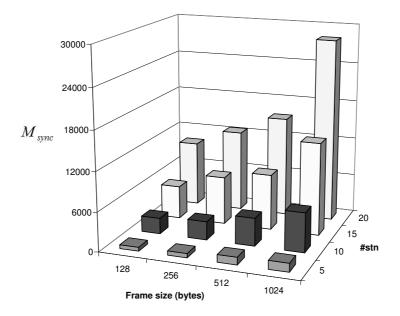

| Figure 4.12: $M_{sync}$ for Ethernet                                      | 87 |

| Figure 4.13: Time ( $\Pi_{ord}$ ) and space ( $M_{ord}$ ) tradeoff        | 91 |

# List of Tables

| Table 2.1: Event sequence with timestamps in Pipeline simulation                |

|---------------------------------------------------------------------------------|

| Table 2.2: Performance results of Pipeline simulation                           |

| Table 2.3: Causal relationships between events in Pipeline                      |

| Table 2.4: Event execution sequences for all event orderings in Pipeline        |

| Table 3.1: Validation of SPaDES/Java Ethernet simulator (fix value)       58    |

| Table 3.2: Validation of SPaDES/Java Ethernet simulator    59                   |

| Table 3.3: Event types and their scheduling information in Ethernet simulator65 |

| Table 4.1: $\Pi_{prob}$ for Ethernet                                            |

| Table 4.2: $\Pi_{ord}$ for Ethernet                                             |

| Table 4.3: $\Pi_{sync}$ for Ethernet                                            |

| Table 4.4: Comparison of three parallelisms in Ethernet simulation              |

| Table 4.5: $M_{ord}$ for Ethernet                                               |

| Table 4.6: $M_{sync}$ for Ethernet                                              |

| Table 4.7: Null message ratio changes with problem size    89                   |

| Table 4.8: Memory requirement of Ethernet simulation                            |

# **Chapter 1**

# Introduction

Two major methods are used to understand real world problems and applications: mathematics and simulation. Mathematics is a highly abstract method. It is general but lacks the detailed information of the real world applications. On the other hand, computer simulation is more application specific and can provide more detailed information that aids in the understanding of the behavior of the real world systems. Researchers in several areas like engineering, computer science, economics, and military applications are particularly interested in using simulation to study the potential behavior of some of their complex models prior to implementation [11].

Parallel simulation emerged with the development of parallel computer systems. However, parallel simulations introduce much complexity in the management of event synchronization and additional programming effort is required to exploit parallelism efficiently. Many synchronization protocols have been proposed to speedup parallel simulations but they incorporate different degrees of complexity [19, 27]. Synchronization protocols may need additional working memory to maintain event causality during execution. Memory management in parallel simulation is also a main research interest [16, 21, 38].

This chapter is organized as follows. We first introduce parallel discrete-event simulation (PDES). Next, we survey the related works on performance analysis of parallel simulation. We finally present our performance study methodology based on event ordering.

### **1.1 Parallel Discrete-Event Simulation**

PDES refers to the execution of a single discrete-event simulation program on a parallel computer [13]. In the past two decades, PDES has attracted a considerable amount of interest in the research community. This trend stems from the rapid development in parallel processing in the period, along with the fact that simulations involving large problem sizes and granularity often have poor performance when they are run on sequential machines. It represents a kind of problem that contains substantial amounts of parallelism but is very difficult to parallelize in practice.

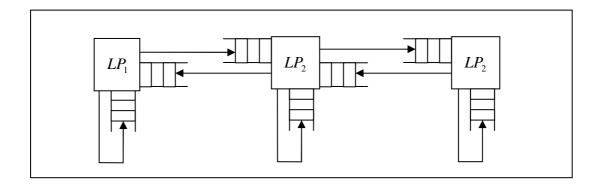

The use of logical processes (LP) [22] and virtual time [16] has separated PDES from other simulation categories. Most existing PDES implementation mechanisms use a process-oriented methodology that strictly forbids processes to directly access the shared state variables. Sequencing constraints must be maintained by these strategies. The physical system is viewed as being composed of some number of physical processes that interact at various points in simulated time. Hence the simulator is organized as a set of LPs. One or more LPs can be mapped to a physical

processor. All interactions between physical processes are modeled by time stamped event messages sent between the corresponding logical processes. Each logical process contains a portion of the state corresponding to the physical process it models, as well as a local clock that denotes how far the process has processed. The logical process methodology requires application programmers to partition the simulator's state variables into a set of disjoint states, and ensure that no simulator event directly accesses more than one state.

Simulation systems are divided into two categories in PDES: *synchronous* and *asynchronous*. In synchronous systems events are synchronized by a global clock. One iteratively determines which events are safe to process, and then processes them. Barrier synchronizations are used to keep iterations (or components of a single iteration) from interfering with each other. Because barrier synchronizations are necessary, these algorithms are best suited for shared memory machines in order to keep the associated overheads to a minimum [11]. However, in asynchronous systems events occur at irregular time intervals. Asynchronous LP simulation relies on the presence of events occurring at different simulated times that do not affect one another. Concurrent processing of those events thus effectively accelerates sequential simulation execution time.

PDES mechanisms generally fall into two categories of synchronization protocols: *conservative* and *optimistic*. Conservative mechanism executes only safe events. An LP blocks when no safe events can be executed. The typical conservative

protocol is CMB null message protocol [5]. The obvious drawback of conservative approaches is that they cannot fully exploit the parallelism available in the simulation problem. From the programmer's point of view, the most serious drawback of existing conservative simulation protocols is that the simulation programmer must be concerned with the details of the synchronization mechanism in order to achieve good performance. On the other hand, an optimistic mechanism allows an unsafe event to be executed. An error-detection mechanism is required to determine when an error has occurred, and then it will invoke a procedure to recover. One advantage of optimistic approach is that it can exploit parallelism in situations where causality errors may occur but actually do not. The typical protocol of optimistic mechanism is Time Warp [15]. Because optimistic mechanisms need to save system states frequently, they generally consume much more memory than conservative protocols.

Although PDES remains an active area of research, it has not achieved industrial widespread use [12]. There are several reasons for this fact. Firstly, the positive results will easily find their ways to publication, so we tend to see a biased picture. Secondly, the gained speedup is always attractive, but the effort spent on programming is also quite substantial. Finally the positive results usually can only be achieved by experts in certain fields.

### **1.2 Related Works**

Much effort has been exploited to analyze the *parallelism* of a simulator either

before or after parallel implementation [19, 27]. Performance analysis methods generally fall into the following three categories: *analytic method*, *simulation-based method* and *critical path method*.

Analytic methods usually use stochastic process, queuing theory or operational laws. Some kinds of Markov chains underlie these analyses [25]. Felderman and Kleinrock show that the average performance difference between synchronous and asynchronous algorithm is less than  $O(\log P)$  [8]. Tay et al. presents an analytical model for evaluating the performance of Time Warp simulators [35]. Wang et al. propose an analytical method to predict the parallelism of a simulation where causal relationship among events is considered [43]. In general, the analytic methods are faster than other methods, but the drawback is that it usually has unrealistic assumptions.

The second performance analysis method is based on simulation, which analyzes performance by directly simulating particular PDES protocols. Dickens and Reynolds develop a model to study the performance of a system synchronized by a windowing protocol [7]. The model extends the windowing protocol to allow computation of conditional events and predicts the probability of a causal error. Lim et al. describe three parallelism prediction tools for different synchronization protocols [19]. However, the tools can only be applied to some conservative protocols. Cavitt et al. propose a framework for identifying the factors affecting the performance of simulation [4]. The identified factors can in turn give feedbacks to

simulation hardware/software configuration. Marin et al. devise a simple automated methodology to predict running time cost of discrete-event simulation [23]. However, the methodology can only be used for BSP (Bulk-Synchronous Parallel) model. Teo et al. concentrate on the performance analysis on a particular simulation library SPaDES/C++ [36]. Rawling et al. analyze an existing sequential simulation in order to predict concurrency speedup bounds for conservative parallel simulation [29]. The model is based on real commercial VLSI simulations. Noble et al. explore the performance of three synchronous discrete-event simulation algorithms: global clock algorithm, conservative look-ahead algorithms and speculative computation algorithm [26]. De Carvalho Klingelfus et al. developed an object oriented Ethernet network simulation and model system to aid in the activity of element measurements, error detection and performance analysis [6]. In summary, simulation-based method usually uses one particular protocol or one particular category of protocols to model applications. They require fewer assumptions than analytical method, but the method has only limited usage, for there are so many protocols and applications to be simulated.

Critical path analysis simulates event execution based on causal relationship and builds critical path to analyze the simulation performance. Wong et al. proposes a critical path-like analyzer to predict the memory used in a Chandy-Misra simulation [48]. The analyzer can derive the parallelism directly from a path-like analyzer. Lim et al. use a critical path analyzer to give the ideal maximum speedup for a simulation model [19]. The critical path analysis assumes each physical processor to be an

independent LP and there is unlimited number of processors. Wieland et al. use a new technique to determine the critical path [46]. A metric called the earliest process time (EPT) can be implemented either as a centralized algorithm or a distributed algorithm. Critical path analysis is easy to understand but it cannot be used to compare different protocols.

Fujimoto states that the performance of conservative strategies is closely related with the degree to which processes can look ahead and predict future events [11]. For optimal protocols, state-saving overhead can seriously degrade performance. In addition, optimistic algorithms usually use more memory than conservative ones.

Parallel simulation provides the potential to speedup simulations, but additional memory is required by the parallel synchronization protocols. Specifically, for conservative protocols, the additional memory is required to hold the null messages. Optimistic protocols require additional memory to save the simulation states periodically for possible rollback. Every processor in parallel simulation has only limited space, so memory consumption is also an important issue that we should address.

There are many publications on the *space* aspect of parallel simulation [16, 21, 38]. But most publications concentrate only on the space management of some particular synchronization protocols. For conservative approaches, much effort is done to reduce the number of null messages, such as demand-driven null message algorithm presented in [1]. For optimistic approaches, the focus is on reducing

optimism while limiting the usage of space. The "artificial rollback" in [21] is such an example. Many researchers examine the storage utilization of optimistic mechanisms such as Time Warp. To support rollback, it is necessary to save the old states of a logical process but there is no need to save the "ancient history" [13]. Hence these memories can be reutilized to save new state vectors. Several approaches have been proposed to limit the amount of memory that is required to perform the simulation in Time Warp.

The first one is fossil collection and global virtual time (GVT) [50]. The smallest timestamp among all unprocessed event messages is called GVT. No event with timestamp smaller than GVT will ever be rolled back, so storage used by such events can be discarded. In addition, irrevocable operations (I/O for example) cannot be committed until GVT passes the simulated time at which the operation occurs.

The second approach is incremental and infrequent state savings. In conjunction with fossil collection, there are many other mechanisms to save more memory. When the state vector is large and only a part of it is modified by each event, incremental state saving may be useful. Only changes to the state are recorded to reduce both memory utilization and copying time. A drawback of this mechanism is that the rollbacks become more expensive. An alternative approach is to save entire state vectors, but reduce the frequency of state saving [20]. It decreases the time required to perform state saving, but increases rollback overhead. This tradeoff suggests that there may be an optimal state saving frequency that balances state saving overhead

and re-computation costs [28].

The next method is rollback-based recovery mechanisms. With the aforementioned mechanisms, when the system does run out of memory, there is no recourse but to terminate the simulation. It is problematic because the "fault" may lay with the Time Warp mechanism itself rather than the application program. Several approaches have been developed to address this concern. Such mechanisms include cancel-back [16] and artificial rollback [21] algorithm.

The last method is to limit memory by using the protocols with limited optimism. If the simulation mechanism is too optimistic in executing the program, then the program, as a result, will run out of memory. There are emerging approaches that use limiting optimistic protocols [49].

### **1.3 Event Ordering Based Approach**

Simulation protocols maintain a certain event ordering to produce correct simulation results. Ordering of concurrent events in discrete-event simulation is an important issue as it has an impact on modeling expressiveness, model correctness and causal dependencies [32]. In sequential simulation, only one event ordering is maintained by global FEL. In parallel simulation, every LP maintains its own FEL and many events can be executed simultaneously. Synchronization protocols order the events in an appropriate manner to guarantee that no causality errors occur. Different event orderings are allowed to generate correct simulation results, but they

give different degrees of parallelisms. In addition, each LP needs extra memory to keep track of pending events in its future event list (FEL) to follow a certain event ordering. Therefore different event orderings may require different amounts of memory.

Teo et al. have developed a formal methodology to study how event ordering influences the performance of parallel simulation [40]. The methodology can predict the performance of parallel simulation before it is actually implemented. It executes events based on causal relationship and event ordering to analyze event parallelism and memory requirement of a simulator. It can compare the performance between different event orderings, which is more general than simulation-based methods. Because event orderings, not synchronization protocols, are taken into account, the methodology requires less implementation than simulation-based performance analysis methods.

Four simulation event ordering rules are formally defined with partial order set theory: *total event ordering*, *timestamp event ordering*, *time interval event ordering* and *partial event ordering* (Axiom 1 to Axiom 4).

**AXIOM 1:** Let  $\langle E, <_{par} \rangle$  be a poset, where E is a set of events. Under partial event ordering,  $e_1$  happens before  $e_2$  (denoted by  $e_1 <_{par} e_2$ ), if:

- $\neg (e <_{par} e)$ , for any event  $e \in E$ ;

- $e_1$  and  $e_2$  are events in the same process, and  $e_1$  comes before  $e_2$ ;

- e<sub>1</sub> is the sending event in process P<sub>1</sub>, and e<sub>2</sub> is the corresponding receiving event in process P<sub>1</sub>;

- *if*  $e_1 <_{par} e_2$  and  $e_2 <_{par} e_3$ , then  $e_2 <_{par} e_3$ .

**AXIOM 2**: Let  $\langle E, <_{par} \rangle$  be a poset, where E is a set of events. Assume that each  $e \in E$  can be stamped with a simulation time (denoted by ts(e)). Under total event ordering,  $e_1$  happens before  $e_2$  (denoted by  $e_1 <_{tot} e_2$ ), if:

- $ts(e_1) < ts(e_2), or$

- $ts(e_1) = ts(e_2) \land e_1$  has higher priority than  $e_2$ .

**AXIOM 3**: Let  $\langle E, <_{par} \rangle$  be a poset, where E is a set of events. Assume that each  $e \in E$  can be stamped with a simulation time (denoted by ts(e)). Under timestamp event ordering,  $e_1$  happens before  $e_2$  (denoted by  $e_1 <_{ts} e_2$ ), iff  $ts(e_1) < ts(e_2)$ .

**AXIOM 4**: Let  $\langle E, \langle e_{par} \rangle$  be a poset, where E is a set of events. Suppose that the simulation duration can be divided into mutually exclusive time windows,  $\{W_1, W_2, ..., W_n\}$ , where  $W_i = W_j$  iff i=j. Assume that each  $e \in E$  can be placed in a  $W_i$  with base time denoted by tw(e). Under time interval event ordering,  $e_1$  happens before  $e_2$  (denoted by  $e_1 <_{ti} e_2$ ), iff tw( $e_1$ ) < tw( $e_2$ ).

The definitions in Axiom 1 and Axiom 4 are consistent with those by Lamport in [17] where "happened before" relation is the same as partial event ordering. For Axiom 1, e1 happens before e2 because the sending event will causally affect e2. Partial event ordering is anti-symmetric, so if that e1 is a receiving event and e2 is the corresponding sending event, e2 will happen before e1 [40].

The event orderings in decreasing order of *strictness* are *total event order*, *timestamp event order*, *time-interval event order* and *partial event order*. The detailed definition of event orderings and proof of their strictness are illustrated in [40]. The main difference among these four event orderings lies in the definition of concurrent event. The methodology can be applied to all event orderings as long as they are well defined.

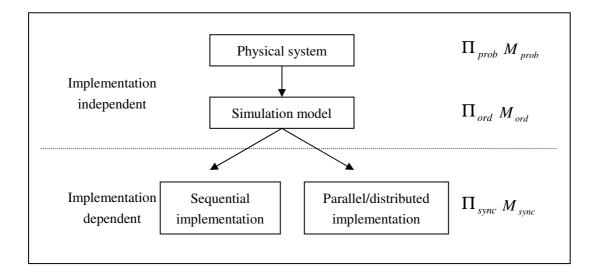

The methodology is based on the typical steps of a simulation. A computer simulation is a program that emulates the behavior of another system. A typical modeling and simulation process contains three steps: *physical system, simulation model* and *implementation model* as shown in Figure 1.1. Physical system represents the real-world problem that one simulates. A simulation model is a logical model of a physical system that defines the input parameters, output results, and other physical system components to be simulated. There are three world views in simulation model: *event oriented, process oriented* and *activity scanning* [13]. The physical system and simulation model is independent of the implementation. Either sequential or parallel implementation needs to be built on the simulation model.

Figure 1.1: A typical simulation process

We divide the memory required by a simulator into three main parts:  $M_{prob}$ ,  $M_{ord}$  and  $M_{sync}$ .  $M_{prob}$  denotes the memory to model the states of the physical system,  $M_{ord}$  denotes the memory required by future event list (FEL) to schedule event execution based on the selected event ordering, and  $M_{sync}$  denotes the additional amounts of memory to implement a synchronization protocol on a specific execution platform. Therefore, the total memory requirement of implementing a simulation model on real machines with a particular implementation is  $M_{orb} + M_{ord} + M_{sync}$  [40].

We measure  $M_{prob}$  by observing the queue size, and its upper bound is defined as the total maximum queue length, i.e.,  $M_{prob} \leq \sum_{i=1}^{n} Q_i$ , where  $Q_i$  is the maximum queue size at service center *i*, and *n* is the number of service centers. For simplicity, we only count the entry number for the queue. The actual  $M_{prob}$  is dependent on the data structure of queue implementation.  $M_{ord}$  depends on the characteristics of system under study, i.e., event arrival and service rates, and the event ordering adopted. The upper bound of  $M_{ord}$  is defined as the sum of all FEL lengths, i.e.,  $M_{ord} \leq \sum_{i=1}^{n} FEL_i$ , where  $FEL_i$  is the maximum FEL size at service center *i*, and *n* is the number of service centers. The actual value of  $M_{ord}$  is dependent on the implementation of FEL.

$M_{sync}$  accounts for the additional memory used for synchronization. For sequential implementation,  $M_{sync} = 0$ . In optimistic protocol, memory is required for state saving in anticipation of rollbacks. In the case of the null message protocol, it can be defined as the total of the maximum buffer sizes required for maintaining null messages. Therefore, for the conservative null message parallel simulation used in SPaDES/Java [41], we can define  $M_{sync} \leq \sum_{i=1}^{n} NMB_i$ , where  $NMB_i$  is the maximum null message buffer size at  $LP_i$ , and *n* is the total number of LPs involved in the simulation.

*Event parallelism* is defined as the average number of events executed per unit time. Average event parallelism ( $\Pi$ ) is different from speedup here. The range of  $\Pi$  is [1, $\infty$ ]. All events are assumed to take the same execution time and we need to specify what one unit time is.

For sequential simulation the average event parallelism is one. However, different types of events may take different execution time. When a sequential simulation is mapped to the parallel environment, events can be executed

simultaneously at different processors. The number of events per unit time will increase, thus the parallelism will be larger than one for parallel simulation. However, parallel simulation needs additional overhead for synchronization, such as null message, which will decrease the parallelism.

Similar to the memory classification, the average event parallelism of a simulator is also studied at three steps, namely: physical system, event ordering, and implementation [27]. In the physical system level, events may happen concurrently. Hence, physical system has parallelism which is called the *inherent event parallelism* ( $\Pi_{prob}$ ). Discrete-event simulation compresses simulation time by applying a certain event ordering. Different event orderings exploit different degrees of event parallelism which is called *event ordering parallelism* ( $\Pi_{ord}$ ). The communication overhead and other implementation overhead are neglected, so event ordering parallelism is optimal. At the implementation level, maintaining a certain event ordering on a specific platform requires addition overhead of synchronization. We refer this parallelism as the effective event parallelism ( $\Pi_{sync}$ ).

Inherent event parallelism ( $\Pi_{prob}$ ) refers to the parallelism that exists in the physical system. It is mainly determined by physical system factors, the traffic intensity for example. In a physical system some service centers can execute events concurrently. The dependency between events influences the inherent event parallelism. Less dependency between events gives higher parallelism. The topology between service centers can influence the inherent event parallelism because it will

influence the dependency between events [27].  $\Pi_{prob}$  is measured from an analytical method and it is defined as the sum of all LPs' utilization, i.e.,  $\Pi_{prob} = \sum_{i=1}^{n} U_i$ , where  $U_i$  denotes the utilization of  $LP_i$ . Teo et al. has proved the measurement from a common measure of program parallelism [37]

Different event ordering exploits different degrees of event parallelism. This parallelism is referred to as  $\Pi_{ord}$ . As mentioned before, four simulation event orderings are defined in the methodology representing four different degrees of parallelism, i.e. *total event ordering, timestamp event ordering, time-interval event ordering* and *partial event orderings*. This work can be extended to include other event orderings. Both causal restriction and event ordering rules are considered in the measurement of  $\Pi_{ord}$ . The detailed measurement of  $\Pi_{ord}$  is presented in Chapter 2 when we present the implementation of the methodology.

At the implementation level, maintaining a certain event ordering on a specific execution platform requires synchronization overhead, hence the implementation may reduce  $\Pi_{ord}$ . We call this parallelism the effective event parallelism  $\Pi_{sync}$ . Both of the implementation algorithm and execution platform (processor, network, operating system, etc) may affect  $\Pi_{sync}$ .  $\Pi_{sync}$  is measured from the actual simulation and the detailed measurement is presented in Chapter 2.

It is known that the total communication time or cost is dependent on the interconnection topology of processors (LPs) used in parallel simulation. The effects

of interconnection topology of a physical system on exploitable event ordering parallelism are studied at [27]. Four synthetic benchmarks representing basic queuing network topologies are implemented and studied: Linear Pipeline, Pipeline with Feedback, Circular Pipeline and PHOLD. It is found that feedback channel reduce  $\Pi_{ord}$  that can be exploited by relaxing the event ordering, i.e. the physical system limits the amount of  $\Pi_{ord}$  exploitable by parallel simulation.

The degree of event parallelism is related to the granularity that the number and size of events or tasks into which a problem is decomposed. The formal methodology studies the performance (event parallelism and memory requirement) from three levels. At the event ordering level, we study the performance of parallel simulation with different event orderings. Each event is assumed to take one unit time to execute.  $\Pi_{ord}$  is independent of the implementation. At the implementation level, the granularity is considered and we normalize the event execution time to the average execution time as presented in section 2.1.

### **1.4 Research Contribution**

It is essential to understand the degree of event parallelism *before* substantial programming effort is invested to develop a simulator [36]. If there is low degree of parallelism in the system, the performance benefits of exploiting parallelism will be low. In addition, every processor in a parallel system has only limited space capacity. Therefore, it is also important to predict the memory consumption of a parallel simulation before implementation. Teo. et al develop a performance analysis

framework – time space analyzer (TSA) tool which implements performance analysis based on event orderings [40, 42]. The methodology has previously been validated with several limiting queuing network benchmarks such as LPIPE and PHOLD.

In this thesis, we use a realistic application, Ethernet network, to further study and validate the methodology. Our performance results are consistent with the existing results [27, 40], i.e., a weak event ordering gives higher parallelism without increasing memory usage in a closed system. Apart from assessing the cost of event orderings, the methodology can also analyze the simulation performance of a simulation problem and the overhead of implementation. To study the cost of implementation, we analyzed the conservative null message simulation protocol and observed that much more memory is required in implementation than for maintaining event orderings. The relationship among performance results of these levels is also discussed in this thesis.

### **1.5 Thesis Overview**

The rest of this thesis is organized as follows:

Chapter 2 introduces our overall research methodology. We introduce the implementation and validation tools used in our research, including CSIM, SPaDES/Java, and TSA. We also validate TSA in detail with a simple Pipeline example.

Chapter 3 introduces Ethernet network modeling and its implementation. Ethernet network is introduced through three steps: physical system, conceptual model and implementation. We specify the processes and resources in Ethernet network simulator at the conceptual model. At implementation level, both the sequential and parallel simulator are implemented and validated. Lastly, we instrumented Ethernet network simulator to obtain event sequence, which will be analyzed by TSA.

Chapter 4 illustrates the experimental results and analysis. Both time (event parallelism) and space (memory requirement) are characterized at three levels: physical system, event ordering and implementation. We also compare and discuss the relationship among three levels. Next, the performance tradeoff is analyzed.

Chapter 5 concludes the thesis and discusses future work.

# Chapter 2

# Methodology

We discuss our research methodology in this chapter. An analytical method is used to analyze the inherent event parallelism. TSA is used to analyze event parallelism and memory requirement for different event orderings. We modeled and implemented the Ethernet network simulator using the SPaDES/Java simulation library and studied its performance. The implementation and validation tools used include CSIM, SPaDES/Java, and TSA. TSA is validated in detail using a simple Pipeline example.

### 2.1 Research Methodology

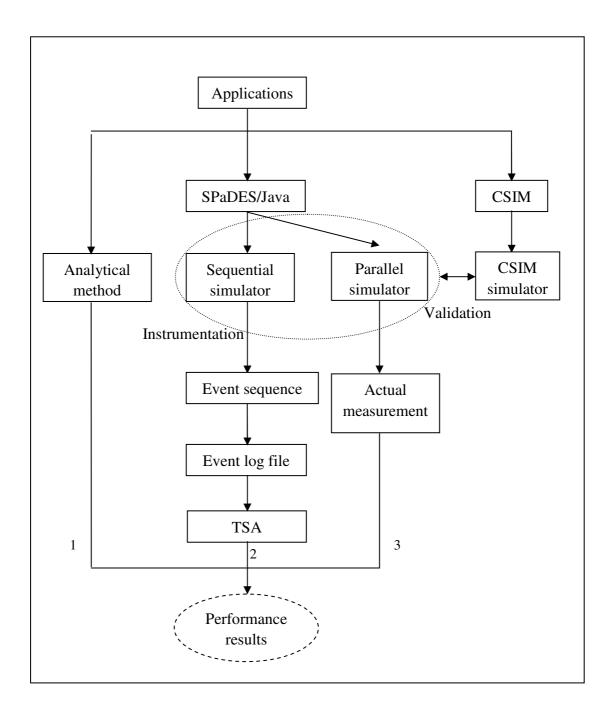

Figure 2.1 illustrates our overall research approach. The performance results contain three steps. In step 1, we use an analytical model to obtain the inherent event parallelism of a problem. In step 2, we use TSA to derive event parallelism and memory requirement for different event orderings. Step 3 measures effective event parallelism and memory for synchronization from the actual simulation.

Figure 2.1: Research approach

As presented in Chapter 1, the inherent event parallelism  $(\Pi_{prob})$  is measured in terms of the sum of processors' utilization. For an open system, the utilization of a service center is defined as  $\lambda/\mu$ , where  $\lambda$  is its arrival rate and  $\mu$  is its service rate. The utilization of an LP can also be calculated by the ratio of its mean *service*

time to mean inter-arrival time.

For a closed system, such as Ethernet network, we can apply mean value analysis (MVA) [14] to analyze the queuing characteristics of the problem. MVA uses a number of fundamental queuing relationships to determine the mean values of throughput, delay and queue size for closed queuing networks. Unlike the service centers with finite service units, Ethernet network nodes are delay servers (centers) where

- Infinite servers/dedicated servers queues on a service center;

- There is no waiting time but only service time for a service center.

Hence the mean response time is equal to mean service time for a delay center.

$$Q_i = X_i R_i = X_i S_i = U_i$$

where  $Q_i$  is the average queue size,  $X_i$  is the throughput,  $R_i$  is the mean response time,  $S_i$  is the mean service time and  $U_i$  is the utilization of an LP. We can observe that the utilization of a delay center is the mean number of jobs receiving service. Therefore, the utilization of a delay center is equal to its average service rate.

In step 2, a sequential Ethernet network simulator is developed using the SPaDES/Java simulation library. We obtain the event sequence and causal relationships from instrumentation of sequential Ethernet network simulator. All

CHAPTER 2 METHODOLOGY

events are then recorded in an event log file. Every event is recorded with its detailed information, such as event type, timestamp, the location, etc. The event sequence are analyzed by TSA to derive event ordering parallelisms ( $\Pi_{ord}$ ) and memory requirement ( $M_{ord}$ ).

The CSIM simulation library is used to validate our model and implementation. If Ethernet network simulation is developed correctly using SPaDES/Java, it will produce the same simulation results as the one developed by CSIM [45].

In step 3, we implement the parallel Ethernet network simulator using the SPaDES/Java simulation library. A conservative null message simulation protocol is used to synchronize the parallel execution on different LPs. We measure the actual execution of the parallel simulator to obtain the memory requirement for synchronization ( $M_{sync}$ ), which is measured as the sum of maximum null message buffer sizes in all LPs.

The effective event parallelism ( $\Pi_{sync}$ ) is also measured from the actual simulation. When event ordering parallelism is measured, we assume an event is executed in one unit time and thus all events take the same execution time. However, in actual simulation different types of events may have various execution times. With reference to this, we measure the unit time ( $T_{unit}$ ) as the average event execution time.

The execution time of an LP in a parallel SPaDES/Java simulation includes the

following several parts:

- Time used to execute event messages;

- Time used to execute null messages;

- Communication delay, time used to wait for messages from other LPs;

- Other delays.

The null messages and other execution delays are incurred due to the additional implementation overhead. Quite a lot of factors may affect the event parallelism at implementation level. To simplify the measurement, we consider only the execution of events and null messages when measuring the execution time of an LP. From the definition of event parallelism, average number of executed events per unit time, we get the measurement of the effective event parallelism as follows:

$$\Pi_{sync} = \frac{\#Events}{\binom{T}{T_{unit}}}$$

(Eq. 2.1)

where #Events is the number of all events in the problem and T is the execution time (events and additional null messages) of the LP which has the longest execution time compared to the others.

### 2.2 Tools

The following tools are used in this study. The Ethernet network simulation is written in SPaDES/Java and it is validated by CSIM. TSA analyzes the simulation

performance for different event orderings.

### 2.2.1 CSIM

CSIM is a simulation library in C language by Watkins [45] and it supports three simulation worldviews, namely, *event scheduling*, *three phase event scheduling* and *process interaction*. Three phase approach is different from event scheduling approach by specifying the conditional events and scanning them in a new phase. C has two major advantages over many other languages: *portability* and *availability*.

Objects in the real system are modeled in terms of entities and resources in CSIM simulation library. *Entities* present active objects in the system such as customers or processors. Entities have a close affiliation with events because they are active. Entities are usually involved in several activities. A *resource* in the real-world systems is usually some form of reusable asset such as the amount of free storage in a computer system or a checkout in a supermarket. The principal characteristic of a resource is that it has only limited capacity.

A simulator developed by CSIM usually has a better performance in comparison with one by other simulation libraries. This is due to the higher efficiency of the C language. However, CSIM does not support parallel simulation, so we cannot measure effective event parallelism ( $\Pi_{sync}$ ) and memory for synchronization ( $M_{sync}$ ).

#### 2.2.2 SPaDES/Java

SPaDES/Java (Structured Parallel Discrete-Event Simulation in Java) is an object-oriented modeling toolkit for general-purpose simulations [41]. The synchronization processes and mechanism are hidden from the simulationists. It supports both sequential and parallel simulation. Parallel event synchronization is facilitated through a hybrid carrier-null, demand-driven flushing conservative null message mechanism.

The SPaDES system adopts the approach of augmenting a general-purpose language with essential constructs to support simulation modeling based on the process-oriented modeling technology. The simulation programmer can concentrate on modeling and be lifted from the burden of programming the complicated event synchronization protocol and message passing mechanism.

SPaDES adopts a modified process-interaction modeling view called *process-oriented* modeling view. In this view, entities in the real world are viewed as a set of processes each encapsulating its own state and behaviors, and processes interact with one another through message passing. Furthermore, it is necessary for a process-oriented model to be mapped to an operational model that is suitable for parallelization. The operational model of SPaDES is based on the virtual time paradigm [16].

In the process-oriented view, real-world entities are categorized into permanent

CHAPTER 2 METHODOLOGY

and *temporary* entities. A permanent entity, modeled as a *resource*, exists throughout the simulation duration. A temporary entity, modeled as a *process*, is a process that can be created dynamically at any point during the simulation and thus does not exist throughout the simulation duration. A *process* can be in some states during its entire simulation lifetime. In the operational model, resources are modeled as LPs and processes are modeled as time-stamped event messages passed between LPs. SPaDES/Java adopts RMI library to facilitate the message passing between processors.

Resources are the permanent simulation entities present to provide services to the active processes upon request. Each resource comprises of a default FIFO queue, created when the resource is constructed, and whose function is to maintain the arrival of processes to the resource according to their timestamp values, followed by event priority. Each resource is really a collection set of *service units*, which is the basic functional unit of a resource. When an active process requests for service at any particular resource, the total number of service units required must be explicitly mentioned. SPaDES/Java implements all the event lists using *binary min-heaps*. The time complexity for inserting and removing a message is  $O(\log n)$ .

Using Java as the base language, SPaDES/Java is portable across all platforms. It can support parallel simulation, so we can measure  $\Pi_{sync}$  and  $M_{sync}$ . SPaDES/Java is object-oriented, which facilitates the program development and maintenance. However, one drawback of SPaDES/Java is that its performance is

27

worse than CSIM. Java's platform independence requires a Java virtual machine to run on the local machine, thus sacrificing some degree of its performance. However, in comparison with CSIM, SPaDES/Java is a better choice for our implementation.

# 2.2.3 TSA

Teo et al. originally implement TSA in C [40]. It can be instrumented to a simulator by CSIM to derive the performance results. TSA measures  $M_{prob}$ ,  $M_{ord}$ , and  $\Pi_{ord}$  by analyzing the event sequence provided by a simulator. Java version TSA is the translation of original C version TSA [42]. Java version TSA can be instrumented to a simulator in SPaDES/Java.

TSA is designed to measure the performance results for different event orderings. The input of TSA is an event sequence with its causal relationships from simulator. Every event is recorded with its event type, its location and timestamp. Event sequence is stored in a doubly-linked list. Because event sequence is obtained from a sequential simulator, the events are automatically sorted by their timestamp.

Events are fetched into TSA in the order they are executed in a sequential simulator. TSA executes these events in parallel by following a particular event ordering. Each event is assumed to execute in one unit time. Figure 2.2 shows the main loop in a sequential simulator with TSA instrumentation. The simulator invokes TSA for each event that is removed from the future event list. Typically a simulator advances its virtual time to the event's timestamp. We record the event information (line 5) and then write the event to a log file or schedule it to the TSA routine (line

6).

```

1. While <<simulation is running>>{

2.      <<remove top event e from future event list>>;

3.      execute(e);

4.      simulation_clock=timestamp of e;

5.      TSA_record(e);

6.      TSA_schedule(e);/event_log(e);

7. }

```

Figure 2.2: Simulation executive main loop with TSA instrumentation

TSA has two options to analyze event sequence: (a) It executes in parallel with the simulation with one event scheduled to TSA immediately when the simulation executes it; (b) TSA executes after the simulation by fetching events from a log file and works as a post-execution instrumentation analyzer. We adopted the latter option. For a large simulation that has a large execution time, we run the simulation once. The event log file is used by TSA many times without rerunning the simulation. Another benefit is that the event log file can be used to validate the instrumentation.

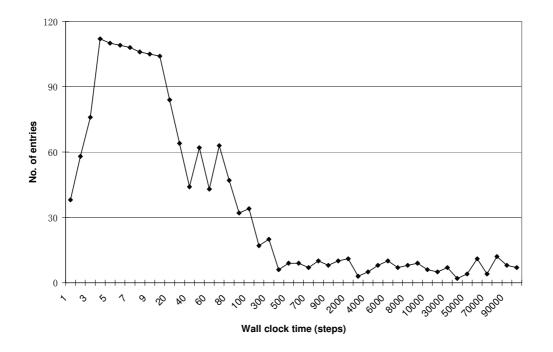

When TSA is initialized, it sets up four instrumentation classes representing four simulation event orderings. Each class maintains two arrays: maxFEL and maxCEL, with n slots, where n is the problem size. These two arrays keep track of the maximum lengths of the FEL and CEL of each LP throughout the simulation. Each class also records the critical path length. When the TSA-instrumented simulator is running and a new customer arrives in the system, or an event has been scheduled in a particular LP, a new *event* is created to record this change in state of the simulator. When all LPs have at least one event in its event list, TSA advances its time by one

time unit, i.e., increasing the critical path by one, and execute the top events according to the defined event ordering rule.

After all events are analyzed, TSA computes  $M_{prob}$ ,  $M_{ord}$  and  $\Pi_{ord}$  as defined below:

$$M_{prob} = \sum_{i=1}^{n} \max CEL_{i}$$

$$M_{ord} = \sum_{i=1}^{n} \max FEL_{i}$$

$$\Pi_{ord} = \frac{\#events}{critical\_path\_length_{ord}}$$

where #events is the number of all events and  $critical_path_length_{ord}$  is the critical path length of a particular event ordering.

# 2.3 TSA Validation

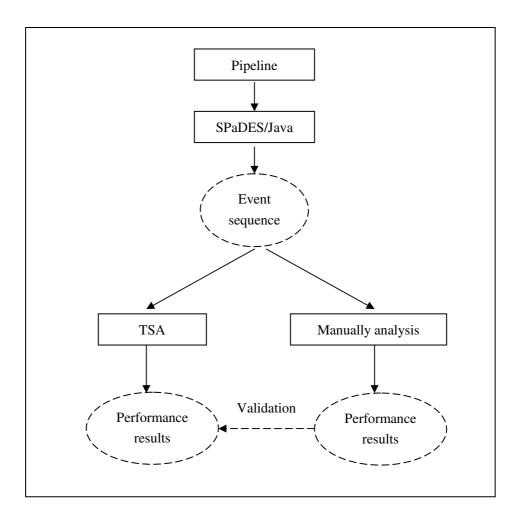

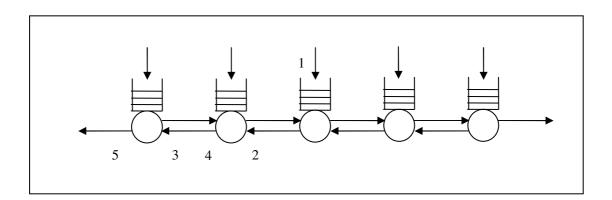

We validated TSA before it is used to analyze performance results. A simple linear Pipeline (PL) example is used to validate TSA. PL is manually analyzed and the corresponding event sequence is stored into an event log file. The causal relationships between events and other event information are recorded in the file. The file is small enough for us to analyze event sequence and manually derive the performance results. Then the results are compared with the results generated by TSA. Figure 2.3 illustrates our validation methodology.

Figure 2.3: TSA validation methodology

A 2-LP Pipeline example is used as our validation program. A laundry with wash point  $(LP_0)$  and dry point  $(LP_1)$  is such an example. There are four event types in linear Pipeline: external arrival, internal arrival, external departure and internal departure. Four messages are modeled to flow through the pipeline. The inter-arrival-time is fixed to 7 time units and the service time in one LP is set to 8 time units. *Message*<sub>0</sub> is scheduled to enter  $LP_0$  at simulation time 1. The runtime information is listed in Appendix A, which is a "trace" of a simulation.

| Message              | External                 | Internal                 | Internal                   | External     |

|----------------------|--------------------------|--------------------------|----------------------------|--------------|

| ID                   | Arrival at               | Departure                | Arrival at                 | Departure    |

|                      | $LP_0$                   | from $LP_0$              | $LP_1$                     | from $LP_1$  |

| message <sub>0</sub> | $e_1: 1$                 | <i>e</i> <sub>3</sub> :9 | <i>e</i> <sub>4</sub> :9   | $e_6: 17$    |

| $message_1$          | <i>e</i> <sub>2</sub> :8 | $e_7: 17$                | <i>e</i> <sub>8</sub> : 17 | $e_{10}: 25$ |

| message <sub>2</sub> | $e_5:15$                 | $e_{11}: 25$             | $e_{12} 25$                | $e_{15}:33$  |

| message <sub>3</sub> | $e_9:22$                 | $e_{13}:33$              | $e_{14}:33$                | $e_{16}:41$  |

Table 2.1: Event sequence with timestamps in Pipeline simulation

Table 2.1 lists all the sixteen events with time stamps generated from PL simulation. Every event is recorded with its message ID, timestamp, location, Event type, next location and the antecedent event information as required by TSA. Appendix B lists the detailed event information for all sixteen events in the log file.

According to aforementioned measurement,  $M_{prob}$  is the sum of maximum CEL lengths (*maxCEL*) of all LPs,  $M_{ord}$  is the sum of maximum FEL lengths (*maxFEL*) of all LPs and  $\Pi_{ord}$  is the ration of the number of events to the critical path length of a particular event ordering. The results of  $M_{prob}$ ,  $M_{ord}$  and  $\Pi_{ord}$  for PL are listed at Table 2.2.

| Event ordering | $M_{prob}$ | $M_{\it ord}$ | Critical path length | $\Pi_{\mathit{ord}}$ |

|----------------|------------|---------------|----------------------|----------------------|

| Partial        |            | 3             | 10                   | 1.60                 |

| Time interval* | 2          | 3             | 11                   | 1.45                 |

| Time stamp     |            | 3             | 12                   | 1.33                 |

| Total          |            | 3             | 16                   | 1.00                 |

\*window size of time interval event ordering is 2 time units

Table 2.2: Performance results of Pipeline simulation

Because  $message_1$  should wait in CEL [0] for the  $message_0$  to depart from

$LP_0$ , the maxCEL[0] is equal to 1. Message<sub>2</sub> should wait in CEL[1] for message<sub>1</sub> to depart from  $LP_1$ , so maxCEL[1] is equal to 1. Thus  $M_{prob}$  is the sum of maxCEL[0] and maxCEL[1], which is 2. When a new message arrives at  $LP_0$ , it will schedule its internal departure and next message's external arrival, so maxFEL [0] is equal to 2. Arrival at  $LP_1$  can only schedule one departure event, so maxFEL [1] is equal to 1. Therefore,  $M_{ord}$  is the sum of maxFEL[0] and maxFEL[1], which is 3.

Let us analyze  $\Pi_{ord}$  now. Table 2.3 shows the event dependency information of the 16 events, where " $e_1 \rightarrow e_2$ " means that  $e_1$  is the antecedent event of  $e_2$ .

| Simulated time | $LP_0$                      | $LP_1$                      |

|----------------|-----------------------------|-----------------------------|

| 1              | $e_1 \rightarrow e_2$       |                             |

| 8              | $e_2 \rightarrow e_5$       |                             |

| 9              | $e_3 \rightarrow e_4$       | $e_4 \rightarrow e_6$       |

| 15             | $e_5 \rightarrow e_9$       |                             |

| 17             | $e_7 \rightarrow e_8$       | $e_8 \rightarrow e_{10}$    |

|                | $e_7 \rightarrow e_{11}$    |                             |

| 25             | $e_{11} \rightarrow e_{12}$ | $e_{12} \rightarrow e_{15}$ |

|                | $e_{11} \rightarrow e_{13}$ |                             |

| 33             | $e_{13} \rightarrow e_{14}$ | $e_{15} \rightarrow e_{16}$ |

Table 2.3: Causal relationships between events in Pipeline

Table 2.4 lists the event execution sequence of the four simulation event orderings. Whether an event can be executed in one step is determined by the causal restriction and event ordering rules. First, the critical path length of total event ordering is 16 since there are 16 events in the system. For total event ordering, only one event can be executed at one step and there is no event parallelism,  $\Pi_{ord}$  is 1.

CHAPTER 2 METHODOLOGY

Events can be executed under partial event ordering as long as they do not violate causal restriction. In timestamp event ordering, if two events can be concurrently executed at one step, they must reside in one time window. Therefore  $e_9$  and  $e_{10}$  cannot be executed concurrently at step 6 under time interval event ordering (window size is 2 time units), even though they can be concurrently executed under partial event ordering. For timestamp event ordering, only two events with the same timestamp can be executed concurrently in one step.  $e_5$  and  $e_6$  cannot be executed concurrently at step 4 under timestamp event ordering because they have different timestamps, even though they can be concurrently under time interval event ordering.

| Step | Partial event       | 1                   |                     | Total event            |

|------|---------------------|---------------------|---------------------|------------------------|

|      | ordering            | event ordering      | event ordering      | ordering               |

| 1    | $e_1$               | $e_1$               | $e_1$               | $e_1$                  |

| 2    | $e_2$               | $e_2$               | $e_2$               | $e_2$                  |

| 3    | $e_3 \& e_4$        | $e_{3}$ & $e_{4}$   | $e_{3}$ & $e_{4}$   | $e_3$                  |

| 4    | $e_5 \& e_6$        | $e_5 \& e_6$        | $e_5$               | $e_4$                  |

| 5    | $e_7 \& e_8$        | $e_7 \& e_8$        | $e_7 \& e_6$        | $e_5$                  |

| 6    | $e_9$ & $e_{10}$    | $e_9$               | $e_8$               | $e_6$                  |

| 7    | $e_{11}$ & $e_{12}$ | $e_{11}$ & $e_{10}$ | $e_9$               | $e_7$                  |

| 8    | $e_{13}$ & $e_{14}$ | $e_{12}$            | $e_{11}$ & $e_{10}$ | $e_8$                  |

| 9    | $e_{15}$            | $e_{13}$ & $e_{14}$ | $e_{12}$            | $e_9$                  |

| 10   | $e_{16}$            | $e_{15}$            | $e_{13}$ & $e_{14}$ | $e_{10}$               |

| 11   |                     | $e_{16}$            | $e_{15}$            | $e_{11}$               |

| 12   |                     |                     | $e_{16}$            | $e_{12}$               |

| 13   |                     |                     |                     | <i>e</i> <sub>13</sub> |

| 14   |                     |                     |                     | $e_{14}$               |

| 15   |                     |                     |                     | $e_{15}$               |

| 16   |                     |                     |                     | <i>e</i> <sub>16</sub> |

Table 2.4: Event execution sequences for all event orderings in Pipeline

We execute the Pipeline simulation and obtain the same event sequence. TSA executes the event sequence and produces the same performance results as our manual analysis method. Therefore, TSA implementation is validated.

# 2.4 Summary

We illustrated our overall research methodology in this chapter. An analytical method was used to analyze the inherent event parallelism of a problem. TSA was used to analyze the performance of parallel simulation based on event orderings. The Ethernet network simulator was implemented using SPaDES/Java simulation library. CSIM simulation library was used for validation. Lastly, a simple Pipeline example

was used to validate our TSA implementation in detail.

# Chapter 3

# **Ethernet Modeling and Implementation**

We discuss the modeling and implementation of Ethernet network in this chapter. Ethernet is currently the most-used LAN technology. There is no central control in Ethernet network and all stations transmit data independently, so we expect a high degree of event parallelism. Simulation plays a vital role in attempting to characterize the behavior of Network applications [9].

## **3.1 Problem**

Ethernet is a branching broadcast communication system for carrying digital data packets among locally distributed computing stations [24]. A station can be attached anywhere to a passive coaxial cable, sometimes known as Ether, via a device called a transceiver. Ethernet network is reliable because of its distributed control - a single point failure can cause only partial interruption.

Ethernet uses CSMA/CD (Carrier Sense Multiple Access with Collision Detect) protocol. Any Ethernet station having frames to send will attempt to do so after it finds an empty cable. If two or more stations transmit frames simultaneously, there

will be a collision. Each station detects the collision, abort its transmission, wait a random period of time, and then try again until its packet is successfully transmitted or the transmission is considered to fail because the maximum number of retransmission, 16, is reached. Binary exponential back-off algorithm is used to determine the time (back-off) before a retransmission. The back-off in terms of the number of slots (512 bit times) is defined by a uniformly distributed number between [0, N], and

$$N = 2^{i} - 1 \qquad (1 \le i \le 10)$$

= 1023 (10 < i < =16)

where i is the number of transmissions made so far.

The Ethernet network exists to move frames carrying application data between computers. Hence the structure of a frame is central to the operation of the system. Preceded by a start bit, a frame starts with the destination and source address, which are both 6 bytes long. Following the address are 46 to 1,500 bytes of data. The last 4 bytes of a frame are the Frame Check Sequence or CRC. Only the address and data part are accessible to software. The minimum frame size is 64 bytes and the maximum frame size is 1518 bytes.

Simulation methods have been used to analyze the performance of Ethernet. Watkins uses a simulation method to study Ethernet protocol efficiency in the steady state [45]. He observes that an Ethernet network with larger frames has higher protocol efficiency than one with smaller frames.

#### **3.2 Simulation Model**

The input parameters, output, system states and components (processes and resources) of Ethernet network are specified in our simulation model. The input parameters are:

- *Number of stations*. This is the number of stations on the LAN.

- *Frame size*. This is the size of a frame in bytes with values from 64 bytes to 1024 bytes.

- *Time between transmissions.* This is the mean idle time after a frame has been either transmitted or discarded (because 16 attempts have been made) until the next transmission attempt.

The simulation outputs are:

- *Transmit delay*. This is the average time delay per successful frames.

- *Protocol efficiency*. This is the ratio of the number of successful frames to the maximum number possible when the LAN is being operated at its maximum rate.

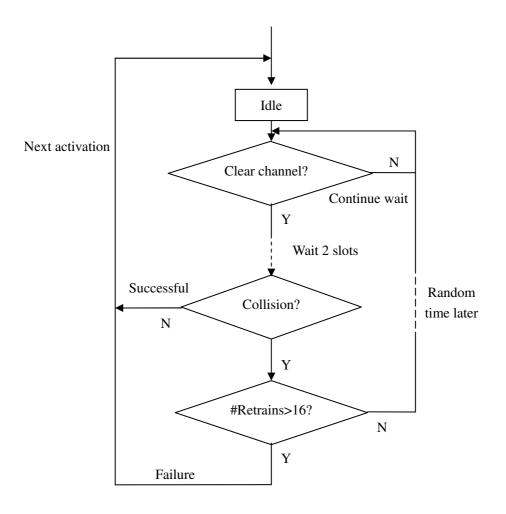

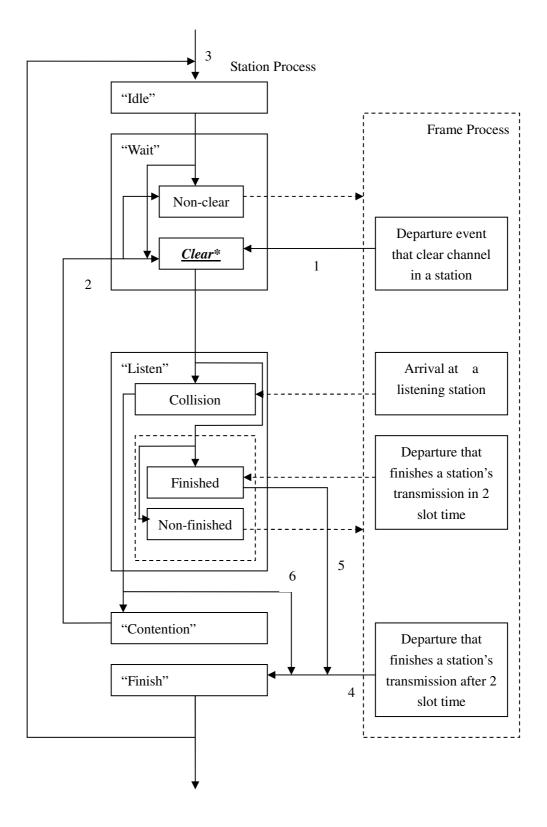

There are two important objects in the Ethernet protocol – "Stations" which communicate with each other on the channel and "Frames" with which they communicate. There are five states for a station: "Idle", "Wait", "Listen", "Contention" and "Finish". The state transit diagram of a station is shown in Figure 3.1. When the simulation is initialized, every station is in "Idle" state. A station goes to "Wait" state if it wants to send a frame through the channel. If the channel is clear, it transmits the frame to the cable immediately. Otherwise, it blocks until a clear channel is found. After transmitting a frame, a station waits for 2-slot time. If no collision occurs in this period of time, the package was transmitted successfully; otherwise, the station has collided. If collision occurs, the station waits for a random period of time, go back to "Wait" state and retransmit the frame. However, if the number of retransmissions is larger than 16, the transmission fails and the station goes back to "Idle" state and begin its next activation.

Figure 3.1: State transit diagram of an Ethernet station

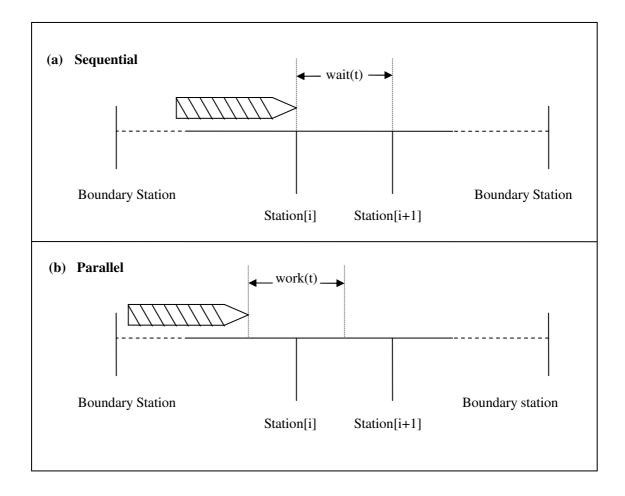

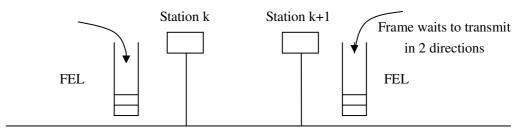

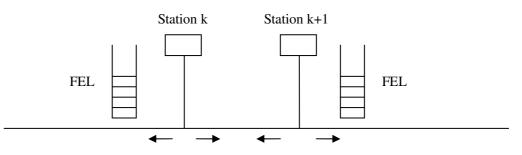

There are three states for a frame: "Arrival", "Transit" and "Departure". The "Transit" state can be modeled implicitly after the "Arrival" state and before the "Departure" state. When a frame arrives at a station, it passes through it without delay. All frames contend for the clear channel in Ethernet network. A station must wait for an empty channel to transmit frames. The *frame transmission time* (frame-size divided by LAN-speed) cannot be neglected, so a frame cannot be modeled as one process. We model two processes for a frame: *frame head* (the first bit of a frame) and *frame tail* (the last bit of a frame). Every time a station wants to transmit frames, it schedules the frame head activation immediately, but schedules the frame tail activation *frame transmission time* later. When a frame arrives at a station which is in the "Listen" state (within 2-slot time after transmission), the transmission is flagged as failed. The station then goes to "Contention" state and corrupts the frame(s) it sent.

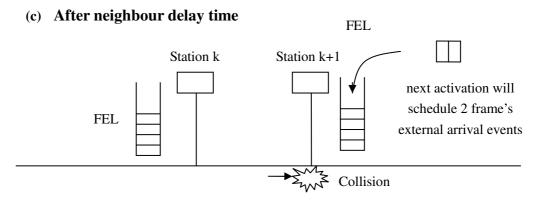

A station is also modeled as a resource in parallel simulation. Frame head or tail stays at a station for a period of time equal to the *neighbour delay time* (distance between two neighbouring stations divided by signal transmission speed  $2*10^8$  m/s). There is no need to model conditional event list (CEL) for a station resource because it is a delay center where infinite service units are available. The station process always stays at a station resource and does not move, while a frame moves between stations.

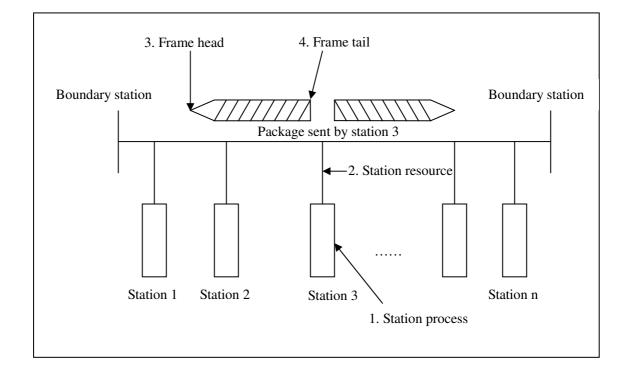

In summary, there are 4 objects in our conceptual model of Ethernet network as

shown in Figure 3.2: station process, station resource, frame head process and frame tail process. The frame head and tail are modeled separately. Frame head arrival at a station means the arrival of the frame. Frame tail departure from a station refers to the departure of the frame. If a frame is corrupted within 2 slot time, the frame's tail will be rescheduled to transmit immediately. Otherwise, the transmission is flagged as successful.

Figure 3.2: Processes and resources in simulation model of Ethernet.

# **3.3 Simulation and Implementation**

At the implementation level, some assumptions are made about our simulated Ethernet network. Firstly, we assume there is a straight cable without any branches. All stations are equally distributed along the cable. The channel is noiseless and the station is reliable. Frames travel along the cable from the source station in both directions and are absorbed at the cable ends. The time between transmissions is exponentially distributed. Protocol efficiency is required with all stations working continuously, i.e. no idle periods. Ethernet standards specify a maximum delay of  $51.2 \,\mu$  s (slot size) but this is supposed to include the transmit delay through repeaters. The length of cable is assumed to have the maximum delay equally distributed throughout its entire length (approximately 10 km), which is the product of the slot size ( $51.2 \,\mu$  s) and the signal transmission speed ( $2*10^8$  m/s).

#### **3.3.1 Sequential**

We implemented the simulator with SPaDES/Java and validated it with the C simulator developed by Watkins [45]. There are two classes of active objects in Ethernet network: station and frame. In addition, one kernel class is used to initialize the simulation parameters, start the simulation and print the simulation results. The simulation terminates when the simulated time exceeds a specified duration. The kernel class is also responsible for initially activating the station classes. The kernel class is listed in Figure 3.3.

```

1: import spades_Java.*;

2:

3: //EthernetKernel.java

4: // Executive instance

5: public class EthernetKernel extends Executive{

6:

7:

Resource Service[];

8:

//station process

Station station[];

9:

10:

11:

//define parameters for Ethernet

12:

double cable_length; /* Cable length in meter */

13:

int num_stations; /* Number of users in the LAN */

14:

/* Frame size in bytes */

15:

int frame_size;

```

```

16:

double duration;

/* Simulation duration in ms */

17:

18:

public void init() {

19:

:

20:

<<Initialize Ethernet parameters>>

21:

:

22:

<<Initialize resource>>

23:

24:

//Active station process

25:

for (int i=0, i<num stations, i++) {</pre>

26:

27:

station[j]=new Station("Station "+j,this);

28:

<<Initialize station[i]>>

29:

mapProcess(station[j], Service[j]);

30:

activate(station[j], 0);

31:

:

32:

}

33:

}

34:

public static void main(String[] args) {

35:

EthernetKernel ek = new EthernetKernel();

36:

ek.initialize(args.length, args);

37:

ek.startSimulation(duration);

38:

<<Print simulation results>>

39:

}

40: }

```

Figure 3.3: Kernel class of Ethernet network simulation

Once a station entity has been created it exists permanently for the life of the simulation and is involved in a succession of transmission attempts. The following pseudo code describes the behavior of a station class.

```

1: import spades_Java.*;

2: Class Station extends SProcess{

3:

:

int successful; /* Number of frames sent */

4:

5:

int number_retrans; /* Number of retransmission so far */

/* Frames transmitted out */

6:

Aframe[] end;

7:

<<Initialize other Station parameters>>

8:

9:

public void execute() {

10:

switch(phase) {

11:

case Idle:{

12:

<<Set phase to Wait>>

13:

wait(0.0);

14:

break;

15:

}

16:

case Wait:{

17:

if <<Channel is clear>> {

18:

<<Create and transmit frames>>

19:

<<Set phase to Listen>>

```

| 20:         |   | <pre>wait(2*slot_time);</pre>                                  |

|-------------|---|----------------------------------------------------------------|

| 21:         |   | }else{                                                         |

| 22:         |   | //continue waiting                                             |

| 23:         |   | susPend();                                                     |

| 24:         |   | }                                                              |

| 25:         |   | break;                                                         |

| 26:         |   | }                                                              |

| 27:         |   | case Listen:{                                                  |

| 28:         |   | if < <frame be="" is="" or="" successfully<="" td="" will=""/> |

| 29:         |   | transmitted>>{                                                 |

| 30:         |   | if < <both frames="" transmitted="">&gt;{</both>               |

| 31:         |   | <set finish="" phase="" to="">&gt;</set>                       |

| 32:         |   | <pre>wait(0.0);</pre>                                          |

| 33:         |   | }else{                                                         |

| 34:         |   | <wait 2="" frames="" left="" until="">&gt;</wait>              |

| 35:         |   | < <set finish="" phase="" to="">&gt;</set>                     |

| 36:         |   | susPend();                                                     |

| 37:         |   | }                                                              |

| 38:         |   | }else{                                                         |

| 39:         |   | <pre>&lt;<retransmit frame="" this="">&gt;</retransmit></pre>  |

| 40:         |   | <pre></pre>                                                    |

| 40.<br>41:  |   | ·                                                              |

| 41:<br>42:  |   | break;                                                         |

|             |   | }                                                              |

| 43:         |   | case Contention:{                                              |

| 44:         |   | < <set phase="" to="" wait="">&gt;</set>                       |

| 45:         |   | wait(0.0);                                                     |

| 46:         |   | break;                                                         |

| 47:         |   | }                                                              |

| 48:         |   | case Finish:{                                                  |

| 49:         |   | < <reset station="" this="">&gt;</reset>                       |

| 50:         |   | < <set idle="" phase="" to="">&gt;</set>                       |

| 51:         |   | wait(0.0);                                                     |

| 52:         |   | break;                                                         |

| 53:         |   | }                                                              |

| 54:         |   | }                                                              |

| 55 <b>:</b> | } |                                                                |

| 56:}        |   |                                                                |

Figure 3.4: A station class

The station class follows straightly from the state transit diagram of a station in Figure 3.1. A station needs to record the number of frames it sent out (Line 4) and number of retransmissions so far in this station (Line 5). If a clear channel is found, the station transmits two (one for boundary station) frames in both directions. The station schedules the frame head's arrival at its neighbouring station *neighbour delay time* later. In the mean time, the station schedules the frame tail's departure from

itself *frame transmission time* later. The station also needs to record frames that it sent (Line 6) because it is necessary for a station to identify the frames it sent when a collision occurs. After transmitting two frames, the station will listen for 2 slot size time. If no other frames arrive at this station in this period of time, the transmission is successful. If both frames have been transmitted, the station will go to "Finish" state and prepare for another transmission some idle time (exponentially distributed) later. Otherwise the station will suspend itself and wait for another frame's departure. However, if some frame(s) arrive at this station in 2 slot size time, the transmission is considered to fail.

Once a collision has occurred a time delay must be calculated after which a retransmission can be attempted. However, if the maximum number of attempts has already been made, the transmission request must be rejected. The function *retrans\_time()* in Figure 3.5 calculates the retransmission time according to binary exponential back-off algorithm. The actual retransmission is performed with *retransmit()*, which is called in phase "Listen" after the two-slot delay.

| 1:  | class Station extends SProcess {                         |

|-----|----------------------------------------------------------|

| 2:  | :                                                        |

| 3:  | <pre>void retransmit(Station this_station){</pre>        |

| 4:  | /*Have maximum number of attempts been made?*/           |