# HIGH DIELECTRIC CONSTANT MATERIALS IN SONOS-TYPE NON-VOLATILE MEMORY STRUCTURES

**TAN YAN NY**(B. Eng. and M. Eng., NUS)

## A THESIS SUBMITTED FOR THE DEGREE OF DOCTOR OF PHILOSOPHY IN ENGINEERING

# DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

NATIONAL UNIVERSITY OF SINGAPORE 2007

## Acknowledgements

I would like to thank my thesis supervisors, Associate Professor Chim Wai Kin, Associate Professor Cho Byung Jin and Professor Choi Wee Kiong, for their teaching and guidance throughout my candidature.

I would like to thank Mr. Joo Moon Sig, Kim Sun Jung, Mr. Whang Sung Jin, Lau Boon Teck and O Yann Wai Lin for their assistance rendered during device fabrication in Silicon Nano Devices Laboratory. In addition, I would like to thank Walter Lim and Chew Han Guan for their kind assistance while working in Microelectronics Laboratory. In Centre for Integrated Circuits Failure Analysis and Reliability Laboratory, I would like to thank Mrs. Ho Chiew Mooi, Mr. Goh Thiam Peng, Anna Li and Koo Chee Kiong for their assistance in equipment maintenance. My appreciation to fellow postgraduate students, Tsu Hau, Guan Song, Xin Hua, Soon Leng, Soon Huat, Mans Osterberg, Jian Xin, Alfred, Szu Huat, Heng Wah, Shen Chen, Jin Quan and Wen Zhuo for making my stay in NUS an enriching experience.

Last but not least, I would like to thank my family for their constant support and encouragement.

## **Table of Contents**

|             |                                              | PAGE |

|-------------|----------------------------------------------|------|

| ACKNOWLE    | DGEMENTS                                     | i    |

| TABLE OF C  | ONTENTS                                      | ii   |

| SUMMARY     |                                              | v    |

| LIST OF TAE | BLES                                         | vii  |

| LIST OF FIG | URES                                         | viii |

| LIST OF SYN | ABOLS                                        | xvi  |

| CHAPTER 1   | Introduction                                 | 1    |

| 1.1         | Background                                   | 1    |

| 1.2         | Motivation for the Project                   | 4    |

| 1.3         | Research Objectives                          | 5    |

| 1.4         | Organization of Thesis                       | 6    |

|             | References                                   | 8    |

| CHAPTER 2   | Literature Review                            | 10   |

| 2.1         | History of Nonvolatile Memory Structures     | 10   |

| 2.2         | Current and Future Nonvolatile Memories      | 16   |

| 2.3         | SONOS Nonvolatile Memory                     | 23   |

|             | 2.3.1 SONOS gate stack scaling               | 27   |

|             | 2.3.2 Novel SONOS Structures                 | 28   |

|             | References                                   | 34   |

| CHAPTER 3   | Hafnium Oxide as the Charge Storage Layer in |      |

|             | SONOS-type Nonvolatile Flash Memory for      |      |

|             | Minimization of the Over-erase Phenomenon    | 40   |

| 3.1         | Introduction                                 | 40   |

| 3.2       | Sample Fabrication                                   | 41 |

|-----------|------------------------------------------------------|----|

| 3.3       | Results and Discussion                               | 43 |

| 3.4       | Summary                                              | 51 |

|           | References                                           | 52 |

| CHAPTER 4 | Hafnium Aluminum Oxide as the Charge Storage         |    |

|           | Layer in SONOS-type Nonvolatile Memory for           |    |

|           | High-Speed Operation with Improved Charge            |    |

|           | <b>Retention and Endurance Performance</b>           | 54 |

| 4.1       | Introduction                                         | 54 |

| 4.2       | Sample Fabrication                                   | 55 |

| 4.3       | Results and Discussion                               | 56 |

| 4.4       | Summary                                              | 71 |

|           | References                                           | 72 |

| CHAPTER 5 | Development of High-κ Blocking Oxide Layer in        |    |

|           | SONOS-type Nonvolatile Memory                        | 76 |

| 5.1       | Introduction                                         | 76 |

| 5.2       | Hafnium Aluminum Oxide Blocking Oxide Layer in       |    |

|           | SONOS-type Nonvolatile Memory for High-Speed         |    |

|           | Operation                                            | 77 |

|           | 5.2.1 Introduction                                   | 77 |

|           | 5.2.2 Sample Fabrication                             | 78 |

|           | 5.2.3 Results and Discussion                         | 79 |

| 5.3       | Evaluation of Lanthanum Aluminum Oxide and Lanthanum |    |

|           | Yttrium Aluminum Oxide as the Blocking Oxide Layer   |    |

|           | in SONOS-type Nonvolatile Memory                     | 93 |

iii

|             | 5.3.1   | Introdu  | action                                          | 93  |

|-------------|---------|----------|-------------------------------------------------|-----|

|             | 5.3.2   | Sample   | e Fabrication                                   | 94  |

|             | 5.3.3   | Results  | s and Discussion                                | 95  |

|             |         | (A)      | Evaluation of $(La_2O_3)_x(Al_2O_3)_{1-x}$ with |     |

|             |         |          | different composition ratios as blocking oxide  | 95  |

|             |         | (B)      | Feasibility study of $(LaAl)_x Y_{1-x}O_3$ with |     |

|             |         |          | different composition ratios as blocking oxide  |     |

|             |         |          | for SONOS memory                                | 97  |

| 5.4         | Summ    | ary      |                                                 | 102 |

|             | Refere  | nces     |                                                 | 104 |

| CHAPTER 6   | SONO    | S-type   | Nonvolatile Memory with Ultra-high-κ            |     |

|             | Charg   | e Stora  | ge Layer and High-κ Tunnel and                  |     |

|             | Blocki  | ng Oxi   | de Layers                                       | 108 |

| 6.1         | Introdu | uction   |                                                 | 108 |

| 6.2         | Sample  | e Fabric | cation                                          | 111 |

| 6.3         | Result  | s and D  | iscussion                                       | 112 |

| 6.4         | Summ    | ary      |                                                 | 121 |

|             | Refere  | nces     |                                                 | 122 |

| CHAPTER 7   | Concl   | usion    |                                                 | 125 |

| 7.1         | Summ    | ary of F | ïndings                                         | 125 |

| 7.2         | Recom   | mendat   | ions for future work                            | 128 |

|             | Refere  | nces     |                                                 | 130 |

| LIST OF PUE | BLICAT  | IONS     |                                                 | 131 |

## Summary

SONOS (polysilicon-oxide-silicon nitride-oxide-silicon) Flash memory is one of the more attractive candidates to realize FLASH vertical scaling. This work entails finding innovative solutions, using high dielectric constant (high- $\kappa$ ) materials, to overcome the limitations of the conventional floating gate structure as a result of rapidly shrinking device geometries.

The conventional method to increase the programming speed and to lower the operating voltage of SONOS devices is by reducing the tunnel oxide thickness. However, this seriously degrades the charge retention capability of the device. To overcome this limitation, the SOHOS (polysilicon-oxide-high- $\kappa$ -oxide-silicon) Flash memory has been attempted in this work by replacing the silicon nitride layer with a high dielectric constant material. Basically, due to the higher  $\kappa$  value, the equivalent oxide thickness is reduced for the same physical thickness of the film. Hence, the effect on device performance is expected to be similar to that of scaling the tunnel oxide thickness without the disadvantages that come with smaller physical thicknesses, especially increased tunneling current leakage. SOHOS structure with hafnium oxide (HfO<sub>2</sub>) as the charge storage layer demonstrated superior charge storage capability at low voltages, faster programming and less over-erase problem as compared to the conventional SONOS device. However, such a SOHOS device had poorer charge retention capability than SONOS. On the other hand, using aluminum oxide  $(Al_2O_3)$  as the charge storage layer resulted in a SOHOS structure with improved charge retention performance, but at the expense of a slower programming speed. By adding a small amount of aluminum to HfO<sub>2</sub> to form hafnium aluminum oxide (HfAlO), the resultant SOHOS structure with HfAlO as a charge storage layer can combine the advantages of both  $HfO_2$  and  $Al_2O_3$ , such as fast programming speed, good charge retention and good program/erase endurance. Hence, the programming speed of the SOHOS device was successfully increased without reducing the tunnel oxide thickness through an appropriate choice of the high- $\kappa$  charge storage layer.

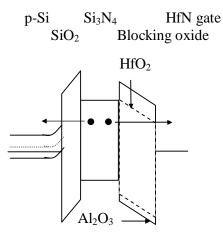

An alternative method to increase program/erase speed without decreasing the tunnel oxide thickness is by using a high- $\kappa$  material as the blocking oxide. From electrostatics consideration, the use of a high dielectric constant blocking oxide layer will cause a smaller voltage drop across the blocking oxide and greater voltage drop across the tunnel oxide. This will result in a simultaneous increase of the electric field across the tunnel oxide and reduction of the electric field across the blocking oxide, leading to more efficient program and erase processes. The effect of the  $\kappa$  value and band gap energy of the blocking oxide layer on the program/erase speed and charge retention of SONOS devices was investigated by using  $(HfO_2)_x(Al_2O_3)_{1-x}$  with different  $HfO_2$  concentration ratios (x) as the blocking oxide. Other high- $\kappa$  materials with suitable conduction and valence band offsets were also evaluated.

Finally, the integration of high- $\kappa$  tunnel and blocking oxides and an ultra-high- $\kappa$  charge storage layer (TiO<sub>2</sub>) was also demonstrated in this project. HfAlO/TiO<sub>2</sub>/HfAlO SOHOS capacitors showed much greater flatband voltage shift at lower program/erase voltages compared to the conventional SONOS device after post-deposition and forming gas anneals.

# List of Tables

|           |                                                                                                                                                                                                | Pages |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Table 2.1 | Summary of memory parameters for different types of nonvolatile memories                                                                                                                       | 23    |

| Table 4.1 | The split conditions of samples with different HfAlO charge storage layer thicknesses, different tunnel oxide thicknesses and 65 Å blocking oxide. The cell structure is similar to Fig. 4. 1. | 67    |

| Table 4.2 | Comparison between this work (HfAlO device) and published data. SRO is silicon rich oxide.                                                                                                     | 70    |

| Table 5.1 | Comparison between this work and published data.<br>SRO is silicon rich oxide.                                                                                                                 | 89    |

| Table 5.2 | Estimated barrier heights of the $TaN/(LaAl)_xY_{1-x}O_3$<br>interface and conduction band offsets of $(LaAl)_xY_{1-x}O_3$<br>with respect to silicon.                                         | 101   |

# **List of Figures**

|              |                                                                                                                                                                                                                         | Pages |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

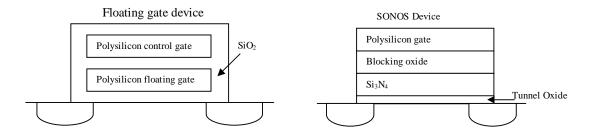

| Figure 1.1:  | Two classes of nonvolatile semiconductor memory devices:<br>(a) floating-gate device and (b) charge-trapping device<br>(b) (SONOS device).                                                                              | 2     |

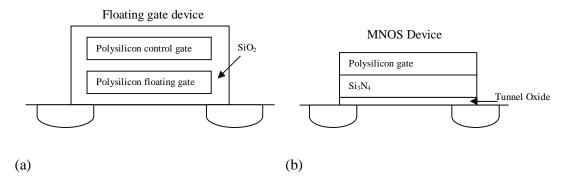

| Figure 2.1:  | Two classes of nonvolatile semiconductor memory devices:<br>(a) floating-gate device and (b) charge-trapping device<br>(MNOS device).                                                                                   | 11    |

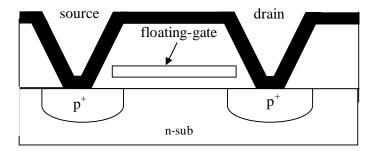

| Figure 2.2:  | First operating floating-gate device: the FAMOS (Floating-gate Avalanche injection MOS) device, introduced by Frohman-Bentchkowsky [3-6].                                                                               | 12    |

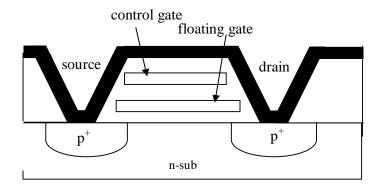

| Figure 2.3:  | The SAMOS (Stacked gate Avalanche injection MOS)<br>device [7-8]. The device is written like the FAMOS device.<br>Several different erasure mechanisms are possible.                                                    | 13    |

| Figure 2.4:  | NOR Flash array equivalent circuit [18].                                                                                                                                                                                | 17    |

| Figure 2.5:  | A NOR-structured memory array illustrating the over-erase phenomenon.                                                                                                                                                   | 18    |

| Figure 2.6:  | Equivalent circuit of the NAND-structured cell array.                                                                                                                                                                   | 19    |

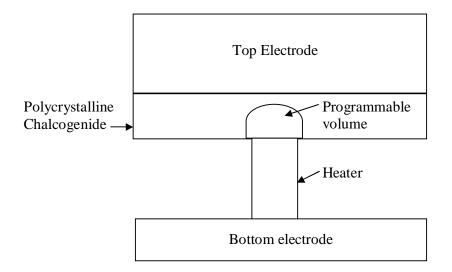

| Figure 2.7:  | Basic cross section of a Phase Change Memory [19].                                                                                                                                                                      | 22    |

| Figure 2.8:  | Evolution of the SONOS NVSM device [24].                                                                                                                                                                                | 24    |

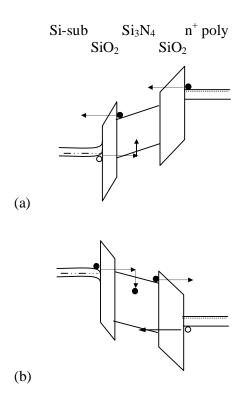

| Figure 2.9:  | Physical operation of a SONOS device [25].                                                                                                                                                                              | 25    |

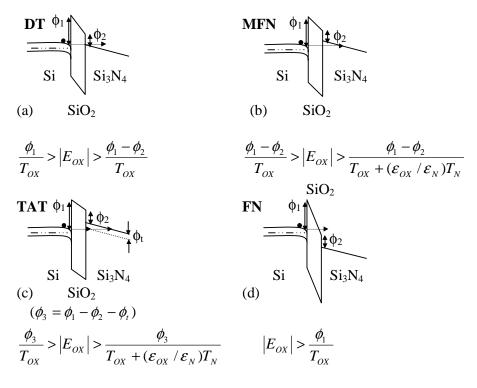

| Figure 2.10: | Energy band diagrams of the programming mechanisms:<br>(a) Direct tunneling, (b) Modified Fowler-Nordheim<br>tunneling, (c) trap assisted tunneling (d) Fowler-Nordheim<br>tunneling [26].                              | 26    |

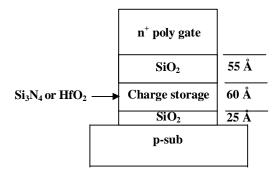

| Figure 3.1:  | Fabricated SONOS-type memory devices with $Si_3N_4$ or $HfO_2$ charge storage layers.                                                                                                                                   | 42    |

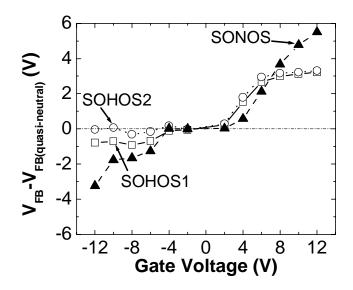

| Figure 3.2:  | Flatband voltage shift plotted against the charging (positive)<br>and discharging (negative) gate voltage for SONOS,<br>SOHOS1 and SOHOS2 memory devices.                                                               | 44    |

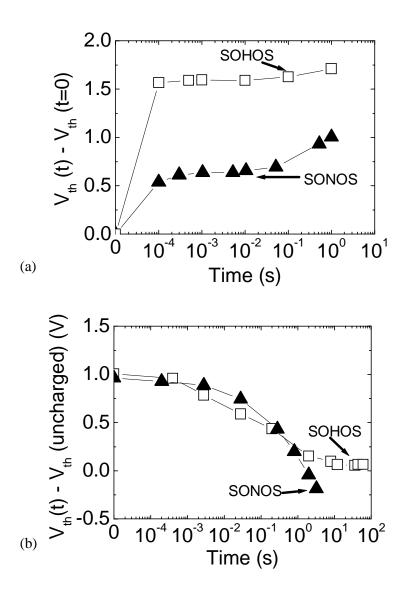

| Figure 3.3:  | (a) Program and (b) erase threshold voltage shift of SOHOS1 (with HfO <sub>2</sub> charge storage layer) and SONOS n-channel MOSFETs for $V_g - V_{fb} = +6$ V during program and $V_g - V_{fb} = -5.3$ V during erase. | 45    |

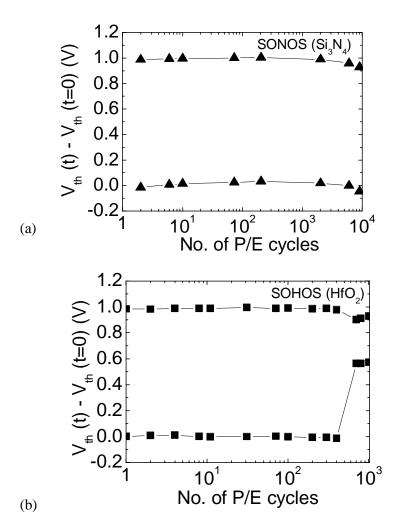

| Figure 3.4:  | Program/erase (P/E) cycling data for (a) SONOS and                                                                                                                                                                      |       |

|             | (b) SOHOS1 (with $HfO_2$ charge storage layer) n-channel MOSFETs.                                                                                                                                                                                                                                                                                                                                               | 46 |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

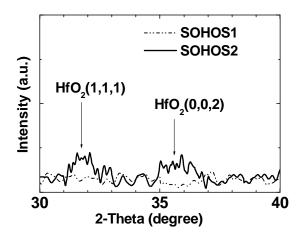

| Figure 3.5: | X-ray diffraction spectra of SOHOS1 and SOHOS2 structures.                                                                                                                                                                                                                                                                                                                                                      | 48 |

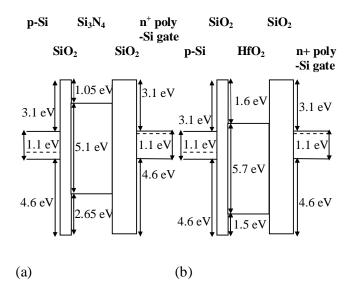

| Figure 3.6: | Ideal energy band diagrams for (a) SONOS and (b) SOHOS structures.                                                                                                                                                                                                                                                                                                                                              | 48 |

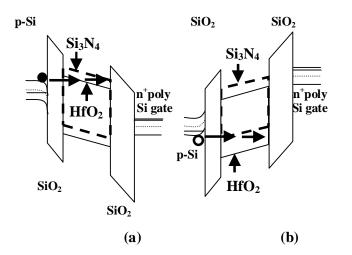

| Figure 3.7: | Energy band diagram schematic of the SONOS structure with $HfO_2$ (solid lines) or $Si_3N_4$ (dashed lines) as the charge storage layer during (a) write (program) and (b) erase operations.                                                                                                                                                                                                                    | 50 |

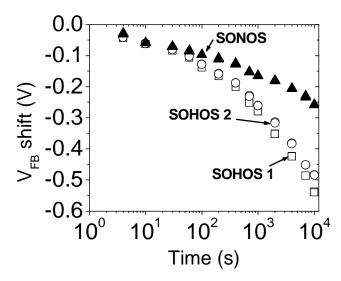

| Figure 3.8: | Charge retention performance of the SOHOS1, SOHOS2<br>and SONOS devices as characterized by the flatband voltage<br>shift at an applied gate bias ( $V_g$ ) of 0V after the device has<br>been charged at $V_g = 6V$ .                                                                                                                                                                                          | 50 |

| Figure 4.1: | Fabricated SOHOS (with $HfO_2$ or $HfAlO$ or $Al_2O_3$ charge storage layer) and SONOS ( $Si_3N_4$ ) transistor structures with $HfN/TaN$ gate electrode.                                                                                                                                                                                                                                                       | 55 |

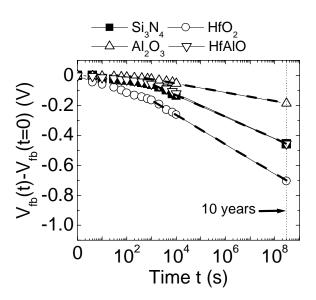

| Figure 4.2: | Flatband voltage shift during charge retention measurements versus time of SONOS-type memory devices with $Si_3N_4$ , $Al_2O_3$ , $HfO_2$ or $HfAlO$ as the charge storage layer during discharging at a gate bias of -1.45 V below the initial flatband voltage of a charged device. The devices were programmed to an initial $V_{fb}$ shift of 1.1 V before the retention measurements.                      | 56 |

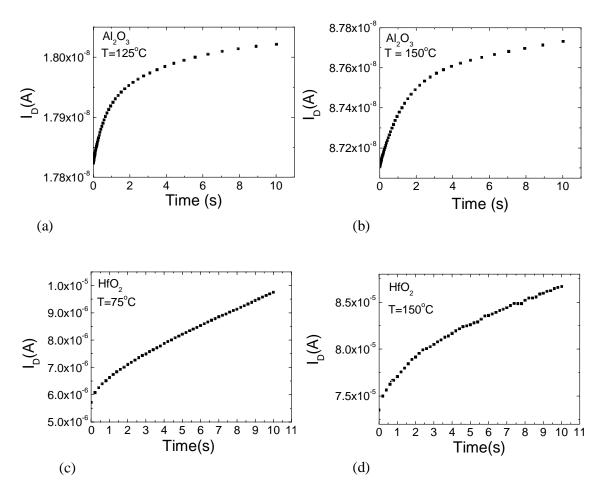

| Figure 4.3: | The drain current transients of (a), (b) $Al_2O_3$ memory<br>devices and (c), (d) HfO <sub>2</sub> memory devices during the<br>application of a read voltage after the application of a<br>program voltage for 20s. The read and program voltages<br>for $Al_2O_3$ devices were 3.3 V and 9 V, respectively. For<br>HfO <sub>2</sub> devices the read and program voltages were 2.9 V and<br>7 V respectively. | 60 |

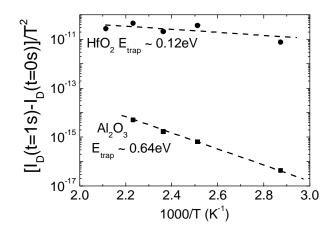

| Figure 4.4: | Drain current difference during discharging divided by squared temperature (T) versus the inverse of T for $HfO_2$ and $Al_2O_3$ memory devices.                                                                                                                                                                                                                                                                | 61 |

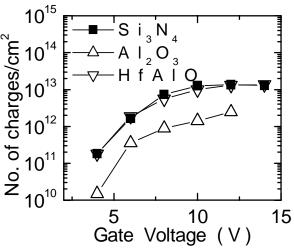

| Figure 4.5: | Density of stored charge, extracted from the hysteresis in the C-V curves, and plotted against the gate voltage sweep range for SONOS-type capacitor structures with $Si_3N_4$ , $Al_2O_3$ or HfAlO as the charge storage layer.                                                                                                                                                                                | 61 |

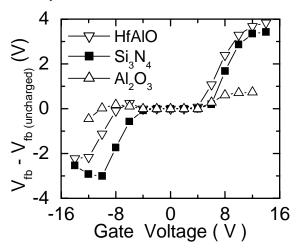

| Figure 4.6: | Flatband voltage shift plotted against the charging/discharging (program/erase) voltage extracted from the hysteresis in the                                                                                                                                                                                                                                                                                    |    |

|              | C-V curves for memory capacitors with $Si_3N_4$ , $Al_2O_3$ or HfAlO as the charge storage layer.                                                                                                                                                                                                                                                                                                                                                                                                     | 63 |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

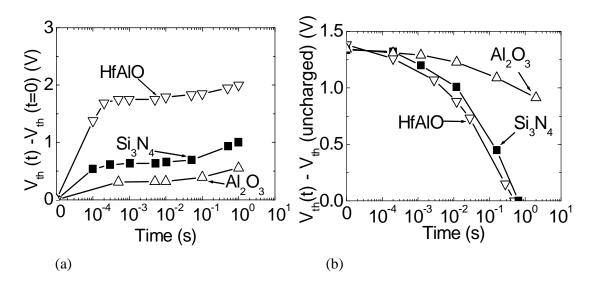

| Figure 4.7:  | (a) Programming ( $V_g$ - $V_{fb} = 6V$ ) and (b) erasing ( $V_g$ - $V_{fb} = -6V$ ) characteristics of SONOS and SOHOS transistors with Si <sub>3</sub> N <sub>4</sub> , HfAlO and Al <sub>2</sub> O <sub>3</sub> charge storage layers.                                                                                                                                                                                                                                                             | 63 |

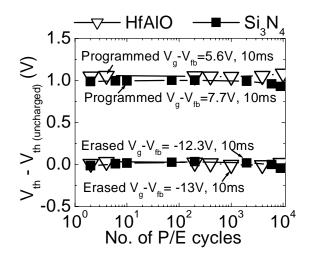

| Figure 4.8:  | Program/Erase (P/E) endurance characteristics of SONOS and SOHOS transistors with $Si_3N_4$ and HfAlO charge storage layers.                                                                                                                                                                                                                                                                                                                                                                          | 64 |

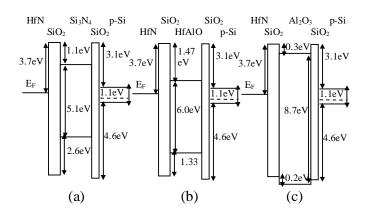

| Figure 4.9:  | Ideal energy band diagrams of SONOS-type structures (HfN/TaN gate) with (a) $Si_3N_4$ (conventional SONOS), (b) HfAlO (10% Al <sub>2</sub> O <sub>3</sub> concentration) and (c) Al <sub>2</sub> O <sub>3</sub> as the charge storage layer.                                                                                                                                                                                                                                                          | 65 |

| Figure 4.10: | Energy band diagram schematic of SONOS-type structures with HfAlO (solid lines) or $Si_3N_4$ (dashed lines) as the charge storage layer during (a) write (program) and (b) erase operations.                                                                                                                                                                                                                                                                                                          | 65 |

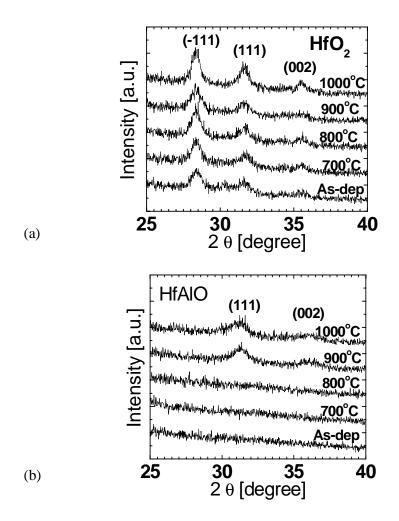

| Figure 4.11: | XRD spectra of (a) $HfO_2$ and (b) $HfAlO$ . As-deposited $HfO_2$ was already crystallized while $HfAlO$ remained amorphous up to $800^{\circ}C$ .                                                                                                                                                                                                                                                                                                                                                    | 66 |

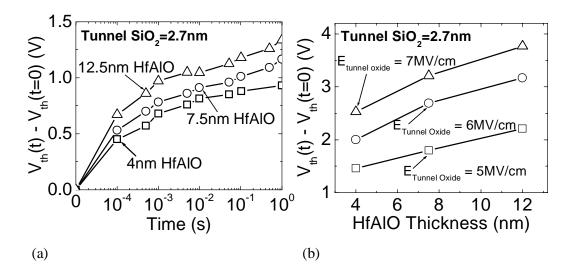

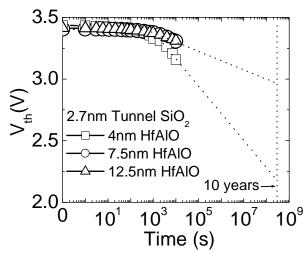

| Figure 4.12: | (a) Programming characteristics (i.e., threshold voltage shift versus time at a tunnel oxide field of 5 MV/cm) of SOHOS transistors with 40 Å, 75 Å and 125 Å thick HfAlO charge storage layer and 27 Å thick tunnel oxide. (b) Threshold voltage shift of SOHOS transistors after 50 s programming versus thickness of the HfAlO charge storage layer for tunnel oxide fields of 5, 6 and 7 MV/cm during programming. The tunnel oxide is 27 Å thick. The traps are saturated after 50s programming. | 68 |

| Figure 4.13: |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 69 |

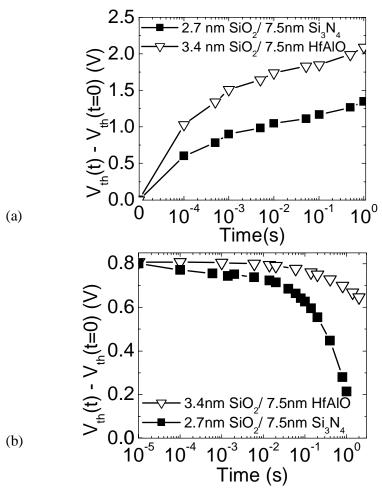

| Figure 4.14: | (a) Programming ( $V_g$ - $V_{fb}$ = 8.5V) and (b) erasing<br>( $V_g$ - $V_{fb}$ = -15V) characteristics of threshold voltage shift<br>versus time of SONOS transistor with 27 Å tunnel SiO <sub>2</sub> /75 Å<br>Si <sub>3</sub> N <sub>4</sub> charge storage layer and SOHOS transistor with 34 Å<br>tunnel SiO <sub>2</sub> /75Å HfAlO charge storage layer. $V_{th}(t=0)$<br>denoted the V <sub>th</sub> of uncharged device.                                                                    | 69 |

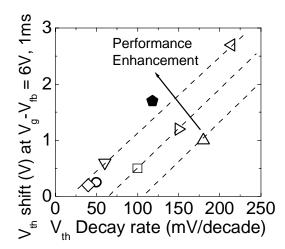

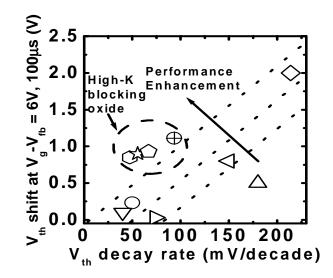

| Figure 4.15: | Graph of $V_{th}$ shift after programming at $V_g$ - $V_{fb}$ = 6V, 1ms against the $V_{th}$ decay rate per decade of retention measurement time. Comparison between this work (HfAlO                                                                                                                                                                                                                                                                                                                 |    |

|             | device) and published data (refer to Table 4.2).                                                                                                                                                                                                                                                                                                                                                                                  | 70 |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

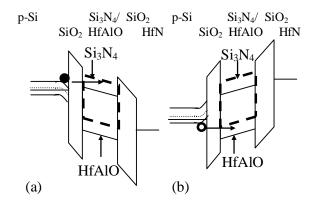

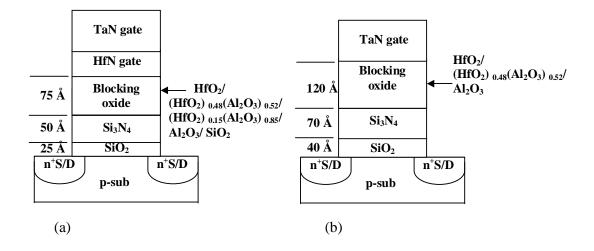

| Figure 5.1: | (a) Fabricated SONOS Flash transistor structures with HfN/TaN gate electrode. The blocking oxide layer is either SiO <sub>2</sub> or high- $\kappa$ dielectric. (b) Fabricated SONOS Flash transistor structures with TaN gate electrode. The blocking oxide layer is high- $\kappa$ dielectric.                                                                                                                                  | 79 |

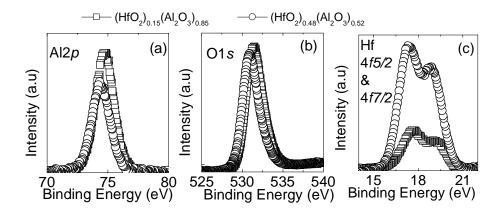

| Figure 5.2: | XPS spectra for (a) Al 2 <i>p</i> core levels, (b) O 1 <i>s</i> core levels<br>and (c) Hf 4 <i>f</i> core levels taken from $(HfO_2)_x(Al_2O_3)_{1-x}$<br>samples (used in the blocking oxide layer), with x values<br>determined to be 0.15 and 0.48.                                                                                                                                                                            | 80 |

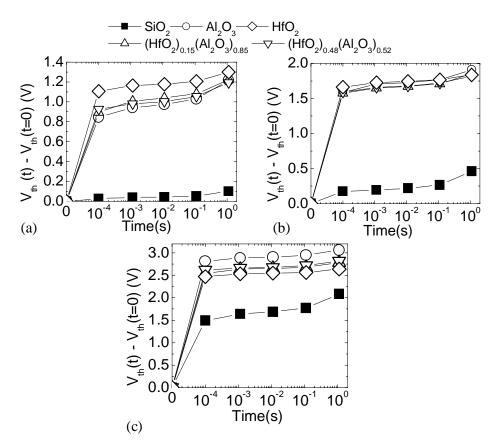

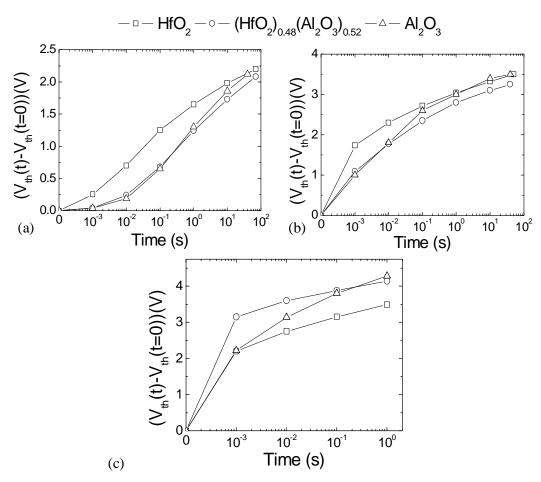

| Figure 5.3: | Programming transient for (a) $V_g - V_{fb} = 6V$ (b) $V_g - V_{fb} = 7V$ and (c) $V_g - V_{fb} = 9V$ for SONOS devices with SiO <sub>2</sub> (solid symbol) or high- $\kappa$ (open symbols) blocking oxide layers. The gate stacks of the SONOS devices are 25 Å SiO <sub>2</sub> / 50 Å Si <sub>3</sub> N <sub>4</sub> / 75 Å high- $\kappa$ or SiO <sub>2</sub> blocking oxide, as illustrated in Fig. 5.1 (a).               | 81 |

| Figure 5.4: | Threshold voltage shift after programming at $V_g - V_{fb} = 6V$ ,<br>7V, 8V and 9V for 100 µs for SONOS devices with HfAlO<br>blocking oxide layer with different HfO <sub>2</sub> mole fraction x.<br>The gate stacks of the SONOS devices are 25 Å SiO <sub>2</sub> / 50 Å<br>Si <sub>3</sub> N <sub>4</sub> / 75 Å high- $\kappa$ or SiO <sub>2</sub> blocking oxide, as illustrated in<br>Fig. 5.1 (a).                      | 81 |

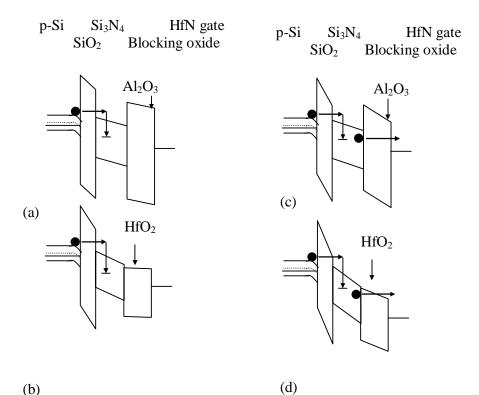

| Figure 5.5: | Schematic energy band diagrams for SONOS devices with $Al_2O_3$ [(a) and (c)] and $HfO_2$ [(b) and (d)] blocking oxide layers in the program mode for low [(a) and (b)] and high [(c) and (d)] gate voltage situations.                                                                                                                                                                                                           | 83 |

| Figure 5.6: | Erasing transient for (a) $V_g - V_{fb} = -6V$ (b) $V_g - V_{fb} = -7V$ and<br>(c) $V_g - V_{fb} = -8V$ for SONOS devices with SiO <sub>2</sub> (solid<br>symbol) or high- $\kappa$ (open symbols) blocking oxide layers.<br>The gate stacks of the SONOS devices are 25 Å SiO <sub>2</sub> / 50 Å<br>Si <sub>3</sub> N <sub>4</sub> / 75 Å high- $\kappa$ or SiO <sub>2</sub> blocking oxide, as illustrated in<br>Fig. 5.1 (a). | 84 |

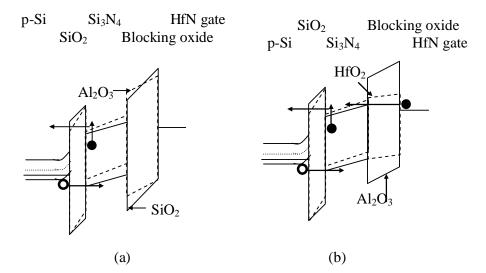

| Figure 5.7: | Schematic energy band diagrams for SONOS devices in the erase mode: (a) Comparing SiO <sub>2</sub> (solid lines) and high- $\kappa$ (e.g., Al <sub>2</sub> O <sub>3</sub> ) (dashed lines) blocking oxide layers, and (b) Comparing Al <sub>2</sub> O <sub>3</sub> (solid lines) and HfO <sub>2</sub> (dashed lines) blocking oxide layers.                                                                                       | 86 |

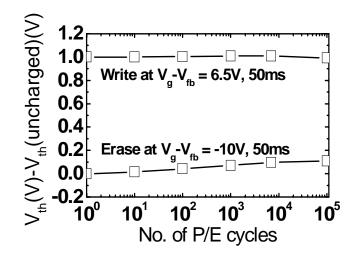

| Figure 5.8: | Program/Erase (P/E) endurance characteristics of SONOS device with (HfO <sub>2</sub> ) $_{0.48}$ (Al <sub>2</sub> O <sub>3</sub> ) $_{0.52}$ (48% HfO <sub>2</sub> ) blocking oxide. The gate stacks of the SONOS devices are 25 Å SiO <sub>2</sub> / 50 Å Si <sub>3</sub> N <sub>4</sub> / 75 Å high- $\kappa$ or SiO <sub>2</sub> blocking oxide, as illustrated in Fig. 5.1 (a).                                               | 86 |

xi

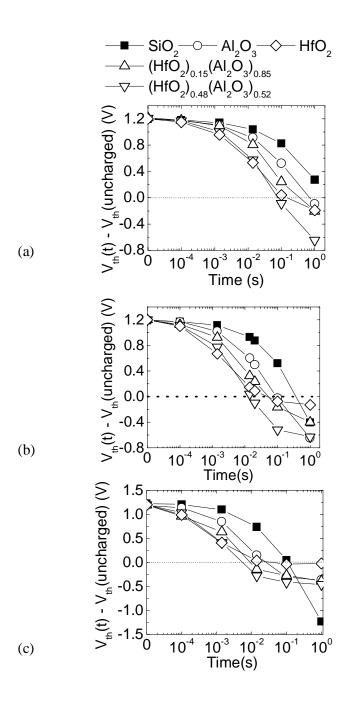

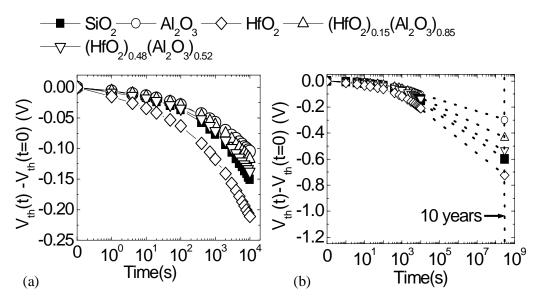

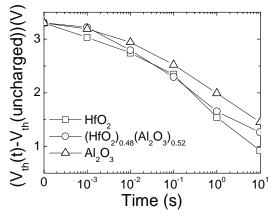

| Figure 5.9:  | (a) Charge retention characteristics of SONOS devices with SiO <sub>2</sub> (solid symbol) or high- $\kappa$ (open symbols) blocking oxide layers performed at V <sub>g</sub> = 0V with source/drain and substrate grounded. The devices were programmed to an initial V <sub>th</sub> shift of 1.25V before the retention measurements. (b) The same result as in (a) but with the time scale plotted up to 10 <sup>9</sup> seconds. The gate stacks of the SONOS devices are 25 Å SiO <sub>2</sub> / 50 Å Si <sub>3</sub> N <sub>4</sub> / 75 Å high- $\kappa$ or SiO <sub>2</sub> blocking oxide, as illustrated in Fig. 5.1 (a). | 87 |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 5.10: | Schematic energy band diagrams for SONOS devices with $Al_2O_3$ (solid lines) and $HfO_2$ (dashed lines) blocking oxide layer during charge retention measurement.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 88 |

| Figure 5.11: | Graph of $V_{th}$ shift after programming at $V_g$ - $V_{fb} = 6V$ , 100µs against the $V_{th}$ decay rate per decade of retention measurement time. Comparison between this work and published data (refer to Table 5.1).                                                                                                                                                                                                                                                                                                                                                                                                           | 89 |

| Figure 5.12: | Programming transient for (a) $V_g - V_{fb} = 9V$ (b) $V_g - V_{fb}$<br>= 11V and (c) $V_g - V_{fb} = 13.5V$ for SONOS devices<br>with HfO <sub>2</sub> , (HfO <sub>2</sub> ) <sub>0.48</sub> (Al <sub>2</sub> O <sub>3</sub> ) <sub>0.52</sub> or Al <sub>2</sub> O <sub>3</sub> blocking oxide<br>layers. The gate stacks of the SONOS devices are 40 Å<br>SiO <sub>2</sub> / 70 Å Si <sub>3</sub> N <sub>4</sub> / 120 Å high- $\kappa$ or SiO <sub>2</sub> blocking oxide, as<br>illustrated in Fig. 5.1 (b).                                                                                                                    | 91 |

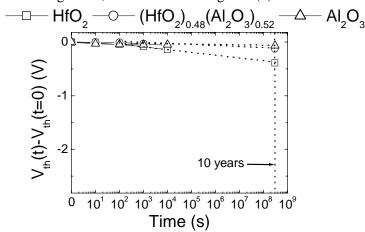

| Figure 5.13: | Erasing transient at $V_g - V_{fb} = -12.5V$ for SONOS devices<br>with HfO <sub>2</sub> , (HfO <sub>2</sub> ) <sub>0.48</sub> (Al <sub>2</sub> O <sub>3</sub> ) <sub>0.52</sub> or Al <sub>2</sub> O <sub>3</sub> blocking oxide<br>layers. The gate stacks of the SONOS devices are 40 Å<br>SiO <sub>2</sub> / 70 Å Si <sub>3</sub> N <sub>4</sub> / 120 Å high- $\kappa$ or SiO <sub>2</sub> blocking oxide, as<br>illustrated in Fig. 5.1 (b).                                                                                                                                                                                    | 92 |

| Figure 5.14: | Charge retention characteristics of SONOS devices with $HfO_2$ , $HfAlO$ or $Al_2O_3$ blocking oxide layers performed at $V_g = 0V$ and source/drain and substrate grounded. The devices were programmed to an initial $V_{th}$ shift of 2.9V before retention measurements.                                                                                                                                                                                                                                                                                                                                                         | 92 |

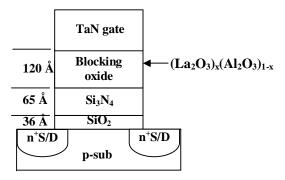

| Figure 5.15: | Fabricated SONOS structures with TaN gate electrode. The blocking oxide layer is $(La_2O_3)_x(Al_2O_3)_{1-x}$ with different composition ratios.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 94 |

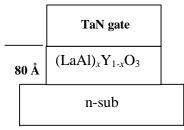

| Figure 5.16: | Fabricated $(LaAl)_x Y_{1-x}O_3$ capacitor structures with TaN gate electrode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 95 |

| Figure 5.17: | High-Frequency Capacitance-Voltage (HFCV)<br>measurements of SONOS capacitors with $(La_2O_3)_x(Al_2O_3)_{1-x}$<br>blocking oxide. The capacitors have dimensions of                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

|              | 200 μm × 200 μm.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 97 |

| Figure 5.18: | measurements of SONOS capacitors with $(La_2O_3)_x(Al_2O_3)_{1-x}$ blocking oxide. The capacitors have dimensions of                                                                                                                                                                                                       |     |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|              | $200 \ \mu\text{m} \times 200 \ \mu\text{m}.$                                                                                                                                                                                                                                                                              | 97  |

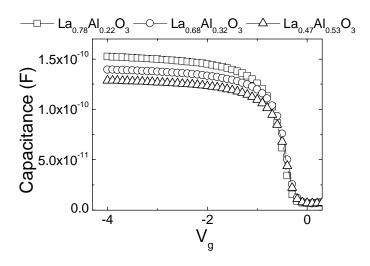

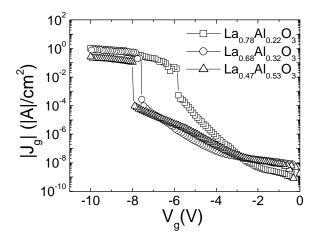

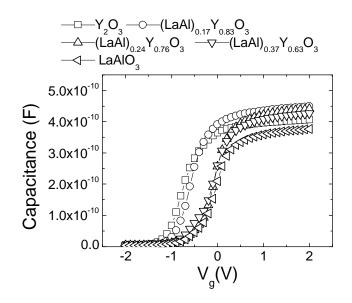

| Figure 5.19: | High-frequency capacitance-voltage (HFCV) results of capacitors with $(LaAl)_x Y_{1-x}O_3$ dielectric with different compositions. The capacitors have dimensions of 200 $\mu$ m × 200 $\mu$ m.                                                                                                                            | 98  |

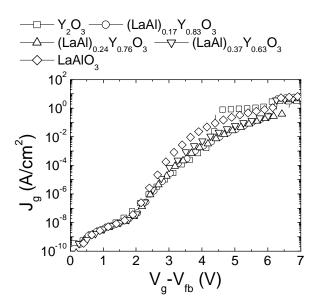

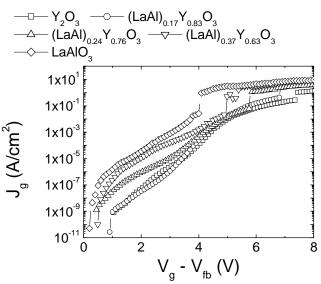

| Figure 5.20: | Gate-current versus gate voltage $(J_g-V_g)$ results of capacitors with $(LaAl)_x Y_{1-x}O_3$ dielectric with different compositions.<br>The capacitors have dimensions of 200 $\mu$ m × 200 $\mu$ m.                                                                                                                      | 99  |

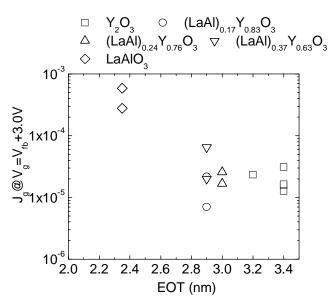

| Figure 5.21: | Gate-current density at gate voltage of 3V above the flatband voltage against EOT of capacitors with $(LaAl)_x Y_{1-x}O_3$ dielectric with different compositions. The capacitors have dimensions of 200 $\mu$ m × 200 $\mu$ m.                                                                                            | 99  |

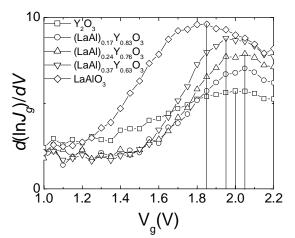

| Figure 5.22: | $d(\ln J)/dV$ plotted against V <sub>g</sub> for TaN /(LaAl) <sub>x</sub> Y <sub>1-x</sub> O <sub>3</sub> /n-Si devices.                                                                                                                                                                                                   | 100 |

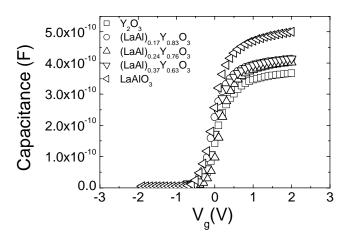

| Figure 5.23: | High-Frequency Capacitance-Voltage (HFCV) results of capacitors with $(LaAl)_x Y_{1-x}O_3$ dielectric with different compositions after 900°C, 60s, N <sub>2</sub> anneal. The capacitors have dimensions of 200 $\mu$ m × 200 $\mu$ m.                                                                                    | 102 |

| Figure 5.24: | Gate current versus gate voltage $(J_g-V_g)$ results of capacitors with $(LaAl)_x Y_{1-x}O_3$ dielectric with different compositions after 900°C, 60s, N <sub>2</sub> anneal. The capacitors have dimensions of 200 $\mu$ m × 200 $\mu$ m.                                                                                 | 102 |

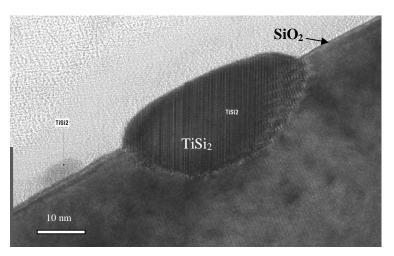

| Figure 6.1:  | TEM micrograph of TiN film on $SiO_2$ underlayer after 850°C, 10 s anneal in vacuum. EDX analysis revealed formation of TiSi <sub>2</sub> after annealing [6].                                                                                                                                                             | 110 |

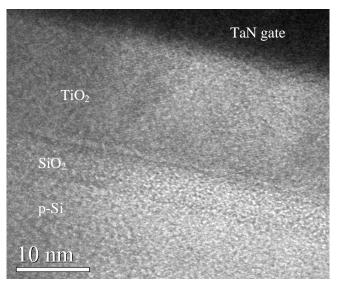

| Figure 6.2:  | TEM micrograph of $4$ nm SiO <sub>2</sub> /17nm TiO <sub>2</sub> layers after forming gas annealing at $420$ °C for 30 minutes.                                                                                                                                                                                            | 110 |

| Figure 6.3:  | Fabricated $SiO_2/TiO_2$ capacitor structures with TaN gate electrode.                                                                                                                                                                                                                                                     | 112 |

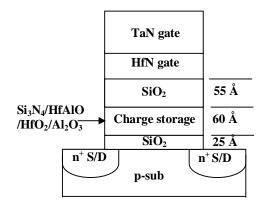

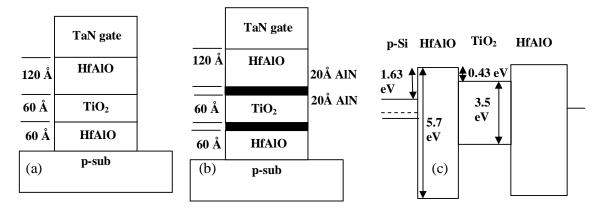

| Figure 6.4:  | (a) Device structure of fabricated HfAlO/TiO <sub>2</sub> /HfAlO<br>capacitor structures with TaN gate electrode (b) Device<br>structure of fabricated HfAlO/AlN/TiO <sub>2</sub> /AlN/HfAlO<br>capacitor structures with TaN gate electrode. (c) Ideal energy<br>band diagram of HfAlO/TiO <sub>2</sub> /HfAlO capacitor. | 112 |

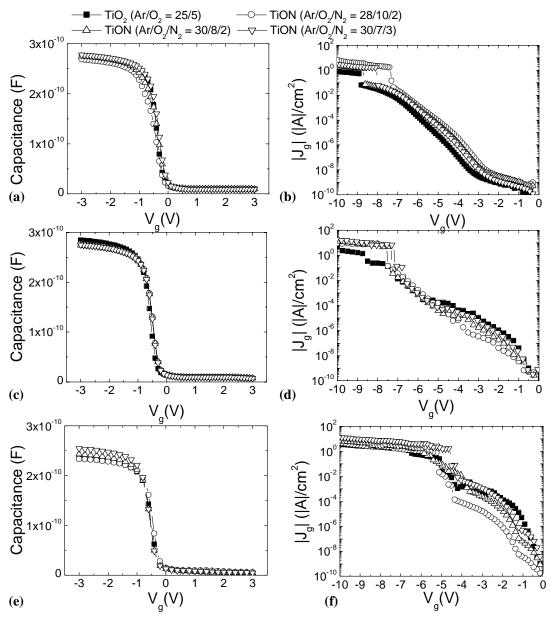

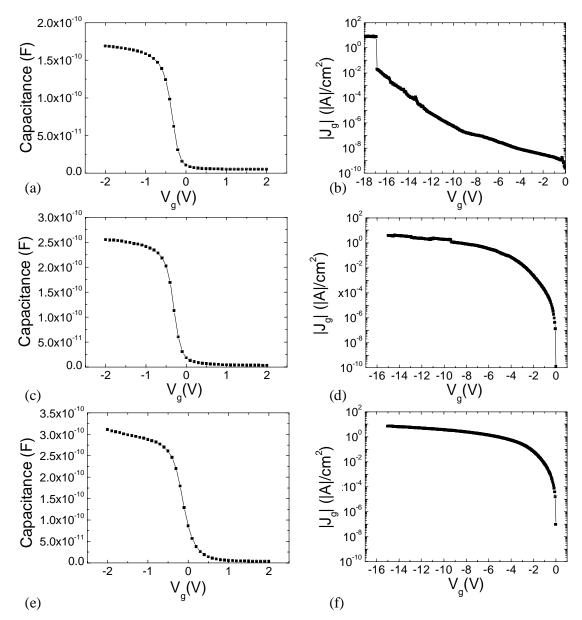

| Figure 6.5:  | (a), (c) and (e) HFCV and (b), (d) and (f) $J_g$ - $V_g$ graphs of                                                                                                                                                                                                                                                         |     |

|              | SiO <sub>2</sub> /TiO <sub>2</sub> capacitors; (a) and (b) after forming gas anneal only, (c) and (d) after 700°C, 30 s, O <sub>2</sub> PDA and (e) and (f) after 950°C, 30 s, N <sub>2</sub> anneal. The devices have gate areas of 200 $\mu$ m × 200 $\mu$ m.                                                                                                                               | 114 |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

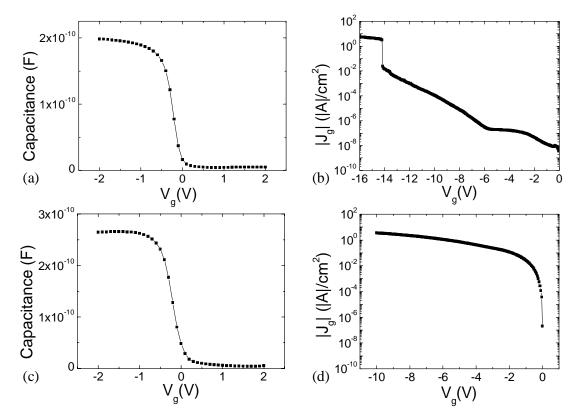

| Figure 6.6:  | (a) and (c) HFCV and (b) and (d) $J_g$ - $V_g$ graphs of HfAlO/TiO <sub>2</sub> /HfAlO capacitors; (a) and (b) after 700°C, 30 s, O <sub>2</sub> PDA of the TiO <sub>2</sub> layer and (c) and (d) after 900°C, 30 s, N <sub>2</sub> anneal. The devices have gate areas of 200 $\mu$ m × 200 $\mu$ m.                                                                                        | 116 |

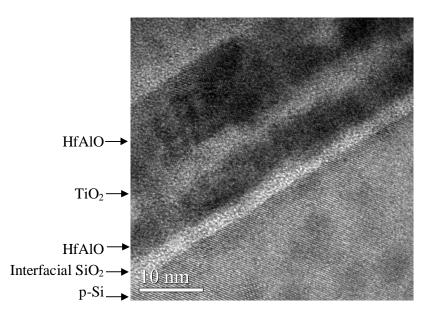

| Figure 6.7:  | TEM micrograph of HfAlO/TiO <sub>2</sub> /HfAlO capacitors after 900°C $N_2$ anneal for 30s.                                                                                                                                                                                                                                                                                                  | 116 |

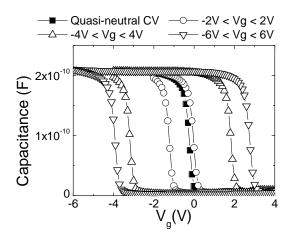

| Figure 6.8   | C-V curves of HfAlO/TiO <sub>2</sub> /HfAlO memory capacitors after PDA at 700°C for 30s in O <sub>2</sub> showing counter-clockwise hysteresis for various gate voltage (V <sub>g</sub> ) sweep ranges as indicated. The capacitance was measured at 100 kHz, with a gate voltage sweep rate of 0.1 V/s. Gate area is 200 $\mu$ m × 200 $\mu$ m.                                             | 117 |

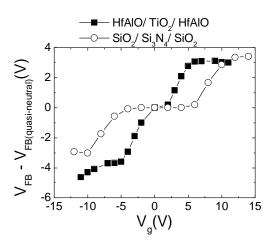

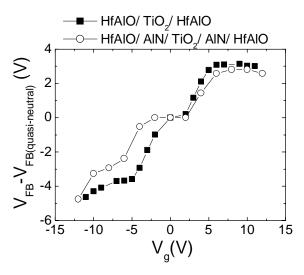

| Figure 6.9:  | Flatband voltage shift extracted from the hysteresis C-V curves plotted against the charging (positive) and discharging (negative) gate voltage for 60 Å HfAlO/60 Å TiO <sub>2</sub> /120 Å fAlO and 25 Å SiO <sub>2</sub> /60 Å Si <sub>3</sub> N <sub>4</sub> /60 Å SiO <sub>2</sub> memory devices. Gate area is 200 $\mu$ m × 200 $\mu$ m.                                                | 117 |

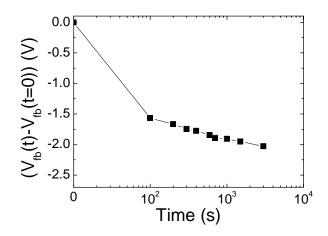

| Figure 6.10: | Charge retention characteristics of HfAlO/TiO <sub>2</sub> /HfAlO memory devices measured with $V_g = 0V$ . The devices were programmed to a V <sub>fb</sub> shift of 2.7V before retention measurement.                                                                                                                                                                                      | 118 |

| Figure 6.11: | (a), (c) and (e) are HFCV while (b), (d) and (f) are $J_g$ - $V_g$ graphs of HfAlO/AlN/TiO <sub>2</sub> /AlN/HfAlO capacitors; (a) and (b) with only 600°C, 30s, O <sub>2</sub> PDA of the TiO <sub>2</sub> layer, (c) and (d) after 800°C, 30 s, N <sub>2</sub> anneal while (e) and (f) after 900°C, 30 s, N <sub>2</sub> anneal. The devices have gate areas of 200 $\mu$ m × 200 $\mu$ m. | 119 |

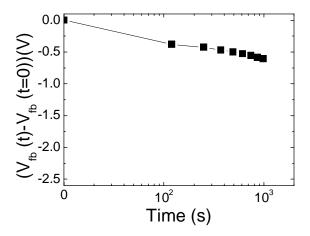

| Figure 6.12: | Retention characteristics of HfAlO/AlN/TiO <sub>2</sub> /AlN/HfAlO memory devices measured with $V_g = 0V$ . The devices were programmed to a $V_{fb}$ shift of 2.6V before retention measurement.                                                                                                                                                                                            | 120 |

| Figure 6.13: | Flatband voltage shift extracted from the hysteresis C-V<br>curves plotted against the charging (positive) and<br>discharging (negative) gate voltage for 60 Å HfAlO/60 Å<br>TiO <sub>2</sub> / 120 Å HfAlO and 60 Å HfAlO/20 Å AlN/60 Å<br>TiO <sub>2</sub> /20 Å AlN/120 Å HfAlO memory devices. Gate area is                                                                               |     |

|              | $200 \ \mu\text{m} \times 200 \ \mu\text{m}.$                                                                                                                                                                                                                                                                                                                                                 | 121 |

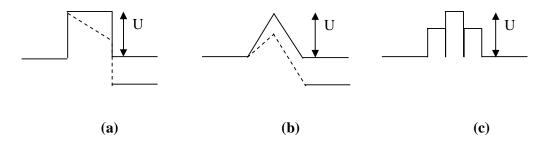

Figure 7.1:Conduction band edge diagrams of various tunnel barriers:<br/>(a) a typical uniform barrier; (b) idealized crested<br/>symmetric barrier; (c) crested, symmetric layered barrier.<br/>U is the maximum barrier height, expressed in units of energy.128

# List of Symbols

| Å               | $10^{-10}$ m                                        |

|-----------------|-----------------------------------------------------|

| MOS             | Metal oxide semiconductor                           |

| SONOS           | Polysilicon-oxide-silicon nitride-oxide-silicon     |

| EEPROM          | Electrically-erasable-programmable-read-only-memory |

| ONO             | Oxide-nitride-oxide                                 |

| W/L             | Transistor gate width to gate length dimensions     |

| C-V             | Capacitance-Voltage                                 |

| $V_{FB}$        | Flatband voltage                                    |

| P/E             | Program/erase                                       |

| PDA             | Post-deposition-anneal                              |

| XRD             | X-ray diffraction                                   |

| V <sub>th</sub> | Threshold voltage                                   |

| F-N             | Fowler-Nordheim                                     |

| I <sub>D</sub>  | Transistor drain current                            |

| μ               | Mobility of charge carrier                          |

| C <sub>ox</sub> | Gate oxide capacitance                              |

| V <sub>G</sub>  | Gate voltage                                        |

| V <sub>D</sub>  | Transistor drain voltage                            |

| γ               | Transistor body effect parameter                    |

| φ <sub>s</sub>  | surface potential                                   |

| $Q_{G}$         | Charge at the gate                                  |

| Qot             | Oxide trapped charge                                |

| Qs              | Charge in silicon                                   |

| E <sub>trap</sub> Energy level of charge trap |

|-----------------------------------------------|

|-----------------------------------------------|

- T Temperature (in Kelvin)

- k Boltzmann constant

- J<sub>g</sub> Gate current density

## **Chapter 1**

## Introduction

#### 1.1 Background

Since the very first days of the mid-1960s, when the potential of metal-oxidesemiconductor (MOS) technology to realize semiconductor memories with superior density and performance than would ever be achievable with the then commonly used magnetic core memories became known, chip makers have thought of solutions to overcome the main drawback of the MOS memory concept, that is, its intrinsic volatility. The first sound solutions to this problem were the floating gate concept [1] and the metal-nitride-oxide-semiconductor (MNOS) memory device [2] both of which were proposed in 1967. Tremendous progress has been made over the years in realizing the idea of a reliable, high-density reprogrammable read-only-memory (ROM) memory.

New applications and lower memory costs have driven increases in memory chip sales. Flash memory chips permitted cellular phones, audio internet players and digital cameras to be manufactured at a price that is affordable for consumers. The term Flash refers to the fact that the contents of the whole memory array, or of a memory block (sector), is erased in a single step. Low power and high-density dynamic random access memory (DRAM) chips permitted the personal digital assistant to meet low-power battery requirements and to have the capability of performing tasks that were once the domain of desktop personal computers (PCs). Advances in semiconductor lithography will continue to result in increased data storage density and lower costs per unit megabyte of storage. New nonvolatile memory technologies such as ferroelectric, polymer and magnetoresistive memories will promote new applications for nonvolatile memory and will allow nonvolatile memory to replace volatile memory in PCs, network equipment and cellular phone applications.

The basic operating principle of nonvolatile semiconductor memory devices is the storage of charges in the gate stack structure of a MOS field effect transistor (MOSFET). The charge storage can be realized in two ways, which has led to the subdivision of nonvolatile semiconductor memory devices into two main classes. The first class of devices is based on the storage of charge on a conducting or semiconducting layer that is completely surrounded by a dielectric, usually silicon dioxide (SiO<sub>2</sub>), as shown in Fig. 1.1(a). Since this layer acts as a completely electrically isolated gate, this type of device is commonly referred to as a floating-gate device [1]. In the second class of devices, the charge is stored in discrete trapping centers of an appropriate dielectric layer. These devices are, therefore, usually referred to as charge trapping devices. The most successful devices in this category are the MNOS (metal-nitride-oxide-silicon) and SONOS (silicon-oxide-nitride-oxidesilicon) or MONOS (metal-oxide-nitride-oxide-silicon) structures, in which the charge storage layer is a silicon nitride layer on top of a very thin silicon oxide layer. Figure 1.1(b) illustrates the SONOS structure.

**Figure 1.1**: Two classes of nonvolatile semiconductor memory devices: (a) floatinggate device and (b) charge-trapping device (SONOS device).

The Semiconductor Industry Association (SIA) International Technology Roadmap for Semiconductors (ITRS) [3] states that the difficult challenge, beyond the year 2005, for nonvolatile semiconductor memories is to achieve reliable, low-power, low-voltage performance. This challenge is formidable since memory program and erase operations are incompatible with aggresively scaled low-voltage devices. The ITRS projection is based on the continued scaling of polysilicon floating-gate nonvolatile semiconductor memory (NVSM) devices, which employ tunnel oxides with thicknesses greater than 7 nm and with concomitant program/erase electric fields in excess of 6 MV/cm [6]. The net result is the need for high-voltage generator charge-pump circuits.

Currently, most Flash electrically erasable and programmable read only memories (EEPROMs) are based on floating-gate devices [4]. However, the floating-gate memory has limitations with respect to scaling the cell size and program/erase voltages [5]. The relatively thick (7-12 nm) tunnel oxide in floating-gate type memories provides good 10-year data retention. However, the high voltage requirement [5] has created a reliability issue, as it has exceeded the voltage limits of the scaled peripheral complementary MOS (CMOS) devices. The concern over the loss of the entire memory charge through a single defect in the tunnel oxide limits vertical scaling of the tunnel oxide thickness [5]. The demand for low power and low voltage electronics has accelerated the pace for NVSM circuit designers to consider SONOS for low voltage, high density EEPROMs. The motivation for the interest in SONOS lies in low programming voltages, endurance to extended write/erase cycling, resistance to radiation and compatibility with high density scaled CMOS technology.

SONOS device structure, a single defect in the tunnel oxide will not result in the loss of the entire memory charge.

#### 1.2 Motivation for the Project

Applications for portable data equipment are becoming widespread, and in this field the nonvolatile memory is generating particularly strong interest. Pre-eminent among applications of nonvolatile memory are Flash memory cell structures. The Flash memory is a type of nonvolatile memory based on block erasure of electrically rewriteable EEPROM. Because it has achieved low cost and high integration, this type of memory is being put to a wide range of uses. Currently, most Flash EEPROMs are based on floating-gate devices [4]. However, the floating-gate memory has limitations with respect to scaling the cell size and program/erase voltages [5]. The demand for low power and low voltage electronics has accelerated the pace for NVSM circuit designers to consider SONOS for low voltage, high density EEPROMs. The floating-gate Flash EEPROM is a slow write/erase device because of low tunneling currents in the oxide [6]. Hence, the floating gate NVSM is limited to a rather low number (e.g., 10<sup>5</sup>) write/erase cycles due to a low charge-to-breakdown,  $Q_{BD}$ , of its relatively thick tunnel oxide. In contrast, an ultra-thin tunnel oxide can conduct a high current for a dramatic increase in the Q<sub>BD</sub> [6], leading to an improvement in NVSM reliability for scaled SONOS devices. In addition, the better scaling perspective, together with easier integration in a base line CMOS process, makes SONOS an excellent candidate for embedded Flash in the 90 nm technology node and beyond [7]. For example, the embedded SONOS NVSM requires only four additional noncritical masking steps over the base logic process, compared to eleven additional masking steps for the embedded floating-gate NVSM. Hence, SONOS

requires lower production cost. This makes SONOS memory as one of the most attractive candidates to realize Flash vertical scaling.

Increase in programming speed of SONOS devices and lower voltage operation had been accomplished previously by reducing the tunnel oxide thickness [8], [9]. However, this seriously degrades the charge retention capability of the device. To overcome this limitation, the SOHOS (polysilicon-oxide-high- $\kappa$ -oxide-silicon) Flash memory has been attempted by replacing the silicon nitride layer with a high dielectric constant (high- $\kappa$ ) material. Basically, due to the higher  $\kappa$  value, the equivalent oxide thickness is reduced for the same film physical thickness. Hence, the effect on device performance is expected to be similar to that of tunnel oxide scaling without the disadvantages that come with smaller physical thicknesses.

An alternative method to increase program/erase speed without decreasing the tunnel oxide thickness is by using a high- $\kappa$  material as the blocking oxide [10-13]. From electrostatics consideration, the use of a high dielectric constant blocking oxide layer will cause a smaller voltage drop across the blocking oxide and greater voltage drop across the tunnel oxide. This will result in a simultaneous increase of the electric field across the tunnel oxide and reduction of the electric field across the blocking oxide and reduction of the electric field across the blocking oxide leading to more efficient program and erase processes [10-13]. The effect of the  $\kappa$  (dielectric constant) value and band gap energy of the blocking oxide layer on the program/erase speed and charge retention of SONOS devices is also investigated.

## 1.3 Research Objectives

The objective of this project is to find innovative solutions, using high dielectric constant materials in the SONOS memory structure, to overcome the limitations of conventional floating-gate NVSM as a result of fast shrinking device geometries.

5

SONOS type memory devices with suitable high- $\kappa$  charge storage layers to replace Si<sub>3</sub>N<sub>4</sub> (SOHOS structure) will be fabricated and characterized. Different types of high- $\kappa$  materials with different band gaps, valence and conduction band offsets with respect to silicon,  $\kappa$ -value, crystallization temperature and other material properties will be evaluated. By using materials with higher dielectric constant compared to Si<sub>3</sub>N<sub>4</sub> will result in lower program/erase voltages due to higher tunnel oxide coupling ratio. In addition, by using materials with suitable band gap and valence and conduction band offsets, with respect to silicon, may reduce hole tunneling and over-erase effects.

In addition, the use of high- $\kappa$  blocking oxide in the SONOS memory device will be evaluated. The effect of the  $\kappa$  value and band gap energy of the blocking oxide layer on the program/erase speed and charge retention of SONOS devices is investigated by using hafnium aluminium oxide, or  $(HfO_2)_x(Al_2O_3)_{1-x}$ , with different concentration ratios (x) as the blocking oxide. Other high- $\kappa$  materials with suitable conduction and valence band offsets will also evaluated.

Finally, the integration of high- $\kappa$  tunnel and blocking oxides and ultra-high- $\kappa$  charge storage layer will also be demonstrated in this project.

#### 1.4 Organization of Thesis

Chapter 2 reports the key findings in the literature on SONOS memory devices with an emphasis on the use of high- $\kappa$  material in the SONOS memory structure.

Chapter 3 investigates the use of a hafnium oxide (HfO<sub>2</sub>) high- $\kappa$  charge storage layer in SONOS memory devices in order to increase the programming speed without reducing the tunnel oxide thickness. By using HfO<sub>2</sub> instead of Si<sub>3</sub>N<sub>4</sub> in the SONOS device structures, faster programming speed and over-erase reduction are achieved. Chapter 4 presents the results on SOHOS devices using hafnium aluminum oxide (HfAlO) as the charge storage layer. The SOHOS structure, with HfO<sub>2</sub> as the charge storage layer, demonstrates faster programming and less over-erase problem as compared to the conventional SONOS device using  $Si_3N_4$  as the charge storage layer. However, such a SOHOS device has poorer charge retention capability than SONOS and also poor program/erase endurance. On the other hand, using aluminum oxide (Al<sub>2</sub>O<sub>3</sub>) as the charge storage layer results in a SOHOS structure with improved charge retention performance, but at the expense of a slower programming speed. By adding a small amount of aluminum to HfO<sub>2</sub> to form HfAlO, it will be demonstrated that the resultant SOHOS structure with HfAlO as the charge storage layer can combine the advantages of both HfO<sub>2</sub> and  $Al_2O_3$ , such as fast programming speed, good charge retention capability and good program/erase endurance.

Chapter 5 investigates the use of a high- $\kappa$  blocking oxide in SONOS memory devices. The effect of the  $\kappa$  (dielectric constant) value and band gap energy of the blocking oxide layer on the program/erase speed and charge retention of SONOS devices is investigated by using (HfO<sub>2</sub>)<sub>x</sub>(Al<sub>2</sub>O<sub>3</sub>)<sub>1-x</sub> with different HfO<sub>2</sub> concentration ratios (x) as the blocking oxide. Other high- $\kappa$  materials with suitable conduction and valence band offsets are also evaluated.

Finally, the integration of high- $\kappa$  tunnel and blocking oxides and an ultra-high- $\kappa$  titanium dioxide (TiO<sub>2</sub>) charge storage layer into a SONOS memory structure is discussed in chapter 6. HfAlO/TiO<sub>2</sub>/HfAlO SOHOS capacitors showed much greater flatband voltage shift at lower program/erase voltages compared to the conventional SONOS device after post-deposition and forming gas anneal. Chapter 7 summarizes and concludes the work presented in this thesis.

### References

- [1] D. Kahng and S. M. Sze, "A floating gate and its application to memory devices", *Bell Syst. Tech. J.*, vol. 46, pp. 1288-1292, 1967.

- [2] H. A. R. Wegener, A. J. Lincoln, H. C. Pao, M. R. O'Connell and R. E. Oleksiak, "The variable threshold transistor, a new electrically alterable non-destructive read-only storage device", in *IEEE IEDM Tech. Dig.*, 1967, p. 70.

- [3] The International Technology Roadmap for Semiconductors (ITRS) 2005-Emerging Research Devices.

- [4] B. Kim, S. B. Yi and K. Y. Seo, "A scaled SONOS single transistor memory cell for a high density NOR structure with common source lines", *Journal of the Korean Physical Society*, vol. 41, pp. 945-948, 2002.

- [5] B. Jiankang and M. H. White, "Design considerations in scaled SONOS nonvolatile memory devices", *Solid State Electronics*, vol. 45, pp. 113-120, 2001.

- [6] M. H. White, D. A. Adams and B. Jiankang, "On the go with SONOS", *IEEE Circuits and Devices Magazine*, pp. 22-31, 2000.

- [7] C. T. Swift, G. L. Chindalore, K. Harber, T. S. Harp, A. Hoefler, C. M. Hong,

P. A. Ingersoll, C. B. Li, E. J. Prinz and J. A. Yater, "An embedded 90 nm

SONOS nonvolatile memory utilizing hot electron programming and uniform tunnel erase", in *IEEE IEDM Tech. Dig.*, 2002, p. 927.

- [8] M. L. French and M. H. White, "Scaling of multidielectric nonvolatile SONOS memory structures", *Solid State Electronics*, vol. 37, pp. 1913-1923, 1994.

- [9] M. L. French, C. Y. Chen, H. Sathianathan and M. H. White, "Design and scaling of a SONOS multidielectric device for nonvolatile memory

applications", IEEE Trans. Components, Packaging and Manufacturing Technology.- Part A, vol. 17, pp. 390-397, 1994.

- [10] V.A. Gritsenko, "Design of SONOS memory transistor for Terabit scale

EEPROM", in *IEEE Conf. Electron Device and Solid State Circuits*, 2003, p. 345.

- [11] C. H. Lee, K. I. Choi, M. K. Cho, Y. H. Song, K. C. Park and K. Kim, "A novel SONOS structure of SiO<sub>2</sub>/SiN/Al<sub>2</sub>O<sub>3</sub> with TaN metal gate for multigigabit flash memories", in *IEDM Tech. Dig.*, 2003, p. 613.

- [12] S. Choi, M. Cho, H. Hwang and J. W. Kim, "Improved metal-oxide-nitrideoxide-silicon-type flash device with high-κ dielectrics for blocking layer", J. *Appl. Phys.*, vol. 94, pp. 5408-5410, 2003.

- [13] C. H. Lee, S. H. Hur, Y. C. Shin, J. H. Choi, D. G. Park and K. Kim, "Chargetrapping device structure of SiO<sub>2</sub>/SiN/High-κ dielectric Al<sub>2</sub>O<sub>3</sub> for high-density flash memory", *Appl. Phys. Lett.*, vol. 86, pp. 152908 (1-3), 2005.

## Chapter 2

## **Literature Review**

### 2.1 History of Nonvolatile Memory Structures

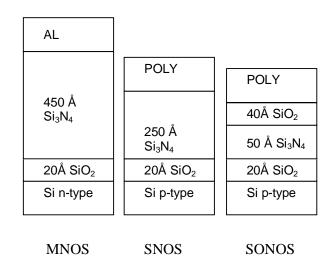

The first nonvolatile metal-oxide-semiconductor (MOS) memory device was introduced in 1967 by D. Kahng and S. M. Sze [1]. Their idea was to use a floatinggate device to store charges. The memory transistor that they proposed started from a basic MOS structure where the gate structure is replaced by a layered structure of a thin oxide, a floating but conducting metal layer, a thick oxide and an external metal gate, as shown in Fig. 2.1. This device is referred to as the MIMIS (metal-insulatormetal-insulator-semiconductor) cell. Electrons were injected into the floating-gate by direct tunneling during programming. To discharge the floating-gate, a negative voltage pulse is applied to the metal gate, removing the electrons by the same direct tunneling mechanism.

The tunnel oxide thickness is limited to less than 5 nm due to the direct tunneling programming mechanism. Hence, any defects in the tunnel oxide will cause all the stored charges in the floating-gate to leak off. Due to technological constraints, the MIMIS cell could not be reliably built at that time. However, the introduction of this device contained several important concepts that have led to the development of both classes of nonvolatile memory devices. The direct tunneling concept has been used in charge trapping devices while the floating-gate concept has led to a whole range of floating-gate memory types.

In order to solve the technological constraint of the MIMIS cell, two approaches are possible: (1) replacing the conducting charge trapping layer with an

10

insulating one, or (2) increasing the tunnel dielectric thickness and employing other charge injection mechanisms.

The first solution was used in the MNOS (metal-nitride-oxide-semiconductor) cell (Fig. 2.1 (b)), introduced by Wegener *et al.* [2], almost simultaneously with the MIMIS cell. In the MNOS cell, the polysilicon floating-gate is replaced by a nitride layer, which contains numerous electron and hole trapping centers. As the charge storage layer is an insulator, any defects in the tunnel oxide will not cause all the stored charges to leak out.

Figure 2.1: Two classes of nonvolatile semiconductor memory devices: (a) floatinggate device and (b) charge-trapping device (MNOS device).

The second solution has been used in a wide range of nonvolatile memory devices. The first operating floating-gate device, shown in Fig. 2.2, was introduced in 1971 by Frohman-Bentchkowsky and is known as the Floating-gate Avalanche injection MOS (FAMOS) device [3-6]. In the original p-channel FAMOS cell, the floating-gate is completely surrounded by a thick (~ 100 nm) oxide. Hence the problem of possible shorting paths is reduced. In the FAMOS cell, programming is performed by charge transport to the floating-gate by avalanche injection of electrons from a reverse biased p-n junction. However, no mechanism for electrical erasure exists due to the lack of an external gate. Hence, erasure was done using ultraviolet

(UV) irradiation. The FAMOS device has found wide applications and was the first cell to reach volume manufacturing levels comparable to other semiconductor memory types. FAMOS devices have evolved into a class of memory products called EPROM (electrically-programmable-read-only-memory).

**Figure 2.2**: First operating floating-gate device: the FAMOS (Floating-gate Avalanche injection MOS) device, introduced by Frohman-Bentchkowsky [3-6].

The drawbacks of the FAMOS device were alleviated in several adapted concepts. In the Stacked gate Avalanche injection MOS (SAMOS) [7-8], as shown in Fig. 2.3, an external control gate is added to improve the writing efficiency by an increased drift velocity of the electrons in the oxide and a field-induced energy barrier lowering at the silicon-silicon dioxide (Si-SiO<sub>2</sub>) interface. Electrical erasure also became possible by field emission through the top dielectric due to polyoxide conduction. Consequently, electrically-erasable-programmable-read-only-memory (EEPROM) products became feasible.

These first floating-gate memory devices were all p-channel devices. In nchannel devices, drain avalanche results in hole injection, which is much less efficient due to the higher energy barrier experienced by the holes. Hence, for n-channel devices, several alternative injection mechanisms were proposed and used for floating-gate applications. These include Fowler-Nordheim (F-N) tunneling through thin oxides (<12 nm) and channel hot-electron (CHE) injection [9].

**Figure 2.3**: The SAMOS (Stacked gate Avalanche injection MOS) device [7-8]. The device is written like the FAMOS device. Several different erasure mechanisms are possible.

F-N tunneling is a field-assisted electron tunneling mechanism. At high electric fields, electrons in the silicon conduction band will see a triangular energy barrier with a width dependent on the applied field. Electrons in the silicon conduction band can tunnel through the triangular energy barrier giving rise to F-N current.

At large drain biases, the minority carriers that flow in the channel of a MOS transistor are heated by the large electric fields seen at the drain side of the channel and their energy distribution is shifted higher. These electrons can collide with the silicon lattice atoms near the drain and generate minority and majority carriers through impact ionization. The majority carriers are normally collected at the substrate contact and form the substrate current. The minority carriers are collected at the drain. Some of these carriers gain enough energy to surmount the Si-SiO<sub>2</sub> energy barrier. If the oxide field favours injection, these carriers are injected over the barrier into the gate insulator and give rise to the so-called hot carrier injection gate current.

The first nonvolatile memory product that can be electrically programmed by the user and erased afterwards is the EPROM device, introduced in the 1970s. Programming can be carried out by channel hot-electron injection while UV light is used to erase the memory. The EPROM cell can consist of a single transistor as it does not need addressing down to the byte level during an erase operation.

Since UV light is used for erasure, a quartz window has to be provided in the EPROM package, which makes this package quite expensive. Reprogramming of the device is also not user friendly. The circuit has to be taken off the circuit board for erasing. The erase operation takes about 20 minutes, and then the whole memory has to be reprogrammed byte by byte. This rather tedious procedure must be performed even if the content of a single byte has to be changed. These drawbacks have been obviated in the EEPROM. As both programming and erasing are controlled by electrical signals, the circuit can be reprogrammed while residing on the circuit board. Each operation, including erasing, can be performed in a byte-addressable way. The EEPROM cell consists of a memory transistor and a select transistor [10], thus leading to the so-called two transistor memory cell. However, the large area requirements and the relatively high operating voltages (15 to 20 V) due to the thick (8 to 10 nm) tunnel oxide limits further scaling down of the EEPROM cell [11]. Charge-trapping, as well as floating-gate devices, are used for EEPROM products.

During the 1980s, a novel nonvolatile memory product was introduced; referred to as the Flash EEPROM [12]. The general idea was to combine the fast programming capability and high density of EPROMs with the electrical erasibility of EEPROMs. The first products were merely the result of adapting EPROMs in such a way that the cell could be erased electrically. Consequently, these devices use channel hot-electron injection for programming and F-N tunneling for erasure. The memory

14

can be erased electrically but not selectively. The content of the whole memory chip is always cleared in one step. The advantages over the EPROM are the faster (electrical) erasure and the in-circuit reprogrammability, which leads to a cheaper package. Although Flash EEPROM has a higher density compared to traditional EEPROM, many bytes are erased simultaneously instead of a single byte at a time. The Flash memory technology has been a dominant technology for the past two decades.

Other forms of nonvolatile memory technologies that have evolved in the past few decades include the MNOS, SONOS (polysilicon-oxide-nitride-oxide-silicon) and ferroelectric devices. The MNOS devices were invented in 1967 [2] and were the first electrically alterable read only memory (EAROM) devices. The nonvolatile function of these devices is based on the storage of charges in discrete traps in the nitride layer. These charges (electrons or holes) are injected from the channel region into the nitride by quantum mechanical tunneling through an ultra-thin oxide (typically 1.5 to 3nm).

Hole injection from the gate limits the memory window in MNOS devices. The problem becomes more severe for thinner nitride layers. An efficient way to solve this problem is by introducing a top blocking oxide layer in between the silicon nitride and the gate electrode resulting in the SONOS memory structure [13]. The aim of the top oxide is not only to inhibit gate injection, but also to block the charges injected from the silicon substrate at the top oxide-nitride interface. This results in higher trapping efficiency. In this way, the total thickness of the insulator structure can be reduced, and consequently, the programming voltage can be reduced.

Ferroelectric memory devices store information based on polarization state rather than stored charge [14]. Certain crystalline materials show the tendency to polarize spontaneously under the influence of an external field and to remain

15

polarized after the external field is removed. The polarization can simply be reversed by applying a field of opposite polarity. The ferroelectric material used is a leadzirconate-titanate compound (Pb[Zr, Ti]O<sub>3</sub>, PZT), which is a perovskite-type ceramic. These memories have fast write time (~100 ns) and good endurance [15]. However, the main drawback is the problem of incorporating these materials to mainstream silicon technology [16].

#### 2.2 Current and Future Nonvolatile Memories

The present baseline for non-volatile memory technology is based on both NOR and NAND Flash employing the floating-gate structure [17]. The current Flash technology node, based on the polysilicon half pitch, is at 70 nm for NOR Flash and 64 nm for NAND Flash. According to the International Technology Roadmap for Semiconductors, the difficult challenge for Flash scaling to 32 nm technology and beyond is the non-scalability of the tunnel and interpoly dielectrics [17].

In the coming years, portable systems will demand even more nonvolatile memories, either with high density and very high writing throughput for data storage application or with fast random access for code execution. Although in the past, different types of Flash cells and architectures have been proposed, two of them can be considered as industry standard today. These are the common ground NOR Flash due to its versatility in addressing both the code and data storage segments, and the NAND Flash which is optimized for the data storage market. In code storage, the program or operating system is stored in the Flash memory (usually NOR structure) and is executed by the microprocessor or microcontroller [18]. NOR chips function like a computer's main memory, while NAND works like a hard disk. For example, in

a digital camera, NOR Flash contains the camera's internal software, while NAND Flash is used to store the images.

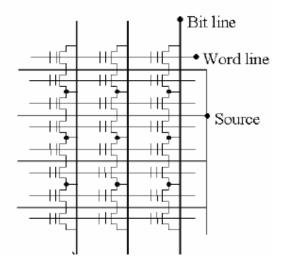

The "NOR" Flash name is related to the way the cells are arranged in an array, through rows and columns in a NOR-like structure as shown in Fig. 2.4. Flash cells sharing the same gate constitute the so-called word line (WL), while those sharing the same drain electrode (one contact common to two cells) constitute the bit line (BL). In this array organization, the source electrode is common to all of the cells (Fig. 2.4). A NOR Flash memory cell is usually programmed by channel hot electron injection into the floating gate at the drain side and it is erased by means of Fowler-Nordheim electron tunneling through the tunnel oxide from the charge storage layer to the silicon surface.

Figure 2.4: NOR Flash array equivalent circuit [18].