# NOVEL DESIGN AND IMPLEMENTATION OF A BROADBAND AND HIGHLY EFFICIENT DOHERTY POWER AMPLIFIER

MEHDI SARKESHI

(M. ENG, National University of Singapore)

A THESIS SUBMITTED

FOR THE DEGREE OF MASTER OF ENGINEERING

DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

NATIONAL UNIVERSITY OF SINGAPORE

2007

### Acknowledgements

I am truly indebted to my supervisors, Assoc. Prof. Ooi Ban Leong and Prof. Leong Mook Seng for their invaluable guidance and support during this work. I would specially wish to extend my thank to Ms. Atoosa Nasiri for her support and encouragement without which, this journey would not be so pleasant and memorable.

I would also like to gratefully acknowledge Mr. Tan Hong San for his kind support during my studies. Lastly, I would like to thank my parents for their endless love and priceless support.

Mehdi Sarkeshi

July 2007

### Contents

| Acknowledgements                          | i    |

|-------------------------------------------|------|

| Abstract                                  | viii |

| List of Tables                            | x    |

| List of Figures                           | xi   |

| List of Symbols                           | xix  |

| 1 Introduction                            | 1    |

| 1.1 Power Amplifiers                      | . 2  |

| 1.1.1 Conjugate Match and Load-line Match | . 2  |

|          |     | 1.1.2       | Output Efficiency and Power Added Efficiency |

|----------|-----|-------------|----------------------------------------------|

|          |     | 1.1.3       | Power Amplifier Classification               |

|          |     |             | 1.1.3.1 Class A                              |

|          |     |             | 1.1.3.2 Class B                              |

|          |     |             | 1.1.3.3 Class AB                             |

|          |     |             | 1.1.3.4 Class C                              |

|          |     |             | 1.1.3.5 Class D                              |

|          |     |             | 1.1.3.6 Class E $\ldots$ 12                  |

|          |     |             | 1.1.3.7 Class F                              |

|          |     |             | 1.1.3.8 Class S                              |

|          | 1.2 | RF Po       | wer Amplifier Technologies                   |

|          |     | 1.2.1       | Si-BJT and CMOS Power amplifiers 17          |

|          |     | 1.2.2       | LDMOS                                        |

|          |     | 1.2.3       | GaAs HBT                                     |

|          |     | 1.2.4       | SiGe HBT                                     |

|          |     | 1.2.5       | GaAs HEMT                                    |

|          | 1.3 | Resear      | rch Focus                                    |

|          | 1.4 | Disser      | tation Organization                          |

| <b>2</b> | The | <b>Dohe</b> | rty Power Amplifier 26                       |

|   | 2.1 | Effici  | ency Enhancement Techniques                                 | 26 |

|---|-----|---------|-------------------------------------------------------------|----|

|   |     | 2.1.1   | Envelope Elimination and Restoration (Kahn Technique)       | 27 |

|   |     | 2.1.2   | Bias Adaptation (Envelope Tracking)                         | 28 |

|   |     | 2.1.3   | Switched Dynamic Biasing Technique                          | 29 |

|   |     | 2.1.4   | Chireix Outphasing Technique (LINC Amplifier)               | 31 |

|   | 2.2 | The D   | Ooherty Technique                                           | 32 |

|   |     | 2.2.1   | Principles of Doherty Amplifier                             | 32 |

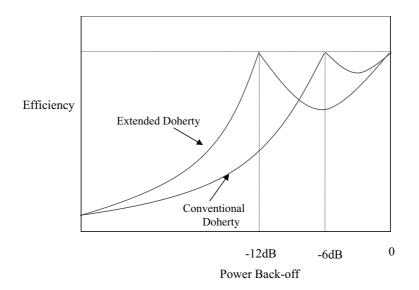

|   |     | 2.2.2   | Extended Doherty Amplifier                                  | 47 |

|   |     | 2.2.3   | Doherty Power Amplifier with uneven power-divide $\ldots$ . | 48 |

|   |     | 2.2.4   | Doherty Amplifier with offset lines                         | 50 |

|   |     | 2.2.5   | Doherty Amplifier with Envelope Tracking                    | 51 |

|   |     | 2.2.6   | Multi-stage Doherty Amplifier                               | 52 |

|   |     | 2.2.7   | Doherty Amplifier with active power splitter                | 55 |

|   |     | 2.2.8   | The Series-type Doherty Amplifier                           | 55 |

|   |     | 2.2.9   | Linearizing The Doherty Power Amplifier                     | 56 |

| 3 | AN  | Novel 7 | Topology for the Doherty Amplifier                          | 58 |

|   | 3.1 | Proble  | ems With The Conventional Approach                          | 58 |

|   |     | 3.1.1   | Large Size                                                  | 59 |

|   |     | 3.1.2   | Bandwidth                                                   | 60 |

|   |     | 3.1.3   | Effect of Parasitics on Load Modulation                        | 60 |

|---|-----|---------|----------------------------------------------------------------|----|

|   | 3.2 | The N   | ovel Impedance Transformation                                  | 63 |

|   |     | 3.2.1   | Envelope Tracking for Load Modulation                          | 64 |

|   |     | 3.2.2   | Adaptive Impedance Matching                                    | 65 |

|   |     |         | 3.2.2.1 Varactor-based RF Adaptability                         | 68 |

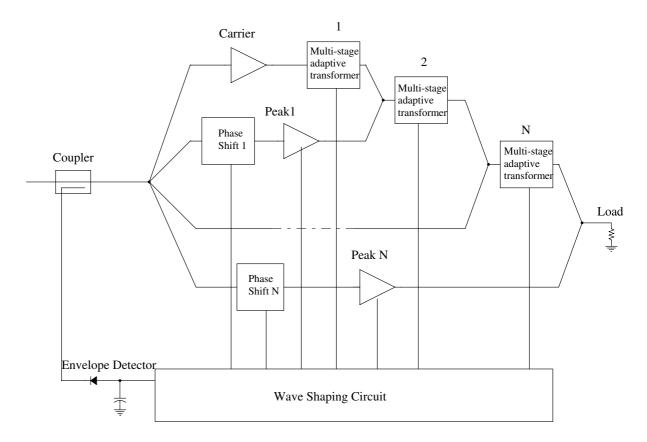

|   |     | 3.2.3   | Solution Generalization, Broadband Performance                 | 69 |

| 4 | The | eoretic | al Development                                                 | 71 |

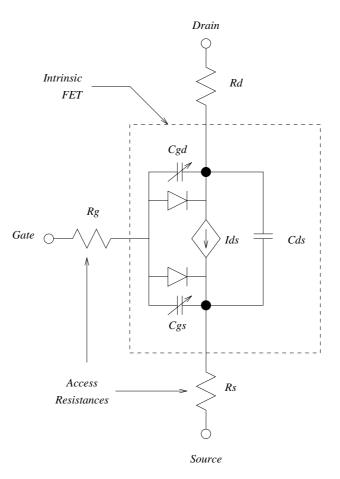

|   | 4.1 | Device  | e Modeling                                                     | 72 |

|   |     | 4.1.1   | TOM-2 Model                                                    | 72 |

|   |     | 4.1.2   | Equivalent Circuit                                             | 72 |

|   |     | 4.1.3   | Basic Equations                                                | 74 |

|   |     |         | 4.1.3.1 Current Source Equations                               | 74 |

|   |     |         | 4.1.3.2 Capacitance Equations                                  | 76 |

|   |     |         | 4.1.3.3 Temperature Effects                                    | 77 |

|   |     |         | 4.1.3.4 Model Parameters and scaling                           | 78 |

|   |     |         | 4.1.3.5 Expressions for the Conductances                       | 78 |

|   | 4.2 | Load I  | Pull                                                           | 81 |

|   | 4.3 | Analy   | sis of Varactor-based Adaptive Impedance Transformers $\ldots$ | 84 |

|   |     | 4.3.1   | Linearity of Varactor-based Adaptive Circuits                  | 85 |

|   |                |         | 4.3.1.1   | Shunt Varactor Circuits                                | 86  |

|---|----------------|---------|-----------|--------------------------------------------------------|-----|

|   |                |         | 4.3.1.2   | Series Varactor Circuits                               | 87  |

|   |                | 4.3.2   | Multi-die | ode configurations                                     | 88  |

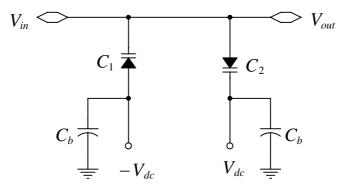

|   |                |         | 4.3.2.1   | Anti-parallel configuration                            | 88  |

|   |                |         | 4.3.2.2   | Anti-series configuration                              | 89  |

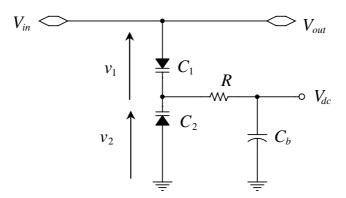

|   |                | 4.3.3   | The prop  | posed topology for adaptive load modulation $\ldots$ . | 93  |

| 5 | $\mathbf{Sim}$ | ulatior | and M     | easurements                                            | 95  |

|   | 5.1            | Design  | and Sim   | ulation of a class AB Power Amplifier                  | 96  |

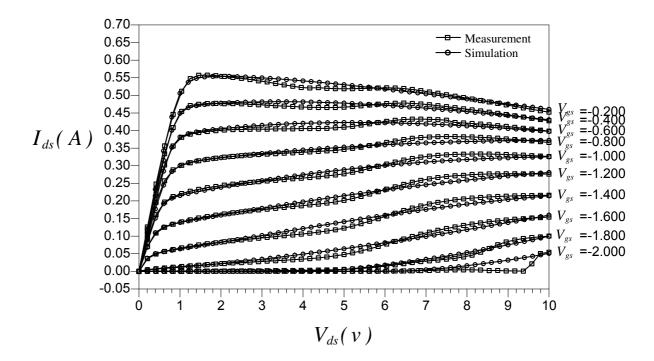

|   |                | 5.1.1   | DC IV-C   | Curves Simulation and Measurement                      | 96  |

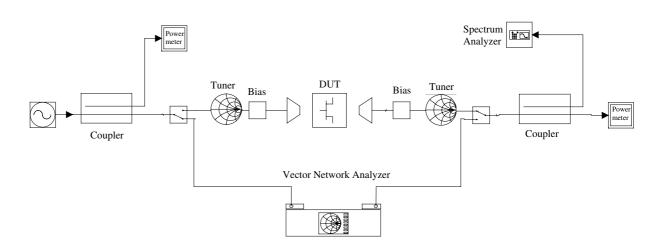

|   |                | 5.1.2   | Load Pu   | ll Setup                                               | 98  |

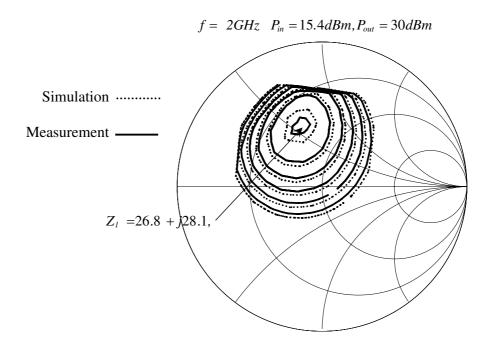

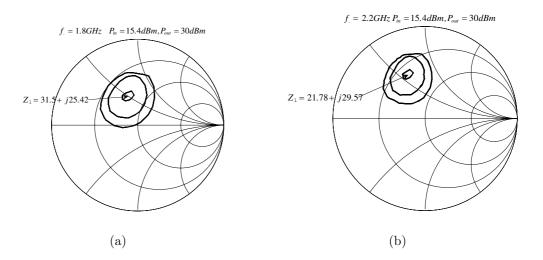

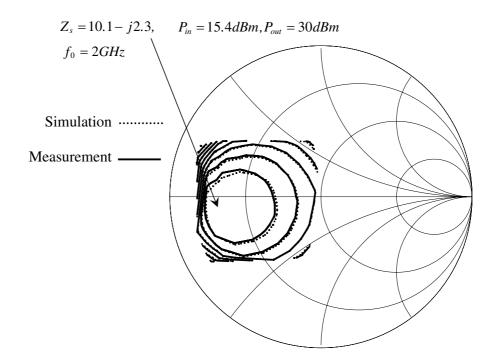

|   |                | 5.1.3   | Load Pu   | ll Simulation and Measurement                          | 98  |

|   |                | 5.1.4   | Input an  | d Output Matching Network Design                       | 99  |

|   |                |         | 5.1.4.1   | Input Matching Network                                 | 99  |

|   |                |         | 5.1.4.2   | Output Matching Network                                | 103 |

|   | 5.2            | Perform | mance of  | the Class AB Power Amplifier                           | 103 |

|   | 5.3            | Design  | and Sim   | ulation of a Conventional Doherty Amplifier            | 108 |

|   | 5.4            | Design  | of the A  | daptive Impedance Transformer                          | 114 |

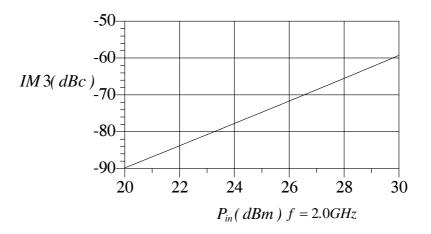

|   |                | 5.4.1   | Linearity | y of the Adaptive Impedance Transformer                | 116 |

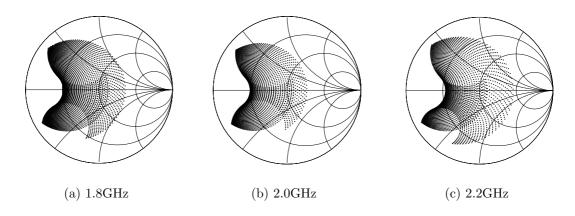

|   |                | 5.4.2   | Design    | of the Impedance Transformation Trajectory $\ldots$ .  | 116 |

|       | 5.4.3   | Design of the Phase Compensator                           | . 117 |

|-------|---------|-----------------------------------------------------------|-------|

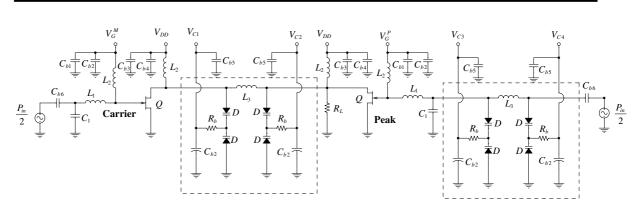

| 5.5   | Desig   | n of the Doherty Amplifier with Adaptive Impedance Trans- |       |

|       | forme   | r                                                         | . 120 |

| 5.6   | Perfor  | rmance Comparison                                         | . 127 |

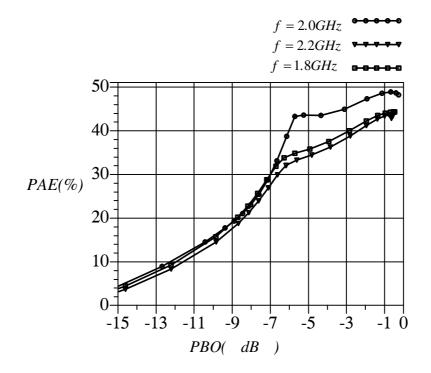

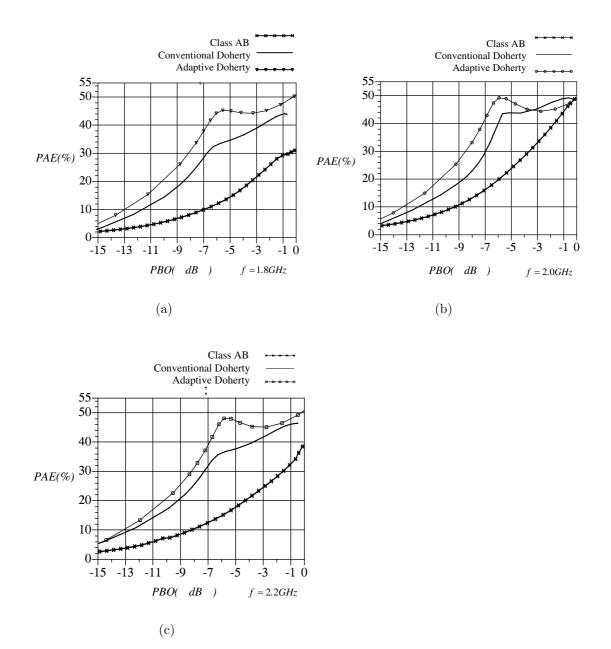

|       | 5.6.1   | Power Added Efficiency                                    | . 127 |

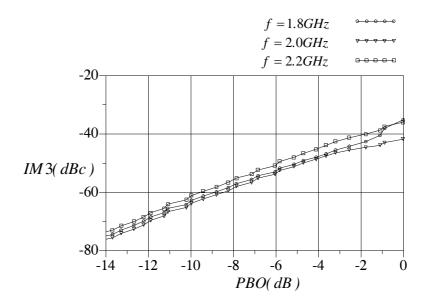

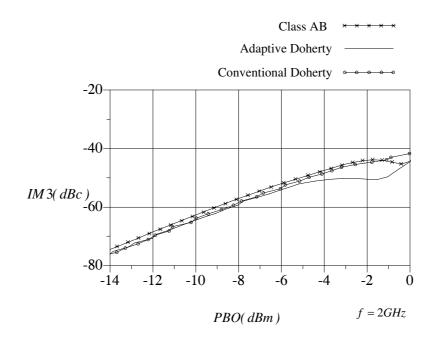

|       | 5.6.2   | Linearity                                                 | . 128 |

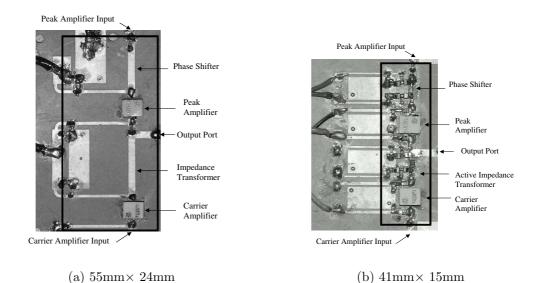

|       | 5.6.3   | Size                                                      | . 128 |

| 6 Co  | nclusio | ons                                                       | 131   |

| Refer | ences   |                                                           | 133   |

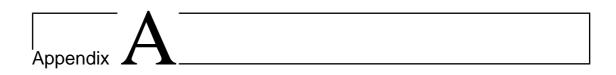

| A Ma  | anufact | urer Specifications of the Selected Transistor            | 142   |

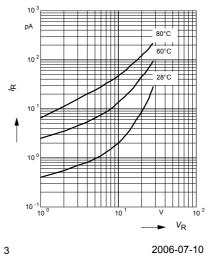

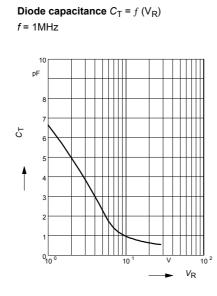

| B Ma  | anufact | urer Specifications of the Selected Varactor Diode        | 145   |

### Abstract

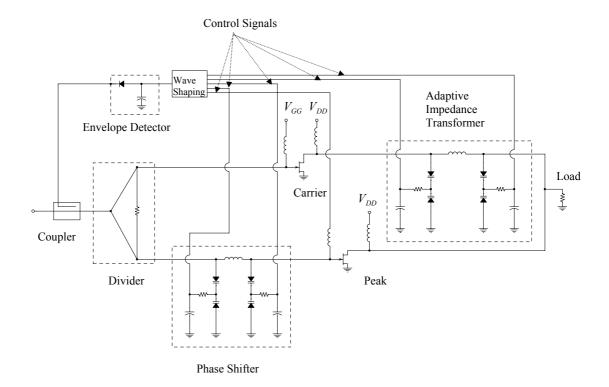

Modern communication systems require stringent capabilities in terms of linearity and efficiency. The need to amplify a variable envelope signal with high peak-toaverage ratio in multi-carrier technologies such as WCDMA or OFDM, imposes tough challenges on the amplifiers that basically deliver their highest efficiency at their maximum output power. The Doherty power amplifier has recently gained a lot of attraction due to its simple concept, ease of implementation and promising efficiency enhancement in backed-off power region. However, the conventional Doherty power amplifier suffers from some disadvantages such as narrow bandwidth and large size due to its critical use of passive  $\lambda/4$ -transmission lines as impedance inverters. In this work, a novel configuration is proposed, which promises to eliminate the above mentioned problems by replacing the  $\lambda/4$ -transmission line with an adaptive, compact and broadband alternative. A highly linear, varactor-based impedance transformer is placed at the output of the carrier amplifier, which performs wideband load-modulation by adaptively biasing the varactors according to the input signal envelope. Infineon's BB837 varactors have been used to realize the adaptive impedance inverter.

Three configurations, namely, a class AB, a conventional Doherty amplifier and the proposed novel Doherty amplifier, have been designed, simulated and fabricated using Transcom's TC2571 GaAs pHEMT discrete transistors. The proposed Doherty amplifier has displayed superior performance to the other two designs. Power added efficiency of more than 49.5% is achieved at maximum power level(33dBm) over a wide bandwidth (1.8GHz-2.2GHz). The high power added efficiency has been maintained within the 6-dB backoff power range. At 6-dB backoff point, power added efficienciy is more than 45.3% within the bandwidth of 1.8GHz to 2.2GHz. Third order harmonic distortion has been better than -42dBc within the entire power range over the above mentioned bandwidth. This verifes broadband performance of the proposed circuit. Moreover, 50% size reduction compared to conventional Doherty amplifier is achieved as a direct result of elimination of the  $\lambda/4$ -transmission lines .

## List of Tables

| 1.1 | Common technologies for RF power amplifiers                         | 17  |

|-----|---------------------------------------------------------------------|-----|

| 4.1 | TOM-2 model parameters                                              | 79  |

| 5.1 | Design Objectives for the proposed Doherty amplifier                | 96  |

| 5.2 | The class AB design components                                      | 104 |

| 5.3 | The conventional Doherty amplifier components $\ . \ . \ . \ . \ .$ | 110 |

| 5.4 | The proposed Doherty amplifier components                           | 123 |

## List of Figures

| 1.1 | Optimum load resistance for maximum power delivery                                                                         | 3  |

|-----|----------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Class-A mode                                                                                                               | 6  |

| 1.3 | Class-B mode                                                                                                               | 7  |

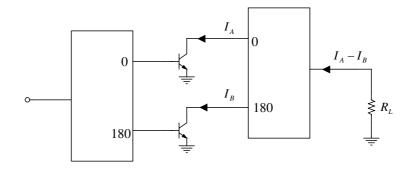

| 1.4 | Push-pull class B amplifier with power combiner                                                                            | 7  |

| 1.5 | (a) and (b): Currents of the individual transistors and (c): Com-                                                          |    |

|     | bined current waveform                                                                                                     | 8  |

| 1.6 | Schematic diagram of a class-B Power Amplifier                                                                             | 8  |

| 1.7 | Class-AB mode                                                                                                              | 9  |

| 1.8 | Class-C mode                                                                                                               | 10 |

| 1.9 | Power amplifier classes categorized based on the quiescent current $% \left( {{{\bf{n}}_{{\rm{s}}}}_{{\rm{s}}}} \right)$ . | 11 |

| 1.10 | Schematic diagram of a class D power amplifier               | 12 |

|------|--------------------------------------------------------------|----|

| 1.11 | Class D current and voltage waveforms                        | 13 |

| 1.12 | Schematic diagram of a class E power amplifier               | 14 |

| 1.13 | Voltage and current waveforms of a class $E$ power amplifier | 14 |

| 1.14 | Schematic diagram of a class F amplifier                     | 15 |

| 1.15 | Schematic diagram of a class S amplifier                     | 16 |

| 1.16 | Si BJT cross-sectional structure                             | 18 |

| 1.17 | NMOS cross-sectional structure                               | 18 |

| 1.18 | LDMOS cross-sectional structure                              | 19 |

| 1.19 | GaAs HBT cross-sectional structure                           | 20 |

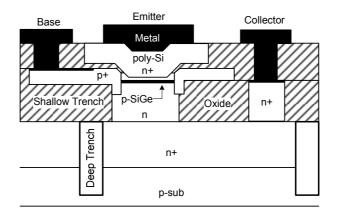

| 1.20 | SiGe HBT cross-sectional structure                           | 21 |

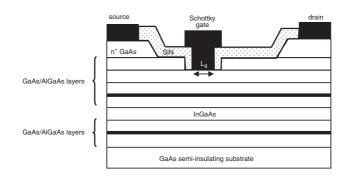

| 1.21 | GaAs pHEMT cross-sectional structure                         | 23 |

| 1.22 | Transcom's TC2571 Pseudomorphic-HEMT                         | 23 |

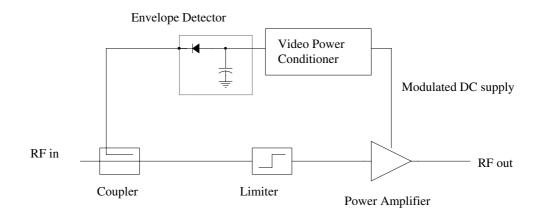

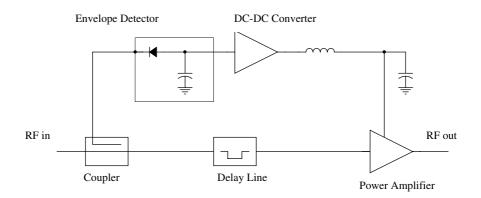

| 2.1  | Envelope elimination and restoration                         | 28 |

| 2.2  | Block diagram of Envelope tracking technique                 | 29 |

| 2.3  | Switched dynamic biasing technique                           | 30 |

| 2.4  | Block diagram of Chireix outphasing amplifier                | 32 |

| 2.5  | Efficiency of a class B power amplifier                      | 33 |

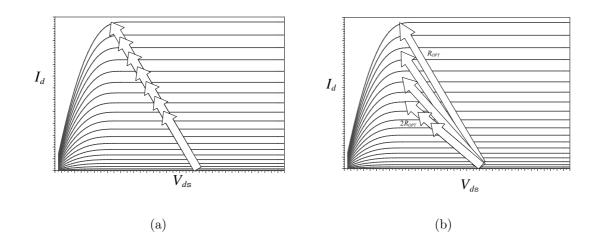

| 2.6  | Load line projection of (a) a class B power amplifier and (b) a Load                    |    |

|------|-----------------------------------------------------------------------------------------|----|

|      | modulated amplifier for constant efficiency $\ldots \ldots \ldots \ldots \ldots \ldots$ | 35 |

| 2.7  | Load modulation using an additional source                                              | 37 |

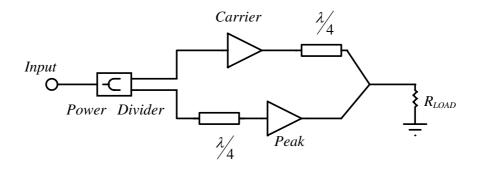

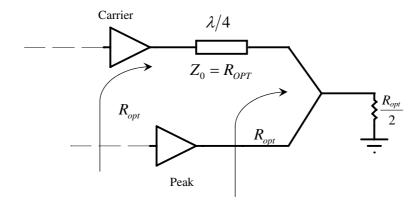

| 2.8  | Block diagram of a Doherty amplifier                                                    | 37 |

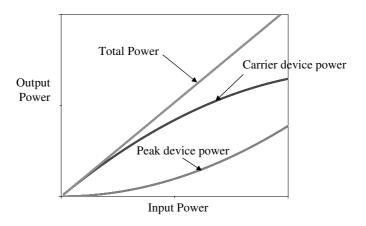

| 2.9  | Power characteristics of the carrier and peak amplifier                                 | 39 |

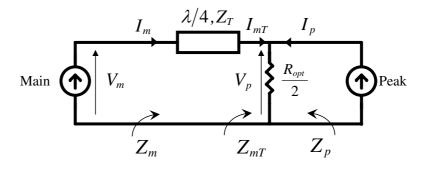

| 2.10 | Schematic diagram of a Doherty amplifier                                                | 39 |

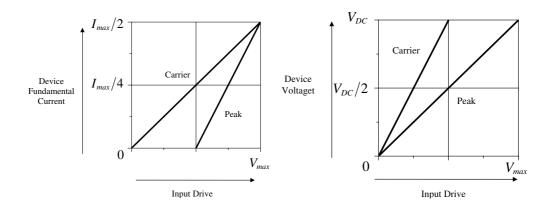

| 2.11 | Device currents and voltages versus input drive                                         | 40 |

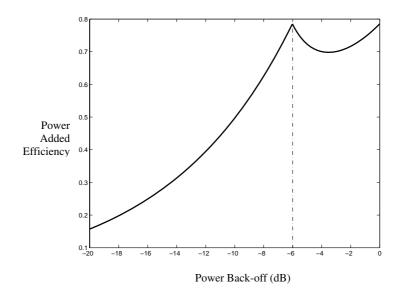

| 2.12 | Power added efficiency of a Doherty amplifier versus power backoff .                    | 45 |

| 2.13 | Doherty configuration below the break-point                                             | 46 |

| 2.14 | Doherty configuration above the break-point                                             | 46 |

| 2.15 | Load pulling effects on the carrier and peak amplifier $\ldots$                         | 47 |

| 2.16 | Efficiency of an assymetrical Doherty amplifier compared with a                         |    |

|      | conventional Doherty amplifier                                                          | 49 |

| 2.17 | Current and voltage characteristics of asymptrical Doherty amplifier                    | 49 |

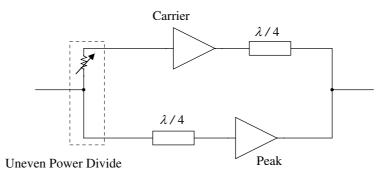

| 2.18 | Doherty amplifier with uneven power divide                                              | 50 |

| 2.19 | Doherty amplifier with offset lines                                                     | 51 |

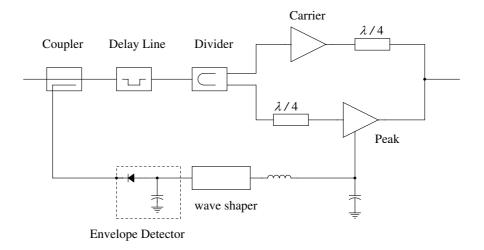

| 2.20 | Block diagram of a Doherty amplifier with bias adaptation $\ . \ . \ .$                 | 52 |

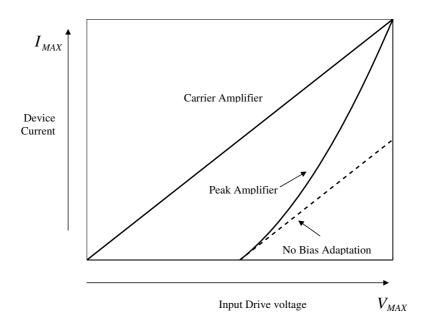

| 2.21 | Bias adaptation for peak amplifier                                                      | 53 |

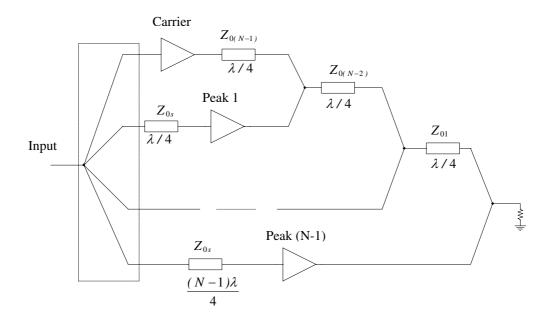

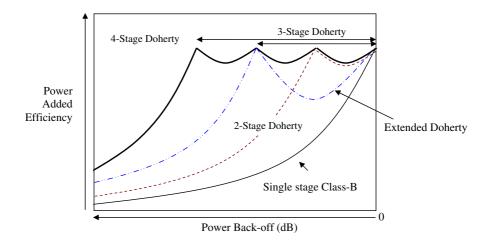

| 2.22 | Block diagram of N-way Doherty amplifier                                                | 54 |

| 2.23 | Efficiency of a multi-stage Doherty amplifier                                    | 54 |

|------|----------------------------------------------------------------------------------|----|

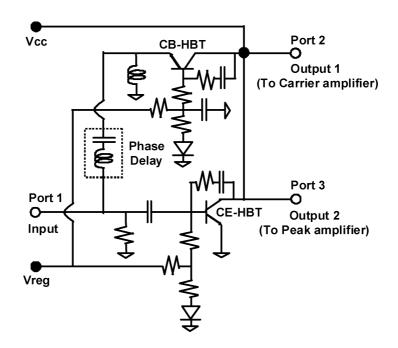

| 2.24 | Schematic of the active phase splitter proposed in $[1]$                         | 56 |

| 2.25 | Series-type Doherty amplifier                                                    | 56 |

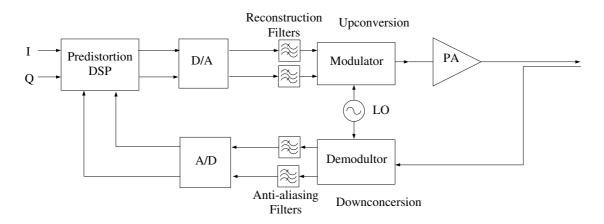

| 2.26 | Block diagram of a digital predistorter                                          | 57 |

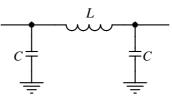

| 3.1  | Lumped-element realization of the transmission line                              | 59 |

| 3.2  | Bandwidth of a $\lambda/4\text{-transmission}$ line compared to its lump element |    |

|      | equivalent  .  .  .  .  .  .  .  .  .                                            | 61 |

| 3.3  | Effect of device parasitics on load modulation                                   | 63 |

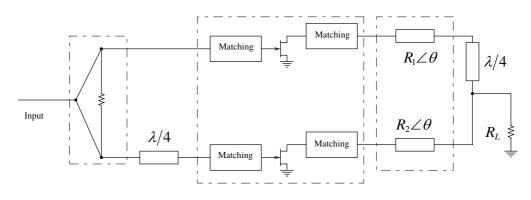

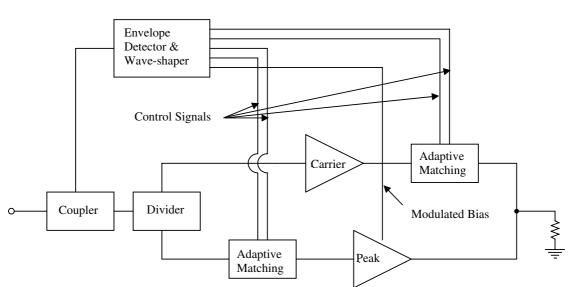

| 3.4  | Block diagram of proposed topology                                               | 65 |

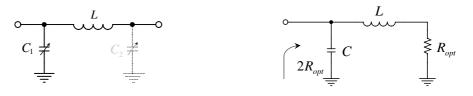

| 3.5  | Adaptive impedance transformation                                                | 66 |

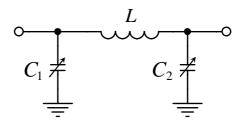

| 3.6  | Adaptive load modulation with variable capacitors, Case I $\ . \ . \ .$ .        | 67 |

| 3.7  | Adaptive load modulation with variable capacitors, Case II                       | 68 |

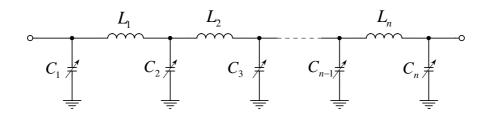

| 3.8  | Generalization of the topology for broadband performance $\ldots$ .              | 69 |

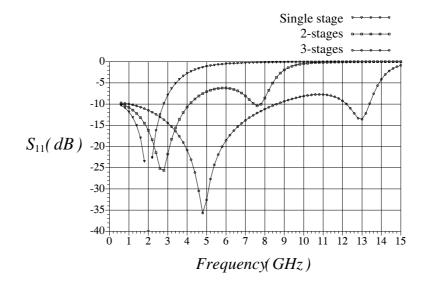

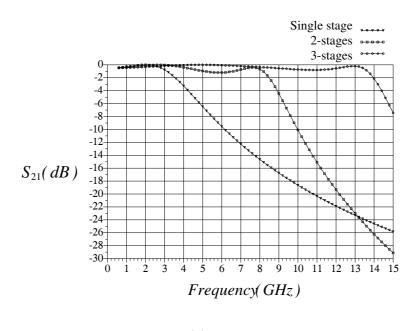

| 3.9  | Bandwidth of impedance transformers with different stages                        | 70 |

| 4.1  | TOM-2 model                                                                      | 73 |

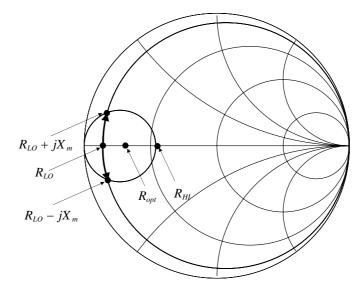

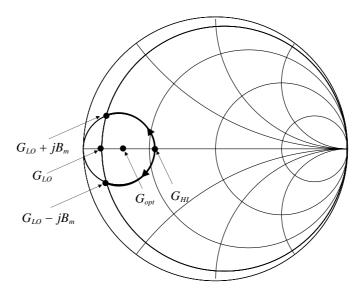

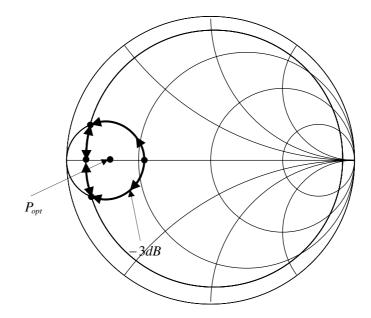

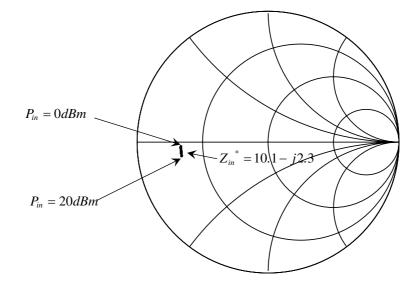

| 4.2  | Constant power contour for the load impedances with resistive part               |    |

|      | lower than $R_{opt}$                                                             | 82 |

| 4.3  | Constant power contour for the load impedances with resistive part               |    |

|      | higher than $R_{opt}$                                                            | 83 |

| 4.4                                                       | Theoretical load pull contour for $k = 2$                                                  | 84                   |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------|----------------------|

| 4.5                                                       | Varactor diode in shunt configuration                                                      | 86                   |

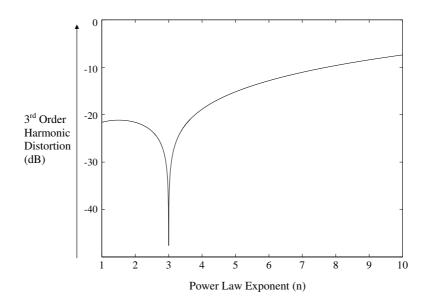

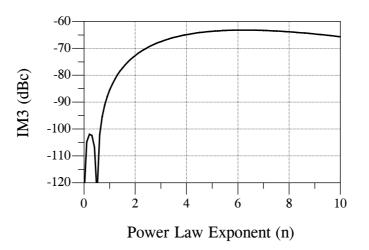

| 4.6                                                       | IM3 plot of a shunt varactor diode versus power law $\operatorname{exponent}(n)$           | 87                   |

| 4.7                                                       | Series Varactor Resonator                                                                  | 88                   |

| 4.8                                                       | Anti-parallel Configuration                                                                | 89                   |

| 4.9                                                       | Anti-series Configuration                                                                  | 90                   |

| 4.10                                                      | IM3 plot of two varactor diodes in anti-series connection for typical                      |                      |

|                                                           | parameters versus power law $\operatorname{exponent}(n)$                                   | 92                   |

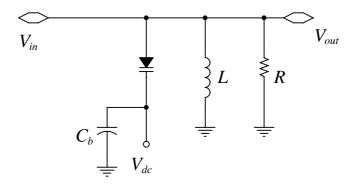

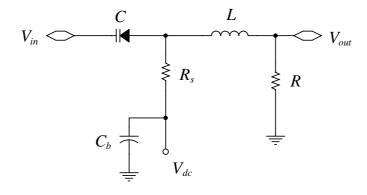

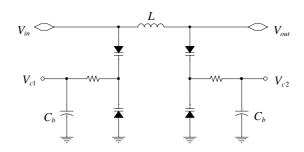

| 4.11                                                      | The single-stage proposed adaptive impedance transformer                                   | 93                   |

|                                                           |                                                                                            |                      |

| 4.12                                                      | Deployment of the proposed impedance transformation scheme in a                            |                      |

| 4.12                                                      | Deployment of the proposed impedance transformation scheme in a<br>Doherty power amplifier | 94                   |

| <ul><li>4.12</li><li>5.1</li></ul>                        |                                                                                            | 94<br>97             |

|                                                           | Doherty power amplifier                                                                    | 97                   |

| 5.1                                                       | Doherty power amplifier                                                                    | 97                   |

| 5.1<br>5.2                                                | Doherty power amplifier                                                                    | 97<br>97<br>98       |

| 5.1<br>5.2<br>5.3                                         | Doherty power amplifier                                                                    | 97<br>97<br>98       |

| <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>5.4</li></ul> | Doherty power amplifier                                                                    | 97<br>97<br>98<br>99 |

| 5.7  | Simulated and measured source pull contours with 0.5 dB steps for              |

|------|--------------------------------------------------------------------------------|

|      | maximum output power in class AB mode of operation 101                         |

| 5.8  | Variation of the transistors input impedance with input power level 102        |

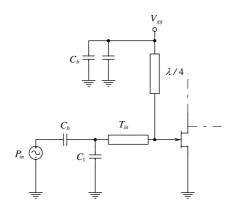

| 5.9  | Input matching network for class AB design                                     |

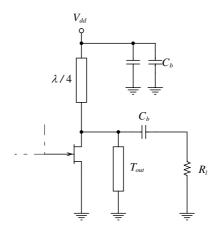

| 5.10 | Output matching network for class AB design                                    |

| 5.11 | Schematic diagram of the class AB design                                       |

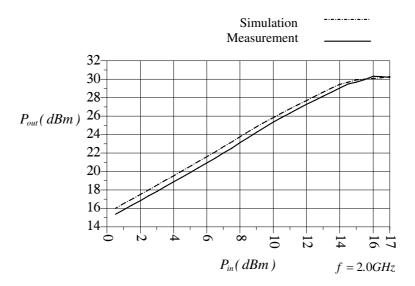

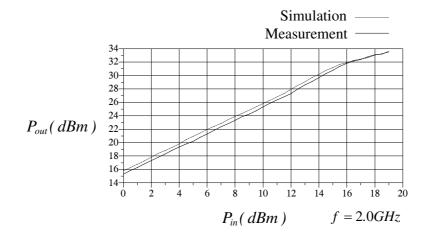

| 5.12 | Simulated and measured output power of the class AB power am-                  |

|      | plifier design                                                                 |

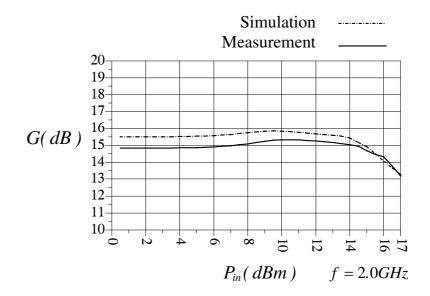

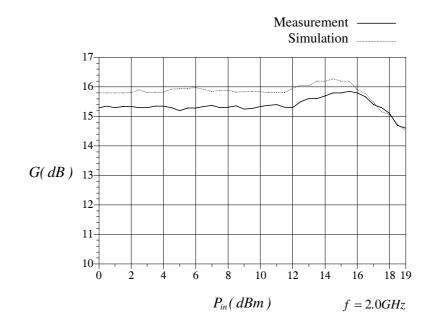

| 5.13 | Simulated and measured gain of the class AB design 106                         |

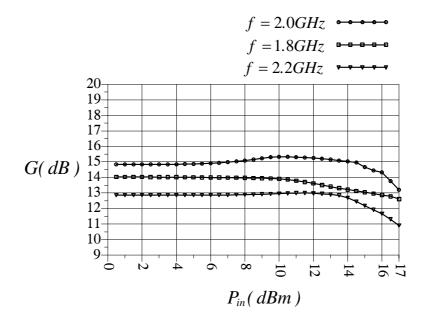

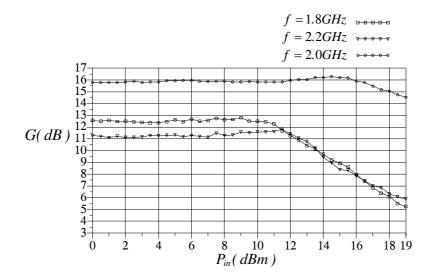

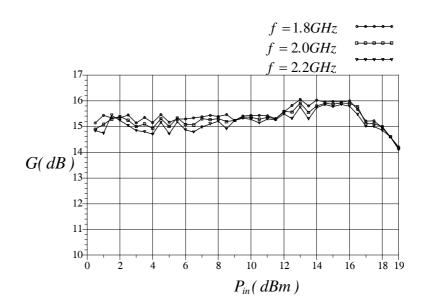

| 5.14 | Gain performance of the class AB design at different frequencies $106$         |

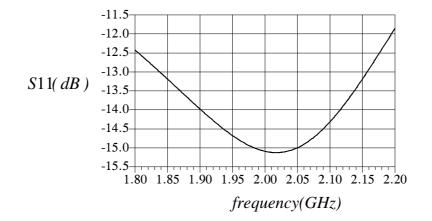

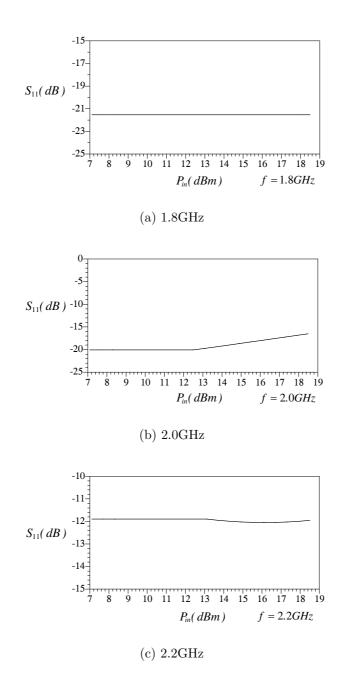

| 5.15 | Input return loss of the class AB design at maximum power level $107$          |

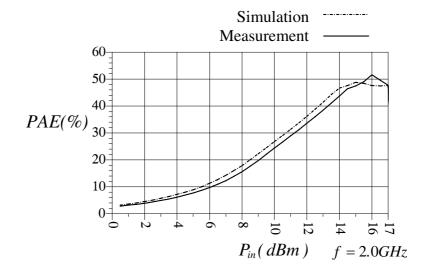

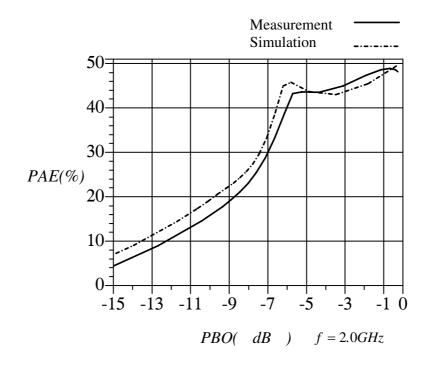

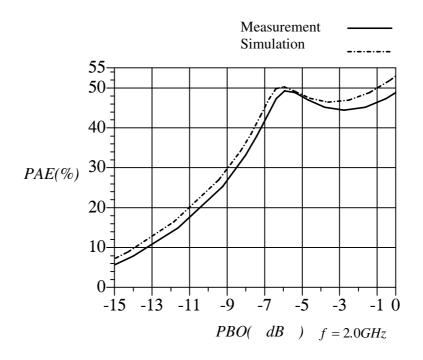

| 5.16 | Simulated and measured PAE of the class AB amplifier 107                       |

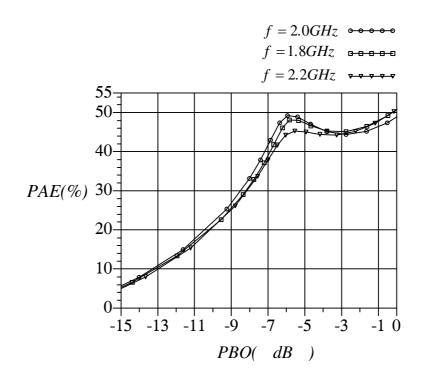

| 5.17 | Measured PAE of the class AB design at different frequencies 108 $$            |

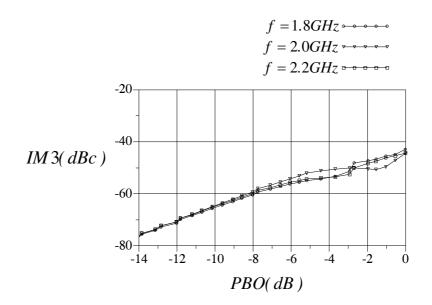

| 5.18 | Simulated and measured third order distortion of the class AB design<br>109 $$ |

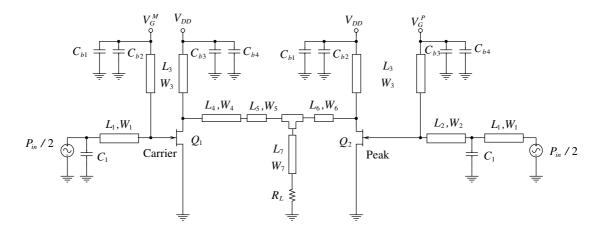

| 5.19 | Schematic diagram of the designed conventional Doherty amplifier . $109$       |

| 5.20 | Peak amplifier's gate voltage profile versus input power level for             |

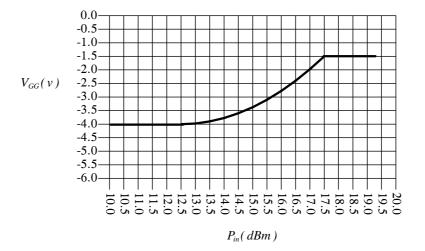

|      | optimum Doherty effect                                                         |

| 5.21 | Simulated and measured output power of the conventional Doherty                |

|      | amplifier                                                                      |

| 5.22 | Simulated and measured gain of the designed conventional Doherty            |

|------|-----------------------------------------------------------------------------|

|      | amplifier                                                                   |

| 5.23 | Comparison of gain performance of the conventional Doherty am-              |

|      | plifier at different frequencies                                            |

| 5.24 | Simulated and Measured PAE of the conventional Doherty amplifier 113        |

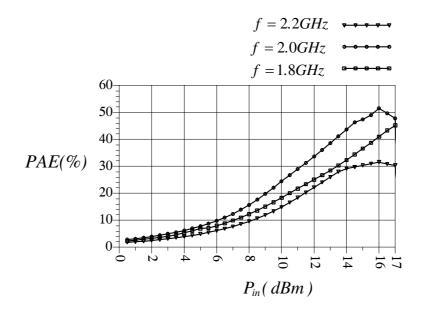

| 5.25 | PAE of the conventional Doherty amplifier design at several frequencies 113 |

| 5.26 | Comparison of third order harmonic distortion of the designed con-          |

|      | ventional Doherty amplifier measured at three frequencies 114               |

| 5.27 | Impedance transformation coverage of the varactor-based impedance           |

|      | inverter with swept control voltages                                        |

| 5.28 | Measured third order intermodulation distortion of the varactor-            |

|      | based impedance inverter                                                    |

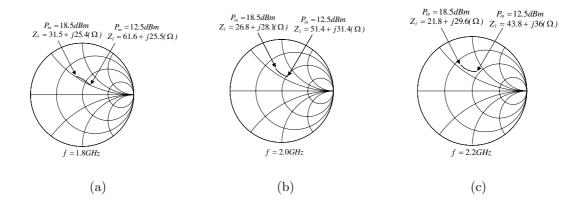

| 5.29 | Simulated impedance transformation trajectory at the output of the          |

|      | carrier amplifier in three design frequencies                               |

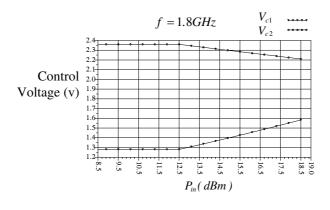

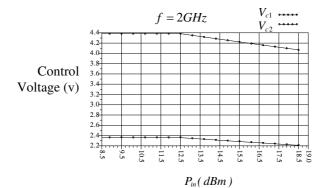

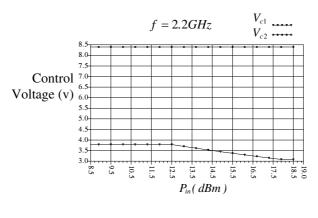

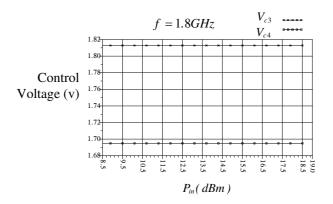

| 5.30 | Control voltages of the adaptive inverter versus input power $\ldots$ 118   |

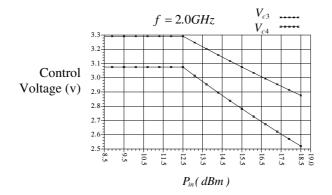

| 5.31 | Control voltages of the phase compensator versus input power $\ldots$ 119   |

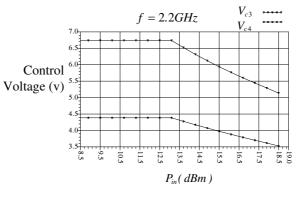

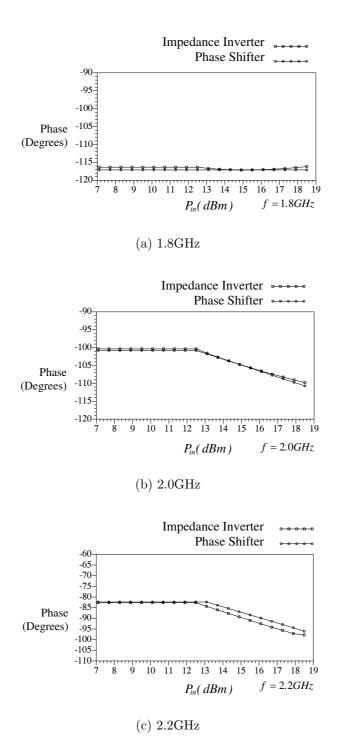

| 5.32 | Measured phase delay of the adaptive inverter and the phase com-            |

|      | pensator                                                                    |

| 5.33 | Matching performance of the phase compensator within the entire             |

|      | input power range                                                           |

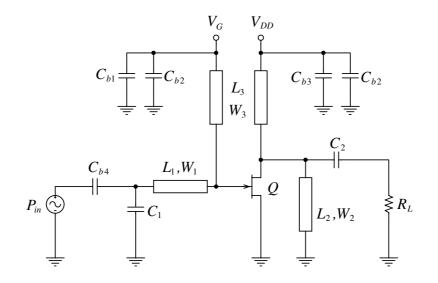

| 5.34 | Complete design schematic of the proposed Doherty power amplifier   | 123 |

|------|---------------------------------------------------------------------|-----|

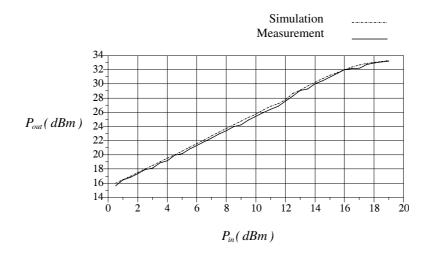

| 5.35 | Output power of the proposed Doherty amplifier                      | 124 |

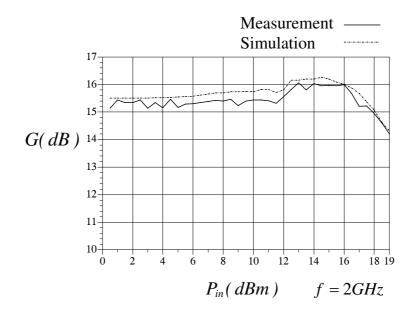

| 5.36 | Gain of the proposed Doherty amplifier                              | 124 |

| 5.37 | Measured gain of the novel Doherty amplifier compared at different  |     |

|      | frequencies                                                         | 125 |

| 5.38 | Power added Efficiency of the proposed configuration                | 125 |

| 5.39 | Comparison of measured PAE performance of the proposed design       |     |

|      | at different frequencies                                            | 126 |

| 5.40 | Third order harmonic distortion of the novel Doherty amplifier mea- |     |

|      | sured at 1.8GHz, 2GHz and 2.2GHz                                    | 127 |

| 5.41 | Comparison of PAE performance for class AB, conventional Doherty    |     |

|      | and proposed Doherty amplifiers over the bandwidth $\ldots$         | 129 |

| 5.42 | Comparison of linearity performance for the class AB, conventional  |     |

|      | Doherty and proposed Doherty amplifier                              | 130 |

| 5.43 | Layout Sizes of (a) conventional Doherty amplifier and (b) proposed |     |

|      | Doherty amplifier                                                   | 130 |

| 6.1  | Block diagram of a multi-stage Doherty amplifier with multi-stage   |     |

|      | adaptive impedance transformer                                      | 134 |

## List of Symbols

| A(t)                   | Time-dependent amplitude                     |

|------------------------|----------------------------------------------|

| C                      | Capacitance                                  |

| f                      | Frequency                                    |

| G                      | Gain                                         |

| $I_{dc}$               | DC current                                   |

| $I_1$                  | Fundamental current component                |

| $I_Q$                  | Quiescent current                            |

| $IM_3$                 | Third order harmonic distortion              |

| L                      | Inductance                                   |

| $M_0, M_1, M_2 \ldots$ | Nonlinear capacitance expansion coefficients |

| $N_0, N_1, \ldots$     | Nonlinear capacitance expansion coefficients |

| n                | Power law exponent                         |

|------------------|--------------------------------------------|

| $P_{RF}$         | RF power                                   |

| $P_{dc}$         | DC power                                   |

| $P_{in}$         | Input power                                |

| $P_{opt}$        | Optimum power                              |

| PBO              | Power backoff                              |

| PAE              | Power Added Efficiency                     |

| $P_{dcc}$        | DC power consumption of the carrier device |

| $P_{dcp}$        | DC power consumption of the peak device    |

| $R_L$            | Load resistance                            |

| $R_{opt}$        | Optimum resistance                         |

| t                | Time                                       |

| $V_Q$            | Quiescent voltage                          |

| $V_t$            | Threshold voltage                          |

| $V_i$            | Input voltage                              |

| $V_{dd}$         | Supply voltage                             |

| $V_{SW}$         | Switch Voltage                             |

| $V_{dc}$         | DC voltage                                 |

| $V_{c1}, V_{c2}$ | Control voltages of the impedance inverter |

| $V_{c3}, V_{c4}$ | Control voltages of the phase compensator  |

| υ                | AC voltage                                 |

| $V_{GG}$        | Gate bias voltage                          |

|-----------------|--------------------------------------------|

| $Z_m$           | Impedance seen by the main(carrier) device |

| $Z_p$           | Impedance seen by the peak device          |

| $Z_0$           | Characteristic impedance                   |

| $Z_s$           | Source impedance                           |

| $Z_l$           | Load impedance                             |

| $\Gamma_{load}$ | Load reflection coefficient                |

| $\Gamma_{out}$  | Output reflection coefficient              |

| η               | Efficiency                                 |

| ω               | Angular frequency                          |

| $\lambda$       | Wavelength                                 |

| $\phi(t)$       | Time-dependent phase                       |

| ζ               | Input drive level coefficient              |

| $\phi$          | Built-in potential                         |

Chapter 1

### Introduction

The wireless communication industry is pushing the next generation technology for higher data rates and broadband multimedia communications. Spectrum is costly so complex modulation schemes are required to transmit maximum amount of data with minimum spectrum occupation, which will result in complex signal waveforms.

Variable envelope signals with high peak-to-average ratios have to be linearly amplified and transmitted. This makes the power amplification block, the bottleneck of the entire transceiver system. Although acceptable linearity can be obtained from power amplifiers, it is almost always achieved at the expense of reduced efficiency. With the industry's demand for lower power consumption at base stations and smaller battery sizes and longer battery lifetime in hand held devices, tougher challenges are imposed on power amplifiers which are seemingly being urged to satisfy contradictory requirements. Another problem with amplifying a variable envelope signal is that the power amplifier will be forced to operate at backed off power region for most of its "on" time. This is specially a problem for conventional power amplifiers which basically deliver their maximum efficiency only at a single power level near saturation. In the recent years, linearity issues have been somehow alleviated by linearization techniques such as digital predistortion, but achieving acceptable power added efficiency and maintaining it over the entire power level range remains to be a problem with no widely accepted solution.

Before moving to the motives of this research, we begin with a brief review of power amplifiers and their classifications followed by a review of power amplifier technologies. Subsequently, the focus of this work is detailed. Finally, this chapter will be concluded by outlining the organization of this dissertation.

#### **1.1** Power Amplifiers

#### 1.1.1 Conjugate Match and Load-line Match

For linear, small signal amplifiers, maximum power is delivered to the load when the load is conjugately matched to the output impedance of the amplifier, that is

$$\Gamma_{out} = \Gamma^*_{load}.\tag{1.1}$$

Figure 1.1: Optimum load resistance for maximum power delivery

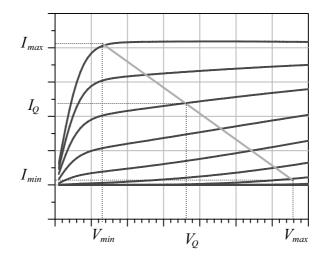

However, this is not the case with power amplifiers where nonlinearities result in gain compression. For this reason, in large signal amplifiers, there is an optimum load  $R_{opt}$  for maximum power delivery, which is typically found by a method called load pull. An estimate of the optimum impedance  $R_{opt}$  can be made by adjusting the load so that the transistor current and voltage is maximized, as shown in Figure 1.1, with the reactive part of the output impedance resonated out.  $R_{opt}$  can be determined as

$$R_{opt} = \frac{V_{max} - V_{min}}{I_{max} - I_{min}},\tag{1.2}$$

where  $V_{min}$  is the knee voltage,  $V_{max}$  is the maximum device voltage limited by breakdown voltage,  $I_{min}$  is the minimum drain conduction current and  $I_{max}$  is the maximum conduction current that the device can tolerate.

#### 1.1.2 Output Efficiency and Power Added Efficiency

Since power amplifiers are classified in different categories based on efficiency, it is necessary to review the precise definition of efficiency in the power amplifier design. There are two typical definitions to characterize the efficiency of an RF power amplifiers [2], "Output Efficiency" and " Power Added Efficiency". Output efficiency is defined as the ratio of the RF output power  $P_{RF}$  to the dc power  $P_{dc}$ ,

$$\eta = \frac{P_{RF}}{P_{dc}}.\tag{1.3}$$

The above definition does not take into account the input power,  $P_{in}$ , and power gain G, whose effects are significant in RF power amplifiers specially when gain drops below 10 dB. This mandates the definition of the Power Added Efficiency (PAE),

$$PAE = \frac{P_{RF} - P_{in}}{P_{dc}} = \eta \left(1 - \frac{1}{G}\right). \tag{1.4}$$

#### **1.1.3** Power Amplifier Classification

Based on their maximum possible efficiencies, RF power amplifiers are classified as class A, AB, B, C, D, E, F and S. In Class A, AB, B and C, the transistor is considered as a transconductive device. The classification as A, AB, B, or C describes the fraction of the full cycle, for which, current is flowing in the device. Such a fraction can be described as a conduction angle, which is the number of degrees (out of 360) for which current is flowing. If current is always flowing, the conduction angle is 360. As for Class D, E, F and S, the device acts like a switch. In order to provide a background for the motivations of this research, it is essential to briefly review the power amplifier classifications at this point.

#### 1.1.3.1 Class A

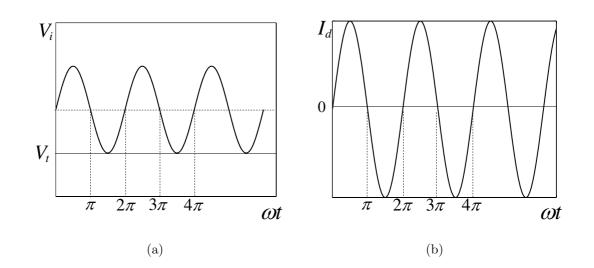

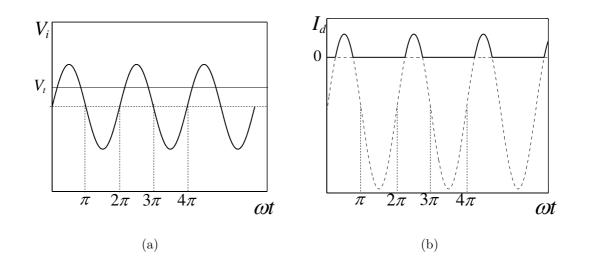

Class A amplifiers are biased such that the variations in input signal occur within the limits of cutoff and saturation. The input instantaneous voltage,  $V_i$ , is always higher than the threshold voltage,  $V_t$ , so the drain(collector) current,  $I_d$ , flows during the complete cycle (360 degrees) of the input signal as shown in Figure 1.2. The center of the active region is set as the bias point. Class A operation provides the maximum linearity among all classes of operation since no clipping occurs under ideal circumstances. This, of course, comes at the price of reduced efficiency. Theoretical maximum efficiency of Class A amplifier is 50%.

#### 1.1.3.2 Class B

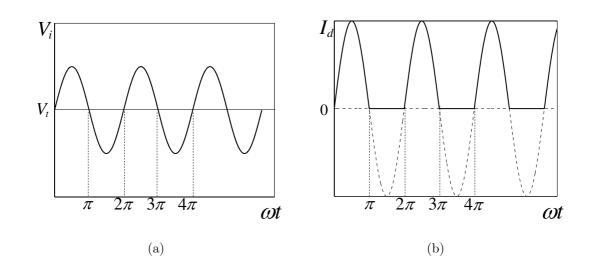

The conduction angle of the class B amplifier operation is 180 degrees, or one half the input cycle as seen in Figure 1.3. The DC bias point is selected so that no current flows in the device when there is no RF input. This is achieved by biasing the transistor at its threshold voltage,  $V_t$ . Maximum theoretical efficiency of class

Figure 1.2: Class-A mode

B mode is 78.5%. Although this class of operation can achieve greater efficiencies than class A, linearity is compromised since the current waveform is significantly distorted. In low frequency applications, this problem is solved by realizing the class B mode of operation, in a push-pull topology as shown in Figure 1.4. In a push-pull configuration, each transistor conducts only for half of a period cycle. The two half-sine waveforms generated by the transistors, are combined to give the complete output waveform as shown in Figure 1.5. At RF frequencies, the pushpull arrangement is not viable due to difficulties in realizing the transformers. A harmonic short, realize by a parellel LC is usually employed at RF frequencies to filter out the harmonic components of the output signal and extract the fundamental component. The structure of the harmonic short will be more elaborated in the next sections where class F mode of operation is discussed. The schematic

Figure 1.3: Class-B mode

diagram of a class B RF power amplifier is shown in Figure 1.6.

Figure 1.4: Push-pull class B amplifier with power combiner

#### 1.1.3.3 Class AB

The operating point of the class AB operation is somewhere between class A and class B. The collector current flows for more than 180 degrees but less than 360 degrees of the RF input signal as seen in Figure 1.7. The linearity of a class AB

Figure 1.5: (a) and (b): Currents of the individual transistors and (c): Combined current waveform

Figure 1.6: Schematic diagram of a class-B Power Amplifier

Figure 1.7: Class-AB mode

power amplifier is closer to Class A operation and its efficiency closer to class B operation. This enables the selection of operating point of the class AB amplifier based on whether linearity or efficiency is the dominant requirement. Similar to class B mode of operation, a harmonic short is required to extract the fundamental component. Efficiency of Class AB amplifiers vary from 50% to 78.5%, depending on the bias point.

#### 1.1.3.4 Class C

In class C mode of operation, drain current flows for less than one-half cycle of the input signal. The class C operation is achieved by setting the dc operating point below cutoff. Conduction is allowed only on the portion of the input signal that overcomes the reverse bias of the source gate junction as seen in Figure 1.8.

Figure 1.8: Class-C mode

Although class C amplifiers are severely nonlinear, they provide highest efficiency among the four classes of amplifier operations discussed. Theoretical maximum efficiency of a class C amplifier is 100%.

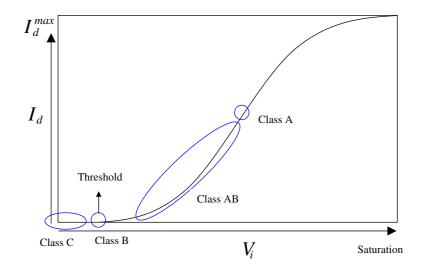

Different classes of operation based on the device transfer characteristics are summarized in Figure 1.9.

#### Switch-mode Amplifiers

In switch mode amplifiers, the active device departs from its function as a transconductive element and behaves as a switch. This results in minimum overlap of drain (collector) voltage and current waveforms, which maximizes the efficiency. Class D, E, F and S amplifiers are defined in this course of device behavior. Switch-mode

Figure 1.9: Power amplifier classes categorized based on the quiescent current amplifiers are unquestionably nonlinear which means that information in the envelope of the input signal will be heavily distorted. This makes the switch-mode amplifiers suitable for constant-envelope signals.

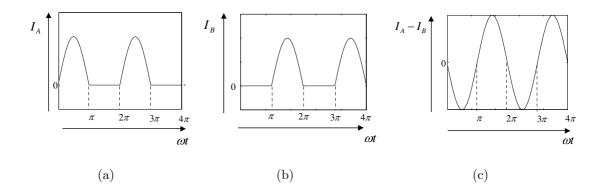

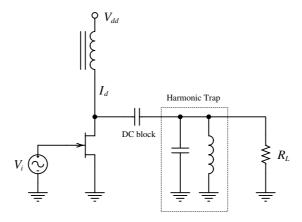

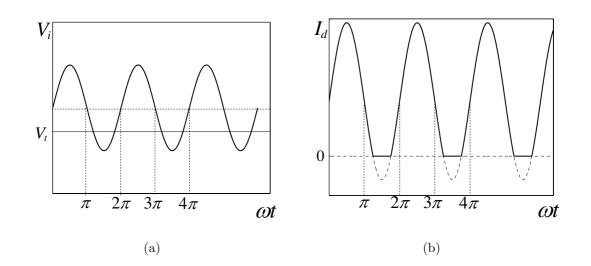

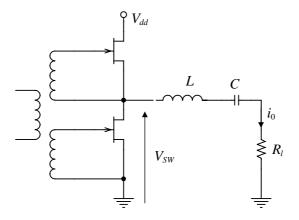

#### 1.1.3.5 Class D

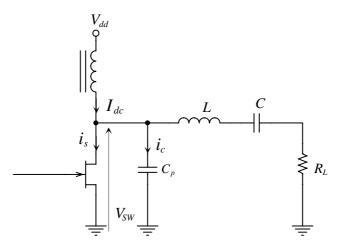

Class D amplifiers have been overshadowed by class E amplifiers which are discussed in next section. This is because class E amplifiers outperform class D amplifiers and offer more attractions. Figure 1.10 shows a class D amplifier schematic diagram. It is made up of a two way switch, which is usually implemented using two transistors. A series resonator is employed at the output. The resonator is switched between a bypassed dc voltage and ground for alternate half cycles. Current and voltage waveforms of the class D power amplifiers are shown in Figure 1.11. Assuming that the transistors are ideal, the Q factor of the resonator is high and the repetition cycle matches the resonant frequency of the LCR circuit, theoretical maximum efficiency is 100%. In practice, though, the switches pose problems at high frequencies in terms of parasitic reactances and driver requirements. This limits the application of Class-D amplifiers to low frequencies [2].

Figure 1.10: Schematic diagram of a class D power amplifier

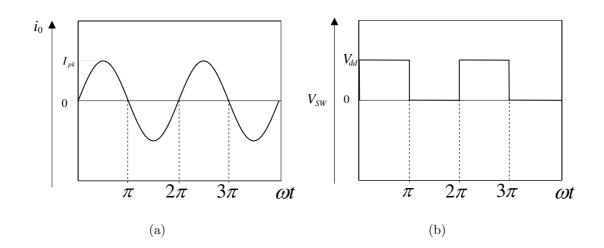

#### 1.1.3.6 Class E

Unlike other switch mode classes, the class E power amplifier promises potential possibilities of implementation at high frequencies. This is mostly due to the fact that, the class E amplifier can successfully achieve very high efficiencies in the presence of parasitics without requiring a nearly ideal switch. A schematic diagram of a class E amplifier is shown in Figure 1.12. The shunt capacitor at the output of the switch is a key component. A series resonator follows this arrangement [3]. The idea behind class E mode of operation is that when the switch is open, the

Figure 1.11: Class D current and voltage waveforms

entire switch current will pass through the capacitor and the current will only pass through the switch when the collector (drain) voltage is zero and hence, there is no power loss in the switch. The voltage and current waveforms are depicted in Figure 1.13. It is important to note that, the component values and the switch frequency is chosen so that the switch will turn on at the exact moment that the capacitor current reaches zero. As seen in Figure 1.13, the high peak voltage of the shunt capacitor is a disadvantage of class E amplifiers [2].

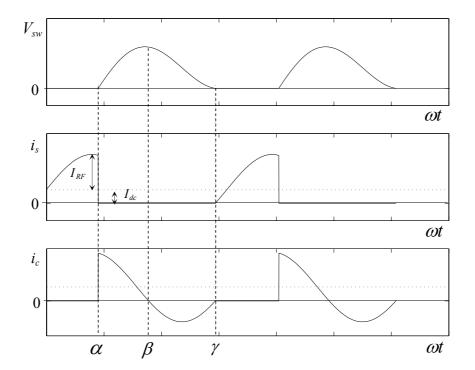

#### 1.1.3.7 Class F

The idea behind a class F amplifier is to simply add third order harmonics to the output voltage fundamental component to make it look more like a square-wave signal. This implies that the drain (collector) voltage is lower while current is flowing, but higher while current is not flowing, and hence the increase in efficiency.

Figure 1.12: Schematic diagram of a class E power amplifier

Figure 1.13: Voltage and current waveforms of a class E power amplifier

It has been derived in detail in [2] that this arrangement could maximize the efficiency. A class-F amplifier is shown in Figure 1.14. It is pretty much like a class B amplifier except that, instead of using a resonator at the output to extract the fundamental, a  $\lambda/4$ -transmission line has been employed to trap even order harmonics while letting in the odd order ones to square the sine wave.

Figure 1.14: Schematic diagram of a class F amplifier

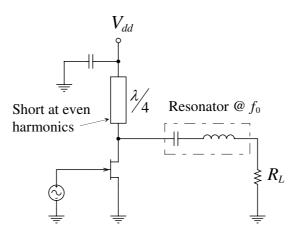

#### 1.1.3.8 Class S

In class S amplifiers, the input signal is converted to a constant envelope signal using a pulse-width-modulator. The information in the envelope of the signal is transferred to the duty-cycle of an oscillating reference. This is subsequently applied to an inverter-like limiter which amplifies the pulse-width modulated signal. The amplified original signal is then retrieved using a bandpass filter. Theoretically, high linearity and efficiency are achieved but, in practice, problems arise since a broad bandwidth is required for the device to amplify pulse shaped signals [3]. The need for a clock signal with frequencies much higher than the input signal is another challenge since high performance material/technology would be essential.

Figure 1.15: Schematic diagram of a class S amplifier

## **1.2 RF Power Amplifier Technologies**

Several technologies are available for RF power amplifiers. Common benchmarks for a comparative study of the available technologies are efficiency, linearity, power gain, thermal conductivity, size, cost, integration level, breakdown voltage and cutoff frequency. The typical values of these parameters for some of the most common RF power amplifier technologies are summarized in Table 1.1 [4]. A brief description of each technology follows.

| Technology                    | GaAs HBT | Si BJT                            | SiGe HBT          | CMOS      | LDMOS    |

|-------------------------------|----------|-----------------------------------|-------------------|-----------|----------|

| $f_T(GHz)$                    | 46       | $27(\text{HF})^1 22(\text{HV})^2$ | 44 (HF) 25 (HV)   | > 20      | > 20     |

| 0 - ( )                       | -        |                                   |                   | > 20      |          |

| $BV_{ceo}(V)$                 | 14.3     | 3.3 (HF) 6.2 (HV)                 | 3.0 (HF) 6.0 (HV) | 5         | 15       |

| Thermal Conductivity (W/cm-C) | 0.49     | 1.5                               | 1.5               | 1.5       | 1.5      |

| Normalized Cost 1mm2          | 1        | 0.3                               | 0.3               | < 0.2     | 0.3      |

| Wafer Size                    | 6" wafer | 8" wafer                          | 8" wafer          | 12" wafer | 8" wafer |

| PAE                           | >40%     | > 30%                             | > 30%             | >30%      | > 35%    |

| Linearity                     | great    | good                              | good              | good      | good     |

| Power Gain                    | great    | good                              | great             | poor      | poor     |

| Integration Level             | poor     | good                              | good              | great     | good     |

Table 1.1: Common technologies for RF power amplifiers

### **1.2.1** Si-BJT and CMOS Power amplifiers

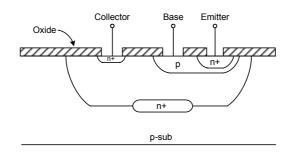

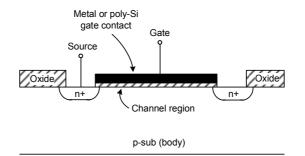

Since the entire digital communication world is dominated by Si-based devices, it is natural that the attention of the designers have turned to realization of RF circuits in Si-based technologies. The possibility of integration of the entire system in a single chip has been very appealing although, obviously, this will cause numerous problems such as cross-coupling and noise. Si-based devices such as Si-BJT and CMOS enjoy high thermal conductivity and good 1/f noise as well as low cost. However, they suffer from poor linearity and high substrate loss. Presence of parasitics limits very high frequency applications as well. For power amplifier applications, high power levels can not be achieved with CMOS due to the low breakdown voltage. CMOS power amplifiers are also larger than their SiGe or GaAs counterparts for the same functionality. This is because CMOS devices, unlike GaAs or SiGe HBT technology which incorporate vertical transistors, become rapidly larger when scaled up to accommodate high output powers. The cross sections of an Si-BJT transistor and an NMOS transistor are shown in Figure 1.16 and Figure 1.17 respectively.

Figure 1.16: Si BJT cross-sectional structure

Figure 1.17: NMOS cross-sectional structure

### 1.2.2 LDMOS

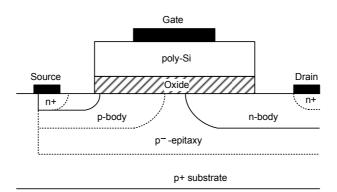

The laterally diffused MOSFET (LDMOS) is a suitable choice for high power applications which can be realized in standard CMOS process. High breakdown voltage is achieved by using high resistivity Silicon. High bias voltage of LDMOS devices makes them suitable for base-station applications rather than hand-held ones. Unlike HEMTs that require a negative bias for the gate, LDMOS requires a single polarity supply since it is an enhancement mode FET. Major disadvantages of LDMOS are poor linearity and lower efficiency compared to GaAs HEMT and GaAs HBT. Silicon LDMOS has dominated the market of devices in the GSM and WCDMA base-stations, primarily because of low cost and acceptable performance [5]. As shown in the cross-sectional structure in Figure 1.18, LDMOS consists of a p-doped layer of silicon underneath the n-type channel to isolate it from ground. The source is grounded using p+ sinkers that run vertically from the source contact at the surface through to the bottom of the substrate.

Figure 1.18: LDMOS cross-sectional structure

### 1.2.3 GaAs HBT

The HBT<sup>3</sup> can provide faster switching speeds than silicon bipolar transistors mainly because of reduced base resistance and collector-to-substrate capacitance. Since GaAs has a poorer thermal conductivity compared to silicon, its thermal effects are higher than BJTs. The HBT has also higher current gain and power

<sup>&</sup>lt;sup>3</sup>Heterojunction Bipolar Transistor

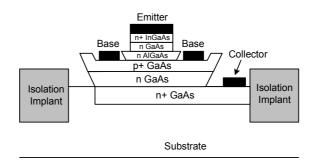

density. The base region in the HBT can be made thinner and more heavily doped than in a normal BJT, decreasing the electron transit time and base capacitance, without increasing the base resistance [5] and hence, the high-frequency performance. However, HBTs suffer from high cost and low integration level. As shown in the cross-section shown in Figure 1.19, GaAs HBTs are fabricated using p-type GaAs in the base sandwiched between n-type GaAs in the collector and a layer of n-type AlGaAs in the emitter. The ohmic contacts to the emitter and collector are formed with heavily doped n-type GaAs.

Figure 1.19: GaAs HBT cross-sectional structure

### 1.2.4 SiGe HBT

In order for better integration with Si-based devices, HBTs have also been fabricated using SiGe instead of AlGaAs in GaAs. Recent technologies have overcome the speed limitations of conventional silicon technologies. GaAs HBTs allow lower supply voltages due to a lower base-emitter turn-on voltage compared to GaAs HBTs. The possibility of using larger wafers, better strength and thermal conductivity are other advantages over GaAs. In SiGe, between 10% to 20% of the silicon atoms are replaced by germanium. This will create a built-in electric field that results in acceleration of the carriers across the base due to reduction of the base transit time. Therefore, the  $f_T$  of the SiGe HBT is higher than a silicon BJT. The ultimate achievable power of SiGe devices is limited due to the low breakdown voltage of silicon technology. The cross-section of a SiGe HBT device is shown in Figure 1.20. The SiGe HBT uses a moderately doped p-type base of SiGe sandwiched between a lightly doped n-type collector and an n-type emitter, both of silicon. For power devices, a thick collector with light doping is frequently used to increase the base-collector breakdown voltage and also to improve linearity, even though the resulting current density (and output power) will still be smaller than for the GaAs HBTs [5].

Figure 1.20: SiGe HBT cross-sectional structure

#### 1.2.5 GaAs HEMT

The High Electron Mobility Transistor (HEMT) has a very similar structure to MESFET. The channel between the gate and the GaAs substrate is formed by an AlGaAs layer. HEMTs have also been fabricated using newer material structures, such as the pseudomorphic-HEMT (AlGaAs-InGaAs layers on GaAs), or the lattice-matched InP HEMT (AlInAs-GaInAs on an InP substrate) recently [5]. There is an important difference between HEMT and MESFET which results in higher gain and extended frequency performance in HEMTs. In MESFET devices, since the channel is doped, the ionized donors scatter the electrons. Therefore, the electron mobility is degraded due to high parasitic resistances. In HEMT devices, the channel and electron source are in different layers so there are no impurities in the channel. This results in a trapped layer of electrons (a two-dimensional "electron gas") having high saturated electron velocity under the compound semiconductor which explains HEMT's better performance compared to MESFETs. While HEMTs are inherently more efficient than HBTs, by properly tailoring the HEMT layers, increased linearity can also result. Although the current density is lower than HBTs, multiple heterojunctions can be created to increase the power. Figure 1.21 shows the cross-section of a GaAs pHEMT transistor. For realization of the present work, GaAs pHEMT devices have been used. TC2571 GaAs pHEMT transistors from Transcom company (Appendix A) have been employed to realize

the design. A photograph of the die of this transistor is shown in Figure 1.22.

Figure 1.21: GaAs pHEMT cross-sectional structure

Figure 1.22: Transcom's TC2571 Pseudomorphic-HEMT

# 1.3 Research Focus

One of the promising methods for efficiency enhancement in the backed-off power region is the Doherty power amplifier, named after W.H. Doherty. It was introduced in 1936 [6] and was used to enhance the efficiency of traveling wave tubes in the lower power regime. Due to its simple concept, ease of implementation, and promising potential for efficiency enhancement, it has recently gained a lot of attraction for applications in modern wireless systems such as WCDMA, OFDM, and WLAN, in which, variable envelope signals are involved. Although Doherty amplifiers can achieve significant efficiency enhancement in the backed-off region, they suffer major drawbacks. The Doherty amplifier has a narrow bandwidth, which is mainly because the Doherty amplifier employs a passive  $\lambda/4$ -transmission line as an impedance inverter for load modulation. The large size of the  $\lambda/4$ -impedance inverter in common wireless communication frequencies is another drawback which is the main obstacle for realizing a compact Doherty amplifier. As the main contribution of this research, a novel topology for the Doherty amplifier is proposed which tries to overcome the above mentioned problems by eliminating the  $\lambda/4$ impedance inverter and replacing it with a compact and broadband alternative. The proposed circuit has been designed, simulated and fabricated. As a result of this research, a provisional patent has been filed in the United States with the reference number of "No. 60/936,151"<sup>4</sup> on 18 June 2007. Publications regarding this work are pending to be submitted after protection issues are resolved.

# 1.4 Dissertation Organization

Chapter 2 revisits the most common efficiency enhancement techniques. A literature review is carried out. Advantages and disadvantages of different approaches are briefly explained. The Doherty amplifier is discussed next and different aspects

<sup>&</sup>lt;sup>4</sup>NUS ILO reference:OOI BL 01-US/PRV

and characteristics of the technique are detailed. The mechanism of efficiency enhancement in Doherty amplifiers through load modulation is comprehensively formulated. A review of major research works on Doherty amplifiers in recent years is also covered. Chapter 3 explains the drawbacks of the conventional approach in detail and a novel load modulation technique with the potential to overcome the mentioned problems is proposed. In chapter 4, the theoretical development of the proposed topology is presented. Detailed study of the models used for the devices, load pull theory and characteristics of the adaptive impedance transformation are covered. In chapter 5, the proposed circuit is challenged through simulations and measurements. Simulation results are compared with measured data from fabricated modules. Measured results from conventional approach and the proposed topology are compared. Chapter 6 concludes the dissertation with a discussion on the objectives achieved.

# The Doherty Power Amplifier

## 2.1 Efficiency Enhancement Techniques

There are two major problems with power amplifiers in modern communication systems. Firstly, power amplifiers generally deliver their maximum achievable efficiency at a single power level, which is somewhere near maximum output power. If the power is backed off from that single point, the efficiency will decrease. Since modern communication systems require amplification of a variable envelope signal with high peak-to-average ratios, power amplifiers are forced to work in the power back-off regime for most of their "on" time. The second problem is the difficulty in preserving the information carried in the envelope of the signals. Usually, the amplitude modulation information of signals will be heavily distorted especially near the maximum power level. "Efficiency enhancement techniques" have been available for many years [2]. They mainly deal with the first problem but they certainly affect the second problem as well since linearity and efficiency are closely interrelated. Some techniques can be used to improve either efficiency or linearity, focusing on one as the primary design target. This chapter discusses the techniques that mainly deal with improving the efficiency under variable envelope conditions.

# 2.1.1 Envelope Elimination and Restoration (Kahn Technique)

First demonstrated by Kahn in 1956 [7], Envelope Elimination and Restoration (EER) is a technique to provide high efficiency and linearity using a switch-mode amplifier and a linear low frequency modulator. EER technique is a more efficient alternative for conventional class AB amplification. A block diagram of the EER system is shown in Figure 2.1. The basic idea is that the input signal is passed though a limiter so that the possibility of AM-PM distortion is eliminated and the phase information is preserved. The signal is then amplified using a switch mode nonlinear amplifier. The envelope of the signal, on the other hand, is retrieved by passing a sample of the input signal through an envelope detector and amplifying it using a voltage supply modulator. This, in return, is used to modulate the output signal to result in an undistorted amplified signal with the original waveform. Since the switch mode amplifier could be considered as a voltage source, the output signal

amplitude could be linearly modulated with bias supply. In practice, the process of supply modulation of the power amplifier requires a significant amount of power. If this process could be carried out with 100% efficiency, the overall efficiency could be maintained over the entire envelope range. One potential problem with this technique is poor bandwidth. Highly efficient amplification of broadband envelope signals introduces a big challenge in EER systems.

Figure 2.1: Envelope elimination and restoration

### 2.1.2 Bias Adaptation (Envelope Tracking)

Bias Adaptation or Envelope Tracking (ET) technique [8] is in many ways similar to Envelope Elimination and Restoration (EER) technique. The difference is that the main power amplifier can be any conventional device and input drive contains both envelope and phase information (no limiter is used). The envelope tracking path decreases the DC bias voltage for the low power input signals and increases it

Figure 2.2: Block diagram of Envelope tracking technique

at the high power regime and hence the improvement in efficiency. Figure 2.2 shows the block diagram of the system. The envelope tracking technique appears to be more viable than the EER technique since there is no need to accurately replicate the signal envelope anymore. Practical implementations of ET technique [8],[9],[10] suffer from integration issues with the dc-to-dc converter and gain variation during the bias adaptation.

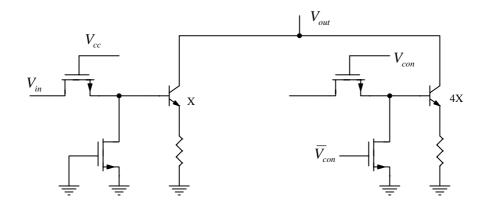

### 2.1.3 Switched Dynamic Biasing Technique

From the definition of power efficiency in section 1.4, it is obvious that an increase in efficiency can be achieved by reducing dc power consumption. This is typically carried out by reducing either the DC current (DCB) or DC bias voltage (DVB) or both. The problem with these approaches is that as the DC current is decreased dynamically as a means of maintaining high efficiency, the gain of the amplifier is reduced significantly. It is found that the gain variation in Envelope Tracking(ET)

Figure 2.3: Switched dynamic biasing technique

and Envelope Elimination and Restoration(EER) technique, are mainly due to the decrease in drain (collector) current density. In order to overcome this issue, switched dynamic biasing techniques have been proposed [11] to keep the current density constant as the input power level changes. Low-loss switches have been utilized to switch on/off a number of parallel transistors according to the input power level as shown in Figure 2.3. As the input power increases more transistors are switched on while the current density of all transistors remain constant and hence the constant gain. The drawback of this approach is the difficulty to realize high isolation when the switch is turned off and low insertion loss as the switch is turned on.

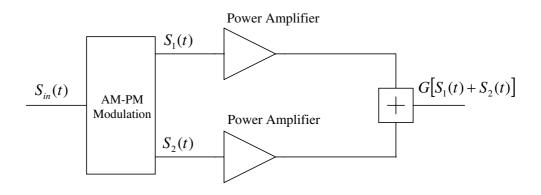

### 2.1.4 Chireix Outphasing Technique (LINC Amplifier)

LINC<sup>1</sup> Amplifier was introduced by Chireix in 1935 [12]. As illustrated in the block diagram in Figure 2.4, the idea of the Chireix Amplifier is to decompose a variable envelope signal

$$S_{in}(t) = A(t) \cdot \cos(\omega t + \phi(t)), \qquad (2.1)$$

into two outphased constant envelope signals

$$S_1(t) = \cos\left(\omega t + \phi(t) + \cos^{-1}(A(t))\right),$$

(2.2)

$$S_2(t) = \cos\left(\omega t + \phi(t) - \cos^{-1}(A(t))\right).$$

(2.3)

These two signals can then be combined together after being amplified separately using two highly efficient (and possibly nonlinear) amplifiers. The resulting output  $S_{out}(t)$ , will be

$$S_{out}(t) = G[S_1(t) + S_2(t)] = 2GA(t) \cdot \cos(\omega t + \phi(t)).$$

(2.4)

This is also known as out-phasing technique.

<sup>&</sup>lt;sup>1</sup>LInear amplification using Nonlinear Components

Figure 2.4: Block diagram of Chireix outphasing amplifier

## 2.2 The Doherty Technique

The Doherty Amplifier, first demonstrated in a classic paper by W. Doherty [6], primarily focuses on improving the efficiency in the backed-off region. As mentioned earlier, conventional power amplifiers are basically most efficient near the maximum output power. This degrades the average efficiency when a variable envelope signal with high peak-to-average ratio has to be amplified. Ideally, a constant maximum efficiency has to be maintained over the entire envelope range. The technique was originally applied to high power tube amplifiers but its simplicity and the novel idea behind it, has made it attractive, in recent years, for re-invention in solid-state applications.

### 2.2.1 Principles of Doherty Amplifier

In order to understand how the Doherty technique can improve the efficiency in backed-off power levels, we have to look into the nature of efficiency roll-off at lower power levels. This will help to understand how load modulation can lift-up the efficiency curve in backed-off power regime. Let's consider a conventional Class-B amplifier as was previously shown in Figure 1.6. The theoretical efficiency of a class B power amplifier is shown in Figure 2.5. The optimum load for load line

Figure 2.5: Efficiency of a class B power amplifier

match would be

$$R_{opt} = 2\frac{V_{dc}}{I_{max}}.$$

(2.5)

RF output power will be calculated as

$$P_{RF} = \frac{V_{dc}I_{max}}{4}.$$

(2.6)

DC power consumption is

$$P_{dc} = \frac{V_{dc}I_{max}}{\pi}.$$

(2.7)

Maximum efficiency is

$$\eta = \frac{\pi}{4} = 78.5\%. \tag{2.8}$$

Now if we decrease the input power by a factor of  $k^2$   $(k = \frac{v_i}{V_{max}})$ , the fundamental RF current component  $I_1$  would be

$$I_1 = \frac{I_{max}}{2k},\tag{2.9}$$

$\mathbf{SO}$

$$P_{RF} = \frac{1}{2}I_1^2 R_{opt} = \frac{V_{dc}I_{max}}{4k^2},$$

(2.10)

and

$$P_{dc} = I_{dc} V_{dc} = \frac{V_{dc} I_{max}}{k\pi}.$$

(2.11)

Efficiency will then become

$$\eta = \frac{P_{RF}}{P_{dc}} = \frac{\pi}{4k}.$$

(2.12)

This shows that the efficiency decreases by a factor of k if the input power is decreased by a factor of  $k^2$ . Looking carefully at equation 2.10, it can be seen that if the load could be adaptively increased (modulated) in proportion to k as the input power decreases in proportion to  $k^2$ , the efficiency would have remained constant regardless of input power level. This is the main idea behind the Doherty technique. In a nutshell, a Doherty amplifier employs load modulation to keep the

Figure 2.6: Load line projection of (a) a class B power amplifier and (b) a Load modulated amplifier for constant efficiency

efficiency at constant maximum over a range of power back-off. Equation 2.10 also implies that increasing the load impedance with decreasing input power will result in constant output rail-to-rail voltage over a range of input power levels. This is illustrated in Figure 2.6, where the dynamic load line of a load modulated power amplifier is compared with the one of a conventional Class-B. In fact the reason for increasing the load impedance is to allow the output voltage, a full rail-to-rail swing within a range of input power.

Obviously, it is a physical challenge to dynamically modify the load impedance as the input power changes [2]. The other immediate problem with this approach is that even if this challenge could somehow be overcome, the amplifier would be inherently nonlinear even if an ideal device is used because the output power will decrease in proportion to k instead of  $k^2$ . So the enhancement in efficiency would

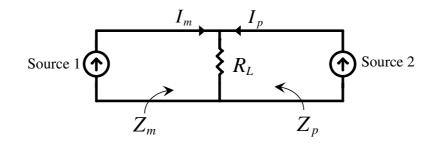

come at the price of a heavily distorted output waveform. In fact, both above mentioned problems, realizing the level-dependent impedance and the nonlinearity issue could be solved at the same time by Doherty's genius invention. Unlike the conventional power amplifier in which the RF load is considered a fixed, physically passive entity, Doherty amplifier employs a second, phase-coherent source to modify the load seen by the first. This configuration should not be mistaken with the Travelling wave amplifier despite the similarities in their structure. In a TWA multiple active devices are connected in series so that the parasitics of the gate port and the drain port build a transmission line network and thus they are cancelled out. Unlike the Doherty Power Amplifier all the transistors in a TWA are biased at the same point and the contribute equally to the output power while in a Doherty structure the Main and the Peak amplifier are biased differently and the contribute to the output power differently at different input power levels. Figure 2.7 shows two current generators driving a single load. If source 2 is set to give zero current, source 1 will see a load resistance of  $R_L$ . If both sources contribute in load current, the impedance seen by source 1 will be

$$Z_m = R_L \left( 1 + \frac{I_p}{I_m} \right). \tag{2.13}$$

Figure 2.7: Load modulation using an additional source

Figure 2.8: Block diagram of a Doherty amplifier

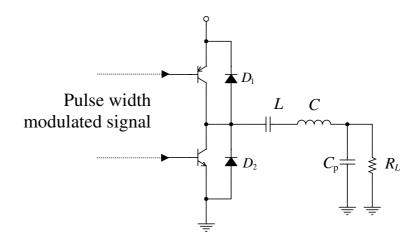

Similarly, source 2 would see an impedance of

$$Z_p = R_L \left( 1 + \frac{I_m}{I_p} \right). \tag{2.14}$$

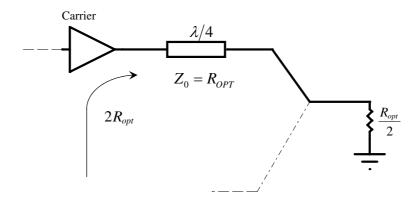

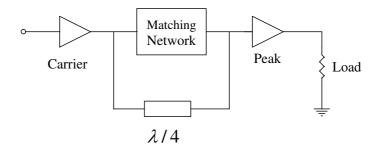

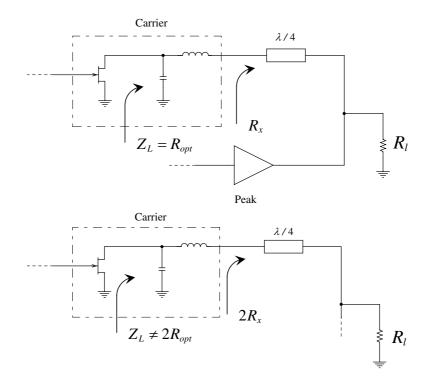

This shows that the impedance seen by either of generators can be pulled by changing the magnitude and phase of the other. In Doherty amplifiers, generators are considered to be the transconductances of possibly different transistors. For convenience, the transistors are termed "carrier" and "peak" devices [2]. Figure 2.8 shows a basic block diagram of a Doherty Amplifier. As the input drive is decreased, both transistors contribute to the load current until a certain threshold point, which is conventionally 6-dB lower than the maximum combined power. Below this point, the peak amplifier shuts down, leaving only the carrier amplifier active. In practical implementations, the carrier amplifier is operated in class AB or class B while the peak amplifier is biased at deep class C to facilitate its shutdown at a certain drive level. In fact, the Doherty technique makes use of the dis-similarities between the two elements to open up opportunities to improve the efficiency through active load pull. A  $\lambda/4$  impedance transformer is placed between the load and the carrier amplifier. This is a key element that acts like an impedance inverter. It makes the impedance seen by the carrier amplifier decrease while the peak amplifier current,  $I_p$ , increases. A second  $\lambda/4$  transmission line is placed before the peak amplifier to compensate for the 90 degree delay imposed by the first  $\lambda/4$  transmission line, placed after the carrier amplifier. This makes the output currents of the carrier and peak amplifier to combine in-phase. The  $\lambda/4$  transformer is narrow-band and bulky in common frequencies used for wireless communications. This is the main obstacle for realization of broadband and highly integrated Doherty amplifiers.

The second problem associated with the load modulation technique was the inherent nonlinearity as mentioned before. Looking at the Doherty configuration, the output power increases in proportion to the input power level in a "square root" fashion. Meanwhile, the peak amplifier gives a "three-half" power transfer characteristic due to the upward load-pull effect[2]. The combination of the two power

Figure 2.9: Power characteristics of the carrier and peak amplifier

Figure 2.10: Schematic diagram of a Doherty amplifier

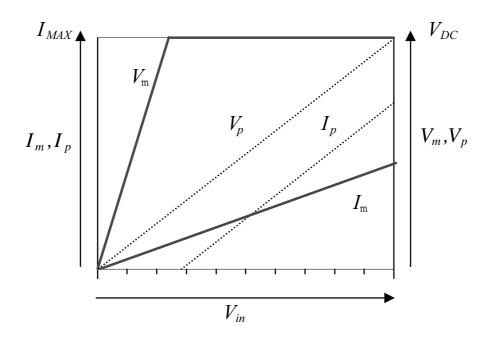

transfer characteristics results in an overall linear power response as shown in figure 2.9 while at the same time, efficiency has been kept at its maximum level above the 6-dB back-off point, up to the maximum power level. Figure 2.10 shows the schematic diagram of a Doherty amplifier and Figure 2.11 shows current/voltage relationships of the carrier and peak amplifiers. Above the 6-dB back-off point, both devices are contributing to the load current. Their fundamental currents would be

$$I_m = \frac{I_{max}}{4} (1 + \zeta),$$

(2.15)

Figure 2.11: Device currents and voltages versus input drive

and

$$I_p = \frac{I_{max}}{2}\zeta, \qquad (2.16)$$

where

$$0 \leq \zeta \leq 1$$

$\zeta = 0$  corresponds to the 6-dB back-off point and  $\zeta = 1$  corresponds to the maximum power level. It is assumed that both carrier and peak amplifier are identical and have the same  $I_{max}$ . Now, the load pulling relationships of equations 2.13 and 2.14 become

$$Z_{mT} = \frac{R_{opt}}{2} \left( 1 + \frac{I_p}{I_{mT}} \right), \qquad (2.17)$$

$$Z_p = \frac{R_{opt}}{2} \left( 1 + \frac{I_{mT}}{I_p} \right).$$

(2.18)

It can be seen that at the maximum power level

$$I_{mT} = I_p = \frac{I_{max}}{2},$$

(2.19)

$$Z_{mT} = Z_p = R_{opt}. (2.20)$$

The relationship between the input and output voltages and currents of the  $\lambda/4\text{-}$  transmission line are

$$V_p I_{mT} = V_m I_m, (2.21)$$

$$\left(\frac{V_p}{I_{mT}}\right)\left(\frac{V_m}{I_m}\right) = Z_T^2.$$

(2.22)

Combining equations 2.21 and 2.13 gives,

$$Z_{mT} = \frac{R_{opt}}{2} \left( 1 + \frac{I_p Z_T}{V_m} \right). \tag{2.23}$$

The impedance seen by the carrier device is

$$Z_{m} = \frac{Z_{T}^{2}}{Z_{mT}} = \frac{2Z_{T}^{2}}{R_{opt} \left(1 + \frac{I_{p}Z_{T}}{V_{m}}\right)}.$$

(2.24)

The amplitude of the RF voltage swing at the output of the carrier device is

$$V_m = I_m Z_m = \frac{2I_m Z_T^2}{R_{opt} \left(1 + \frac{I_p Z_T}{V_m}\right)}.$$

Substituting for  $I_m$  and  $I_p$  from equations 2.15 and 2.16,

$$V_m = \frac{Z_T^2\left(\frac{I_{max}}{2}\right)(1+\zeta)}{R_{opt}\left(1+\frac{\zeta\left(\frac{I_{max}}{2}\right)Z_T}{V_m}\right)}.$$

After re-arrangement,

$$V_m = \left(\frac{Z_T}{R_{opt}}\right) \left(\frac{I_{max}}{2}\right) \left[Z_T + \zeta \left(Z_T - R_{opt}\right)\right].$$

(2.25)

If we choose  $Z_T = R_{opt}$ , the carrier device output voltage will become independent of input drive level ( $\zeta$ ) and it will become constant at

$$V_m = R_{opt} \left( \frac{I_{max}}{2} \right). \tag{2.26}$$

which is the maximum output voltage swing as desired. From equation 2.21 we can write,

$$\left(\frac{V_p}{I_m}\right) = \left(\frac{I_m}{V_p}\right) R_{opt}^2,\tag{2.27}$$

knowing that  $Z_T = R_{opt}$

$$V_p = I_m R_{opt}.$$

(2.28)

Equation 2.28 and Figure 2.11 show that the power delivered to the load is linearly proportional to the input power. The final maximum power is twice as large as the power of each device. Assuming that the efficiency of both amplifiers is  $\pi/4$ at maximum swing voltage, corresponding to class B operation, discussed in detail in section 2.2.1, the efficiency of each device will drop proportionally as the RF voltage swing decreases. For the low power regime, only the carrier device is active. The efficiency as shown in section 2.2.1, is

$$\eta = \frac{P_{RF}}{P_{dc}} = \frac{\pi}{4} \left( \frac{2v_i}{V_{max}} \right). \tag{2.29}$$

Above the break point, the RF output power is

$$P_{RF} = I_m^2 R_{opt}, \qquad (2.30)$$

so from equations 2.9 and 2.5, we can write

$$P_{RF} = \left(\frac{I_{max}}{2}\right) \left(\frac{v_i}{V_{max}}\right)^2 V_{dc}.$$

(2.31)

The DC power consumption of the carrier device, for class B operation, is

$$P_{dcc} = \left(\frac{I_{max}}{\pi}\right) \left(\frac{v_i}{V_{max}}\right) V_{dc}, \qquad (2.32)$$

and the DC power consumed by the peak amplifier will be

$$P_{dcp} = \left(\frac{I_{max}}{\pi}\right) \left(\frac{2v_i}{V_{max} - 1}\right) V_{dc},\tag{2.33}$$

so the total DC power consumption is

$$P_{dc} = \left(\frac{I_{max}}{\pi}\right) \left[3\left(\frac{2v_i}{V_{max}}\right) - 0.5\right] V_{dc}.$$

(2.34)

The overall efficiency from equations 2.31 and 2.34 is given by

$$\eta = \frac{\pi}{2} \frac{\left(\frac{v_i}{V_{max}}\right)^2}{3\left(\frac{v_i}{V_{max}}\right) - 1}.$$

(2.35)

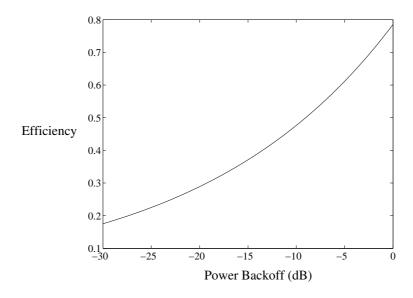

It can be easily seen that the efficiency will reach its maximum  $\pi/4$  limit with both the maximum power condition  $v_{in} = V_{max}$  and 6 dB backoff point  $v_i = V_{max}/2$ . For  $v_i \leq V_{max}/2$ , efficiency rolls off. Figure 2.12 shows the efficiency of the Doherty amplifier [2].

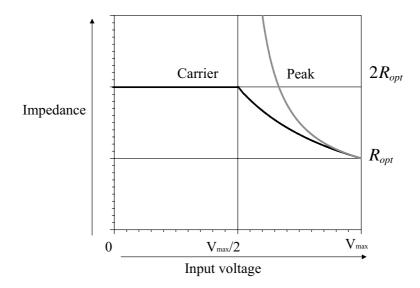

Let's now take a closer look at how the impedance transformation takes place. Below the break-point, the Doherty amplifier looks like the one shown in Figure

Figure 2.12: Power added efficiency of a Doherty amplifier versus power backoff 2.13. The  $\lambda/4$ -transmission line with  $Z_T = R_{opt}$  transforms an impedance of  $R_{opt}/2$ to  $2R_{opt}$ , which is twice as large as the optimum impedance for the carrier amplifier. At this point, the carrier device's output voltage swing reaches saturation with only half of the maximum input drive. This is exactly the point where the peak device is turned on to contribute to the load current and reduce the impedance seen by the carrier amplifier. This way, the carrier amplifier current can increase while its rail-to rail voltage swing remains constant. With its output voltage swing kept constant, the carrier amplifier can retain the constant maximum efficiency within the whole power range above the break-point. At maximum power level, as shown in Figure 2.14, carrier and peak amplifiers supply equal maximum current to the load. The impedance seen at the input of the  $\lambda/4$ -transmission line will, therefore, become  $R_{opt}$ . Figure 2.15 shows the pulling effects on the impedances seen by the

carrier and peak amplifiers versus the input power drive.

Figure 2.13: Doherty configuration below the break-point

Figure 2.14: Doherty configuration above the break-point

Realization of defined characteristics of the peak amplifier brings a lot of problems. It is required for the peak amplifier to remain shut-off up to a certain break point (6-dB backoff from the maximum level in conventional Doherty power amplifier). The most straight forward way to obtain such a performance is to bias it in deep class C mode [2]. Another problem with the peak amplifier is that, once

Figure 2.15: Load pulling effects on the carrier and peak amplifier