# RADIO FREQUENCY FRONT-END CIRCUITS FOR W-CDMA DIRECT CONVERSION RECEIVER

WONG SHENG JAU

NATIONAL UNIVERSITY OF SINGAPORE

2007

# RADIO FREQUENCY FRONT-END CIRCUITS FOR W-CDMA DIRECT CONVERSION RECEIVER

### WONG SHENG JAU

(B. Eng. (Hons), NTU)

### A THESIS SUBMITTED

# FOR THE DEGREE OF MASTER OF ENGINEERING DEPARTMENT OF ELECTRICAL ENGINEERING NATIONAL UNIVERSITY OF SINGAPORE

2007

### Acknowledgements

I would like to thank Dr. Zheng YuanJin for supervising this thesis project. His guidance and supervision style allowed me to exercise my full potential and creativity in research. I would also like to thank Professor Xu YongPing for being a second reader of this thesis and whose detailed comments have helped me remove many errors and improve the argument.

I am deeply grateful to the help provided by Ms. Khoo Ee Sze. She has been both a mentor and a friend since I have known her. Her technical insight and experience in RF circuit designs provide a great source of information.

The research and design of RF front-end circuits were carried out in the Integrated Circuit and System (ICS) Laboratory of Institute of Microelectronics (IME) from 2004 to 2005. The financial and technical support provided by IME and its management staff, especially Mr. Yeo Wooi Gan, Mr. Uday Dasgupta and Dr. Rajinder Singh are greatly appreciated. I also wish to thank the employees of IME, especially Ms. Tan Guek Hong and Ms. Angeline Pay, for their help with layout of the circuits.

Lastly, but definitely not least, I would like to thank my family, especially my parents, Mr. Wong Weng Hong and Madam Nyu Seng Lim, for their continuous support during my studies. I would like to acknowledge the support of my ex-colleagues in IME who share the fun and learning experience.

# **Table of Contents**

| Acknowledgements                                                 | ĺ |

|------------------------------------------------------------------|---|

| Table of Contentsi                                               | i |

| Summary                                                          | 7 |

| List of Tables                                                   | i |

| List of Figures                                                  | i |

| List of Abbreviationsxii                                         | i |

| List of Symbols xv                                               | 7 |

| Chapter 1 Introduction 1                                         |   |

| 1.1 Motivation                                                   | 1 |

| 1.2 Objectives of The Work                                       | 3 |

| 1.3 Thesis Outline                                               | 4 |

| Chapter 2 RF System for W-CDMA Applications                      | ý |

| 2.1 Overview of W-CDMA System                                    | 6 |

| 2.2 Receiver Architectures for Wireless Applications             | 8 |

| 2.3 Direct Conversion Receivers1                                 | 1 |

| 2.3.1 Issues Associated with Direct Conversion Receivers1        | 1 |

| 2.3.1.1 DC Offsets1                                              | 2 |

| 2.3.1.2 Flicker Noise1                                           | 9 |

| 2.3.1.3 LO Leakage and Spurious Radiation2                       | 0 |

| 2.3.1.4 Intermodulation Products from Second-order Nonlinearity2 | 1 |

| 2.4 Direct Conversion Receiver for W-CDMA System2                | 6 |

| 2.4.1       | Introduction                                      | 26 |

|-------------|---------------------------------------------------|----|

| 2.4.2       | System Considerations of Front-end Design         | 28 |

| 2.4.2.      | 1 Single-ended Input vs. Differential Input       | 29 |

| 2.4.2.2     | 2 Reciprocal Mixing                               |    |

| 2.5 Sys     | stem Plan for Direct Conversion Receiver          | 34 |

| 2.5.1       | System Requirements of W-CDMA Receiver            | 34 |

| 2.5.2       | Gain Budget of Direct Conversion Receiver         | 35 |

| Chapter 3 F | RF Front-end Circuits                             | 41 |

| 3.1 Intr    | oduction                                          | 41 |

| 3.1.1       | Trade-offs Between the Noise Figure and Linearity | 41 |

| 3.1.2       | RF Modeling Issues                                | 47 |

| 3.2 Des     | sign of Low Noise Amplifier                       | 49 |

| 3.2.1       | Introduction                                      | 49 |

| 3.2.2       | Design Considerations                             | 50 |

| 3.2.3       | Circuit Topologies                                | 51 |

| 3.2.3.      | 1 Low Noise Amplifier                             | 52 |

| 3.2.3.2     | 2 Active Balun                                    | 61 |

| 3.2.3.      | 3 LNA with Gain Switching                         | 66 |

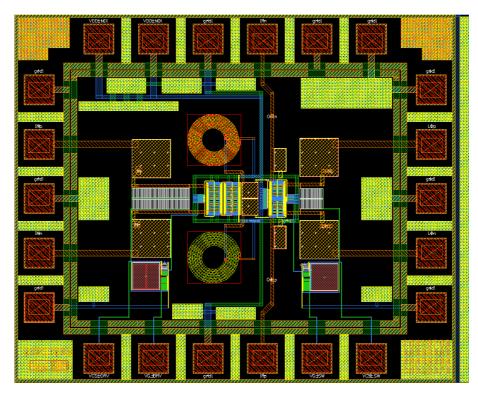

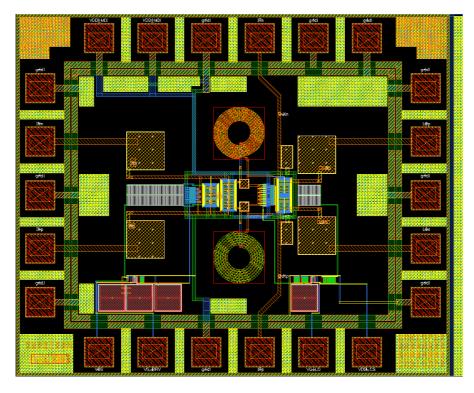

| 3.2.4       | Circuit Implementations                           | 69 |

| 3.2.5       | Simulation Results of LNA                         | 74 |

| 3.3 Des     | sign of Mixer Circuit                             | 81 |

| 3.3.1       | Introduction                                      | 81 |

| 3.3.2       | Design Considerations                             | 82 |

| 3.3.3       | Circuit Topologies                                | 84 |

| 3.3.4          | Circuit Implementations                         | 94  |

|----------------|-------------------------------------------------|-----|

| 3.3.5          | Simulation Results of Mixer                     | 100 |

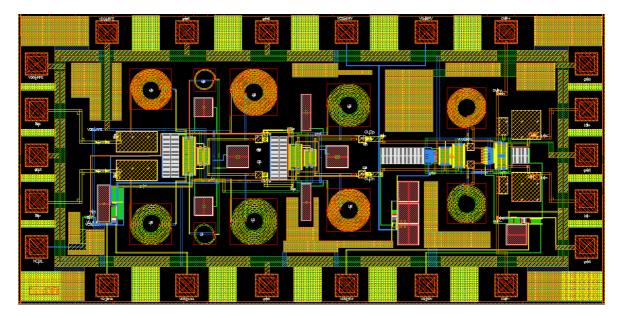

| 3.4 Dest       | ign of an Integrated RF Front-end               | 106 |

| 3.4.1          | Circuit Implementations                         | 106 |

| 3.4.2          | Simulation Results of the RF Front-end Circuits | 107 |

| Chapter 4 E    | xperimental Results                             | 113 |

| 4.1 Intro      | oduction                                        | 113 |

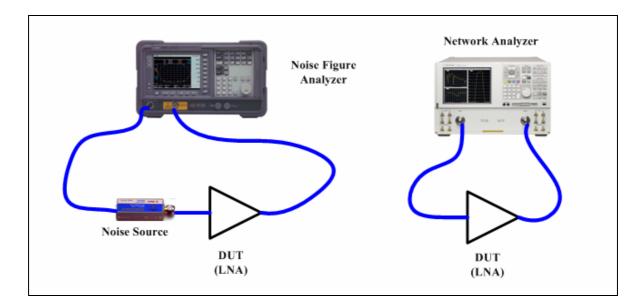

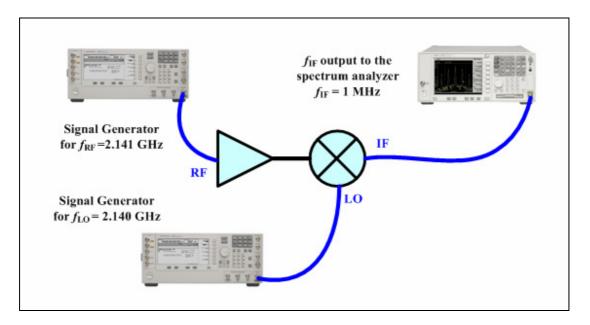

| 4.2 Test       | Methodology                                     | 114 |

| 4.3 Mea        | surement of Test Chips                          | 115 |

| 4.3.1          | Low Noise Amplifier                             | 116 |

| 4.3.2          | Down-conversion Mixer                           | 131 |

| 4.4 Integ      | grated RF Front-end Chip                        | 138 |

| 4.5 Con        | nparisons with published results                | 145 |

| Chapter 5 C    | onclusions                                      | 146 |

| Chapter 6 R    | ecommendations                                  | 148 |

| Bibliography . |                                                 | 150 |

| Appendix A     | Simulation Results                              | 157 |

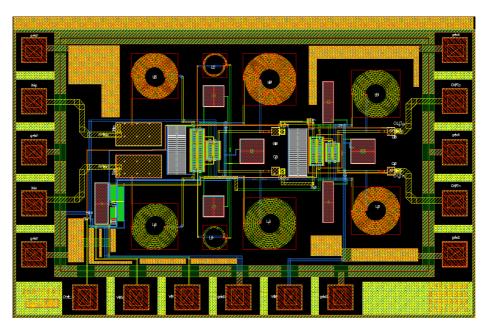

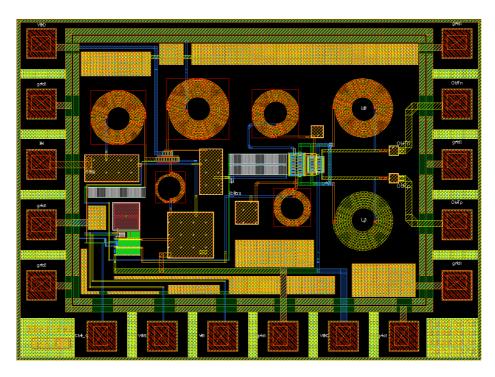

| Appendix B     | Chip Layout Diagrams                            | 164 |

| Appendix C     | PCBs for Test Chip Measurements                 | 167 |

| Appendix D     | Test Setup for Measurements                     | 169 |

### **Summary**

The work presented in this thesis focuses on the system analysis and the development of RF front-end circuits for the direct conversion receiver. The system analysis includes the brief review on the W-CDMA system, the studies of different wireless receiver topologies and in-depth analysis of the problem associated with the direct conversion receiver. Furthermore, the technical requirements of the direct conversion receiver for the W-CDMA application are also analyzed and the design goals for the RF front-end circuits are derived.

In the second part of the thesis, the designs, simulations and the measurements from two LNA topologies, two down-converted mixers and one integrated front-end circuit are covered. In the LNA designs, single-ended and differential versions are presented. The core circuits for both versions are based on the cascode topology with inductive source degeneration. The active balun circuit is also included for the conversion of single-ended LNA output to differential signals. For the mixer circuits, two different approaches are adopted for improving the issues related to LO-leakage and the second-order intermodulation products. In the first mixer design, the transconductance driver stage and the switching stage are separated to avoid the direct path for the leakage from LO – port to RF – port. The second mixer circuit, the common-gate configuration is utilized as driver stage and current injection technique and frequency trap are used to improve the flicker noise and the second-order intermodulation products. For the verification of the IM2

performance of the direct conversion receiver, the integrated front-end design which consists of the differential LNA and the second mixer circuit are fabricated and measured.

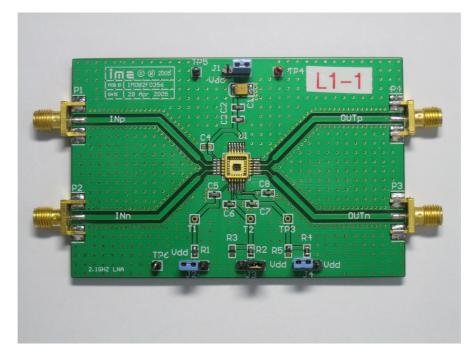

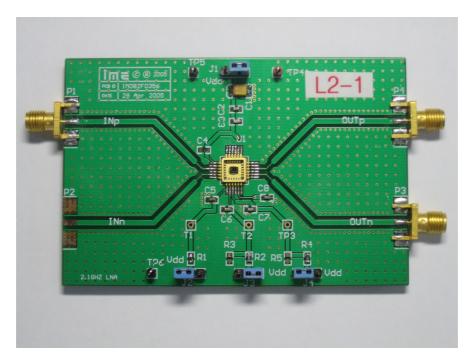

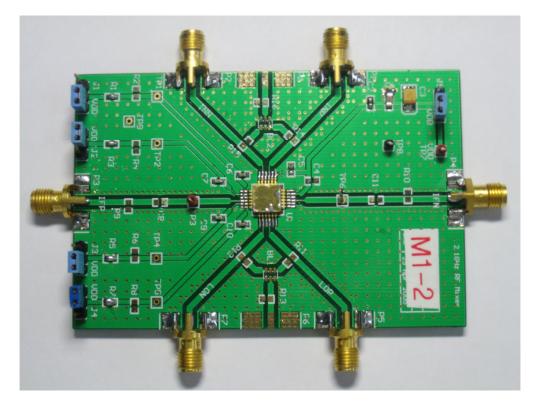

All the circuits are implemented through the Chartered Semiconductor Manufacturing  $0.35 \ \mu m$  CMOS technology with the RF option. The models of active and passive devices used in the designs are based on IME in-house extracted RF model. All the circuits are mounted on QFP-24 pin package and measured on the FR-4 PCBs.

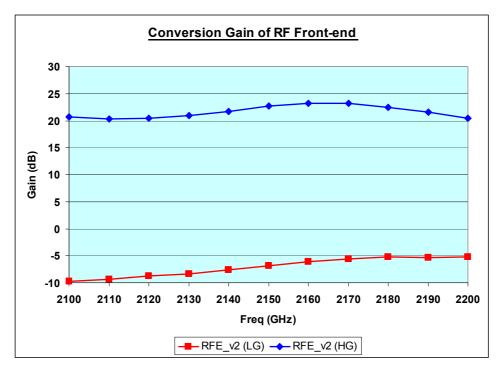

The measurement of LNAs showed that the version consisting of single-ended LNA and active balun has better noise figure and power gain than differential design. However, the measured noise figure and power gain are lower than the simulated results. This discrepancy becomes larger for the low gain mode when the bypass switches are turned on. The unexpected higher loss from the transmission gate is the suspected root cause for such deviations. For the down-converter, the Gilbert cell mixer with the common-gate input has inferior conversion gain and worse port-to-port isolation than the other approach. The mismatches of the common-gate input may result in considerable signal loss. However, the integrated front-end design shows more encouraging results, the total gain and noise figure in high gain mode are 22 dB and 9.5 dB respectively. The *IIP2* is 23 dBm in high gain mode, this result will be further improved when the bypass switch of the LNA is turned on. The total current consumption is 17 mA in high gain mode and it is reduced to 12 mA when the LNA is switched off.

### List of Tables

| Table 2.1 | System characteristics of WCDMA UMTS – FDD mode                     | 7   |

|-----------|---------------------------------------------------------------------|-----|

| Table 2.2 | Summary of the system requirements of W-CDMA receiver               | 34  |

| Table 2.3 | Baseband (VGA and filter) performance reported in [2]               | 36  |

| Table 2.4 | The hand calculated receiver plan                                   | 39  |

| Table 2.5 | Design goals of the RF front-end circuit for the W-CDMA application | 40  |

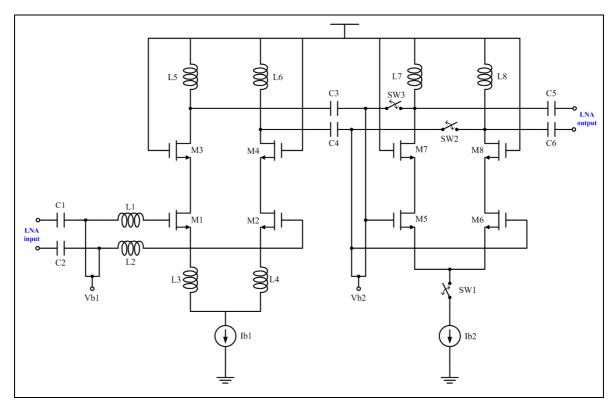

| Table 3.1 | The feature sizes of the elements used in LNA_v1                    | 70  |

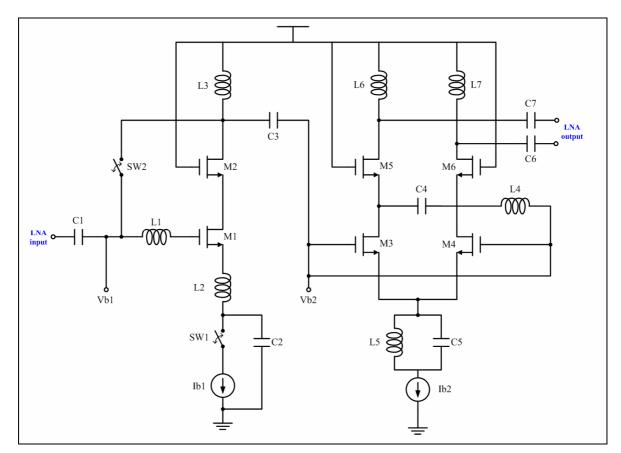

| Table 3.2 | The feature sizes of the elements used in LNA_v2                    | 72  |

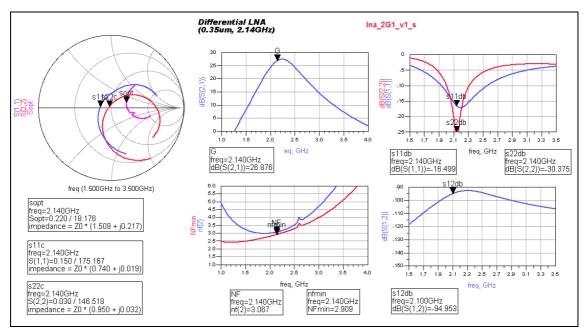

| Table 3.3 | Summary of LNA Simulation Results                                   | 80  |

| Table 3.4 | The feature sizes of the elements used in MIX_v1                    | 95  |

| Table 3.5 | The feature sizes of the elements used in MIX_v2                    | 98  |

| Table 3.6 | Summary of mixer simulation results                                 | 105 |

| Table 3.7 | Summary of RF front-end simulation results (LNA v.1 + Mix v.2)      | 108 |

| Table 4.1 | Summary of test chip versions                                       | 113 |

| Table 4.2 | Summary of low noise amplifier measurements (LNA_v1)                | 116 |

| Table 4.3 | Summary of low noise amplifier measurements (LNA_v2)                | 116 |

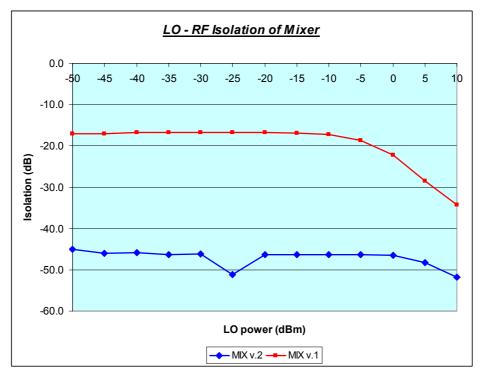

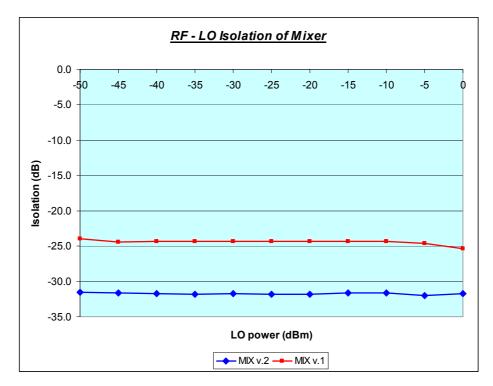

| Table 4.4 | Summary of direct conversion mixer measurements (MIX_v1)            | 132 |

| Table 4.5 | Summary of direct conversion mixer measurements (MIX_v2)            | 132 |

| Table 4.6 | Summary of RF front-end measurements                                | 138 |

| Table 4.7 | Performance comparison with the published results.                  | 145 |

# List of Figures

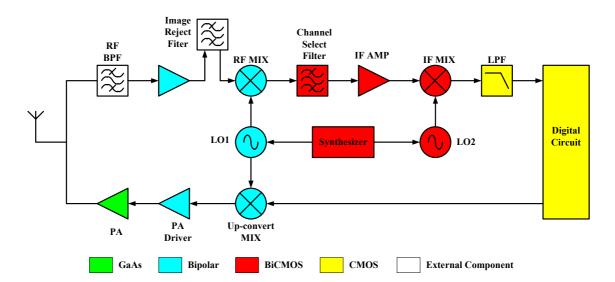

| Figure 1.1  | The semiconductor technologies used in wireless transceiver modules      | 2  |

|-------------|--------------------------------------------------------------------------|----|

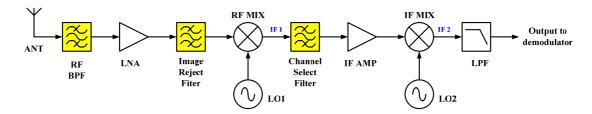

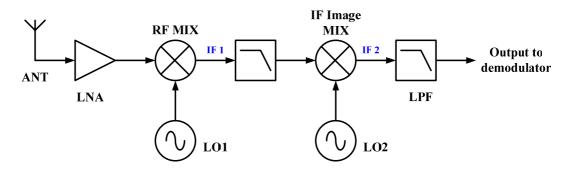

| Figure 2.1  | Building blocks of superheterodyne receiver                              | 10 |

| Figure 2.2  | Building blocks of direct conversion receiver                            | 10 |

| Figure 2.3  | Building blocks of low-IF single conversion receiver                     | 10 |

| Figure 2.4  | Building blocks of wideband IF double conversion receiver                | 10 |

| Figure 2.5  | The mechanism of self-mixing due to LO – RF leakage                      | 15 |

| Figure 2.6  | The simplified spectrum diagram of RF – LO leakage                       | 17 |

| Figure 2.7  | The mechanism of self-mixing due to RF leakage to LO port                | 19 |

| Figure 2.8  | The spectrum diagram of the self-mixing of RF – LO leakage               | 19 |

| Figure 2.9  | IM2 product from two-tone inputs                                         | 23 |

| Figure 2.10 | Single blocker envelope distortion                                       | 25 |

| Figure 2.11 | Typical direct conversion receiver for WCDMA application                 | 27 |

| Figure 2.12 | Typical front-end design of direct conversion receiver                   | 28 |

| Figure 2.13 | Fully differential RF front-end design                                   | 29 |

| Figure 2.14 | RF front-end with single-ended input                                     | 30 |

| Figure 2.15 | The typical front-end design of WCDMA transceiver                        | 31 |

| Figure 2.16 | Strong blocker arisen from the leakage of transmitter signal             | 32 |

| Figure 2.17 | An alternative way to reduce the effect of a strong out-of-band blocker. | 33 |

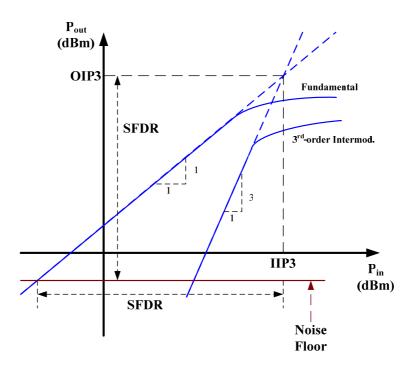

| Figure 3.1  | Graphical representation of spurious-free dynamic range                  | 42 |

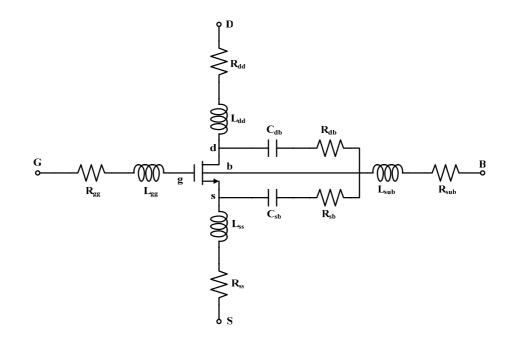

| Figure 3.2  | The RF model and substrate network of NMOS transistor [51]               | 48 |

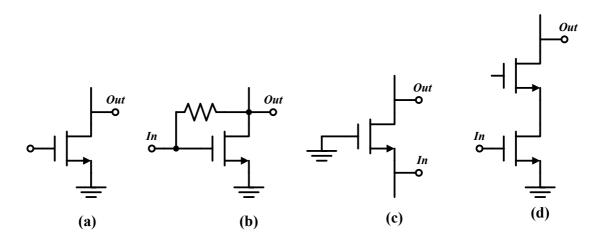

| Figure 3.3  | The circuit topologies of CMOS LNA design                                | 53 |

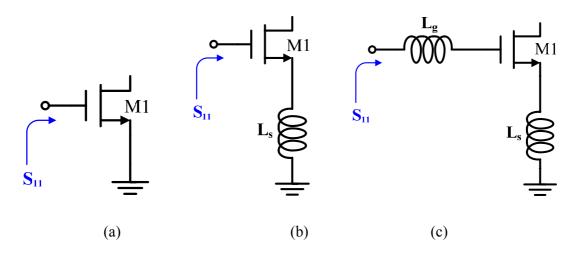

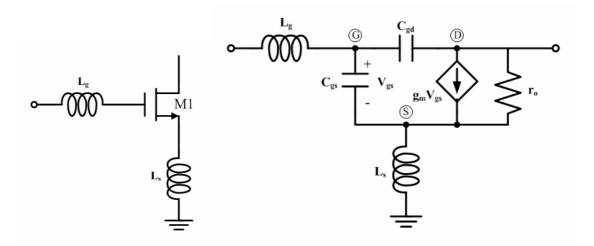

| Figure 3.4  | The matching of transistor M1                                                     | 55 |

|-------------|-----------------------------------------------------------------------------------|----|

| Figure 3.5  | The change of $S_{11}$ , $S_{opt}$ and $F_{min}$ after adding the source inductor | 56 |

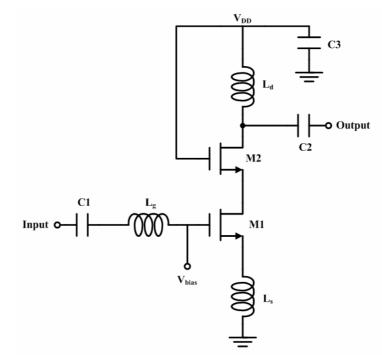

| Figure 3.6  | Schematic of single-ended LNA with inductive source degeneration                  | 57 |

| Figure 3.7  | The small signal model of M1                                                      | 57 |

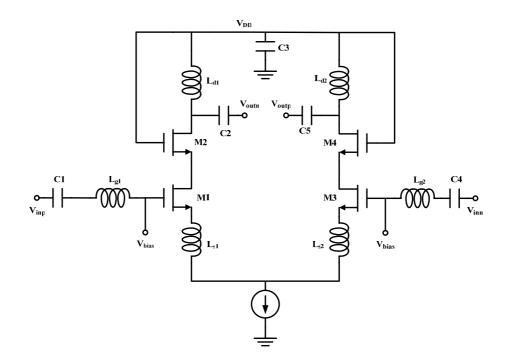

| Figure 3.8  | Schematic of differential LNA with inductive source degeneration                  | 61 |

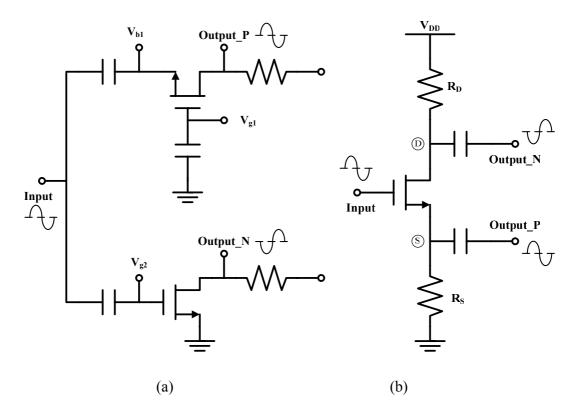

| Figure 3.9  | Examples of active balun circuits                                                 | 63 |

| Figure 3.10 | Problems of differential circuit use as an active balun                           | 64 |

| Figure 3.11 | The modified active balun                                                         | 65 |

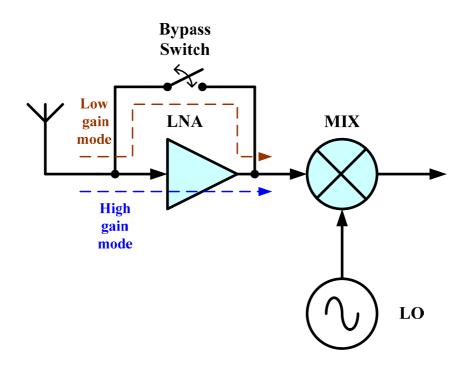

| Figure 3.12 | The LNA with gain switching                                                       | 67 |

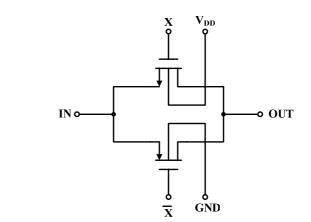

| Figure 3.13 | Structure of transmission gate                                                    | 68 |

| Figure 3.14 | Schematic of LNA v1                                                               | 70 |

| Figure 3.15 | Schematic of LNA v2                                                               | 72 |

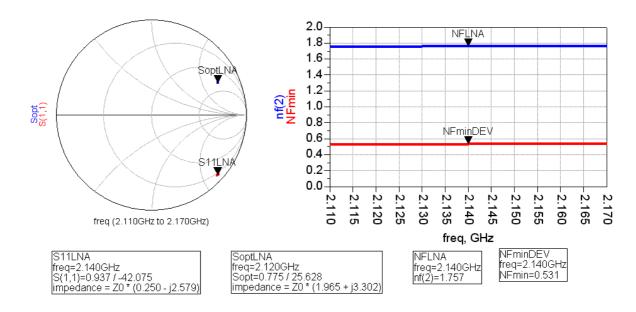

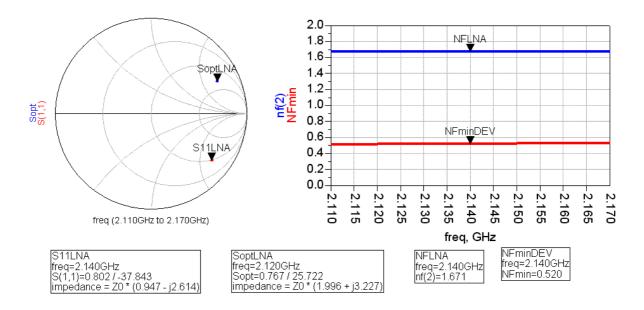

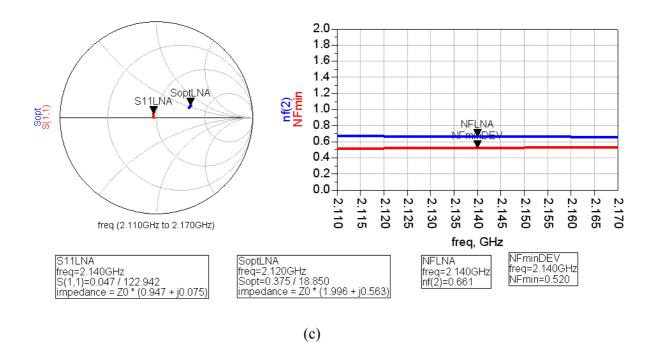

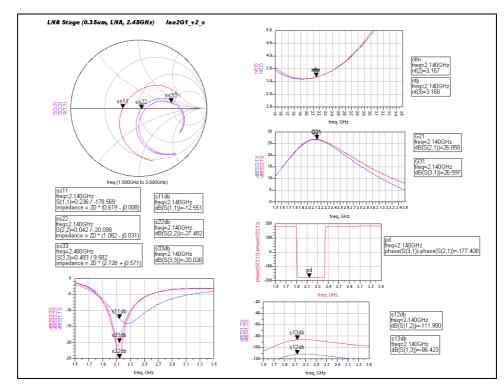

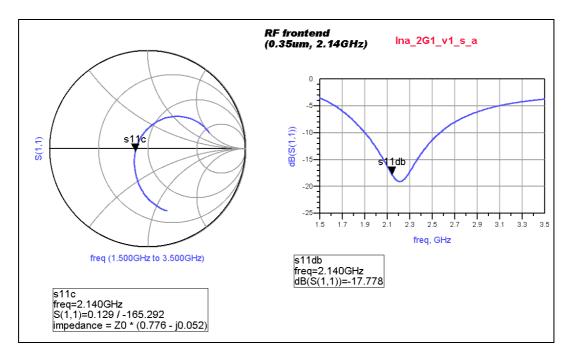

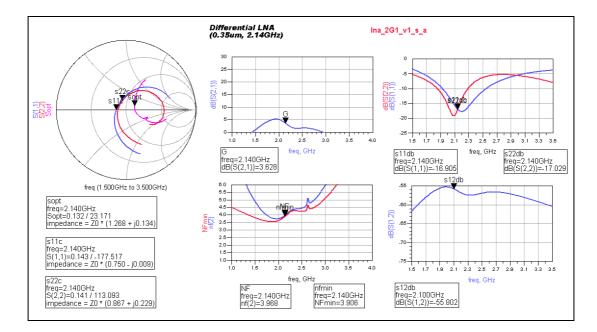

| Figure 3.16 | S-parameters and noise figure of LNA_v1 (high gain mode)                          | 75 |

| Figure 3.17 | S-parameters and noise figure of LNA_v2 (high gain mode)                          | 75 |

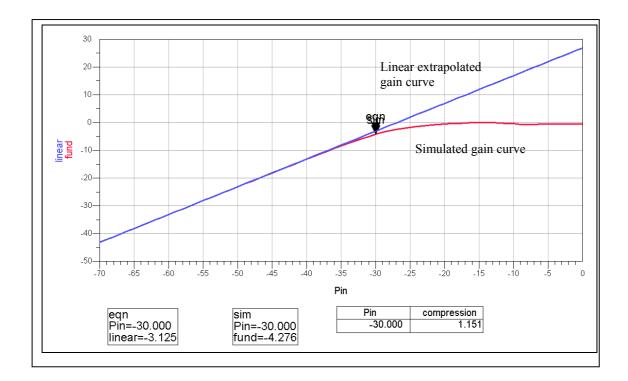

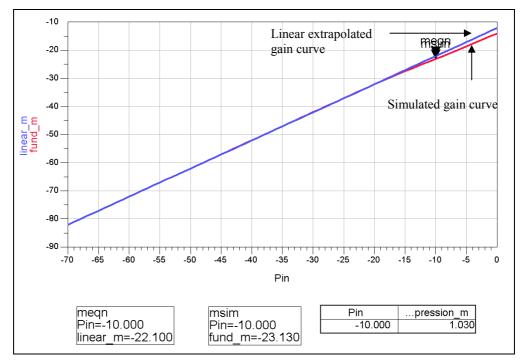

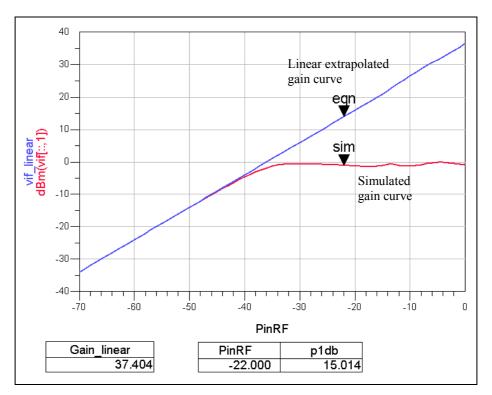

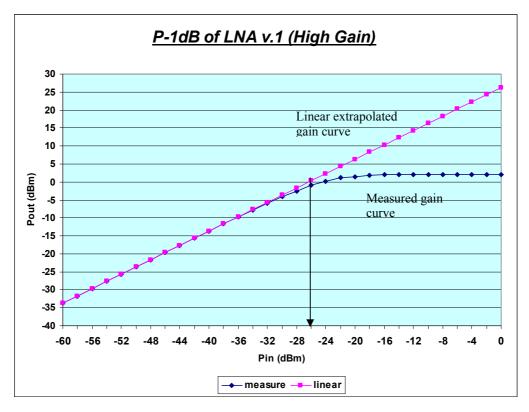

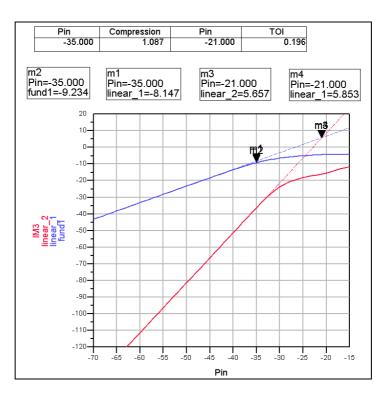

| Figure 3.18 | 1-dB compression point of LNA_v1 (high gain mode)                                 | 76 |

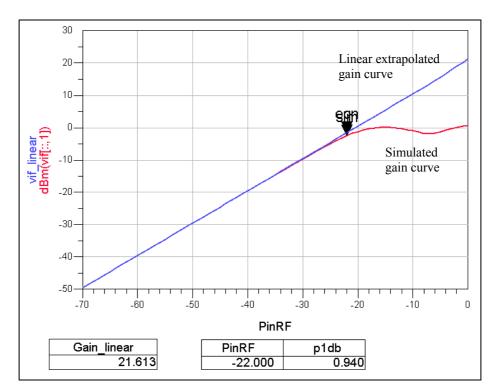

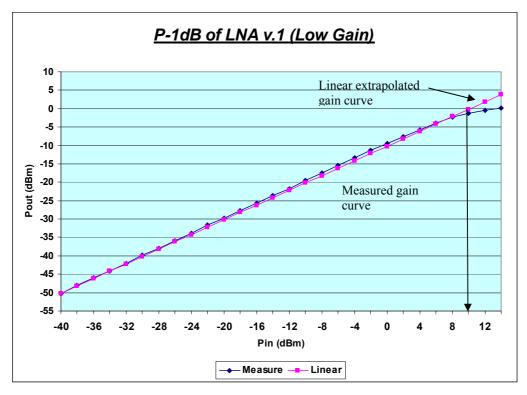

| Figure 3.19 | 1-dB compression point of LNA_v1 (low gain mode)                                  | 76 |

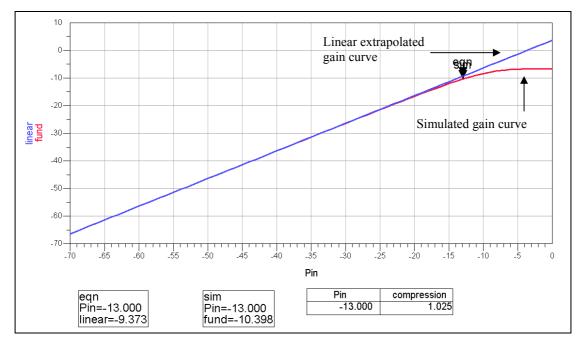

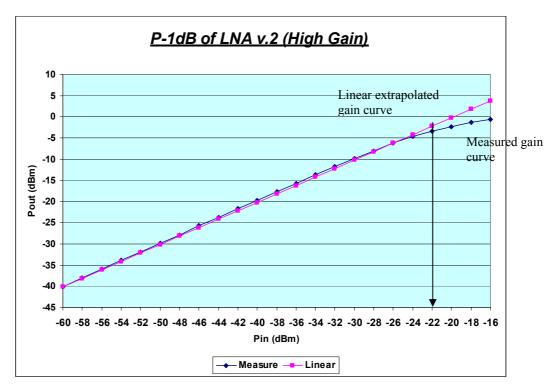

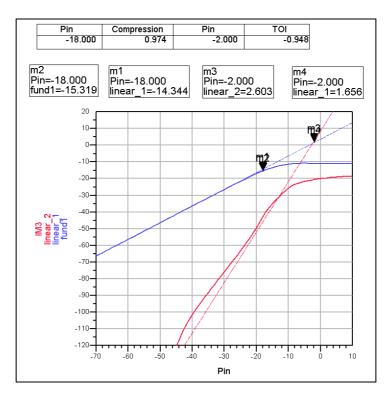

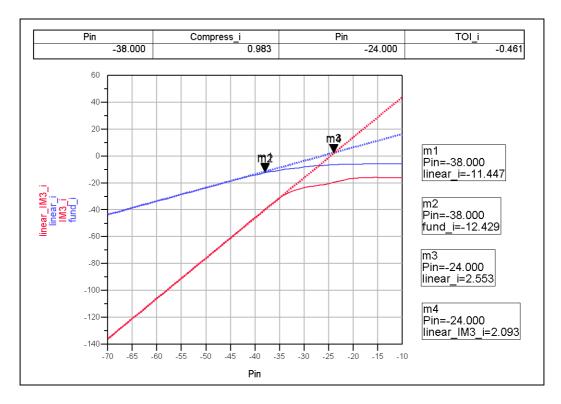

| Figure 3.20 | 1-dB compression point of LNA_v2 (high gain mode)                                 | 77 |

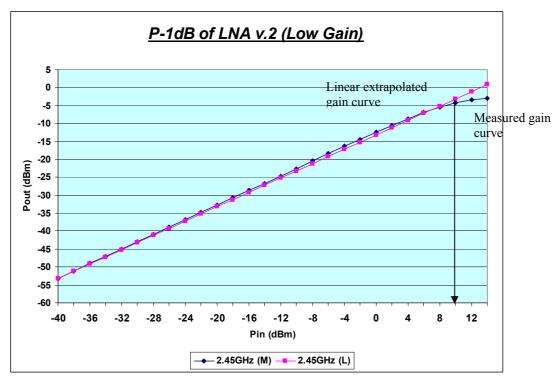

| Figure 3.21 | 1-dB compression point of LNA_v2 (low gain mode)                                  | 77 |

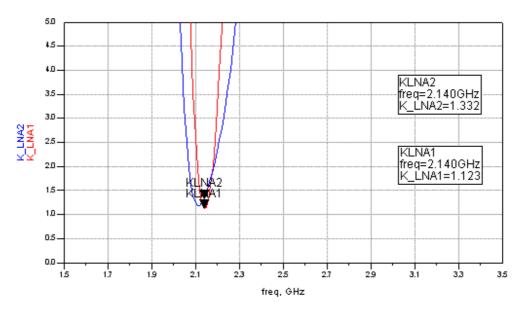

| Figure 3.22 | Simulated <i>K</i> -factor of LNA_v1 and LNA_v2                                   | 79 |

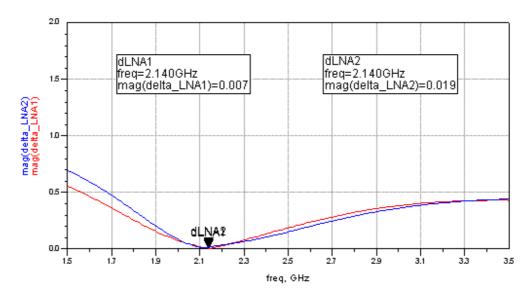

| Figure 3.23 | Simulated $\Delta$ of LNA_v1 and LNA_v2                                           | 79 |

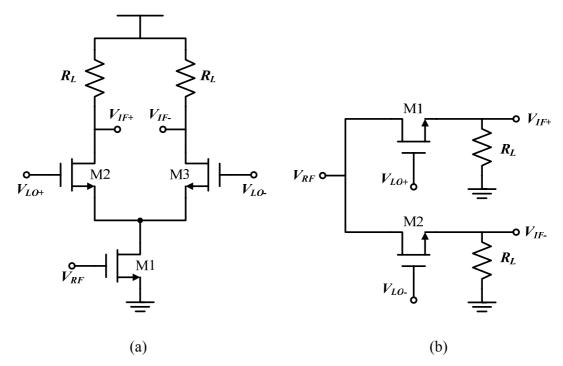

| Figure 3.24 | Mixer circuits for RF applications: (a) active mixer (b) passive mixer            | 83 |

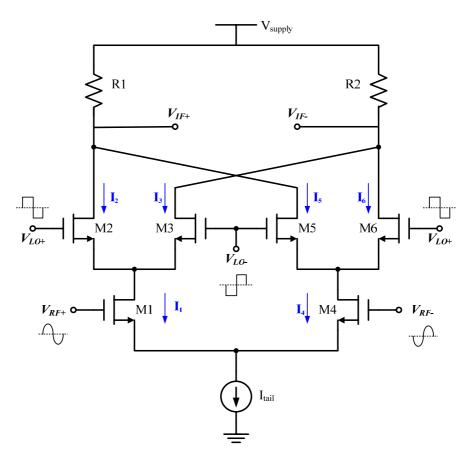

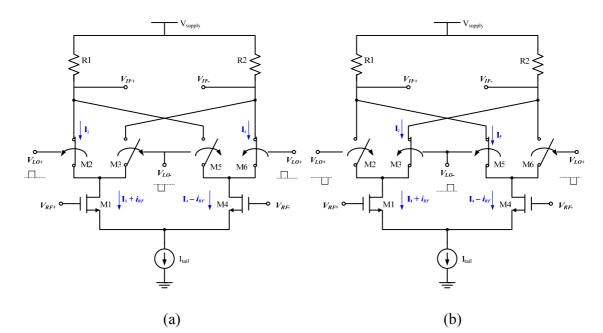

| Figure 3.25 | The double-balanced Gilbert cell mixer                                            | 85 |

| Figure 3.26 | The switching action of the double-balanced Gilbert cell mixer                    | 87 |

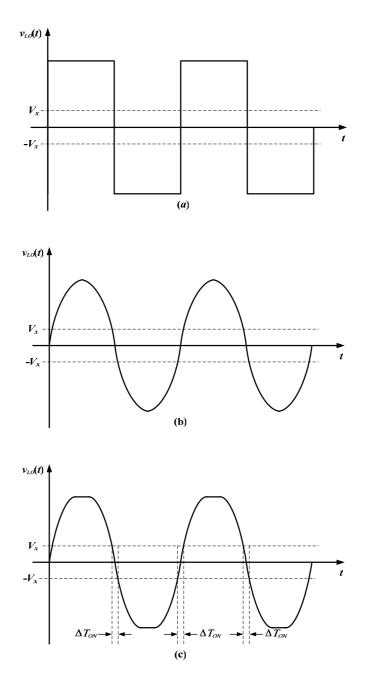

| Figure 3.27 | The various input waveforms at the LO-port of mixer                  | 90    |

|-------------|----------------------------------------------------------------------|-------|

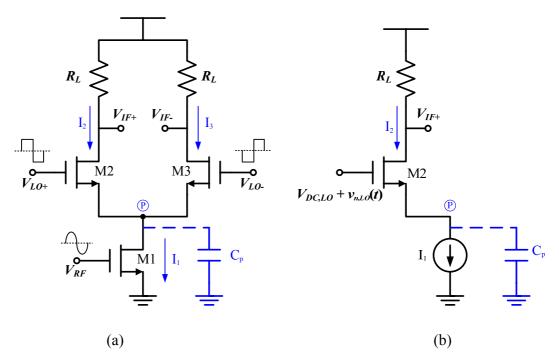

| Figure 3.28 | The model of switching noise                                         | 92    |

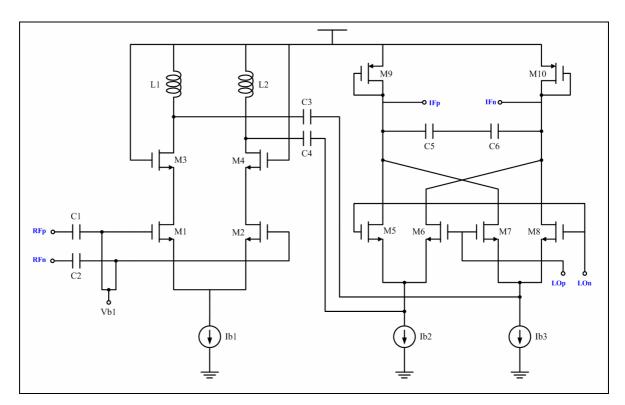

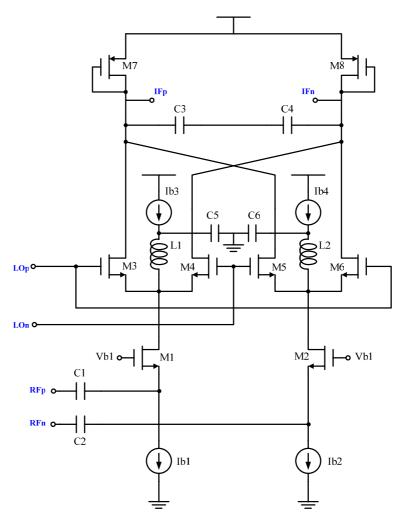

| Figure 3.29 | Schematic of MIX_v1                                                  | 95    |

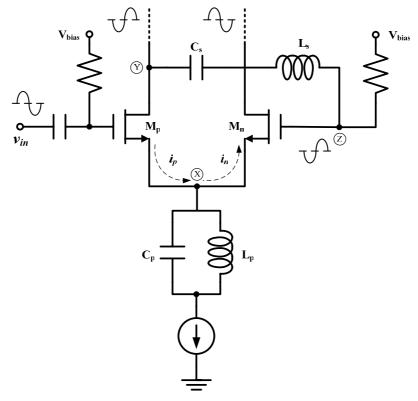

| Figure 3.30 | Schematic of MIX_v2                                                  | 97    |

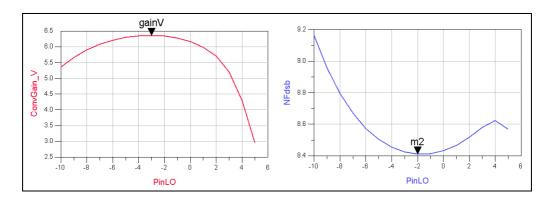

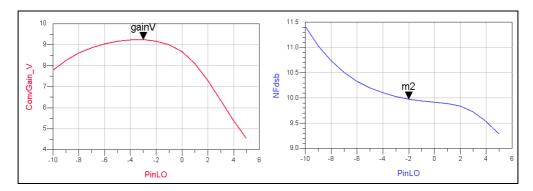

| Figure 3.31 | Voltage conversion gain and double side band noise figure of MIX_v   | 1.100 |

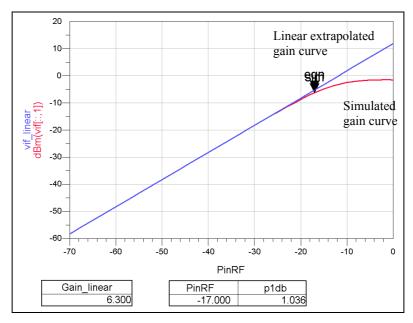

| Figure 3.32 | 1-dB compression point of MIX_v1                                     | 101   |

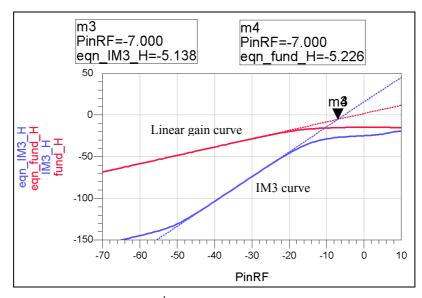

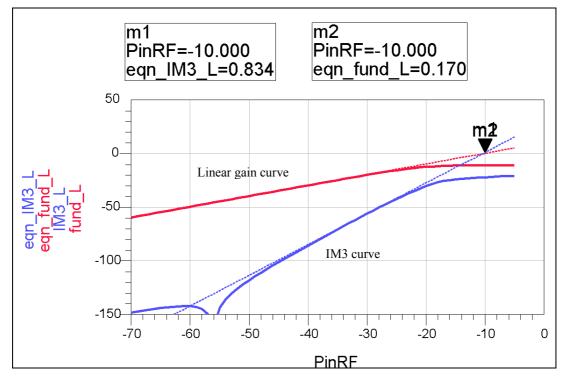

| Figure 3.33 | 3 <sup>rd</sup> -order intercept point of MIX_v1                     | 101   |

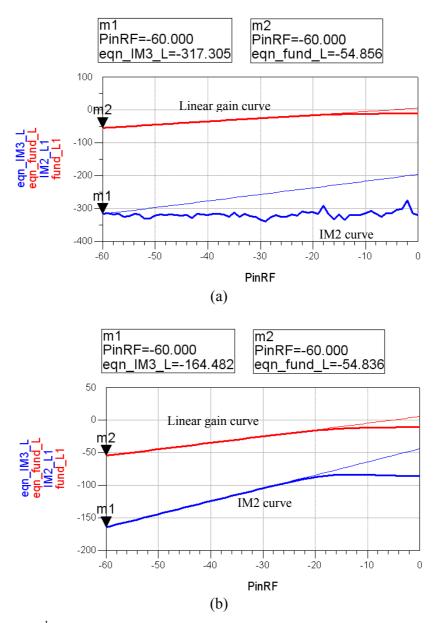

| Figure 3.34 | 2 <sup>nd</sup> -order intercept point of MIX_v1                     | 102   |

| Figure 3.35 | Voltage conversion gain and double side band noise figure of MIX_v   | 2.103 |

| Figure 3.36 | 1-dB compression point of MIX_v2                                     | 103   |

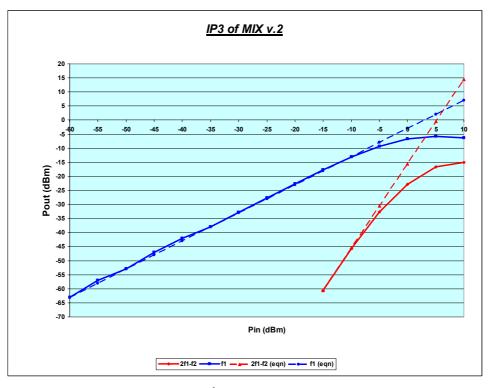

| Figure 3.37 | 3 <sup>rd</sup> -order intercept point of MIX_v2                     | 104   |

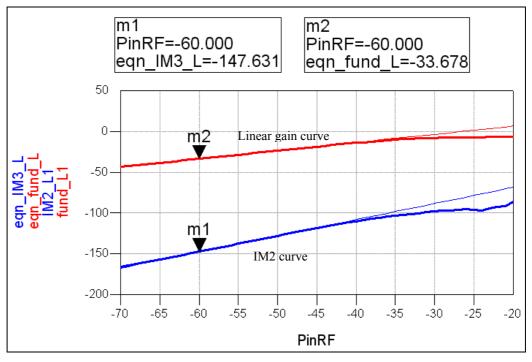

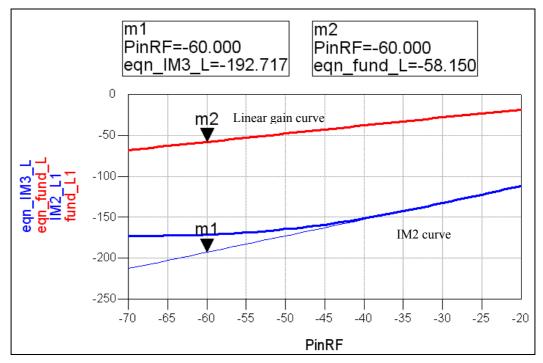

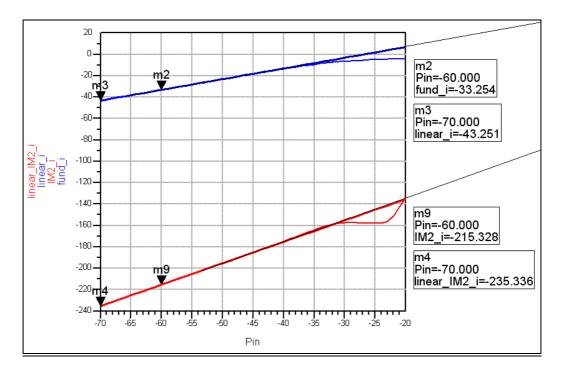

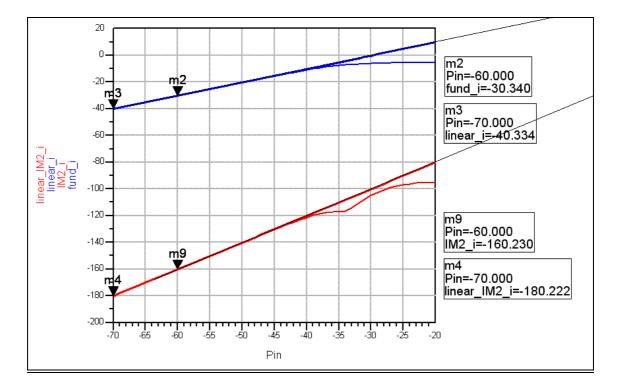

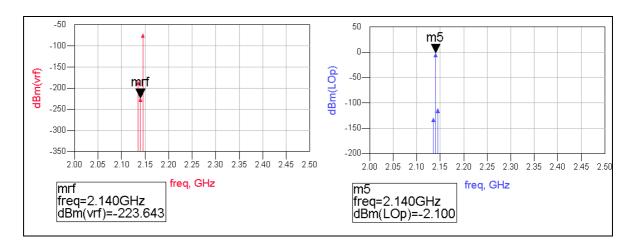

| Figure 3.38 | 2 <sup>nd</sup> -order intercept point of MIX_v1                     | 105   |

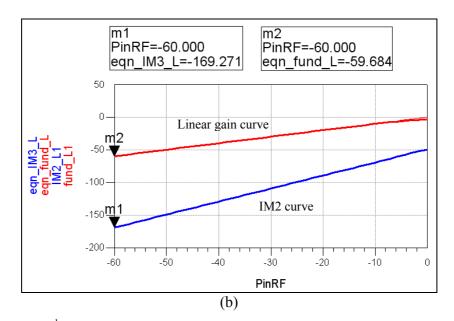

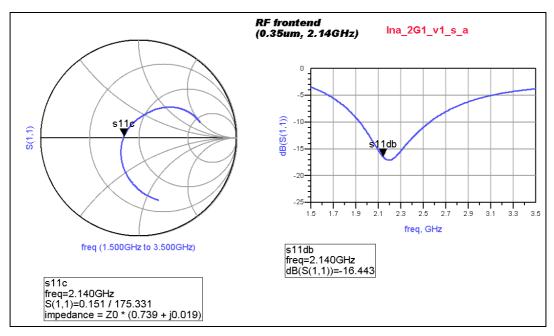

| Figure 3.39 | S <sub>11</sub> of RF front-end (high gain mode)                     | 109   |

| Figure 3.40 | S <sub>11</sub> of RF front-end (low gain mode)                      | 109   |

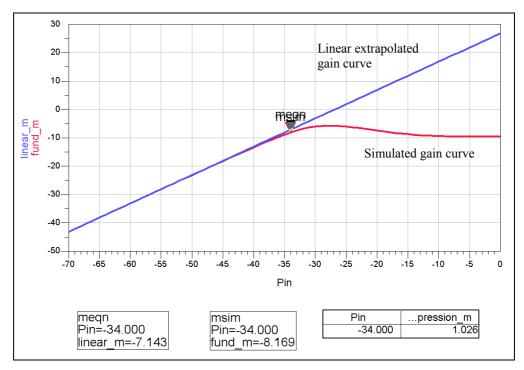

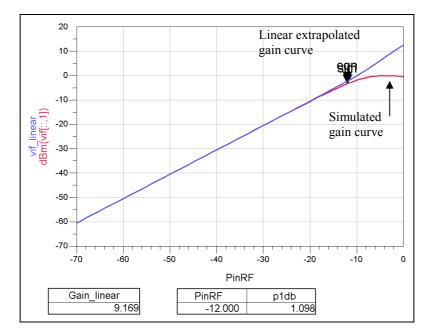

| Figure 3.41 | 1-dB compression point of RF front-end (high gain mode)              | 110   |

| Figure 3.42 | 1-dB compression point of RF front-end (low gain mode)               | 110   |

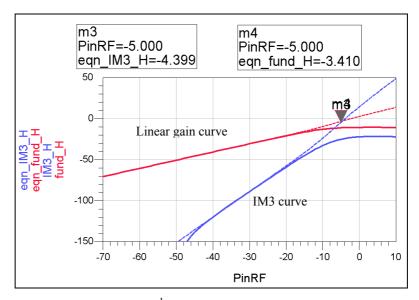

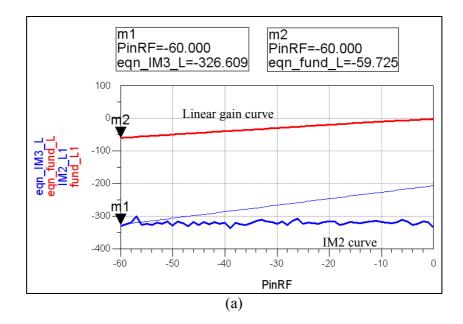

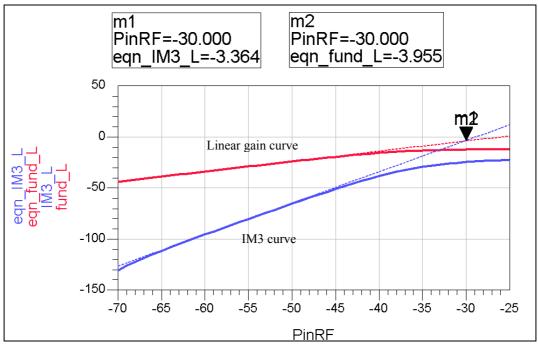

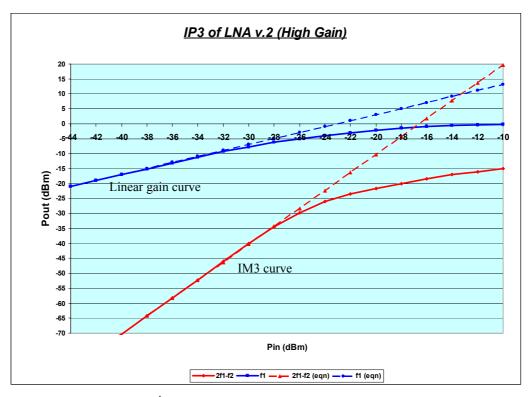

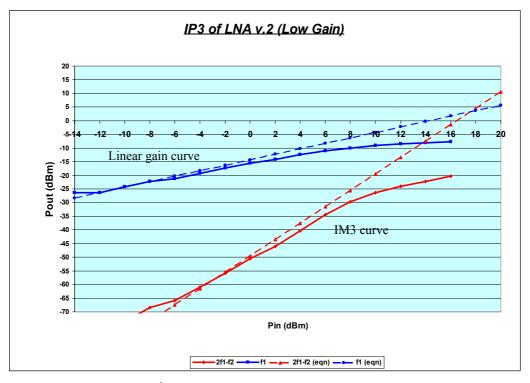

| Figure 3.43 | IIP3 of RF front-end (high gain mode)                                | 111   |

| Figure 3.44 | IIP3 of RF front-end (low gain mode)                                 | 111   |

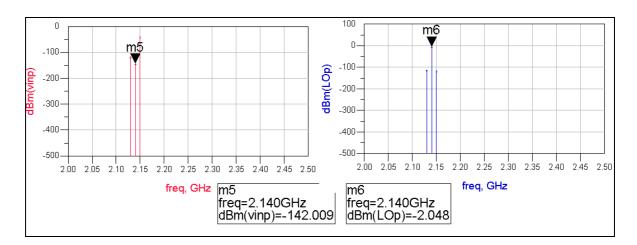

| Figure 3.45 | IIP2 of RF front-end (high gain mode)                                | 112   |

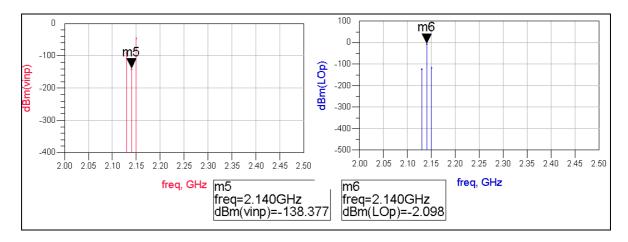

| Figure 3.46 | IIP2 of RF front-end (low gain mode)                                 | 112   |

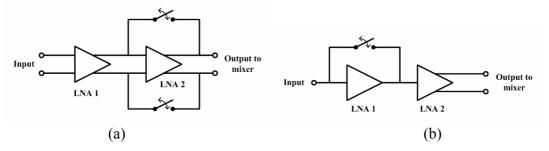

| Figure 4.1  | Illustration of bypass topologies for LNA operating in low gain mode | e118  |

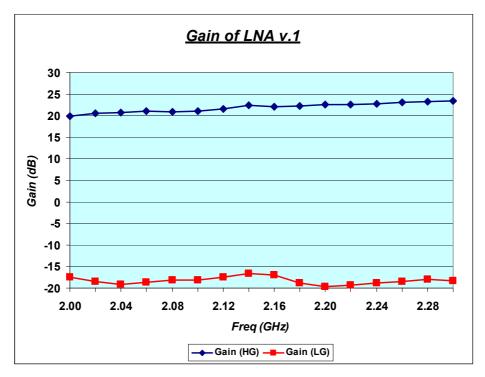

| Figure 4.2  | Gain of LNA_v1 (high/low gain mode)                                  | 119   |

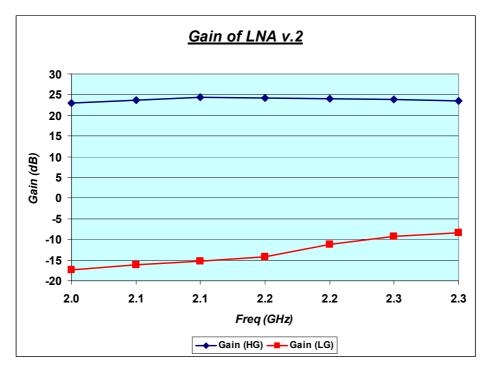

| Figure 4.3  | Gain of LNA_v2 (high/low gain mode)                                  | 119   |

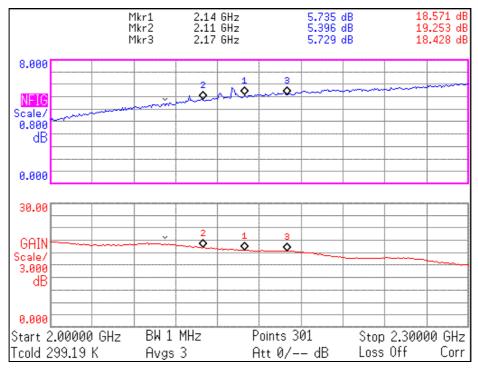

| Figure 4.4  | Noise figure of LNA_v1 (high gain mode)                              | 120   |

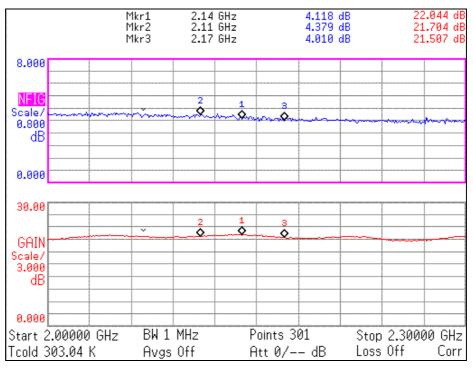

| Figure 4.5  | Noise figure of LNA_v2 (high gain mode)                           | 120 |

|-------------|-------------------------------------------------------------------|-----|

| Figure 4.6  | 1-dB compression point of LNA_v1 (high gain mode)                 | 121 |

| Figure 4.7  | 1-dB compression point of LNA_v1 (low gain mode)                  | 121 |

| Figure 4.8  | 1-dB compression point of LNA_v2 (high gain mode)                 | 122 |

| Figure 4.9  | 1-dB compression point of LNA_v2 (low gain mode)                  | 122 |

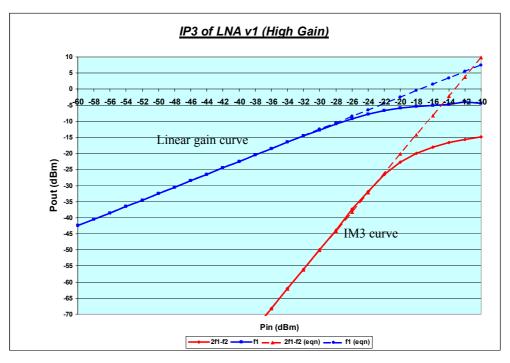

| Figure 4.10 | 3rd-order intercept point of LNA_v1 (high gain mode)              | 123 |

| Figure 4.11 | 3 <sup>rd</sup> -order intercept point of LNA_v1 (low gain mode)  | 123 |

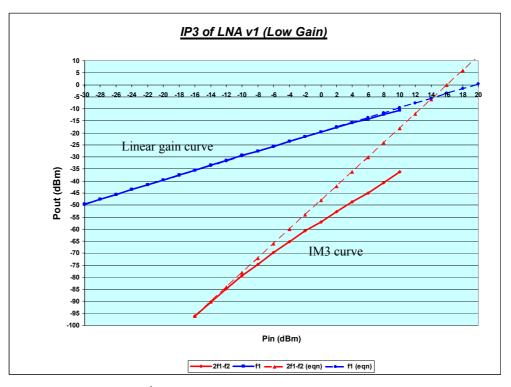

| Figure 4.12 | 3 <sup>rd</sup> -order intercept point of LNA_v2 (high gain mode) | 124 |

| Figure 4.13 | 3 <sup>rd</sup> -order intercept point of LNA_v2 (low gain mode)  | 124 |

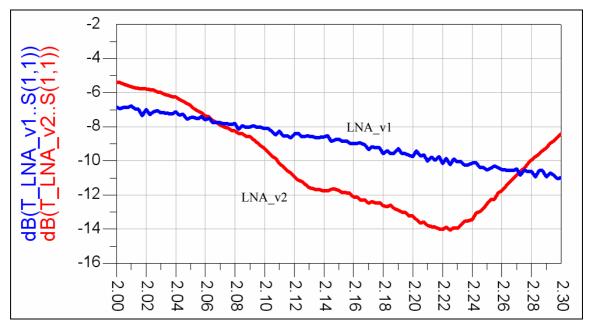

| Figure 4.14 | S <sub>11</sub> of LNA_v1 and LNA_v2 (high gain mode)             | 125 |

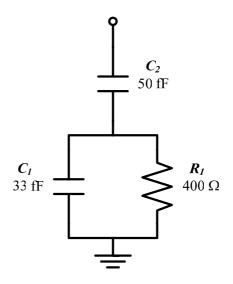

| Figure 4.15 | The estimated model of bond pad                                   | 127 |

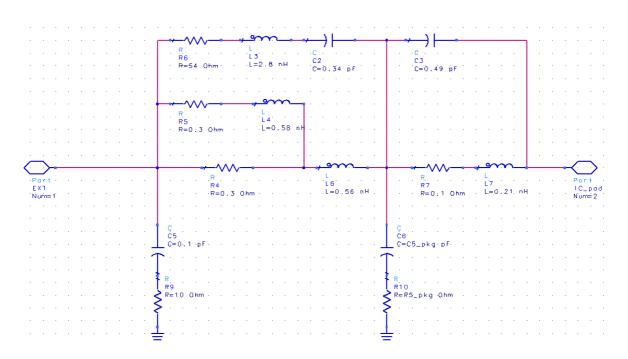

| Figure 4.16 | The estimated model of the package                                | 127 |

| Figure 4.17 | The simulation of the LNA                                         | 128 |

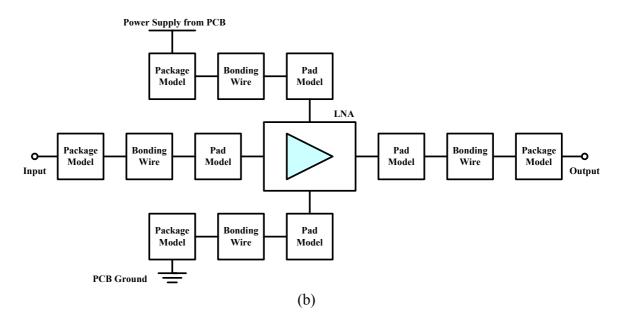

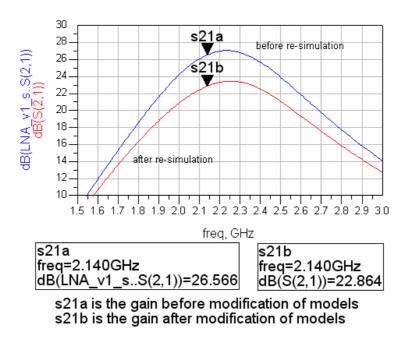

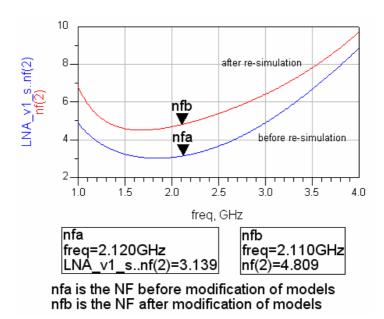

| Figure 4.18 | Reduction of the gain (LNA_v1)                                    | 129 |

| Figure 4.19 | Degradation of the noise figure (LNA_v1)                          | 129 |

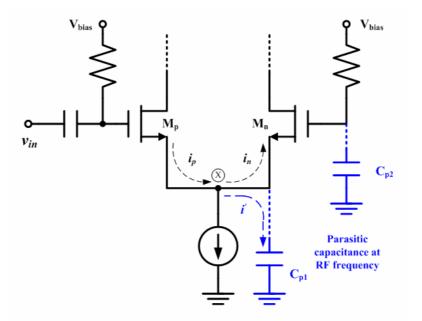

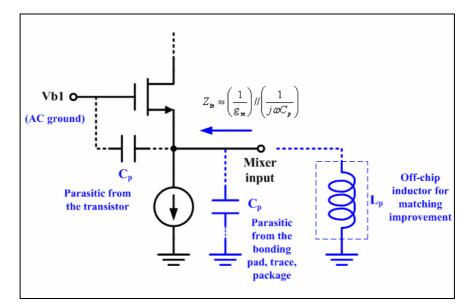

| Figure 4.20 | The parasitic capacitance associated with common-gate topology    | 134 |

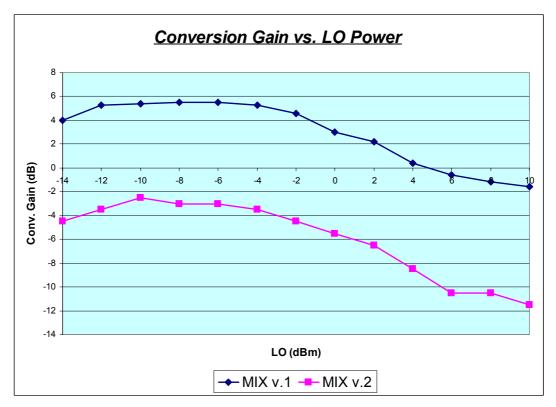

| Figure 4.21 | Mixer conversion gain vs. LO level                                | 134 |

| Figure 4.22 | 1-dB compression point of MIX v.1                                 | 135 |

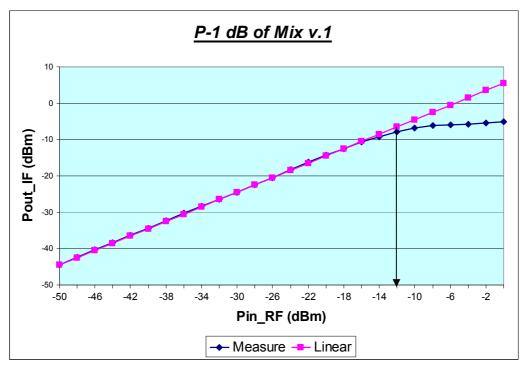

| Figure 4.23 | 1-dB compression point of MIX v.2                                 | 135 |

| Figure 4.24 | 3 <sup>rd</sup> -intercept point of MIX v.1                       | 136 |

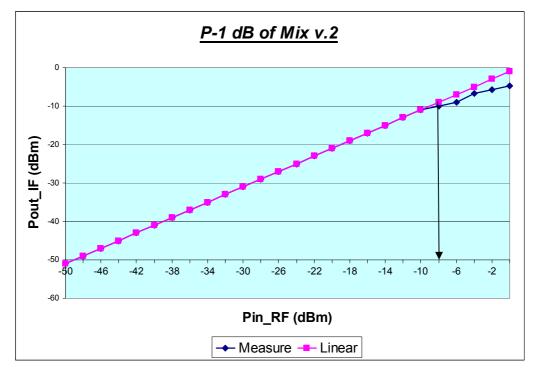

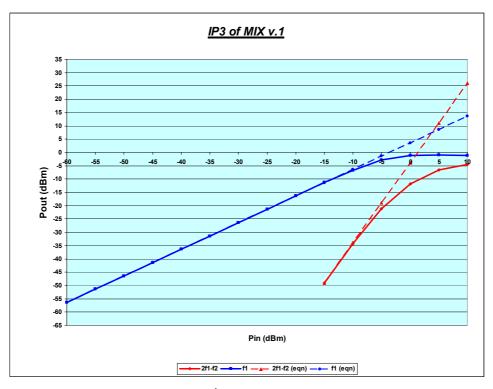

| Figure 4.25 | 3 <sup>rd</sup> -intercept point of MIX v.2                       | 136 |

| Figure 4.26 | LO – RF isolation of mixer                                        | 137 |

| Figure 4.27 | RF – LO isolation of mixer                                        | 137 |

| Figure 4.28 | Voltage conversion gain of RF front-end at high/low gain mode     | 141 |

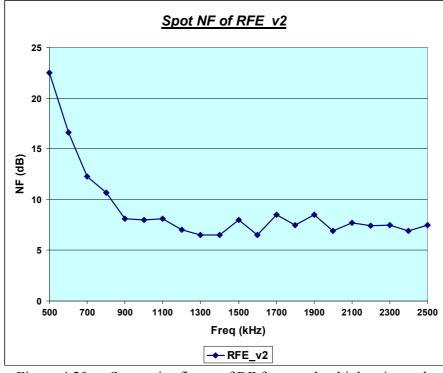

| Figure 4.29 | Spot noise figure of RF front-end at high gain mode | 141 |

|-------------|-----------------------------------------------------|-----|

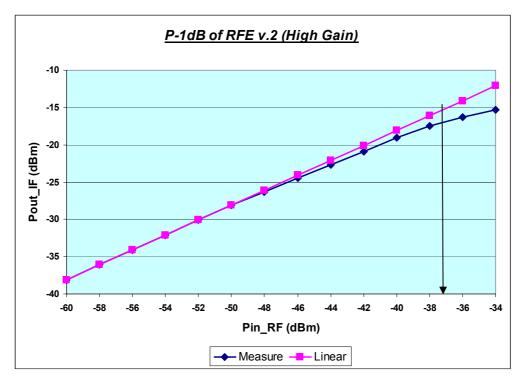

| Figure 4.30 | P-1dB of RF front-end at high gain                  | 142 |

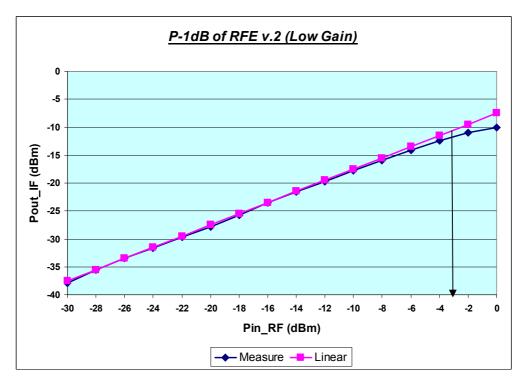

| Figure 4.31 | P-1dB of RF front-end at low gain                   | 142 |

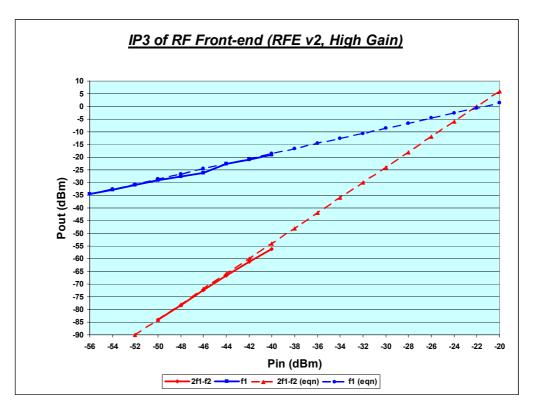

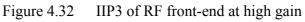

| Figure 4.32 | IIP3 of RF front-end at high gain                   | 143 |

| Figure 4.33 | IIP3 of RF front-end at low gain                    | 143 |

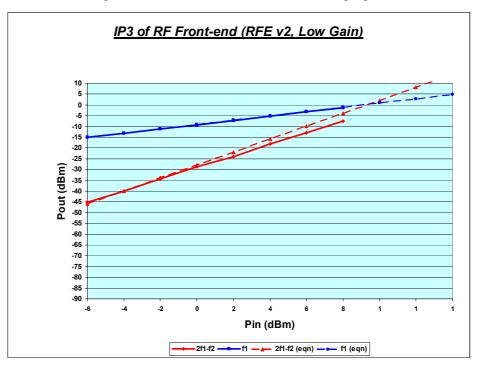

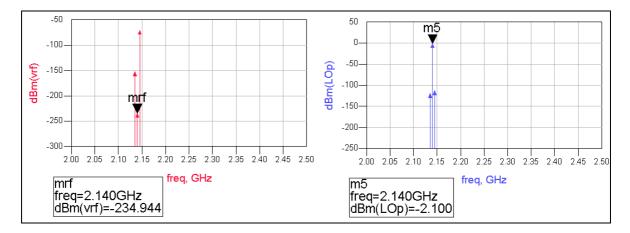

| Figure 4.34 | IIP2 of RF front-end at high gain                   | 144 |

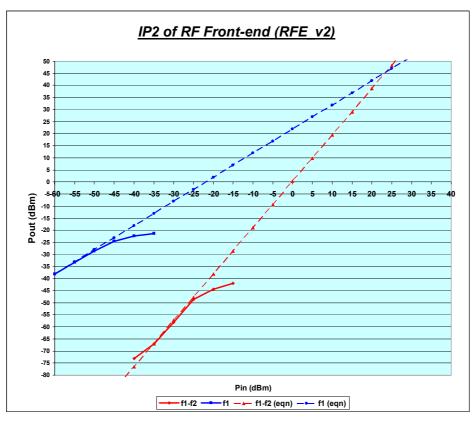

| Figure 4.35 | LO-RF isolation of RF front-end at high gain        | 144 |

## List of Abbreviations

| GSM    | Global System of Mobile Communication       |

|--------|---------------------------------------------|

| CDMA   | Code-Division Multiple Access               |

| WLAN   | Wireless Local Area Network                 |

| W-CDMA | Wideband Code-Division Multiple Access      |

| GPS    | Global Positioning System                   |

| РСВ    | Printed Circuit Board                       |

| IC     | Integrated Circuit                          |

| BiCMOS | Bipolar – Complementary Metal Oxide Silicon |

| CMOS   | Complementary Metal Oxide Silicon           |

| BJT    | Bipolar Junction Transistor                 |

| RF     | Radio Frequency                             |

| DCR    | Direct Conversion Receiver                  |

| LO     | Local Oscillator                            |

| DSP    | Digital Signal Processor                    |

| LNA    | Low Noise Amplifier                         |

| MIX    | Down-Conversion Mixer                       |

| 3G     | Third Generation                            |

| 2G     | Second Generation                           |

| DS-SS  | Direct-Sequence Spread Spectrum             |

| FDD    | Frequency-Division Duplexing                |

|        |                                             |

- UMTS Universal Mobile Telecommunication System

- 3GPP 3<sup>rd</sup>- Generation Partnership Project

- BPSK Binary Phase Shift Keying

- QPSK Quadrature Phase Shift Keying

- IF Intermediate Frequency

- SAW Surface Acoustic Wave

- BOM Bill of Materials

- DC Direct Current

- FSK Frequency Shift Keying

- BER Bit-Error Rate

- TDMA Time-Division Multiple Access

- ETSI European Telecommunication System Institute

- GPRS General Packet Radio Service

- EDGE Enhanced Data Rates for GSM Evolution

- SiGe Silicon Germanium

- BPF Bandpass Filter

- SINAD Signal Power / (Noise Power + Distortion)

- ESD Electrostatic Discharge

- SOC Silicon-on-Chip

- MESFET Metal-Semiconductor Field Effect Transistor

# List of Symbols

| SNR                 | Signal-to-noise ratio                             |

|---------------------|---------------------------------------------------|

| NF                  | Noise figure                                      |

| F                   | Noise factor                                      |

| $F_{min}$           | Minimum noise factor                              |

| flo                 | Frequency at mixer's LO port                      |

| $f_{RF}$            | Frequency at mixer's RF input port                |

| $f_{IF}$            | Frequency at mixer's IF output port               |

| $L_{e\!f\!f}$       | Effect channel length of MOS transistor           |

| HD2                 | Second-order harmonic distortion                  |

| HD3                 | Third-order harmonic distortion                   |

| IM2                 | Second-order intermodulation product              |

| IM3                 | Third-order intermodulation product               |

| IP2                 | The second-order intercept point                  |

| IIP2                | Input-referred second-order intercept point       |

| OIP2                | Output-referred second-order intercept point      |

| IP3                 | The third-order intercept point                   |

| IIP3                | Input referred third-order intercept point        |

| OIP3                | Output referred third-order intercept point       |

| P <sub>IIP3</sub>   | Input referred third-order intercept point in dBm |

| $P_{1dB}$           | 1-dB power compression point in dBm               |

| P <sub>in,min</sub> | Minimum input signal power to the receiver in dBm |

| $S_{11}$                   | Input reflection coefficient of S-parameter     |

|----------------------------|-------------------------------------------------|

| $S_{22}$                   | Output reflection coefficient of S-parameter    |

| $S_{21}$                   | Forward gain of S-parameter                     |

| $S_{12}$                   | Reverse isolation of S-parameter                |

| SFDR                       | Spurious-free dynamic range                     |

| $DR_{min}$                 | Minimum dynamic range required for the receiver |

| $g_m$                      | Transconductance                                |

| g <sub>m,sat</sub>         | Transconductance of transistor in saturation    |

| I <sub>d,sat</sub>         | Drain current of transistor in saturation       |

| W                          | Width of MOS transistor                         |

| $f_{\scriptscriptstyle T}$ | Unity-gain cutoff frequency                     |

| $\mathcal{O}_T$            | Unity-gain cutoff angular frequency             |

| $V_{od}$                   | Gate overdrive voltage                          |

| Vsat                       | Saturation velocity                             |

| $E_{sat}$                  | Velocity saturation field strength              |

| $\mu_{e\!f\!f}$            | Effective mobility                              |

| $\mu_o$                    | Low field mobility                              |

| θ                          | fitting parameter                               |

### Chapter 1 Introduction

#### 1.1 Motivation

A successful launch of cellular communication system, such as Global System of Mobile Communication in late 1980s, has ignited an explosive growth of the number of wireless services subscribers in recent years. From 1990s onward, many wireless services (e.g. CDMA, WLAN, HiperLAN, Bluetooth, etc.) were offered by telecommunication companies world wide to meet the strong consumer demand on portable terminals. The current trend of convergence among various technologies such as data communications and mobile communications into a single platform will greatly improve the capabilities of a wireless handset, however, this development will also increase the technical complexity of the wireless system. It can be foreseen that the strong consumers' demands on such multi-mode and multi-band wireless terminals, which are inclusive of short range applications (e.g. Bluetooth, WLAN, etc.) and long range mobile services (e.g. GSM, W-CDMA, GPS, etc.), will drive the developments of RF transceiver into smaller form factor, lower power consumption, and higher performance in all aspects.

In the past decade, wireless systems were realized by assembling different modules on to single printed circuit board. These modules usually consist of discrete passive components together with various integrated circuits. Because of different functionalities and technical challenges, the ICs for wireless communication systems are fabricated from different semiconductor technologies as shown in Figure 1.1. To build a cost effective transceiver for consumer markets, it is preferable to have all the circuits manufactured in the same semiconductor technology. Among the current semiconductor processes, BiCMOS technology is considered the most suitable process for meeting the technical challenges, however, higher manufacturing cost may not be a viable solution for the wireless devices targeted for consumer market. On the other hand, continuous improvement of the CMOS processes has provided an alternative way of achieving low cost single-chip solution for wireless transceiver. Although a standard CMOS process can increase the integration level with lower cost and avoid the interfacing and compatibility issue with the digital baseband circuit, the performance of CMOS circuits is still not very competitive to operate in radio frequency range due to inferior transconductance ( $g_m$ ) and lower unity-gain cut-off frequency ( $f_T$ ) than bipolar transistor. Hence, it is a challenge to implement the RF frontend circuit in CMOS technology.

Figure 1.1 The semiconductor technologies used in wireless transceiver modules

To meet the technical challenges mentioned above, the receiver architecture plays a crucial role in wireless system. Among receiver topologies, direct conversion receiver has the simplest structure and attains the highest integration level of receiver circuitry, it is also considered as one of the most promising solutions for the next generation wireless communication platform. However, the unique problems associated with the direct conversion receiver, such as dc offsets, leakages from local oscillator, etc., have limited the use of direct conversion receiver in highly demanding services (e.g. GSM and W-CDMA). The intense research efforts from academic communities and industrial players have shown encouraging results and great progress in the receiver design from system and circuit level respectively. It is believed that by combining the direct conversion receiver with the growing power of digital signal processing, the ultimate goal of having a single-chip solution for all wireless systems becomes realistic and achievable in the near future.

#### **1.2** Objectives of The Work

The main objectives of this project primarily focus on the development of low-power RF front-end circuits for an integrated CMOS direct conversion receiver, which will be targeted for the application of W-CDMA wireless communication system.

The design and realization of the RF front-end consist of two main circuits, namely, a low noise amplifier for providing signal amplification and a down-conversion mixer for frequency translation. The design goals of having low noise figure and achieving good linearity are essential to meet the technical requirements for the W-CDMA applications. Apart from these design goals, the integrated front-end circuits also need to have low dcoffset at the output of the mixer stage and provide sufficient gain to the received signal before signal processing in the subsequent stages.

All the circuit blocks are developed and implemented with CMOS technology, so that the front-end circuits can be further integrated with other RF, mixed-signal and digital baseband circuits to alleviate the issues of interface and compatibility among different process technologies.

#### **1.3** Thesis Outline

The presentation of this thesis is organized from the system level down to the circuit level, and then followed by the experimental results, discussion and conclusion. The thesis is divided into five chapters.

After the introductory chapter on the project scope and objectives, an overview of a W-CDMA communication system is presented in Chapter 2. The unique properties and technical requirements of W-CDMA system are highlighted. This chapter also covers the basics of receiver architecture, followed by the introduction of the direct conversion receiver for the W-CDMA system and its advantages and disadvantages as a radio frequency wireless receiver. The second part of the chapter focuses on the analysis and

system planning of the proposed DCR architecture. Finally, the design goals of RF frontend circuits for the W-CDMA receiver are derived.

In Chapter 3, the technical challenges of the RF circuits and the design considerations of the respective circuits are presented. In the second section, the design equations for the circuit topologies are derived and a detailed discussion on the implementation issues of LNA and mixer is presented. In the last section of Chapter 3, the design of the integrated RF front-end circuit is introduced.

Chapter 4 contains the details of IC implementation of the LNA and mixer, and then the experimental results of the chipset and integrated version of RF front-end design are shown and discussed. All the designs are implemented using a CMOS 0.35µm technology.

In the final chapter, the conclusion of this work is presented and the recommendations for future work are given.

### Chapter 2 RF System for W-CDMA Applications

#### 2.1 Overview of W-CDMA System

The communication protocol of wideband code-division multiple access technology for the third generation cellular network was officially adopted in 1999 [49]. Comparing with the current second generation GSM system, the W-CDMA system provides higher subscriber capacity and enhanced capability in handling mobile data communication, where the data rate can be as high as 2 Mbps [1]. During the high speed data communication, wider channel bandwidth is required for signal transmission and maintaining good signal quality. For W-CDMA technology, the efficient utilization of valuable communication bandwidth is achieved by using a direct-sequence spread spectrum technique, coupled with the code division multiple access method for baseband signal processing. This kind of system not only increases the capacity of wireless subscribers, it also offers strong resistance to interferences and jamming signals under the same signal condition as GSM. By randomly spreading the data stream, the transmitted signal can be recovered by de-spreading the received signal back from the level as low as noise floor [1], [2].

The operating frequencies of W-CDMA handset range from  $1920 \sim 1980$  MHz for the uplink communication (from handset to base station) and  $2110 \sim 2170$  MHz for the downlink communication (from base station to handset). The communication bandwidth is

60 MHz for transmit and receive respectively. Since W-CDMA performs full duplex communication, the minimum frequency gap of 30 MHz between the transmit signal and receive signal become very essential to the performance. With such a frequency gap, the technical requirements of the transceiver design can be relaxed by having a bandpass filter to isolate the receiver and transmitter from signal leakage. In the W-CDMA system, there are twelve channels and each channel occupies about 5 MHz. Since the channel bandwidth is much wider than GSM (i.e. 200 kHz), it is relatively easier to implement the direct conversion receiver architecture because a fractional loss of information caused by the dc-offset at baseband frequencies does not degrade the performance significantly.

Some key performance characteristics of band I of W-CDMA Universal Mobile Telecommunication System – Frequency Division Duplex mode are summarized in Table 2.1. The details of the technical specifications on wireless transmission and reception can be found in the document written by the 3<sup>rd</sup>-Generation Partnership Project group [3]:

| Parameter                 | Specification           | Unit          |

|---------------------------|-------------------------|---------------|

| Uplink frequency          | 1920 ~ 1980             | MHz           |

| Downlink frequency        | 2110~2170               | MHz           |

| Nominal channel spacing   | $5 \pm 0.2$             | MHz           |

| Chip rate                 | 3.84 (or 4.096)         | Mcps          |

| Data rate                 | 32/64/128/256/1024/2048 | Kbps          |

| Channel bandwidth         | 5/10/20                 | MHz / channel |

| Modulation: Uplink        | BPSK                    |               |

| Downlink                  | QPSK                    |               |

| Multiple access technique | DS-CDMA                 |               |

| Duplex procedure          | FDD                     |               |

| Maximum output power      | 24 (average)            | dBm           |

Table 2.1System characteristics of WCDMA UMTS – FDD mode

#### 2.2 Receiver Architectures for Wireless Applications

In general, there are three categories of RF receivers used in wireless communication industry based on the bandwidth of intermediate frequency before the demodulation process takes place [4], [5]. All the receiver architectures have their advantages and disadvantages in terms of integration level, power consumption and technical performance. Among RF wireless receivers, the most common form is "superheterodyne" which is invented by E. Armstrong in 1918. As shown in Figure 2.1, this receiver utilizes multiple frequency translations and signal amplifications to improve the received signal-to-noise ratio before the baseband signal processing. By using multiple amplifiers and filters for boosting the signal level and rejecting the interferences, the superheterodyne receiver can achieve superior performance in terms of sensitivity and selectivity. However, these advantages are mainly achieved by implementing many bulky and expensive off-chip filters, for example, the surface acoustic wave filter is used for image rejection and the crystal filter is used for channel selection. These filters limit the integration level of this architecture and increase the cost and the bill of material of the receiver.

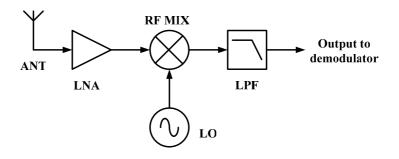

To realize a cost effective solution for wireless handsets, the research direction of RF receiver in recent years is to improve the integration level of the receiver. The simplest approach is to make only one signal down-conversion in the receiver (Figure 2.2), which is also called "homodyne" or "direct conversion" receiver [4] - [7]. The single conversion

architecture is suitable for implementation in the form of integrated circuit because no offchip filters are required, however, the technical challenges like dc-offset, self-mixing, LO leakage, etc. have deterred the use of this architecture in many stringent applications.

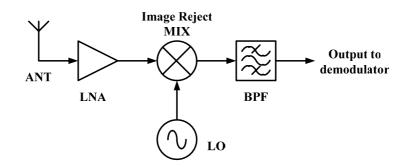

Another method (Figure 2.3) of increasing the integration level and avoiding the problems associated with direct conversion receiver is to down-convert the received signal to a very low intermediate frequency ("low-IF"), which is usually in the range of 1 kHz to 10 MHz, and then the low-IF signal is processed digitally [8]. Although dc-offset is not a critical issue in this design, the image frequency may become a serious problem. To overcome this problem, a highly symmetrical image-reject RF mixer is necessary. It is required to ensure that the cancellation of the image signal is substantial without degrading the sensitivity of the receiver (>50 dB rejection in some applications). Since the multi-path mismatches in the circuit layout cannot be completely removed, the image rejection is always limited to  $30 \sim 40$  dB for a CMOS low-IF receiver. This image frequency problem can be alleviated to a certain degree by moving the image-reject operation to lower frequency range rather than at RF frequency, as proposed in [9]. By using the "wideband-IF" receiver approach as shown in Figure 2.4, the received signal is down-converted twice, image-reject mixer is located after the IF1. As long as IF1 is chosen wide enough, the image rejection can be more effective by trading off higher power consumption with the high frequency active filters.

Figure 2.1 Building blocks of superheterodyne receiver

Figure 2.2 Building blocks of direct conversion receiver

Figure 2.3 Building blocks of low-IF single conversion receiver

Figure 2.4 Building blocks of wideband IF double conversion receiver

#### **2.3 Direct Conversion Receivers**

The direct conversion receiver has a very simple architecture as shown in Figure 2.2, a modulated signal only requires signal down-conversion before demodulation and baseband signal processing. Since the  $f_{LO}$  is exactly the same as the received carrier  $f_{RF}$ , no  $f_{IF}$  will be produced, i.e.  $f_{IF} = 0$ , and the down-converted signal will be centered at 0 Hz. In the low frequency regime, the construction of an active filter is simpler and the rejection of unwanted out-of-band signals accompanied with the RF carrier during the down-conversion process is higher. Theoretically, no image frequency will be observed at the mixer output if the I/Q-path shows a good symmetrical property. In fact, the requirement of the image rejection ratio for the DCR is less stringent (> 25 dB) than the requirement for low-IF receiver (> 50 dB) [10].

#### 2.3.1 Issues Associated with Direct Conversion Receivers

Although the direct conversion receiver offers many advantages such as smaller die area, lower count of off-chip components and lesser power consumption, some problems associated with DCR implementation are still quite challenging to tackle [6], [7]. These inherent problems of DCR are listed below:

- DC-offset after the signal down-conversion

- LO leakage and radiation

- Self-mixing of leaked LO or RF signal

- The impact of flicker noise to output SNR

- Intermodulation products from second-order nonlinearity

The origins of these issues are discussed in detail in the following sections.

#### 2.3.1.1 DC Offsets

In a direct conversion receiver, the RF modulated signal is directly down-converted to baseband after the mixer. Since the down-converted signal is centered at *0 Hz*, the baseband signal is subjected to the disturbance of dc operating point or "dc-offset" at the mixer output. There are many factors contributing to the dc-offsets, the major root causes are from circuit imperfections, for example an asymmetric differential circuit, mismatches of active or passive components, self-mixing of LO or RF leakage signals, even-order distortion of nonlinear active components, etc.

From the origins of dc-offsets, it can be categorized into two types, which are based on the time-varying nature of the offset.

#### Type I: Static DC-Offsets

These types of discrepancies usually result from the components' mismatches or multipath errors, the offsets are usually time-invariant. The circuit solutions to these problems have been discussed in many references [4] – [7]. Basically, these can be categorized into the following approaches:

- (a) ac coupling

- (b) high-pass filtering;

- (c) dc-calibration method;

- (d) dc-cancellation method.

The feasibilities and effectiveness of these solutions strongly depend on the modulation scheme applying to the received signal. When the modulation scheme has no information content at dc, e.g. frequency shift keying, the solutions have less impact to the degradation of bit-error rate after the baseband signal processing. If the baseband signal happens to fall exactly on 0 Hz, some information loss is unavoidable when method (a) and (b) are implemented. The ac-coupling and high-pass filtering will result finite response time and will cause significant loss in data frame of time-division multiple access system [4], [5]. The method (c) and (d) rely on the servo feedback mechanism to perform one-time or real-time dc-offset removal. Special attention needs to be taken when implementing the feedback circuits, so that the stability and the settling time can meet the timing requirements of the application [5].

#### Type II: Dynamic DC-Offsets

Aside from the static dc-offsets mentioned above, there is another scenario, which will generate time-variant dc-offset. This scenario arises from the finite isolation between the LO-port and RF-port in the receiver IC. When the leakage happens either from LO-to-RF port or from RF-to-LO port coupled with the nonlinearity of active devices as shown in Figure 2.5, the dynamic dc-offset will be produced at the mixer outputs due to self-mixing

of the signal and its own replica. This kind of time-varying dc-offset is difficult to be removed completely by any offset cancellation schemes.

The mechanism of the leakage signal can be illustrated in the following sections:

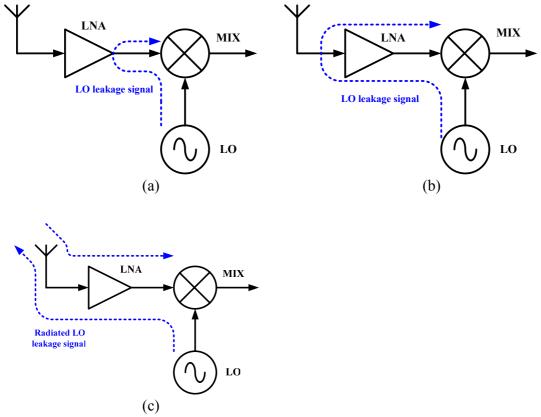

#### (a) LO – RF leakage

The LO – RF leakage mechanisms are illustrated in Figure 2.5. When the reverse isolation between the RF-port and LO-port is not high enough, the strong LO signal may leak to the RF front-end circuits. The LO leakage will be reflected whenever there is a mismatch of impedances between the interface of LNA and mixer (Figure 2.5 (a)) or between the interface of antenna and LNA (Figure 2.5 (b)). After the reflection, the LO leakage signal will travel to the RF-port of down-converter and mix with the actual LO signal, dc-offset is then produced at the output. There is another circumstance when the LO leakage radiate through the antenna and then reflects back by the nearby obstacle as shown in Figure 2.5 (c). This reflected wave is then received by the antenna and amplified by the LNA before mixing. Since the reflected wave by the obstacle may result in a change of the phase in the LO signal, the dc-offset caused by the self-mixing of radiated LO signal will also distort the phase information at the baseband.

Figure 2.5 The mechanism of self-mixing due to LO - RF leakage. (a) Self-mixing due to reflected wave of LO - RF leakage from LNA output (b) Self-mixing due to reflected wave of LO - RF leakage from antenna port (c) Self-mixing due to receiving of radiated LO signal.

The mathematical formulation of these mechanisms is presented below. Assume that the modulated RF carrier signal (both amplitude and phase) and the LO signal are represented by  $V_{RF}(t) = A_{RF}(t)\cos(\omega_c t + \theta(t))$  and  $V_{LO}(t) = A_{LO}\cos(\omega_o t)$  respectively. The reflected wave of LO – RF leakage which suffers from phase delay,  $\alpha$ , can be represented by  $V_{LO\_leak}(t) = A_{LO\_leak}\cos(\omega_o t + \alpha)$ .

During the mixing process, the following frequency components are produced:

$$\begin{split} &\left[V_{RF}(t) + V_{LO\_leak}(t)\right] \times V_{LO}(t) \\ &= \left\{A_{RF}(t)\cos(\omega_{c}t + \theta(t)) + A_{LO\_leak}\cos(\omega_{o}t + \alpha)\right\} \times A_{LO}\cos(\omega_{o}t) \\ &= \frac{A_{RF}(t)A_{LO}}{2}\cos[(\omega_{c} - \omega_{o})t + \theta(t)] + \frac{A_{RF}A_{LO}}{2}\cos[(\omega_{c} + \omega_{o})t + \theta(t)] \\ &+ \frac{A_{LO\_leak}A_{LO}}{2}\cos(\alpha) + \frac{A_{LO\_leak}A_{LO}}{2}\left[\cos(2\omega_{o}t) + \alpha\right] \end{split}$$

(2.1)

After the mixing, the low pass filter will reject the high frequency components of the baseband signal.

$$\begin{bmatrix} V_{RF}(t) + V_{LO\_leak}(t) \end{bmatrix} \times V_{LO}(t)$$

$$\approx \underbrace{\frac{A_{RF}(t)A_{LO}}{2} \cos[(\omega_c - \omega_o)t + \theta(t)]}_{wanted signal} + \underbrace{\frac{A_{LO\_leak}A_{LO}}{2} \cos(\alpha)}_{unwanted dc \text{ component}}$$

(2.2)

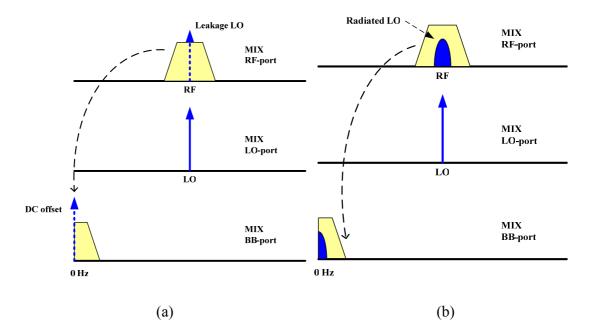

The self-mixing of the reflected LO - RF leakage and the LO produces a dc-offset voltage at the mixer output as shown in Figure 2.6. The level of the dc offset is proportional to the product of the LO signal strength and its leakage. This offset may degrade the receiver performance because the offset voltage level is sometimes stronger than the received signal.

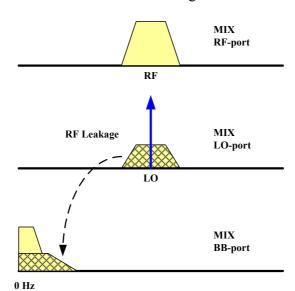

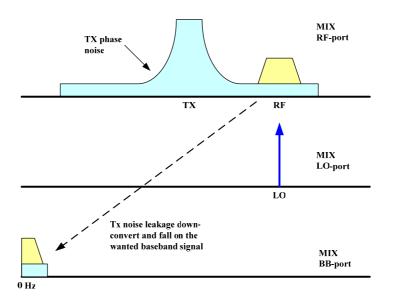

Figure 2.6 The simplified spectrum diagram of RF - LO leakage. (a) LO signal leaks to RF-port of mixer and then down-convert to baseband. (b) The reflected LO signal is received by its own antenna and then down-convert to baseband.

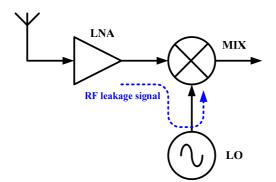

#### (b) RF – LO leakage

Another leakage mechanism occurs from the RF–port to LO–port. This is seldom mentioned in the publications but it has a more damaging impact on the demodulation. The self-mixing of the RF signals due to RF - LO leakage happens when the amplified carrier signal after the LNA leaks to the LO-port and then reflects back and mixes with the carrier signal itself. The mechanism is illustrated in Figure 2.7. Because of the time-varying nature of the modulated carrier wave, the offset produced by this mixing effect is always changing with time, furthermore, the offset signal is not a pure dc but has a frequency bandwidth of two times of the original signal. The overlapping of this down-converted interferer on the desired baseband signal can seriously affect the demodulation and degrade the *SNR* significantly.

Assume that the leakage of RF signal to the LO port suffers from amplitude variation and phase change:  $V_{RF\_leak}(t) = A_{RF\_leak}(t) \cos[\omega_c t + \alpha(t)]$

During the mixing process, the following frequency components are produced:

$$V_{RF}(t) \times \left[ V_{LO}(t) + V_{RF\_leak}(t) \right]$$

$$= A_{RF}(t) \cos\left[ \omega_c t + \theta(t) \right] \times \left\{ A_{LO} \cos(\omega_o t) + A_{RF\_leak}(t) \cos\left[ \omega_c t + \alpha(t) \right] \right\}$$

$$= \frac{A_{RF}(t) A_{LO}}{2} \left\{ \cos\left[ (\omega_c + \omega_o) t + \theta(t) \right] + \cos\left[ (\omega_c - \omega_o) t + \theta(t) \right] \right\}$$

$$+ \frac{A_{RF}(t) A_{RF\_leak}(t)}{2} \left\{ \cos\left[ 2\omega_c t + \theta(t) + \alpha(t) \right] + \cos\left[ \theta(t) + \alpha(t) \right] \right\}$$

(2.3)

After the mixing and following the low pass filter, high frequency components of the baseband signal are rejected.

$$V_{RF}(t) \times \left[ V_{LO}(t) + V_{RF\_leak}(t) \right] \approx \underbrace{\frac{A_{RF}(t)A_{LO}}{2} \cos[(\omega_c - \omega_o)t + \theta(t)]}_{wanted signal} + \underbrace{\frac{A_{RF}(t)A_{RF\_leak}(t)}{2} \cos[\theta(t) + \alpha(t)]}_{unwanted baseband signal}$$

(2.4)

The self-mixing of RF – LO leakage with the RF signal produces a time-varying modulated signal which falls into the baseband as shown in Figure 2.8. The bandwidth of this unwanted signal can be as large as twice the desired signal due to the multiplication of  $A_{RF}(t) A_{RF\_leak}(t)$ .

Figure 2.7 The mechanism of self-mixing due to RF leakage to LO port

Figure 2.8 The spectrum diagram of the self-mixing of RF – LO leakage

### 2.3.1.2 Flicker Noise

The direct conversion receiver has only one frequency translation to baseband, the *SNR* after the down-conversion may not be as good as the superheterodyne receiver or low-IF receiver, which has multiple gain stages for signal amplification and filtering. As a result, there is always an issue for the direct conversion receiver. Besides dealing with the dc-offset, it also needs to combat with the low frequency flicker noise overlapping on the desired baseband signal centered at 0 Hz.

The flicker noise effect is more obvious in CMOS process than in bipolar process. This low-frequency noise spectrum at the mixer output originates from the switching stage of the mixer and direct feedthrough of flicker noise from the driver stage during the imperfect switching among transistors. For short channel MOSFETs ( $L_{eff} < 1 \mu m$ ), the flicker noise can be significantly higher and the corner frequency can be as large as 1 MHz. This detrimental effect will degrade the *SNR* before the demodulation takes place. If the communication system has a narrow information bandwidth, the flicker noise can degrade the receiver performance considerably.

### 2.3.1.3 LO Leakage and Spurious Radiation

This is the problem unique to direct conversion receiver. Because of the same LO frequency and RF carrier frequency, the undesirable LO signal may leak through the frontend circuits and then radiate through the antenna as shown in Figure 2.5 (c). This radiated spurious signal will interfere with the nearby wireless handsets and disrupt the reception of the signal.

In order to pass the stringent type approval test specified in the ETSI document during the certification of the devices [3], this kind of electromagnetic interference needs to be sufficiently suppressed or shielded, so that the radiation level is controlled below a certain level. Another way of reducing the radiation is to improve the reverse isolation from the

LO to RF path, a low noise amplifier with good reserve isolation,  $S_{12}$ , can substantially reduce the LO leakage signal.

### 2.3.1.4 Intermodulation Products from Second-order Nonlinearity

In general, a receiver can only maintain as a linear system with limited range of input signal. The unwanted nonlinear products start to appear at the output of the system whenever the input signal becomes too large. Nonlinear products can also be generated because of the inherent nonlinear properties of active devices used in the receiver. The most important nonlinear frequency products include the harmonic components of the signal, *HD2* and *HD3*, which are generated from the distortion of one-tone input. There are other non-linear products as well, for example the second-order and third-order intermodulation products, *IM2* and *IM3*, which are generated by the two-tone inputs.

The harmonic distortion caused by gain compression of the system can be easily filtered off if the fundamental frequency is in the *GHz* range. However, the third-order intermodulation products from two-tone inputs ( $f_1$  and  $f_2$ ), such as  $(2 f_1 - f_2)$  and ( $f_1 - 2 f_2$ ) can occur at the frequencies too close to the desired operating frequency band, hence, the interferers cannot be filtered easily after the mixing because the required Q-factor of the filter is too high and it is difficult to be realized by integrated circuit. This problem has been well presented in the literature, the solutions include the pre-select filter for rejecting the interferers before mixing or improving the linearity of the system by selecting a proper biasing. In general, these effects can be characterized by *IIP3* and *OIP3* when designing the communication system.

For the second-order intermodulation products ( $|f_1 - f_2|$ ), there is usually not a serious issue whenever the system is fully differential. The symmetrical nature of the differential circuit can cancel the common-mode terms generated by the active devices, however, the rejection of the *IM2* products are far from infinite because of the imbalances of the devices introduced during the fabrication process. The *IM2* products are usually in the low frequency range and these can be easily filtered out by a bandpass filter after the mixer in superheterodyne receiver or low-IF receiver. However, this situation becomes problematic for the direct conversion receiver because the *IM2* product may coincide with the baseband and affect the receiver performance.

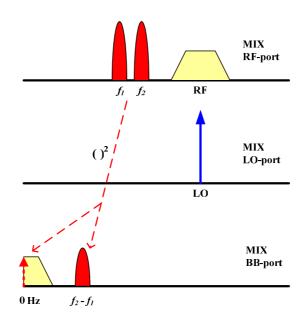

There are two scenarios that can generate the *IM2* products. In the case (I), the *IM2* products are produced by two strong and close-by blockers passing through the nonlinear mixer. Because of the nonlinear property of the mixer, the two blockers experience the second-order distortion and produce the unwanted dc component and low frequency beat at  $|f_1 - f_2|$ . All these unwanted components fall into the baseband and there will corrupt the desired signal as shown in Figure 2.9.

Figure 2.9 IM2 product from two-tone inputs

These effects can be modeled using Taylor series approximation:

$$y(t) = a_0 + a_1 x(t) + a_2 x^2(t) + a_3 x^2(t) + \cdots$$

(2.5)

where y(t) and x(t) represent the output signal and input signal of the system.

Neglecting the dc and higher order terms, the second-order distortion comes from the  $a_x x^2(t)$  term:

$$y(t) = a_2 x^2(t)$$

=  $a_2 \times A_{blk}^2 \left[ \cos(\omega_1 t) + \cos(\omega_2 t) \right]^2$

=  $a_2 A_{blk}^2 \left\{ 1 + \frac{1}{2} \left[ \cos(2\omega_1 t) + \cos(2\omega_2 t) \right] + \cos[(\omega_1 + \omega_2)t] + \cos[(\omega_1 - \omega_2)t] \right\}$  (2.6)

After the mixing and followed by the low pass filter, the high frequency components of the baseband signal are rejected:

$$y_{baseband}(t) \approx \underbrace{a_2 A_{blk}^2}_{unwanted \ dc} + \underbrace{a_2 A_{blk}^2 \cos[(\omega_1 - \omega_2)t]}_{unwanted \ baseband}$$

(2.7)

The unwanted *IM2* components fall into the baseband and there are not possible to be filtered by the channel select filter. To reduce the *IM2* effect, the mixer needs to be as linear as possible and maintain good symmetry. RF bandpass filter inserted in between the LNA and mixer also could help suppressing the blocker signals before mixing, hence the *IM2* products are much lower than the desired signal at the baseband.

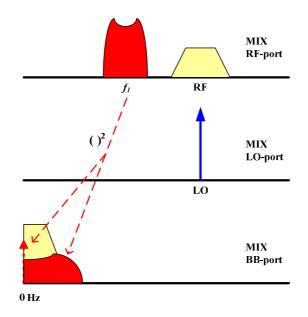

In the case (II), the unwanted baseband components are produced when a single-tone amplitude modulated blocker experiences the second-order distortion as shown in Figure 2.10 [11]. The mathematical analysis of this mechanism is shown below.

Assume that the single-tone blocker is represented by  $[1 + m(t)]A_{blk} \cos[\omega_{blk}t + \theta(t)]$ . From the simplified Taylor series shown in Equation 2.6,

$$y(t) = a_{2}x^{2}(t)$$

$$= a_{2} \times \{[1 + m(t)]A_{blk} \cdot \cos[\omega_{blk}t + \theta(t)]\}^{2}$$

$$= a_{2} \cdot [1 + m(t)]^{2} \cdot A_{blk}^{2} \cdot \left\{\frac{1}{2} + \frac{1}{2}[\cos(2\omega_{blk}t + 2\theta(t))]\right\}$$

(2.8)

Figure 2.10 Single blocker envelope distortion

After the mixing and followed by the low pass filter, the high frequency components of the baseband signal are rejected:

$$y_{baseband}(t) \approx \underbrace{\frac{1}{2}a_2 A_{blk}^2}_{unwanted \ dc} + \underbrace{\frac{1}{2}a_2 A_{blk}^2 \left[2m(t) + m^2(t)\right]}_{unwanted \ baseband}$$

(2.9)

The overlapping of the distortion products on the desired baseband can desensitize the receiver significantly.

# 2.4 Direct Conversion Receiver for W-CDMA System

### 2.4.1 Introduction

The recent demand of multi-mode (e.g. WLAN, GSM, GPRS, EDGE and W-CDMA) and multi-band (e.g. 900 MHz, 1.8 GHz and 2.14 GHz) handsets have changed the technology path projected by the wireless communication industry. The direct conversion receiver becomes the most promising solution to provide a common platform for different wireless applications. The advantages of the direct conversion receiver, such as simpler architecture and fewer number of off-chip components not only reduce the cost of a receiver but also allow different applications to coexist in the same receiver.

For narrowband applications, e.g. GSM, the implementation of the direct conversion receiver poses a very tough technical challenge for the circuit designers. The problems of dc-offset and flicker noise can dominate the receiver performance completely because fractional loss of signal content at baseband with dc-removal circuits may considerably affect the demodulation and decoding of the received signal. For W-CDMA application, the channel bandwidth is significantly wider than GSM, hence it is possible to implement the direct conversion receiver with a simpler dc-cancellation circuit. It is reported in [12], the dc notch filter with 2000 *Hz* cutoff frequency was realized to achieve the BER of  $10^{-6}$  for W-CDMA direct conversion receiver.

The direct conversion receiver is an active research area for recent years. Many researchers have focused on SiGe bipolar technology, which shown superior performance in RF front-end design, lower flicker noise and better device matching of bipolar transistors also improve the production yield, hence many reported direct conversion receivers for W-CDMA are related to SiGe processes [12]  $\sim$  [17]. CMOS technology started to receive the attention from the research community in the last three years, [18]  $\sim$  [19]. The improvement of processing power of digital baseband circuits can compensate some of the performance degradation originated from RF CMOS circuits.

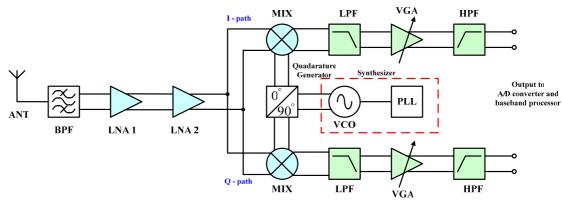

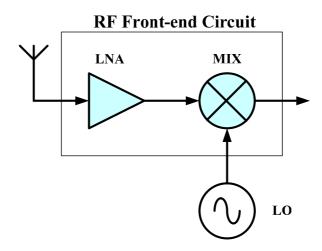

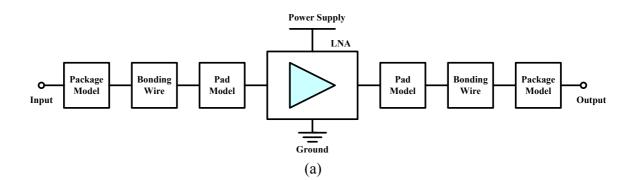

The typical block diagram of the direct conversion receiver is shown in Figure 2.11. Due to the project scope, only the RF front-end circuits, LNA and mixer, are discussed here.

Figure 2.11 Typical direct conversion receiver for WCDMA application

### 2.4.2 System Considerations of Front-end Design

For the direct conversion receiver, the front-end design is straightforward because only one down-conversion of signal is involved as shown in Figure 2.12. Such a simpler design does not offer good immunity to interference and always requires superior performance from LNA and mixer, hence it is not suitable for CMOS IC implementation.

Figure 2.12 Typical front-end design of direct conversion receiver

The front-end design of any communication systems always involves the trade-offs among different electrical parameters such as gain, noise figure and linearity under the constraint of power consumption. These design trade-offs are not easily achieved for cellular applications as the power consumption of the receiver keeps reducing. For a highly integrated receiver to meet the stringent design specifications, some off-chip components are used in commercial products to compensate the drawbacks of integrated circuits. The most common off-chip components include duplexer, T/R switch, passive balun, RF

bandpass filter, etc. These bulky off-chip components not only occupy large PCB area, they also increase the bill-of-material and the cost of the receiver. As a result, it is necessary to minimize the number of off-chip components used in the front-end design. In the following sections, some issues associated with the front-end design are discussed.

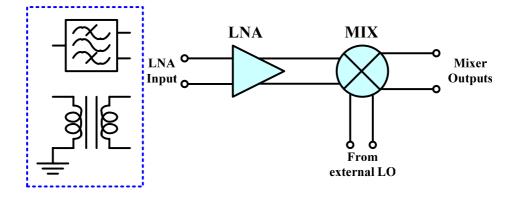

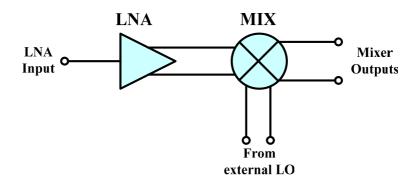

### 2.4.2.1 Single-ended Input vs. Differential Input

Differential circuits are always implemented in the receiver IC, so that better commonmode rejection can be achieved. However, the majority of the antennas implemented in the handset are monopole and single-ended, which is in contrast to the differential input of the receiver. The interface between antenna and differential low noise amplifier requires off-chip balun or RF bandpass filter as a device to perform single-to-differential conversion (Figure 2.13). Because of the passive nature of the balun (or filter), the loss incurred by this device will be directly converted to an increment of system noise figure.

Figure 2.13 Fully differential RF front-end design

To remove the off-chip balun, the function of single-to-differential conversion is incorporated into the LNA as shown in Figure 2.14. By choosing the single-ended LNA

design, the interface between antenna and LNA can be straightforward. However, the multi-path (I/Q-path) approach for signal processing in DCR will require the differential signal before the down-conversion mixer, hence a single-to-differential conversion circuit is added after the LNA to split the amplified signal into two 180° out-of-phase signals. It is a challenge to design such a circuit operating in RF because the amplitude imbalance and phase error in the circuit needs to be compensated carefully without further degrading the noise figure of the front-end circuits.

Figure 2.14 RF front-end with single-ended input

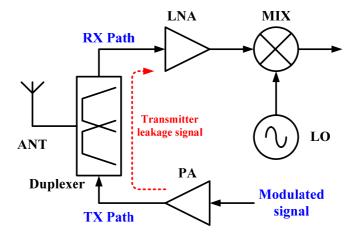

### 2.4.2.2 Reciprocal Mixing

In W-CDMA system, the receiver and transmitter are operating simultaneously to realize the full duplex communication. In order to avoid interference from each other, the received frequencies and transmitted frequencies occupy a different spectrum according to the frequency-division duplexing scheme. The minimum separation of these two frequency bands is 30 MHz. It can be seen from Figure 2.15 that an off-chip duplexer is necessary to isolate the receiver and transmitter, more than 40 dB of out-of-band rejection is needed for the received and transmitted signal in their respective operating frequency bands.

Figure 2.15 The typical front-end design of WCDMA transceiver

Although the duplexer can be used as the first level of isolation, the rejection of the transmit leakage may not be sufficient for the receiver because the strong leakage from transmitted signal may still appear at the receiver input through substrate coupling. This scenario is similar to the blocker test when a receiver faces desensitization the problem due to a strong nearby signal. If the far-out phase noise of the transmitted spectrum is too high, it may fall into the received band and seriously impact the demodulation after the mixing (Figure 2.16). This scenario is called "reciprocal mixing" [21] and it appears to be the most thorny issue in W-CDMA system.

The reciprocal mixing is very similar to the issue caused by the second-order nonlinearity discussed in the previous section. To alleviate the desensitization of the receiver due to the strong transmitted blocker signal, the mixer in a DCR needs to operate in a very linear

manner, hence the requirement of the input second-order intercept point could be very stringent, i.e. IIP2 > 60 dB [11]. It is a very challenging task to realize this design goal in CMOS due to the poor matching of sub-micron devices and low substrate isolation.

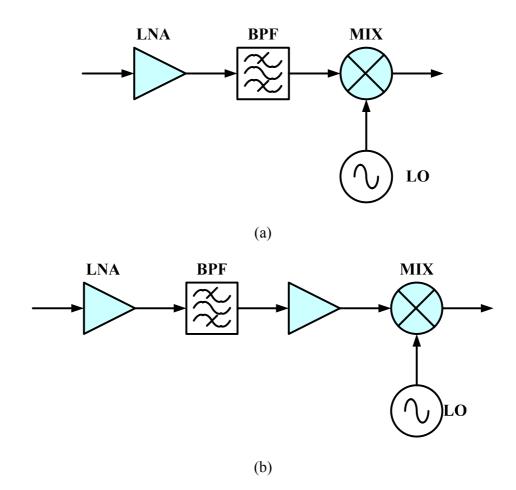

Figure 2.16 Strong blocker arisen from the leakage of transmitter signal The alternative way of relaxing the IIP2 requirement is to add a RF bandpass filter in between the LNA and mixer as shown in Figure 2.17 (a) for suppressing the blocker signal originated from the transmit leakage. Since the required Q-factor for this RF filter is more than 37 and need to achieve 40 dB of rejection at the transmit frequency range, it is very difficult to be realized on-chip, hence an off-chip SAW filter is usually selected. The disadvantage associated with this filter is an insertion loss, which would degrade the system noise figure and attenuate the passband signal level. To circumvent this issue, another RF amplifier is added after the BPF in Figure 2.17 (b) to amplify the received signal and improve the *SNR* before the mixer. The alternative solution is to increase the

LNA gain before the lossy filter but this would significantly degrade the linearity performance when the input signal is large.

Figure 2.17 An alternative way to reduce the effect of a strong out-of-band blocker

# 2.5 System Plan for Direct Conversion Receiver

System budgeting of the receiver is a very essential step to ensure the receiver complying with the technical requirement stated in ETSI documents [3]. In this section, the system requirements of direct conversion receiver for the W-CDMA are analyzed and the design targets are derived.

## 2.5.1 System Requirements of W-CDMA Receiver

The interpretation of the W-CDMA communication protocol and the conversion of the RF link budget into the system requirements of the receiver are not covered in this project. The reader can refer to publications [22] - [26] for the detailed derivations of system requirements on noise figure, adjacent channel selectivity, second-order intercept point, third-order intercept point, and image-rejection ratio. Table 2.2 summarizes the requirements for the W-CDMA receiver based on the research work reported in [22].

| Parameter                | Description            | Freq. Deviation<br>$(f_c \pm \Delta f)$ | Entire<br>Receiver | Unit |

|--------------------------|------------------------|-----------------------------------------|--------------------|------|

| Sens.                    | Reference sensitivity  | -                                       | -114               | dBm  |

| (SNR) <sub>out,min</sub> | Output SNR of receiver | -                                       | 7                  | dB   |

| $P_{in(max)}$            | Max. input level       | -                                       | -25                | dBm  |

| NF                       | Noise figure           | -                                       | ≤ 9                | dB   |

|                          | In-band Selectivity    |                                         |                    |      |

Table 2.2Summary of the system requirements of W-CDMA receiver

| $ACS_{(5MHZ)}$         | 1 <sup>st</sup> Adjacent Channel       | 5 MHz          | ≥ 33      | dB  |

|------------------------|----------------------------------------|----------------|-----------|-----|

| $ACS_{(CW)}$           | CW Interferer                          | 5 MHz          | ≥ 58      | dB  |

| ACS <sub>(15MHz)</sub> | 3 <sup>rd</sup> Adjacent Channel       | 15 MHz         | ≥ 58      | dB  |

| $ACS_{(20MHZ)}$        | Modulation Blocker                     | >15 MHz        | ≥ 58      | dB  |

|                        |                                        |                |           |     |

|                        | Intercept Point                        |                |           |     |

| $IIP2_{(10MHz)}$       | 2 <sup>nd</sup> -order Intercept Point | 10 MHz         | ≥-16      | dBm |

| $IIP2_{(15MHz)}$       | 2 <sup>nd</sup> -order Intercept Point | 15 MHz         | $\geq +8$ | dBm |

| $IIP2_{(TX)}$          | 2 <sup>nd</sup> -order Intercept Point | Tx             | ≥+47      | dBm |

| $IIP3_{(10/20MHz)}$    | 3 <sup>rd</sup> -order Intercept Point | 10/20 MHz      | ≥-17      | dBm |

| $IIP3_{(67/134MHz)}$   | 3 <sup>rd</sup> -order Intercept Point | 67.4/134.8 MHz | ≥ -8      | dBm |

|                        |                                        |                |           |     |

| IRR                    | Image Rejection Ratio                  | >85 MHz        | ≥ 84      | dB  |

|                        |                                        |                |           |     |

The different IIP2 and IIP3 requirements come from the in-band and out-of-band interferers specified in the type approval tests outlined in [3].

### 2.5.2 Gain Budget of Direct Conversion Receiver

To determine the front-end system requirements, the performance of baseband circuits are required. However, baseband designs are beyond the project scope, hence, the experimental results of baseband circuit listed in [2] is used as a reference for gain budgeting of the front-end design. The critical parameters used in the system calculation are listed in Table 2.3. It is assumed that a variable gain amplifier and a channel select filter are used in the receiver chain as shown in Figure 2.11. The variable gain amplifier provides the feature of automatic gain control when the input signal varies. Gain control is realized by the demodulator, which uses the analog-digital converter to monitor the output signal level. With the channel select filter, it is assumed that the out-of-band interferers will be fully suppressed without affecting the receiver performance.

| Parameter                   | Description                                  |        | Unit |

|-----------------------------|----------------------------------------------|--------|------|

| $G_{\scriptscriptstyle BB}$ | Voltage gain range                           | -9 +69 | dB   |

| $NF_{BB}$                   | Noise figure                                 | 27     | dB   |

| $IIP3_{BB}$                 | Input 3 <sup>rd</sup> -order intercept point | +14    | dBm  |

| $IIP2_{BB}$                 | Input 2 <sup>nd</sup> -order intercept point | +60    | dBm  |

Table 2.3Baseband (VGA and filter) performance reported in [2]

To obtain the design targets for the RF front-end circuit, a simpler hand calculation is performed here. From Table 2.2, the minimum dynamic range,  $DR_{min}$ , and minimum front-end gain,  $G_{RFE(min)}$ , are calculated as follows.

$$DR_{\min} = Max. Input Level - Reference Sensitivity$$

= -25 - ( -114)

= 89 (dB) (2.10)

$$G_{RFE(\min)} = DR_{\min} - G_{BB(\max)}$$

= 89 - 69 (2.11)

= 20 (dB)

To achieve the dynamic range of 89 dB, the minimum front-end gain must be greater than 20 dB. As discussed earlier, the number of high frequency gain stages for DCR is less than other receiver topologies, hence the *SNR* at the mixer output may not be sufficient for the baseband circuits. Although the VGA can provide higher gain for the downconverted signal to meet the input requirement of the ADC, this scenario is always accompanied by a large dc-offset seen by the ADC because the dc-offset produced by the mixing process will also be amplified. To circumvent this issue, the front-end gain for DCR needs to be as

high as possible. However, for front-end gain of more than 30 dB, the circuits may become unstable due to poor reverse isolation.

From Table 2.2, the total noise figure of the receiver cannot exceed 9 dB. Assuming 3 dB loss from the duplexer, the noise figure of the receiver IC must be below 6 dB. Although the minimum front-end gain is only 20 dB, another 3 dB is added to compensate for the signal loss at the duplexer. For the purpose of reliable operation, 3 dB of design margin is provided, hence 26 dB of gain is assigned to front-end circuits.

To obtain the required noise figure of the front-end circuit, Friss' formula expressed in Equation (2.12) is applied [21], [50].

$$F = F_1 + \frac{F_2 - 1}{G_1} + \frac{F_3 - 1}{G_1 \times G_2} + \dots + \frac{F_n - 1}{G_1 \times G_2 \times \dots \times G_{n-1}}$$

(2.12)

It is noted that all the variables in Friss' formula are dimensionless. The conversion of noise figure and gain in decibel to magnitude are shown in the following equations.

$$NF_{(dB)} = 10 \times \log(F) \Longrightarrow F = 10^{NF_{(dB)}/10}$$

(2.13)

$$G_{(dB)} = 10 \times \log(G) \Longrightarrow G = 10^{G_{(dB)}/10}$$

(2.14)

Since only three gain stages are involved, Equation (2.12) is simplified into Equation (2.15), where  $NF_{FE}$ ,  $F_{sys}$ ,  $F_{Duplexer}$ ,  $F_{FE}$ ,  $F_{BB}$ ,  $G_{Duplexer}$  and  $G_{FE}$  represent the front-end noise

figure, system noise factor, noise factor of duplexer, noise factor of front-end circuits, noise factor of baseband circuit, duplexer gain and front-end gain respectively.

$$F_{sys} = F_{Duplexer} + \frac{F_{FE} - 1}{G_{Duplexer}} + \frac{F_{BB} - 1}{G_{Duplexer} \times G_{FE}}$$

$$\Rightarrow F_{FE} = G_{Duplexer} \times \left(F_{sys} - F_{Duplexer} - \frac{F_{BB} - 1}{G_{Duplexer} \times G_{FE}}\right) + 1$$

$$\Rightarrow F_{FE} = 10^{-3/10} \times \left(10^{6/10} - 10^{3/10} - \frac{10^{27/10} - 1}{10^{-3/10} \times 10^{26/10}}\right) + 1$$

$$\Rightarrow F_{FE} = 2.725$$

(2.15)

$$NF_{FE} = 10 \times \log(F_{FE}) = 4.353$$

(dB) (2.16)

For the third-order intercept point, the following equation is used [50]. All the IIP3 terms described in the equation (2.17) are expressed in power (W):

$$\frac{1}{IIP3} = \frac{1}{IIP3_1} + \frac{G_1}{IIP3_2} + \frac{G_1 \times G_2}{IIP3_3} + \dots + \frac{G_1 \times G_2 \times \dots \times G_{n-1}}{IIP3_n}$$

(2.17)

$$IIP3_{(dBm)} = 10 \times \log(IIP3/0.001) \Longrightarrow IIP3 = 0.001 \times 10^{IIP3_{(dBm)}/10}$$

(2.18)

The general form of the *IIP3* equation can be modified into Equation (2.19). Here *IIP3*<sub>sys</sub>, *IIP3*<sub>Duplexer</sub>, *IIP3*<sub>FE</sub>,  $G_{Duplexer}$ , and  $G_{FE}$  represent the system *IIP3*, duplexer *IIP3*, *IIP3* of frontend circuit, gain of duplexer and front-end gain respectively. The calculated IIP3 for the front-end circuit is -19 dBm, however, 3 dB of design margin is added to cater for some process variations and inaccuracy of the calculation.

$$\frac{1}{IIP3_{sys}} = \frac{1}{IIP3_{Duplexer}} + \frac{G_{Duplexer}}{IIP3_{FE}} + \frac{G_{Duplexer}G_{FE}}{IIP3_{BB}}$$

$$\Rightarrow \frac{1}{IIP3_{FE}} = \frac{(IIP3_{sys})^{-1} - (IIP3_{Duplexer})^{-1} - G_{Duplexer}G_{FE} \cdot (IIP3_{BB})^{-1}}{G_{Duplexer}}$$

$$\Rightarrow \frac{1}{IIP3_{FE}} = \frac{10^{-IIP3_{sys}/10} - 10^{-IIP3_{Duplexer}/10} - (10^{G_{Duplexer}/10} \times 10^{G_{FE}/10} \times 10^{-IIP3_{BB}/10})}{10^{G_{Duplexer}/10}}$$

$$\Rightarrow \frac{1}{IIP3_{FE}} = \frac{10^{-17/10} - 10^{-\infty} - (10^{-3/10} \times 10^{26/10} \times 10^{-14/10})}{10^{-3/10}}$$

$$\Rightarrow \frac{1}{IIP3_{FE}} = 84151$$

$$\Rightarrow IIP3_{FE} = 1.188 \times 10^{-5}$$

$$IIP3_{FE} = 10 \times \log(IIP3_{FE} / 0.001) = -19.251 \text{ (dBm)}$$

(2.20)

The calculations of the system parameters are summarized in Table 2.4.

| Parameter | Duplexer | LNA + MIX | Filter + VGA | Total | Unit |

|-----------|----------|-----------|--------------|-------|------|

| Gain      | -3       | 26        | 69           | 89    | dB   |

| NF        | 3        | 4.4       | 27           | 6     | dB   |

| IIP3      | $\infty$ | -19.3     | 14           | -17   | dBm  |

Table 2.4The hand calculated receiver plan

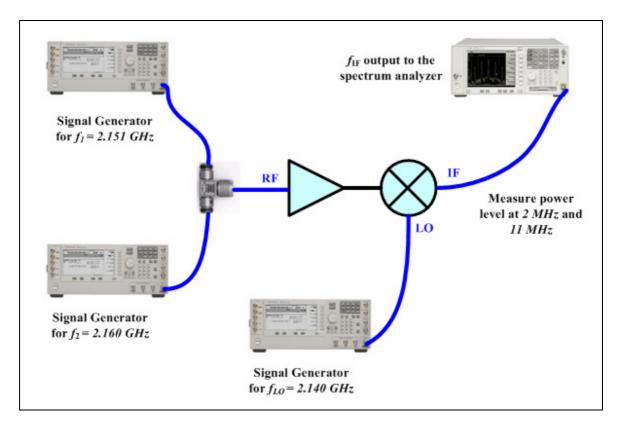

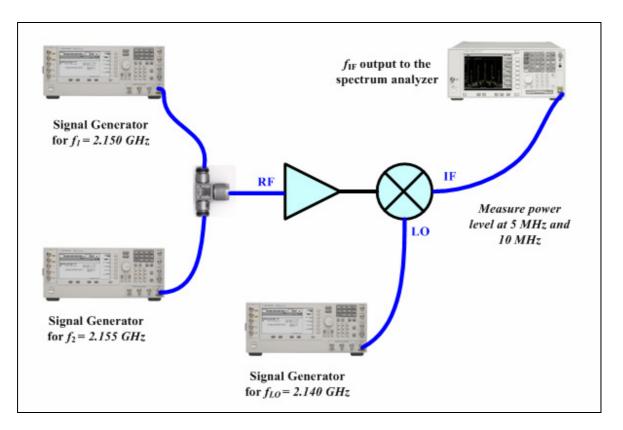

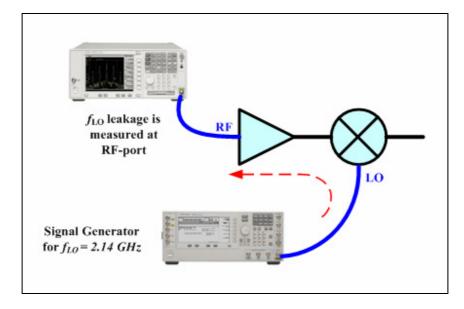

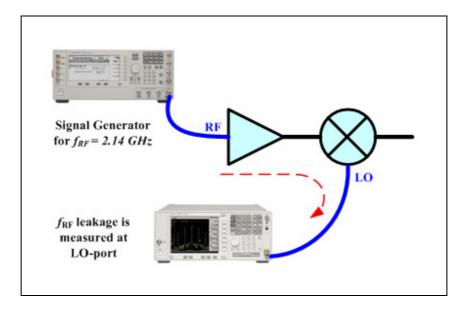

Table 2.4 shows the minimum requirements for the front-end circuit to meet the W-CDMA system requirement. To achieve better performance, more stringent design targets for the RF front-end are tabulated in Table 2.5.