### ADVANCED PROCESS AND EQUIPMENT CONTROL FOR THERMAL PROCESSING IN LITHOGRAPHY

WU XIAODONG (B.Eng., USTC)

#### A THESIS SUBMITTED

#### FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

### DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

NATIONAL UNIVERSITY OF SINGAPORE

2007

### Acknowledgments

I would first like to express my deepest gratitude to my supervisors Dr. Arthur Tay and Associate Professor Ho Weng Khuen for their support, guidance and encouragement during my graduate years in National University of Singapore. I thank them for their consistent involvements, suggestions, enlightenments and help in every detail of my research. Without their guidance, this work would not be possible. I thank them for their gracious understandings and supports on many aspects of life beyond research. I would also like to express my great gratitude to Associate Professor Hui Tong Chua from University of Western Australia and Dr. Chen Xiaoqi from Singapore Institute of Manufacturing Technology for their helpful insight, invaluable suggestion and comments on my research. I thank them for their detailed guidance at different stages of my research progress as well as their professional attitudes towards research. Without their suggestion and enlightenment, this work would not be what it is now.

I would like to thank Kiew Choon Meng for sharing precious ideas when doing the experiments. I thank members of our research group for their help and friendship. I thank all of you. You make all these years of experience in NUS and SimTech unforgettable. I thank Vathi for her support. I would like to thank my parents, Jinquan Wu and Xiezhen Zhou, for their unconditional love and support. I thank my brother Xiaoge Wu and his wife for their encouragement. Finally and most importantly, I declare my deepest debt of gratitude to my wife Yuemei He for her genuine understanding and encouragement. Without her love and companion, this thesis would not be possible. I look forward to spending more time with her. This degree is shared with her.

> Wu Xiaodong February, 2007

# Contents

| A             | ckno   | wledge | ments                                                          | i    |

|---------------|--------|--------|----------------------------------------------------------------|------|

| Sı            | umma   | ary    |                                                                | vi   |

| $\mathbf{Li}$ | ist of | Figure | 2S                                                             | xiii |

| $\mathbf{Li}$ | ist of | Tables | 5                                                              | xiv  |

| 1             | Intr   | oducti | on                                                             | 1    |

|               | 1.1    | Motiva | ation                                                          | 1    |

|               |        | 1.1.1  | Effects of resist property variation in lithography process    | 3    |

|               |        | 1.1.2  | Thermal effects in lithography process                         | 4    |

|               | 1.2    | Contri | bution                                                         | 5    |

|               |        | 1.2.1  | Real-time monitoring and control of photoresist extinction     |      |

|               |        |        | coefficient uniformity                                         | 6    |

|               |        | 1.2.2  | In-situ monitoring of photoresist thickness contour in lithog- |      |

|               |        |        | raphy                                                          | 7    |

|               |        | 1.2.3  | A lamp thermoelectricity based integrated bake/chill system    |      |

|               |        |        | for photoresist processing                                     | 7    |

|               | 1.3    | Organ  | ization                                                        | 8    |

| <b>2</b>      | Rea    | l-time | Control of Photoresist Extinction Coefficient Unifor-          |      |

|               | mit    | у      |                                                                | 10   |

|   | 2.1                                                                                                                             | Introduction                                                                                                                                                                                                                                                              | 10                                                                                             |

|---|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

|   | 2.2                                                                                                                             | Experimental setup                                                                                                                                                                                                                                                        | 12                                                                                             |

|   | 2.3                                                                                                                             | Photoresist extinction coefficient estimation                                                                                                                                                                                                                             | 15                                                                                             |

|   | 2.4                                                                                                                             | Control of photoresist extinction coefficient uniformity                                                                                                                                                                                                                  | 19                                                                                             |

|   | 2.5                                                                                                                             | Conclusion                                                                                                                                                                                                                                                                | 21                                                                                             |

| 3 | Pho                                                                                                                             | otoresist Extinction Coefficient and Thickness Estimation in                                                                                                                                                                                                              |                                                                                                |

|   | $\mathbf{the}$                                                                                                                  | Presence of Wafer Warpage                                                                                                                                                                                                                                                 | <b>24</b>                                                                                      |

|   | 3.1                                                                                                                             | Introduction                                                                                                                                                                                                                                                              | 24                                                                                             |

|   | 3.2                                                                                                                             | Experimental setup                                                                                                                                                                                                                                                        | 25                                                                                             |

|   | 3.3                                                                                                                             | Photoresist properties estimation                                                                                                                                                                                                                                         | 27                                                                                             |

|   | 3.4                                                                                                                             | Effect of warpage on photoresist properties estimation                                                                                                                                                                                                                    | 32                                                                                             |

|   | 3.5                                                                                                                             | In-situ detection of wafer warpage                                                                                                                                                                                                                                        | 35                                                                                             |

|   | 3.6                                                                                                                             | Conclusion                                                                                                                                                                                                                                                                | 38                                                                                             |

|   |                                                                                                                                 |                                                                                                                                                                                                                                                                           |                                                                                                |

| 4 | In-S                                                                                                                            | Situ Monitoring of Photoresist Thickness Contour in Lithogra-                                                                                                                                                                                                             |                                                                                                |

| 4 | In-S                                                                                                                            |                                                                                                                                                                                                                                                                           | 39                                                                                             |

| 4 |                                                                                                                                 |                                                                                                                                                                                                                                                                           |                                                                                                |

| 4 | phy                                                                                                                             |                                                                                                                                                                                                                                                                           | 39                                                                                             |

| 4 | <b>phy</b><br>4.1                                                                                                               | Introduction                                                                                                                                                                                                                                                              | <b>39</b><br>39<br>41                                                                          |

| 4 | <b>phy</b><br>4.1<br>4.2                                                                                                        | Introduction                                                                                                                                                                                                                                                              | <b>39</b><br>39<br>41                                                                          |

| 4 | <ul><li>phy</li><li>4.1</li><li>4.2</li><li>4.3</li></ul>                                                                       | Introduction                                                                                                                                                                                                                                                              | <ul> <li><b>39</b></li> <li>41</li> <li>43</li> <li>46</li> </ul>                              |

| 4 | <ul> <li>phy</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> </ul>                                                     | Introduction       Introduction         Experimental setup       Introduction         Reflection of light by moving medium       Introduction         Thickness estimation       Introduction                                                                             | <ul> <li><b>39</b></li> <li>39</li> <li>41</li> <li>43</li> <li>46</li> <li>48</li> </ul>      |

| 4 | <ul> <li>phy</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> </ul>                           | Introduction       Introduction         Experimental setup       Introduction         Reflection of light by moving medium       Introduction         Thickness estimation       Introduction         In-situ monitoring of thickness contour       Introduction          | <ul> <li>39</li> <li>39</li> <li>41</li> <li>43</li> <li>46</li> <li>48</li> <li>52</li> </ul> |

|   | <ul> <li>phy</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>A I</li> </ul>              | Introduction                                                                                                                                                                                                                                                              | <ul> <li>39</li> <li>39</li> <li>41</li> <li>43</li> <li>46</li> <li>48</li> <li>52</li> </ul> |

|   | <ul> <li>phy</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>A I</li> </ul>              | Introduction       Introduction         Experimental setup       Experimental setup         Reflection of light by moving medium       Introduction         Thickness estimation       Integrated Bake/chill System         Conclusion       Integrated Bake/chill System | <b>39</b><br>39<br>41<br>43<br>46<br>48<br>52                                                  |

|   | <ul> <li>phy</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>A I</li> <li>for</li> </ul> | Introduction                                                                                                                                                                                                                                                              | <b>39</b><br>39<br>41<br>43<br>46<br>48<br>52<br><b>54</b>                                     |

|    | 5.4   | Control and simulation results | 73 |

|----|-------|--------------------------------|----|

|    | 5.5   | Conclusion                     | 85 |

| 6  | Con   | clusions                       | 89 |

|    | 6.1   | Conclusions                    | 89 |

|    | 6.2   | Future work                    | 91 |

| Aι | ıthor | 's Publications                | 93 |

| Bi | bliog | raphy                          | 95 |

### Summary

Lithography is the key technology driver and "bottleneck" controlling the device scaling, circuit performance and magnitude of integration for silicon semiconductors. Critical dimension (CD) or linewidth is one the most critical variable in the lithography process with the most direct impact on the device speed and performance. During the lithography sequence, one important source of CD variation comes from variations in photoresist properties including extinction coefficient and thickness. It is important to achieve a uniform extinction coefficient and thickness profile across wafer. This can be achieved by integrating control system into the existing process like softbake process. Previous works in the literature can only control the average uniformity of the extinction coefficient. Using a spectrometer, a multi-zone bakeplate and simple PI control algorithms, the temperature distribution of a bakeplate is manipulated in real-time to reduce the variation of extinction coefficient within wafer and from wafer to wafer.

It is also important to ensure the uniformity of the photoresist thickness across the substrate. An in-situ photoresist thickness contour monitoring system is proposed and developed by integrating a spectrometer to acquire the photoresist thickness contour on the wafer during the spin-coating step or edge-bead removal step. The influence of wafer warpage on the resist properties estimation is also investigated.

The temperature non-uniformity in post-exposure bake (PEB) process also contributes to the final variation in CD. A design of an integrated bake/chill module for photoresist processing is then presented in the thesis, with an emphasis on the spatial and temporal temperature uniformity of the substrate. The system consists of multiple radiant heating zones for heating the substrate, coupled with an array of thermoelectric devices (TEDs) which provide real-time regulation of the substrate temperature. The feasibility of the proposed approach is demonstrated via detailed modelling and simulations based on first principle heat transfer analysis. Less than  $0.1^{\circ}C$  temperature non-uniformity is achieved across the wafer substrate during the whole cycle of heating and cooling process.

# List of Figures

| 1.1 | The typical lithography sequence including spin-coating, soft bake,    |    |

|-----|------------------------------------------------------------------------|----|

|     | exposure, post exposure bake, develop and post develop bake process.   | 2  |

| 1.2 | The conventional approach for lithography baking and chilling in-      |    |

|     | volves substrate transfer between large thermal mass, fixed temper-    |    |

|     | ature plates                                                           | 5  |

| 2.1 | Schematics of the experimental setup used to control resist extinc-    |    |

|     | tion coefficient. The system consists of three main parts: a multi-    |    |

|     | zone bakeplate, extinction coefficient sensors, and a computing unit.  | 12 |

| 2.2 | Photograph of the experimental setup                                   | 13 |

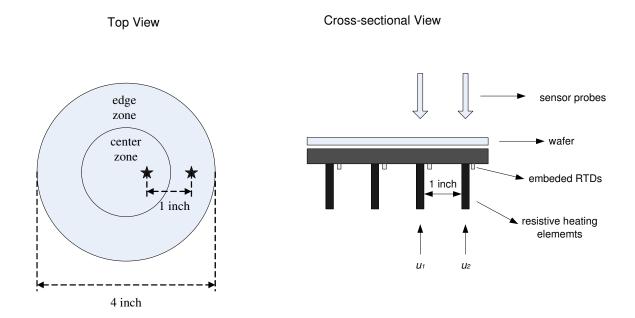

| 2.3 | Schematics of multizone bakeplate                                      | 14 |

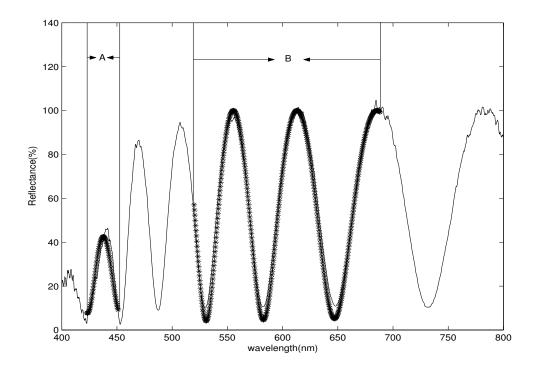

| 2.4 | Extraction of resist thickness and extinction coefficient using least  |    |

|     | square estimation: range A is used to estimate extinction coefficient, |    |

|     | while range B is used to estimate resist thickness. Solid line shows   |    |

|     | the experimental data while the '*'-line shows the theoretical fitted  |    |

|     | result.                                                                | 17 |

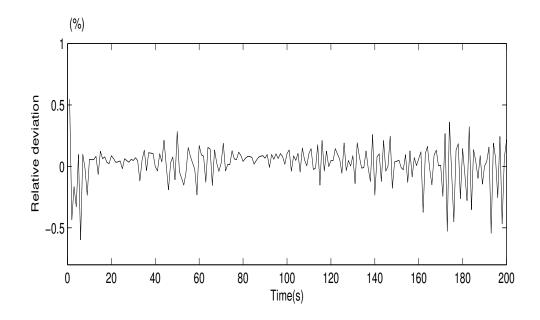

| 2.5 | Comparison of least square estimation and nonlinear curve fitting      |    |

|     | methods of estimating photoresist extinction coefficient               | 19 |

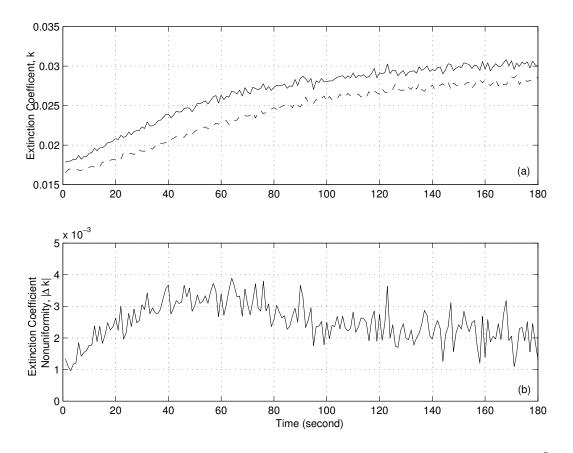

| 2.6 | Conventional softbake with bakeplate maintained uniformly at $90^{0}$ C:             |    |

|-----|--------------------------------------------------------------------------------------|----|

|     | (a) resist extinction coefficient, (b) resist extinction coefficient non-            |    |

|     | uniformity profile of the two sites monitored. Solid line represents                 |    |

|     | center zone of the wafer, while dashed line represents edge zone                     | 20 |

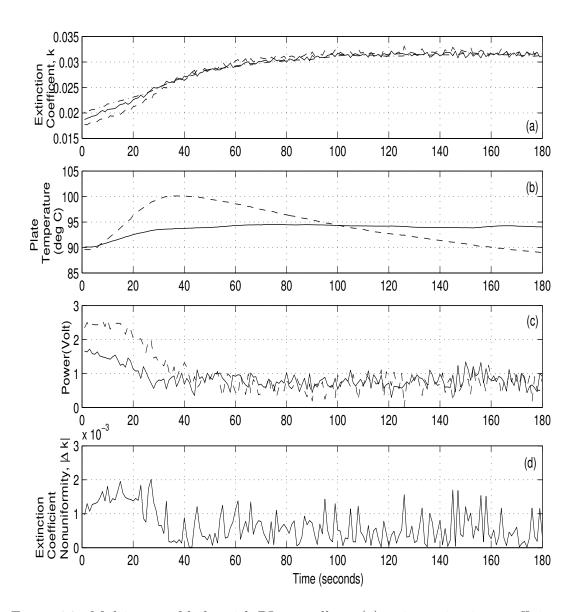

| 2.7 | Multizone softbake with PI controllers: (a) resist extinction coeffi-                |    |

|     | cient, (b) bake plate temperature, (c) heater power, (d) resist ex-                  |    |

|     | tinction coefficient non-uniformity profile of the two sites monitored.              |    |

|     | Solid line represents center zone of the wafer, while dashed line rep-               |    |

|     | resents edge zone. The reference extinction coefficient trajectory is                |    |

|     | given by the dash-dot line in plot (a). $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 22 |

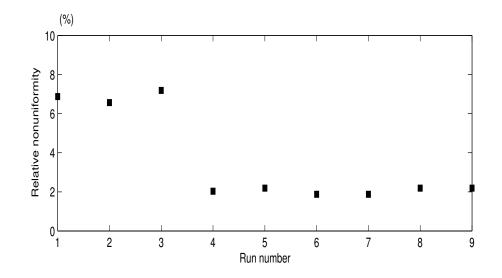

| 2.8 | Extinction coefficient non-uniformity comparison for different exper-                |    |

|     | imental runs. The first three runs are under the conventional bake,                  |    |

|     | while the next 6 runs are using the multizone bake with real-time                    |    |

|     | control                                                                              | 23 |

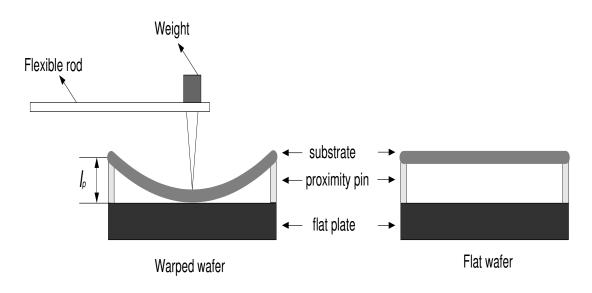

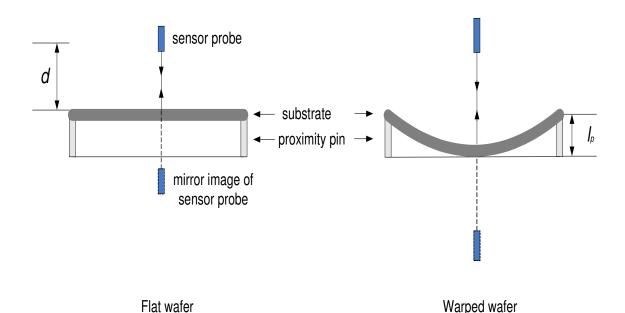

| 3.1 | Schematics of warped substrate and flat substrate                                    | 27 |

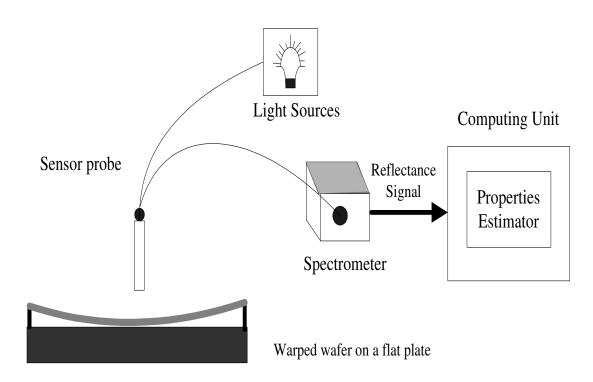

| 3.2 | Experimental setup, including warped wafer, reflectometer sensor,                    |    |

|     | and computing unit                                                                   | 28 |

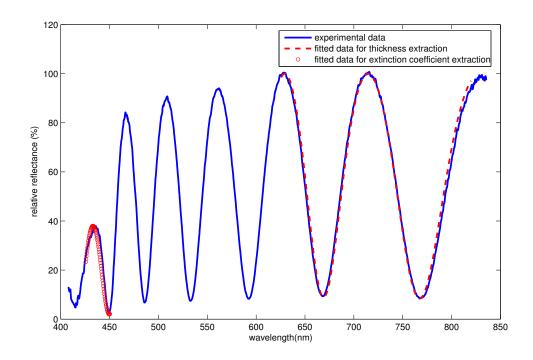

| 3.3 | Extraction of resist thickness and extinction coefficient for flat wafer:            |    |

|     | low wavelength range is used to estimate extinction coefficient, while               |    |

|     | high wavelength range is used to estimate resist thickness                           | 29 |

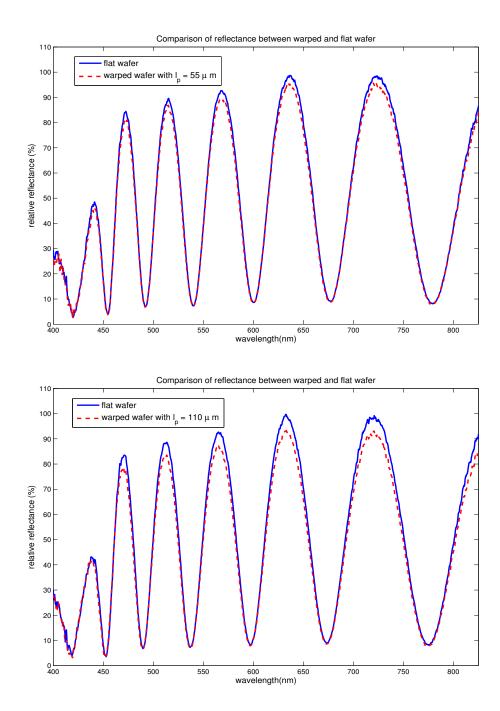

| 3.4 | Comparison of reflectance curve between flat wafer and warped                        |    |

|     | wafer. Wafer warpage $l_p = 55 \mu m$ and $l_p = 110 \mu m$ . The solid line         |    |

|     | is the reflectance curve for flat wafer, while the dash line is the one              |    |

|     | for warped wafer.                                                                    | 30 |

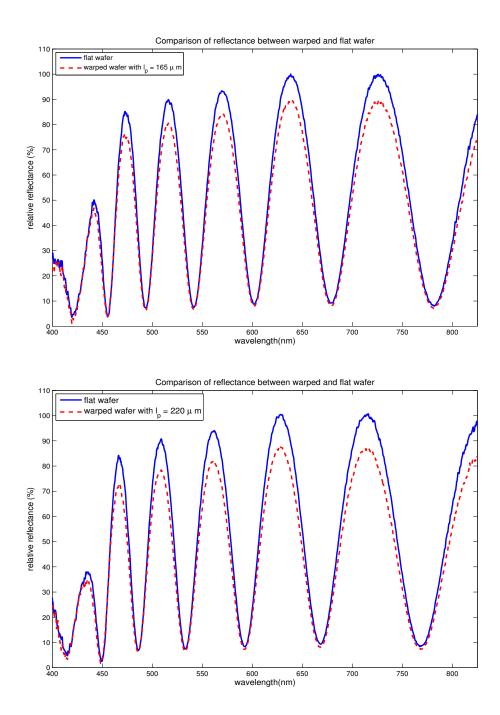

| 3.5 | Comparison of reflectance curve between flat wafer and warped                        |    |

|-----|--------------------------------------------------------------------------------------|----|

|     | wafer. Wafer warpage $l_p = 165 \mu m$ and $l_p = 220 \mu m$ . The solid             |    |

|     | line is the reflectance curve for flat wafer, while the dash line is the             |    |

|     | one for warped wafer                                                                 | 31 |

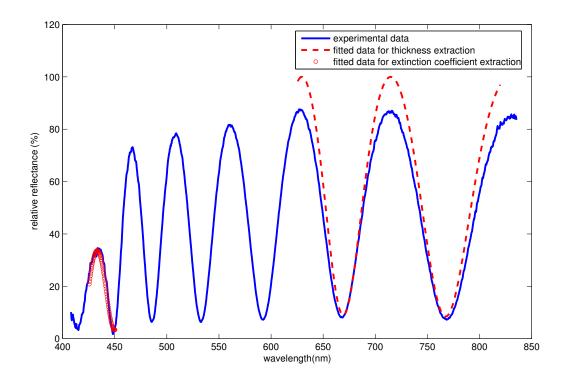

| 3.6 | Extraction of resist thickness and extinction coefficient for warped                 |    |

|     | wafer.                                                                               | 34 |

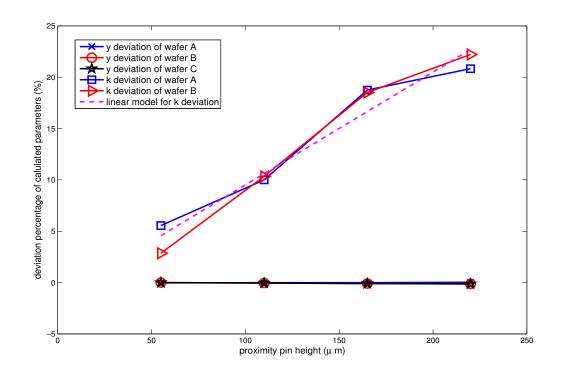

| 3.7 | Effect of wafer warpage on the thickness and extinction coefficient                  |    |

|     | estimation                                                                           | 35 |

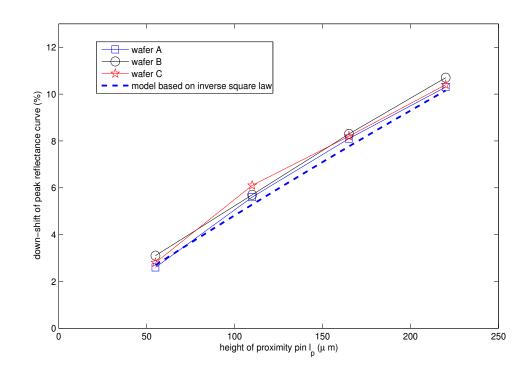

| 3.8 | Calculation of reflected light intensity deviation using inverse square              |    |

|     | law                                                                                  | 36 |

| 3.9 | Validation of light intensity deviation model with experimental data                 | 37 |

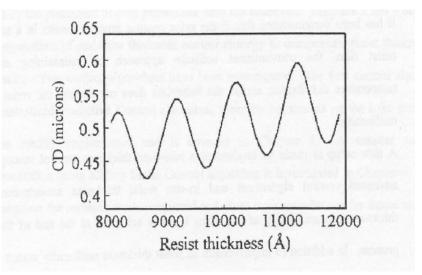

| 4.1 | Variation of CD with resist thickness                                                | 40 |

|     |                                                                                      | 40 |

| 4.2 | Experimental setup, including the X-Y table, spectrometer sensor,                    | 10 |

|     | and computing unit                                                                   | 42 |

| 4.3 | The experimental setup for photoresist thickness contour monitoring                  | 43 |

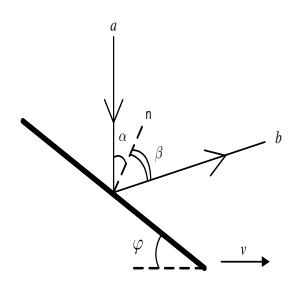

| 4.4 | The geometry of the problem. The plate is moving at a constant                       |    |

|     | speed of v. a is the incident light, with a angle of $\alpha$ . b is the reflected   |    |

|     | light, with a angle of $\beta$                                                       | 44 |

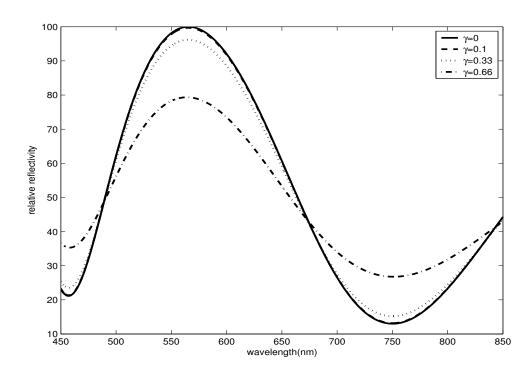

| 4.5 | The influence of moving speed to the spectral reflectivity curve.                    |    |

|     | $\gamma = \frac{v}{c}$ where v is the speed of moving plate and c the speed of light |    |

|     | in the air.                                                                          | 45 |

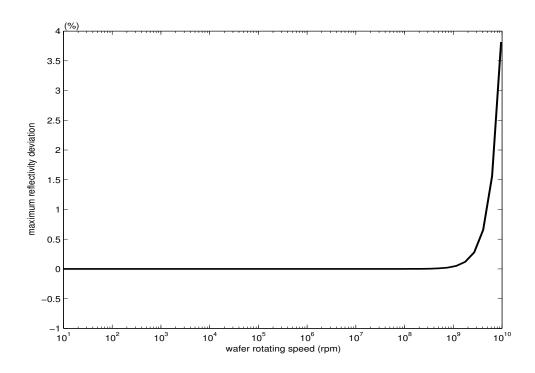

| 4.6 | The calculated maximum reflectivity deviation in the spectrum of                     |    |

|     | 450-850nm corresponding to different wafer rotating speed.(The in-                   |    |

|     | cident light is normal to the wafer edge surface.)                                   | 46 |

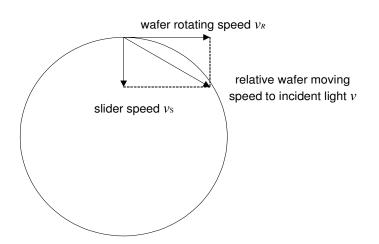

| 4.7 | Calculation of relative wafer moving speed corresponding to incident                 |    |

|     | light based on wafer rotating and sensor probe sliding                               | 47 |

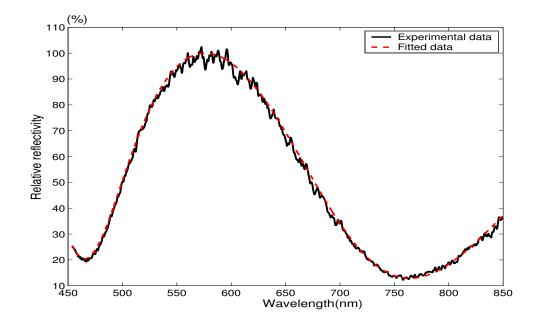

| 4.8  | Fitting of experimental data with optical model. Solid line is the        |    |

|------|---------------------------------------------------------------------------|----|

|      | experimental data, while dash line is the theoretical data based on       |    |

|      | model                                                                     | 48 |

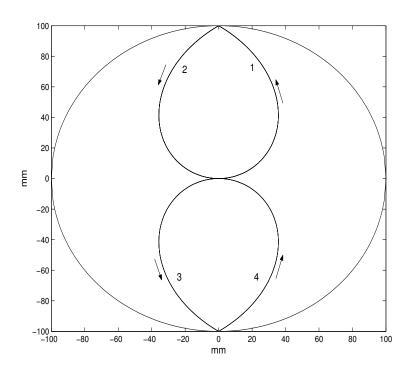

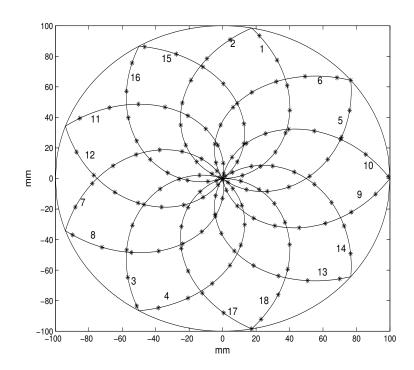

| 4.9  | In the course of wafer rotating, the slider will also travel from origin  |    |

|      | to edge and reverse. This figure shows the actual sensor travelling       |    |

|      | trajectory on a 200mm wafer with a speed ratio of $\eta = 4$              | 49 |

| 4.10 | In the course of wafer rotating, the slider will also travel from origin  |    |

|      | to edge and reverse. This figures shows the actual sensor travel-         |    |

|      | ling trajectory on a 200mm wafer with a speed ratio of $\eta = 4.5$ .     |    |

|      | Thicknesses are measured at the positions marked by "*"                   | 50 |

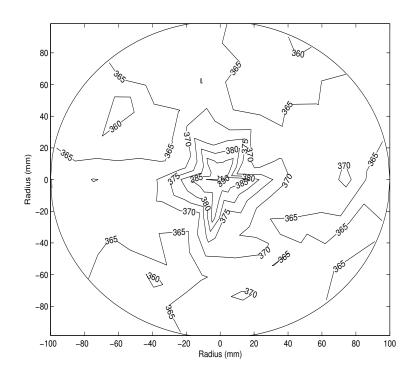

| 4.11 | Resist thickness contour based on thickness measurements $\ldots$ .       | 51 |

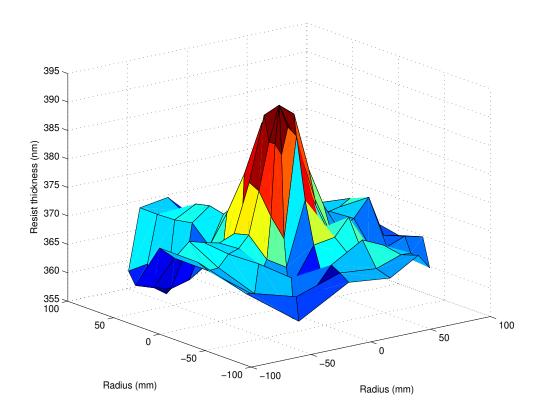

| 4.12 | Resist thickness profile: 3-D representation.                             | 52 |

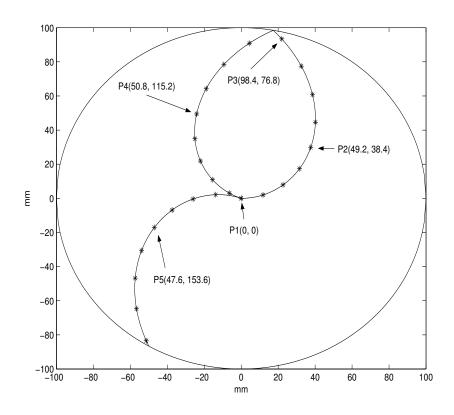

| 4.13 | Five positions at the monitoring trajectory shown in Figure 4.10 are      |    |

|      | selected to be monitored by off-line ellipsometer to validate the accu-   |    |

|      | racy of the dynamic measurement, which are P1-P5. The positions           |    |

|      | are given in polar coordinate $(r,\theta)$ in mm and degree, respectively | 53 |

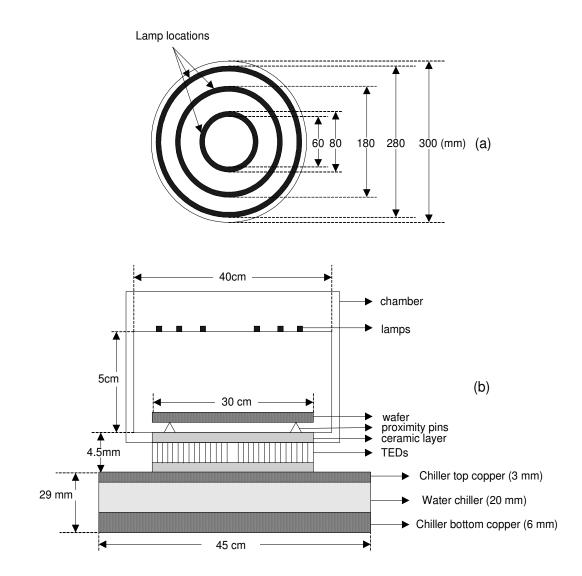

| 5.1  | Schematic diagram of the integrated bake/chill design. (a) is the         |    |

|      | top view of lamp locations; (b) is the cross section of whole designed    |    |

|      | system.(Note: Figure not drawn to scale.)                                 | 59 |

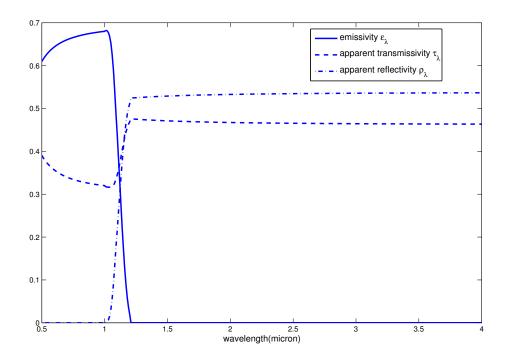

| 5.2  | Spectral emissivity, apparent transmissivity and apparent reflectiv-      |    |

|      | ity of a silicon wafer at a temperature of 373 K. The wafer is $300$      |    |

|      | mm in diameter and 675 $\mu$ m thick                                      | 63 |

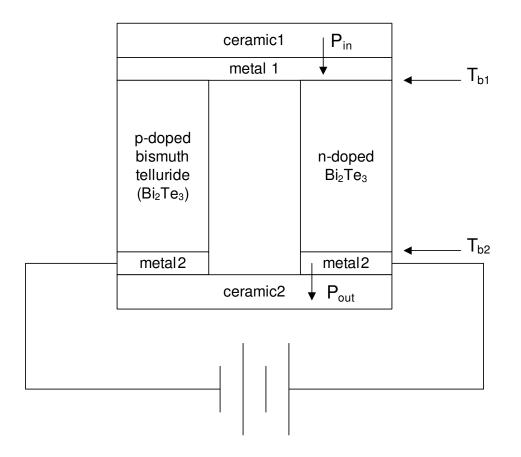

| 5.3  | Schematic diagram of a TED element. (Note: Figure not drawn to            |    |

|      | scale.)                                                                   | 70 |

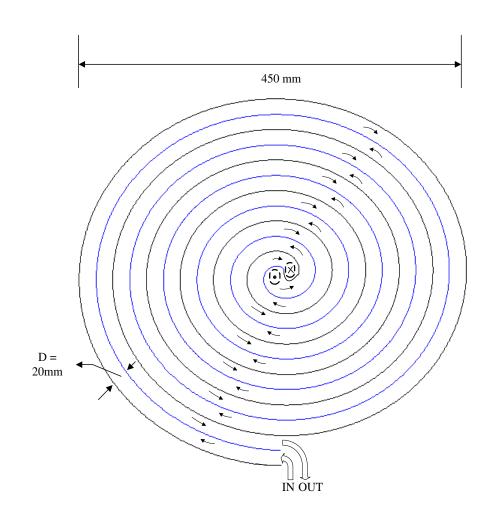

| 5.4  | Top view of wafer chiller                                                 | 72 |

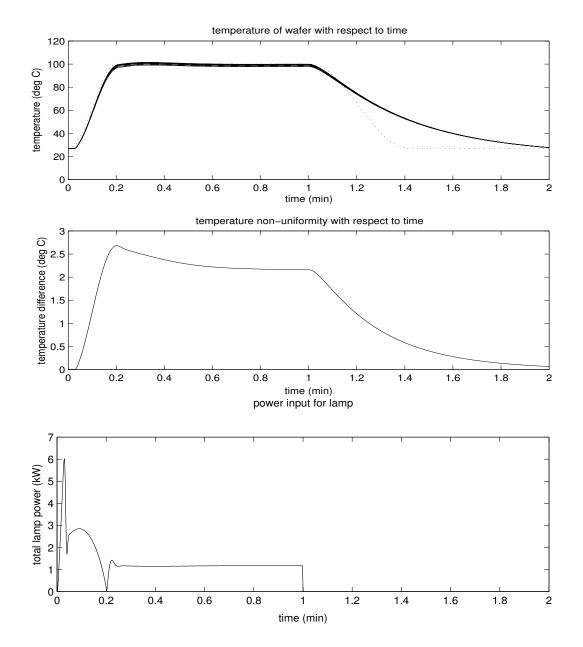

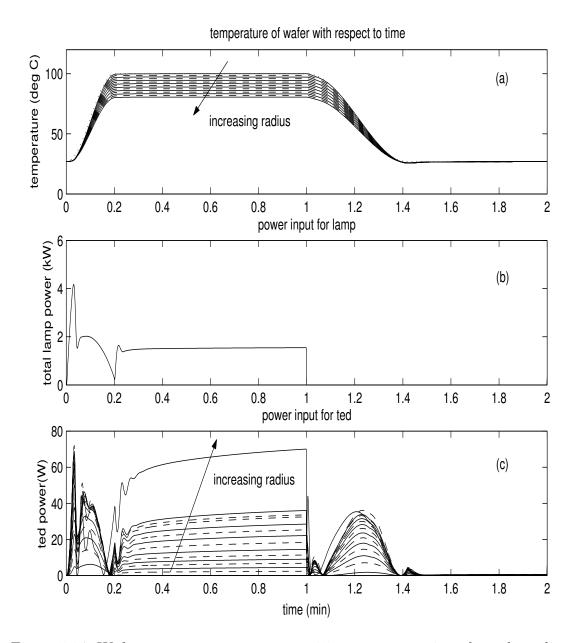

- 5.5 Wafer temperature responses at 15 measurement sites along the radius of the wafer during a thermal cycle. The system is set up as a single zone system with the center of the wafer temperature being fed back to the controller. The second plot shows the maximum temperature nonuniformity between the different zones during the entire thermal cycle. The third plot shows the total lamp power. . .

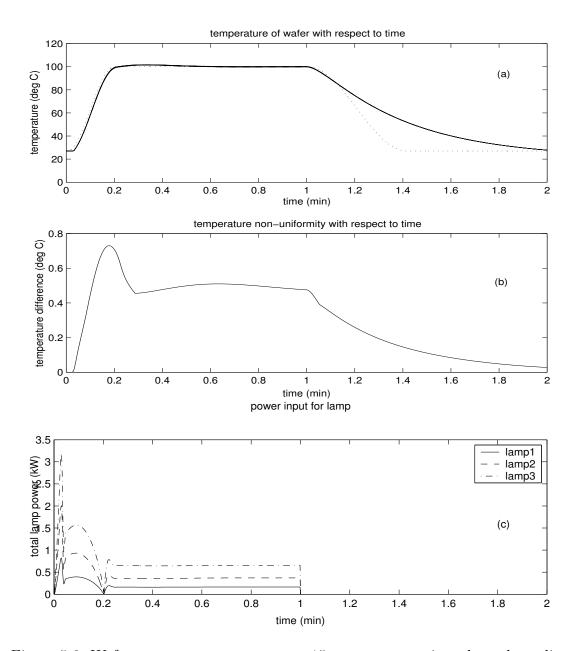

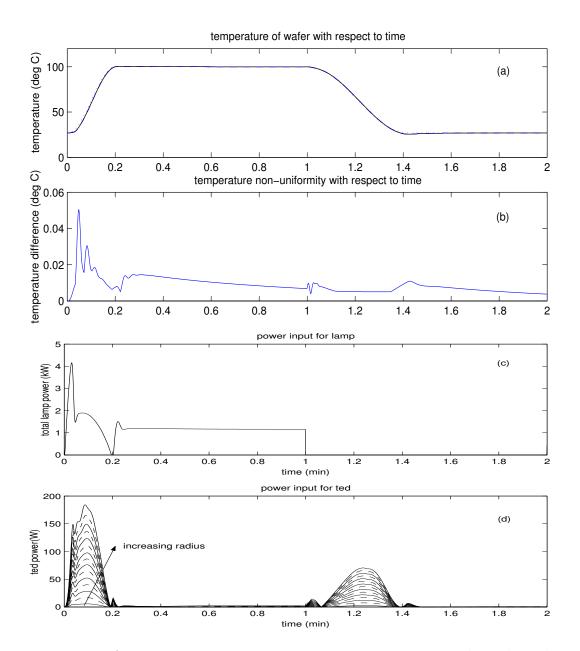

- 5.6 Wafer temperature responses at 15 measurement sites along the radius of the wafer during a thermal cycle shown at plot (a). The system is set up as 3 single decentralized systems with each of the wafer temperatures directly below each of the lamp locations being fed back to the respective lamp controllers. Plot (b) shows the maximum temperature nonuniformity between the different zones during the entire thermal cycle. Plot (c) shows the lamp power in each of the lamp zones. Solid line indicates the innermost zone, dashed line indicates the middle zone and dotted line indicates the outermost zone. 76

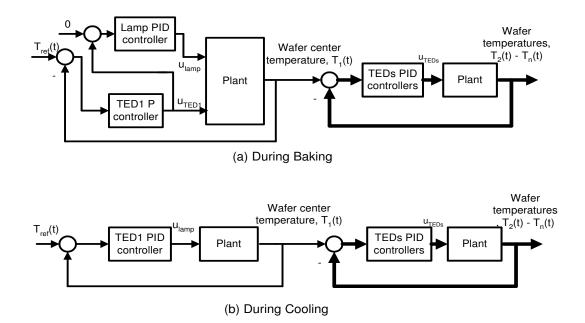

5.7 Block diagram of the integrated bake/chill control configuration.

- Plot(a) is the control scheme at the phase of heating; plot(b) is the control scheme at the phase of cooling.

5.8 We for the phase of cooling.

75

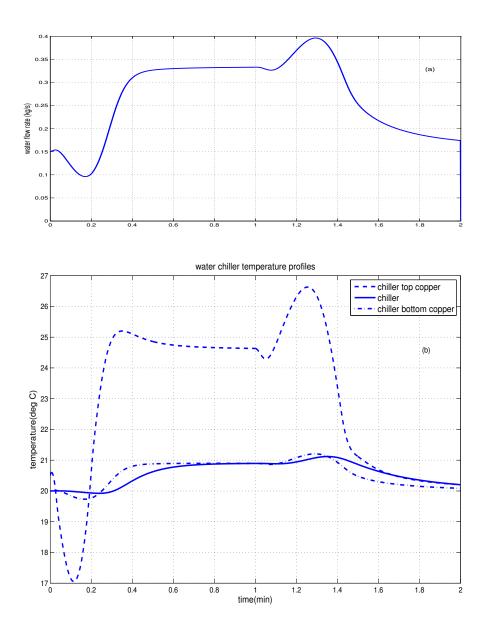

| Flow rate and chiller temperature responses during the entire ther-                 |                                                                                                                                                                    |

|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| mal cycle. Plot (a) is the cooling water flow rate in the whole cycle;              |                                                                                                                                                                    |

| plot (b) shows the temperature profiles for chiller and top and bot-                |                                                                                                                                                                    |

| tom copper plate                                                                    | 81                                                                                                                                                                 |

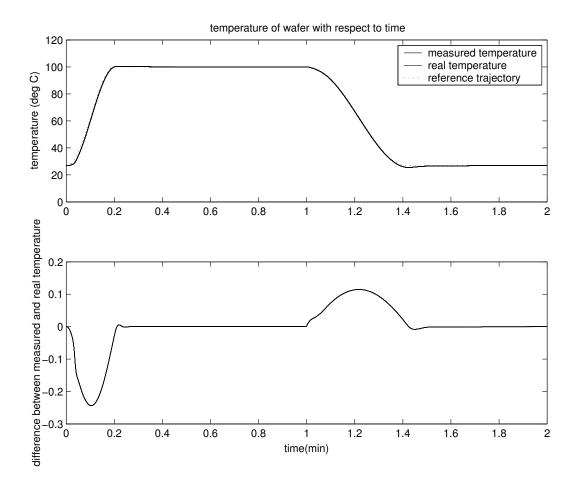

| Comparison between real and measured wafer temperatures. The                        |                                                                                                                                                                    |

| first plot shows the comparison between real and measured temper-                   |                                                                                                                                                                    |

| atures, and the second plot is the difference plot                                  | 82                                                                                                                                                                 |

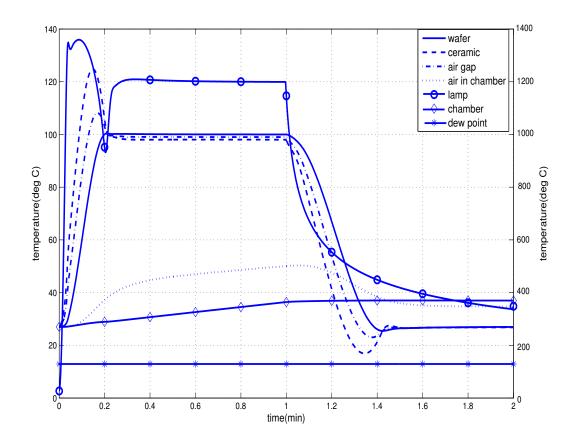

| Different surface temperature during the entire thermal cycle is                    |                                                                                                                                                                    |

| shown. The lamp temperature is indicated on the right ordinate.                     |                                                                                                                                                                    |

| The rest are indicated on the left ordinate                                         | 83                                                                                                                                                                 |

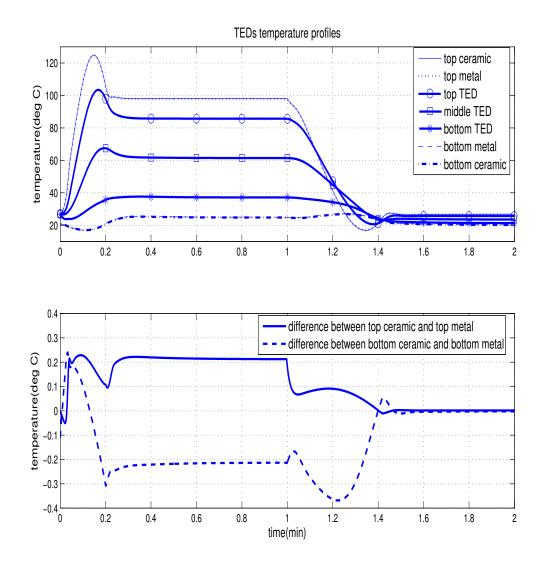

| Different surface temperature during the entire thermal cycle shown                 |                                                                                                                                                                    |

| in Figure 5.8. The lamp temperature is indicated on the right or-                   |                                                                                                                                                                    |

| dinate. Temperatures of different layers of TEDs during an entire                   |                                                                                                                                                                    |

| thermal cycle shown in (b) and (c). $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$    | 84                                                                                                                                                                 |

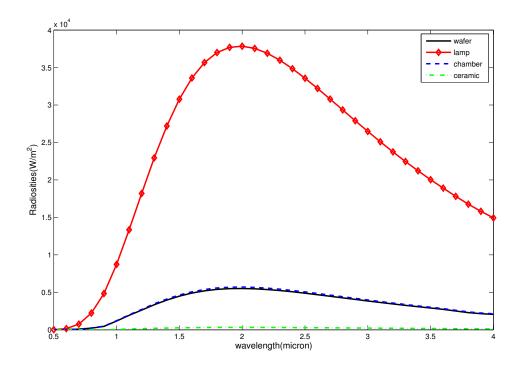

| Spectral radiosities for the different surfaces at 10 seconds of the                |                                                                                                                                                                    |

| thermal cycle shown in Figure 5.8                                                   | 85                                                                                                                                                                 |

| Wafer temperature responses at 15 measurement sites along the ra-                   |                                                                                                                                                                    |

| dius of the wafer during a thermal cycle with temperature biasing.                  |                                                                                                                                                                    |

| Each zone is set to a different temperature trajectory with a tem-                  |                                                                                                                                                                    |

| per<br>ature difference of $1.4^o\mathrm{C}$ between each zone at steady state. The |                                                                                                                                                                    |

| lamp and TEDs power are also shown.                                                 | 86                                                                                                                                                                 |

|                                                                                     | mal cycle. Plot (a) is the cooling water flow rate in the whole cycle;<br>plot (b) shows the temperature profiles for chiller and top and bot-<br>tom copper plate |

# List of Tables

| 1.1 | Temperature sensitivity of the thermal processing steps            | 6  |

|-----|--------------------------------------------------------------------|----|

| 3.1 | Estimation of resist thickness $(y (nm))$                          | 32 |

| 3.2 | Estimation of resist extinction coefficient $(k)$                  | 33 |

| 4.1 | Comparison of in-situ measurements with off-line ellipsometer mea- |    |

|     | surements                                                          | 52 |

| 5.1 | Physical parameters of the thermal processing system               | 88 |

### Chapter 1

### Introduction

#### 1.1 Motivation

The evolution of integrated circuit (IC) technology has been governed mainly by device scaling due to rapid technology development (Plummer *et al.*, 2000). However, the semiconductor industry is facing increasingly difficult challenges as the feature sizes go beyond 100 nm, which almost reach the physical limit of existing technology. One of the "grand challenges" is to make affordable lithography available at and below 100nm (ITRS, 2005).

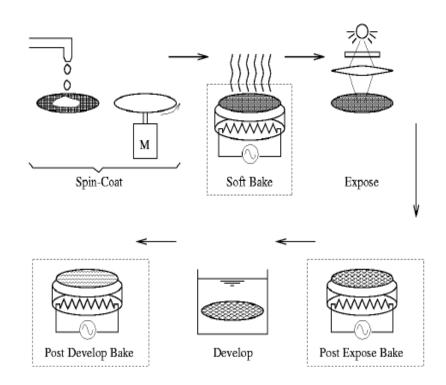

For many years, as the key technology driver for semiconductor industry, optical lithography has been the engine driving Moore's Law. Lithography is also a significant economic factor, currently representing 30-35% of the chip manufacturing cost (Plummer *et al.*, 2000). Figure 1.1 depicts the typical steps in a lithography process (Quirk and Serda, 2001). This sequence of operations begins with a priming step to promote adhesion of the polymer photoresist material to the substrate. A thin layer of resist is spin-coated on the wafer surface. The solvent is evaporated from the resist by a baking process (softbake). After patterning with (deep UV) radiation, a post-exposure bake process is used to promote a reaction that alters the solubility of the resist in the exposed areas. A subsequent chemical

Figure 1.1. The typical lithography sequence including spin-coating, soft bake, exposure, post exposure bake, develop and post develop bake process.

develop step then removes the exposed/reacted resist material while keeping the non-exposed areas in place. The developed resist is then baked to promote etching stability. In addition to the exposure step, lithography requires precise thermal processing of the photoresist including softbake, post exposure bake (PEB) and post develop bake.

The most important variable in the lithography process is the linewidth or critical dimension (CD), which is the single variable with the most direct impact on the device speed and performance (Edgar *et al.*, 2000). CD control is required for obtaining adequate transistor, interconnect and consequently overall circuit performance. The application of advanced computational and control methodologies have seen increasing utilization in recent years to improve yields, throughput, and, in some cases, to enable the actual process to print smaller devices (Edgar *et al.*, 2000; Schaper *et al.*, 1999). The value of applying such mathematical systems science tools to microelectronics manufacturing has already been demonstrated in the area of photoresist processing (Schaper *et al.*, 1999; Tay *et al.*, 2001; Ho *et al.*, 2002; Palmer *et al.*, 1996).

One exciting new challenge for process control is the development of control and optimization strategies that compensate for the non-uniform processing in one step (process) with that in another (Edgar *et al.*, 2000). An effective controller could work to resolve several integration problems, possibly speeding development time.

There are many factors that contribute to the final variation of the printed critical dimension (Zhang, 2002). Any drifts and variations in the lithographic process variables will affect the final linewidth. Two important sources of CD variation are: 1) photoresist properties non-uniformity, including extinction coefficient (Sheats and Smith, 1998; Sung *et al.*, 2000; Palmer *et al.*, 1996) and thickness variation (Levison, 1999; Lee *et al.*, 2002); 2) post-exposure bake temperature non-uniformity (Friedberg *et al.*, 2004; El-Awady, 2000; Leang *et al.*, 1996).

### 1.1.1 Effects of resist property variation in lithography process

The thickness and extinction coefficient are two of the photoresist properties that can have an impact on the CD uniformity (Lee *et al.*, 2002; Palmer *et al.*, 1996). The extinction coefficient is a measure of the absorption of the photoresist and determines the required exposure dose for printing the features (Sheats and Smith, 1998). Non-uniformity in extinction coefficient across the wafer will lead to nonuniformity in the linewidth (Sung *et al.*, 2000). Due to thin-film interference effects, CD varies with the resist thickness (Levison, 1999). The resist thickness has to be well controlled to remain at the the extrema of the swing curve where the sensitivity of CD to resist thickness variations is minimized (Brunner, 1991). In addition, the industry is also moving toward 300mm wafers for economic reasons. This places a stringent demand on the lithographic processes as the control requirement is now stretched over a larger area.

#### 1.1.2 Thermal effects in lithography process

Thermal processing of semiconductor substrates through conductive heat transfer is common and critical to the lithography process as shown in Figure 1.1. Each thermal processing step involves baking the substrate to an elevated temperature for a given period of time, this is then usually followed by a chill step which is used to cool the wafer to an appropriate temperature for subsequent processing (Plummer *et al.*, 2000). The effect of temperature on CD has been studied extensively. For every degree variation in wafer temperature uniformity, CD can vary as much as 20 nm (Levison, 1999). A 9% variation in CD per 1°C variation in temperature has been reported for a Deep ultraviolet (DUV) resist (Leang *et al.*, 1996). As the width of the feature size continues to shrink, temperature uniformity specifications become more stringent. Table 1.1.2 shows the temperature requirements for different thermal processing steps in lithography (Parker and Renken, 1997). For some critical bake processes such as post-exposure bake (PEB), temperature uniformity as stringent as  $\pm 0.1°C$  is required.

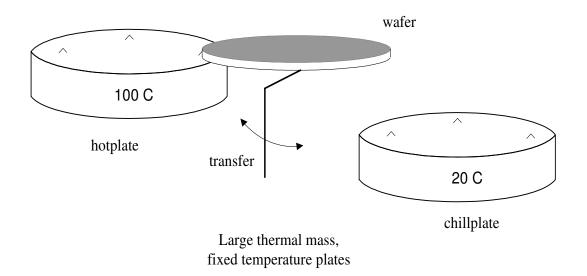

In the conventional thermal processing of semiconductor substrate, the heated plate is usually thermally massive relative to the substrate and is held at a constant temperature by a feedback controller. Because of its large thermal mass and resultant sluggish dynamics, conventional hotplates are robust to large temperature fluctuations and loading effects, and demonstrate good long-term stability. These advantages however become shortcomings in terms of process control and achievable performance when tight tolerances must be maintained. Other disadvantages include uncontrolled and nonuniform temperature fluctuation during the mechani-

Figure 1.2. The conventional approach for lithography baking and chilling involves substrate transfer between large thermal mass, fixed temperature plates.

cal transfer of the substrate from bake to chill plates (see Figure 1.2), spatial temperature non-uniformities during the entire thermal cycle, etc (El-Awady, 2000). This lack of a method to conduct real-time distributed, closed-loop temperature control with conventional hotplates is a source of process error in the lithography chain.

Although some improvements are possible (Ho *et al.*, 2000; Tay *et al.*, 2001; Tay *et al.*, 2004*b*), we conclude that the conventional hotplate design has poor controllability that ultimately limits the achievable performance. Hence, new thermal processing system have to be developed for optimal processing of temperaturesensitive photoresist so as to address the abovementioned issues.

#### 1.2 Contribution

In this thesis, the application of advanced process control and equipment control to reduce the process variation in lithography is investigated. This thesis addresses these areas: 1) Real-time monitoring and control of photoresist extinction coefficient uniformity; 2) In-situ monitoring of photoresist thickness contour in lithog-

| Thermal Step       | Purpose                | Temperature          | Precision                 |

|--------------------|------------------------|----------------------|---------------------------|

|                    |                        | Range                | Required                  |

| HMDS bake          | Promote Adhesion       | $70 - 150^{\circ}C$  | $\pm 5^{\circ}C$          |

| ARC bake           | Cure ARC               | $90 - 180^{\circ}C$  | $\pm 1 - 2^{\circ}C$      |

| Softbake           | Drive off solvent      | $90 - 140^{\circ}C$  | $\pm 1^{o}C$              |

|                    | stabilize thickness    |                      |                           |

| Post-exposure bake | i-line resist:         | $90 - 180^{\circ}C$  | $\pm 0.5 - 1^{\circ}C$    |

| (PEB)              | smooth standing waves  |                      |                           |

| PEB                | DUV resist:            | $90 - 150^{\circ}C$  | $\pm 0.12 - 0.5^{\circ}C$ |

|                    | deblock exposed resist |                      |                           |

| Post-develop bake  | Improve etch stability | $120 - 180^{\circ}C$ | $\pm 1^{o}C$              |

Table 1.1. Temperature sensitivity of the thermal processing steps

raphy; 3) Development of a lamp thermoelectricity based integrated bake/chill system for photoresist processing.

### 1.2.1 Real-time monitoring and control of photoresist extinction coefficient uniformity

Critical dimension (CD) is one of the most critical variables in the lithography process. The extinction coefficient can have an impact on the CD uniformity (Sung *et al.*, 2000). Non-uniformity in extinction coefficient across the wafer leads to non-uniformity in the linewidth. In this thesis, an innovative approach to control the within-wafer photoresist extinction coefficient uniformity is proposed and demonstrated. Previous research in the literature can only control the average uniformity of the extinction coefficient (Palmer *et al.*, 1996). Our approach uses an array of spectrometers positioned above a multizone bakeplate to monitor the extinction coefficient in real-time. The extinction coefficient can be extracted from the spectrometer data using standard optimization algorithms. With these in-situ measurements, the temperature profile of the bakeplate is controlled in real-time by manipulating the heater power distribution using conventional proportionalintegral (PI) control algorithm. We have experimentally obtained a repeatable improvement in the extinction coefficient uniformity within wafer and from wafer to wafer. A 70% improvement in extinction coefficient uniformity is achieved (Tay  $et \ al., 2006$ ).

The effect of warpage on the extinction coefficient estimation has also been investigated and an in-situ calibration method has been proposed. Based on it, accurate estimation of resist extinction coefficient in the presence of wafer warpage is obtained.

### 1.2.2 In-situ monitoring of photoresist thickness contour in lithography

The coating of photoresist on semiconductor substrate is a common process in the lithography sequence. It is important to ensure the uniformity of the photoresist thickness across the substrate as nonuniformity in photoresist thickness leads to nonuniformity in critical dimension (Levison, 1999). An in-situ photoresist thickness contour monitoring system has been proposed (Ho *et al.*, 2006). In the setup, a spectrometer is used to measure the photoresist thickness contour on the wafer after the spin-coat process or edge-bead removal process. The experimental results are compared with offline ellipsometer measurement. The worst-case error is experimentally found to be less than 2%.

### 1.2.3 A lamp thermoelectricity based integrated bake/chill system for photoresist processing

Thermal processing of semiconductor substrates through conductive heat transfer is critical to the lithography process. Of these baking steps, the post-exposure bake step is the most sensitive to temperature variation for the current generation of chemically-amplified resists (CARs) (Plummer *et al.*, 2000; Parker and Renken, 1997). In this thesis, a new design of an integrated bake/chill module for photoresist processing in lithography is presented, with an emphasis on the spatial and temporal temperature uniformity of the substrate (Tay et al., 2007). The system consists of multiple radiant heating zones for heating the substrate, coupled with an array of thermoelectric devices (TEDs) which provide real-time dynamic and spatial control of the substrate temperature. The TEDs also provide active cooling for chilling the substrate to a temperature suitable for subsequent processing steps. The use of lamps for radiative heating offers fast ramp-up and ramp-down rates during thermal cycling operations. In the proposed system, the bake and chill steps are integrated thereby eliminating the loss of temperature control typically encountered during the mechanical transfer from the bake to chill step as in the conventional lithography track system. The feasibility of the proposed approach is demonstrated via detailed modelling and simulations based on first principle heat transfer analysis, in particular the complete spectral optical properties of the wafer has been accounted for. The distributed nature of the design also engenders a simple decentralized control scheme which satisfies tight spatial and temporal temperature uniformity specifications. Original contributions have been made to account for spectral optical properties of wafer in the simulation. It is a new modelling with higher accuracy without assuming that the wafer is a opaque object. Based on it, new modelling of radiation absorption by translucent silicon wafer is proposed and implemented. A simple modelling of spiral wafer chiller is also presented.

#### **1.3** Organization

This thesis is organized as follows. The first chapter covers the the motivation, contribution and organization of the thesis. Chapters 2, 3 and 4 discuss the real-time monitoring and control of photoresist properties in lithography. Chapter 2 presents an application of control system methodology for extinction coefficient uniformity improvement by manipulating the power distribution for a multi-zone bakeplate. Chapter 3 investigates the effect of wafer warpage on the resist extinction coefficient and thickness estimation and proposes a calibration method for extinction coefficient estimation. In Chapter 4, an in-situ monitoring of photoresist thickness contour on wafer is implemented. Chapter 5 discusses a new design of integrated bake/chill equipment for photoresist processing in lithography. Chapter 6 gives the conclusions and recommendations for future work.

### Chapter 2

# Real-time Control of Photoresist Extinction Coefficient Uniformity

#### 2.1 Introduction

To form the resist patterns, the wafer substrate is spin-coated with a thin film of resist, followed by a softbake process to remove excess solvent in the resist film. The desired patterns are then patterned onto the resist film by exposing the substrate with deep UV radiation. During the exposure step, some of the incident light is absorbed by resist and it becomes more soluble in develop solution for positive resist or less soluble for negative one. The extinction coefficient is a measure of the absorption of the photoresist and determines the required exposure dose for printing the features (Sheats and Smith, 1998). Non-uniformity in the extinction coefficient across wafer can result in the consequence that the resist is effectively underexposed where the extinction coefficient is lower and overexposed where it is higher (Plummer *et al.*, 2000). This leads to non-uniformity in the final CD printed on wafer. Hence, the uniformity of extinction coefficient has to be well controlled within wafer and from wafer to wafer. Furthermore, the industry is moving towards the use of 300 mm substrate for economic reasons. This places a stringent demand on the lithographic processes as the control requirement is now stretched over a larger area.

Softbake process is performed after the spin-coating process (see Figure 1.1) to remove excess solvent from the resist film, reduce standing waves and relax the resist polymer chain into an ordered matrix (Plummer *et al.*, 2000). The temperature control during softbake process is important (Sheats and Smith, 1998; Ho *et al.*, 2000). Conventionally, the resist is baked at a fixed temperature with temperature of  $\pm 1^{\circ}C$  for consistent lithographic performance (Sheats and Smith, 1998). In general, the resist extinction coefficient formed after the spin-coating process will not be uniform. If a non-uniform resist film is formed during spin-coating, experiments have shown that maintaining a uniform temperature profile across the bakeplate will not reduce the resist extinction coefficient non-uniformity.

Our approach to controlling the photoresist extinction coefficient uniformity make use of an array of in-situ photoresist film properties extraction sensors positioned above a multizone bakeplate (Schaper *et al.*, 1999; Tay *et al.*, 2001; Schaper *et al.*, 2003) to monitor and control the resist extinction coefficient. With these in-situ measurements, the temperature profile of the bakeplate is controlled in real-time by manipulating the heater power distribution using a standard PI controller for each of the zones. Various sites on the wafer are made to follow a predefined resist extinction coefficient trajectory to reduce the extinction coefficient non-uniformity at the end of the softbake process.

The literature consists of a number of different techniques for in-situ monitoring of photoresist properties during the different baking process in lithography (Paniez *et al.*, 1998; Fadda *et al.*, 1996; Morton *et al.*, 1999; Metz *et al.*, 1991; Leang and Spanos, 1996). In related work, Metz *et al.* (Metz *et al.*, 1991) used in-situ multiwavelength reflection interferometers to measure the resist thickness versus bake time to determine the optimum bake time. Leang and Spanos (Leang and Spanos, 1996) developed a novel metrology using photospectrometers to monitor both resist

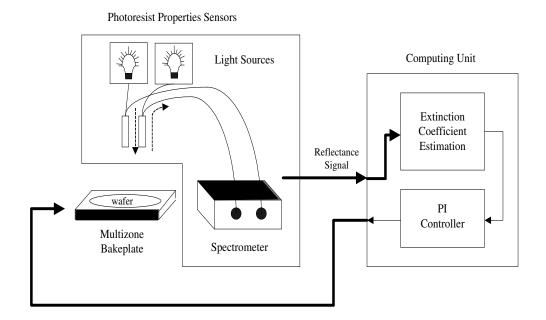

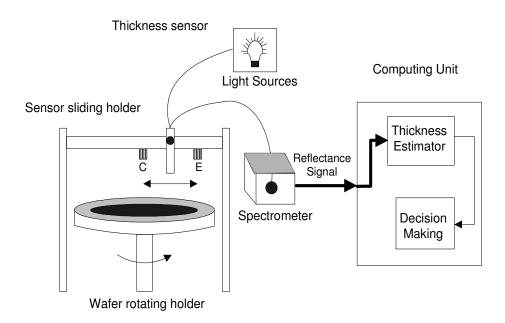

Figure 2.1. Schematics of the experimental setup used to control resist extinction coefficient. The system consists of three main parts: a multizone bakeplate, extinction coefficient sensors, and a computing unit.

thickness and photoactive compound concentration. Existing approaches in the literature (Palmer *et al.*, 1996) can only control the average non-uniformity of the extinction coefficient across the wafer from wafer-to-wafer, and it is not a real-time approach. Our approach make use of an array of multi-wavelength spectrometers to monitor and control the resist properties across the wafer in real-time during the softbake process. Our objective is to develop a metrology and control scheme capable of controlling the spatial uniformity of the photoresist extinction coefficient on the wafer.

#### 2.2 Experimental setup

Figure 2.1 shows the experimental setup for monitoring and control of the photoresist properties during the softbake process. An array of 2 in-situ film properties extraction sensors is positioned above the wafer to monitor the resist extinction coefficient at 2 sites on the wafer as shown in Figure 2.1. The in-situ measure-

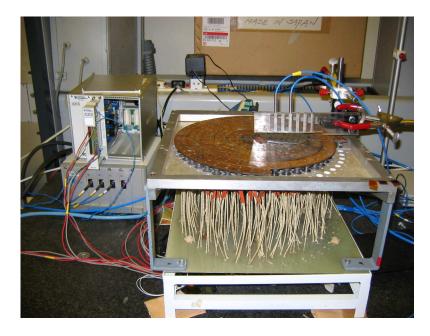

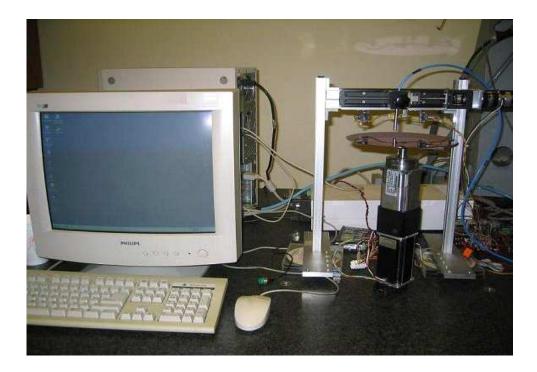

Figure 2.2. Photograph of the experimental setup.

ments are also used to detect the endpoint of the softbake process. The setup comprises a broadband light source (LS-1), a spectrometer with the capability of monitoring the reflected light intensity at two sites simultaneously (SQ2000) and a bifurcated fiber optics reflection probe (R200) from OceanOptics (*Product catalog*, 2002). The reflection probe consisting of a bundle of 7 optical fibers (6 illumination fibers around 1 read fiber) is positioned above the wafer to monitor the resist properties in real-time. During softbake, light from the broadband light source is focused on the resist through one end of the probe and the reflected light is guided back to the spectrometer through the other end. Figure 2.2 shows a photograph of the experimental setup.

The programmable thermal processing module developed comprises an array of heating zones that allow for spatial control of temperature in non-symmetric configurations. The schematics is shown in Figure 2.3. Resistive heating elements are embedded within each of the heating zones. The heating zone is configured with its own temperature sensor (RTDs) and electronics for feedback control. The heating zones are separated with a small air-gap of approximately 1 mm. The fact

Figure 2.3. Schematics of multizone bakeplate

that the zones are spatially disjoint ensures no direct thermal coupling between the zones, enhancing controllability. Its small thermal mass allows for fast dynamic manipulation of the temperature profile. Depending on the application, the number of zones of the bakeplate can easily be configured. We will make use of this system to control the photoresist extinction coefficient through temperature manipulation at different locations on the bakeplate in real-time.

For all our experiments, the photoresist used is Shipley 1813, a positive resist. The sampling rate is 1 second. In all our experiments, the resist is spin-coated at 2000 rpm for 30 seconds on a 4-inch wafer. The wafer is then baked for 3 minutes during the softbake process. On average, we have obtained about 70% improvement in extinction coefficient uniformity at steady-state. Currently, the experimental setup is for a 4-inch wafer. This can be easily scaled to a 12-inch wafer with the addition of more sensor probes. The number of sensors and hence the amount of computation required for a 12-inch wafer is roughly tripled and this should not be an issue. Besides silicon wafers, our method may also be applied to photomask manufacturing.

#### 2.3 Photoresist extinction coefficient estimation

The photoresist extinction coefficient may be estimated from the reflectance signals of the multi-wavelength spectrometer using a thin film optical model. When light is focused onto the resist film, phase difference between the incident and reflected light creates interference effects within the resist. Consider an absorbing photoresist film with a complex index of refraction,  $n_r+ik$ . Its relation with the reflectance intensity is given by (Born and Wolf, 1980)

$$h(\lambda, k, y) = \frac{\rho_{12}^2 e^{2k\eta} + \rho_{23}^2 e^{-2k\eta} + 2\rho_{12}\rho_{23}cos(\phi_{23} - \phi_{12} + 2n_r\eta)}{e^{2k\eta} + \rho_{12}^2\rho_{23}^2 e^{-2k\eta} + 2\rho_{12}\rho_{23}cos(\phi_{23} + \phi_{12} + 2n_r\eta)}$$

(2.1)

where

$$\rho_{12}^{2} = \frac{(n_{a} - n_{r})^{2} + k^{2}}{(n_{a} + n_{r})^{2} + k^{2}},$$

$$\rho_{23}^{2} = \frac{(n_{s} - n_{r})^{2} + k^{2}}{(n_{s} + n_{r})^{2} + k^{2}},$$

$$\phi_{12} = \arctan \frac{2k}{n_{r}^{2} + k^{2} - 1},$$

$$\phi_{23} = \arctan \frac{2kn_{s}}{n_{r}^{2} + k^{2} - n_{s}^{2}},$$

$$\eta = \frac{2\pi}{\lambda}y;$$

and  $n_a, n_r$  and  $n_s$  are the refractive index of air, resist, and substrate, respectively. y is the resist thickness, k is the resist extinction coefficient and  $\lambda$  is the wavelength of light.

The resist refractive index,  $n_r$ , is a function of wavelength,  $\lambda$ , and is given by the Cauchy equation (Born and Wolf, 1980)

$$n_r(\lambda) = A + \frac{B}{\lambda^2} + \frac{C}{\lambda^4}$$

(2.2)

where A, B, C are the Cauchy parameters of the resist. The Cauchy parameters

for Shipley 1813 resist are A = 1.5935,  $B = 1.8854 \times 10^4$ , and  $C = 4.1211 \times 10^6$ .

Equation (2.1) is a function of wavelength, resist extinction coefficient and resist thickness. Leang and Spanos (Leang and Spanos, 1996) proposed an approach for estimating both the resist thickness and extinction coefficient at each time instant. First, at higher wavelength of the reflectance signal shown in Figure 2.4, the photoresist extinction coefficient of light is essentially zero (Leang and Spanos, 1996; Born and Wolf, 1980). Hence solving the best curve fit at these wavelength is equivalent to solving the resist thickness. Once the resist thickness is obtained, the resist extinction coefficient can be computed making use of the spectrum at shorter wavelengths, where resist is absorptive. The approach is thus to decouple the computation of the resist thickness and the extinction coefficient. Essentially, at higher wavelength, Equation (2.1) reduces to a function of wavelength and resist thickness, which is given as Equation (2.5); at shorter wavelength, with the computed thickness, Equation (2.1) reduces to a function of wavelength and resist extinction coefficient.

The solution to the above problem is non-convex and does not contain a global minimum over the search space. However, we have a reasonably good initial estimate of the resist thickness from the coating process. Therefore, a local minimum solution for the resist thickness is obtained using least square estimation. First, for thickness computation at the higher wavelengths, the extinction coefficient, kis zero and Equation (2.1) is approximated by taking the Taylor series expansion such that

$$h(\lambda, y) = h(\lambda, y_0) + \frac{\partial h}{\partial y}\Big|_{\lambda, y_0} \Delta y$$

(2.3)

where  $y_0$  is the initial thickness estimate and  $\partial h/\partial y$  the derivative. The estimated

Figure 2.4. Extraction of resist thickness and extinction coefficient using least square estimation: range A is used to estimate extinction coefficient, while range B is used to estimate resist thickness. Solid line shows the experimental data while the '\*'-line shows the theoretical fitted result.

resist thickness,  $\hat{y}$ , is given as

$$\hat{y} = y_0 + \Delta y \tag{2.4}$$

and the change in thickness,  $\Delta y$ , is estimated using the least square estimation

$$\Delta y = \left(\frac{\partial h}{\partial y}^{T} \frac{\partial h}{\partial y}\right)^{-1} \frac{\partial h}{\partial y}^{T} (h - h_{0})$$

(2.5)

where

$$\frac{\partial h}{\partial y} = \begin{bmatrix} \frac{\partial h}{\partial y} \Big|_{\lambda_1, y_0} \\ \frac{\partial h}{\partial y} \Big|_{\lambda_2, y_0} \\ \vdots \\ \frac{\partial h}{\partial y} \Big|_{\lambda_M, y_0} \end{bmatrix} \qquad h = \begin{bmatrix} h(\lambda_1, y) \\ h(\lambda_2, y) \\ \vdots \\ h(\lambda_M, y) \end{bmatrix} \qquad h_0 = \begin{bmatrix} h(\lambda_1, y_0) \\ h(\lambda_2, y_0) \\ \vdots \\ h(\lambda_M, y_0) \end{bmatrix}$$

Once the resist thickness is obtained, for the computation of the resist extinction coefficient at shorter wavelengths, Equation (2.1) is approximated by taking the Taylor series expansion such that

$$h(\lambda, k) = h(\lambda, k_0) + \frac{\partial h}{\partial k} \Big|_{\lambda, k_0} \Delta k$$

(2.6)

where  $k_0$  is the initial coefficient estimate and  $\partial h/\partial k$  the derivative. The derivative is calculated using numerical method as the explicit expression of derivative is quite tedious. The estimated extinction coefficient is then given as

$$\hat{k} = k_0 + \Delta k \tag{2.7}$$

and the change in extinction coefficient,  $\Delta k$ , is estimated using least squares estimation

$$\Delta k = \left(\frac{\partial h}{\partial k}^{T} \frac{\partial h}{\partial k}\right)^{-1} \frac{\partial h}{\partial k}^{T} (h - h_{0})$$

(2.8)

where

$$\frac{\partial h}{\partial k} = \begin{bmatrix} \frac{\partial h}{\partial k} |_{\lambda_1, k_0} \\ \frac{\partial h}{\partial k} |_{\lambda_2, k_0} \\ \dots \\ \frac{\partial h}{\partial k} |_{\lambda_N, k_0} \end{bmatrix} \qquad h = \begin{bmatrix} h(\lambda_1, k) \\ h(\lambda_2, k) \\ \dots \\ h(\lambda_N, k) \end{bmatrix} \qquad h_0 = \begin{bmatrix} h(\lambda_1, k_0) \\ h(\lambda_2, k_0) \\ \dots \\ h(\lambda_N, k_0) \end{bmatrix}$$

To estimate the resist thickness and extinction coefficient, reflectance measurements are obtained at wavelength between 520-690 nm (501 points in total each 0.34 nm apart) and 420-450 nm (81 points in total each 0.35 nm apart) respectively. The initial estimated  $k_0$  is updated with the current value of  $\hat{k}$  at every sample. The curve fitting result is shown in Figure 2.4. The least squares estimation approach is compared with a nonlinear estimation approach. The nonlinear estimation method uses Equation (2.1) to search for a solution. Since no approximation is made to

Figure 2.5. Comparison of least square estimation and nonlinear curve fitting methods of estimating photoresist extinction coefficient.

Equation (2.1) in this approach, it gives the most accurate measurements. The resist extinction coefficient obtained using least squares estimation is compared with the one using the nonlinear estimation method. Figure 2.5 shows the percentage deviation during the 200 seconds softbake. Despite making an approximation to Equation (2.1), there is only a negligible difference in the results between the least squares estimation and nonlinear estimation method.

## 2.4 Control of photoresist extinction coefficient uniformity

For conventional softbake, the wafer was baked at a uniform temperature of  $90^{\circ}$ C across the whole bakeplate. During the softbake process, the extinction coefficients at two different sites (center zone and edge zone of wafer which is 1 inch apart along the radial direction, as shown in Figure 2.3) were monitored. A feedback controller is used to maintained the bakeplate temperature at  $90^{\circ}$ C during

Figure 2.6. Conventional softbake with bakeplate maintained uniformly at  $90^{\circ}$ C: (a) resist extinction coefficient, (b) resist extinction coefficient non-uniformity profile of the two sites monitored. Solid line represents center zone of the wafer, while dashed line represents edge zone.

the entire softbake process. Figure 2.6 shows the experimental result under conventional softbake. The experiment shows that at the end of the softbake process, the extinction coefficients is non-uniform. An average non-uniformity of 0.0023 in absolute extinction coefficient is obtained at steady-state as shown in Figure 2.6(b).

To control the extinction coefficient uniformity, the spectrometers is used to provide in-situ measurement of the resist extinction coefficient. Based on the measured information, two decentralized proportional-integral (PI) controllers of the following form are implemented:

$$u(t) = k_{Pi}e(t) + k_{Ii}\int e(t)dt$$

where u(t) and  $e(t) = k_{ref}(t) - k(t)$ , are the control signal to the bakeplate and the error signal (difference between the reference extinction coefficient,  $k_{ref}(t)$ , and actual extinction coefficient, k(t)) respectively. The PI parameters for the center zone and edge zone are  $k_{P1} = 320$ ,  $k_{I1} = 5$ ,  $k_{P2} = 335$  and  $k_{I2} = 5$  respectively.

The above PI controllers are used to control the resist extinction coefficients at the two different sites to track a predefined reference trajectory. The reference trajectory shown in Figure 2.7(a) is designed by shifting the extinction coefficient trajectory of a typical conventional softbake extinction coefficient profile (e.g. Figure 2.6(a)) such that the trajectory settle at a certain peak value, e.g. 0.032 in our experiment. Other predefined trajectories can also be implemented. The experimental results were shown in Figure 2.7. After about 35 seconds, the resist extinction coefficients of two different sites begin to converge to the specified target extinction coefficient. At about 90 seconds, the extinction coefficients approaches and is maintained at the peak value of 0.032. An average extinction coefficient nonuniformity of 0.0007 was maintained at steady-state, as shown in Figure 2.7(d). As shown in Figure 2.7(b), a non-uniform bakeplate temperature profile is required to maintain a uniform resist extinction coefficient. The corresponding heater power is shown in Figure 2.7(c).

Next, the repeatability of the proposed approach is demonstrated in Figure 2.8. Experimental runs 1 to 3 is for the case of conventional softbake while experimental runs 4 to 9 is for the case of multizone PI controlled softbake. On average a 70% improvement is achieved in the resist extinction coefficient average non-uniformity.

#### 2.5 Conclusion

The lithography manufacturing process will continue to be a critical area in semiconductor manufacturing that limits the performance of microelectronics. Enabling advancements by computational, control and signal processing methods are effec-

Figure 2.7. Multizone softbake with PI controllers: (a) resist extinction coefficient, (b) bake plate temperature, (c) heater power, (d) resist extinction coefficient nonuniformity profile of the two sites monitored. Solid line represents center zone of the wafer, while dashed line represents edge zone. The reference extinction coefficient trajectory is given by the dash-dot line in plot (a).

Figure 2.8. Extinction coefficient non-uniformity comparison for different experimental runs. The first three runs are under the conventional bake, while the next 6 runs are using the multizone bake with real-time control.

tive in reducing the enormous costs and complexity associated with the lithography sequence. In this chapter, real-time control of extinction coefficient has been implemented using an array of in-situ spectrometers, a multizone bakeplate and a conventional PI control strategy. It has been demonstrated that by maintaining a nonuniform temperature profile through the manipulation of power distribution, an average of 70% improvement in resist extinction coefficient nonuniformity has been obtained across the wafer and from wafer to wafer.

## Chapter 3

# Photoresist Extinction Coefficient and Thickness Estimation in the Presence of Wafer Warpage

#### 3.1 Introduction

Resist extinction coefficient and thickness are two important parameters in the lithography process (Palmer *et al.*, 1996; Lee *et al.*, 2002). Both of them can have an impact on the final CD printed on wafer (Levison, 1999; Sung *et al.*, 2000). Hence, accurate estimation of these two parameters is critical for CD control as feature size continually shrinks. Estimation of these photoresist film properties can be obtained using reflectrometry (Leang and Spanos, 1996). In related work, Metz *et al.* (Metz *et al.*, 1991) used in-situ multi-wavelength reflectometer to measure the resist thickness versus bake time to determine the optimum bake time. In Lee *et al.* (Lee *et al.*, 2002), in-situ thickness measurements using reflectometer was used to realize a thickness control strategy, thereby reducing the resist thickness non-uniformity at the end of the process.

The above mentioned monitoring methods using reflectometer work under the

assumption that the inspected wafer is flat. Wafer warpage is common in microelectronics processing. Warpage can affect device performance, reliability and linewidth or critical dimension (CD) control in various microlithographic patterning steps. Warped wafers also affect the various baking steps in the lithography sequence (Ho *et al.*, 2004).

Wafer warpage will result in a non-uniform distance between the wafer and the sensors (e.g. reflectometers) mounted above the wafer. As such, the measured data from the sensors have to be compensated to account for the variation in distance. In this chapter, the effect of wafer warpage on the accuracy of resist properties estimation is investigated and an in-situ calibration method is proposed. We will also demonstrate how the measured data can be used to detect wafer warpage in real-time during wafer processing. This is an improvement compare to existing methods which are mainly off-line where the wafer have to be removed from the processing chamber to the measurement system.

Current techniques for measuring wafer warpage include thermal processing method (Ho *et al.*, 2004; Tay *et al.*, 2005), capacitive measurement probe (Poduje and Balies, 1988), shadow Moire technique (Wei *et al.*, 1998), and pneumaticelectromechanical technique (Fauque and Linder, 1998). The thermal method (Ho *et al.*, 2004) is an in-situ detection method which requires no extra sensor and can be realized in a common thermal processing step. The rest methods are offline methods where the wafer has to be removed from the processing equipment and placed in the metrology tool resulting in increase of processing steps, time and cost.

#### 3.2 Experimental setup

Figure 3.1 shows the schematics of the warped wafer and flat wafer (Tay *et al.*, 2005). Warpage is realized by mechanically pressing the center of the wafer against

a thermal insulating tape of known thickness. No tape is used under the center of wafer so that the warpage is decided by the proximity pin height  $l_p$ . The proximity pin height can be increased at interval of 55  $\mu m$ . For all our experiments, the degree of warpage corresponds to 55, 110, 165, and 220  $\mu m$ .

The experimental setup is shown in Figure 3.2. The sensor probe from a reflectometer is positioned above the warped wafer or flat wafer with a distance of 4 mm and it is perpendicularly pointing to the center ares to acquire the reflected light intensity. The reflectometer sensor has the same setup as the sensor used in Chapter 2. It comprises a broadband light source (LS-1), fiber optics reflection probe (R200), and a spectrometer from Ocean Optics (*Product catalog, 2002*). The reflection probe consisting of a bundle of 7 optical fibers(6 illumination fibers around 1 read fiber) is positioned above the wafer to monitor the resist properties in real-time. The reflectance signal collected by the spectrometer is transmitted to the computer, from which the resist properties including the resist thickness, extinction coefficient can be estimated. The algorithms of properties estimation will be discussed in the next section. By analyzing the acquired reflectance signal, we also notice that the spectral reflectance curve itself is related the degree of warpage, which make the in-situ detection of warpage possible using the acquired reflectance curve.

Two types of photoresist are used the photoresist used in the experiments, namely Shipley 1813 (g-line resist) and SL4000 (DUV resist). The Cauchy parameters of refractive index for Shipley 1813 resist are A = 1.5935,  $B = 1.8854 \times 10^4$ , and  $C = 4.1211 \times 10^6$ . And for SL4000, A = 1.546,  $B = 0.59 \times 10^4$ , and  $C = 6 \times 10^8$ . The Shipley 1813 resist is spin-coated at 1000 rpm on wafer A, and 2000 rpm on wafer B. SL4000 resist is coated at 1000 rpm on wafer C.

Figure 3.1. Schematics of warped substrate and flat substrate

### 3.3 Photoresist properties estimation

The photoresist thickness and extinction coefficient can be estimated from the reflectance signals using a thin film optical model, as done in Chapter 2. When light is focused onto the resist film, phase difference between the incident and reflected light creates interference effects within the resist. Consider an absorbing photoresist film with a refractive index of  $n_r$ , a extinction coefficient of k and a thickness of y, they relate to the reflectance light intensity as given in Equation (2.2).

Equation (2.2) is a function of wavelength, resist extinction coefficient and resist thickness. The detailed estimation algorithms for resist thickness and extinction coefficient have also been elaborated in Chapter 2. They are summarized as follows. First, at higher wavelength of the reflectance signal shown in Figure 3.3, the photoresist extinction coefficient of light is essentially zero (Leang and Spanos, 1996; Born and Wolf, 1980). Hence solving the best curve fitting at these wavelength is equivalent to solving the resist thickness. Once the resist thickness is obtained, the resist extinction coefficient can be computed making use of the spectrum at shorter wavelengths, where resist is absorptive. The approach is thus

Figure 3.2. Experimental setup, including warped wafer, reflectometer sensor, and computing unit

to decouple the computation of the resist thickness and the extinction coefficient. Essentially, at higher wavelength, Equation (2.2) reduces to a function of wavelength and resist thickness; at shorter wavelength, with the computed thickness, Equation (2.2) reduces to a function of wavelength and resist extinction coefficient.

To estimate the resist thickness and extinction coefficient, reflectance measurements are obtained at wavelength between 625-800 nm and 420-450 nm, respectively. To extract resist thickness and extinction coefficient, the problem is formulated as

$$\min \sum_{\lambda=625nm}^{800nm} (h_{meas}(\lambda, y) - h_{theo}(\lambda, y))^2$$

(3.1)

and

$$\min \sum_{\lambda=420nm}^{450nm} (h_{meas}(\lambda,k) - h_{theo}(\lambda,k))^2$$

(3.2)

where h is the relative reflectance data and  $\lambda$  is the wavelength.  $h_{meas}$  refers to

Figure 3.3. Extraction of resist thickness and extinction coefficient for flat wafer: low wavelength range is used to estimate extinction coefficient, while high wavelength range is used to estimate resist thickness.