# Advanced Design of Microwave Power Divider with Enhanced Harmonic Suppression

IP, Wei Chi

A Thesis Submitted in Partial Fulfillment of the Requirement for the Degree of Master of Philosophy

in

**Electronic Engineering**

The Chinese University of Hong Kong August 2011

### Abstract

Currently, miniaturized and high-performance microwave circuits are in great demand for many wireless or RF applications in order to reduce the system cost. Moreover, microwave devices based on planar microstrip structure can offer many benefits over the other types of transmission line such as strip-line and waveguide, as they can easily be integrated with other planar circuits and provide a low-cost, large volume production with increased reliability.

Wilkinson power divider is one of the major passive devices used in radio frequency (RF) and microwave front-end design due to its simplicity and high degree of isolation between the two output ports. It has a wide range of applications such as the feeding network for an antenna array and the power splitting/combining networks for amplifier modules. The major drawback of the conventional Wilkinson power divider is the presence of spurious response, due to the adoption of simple quarter-wavelength transmission lines. This affects the performance of the system drastically, especially in wireless applications. In the past, the suppression of harmonic bands is usually attained by adding separate filter modules.

In the last decade, this problem has been partially overcome by using defected ground structure (DGS) or electromagnetic bandgap (EBG) cells for the suppression of one or two harmonic frequency bands. Unfortunately, these circuits usually require either backside etching or additional lumped reactive element, which is undesirable for low-cost and mass production environment. Moreover, explicit design formulas are often not available and the desired responses are mainly obtained by computer optimization.

In this research, new designs of two-way and three-way power dividers with enhanced spurious suppression have been developed and demonstrated. The proposed structures require no DGS or reactive elements, and feature low loss, readily available closed form solutions, flexible layout, enlarged suppression bandwidth, and compact size. For the purpose of verification, all designs have been fabricated using microstrip, characterized and compared with simulation results. These devices offer both power dividing capability and multi-harmonic rejection in a single design. As a result, low cost, miniaturized RF front-end may easily be implemented by the adoption of these multi-functional devices, rather than the cascaded connection of multiple modules.

## 摘要

目前,小型化、高性能微波電路的需求量很大,以減低無線應用中系統成本。 此外,在微波器件基礎上,平面微帶結構比其他類型的傳輸線,如帶狀線和波 導,有很多好處。因為他們可以很容易地與其他平面電路集成,可作低成本, 具有高度可靠性的大批量生產。

由於其簡單性及兩輸出端口之間的高度隔離,在無線電頻率和微波的前端設計 之中,威爾金森功率分配器是一個的關鍵設備。該分頻器具有廣泛的應用,如 應用於網絡天線陣列和功率分配/結合網絡的放大器模塊。常規威爾金森功率分 配器的主要缺點是雜散響應的存在,由於採用簡單的四分之一波長傳輸線。這 會影響電路的性能,尤其是對無線系統。單獨的過濾器通常被用作抑制諧波頻 帶。

過去的十年,這個問題已經部分克服,通過使用缺陷地面結構(分散型發電) 或電磁能隙(EBG 結構)細胞,以抑制諧波的一個或兩個頻段。但是,這些電 路通常需要額外的集總反應元件或背面蝕刻,這些方法不適用於低成本和大規 模的生產環境。此外,缺乏明確的設計公式,所需的響應主要來自計算機優 化。

在本研究中,新設計的雙向及三路功率分配器具有雜散抑制的功能,表現出理想的特性而不使用任何反應的元件,具有損耗低、明確的設計公式,靈活的設計、擴大抑制帶寬和體積小等優點。所有設計的製作,均採用了微帶,並與其仿真結果作對比,以驗證其真僞。新的設計電路同時具備功率劃分及多諧波抑制的功能。因此,低成本、小型化的射頻前端可以很容易的實施通過利用這些多功能設備,而不是串聯多個模塊。

### Acknowledgement

The author would like to thank his supervisor, Dr. K.K. Michael Cheng, for his effort, guidance and inspiration throughout the process of this work. Michael is particularly tolerant with his students when making mistakes and helps them to solve problems. The author has learnt a great deal during his guidance that research is not only to focus, but also to wisely diversify his attention in work, to rest, to relax, to innovate and integrate ideas from different fields. To a practical aspect, the author would like to conclude his note of acknowledgement to Mr Li Pak Wing, who has been tremendously generous in helping out to familiarize with the ADS simulation environment, EM and layout issues, and points to note during fabrication in the dark room. Besides, the author would like to appreciate his friends who fully support his research and work.

This work is dedicated to my family.

## **Table of Content**

| Abstract                                                                | ĺ. |

|-------------------------------------------------------------------------|----|

| 摘要i                                                                     | i  |

| Acknowledgementii                                                       | i  |

| Table of Contentiv                                                      | 7  |

| Lists of Figuresvi                                                      | i  |

| Lists of Tablesxi                                                       | i  |

| Chapter 1: Introduction                                                 | L  |

| 1.1 Research Motivation and Objective                                   | l  |

| 1.2 Original Contribution                                               | 2  |

| 1.3 Overview of the Thesis Organization                                 | 3  |

| 1.4 Research Approach, Assumptions and Limitations                      | 4  |

| Chapter 2: Power Divider Design Fundamentals                            | 5  |

| 2.1 Power Divider Basics                                                | 5  |

| 2.2 Wilkinson Power Divider                                             | 6  |

| 2.3 Power Divider with Unequal Power Division                           | 8  |

| 2.4 Multi-way Power Divider                                             |    |

| 2.4.1 Wilkinson N-way Hybrid                                            | 0  |

| 2.4.2 Radial Hybrid                                                     | 1  |

| 2.4.3 Fork Hybrid                                                       | 2  |

| 2.4.4 Multi-layer Approach                                              | 3  |

| 2.4.5 Power Recombination Concept                                       | 5  |

| 2.4.6 Multi-coupled-line Approach                                       | 8  |

| Chapter 3: Conventional Power Divider Designs with Harmonic Suppression | 20 |

| 3.1                  | Resonating-stubs Topology                                                          |

|----------------------|------------------------------------------------------------------------------------|

| 3.2                  | Asymmetric Defected Ground Structure (DGS)                                         |

| 3.3                  | Anti-Coupled Line Structure                                                        |

| 3.4                  | Microstrip Electromagnetic Bandgap (EBG) Based Topology                            |

| 3.5                  | Embedded Resonators Topology                                                       |

| 3.6                  | Extended Line Approach                                                             |

|                      | 4: New 2-way Power Divider Design with Spurious Suppression and nee Transformation |

| 4.1                  | Proposed Topology                                                                  |

| 4.2                  | Design and Analysis                                                                |

| 4.3                  | Simulation Study                                                                   |

| 4.4                  | Experimental Verification                                                          |

| 4.5                  | Summary                                                                            |

| Chapter<br>Suppres   | 5: New 2-way Power Divider Design with Extended Spurious<br>ssion                  |

| 5.1                  | Proposed Topology                                                                  |

| 5.2                  | Design and Analysis                                                                |

| 5.3                  | Simulation Study                                                                   |

| 5.3                  | Experimental Verification                                                          |

| 5.4                  | Summary                                                                            |

| Chapter<br>Rejection | r 6: New 2-way Unequal Power Divider Design with Dual-harmonic<br>on               |

| 6.1                  | Proposed Topology                                                                  |

| 6.2                  | Design and Analysis                                                                |

| 6.3                  | Simulation Study                                                                   |

| 6.4                  | Experimental Verification77                                                        |

| 6.4                  | Summary                                                                            |

| Chapte               | r 7: New 3-way Power Divider Design with Multi-harmonic Rejection 81               |

•

| 7.1     | Proposed Topology                                                    |

|---------|----------------------------------------------------------------------|

| 7.2     | Design and Analysis                                                  |

| 7.3     | Simulation Study                                                     |

| 7.4     | Experimental Verification                                            |

| 7.4     | Summary                                                              |

| Chapter | 8: Conclusion                                                        |

| Referen | ices                                                                 |

| Author  | 's Publications and Awards                                           |

| Append  | lix 1: ABCD Parameters of Some Useful Two-port Circuits              |

| Append  | lix 2: More Designs of Proposed Configuration in Chapter 597         |

| A2.3    | Miniaturized version of Example 197                                  |

| A2.2    | 2 Design with improved stop-band response                            |

| A2.3    | B Design of prototype with 2 GHz operating frequency                 |

| Append  | dix 3: Brief Summary of Power Dividers with Harmonic Suppression 108 |

|         |                                                                      |

# **Lists of Figures**

| Figure 2.1 Power division and combination: (a) Power division. (b) Power combination                                                                                                                                                  |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.2 Schematic of Wilkinson power divider6                                                                                                                                                                                      |    |

| Figure 2.3 Even-mode excitation7                                                                                                                                                                                                      |    |

| Figure 2.4 Odd-mode excitation7                                                                                                                                                                                                       |    |

| Figure 2.5 Frequency response of a typical 3dB Wilkinson power divider                                                                                                                                                                |    |

| Figure 2.6 Wilkinson power divider with unequal power division                                                                                                                                                                        | ;  |

| Figure 2.7 Broadband unequal power divider9                                                                                                                                                                                           | )  |

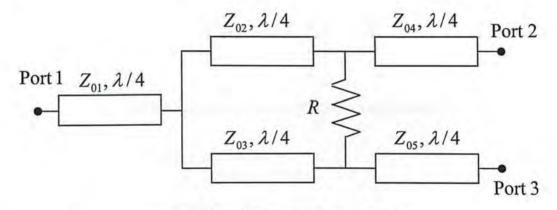

| Figure 2.8 Equivalent circuit of Wilkinson N-way Hybrid                                                                                                                                                                               | )  |

| Figure 2.9 3D shape of Wilkinson N-way Hybrid10                                                                                                                                                                                       | )  |

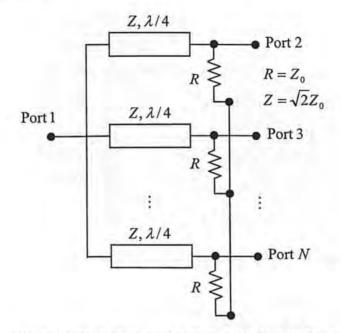

| Figure 2.10 The radial N-way hybrid power divider/ combiner                                                                                                                                                                           | ĺ, |

| Figure 2.11 The schematic diagram of the single-stage radial N-way hybrid                                                                                                                                                             | l  |

| Figure 2.12 The fork N-way hybrid power divider/ combiner                                                                                                                                                                             | 2  |

| Figure 2.13 The schematic diagram of the single-stage fork N-way hybrid                                                                                                                                                               | 2  |

| Figure 2.14 The schematic diagram of the M-stage fork N-way hybrid                                                                                                                                                                    | 3  |

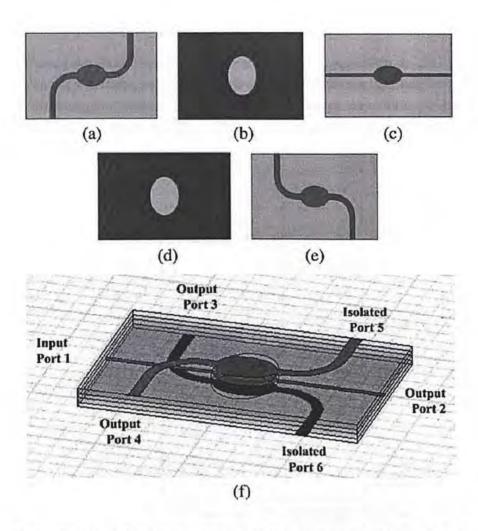

| Figure 2.15 Configuration of the three-way power divider: (a) top layer, (b) second layer (ground with coupling slot), (c) mid layer, (d) fourth layer (ground with coupling slot), (e) bottom layer, and (f) the whole configuration | 4  |

| Figure 2.16 Three-way recombinant power divider1                                                                                                                                                                                      | 5  |

| Figure 2.17 Recombinant power divider 1                                                                                                                                                                                               |    |

| Figure 2.18 Equivalent circuit for synthesis of a three-way divider under in-phase excitation                                                                                                                                         | 6  |

| Figure 2.19 Schematic diagram of three-way power divider form Chiu et al                                                                                                                                                              | 8  |

| Figure 2.20 Schematic diagram of the new three-way power divider 1                                                                                                                                                                    | 9  |

| Figure 3.1 Schematic diagram of the Wilkinson power divider for <i>n</i> th harmonic suppression                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.2 Photograph of fabricated 2 GHz Wilkinson power divider for third harmonic suppression                                                     |

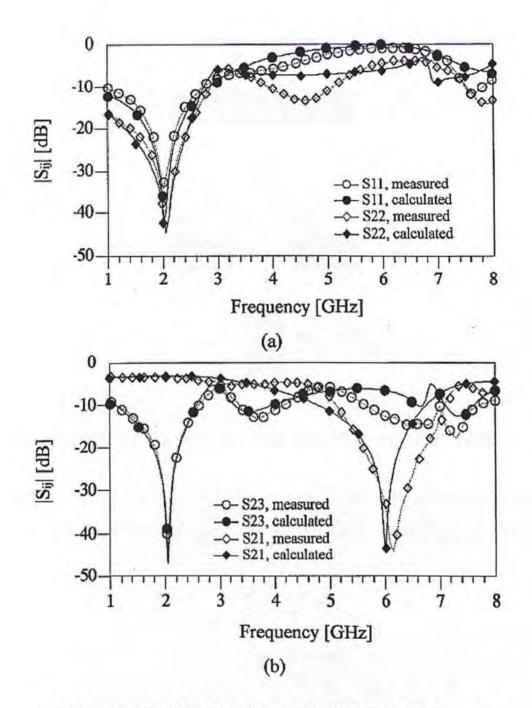

| Figure 3.3 Measured and Simulated S-parameters: (a) $S_{11}$ and $S_{22}$ ; (b) $S_{23}$ and $S_{21}$ 22                                             |

| Figure 3.4 Structure of (a) the $\lambda/4$ conventional TL and (b) an equivalent T-shaped TL                                                        |

| Figure 3.5 The new power divider with harmonic rejection: (a) Schematic; (b)<br>Photograph                                                           |

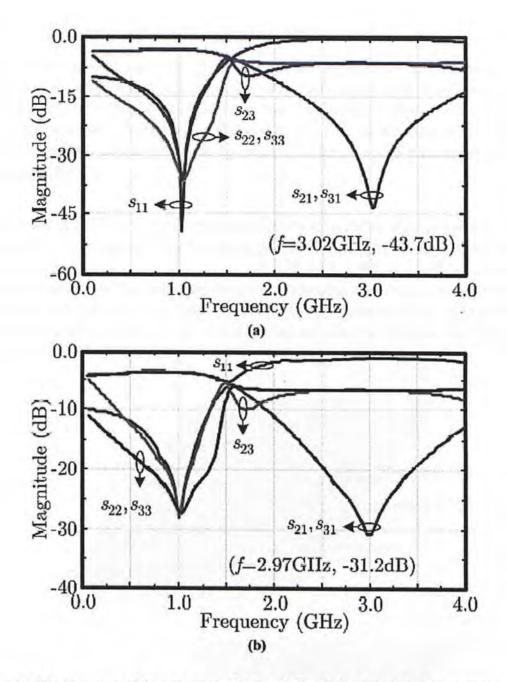

| Figure 3.6 Performances of the new power divider: (a) Simulation results; (b)<br>Meaasured results                                                   |

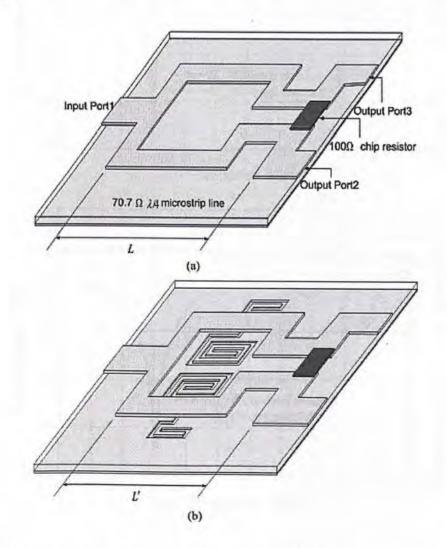

| Figure 3.7 Structure of (a) Wilkinson power divider; (b) power divider using asymmetric DGS                                                          |

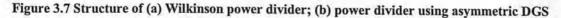

| Figure 3.8 Simulated S-parameters of (a) original Wilkinson power divider; (b) power divider using asymmetric DGS                                    |

| Figure 3.9 Fabricated 3-dB Wilkinson power divider with asymmetric spiral DGS. (a)<br>Top view; (b) Bottom view                                      |

| Figure 3.10 Measured S-paramters of the fabricated divider: (a) S <sub>11</sub> ; (b) S <sub>21</sub>                                                |

| Figure 3.11 Layout of a short circuit anti-coupled line                                                                                              |

| Figure 3.12 Photograph of the divider using anti-cooupled line (right) and conventional power divider                                                |

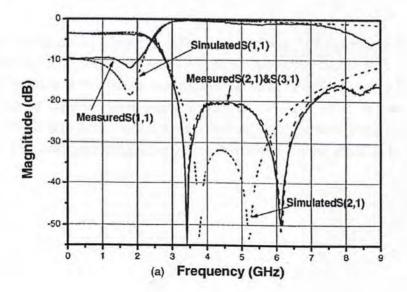

| Figure 3.13 Frequency responses of the power divider: (a) at whole frequency band;<br>(b) at frequency band near the operating frequency             |

| Figure 3.14 Schematic diagram of the power divider using EBG cells                                                                                   |

| Figure 3.15 Structure of a microstrip EBG cell                                                                                                       |

| Figure 3.16 Equivalent L-C circuit of a microstrip EBG cell                                                                                          |

| Figure 3.17 Photograph of the power divider with EBG cells                                                                                           |

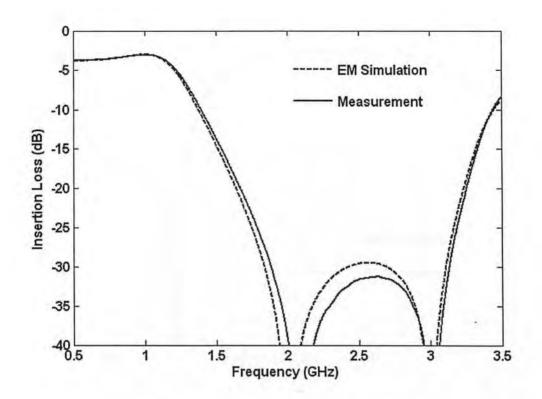

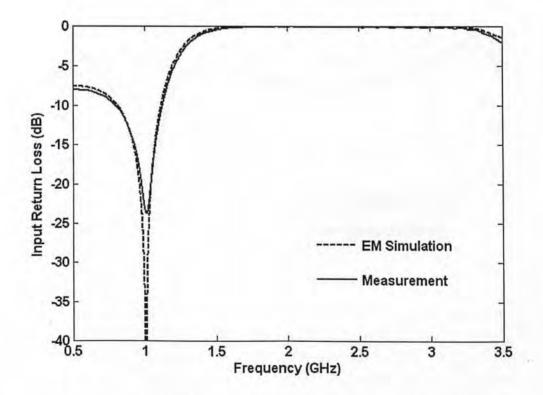

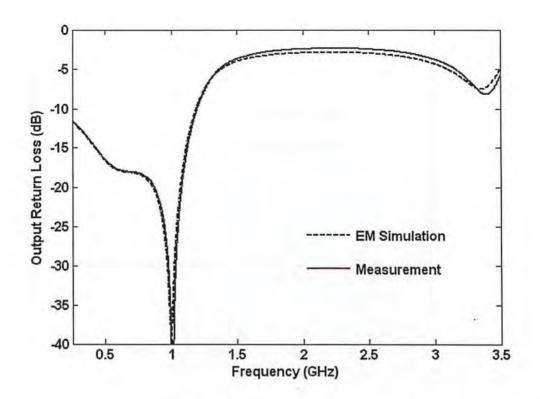

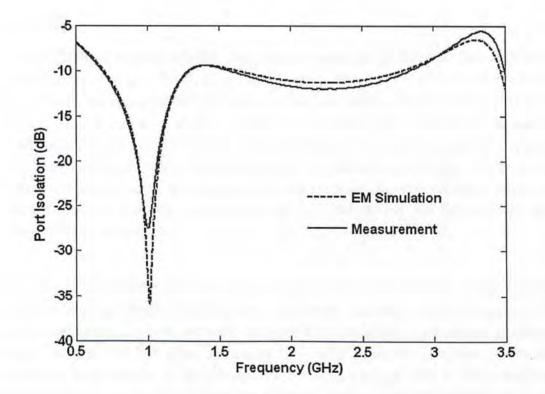

| Figure 3.18 Frequency responses for the power divider using EBG cells: (a) Insertion loss; (b) Input / output return loss; (c) Output port isolation |

| Figure 3.19 Configuration of the power divider using embedded resonators                                                                             |

| Figure 3.20 Photograph of the divider using embedded resonators                                                                                      |

| Figure 3.21 Frequency responses for the power divider using embedded resonators: (a) Insertion loss; (b) Input return loss; (c) Output port isolation |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.22 Modified two-way Wilkinson power divider                                                                                                  |

| Figure 3.23 Photograph of the modified Wilkinson power divider                                                                                        |

| Figure 3.24 Frequency responses of the power divider with extended lines: (a) $S_{21}$ and $S_{23}$ ; (b) $S_{11}$ and $S_{22}$                       |

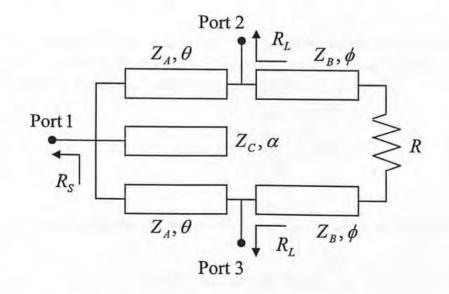

| Figure 4.1 Circuit configuration of proposed power divider                                                                                            |

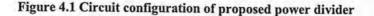

| Figure 4.2 Equivalent circuit: even-mode                                                                                                              |

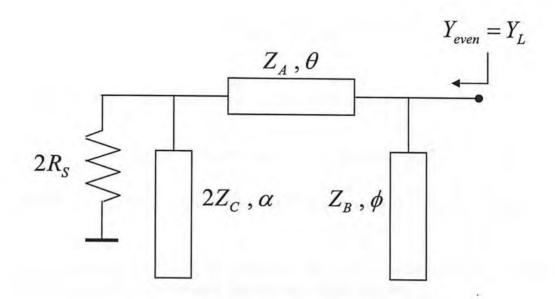

| Figure 4.3 Equivalent circuit: odd-mode                                                                                                               |

| Figure 4.4 Line impedance and length versus $\beta$                                                                                                   |

| Figure 4.5 Simulated responses of the proposed divider                                                                                                |

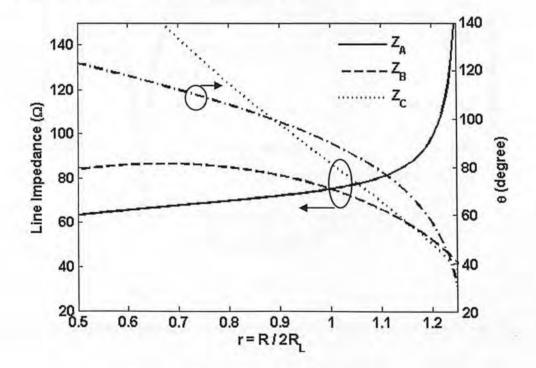

| Figure 4.6 Calculated circuit parameters versus r                                                                                                     |

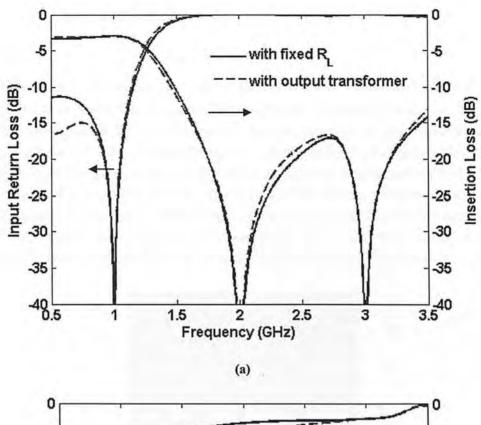

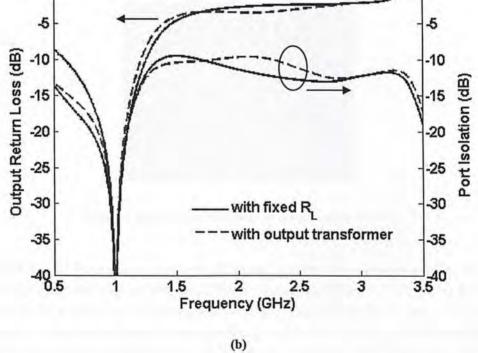

| Figure 4.7 Simulated frequency responses of the proposed divider with $r = 1.21$ , $R_{\rm S} = 50 \Omega$ , and $R_{\rm L} = 75 \Omega$              |

| Figure 4.8 Simulated responses of the proposed divider                                                                                                |

| Figure 4.9 Simulated and measured insertion loss                                                                                                      |

| Figure 4.10 Simulated and measured input return loss                                                                                                  |

| Figure 4.11 Simulated and measured output return loss                                                                                                 |

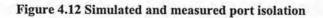

| Figure 4.12 Simulated and measured port isolation                                                                                                     |

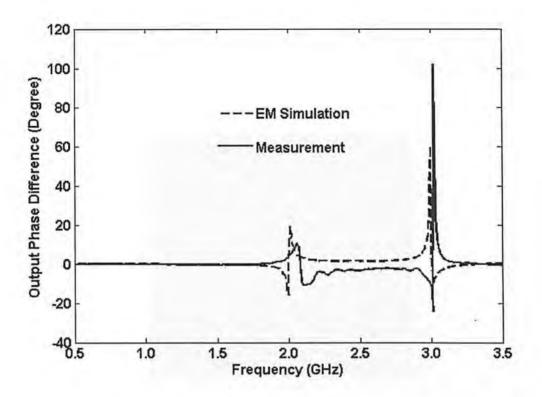

| Figure 4.13 Simulated and measured output phase difference                                                                                            |

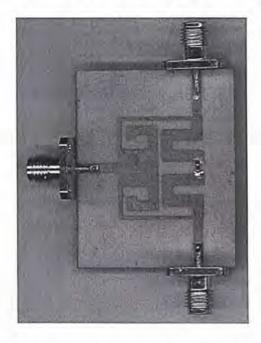

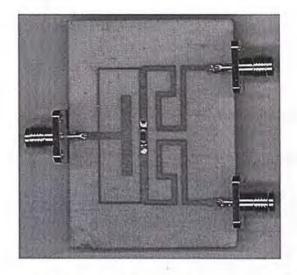

| Figure 4.14 Photograph of the prototype (Example 2)                                                                                                   |

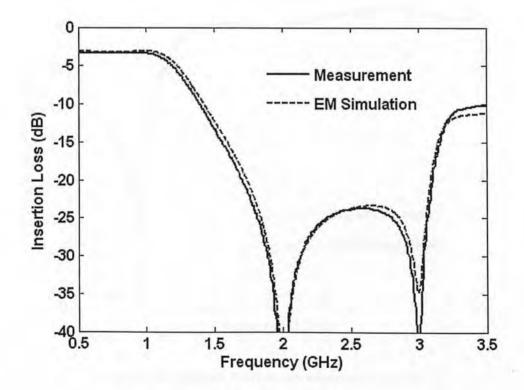

| Figure 4.15 Simulated and measured insertion loss                                                                                                     |

| Figure 4.16 Simulated and measured input return loss                                                                                                  |

| Figure 4.17 Simulated and measured output return loss                                                                                                 |

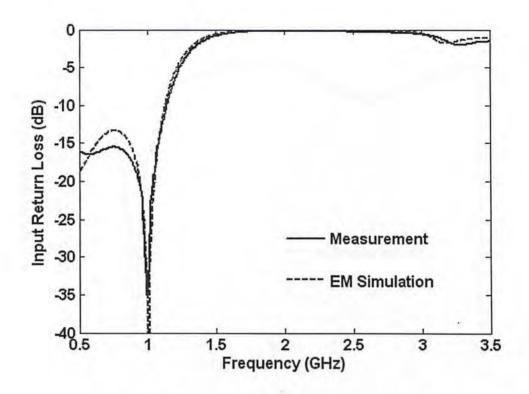

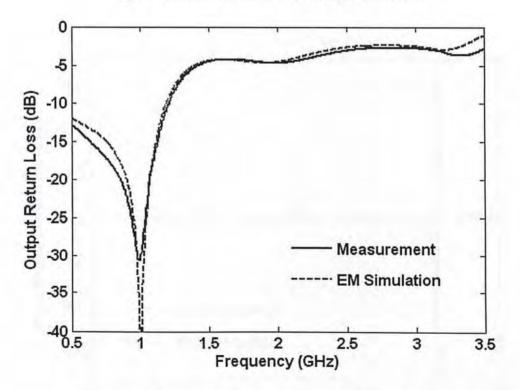

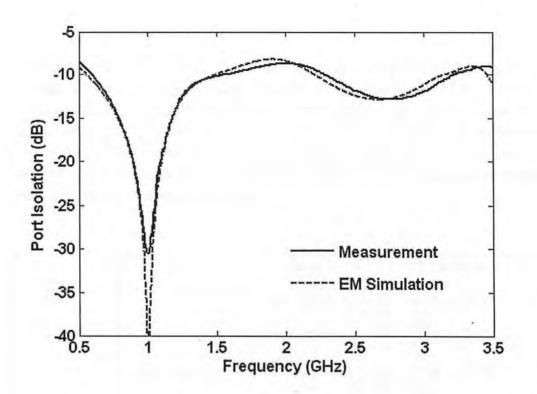

| Figure 4.18 Simulated and measured port isolation                                                                                                     |

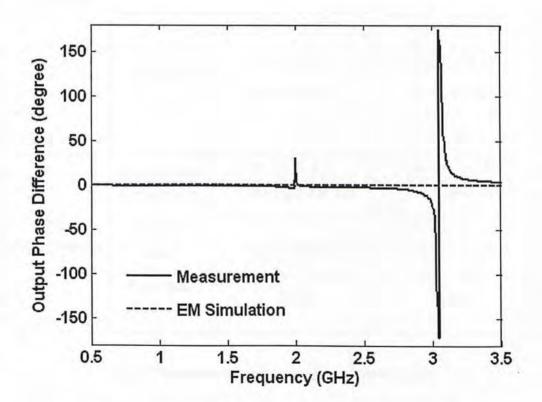

| Figure 4.19 Simulated and measured output phase difference                                                                                            |

| Figure 5.1 Circuit configuration of proposed power divider                                                                                            |

| Figure 5.2 Equivalent circuit: even-mode                                                                                                              |

| Figure 5.3 Equivalent circuit: odd-mode61                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

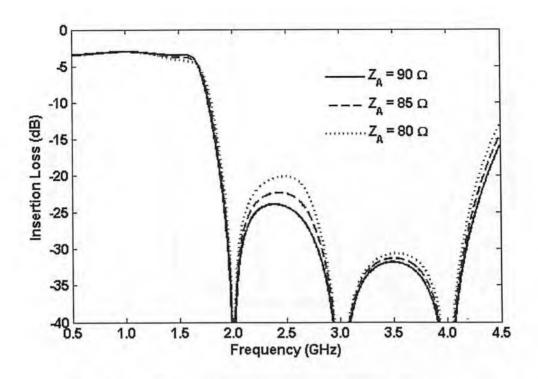

| Figure 5.4 Insertion loss of the proposed structure with different choices of $Z_A$ 64                                                                                                                                                                                                                                                               |

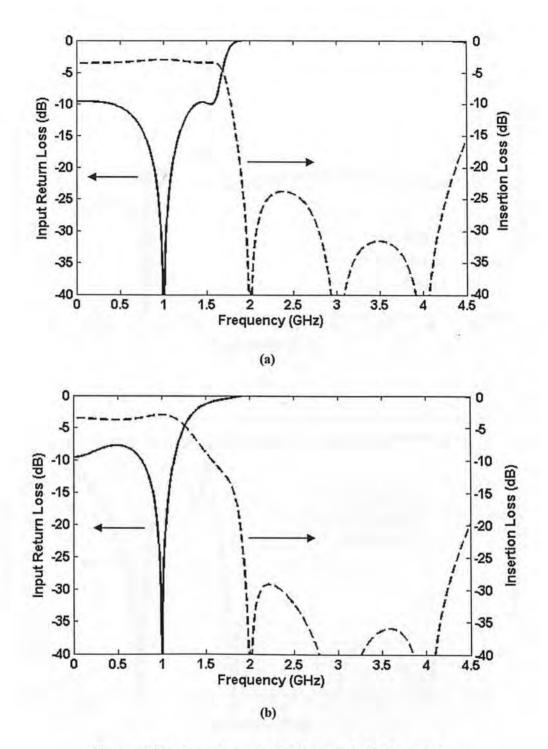

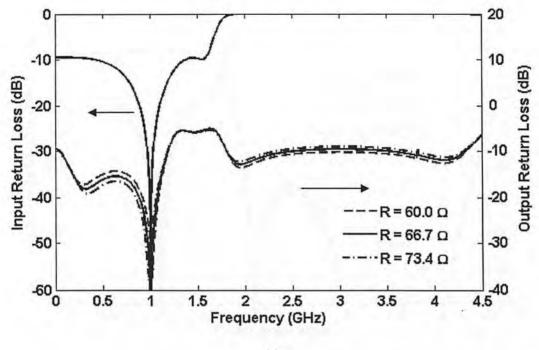

| Figure 5.5 Simulated responses: (a) Example 1, (b) Example 265                                                                                                                                                                                                                                                                                       |

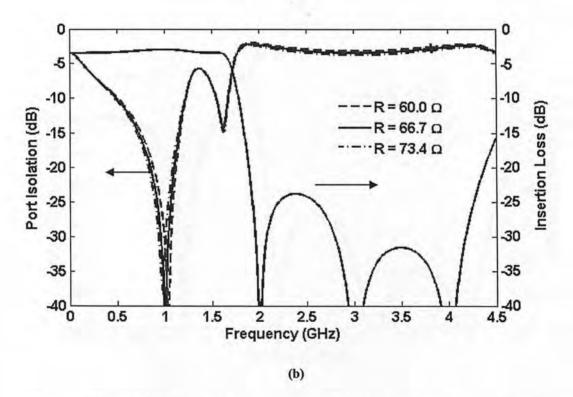

| Figure 5.6 Simulated circuit performances versus <i>R</i> : (a) input and output return loss, (b) insertion loss and port isolation                                                                                                                                                                                                                  |

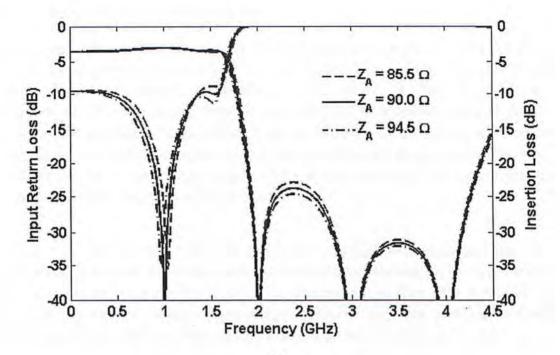

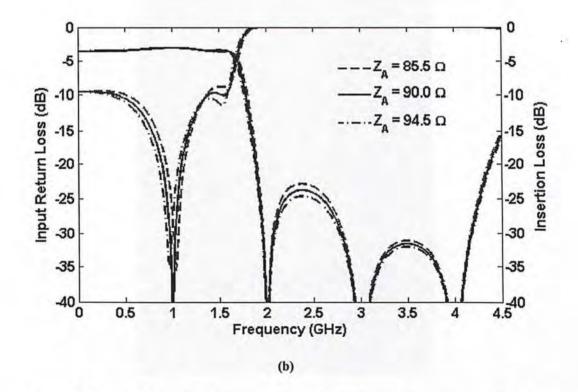

| Figure 5.7 Simulated circuit performances versus Z <sub>A</sub> : (a) input and output return loss, (b) insertion loss and port isolation                                                                                                                                                                                                            |

| Figure 5.8 Photograph of the prototype (Example 1)                                                                                                                                                                                                                                                                                                   |

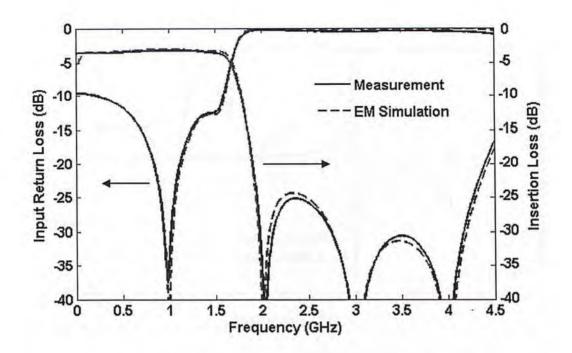

| Figure 5.9 Simulated and measured insertion loss and input return loss                                                                                                                                                                                                                                                                               |

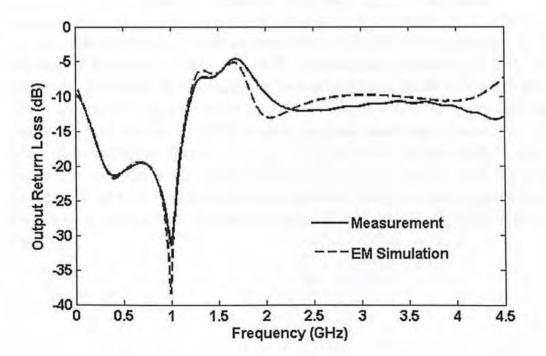

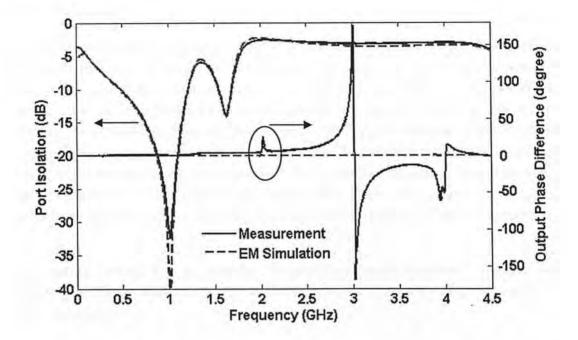

| Figure 5.10 Simulated and measured output return loss                                                                                                                                                                                                                                                                                                |

| Figure 5.11 Simulated and measured port isolation and output phase difference 70                                                                                                                                                                                                                                                                     |

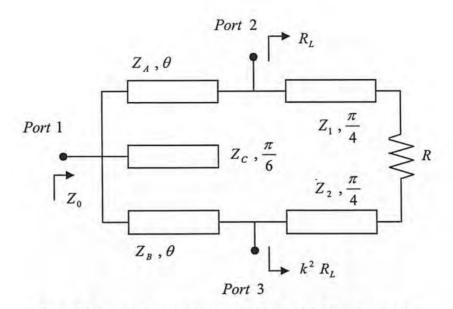

| Figure 6.1 Proposed unequal power divider with harmonic rejection                                                                                                                                                                                                                                                                                    |

| Figure 6.2 Circuit representation of the proposed divider evaluated at $2f_0$                                                                                                                                                                                                                                                                        |

| Figure 6.3 Equivalent circuit with in-phase excitation74                                                                                                                                                                                                                                                                                             |

| Figure 6.4 Equivalent circuit with anti-phase excitation                                                                                                                                                                                                                                                                                             |

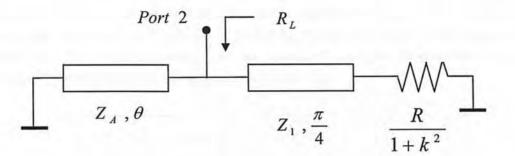

| Figure 6.5 Computed line impedances versus power dividing ratio: (a) $R_L = 35 \Omega$ , $R = 100 \Omega$ ; (b) $R_L = 40 \Omega$ , $R = 70 \Omega$                                                                                                                                                                                                  |

| Figure 6.6 Simulated frequency responses (power dividing ratio of 2)                                                                                                                                                                                                                                                                                 |

| Figure 6.7 Photograph of the prototype                                                                                                                                                                                                                                                                                                               |

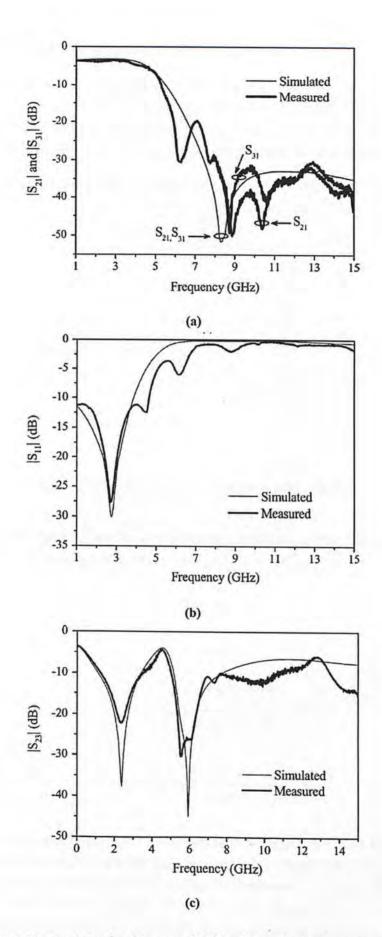

| Figure 6.8 Measured S-parameters: (a) input return loss and port isolation, (b) & (c) output return loss and insertion loss                                                                                                                                                                                                                          |

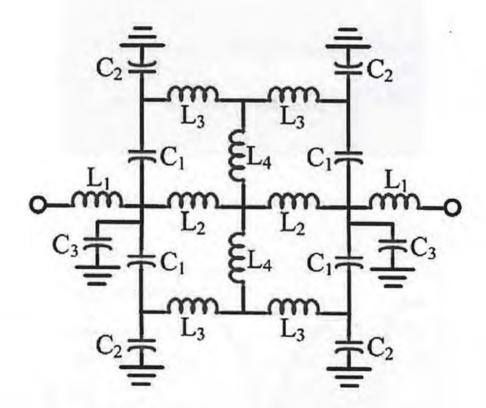

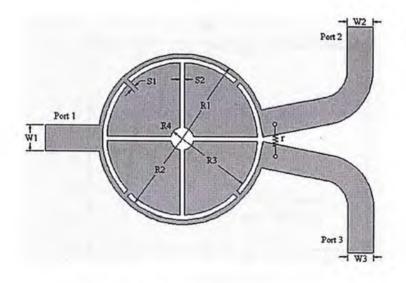

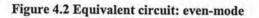

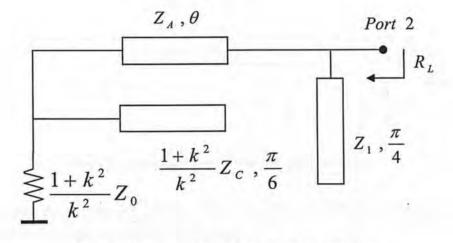

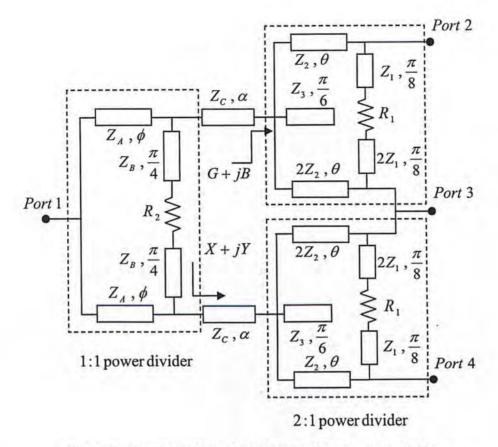

| Figure 7.1 Circuit configuration of proposed 3-way power divider                                                                                                                                                                                                                                                                                     |

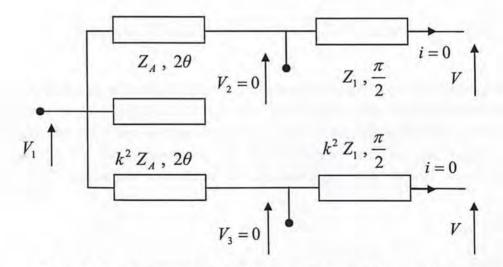

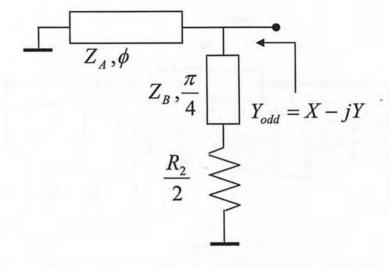

| Figure 7.2 1:1 power divider: (a) odd- and (b) even-mode                                                                                                                                                                                                                                                                                             |

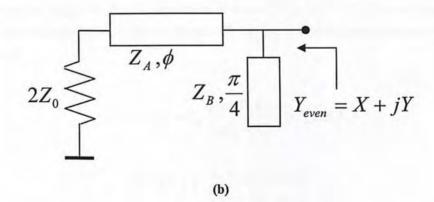

| Figure 7.3 2:1 power divider: (a) odd- and (b) even-mode                                                                                                                                                                                                                                                                                             |

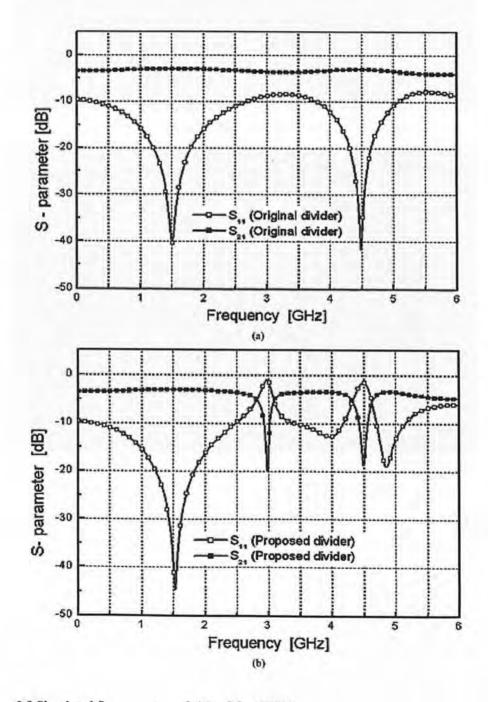

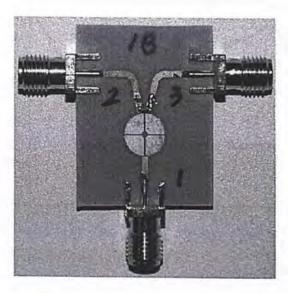

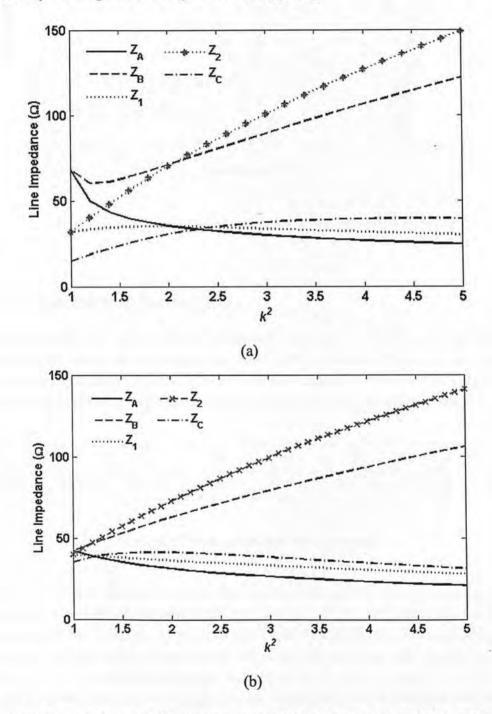

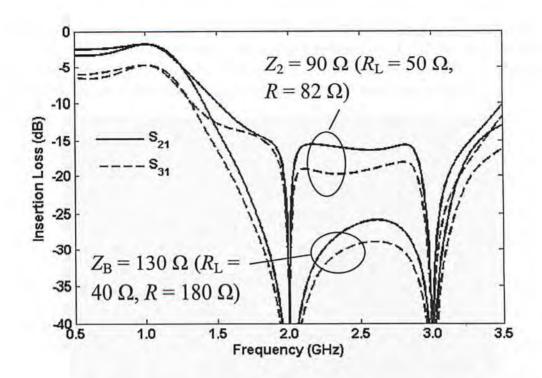

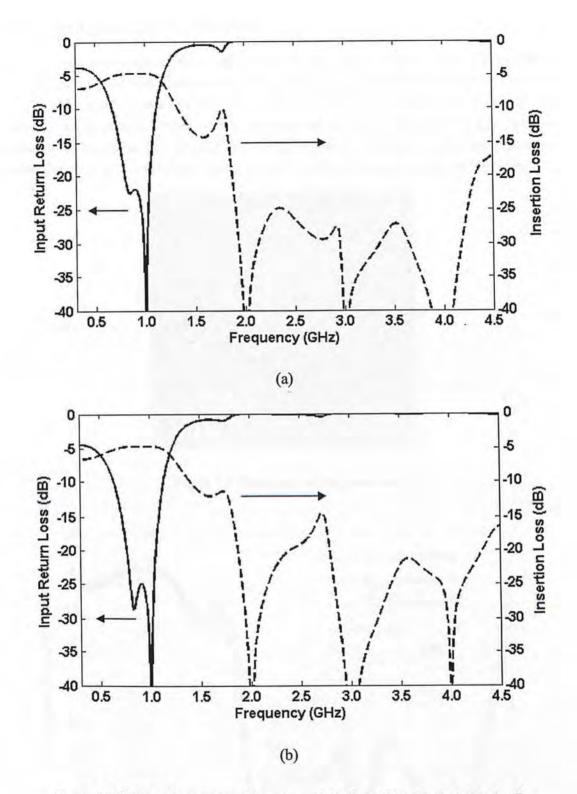

| Figure 7.4 Simulated responses of the proposed divider: (a) Design A; (b) Design B86                                                                                                                                                                                                                                                                 |

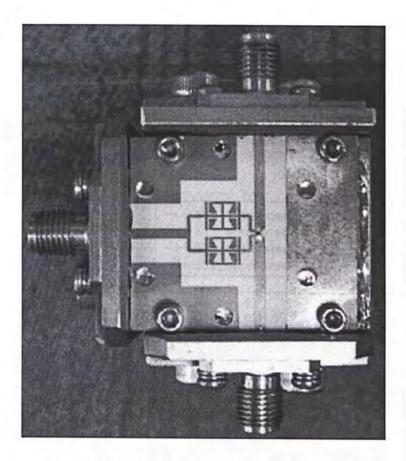

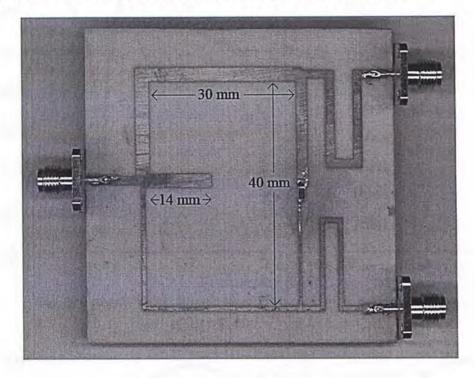

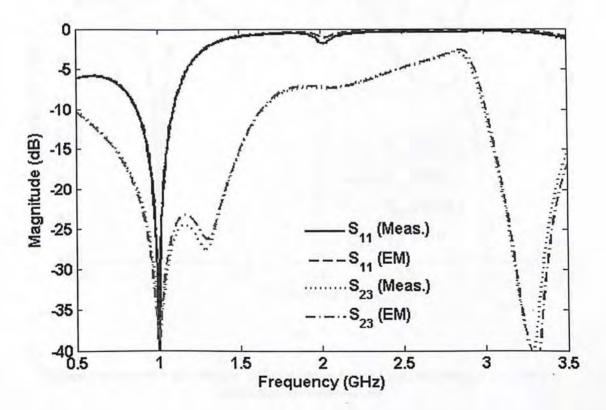

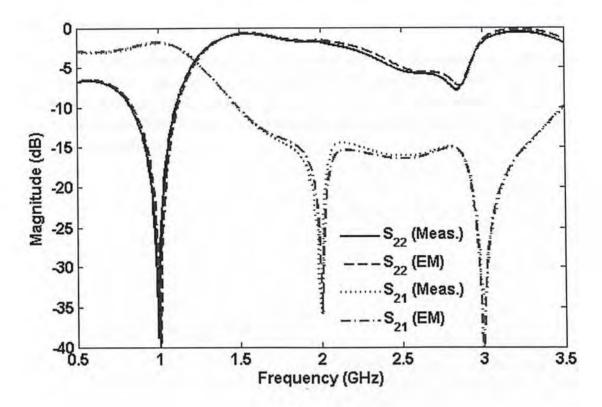

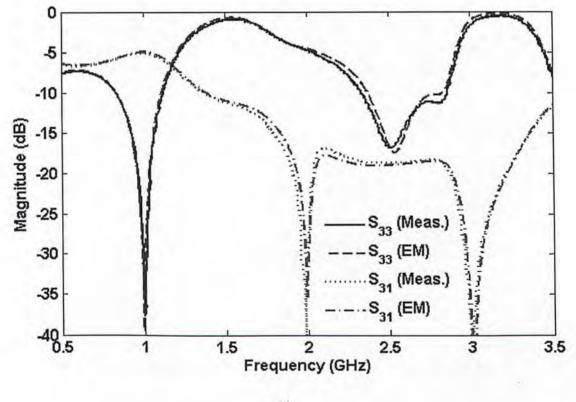

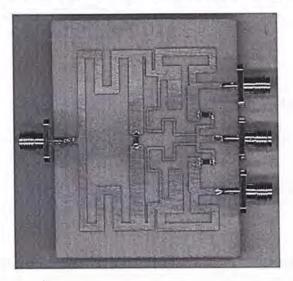

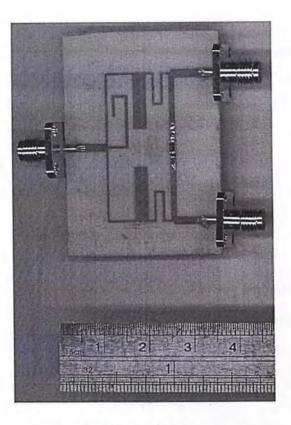

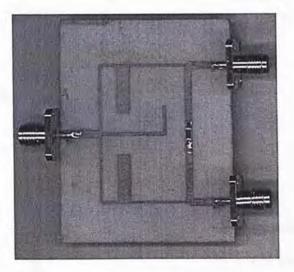

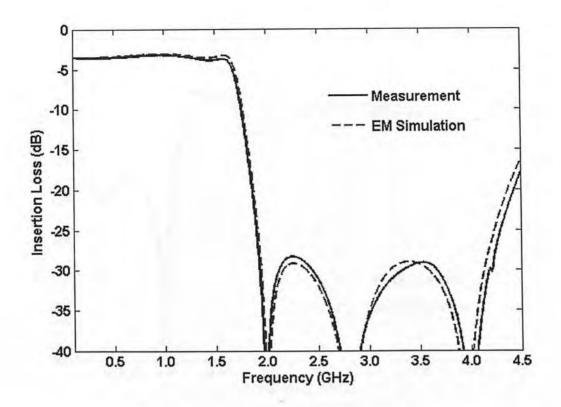

| Figure 7.5 Photograph of the prototype                                                                                                                                                                                                                                                                                                               |

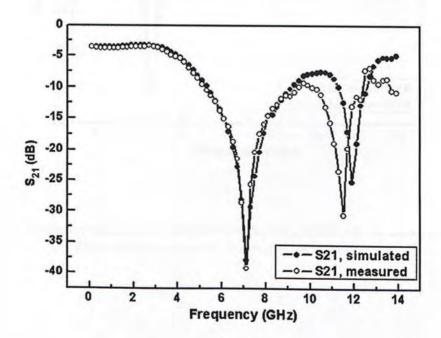

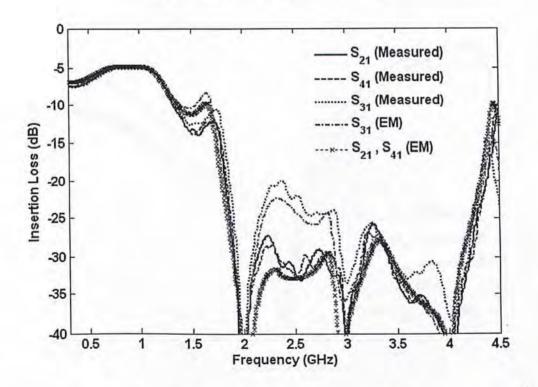

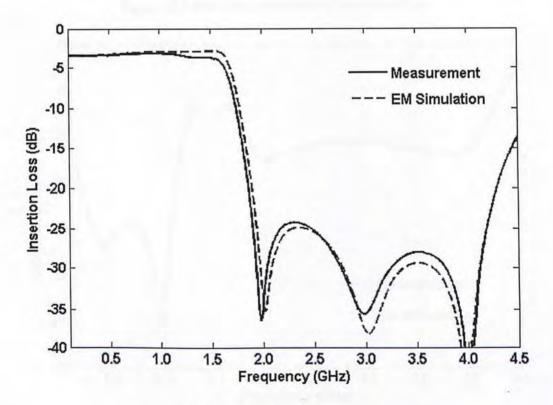

| Figure 7.6 Simulated and measured insertion loss                                                                                                                                                                                                                                                                                                     |

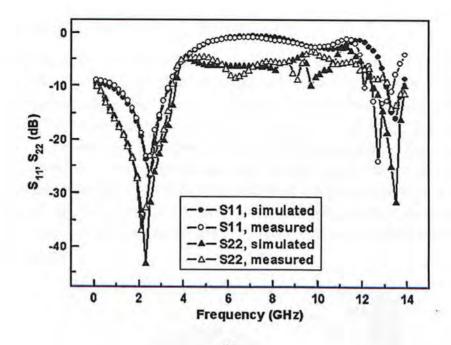

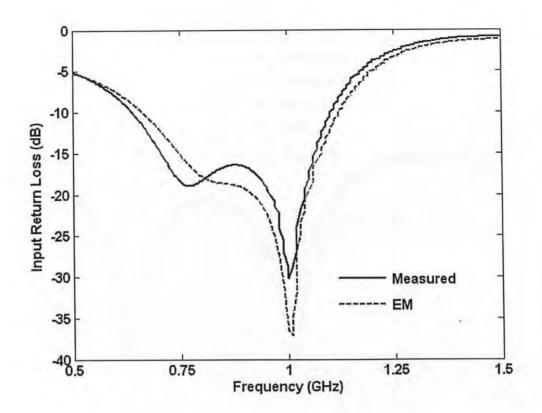

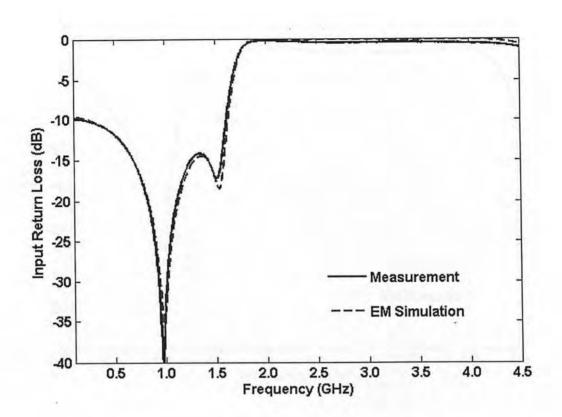

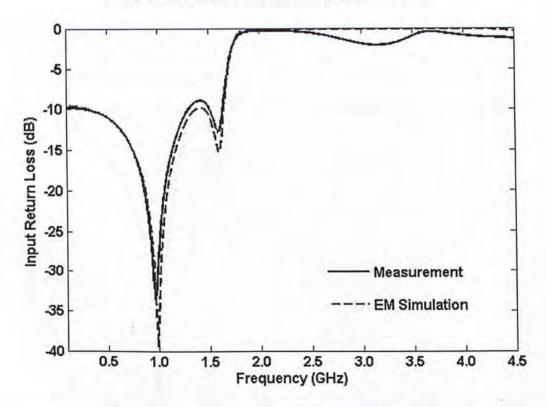

| Figure 7.7 Simulated and measured input return loss                                                                                                                                                                                                                                                                                                  |

| <ul> <li>Figure 7.2 1:1 power divider: (a) odd- and (b) even-mode</li> <li>Figure 7.3 2:1 power divider: (a) odd- and (b) even-mode</li> <li>Figure 7.4 Simulated responses of the proposed divider: (a) Design A; (b) Design B</li> <li>Figure 7.5 Photograph of the prototype</li> <li>Figure 7.6 Simulated and measured insertion loss</li> </ul> |

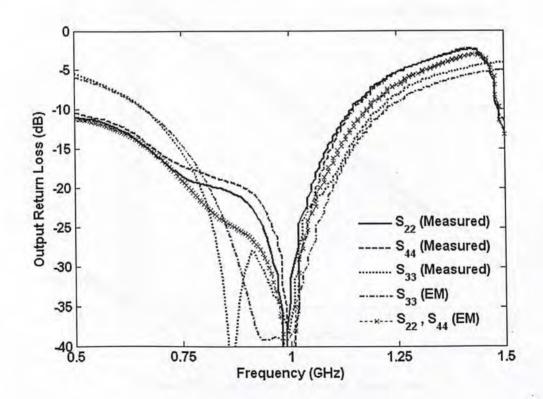

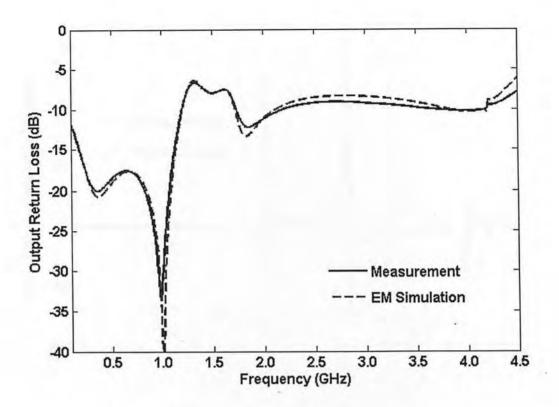

| Figure 7.8 Simulated and measured output return loss                       |

|----------------------------------------------------------------------------|

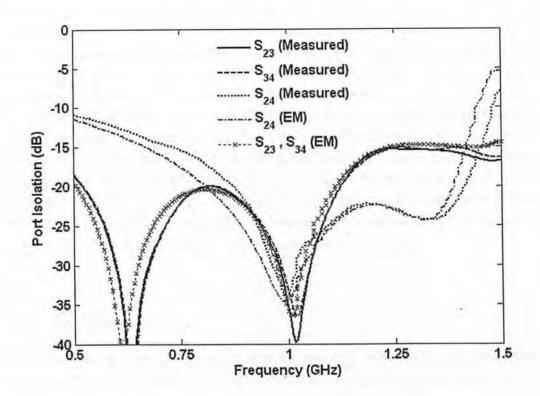

| Figure 7.9 Simulated and measured port isolation                           |

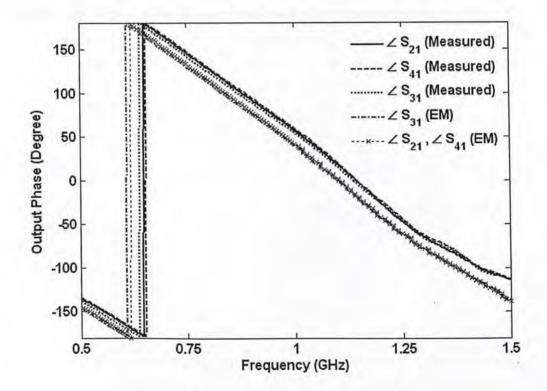

| Figure 7.10 Simulated and measured output phase                            |

| Figure A2.1 Photograph of the prototype                                    |

| Figure A2.2 Simulated and measured insertion loss                          |

| Figure A2.3 Simulated and measured input return loss                       |

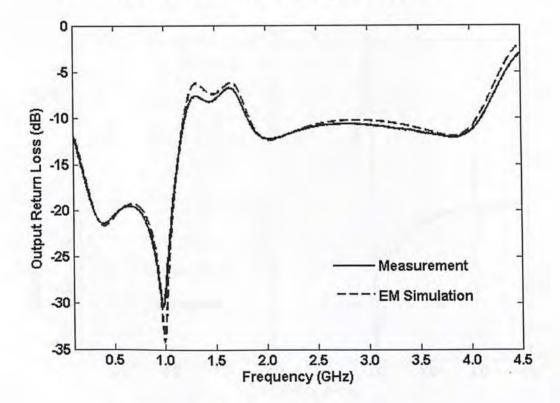

| Figure A2.4 Simulated and measured output return loss                      |

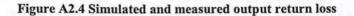

| Figure A2.5 Simulated and measured port isolation                          |

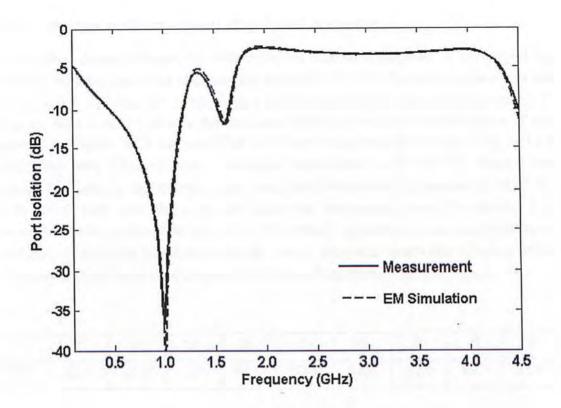

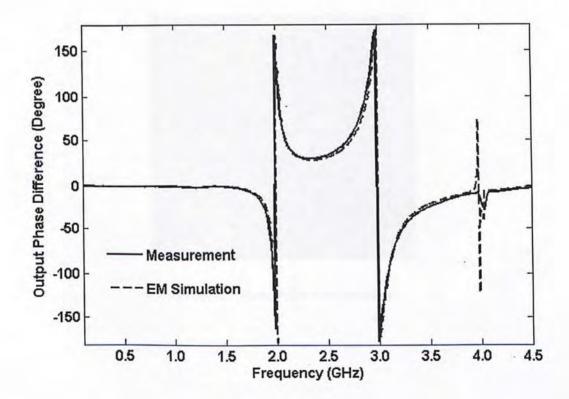

| Figure A2.6 Simulated and measured output phase difference                 |

| Figure A2.7 Photograph of the prototype                                    |

| Figure A2.8 Simulated and measured insertion loss                          |

| Figure A2.9 Simulated and measured input return loss                       |

| Figure A2.10 Simulated and measured output return loss 103                 |

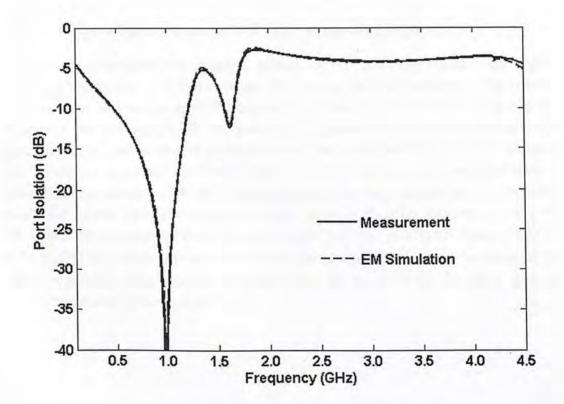

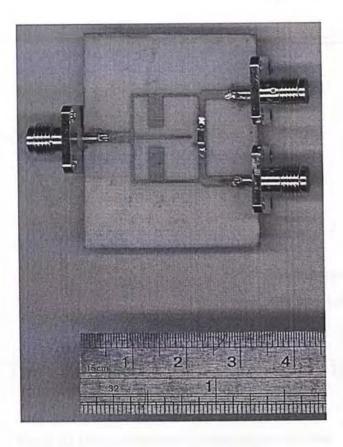

| Figure A2.11 Simulated and measured port isolation103                      |

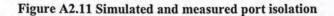

| Figure A2.12 Simulated and measured output phase difference                |

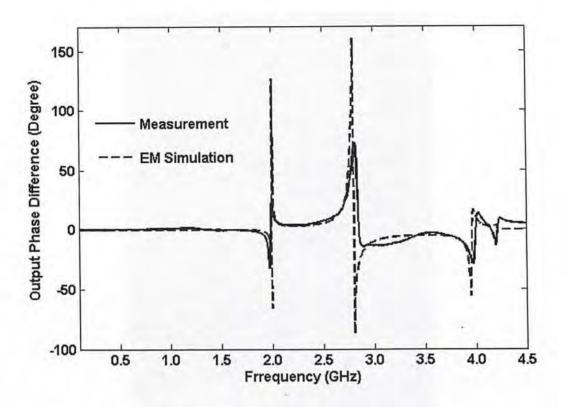

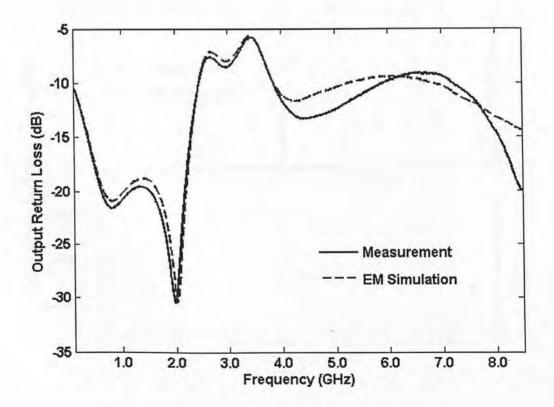

| Figure A2.13 Photograph of the prototype with centre frequency at 2 GHz105 |

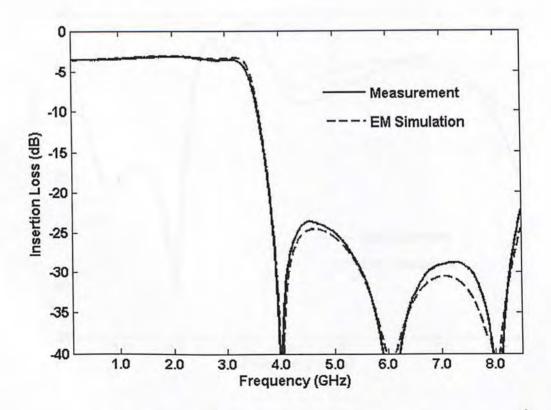

| Figure A2.14 Simulated and measured insertion loss                         |

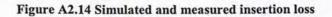

| Figure A2.15 Simulated and measured input return loss                      |

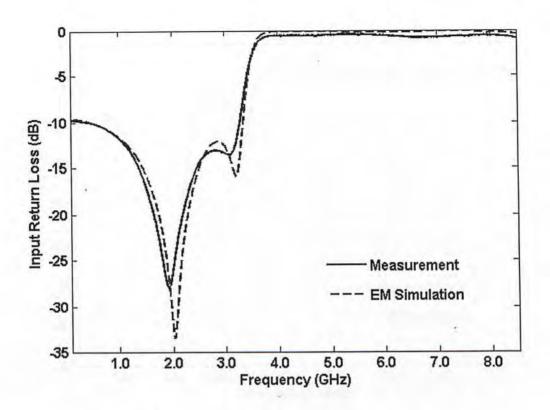

| Figure A2.16 Simulated and measured output return loss                     |

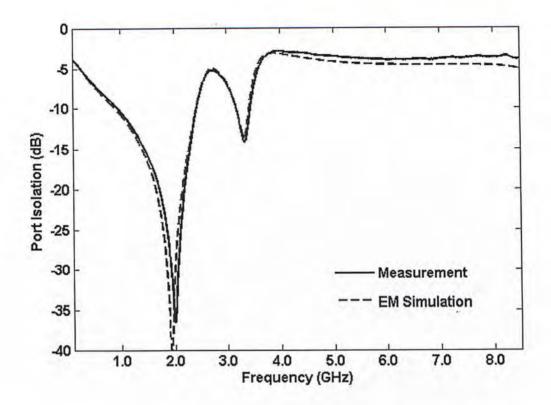

| Figure A2.17 Simulated and measured port isolation                         |

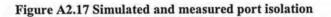

| Figure A2.18 Simulated and measured output phase difference                |

|                                                                            |

## **Lists of Tables**

| Table 4.1 Circuit parameters of the proposed power divider (Example 1)       45 |

|---------------------------------------------------------------------------------|

| Table 4.2 Circuit parameters of the proposed power divider (Example 2)       48 |

| Table 4.3 Summary of the proposed power divider design    57                    |

| Table 5.1 Circuit parameters of illustrative designs    64                      |

| Table 6.1 Circuit parameters of the prototype    77                             |

| Table 7.1 Circuit parameters of design examples                                 |

| Table A1.1 ABCD Parameters of Some Useful Two-port Circuits       96            |

| Table A2.1 Circuit parameters of the prototype    97                            |

| Table A2.2 Circuit parameters of the prototype    101                           |

| Table A3.1 Brief summary of different power dividers    108                     |

### **Chapter 1:** Introduction

#### 1.1 Research Motivation and Objective

This is a High Technology Era. Electronic devices are widely used in the community. Mobile communication devices such as portable computers and mobile phones are closely related to our daily life. The quality of electronic products increases with advances in technology. For instant, the mobile phone, from the first to the third generation, has a general decrease in its size and weight. Faster, lighter and cheaper will be the trends of electronic products. Devices with multiple functions are expected to gain even more attention in research and development. This highlights the motivation behind this work.

Power dividers and combiners are frequently adopted in various microwave applications such as the feeding network for an antenna array, the signal splitting/combining networks for power amplifying stage, mixers and frequency multipliers. It is made available both in the form of lumped-element and distributed structures. However, the major drawback of the conventional Wilkinson power divider is the presence of spurious response due to the adoption of quarter-wavelength transmission lines. If the power divider or combiner structure is able to suppress the unwanted harmonics, a separate harmonic rejection filter will then be eliminated from the microwave circuit and a compact RF-system could be implemented.

In the past, this problem has been partially overcome [1-8] by using Defected Ground Structure (DGS) or Electromagnetic Band-Gap (EBG) cells, for the suppression of one or two harmonic frequency bands. Unfortunately, these circuits usually require either backside etching or additional lumped reactive element, which is undesirable for low-cost and mass production environment. Moreover, explicit design formulas are often not available and the desired responses are mainly obtained by computer optimization [4-8]. In [1-3], modified Wilkinson divider structures based upon either shunt stub or extended line were demonstrated for third-harmonic suppression.

Moreover, these topologies only offer harmonic suppression with equal output power and no more than two output ports. The main objective of this work is to propose new types of power divider with multi-functions including unequal power division, multioutputs, impedance transformation and enhanced spurious suppression, using standard microstrip technology.

#### 1.2 Original Contribution

This thesis presents four new and original power divider topologies with distinctive features. These include:

1) 2-way Power Divider Design with Spurious Suppression and Impedance Transformation

- Compact size, simple structure and flexible layout

- > Low insertion loss

- Enhanced stop-band attenuation (> 30 dB)

- Impedance transformation

- 2) 2-way Power Divider Design with Extended Spurious Suppression

- Simple structure, flexible layout and compact size

- > Moderate line impedance  $(30 \Omega 90 \Omega)$

- Large fundamental bandwidth (almost 25%)

- > Wide spurious suppression bandwidth (over an octave)

- Low insertion loss

- 3) 2-way Unequal Power Divider Design with Dual-harmonic Rejection

- Simple structure, compact size and flexible layout

- Power dividing ratio up to 4:1

- Stop-band attenuation (15 dB)

- Low insertion loss

- 4) 3-way Power Divider Design with Multi-harmonic Rejection

- Simple, compact structure and flexible layout

- Multiple outputs with equal power ratio

- Large fundamental bandwidth (almost 30%)

- > Enhanced spurious attenuation (> 20 dB) over an octave frequency range

- Low insertion loss

#### 1.3 Overview of the Thesis Organization

This thesis focuses on the work of advanced microwave power divider designs with harmonic suppression. It is divided into eight chapters.

The first chapter begins with a brief introduction of the research motivation and objective, followed by a list of original designs, an overview of this thesis, and concludes with a statement of the necessary assumptions and limitations for later study.

Chapter 2 briefly describes the fundamentals of power dividers such as operating principles, method of analyses, and practical limitations.

Chapter 3 reviews and compares different design approaches of conventional power dividers.

Chapter 4 describes a new 2-way power divider design with spurious suppression and impedance transformation. Design equations are derived. Electromagnetic (EM) simulations were carried out to tackle the effects of junction discontinuities. Two prototypes of power divider were fabricated and measured.

Chapter 5 presents another 2-way power divider design with extended spurious suppression. This design offers enhanced spurious attenuation (> 25 dB) over an octave frequency range with the presence of three controllable transmission zeros. Design equations are derived and verified by circuit simulation, and experimental results.

Chapter 6 discusses the design of 2-way unequal power divider with dual-harmonic rejection. Closed-form design expressions are given for the evaluation of circuit parameters. Trade-off between the line impedances and spurious response is studied. Both simulation and measurement results are presented.

Chapter 7 gives the design of 3-way power divider with multi-harmonic rejection. The number of circuit parameters to be optimized is largely reduced by analytical formulation. This design offers wide fundamental bandwidth, low insertion loss and broad upper stop-band.

Chapter 8 outlines the pros and cons of the proposed power divider designs. It leads to suggestions for future work and a conclusion of the whole thesis.

#### 1.4 Research Approach, Assumptions and Limitations

This project focuses on the design and implementation of microwave power divider with spurious suppression. It aims at the rigorous formulation and analysis based on transmission line theory, which is carefully verified with ADS circuit models and Electromagnetic (EM) Simulation. Each design is prototyped, characterised and compared with EM simulations.

Designs are implemented on microstrip lines for low-cost, ease of fabrication and compatibility. Duroid substrate with dielectric constant of 3.38 and thickness of 0.813 mm is employed for prototyping. Two to three samples are fabricated for each design with line impedances lying between 20  $\Omega$  to 100  $\Omega$ . All the designs are realized by distributed elements, except isolation resistors in power dividers. No reactive components or backside etching are needed.

All design equations are formulated based on the assumption of lossless transmission line theory. Even-odd mode analysis is applied for the purpose of circuit analysis. The non-ideal effect of the resistors has been probed through simulations in Advanced Design Systems (ADS) with manufacturer models. Capacitive and inductive effects associated with junction discontinuities are thoroughly studied by commercially available EM tools. Demonstrations illustrate that the assumptions have been reasonably precise for the technology used.

## Chapter 2: Power Divider Design Fundamentals

This chapter describes the fundamental theories of power divider that are necessary for the analysis, design and understanding of the later chapters. Topics such as Wilkinson power divider, N-way power divider and divider with unequal power split will be covered in this chapter.

#### 2.1 Power Divider Basics

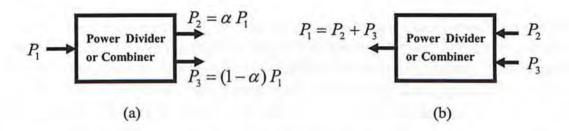

Power dividers are passive microwave components used for power division or power combining, as illustrated in Figure 2.1. In power division application, an input signal is divided by the coupler into two (or more) signals. Power dividers are often of the equal-division (3 dB) type, but unequal power division ratios are also possible. It is also required that all ports are well matched and the output ports are highly isolated.

Figure 2.1 Power division and combination: (a) Power division. (b) Power combination

Two-way Power divider is either a three-port or a four-port component. Three-port networks take the form of T-junctions like Wilkinson power dividers, while four-port networks take the form of directional couplers and hybrids.

Different types of couplers and power dividers were invented and developed at the MIT Radiation Laboratory in the 1940s, mainly for the non-planar designs like E- and H-plane waveguide tee junctions, the waveguide magic-T, and various types of couplers and dividers using coaxial probes. In the mid-1950s to the 1960s, many of these couplers and dividers were redesigned using planar structure including stripline and microstrip technologies.

The earliest three port power divider known was developed by Wilkinson [9] in 1960. He presented a circularly symmetric power divider which splits a signal into N signals with equal magnitude and phase. When N = 2, this is known as the most conventional

single-band 3-dB power divider. In 1965, Parad and Moynihan [10] described a power divider that provides two in-phase isolated outputs with arbitrary signal division. Further studies were conducted to improve its bandwidth in the following years [11, 12].

A few years later, Cohn [13] introduced a type of broad-band three-port power dividers which provide perfect isolation between the two output ports and good matching in all ports. It consists of multi-section of transmission line pairs and interconnecting resistors. This paper, published in 1968, suggested that infinite bandwidth can be obtained when the number of sections and resistors is increased without limit. Ekinge [14] improved Cohn's design from the aspects of electrical length and arbitrary power split in 1971.

Multi-way power divider with equi-amplitude equi-phase was first designed by Wilkinson [9] in 1960. In subsequent years, [15-18] radial, fork, multi-section or multi-layer topologies were developed for enhanced bandwidth and reduced circuit complexity.

#### 2.2 Wilkinson Power Divider

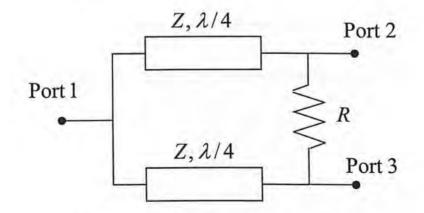

Before 1960, T-junctions and circular symmetric dividers were commonly used to provide multiple outputs with equal signal magnitude and phase. However, perfect isolation and port matching were not attainable by those configurations. Wilkinson is the first one to introduce a design (any number of outputs) with ideal return loss and port isolation. For simplicity, a 2-way power divider (3dB) is illustrated.

Figure 2.2 Schematic of Wilkinson power divider

Figure 2.2 shows the schematic of a Wilkinson power divider with equal output power. The even-odd mode formulation was introduced by Reed and Wheeler [19] in 1956, which is helpful in analysing symmetrical network. For analysis purposes, in phase signals with equal amplitude are applied to port 2 and 3. The voltage difference between the upper and lower transmission lines is zero. No power is dissipated in the resistors. The circuit is split into two identical halves (Figure 2.3). The load at the input port is replaced by 2Zo as a result of bisection.

Figure 2.3 Even-mode excitation

For the odd-mode case, a pair of anti-phase signals with equal amplitude is inserted at port 2 and 3. Due to symmetry, the divider is again bisected. However, the midpoints of the resistor and the input junction are now replaced by a virtual ground (Figure 2.4).

Figure 2.4 Odd-mode excitation

For perfect port matched  $(S_{11} = S_{22} = S_{33} = 0)$  and isolation  $(S_{23} = 0)$ , we have

$$Z_{in}^{e} = Z_0 \tag{2.1}$$

$$Z_{in}^{o} = Z_0 \tag{2.2}$$

$$Z = \sqrt{2}Z_0 \tag{2.3}$$

$$R = 2Z_0 \tag{2.4}$$

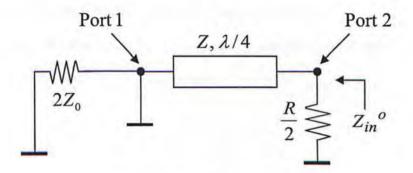

The idealized frequency response of Wilkinson power divider is shown in Figure 2.5 for easy reference.

Figure 2.5 Frequency response of a typical 3dB Wilkinson power divider

#### 2.3 Power Divider with Unequal Power Division

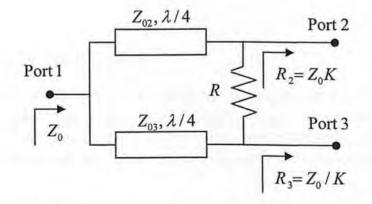

Wilkinson power dividers can also be made with unequal power splits (Figure 2.6). With the assumption that  $K^2 = \frac{P_3}{P_2}$ , we have

$$\frac{R_2}{R_3} = \frac{Z_{02}}{Z_{03}} = K^2$$

(2.5)

Figure 2.6 Wilkinson power divider with unequal power division

Using the even-odd mode analysis, the design equations are simply given by:

$$R = \frac{1+K^2}{K} Z_o \tag{2.6}$$

$$Z_{02} = Z_0 \sqrt{K(1+K^2)}$$

(2.7)

$$Z_{03} = Z_0 \sqrt{\frac{1+K^2}{K^3}}$$

(2.8)

Quarter-wavelength transformers may be introduced to transform the unequal load impedances  $(R_2, R_3)$  to  $Z_0$ . A quarter-wavelength transformer may be placed [10] at the input port (Figure 2.7) to further improve the bandwidth of the divider. The major drawback of these topologies are the extreme branch-line impedances involved when  $K^2 > 2$ .

Figure 2.7 Broadband unequal power divider

#### 2.4 Multi-way Power Divider

Multi-way power dividers and combiners are frequently used in the design of microwave and mm-wave systems. In the following section, several multi-way power divider designs like radial, fork, multi-section and multi-layer will be briefly discussed. Some planar design of 3-way power divider will also be covered.

#### 2.4.1 Wilkinson N-way Hybrid

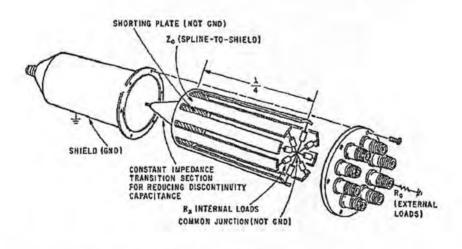

The *N*-way power divider was first introduced by Wilkinson [9] in 1960. The design maintains phase and amplitude equality between any numbers of outputs (independent of frequency) and provides good input/output matching as well as output port isolation. Figure 2.8 shows the schematic diagram of the power divider and Figure 2.9 presents its 3D structure.

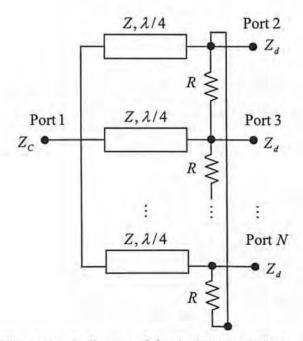

Figure 2.8 Equivalent circuit of Wilkinson N-way Hybrid

Figure 2.9 3D shape of Wilkinson N-way Hybrid

The power divider consists of N quarter-wavelength transmission lines and isolation resistors. Those resistors are connected from the end of the N transmission lines to a common junction (floating), which lead to a non-planar design. Yee [20] combined the ideas of Wilkinson [9] and Cohn [13] to obtain a broadband N-way hybrid power divider. However, the design is still non-planar in structure.

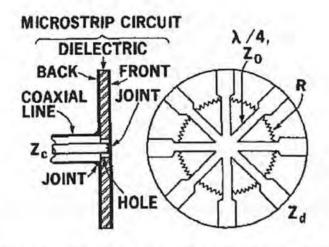

#### 2.4.2 Radial Hybrid

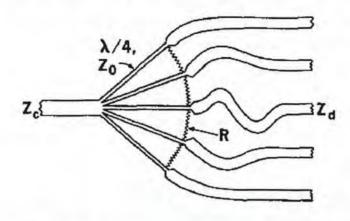

The radial *N*-way hybrid was introduced in the last 1970s [21-23]. It is semi-planar in structure, low-loss and electrically symmetric. Figure 2.10 and 2.11 show the structure of the radial hybrid and its schematic diagram. The input port is assumed to terminate in  $Z_c$  and the output ports are each terminated in  $Z_d$ .

Figure 2.10 The radial N-way hybrid power divider/ combiner

Figure 2.11 The schematic diagram of the single-stage radial N-way hybrid

Unlike the Wilkinson hybrid, the match and isolation of the radial cannot be made perfect, even at the centre frequency. No closed-form solutions are available for the evaluation of characteristic impedances and the isolation resistances. Saleh [16] developed the design formulas and tables for optimum match and isolation at the centre frequency for radial hybrids employing one or two stages of quarter-wave lines and isolation resistors (i.e. M = 1 or 2).

#### 2.4.3 Fork Hybrid

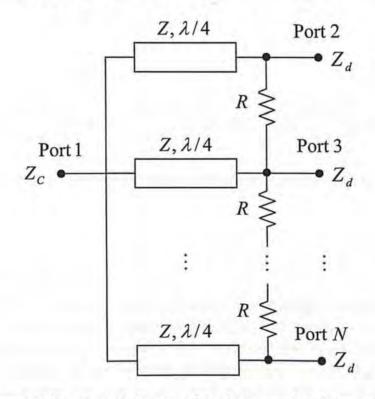

The fork hybrid was first invented by Galani and Temple [17]. Figure 2.12 and 2.13 shows the structure of fork hybrid and its schematic diagram, respectively. The input and output ports are assumed to be terminated by  $Z_{\rm C}$  and  $Z_d$ , respectively.

Figure 2.12 The fork N-way hybrid power divider/ combiner

Figure 2.13 The schematic diagram of the single-stage fork N-way hybrid

Unlike the radial hybrid, this design is completely planar in structure, but the matching and isolation at the output ports are degraded accordingly. Acceptable performance is often obtained by computer optimization.

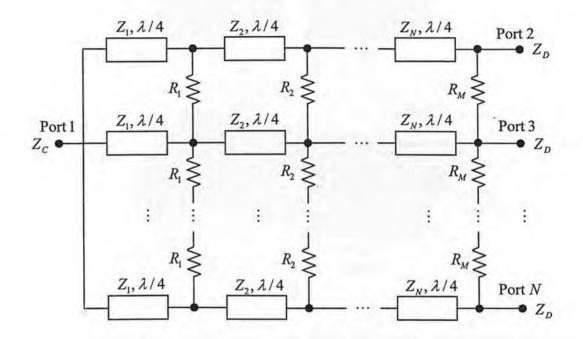

#### N-section Hybrid

The fork hybrid power divider can be further developed into multi-section structure. The schematic diagram of an M-stage fork hybrid power divider is shown in Figure 2.14. It was stated in [15] that N-1 stages are needed to obtain perfect match and isolation for a divider circuit with N output ports. Saleh [16] derived the design equations and tables for optimum match and isolation at the centre frequency for M = 1 or 2. The general design for broadband operation can be obtained by optimization.

Figure 2.14 The schematic diagram of the M-stage fork N-way hybrid

#### 2.4.4 Multi-layer Approach

A compact UWB three-way power divider was proposed recently [18]. The configuration of the divider is shown in Figure 2.15. It consists of five conductor layers interleaved by three dielectrics. The input and one of the output ports are located at the mid layer of the structure. While the other two output ports are at the top and bottom layers. The second and fourth layers are the ground plane with the coupling slots. The coupling patches and slots are elliptical in shape. The two isolated ports have no output power. They are terminated by a matched load to absorb any reflected power from the output ports.

Figure 2.15 Configuration of the three-way power divider: (a) top layer, (b) second layer (ground with coupling slot), (c) mid layer, (d) fourth layer (ground with coupling slot), (e) bottom layer, and (f) the whole configuration.

The even  $(Z_{oe})$  and odd  $(Z_{oo})$  mode characteristic impedances for each of the coupled patches are calculated using the following equations:

$$Z_{oe} = Z_o \sqrt{\frac{1+C}{1-C}}; \quad Z_{oo} = Z_o \sqrt{\frac{1-C}{1+C}}$$

(2.9)

where  $Z_o$  is the characteristic impedance of the input/output ports of the coupler. Assuming  $Z_o = 50 \Omega$  and  $C = \sqrt{1/3}$ , then  $Z_{oe} = 96.5 \Omega$  and  $Z_{oo} = 25.9 \Omega$ .

Dimensions of the elliptical patches and slots calculated from design formulas were derived using conformal mapping technique. Optimization through EM solver is needed to obtain the final dimensions of the coupler. Its main disadvantage is the need of multi-layer substrate, which increases the complexity of the fabrication process and thus the fabrication cost.

#### 2.4.5 Power Recombination Concept

The power recombination concept was first introduced by Goldfarb in 1991 [24]. This topology was used to design a planar power divider containing odd number of output ports with either equal or unequal power division. Design equations can be derived through even and odd mode analysis. Figure 2.16 shows the general topology for a recombinant device.

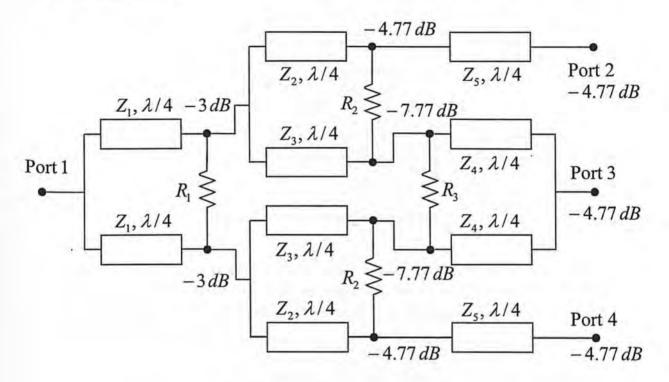

Figure 2.16 Three-way recombinant power divider

A conventional corporate feed power divider design results in  $2^n$  outputs, where *n* is the number of stages of division. If the second section is designed to provide a 1:2 dividing ratio, as shown in the above figure, the two lower power arms can be recombined into a single centre arm using an equal power combiner. Notice that the resistor ( $R_3$ ) nearest the centre output arm does nothing to improve the isolation performance under any combination of excitations of the output ports. If the resistor is removed and the two transmission lines ( $Z_4$ ) at port 3 are combined into a single line, the final result is the topology shown in Figure 2.17.

Figure 2.17 Recombinant power divider

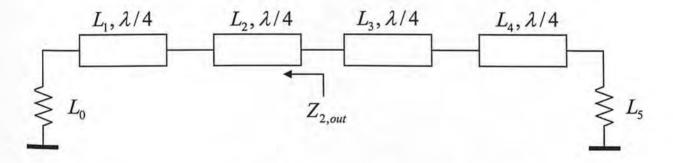

To derive the circuit parameters, in-phase / out-of-phase excitation are used to perform the analysis. Under the in-phase excitation, the voltage across each isolation resistor is zero. This allows an equivalent circuit shown in Figure 2.18, to be generated for this divider.

Figure 2.18 Equivalent circuit for synthesis of a three-way divider under in-phase excitation

In this case, a 0.1 dB Chebyshev transformer was selected, resulting in the following impedances:

$$L_{0} = Z_{0} \qquad L_{1} = Z_{1} = 0.91Z_{0} \qquad L_{2} = \frac{Z_{2}}{2} = 0.70Z_{0} \qquad L_{5} = \frac{Z_{0}}{3}$$

$$L_{3} = \frac{1}{2} \left( \frac{Z_{3}Z_{4}}{Z_{3} + Z_{4}} \right) = 0.48Z_{0} \qquad L_{4} = \left( \frac{Z_{5}Z_{6}}{Z_{5} + 2Z_{6}} \right) = 0.36Z_{0} \qquad (2.10)$$

The power dividing ratio,  $k^2$ , places additional requirements on the ratio of  $Z_3$  and  $Z_4$ . The constraints are presented in the following relationships:

$$Z_{2,out} = \left(\frac{Z_2}{2Z_1}\right)^2 Z_0 = \frac{k^2}{1+k^2} \left(\frac{Z_3}{Z_5}\right)^2 \frac{Z_0}{2}$$

$$\frac{Z_4}{Z_3} = k\sqrt{2}\frac{Z_6}{Z_5}$$

(2.11)

After some algebraic manipulation, these constraints can be written as the following expressions:

$$Z_{6} = \frac{L_{3}L_{4}\left(1 - k\frac{\sqrt{2}}{2}\right)}{\left(\frac{L_{2}}{L_{1}}\right)L_{4}\sqrt{k^{2} + 1} - k\frac{\sqrt{2}}{2}L_{3}}$$

(2.12)

$$Z_5 = \frac{2L_4 Z_6}{Z_6 - L_4} \tag{2.13}$$

$$Z_4 = 2L_3 \left[ 1 + \frac{k\sqrt{2}}{2L_4} (Z_6 - L_4) \right]$$

(2.14)

$$Z_3 = \frac{2L_3Z_4}{Z_4 - 2L_3} \tag{2.15}$$

$$Z_2 = 2L_2$$

(2.16)

$$Z_1 = L_1$$

(2.17)

To determine the value of the isolation resistors, the above technique can be repeated for out-of-phase excitation. By a proper selection of  $0^{\circ}-180^{\circ}-0^{\circ}$  or  $0^{\circ}-0^{\circ}-180^{\circ}$  signals at output ports, the values of  $R_1$  and  $R_2$  can be found. However, the above relationship are singular for the equal dividing ratio where  $k^2 = 2$ . As a result, it is necessary to begin with the non-singular values of  $Z_1$  and  $Z_2$  and solve for the remainder of the values iteratively.

The recombinant power divider achieves wide isolation bandwidth and requires only three isolation resistors. In addition, this topology allows some freedom to choose the impedance of the transmission lines. The main drawback of this design is that the number of stages of division increases with the number of output ports, resulting in a large circuit size and high insertion loss.

#### 2.4.6 Multi-coupled-line Approach

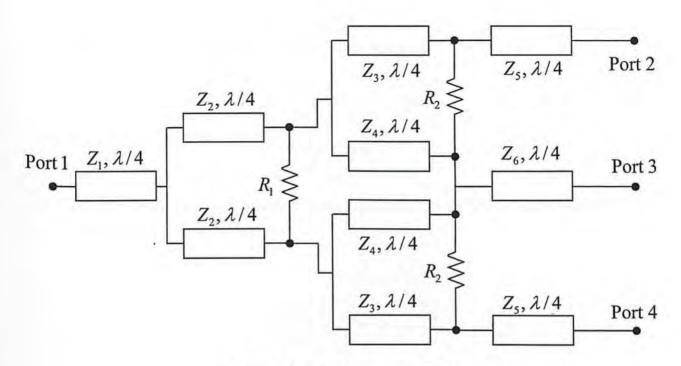

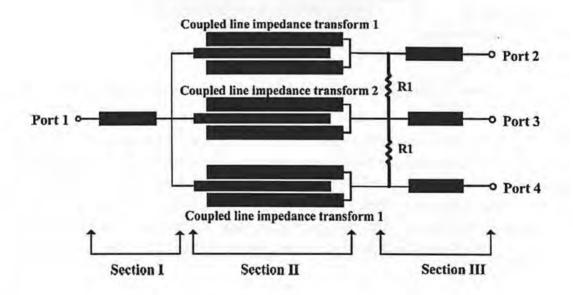

Three-way power divider using multi-coupled-line topology was developed in recent years [25-26]. This topology allows a planar structure, reduces isolation resistors and circuit dimension. By using the coupled-line structure, the power divider not only compact but also has dc block characteristics. Figure 2.19 shows the schematic diagram of the three-way power divider using coupled-line which was proposed by Chiu *et al.* [25] in 2006.

Figure 2.19 Schematic diagram of three-way power divider form Chiu et al.

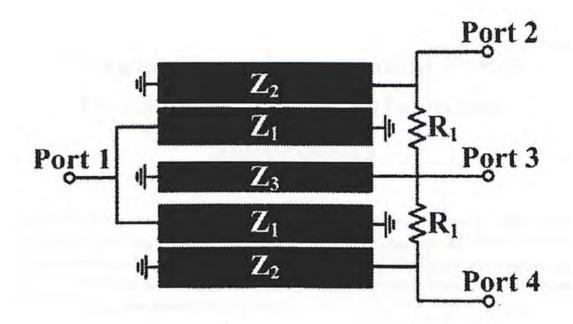

It consists of three  $\lambda/4$  microstrip coupled lines and 2 isolation resistors, which is easy to design and fabricate. The major drawback of this circuit is that the line impedances and the separation spaces of the coupled lines are estimated by computer optimization. Furthermore, the area utilization rate of this device is still quite low and is not compact enough for monolithic microwave integrated circuits (MMIC) and hybrid microwave integrated circuits (HMIC) applications. Therefore, a new structure of three-way power divider using coupled line approach was presented in 2007 [26]. Figure 2.20 shows the schematic of the new three-way power divider.

Figure 2.20 Schematic diagram of the new three-way power divider

This new design combined the ideas of Goldfarb [24] and Chiu *et al.* [25]. By utilizing power combination with coupled lines instead of transmission lines, the nine coupled lines can be improved with five  $\lambda/4$  coupled lines and two isolation resistors. The circuit size is greatly reduced, but still no close-form design formulas can be derived. Thus, the design is time consuming and huge computing resources are needed. The major drawbacks are small gap size and need of ground holes.

# Chapter 3: Conventional Power Divider Designs with Harmonic Suppression

In this chapter, some conventional power divider designs with harmonic suppression will be reviewed, which provide the basis and important background information for new designs and topologies to evolve. A summary of the existing divider designs with spurious rejection will be presented in chronological order, from resonating-stubs topology to recent extended line approach.

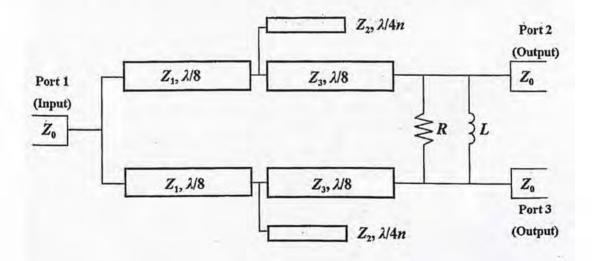

#### 3.1 Resonating-stubs Topology [27-28]

This is one of the earliest power divider designs with harmonic suppression that have been proposed [27]. As shown in Figure 3.1, the divider is basically modified conventional Wilkinson power divider structure by placing two  $\lambda/4n$  open stubs at the centre of each quarter-wave branch of the power divider. An inductor (L) is added in parallel with the isolation resistor (R). Using this topology, the *n*th harmonic component and its odd multiples are suppressed without surrendering the characteristics of the conventional Wilkinson divider at the operating frequency.

According to the above diagram, the  $\lambda/4$  branch of the original Wilkinson divider is divided into two  $\lambda/8$  sections with different characteristic impedances ( $Z_1$  and  $Z_3$ ). The *n*th harmonic component is suppressed using two  $\lambda/4n$  open stubs with impedance  $Z_2$ . The power divider is symmetric and hence the even-odd mode analysis can be applied to determine the circuit parameters.

The design equations are shown as follow:

$$Z_1 = 2Z_0 \tag{3.1}$$

$$Z_2 = 2\sqrt{3} \tan\left(\frac{\pi}{2n}\right) Z_0 \tag{3.2}$$

$$Z_3 = \sqrt{3}Z_0 \tag{3.3}$$

$$R = 2Z_0 \tag{3.4}$$

$$L = \frac{2(2+\sqrt{3})}{2\pi f_0} Z_0$$

(3.5)

A modified power divider ( $f_0 = 2$  GHz, n = 3) is illustrated in Figure 3.2 and its frequency responses are plotted in Figure 3.3.

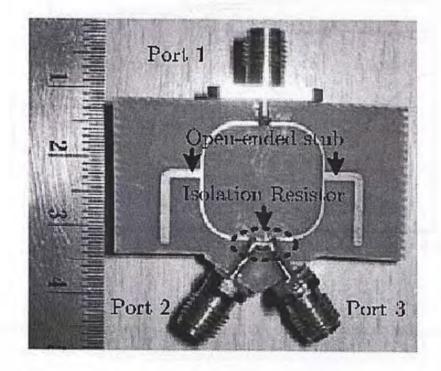

Figure 3.2 Photograph of fabricated 2 GHz Wilkinson power divider for third harmonic suppression

Figure 3.3 Measured and Simulated S-parameters: (a) S11 and S22; (b) S23 and S21

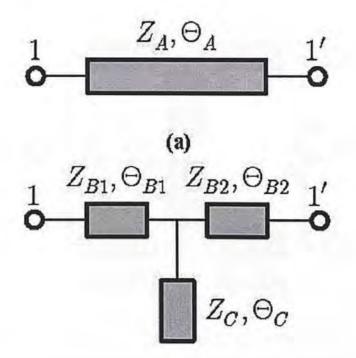

The drawback of this design is the adoption of additional lumped reactive element (i.e. inductor), as they represent uncertainties in higher frequency operation. In addition, the use of reactive element would increase the manufacturing cost. Therefore, a new design of power divider with harmonic suppression using resonating stubs topology was introduced [28]. Compared to the conversional divider, the  $\lambda/4$  branch is replaced by a T-network of transmission lines (TL). Figure 3.4 shows the structure of the conventional  $\lambda/4$  TL and T-network design.

Figure 3.4 Structure of (a) the 1/4 conventional TL and (b) an equivalent T-shaped TL

Given that  $\Theta_A = \frac{\pi}{2}$ ,  $Z_{B1} = Z_{B2} = Z_B$  and  $\Theta_{B1} = \Theta_{B2} = \Theta_B$ , the conversion between quarter-wave TL and the T-network TL are summarized by the following equations:

$$\frac{Z_B}{Z_A} = \cot \Theta_B \tag{3.6}$$

$$\frac{Z_C}{Z_A} = \frac{\cos^2 \Theta_B \tan \Theta_C}{1 - 2\sin^2 \Theta_B}$$

(3.7)

$$\Theta_c = \left(\frac{\pi}{2}\right) \left(\frac{f_0}{f_1}\right) \tag{3.8}$$

where  $f_0$  is the operating frequency and  $f_1$  is the suppressed frequency ( $f_1 > f_0$ ). Figure 3.5 shows the new power divider configuration ( $Z_A = 100 \Omega$ ,  $\Theta_B = \pi/6$ ), whereas its frequency response is plotted in Figure 3.6.

(a)

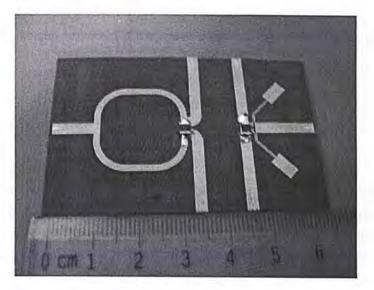

Figure 3.5 The new power divider with harmonic rejection: (a) Schematic; (b) Photograph

Figure 3.6 Performances of the new power divider: (a) Simulation results; (b) Meaasured results

The two divider designs are similar to each other in structure and occupy almost the same substrate area. Only one harmonic frequency can be suppressed. The only difference is that no reactive lumped component is used in the new design. The later design, however, involves transmission lines of high impedances for  $f_1 = 2f_0$ .

## 3.2 Asymmetric Defected Ground Structure (DGS) [29]

The defected ground structure (DGS) has various applications in microwave and millimetre-wave systems. The DGS of the microstrip line is implemented by making defected pattern on the ground plane. It provides band rejection characteristic at some resonance frequency depending on the design of DGS. In RF circuits, the band-rejection property of the DGS can be utilized in the selective suppression of the harmonics [30-31].

Woo and Lee [29] used asymmetric spiral DGS to suppress the second and third harmonics simultaneously. The Wilkinson power divider with the asymmetric spiral DGS in a quarter-wave line suppresses two harmonics effectively without affecting the performances of the power divider at the operating frequency. The size of the divider is reduced due to the slow-wave effect. The structure of the conventional Wilkinson power divider and the divider using asymmetric DGS are illustrated in Figure 3.7.

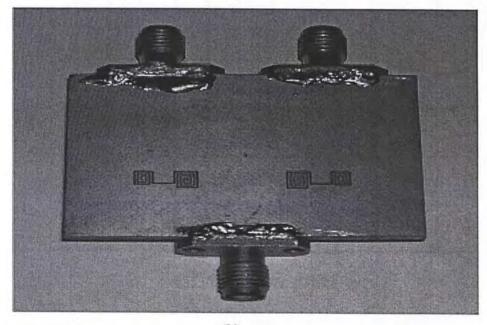

The size of the proposed power divider is reduced by 9.1 %. Figure 3.8 shows the simulated frequency responses of the two power dividers. From the simulation results, the second and third harmonic are selected to be suppressed using an asymmetric spiral DGS, while for the conventional one, no suppression is formed. Figure 3.9 and 3.10 shows the photograph of the DGS-based power divider with centre frequency of 1.5 GHz and its frequency response, respectively. However, this design requires backside etching, which is undesirable for low-cost and mass production. Furthermore, this technique can only provide limited rejection (less than 20 dB) at the two harmonic bands with narrow suppression bandwidth.

Figure 3.8 Simulated S-parameters of (a) original Wilkinson power divider; (b) power divider using asymmetric DGS

(a)

(b)

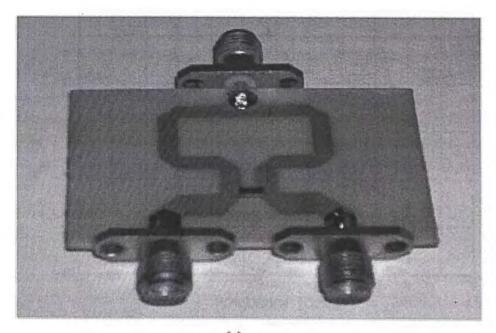

Figure 3.9 Fabricated 3-dB Wilkinson power divider with asymmetric spiral DGS. (a) Top view; (b) Bottom view

Figure 3.10 Measured S-paramters of the fabricated divider: (a)  $S_{11}$ ; (b)  $S_{21}$

## 3.3 Anti-Coupled Line Structure [32]

A short-circuited, anti-coupled line (Figure 3.11) is another technique to enlarge the stop-band bandwidth due to the additional finite attenuation poles, which is useful for harmonic suppression. The circuit consists of a pair of anti-coupled lines short circuited at one end by a low impedance line. The Z –parameter of the structure can be formulated as:

$$Z_{T} = \begin{bmatrix} j \left( \frac{Z_{oe} \tan \theta_{e} + Z_{oo} \tan \theta_{o}}{2} - Z_{C} \cot \theta_{Lc} \right) & j \left( \frac{Z_{oe} \tan \theta_{e} - Z_{oo} \tan \theta_{o}}{2} - Z_{C} \cot \theta_{Lc} \right) \\ j \left( \frac{Z_{oe} \tan \theta_{e} - Z_{oo} \tan \theta_{o}}{2} - Z_{C} \cot \theta_{Lc} \right) & j \left( \frac{Z_{oe} \tan \theta_{e} + Z_{oo} \tan \theta_{o}}{2} - Z_{C} \cot \theta_{Lc} \right) \end{bmatrix}$$

(3.9)

where  $\theta_e$  and  $\theta_o$  are the even- and odd-mode electrical length, and  $Z_c$  and  $\theta_{Lc}$  represent the characteristic impedance and the electrical length of the low impedance line respectively.

Figure 3.11 Layout of a short circuit anti-coupled line

From (3.9),  $S_{21}$  can be obtained as follows:

$$S_{21} = \frac{2Z_{21}}{|Z_T| + Z_{11} + Z_{22} + 1}$$

(3.10)

Finite attenuation poles occur when  $Z_{21} = 0$ , which reduces to:

$$Z_{C}\cot\theta_{Lc} = \frac{Z_{oe}\tan\theta_{e} - Z_{oo}\tan\theta_{o}}{2}$$

(3.11)

As  $Z_c \cot \theta_{Lc}$  is monotonically decreasing with frequency; while the function of  $Z_{oe} \tan \theta_e - Z_{oo} \tan \theta_o$  has maximum and minimum at its discontinuity spot, three controllable attenuation poles will be presented over the stop-band. From the above analysis, it can be concluded that the first and the third finite attenuation poles would shift as the load capacitance changes and the second one would have no shift. Figure 3.12 illustrates the layout of the power divider with anti-coupled lines and a conventional Wilkinson power divider. Both simulated and measured frequency responses are shown in Figure 3.13.

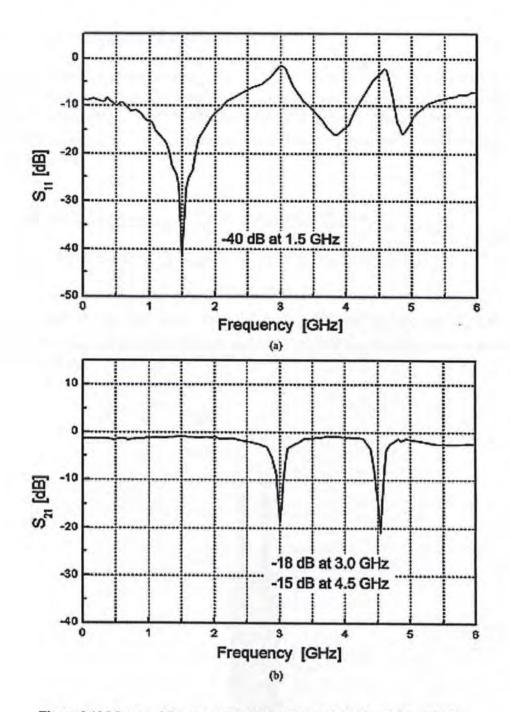

Figure 3.12 Photograph of the divider using anti-cooupled line (right) and conventional power divider

Figure 3.13 Frequency responses of the power divider: (a) at whole frequency band; (b) at frequency band near the operating frequency

According to the above results, the divider can operate with spurious suppression from 3.2 to 7 GHz by more than 20 dB. However, the input return loss  $(S_{11})$  and the output port isolation  $(S_{23})$  are both less than 15 dB, which means that the circuit is not perfectly matched and some power can be coupled between the outputs. Furthermore, as the size of the microstrip lines and gaps (anti-coupled lines) are quite small ( $W_c =$ 0.3 mm and  $G_c = 0.15$  mm), precise manufacturing facility is required, which is undesirable for low cost production. In addition, no closed-form design formulas are available and the structural dimensions can only be obtained by computer optimization.

# 3.4 Microstrip Electromagnetic Bandgap (EBG) Based Topology [33]

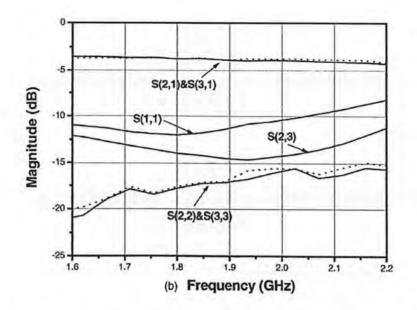

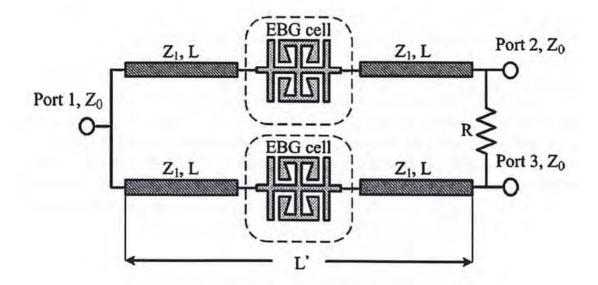

Microstrip transmission lines incorporating the electromagnetic bandgap (EBG) structure demonstrate band-stop and slow-wave characteristics, which can be utilized to suppress unwanted harmonics and reduce the sizes of the microstrip branch. Power divider with microstrip EBG cells (Figure 3.14) can offer several advantages including planar structure, compact size and superior harmonic suppression. Figure 3.14 shows the schematic diagram of the power divider using EBD cells.

Figure 3.14 Schematic diagram of the power divider using EBG cells

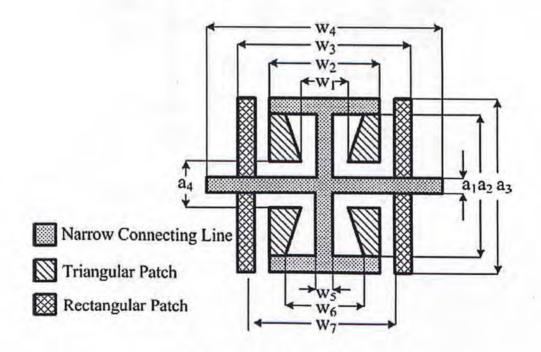

Referring to Figure 3.14, the power divider is consisted of two microstrip EBG cells and four microstrips (length L and characteristic impedance  $Z_1$ ). The EBG cell can provide two resonances to suppress the unwanted harmonics and reduce the length of a quarter-wave transmission line simultaneously. Figure 3.15 shows the detailed structure of a microstrip EBG cell.

Figure 3.15 Structure of a microstrip EBG cell

By adjusting the narrow connecting lines and the size of the etched pattern, different slow-wave effects can be obtained at different frequencies to suppress the unwanted *n*th harmonics. The dimensions of the EBG cell is first determined by its equivalent circuit model [34] (Figure 3.16) and then finalized by optimization through EM solver. The photograph of the fabricated circuit is shown in Figure 3.17. The frequency responses are illustrated in Figure 3.18. According to the measured results, the prototype operates as a conventional Wilkinson power divider at the centre frequency while suppressing the third and fifth harmonics simultaneously. The size of the  $\lambda/4$  branch is reduced by more than 30 % compared to the conventional one. Its major disadvantage is the narrow rejection bandwidth.

Figure 3.16 Equivalent L-C circuit of a microstrip EBG cell

Figure 3.17 Photograph of the power divider with EBG cells

(a)

(b)

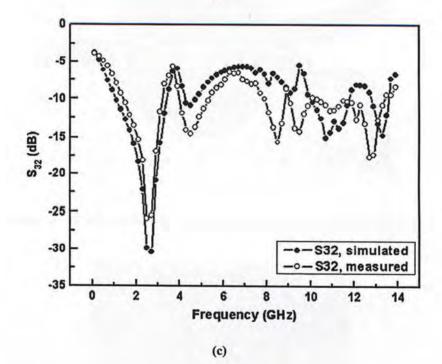

Figure 3.18 Frequency responses for the power divider using EBG cells: (a) Insertion loss; (b) Input / output return loss; (c) Output port isolation

## 3.5 Embedded Resonators Topology [35]

A miniaturized microstrip power divider using embedded resonators (Figure 3.19) was proposed recently. It has four microstrip high-low impedance resonator cells uniformly placed inside the Wilkinson power divider. These resonators allow reduction of circuit size and the suppression of harmonic bands (third and fifth). The dimensions of the resonator were obtained by computer optimization. Figure 3.20 and 3.21 give, respectively, the physical layout and frequency response of the prototype. This circuit performs like a low pass filter with high frequency rejection of about 30 dB. However, the drawback is the slow roll-off. Good isolation and return loss performances were achieved. The divider is compact and easy to fabricate by standard etching process.

Figure 3.19 Configuration of the power divider using embedded resonators

Figure 3.20 Photograph of the divider using embedded resonators

Figure 3.21 Frequency responses for the power divider using embedded resonators: (a) Insertion loss; (b) Input return loss; (c) Output port isolation

## 3.6 Extended Line Approach [36]

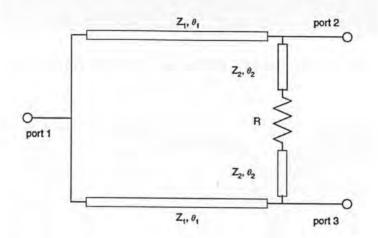

Figure 3.22 shows the configuration of the modified two-way power divider with single harmonic rejection. It basically consists of four branch-line sections and a resistor. Two extended lines with impedance  $Z_2$  are inserted between the output ports. The extended lines are used for harmonic suppression by the proper selection of  $\begin{pmatrix} \pi \\ \end{pmatrix}$

$\theta_2 \left(=\frac{\pi}{2n}\right)$ , where *n* is the number of harmonic band to be rejected.

By applying even- and odd-mode formulations, the design parameters can be derived and expressed as follows  $(z_1 = Z_1 / Z_0, z_2 = Z_2 / Z_0, r = R / Z_0)$ :

$$r = 2 \left( 1 - \tan^2 \theta_2 \right) \tag{3.12}$$

$$z_2 = \sqrt{r} \tag{3.13}$$

$$z_1 = z_2 \sqrt{\frac{2}{z_2^2 + 2\tan^2 \theta_2}}$$

(3.14)

$$\theta_1 = \pi - \tan^{-1} \left( \frac{1}{\tan \theta_2} \frac{z_2}{z_1} \right)$$

(3.15)

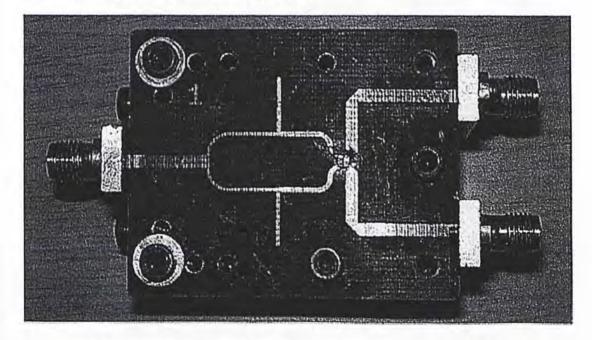

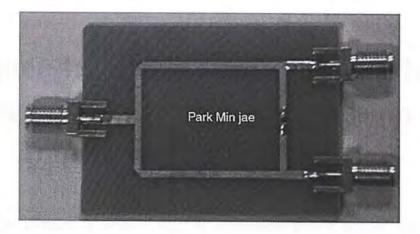

Figure 3.23 shows the fabricated circuit designed to reject the third harmonic band. Both measured and simulated frequency responses are illustrated in Figure 3.24. The power divider was found to exhibit excellent performance at both the fundamental as well as the third harmonic bands. However, only single harmonic rejection and narrow stop band bandwidth were realizable by the proposed topology.

Figure 3.23 Photograph of the modified Wilkinson power divider

Figure 3.24 Frequency responses of the power divider with extended lines: (a)  $S_{21}$  and  $S_{23}$ ; (b)  $S_{11}$ and  $S_{22}$

# Chapter 4: New 2-way Power Divider Design with Spurious Suppression and Impedance Transformation

This chapter presents a novel design of microwave power divider with spurious suppression and impedance transformation. Explicit closed-form design equations are derived based upon even- and odd- mode analysis. The proposed circuit also features simple structure, compact size and enhanced stop-band attenuation. For demonstration, the simulated and experimental results of two prototypes implemented on microstrip are given.

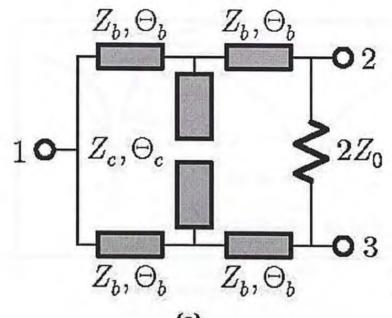

## 4.1 Proposed Topology

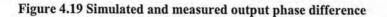

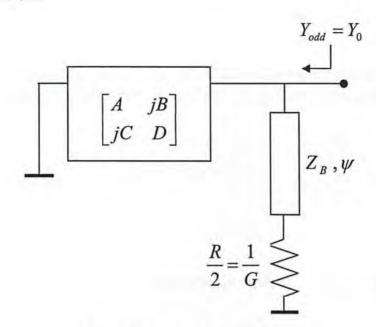

Figure 4.1 shows the schematic diagram of the proposed power divider with harmonic suppression. It basically consists of four branch-line sections, single shunt stub (open-circuited) and a resistor. Unlike all previous designs, the output ports are kept distance away from the isolation resistor by the insertion of two extended lines  $(Z_B)$  for increased layout flexibility and reduced parasitic effect. The load impedance,  $R_L$ , is assumed to be different from the source impedance  $R_S$ .

It is further assumed that  $R_S$ ,  $R_L$ , R,  $\phi$  and  $\alpha$  are free variables while  $Z_A$ ,  $Z_B$ ,  $Z_C$  and  $\theta$  are unknowns to be determined. By applying the even- and odd-mode formulation, these unknown parameters can simply be derived from the electrical properties of an ideal power divider (perfect return loss and port isolation) evaluated at the fundamental frequency ( $f_0$ ).

### 4.2 Design and Analysis

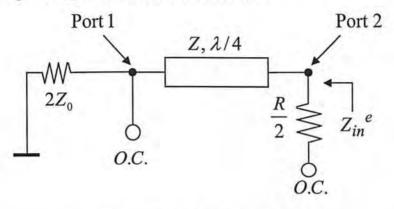

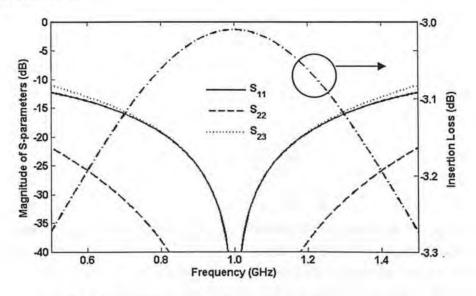

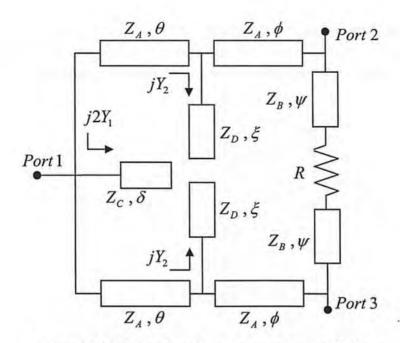

#### Even-mode Analysis

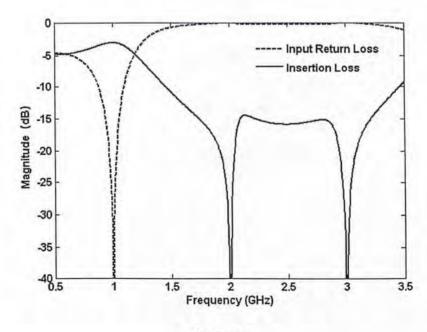

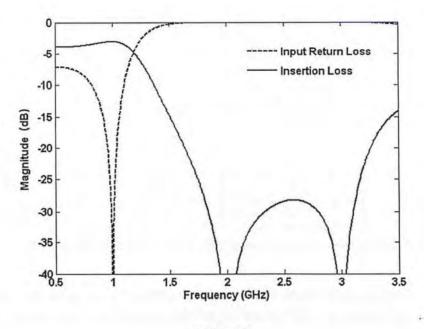

Figure 4.2 depicts the equivalent circuit of the proposed divider under even-mode excitation. It can be seen that the extended line  $(Z_B)$  and the open circuit stub  $(2Z_C)$  are responsible for the creation of two transmission zeros. For instant, an electrical length of 45°, 30° or 22.5° corresponds to the suppression of the second, third or fourth harmonic frequencies, respectively. According to (4.1) and (4.2), the frequencies of the transmission zeros ( $f_{z1}$  and  $f_{z2}$ ) can be adjusted by the selection of  $\phi$  and  $\alpha$ . Meanwhile, the low-pass characteristics of the resulting network can help to further increase the attenuation level of spurious suppression.

$$f_{Z1} = \frac{\pi}{2\alpha} f_0 \tag{4.1}$$

$$f_{Z2} = \frac{\pi}{2\phi} f_0 \tag{4.2}$$

Under the condition of ideal input return loss, it can be proved that the output admittance  $Y_{even}$  of the even-mode circuit is simply equal to  $Y_L$  at  $f_0$ . Mathematically, this relation can be formulated and expressed by (4.3).

$$Y_{even} = Y_L = Y_B \frac{2 + jRY_B \tan \phi}{RY_B + j2 \tan \phi} - jY_A \cot \theta$$

(4.3)

By equating the real and imaginary parts of the above expression, one obtains:

$$RY_BY_L - 2Y_A \tan\phi \cot\theta = 2Y_B \tag{4.4}$$

$$2Y_L \tan \phi + RY_A Y_B \cot \theta = RY_B^2 \tan \phi \tag{4.5}$$

Odd-mode Analysis

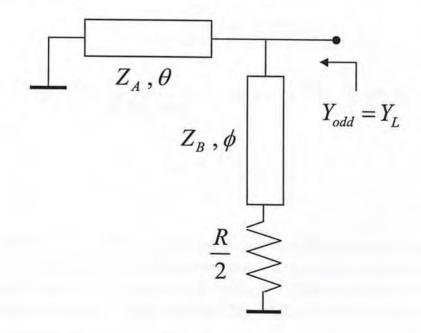

Figure 4.3 Equivalent circuit: odd-mode

Under odd-mode excitation, the equivalent circuit of the proposed divider is given in Figure 4.3. With the assumption that the two output ports are perfectly matched and isolated (evaluated at the center frequency), a second condition may thus be stated as follows:

$$Y_{even} = Y_L = Y_B \frac{2 + jRY_B \tan\phi}{RY_B + j2\tan\phi} - jY_A \cot\theta$$

(4.6)

Similarly, the real and imaginary parts of (4.6) may be equated to give:

$$2Y_A Y_L - Y_C Y_L \tan \alpha \tan \theta + Y_B Y_S \tan \theta \tan \phi = Y_A Y_S$$

(4.7)

$$Y_{S}Y_{L}\tan\theta - 2Y_{A}Y_{B}\tan\phi + Y_{B}Y_{C}\tan\phi\tan\alpha\tan\theta = Y_{A}Y_{C}\tan\alpha + 2Y_{A}^{2}\tan\theta$$

(4.8)

Finally, by solving (4.4), (4.5), (4.7) and (4.8), the circuit parameters of the proposed configuration can thus be obtained via the following expressions.

$$Y_{A} = \frac{1}{Z_{A}} = \sqrt{\frac{Y_{S}Y_{L}}{2} - \frac{Y_{B}^{2}}{2}} (RY_{L} - 2) + \frac{Y_{B}Y_{C}\tan\alpha}{4\tan\phi} (2\sec^{2}\phi - RY_{L}) \quad (4.9)$$

$$Z_{B} = \frac{1}{2\tan\phi} \sqrt{\frac{R}{Y_{L}} (2\sec^{2}\phi - RY_{L})} \quad (4.10)$$

$$Y_{C} = \frac{1}{Z_{C}} = \frac{Y_{B}}{2Y_{L} \tan \phi \tan \alpha} [2Y_{S} \sec^{2} \phi + Y_{L} (2RY_{L} - 4 - RY_{S})] \quad (4.11)$$

$$\theta = \frac{\pi}{2} - \tan^{-1} \left[ \frac{(RY_L - 2)}{2Y_A Z_B \tan \phi} \right]$$

(4.12)

The main objective of the above formulation is to reduce the number of free variables to be adjusted without heavily relying on computer optimization. And for a given set of circuit parameters ( $R_S$ ,  $R_L$ ,  $\phi$  and  $\alpha$ ), the unknown values of  $Z_A$ ,  $Z_B$ ,  $Z_C$  and  $\theta$  are simply a function of R only. Additional flexibility is offered by the selection of  $\phi$  and  $\alpha$ , which determine the locations of the transmission zeros. In practice, the rejection of the 2<sup>nd</sup> and 3<sup>rd</sup> harmonic frequencies ( $\phi, \alpha \in 45^\circ, 30^\circ$ ) are highly desirable.

Two design examples will be discussed next. In Example 1, both input and output loads ( $R_{\rm S}$  and  $R_{\rm L}$ ) are assumed to be 50  $\Omega$ , with  $\phi = 45^{\circ}$  and  $\alpha = 30^{\circ}$ . Impedance transformation will be demonstrated in Example 2, with  $R_{\rm S} = 50 \Omega$ ,  $R_{\rm L} = 75 \Omega$ ,  $\phi = 30^{\circ}$  and  $\alpha = 45^{\circ}$ .

## 4.3 Simulation Study

### Design 1

The circuit parameters of this design (same input and output port impedance) are tabulated in Table 4.1. Subsequently, equations (4.9) - (4.12) can further be simplified as follows:

$$Z_{A} = Z_{0} \sqrt{\beta \frac{2 - \beta}{1 + \beta - \beta^{2}}}$$

(4.13)

$$Z_B = Z_0 \sqrt{\beta(2-\beta)} \tag{4.14}$$

$$Z_c = Z_0 \sqrt{\frac{2-\beta}{3\beta}} \tag{4.15}$$

$$\theta = \frac{\pi}{2} - \tan^{-1} \left[ \frac{\beta - 1}{\sqrt{1 + \beta - \beta^2}} \right]$$

(4.16)

$$\beta = \frac{R}{2Z_0} < \frac{1+\sqrt{5}}{2}$$

(4.17)

| Rs   | RL   | φ   | α   |

|------|------|-----|-----|

| 50 Ω | 50 Ω | 45° | 30° |

Table 4.1 Circuit parameters of the proposed power divider (Example 1)

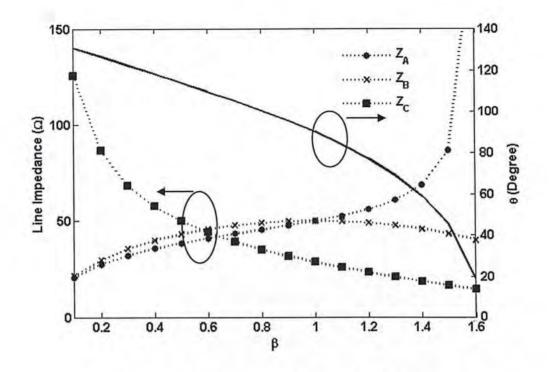

Based on the above formulas, the variation of the line impedances and  $\theta$  as a function of  $\beta$  was calculated and plotted in Figure 4.4.