# Design of Platform for Exploring Application-Specific NoC Architecture

LIU, Zhouyi

A Thesis Submitted in Partial Fulfillment

of the Requirements for the Degree of

Master of Philosophy

in

Electronic Engineering

The Chinese University of Hong Kong

March 2011

## Abstracts

As a new approach to accommodate multiple processing elements (PEs) on a single chip, Network-on-Chip (NoC) brings enhanced performance and scalability, in comparison with conventional communication infrastructures. Since huge research margin exists in NoC research domain which ranges from topology, routing algorithm to flow control mechanism, many innovative NoC architectures with distinctive configurable features emerge recently that either emphasizes on short runtime, or concentrates on low power consumption or takes both into account. Among all those candidate NoCs, how to single out the most suitable one, satisfying strict performance requirement or resource constraint, for specific application becomes an compelling and urgent challenge. Systematic platform which is capable of searching optimal NoC for specific application is called for.

This thesis proposes an integrated environment aiming at optimal NoC exploration for specific application. The entire process consists of picking out a suitable architecture from available ones and exploring appropriate configuration of selected architecture. Graphical User Interface (GUI) is well designed as the service window of the whole package of user operation, including architecture selection, feature configuration, benchmark generation, performance evaluation as well as NoCs optimization and comparison. All operations proceed by observing decently developed rules to ensure integrity of architecture library and reproducibility of any evaluation.

Configurable NoC architectures integrated to platform (NoC Library) are low-latency & low-power oriented, respectively, providing broadened application space for various performance requirements / cost constraints. Associated features of NoC architecture are all extracted and displayed on GUI for convenient access. NoCs optimization concentrates on buffer distribution that influences chip area, power consumption as well as network performance. Comparison among NoCs reaches beyond plain numeric comparison alone. Validity check is introduced to ensure that the performance metrics to compare are obtained by identical standard.

I.

摘要

单晶片网络,作为单晶片系统的发展趋势,在集成电路研究领域引起了广泛的兴趣。随着工艺的不断改进和电路设计能力的持续提高,将单元数目繁多的网络系统集成在单一晶片成为必然。网络中的各个处理和存储单元之间存在着大量的数据交换,以期实现复杂的功能或完成巨量的数值计算。设计和选择一个高效率的网络系统来协调和优化数据交换成为一个重要的议题。

近年来有许多单晶片网络设计相关的先进技术提出,以期增强片上网络的数据传输速度,降低晶片功耗和面积,由这些技术衍生出了不同的单晶片网络的设计。这些设计往往在某一项特定的参数上对通用网络有显著的改进,要么网络传输速度,要么网络功耗。然而这些参数的提高或者以牺牲其他性能指标为代价,或者仅仅适用某一特定类型的数据交换模式。没有哪一项设计可以全面解决所有问题。

单晶片网络设计的一个显著特点,是其设计的多样性和参数配置的复杂性。 不同的网络设计具有各自的优势和局限性,往往是在特定的数据交换模式下发挥 最大的功效。想要有效的比较两个网络设计,最好的方式就是把它们集成在一个 统一的环境下,利用严格的控制流程来配置、评估和比较多个片上网络。如何配 置选定的单晶片网络设计,让它在特定的数据交换环境下发挥最大功效,是一个 同样重要的课题。

本文提出的是一个综合性的单晶片网络应用平台。它的功能是探寻已有片上 网络的优点,为指定的数据交换模式,定位最合理的网络配置。综合性的平台可 以保证所有片上网络的性能比较基于完全相同的条件,大大减少不同平台间比较 造成的误差。与此同时,平台的优化功能可以自动调整用户定义的存储单元大小, 提出更合理的配置建议。图形化的用户界面既便于用户操作,也保证系统文件不 会被意外修改。

# Contents

| ABSTRACTS                                   |     |

|---------------------------------------------|-----|

| 摘要                                          |     |

| CONTENTS                                    | m   |

| LIST OF FIGURE                              | v   |

| LIST OF TABLE                               | vı  |

| ACKNOWLEDGEMENT                             | VII |

| CHAPTER 1 INTRODUCTION                      | 1   |

| 1.1 NETWORK-ON-CHIP                         | 1   |

| 1.2 RELATED WORKS                           | 2   |

| 1.3 PLATFORM OVERVIEW                       | 6   |

| 1.4 AUTHOR'S CONTRIBUTION                   | 10  |

| CHAPTER 2 NOC LIBRARY                       | 12  |

| 2.1 NETWORK TERMINOLOGY                     | 12  |

| 2.2 BASIC STRUCTURE                         |     |

| 2.3 LOW-POWER ORIENTED ARCHITECTURE         |     |

| 2.3.1 Low-Cost Allocator Design             |     |

| 2.3.2 Clock Gating                          |     |

| 2.3.3 Express Virtual Channel Insertion     |     |

| 2.4 LOW-LATENCY ORIENTED ARCHITECTURE       |     |

| 2.4.1. Lookahead Bypass Scheme              |     |

| 2.4.2. Lookahead Bypass Router Architecture |     |

| CHAPTER 3 BENCHMARK AND MEASUREMENT         | 31  |

| 3.1 BENCHMARK GENERATION                    | 32  |

| 3.1.1 Types of Traffic Patterns             |     |

| 3.1.2 Traffic Generator                     |     |

| 3.2 MEASUREMENT SETTING                     |     |

| 3.2.1 Warming-up Period                     |     |

| 3.2.2 Latency Definition                    |     |

| 3.2.3 Throughput Definition                 |     |

| 3.2.4 Virtual Channel Utilization           | 40  |

| CHAPTER 4 PLATFORM STRUCTURE                | 41  |

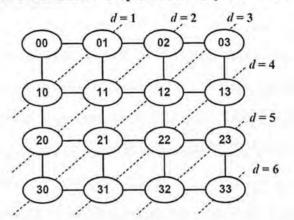

| 4.1 FILE TREE                               |     |

| 4.1.1 System Files                          |     |

| 4.1.2 Low-Power NoC Related                 |     |

| 4.1.3 Low-Latency NoC Related               |     |

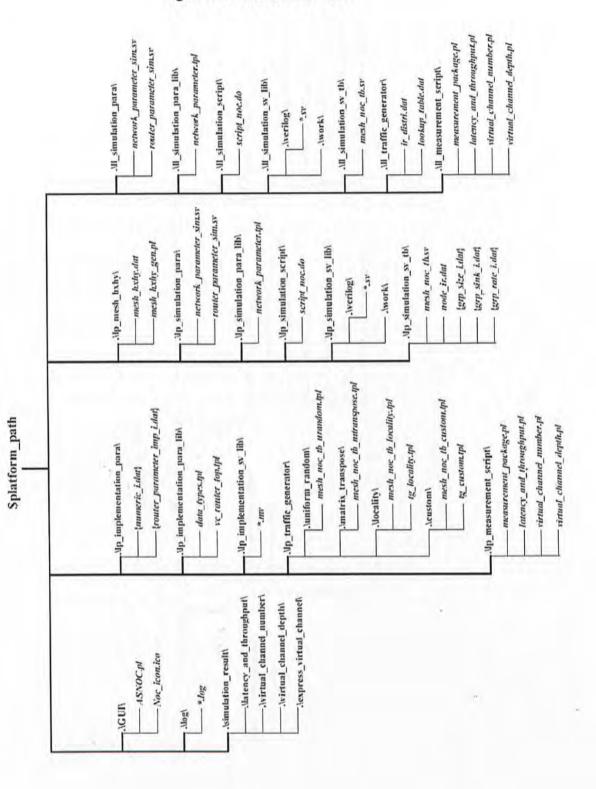

| 4.1.  | 4 Project Related                         | 51 |

|-------|-------------------------------------------|----|

| 4.2   | PROCESSES                                 |    |

| 4.3   | GUI ACCESS                                | 56 |

| 4.3.  | 1 Section 1: Project Setup                | 58 |

| 4.3.  | 2 Section 2-a: Low-Power Router Structure | 59 |

| 4.3.  |                                           |    |

| 4.3.  |                                           |    |

| 4.3.  |                                           |    |

| 4.3.  | 6 Low-Power NoC Example                   | 62 |

| CHAPT | ER 5 OPTIMIZATION AND COMPARISON          | 72 |

| 5.1   | OPTIMIZATION TECHNIQUE                    | 72 |

| 5.1.  |                                           |    |

| 5.1.  |                                           |    |

| 5.1.  | 3 Over-Optimization                       | 78 |

| 5.1.  | 4 Optimization Example                    | 79 |

| 5.2   | NOCS COMPARISON                           | 83 |

| 5.3   | LOW-POWER IMPLEMENTATION CODE EXPORT      | 88 |

| СНАРТ | ER 6 SUMMARY AND FUTURE WORK              | 92 |

| 6.1.  | SUMMARY                                   | 92 |

| 6.2.  | FUTURE WORK                               | 93 |

| REFER | ENCES                                     | 95 |

.

# List of Figure

| FIGURE 1-1 ILLUMINATION OF PLATFORM STRUCTURE                         | 8  |

|-----------------------------------------------------------------------|----|

| FIGURE 2-1 TYPICAL NOC DATA FORMAT                                    | 14 |

| FIGURE 2-2 NORMAL NETWORK ROUTER ARCHITECTURE                         |    |

| FIGURE 2-3 VIRTUAL CHANNEL ALLOCATION                                 | 17 |

| FIGURE 2-4 SWITCH ALLOCATION                                          |    |

| FIGURE 2-5 FIVE STAGES OF NORMAL NETWORK ROUTER                       | 19 |

| FIGURE 2-6 PIPELINE STAGE COMPARISON                                  | 21 |

| FIGURE 2-7 EVC PIPELINE COMPARISON                                    | 23 |

| FIGURE 2-8 EVC BYPASS EXAMPLE                                         |    |

| FIGURE 2-9 EVC ROUTER ARCHITECTURE COMPARISON                         | 24 |

| FIGURE 2-10 COMPARISON OF NON-AGGRESSIVE AND AGGRESSIVE EXPRESS       |    |

| FIGURE 2-11 DEAD LOCK EXAMPLE                                         | 27 |

| FIGURE 2-12 UNIFORM EVC INSERTION FOR 5×5 MESH NETWORK                |    |

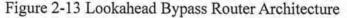

| FIGURE 2-13 LOOKAHEAD BYPASS ROUTER ARCHITECTURE                      |    |

| FIGURE 3-1 DISTANCE GRAPH FOR LOCALITY TRAFFIC PATTERN                | 35 |

| FIGURE 4-1 PLATFORM FILE TREE                                         |    |

| FIGURE 4-2 PROJECT FILE TREE                                          |    |

| FIGURE 4-3 PLATFORM GUI TREE                                          | 57 |

| FIGURE 4-4 NOC CONFIGURATION EXAMPLE, SECTION 1                       |    |

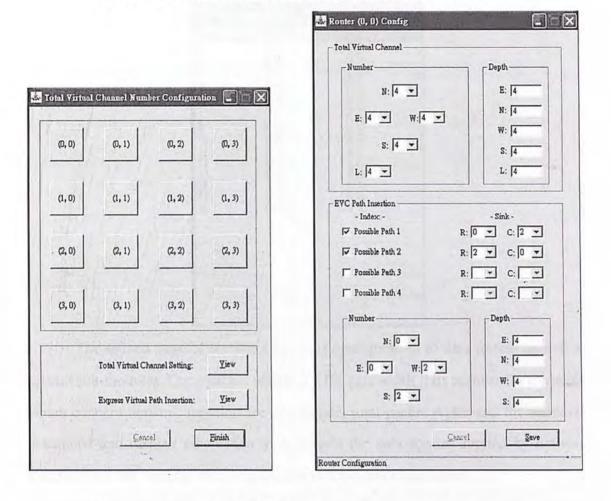

| FIGURE 4-5 NOC CONFIGURATION EXAMPLE, SECTION 2                       | 64 |

| FIGURE 4-64×4 MESH NETWORK WITH UNIFORM EVCS INSERTION                | 65 |

| FIGURE 4-7 CONFIGURATION GUI PAGE OF INDIVIDUAL NETWORK ROUTER        |    |

| FIGURE 4-8 TOTAL VIRTUAL CHANNEL SETTING VIEW                         | 66 |

| FIGURE 4-9 EXPRESS VIRTUAL PATH INSERTION VIEW                        | 67 |

| FIGURE 4-10 NOC CONFIGURATION EXAMPLE, SECTION 3                      |    |

| FIGURE 4-11 NOC CONFIGURATION EXAMPLE, SECTION 4                      | 69 |

| FIGURE 4-12 LATENCY AND THROUGHPUT REPORT                             | 70 |

| FIGURE 4-13 VIRTUAL CHANNEL NUMBER UTILIZATION REPORT                 | 71 |

| FIGURE 4-14 VIRTUAL CHANNEL DEPTH UTILIZATION REPORT                  | 71 |

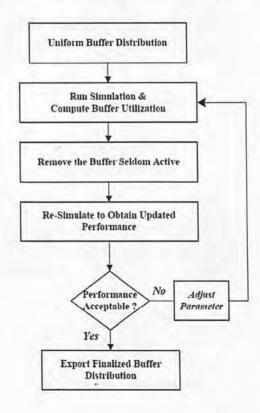

| FIGURE 5-1 PLAIN BUFFER OPTIMIZATION FLOW                             | 73 |

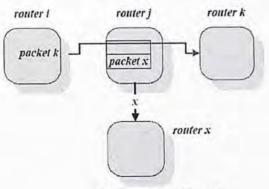

| FIGURE 5-2 VIRTUAL CHANNEL ORIGINATION                                | 74 |

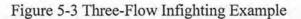

| FIGURE 5-3 THREE-FLOW INFIGHTING EXAMPLE                              | 76 |

| FIGURE 5-4 INFIGHTING AFFECTS ON UNIFORM TRAFFIC                      | 77 |

| FIGURE 5-5 WAVE FORM OF CONTINUOUS REQUESTS TO SINGLE VIRTUAL CHANNEL | 78 |

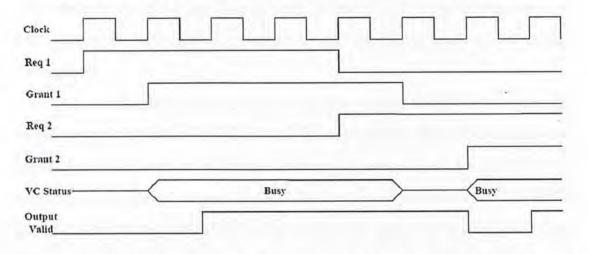

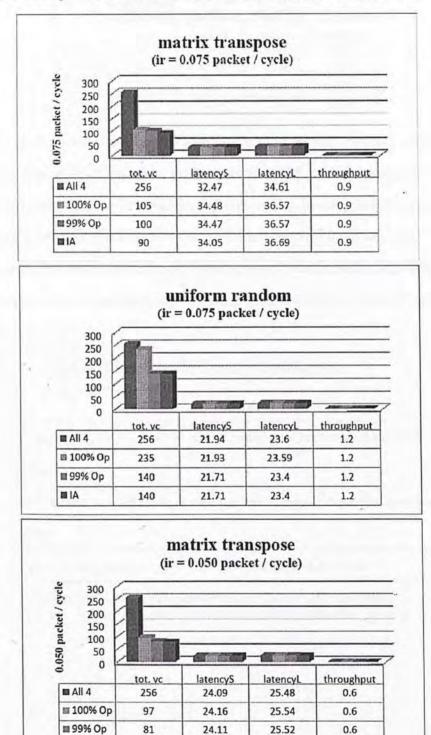

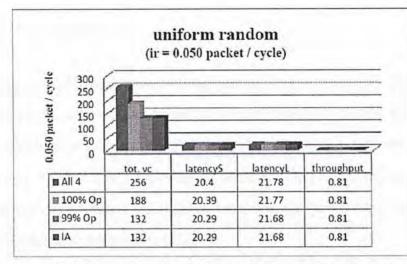

| FIGURE 5-6 OPTIMIZATION EXAMPLE ON MATRIX TRANSPOSE AND UNIFORM       | 81 |

| FIGURE 5-7 NOC CONFIGURATION EXAMPLE, SECTION 6                       | 84 |

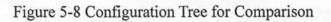

| FIGURE 5-8 CONFIGURATION TREE FOR COMPARISON                          | 85 |

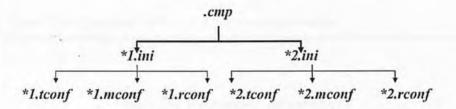

| FIGURE 5-9 FLOW OF NOCS COMPARISON                                    |    |

# List of Table

| TABLE 1-1 FEATURES OF THE PLATFORM FROM LITERATURE [4]        | 3  |

|---------------------------------------------------------------|----|

| TABLE 1-2 FEATURES OF THE PLATFORM FROM LITERATURE [5]        | 4  |

| TABLE 1-3 FEATURES OF THE PLATFORM FROM LITERATURE [9]        | 4  |

| TABLE 1-4 FEATURES OF THE PLATFORM FROM LITERATURE [10]       | 4  |

| TABLE 1-5 FEATURES OF THE PLATFORM FROM LITERATURE [11]       |    |

| TABLE 1-6 FEATURES OF THE PLATFORM FROM LITERATURE [34]       | 5  |

| TABLE 2-1 FEATURES OF LOW-POWER NOC ARCHITECTURE              |    |

| TABLE 2-2 FEATURES OF LOW-LATENCY NOC ARCHITECTURE            |    |

| TABLE 3-1 COMPARISON AMONG FOUR TRAFFIC PATTERNS              |    |

| TABLE 4-1 PLATFORM FILE TYPES                                 | 45 |

| TABLE 4-2 PROCESSES OF SYSTEM LEVEL                           |    |

| TABLE 4-3 PROCESSES INVOLVED OF LOW-POWER NOC SIMULATION      |    |

| TABLE 4-4 PROCESSES INVOLVED OF LOW-LATENCY NOC SIMULATION    |    |

| TABLE 4-5 CONFIGURATION OF GUI SECTION 1 & 2                  | 60 |

| TABLE 4-6 CONFIGURATION OF GUI SECTION 3 & 4                  | 62 |

| TABLE 5-1 FLOW ANALYSIS ON UNIFORM TRAFFIC                    |    |

| TABLE 5-2 NOC ARCHITECTURE AND TESTING CONFIGURATION          | 80 |

| TABLE 5-3 PROCESSES INVOLVED OF OPTIMIZATION                  | 82 |

| TABLE 5-4 PROCESSES INVOLVED OF COMPARISON                    | 84 |

| TABLE 5-5 CONTENTS OF , CMP FILE                              |    |

| TABLE 5-6 CONTENTS OF . TCONF FILE                            |    |

| TABLE 5-7 FUNCTION OF .MCONF FILE                             | 86 |

| TABLE 5-8 CONTENTS OF . RCONF FILE                            |    |

| TABLE 5-9 CONTENTS OF .CRPT FILE                              |    |

| TABLE 5-10 PROCESSES INVOLVED OF LOW-POWER NOC IMPLEMENTATION |    |

# Acknowledgement

When the first time stepped on this lovely campus, passion, relieve and thirsty all came up and I could barely hold my thought. It was not only about a dream that finally came true, but also the fancy of the next two years contribute to a great research topic. I saw nothing but sun shining, heard nothing but birds chirping.

Things were turning down half a year later. All at a once the whole year efforts turned to be naught and I hovered to have nowhere to settle down. I knew I had to start over, again, just had no idea from where. Things were not getting better after department transfer. Striving in cracking out source code, struggling in gloomy direction. Thesis of master degree was noting but a myth.

At this very moment, upon the completion of the thesis, I have my own heart filled with gratitude and appreciation. I am sincerely thankful for my supervisor, Professor Choy Chiu Sing, for his guidance as well as support. I would thank Zhang Min and Xin Ling, for their generous sharing and sharp insights. Thank Professor PUN Kong Pang, Professor LEUNG Ka Nang, Mr. YEUNG Wing Yee and all the ASIC Lab members who genuinely offer me help and forgive my immature all along. I can not make it without you all. I am so blessed to have the wonderful time with your accompany.

In the end, I would like to give my appreciation to my parents. Your love and concerns accompany me for all these years, which I could never ever pay off.

# **Chapter 1** Introduction

This chapter briefs the background of Network-on-Chip and similar platform designs presented by other literatures, introduces the overview of proposed platform by this thesis, and explains contribution of the platform design.

## 1.1 Network-on-Chip

With the development of silicon process technology and circuit design capacity, System-on-Chip (SoC) becomes the mainstream solution to challenge problems in the field of electronic devices. Typical SoC structure comprises of processors, controllers, memory arrays, and other possible components. The success of SoC relies on design of individual cores as well as the infrastructure interconnecting involved components.

Initially, SoC consists of a few components where communication among them are implemented by point-to-point connection. Given small number of communication paths, customizing interconnection between any pair of cores of data exchange while leaving others unconnected directly achieves tightened integrity with minimum design overhead. It occupies insignificant proportion of system design effort, with regard to the entire development duration.

Increasing complexity of chip design makes reuse of cores frequent, thus standardized core interface is widespread and share-medium architecture becomes the prevailing option in SoC domain. The backplane bus is the most common example of an on-chip, shared medium structure. The methodology of customizing connection of cores in SoC design was gradually abandoned in a general sense, and designers started to develop component interface complying with particular protocols. With well tested and verified bus structure and compatible components, it becomes no longer necessary to concern about details of interconnection. Design, verification and test of bus system are all pre-completed.

In spite of the advantage of low overhead and being convenient to use, shared medium infrastructure has limited scalability and poor power efficiency. Every data being broadcast indicates the data must reach every possible receiver at great energy cost. The impact is insignificant in the case of less than 10 cores. As future integrated systems predicted to contain tens or hundreds of components, bus based system would inevitably suffer from limited scalability and poor performance, as recognized in [1].

The plug-and-play fashion of shared-medium structure is appreciated. What is expected is an advanced communication infrastructure inheriting shared-medium's reliability, while retaining scalability and power efficiency. Communication centric design methodologies, e.g. Network-on-Chip (NoC), have been proposed in [2][3] where interconnection and communication among cores for a SoC will captivate the major portion of the design and test effort. As an approach to accommodate multiple components on a single chip, NoC satisfies all expectations and has huge research margin. Once dozens of cores involved, NoC is the promising one of the few options for now. Due to the vast range of NoC design, numerous NoC architectures are proposed with distinctive routing algorithm, flow control mechanism, arbitration strategy, etc. These configurable NoCs offer flexibility across plenty of products and reduce design-and-test effort as well as time-to-market [22].

## **1.2 Related Works**

The NoC platform is an integrated environment that provides comprehensive support for on-chip network research. Most of them are simulation based, as proposed by literature [4][5][8][10][11]. Fundamental operation flow of the platform proceeds as configuration of network architecture, traffic pattern generation, simulation and performance evaluation. The platforms differ from one another in supported network topology, buffer distribution, traffic pattern and other configurations. Average network latency is the evaluation metric shared by all platforms, while some of them extend it further to include more. Several typical platform designs are listed as below with pros and cons elaborated, individually.

J.C. Villanueva, J. Flich and etc. from Universidad Politecnica de Valencia and Sun Microsystems [4] presents a full-system simulation framework by combining Virtutech Simics [6] with an extended Wisconsim GEMS toolset [7]. It is a complete software-level event-driven simulator supporting collective communication, wormhole & virtual cut through switching and virtual channels. Supported network topologies include two dimensional mesh and bidirectional ring. A subset of the SPLASH-2 benchmarks, including FMM, LU, Radix, Radiosity, FFT, Barnes and Raytrace are applied for performance evaluation. Due to the capacity of Simics, memory behaviors are fully emulated with cache misses being detected. Impacts of various topologies and flit sizes are analyzed and compared.

| Pros                         | Cons                       |

|------------------------------|----------------------------|

| numerous benchmarks involved | software-level simulator   |

| memory behaviors detectable  | basic router functionality |

| configurable topology        | and the second second      |

| configurable flit size       |                            |

Table 1-1 Features of the Platform from Literature [4]

The system [5] proposed by B. Talwar and B. Amrutur from Indian Institute of Science is System-C based framework to explore the impact of various architectural parameters of the on-chip interconnection network on cost and performance. Its configurable parameters include topology (mesh, torus and folded torus), I/O ports number, buffer size, link bit-width and link pipeline degree. Available benchmarks are comprised of uniform random, hot-spot, matrix transpose and localized traffic patterns. Request-response traffic, or called data dependency is also taken into account. Latency and throughput are reported as performance metrics. Power consumption of link is revealed with that of network routers excluded. The authors also analyze the network parameter tradeoffs, such as NoC power/latency tradeoff, power-performance tradeoff with frequency scaling and power-performance tradeoff with voltage and frequency scaling.

| Pros                                     | Cons                               |  |  |

|------------------------------------------|------------------------------------|--|--|

| data dependence traffic involved         | basic router functionality         |  |  |

| configurable topology                    | buffer allocation strategy ignored |  |  |

| configurable link                        | data size impact ignored           |  |  |

| configurable buffer size                 |                                    |  |  |

| frequency and voltage taken into account |                                    |  |  |

Table 1-2 Features of the Platform from Literature [5]

L. Papadopoulos, S. Mamagkakis and etc. from Democritus University Thrace, Greece extends Nostrum NoC Simulation Environment (NNSE) [9] by adding new features like interface for thread allocation, irregular topology and providing new evaluation metrics [8]. It is more suitable for implementing high level transformations on dynamic network and multimedia application.

Table 1-3 Features of the Platform from Literature [9]

| Pros                                    | Cons                       |  |  |

|-----------------------------------------|----------------------------|--|--|

| can simulate fairly complex application | basic router functionality |  |  |

|                                         | small configuration space  |  |  |

S. Chai, C. Wu etc. from University of Electronic Science and Technology of China implement general NoC router architecture in System-C [10], with support to mesh & torus topologies, configurable buffer depth and bit-width. Five synthetic traffic patterns (uniform, matrix transpose I, matrix transpose II, hot-spot and NN) are modeled for performance evaluation. It claims high-extensibility of design by code modification due to modularization modeling. Simulation results with different traffic patterns are compared and buffer optimization is also taken into account. The buffer optimization focuses on general buffer depth, by observing the impact of universal buffer depth on network performance. In spite of high extensibility claimed, it is not easy for the platform users to do it.

Table 1-4 Features of the Platform from Literature [10]

| Pros                      | Cons                                          |

|---------------------------|-----------------------------------------------|

| configurable topology     | basic router functionality                    |

| configurable buffer depth | claimed extensibility is difficult to achieve |

| multiple traffic patterns | primitive buffer optimization                 |

F. Fu, S. Sun and etc. from Harbin Institute of Technology, China builds an evaluation platform for NoC on multiple levels [11]. Transaction level modeling and RTL model are both implemented for speed simulation and cycle-accurate emulation, respectively. Synthetic benchmarks are applicable, including random uniform, random locality and fixed distribution traffic. Evaluation metrics include latency, throughput and link utilization.

| Cons                               |                                                      |

|------------------------------------|------------------------------------------------------|

| basic router functionality         |                                                      |

| small configuration space          |                                                      |

| buffer allocation strategy ignored |                                                      |

|                                    | basic router functionality small configuration space |

Table 1-5 Features of the Platform from Literature [11]

N. Banerjee, P. Vellanki and K.S. Chatha from Department of CSE, Arizona State University, Tempe, proposes a VHDL based cycle accurate RTL model for evaluating the latency, throughput, dynamic, and leakage power consumption of NoC based interconnection architectures [34]. The model is configurable in packet size, link length and width, virtual channel size as well as switch technique. The RTL model is synthesized to extract SPICE level netlist. Delay, dynamic and leakage power at 180nm are all available for comparison. The authors compare the performance and power consumption, respectively of the network for varying virtual channel number or switch technique.

| Pros                       | Cons                          |

|----------------------------|-------------------------------|

| VHDL based RTL model       | basic router functionality    |

| configurable buffer size   | single traffic pattern        |

| configurable link          | primitive buffer optimization |

| selective switch technique |                               |

| power estimation possible  |                               |

Table 1-6 Features of the Platform from Literature [34]

To summarize, the platforms stated above all implement fundamental NoC functionality and are capable of running some traffic patterns to compare or report evaluated performance. Some platforms are supporting realistic cores, e.g. [5], where

real applications and memory evaluation are possible. While most of them choose synthetic benchmark. Significant insufficiency of these platforms is concluded as below:

- a) NoC architecture selected for platform development are fundamental, with limited configuration margin. Topology and buffer size are the common flexible features. Meanwhile, plenty of novel performance enhancement techniques, no matter low latency oriented or low power oriented, are not considered so far.

- b) No optimization technique is proposed to obtain better configuration for specific application. Some literatures address on buffer parameter searching by adjustment of virtual channel number at all ports simultaneously. But it can not be justified as automatic optimization.

- c) Accurate NoCs comparison across platforms is infeasible because neither traffic pattern generation nor measurement methodology is explicitly revealed and there is no mechanism to check validity of any comparison operation.

Platform proposed by this thesis addresses all those issues by introducing a systematic environment with enhanced NoC library, optimization technique and comparison mechanism. The NoC library includes multiple NoC architectures with advanced low-power and low-latency techniques. Buffer optimization tool is offered to obtain better configuration while comparison mechanism is introduced to the platform for result reproduction and valid comparison. Moreover, graphic user interface unifies the whole operation. All of them distinguish proposed platform from all the others stated before.

## 1.3 Platform Overview

Proposed platform by the thesis is a simulation-based, HDL-level integrated environment which applies synthetic benchmark for performance evaluation.

Simulation-based is the methodology chosen by all mentioned platforms above. There are a number of programming languages and tools to emulate behaviors of a complete network that are simpler in comparison with hardware description language,

in terms of development time and effort. High level programming language is widely adopt because it is easier to model network behaviors and it is possible to run real applications and assess memory status. Nevertheless, HDL is still chosen to describe NoC in current platform. High level simulation is widespread so far partly due to the fact that NoC is rare to put into practice nowadays. However, it believes that NoC technique is deemed to implement on hardware extensively some day. Then software simulation can not deliver satisfied result any more. Further, many innovative NoC designs are realized in HDL. It is beneficial to have them in platform library.

Generally, the most accurate approach to evaluate NoC for specific application is to run the actual application on well-configured NoC. But it is not the best option in reality. Running real application requires completion of the entire NoC development flow, which comprises of NoC configuration, synthesizable code generation, hardware mapping, development of processing elements and integration of network components. That is tedious and time-consuming. If reconfiguration required, the whole flow has to re-traverse again. Apparently, running real applications in early development stage is an inappropriate development methodology. Therefore, synthetic benchmark is chosen to shorten development duration and the entire flow is simplified to a large extend.

Above all, this thesis aims at development of a systematic environment for NoC research domain. It covers wide range of NoC topics: fundamental network router architecture, low-power technique, low-latency technique, configurable buffer size, various traffic patterns, performance metrics (latency and throughput), cost metrics (area and power), resource efficiency (buffer and link utilization), buffer optimization and network comparison.

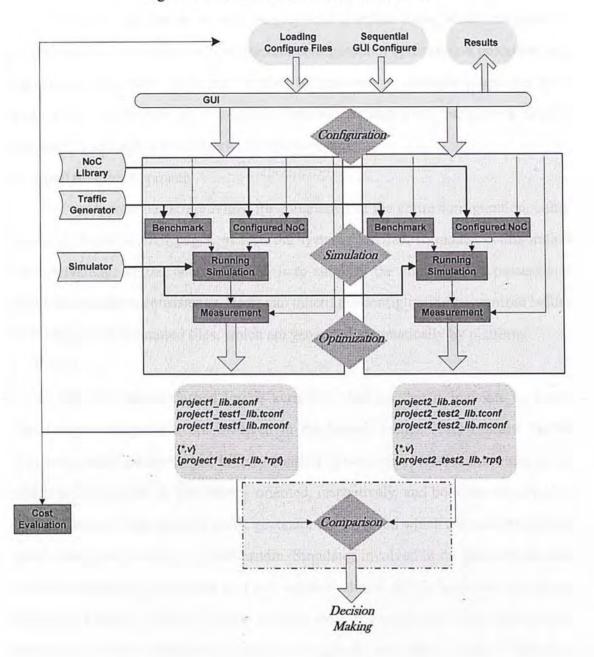

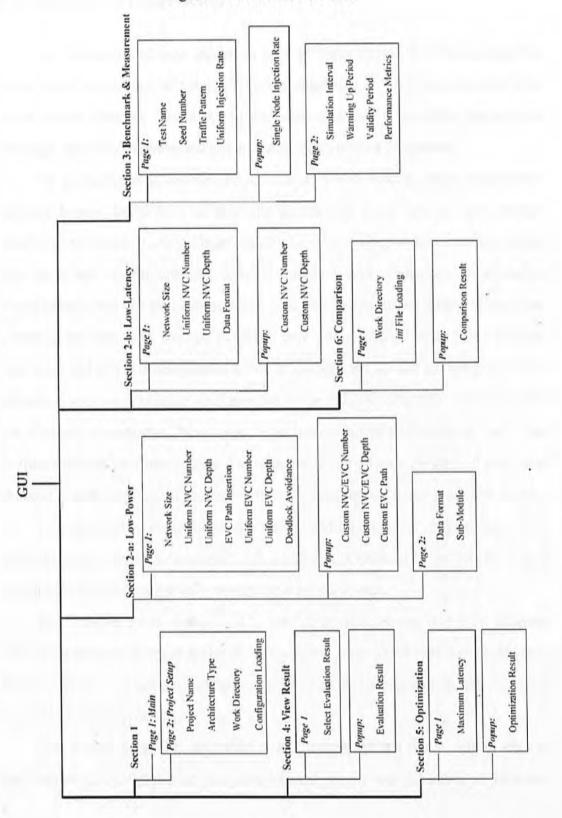

Figure 1-1 illuminates the platform structure. It composes of two major components, GUI and kernel, allowing two approaches of configuration and exporting sets of relevant files.

#### • GUI

What is viewable by users is the graphical interface alone, which composes of several sections, covering NoC architecture configuration, optimization procedure and comparison procedure. Each section may include one or multiple pages. As NoC architecture, low-power or low-latency, selected, related NoC parameters display followed by settings of benchmark and measurement.

Configuration Approach

Two approaches are provided for completion of the entire configuration, either follow guidance of GUI pages, or load the system-specified, formatted configuration files. Advantage of the latter approach is to simplify the configuration process and maintain evaluation consistency. Users can inherit the configuration customized before by loading these formatted files, which are generated automatically by platform.

Kernel

The part within dashed line is kernel of platform that is invisible by users. Three major components are involved in the kernel, named NoC Library, Traffic Generator, and Simulator. NoC Library consists of two sets of NoC architecture so far, which are low-power & low-latency oriented, respectively, and both are developed in System Verilog. Four types of traffic generator are involved which are random uniform, matrix transpose, locality and full custom. Simulator involved in the platform for now is Mentor Graphics QuestaSim 6.3f that supports almost all the hardware description languages (Verilog, VHDL, System Verilog, etc.). It ensures that NoC architectures developed by other languages can also be integrated into platform without linking to another simulator. A set of scripts in Perl called process links them all to make the platform operate properly.

Export Files

As optimal NoC architecture and configuration explored, synthesizable code of each router can be generated for area, power estimation and further practical applications. In the mean time, performance reports *project\_test\_lib.\*rpt* are also generated for future comparison. *project\_lib.aconf*, *project\_test\_lib.tconf* and *project\_test\_lib.mconf* are files of NoC configuration, benchmark setting and

measurement setting. All of them are produced for system purposes.

Proposed platform features in three major aspects. The first is configuration through GUI. With the friendly graphical interface, users can conveniently configure network architectures. This procedure can be completed without comprehension of design details of network architecture and without accessing HDL source code personally. It improves configuration efficiency, ensures architecture integrity and shortens development time. The second is buffer optimization technique. Proposed platform is capable of analyzing buffer utilization rate and offers suggestions for optimized buffer allocation. The third is NoCs comparison. Comparison among NoCs is prominent as so many innovative NoC designs emerge these days. To compare them consistently and efficiently is critical for selecting the final NoC for specific application. Particular schemes ensure that the comparison is meaningful and efficient.

All of those features ensure integrity of NoC library and shortens time for sifting out appropriate solution among multiple choices. If users' requirement can be satisfied by available NoC architecture with proper configuration, screening process is fast to complete. If not, the platform still assists users to explore configuration priority and possibilities.

# 1.4 Author's Contribution

Given the fact that so many innovative configurable NoC architectures emerge recently, it is necessary and urgent to have a platform to utilize these designs in a unified manner. It assists to identify pros and cons of each design and to single out the most suitable one for specific application or application domain.

The proposed platform achieves this objective by presenting a complete flow from NoC architecture configuration, to NoCs optimization and comparison. NoC architectures of proposed platform integrate advanced high-performance techniques that are unavailable in rival platforms. Moreover, accurate area and power estimation is feasible to obtain. The platform also offers suggestions for buffer optimization. The entire flow is strictly administered to satisfy system quality requirement, making sure

that comparison proceeds validly. The platform is open to integrate more NoC architectures and extension of optimization tools is also feasible. Proposed platform design lays the foundation for systematic environment of NoC research domain in the long run.

The thesis is organized in six chapters. Chapter 2 elaborates router architecture of NoC library which are the most important platform component; Chapter 3 introduces benchmark and measurement setting; Platform structure, including file system, graphical interface and platform processes are described in Chapter 4; Chapter 5 addresses optimization technique as well as comparison mechanism, and Chapter 6 summarizes the thesis and presents the future work.

# Chapter 2 NoC Library

NoC is such a communication structure that connects all the cores (processors, memories, controllers, etc.) and facilitates message transfer among them. The cores connected by NoC are called processing elements. A complete NoC infrastructure consists of three types of components, named network router, network interface and physical link. Network router, as backbone of NoC is the module guides the message from one network node to another. It determines the path of the message as well as tackles resource contention. Network interface is the module connecting network router to processing element. It is responsible for packetization and depacketization of the message, as well as signaling exchange for message acquisition and halt. Specific bus protocol must be complied by both processing element and network interfaces. Physical link connects neighboring or non-neighboring routers which transits the message from one spot to another. Simplest physical link is wire with or without register. Complex and high-efficiency physical links are also proposed to satisfy extraordinary quality requirements [18].

NoC library, as the most important platform component, comprises of two sets of configurable NoC architecture, low-power oriented architecture developed by M. Zhang and C.S. Choy [12] and low-latency oriented architecture developed by L. Xin and C.S. Choy [13], both are from Electronic Engineering Department, The Chinese University of Hong Kong. Each set of architecture is described by a number of System Verilog files which are called and copied by platform. Platform users can select either set of architecture, and configure it to apply to specific application.

## 2.1 Network Terminology

#### NoC Data Format

To clarify the description of network communication, definitions of key terms are explained herein. *Data* and *message*, if not specified, are synonymous in this thesis,

#### Chapter 2 NoC Library

both are abstract description of the information generated by one processing element and required by another. The data unit within processing element could be in any shape, while the message transferring within network must comply with particular protocol for less complex hardware design overhead and communication efficiency. Thus besides of meaningful processing element payload, information on routing path, reserved buffer lane, message validity are all integrated into a message unit for network transfer. The encasement is called packetization, accomplished by network interface. Therefore what the network routers are dealing with is fixed message block, rather than arbitrary data shape.

When going through packetization step in network interface, data from processing element is sliced into pieces and packaged into fixed width of unit, called *packet*. It is the basic shape of network message, all bits of which share the same routing path within the network. A packet comprises with two parts, control signals and payload. Payload is the actual data segment for transfer. On contrary, control signal is added by network interface for routing computation. It includes packet status, destination address, output port index, etc. Width of control signal is determined by network size, maximum virtual channel number at single port and so on. While the width of payload can be arbitrary. Figure 2-1 shows the format of typical packet.

Packet is further sliced into smaller units, called *flit*, which is also the smallest unit in network data exchange. The number of flits comprising a packet is called packet length. As width and length of packet are determined by users, width of flit is fixed automatically since all flits are forced identical width for the sake of lower hardware complexity. Every packet consists of at least one *head flit* and one *tail flit*. Head flit comprises routing information while tail flit indicates transfer completion. If more than two flits are assigned for a packet, others rather than head or tail are named *body flits*. Since flit is just a transformed representation of identical message as packet, extra controlling information is also imbedded in flits, specificly within head flit alone. Head flit comprises the data contained in packet as well as flit type information (head, body or tail) and virtual channel information (which virtual channel at downstream router is reserved for current packet).

| at | Туре | нх | HY | Port_Inde | ex | <br>                   | Data |  |

|----|------|----|----|-----------|----|------------------------|------|--|

|    |      |    |    |           |    | <br>Data<br>Port Index |      |  |

Importance of data format is often understated in NoCs evaluation and comparison. Although network bandwidth is approximated by packet number, the maximum amount of data transferred by a link is one flit. If literatures reports evaluation results with data format undisclosed, comparison across NoC designs is meaningless. Impact of different packet lengths on network performance is seldom taken into account in NoCs comparison.

#### Topology

Given the three types of network components and associated processing elements, the second step to build NoC is to organize all those modules in particular layout, called topology. Network topology can be simply categorized to regular and irregular. Irregular network is highly relevant with application and not commonly suitable for the purpose of reuse. Common regular topology includes two-dimensional mesh, torus, star, butterfly, etc. Two-dimensional mesh is the only topology covered in this thesis. The number of router port is configurable in both network architectures of NoC library, thus arbitrary two-dimensional topology is feasible to implement, as long as top HDL module and associated routing algorithm are revised accordingly.

#### Routing Algorithm

Routing algorithm is used to determine the path that message follows from its source node to destination. It often relies on network topology. Routing algorithm falls into two types, determined or dynamic. Determined routing algorithm refers to fixed path once source and destination nodes are selected. On contrary, dynamic routing algorithm evaluates traffic congestion and allocates path dynamically. Determined routing algorithm is easy to implement and costs less chip resources. Dynamic routing algorithm might ease traffic congestion to some extent, yet resource occupation and computation time are its shortcomings in comparison with the former one.

### Virtual Channel

Virtual channel is a flow control mechanism proposed to increase network throughput while reduce average network latency [30]. It is obtained by dividing the buffer storage associated with each physical channel into several small queues that can hold one or more data unit. The virtual channels associated with one physical port are allocated independently.

# 2.2 Basic Structure

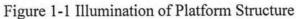

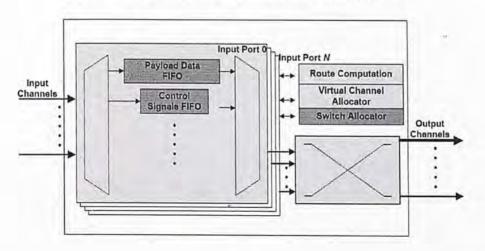

Function of network router is to receive packets and determine their succeeded network position, neighboring router buffer or local processing element. Architecture of basic network router is described as below ( Figure 2-2). Network router owns multiple input ports and output ports of identical number. Certain input ports are connected with associated output ports at each cycle, allowing packets at input ports to move forward. Three major components inside of router are buffer, controller and switch. Buffer is used to store packets in case downstream router is busy. Controller calculates succeeded path of arriving packets and switch provides the path from input ports to granted output ports. Suppose five ports (input and output) are labeled as *East*, *North*, *West*, *South* and *Local*. If *East* input port and *West* output port are connected by controller, then packets at *East* input port of current router move forward, leaving current router through *West* output port and ultimately arrive at *East* input port of downstream router.

Figure 2-2 Normal Network Router Architecture

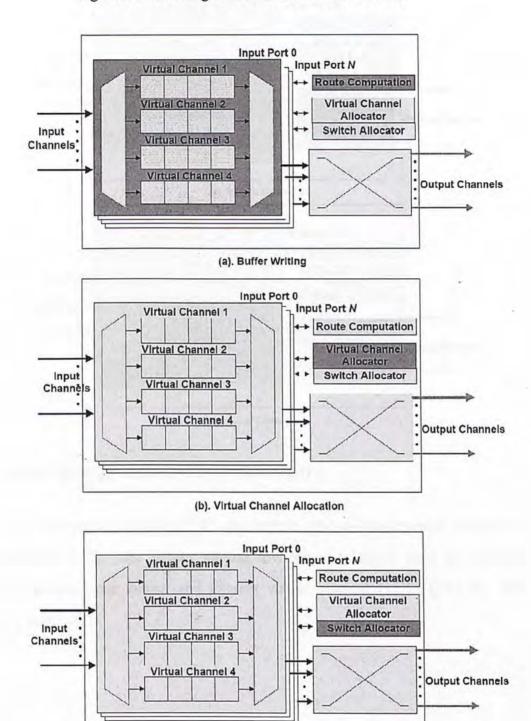

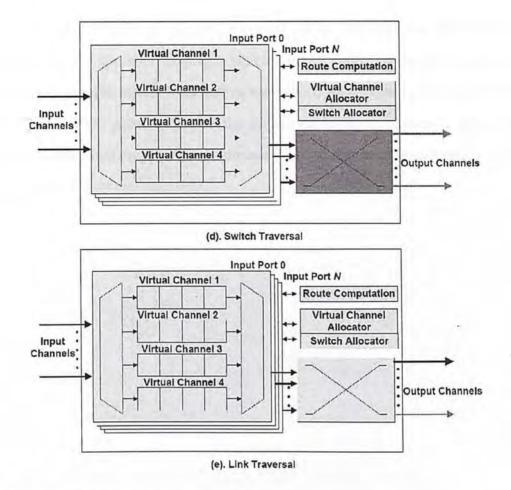

Typical network router is of five pipeline stages, listed as buffer writing (BW), virtual channel allocation (VA), switch allocation (SA), switch traversal (ST) and link traversal (LT). Function of each stage is:

#### Buffer Writing

Network router has configurable number of input ports as well as output ports, with the exact number depending on applied topology. For 2-D mesh topology, maximum number of input ports of the network router is five. As a packet arriving at one input port of the router, it is stored in buffers of the router temporarily in case of switch unavailable or downstream router being busy. This mechanism increases network throughput by letting idle links be utilized as much as possible.

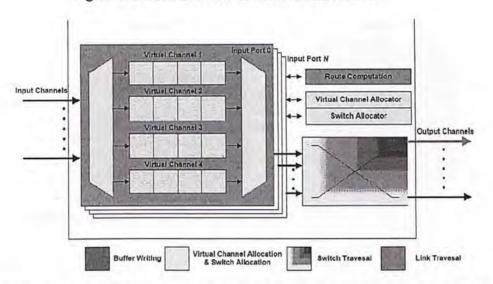

## Virtual Channel Allocation

Since only stop at buffers during transferring, the packets stored in current router buffer has to be granted with buffer of downstream router before moving forward [16][20]. As virtual channel adopt as flow control mechanism, the packet has to succeed requesting of a non-full virtual channel. If buffers at downstream router are all fully filled, there is no way packets can keep transferring in spite that no contention occurs.

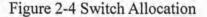

For example, in

Figure 2-3, *packet A* is stored at *virtual channel 1*, *East* input port of *router i*, and its next stop is *router j*, according to routing algorithm. Since *router i* and *router j* are connected via *West* output port of *router i* and *East* input port of *router j*, virtual channel allocation is the process of checking virtual channel status at *East* input port of *router i*), to select an available virtual channel, which is neither full nor reserved, and reserve it for *packet A*.

#### Switch Allocation

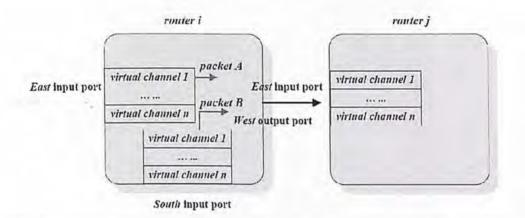

With virtual channel successfully reserved at downstream router, one packet still needs to compete switch with other packets requesting for identical output port of current router. The process of granting one output port to one input port requesting for it is called switch allocation.

In Figure 2-4, if virtual channel 1 at East input port of router j is reserved for packet A (virtual channel 1 at East input port of router i) and virtual channel 2 at East input port of router j is reserved for packet B (virtual channel 1 at South input port of router i), contention occurs as both packets requesting West output port of router i to reach router j simultaneously. Switch allocation is the mechanism to decide which input port will be granted the switch to connect to West output port of router i.

#### Switch Traversal

After packet having succeeded in both virtual channel allocation and switch allocation, associated input / output port.link is connected by switch and the granted packet takes one cycle to travel from input virtual channel to output port, called switch traversal.

### • Link Traversal

Neighboring routers are all connected with links, through which packets transfer from one node to another. Normally, one cycle is spent on travelling physical link from output port of current router to input port of downstream router. Actually latency depends on specified configuration.

Figure 2-5 illuminates the five pipeline stages of network router. The block in gray indicates that the blocks are activated at current pipeline stage.

Figure 2-5 Five Stages of Normal Network Router

(c). Switch Allocation

# 2.3 Low-Power Oriented Architecture

The low-power oriented NoC architecture inherits fundamental features of basic network router and applies several low-power schemes, such as low-cost allocator design, clock gating and express virtual channel [15][24][25][26]. The summary is shown in

Table 2-1. First two low-power schemes in regard to cost reduction are impossible to be implemented in high level languages which emulate functionality alone. Express virtual channel insertion affects both latency and power, yet it is also never reported to be add into any NoC platform. Since the impact of EVC on latency is generally unpredictable while that on power is determined, current architecture supporting EVC is categorized as low-power oriented.

| Topology            | 2-D Mesh                |

|---------------------|-------------------------|

| Routing Algorithm   | X-Y                     |

| Buffer              | Size Configurable       |

| Low-Power Schemes   |                         |

|                     | Low-Cost Allocator      |

|                     | Clock Gating            |

|                     | Express Virtual Channel |

| Low-Latency Schemes |                         |

|                     | Low-Cost Allocator      |

|                     | Express Virtual Channel |

Table 2-1 Features of Low-Power NoC Architecture

## 2.3.1 Low-Cost Allocator Design

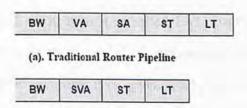

Just as stated in last chapter, conventional network router is of five stages including virtual channel allocation and switch allocation. Low-power oriented architecture from NoC library merges two allocator into one, to reduce clock cycles from two to one. It scales silicon area and power consumption with little observed penalty. With substitution of generic allocator with a combined one, network router pipeline stage drops from five to four.

Figure 2-6 Pipeline Stage Comparison

(b). Optimized Router Pipeline

## 2.3.2 Clock Gating

System clock contributes to significant power consumption to integrated circuits [27]. As clock frequency fixed, certain amount of power consumption is bound to generate by clock voltage reverse, no matter how extensively circuit components are in operation. Turning off system clock of specific components or sub-modules while they are idle is a feasible solution to optimize power consumption. Such technique named clock gating applies to most sub-modules within network router.

### 2.3.3 Express Virtual Channel Insertion

As a flow control mechanism, Express Virtual Channel (EVC) distinguishes certain paths within the network from others [31]. The privileged path is called EVC path that benefits in terms of latency and power. Low-power oriented architecture of NoC library supports express virtual channel that provides more flexibility to network configuration.

#### 2.3.3.1 Notation

According to the definition of express virtual channel, EVC path starts at any node within the network and ends at another. The starting node is named *source* node, with ending node as *sink*. Routing algorithm calculates the routing path in between and all node(s) along the EVC path is(are) called *bypass* node(s). If, routing path of a packet overlaps with an EVC path, then it is called EVC packet, distinguished from other packets which never pass through any EVC path called NVC packets. Any EVC packet must associate with at least one EVC path. Once the EVC packet reaches its associated source node, network router would deal with it by distinctive mechanism rather than the conventional one.

#### 2.3.3.2 Pipeline and Latency

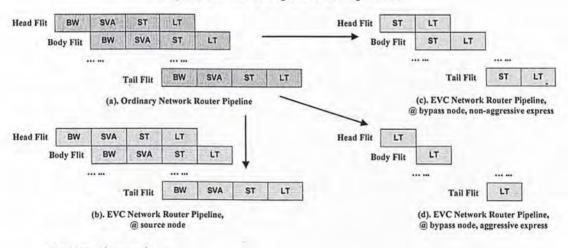

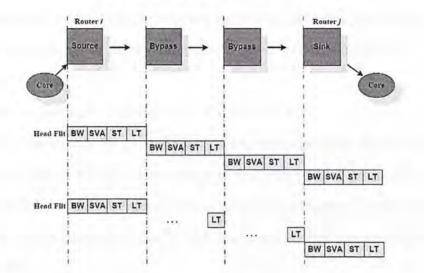

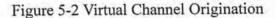

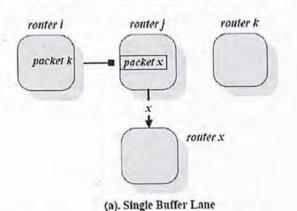

Whenever EVC packet reaches associated source node, it proceeds router

stages as normal until being granted to output port of source node and arriving at input port of the first bypass node. Then EVC packet skips BW (buffer write), SVA (switch and virtual channel allocation), ST (switch traversal), and directly go for LT (link traversal) stage. This is achieved by assigning EVC packets higher priority over NVC packets that contend resources with them.

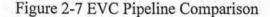

Figure 2-7 lists pipeline stage of involved cases. When EVC path is inserted into network, pipeline stage at source node is identical as inserted before, only the pipeline stage at bypass node is updated. As two bypass schemes, non-aggressive and aggressive bypass, available, EVC flit could spend two cycles through bypass node (Figure 2-7(c)) or one cycle only (Figure 2-7(d)). In non-aggressive express router, switch traversal and link traversal stages are inherited; while in aggressive express router, only link traversal stage remains.

Just as shown in

Figure 2-8. A packet injects into network from node *i* with destination of node *j*. In conventional four stage pipelining network, the packet spends four clock cycles at each router, amounts to 16 cycles in total. If, with EVC path inserted, it spends 4 cycles at source node just like before, and then only 1 cycle at each bypass node and 4 cycles at sink node finally. Then the latency spent on the path adds up to 4+1+1+4 = 10 cycles, with six cycles cut on bypass routers. Thus, more routers are bypassed along EVC path, more latency improvement brought in.

Figure 2-8 EVC Bypass Example

#### 2.3.3.3 Power Consumption

Similar with latency, power consumed by skipped stages is saved to achieve less overall cost. Due to the insertion of EVC, routers of NoC can be categorized into four types, source, sink, bypass and normal, where normal is the one not involved in any EVC path. A router can be source and/or sink and/or bypass as long as no multiple EVC paths overlapped. Various types of router have different architectures. Figure 2-9 displays all possible network router structure. Specifically, EVC allocator is present in source router alone and EVC lane only in sink router, while switch in bypass router is tiny different from that of other types of router.

Figure 2-9 EVC Router Architecture Comparison

Chapter 2 NoC Library

Thus in comparison with conventional network router, EVC insertion brings extra components and complicates arbitrate operation. However, the overhead is offset by improvement elsewhere. In general, relevant per-hop energy is given as

$$Enode = Erouter + Elink \tag{1}$$

$$Erouter = Ewritebuffer + Ereadbuffer + Esvaarb + Exb$$

(2)

where *Enode* is the energy for passing through one particular node, *Erouter* is the energy consumed on passing through router, *Elink* is the energy spent on passing link wire, *Ewritebuffer* and *Ereadbuffer* are the buffer write and read energy, *Esvaarb* is the virtual channel and switch arbitration energy, and *Exb* is the energy required to traverse the crossbar switch.

While EVC flit traveling, it skips router pipeline at bypass router without being buffered or evoking arbitrator. If non-aggressive bypass scheme adopt, switch traversal remains and the pipeline stage decreases to two. If aggressive bypass scheme adopt, switch traversal is further skipped as well then power consumption is significantly reduced to approach *Elink*. Equation (3,4) express energy constitution for bypass router when EVC flit going through.

| Enode = Exb + Elink      | (3) |

|--------------------------|-----|

| Enode = Econnect + Elink | (4) |

*Econnect* represents energy consumed by wire within network router when aggressive express applies. The actual energy of *Econnect* is tiny but specified here to distinguish from energy exhausted by passing switch itself. The bold line shown in

Figure 2-10 is the bypass wire for aggressive bypass scheme.

windther Think Hall Instantia and the State F. Schert F. Somethers F.V.

the print of the second s

we do not be a set of the set of

Figure 2-10 Comparison of Non-Aggressive and Aggressive Express

## 2.3.3.4 Deadlock Avoidance

EVC insertion has an underlying assumption that EVC packet must be in greater amount or is expected to reach destination as early as possible. Granting higher priority ensures enhancement to this expectation. Meanwhile underlying hazard could hurt network performance if no extra mechanism introduced. For example, if during a relative long period, EVC packets are continuously ejecting out from source node and NVC packets sharing the same path are injecting into network simultaneously. Then the NVC packets are blocked constantly until all EVC packets complete transferring. This is called deadlock which brings in substantial and unacceptable system delay.

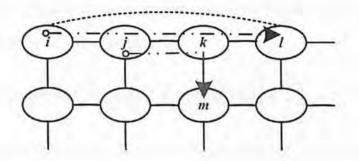

Figure 2-11 indicates a case of two flows, sourcing from node i to node l and from node j to node m respectively, and EVC path is inserted from node i to node l. Assuming within a certain interval, node i and node j keep ejecting packets to their destinations. Since they both share the path from node j to node k, only one flow can be arbitrated to pass through west output port of node j at a single cycle. Due to the higher priority of EVC packets, the packets from node j to node m will be blocked indefinitely. Output flits from node j would be "*EEEE*..." where "*E*" represents EVC flits. The scheme to eliminate deadlock is to set upper limit duration of continuous EVC flits transfer. Whenever source node ejecting EVC flits out a certain number of clock cycles in a row, succeeding EVC flits are forced to give way to the NVC flits. Continuous transfer of NVC flits is as well constrained to a fixed number of cycles for similar reason. When upper limit touched, it switches to transfer EVC flits instead. If it allows EVC flits to be transferred at most 4 in a row, and then 2 cycles are reserved for NVC flits, the deadlock avoidance parameter is set to be 4:2, output packets should be "*EEEENNEEEENN...*" where "N" represents NVC flits.

Figure 2-11 Dead Lock Example

#### 2.3.3.5 EVC Insertion Strategy

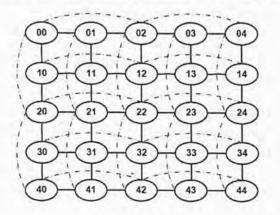

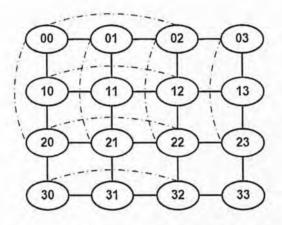

The actual efficiency of express virtual channel largely rests with distribution of EVC paths and characteristics of applied traffics. In general, there are two approaches of EVC insertion. The first is uniform distribution, and the second is custom distribution. Figure 2-12 depicts uniform EVC insertion for  $5 \times 5$  mesh network. The only insertion rule is EVC paths overlapping prohibited.

Figure 2-12 Uniform EVC Insertion for 5×5 Mesh Network

Uniform is just an abstract notation indicating that EVC paths are roughly distributed uniformly rather than a mandated principle to follow. For instance, given 4  $\times$ 4 network, designating (0, 0) -> (0, 2) as EVC path essentially has no difference from designating (0, 1) -> (0, 3). As no analysis flow proposed yet, custom distribution is also a general conception and manual analysis and tentative planning still works to some extent. [12] proposed a greedy EVC insertion algorithm for low-power objective. It models energy savings with regard to any possible EVC path inserted in the network and ranks them in descending order. Then iterative insertion process evokes to insert EVC path in sequence until insertion rule violation occurs. Although current insertion rule and insertion approach do not guarantee ideal EVC insertion outcome, evaluation experiments still shows considerable results.

## 2.4 Low-Latency Oriented Architecture

Low-latency architecture from NoC library shares the same network topology, routing algorithm, buffer configuration as well as allocator design with low-power architecture. Configurable parameters of low-latency architecture is less than that of low-power.

| Topology              | 2-D Mesh          |  |

|-----------------------|-------------------|--|

| Routing Algorithm     | X-Y               |  |

| Buffer                | Size Configurable |  |

| Pipeline Stage Number | 4                 |  |

| Types of Router       | 1                 |  |

| Low-Latency Schemes   | Look-ahead Bypass |  |

Table 2-2 Features of Low-Latency NoC Architecture

#### 2.4.1. Lookahead Bypass Scheme

In NoCs, the width of control signal is usually smaller than that of payload data. After obtained all the necessary control signals from its neighborhood, the router can complete all the allocations. Since the allocation computation is ahead of the switch traversal of payload data in the router pipeline, the control signal is required earlier. Similarly, suppose generation of control signal completes earlier, the control signal can be transferred to the next router in advance too. Once router completes allocation early enough, payload can bypass the input buffer and go across the router's switch directly. This is called lookahead bypass (LA-BP) scheme which is dynamically determined for each incoming flit.

## 2.4.2. Lookahead Bypass Router Architecture

The NoC architecture in [13] that uses lookahead bypass mechanism to speed up arbitration with small penalty along critical path is integrated into proposed platform as the low-latency architecture. Once lookahead bypass enabled, flit latency at single node reduces from four to two. Although it sounds like less improvement in comparison with express virtual channel that minimizes latency to one clock cycle utmost, it brings no adverse effect to other flits and results far significant enhancement in terms of network latency.

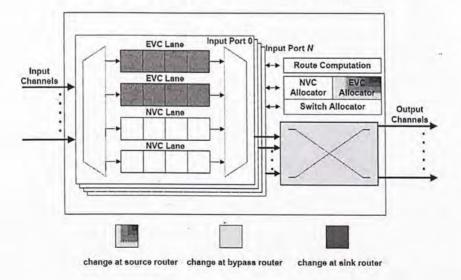

Figure 2-13 illuminates architecture of lookahead bypass router. The lookahead bypass router is capable of handling two types of flits: lookahead and normal ones, so that additional components are integrated into the normal router. A distinctive feature of lookahead bypass router is that routing information is separate from payload in router buffer. Therefore, input buffer is divided into two types. Payload FIFO stores flit payload while control signal FIFO stores control signal.

Switch allocator is another module redesigned for lookahead bypass. Since all flits need to send control signals to downstream router ahead of payload, the traversal of control signal is integrated into the pipeline stage of switch allocation. For the purpose of acceleration, two stage speculative control signal multiplexers are applied to switch allocator. If a flit wins the first stage arbiter, which arbitrates requests from the same input port, its control signal will be transferred by the first stage multiplexer instantaneously. Virtual channel allocator is similar with that of normal network router, while crossbar of lookahead router only delivers flit payload.

The essence of low-latency NoC architecture is to parallelize some arbitrate computation to reduce network router latency. Evaluation result shows distinctive improvement for various traffic characteristics. When injection rate is relatively low, low-latency network router brings in significant latency reduction; with heavy traffic, it as well shows enhancement to some extent.

## **Chapter 3** Benchmark and Measurement

The ultimate objective of NoC design is to run real applications on spread cores interconnected by network. If so, processors and cache structures are supposed to be taken into account for real circumstance evaluation. This entire process is so complex that plenty of efforts and time for functionality partition, processing elements development and network integration is demanded. Particularly, due to the complexity of real application, it is infeasible to track traffic or analyze capability of contention resolution. Therefore, it is more realistic to implement real application later on and to use synthetic benchmark for rough NoC evaluation at first. The synthetic traffic can capture the salient aspects of the application-driven workloads, and is easier to design and manipulate [21].

Synthetic benchmark is typically characterized and constructed along three dimensions: spatial distribution, temporal distribution and message size specification. Spatial distribution governs the spatial traffic pattern: who communicates with whom; temporal distribution describes the message generation probability over time while message size specification defines packet length as well as packet width [14].

Simple synthetic benchmark leads to easy measurement process and less time consumption. On the contrary, detailed consideration along all the three dimensions brings accuracy at the price of more efforts in performance analysis [29]. Proposed platform provides four types of synthetic benchmark to evaluate NoCs, including random uniform, matrix transpose, locality traffic and full custom. Each type of benchmark is implemented by corresponding traffic generator.

Traffic generator is the substitute of processing element to generate synthetic benchmark. Each generator associates with one processing element. It is controlled to eject data outwards. The data comprises no actual meaning but comply with particular statistics characteristic. Traffic generator is categorized by spatial distribution alone while temporal distribution of all traffics is manipulated by pseudo-random scheme. It generates traffic randomly in every single cycle but certain communication probability

is satisfied if measurement interval is prolonged. The longer statistics interval, more accurate final communication probability is as pre-set value. Term definitions are listed as below.

*Pi*: communication probability of node *i*, to indicate the likelihood of sending messages to the network from node *i*. It is measured by number of packets ejected out every cycle.

*Dest(i)*: an array of numbers, each element represents index of one node that receives messages generated from node *i*

*flow*(*i*, *j*):messages entering network from node *i* and leaving network at node *j*

IR(i, j): injection rate of flow(i, j), to indicate likelihood of occurrence of flow(i, j).  $P_i = \sum IR(i, j), \ j \in Dest(i)$

# 3.1 Benchmark Generation

## 3.1.1 Types of Traffic Patterns

Four traffic patterns are available in proposed NoC platform that are uniform random, matrix transpose, locality and full custom. Uniform random and matrix transpose are categorized as classic traffic patterns because they are fundamental ones for NoC evaluation. Uniform random is the most balanced traffic which emulates the best case of data communication among all nodes. It reflects the capability of target network but also hides network sins such as poor routing algorithm. Matrix transpose, on contrary, is extremely unbalanced and tends to get congested as communication probability increases. It predicts the worst capability of a network. Locality traffic pattern evolves from uniform random, but takes into account of the relation between transfer distance and communication probability. It reflects the fact that function components of heavy data exchange are always mapped localized. Finally, full custom traffic pattern allows any form of traffic spatial distribution. It is able to approximate any realistic application.

| Traffic Pattern  | Pros                                     | Cons                                                            |  |

|------------------|------------------------------------------|-----------------------------------------------------------------|--|

| Uniform Random   | easy to implement and analyze;           | best case, seldom occur in reality;<br>network sins hidden;     |  |

| Matrix Transpose | easy to implement and analyze;           | worst case, seldom occur in reality;<br>network sins magnified; |  |

| Locality         | function components mapped localized;    | treat nodes of identical distance equally;                      |  |

| Full Custom      | emulate any traffic spatial distribution | difficult to implement and analyze                              |  |

Table 3-1 Comparison Among Four Traffic Patterns

#### 3.1.1.1 Classic Traffic Patterns

Certain types of traffic pattern are considered as first resort to evaluate a newly designed NoC, e.g. uniform and matrix transpose. They are both fundamental synthetic benchmarks to evaluate NoCs, which differ from each other along spatial dimension.

Uniform traffic pattern assumes that any node of the network has exact the same probability to send messages to any other nodes. Thus the entire traffic is strictly, uniformly distributed within the network. Uniform random traffic is quite benign because it naturally balances load across network channels, very close to the best-case workload.

Matrix transpose traffic pattern otherwise is one of the permutation type, which is seriously congested along certain paths. As network size increases, it deteriorates further. For instance, suppose X-Y routing algorithm adopt with injection rate of each node equals to 0.2 flit/cycle, then the total traffic across node (0,0) is 0.6 flit/cycle in 4 ×4 mesh network and 1.0 flit cycle in  $6 \times 6$ , which means the channel is saturated. Matrix transpose traffic pattern allows for extreme spatial distribution and magnifies the sins of network design.

Both traffic patterns are widely used due to easiness of implementation and reflection of NoC performance under extreme traffic characteristics. Allowing for both simultaneously delivers a relatively complete overview of NoC performance.

#### 3.1.1.2 Locality Traffic Pattern

Classic traffic patterns either broadcast to every point of the network, or assign single destination for individual flow, overlooking the fact that function components of heavy data exchange are always mapped localized. A unified expression that is allowed to adjust the locality so as to analyze the network behavior under locality traffic is presented. By setting locality factor with distance *d* for each individual node, amount of traffic sending to nodes of certain distances is finely controlled.

According to the literature, locality traffic pattern has to follow two rules, first, the probabilities of a node sending message to the nodes of identical distance are exactly the same; second, this probability is determined by locality factor array a(d). Given a(d), communication distribution probability *DP* is calculated by Equation (5-6).

$$coef(d) = 1 + \frac{\alpha(d)}{d+1}$$

$$P_{c} = \frac{1}{\sum_{d=0}^{D} N(d) coef(d)}$$

(5)

(6)

$$DP(d) = coef(d)P_c \tag{7}$$

Where coef(d) is the distribution coefficient for a node with distance d; N(d) is the number of nodes of distance d; D is the maximum distance between the target node and any other node within the network; Pc is the common probability factor; DP(d) is the communication distribution probability.

For instance, according to Figure 3-1, if  $\alpha$  fixed to constant 1, to determine the communication distribution probability of node (0,0), for its distance array [0, 1, 2, 3, 4, 5, 6], we obtain number of destination nodes with identical distance is [1, 2, 3, 4, 3, 2, 1]. By Equation (5), we obtain the coefficient array *coef(d)* of node (0,0) as [2, 1.5, 1.33, 1.25, 1.2, 1.166, 1.143]. By Equation (6), we calculate  $P_c = 0.0474$ . Thus DP(d) = [0.0948, 0.0711, 0.0630, 0.0593, 0.0569, 0.0553, 0.0542]. A specific case is  $\alpha$  of all nodes being fixed to 0, then *coef(d)* is fixed to constant 1 for all distance, locality traffic pattern turns into random uniform traffic pattern.

Figure 3-1 Distance Graph for Locality Traffic Pattern

Since DP(d) is no less than zero, valid range of  $\alpha$  depends on distance d, and it can be basically divided into four intervals (or points).

$\alpha = -(d+1) \qquad => coef(d) = 0$  $0 > \alpha > -(d+1) \qquad => 1 > coef(d) > 0$  $\alpha = 0 \qquad => coef(d) = 1$  $\alpha > 0 \qquad => coef(d) > 1$

Communication probability of any flow is multiple of common probability factor. Thus selection of proper  $\alpha$  value determines the approximate domain of final probability.

#### 3.1.1.3 Full Custom

Full custom traffic pattern implies that any new characterized traffic pattern could be simulated by platform for more specific purposes. For instance, the generic traffic pattern which takes into account temporal burstiness [14] can be added to enhance platform capability of emulating real application of significant temporal distribution. Any imitation of real application by statistics can also integrated into proposed platform in this manner. Manual configuration through graphical interface flow by flow is required to import traffic pattern.

## 3.1.2 Traffic Generator

As synthetic benchmark applied to NoC exploration, the processing element which is supposed to be processor, memory, etc. in real application is replaced by other module named traffic generator which involves with no data processing but is capable of generating traffic of specified characteristics. In the meantime, network interface is simplified to FIFO [17].

The data produced by traffic generator is formatted as network requires then packetization module in conventional network interface becomes dispensable. FIFO, as a module within network interface, buffers the excessive messages when network is incapable of dealing with plenty of data timely. FIFO in our design is of very large volume to store thousands of packets, which is obviously not realistic. The reason of it is that data dependence is ignored in traffic generator case, and no stop signal would have ever been issued to pause traffic generator sending data out. Thus sufficient FIFO volume is necessary to prevent overflow or message drop as congestion being severe in some cases. If, which is rare, the FIFO is filled, it indicates that either faulty exists or current NoC design is incapable dealing with such amount of traffic. Structure of FIFO is simply the fundamental synchronous write and asynchronous read one. Since only simulation proceeds in platform operation, huge size of FIFO is not a concern. Normally, processing elements interact with network by receiving messages. Modules for receiving messages are omitted here because no further processing involved except that relevant packet information is written into text files for statistics.

The essence of traffic generator is to configure all flows sourcing from current node. Each flow is determined by three factors: source node, destination node and injection rate. Every node involved in sending data to network would mount a traffic generator and a FIFO. As source node of flow is default determined, traffic generator requires data from platform users to clarify destination node and injection rate of each flow. Specific design of each type of traffic generator is presented below.

#### Random Uniform

The "Uniform" feature of random uniform traffic pattern is guaranteed by two rules: Dest(i) includes all the nodes of the network other than i, so if given mesh network  $m \times n$ , size of Dest(i) equals to  $(m \times n-1)$ ; secondly, assign identical value to any IR(i, j) or IR(i, j)=Constant,  $j \in Dest(i)$ . Sum of injection rates of all flows amounts to communication probability of node i,  $Pi = \Sigma IR(i, j)$ =Constant,  $j \in Dest(i)$ .

Since on hardware level, traffic generator associates with specific node and is irrelevant with that of any other node, proposed platform further extends it to allow communication probabilities of different nodes differ from one another. Therefore, communication probability of each node is read specifically and applied to configure associated traffic generator. Zero communication probability Pi = 0, namely no message sending to the network from current node, is permitted as well. Provided that, no traffic generator is connected to corresponding network router.

#### Matrix Transpose

In comparison with random uniform, spatial distribution of matrix transpose pattern is concise as at most one unique flow exists for each node, with index of destination node obtained by unified expression. Nodes along diagonal line are excluded that they send and receive no message. Thus size of Dest(i) = 0 or 1. Matrix transpose pattern here is tailored to apply for non-square mesh topology as well. The nodes, whose destination node coordinate beyond network range, are excluded from data exchange. Given mesh network  $6 \times 5$ , then node(5, x), x = 0...4 are excluded from communication (suppose node index labeled from (0, 0)) which makes it virtually  $5 \times 5$ network. Like random uniform, communication probabilities of valid nodes can be identical or distinctive, depending on desired traffic characteristics.

#### Locality

In the case of locality traffic pattern, size of Dest(i) equals  $(m \times n-1)$  as well if given network  $m \times n$ . These destination nodes are further grouped by distance from node *i*, Dest(i,d). Upon selection of network size, group numbers and destination nodes associated with each group are calculated automatically by the platform. Users are supposed to fill locality factor array  $\alpha(d)$  for each node, or unify them under the

identical  $\alpha(d)$ . coef(d) and  $P_c$  are not directly used in traffic generator but combined to obtain total injection rate of group IR(i, d, -). The method is feasible because all flows within a group share the same injection rate. Picking up any node randomly among destination nodes of the group ensures exact individual IR(i, d, j),  $IR(i, d, -) = \sum IR(i, d, j)$ ,  $j \in Dest(i, d)$ .

Custom

Full custom traffic pattern involves largest number of parameters to set. All the Dest(i) and IR(i, j) are configured manually one by one. This process is error-prone and there is no way to find them out automatically. Custom traffic generator is quite similar with locality as if *group* is not featured by distance. For instance, if node *i* from  $4 \times 4$  mesh network is sending messages to all other nodes just like random uniform, but with all distinctive injection rates. Then we get size of Dest(i) equals 15, and IR(i, j),  $j \in Dest(i)$  are all independent. It seems like slicing all flows sourcing from node *i* into 15 groups, each of which comprises with unique flow and is of particular injection rate.

## 3.2 Measurement Setting

After synthetic benchmark configured and applied to NoC with simulator evoked, simulation proceeds until all simulation data is collected. Then platform starts to conduct measurement.

### 3.2.1 Warming-up Period

Generally network is initialized with empty buffers and idle resources before packets injected in. Thus, packets that are injected early in the simulation confront less contention and traverse more swiftly. However, as buffers begin to fill up, later packets confront more contention with increased latency. The influence of initialization fades over time and at some point the simulation is justified to be warmed up.

Take warming-up period into account ensures that packets to be measured are all within steady state, otherwise systematic inaccuracy is introduced in. Although real

application running on network also initializes with empty buffers, it always costs a long time before completion. In terms of synthetic traffic pattern, only statistic features are emulated with relatively short simulation interval to obtain evaluation outcome much faster. That is why warming-up period is critical for measurement.

In the domain of synthetic benchmark, standardized definition yet exists for warming-up period. All literatures choose to set warming-up period empirically and the exact setting is always unrevealed. Range of warming-up period varying from one literature to another makes designs from different authors incomparable.

Normally, warming-up period can be measured by clock cycle or packet number. The first approach is that, only packets injecting into network after certain number of system clock cycle are counted valid in measurement. Second approach is to start measurement after certain number of packets having completed transferring in network. Proposed platform supports both modes and records the setting for future comparison for reproduction.

## 3.2.2 Latency Definition

Network latency is a common metric for runtime estimation of NoC applied synthetic benchmark, but its definition is ambiguous. It can be measured per data word, header, packet, or transfer (with several packets as a block) while include or exclude the latency at FIFOs. In proposed platform, two types of latency are defined, called latency without source queue and latency with source queue, both with packet as data unit. By unifying and explicitly stated network latency, different NoCs can be compared under identical standard

| LatencyL = Timeout - Timegen        | (8) |

|-------------------------------------|-----|

| $Latencys = Time_{out} - Time_{in}$ | (9) |

Where, *Timegen* indicates the time of packet generation, *Timein* is the time packet injecting into the network and *Timeout* the time of ejecting out from network.

## 3.2.3 Throughput Definition

Network throughput is the metric to evaluate NoC bandwidth. By comparing throughput of messages injecting into and ejecting out from network, congested flows are distinguished out.

Throughput = Packet\_Numioi / Timeioi

Where *Timetot* represents the time interval for measurement, in the unit of clock cycle. *Packet\_Numtot* indicates the total number of packets received by the network (amount to all packets received by any node within the network).

(10)

## 3.2.4 Virtual Channel Utilization