# CMOS Power Amplifier and Transmitter Front-End Design in Wireless Communication

NG, Yuen Sum

A Thesis Submitted in Partial Fulfilment of the Requirements for the Degree of Master of Philosophy

in

**Electronic Engineering**

The Chinese University of Hong Kong July 2009

### Abstract

Abstract of thesis entitled:

CMOS Power Amplifier and Transmitter Front-End Design in Wireless Communication Submitted by NG, Yuen Sum

for the degree of Master of Philosophy In Electronic Engineering

at The Chinese University of Hong Kong in July 2009

In the recent years, radio-frequency (RF) front-end circuit design is a hot and challenging topic in both the industry and research. RF transceivers with different standards are integrated into a single chip. Different technologies, for example, SiGe bipolar or GaAs are chosen in some research works due to the high transition frequency, high breakdown voltage, high voltage supply and high DC current limitation. Nowadays, CMOS technology is another choice to implement RF front-end with the submicron or even the nano-scale channel length. Some of the RF front-end building blocks, such as low-noise amplifier (LNA) and mixer, can be implemented in CMOS technology due to the downscaling of the channel length. Although CMOS technology suffers from higher threshold voltage, lower breakdown voltage, and lower supply voltage compared with the non-CMOS technologies mentioned above, CMOS is relatively inexpensive and more feasible to integrate the RF circuit with the digital part. Among other building blocks of the RF front-end circuit, power amplifier (PA) consumes the most power. In order to have high power efficiency, the PA is usually implemented by offchip active and passive components. However, this approach causes the production cost increase dramatically. Therefore, the development of on-chip PA is, so far, a proper choice to reduce the production cost. In this thesis, the design consideration of PA and transmitter front-end circuit is outlined. A PA operating at 3 GHz under the supply voltage of 3.3 V is fabricated in a 0.18 µm RF CMOS technology. The PA can provide saturated power of 20 dBm with the input power of -12 dBm, according to measurement. Measured linear gain and power-added efficiency are 27.89 dB and 12%, respectively. The PA is also measured with IEEE 802.11a Wireless LAN and IEEE 802.16 WiMAX data. The measured EVM are -30.3 dB with an output power of 7.79 dBm and -26.4 dB with an output power of 8.73 dBm, respectively.

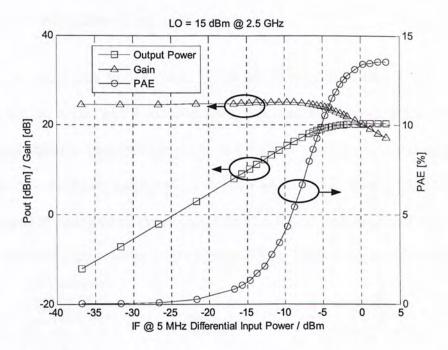

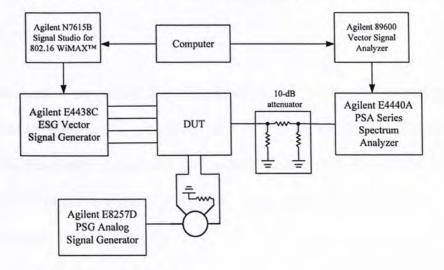

The transmitter front-end circuit for the WiMAX applications, including on-chip PA, has been fabricated by a  $0.18 \ \mu m$  RF CMOS technology with the frequency band of 2.5 GHz. The transmitter is measured under 3.3 V for the power stage, 1.27 V for the driver stage and 1.5 V for the I/Q modulator. In the measurement, the circuit can provide output saturated power of 20 dBm, with linear gain of 24 dB and power-added efficiency of 14 %. This research work is tested using with 20-MHz bandwidth, 64-QAM-5/6-CTC WiMAX baseband signal corresponding to output power of 13 dBm associated with error vector magnitude of -30.52 dB.

## 概要

近年,射頻前端綫路設計無論在工業還是科研都是一個熱門項目.不同制式的射頻收發器建立在 單晶片上.不同工藝如 SiGe 三極管及 GaAs 可以用於射頻前端綫路,因為這些工藝都具有高過渡 頻率高臨界極限,高供電與高電承受能力.近期,CMOS 工藝成為了另一個射頻前端綫路設計的 方法.一些在接收器上的模組如低燥音放大器都有應用 CMOS 工藝生成.雖然 CMOS 工藝的缺 點有高限極,低臨界極限,低電流承受能力,但 CMOS 工藝的價格較低與較容易同數碼世界結合. 而在眾多射頻前端的模塊中,功率放大器是最消耗電能的.所以功率放大器多是用外置電子零件 來設計.但是製造成本就會因此上升.所以,把功率放大器設計在 CMOS 工藝上是另一個可以節 省成本的方法之一.

在這篇論文中,會談及有關功率放大器以及發訊器的前端綫路設計.首先,一個以 3.3 V 作為工作 電壓及 3 GHz 為工作頻律的功率放大器已經用 0.18 微米制程設計並且製造. 在測試中可以得知 這個功率放大器可以發出 20 dBm 電能.而它的綫性發大率為 27.89 dB 以及附加功率效率為 12 %.同時也有用 IEEE 802.11a 無綫網路制式以及 IEEE WiMAX 制式測驗. 結果顯示在這兩個制式 中,這個功率放大器可以分別在發出 7.79 dBm 時 EVM 值是-30.3 dB 以及 8.73 dBm 電能時 EVM 值是-26.4 dB.

此外,一個發訊器前端,包括一個功率放大器,也用了 0.18 微米制程設計並且製造.這個發訊器前端是用於 2.5 GHz 頻帶 WiMAX 的應用上.功率放大器的工作電壓為 3.3 V,前級放大器的工作電 壓為 1.27 V,而 I/Q 混頻器的工作電壓為 1.5 V. 在測試中,這個發訊器前端可以提供 20 dBm 電能. 綫性放大率為 24 dB 以及以及附加功率效率為 14 %. 這個電路也有用 WiMAX 制式的基頻訊號 測試,結果以 20 MHz 64-QAM-5/6-CTC WiMAX 的基頻訊號中,可提供 13 dBm 電能而 EVM 値 是-30.52 dB

## Acknowledgements

I want to specially thank to my supervisor, Professor Leung Ka Nang Alex, who provides me full support of my work. I am grateful for the help from Dr. Siu-Kei Tang who gave me a lot of guidelines on PCB layout techniques for the RF front-end circuit testing. In addition to the testing boards, I want to specially thank again Dr. Tang and Dr. Lincoln Lai Kan Leung who gave me a lot of technical advices on the circuit-level design and measurement skills. Furthermore, I want to specially thank Mr. Yeung Wing Yee who gave me a lot of technical supports on the all the simulation and layout CAD tools. Finally, I want to thank my colleagues in ASIC and Microwave Laboratories for their supports.

## Table of Contents

| 1. | INTI  | RODUCTION                                                                          |    |

|----|-------|------------------------------------------------------------------------------------|----|

|    | 1.1   | MOTIVATION                                                                         |    |

|    | 1.2   | SPECIFICATIONS                                                                     |    |

|    | 1.3   | ORGANIZATION OF THE THESIS                                                         |    |

|    | 1.4   | References                                                                         |    |

| 2. | RAS   | IC THEORY OF POWER AMPLIFIER AND TRANSMITTER FRONT-END                             |    |

|    | 2.1   | CLASSIFICATION OF POWER AMPLIFIER                                                  |    |

|    | 2.1.1 |                                                                                    |    |

|    | 2.1.1 |                                                                                    |    |

|    |       |                                                                                    |    |

|    | 2.1.3 |                                                                                    |    |

|    | 2.1.4 |                                                                                    |    |

|    | 2.1.5 |                                                                                    |    |

|    | 2.1.6 |                                                                                    |    |

|    | 2.1.7 |                                                                                    |    |

|    | 2.2   | FIGURE-OF-MERIT OF POWER AMPLIFIER                                                 |    |

|    | 2.2.1 |                                                                                    |    |

|    |       |                                                                                    |    |

|    |       |                                                                                    | 32 |

|    | 2.2.2 |                                                                                    |    |

|    |       | 2.2.1     1-dB compression point       2.2.2     Third-order intermodulation point | 33 |

|    |       | 2.2.3 Power Gain                                                                   |    |

|    |       | 2.2.4 Drain Efficiency and Power Added Efficiency                                  |    |

|    |       | 2.2.5 AM-AM and AM-PM conversion                                                   |    |

|    | 2.2.3 | Modulation Analysis                                                                |    |

|    |       | 2.3.1 Constellation Diagram and Error Vector Magnitude                             |    |

|    | 2.3   | REFERENCE                                                                          |    |

| 3. | CIR   | CUIT DESIGN OF POWER AMPLIFIER                                                     |    |

|    |       |                                                                                    |    |

|    | 3.1   | INTRODUCTION                                                                       |    |

|    | 3.2   | TOPOLOGY OF THE POWER AMPLIFIER DESIGN                                             |    |

|    | 3.3   | DESIGN IN POWER AMPLIFIER                                                          |    |

|    | 3.2.  | Power Stage                                                                        |    |

|    | 3.2.  | 2 Driver Stage and Input matching                                                  |    |

|    | 3.4   | SIMULATION RESULT ON POWER AMPLIFIER                                               |    |

|    | 3.5   | LAYOUT CONSIDERATION                                                               |    |

|    | 3.6   | MEASUREMENT RESULT ON POWER AMPLIFIER                                              |    |

|    | 3.4.  | I Small signal measurement                                                         |    |

|    | 3.4.  | 2 Large signal measurement                                                         |    |

|    | 3.4.  |                                                                                    |    |

|    | 3.7   | PERFORMANCE SUMMARY                                                                |    |

|    | 3.8   | REFERENCE                                                                          |    |

| 4. | CIF   | CUIT DESIGN OF TRANSMITTER FRONT-END                                               | 60 |

|    | 4.1   | INTRODUCTION                                                                       |    |

|    | 4.2   | TOPOLOGY OF THE TRANSMITTER FRONT-END DESIGN                                       | 61 |

|    | 4.3   | DESIGN IN TRANSMITTER FRONT-END CIRCUIT                                            |    |

|    | 4.2.  |                                                                                    |    |

|    | 4.2.  |                                                                                    | 66 |

|    | 4.2.  |                                                                                    |    |

|    | 4.4   | SIMULATION RESULT OF THE TRANSMITTER FRONT-END DESIGN                              | 74 |

|    |       | LAYOUT CONSIDERATION                                                               |    |

|    | 4.5   | MEASUREMENT RESULT OF THE TRANSMITTER FRONT-END DESIGN                             |    |

|    | 4.6   |                                                                                    |    |

|    | 4.4.  |                                                                                    |    |

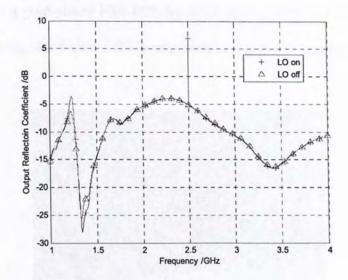

|    |       | I.4.1.1 Output Reflection coefficient                                              |    |

|    | 4.4.1.2    | Large Signal Measurement                            |    |

|----|------------|-----------------------------------------------------|----|

|    | 4.4.1.3    | Modulation Measurement                              |    |

|    | 4.4.2. LC  | Balun Measurement                                   |    |

|    | 4.7 PERFOR | RMANCE SUMMARY OF THE TRANSMITTER FRONT-END CIRCUIT |    |

|    | 4.8 REFERI | ENCE                                                |    |

|    |            | ON                                                  |    |

| 5. | FUTURE W   | /ORK                                                | 91 |

## List of Figures

| Fig. 1.2-1 Spectrum mask for different Channel bandwidth                                   | 15  |

|--------------------------------------------------------------------------------------------|-----|

| Fig. 2.1-1 Current waveform                                                                | 19  |

| Fig. 2.1-2 Different harmonic current amplitude with different value of the conduction any | gle |

|                                                                                            |     |

| Fig. 2.1-3 RF power versus conduction angle                                                | 20  |

| Fig. 2.1-4 Efficiency versus conduction angle                                              | 20  |

| Fig. 2.1-5 Class A amplifier operation                                                     |     |

| Fig. 2.1-6 Class B amplifier operation                                                     | 22  |

| Fig. 2.1-7 Class B amplifier operation using transformer                                   |     |

| Fig. 2.1-8 Class AB amplifier operation                                                    |     |

| Fig. 2.1-9 Class C amplifier operation                                                     |     |

| Fig. 2.1-10 Voltage and current waveforms in class-D operation                             |     |

| Fig. 2.1-11 Class D amplifier operation                                                    |     |

| Fig. 2.1-12 Another class D amplifier                                                      |     |

| Fig. 2.1-13 Waveform of class-E operation. (top) switching voltage (center) drain voltage  |     |

| transistor. (bottom) drain current of transistor                                           |     |

| Fig. 2.1-14 Class E amplifier operation                                                    |     |

| Fig. 2.1-15 Drain modulation                                                               |     |

| Fig. 2.1-16 Class F amplifier                                                              | 28  |

| Fig. 2.2-1 Simple microwave amplifier diagram                                              | 31  |

| Fig. 2.2-2 Graphical illustration of 1-dB compression point and IIP3                       |     |

| Fig. 2.2-3 64-QAM Constellation diagram                                                    |     |

| Fig. 2.2-4 Error vector magnitude                                                          |     |

| Fig. 3.2-1 Block diagram of power amplifier                                                |     |

| Fig. 3.3-1 OP1dB vs R <sub>OPT</sub>                                                       |     |

| Fig. 3.3-2 Output matching network with series inductor and shunt capacitor                |     |

| Fig. 3.3-3 Output matching network with series capacitor and shunt inductor                |     |

| Fig. 3.3-4 Power Stage                                                                     |     |

| Fig. 3.3-5 Parasitic common mode oscillation                                               |     |

| Fig. 3.3-6 Driver stage                                                                    |     |

| Fig. 3.3-7 Series resonator at input port                                                  |     |

| Fig. 3.4-1 Simulation schematic                                                            |     |

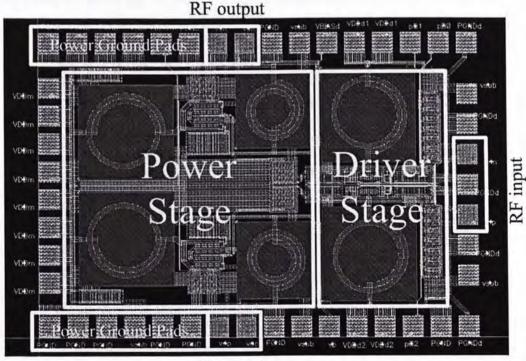

| Fig. 3.5-1 Floorplan of the PA                                                             |     |

| Fig. 3.6-1 Chip Photo                                                                      |     |

| Fig. 3.6-2 Testing board configuration                                                     |     |

| Fig. 3.6-3 Small signal measurement configuration                                          |     |

| Fig. 3.6-4 Port arrangement in the 4-port s-parameter measurement                          |     |

| Fig. 3.6-5 Common mode return loss at input                                                |     |

| Fig. 3.6-6 Common mode return loss at output                                               |     |

| Fig. 3.6-7 Common mode gain                                                                |     |

| Fig. 3.6-8 Common mode isolation                                                           | 54  |

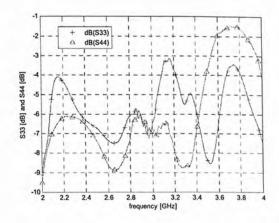

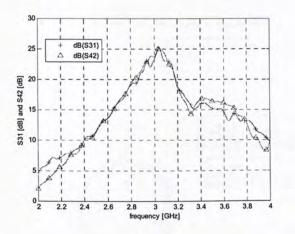

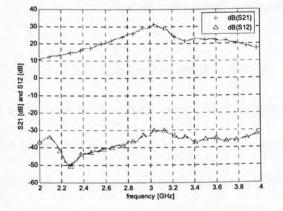

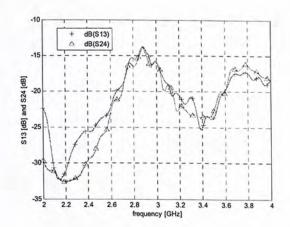

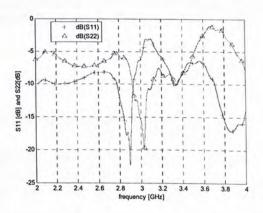

| Fig. 3.6-9 Differential mode gain and isolation                                            | 54  |

| Fig. 3.6-10 Differential mode return loss at input and output                              | 54  |

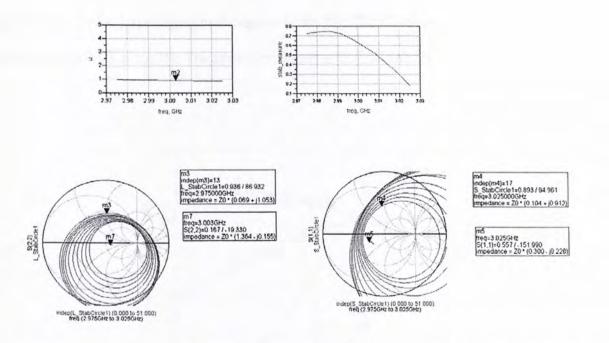

| Fig. | 3.6-11 Stability analysis (top left: K-factor, top right: $\Delta$ , bottom left: output reflection |    |

|------|-----------------------------------------------------------------------------------------------------|----|

|      | coefficient and load stability circuit, bottom right: input reflection coefficient and source       |    |

| P    | stability circuit                                                                                   |    |

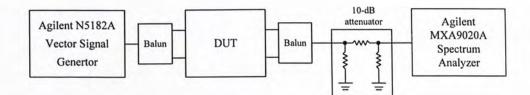

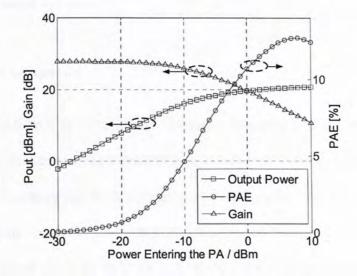

|      | 3.6-12 Large signal measurement configuration                                                       |    |

|      | 3.6-13 Large signal performance                                                                     |    |

|      | 3.6-14 Modulation Test configuration                                                                |    |

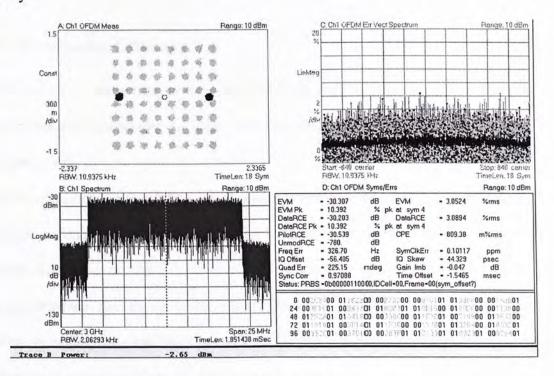

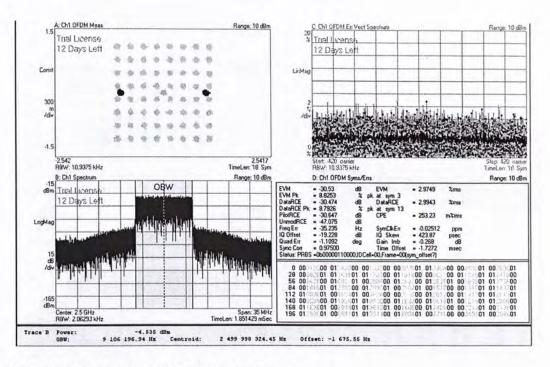

|      | 3.6-15 Constellation Diagram and Output Spectrum of the WiMAX output RF signal . 5                  | )/ |

| F1g. | 3.6-16 Constellation Diagram and Output Spectrum of the IEEE 802.11a output RF                      |    |

|      | signal                                                                                              |    |

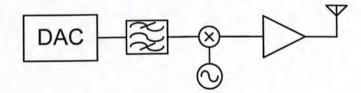

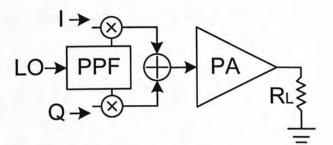

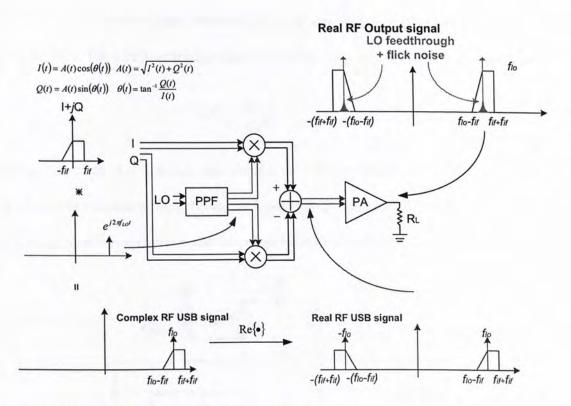

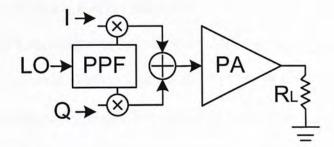

|      | 4.2-1 Simple direct conversion transmitter                                                          |    |

|      | 4.2-2 Proposed on-chip direct conversion transmitter                                                |    |

| -    | . 4.2-3 The signal flow graph of the transmitter front-end circuit                                  |    |

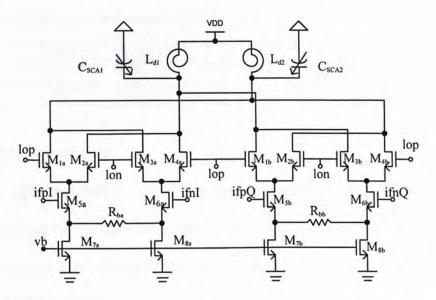

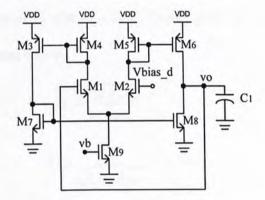

| -    | . 4.3-1 I/Q Modulator                                                                               |    |

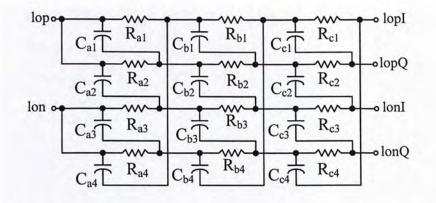

| -    | . 4.3-2 3-stage polyphase filter                                                                    |    |

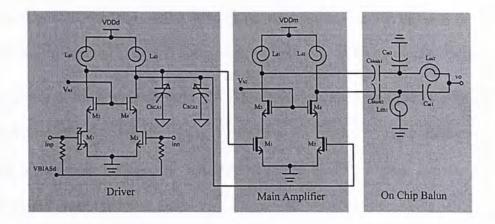

|      | . 4.3-3 Overall schematic of PA                                                                     | 57 |

| Fig  | . 4.3-4 Parametric simulation of 1-dB compression point versus differential output                  |    |

|      | resistance                                                                                          |    |

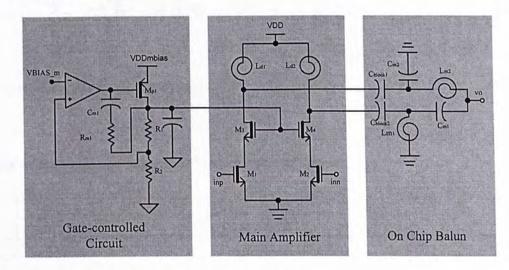

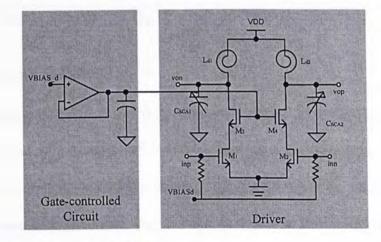

|      | . 4.3-5 Power Stage with on-chip balun and gate-controlled circuit                                  |    |

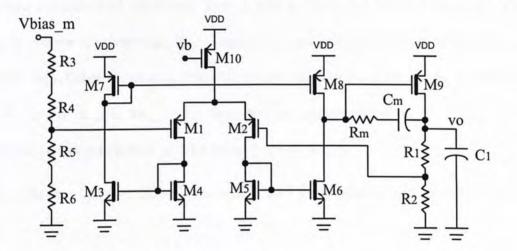

| Fig  | . 4.3-6 Full schematic of gate-controlled circuit in power stage                                    | 7( |

| Fig  | . 4.3-7 Driver Stage and the Gate-controlled Circuit                                                | 7  |

| Fig  | . 4.3-8 Full schematic of gate-controlled circuit in driver stage                                   | 72 |

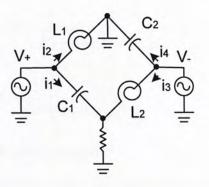

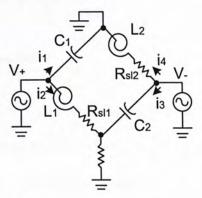

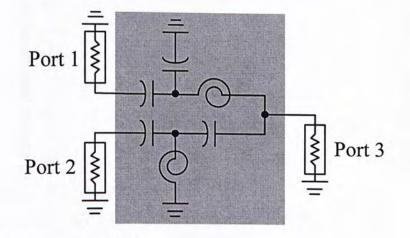

| Fig  | . 4.3-9 LC balun                                                                                    | 7  |

| Fig  | . 4.3-10 LC balun model including loss in inductor                                                  | 7  |

| Fig  | . 4.4-1 Simulation schematic of the transmitter                                                     | 7  |

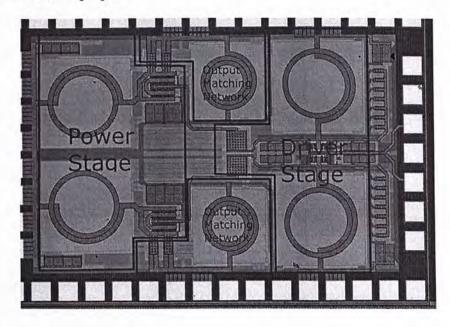

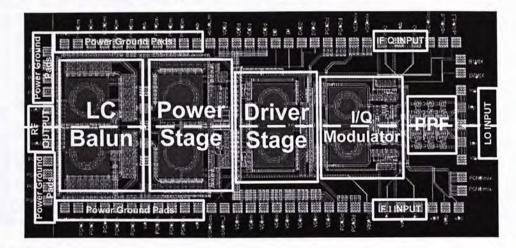

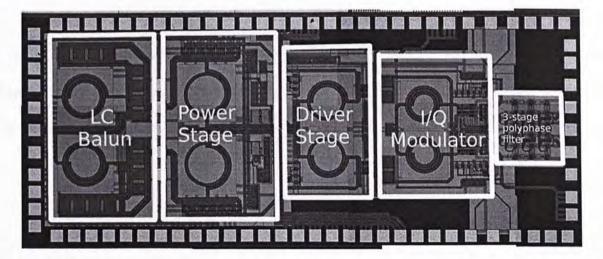

| Fig  | . 4.5-1 Floorplan of the transmitter front-end circuit                                              | 7  |

|      | . 4.6-1 Chip Photo                                                                                  |    |

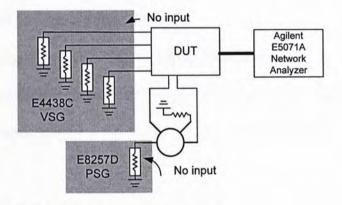

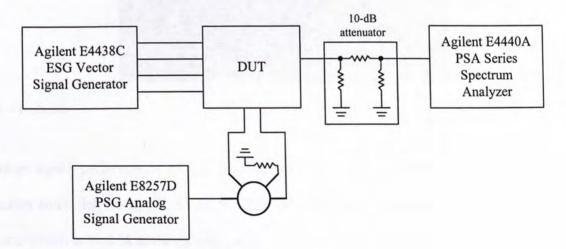

|      | . 4.6-2 Measurement setup for the tone measurement                                                  |    |

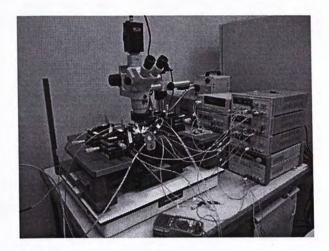

|      | . 4.6-3 Measurement setup in the test bench                                                         |    |

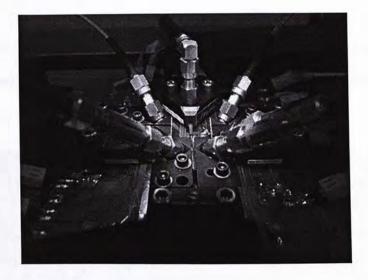

|      | . 4.6-4 Probe station                                                                               |    |

|      | . 4.6-5 Large Signal Performance                                                                    |    |

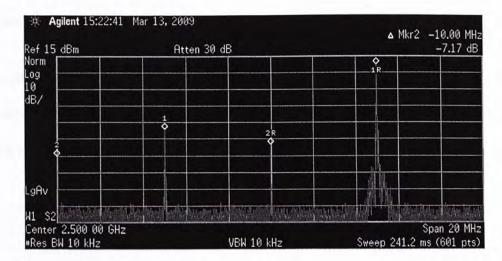

| Fig  | 4.6-6 LO feedthrough and carrier suppression                                                        | 8  |

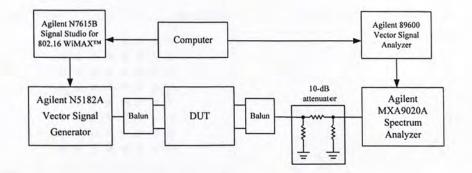

|      | 4.6-7 Measurement setup for the modulation test                                                     |    |

|      | . 4.6-8 EVM vs. IF differential input power                                                         |    |

| Fie  | 4.6-9 WiMAX modulation test with 10-MHz baseband signal                                             | 8  |

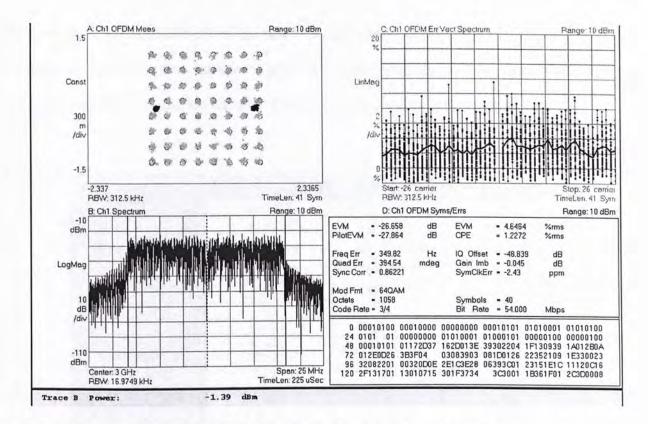

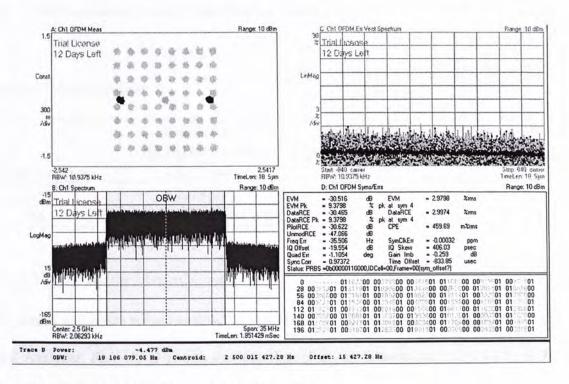

|      | g. 4.6-10 WiMAX modulation test with 20-MHz baseband signal                                         |    |

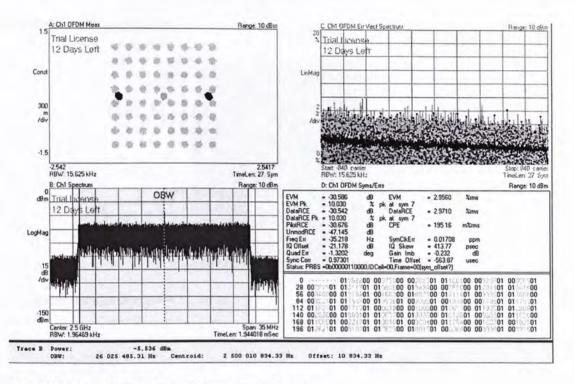

|      | g. 4.6-11 WiMAX modulation test with 28-MHz baseband signal                                         |    |

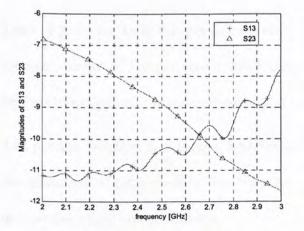

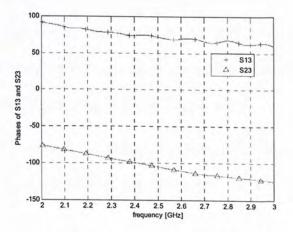

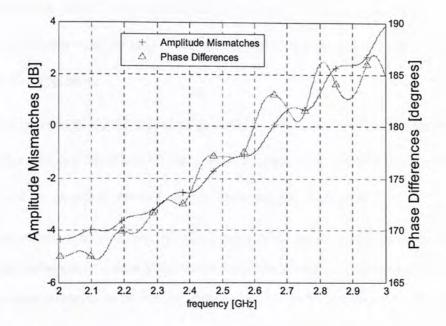

|      | g. 4.6-12 S-parameter measurement in LC balun                                                       |    |

|      | g. 4.6-13 Magnitude response of the LC balun                                                        |    |

|      | 2. 4.6-14 Phase response of the LC balun                                                            |    |

| 1.15 | g. 4.6-15 Amplitude and phase mismatch of the LC balun                                              | 0  |

## List of Tables

| Table 1-1 Frequency bands for WiMAX standards [1]                                   | 13 |

|-------------------------------------------------------------------------------------|----|

| Table 1-2 Bandwidth requirement of WiMAX standard [3]                               | 14 |

| Table 1-3 Uplink modulation requirement.                                            | 14 |

| Table 1-4 Power control requirement for WiMAX standard [2]                          | 15 |

| Table 3-1 Pre-layout and post-layout simulation result at 3 GHz                     | 49 |

| Table 3-2 Comparison between the pre-layout, post-layout simulation and measurement |    |

| result                                                                              | 59 |

| Table 4-1 Comparison between the pre-layout and post-layout simulation result       | 75 |

| Table 4-2 Simulation and Measurement Result                                         |    |

| Table 4-3 Transmitter performance summary                                           | 88 |

| Table 4-4 Comparison Table                                                          |    |

### 1. Introduction

#### 1.1 Motivation

Radio-frequency integrated circuit (RFIC) design becomes a hot topic on both the research and industry recently, because of the maturity of the sub-micron and nano-scale semiconductor technologies. Based on those technologies, there are many commercial products which were designed based on different standards to cater the consumer market. Some examples are GSM, Bluetooth, Wireless LAN and WiMAX, etc.

Regarding to the recent trend, some RF-front end circuits, either the receiver or the transmitter, are implemented by GaAs (Gallium arsenide), BiCMOS or silicon bipolar technologies. On the transmitter side, the front-end circuit including the power amplifiers and mixers are implemented by the aforementioned non-CMOS components due to high supply voltage and high breakdown voltage in order to deliver high output power. However, there are over 80 % semiconductor products manufactured by CMOS technology due to that fact that most of them are digital circuits. It is well-known that CMOS technology has many advantages such as low threshold voltage to enable low operational supply voltage. The low supply voltage can reduce the power consumption in the digital circuit. But it is not beneficial to the both the analog and RF IC design, as the voltage swing and output power delivery are limited and cascode structures may not be a good design technique. As a result, with GaAs, BiCMOS and SiGe bipolar technologies are better choice in implement analog and RF circuit as they have high supply voltage and current density limitation. However, these non-CMOS technologies are relatively much more expensive compared with the CMOS counterpart.

Therefore, most of the RF building blocks which can be analyzed in small signal domain, such as low noise amplifier (LNA), mixer, intermediate frequency (IF) filters and data conversion blocks, are designed using CMOS technology. Power Amplifier (PA), however, is required to deliver high output

power. It is not significantly benefited by the advanced sub-micron CMOS technology with the shortcomings mention above. As a result, special techniques are required to overcome these problems. In addition to the supply voltage and current density limitation, CMOS technologies also suffer from poor quality factor of the monolithic passive components. The on-chip inductors generally have low the quality factor of about 8-10. The on-chip parasitic capacitance and resistance degrade their performance.

In the PA design, the output power, the efficiency and the linearity are the most important parameters. Switching PA could have good efficiency but poor linearity. Therefore, the communication standard with only phase and frequency modulation should use switching PA, e.g. GSM and Bluetooth. Nowadays, some new communication standards incorporate the orthogonal frequency division multiplexing (OFDM) is used for higher data rate transmission and multiple access, but the linearity requirement is high. IEEE 802.11 a/g wireless LAN, IEEE 802.16e Mobile WiMAX and Ultra-Wideband (UWB) are examples of using the OFDM scheme. All of them require the PA having good linearity, but the efficiency of a PA with good linearity is generally low.

This thesis would focus on the design in PA to provide high output power from a low supply voltage and high knee voltage in CMOS technology. In additional to the PA, the design of a transmitter frontend circuit with on-chip integrated PA is also discussed.

#### 1.2 Specifications

Both the PA and transmitter front-end circuit are designed for the IEEE 802.16e Mobile WiMAX applications. It is based on OFDM in order to have high data rate transmission. OFDM system can also prevent inter-block interference (ISI). Mobile WiMAX incorporates orthogonal frequency division multiple access (OFDMA) which enable Multiple-Input-Multiple-Output (MIMO). In order to deliver optimum performance in channel bandwidth, the parameter in the physical layer is scalable. The

channel bandwidth is ranged from 1.25 MHz to 20 MHz [2]. The frequency bands [3] and the bandwidth requirement are shown in Table 1-1 and Table 1-2, respectively. WiMAX devices operates at 2.3-2.4 GHz, 2.305-2.320 GHz, 2.345-2.36 GHz, 2.496-2.69 GHz, 3.3-3.4 GHz, 3.4-3.8 GHz, 3.4-3.6 GHz and 3.6-3.8 GHz.

| Band<br>Class<br>Index | Frequency<br>Range (GHz) | Channel<br>Frequency<br>Step (kHz) | Channel<br>Bandwidth<br>(MHz) | FFT sizes | Duplexing Mode |

|------------------------|--------------------------|------------------------------------|-------------------------------|-----------|----------------|

| 1                      | 2.3-2.4                  | 250                                | 5                             | 512       | TDD            |

| 1                      |                          |                                    | 10                            | 1024      | TDD            |

| 2                      | 2.305-2.320              | 250                                | 3.5                           | 512       | TDD            |

|                        | 2.345-2.360              |                                    | 5                             | 512       | TDD            |

|                        |                          |                                    | 10                            | 1024      | TDD            |

| 3                      | 2.496-2.69               | 250                                | 5                             | 512       | TDD            |

| 1.10.00                |                          |                                    | 10                            | 1024      | TDD            |

| 4                      | 3.3-3.4                  | 250                                | 5                             | 512       | TDD            |

|                        |                          |                                    | 7                             | 1024      | TDD            |

|                        |                          |                                    | 10                            | 1024      | TDD            |

| 5                      | 3.4-3.8                  | 250                                | 5                             | 512       | TDD            |

|                        |                          |                                    | 7                             | 1024      | TDD            |

| 1                      |                          |                                    | 10                            | 1024      | TDD            |

|                        | 3.4-3.6                  | 250                                | 5                             | 512       | TDD            |

| 1000                   |                          |                                    | 7                             | 1024      | TDD            |

|                        |                          |                                    | 10                            | 1024      | TDD            |

|                        | 3.6-3.8                  | 3.6-3.8 250                        | 5                             | 512       | TDD            |

|                        |                          |                                    | 7                             | 1024      | TDD            |

|                        |                          |                                    | 10                            | 1024      | TDD            |

Table 1-1 Frequency bands for WiMAX standards [1]

As there are several frequency bands available in the standard, the design target is for specific frequency band that are needed to set first. The frequency band for Band Class Index 3 is chosen as the design target. It is because there are many publications [4] - [7] about the WiMAX applications for comparison.

| Parameters                         | Values |       |      |      |     |      |          |

|------------------------------------|--------|-------|------|------|-----|------|----------|

| System bandwidth (MHz)             | 1.25   | 5     | 10   | 20   | 3.5 | 7    | 8.75     |

| Sampling factor                    | 28/25  |       |      |      | 8/7 |      |          |

| Sampling frequency (Fs MHz)        | 1.4    | 5.6   | 11.2 | 22.4 | 4   | 8    | 10       |

| Sample time (1/Fs nsec)            | 714.3  | 178.6 | 89.3 | 44.6 | 250 | 125  | 100      |

| FFT sizes                          | 128    | 512   | 1024 | 2048 | 512 | 1024 | 1024     |

| Subcarrier frequency spacing (kHz) |        | 10.9  | 375  |      | 7.8 | 125  | 9.765625 |

| Useful symbol time                 |        | 91    | .4   | _    | 1   | 28   | 102.4    |

| Guard time                         |        | 11    | .4   |      | 1   | 16   | 12.8     |

| OFDMA symbol time                  |        | 10    | 2.8  |      | 1   | 44   | 115.2    |

Table 1-2 Bandwidth requirement of WiMAX standard [3]

As WiMAX is an OFDM system, its linearity requirement is high. Switching PA is not a candidate for this application. PA is designed in the linear operation mode. The detailed analysis will be described in Chapter 2. The Error Vector Magnitude (EVM) is the major parameter in order to analyze the linearity of the OFDM system. The detailed definition will be shown in Chapter 2 also. The EVM requirement for the WiMAX system varies based on different modulations and coding schemes. Table 1-3 shows the EVM requirement needed. For the 64-QAM modulation with 5/6 coding, the EVM of the transmitter must be below 30 dB.

Table 1-3 Uplink modulation requirement

| Modulation | EVM value required /<br>dB |  |  |

|------------|----------------------------|--|--|

| QPSK 1/2   | <= -15                     |  |  |

| QPSK 3/4   | <= -18                     |  |  |

| 16-QAM 1/2 | <=- 20.5                   |  |  |

| 16-QAM 3/4 | <=-24                      |  |  |

| 64-QAM 1/2 | <=-26                      |  |  |

| 64-QAM 2/3 | <=-28                      |  |  |

| 64-QAM 3/4 | <=-30                      |  |  |

| 64-QAM 5/6 | <=-30                      |  |  |

The Power Class requirement is shown in Table 1-4. There are 4 power classes in the WiMAX standards. For the low output power class, such as power class 1, it may be implemented by the CMOS

technology. For the higher output power, CMOS technology may not be a good candidate as power combining technique are required and it is quite hard to design. So, an offchip PA may be used.

| Class Identifier | Transmit Power (dBm) for 16-QAM | Transmit Power (dBm) for QPSK |

|------------------|---------------------------------|-------------------------------|

| Power Class 1    | 18 <= PTx,max < 21              | 20 <= PTx,max < 23            |

| Power Class 2    | 21 <= PTx,max < 25              | 23 <= PTx,max < 27            |

| Power Class 3    | 25 <= PTx,max < 30              | 27 <= PTx,max < 30            |

| Power Class 4    | 30 <= PTx,max                   | 30 <= PTx,max                 |

Table 1-4 Power control requirement for WiMAX standard [2]

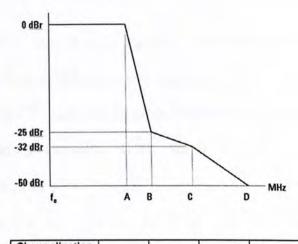

In addition to the power and EVM requirement, the OFDM output spectrum should meet the spectrum mask requirement as shown in Fig. 1.2-1. The spectrum mask requirement depends on the channel bandwidth [9].

| (MHz) | A    | в    | c    | D     |

|-------|------|------|------|-------|

| 20    | 9.5  | 10.9 | 19.5 | 29.5  |

| 10    | 4.75 | 5.45 | 9.75 | 14.75 |

Fig. 1.2-1 Spectrum mask for different Channel bandwidth

As a result, this work will focus on the frequency band of 2.496-2.69 GHz. The center frequency is set to be 2.5 GHz. This work is implemented by a 0.18-µm RF CMOS technology. For the down-scaling technology, the supply voltage is quite low and there is only 3.3 V in the thick-oxide option in the technology. Loadpull design technique can be applied to extract more output power from the low supply voltage. The design technique and effect would be discussed in Chapter 3 and Chapter 4.

#### 1.3 Organization of the Thesis

This thesis will be presented in six chapters. In Chapter 2, the basic theory and the figure-of-merit of a PA would be discussed. In Chapter 3, a prototype PA is designed. Its center frequency is set to be 3-GHz. The loadpull technique would be addressed. All the design and the measurement result will be outlined. In Chapter 4, the design of a 2.5-GHz transmitter front-end circuit for WiMAX applications is presented. All the circuit-level design and measurement result would be given. Finally, the conclusion and the future work will be shown in Chapter 5 and Chapter 6, respectively.

#### 1.4 References

- S.C. CRIPPS, *RF Power Amplifier for Wireless Communications*, 1<sup>st</sup> ed. 685 Canton Street, Norwood, MA 02062, Boston, U.S., Artech House, Inc.

- [2] WiMAX forum, WiMAX<sup>TM</sup> System Evaluation Methodology, (ersion 2.1: 2008-07-07)

- [3] WiMAX forum, WiMAX Forum® Mobile System Profile, Release 1.5 Common Part, (Revision 0.2.1: 2009-02-02)

- [4] H H Kuo et al., "A 0.13 μm CMOS transmitter with 72-dB RF gain control for mobile WiMAX/WiBro applications," in Proc. 2008 RFIC Symp., Jun. 2008, pp. 105-108.

- [5] M. Locher *et al.*, "A Versatile, Low Power, High Performance BiCMOS MIMO/Diversity Direct Conversion Transceiver IC for WiBro/WiMAX (802.16e)," *IEEE J. Solid-State Circuits*, vol. 43, no. 8, pp. 1731-1739, Aug. 2008.

- [6] D. Yamazaki et al., "2.5-GHz fully-integrated WiMAX transceiver IC for a compact, low-powerconsumption RF module," in Proc. 2008 RFIC Symp., Jun. 2008, pp. 109-112.

- [7] F. Beaudoin et al., "A fully integrated tri-band, MIMO transceiver RFIC for 802.16e," in Proc. 2008 RFIC Symp., Jun. 2008, pp. 113-116.

- [8] Agilent, "WiMAX Concepts and RF Measurements.pdf".

17

# 2. Basic Theory of Power Amplifier and Transmitter Front-End

Unlike LNA which is a small-signal amplifier, PA operates in the large signal domain. PA cannot be designed using the small signal analysis method only. Traditionally, PA can be modeled by Volterra series, which models the weak non-linear effect of the transistor. However, it must be based on an accurate model. Parametric simulation is more suitable to design the PA. Another approach to design PA is based on that the PA is terminated with optimum output impedance location at the Smith chart where the PA can deliver highest amount of power. However, the transistor is needed to be fabricated, de-assembled and tested using large signal loadpull testing, which is very expensive. Therefore, most of the people may match the output of the transistor to a resistance value lower than 50  $\Omega$ . In this work, this approach is adopted.

As stated in Chapter 1, the design of PA depends on different modulation schemes. For the digital communication which adopts OFDM or involves amplitude modulation, PA should be designed in the linear mode. These PAs are classified by Class A, Class B, Class AB, Class C and Class F differentiated by the conduction angle. For the digital modulation which does not have amplitude modulation, for example GMSK in GSM, PA should be designed in switching mode (i.e. Class D and Class E), where amplitude modulation is not used and the linearity is not concern. The classification of the PA will be shown in the sub-section.

#### 2.1 Classification of Power Amplifier

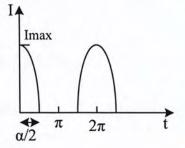

For a linear PA, the PA is classified based on the conduction angle. Due to the operation, the current waveform of the PA is shown below, where  $\alpha$  is the conduction angle,  $I_{max}$  is the peak current. The average DC, the 1st harmonic and the nth harmonic current are [1]:

$$I_{dc} = \frac{I_{\max}}{2\pi} \frac{2\sin(\alpha/2) - \alpha\cos(\alpha/2)}{1 - \cos(\alpha/2)}$$

(2.1)

$$I_1 = \frac{I_{\max}}{2\pi} \frac{\alpha - \sin \alpha}{1 - \cos(\alpha/2)}$$

(2.2)

$$I_{n} = \frac{I_{\max}}{2\pi} \frac{\alpha - \sin \alpha}{1 - \cos(\alpha/2)} \left| \frac{\sin(n+1)\frac{\alpha}{2}}{n+1} + \frac{\sin(n-1)\frac{\alpha}{2}}{n-1} - \frac{2}{n} \cos\frac{\alpha}{2} \sin\frac{n\alpha}{2} \right|$$

(2.3)

Fig. 2.1-1 Current waveform

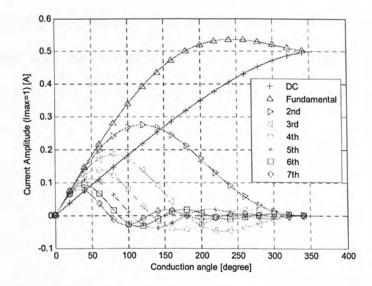

With  $I_{max}$  normalized to 1, the current waveform with different harmonics versus the conduction angle could be plotted using (2.3) [1].

Fig. 2.1-2 Different harmonic current amplitude with different value of the conduction angle

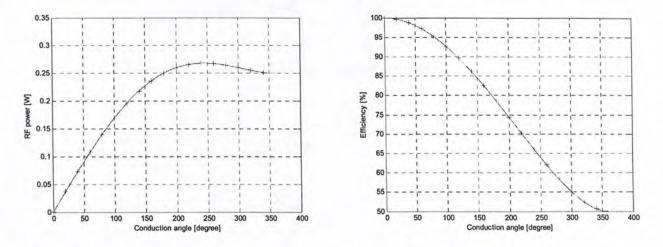

Furthermore, the RF output power and the efficiency can be calculated based on the assumption that all the amplitudes are the same. Fig. 2.1-3 and Fig. 2.1-4 show the results. The efficiency of the amplifier approaches 100% when the conduction angle decreases, but the RF output power also approaches zero.

Fig. 2.1-3 RF power versus conduction angle

Fig. 2.1-4 Efficiency versus conduction angle

#### 2.1.1Class A

In Class-A operation,  $\alpha = 2\pi$ , the transistor conducts current all the time over a cycle, as shown in Fig. 2.1-5. In Class-A mode, the transistor still operates in the small signal domain, with constant transconductance. Therefore, the amplifier has linear transconductance. From (2.8), it is known that the maximum efficiency  $\eta$  of a Class-A amplifier is 50%, in the case that the output voltage amplitude is equal to supply voltage, with the assumption that there is no knee voltage existed in the device, as shown in Fig. 2.1-4. From Fig. 2.1-2, there is no 2nd and higher harmonic generated when the conduction angle is  $2\pi$ .

Fig. 2.1-5 Class A amplifier operation

$$I_{DC} = \frac{I_{\text{max}}}{2} \tag{2.4}$$

$$I_1 = \frac{I_{\text{max}}}{2} \tag{2.5}$$

$$P_{o} = \frac{1}{2} \frac{V_{o}^{2}}{R_{*}}$$

(2.6)

$$P_{DC} = \frac{V_{DD}V_o}{R}.$$

(2.7)

$$\eta = \frac{V_o}{2V_{DD}} \tag{2.8}$$

#### 2.1.2Class B

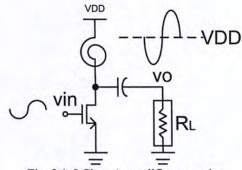

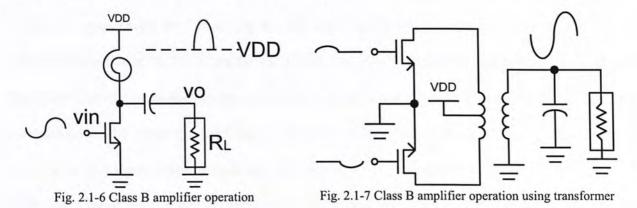

In Class-B operation, the conduction angle is  $\pi$ . The amplifier operation is shown in Fig. 2.1-6. The transistor only conducts current in half of the cycles. From (2.1) and (2.2) with  $\alpha = \pi$ , the DC, the 1st harmonic current, DC power and RF power are shown in (2.9)-(2.13). From (2.13), the efficiency is about 78% if the amplitude of the output waveform is equal to  $V_{DD}$  in the case that no knee voltage is present, as shown in Fig. 2.1-6. From Fig. 2.1-2, it is seen that the higher harmonics start to be generated due to the reduced conduction angle.

$$I_{DC} = \frac{I_{\text{max}}}{2} \tag{2.9}$$

$$I_1 = \frac{I_{\text{max}}}{\pi} \tag{2.10}$$

$$P_{o} = \frac{1}{2} \frac{V_{o}^{2}}{R_{L}}$$

(2.11)

$$P_{DC} = \frac{2V_{DD}V_o}{\pi R_c}$$

(2.12)

$$\eta = \frac{\pi}{4} \frac{V_o}{V_{DD}}$$

(2.13)

As the transistor conducts half of a cycle only, the overall output waveform can be generated out by combining RF current from another PA with 180° phase difference using transformer with the current from another half of cycle, as shown in Fig. 2.1-7.

### 2.1.3Class AB

The conduction angle of a Class-AB amplifier is between  $\pi$  and  $2\pi$ . Although several harmonic components are generated, it has a small magnitude, as shown in Fig. 2.1-2. The voltage waveform is also shown in Fig. 2.1-8. From Fig. 2.1-2, the magnitude of the 2nd harmonic current waveform is generated rapidly, compared with other harmonics. However, the even harmonics can be suppressed by

using differential structure. As a result, differential Class-AB is the suitable candidate of the PA design in OFDM system, as it maintains the linearity with acceptable efficiency. The efficiency of a Class-AB amplifier is between 50% (class-A) and 78.5% (class-B).

Fig. 2.1-8 Class AB amplifier operation

#### 2.1.4Class C

The conduction angle of a Class-C amplifier is between 0 and  $\pi$ . As the conduction angle is further reduced, higher-order harmonics are generated with a large magnitude, but the efficiency is improved. The voltage waveform of a Class-C amplifier is shown in Fig. 2.1-9. The RF power generated is smaller compared with the Class A, Class AB and Class B counterparts, as shown in Fig. 2.1-3. The efficiency is between 78.5% (Class B) and 100%. However, it is almost impossible to achieve 100% in the Class C operation, as the voltage waveform is nearly a pulse in a very short duration. The amplitude modulation can be applied to the Class-C amplifier by applying drain modulation. This is an approach to apply an AM signal at the drain of the transistor in the Class-C amplifier.

Both the Class-C and Class E amplifiers, which will be described in the other section, are the candidates in the system using constant envelope modulation. The major difference between them is the amplitude relationship between the input and the output waveforms. In a Class-C amplifier, the output waveform still follows the input waveform, although a lot of higher-order harmonics are generated. However, it is not the case for the Class-E amplifier, as the transistor is a switch only.

Most of the publications reported that the design of the Class-E amplifier rather than Class-C amplifier as CMOS technology is good in implementing switch.

Fig. 2.1-9 Class C amplifier operation

#### 2.1.5Class D

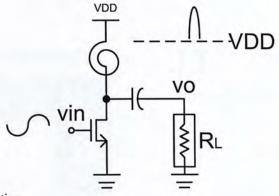

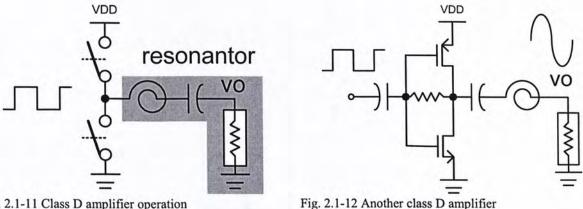

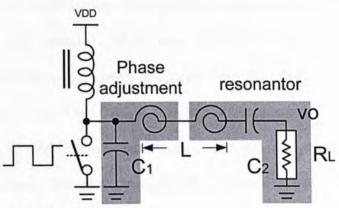

In a Class D amplifier, the transistor operates as a switch. The input signal should be large enough to drive the transistor as a switch. Fig. 2.1-11 shows the implementation of a Class-D amplifier. The complementary switch drives the resonator. The input signal is large enough to approximate it as a square wave. The resonator filters output high-order harmonics so the output waveform is sinusoidal wave.

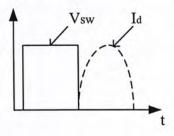

In the operation of the Class-D amplifier, the voltage at the switch node  $V_{SW}$  does not overlap with the drain current waveform. Therefore, no DC power is dissipated at the switch. As a result, the efficiency is 100% theoretically. However, the finite gate-source and source-drain capacitance of the CMOS switch make it differ from the ideal switch. Thus, power is dissipated by the parasitic capacitance [2].

Fig. 2.1-10 Voltage and current waveforms in class-D operation

Fig. 2.1-12 shows a simple Class-D amplifier implemented in the CMOS technology. The transistors are driven as a pair of complementary switches. A feedback resistor is used to obtain high gain.

Fig. 2.1-11 Class D amplifier operation

#### 2.1.6Class E

The Class-E amplifier is another type of switching mode amplifier [7]. Similar to the class-D operation, the ideal efficiency is 100%. As it operates in switching mode, the on-resistance of the transistor should be as small as possible. The large drain-source capacitance of the CMOS devices can be incorporated in the Class-E amplifier design, as shown in (2.14). To make on-resistance  $R_{ON}$  small, the gate voltage of the CMOS devices should be large and the aspect ratio  $\frac{W}{L}$  should also be large. Sometimes, the aspect ratio can be above 1000. However, the large parasitic drain-source capacitance can be incorporated into class-E amplifier design.

$$R_{ON} = \frac{1}{\mu_N C_{OX} \frac{W}{L} (V_{GS} - V_t)}$$

(2.14)

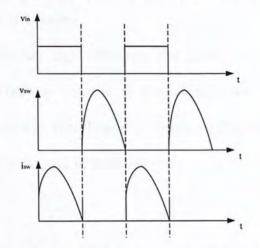

In the Class-E operation, there are two conditions needed to fulfill:

$$V_{SW} = 0$$

at  $t = t_1$  (2.15)

$$\frac{\partial V_{SW}}{\partial t}\Big|_{t=t_1} = 0 \tag{2.16}$$

In order to achieve the above conditions given by (2.15) and (2.16), the inductance and capacitance values are carefully chosen. The simplified resultant voltage and current waveform is shown below:

Fig. 2.1-13 Waveform of class-E operation. (top) switching voltage (center) drain voltage at transistor. (bottom) drain current of transistor

The design equation of the Class-E operation is developed under the condition that there is no loss in the inductors and capacitors. The simplified Class-E amplifier circuit is shown in Fig. 2.1-14. The design equation is shown as follows [7]:

$$R = \frac{2}{\frac{\pi^2}{4} + 1} \frac{VDD^2}{P}$$

(2.17)

$$L = \frac{Q_L R}{\omega} \tag{2.18}$$

$$C1 = \frac{8}{\pi(\pi^2 + 4)} \frac{1}{2\omega R}$$

(2.19)

$$C2 = \frac{1}{\omega^2 L} \left( 1 + \frac{1.42}{Q_L - 2.08} \right)$$

(2.20)

where R is the loading resistance

P is the output power

$Q_L$  is the quality factor of the output filter

The peak voltage  $V_{SW}$  is approximately equal to 3.56 times of  $V_{DD}$ . Another approach to analyze the Class-E operation is using state-space equation [2]. All the parasitic resistance of the loading inductor and output inductor are taken into account.

Although the Class-E amplifier has high efficiency, the linearity is poor. It cannot be used in the amplitude modulation applications as there is no relationship between the amplitudes of the input waveform and the output waveform. Therefore, it is widely used in GSM and Bluetooth system since the constant envelope modulation is used in those systems.

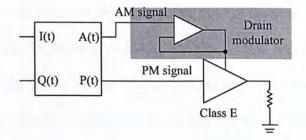

Fig. 2.1-14 Class E amplifier operation

The linearity problem of the Class-E amplifier can be improved by using the drain modulation technique. The RF signal can be decomposed into the amplitude and phase signals. The phase signal is applied to the Class-E amplifier, as it is only interested in the frequency. The amplitude signal is applied to the drain of the Class-E amplifier. The supply voltage of the Class-E amplifier changes according to the amplitude of the AM signal. However, it may have the misalignment problem between AM and PM signals. It is hard to implement the drain modulator, as it needs to supply high DC current with sufficient wide bandwidth [2].

Fig. 2.1-15 Drain modulation

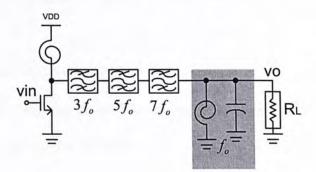

#### 2.1.7Class F

In the Class-F operation, the transistor can work as both the voltage controlled current source or switch. However, the amplifier uses resonator with different harmonics to the fundamental. The transistor is biased to the Class-B operation to have better efficiency. Only the odd-harmonics can pass through the harmonics filters. The efficiency of the Class-F operation can approach to 100% if the infinite numbers of odd harmonics filters are added. It is because there is no overlapping between the waveforms of the drain voltage and drain current. One of the examples of the Class-F amplifier is shown in Fig. 2.1-16.

Fig. 2.1-16 Class F amplifier

#### 2.2 Figure-of-Merit of Power Amplifier

The functionality and performance of a PA should be verified by three analyses. They are small signal analysis, large signal analysis and modulation analysis. Although PA is a large signal circuit, its small signal response is still needed to find out in order to ensure the PA function properly in both the small signal and large signal domains. Finally, PA is the one of the major components in the RF transmitter,

which operates in different standards. In the recent years, most of the new standards, for example, IEEE 802.11a/b/g/n and IEEE 802.16 Mobile WiMAX, use the OFDM modulation scheme. Its linearity requirement is high. In order to ensure the PA can operate in these standards, modulation tests with differential modulated RF signals, for the PA test, or modulated baseband signal, for the transmitter test, are required.

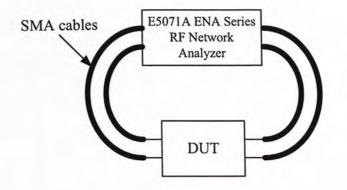

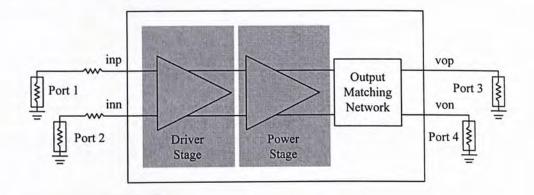

- 2.2.1 Small Signal Analysis

- 2.2.1.1 S-parameter

The small signal response of a PA can be verified by measuring its *s*-parameter. Although the linear PA is large signal circuit, its small signal response should be investigated. In order to test its small signal response, the PA should operate in the condition of low input and output power. For a single-end PA, the *s*-parameter is 2-port. However, when the PA is a differential structure, the common mode and differential *s*-parameter are needed to be measured. These *s*-parameters can be calculated from the 4-port *s*-parameter. The small signal power gain and stability measure can be found out using *s*-parameter.

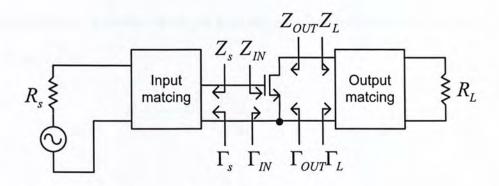

#### 2.2.1.2 Gain and Stability

The power gain of the RF amplifier depends on both the input and output matching. There are three definitions of the power gain under different input and output termination conditions [3]. They are listed below:

Transducer power gain

$$G_T = \frac{P_L}{P_{AVS}}$$

(2.21)

Power gain (operational power gain)

$$G_P = \frac{P_L}{P_{IN}} \tag{2.22}$$

Available power gain

$$G_{A} = \frac{P_{AVN}}{P_{AVS}}$$

(2.23)

where

$P_L$  is power delivered to the load

$P_{IN}$  is power input to the network

$P_{AVS}$  is power available from the source

$P_{AVN}$  is power available from the network

A simple microwave amplifier diagram is shown in Fig. 2.2-1. With the definition of return coefficient, the power gain definition can be rephrased as follows:

$$G_{T} = \frac{1 - \left|\Gamma_{S}\right|^{2}}{\left|1 - \Gamma_{IN}\Gamma_{S}\right|^{2}} \left|S_{21}\right|^{2} \frac{1 - \left|\Gamma_{L}\right|^{2}}{\left|1 - S_{22}\Gamma_{L}\right|}$$

(2.24)

$$G_{P} = \frac{1}{1 - \left|\Gamma_{IN}\right|^{2}} \left|S_{21}\right|^{2} \frac{1 - \left|\Gamma_{L}\right|^{2}}{\left|1 - S_{22}\Gamma_{L}\right|}$$

(2.25)

$$G_{\mathcal{A}} = \frac{1 - \left|\Gamma_{\mathcal{S}}\right|^2}{\left|1 - S_{11}\Gamma_{\mathcal{S}}\right|^2} \left|S_{21}\right|^2 \frac{1}{1 - \left|\Gamma_{OUT}\right|^2}$$

(2.26)

Under the condition that no transistor feedback exists (i.e.  $S_{12} = 0$ ), the transducer gain  $G_T$  can be described as unilateral power gain  $G_{TU}$  [4]. Under the condition that  $S_{12}$  cannot be neglected, using the operational power gain  $G_P$  and available power gain  $G_A$  are more convenient to carry out analysis. The power gain or the operational power gain  $G_P$  is used when either input or output of the amplifier is assumed to be perfectly matched. It can be used for the design of a PA. As in the PA, loadpull technique is used and the transistor may not be conjugate matched at the output. The available power gain  $G_A$  is used when the output is assumed to be perfectly matched to be perfectly matched to be perfectly matched to be perfectly matched to be perfectly matched. It can be used for the design of a PA. As in the PA, loadpull technique is used and the transistor may not be conjugate matched at the output. The available power gain  $G_A$  is used when the output is assumed to be perfectly matched. It can be used to represent the low

noise amplifier (LNA). As in LNA, the input may need to perform noise match to reduce input referred noise.

Fig. 2.2-1 Simple microwave amplifier diagram

In addition to the small signal power gain, the stability is another major concern. The amplifier may oscillate if there is a parasitic feedback path, and both the amplifier and feedback path fulfill the condition of oscillation. For high frequency applications, the parasitic gate-drain capacitance of the transistor is the one of the parasitic feedback path to make the amplifier unstable. Therefore, the amplifier should be terminated by appropriate impedance at both the input and output to maintain stability. In terms of the reflection coefficients, the conditions for the unconditionally stable are listed below:

$$|\Gamma_s| < 1 \tag{2.27}$$

$\left|\Gamma_{L}\right| < 1 \tag{2.28}$

$$\left|\Gamma_{IN}\right| = \left|S_{11} + \frac{S_{12}S_{21}\Gamma_L}{1 - S_{22}\Gamma_L}\right| < 1$$

(2.29)

$$\left|\Gamma_{OUT}\right| = \left|S_{11} + \frac{S_{12}S_{21}\Gamma_s}{1 - S_{11}\Gamma_s}\right| < 1$$

(2.30)

The input and output reflection coefficients in (2.26) and (2.27) are less than 1. It means the incident wave is larger than the reflected waves at both the input and output ports. From (2.29) and (2.30),  $\Gamma_{IN}$  and  $\Gamma_{OUT}$  depend on the load and source reflection coefficient simultaneously. As it is too complicated to calculate, a Rollett factor, or *K*-factor is defined to measure the stability. The definition is listed as follows:

$$K = \frac{1 - |S_{11}|^2 - |S_{22}|^2 + |\Delta|^2}{|2S_{21}S_{12}|}$$

(2.31)

and

$$\Delta = S_{11}S_{22} - S_{12}S_{21} \tag{2.32}$$

The necessary and sufficient conditions for unconditionally stable are listed below:

K > 1 (2.33)

$$\Delta < 1 \tag{2.34}$$

There is another parameter  $B_1$  to measure the stability. The unconditionally stable conditions are K>1and

$$B_{1} = 1 + |S_{11}|^{2} - |S_{22}|^{2} - |\Delta|^{2} > 0$$

(2.35)

#### 2.2.2 Large Signal Analysis

PA is a large signal device due to the large input and output voltage swing. These behaviors cannot be modeled using small signal analysis. In most cases, the output voltage swing must be represented by fundamental, the 2nd harmonic and 3rd harmonics. Higher harmonics are neglected as they are small in magnitude, according to

$$y(t) = \alpha_1 x(t) + \alpha_2 x^2(t) + \alpha_3 x^3(t) + \dots$$

(2.36)

There are several figure-of-merits to analyze the large signal response of a PA.

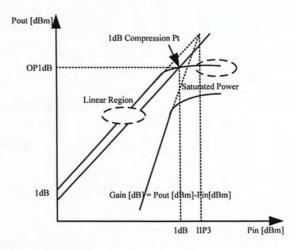

#### 2.2.2.1 1-dB compression point

The 1-dB compression point is defined as the point that the input level causes the linear gain decreased by 1 dB [5]. If a signal  $x(t) = A \cos \omega t$  is applied to the system, harmonics are produced due to the nonlinear gain of the PA. Then, the output voltage will be

$$y(t) = \alpha_1 A \cos \omega t + \alpha_2^2 A^2 \cos^2 \omega t + \alpha_3^3 \cos^3 \omega t$$

(2.37)

$$= \frac{\alpha_2 A^2}{2} + \left(\alpha_1 A + \frac{3\alpha_3 A^3}{4}\right) \cos \omega t + \dots$$

(2.38)

If  $\alpha_1$  and  $\alpha_3$  are out of phase, the constant  $\left(\alpha_1 A + \frac{3\alpha_3 A^3}{4}\right)$  is decreased when the signal amplitude is

increased [5].

$$20 \log \left| \alpha_1 + \frac{3}{4} \alpha_3 A^3 \right| = 20 \log \left| \alpha_1 \right| - 1$$

$$(2.39)$$

$$(2.40)$$

$$(2.40)$$

#### 2.2.2.2 Third-order intermodulation point

The third-order intermodulation point  $(IP_3)$  is another figure-of-merit to analyze the linearity of the PA. However, the output signal is being distorted and cannot be used in amplitude modulation when the amplitude of the input signal swing approaches the 1-dB compression point. Therefore,  $IP_3$  is not an important parameter to examine the linearity of PA.

If the input signals are two tones and close in frequency (i.e.  $x(t) = A_1 \cos \omega_1 t + A_2 \cos \omega_2 t$ ), the fundamental output swing are given by

$$y(t) = \alpha_1 (A_1 \cos \omega_1 t + A_2 \cos \omega_2 t) + \alpha_2^2 (A_1 \cos \omega_1 t + A_2 \cos \omega_2 t)^2$$

$$+ \alpha_3 (A_1 \cos \omega_1 t + A_2 \cos \omega_2 t)^3$$

(2.41)

The following intermodulation products are generated

For

$$2\omega_1 - \omega_2 : \frac{3\alpha_3 A_1^2 A_2}{4}$$

(2.42)

For

$$2\omega_2 - \omega_1 : \frac{3\alpha_3 A_2^2 A_1}{4}$$

(2.43)

Those intermodulation products are close to the fundamental, the signal may be corrupted. The thirdorder intercept point ( $IP_3$ ) is defined as the point where the power of fundamental is equal to the power of the intermodulation. If the amplitudes of two signals are equal ( $A_1 = A_2$ ), then  $IP_3$  can be calculated as follows:

$$|\alpha_1|A_{IP3} = \frac{3}{4}|\alpha_3|A_{IP3}^{3}$$

(2.44)

$$A_{IP3} = \sqrt{\frac{4}{3} \left| \frac{\alpha_1}{\alpha_3} \right|} \tag{2.45}$$

The graphical representation of the 1-dB compression point and IIP3 is shown in Fig. 2.2-2

Fig. 2.2-2 Graphical illustration of 1-dB compression point and IIP3

#### 2.2.2.3 Power Gain

The power gain is defined below:

$$G = \frac{P_{OUT}}{P_{IN}}$$

(2.46)

where  $P_{OUT}$  is power delivered to the load

$P_{IN}$  is power provided by the source

In the power amplifier design, the power gain is not the most important parameter. Most of the power stages of the PA do not have high gain as conjugate match is not used in the PA output stage in order to extract high output power from the supply. Therefore, the gain of power stage is not optimized. In order to have high gain, several gain stages are added before the power stage. In some advanced transceivers, the gain stage can be programmable controlled.

#### 2.2.2.4 Drain Efficiency and Power Added Efficiency

The efficiency is another important parameter in the PA design. There are two definitions for the efficiency. They are listed below:

$$DE = \frac{P_{OUT}}{P_{DC}}$$

(2.47)

where  $P_{OUT}$  is power delivered to the load

$P_{DC}$  is DC supply power

$$PAE = \frac{P_{OUT} - P_{IN}}{P_{DC}}$$

(2.48)

where  $P_{OUT}$  is power delivered to the load

$P_{IN}$  is power available from the source

$P_{DC}$  is DC supply power

## 2.2.2.5 AM-AM and AM-PM conversion

As PA is a nonlinear device, it usually has band-pass frequency response. Assume that PA is memoryless and nonlinear and a modulated signal x(t) is applied to the PA,

$$x(t) = A(t)\cos[2\pi f_{o}t + \phi(t)]$$

(2.49)

the output signal y(t) is given by

$$y(t) = f[A(t)]\cos\{2\pi f_{o}t + \phi(t) + g[A(t)]\}$$

(2.50)

where f[A(t)] is the nonlinear gain (AM-AM conversion)

g[A(t)] is the amplitude-to-phase conversion (AM-PM conversion)

Both the amplitude and phase signal will be corrupted by the nonlinearity of the PA.

## 2.2.3 Modulation Analysis

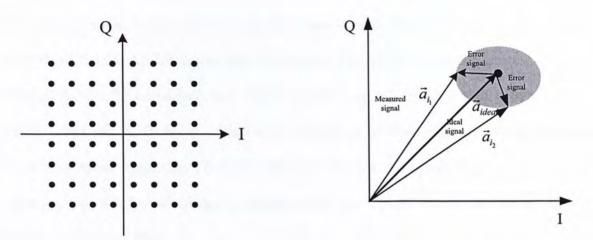

## 2.2.3.1 Constellation Diagram and Error Vector Magnitude

The modulation analysis is used to test the modulation accuracy of the PA or the transmitter. In the digital communication using OFDM, the data symbol is modulated to different modulation types, such as quadrature phase shift keying (QPSK) or M-ray quadrature modulation (M-ray QAM), for example 16-QAM or 64-QAM. After the digital modulation, the fast Fourier transform (FFT) is applied to the data stream and then a time-varying waveform is produced. This waveform is transmitted by the transmitter. The transmitted waveform will be distorted if the transmitter is highly nonlinear. The FFT is applied to the data stream and then the data stream will be demodulated on the receiver side. The error vector magnitude (EVM) is defined as the mean square error between the samples of the actual and the ideal signals, normalized by the average power of the ideal signals [8].

Fig. 2.2-3 64-QAM Constellation diagram

Fig. 2.2-4 Error vector magnitude

$$EVM(\%) = \left[\frac{\sum \left\{\vec{a}_{i} - \vec{a}_{ideal}\right\}^{2}}{\sum \left\{\vec{a}_{ideal}\right\}^{2}}\right]^{\frac{1}{2}} *100$$

(2.51)

The EVM calculated (2.51) is the root mean square value. It can be represent by the in dB form as follows

$$EVM(dB) = 10\log(EVM(\%))$$

(2.52)

## 2.3 Reference

- S.C. CRIPPS, *RF Power Amplifier for Wireless Communications*, 1<sup>st</sup> ed. 685 Canton Street, Norwood, MA 02062, Boston, U.S., Artech House, Inc.

- [2] Patrick Reynaert and Michiel Steyaert, RF power amplifiers for mobile communications, Dordrecht : Springer, c2006.

- [3] Guillermo Gonzalez, Microwave Transistor Amplifiers Analysis and Designs, Englewood Cliffs, N.J., U.S., Prentice-Hall, Inc.

- [4] Reinhold Ludwig and Pavel Bretchko, *RF Circuit Design Theory and Application*, Upper Saddle River, N.J., Pearson/Prentice-Hall, Inc.

- [5] Domine Leenarets, Johan van der Tang and Cicero Vaucher, *Circuit Design for RF Transceivers*,

P.O. Box 17, 3300 AA Dordrecht, The Netherlands, Kluwer Academic Publishers.

- [6] Behzad Razavi, RF microelectronics, Upper Saddle River, NJ : Prentice Hall, c1998

- [7] N. O. Sokal and A. D. Sokal, "Class E- A New Class of High-Efficiency Tuned Single-Ended Switching Power Amplifiers", *IEEE J. Solid-State Circuits*, vo. 10, no. 3, pp. 168-176, Jun. 1975.

- [8] Qizeung Gu, RF System Design of Transceivers For Wireless Communications, New York : Springer Science, c2005

# 3. Circuit Design of Power Amplifier

## 3.1 Introduction

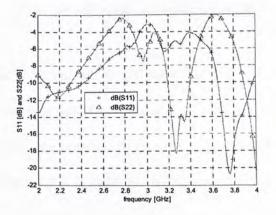

In Chapter 1, it is clear that the requirement of Power Class Index I for WiMAX applications is about 18 dBm to 20 dBm. Therefore, the required output power is set to about 20 dBm. As WiMAX is an OFDM system, the PA cannot operate in the switching mode, so that PA is designed to operate in the linear mode. In order to have high linearity with acceptable efficiency, Class AB topology is chosen. However, this PA is a design prototype, so that the center frequency is set to 3 GHz, which PA has best performance at this frequency band.

In this chapter, the design technique of the PA will be discussed. The PA works under the supply voltage of 3.3 V. The design challenge is that the PA functions under a relatively low supply voltage compared with the SiGe bipolar or GaAs technologies. Therefore, the PA is not terminated with a 50- $\Omega$  load if the output power is needed to be high. In Section 3.2, the topology of the PA is addressed. Afterwards, both the simulation and layout consideration are shown in Section 3.3 and 3.4. The measurement result of the PA will be reported in Section 3.5.

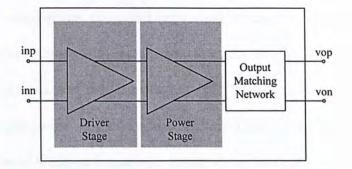

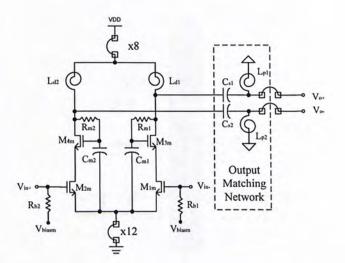

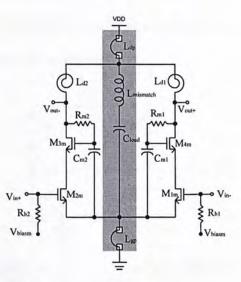

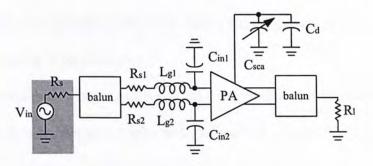

## 3.2 Topology of the Power Amplifier Design

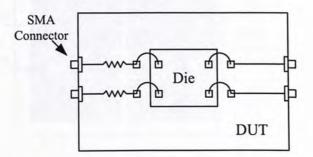

Fig. 3.2-1 shows the overall structure of the proposed PA. It consists of a driver stage, a power stage and an output matching network. The power stage provides adequate output power to the load. As the transistor sizes in the power stage are large, the driver stage is added to drive the large gate capacitance. The gain of the PA is controlled by the transconductance of the driver stage and the quality factor (Q) of its resonant tank. The output matching network is used to transform the 50- $\Omega$  load to the optimum resistance  $R_{OPT}$ .

Fig. 3.2-1 Block diagram of power amplifier

## 3.3 Design in Power Amplifier

#### 3.2.1Power Stage

The design of the power stage involves the selection of appropriate output matching network and transconductance in the power transistors. In order to achieve high output power from low supply voltage because of down-scaling of the CMOS technology, the output resistance should be smaller than 50  $\Omega$ . The optimum output resistance  $R_{OPT}$  can be roughly found by a technique called load-line match method [1] as follows:

$$R_{OPT} = \frac{V_{DD} - V_K}{I_{max}} = \frac{V_{DD} - V_K}{2I_{DD}}$$

(3.1)

where  $V_{DD}$  is the supply voltage and  $V_K$  is the knee voltage and  $I_{max}$  is the peak output current. With a high knee voltage, the transistor falls into the linear or even weak inversion region easily with high voltage swing. The overall gain will, thus, be significantly affected. The W/L ratio of the power transistor is the limiting factor of the knee voltage since the minimum  $v_{ds}$  is proven by

$$v_{ds\,\min} = \sqrt{\frac{2I_{\max}}{\mu C_{ox} \frac{W}{L}}}$$

(3.2)

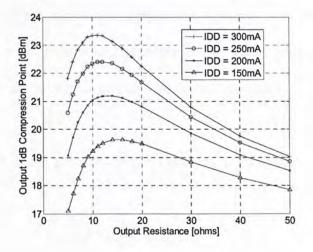

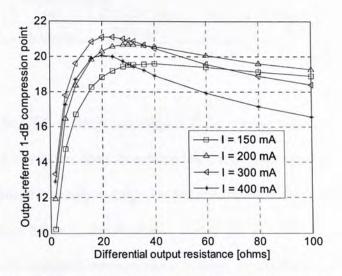

In order to reduce the knee voltage, the aspect ratio should be high in order to reduce  $v_{dsmin}$ . However, this increases the gate capacitance at the same time.  $v_{dsmin}$  can also be reduced by decreasing  $I_{max}$ . Yet, the power gain and output power will then be reduced. Therefore,  $R_{OPT}$ ,  $I_{DD}$  and output power are closely related. The output power should be optimized by varying  $I_{DD}$  and  $R_{OPT}$ , with fixed W/L ratio. The optimization is done in Cadence Spectre-RF by observing the relationship between the output 1-dB compression point (OP1dB) and  $R_{OPT}$  with ideal resistive loads and fixed W/L ratio, as shown in Fig. 3.3-1. An optimum output resistance can be found for each supply current. The curve  $I_{DD} = 250$  mA is used in the design due to the limitation on the DC current through the drain inductors.

Fig. 3.3-1 OP1dB vs ROPT

Although the sizes of the transistors should be large, the upper limit of the size of transistors is dependent on the available size of on-chip inductors at the previous stage. In this case, the previous stage is the driver stage, which will be mentioned at the next section. The on-chip inductors of the driver stage are needed to resonance out the gate capacitance of the transistors at the power stage. However, the on-chip inductors with fixed number of values are provided by the foundry design kit. In order to provide sufficient power gain and minimize loss, the on-chip inductors with highest *Q*-factor are needed to be used.

The on-chip inductor with inductive value of 1.21 nH with the width of 20  $\mu$ m has the highest *Q*-factor, which is used in both the power stage and driver stage.

When the transistors sizes are further increased, the gate capacitance will also increased. A small inductor is required to resonance out the gate capacitance. However, the inductors with values smaller 1 nH, it may be greatly suffered from the process variation. In addition, it may also reduce the power gain of the overall PA, as the power gain depends on the *Q*-factor of the resonator.

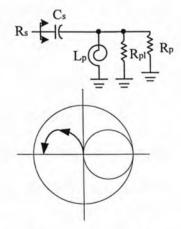

When  $R_{OPT}$  is determined, the output matching network is designed to transform the 50- $\Omega$  load to  $R_{OPT}$ The ratio of the 50- $\Omega$  load and  $R_{OPT}$ , is the transformation ratio of the output matching network. It is shown in [2] that high transformation ratio degrades the efficiency and output power. Therefore,  $R_{OPT}$ should not be smaller than 10. In addition, as shown in Fig. 3.3-1, with a supply current of 250 mA, OP1dB attains the highest value with an output resistance of around 12 $\Omega$ . This is, therefore, chosen as the optimum resistance.

Fig. 3.3-2 and Fig. 3.3-3 show the two output matching topologies. In Fig. 3.3-3, the  $R_L$  can be transformed to  $R_S$  by

$$R_{L} = (Q_{T}^{2} + 1)R_{S} \approx Q_{T}^{2}R_{S}$$

(3.3)

Fig. 3.3-2 Output matching network with series inductor and shunt capacitor

Fig. 3.3-3 Output matching network with series capacitor and shunt inductor

Assuming the  $R_{sl}$  is the parasitic resistance in the on-chip inductor  $L_s$ . The change in resultant resistance due to the parasitic resistance in the on-chip inductor is

$$\Delta R_s = (R_s + R_{sl}) - R_s = R_{sl} \tag{3.4}$$

In the case of Fig. 3.3-3, the  $L_P$  has the same Q-factor as  $L_S$  in Fig. 3.3-2, with the following definition

$$Q_L = \frac{\omega L_s}{R_{sl}} = \frac{R_{pl}}{\omega L_p}$$

(3.5)

With the present of the parasitic resistance in the on-chip inductor in the parallel form, the *Q*-factor of the whole output matching network is the following:

$$Q_T = \frac{R_{pl} //R_L}{\omega L_p}$$

(3.6)

By using the (3.3), the overall series resistance in the output matching network is

$$R_{s}' = \frac{\left(\omega L_{P}\right)^{2}}{R_{pl} / / R_{L}}$$

(3.7)

Finally, the change in series resistance due to the parasitic resistance

$$\Delta R_{S} = R_{S}' - R_{S} = \frac{R_{pl}}{Q_{L}^{2}} = R_{sl}$$

(3.8)

Therefore, the change in resistance due the parasitic resistance in the on-chip inductor is the same in the case of series-inductor-shunt-capacitor and series-capacitor-shunt-inductor. However, the series-inductor-shunt-capacitor configuration is a low-pass filter but the series-capacitor-shunt-inductor is a high-pass filter. The series-capacitor-shunt-inductor cannot filter out the high order harmonic. However, the series-capacitor-shunt-inductor can provides a DC block and the shunt inductor gives lower energy coupling to the substrate as one terminal is grounded [2]. In addition, the series-capacitor-shunt-inductor configuration can relieve the flicker noise upconverted by the upconversion mixer.

The series-capacitor-shunt-inductor topology is chosen for the output matching network. The design equation is set as follows:

$$Q_T = \sqrt{\frac{R_L}{R_S} - 1} = \sqrt{m - 1}$$

(3.9)

$$L_P = \frac{R_L}{\omega Q_T} \tag{3.10}$$

$$C_s = \frac{1}{\omega R_s Q_T} \tag{3.11}$$

where *m* is the transformation ratio,  $R_L$  is the loading resistance,  $R_S$  is the required optimum resistance and  $Q_T$  is the quality factor of the output matching network.

Fig. 3.3-4 shows the overall schematic of the power stage including the output matching network. A supply voltage of 3.3V is used in the power stage. Cascode transistors are used, which are biased by the self-biasing cascode technique as mentioned in [3]. The cascode transistors can extend the breakdown voltage and the PA is more reliable.

In the power stage, the sources of the transistors are connected to ground. The large signal differential drain currents are show as follows:

$$\Delta I_{D} = \frac{1}{2} \mu_{N} C_{OX} \frac{W}{L} \left( V_{GS1} + V_{GS2} - 2V_{T} \right) \left( V_{GS1} - V_{GS2} \right)$$

(3.12)

By keeping  $V_{GS1}$  and  $V_{GS2}$  constant, the differential current can be kept linear under the differential voltage. However, the nonlinearity of the CMOS differential amplifier comes from the nonlinear capacitance within the device, so that CMOS differential amplifier is still nonlinear even this topology is used.

Fig. 3.3-4 Power Stage

The transistors sizes and other component values are listed as follows:

| $M_{lm}$        | 840µ/0.18µ | $M_{2m}$        | 840µ/0.18µ | $M_{3m}$ | 840µ/0.18µ | $M_{4m}$        | 840µ/0.18µ |

|-----------------|------------|-----------------|------------|----------|------------|-----------------|------------|

| $R_{ml}$        | 2.56 kΩ    | R <sub>m1</sub> | 2.56 kΩ    | $R_{b1}$ | 2.56 kΩ    | $R_{b2}$        | 2.56 kΩ    |

| L <sub>d1</sub> | 1.21 nH    | $L_{d2}$        | 1.21nH     | $L_{pl}$ | 1.654 nH   | $L_{p2}$        | 1.654 nH   |

| $C_{ml}$        | 10.45 pF   | $C_{m2}$        | 10.45 pF   | $C_{sl}$ | 3.09 pF    | C <sub>s2</sub> | 3.09 pF    |

In addition, on-chip loading inductors  $L_{d1}$  and  $L_{d2}$  are used. The on-chip inductors suffer from relatively large parasitic resistance compared with the bondwire inductor. The parasitic resistance may reduce the output voltage swing and affect the output power level. However, the differential matching of bondwire inductors are poor as it is hard to produce two bondwire inductors with little or no difference. The poor differential matching at the loading inductors may lead to common mode oscillation shown below

Fig. 3.3-5 Parasitic common mode oscillation

The common mode oscillation frequency due to the resonator at the power supply is given by

$$f = \frac{1}{2\pi \sqrt{\left(L_{dp} + L_{gp} + L_{mismatch}\right)C_{load}}}$$

(3.13)

The common mode oscillation may occur at the desired frequency. In order to prevent the oscillation, two methods may be used. One method is to add a damping resistor in series with the  $C_{load}$ . The other method is to reduce the  $L_{dp}$  and  $L_{gp}$  by using more bondwires. The resonator may be unstable at higher frequency but the gain is insufficient to trigger oscillation.

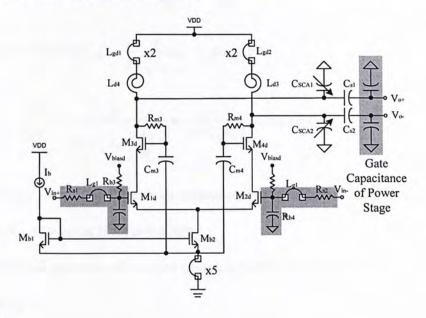

# 3.2.2Driver Stage and Input matching

Input signals will be reflected back when the gate capacitance of the power stage is too large and the PA is connected to the input source directly. Thus, a driver stage, as shown in Fig. 3.3-6, is added to drive the power stage. The gate capacitance in the power stage is resonated by the drain inductors ( $L_{d3}$  and  $L_{d4}$ ). The biasing current in the driver stage can be tuned in order to adjust the gain of the whole PA. A supply voltage of 1.8 V is sufficient to provide the necessary gain. Cascode structure is still used

to provide better stability in the high-gain driver. Similar to the power stage, the cascode transistors are also biased by the self-biasing cascode technique.

Fig. 3.3-6 Driver stage

The lists of transistor sizes and values of components are as follows:

| $M_{ld}$ | 210µ/0.18µ | $M_{2d}$        | 210µ/0.18µ | M <sub>3d</sub> | 210µ/0.18µ | $M_{4d}$        | 210µ/0.18µ |

|----------|------------|-----------------|------------|-----------------|------------|-----------------|------------|

| $R_{m3}$ | 2.56 kΩ    | $R_{m4}$        | 2.56 kΩ    | $R_{b3}$        | 2.56 kΩ    | $R_{b4}$        | 2.56 kΩ    |

| $L_{d3}$ | 1.21 nH    | L <sub>d4</sub> | 1.21nH     | $C_{s1}$        | 5.047 pF   | C <sub>s2</sub> | 5.047 pF   |

| $C_{ml}$ | 10.45 pF   | C <sub>m2</sub> | 10.45 pF   | $M_{b1}$        | 125/0.18   | $M_{b2}$        | 1000/0.18  |

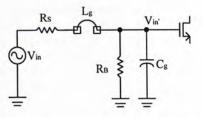

At the input port, a series resonator is formed by bondwire inductors  $L_g$ , gate capacitance  $C_g$ , source resistance  $R_s$  and resistive biasing resistor  $R_B$ . This resonator shown in Fig. 3.3-7 controls the input reflection coefficient of the PA.

Fig. 3.3-7 Series resonator at input port

The resonator forms a potential divider and the ratio  $\frac{Vin}{Vin}$  is shown in (3.14).

$$\frac{Vin'}{Vin} = \frac{1}{j\omega\left(C_g R_s + \frac{L_g}{R_B}\right) + 1 + \frac{R_s}{R_B} - \omega^2 L_g C_g}$$

(3.14)

$\frac{Vin'}{Vin}$  at the resonant frequency  $f_o = \frac{1}{2\pi\sqrt{L_g C_g}}$  is given by

$$\frac{Vin'}{Vin} = \frac{1}{j\omega\left(C_g R_s + \frac{L_g}{R_B}\right)} \approx \frac{1}{j\omega\left(C_g R_s\right)} \text{ as } R_B >> L_g$$

(3.15)

To reduce the voltage loss,  $C_g$  and the series resistance  $R_s$  should be reduced. However, common mode oscillation due to  $L_g$  may occur if  $R_s$  is too small.

The CMOS differential pair with tail current source is used in the driver configuration. The large signal response is given by

$$I_{D1} - I_{D2} = \frac{1}{2} \mu_N C_{OX} \frac{W}{L} (V_{in1} - V_{in2}) \sqrt{\frac{4I_{SS}}{\mu_N C_{OX} \frac{W}{L}} - (V_{in1} - V_{in2})}$$

(3.16)

From (3.16), it can be shown that driver is more nonlinear compared with the source-grounded differential pair in power stage. However, it can have better common mode rejection.

The overall gain of the PA depends on the shunt resonator, consisting of the drain inductors ( $L_{d3}$  and  $L_{d4}$ ), switched capacitor network ( $C_{scal}$  and  $C_{sca2}$ ), gate capacitance of the power stage ( $C_g$ ) and coupling capacitors ( $C_{s1}$  and  $C_{s2}$ ). Its resonant frequency, determined by (3.17) can be tuned by changing the value of  $C_{sca}$ .

$$\omega = \frac{1}{\sqrt{L_d \left(C_{sca} + \frac{C_s C_g}{C_s + C_g}\right)}}$$

(3.17)

## 3.4 Simulation Result on Power Amplifier

The design is simulated using Cadence Spectre-RF simulator. In the pre-layout simulation, some shunt capacitor is added to model the parasitic capacitance of metal wires. The simulation schematic is shown below

Fig. 3.4-1 Simulation schematic

As the PA is differential, two baluns with no loss are added at both input and output port. The  $L_g$  and  $R_s$  are the inductor and resistor for input matching.  $C_{in}$  models the parasitic capacitance of metal wires at the input port, and  $C_d$  model the parasitic capacitance at the node between driver stage and power stage.  $C_{sca}$  model the switched capacitor array at the circuit.

Both the pre-layout and post-layout simulation result is shown as follows. In the pre-layout simulation,  $C_{in}$  is set to 200fF to model the on-chip metal wires. The circuit is measured at 3 GHz center frequency with different values of  $L_g$ ,  $C_{in}$  and  $C_{sca}$ .

|                  | Pre-layout @ 3G | Post-layout @3G |

|------------------|-----------------|-----------------|

| Psat [dBm]       | 24.0762         | 24.7746         |

| P1dB [dBm]       | -11.9796        | -12.1258        |

| OP1dB [dBm]      | 19.054          | 21.2942         |

| linear gain [dB] | 32              | 34.4            |

| gain @ P1dB [dB] | 31.0338         | 33.42           |

| PAE @ P1dB [%]   | 11.06946        | 18.253          |

| PAE @ Psat [%]   | 36              | 34              |

| DR power [W]     | 66.4m           | 65.5m           |

| PW power [W]     | 615m            | 611m            |

| Cin / fF         | 200             | 1               |

| Lg / nH          | 4.5             | 3.5             |

| Cd / F           | 2р              | 1f              |

| code             | b'111'          | b'000'          |

Table 3-1 Pre-layout and post-layout simulation result at 3 GHz