## **Voltage Island-driven Floorplanning**

### MA, Qiang

A Thesis Submitted in Partial Fulfilment of the Requirements for the Degree of Master of Philosophy

in

Computer Science and Engineering

©The Chinese University of Hong Kong July 2008

The Chinese University of Hong Kong holds the copyright of this thesis. Any person(s) intending to use a part or whole of the materials in the thesis in a proposed publication must seek copyright release from the Dean of the Graduate School.

#### Thesis/Assessment Committee

Professor Prof. WU Yu Liang (Chair) Prof. YOUNG Fung Yu (Thesis Supervisor) Prof. XU Qiang (Committee Member) Prof. LUK Wai Shing (External Examiner)

## Abstract

As the integration density continues to advance, energy efficiency has become one of the most important issues to be addressed in today's System-on-a-Chip (SoC) designs. One way to lower the power consumption is to reduce the supply voltage. *Multiple Supply Voltage* (MSV) is thus introduced to provide higher flexibility in controlling the power and performance trade-off. In region-based MSV, circuits are partitioned into "voltage islands" where each island occupies a contiguous physical space and operates at one supply voltage. These tasks of voltage island partitioning and voltage level assignments should be done simultaneously in the floorplanning process in order to take those important physical information into consideration.

In this thesis, we formulate the MSV driven floorplanning problem and solve it. Particularly, we address this problem in two stages. In the first stage, we solve a simpler version of this problem by assuming that timing requirements of the given circuit can be achieved by all different voltage levels of the modules; in the second stage, we try to consider this problem in more details, i.e., the working voltage levels of the modules are properly assigned to meet the timing requirements.

In the first stage, we focus on optimal voltage island partitioning and voltage assignment, where the voltage islands generated are rectangular in shape. An elegant voltage island-driven floorplanner is provided to generate a floorplan with rectangular voltage islands. Given a candidate floorplan solution represented by a normalized Polish expression, optimal voltage level assignment and island partitioning can be obtained simultaneously to minimize the total power consumption. Simulated annealing is used as the basic searching engine. By using this approach, significant power savings (up to 50%) can be achieved for all data sets. This floorplanner can also be extended to minimize the number of level shifters between different voltage islands and to simplify the power routing step by placing the islands in proximity to the corresponding power pins.

In the second stage, we focus on solving the sub-problem of voltage assignment on a given netlist under timing constraints. We first show that the voltage assignment task on a given netlist can be formulated as a convex cost dual network flow problem and can be solved optimally in polynomial time using a cost-scaling algorithm when the delay choices of each module are continuous in the real or integer domain. We can make use of this approach to obtain a feasible voltage assignment solution in the general cases with power consumption approximating the minimum one. Furthermore, we propose a framework to optimize power consumption and physical layout of a circuit simultaneously during the floorplanning stage, by embedding this cost-scaling solver into a simulated annealing based floorplanner. We compared our approach with the latest work [11] on the same problem, and the experimental results show that, using our framework, significant improvement on power saving (18% less power cost on average) can be achieved in much less running time (7X faster on average) for all the test cases, which confirms the effectiveness of this approach.

摘要

由於電路集成密度不斷增加,功耗逐漸成為了當今片上系統(SoC)設計中最重要的問題之一。降低供電電壓是降低功耗的一種有效措施。因此,多供應電壓(MSV)設計方法為平衡電路的功耗和性能提供了更大的靈活性。在區域性多供應電壓設計中,電路被分為若干個"電壓島",其中每一個電壓島佔據一塊連續的區域,而且同一個電壓島裏的電路單元工作於同一個電壓。在 MSV 設計中,同時考慮電壓島的劃分,供應電壓的分配和電路佈局將會很有利於整個設計的優化。

在本論文中,我們提出並解決了多供電電壓驅動的電路佈局問題。具體來說,我 們將這個問題分爲兩個階段進行解決。在第一個階段,我們認爲所有的電壓選 擇都可以滿足電路的時序要求,從而解決了這個問題的一個比較簡單的版本;在 第二個階段,我們通過在分配各個模組的供電電壓時考慮滿足電路時序要求,更 深入的考慮了這個問題。

在第一個階段,我們提供了一個電壓島驅動的佈局工具,它可以產生一個具有矩 形電壓島的電路佈局。給出一個由標準化波蘭運算式表示的電路佈局,我們可 以得到這個佈局上最優的電壓分配和電壓島的劃分,這裏最優指使得整個電路 功耗最低。搜索引擎採用了類比退火方法。這種方法可以很有效地降低功耗(最 大可以達到 50%).另外,我們可以拓展這個佈局工具,使其同時考慮減少需要使 用的電壓轉換器的數量,以及考慮電壓島和與其對應的供電引腳的毗鄰性。

在第二個階段, 我們主要考慮了解決在滿足時序要求下的電壓分配問題。在 MSV 設計中, 電路單元的電壓分配一定要滿足電路時序要求。 我們論證了在一 個給定的電路網表上滿足時序要求的電壓分配問題可以歸結為最小開銷網路流 問題. 當每一個電路單元的延遲的選擇範圍是一些連續整數時, cost-scaling 演算 法可以用多項式時間得到該電壓分配問題的最優結果。 在一般情況下, 即電路 單元延遲的取值範圍不連續時, 我們可以利用這種方法得到一個近似結果。 而 且, 通過把 cost-scaling solver 嵌入一個基於類比退火方法的電路佈局工具, 我們 給出了一個用來同時優化功耗和佈局的框架。 我們跟最近的針對相同問題的工 作[11]做了比較, 實驗結果顯示, 我們的方法可以更在更短的時間內得到更好的 結果, 從而證明了我們的方法的優越性。

# Acknowledgement

This thesis owes much to the thoughtful and helpful comments of my supervisor, Professor Evangeline Fung Yu Young, who patiently motivated me to conceive and develop the main idea of the thesis. Here I would like to express to her my greatest gratitude for her supervision, advice and instructions from the very early stage of this research as well as giving me extraordinary experiences through out the work. Above all and the most needed, she provided me unflinching encouragement and support in various ways. Without her inspirational guidance, this thesis could not be successfully completed.

Also, I gratefully acknowledge Professor David Yu-Liang Wu and Professor Qiang Xu, the committee members during the oral defense. Thanks for having read a draft of this thesis and having made their precious comments and suggestions. As for any remaining errors, the responsibility for the text rests entirely upon the author. Special thanks go to Mr. Lei Shi for his kind help on the formatting of this thesis.

Finally, I would like to thank everybody who was important to the successful realization of thesis, as well as expressing my apology that I could not mention personally one by one.

# Contents

| Ał | Abstract                                                      |                                                  |    |  |  |  |  |

|----|---------------------------------------------------------------|--------------------------------------------------|----|--|--|--|--|

| Ac | know                                                          | ledgement                                        | iv |  |  |  |  |

| 1  | Intro                                                         | roduction                                        |    |  |  |  |  |

|    | 1.1                                                           | Background                                       | 1  |  |  |  |  |

|    | 1.2                                                           | Floorplanning                                    | 2  |  |  |  |  |

|    | 1.3                                                           | Motivations                                      | 4  |  |  |  |  |

|    | 1.4                                                           | Design Implementation of Voltage Islands         | 5  |  |  |  |  |

|    | 1.5                                                           | Problem Formulation                              | 8  |  |  |  |  |

|    | 1.6                                                           | Progress on the Problem                          | 10 |  |  |  |  |

|    | 1.7                                                           | Contributions                                    | 12 |  |  |  |  |

|    | 1.8                                                           | Thesis Organization                              | 14 |  |  |  |  |

| 2  | Lite                                                          | rature Review on MSV                             | 15 |  |  |  |  |

|    | 2.1                                                           | Introduction                                     | 15 |  |  |  |  |

|    | 2.2                                                           | MSV at Post-floorplan/Post Placement Stage       | 16 |  |  |  |  |

|    | 2.2.1 "Post-Placement Voltage Island Generation under Perfor- |                                                  |    |  |  |  |  |

|    |                                                               | mance Requirement"                               | 16 |  |  |  |  |

|    |                                                               | 2.2.2 "Post-Placement Voltage Island Generation" | 18 |  |  |  |  |

|   |     | 2.2.3                                                  | "Timing-Constrained and Voltage-Island-Aware Voltage As- |    |

|---|-----|--------------------------------------------------------|----------------------------------------------------------|----|

|   |     |                                                        | signment"                                                | 19 |

|   |     | 2.2.4                                                  | "Voltage Island Generation under Performance Require-    |    |

|   |     |                                                        | ment for SoC Designs"                                    | 20 |

|   |     | 2.2.5                                                  | "An ILP Algorithm for Post-Floorplanning Voltage-Island  |    |

|   |     |                                                        | Generation Considering Power-Network Planning"           | 21 |

|   | 2.3 | MSV a                                                  | at Floorplan/Placement Stage                             | 22 |

|   |     | 2.3.1                                                  | "Architecting Voltage Islands in Core-based System-on-a- |    |

|   |     |                                                        | Chip Designs"                                            | 22 |

|   |     | 2.3.2                                                  | "Voltage Island Aware Floorplanning for Power and Tim-   |    |

|   |     |                                                        | ing Optimization"                                        | 23 |

|   | 2.4 | Summ                                                   | nary                                                     | 27 |

| 3 | MS  | V Drive                                                | en Floorplanning                                         | 29 |

|   | 3.1 | Introd                                                 | uction                                                   | 29 |

|   | 3.2 | Proble                                                 | em Formulation                                           | 32 |

|   | 3.3 | Algor                                                  | ithm Overview                                            | 33 |

|   | 3.4 | 0.4 Optimal Island Partitioning and Voltage Assignment |                                                          |    |

|   |     | 3.4.1                                                  | Voltage Islands in Non-subtrees                          | 35 |

|   |     | 3.4.2                                                  | Proof of Optimality                                      | 36 |

|   |     | 3.4.3                                                  | Handling Island with Power Down Mode                     | 37 |

|   |     | 3.4.4                                                  | Speedup in Implementation and Complexity                 | 38 |

|   |     | 3.4.5                                                  | Varying Background Chip-level Voltage                    | 39 |

|   | 3.5 | Simul                                                  | lated Annealing                                          | 39 |

|   |     | 3.5.1                                                  | Moves                                                    | 39 |

|   |     | 3.5.2                                                  | Cost Function                                            | 40 |

|   | 3.6 | Exper                                                  | rimental Results                                         | 40 |

|   |     | 3.6.1                                                  | Extension to Minimize Level Shifters                     | 45 |

|   |        | 3.6.2    | Extension to Consider Power Network Routing            | 46 |

|---|--------|----------|--------------------------------------------------------|----|

|   | 3.7    | Summa    | ary                                                    | 46 |

| 4 | MSV    | / Drive  | n Floorplanning with Timing                            | 49 |

|   | 4.1    | Introdu  | action                                                 | 49 |

|   | 4.2    | Problem  | m Formulation                                          | 52 |

|   | 4.3    | Algorit  | thm Overview                                           | 56 |

|   | 4.4    | Voltage  | e Assignment Problem                                   | 56 |

|   |        | 4.4.1    | Lagrangian Relaxation                                  | 58 |

|   |        | 4.4.2    | Transformation into the Primal Minimum Cost Flow Prob- |    |

|   |        |          | lem                                                    | 60 |

|   |        | 4.4.3    | Cost-Scaling Algorithm                                 | 64 |

|   |        | 4.4.4    | Solution Transformation                                | 66 |

|   | 4.5    | Simula   | ated Annealing                                         | 69 |

|   |        | 4.5.1    | Moves                                                  | 69 |

|   |        | 4.5.2    | Speeding up heuristic                                  | 69 |

|   |        | 4.5.3    | Cost Function                                          | 70 |

|   |        | 4.5.4    | Annealing Schedule                                     | 71 |

|   | 4.6    | Experi   | imental Results                                        | 71 |

|   | 4.7    | Summ     | nary                                                   | 72 |

| 5 | Cor    | nclusion |                                                        | 76 |

| В | ibliog | raphy    |                                                        | 80 |

# **List of Figures**

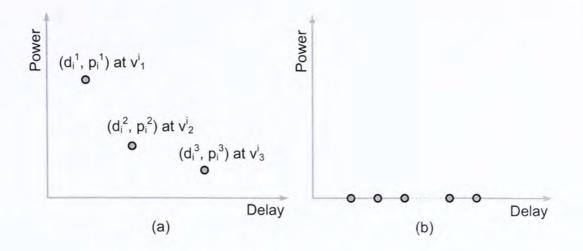

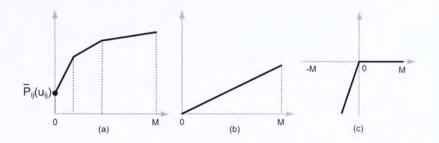

| 1.1 | DP curve of $(a)$ a vertex and $(b)$ an edge in $G$                                    | 10 |

|-----|----------------------------------------------------------------------------------------|----|

| 2.1 | An Example DP-Curve (The three points of the DP-curve repre-                           |    |

|     | sent the delay-power characteristics of different supply voltages) .                   | 25 |

| 2.2 | The backtracing procedure in [11] for getting a solution                               | 26 |

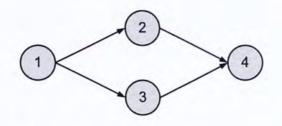

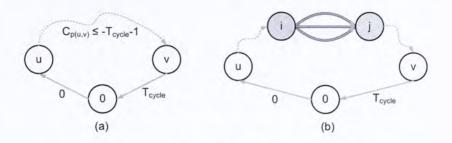

| 2.3 | A reconvergent structure in the netlist                                                | 27 |

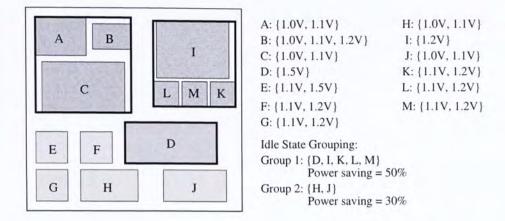

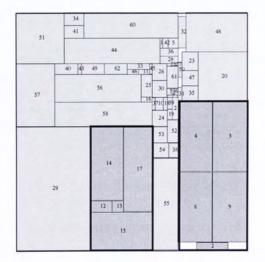

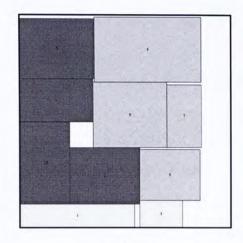

| 3.1 | An example of the voltage island driven floorplanning problem                          | 31 |

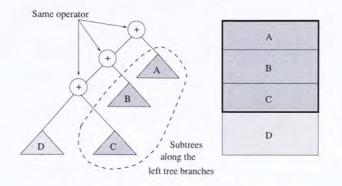

| 3.2 | An example of forming an island across subtrees                                        | 37 |

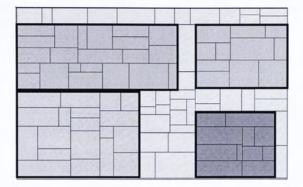

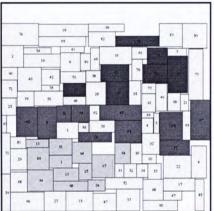

| 3.3 | One Resultant Floorplan of $n100$ with Four Voltage Islands                            | 42 |

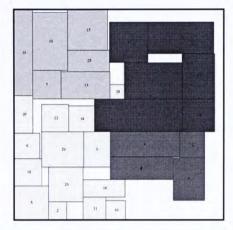

| 3.4 | One resultant floorplan of <i>playout</i> with some blocks operated at                 |    |

|     | very low voltages                                                                      | 42 |

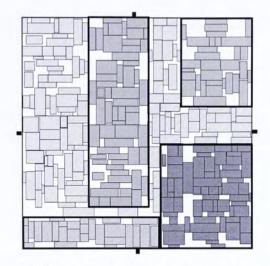

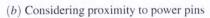

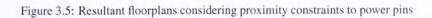

| 3.5 | Resultant floorplans considering proximity constraints to power pins                   | 47 |

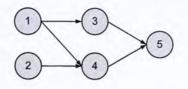

| 4.1 | The DAG representation of a netlist                                                    | 52 |

| 4.2 | The transformed DAG $\overline{G}$ of the graph G in Fig. 4.1                          | 53 |

| 4.3 | Delay power curve $P_{ij}(d_{ij})$ of $(a)$ an edge $e(i, j) \in E_1$ ; $(b)$ an edge  |    |

|     | $e(i,j) \in E_2$ ; (c) an edge $e(i,j) \in E_3$                                        | 57 |

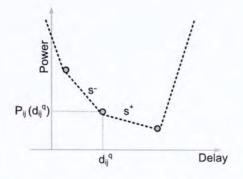

| 4.4 | Left slope $s^-$ and right slope $s^+$ at $(d_{ij}^q, P_{ij}(d_{ij}^q))$ in a DP curve | 61 |

| 4.5 | Function $H_{ij}(x_{ij})$ of (a) an edge in $E_1$ ; (b) an edge in $E_2$ ; and (c)     |    |

|     | an edge in $E_3$                                                                       | 63 |

| 4.6 | Paths in the proof of Lemma 3                                                          | 67 |

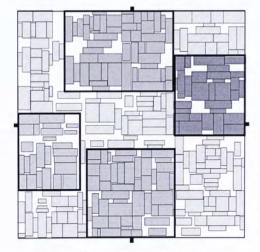

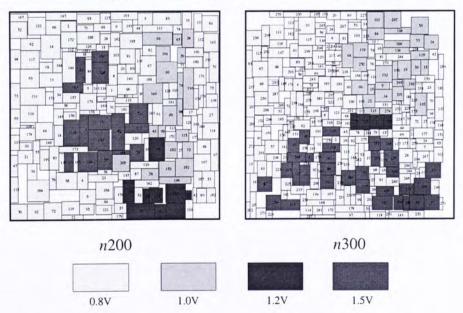

| 4.7 | Resultant floorplanns with each module having multiple legal work- |    |  |  |  |  |

|-----|--------------------------------------------------------------------|----|--|--|--|--|

|     | ing voltage levels                                                 | 73 |  |  |  |  |

# **List of Tables**

| 3.1 | Data sets for MSV driven floorplanning               |     | 41 |

|-----|------------------------------------------------------|-----|----|

| 3.2 | Comparisons of our MSV driven floorplanner with [16] |     | 43 |

| 3.3 | Experimental results of MSV driven floorplanning     |     | 44 |

| 3.4 | Extending for minimization of level shifter number   |     | 45 |

| 4.1 | Comparisons of our framework with previous work [11] |     | 74 |

| 4.2 | Results with more legal working voltage levels       | • • | 74 |

## Chapter 1

# Introduction

### 1.1 Background

The technology of *integrated circuit (IC)* was widely adopted for computing devices like microprocessors, memory modules, and many other interface chips since 1960s. It is not surprising to find that we are surrounded by a huge number of computing devices in daily life, such as our personal computers, the ATM machines we use to withdraw cash, and many other electronic appliances. IC is one of the core components of those computing facilities.

As the Very Deep Sub-Micron(VDSM) technology advances, IC has evolved from Small Scale Integration(SSI) to Very Large Scale Integration(VLSI), which means the integration density becomes much higher while the interconnections tend to be much more complicated, thus introducing many new challenges to VLSI design automation.

Producing a chip is quite a complicated process containing a couple of steps, each of which can be accomplished with the help of the specifically implemented CAD tools. Generally speaking, the process starts with a formal specification, and the final product is a fabricated chip. The VLSI design cycle traditionally

#### CHAPTER 1. INTRODUCTION

consists of steps including Architecture Design, Functional Design, Logic Design, Circuit Design, Physical Design and finally, Fabrication. Among all these steps, Physical Design is of significant importance, whose task is to transform a circuit representation into a geometric representation. The geometric representation of a circuit is called a layout. During physical design, problems like where to place the modules, how the interconnections between the modules should be made, etc, will be addressed. As physical design is a crucial yet complex step in the design cycle, it can be further broken down into sub-steps, such as partitioning, floorplanning, placement, routing, and so on.

Floorplanning is an important step in the physical design cycle, as a good planning in the early design phase is crucial to avoid unnecessary iteration in the design cycle. During the step of floorplanning, the blocks are positioned on the chip roughly, so as to optimize the circuit size and performance according to the circuit specification. A compact design is favorable, but there are many other important aspects that have to be taken care of. For example, issues like the block dimensions, overall delay and power consumption should be taken into account. In addition, there may also be some special constraints needed to be satisfied, e.g., some blocks are pre-placed, while some others are required to be placed adjacent to each other, etc.

#### 1.2 Floorplanning

The input to the floorplanning phase is a set of blocks, the area of each block, the possible shapes of each block, the number of terminals of each block, and the interconnections between blocks. In the floorplanning phase, we are going to plan the position and the shape of each block, together with the pin positions. The shapes for some blocks are fixed and cannot be altered. We called those blocks hard blocks. For other blocks, the shapes can be altered as long as their aspect

ratios are within the desired value range. Those blocks are called soft blocks. A formal definition of the floorplanning problem is given as follows:

**Definition 1 Floorplanning** - Given a set of n modules  $\{M_1, M_2, ..., M_n\}$ , where each module  $M_i$  is associated with an area  $A_i$ , together with two aspect ratio bounds  $r_i$  and  $s_i$  such that  $r_i \leq h_i/w_i \leq s_i$ , where  $h_i$  and  $w_i$  is the height and the width of module i respectively. The output of the problem is a packing of the set of modules, i.e., the x and y coordinates and the dimension  $(h_i, w_i)$  of each module. There should be no overlapping between modules, and the circuit performance should be optimized.

There are several objectives to be optimized in floorplanning, like the total chip area, the total wire length, the critical path delay, etc.

- Chip Area Area minimization is one of the most commonly adopted objectives. Minimizing the chip area implies minimizing the wire length, and hence reducing the circuit delay.

- Total Wire Length In addition to minimizing the chip area, minimizing the total wire length directly is also another important goal. Beside the timing issues, using less wires to connect the modules means consuming less resources, and thus reducing the production cost.

- Delay In some cases, minimizing the total wire length is not enough. Timing is and important issue. The final circuit performance can be optimized by minimizing the delay on the critical path.

- Routability Routability refer to the possibility of completing all the connections. A non-routable floorplan is of no use even if it is area-optimized and delay-optimized. Enhancing the routability of a floorplan means to reduce

the chance of encountering routing problems in the downstream designing steps.

5. *Others* - There are still some other objectives in floorplanning, like minimizing heat dissipation, minimizing power consumption, etc.

### 1.3 Motivations

As technology scales for increased circuit density and performance, the need to reduce power consumption increases in significance as designers strive to utilize the advancing silicon capabilities. The total power consumed by conventional CMOS circuitry is composed of two sources, namely, dynamic power and leakage power. The leakage power refers to the sub-threshold current of the transistors in the circuit [1], while the dynamic power represents the power consumed by the intended work of the circuit to switch states and thus execute logic functions. Dynamic power is primarily composed of the power associated with the charging or discharging of the capacitance of the switching nodes [10]. Generally, the dynamic power consumption can be computed by

$$P_{dynamic} = k \cdot C_{load} \cdot V_{dd}^2 \cdot f$$

where k is the circuit switching rate,  $C_{load}$  is the loading capacitance,  $V_{dd}$  is the supply voltage, and f is the clock frequency. Dynamic power dominates the total power consumption in today's logic design. The dynamic power consumption is proportional to the square of  $V_{dd}$ , implying that lowering supply voltages can effectively reduce dynamic-power consumption, although the performance also degrades. Therefore, *Multiple supply voltage* (MSV) is introduced to provide higher flexibility in controlling power and performance trade-off.

MSV designs involve the partitioning of a chip into areas called "voltage islands" that can be operated at different voltage levels, or be turned off when idle. With the use of voltage islands, the chip design process is becoming more complicated. We need to solve the problems of island partitioning, voltage assignment and floorplanning simultaneously under area, power, timing and other physical constraints. These problems must be solved at the same time since their results will significantly affect each other. In addition, there are other issues to be considered. For example, the voltage islands should be placed close to the power pins in order to minimize the power routing complexity and the IR drop. Besides, each island requires level shifters to communicate with others and overhead in area and delay will be resulted. These additional issues have created many new challenges in generating floorplans for designs using voltage islands.

#### 1.4 Design Implementation of Voltage Islands

An SoC architecture based on voltage islands requires additional design components to ensure reliable communications across island boundaries, distribute and manage power, and save and restore logic state during power-off and on.

A voltage island represents a level of hierarchy with unique powering, and it exists within a parent block which constitutes the physical region in which the island is placed. An island's parent block may be the top level of a chip design or even another island at the next higher level of the chip hierarchy. The circuits within a voltage island are primarily powered from the island voltage, called VDDI (VDD-island), while the circuits in the parent terrain are powered from a supply voltage called VDDO (VDD-outside). With deeper hierarchy, the VDDO of one island may be equivalent to the VDDI of a parent island in which it is contained.

When such a gate operates at a voltage sufficiently lower than the gate it drives, signal margins and performance will degrade, and the driven circuit will consume significantly higher power. Further increases in the voltage difference will eventually result in unreliable signal switching. Clearly, additional circuitry is necessary

#### CHAPTER 1. INTRODUCTION

to handle the differences in both magnitude and timing that can occur between VDDI and VDDO at island boundaries. Circuits called Voltage Island Receivers perform this function for signals going from the parent block into the island, while Voltage Island Driver cells perform similar task for signals going from the island to the parent block. These drivers and receivers must provide reliable voltage level shifting between VDDI and VDDO for a wide range of operating voltages, and do so with minimal impact to signal delay or duty cycle.

Leakage or standby power can be reduced by lowering the voltage of functionallyinactive islands well below the level required for reliable operation. However, some logic states, prior to power-down, may need to be preserved to resume operation once the island is powered up again, at the end of the inactive period. Special state-saving latches provide a solution to this problem, eliminating the need to transfer logic states off-island and back in order to save and restore necessary logic states.

A voltage island requires at least one power source and complete isolation from all other supplies on the chip, in order to enable independent power sequencing. Physical planning of voltage islands includes determining the number of power sources that meets all islands' power requirements. The following are possible types of off-chip and on-chip power source:

- · Solder bumps or C4 pads

- · Wire bond pads

- · Island power switches

- · Voltage regulators

Some voltage island circuits require both the internal voltage island supply (VDDI) and the external voltage supply (VDDO) for proper operation. These include level-shifting circuits, state-saving latches, and power switches. Power-routing tools must be aware of these constraints and make efficient VDDI and

VDDO connections without creating electrical or wireability issues.

The P/G network of the chips using voltage islands can be much more complex than traditional one because many additional decisions must be made to fit the island design. These decisions may include the following: to use on-chip power regulator or off-chip power source, to use separate Vdd networks or use DC-DC converter in every local voltage island, and the topology of the power grid of each island (wire width, pitch, spacing, etc.). Many possibilities exist for powering voltage islands, driving further requirements for special design components. VDDI or VDDO may be supplied directly from a unique, non-switching power source. One or both may be the output of an on-chip voltage regulator, whose voltage value can be fixed or programmable. Finally, VDDI or VDDO may be a switched version of some other voltage supply, controlled by one or more PFET or NFET switches. A given SoC design may use one or more of these approaches depending upon the product design objectives. An example of power network design for a chip with voltage islands is shown below:

• Cells with different supply voltages share the same ground network, but use different power supply networks.

• There is a global power network, to which cells not in any voltage island are connected. For each voltage island, there is a separate Vdd network, connected to special power pads.

• The global power network is part of a uniform mesh, with the same width and pitch across the chip, except the parts over voltage islands are removed.

• There is a boundary power ring along the outer edges of the global power network. The width of the power ring is several times wider than that of the top-level wires in the global power network. The power ring connects the global network to power pads, and is very helpful to ensure power delivery integrity.

#### **1.5 Problem Formulation**

In the MSV driven floorplanning problem, we are given a set of *n* modules with areas  $A_1, A_2...A_n$  and aspect ratio bounds  $[l_i, u_i]$  for i = 1...n. Each module *i* is associated with a power table  $T_i$  that specifies the legal voltage levels for the module and the corresponding average power consumption values. In MSV designs, the timing requirements of the circuits should be satisfied. Besides, the power network resource should also be minimized. Given a floorplan, the power network resource  $\Phi_q$  for the modules working at voltage  $v_q$  can be estimated by the half-perimeter of the bounding box of all those modules [11], while the total power network resource is the sum of  $\Phi_q$ , for q = 1, 2, ..., k where k is the number of different voltage levels available.

We can define the MSV driven floorplanning problem as follows:

**Definition 2 MSV Driven Floorplanning** - Given a netlist, a timing constraint and a set of modules, each of which has multiple choices of supply voltage, generate a floorplan in which each module is assigned to work at a specific voltage level such that the timing constraint is satisfied and a weighted sum of the power consumption, power network resource, area and interconnect length is minimized.

In this thesis, we address this problem in two stages. In the first stage, we solve a simpler version of this problem by assuming that timing requirements of the given circuit can be achieved by all different voltage levels of the modules; in the second stage, we try to consider this problem in more details, i.e., the working voltage levels of the modules are properly assigned to meet the timing requirements.

In the first stage, we focus on optimal voltage island partitioning and voltage assignment, where the voltage islands generated are rectangular in shape. In this work, the timing requirement is not explicitly taken into consideration, and we assume that the given voltage levels of each module can meet timing. Given a constant K and a chip-level voltage  $V_c$ , our goal is to generate a floorplan F with K rectangular voltage islands so that a weighted sum of the total power consumption, area and interconnect length is minimized. Each island will be supplied with the lowest possible voltage level common to all the modules in that island while the remaining modules not assigned to any island will be operated at the chip-level voltage.

In the second stage, we consider timing more explicitly. Each module  $m_i$  is given  $k_i$  choices of supply voltages  $v_q^i$ , for  $1 \le q \le k_i$ , and the power-delay tradeoff in  $m_i$  is represented by a *delay-power curve* (DP Curve), {  $(d_i^1, p_i^1), (d_i^2, p_i^2), ...,$  $(d_i^{k_i}, p_i^{k_i})$ }, where each pair  $(d_i^q, p_i^q)$  is the corresponding delay and power consumption when  $m_i$  is operated at  $v_a^i$ . Note that each  $d_i^q$  is in  $Z^+$  (positive integer set), since the delay of a module is measured in terms of the number of clock cycles. Fig. 1.1(a) is an example of a DP Curve, which contains three choices of supply voltages for this module. Moreover, we assume that for each module, power is a convex function of delay when each point  $(d_i^q, p_i^q)$  is connected to its neighboring point(s) by a linear segment in the DP Curve. We are also given a timing requirement  $T_{cvcle}$ , called clock cycle time, of this circuit and require that the critical path delay is at most  $T_{cvcle}$ . We first focus on solving the sub-problem of voltage assignment on a given netlist under timing constraints, objective of which is to select a delay-power pair for each module in its DP Curve such that the sum of power consumption is minimized while the timing constraint is satisfied. Globally, the voltage assignment procedure is incorporated into a simulated annealing based floorplanner to solve the MSV driven floorplanning problem.

Figure 1.1: DP curve of (a) a vertex and (b) an edge in G

#### 1.6 Progress on the Problem

A number of previous works addressed the voltage assignment and island generation problem in floorplanning and placement. In these previous works, MSV is considered at various design stages, including the floorplanning and placement stages [8], [9], [11], [13], [14], and the post-floorplanning and post-placement stages [5], [12], [16], [19], [20].

For the latter category, Wu *et al.* [19] minimized the number of voltage islands generated on a slicing floorplan using a dynamic programming based approach, Ching *et al* [5] then considered voltage islands that are non-rectangular in shape, and they also targeted at minimizing the number of voltage island generated by iteratively partitioning a tree structure, which is initially constructed according to an adjacency graph of a candidate floorplan to reflect the similarities of required working voltage levels among adjacent blocks. Mak *et al.* [16] formulated the voltage assignment and island generation problem as an *integer linear program* (ILP). In this approach, a few candidate floorplan solutions are generated based on metrics like area and interconnect cost, then voltage assignment and partition-

ing are performed on these candidate floorplans using an ILP approach to identify the best candidate solution. A fragmentation cost (number of adjacent cores operating at different voltages) is used to model the power network complexity but this cost is not related to the number of islands directly. [20] and [12] take timing constraints into consideration. In [20], Wu *et al.* proposed an approximation algorithm based on a *zero slack algorithm* to minimize the power cost and to simplify the power network resource under timing constraints; Lee *et al.* [12] tackled the voltage assignment problem using an ILP based approach with a set of linear inequalities representing the timing requirements. An inevitable deficiency of all these post-floorplanning and post-placement works is that physical layout and power optimization are done separately, hence the solution quality is restricted to a certain extent.

Concurrent physical layout and power optimization will be much more favorable. Hu *et al.* [8] considered this simultaneous voltage assignment, voltage island generation, and floorplanning problem in SoC designs. Simulated annealing is used as the basic searching engine. Given a candidate solution, perturbations are performed to split an island, change the voltage of an island or change all the islands of one voltage to another voltage. Chip-level floorplanning is then performed to find a floorplan in which compatible islands (islands with the same voltage) are likely to be adjacent. An island merging process is then applied to reduce the number of islands. At the end, island-level floorplanning is done to each newly formed island to shrink its area. The whole process is repeated until a satisfactory solution is obtained. The large search space made their approach relatively timing consuming. In one recent work [11], Lee *et al.* handled the voltage assignment problem under timing constraints by dynamic programming, and developed a power network aware floorplanner to generate floorplans with voltage islands after the voltage assignment step. Given a netlist represented by a directed acyclic graph (DAG), voltage assignment is first performed according to the timing requirements before the floorplanning step. Level shifters are then inserted into the nets according to the voltage assignment result. At last, a power-network aware floorplanner is invoked to pack the blocks such that the power-network resource, estimated as the sum of the half-perimeters of the voltage islands, will be minimized. As a result, blocks in the same voltage island will be placed close to each other. In their approach, the voltage assignment step and the floorplanning step are done separately.

There are other works addressing issues like reliability [21] and temperature reduction [9] in SoC voltage island partitioning and floorplanning.

#### 1.7 Contributions

In this thesis, we address the MSV driven floorplanning problem (definition 2 in section 1.5) in two stages, and propose two approaches to solve it.

In the first stage, we propose a floorplanning method for MSV designs that is tightly integrated with the island partitioning and voltage assignment steps. Simulated annealing is used with normalized Polish expression [18] as the floorplan representation. Normalized Polish expression is used because the slicing tree is a suitable data structure on which island partitioning and voltage assignment can be done *optimally and efficiently* given one slicing floorplan. Simulated annealing is adopted to perform the random search. In each step of the annealing process, a candidate floorplan solution is generated on which optimal island partitioning and voltage assignment will be performed simultaneously to compute the smallest possible power consumption for that candidate floorplan solution. This is done by dynamic programming with an efficient cost table update technique. In this way, we can integrate the three steps closely, and reduce the searching space (instead of doing voltage assignment by the "move" operations of the annealing process as

in [8]). In this floorplanning framework, we can also generate islands with power down mode to optimize the total power consumption further. Our floorplanner can be extended to consider the number of level shifters and the ease of power network routing (proximity to power pins and shapes of voltage islands). By using this approach, we can achieve significant power savings (up to 50%) for all data sets, without any significant increase in area and wire length.

In the second stage, we explicitly take timing requirements into account in the MSV driven floorplanning problem by proposing another framework, which is able to simultaneously optimize power consumption and physical layout of the circuit with the given timing constraints being satisfied. We will first show that the voltage assignment problem under timing constraints can be solved optimally under some conditions, i.e., given a netlist and a number of working voltage levels for each module, a specific voltage level can be assigned to each module on the netlist in such a way that maximum power saving can be achieved without violating the timing constraints, if a feasible solution exists. This problem can be solved optimally when the delay choices (each delay choice corresponds to a choice of the working voltage level) are continuous in the real or integer domain. We will present a general formulation of this voltage assignment problem as a set of linear inequalities to represent the timing requirements, with an objective to minimize the sum of the power cost in each cell. This problem can be transformed to a convex cost network flow problem [2], after applying the Lagrangian relaxation technique and can be solved optimally by a cost-scaling algorithm [7] in polynomial time. We can then make use of this method to obtain a feasible voltage assignment solution in which each module has just a discrete number of delay choices. Because of the short running time of this cost-scaling algorithm and, particularly, its capability of handling efficiently incremental changes on edge costs, we can embed this voltage assignment step in a simulated annealing based floorplanner, so that

power consumption and physical information can be taken into consideration simultaneously. We compared our approach with [11], the most updated previous work on this problem, on the data sets provided by the authors of [11]. Experimental results show that our approach performs much better than [11] in terms of both power saving and running time. An average of 24.61% (v.s. 6.68% by [11]) power saving can be achieved in an average running time of 273s (v.s. 1911s by [11]) with our approach on those data sets.

### 1.8 Thesis Organization

The remaining of this thesis is organized as follows. In chapter 2, a number of previous works addressing the voltage island generation problem in the floorplanning context are briefly discussed. A voltage island driven floorplanner is provided in chapter 3, and another floorplanning framework for MSV designs is proposed in chapter 4 to further take timing constraints into consideration. Finally, chapter 5 concludes this thesis.

□ End of chapter.

# Chapter 2

## **Literature Review on MSV**

### 2.1 Introduction

Voltage islands enable core-level power optimization for SoC designs by utilizing a unique supply voltage for each core. Architecting voltage islands involves island partition creation, voltage level assignment and floorplanning. The task of island partition creation and level assignment have to be done simultaneously in a floorplanning context due to the physical constraints involved in the design process. This leads to a floorplanning problem formulation that is very different from the traditional floorplan design. A number of previous works have addressed this problem. According to the design stage at which MSV is applied, these previous works basically fall into two categories.

### 2.2 MSV at Post-floorplan/Post Placement Stage

### 2.2.1 "Post-Placement Voltage Island Generation under Performance Requirement"

This work [19] considered power versus design cost trade-off for the post-placement voltage island generation problem.

In this paper, a candidate placement is viewed as a 2-D array, and the value at each entry of the array is set to be the square of the required working voltage level of the cell occupies the corresponding entry position. Let A be an  $m \times n$  array, and A[i][j] denotes the value of the element at position (i, j). A subarray  $A[l \dots r, b \dots u]$ is the rectangular region in A with (l, b) (resp. (r, u)) as the bottom-left (resp. upper-right) corner. A subarray is referred as a rectangle region. Let  $\mu(R) = \max_{(i,j)\in R} A[i][j]$  be the maximum value of all elements in a subarray rectangle R. The weight of a rectangle R is defined as

$$\omega(R) = \sum_{(i,j)\in R} (\mu(R) - A[i][j])$$

The weight of a rectangle *R* represents the power wastage resulted if rectangle *R* form a voltage island, since the cells in one voltage island are restricted to work at the same voltage level, which should be  $\sqrt{\mu(R)}$  as the voltage level assigned to a cell can not be lower than its required working voltage level.

A partitioning of A is a set of disjoint rectangles (subarrays)  $\Pi = \{R_1, R_2, \dots, R_k\}$ that cover A;  $k = |\Pi|$  is called the size of this partitioning. The weight of a partitioning  $\Pi$ , is defined as

$$\omega(\Pi) = \sum_{1 \le t \le k} \omega(R_t)$$

In their voltage island generation problem, they want to subdivide the placement region into a small number of voltage islands (where every cell in the same voltage island will eventually receive the same voltage), while keeping the total power consumption low.

They defined the Voltage-partitioning problem as follows:

**Definition 3 Voltage-partitioning Problem, or VPP** *Given an*  $m \times n$  *array* A *and an error threshold*  $\delta$ *, among all partitionings whose weight is at most*  $\delta$ *, find one with the smallest size. Let*  $\kappa(A, \delta)$  *be the size of this optimal partitioning.*

They also defined the dual version of VPP, or DVPP. The dual version of this problem (DVPP) is defined as the problem of minimizing the weight of the partitioning with a bound on the size.

They first the dual DVPP problem under the slicing model can be solved optimally by dynamic programming, then proposed an approximation approach to handle primal VPP by using binary search.

Let  $\omega_s^*(l \dots r, b \dots u)$  denote the minimum weight of any rectangle (subarray) Rin A with at most s sub-rectangles, where  $R = A[l \dots r, b \dots u]$ . The ultimate goal is to compute  $w_k^*(l \dots r, b \dots u)$ . At the base level, if s = 1, or if  $\omega(R) = 0$ , and  $\omega_s^*(l \dots r, b \dots u)$  is set as  $\omega(R)$ . Otherwise, the recursion can be written as follows:

$$\begin{split} \omega_s^*(l\dots r, b\dots u) &= \min_{1 \le t < s} \{ \\ \min_{l \le i < r \le j < u} \left\{ \begin{array}{l} \omega_t^*(l\dots i, b\dots u) + \omega_{s-t}^*(i+1\dots r, b\dots u), \\ \omega_t^*(l\dots r, b\dots j) + \omega_{s-t}^*(l\dots r, j+1\dots u) \end{array} \right\} \} \end{split}$$

The second minimization term enumerates all horizontal and vertical cuts, and the first term  $(1 \le t < s)$  enumerates all possible ways to assign the number of rectangles (t and s - t) for the two separated parts obtained by some horizontal or vertical cut.

This provides an optimal solution for the dual DVPP problem under the slicing model. Then, the approximation approach for the primal VPP problem under the

same model can be easily obtained by guessing the optimal number of rectangles  $\bar{k}$  in  $O(log\bar{k})$  time by a binary search, starting with  $\bar{k} = 1$ .

#### 2.2.2 "Post-Placement Voltage Island Generation"

Similar with the paper in the previous sub-section, this work [5] also targeted at minimizing the number of voltage islands generated on a candidate placement, while keeping the power wastage under a certain threshold. The main difference between this work and the previous one lies in that non-rectangular voltage islands are allowed in this work.

The non-rectangular voltage-partitioning problem (NVPP) is defined as follows:

**Definition 4 Non-rectangular Voltage-partitioning Problem, or (NVPP)** *Given an*  $m \times n$  *array* A *and an error threshold*  $\delta$ *, find a partitioning*  $\Pi$  *of connected regions whose weight*  $\omega(\Pi)$  *is at most*  $\delta$  *and the size*  $|\Pi|$  *is as small as possible.*

The input grid (the candidate placement) size  $m \times n$  is usually huge and it is inefficient to work on it directly. Therefore, they first coarsen the grid G to a size of O(N) where N is the number of cells, after which a new grid G' is obtained, where each cell in the original grid G belongs to one and only element of the new grid G'. At the second step, a tree T of the elements in the coarsened grid is built according to their adjacencies and their differences in power requirement. Basically, this is a bottom-up recursive clustering of G'. At each level, pairs of adjacent nodes are clustered to form a "super-node" at the next level according to the amount of power wastage incurred. The binary tree T is constructed to represent this multi-level clustering process, in which the leave nodes are the nodes in G' and the internal nodes are the super-nodes. Subsequently, a dynamic programming will be applied to partition this tree optimally into subtrees (each subtree will correspond to a connected region) such that the total power wastage is minimized. Since the NVPP also targeted at minimizing the number of voltage islands generated, this dynamic programming procedure starts with k = 1, where parameter k denotes the size of the partitioning. The procedure stops if the power wastage is below threshold  $\delta$ ; else, k is increased by 1 and the procedure is invoked again. Furthermore, this tree T will be reconstructed and partitioned repeatedly, so that the nodes can be redistributed among subtrees to refine the solution.

### 2.2.3 "Timing-Constrained and Voltage-Island-Aware Voltage Assignment"

This paper [20] is also a work on post-floorplanning voltage island generation. They present an approximation algorithm to produce an initial voltage assignment that meets timing, while considering proximity of high voltage cells on a candidate floorplan.

They formulate the voltage assignment problem as a delay budgeting problem, with the special objective of physical proximity. Based on the framework of a classic delay budgeting algorithm, the zero slack algorithm (ZSA), they design an algorithm to allocate delay budget and assign voltage to cells towards an objective of physical proximity.

ZSA iteratively assigns delay budget to non-critical cells in the circuit. At each iteration, it first computes the slacks of all cells and find the minimum positive slack  $s_{min}$ ; then it finds a path with this minimum positive slack, and distributes  $s_{min}$  evenly among the cells on the path. Then it updates the delay of these cells and go to the next iteration. The algorithm stops when the slacks of all cells become zero. They adopted the iterative framework of ZSA to solve the voltage assignment problem. The major difference lies in how the path slack is allocated among the cells on each selected path, since the physical proximity of the high voltage cells

has to be taken into consideration.

At first, they compute for each cell *c* the delay budget  $r_c$  it needs for voltage reduction. Let the slack of this cell be  $s_c$ . Those cells satisfying  $s_c < r_c$  will be assigned high voltage because they can not have any voltage reduction. Then at each iteration, for each cell *c* on the selected path, they calculate its distance to the closest high voltage cell, denoted as  $d_c$ . The larger this distance value is, the more likely it's sitting in a potentially non-critical low-voltage region, the more cost there is if this cell becomes a high voltage cell, thus, they give higher priority to it for voltage reduction. Therefore they sort all cells on the selected path with decreasing value of  $d_c$ , and allocate the path slack in the order of this sorted list, giving each cell the delay budget it needs for voltage reduction. If at certain cell in the list, the remaining slack is less than its needed delay budget, then it will be skipped and the next one is proceeded. The allocation stops when it reaches the end of the list, or when there is no more slack left. Such allocation guarantees that high voltage are always assigned to cells as close to the existing high voltage cells.

### 2.2.4 "Voltage Island Generation under Performance Requirement for SoC Designs"

In this work [16], they considered how to perform voltage island floorplanning with multiple supply voltages for SoC design.

In their approach, a few candidate floorplan solutions are first generated based on area and interconnect cost using an ordinary floorplanner, then voltage assignment and partitioning are performed on these candidate floorplans using the ILP approach to identify the best candidate solution. Therefore, this work actually belongs to the post-floorplanning voltage island generation category, although floorplanning has been considered in their framework. In their approach, the voltage assignment and island partitioning problem is formulated as a 0-1 integer linear program, when an input floorplan is given. They presented two formulations for the voltage assignment and voltage island generation problem. The first is exact but takes longer time to compute a solution. The second use some approximation techniques, and it can be solved much faster with insignificant sacrifice on solution quality. The goal of voltage level assignment is to reduce the total power consumption while controlling the level conversion area overhead and the power network complexity without compromising system performance. A fragmentation cost (number of adjacent cores operating at different voltages) is used to model the power network complexity when assigning working voltage levels to cores, but this cost is not related to the number of islands directly.

The separation between the floorplanning step and the voltage assignment step largely confined their solution quality. Besides, the ILP formulation made their approach relatively time consuming.

## 2.2.5 "An ILP Algorithm for Post-Floorplanning Voltage-Island Generation Considering Power-Network Planning"

In this paper [12], they presented a general formulation of this problem that considers level-shifter planning and power-network routing resources at post-floorplanning stage.

The problem inputs include a floorplan with a number of blocks, a netlist specifying the interconnections between the blocks, a timing constraint  $T_{cycle}$  such that the delay of the critical path in the netlist can not exceed  $T_{cycle}$ , a constant *l* that defines the relaxed block adjacency, and the legal working voltage levels of each block. The objective is to assign each block with an available supply voltage and insert necessary level shifters, such that the total power consumption and the total power-network routing resource are minimized, the total size of level shifters do not exceed the white space in the floorplan, and the timing constraint is satisfied.

They proposed a general problem formulation which considers level-shifter planning and power-network routing resource. Moreover, the cost function is dynamic in nature, since they do not have the information on the number of voltage islands during the optimization. To capture the block adjacency in a floorplan for voltage-island generation, they proposed a graph-based representation such that the number of nodes in the graph is linear to the number of blocks. To tackle the addressed problem, an ILP formulation was employed, in which they proposed (1) a box-growing wirelength estimation method to predict the timing overhead incurred by level shifters, (2) a set of linear voltage-island-clustering inequalities to avoid complicated constraint transformations, and (3) a set of linear inequalities to capture the usage of the power-network routing resource. Solving this ILP would give a solution to the problem addressed.

### 2.3 MSV at Floorplan/Placement Stage

### 2.3.1 "Architecting Voltage Islands in Core-based System-ona-Chip Designs"

In this paper [8], the authors addressed the problem of voltage islands planning for core-based SoC designs, which involves partitioning cores into several islands and floorplanning both at chip and island-level. A graph-based representation is used so that the partitioning and floorplanning steps are modeled in an integrated fashion.

Their approach is based on simulated annealing which guides the floorplanning and the island merging processes through a Voltage Island Compatibility Graph (VICG) graph G(V, E), a complete undirected graph which captures the current voltage island partitioning solution in an abstract way. Each vertex  $v_i \in V$  denotes

#### CHAPTER 2. LITERATURE REVIEW ON MSV

a voltage island, and each edge  $e_{ij}$  characterize the "attraction" between island  $v_i$ and island  $v_j$  by its weight, which is dependent on and interconnections between the two islands as well as their working voltage levels. In this way, the floorplanner can be guided in such a way that two compatible voltage islands (working at the same voltage level) with heavy interconnections are placed adjacently.

Given an initial voltage island partitioning and its associated floorplanning, the approach iteratively improves the solution quality by local perturbation, refloorplanning and islands merging. This perturbation is then reflected back to the corresponding VICG. Next, a chip-level floorplanning is applied with the goal of finding a floorplan where compatible islands are likely to be placed adjacently. The island merging process consists of detecting the regions that contain potentially mergeable islands, and eventually merging them. In order to shrink the area of these islands, an island-level floorplanning is applied to each of the newly merged islands with the goal of minimizing its bounding box. Finally, this new solution is evaluated and its costs calculated. The above process is repeated until a satisfactory solution is found. The cost function is a weighted sum of different metrics including the number of islands, average power consumption, and area overhead.

The solution perturbations during their annealing process contain island split move, island voltage change move, and multi-island voltage change move, which produce a large search space and thus make their approach quite timing consuming.

#### 2.3.2 "Voltage Island Aware Floorplanning for Power and Timing Optimization"

In this work [11], Lee *et al.* handled the voltage assignment problem under timing constraints by dynamic programming, and developed a power network aware floorplanner to generate floorplans with voltage islands after the voltage assignment step. In the following the approach of this paper is explained in more details, as we will mainly compare with this paper in chapter 4. Here is their problem formulation.

**Definition 5 Multi-Voltage Floorplanning [MVF] Problem** Given multiple supplyvoltage choices, a set of blocks, a netlist, a static-timing and a fixed-outline constraints, assign each block with a supply voltage and its coordinate in a floorplan so that the power consumption and the power-network resource requirement are minimized and both the static-timing and fixed-outline constraints are satisfied.

#### **Algorithm Flow**

The flow consists of three phases: (I)voltage assignment, (II) level-shifter (block) insertion, and (III) power-network aware floorplanning. For Phase I, they present a dynamic programming (DP) based method to solve the voltage assignment problem. As supply voltages are assigned to the circuit blocks in Phase I, they check in Phase II whether a net needs a level shifter and insert one as a soft block if needed. Finally in Phase III, they transform the precomputed slack into the wirelength constraint and perform floorplanning on all blocks, circuit blocks and level shifters (soft blocks), to minimize the power-network resource requirement. The floorplanning is based on simulated annealing (SA) using the  $B^*$ -tree floorplan representation [4].

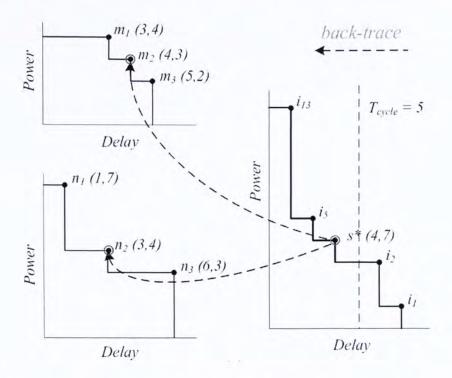

In Phase I, they first represent the netlist by a DAG, and then handle voltage assignment by dynamic programming (DP) on the DAG. Given a netlist without reconvergent fanouts, the DP can guarantee an optimal solution for the voltage assignment. Phase I contains mainly the following steps.

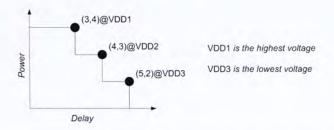

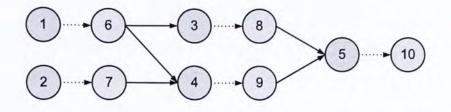

*Step 1. DP-curve initialization.* Represent the delay-power properties of a block as a Delay-Power-curve (DP-curve). DP-curve is a monotonic decreasing chain as shown in Figure 2.1.

Step 2. Joint Curve Generation. For an unvisited node in the DAG, they will

#### CHAPTER 2. LITERATURE REVIEW ON MSV

Figure 2.1: An Example DP-Curve (The three points of the DP-curve represent the delay-power characteristics of different supply voltages)

calculate the joint curve of this node and each of its fanins, after which a set of joint curves will be generated.

Step 3. Lower-Bound Merge Operation. During this step the set of previously generated joint curves will be merged into one curve.

Step 4. Redundant Point Pruning. After all the points on the DP-curve have been produced after the merging operation, a pruning procedure will be employed to delete those redundant points which are dominated by others in terms of both power and delay, so that a monotonic decreasing DP-curve can be obtained for the node that is currently visited.

*Step 5. Solution Backtracing.* Having generated the new accumulative DPcurve at POs, they trace a netlist to get an good solution of voltage assignment. Among all the points that satisfy the timing constraints in the accumulative DPcurve at a PO, the one with lowest power consumption will be chosen, so the delay and power of the whole circuit will be determined. Consequently, they repeat tracing solutions until PIs to assign a voltage level for each core.

In the Phase II of their algorithm flow, level shifters are inserted into a net that connects two blocks in different power domains. After voltage assignment, they trace the circuits from PI's to PO's to search the nets that need level shifters by

Figure 2.2: The backtracing procedure in [11] for getting a solution

breadth-first search. Those level shifters are treated as soft blocks during floorplanning stage.

In Phase III, they conduct power-network aware floorplanning for the original hard blocks and the additional level-shifter (soft) blocks together to make the critical paths satisfy the timing constraint. The objective in this phase is to find a floorplan which simultaneously minimizes the power-network resource requirement and satisfies the timing and the fixed-outline constraints. During the annealing process of floorplanning, they adopted the following cost function to minimize the powernetwork resource without violating the constraints.

$\Phi(T) = \alpha \Phi_{PNR} + (1 - \alpha) \Phi_{area} + \Phi_{timing} + \Phi_{outline}$

where  $\Phi_{PNR}$  denotes the cost of power-network resource,  $\Phi_{area}$  is the area of the floorplan, and  $\alpha$  is a weighting factor.  $\Phi_{timing}$  and  $\Phi_{outline}$  are the penalty for timing and outline violation, respectively.

#### CHAPTER 2. LITERATURE REVIEW ON MSV

Figure 2.3: A reconvergent structure in the netlist

This paper proposed a reasonable design flow, however, their solution quality suffers in several aspects. First of all, the optimality of its voltage assignment step can only be guaranteed when there are no reconvergent structures in the netlist, but there are surely many of such structures in real circuits, which can significantly worsen the quality of their voltage assignment result. Fig. 2.3 shows an example of a reconvergent structure, in which the signals emanating from vertex one reconverges at vertex four, after traversing two disjoint paths. Secondly, physical information is not taken into account while performing the voltage assignment step. Lastly, the length of an interconnect is restricted to stay within a certain range during floorplanning in order to satisfy the timing constraints, which may degrade the solution quality.

## 2.4 Summary

In these previous works, MSV is considered at various design stages, including the floorplanning and placement stages [8], [11], and the post-floorplanning and post-placement stages [5], [12], [16], [19], [20]. For the latter category, Wu *et al.* [19] and Ching *et al* [5] targeted at minimizing the number of voltage islands generated, and Mak *et al.* [16] formulated the voltage assignment and island generation problem as an *integer linear program* (ILP). The other two works also considered timing. In [20], Wu *et al.* proposed an approximation algorithm based on a *zero*

*slack algorithm* to minimize the power cost and to simplify the power network resource under timing constraints; Lee *et al.* [12] tackled the voltage assignment problem using an ILP based approach with a set of linear inequalities representing the timing requirements. An inevitable deficiency of all these post-floorplanning and post-placement works is that physical layout and power optimization are done separately, hence the solution quality is restricted to a certain extent. Concurrent physical layout and power optimization will be much more favorable. In [11], voltage islands are generated during floorplanning, however, the voltage assignment step is done prior to floorplanning, which largely restricted their solution quality. Hu *et al.* [8] considered this simultaneous voltage assignment, voltage island generation, and floorplanning problem, however, the large solution space of their approach rendered their approach quite time consuming, besides, they didn't explicitly considered timing in their problem formulation.

### □ End of chapter.

## **Chapter 3**

## **MSV Driven Floorplanning**

The content of this chapter is included in the proceedings of *IEEE/ACM International Conference of Computer-Aided Design (ICCAD)* 2007 [14].

## 3.1 Introduction

Energy efficiency has become one of the most important issues to be addressed in today's System-on-a-Chip (SoC) designs because of the increasing power density and the wide use of portable systems. There are two kinds of power consumption: dynamic and leakage. Dynamic power is caused by the charging and discharging of the load capacitance during switching. Leakage power is due to the sub-threshold currents when a device is turned off. There are many techniques to reduce power consumption. One of the most effective methods is by lowering the voltage supply. Multi-voltage design is thus introduced to provide "just enough" power to support different functional operations. Both dynamic and leakage power consumption can be reduced in multi-voltage designs. For dynamic power, since the consumption is proportional to the square of the voltage, a minor adjustment to the voltage level can result in a significant reduction. For leakage power, the

consumption can be reduced by powering down parts of a chip when the functions are inactive.

Multi-voltage designs involve the partitioning of a chip into areas called "voltage islands" that can be operated at different voltage levels, or be turned off when idle. With the use of voltage islands, the chip design process is becoming more complicated. We need to solve the problems of island partitioning, voltage assignment and floorplanning simultaneously under area, power, timing and other physical constraints. These problems must be solved at the same time since their results will significantly affect each other. In addition, there are other issues to be considered. For example, the voltage islands should be placed close to the power pins in order to minimize the power routing complexity and the IR drop. Besides, each island requires level shifters to communicate with others and overhead in area and delay will be resulted. These additional issues have created many new challenges in generating floorplans for designs using voltage islands. An example is shown in Figure 3.1. In this example, the possible voltage levels of each core and groupings of similar inactive periods (to generate islands with power down mode) are shown on the right hand side. Assuming that the number of islands is three, one possible partitioning is to group cores A, B and C as one island operating at voltage 1.0V, core D on its own as one island at voltage 1.5V and cores I, K, L and M as one island at 1.2V. Notice that other cores will be operated at the chip-level voltage and the island containing I, K, L and M can be powered down during sleep. A candidate floorplan solution for such a partitioning and voltage assignment is shown on the left hand side.

In this chapter, we propose a floorplanning method for SoC designs that is tightly integrated with the island partitioning and voltage assignment steps. Simulated annealing is used with normalized Polish expression [18] as the floorplan representation. Normalized Polish expression is used because the slicing tree is

Figure 3.1: An example of the voltage island driven floorplanning problem

a suitable data structure on which island partitioning and voltage assignment can be done optimally and efficiently given one slicing floorplan. Note that the restricted use of slicing floorplan can also give satisfactory results since many input cores have flexibilities in shape at this stage. Simulated annealing is adopted to perform the random search. In each step of the annealing process, a candidate floorplan solution is generated on which optimal island partitioning and voltage assignment will be performed simultaneously to compute the smallest possible power consumption for that candidate floorplan solution. This is done by dynamic programming with an efficient cost table update technique. In this way, we can integrate the three steps closely, and reduce the searching space (instead of doing voltage assignment by the "move" operations of the annealing process as in [8]). In this floorplanning framework, we can also generate islands with power down mode to optimize the total power consumption further. Our floorplanner can be extended to consider the number of level shifters and the ease of power network routing (proximity to power pins and shapes of voltage islands). By using this approach, we can achieve significant power savings (up to 50%) for all data sets, without any significant increase in area and wire length.

We will define the problem in section 3.2, then the methodology used will be

discussed in section 3.3. Experimental results will be reported in section 3.6 before the conclusion and discussion in the last section.

#### 3.2 Problem Formulation

In this problem, we are given a set of *n* cores with areas  $A_1, A_2...A_n$  and aspect ratio bounds  $[l_i, u_i]$  for i = 1...n. Each core *i* is associated with a power table  $T_i$ that specifies the legal voltage levels for the core and the corresponding average power consumption values. The power table of a core can be characterized by a core designer. For example, they can run simulations that try applying different supply voltages to the core, and a voltage level will be regarded as a legal one as long as the timing assertion can be satisfied [8]. We assume that the given voltage levels of each core can meet timing, so we do not consider timing explicitly in our formulation. The power consumption corresponding to each legal voltage can then be estimated. In this work, we compute the power cost of a core *i* operated at voltage v as  $v^2A_i$ . We are also given a set of *m* nets  $\{N_1, N_2...N_m\}$  and a set of groupings  $\{G_1, G_2...G_p\}$  between the cores such that the cores in each group  $G_i$ have similar inactive periods and will have a  $s_i$ % saving in power consumption if they are grouped together as an island with power down mode.

Given a constant K and a chip-level voltage  $V_c$ , our goal is to generate a floorplan F with K rectangular voltage islands so that the total power consumption is minimized. Each island will be supplied with the lowest possible voltage level common to all the cores in that island while the remaining cores not assigned to any island will be operated at the chip-level voltage. Islands containing blocks all belonging to the same group  $G_i$  can have a further reduction in power consumption by  $s_i$ % by shutting it down during sleep.

## 3.3 Algorithm Overview

Our floorplanner is based on simulated annealing using normalized Polish expression (NPE) as the representation. For each candidate floorplan solution represented by an NPE, we will perform an optimal island partitioning and voltage assignment to maximize the total power saving. The cost function of the annealing process is to minimize a weighted sum of the area, wire length and power. We can also extend our floorplanner to consider level shifters and proximity to power pins. Details will be given in the following sections.

## 3.4 Optimal Island Partitioning and Voltage Assignment

Given a candidate floorplan solution represented by a normalized Polish expression, we can construct the corresponding slicing tree and perform optimal island partitioning and voltage assignment on it. This can be done efficiently by dynamic programming. The pseudo code is shown below:

#### **Pseudocode** *TreePart(u, k)*

// Partition the subtree under node u into k subtrees to

// minimize the total power consumption such that the cores

// (leaf nodes) in each of these k subtree will form one island

// operated at one common voltage possibly with power down

// mode while the remaining cores not belonging to any of

// these k subtrees will be operated at the chip level voltage V<sub>c</sub>

- 1.  $min\_cost = \infty$

- 2. If k is 0, return(power(u)).

#### CHAPTER 3. MSV DRIVEN FLOORPLANNING

- 3. If cost\_table[u][k] is updated, return(cost\_table[u][k]).

- 4. If k is 1,

- 5.  $C_1 = TreePart(lchild(u), 1) + power(rchild(u))$

- 6.  $C_2 = TreePart(rchild(u), 1) + power(lchild(u))$

- 7.  $C_3 = nonSubtree(u, 1)$

- 8.  $C_4 = cost(\{u\})$

- 9.  $min\_cost = min\{C_1, C_2, C_3, C_4\}$

- 10. Store min\_cost into cost *stable*[u][1].

- 11. Return (min\_cost).

- 12. Else

- 13.  $min\_cost = nonSubtree(u,k)$

- 14. For i = 0 to k

- 15. C = TreePart(lchild(u), i) +TreePart(rchild(u), k - i)

- 16. If  $min\_cost > C$ ,  $min\_cost = C$

- 17. Store min\_cost into cost table[u][k].

- 18. Return(min\_cost).

At the beginning, TreePart(root, K) is called to obtain an optimal island partitioning and voltage assignment of the whole floorplan, where *root* is the root of the slicing tree corresponding to the normalized Polish expression under consideration and K is the number of voltage islands we want to produce. When k is zero (line 2), no voltage island is formed in the subtree of u, so the power consumption power(u) will be computed as  $(V_c)^2 A_{\{u\}}$ , where  $V_c$  is the chip-level voltage and  $A_{\{u\}}$  is the total area of the cores in the subtree of u. For non-zero k, we will first check whether this optimal cost has been computed before and is available in the table for immediate return (line 3). If this value is not available, we will consider the situations when k is one and when k is larger than one separately. When kis one (line 4), there are four cases: case 1 (line 5), we continue to search for a voltage island in the left subtree of u and let the right subtree operates at the chiplevel voltage  $V_c$ ; case 2 (line 6), similarly, we look for a voltage island in the right subtree of u and let all the cores in the left subtree work at  $V_c$ ; case 3 (line 7), use the function nonSubtree() to group the cores across a number of subtrees along the left tree branches of u into a voltage island (details will be given in the next sub-section); case 4 (line 8), the entire subtree u is regarded as one voltage island and the power consumption  $cost(\{u\})$  will be computed as  $(v_{\{u\}})^2 A_{\{u\}}$ , where  $v_{\{u\}}$ is the smallest common voltage among all the cores in the subtree rooted at u and  $A_{\{u\}}$  is the total area of the cores in the subtree rooted at u. We will compute the costs of the four cases respectively, and the smallest one will be returned and recorded in the table for future use. When k is more than one (line 12), we will recursively call the procedure TreePart() to exhaust all the possible partitionings of the subtree of u, including both inter-subtree partitionings (line 13) and intrasubtree ones (line 14-16). The minimum one will be returned and recorded in the table.

#### 3.4.1 Voltage Islands in Non-subtrees

Notice that a voltage island (a rectangular region) may be formed by a set of contiguous right subtrees linked by internal nodes of the same operational type. An example is shown in Figure 3.2. Therefore, we need the procedure *nonSubtree()* to enumerate these cases. The pseudo code of *nonSubtree()* is shown in the following. In this procedure, we exhaust all the cases of forming one island with two or more contiguous right subtrees and the one with the smallest power consumption will be returned. On line 7, we compute the cost of grouping the right subtrees in S as one island and having the remaining k - 1 islands in the last left subtree (subtree

#### D in the example of Figure 3.2).

#### **Pseudocode** *nonSubtree*(*u*, *k*)

// Exhaust the cases of forming one island by a number // of contiguous right subtrees, while the remaining k - 1// islands are formed in the remaining left subtree.

- 1.  $min\_cost = \infty$

- 2. S = rchild(u)

- 3. op = operator(u)

- 4. While operator(lchild(u)) is op,

5.

$$u = lchild(u)$$

- 6.  $S = S \cup rchild(u)$

- 7. C = TreePart(lchild(u), k-1) + cost(S)

- 8. If  $min\_cost > C$ ,  $min\_cost = C$

- 9. Return(min\_cost).

### 3.4.2 Proof of Optimality

The procedure *TreePart()* will give the optimal partitioning to minimize the total power consumption. Given a candidate floorplan solution represented by a normalized slicing tree rooted at u and the number of voltage islands required k, *TreePart()* will exhaust all the possible cases recursively and return the best solution. When k is zero, there is only one case that all the cores in the tree rooted at u(called  $T_u$ ) are operated at the chip voltage. When k is one, there is only one voltage island among all the cores in  $T_u$ . Three of the cases are obvious: (1) the island is in the left subtree of u, (2) the island is in the right subtree and (3) all the cores

A, B and C, not in one subtree, can form one voltage island.

Figure 3.2: An example of forming an island across subtrees