## Logic Perturbation Based Circuit Partitioning and Optimum FPGA Switch-Box Designs

#### CHEUNG Chak Chung

A Thesis Submitted in Partial Fulfillment of the Requirements for the Degree of Master of Philosophy

in

Computer Science and Engineering

©The Chinese University of Hong Kong June, 2001

The Chinese University of Hong Kong holds the copyright of this thesis. Any person(s) intending to use a part or the whole of the materials in this thesis in a proposed publication must seek copyright release from the Dean of the Graduate School.

## Abstract

In this thesis, a framework which integrates an efficient Graph-Based Alternative Wiring (GBAW) technique and state-of-the-art Multi-level hypergraph partitioner (hMETIS-Kway) for multi-way circuit partitioning is proposed. Moreover, the routability of Hyper-Universal Switch Box is examined by reconfiguring the switch-box architecture of well-known Field-Programmable Gate Arrays (FPGAs) router VPR.

Efficient circuit partitioning is gaining more and more importance with the increasing size of modern circuits. Conventionally, circuit partitioning is solved without altering the circuit by modeling a circuit as a hypergraph for the ease of applying graph algorithms. However, there exists rooms for further improvement on even optimum hypergraph partitioning results, if logic information can be applied for circuit perturbation. Such logic transformation based partitioning techniques are usually more complicated and harder to formulate. A multi-way partitioning framework which can couple any hypergraph partitioner is presented. This framework gives a novel logic perturbation technique for further improvement over very excellent partitioning results. This approach can integrate with any graph partitioner. Experiments on 2-, 3-, 4-, and 5-way partitionings for various circuits of different sizes from MCNC benchmarks were performed. The experimental results showed that this partitioning approach can achieve a further 15% reduction in cut size for 2-way partitioning with an area penalty of only 0.33% over existing state-of-the-art graph partitioner.

An FPGA switch box is said to be universal (hyper-universal) if detailed routing can be performed on all possible surrounding 2-pin (multi-pin) net topologies which satisfy the global routing density constraints. A switch box is optimum if it is hyper-universal and the switches inside is minimum. It has been shown that if the net topology is restricted to 2-pin nets, then a 2-D (4way) switch box can be built to be universal with only 6W switches, where Wis the global routing channel density. A previous work has constructed a formal mathematical model of this optimum design problem for switch boxes with arbitrary dimensions, and given a scheme to produce hyper-universal designs with less than 6.7W switches for 4-way FPGA switch boxes. The investigation of the most common 4-way switch box case is presented, and gives new theoretical results followed by extensive experimental justification. It is shown that such an optimum switch box can be built with a very low number of additional switches beyond 6W for today's practical range of low W (e.g. just 6W plus 1 or 2 additional switches for W up to 7). Even for arbitrary large W, the bound can be shown to be under 6.34W. To make experimental comparison, experiments are conducted by running today's published best FPGA router VPR on large benchmarks for the popular disjoint structure and the proposed designs. The results are quite encouraging.

#### 摘要

作者:張澤松

本論文主要對快速「基於圖像可替換線檢驗算法」和著名多層超圖分割規劃法所結合建成的結構,以及對新提出的「超全體開關盒」在著名的現場可編程門陣列佈線程序器的可佈線性作出研究。

由於有電路的數目大大增加,所以分割規劃需要更有效率的算法。首先,電路會被造型成超圖,然後利用圖算法去解決電路分割規劃問題,而且當中沒有對電路作出修改。如果把電路的邏輯資料作出電路擾亂,即使是最佳的超圖分割規劃結果仍然可獲得改進。這種基於邏輯轉換分割規劃法的技術通常是比較複雜,而且很困難用公式表示出來。本論文介紹一個可以和任何超圖分割規劃法結合的多路分割規劃法結構。這結構提供一個新穎的電路擾亂技術並從極好的分割規劃結果中獲得改進。這方法更可以和其他圖分割規劃器結成一體。二路、三路、四路和五路的超圖分割規劃實驗在不同大小的基準電路上,把實驗結果和著名的圖分割規劃法在二路分割結果上的比較,這分割規劃方法可以取得百分之十五的分割成本減少,但只是增大了百分之零點三三的面積。實驗結果證明了這多層超圖分割規劃法和圖像可替換線檢驗算法的共同合作效力。

在現場可編程門陣列中,全體「超全體」的開關盒是指能夠令所有兩端腳「多端腳」線在乎合全局佈線密度限制的情況下,都能詳細地佈線出來。一個最優良的開關盒必須是「超全體的」以及使用的切換線數目爲最少。當網絡拓樸被局限於兩端腳時,只需要用六倍全局佈線通道密度(簡稱「密度」)的切換線便可建成一個兩維「四向」的超全體的開關盒。一個早前的研究已經把數學模型去解決超全體開關盒在任何維數的最優化問題,而且,還有提出了一個少於六點七倍密度的切換線的超全體開關盒設計在四向的現場可編程門陣列的開關盒上。本論文介紹了最普遍的四向開關盒的研究和新理論性的結果及其廣泛的實驗證明。而且一個最佳的開關盒只需要很少數目的附加切換線在現今實際最少的六倍密度上(例如:在佈線路線密度等於七的時候,只需要在六倍密度上加一至兩條附加切換線)。甚至在大的佈線路線密度上,切換線的上限只低於六點三四倍的密度。爲了作出比較,選擇現今發表了最佳的現場可編程門陣列的佈線器,這個新設計及解體的開關盒分別在大型的基準電路上作出實驗和比較,而且結果令人鼓舞。

## Acknowledgments

First of all, I would like to express my greatest gratefulness to my supervisor, Professor David Yu-liang Wu for his invaluable suggestions and comments on different research topics. His support and guidance in the past two years helped me to work in the right direction in academic area and social issues. I am greatly impressed by his working style which work hard and never give up. I learnt "nothing is impossible to achieve". I would also like to thank for his support and arrangement for the study in Chip Implementation Center (CIC), Taiwan 2000 summer. Moreover, I acquired lot of experiences and gained interests in Computer-Aided Design automation through our discussions.

I greatly appreciate the members of my dissertation committee, Professor Philip Heng-wai Leong, Professor Kin-hong Wong and Professor Hong-bing Fan for their useful feedback and suggestions. I would like to specially thank my final year supervisor, Professor Philip Heng-wai Leong for introducing me to Professor David Yu-liang Wu and teaching me in hardware design. I am greatly indebted to Dr. David Ihsin Cheng, Professor Hong-bing Fan and Professor Jiping Liu for the collaboration works with them. I would also like to thank Professor Chak-kuen Wong and Professor Evangeline Fung-yu Young for their advice and courses which enriched my background knowledge.

I would also like to thank my research partner Mr. Cliff Chin-ngai Sze for his encouragement and collaboration work on the development of GBAW. I would like to show my appreciation to Dr. Xao-long Yuan for his assistance in my research work.

Many thanks go to Professor George Karypis of University of Minnesota and the authors of METIS and Professor Jonathan Rose of University of Toronto and the authors of VPR for their prominent works on Partitioning and FPGA Routing.

Thanks also go to my marvelous friends in Room 1026 who helped me to solve many problems and made my life more enjoyable and unforgettable. Especially, I would express my appreciation to Mr. Ivan Ka-ho Leung, Mr. Hiu-yung Wong, Miss Wing-seung Yuen, Mr. Norris Monk-ping Leong and Miss Polly Po-man Wan for their frank warm-hearted help. I would like to thank for all the friends who help me and make my life more colorful.

My unplumbed gratitude goes to my parents, sister and brother-in-law for their endless love and encouragement and my aunt Kit-chi Wong for her support and understanding. Last but not least, I would express my love to my best friend, Miss Victoria Chor-kiu Lee for her sacrifices and patience. They all brought untold happiness to my life.

#### VITA

May 23, 1977 Born, Fujian, China

#### Education

B.Eng. in Computer Engineering, The Chinese University of Hong Kong

#### **Publications**

P.K. Tsang, C.C. Cheung, K.H. Leung, T.K. Lee and P.H.W. Leong, "An Asynchronous Forth Microprocessor", Proceedings of the IEEE Region 10 Conference (TENCON), Vol. 2, pp. 1079-1082, 1999.

Y.L. Wu, C.N. Sze, **C.C. Cheung**, "On Improved Graph-Based Alternative Wiring Scheme for Multi-Level Logic Optimization", IEEE International Conference of Electronics Circuits and Systems (ICECS), 2000.

C.C. Cheung, Y.L. Wu, and D. Ihsin Cheng, "Further Improve Circuit Partitioning using GBAW Logic Perturbation Techniques" Proceedings of IEEE Design Automation and Test in Europe (DATE), pp. 233-239, March. 2001. Munich.

H.B. Fan, J. Liu, Y.L. Wu, and C.C. Cheung, "On Optimum Switch Box Designs for 2-D FPGAs" to appear in Proceedings of IEEE/ACM Design Automation Conference (DAC). June. 2001. Las Vegas.

Y.L. Yu, C.C. Cheung, D. Ihsin Cheng and H.B. Fan, "Further Improve Circuit Partitioning using GBAW Logic Perturbation Techniques" under review of IEEE Transactions on Very Large Scale Integration Systems (TVLSI).

# Contents

| A  | bstra  | ct     |                      |     |   |      |   |   |  |   |   |   |   |   |   |   |   |   | i   |

|----|--------|--------|----------------------|-----|---|------|---|---|--|---|---|---|---|---|---|---|---|---|-----|

| A  | cknov  | wledgn | nents                |     |   |      |   |   |  |   |   |   |   |   |   |   |   |   | iii |

| V  | ita    |        |                      |     |   |      |   |   |  |   |   |   |   |   |   |   |   |   | v   |

| Ta | able o | of Con | tents                |     |   |      |   |   |  |   |   |   |   |   |   |   |   |   | vi  |

| Li | st of  | Figure | es                   |     |   |      |   |   |  |   |   |   |   |   |   |   |   |   | x   |

| Li | st of  | Tables | 5                    |     |   |      |   |   |  |   |   |   |   |   |   |   |   |   | xiv |

| 1  | Intr   | oducti | ion                  |     |   |      |   |   |  |   |   |   |   |   |   |   |   |   | 1   |

|    | 1.1    | Motiv  | ation                | ٠.  |   |      |   |   |  |   |   | ٠ | · |   | • |   |   |   | 1   |

|    | 1.2    | Aims   | and Contribution .   |     |   |      |   |   |  |   |   |   |   |   |   |   |   |   | 4   |

|    | 1.3    | Thesis | Overview             |     |   |      |   | ٠ |  |   |   | • |   |   |   | • |   |   | 5   |

| 2  | VL     | SI Des | ign Cycle            |     |   |      |   |   |  |   |   |   |   |   |   |   |   |   | 6   |

|    | 2.1    | Logic  | Synthesis            |     | • |      |   |   |  | • | • |   |   |   |   | • | ٠ |   | 7   |

|    |        | 2.1.1  | Logic Minimization   | n . |   |      | 3 | • |  | , |   |   | ٠ | ٠ |   |   | • | ÷ | 8   |

|    |        | 2.1.2  | Technology Mapp      | ing |   |      |   |   |  |   |   |   |   | • |   |   |   |   | 8   |

|    |        | 2.1.3  | Testability          |     |   |      |   |   |  |   |   |   | • |   |   |   |   |   | 8   |

|    | 2.2    | Physic | cal Design Synthesis | s . | • |      |   |   |  |   |   |   |   | • |   | • |   |   | 8   |

|    |        | 2.2.1  | Partitioning         |     |   | <br> |   |   |  |   |   |   |   |   |   |   |   |   | 9   |

|   |      | 2.2.2                      | Floorplanning & Placement                  | 0  |  |  |  |  |  |  |  |  |  |  |  |  |

|---|------|----------------------------|--------------------------------------------|----|--|--|--|--|--|--|--|--|--|--|--|--|

|   |      | 2.2.3                      | Routing                                    | 1  |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 2.2.4                      | Compaction, Extraction & Verification      | 2  |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 2.2.5                      | Physical Design of FPGAs                   | 2  |  |  |  |  |  |  |  |  |  |  |  |  |

| 3 | Alte | ernativ                    | ve Wiring 1                                | 3  |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.1  | Introd                     | uction                                     | 3  |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.2  | Notati                     | ion and Definitions                        | 5  |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.3  | Applio                     | cation of Rewiring                         | 7  |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 3.3.1                      | Logic Optimization                         |    |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 3.3.2                      | Timing Optimization                        | 7  |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 3.3.3                      | Circuit Partitioning and Routing           |    |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.4  | Logic                      | Optimization Analysis                      | 9  |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 3.4.1                      | Global Flow Optimization                   | 9  |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 3.4.2                      | OBDD Representation                        | 0  |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 3.4.3                      | Automatic Test Pattern Generation (ATPG) 2 | 2  |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 3.4.4                      | Graph Based Alternative Wiring (GBAW)      | 13 |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.5  |                            |                                            |    |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.6  | Optimization by using GBAW | 8                                          |    |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.7  |                            | usions                                     |    |  |  |  |  |  |  |  |  |  |  |  |  |

| 4 | Mu   | lti-way                    | Partitioning using Rewiring Techniques 3   | 3  |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 4.1  | Introd                     | luction                                    | 3  |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 4.2  | Circu                      | it Partitioning Algorithm Analysis         | 8  |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 4.2.1                      | The Kernighan-Lin (KL) Algorithm           | 9  |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 4.2.2                      | The Fiduccia-Mattheyses (FM) Algorithm 4   | 2  |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 4.2.3                      | Geometric Representation Algorithm         | 6  |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 4.2.4                      | The Multi-level Partitioning Algorithm     | 9  |  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 4.2.5                      | Hypergraph METIS - hMETIS                  | 1  |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 4.3  | The C                      | BAW Partitioning Algorithm                 | 3  |  |  |  |  |  |  |  |  |  |  |  |  |

|   | 4.4 | Experimental Results                                                   |

|---|-----|------------------------------------------------------------------------|

|   | 4.5 | Conclusions                                                            |

| 5 | Opt | mum FPGA Switch-Box Designs - HUSB 62                                  |

|   | 5.1 | Introduction                                                           |

|   | 5.2 | Background and Definitions                                             |

|   |     | 5.2.1 Routing Architectures 65                                         |

|   |     | 5.2.2 Global Routing                                                   |

|   |     | 5.2.3 Detailed Routing                                                 |

|   | 5.3 | FPGA Router Comparison                                                 |

|   |     | 5.3.1 CGE                                                              |

|   |     | 5.3.2 SEGA                                                             |

|   |     | 5.3.3 TRACER                                                           |

|   |     | 5.3.4 VPR                                                              |

|   | 5.4 | Switch Box Design                                                      |

|   |     | 5.4.1 Disjoint type switch box (XC4000-type) 73                        |

|   |     | 5.4.2 Anti-symmetric switch box                                        |

|   |     | 5.4.3 Universal Switch box                                             |

|   |     | 5.4.4 Switch box Analysis                                              |

|   | 5.5 | Terminology                                                            |

|   | 5.6 | Hyper-universal $(4, W)$ -design analysis 82                           |

|   |     | 5.6.1 $H_3$ is an optimum $(4,3)$ -design                              |

|   |     | 5.6.2 $H_4$ is an optimum $(4,4)$ -design                              |

|   |     | 5.6.3 $H_i$ is a hyper-universal $(4, i)$ -design for $i = 5, 6, 7$ 90 |

|   | 5.7 | Experimental Results                                                   |

|   | 5.8 | Conclusions                                                            |

| 6 | Con | clusions 99                                                            |

|   | 6.1 | Thesis Summary                                                         |

|   | 6.2 | Future work                                                            |

| 6.2.1                                               | Alternative Wiring                      | . 100 |  |  |  |  |  |  |  |  |  |  |  |  |

|-----------------------------------------------------|-----------------------------------------|-------|--|--|--|--|--|--|--|--|--|--|--|--|

| 6.2.2                                               | Partitioning Quality                    | . 100 |  |  |  |  |  |  |  |  |  |  |  |  |

| 6.2.3                                               | Routing Devices Studies                 | . 100 |  |  |  |  |  |  |  |  |  |  |  |  |

| Bibliography                                        |                                         |       |  |  |  |  |  |  |  |  |  |  |  |  |

| A 5xp1 - B                                          | erkeley Logic Interchange Format (BLIF) | 115   |  |  |  |  |  |  |  |  |  |  |  |  |

| B Proof of some 2-local patterns                    |                                         |       |  |  |  |  |  |  |  |  |  |  |  |  |

| C Illustrations of FM algorithm                     |                                         |       |  |  |  |  |  |  |  |  |  |  |  |  |

| D HUSB S                                            | tructures                               | 127   |  |  |  |  |  |  |  |  |  |  |  |  |

| E Primitive minimal 4-way global routing Structures |                                         |       |  |  |  |  |  |  |  |  |  |  |  |  |

# List of Figures

| 1.1  | Moore's Law vs Industrial CPU size (from Intel)         |

|------|---------------------------------------------------------|

| 2.1  | The Path to Silicon Chip                                |

| 2.2  | VLSI Physical Design Cycle                              |

| 2.3  | Example of Bi-partitioning                              |

| 2.4  | Example of Floorplanning                                |

| 2.5  | Example of Channel Routing                              |

| 2.6  | Example of Compaction                                   |

| 3.1  | Example of alternative wiring                           |

| 3.2  | Configuration of a sub-network                          |

| 3.3  | Example of Timing Optimization by alternative wiring 18 |

| 3.4  | Example of Circuit Partitioning                         |

| 3.5  | Example of Routing                                      |

| 3.6  | Example of Global Flow Optimization                     |

| 3.7  | Flow graph for the circuit in 3.6                       |

| 3.8  | Result of fanout re-connections                         |

| 3.9  | OBDD representing $f = x1 \cdot x2 + x3$                |

| 3.10 | 0-local pattern in GBAW                                 |

| 3.11 | 1-local patterns in GBAW                                |

| 3.12 | 2-local patterns in GBAW                                |

| 3.13 | Example of one 2-local Pattern Verification             |

| 3.14 | The Logic Optimization Process by GBAW and SIS 30       |

| 4.1  | Circuit partitioning by rewiring                                    | 35 |

|------|---------------------------------------------------------------------|----|

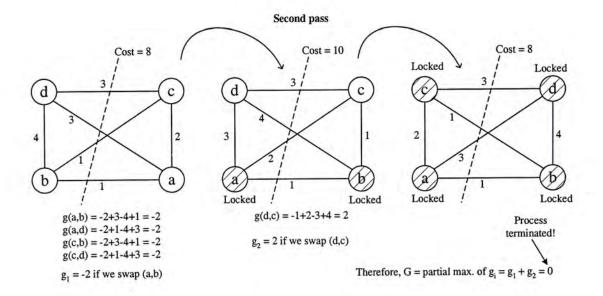

| 4.2  | Example of KL algorithm - First pass                                | 42 |

| 4.3  | Example of KL algorithm - Second pass                               | 42 |

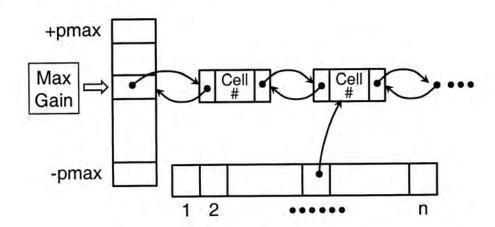

| 4.4  | Bucket list structure                                               | 44 |

| 4.5  | Example of FM algorithm - Initial & Final                           | 45 |

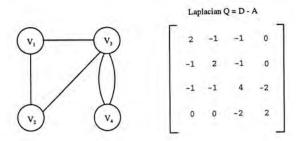

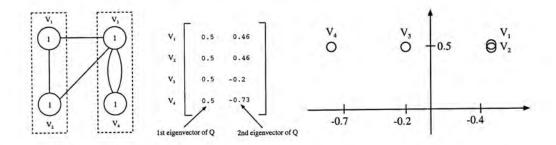

| 4.6  | A simple graph and its Laplacian                                    | 48 |

| 4.7  | Result of spectral partitioning and linear ordering of the vertices |    |

|      | using the second eigenvector                                        | 48 |

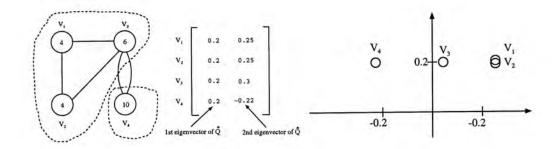

| 4.8  | Result of spectral partitioning by using the modified Laplacian     |    |

|      | $\hat{Q}$ which incorporates the actual vertex size information     | 49 |

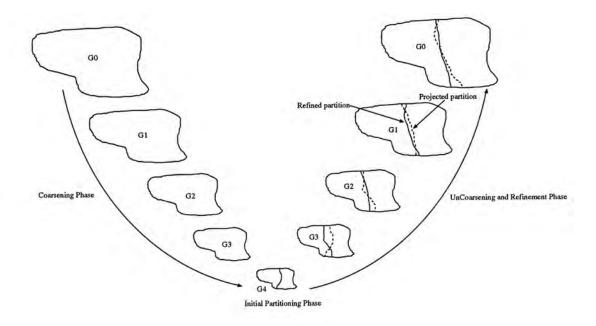

| 4.9  | The various phases of the Multi-level graph bisection               | 50 |

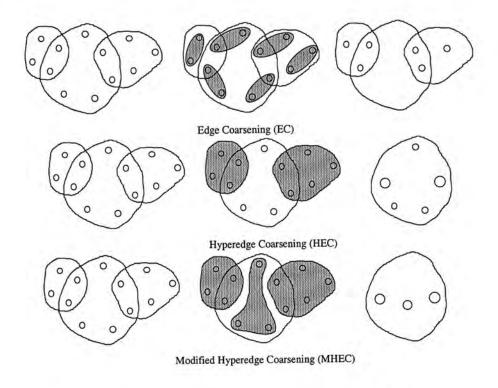

| 4.10 | Various hyperedge coarsening schemes                                | 52 |

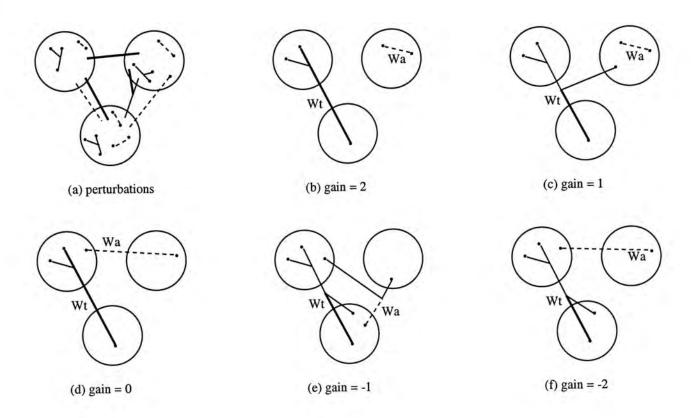

| 4.11 | Perturbations and gains                                             | 54 |

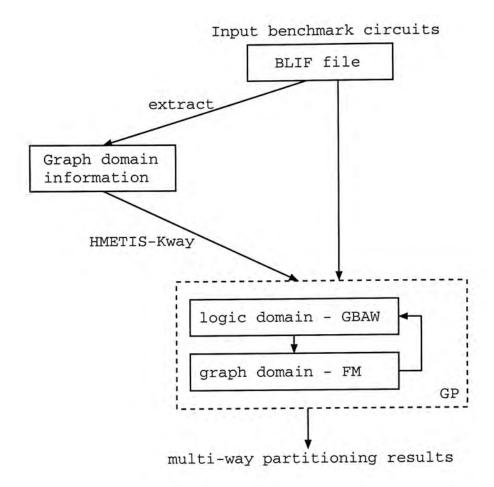

| 4.12 | Extract the Graph domain information for hMETIS-kway                | 55 |

| 4.13 | Algorithm of GBAW-Partitioner (GP)                                  | 61 |

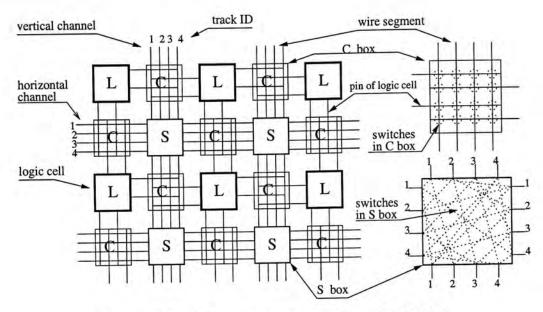

| 5.1  | The architecture of a 2D FPGA                                       | 63 |

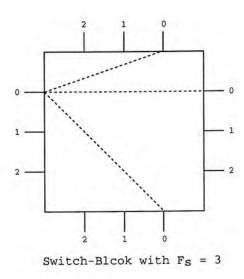

| 5.2  | A Switch module with $F_s=3$                                        | 66 |

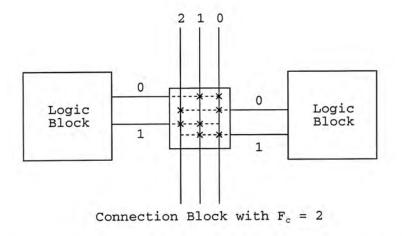

| 5.3  | A Connection module with $F_c=2$                                    | 66 |

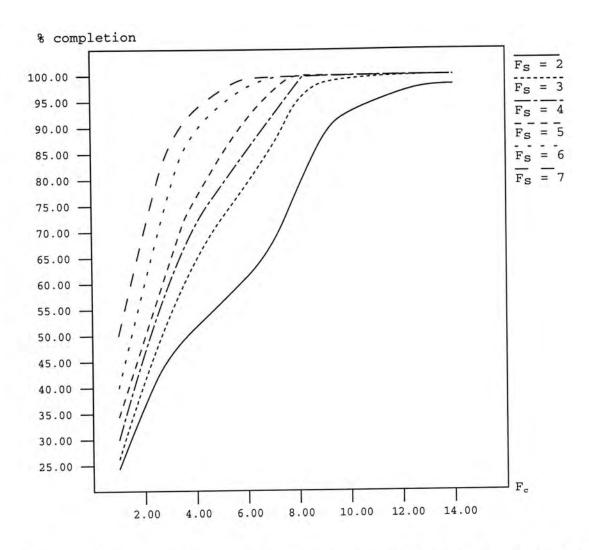

| 5.4  | Percentage of completion versus $F_c$ for the circuit BNRE          | 67 |

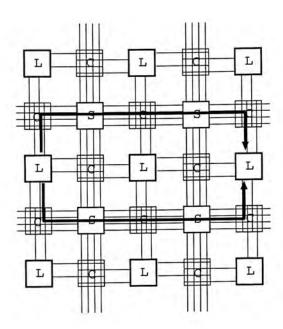

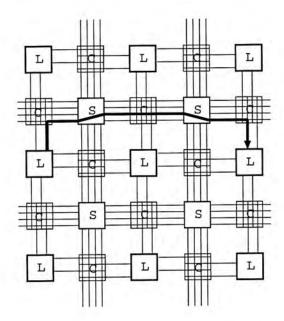

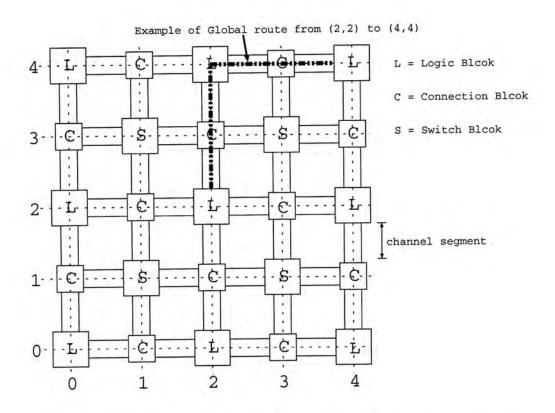

| 5.5  | Example of Global Routing in FPGA                                   | 68 |

| 5.6  | Example of Detailed Routing in FPGA                                 | 68 |

| 5.7  | CGE: The FPGA Model with one Global Route                           | 69 |

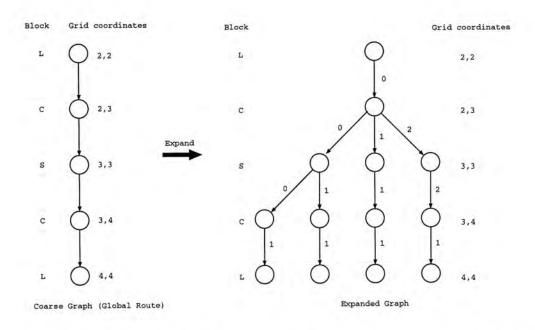

| 5.8  | CGE: The Coarse Graph and its Expanded Graph                        | 70 |

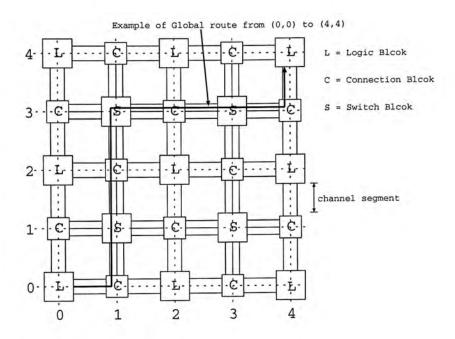

| 5.9  | SEGA: The FPGA Model with one Global Route                          | 71 |

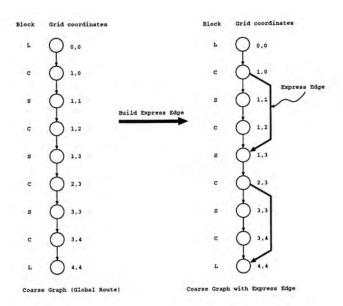

| 5.10 | SEGA: The Coarse Graph with Express Edge                            | 72 |

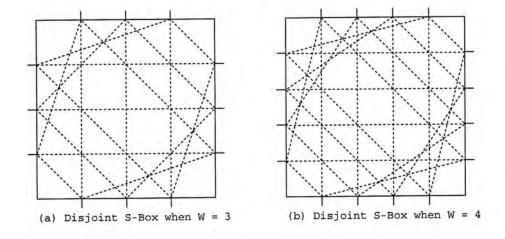

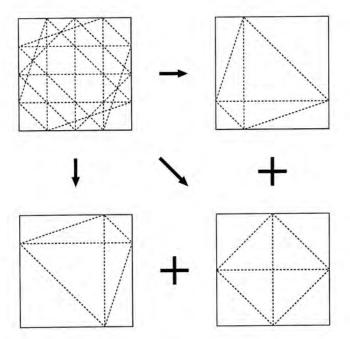

| 5.11 | XC4000-type Switch-Box Architectures for $W=3$ and $4\ \dots$       | 73 |

| 5.12 | Disjoint relationship between different tracks for $W=3$            | 73 |

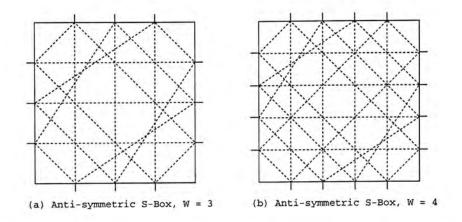

| 5.13 | Anti-symmetric Switch-Box Architectures for $W = 3$ and $4$         | 74 |

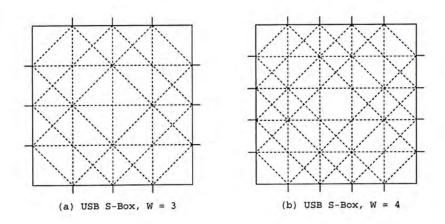

| 5.14 | Universal Switch-Box Architectures for $W = 3$ and $4 \dots$     | 74  |

|------|------------------------------------------------------------------|-----|

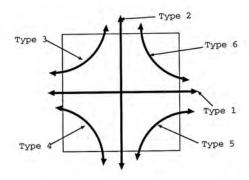

| 5.15 | Six different types of connections                               | 75  |

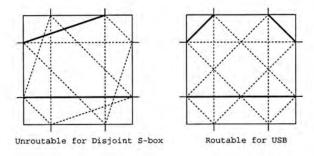

| 5.16 | Example of routing over Disjoint Switch-box                      | 75  |

| 5.17 | Example of routing over Anti-symmetric Switch-box                | 75  |

| 5.18 | Example of routing over Universal Switch-box                     | 76  |

| 5.19 | Another comparison between Disjoint and Universal Switch-box     | 76  |

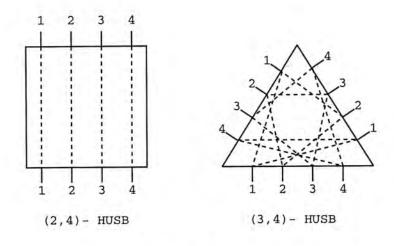

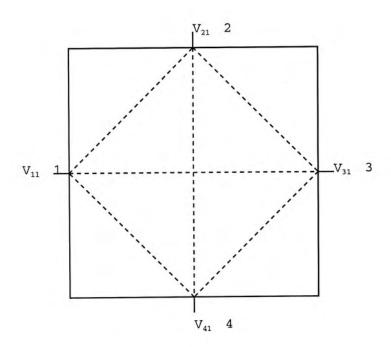

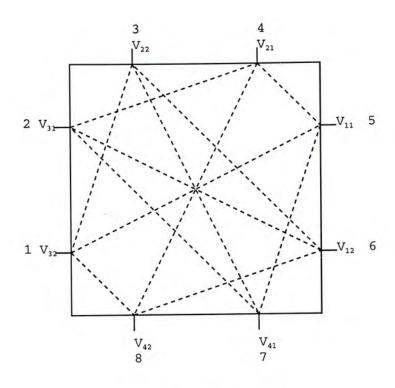

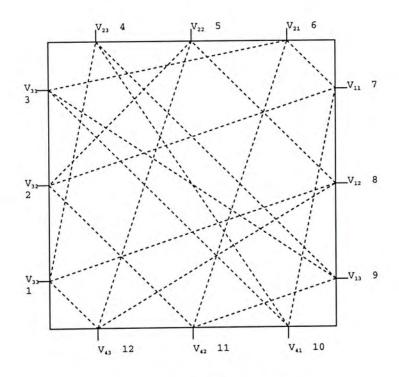

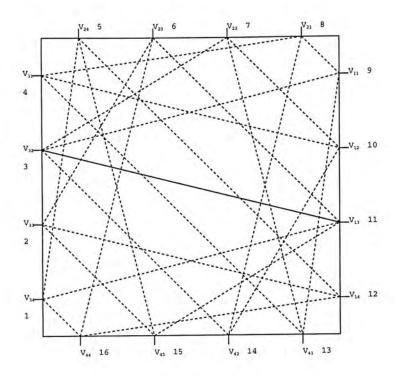

| 5.20 | (2,4) and (3,4) design                                           | 78  |

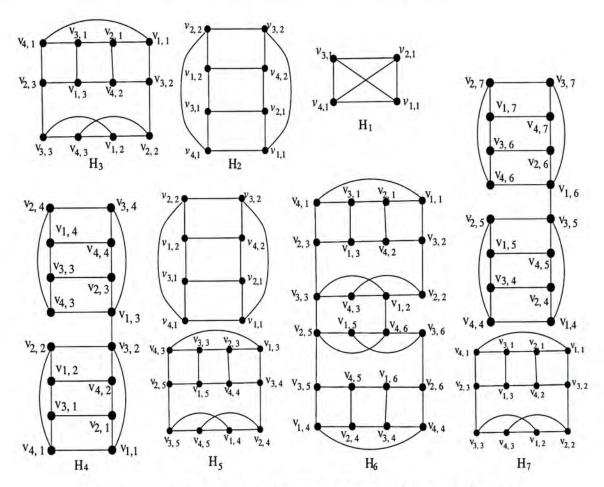

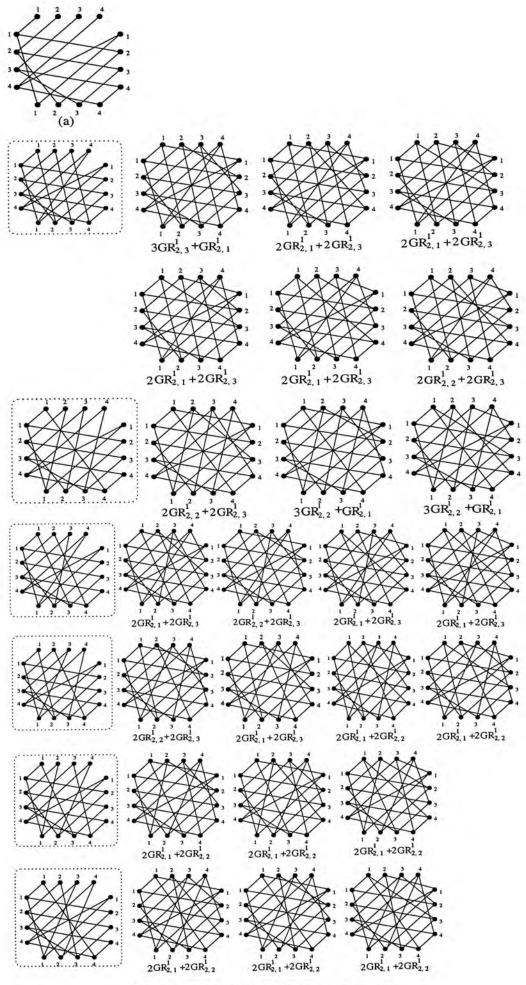

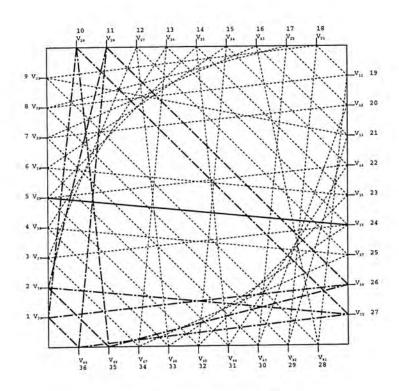

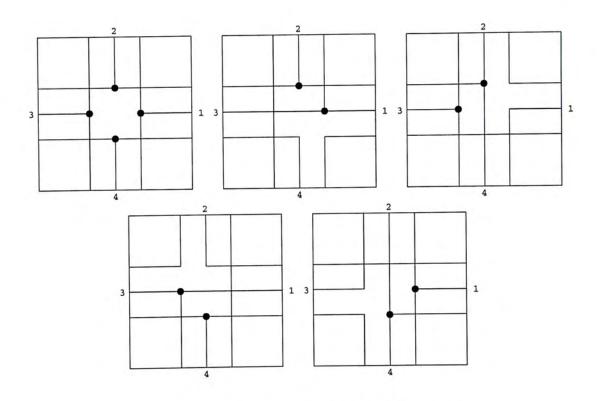

| 5.21 | A family of hyper-universal 4-way designs                        | 82  |

| 5.22 | Structure of H7                                                  | 83  |

| 5.23 | Detailed Routing of $GR$ (Case 1)                                | 86  |

| 5.24 | Detailed Routing for Table 3.2                                   | 87  |

| 5.25 | Detailed Routing of density 2 Global Routing in $H_3$            | 88  |

| 5.26 | Detailed Routing of $GR$ in $H_3$                                | 89  |

| 5.27 | Detailed Routing of $GR$ in $H_4$                                | 89  |

| 5.28 | (4,4)-Global Routing                                             | 91  |

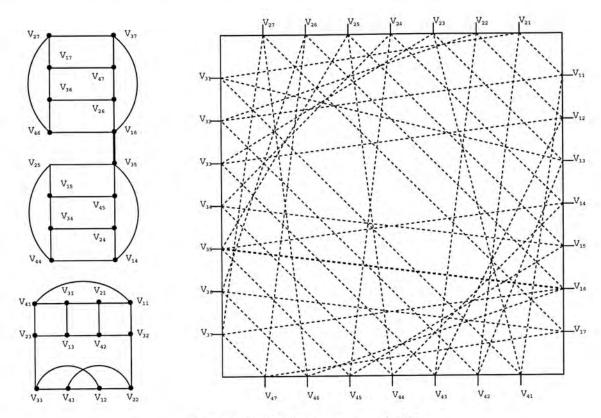

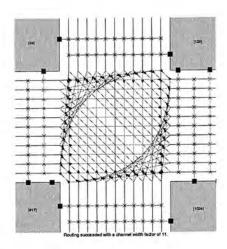

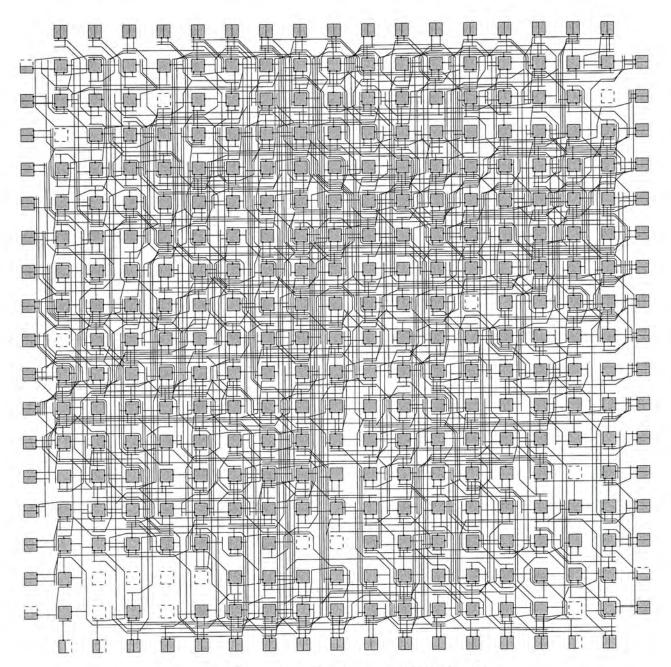

| 5.29 | The structure of Disjoint S-Box, W=11                            | 93  |

| 5.30 | The structure of $H'USB(4,11)$ ( $H'USB(4,7)$ and $H'USB(4,4)$ ) | 93  |

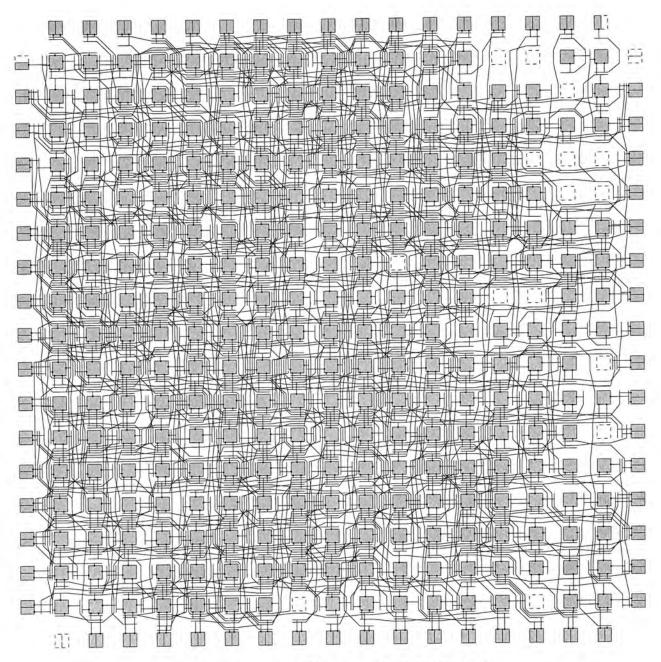

| 5.31 | Detailed Routing by using Disjoint S-Box                         | 94  |

| 5.32 | Detailed Routing by using H'USB S-Box                            | 95  |

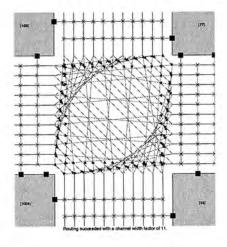

| 5.33 | Detailed Routing by using Disjoint S-Box on $GR_1^3$             | 96  |

| 5.34 | Detailed Routing by using Hyper-Universal S-Box on $GR_1^3$      | 96  |

| 5.35 | Routing result of <b>e64</b> by using Disjoint S-Box, W=9        | 97  |

| 5.36 | Routing result of <b>e64</b> by using H'USB S-Box, W=8           | 98  |

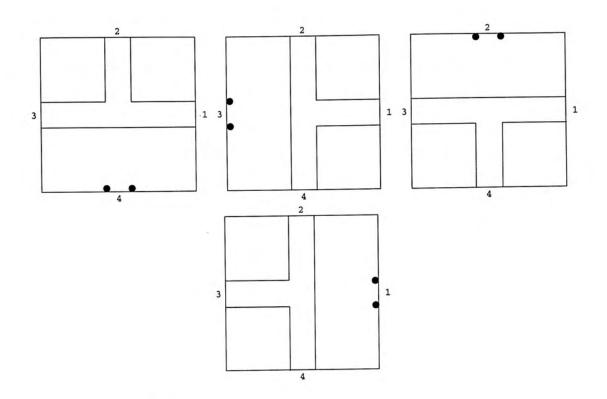

| B.1  | New 2-local pattern 1                                            | 122 |

|      | New 2-local pattern 2                                            |     |

|      | New 2-local pattern 3                                            |     |

|      | New 2-local pattern 4                                            |     |

| C.1  | Example of FM algorithm - First pass                             | 125 |

| C.2 | Example of                 | E   | ?N  | Λ  | al                | gc  | ri | th          | ın      | 1 - |     | Sec          | co           | no  | 1                 | pa      | SS          | 3   | • | • | ٠ | • | ٠ | • | • | • | • | • | • | • | • | 126 |  |

|-----|----------------------------|-----|-----|----|-------------------|-----|----|-------------|---------|-----|-----|--------------|--------------|-----|-------------------|---------|-------------|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|--|

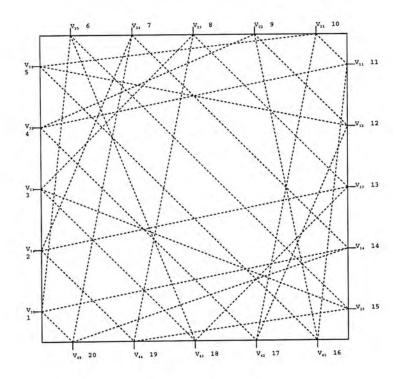

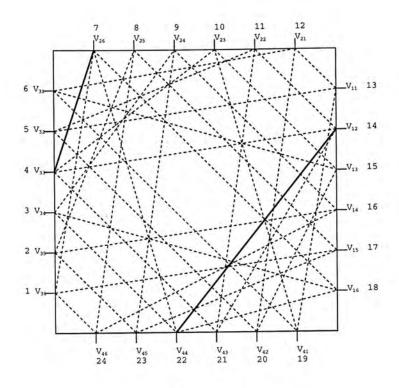

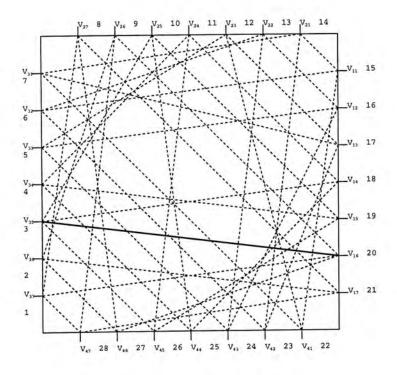

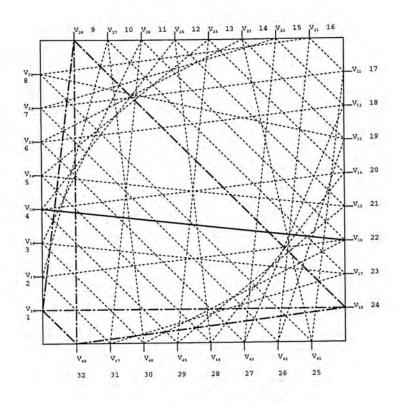

| D.1 | H1 S-Box                   | ٠   |     |    | ÷                 | •   | ·  | •           |         | •   | ٠   |              | ٠            | ٠   | ٠                 |         |             |     |   |   |   |   | ٠ |   | ٠ |   | · | • | ٠ |   |   | 127 |  |

| D.2 | H2 S-Box                   |     | •   |    | ı i               |     |    |             |         |     | •   |              |              |     |                   |         |             |     |   |   |   |   |   |   |   |   |   |   |   | i | • | 128 |  |

| D.3 | H3 S-Box                   |     |     | ٠  | ٠                 |     |    |             |         | •   | i   |              |              |     | ÷                 |         | ÷           |     |   | • |   | ÷ |   | ÷ |   |   |   | • | • |   |   | 128 |  |

| D.4 | H4 S-Box                   |     | ÷   |    |                   |     |    |             | ÷       | ٠   | •   | i,           |              |     | •                 |         |             | •   |   |   | • |   |   |   |   |   |   |   |   |   |   | 129 |  |

| D.5 | H5 S-Box                   |     |     |    |                   | ÷   | ٠  | ٠           |         | 4   |     | •            |              | ٠   | ٠                 |         |             | •   |   |   |   |   | ٠ | ٠ |   |   |   |   |   | ٠ |   | 129 |  |

| D.6 | H6 S-Box                   |     |     |    |                   |     |    |             | ٠       | i   |     |              | ٠            |     |                   |         |             |     |   |   | • | ě |   |   | • |   |   |   |   | • |   | 130 |  |

| D.7 | H7 S-Box                   | ÷   |     |    |                   |     | •  |             | •       | ÷   |     | •            |              | •   | •                 |         |             | ٠   |   |   |   |   |   | · |   |   |   |   |   | 4 |   | 130 |  |

| D.8 | H8 S-Box                   |     |     | •  |                   |     | ٠  | •           | •       |     |     |              | ŭ,           |     | •                 |         |             |     |   |   |   |   |   |   |   | ŀ | ٠ |   | • | ٠ |   | 131 |  |

| D.9 | H9 S-Box                   | •   |     |    |                   |     | ٠  |             |         |     | ٠   | •            |              | •   |                   |         | ٠           | ٠   |   |   |   |   |   | · |   |   |   | å | • |   |   | 131 |  |

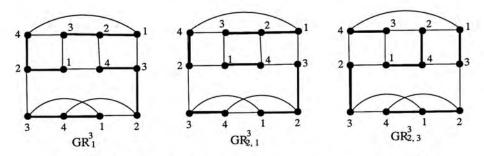

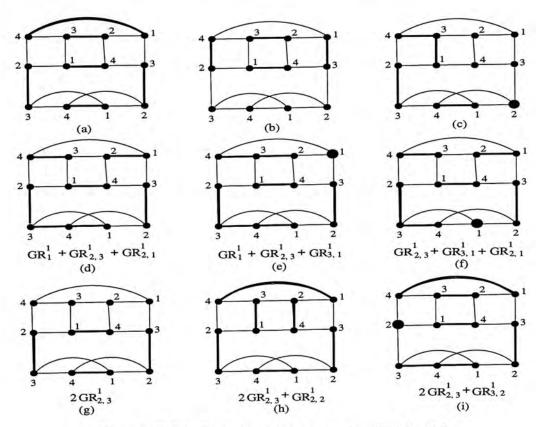

| E.1 | $GR_1^1$                   | ÷   |     |    | à                 |     |    |             |         |     |     |              |              |     |                   | 7       |             |     |   | • |   |   |   |   | • |   | • |   | • | • |   | 132 |  |

| E.2 | $GR_{2,1}^{1}, GR_{2}^{1}$ | ,2  | , ( | 31 | ${\bf R}^{1}_{2}$ | ,3  | •  |             |         | •   |     |              |              | ,   |                   |         |             | •   |   |   |   |   |   |   | ٠ |   | ٠ | • | • |   | • | 132 |  |

| E.3 | $GR_{3,1}^{1},GR_{3}^{1}$  | ,2  | , ( | Gl | $2^{1}_{3}$       | ,3, | G  | R           | 1,3,    | 4   |     |              |              |     | ÷                 |         | •           |     |   | • |   | • | ٠ | • | · | • |   | , |   |   |   | 133 |  |

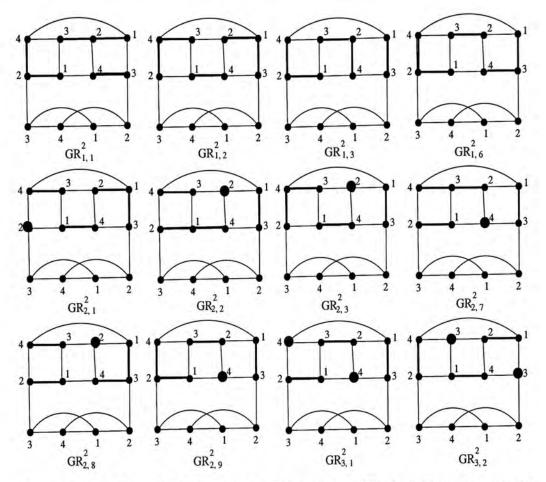

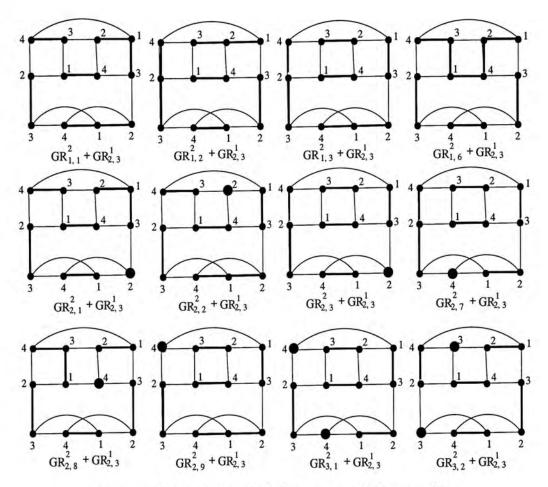

| E.4 | $GR_{1,1}^2, GR_1^2$       | ,2  | , ( | GI | $R_{1}^{2}$       | ,3, | G  | R           | 2<br>1, | 4,  | G   | R            | $^{2}_{1,5}$ | , ( | $G_{\mathcal{A}}$ | $R_1^2$ | ,6          |     | ٠ |   |   |   |   |   |   | · |   |   |   |   |   | 133 |  |

| E.5 | $GR_{2,1}^2, GR_2^2$       | 2,2 | , ( | GI | $R_{2}^{2}$       | ,3, | G  | R           | 2,      | 4,  | G   | R            | $^{2}_{2,5}$ | , ( | $G_{\mathcal{A}}$ | $R_2^2$ | ,6          |     | , |   | ÷ |   |   |   | ٠ | ٠ | Ģ |   |   |   |   | 134 |  |

| E.6 | $GR_{2,7}^2, GR_2^2$       | 2,8 | , ( | GI | $R_{2}^{2}$       | ,9, | G  | R           | 2<br>2, | 10  | , ( | GF           | ${}^{2}_{2}$ | ,11 | , (               | GI      | $R_{2}^{2}$ | ,12 | 2 |   |   | • | ٠ |   | ٠ |   | • |   | ÷ | • | • | 134 |  |

| E.7 | $GR_{3,1}^2, GR_3^2$       | 3,2 | , ( | GI | $\mathbb{R}^2_3$  | ,3, | G  | R           | 23,     | 4   |     |              |              |     |                   |         |             |     |   |   |   | • | · |   | • |   | • |   |   |   |   | 135 |  |

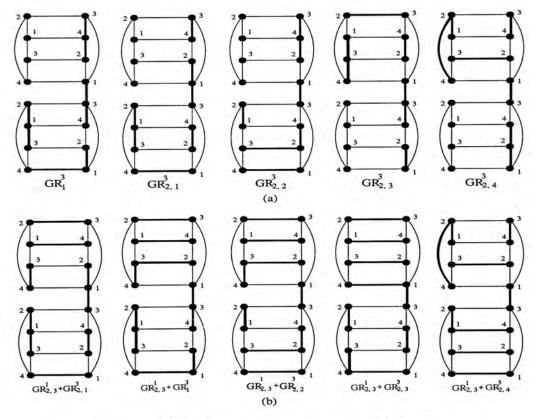

| E.8 | $GR_1^3, GR_{2,1}^3$       | ,   | G   | R  | 3,2,2             | , ( | GI | $7^{3}_{2}$ | ,3;     | G   | F   | $2^{3}_{2,}$ | 4            |     |                   |         |             | Q   |   |   |   |   |   |   |   |   |   |   |   |   |   | 135 |  |

# List of Tables

| 3.1 | 2-local pattern comparison                                             | 29 |

|-----|------------------------------------------------------------------------|----|

| 3.2 | Comparison between RAMBO and GBAW                                      | 31 |

| 3.3 | Results for logic optimization                                         | 32 |

| 4.1 | Alternative wire statistics of RAMBO and GBAW                          | 57 |

| 4.2 | 2-way partitioning results of hMetis-Kway & FM & GP                    | 58 |

| 4.3 | 3-way partitioning results of hMetis-Kway & FM & GP                    | 59 |

| 4.4 | 4-way partitioning results of hMetis-Kway & FM & GP                    | 60 |

| 4.5 | 5-way partitioning results of hMetis-Kway & FM & GP                    | 60 |

| 5.1 | Comparison between different FPGA Routers                              | 72 |

| 5.2 | Detailed routing result by CGE over different switch-box               | 76 |

| 5.3 | Primitive minimal 4-way global routings                                | 81 |

| 5.4 | Primitive minimal 4-way global routings which are not $\sigma$ iso-    |    |

|     | morphic                                                                | 85 |

| 5.5 | Channel widths required for different benchmark circuits $F_C$ =       |    |

|     | $W. F_{S} = 3 \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 96 |

## Chapter 1

## Introduction

#### 1.1 Motivation

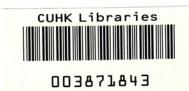

Integrated Circuit (IC) technology has evolved for many times from Small Scale Integration (SSI) to Very Large Scale Integration (VLSI). ICs are widely used in computers, electronic devices and even implantation of human body. According to Moore's law, the capacity of a chip is doubled for every 18-24 months of the previous chip as shown in Figure 1.1. Due to the huge number of components of circuit design, it is not practical for designer to repeat the fabrication process. As a result, Computer-Aided Design (CAD) tools [SW96] are developed for physical design which is one of the critical step in VLSI design cycle. The goal of physical design is to fit the design into a compact area for fabrication. Physical design is a very complex process and thus it is broken into many different stages from partitioning to routing. The netlist extraction by layout synthesis, design verification and validation check are also performed on the layout during physical design stage. This thesis addresses the two important steps of physical design, partitioning and routing especially for Field-Programmable Gate Arrays (FPGAs).

In the era of deep sub-micron, many problems arise and designers have to tackle them such as the domination of interconnect delay, failure to meet timing requirement and insufficient routability on different devices. By considering

Figure 1.1: Moore's Law vs Industrial CPU size (from Intel)

more circuit information in the physical design stage, we can improve the overall performance, get a better utilization of chip area, better yield and reduce the cost. The idea behind is to apply Alternative Wiring techniques [EC95] in order to remove some wires along the critical path, or replace some wires in congested area with those in uncongested area. Alternative wire allows adding and removing wires inside the circuit without changing the circuit functionality. Thus, it can explore a large degree of freedom in many different physical design problems, such as logic optimization [EC95], circuit partitioning [CLMS95] and timing optimization [EEOU96].

The idea of VLSI circuit partitioning is to divide a circuit into smaller subcircuits (clusters). The objective is to minimize the interconnection between clusters with balance constraints. Due to the increase of the VLSI design complexity, circuit partitioning is getting more and more crucial. The system may consist of several hundred million transistors and most of the algorithms in physical design cycle and logic synthesis can not handle such large problem size or become ineffective. As a result, circuit partitioning becomes the first step in physical design cycle. A large system becomes smaller manageable components which can be solved in a top-down hierarchical design methodology. The feasibilities of placement, floorplanning, global routing and detailed routing also depend on the quality of the partitioning solution.

Nowadays, in deep sub-micron VLSI design, the interconnection delays

dominate the gate delays. A larger die size means a longer routing delay on chip. An effective partitioning algorithm becomes the fundermental key to improve system performance. There are many different approaches to tackle this partitioning problem including move-based approaches, geometric representations, combinatorial formulations and clustering approaches [AK95b]. Recently, a new trend is to integrate existing partitioning algorithms with multi-level approach [ZSC96, KAKS97]. Most of the algorithms model the circuit as graph (hypergraph) and seek for optimal solution. However, these methods do not consider the logic function of the circuit, that is the function performed by each node.

Alternative wiring is a technique to transform a circuit into another but functionally equivalent circuit. It can be well-used for post-layout logic synthesis, logic optimization and other CAD problems. Graph Based Alternative Wiring (GBAW) is newly introduced and it is very efficient in identifying alternative wires. This motivates the integration of GBAW technique for circuit partitioning.

Nowadays, logic designers have several good logic devices to realize the digital logic functions. These devices include Small-Scale Integration (SSI) chips such as 7400 series, Application-Specific Integrated Circuits (ASICs) and Programmable Logic Devices (PLDs) such as Simple PLDs (SPLDs), Complex PLDs (CPLDs) and Field-Programmable Gate Arrays (FPGAs) [BFRV92]. With the huge logic resources, short turn-around time and user-programmability, FPGAs are easy for logic designer to modify their sophisticated design and reduce the manufacturing time. After the first emergence into market, FPGAs have been continuously growing and in the leading place amongst other logic devices. A typical FPGA composes of three major components: logic modules, routing devices and Input/Output (I/O) devices. Routing resources compose of pre-fabricated wire segments and programmable switches (switch-box).

Switch modules are the most important components of the routing resources in FPGAs. Programmable switches usually have high resistance and capacitance, and they consume large amount of area [ea88, ea89]. Thus an excessive number of switches means a slower and larger design. Higher routability means a smaller number of tracks to complete the design routing and reduces the size of FPGA. As a result, it is desirable to investigate the routability of switch-box for a better area performance design.

The rewiring technique can also be applied to layout-driven logic synthesis. GBAW technique is able to locate alternative wires such that the congested wire can be removed, thus the whole design can become routable within the smaller number of tracks.

#### 1.2 Aims and Contribution

There are two main parts in this thesis: circuit partitioning by using logic perturbation technique and FPGA routing employing Hyper Universal Switch Box (HUSB).

Firstly, the identifying alternative wiring power of the GBAW is further improved by introducing new rewiring patterns. The comparison of logic optimizations between famous ATPG-based RAMBO and augmented GBAW is also presented. Based on new rewiring technique, logic optimizations on MCNC benchmark circuits are successfully conducted and the integration of GBAW with the well-known multi-level graph partitioner (hMETIS-kway) is also done. The results showed that it is possible to obtain an improved partitioning result from near optimal solution.

Secondly, the construction and mathematical model of Hyper Universal Switch Box (HUSB) are given. Further investigation of the quality of HUSB is done by giving new theoretical results and adopting efficient FPGA router VPR which is used to generate experimental justification. An encouraging result over the comparison between the popular disjoint structure (XC4000) and the proposed designs is obtained.

Our proposed design flow for FPGAs has two stages. In the first stage, the interal switch-box architecture is modified in order to achieve high routability. In the second stage, the rewiring engine GBAW will be integrated into the whole FPGA design flow which is not yet completed.

#### 1.3 Thesis Overview

This thesis is organized as follows. Chapter 2 presents the background of physical design. Chapter 3 introduces the alternative wiring engine (GBAW) and shows the comparison between RAMBO and GBAW on logic optimization. Chapter 4 discusses the new approach to further improve the partitioning solution by hMETIS-kway. Chapter 5 addresses the quality of FPGA routing result by VPR with enhanced HUSB (H'USB). Finally, Chapter 6 concludes this thesis and discusses the future works.

## Chapter 2

# VLSI Design Cycle

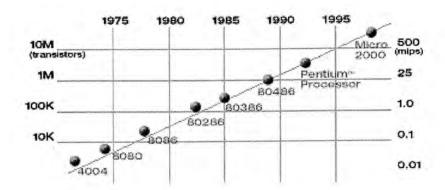

A simple VLSI design cycle starts from system specification of a VLSI chip and ends as a tested and packaged chip. The design flow involves architectural, functional, logic, circuit design and the last step before fabrication is physical design which collects the net-list information of a circuit into layout. At the beginning of the VLSI design process, the user can get the specifications for the size, speed, power and the functionality of the VLSI system [She98, Mic94]. In the next step, the VLSI designers are required to design a system which meet all these constraints. Nowadays, the Hardware Design Language (HDL) such as VHDL and Verilog are commonly used in VLSI design. HDL language are used to express the circuit and timing information for simulation and verification. Since the design scale is large and it is impossible to design by hand, the Computer-Aided Design (CAD) tools become crucial and widely used for a fast and correct design. The typical design flow is shown in Figure 2.1. Logic synthesis is a step to translate the register transfer level (RTL) of a digital system to the gate net-list information. In the other words, logic synthesis is applied to the extraction from RTL language and deals with the logic optimization, testability and verification. In physical design step, there are many CAD tools developed for automatic layout, design rule check and extraction [She98]. A tested VLSI chip will be available after all these complex stages.

Figure 2.1: The Path to Silicon Chip

### 2.1 Logic Synthesis

Logic synthesis enables the mapping from RTL level to an optimized gate-level description. The generated description must fit the functional specification and user constraints. It basically begins with logic optimization and provides an efficient implementation to a high quality silicon chip. With the aid of CAD tools, the circuit designers are allowed to work at higher levels of abstraction and easily modify their design. Logic synthesis tools such as "Synopsys" not only reduce the logic but also perform timing analysis, technology mapping and ensure the testability of the generated net-list. In the process of logic synthesis, it aims at:

- minimizing the layout chip area.

- minimizing the critical path delay.

- maximizing the testability such that all test vector can be found.

#### 2.1.1 Logic Minimization

Logic synthesis are usually divided into two-level synthesis (PLA) and Multi-level synthesis [BHSV90]. Therefore, many optimization methods are developed and can solve the problem in reasonable computation time. The algorithms include the minimization of don't cares [BBH+88], global flow [BT91], OBDD representation [Bry86] and rewiring techniques [CE93, WLF00] which change the original circuit net-list information.

#### 2.1.2 Technology Mapping

Technology mapping [Keu87] is the process to translate the abstract description such as HDL languages into a hardware description by using a specific technology. The result is a mapped circuit. Therefore, one description language can be mapped into different architectures by varying the technology mapping library.

#### 2.1.3 Testability

The circuit which cannot provides a complete single stuck-fault test vector is called an untestable circuit. Testability is an important criteria for circuit design, otherwise the fabricated chip cannot locate the fault wire.

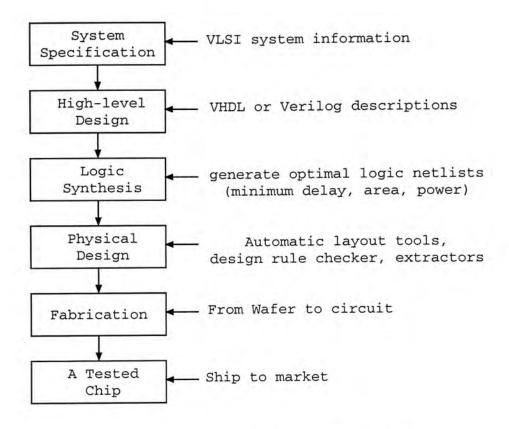

### 2.2 Physical Design Synthesis

Physical design is also called as layout phase which is the process to determine the exact location for the logic devices and the interconnection between different devices. Physical design is a complex process and it can be broken down into several steps which are shown in Figure 2.2. Many research groups focus on each of the sub-steps in order to obtain high performance design [She98].

The cost of fabrication is very high, therefore the objective for physical design is to produce a layout with small area, few defects and high yield.

Figure 2.2: VLSI Physical Design Cycle

### 2.2.1 Partitioning

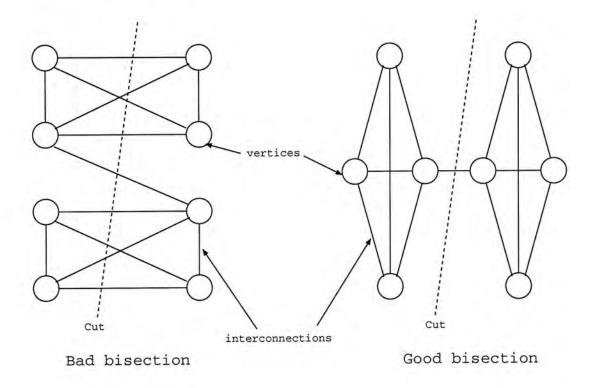

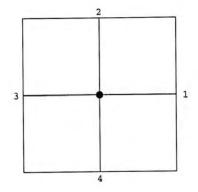

Partitioning is the first step in physical design owing to the increase of problem size. Many of the algorithms in the latter steps become infeasible, thus partitioning breaks the original problem into small sub-problems and solves eventually. The output of partitioning is a set of clusters which contains a set of logic gates, and the interconnections between clusters. In Figure 2.3, it shows a good and a bad bi-partitioning. The partitioning result for the good one is reduced from 9 to 1.

Figure 2.3: Example of Bi-partitioning

### 2.2.2 Floorplanning & Placement

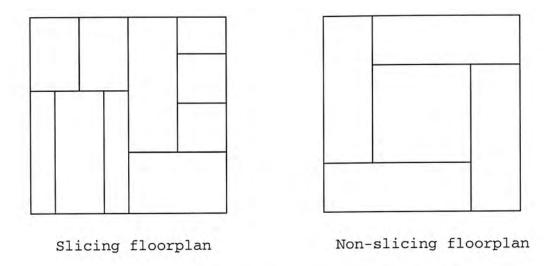

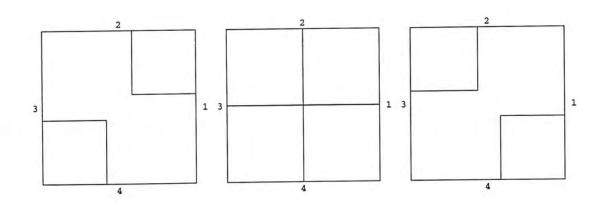

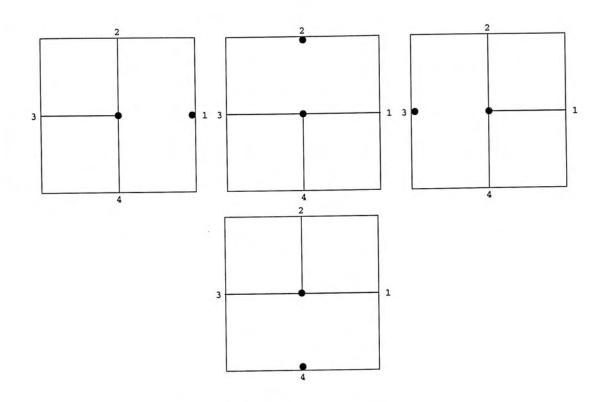

The objective of floorplanning is to arrange the components of an IC in order to have a compact layout. The two floorplans show in Figure 2.4 are slicing and non-slicing floorplan. Slicing floorplan can be recursively cut horizontally or vertically but non-slicing cannot. In the placement stage, the block to be placed are layouted and have pin assignment. After placement, the IC will have minimum area such that the interconnections between modules can be completely routed. Since a packed placement solution does not guarantee a routable design, the placement step is usually taken again after routing.

Figure 2.4: Example of Floorplanning

#### 2.2.3 Routing

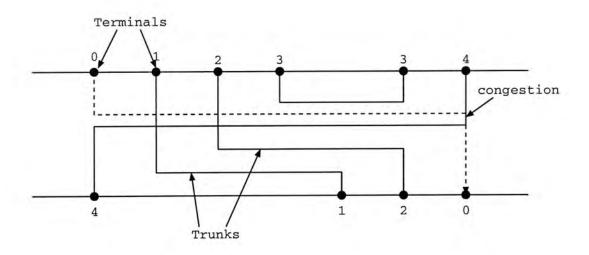

In order to connect the wires between blocks, routing step is usually done in two steps as the *global routing* and *detailed routing*. Global routing will specify the region used for detailed routing and detailed routing will determine the exact location for each connection. It aims at shorter wire length and less resources used. Figure 2.5 shows a failure channel routing example.

Figure 2.5: Example of Channel Routing

#### 2.2.4 Compaction, Extraction & Verification

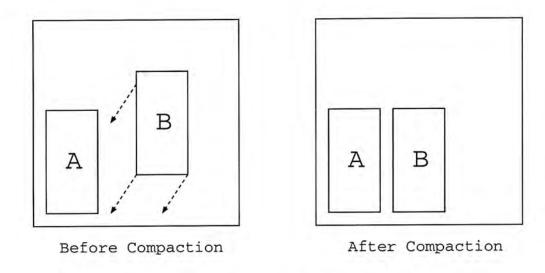

Compaction is a step to reduce the chip's total area and signal delay between modules of the circuit. Example of x-y coordinate compaction is shown in Figure 2.6. The circuit extraction step [BB91] consists of determining the circuit connectivity and calculating various electrical parameters such as resistances and capacitances. The last step before fabrication is to verify the design passing all the design rule.

Figure 2.6: Example of Compaction

#### 2.2.5 Physical Design of FPGAs

The time-to-market for even ASIC chip is unacceptable for many applications, therefore the short turn-around time of FPGAs takes advantage and gain more popularity. Since the most of the physical design algorithms are inapplicable in FPGAs, the CAD tools development of FPGAs are separated from others. For example, the traditional channel routing algorithm [SW96] cannot be applied to FPGAs. It mainly consists of three areas: partitioning, placement and routing.

## Chapter 3

# Alternative Wiring

#### 3.1 Introduction

Alternative wiring technique has a wide range of applications such as circuit optimization [CE93, EC93, EC95, CMSC96, CvGLMS99], partitioning [CLMS95] and FPGA synthesis [CCWMS94b, CCWM97]. Alternative wiring refers to the reconstruction of circuit while keeping its functionality intact by addition and removal of wires. A wire in a circuit is redundant if its addition and removal does not change the functionality of the circuit. The concept of alternative wiring is to add a redundant wire to the circuit that in turn will make another wire become redundant and its removal would lead to some useful circuit transformation for certain objectives. Due to the wide range of application, many research groups are working on the efficiency of locating alternatives wiring. The traditional rewiring tools apply Automatic Test Pattern Generation (ATPG), Implication analysis [KSM97] and Recursive learning [KP94] techniques in order to search alternative wires. However, these kinds of techniques consume too much CPU expenditure, and another Graph-Based Alternative Wiring technique is proposed to replace the ATPG approaches.

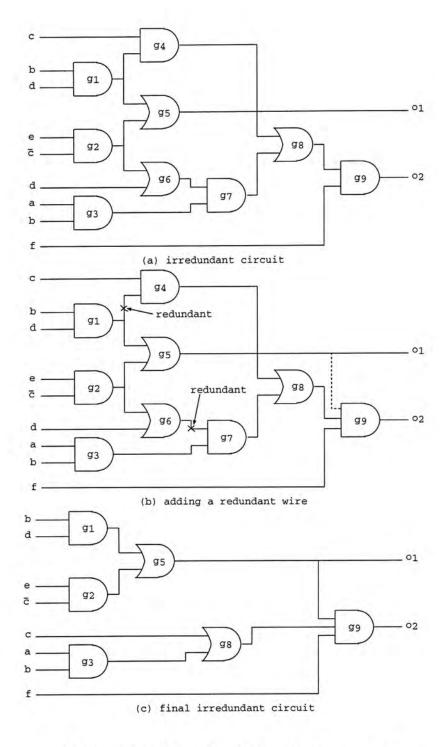

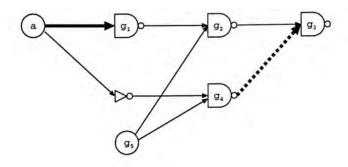

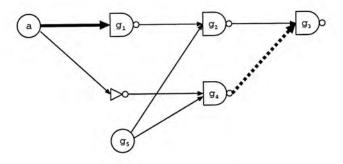

Consider the circuit given in Figure 3.1(a). This circuit is irredundant. By adding a connection from the output of gate  $g_5$  to the input of gate  $g_9$  (shown as a dotted line in Figure 3.1(b)), the functionality of the circuit does

not change. In other words, the added connection is redundant. However, the addition of the connection causes two originally irredundant wires becoming redundant as shown in Figure 3.1(b). After removing these two wires and associated gates that either become floating  $g_6$  or have a single fanin  $g_4$  and  $g_7$ , the circuit can be greatly optimized as shown in Figure 3.1(c).

Figure 3.1: Example of alternative wiring

This chapter is organized as follows. The notation and definitions are introduced in Section 3.1. The application of rewiring is presented in Section 3.2. In Section 3.3, logic optimization analysis is introduced. The details of Augmented Graph-Based Alternative Wiring are stated in Section 3.4. Followed by the discussion on Logic Optimization by using GBAW and experimental results are presented in Section 3.5. Conclusion is drawn in Section 3.6.

#### 3.2 Notation and Definitions

A combinational circuit can be represented by a Directed Acyclic Graph (DAG) where vertices correspond to the primary inputs (PI), primary outputs (PO) and the internal gates of the circuit. PI and PO are nodes which have only outgoing edges and incoming edges respectively. An internal node has at least two incoming edges and one outgoing edge and is associated with a Boolean function. Inverters are not considered as internal nodes, but as polarity of edges during logic domain perturbation. In a Boolean network, the in-degree of node y, denoted by  $d^-(y)$ , is defined as the number of edges entering y. The out-degree of node y, denoted by  $d^+(y)$ , is defined as the number of edges leaving y. A node y is defined by a triplet  $(op, d^-(y), d^+(y))$ , where op is the Boolean operator of y which can be any associative operator like AND, OR, NAND, or NOR.

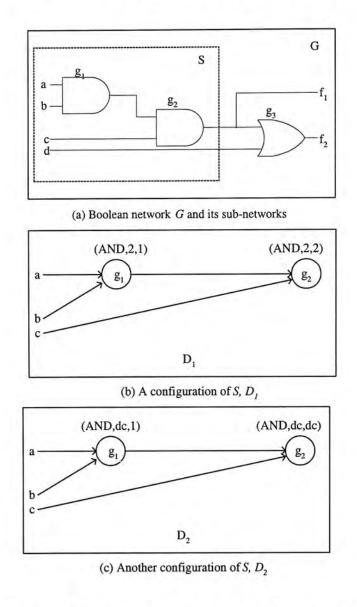

A wire is replaceable if it has at least one alternative wire. A graph configuration D is used to map the logic function from a Boolean Network G. For each node  $n_i$  in sub-network S in network G,  $n_i$  is mapped to a triplet  $(op, i_1, i_2)$  in D where op denotes the operator representing the Boolean function of  $n_i$  and  $i_1$ ,  $i_2$  are non-negative integers. All edges inside S are preserved, while the edges outside S are omitted in D. In most cases,  $i_1$  equals  $d^-(n_i)$  and  $i_2$  equals  $d^+(n_i)$ . The element of a triplet  $(op, d^-(y), d^+(y))$  can also be don't care. For the first element, don't care means any operator. For the other

elements, don't care can be any positive integers. A configuration is used to denote a minimal pattern containing both the target and its alternative wire.

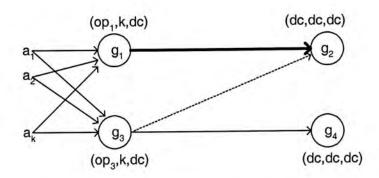

The mapping is illustrated in Figure 3.2. S is a sub-network of G.  $D_1$  and  $D_2$  are two mappable configurations of S. A k-local pattern denotes a minimal sub-graph with the distance between the alternative wire and its target wire being k. The distance between two wires is defined as the difference of maximum path length from any primary input to each of the wires.

Figure 3.2: Configuration of a sub-network

A wire is defined as a 2-point connection between a pair of source and sink nodes. When a larger circuit is partitioned into two sub-circuits, we define the wires crossing the partitioning cut line as cut wires. a cut net is also defined as a hyperedge connecting partitions and the cut cost as the number of partitions that the hyperedge connects.

### 3.3 Application of Rewiring

Alternative wiring greatly increases the flexibility of a circuit in which the wires of the circuit can be altered without changing the circuit functionality. Thus, the circuits before and after rewiring are said to be functionally equivalent. As a result, alternative wiring provides a wide range of applications in different steps of physical design automation.

#### 3.3.1 Logic Optimization

As shown in Figure 3.1, the circuit size is reduced by adding and removing redundant wires. A smaller circuit containing the same logics always implies less resources to spend on each step of VLSI design. Therefore, logic optimization by alternative wiring is always being the frontier of all VLSI design problems [CE93].

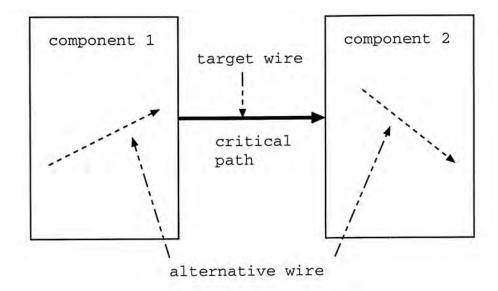

### 3.3.2 Timing Optimization

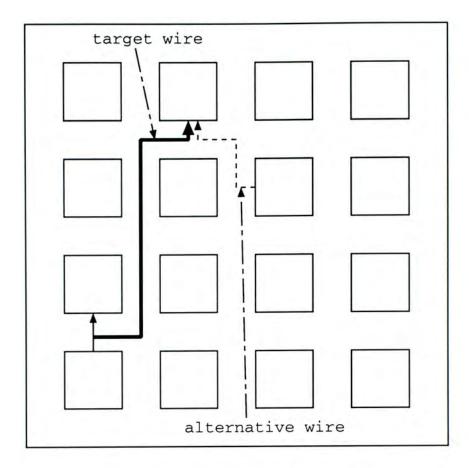

The longest delay path (critical path) usually consists of more than one wire. If it is possible to break the critical path with wire which is not on the critical path. Alternative wiring technique is used to improve the performance as shown in Figure 3.3. The target wire is replaced by other alternative wires inside component 1 or 2. By several iterations which break the critical path, the longest path might be greatly reduced and high performance gain [EEOU96] can be achieved.

Figure 3.3: Example of Timing Optimization by alternative wiring

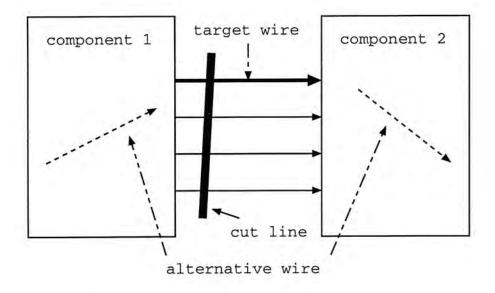

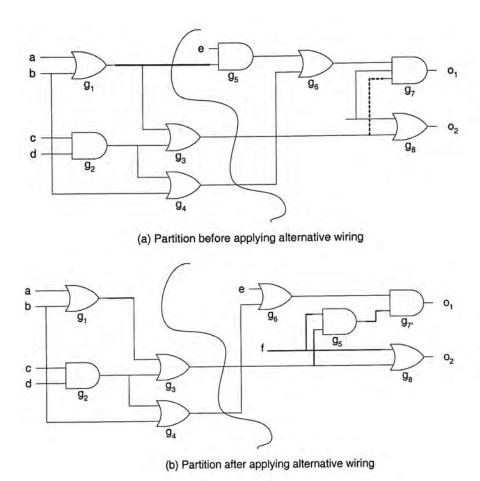

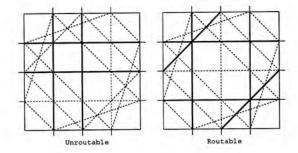

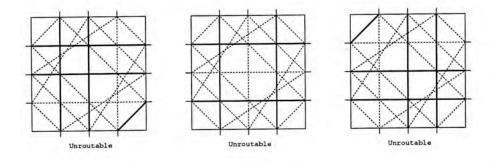

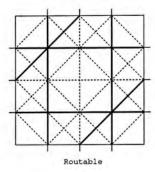

### 3.3.3 Circuit Partitioning and Routing

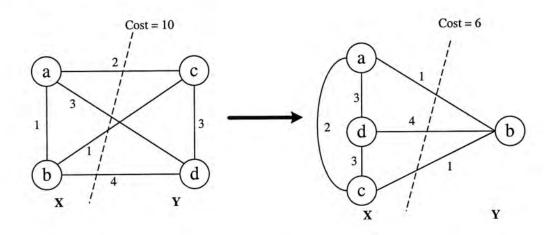

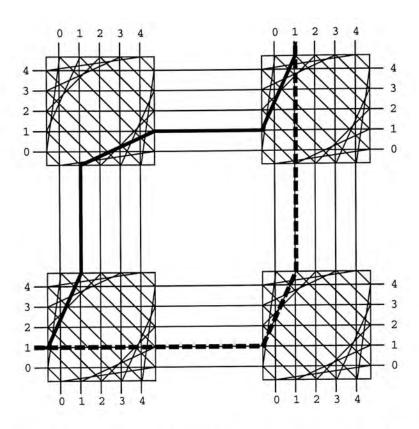

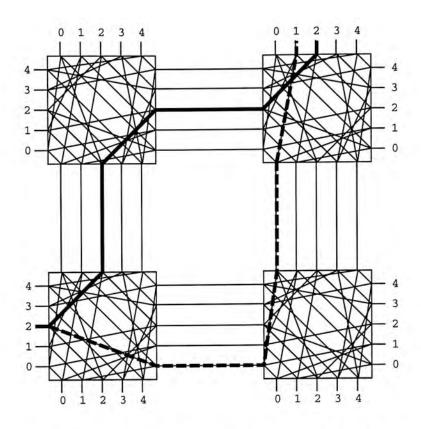

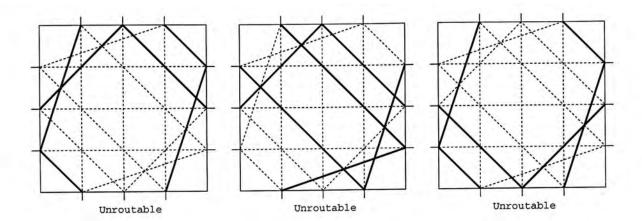

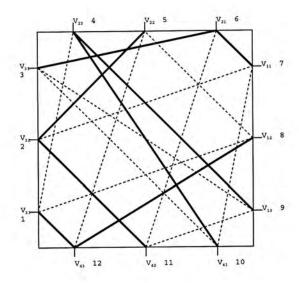

Figure 3.4 shows the number of wires along the cut line can be reduced by replacing with other wires not in cut set. The application of rewiring over circuit partitioning will be further investigated in the next chapter. Rewiring techniques can also be applied to resolve the unroutable FPGA design [CCWM97] as shown in Figure 3.5.

Figure 3.4: Example of Circuit Partitioning

Figure 3.5: Example of Routing

## 3.4 Logic Optimization Analysis

#### 3.4.1 Global Flow Optimization

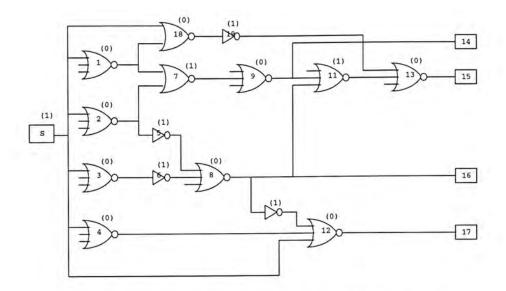

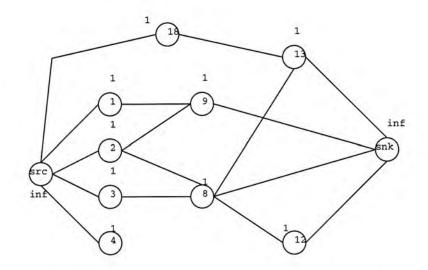

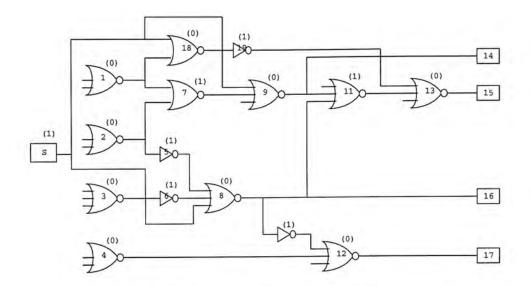

Global Flow Optimization [BT91] allows the reconnection of immediate fanouts of a node to the input of other nodes. By modeling the problem as flow graph and solving the problem by maxflow-mincut algorithm, the original circuit size can be reduced. As shown in Figure 3.6, one of the node s is picked from the circuit and has the following circuit diagram. By proper transformation [BT91], a flow graph is built and is solved by maxflow-mincut method as shown in Figure 3.7. The maxflow-mincut solution is  $g_1 8$ ,  $g_9$  and  $g_8$ . As a result, the original six connections from s is reduced to three without changing the circuit functionality as shown in Figure 3.8. Logic optimization is done by constructing the flow graph on every node in the circuit.

Figure 3.6: Example of Global Flow Optimization

Figure 3.7: Flow graph for the circuit in 3.6

## 3.4.2 OBDD Representation

In [MKLC89], the Transduction (Transformation and Reduction) method is proposed for multilevel logic optimization which allows adding/deleting connections and gate merging. However, the runtime and the memory storage exponentially increase when the number of inputs increases. It is because the Transduction method uses truth tables to represent the logic function. In order to save CPU time and memory space, the same Transduction method is implemented by using Ordered Binary Decision Diagrams (OBDD) [Bry86]

Figure 3.8: Result of fanout re-connections

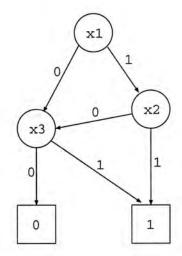

as the data structures for representing the logic functions. OBDD is a compact logic representation and it is a reduced binary decision tree and requires less memory than other methods. As shown in Figure 3.9, a logic function  $f = x1 \cdot x2 + x3$  is represented.

Figure 3.9: OBDD representing  $f = x1 \cdot x2 + x3$

## 3.4.3 Automatic Test Pattern Generation (ATPG)

Nowadays, Multi-level logic synthesis becomes more practical than 2-level logic synthesis because they represent the majority of circuit designs [HS96]. Multi-level circuits refer to those circuits have arbitrary number of gates between primary input and primary output. 2-level circuits are typically represented by SOP or POS forms, i.e. AND plane plus OR plane. There are many methods which address the problem of Multi-level minimization such as considering the don't care set [BBH+88], and Automatic Test Pattern Generation (ATPG) [CE93]. ATPG techniques are built upon the fault models. There are many possible fault models and most common one is single stuck-at-0/1 fault model. If a wire connecting to AND gate detects a stuck-at-1 fault, then it can be removed directly. ATPG will generate a vector for a stuck-at-fault test in the circuit. A vector means the zero or one value to all primary inputs. For a real circuit, if there exists a fault which is untestable that means there is no suitable test vector for such fault. The wire associated with this fault is said to be redundant.

Based on this redundancy test, many ATPG based rewiring tools are proposed. There are two main classes for ATPG tools, they are add-first based and target-first based ATPG techniques. Add-first means by adding one or some redundant wires into a circuit, some other inredundant wires become redundant and thus can be removed. Target-first means first choose one wire (target wire) in the circuit. By adding a suitable wire, this target wire becomes redundant and can be removed.

By using SIS package [SSLea92] which developed by University of California, Berkeley, Redundancy Addition and Removal for Multilevel Boolean Logic Optimization (RAMBO) [EC95] is first proposed. RAMBO creates fault list for each node and removes all redundant wires. The objective is to reduce

the wire count so as the area of the circuit. RAMBO shows significant improvement over combinational and sequential circuit and even better results are obtained when incorporate with MIS-II [BRSVW87]. There are many improvement works and applications built upon RAMBO such as Perturb and Simplify [CMSC96], Rewiring [CGMS96, CvGLMS99] and post-layout in FP-GAs [CCWM97].

# 3.4.4 Graph Based Alternative Wiring (GBAW)

Graph-Based Alternative Wire (GBAW) is a newly proposed and efficient rewiring technique. It models a circuit as a directed acyclic graph (DAG) and searches alternative wires by checking graph matching between local subnetworks and the pre-specified minimal sub-graph configurations. A configuration is a minimal circuit pattern containing alternative wires within a given distance. Experiments show that the number of all such local minimal subgraph is limited. Most of the alternative wires are located topologically "near" to their target wires. It has been shown that about 96% of the closest alternative wires [WLF00] are only 2-edge distant from their target wires. When sub-network matches a pattern, GBAW can quickly determine the target wire and the corresponding alternative wires. Obviously, if  $w_r$  is an alternative wire of  $w_t$ , then  $w_t$  is also an alternative wire of  $w_r$ . Both  $w_t$  and  $w_r$  are presented in a pattern. But in a sub-network, only one of them exists. In [WLF00], it has shown that by using GBAW as a random perturbation engine, a competitive logic optimization result is obtained when comparing to RAMBO while the runtime is much reduced.

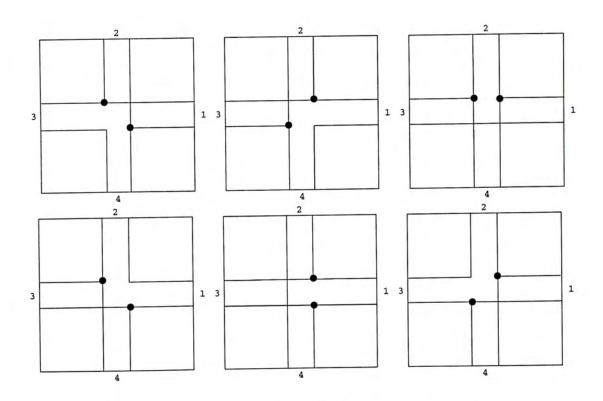

#### 0 local pattern

In GBAW, there are more than 40 patterns for rewiring. These 40 patterns are grouped into three main types, 0-local, 1-local and 2-local. A 0-local pattern

on the other words, it means a node substitution for which two nodes having the same logic function can be replaced by each other. If the two nodes have the same fanins set, they are said to be logically equivalent. Figure 3.10 shows the 0-local pattern in GBAW.

Figure 3.10: 0-local pattern in GBAW

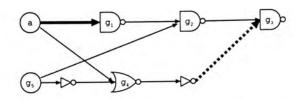

#### 1 local patterns

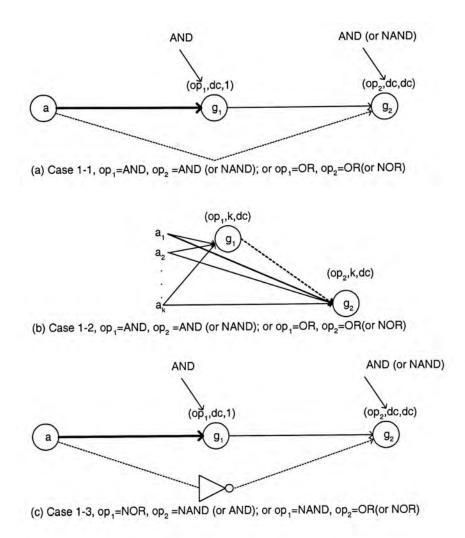

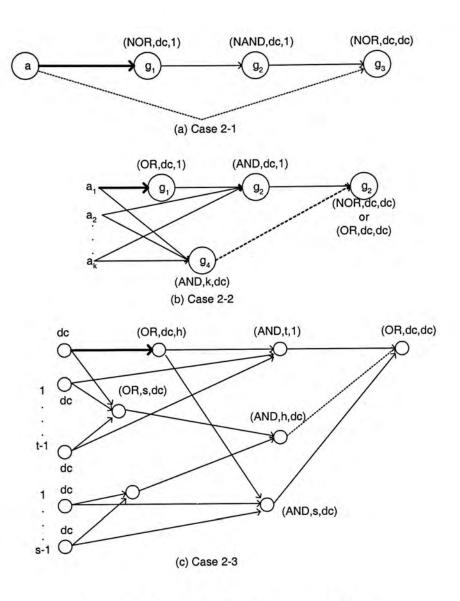

There are three basic 1-local patterns in GBAW as shown in Figure 3.11. The bolded wire represents the target wire that can be removed if the dotted wire is newly added to the circuit. For example, in case 1.1, the target wire  $a \to g_1$  can be replaced by  $a \to g_2$ . Note that the operator of  $g_1$  and  $g_2$  can be changed to other logic gates. This change increases the search space of finding alternative wires in real circuit, and it reduces the runtime in identifying alternative wires.

#### 2 local patterns

The alternative wire is 2-edge far away from the target wire is called 2-local pattern. The number of gates inside a 2-local pattern is increased as well as the number of possible 2-local pattern. Thus, it is necessary to include more 2-local patterns into GBAW. In Figure 3.12, three 2-local patterns are shown.

Figure 3.11: 1-local patterns in GBAW

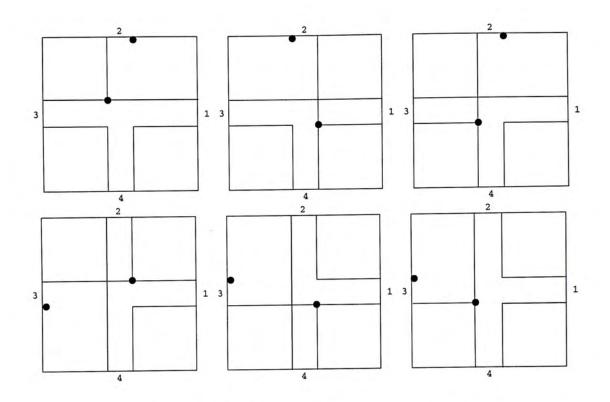

#### Proof of one 2 local pattern

In order to maximize the searching power, pattern cluster is proposed to put similar patterns together. Currently, 5 clusters are built on top of more than 30 2-local patterns and the new family members are continuously put into GBAW in order to enhance its searching ability.

In Figure 3.13 below,  $a \to g_1$  is the target wire. let  $g_1 = (a * x)'$  where x is the other inputs of  $g_1$ .  $g_2 = (g_1 * y)'$  where y is the other inputs of  $g_2$ .  $g_3 = (g_2 * z)'$  where z is the other inputs of  $g_3$ . Therefore,  $g_3 = (((a * x)'y)'z)' = ((a' + x')y)'z)' = ((a'y + x'y)'z)' = ((a'y)'(x'y)'z)' = ((g_4)(x'y)z)'$ . Hence, this pattern is constructed and verified. Some other 2-local patterns are shown in Appendix B.

Figure 3.12: 2-local patterns in GBAW

# 3.5 Augmented GBAW

Owing to the high applicability of alternative wiring technique, many related algorithms were published in last decade. Some research groups prefer algorithms based on Automatic Test Pattern Generation (ATPG) to perform testing of redundancy since ATPG requires little memory to process large circuits. One of the circuit rewiring schemes based on ATPG is the well-known Redundancy-Addition and Removal for Multilevel Boolean Optimization (RAMBO) technique [CE93, EC93, EC95]. RAMBO applies ATPG-based

Figure 3.13: Example of one 2-local Pattern Verification

implication technique to identify redundant wires among a large number of candidate wires. It has demonstrated to be very flexible and practical in solving various CAD problems. Improvement in efficiency is achieved by eliminating unnecessary redundancy check [CvGLMS99, LWB00] on the same wire but since the number of candidate wire for testing can still be large, RAMBO may still require a long running time due to the intrinsic exponential time property of ATPG algorithms.

In [WLF00], a new graph-based technique on identifying alternative wire, called Graph-Based Alternative Wiring (GBAW), was first proposed. It first models a circuit network as a directed acyclic graph (DAG) and identifies alternative wires by performing graph pattern matching between local subgraph of the network and the pre-specified minimal sub-graph configurations containing alternative wires within a given range limit. Experiments show that the number of all such local minimal sub-graph is limited and most of the alternative wires are located topologically "near" to their target wires. It has been shown that about 96% of the closest alternative wires are only 2-edge distant from their target wires.

GBAW produces a competitive result in finding alternative wire when comparing to RAMBO. GBAW not only performs well in searching alternative wires but also runs very fast. Experiments show that on average, the CPU running time of GBAW is just 1.4% of that of RAMBO. This significant short

running time makes GBAW being a potentially considerable different technique for identifying alternative wires. The efficiency of GBAW is gained probably mainly because of its avoidance of running the could-be CPU-expensive Boolean implications. And since there exist common alternative-wire patterns that repeatedly occurs in the same circuit, it makes the one-time analysis effort of pattern based rewiring scheme practical.

It was also observed that GBAW may not find many 2-edge distant patterns, if it is limited to search the small pre-defined set of minimal configurations like the early version shown in [WLF00]. Therefore, a much extended GBAW scheme is presented, mainly 2-local pattern based, to greatly improve the effectiveness of GBAW. By including the concept of pattern cluster, the augmented GBAW is kept simple while expanding the pattern family. With the refined GBAW, an encouraging result in circuit optimization is achieved when using it as a perturbation engine. The refinement and achievement are presented in detail in the next section.

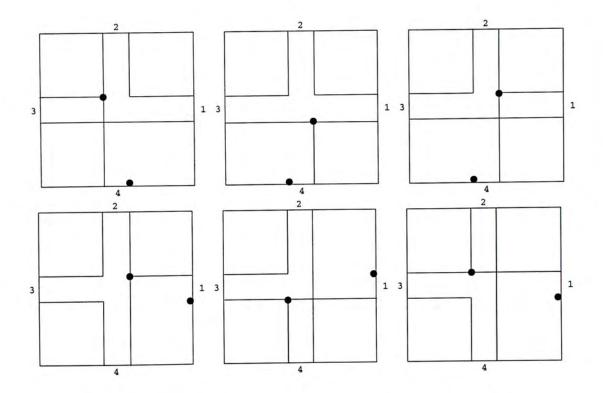

# 3.6 Logic Optimization by using GBAW

A much extended Graph-Based Alternative Wiring (GBAW) scheme to identify alternative wires in multi-level logic with promising results is presented. By modeling subsets of circuits as minimal graphs and applying purely graph-based local pattern search technique, more than 40 graph patterns are found and they contain alternative wires within 2-edge distance from the target wire. Applying proper grouping technique for the similar patterns, the complexity of the rewiring technique can be reduced. Experimental results on MCNC benchmarks show that the technique is much faster than the ATPG-based technique RAMBO with competitive number of alternative wires found. With this augmented pattern family of alternative wires, it is able to find 30% more alternative wires compared to RAMBO with 75 times speedup on average.

GBAW is applied in logic minimization as a perturbation engine and simplify the target circuit by SIS algebraic operations. Results show a further reduction of 11.1% in literal count compared to applying algebraic operations alone.

Table 3.1 shows the number of target wires which have 2-local alternative wires. The results are competitive with RAMBO (98%). For each target wire, it may have more than one alternative wire and some of them may be 2-local patterns. Since RAMBO uses ATPG techniques in locating the alternative wires, and the search space is much larger than GBAW. However, a promising result is obtained by GBAW since backward alternative wire can be done while current RAMBO does not.

|            | RAMBO           | GBAW            | Searched (%)    |

|------------|-----------------|-----------------|-----------------|

| Name       | (target/alter.) | (target/alter.) | (target/alter.) |

| 5xp1       | 10/21           | 10/18           | 100/86          |

| 9sym-hdl   | 5/6             | 5/8             | 100/133         |

| C1908      | 42/57           | 44/44           | 105/77          |

| C2670      | 85/99           | 83/94           | 98/95           |

| C3540      | 208/297         | 238/250         | 114/84          |

| C432       | 33/44           | 40/40           | 121/91          |

| C5315      | 76/113          | 69/73           | 91/65           |

| C6288      | 3/17            | 3/18            | 100/106         |

| C7552      | 132/219         | 76/82           | 58/37           |

| C880       | 27/62           | 27/27           | 100/44          |

| alu2       | 64/100          | 54/56           | 84/56           |

| alu4       | 120/198         | 84/86           | 70/43           |

| apex6      | 72/121          | 68/70           | 94/58           |

| b9_n2      | 8/10            | 3/3             | 38/30           |

| comp       | 28/44           | 17/17           | 61/39           |

| des        | 671/907         | 795/795         | 118/88          |

| duke2      | 35/64           | 29/29           | 83/45           |

| misex3     | 50/167          | 41/41           | 82/25           |

| rot        | 46/75           | 31/32           | 67/43           |

| sao2-hdl   | 25/38           | 9/9             | 36/24           |

| term1      | 41/77           | 27/28           | 66/36           |

| ttt2       | 28/68           | 10/13           | 36/19           |

| <b>x</b> 3 | 71/82           | 76/76           | 107/93          |

| Total      | 1880/2886       | 1839/1909       | 98/66           |

Table 3.1: 2-local pattern comparison

The improved GBAW is implemented on Sun UltraSparc 5 workstation for MCNC benchmark circuits and results are shown in Table 3.2. The smallest benchmark circuit 5xp1.blif is shown in Appendix. The speed and the capability of locating alternative wires between RAMBO and GBAW are also

compared. In the table, it is shown that GBAW are able to find 30% more alternative wires than RAMBO with only 1.38% CPU time on average.

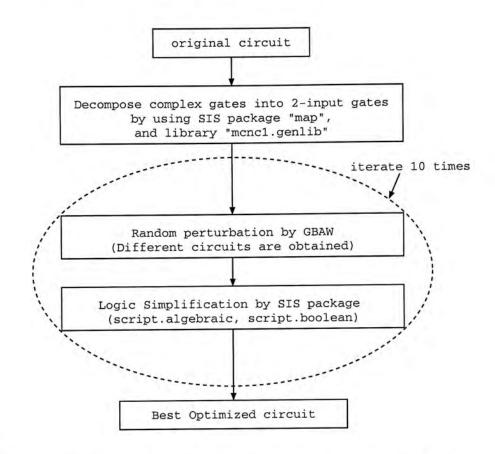

Figure 3.14: The Logic Optimization Process by GBAW and SIS

To demonstrate the application of the proposed scheme, GBAW is deployed in the perturbation and simplification process and depicted in Figure 3.14. In this process, GBAW performed some random transformations on the benchmark circuits and the network structure of the circuit was changed. Then the circuits were minimized by MISII standard script *script.algebraic* provided in SIS package. Before the perturbation using GBAW, the circuits were mapped by SIS command *map* with *mcnc1.genlib* which transforms all the complex gates into gates with 2 fanins. For each circuit, the process was iterated 10 times and all the best results are shown in Table 3.3. The average reduction in circuit size is 43.0% compared to the original circuit. When compared to the minimization with algebraic script alone, a further 11.1% reduction is achieved.

|            | RAMBO      | RAMBO   | GBAW       | GBAW   |

|------------|------------|---------|------------|--------|

| Name       | alt. wires | CPU     | alt. wires | CPU    |

| 5xp1       | 36         | 10.17   | 62         | 0.24   |

| 9sym-hdl   | 27         | 1.56    | 40         | 0.16   |

| C1355      | 185        | 12.82   | 250        | 0.89   |

| C1908      | 127        | 33.52   | 240        | 0.68   |

| C2670      | 267        | 83.57   | 344        | 1.33   |

| C3540      | 569        | 273.80  | 816        | 2.15   |

| C432       | 129        | 10.26   | 188        | 0.37   |

| C499       | 16         | 6.05    | 34         | 0.6    |

| C5315      | 511        | 155.91  | 713        | 2.88   |

| C6288      | 1352       | 361.18  | 2191       | 4.18   |

| C7552      | 1709       | 143.95  | 617        | 4.2    |

| C880       | 151        | 9.86    | 239        | 0.66   |

| alu2       | 169        | 214.71  | 263        | 0.84   |

| alu4       | 333        | 270.50  | 493        | 1.61   |

| apex6      | 239        | 34.32   | 377        | 1.23   |

| b9_n2      | 48         | 1.65    | 71         | 0.17   |

| comp       | 57         | 9.18    | 58         | 0.21   |

| des        | 1468       | 729.92  | 2204       | 8.7    |

| duke2      | 157        | 46.55   | 281        | 0.63   |

| f51m       | 49         | 6.19    | 65         | 0.25   |

| misex      | 216        | 124.48  | 439        | 0.97   |

| my_adder   | 46         | 1.16    | 0          | 0.23   |

| pcler8     | 29         | 1.3     | 30         | 0.12   |

| rot        | 243        | 48.04   | 406        | 1.1    |

| sao2-hdl   | 104        | 16.86   | 153        | 0.39   |

| term1      | 106        | 16.81   | 169        | 0.37   |

| ttt2       | 68         | 9.68    | 133        | 0.34   |

| <b>x</b> 3 | 228        | 23.13   | 348        | 1.2    |

| Total      | 8639       | 2657.13 | 11224      | 36.7   |

| Normalized | 1          | 1       | 1.2992     | 0.0138 |

Table 3.2: Comparison between RAMBO and GBAW

## 3.7 Conclusions

In this chapter, an augmented Graph-Based Alternative Wiring (GBAW) scheme is presented. Although there are more than 40 patterns included, an attractive efficiency is still maintained by using proper grouping of pattern families. GBAW has forward and backward search capability and can identify alternative wire efficiently. Experimental results showed that it is capable to find 30% more alternative wires comparing with the forward search RAMBO version. GBAW has a good coverage of alternative wires with 75 times speedup on average. When using GBAW as the perturbation engine and combining with SIS algebraic operations, there is a further reduction of 11.1% comparing with the results by algebraic operations alone.

| Circuit    | Circuit Size(lit.)of |       |         | Size reduction vs. |       |

|------------|----------------------|-------|---------|--------------------|-------|

|            | Original             | MISII | Perturb | Original           | MISII |

| 5xp1       | 235                  | 172   | 125     | 0.468              | 0.273 |

| 9sym-hdl   | 232                  | 138   | 93      | 0.599              | 0.326 |

| C1908      | 883                  | 582   | 524     | 0.407              | 0.100 |

| C2670      | 1444                 | 800   | 714     | 0.506              | 0.108 |

| C3540      | 2267                 | 1398  | 1367    | 0.397              | 0.022 |

| C432       | 392                  | 296   | 229     | 0.416              | 0.226 |

| C499       | 854                  | 559   | 552     | 0.354              | 0.013 |

| C5315      | 3282                 | 1970  | 1875    | 0.429              | 0.048 |

| C6288      | 5195                 | 3393  | 3339    | 0.357              | 0.016 |

| C7552      | 4105                 | 2423  | 2285    | 0.443              | 0.057 |

| alu2       | 777                  | 488   | 474     | 0.390              | 0.029 |

| alu4       | 1470                 | 921   | 904     | 0.385              | 0.018 |

| apex6      | 1417                 | 856   | 839     | 0.408              | 0.020 |

| b9_n2      | 208                  | 141   | 130     | 0.375              | 0.078 |

| comp       | 270                  | 170   | 141     | 0.478              | 0.171 |

| des        | 6655                 | 3915  | 3766    | 0.434              | 0.038 |

| duke2      | 676                  | 430   | 416     | 0.385              | 0.033 |

| f51m       | 244                  | 169   | 146     | 0.402              | 0.136 |

| misex3     | 990                  | 644   | 593     | 0.401              | 0.079 |

| my_adder   | 339                  | 304   | 197     | 0.419              | 0.352 |

| pcler8     | 174                  | 105   | 96      | 0.448              | 0.086 |

| rot        | 1251                 | 797   | 762     | 0.391              | 0.044 |

| sao2-hdl   | 439                  | 271   | 221     | 0.497              | 0.185 |

| term1      | 439                  | 263   | 220     | 0.499              | 0.163 |

| ttt2       | 376                  | 237   | 203     | 0.460              | 0.143 |

| Total      | 34614                | 21442 | 20211   | Average reduction  |       |

| Normalized | 1                    |       | 0.5857  | 43.0%              | 11.1% |

| Normalized |                      | 1     | 0.9426  |                    |       |

Table 3.3: Results for logic optimization

It is also observed that RAMBO is still more flexible in locating the maximum number of all possible alternative wires, it might be a good approach to couple both the advantages of RAMBO and GBAW for various emphasis of CAD applications. The future direction is to extend the set of k-local pattern to cover more alternative wires for practical complex gates, extract more quantitative analysis of alternative wire pattern distributions for different kinds of circuits, which could turn to be useful for new macro library cell designs. More efficient algorithm will be developed to choose the suitable alternative wire for perturbation and to apply the GBAW technique on other CAD problems such as floorplanning and partitioning.

# Chapter 4

# Multi-way Partitioning using Rewiring Techniques

## 4.1 Introduction

The objective of circuit partitioning is to divide the circuit into sub-circuits such that the size of each component is reasonable and the number of inter-connections between the components is minimized. As design scale expands, partitioning becomes increasingly important to circuit design automation.

Traditionally, circuit partitioning is done by simply modeling the circuit as a graph (or hypergraph). Graph partitioning problems are known to be NP-hard [WC91]. A comprehensive survey [AK95b] has presented the recent directions of partitioning. Commonly used partitioning algorithms can be categorized into three classes. The first class strictly abide by the modeling graph, with no attempt to change the graph. High quality results have been reported by several algorithms which include iterative improvement based [WC91, FM82, DD96], clustering based [YCL92], and spectrum (eigenvector) based [HK91, ZSC96]. The second class of algorithms may modify the graph through node replications [KN91, MW96, EHS97, YW98]. Improvement is achieved by sacrificing some area due to node replications. These two classes both perform the partitioning task on the graph without considering the logic function of

the circuit. The third class [CLMS95, BLSV92, CCMS93, KBZ94] couples the graph domain (nodes and their connections) and logic domain (function perform by each node). The tradeoff of improving the partitioning results is the expensive computational cost [BLSV92, CCMS93] and may only be applied to Field-Programmable Gate Array (FPGA) circuits [KBZ94].

Recently, many research works on multi-level partitioning are proposed [HL93a, HL93b, KK95c, KAKS97, AHK97b, WA98, KK99]. The general idea behind multi-level partitioning is to first cluster the whole problem by some useful algorithms to reduce the size, then apply a well-known graph domain partitioner on the coarsened graph to get a good initial solution. The graph is then unclustered and a suitable partitioning refinement algorithm is applied in order to adjust the cut edge between partitions. The quality and the runtime by multi-level partitioning are very encouraging. In particular, Karypis and Kumar [KK99] proposes a partitioner called hMETIS-Kway. It first coarsens the hypergraph, then recursively bisects the graph into k-parts, followed by uncoarsening the hypergraph with refinement algorithms. More recent research works [CKM00, CL00a, CL00b], in comparison with hMetis-Kway, showed that the solution by hMetis-Kway is of high quality that the cut size cannot be further reduced greatly.

Alternative wiring (rewiring) is the technique of adding single or multiple redundant wires or gates to a circuit such that other wires or gates become redundant and thus removable. This logic domain technique has been widely used for solving many logic level and physical level design problems [CE93, CMSC96, CLMS95, CCWMS94a, CCWM97, CMS94]. Circuit performance can be improved by removing a wire on the critical path and adding its alternative wire elsewhere. Circuit routability can also be improved by substituting an unroutable wire in congested area by a routable alternative wire in some other circuit part. The cut size of a partition can be reduced by replacing the wires crossing the cut line.

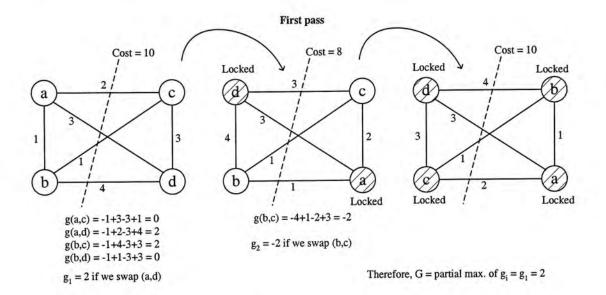

Figure 4.1: Circuit partitioning by rewiring