# CMOS RF Low Noise Amplifier with High ESD Immunity

#### TANG SIU KEI

## A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF PHILOSOPHY

IN

ELECTRONIC ENGINEERING

©The Chinese University of Hong Kong August 2004

The Chinese University of Hong Kong holds the copyright of this thesis. Any person(s) intending to use a part or whole of the materials in the thesis in a proposed publication must seek copyright release from the Dean of the Graduate School.

£100

# Acknowledgements

I would like to express my gratitude to some persons who have helped me throughout my research study. First, I am indebted to my supervisor, Professor C. F. Chan, for his guidance and valuable advice in my undergraduate and master programs in the Chinese University of Hong Kong.

I would also like to express my appreciation to Sin Hang Cheng Tony and Wang Chi Cheng for sharing with me their design experience and techniques. I wish to thank the laboratory technicians, Wing Yee Yeung and Kwok Kin Tse, for their technical support on circuit design tools and measurement equipment. Special thanks are given to Kelvin Cheung and Jessica Leung in Solomon Systech Limited, who have helped me to complete the ESD testing.

I also want to thank my best friend, Chi Wai Chow, for his support and tolerance. Finally, I am grateful to my family and Siu Wa Lee for their love and encouragement. Siu Wa Lee has given her great confidence to me and lets me recognize myself in both working and living.

ii

### Abstract of thesis entitled: CMOS RF Low Noise Amplifier with High ESD Immunity submitted by TANG SIU KEI for the degree of Master of Philosophy in Electronic Engineering at The Chinese University of Hong Kong in June 2004

In this thesis, a new Electro-Static Discharge (ESD) protection method, which is called Common-Gate Input Stage Method (CGISM), is introduced for CMOS RF Low Noise Amplifier (LNA). It utilizes a common-gate amplifier as an input stage to reduce the possibility of the gate oxide breakdown. The major reason for this improvement is that the RF input is connected to the source of the transistor, instead to the gate in CGISM. As a result, it increases ESD immunity of the new LNA by preventing the ESD current from discharging through the thin gate oxide. In addition, the proposed method does not degrade of the LNA performance.

To verify the feasibility of the proposed CGISM circuit to protect CMOS RF LNA, a 1.8 GHz ESD-protected LNA with CGISM and a traditional common-source LNA have been fabricated using an AMS 0.35-µm CMOS technology. In the Human Body Model (HBM) ESD test, the proposed ESD-protected LNA is proved to be capable of surviving positive ESD pulse up to 1.5 kV and negative ESD pulse down to -3.5 kV. In contrast, the common-source LNA can only survive ESD pulse from -200 V to 200 V. These measurement results show the functionality of CGISM. It can substantially improve the ESD immunity of LNA.

Regarding the LNA performance, the measurement results show that the proposed LNA demonstrates a typical performance at 1.5 V low supply voltage.

The power gain, noise figure, input-referred 1-dB compression point and input third-order intercept point (IIP3) are approximately 13.7 dB, 5.3 dB, -16.6 dBm and -7.8 dBm, respectively. The new LNA has the measured performance as good as conventional designs.

摘要

本論文爲 CMOS 射頻電路中的低雜訊放大器提供了一種稱爲共柵輸入級 (CGISM) 的新靜電 (ESD) 保護技術。它使用了一個共柵放大器作爲輸入級, 能夠大大減少柵氧化層被擊穿的概率。這是由於射頻電路的輸入不是連接在共 柵輸入級中電晶體的柵極,而是連接在電晶體的源極。因此,通過阻止靜電電 流經較薄的柵氧化層放電,這大大提高了低雜訊放大器電路的靜電保護性能。 同時,提出的保護技術能維持低雜訊放大器的原有性能。

爲了驗證本文提出的 CMOS 射頻電路低雜訊放大器共柵輸入級技術的可實 現性,我們使用 AMS 0.35 微米 CMOS 製造工藝設計了兩個低雜訊放大器,一 個爲 1.8 千兆赫茲,帶有共柵輸入級靜電保護,另一個則是傳統的低雜訊放大 器。在人體模型 (HBM) 靜電測試中,本文的設計能夠正常工作在-3.5kV~1.5kV 的靜電脈衝下;與此相比,傳統的共源低雜訊放大器只能工作在-200V~200V 的 有限範圍內。測試結果證明了本文提出的共柵輸入級電路能夠有效的提高低雜 訊放大器的靜電保護能力。

同時,在性能方面,測試結果顯示本文設計的低雜訊放大器在1.5V的低輸入電壓下顯示出普遍的性能。能量增益,雜訊形狀,輸入-1dB功率飽和點以及輸入三階截距點(IIP3)分別爲13.7dB,5.3dB,-16.6dB和-7.8dB,這新的低雜訊放大器具有和傳統設計同樣的測量性能。

v

# Contents

| Acknowled    | gements                                                | ii  |

|--------------|--------------------------------------------------------|-----|

| Abstract     |                                                        | iii |

| List of Figu | ires                                                   | xi  |

| List of Tabl | les                                                    | xvi |

| Chapter 1    | Introduction                                           | 1   |

| 1.1          | Overview of Electrostatic Discharge                    | 1   |

|              | 1.1.1 Classification of Electrostatic Discharge Models | 1   |

| 1.2          | Electrostatic Discharge in CMOS RF Circuits            | 4   |

| 1.3          | Research Goal and Contribution                         | 6   |

| 1.4          | Thesis Outline                                         | 6   |

| Chapter 2    | <b>Performance Parameters of Amplifier</b>             | 8   |

| 2.1          | Amplifier Gain                                         | 8   |

| 2.2          | Noise Factor                                           | 9   |

| 2.3          | Linearity                                              | 11  |

|              | 2.3.1 1-dB Compression Point                           | 13  |

|              | 2.3.2 Third-Order Intercept Point                      | 14  |

| 2.4          | Return Loss                                            | 16  |

| 2.5          | Power Consumption                                      | 18  |

| 2.6               | HBM ESD Withstand Voltage                                                                                                                                                                                                                                                                                | 19                                                                                                         |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| Chapter 3         | ESD Protection Methodology for Low Noise                                                                                                                                                                                                                                                                 |                                                                                                            |

|                   | Amplifier                                                                                                                                                                                                                                                                                                | 21                                                                                                         |

| 3.1               | Dual-Diode Circuitry                                                                                                                                                                                                                                                                                     | 22                                                                                                         |

|                   | 3.1.1 Working Principle                                                                                                                                                                                                                                                                                  | 22                                                                                                         |

|                   | 3.1.2 Drawbacks                                                                                                                                                                                                                                                                                          | 24                                                                                                         |

| 3.2               | Shunt-Inductor Method                                                                                                                                                                                                                                                                                    | 25                                                                                                         |

|                   | 3.2.1 Working Principle                                                                                                                                                                                                                                                                                  | 25                                                                                                         |

|                   | 3.2.2 Drawbacks                                                                                                                                                                                                                                                                                          | 27                                                                                                         |

| 3.3               | Common-Gate Input Stage Method                                                                                                                                                                                                                                                                           | 28                                                                                                         |

|                   | 3.3.1 Built-In ESD Protecting Mechanism                                                                                                                                                                                                                                                                  | 29                                                                                                         |

|                   | 3.3.2 Competitiveness                                                                                                                                                                                                                                                                                    | 31                                                                                                         |

|                   |                                                                                                                                                                                                                                                                                                          |                                                                                                            |

| Chapter 4         | <b>Design Theory of Low Noise Amplifier</b>                                                                                                                                                                                                                                                              | 32                                                                                                         |

|                   | Design Theory of Low Noise Amplifier<br>Small-Signal Modeling                                                                                                                                                                                                                                            | <b>32</b><br>33                                                                                            |

| 4.1               |                                                                                                                                                                                                                                                                                                          |                                                                                                            |

| 4.1               | Small-Signal Modeling                                                                                                                                                                                                                                                                                    | 33                                                                                                         |

| 4.1               | Small-Signal Modeling<br>Method of Input Termination                                                                                                                                                                                                                                                     | 33<br>33                                                                                                   |

| 4.1               | Small-Signal Modeling<br>Method of Input Termination<br>4.2.1 Resistive Termination                                                                                                                                                                                                                      | 33<br>33<br>34                                                                                             |

| 4.1               | <ul> <li>Small-Signal Modeling</li> <li>Method of Input Termination</li> <li>4.2.1 Resistive Termination</li> <li>4.2.2 Shunt-Series Feedback</li> </ul>                                                                                                                                                 | 33<br>33<br>34<br>34                                                                                       |

| 4.1<br>4.2        | <ul> <li>Small-Signal Modeling</li> <li>Method of Input Termination</li> <li>4.2.1 Resistive Termination</li> <li>4.2.2 Shunt-Series Feedback</li> <li>4.2.3 1/gm Termination</li> </ul>                                                                                                                 | <ul> <li>33</li> <li>33</li> <li>34</li> <li>34</li> <li>35</li> </ul>                                     |

| 4.1<br>4.2        | <ul> <li>Small-Signal Modeling</li> <li>Method of Input Termination</li> <li>4.2.1 Resistive Termination</li> <li>4.2.2 Shunt-Series Feedback</li> <li>4.2.3 1/gm Termination</li> <li>4.2.4 Inductive Source Degeneration</li> </ul>                                                                    | <ul> <li>33</li> <li>33</li> <li>34</li> <li>34</li> <li>35</li> <li>36</li> </ul>                         |

| 4.1<br>4.2        | <ul> <li>Small-Signal Modeling</li> <li>Method of Input Termination</li> <li>4.2.1 Resistive Termination</li> <li>4.2.2 Shunt-Series Feedback</li> <li>4.2.3 1/gm Termination</li> <li>4.2.4 Inductive Source Degeneration</li> <li>Method of Gain Enhancement</li> </ul>                                | <ul> <li>33</li> <li>33</li> <li>34</li> <li>34</li> <li>35</li> <li>36</li> <li>38</li> </ul>             |

| 4.1<br>4.2<br>4.3 | <ul> <li>Small-Signal Modeling</li> <li>Method of Input Termination</li> <li>4.2.1 Resistive Termination</li> <li>4.2.2 Shunt-Series Feedback</li> <li>4.2.3 1/gm Termination</li> <li>4.2.4 Inductive Source Degeneration</li> <li>Method of Gain Enhancement</li> <li>4.3.1 Tuned Amplifier</li> </ul> | <ul> <li>33</li> <li>33</li> <li>34</li> <li>34</li> <li>35</li> <li>36</li> <li>38</li> <li>38</li> </ul> |

|           | 4.4.2 Cascoded Amplifier                           | 42 |

|-----------|----------------------------------------------------|----|

| Chapter 5 | Noise Analysis of Low Noise Amplifier              | 44 |

| 5.1       | Noise Sources of MOS Transistor                    | 44 |

| 5.2       | Noise Calculation using Noisy Two-Port Network     | 46 |

| 5.3       | Noise Calculation using Small-Signal Model         | 49 |

|           | 5.3.1 Low Noise Amplifier with Inductive Source    |    |

|           | Degeneration                                       | 49 |

|           | 5.3.2 Common-Gate Low Noise Amplifier              | 52 |

| Chapter 6 | Design of an ESD-protected CMOS Low Noise          |    |

|           | Amplifier                                          | 54 |

| 6.1       | Design of DC Biasing Circuitry                     | 55 |

| 6.2       | Design of Two-Stage Architecture                   | 57 |

|           | 8.3.1 Design of Common-Gate Input Stage            | 57 |

|           | 8.3.2 Design of Second-Stage Amplifier             | 59 |

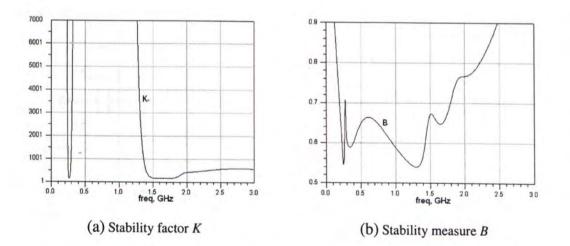

| 6.3       | Stability Consideration                            | 61 |

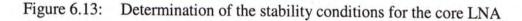

| 6.4       | Design of Matching Networks                        | 62 |

|           | 6.4.1 Design of Inter-Stage Matching Network       | 64 |

|           | 6.4.2 Design of Input and Output Matching Networks | 67 |

| Chapter 7 | Layout Considerations                              | 70 |

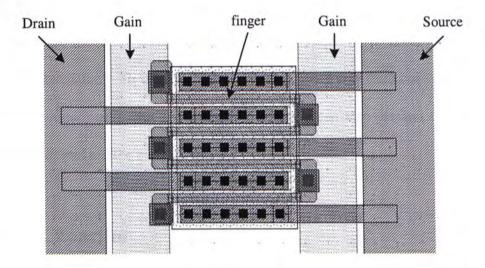

| 7.1       | MOS Transistor                                     | 70 |

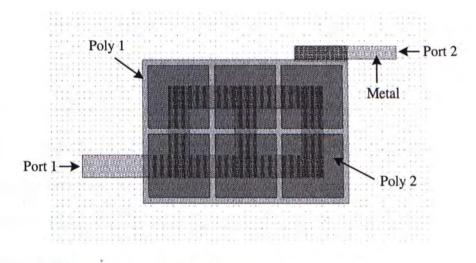

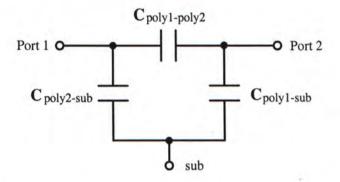

| 7.2       | Capacitor                                          | 72 |

| 7.3       | Spiral Inductor                                    | 74 |

| 7.4       | Layout of the Proposed Low Noise Amplifier         | 76 |

| 7.5       | Layout of the Common-Source Low Noise Amplifier    | 79 |

| 7.6       | Comparisor        | between Schematic and Post-Layout Simulation     |     |

|-----------|-------------------|--------------------------------------------------|-----|

|           | Results           |                                                  | 81  |

| Chapter 8 | Measure           | ment Results                                     | 82  |

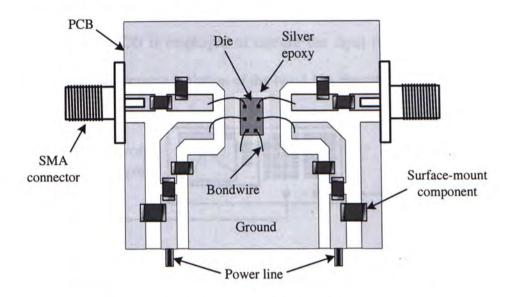

| 8.1       | Experiment        | al Setup                                         | 82  |

|           | 8.1.1 Test        | ing Circuit Board                                | 83  |

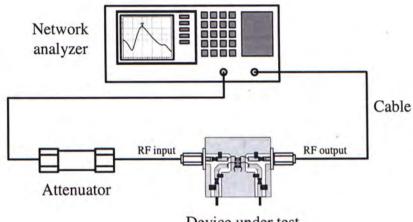

|           | 8.1.2 Exp         | erimental Setup for S-parameter                  | 84  |

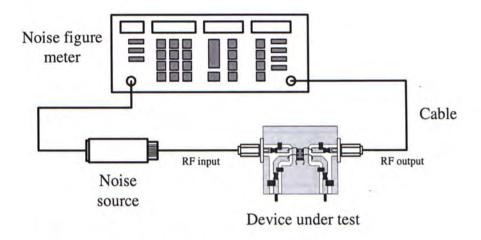

|           | 8.1.3 Exp         | erimental Setup for Noise Figure                 | 84  |

|           | 8.1.4 Exp         | perimental Setup for 1-dB Compression Point      | 85  |

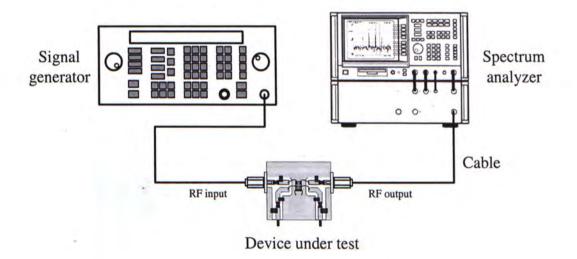

|           | 8.1.5 Exp         | perimental Setup for Third-Order Intercept Point | 86  |

|           | 8.1.6 Setu        | up for HBM ESD Test                              | 87  |

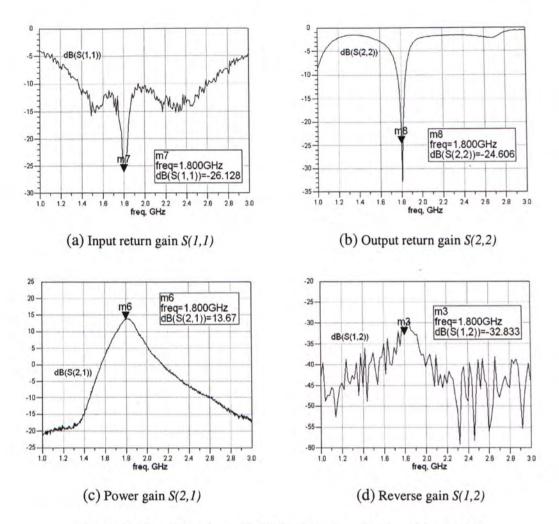

| 8.2       | Measureme         | ent Results of the Proposed Low Noise Amplifier  | 89  |

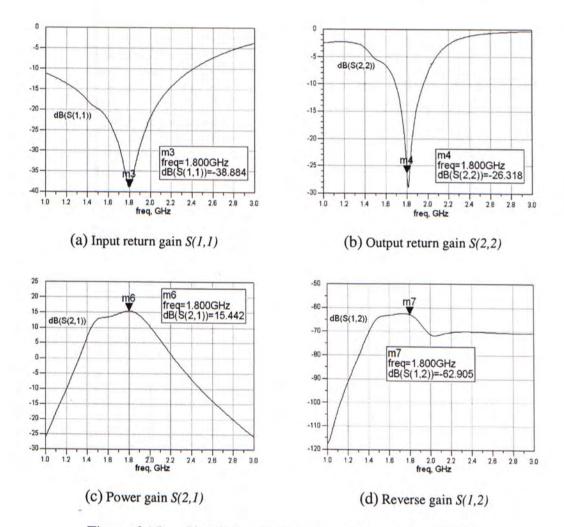

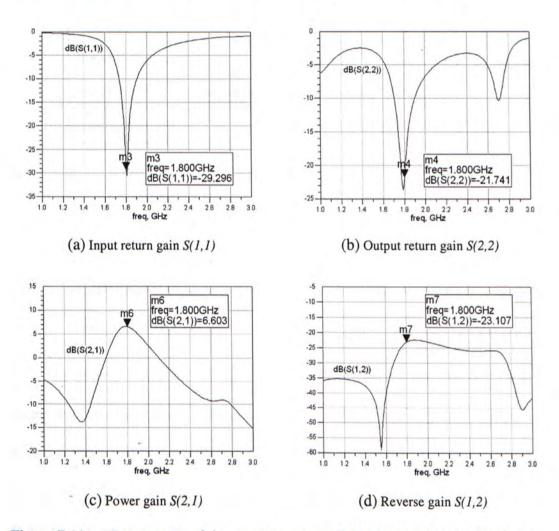

|           | 8.2.1 S-pa        | arameter Measurement                             | 90  |

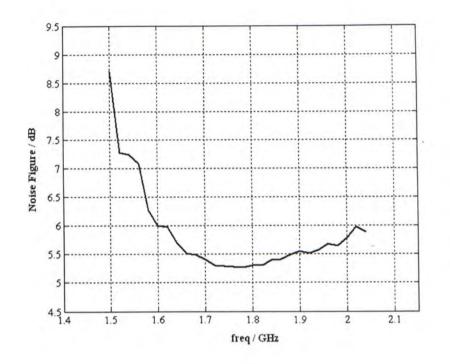

|           | 8.2.2 Noi         | se Figure Measurement                            | 91  |

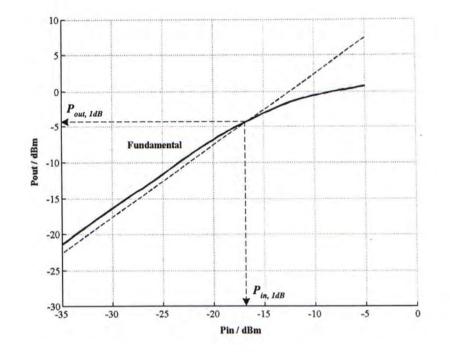

|           | 8.2.3 Me          | asurement of 1-dB Compression Point              | 92  |

|           | 8.2.4 Me          | asurement of Third-Order Intercept Point         | 93  |

|           | 8.2.5 HB          | M ESD Test                                       | 94  |

|           | 8.2.6 Sur         | nmary of Measurement Results                     | 95  |

| 8.3       | Measureme         | ent Results of the Common-Source Low Noise       |     |

|           | Amplifier         |                                                  | 96  |

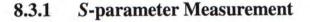

|           | 8.3.1 <i>S</i> -p | arameter Measurement                             | 97  |

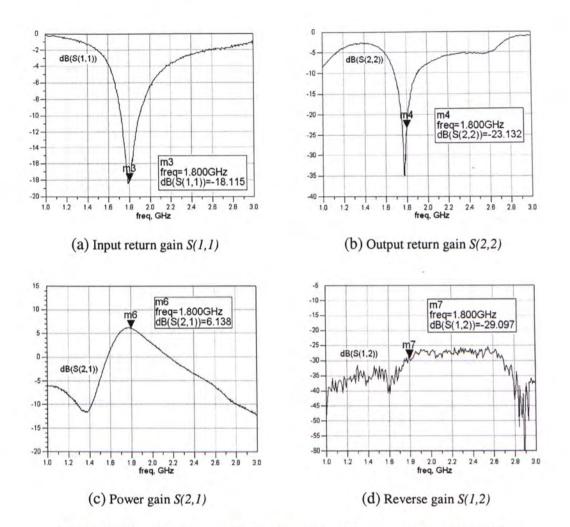

|           | 8.3.2 No          | ise Figure Measurement                           | 98  |

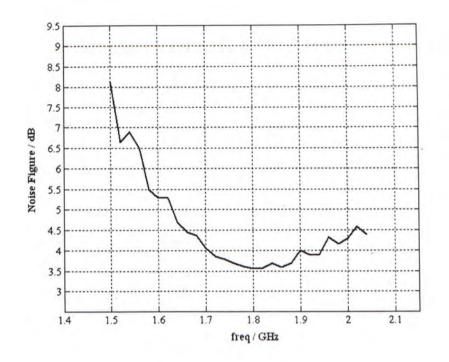

|           | 8.3.3 Me          | asurement of 1-dB Compression Point              | 99  |

|           | 8.3.4 Me          | easurement of Third-Order Intercept Point        | 100 |

|           | 8.3.5 HB          | BM ESD Test                                      | 101 |

|           | 8.3.6 Su          | mmary of Measurement Results                     | 102 |

|           |                   |                                                  |     |

| 8.4        | Performance Comparison between Different Low | w Noise |

|------------|----------------------------------------------|---------|

|            | Amplifier Designs                            | 103     |

| Chapter 9  | <b>Conclusion and Future Work</b>            | 105     |

| 9.1        | Conclusion                                   | 105     |

| 9.2        | Future Work                                  | 106     |

| References |                                              | 107     |

| Author's P | ublications                                  | 112     |

1000

# **List of Figures**

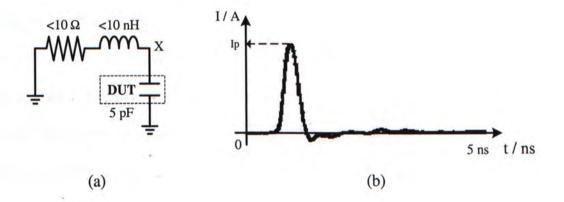

| Figure 1.1 | (a) The schematic of HBM and (b) the pulse waveform at X    | 2  |

|------------|-------------------------------------------------------------|----|

| Figure 1.2 | (a) The schematic of MM and (b) the pulse waveform at X     | 3  |

| Figure 1.3 | (a) The schematic of CDM and (b) the pulse waveform at X    | 3  |

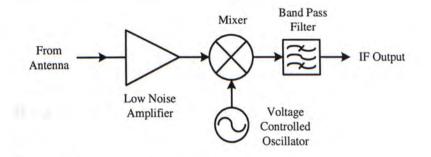

| Figure 1.4 | An RF front-end for wireless communications                 | 5  |

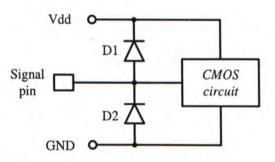

| Figure 1.5 | Dual-diode circuitry used in CMOS digital and mixed-signal  |    |

|            | circuits                                                    | 5  |

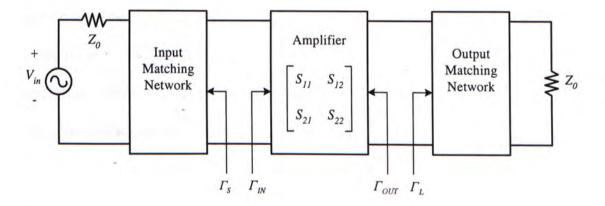

| Figure 2.1 | A microwave amplifier block diagram                         | 8  |

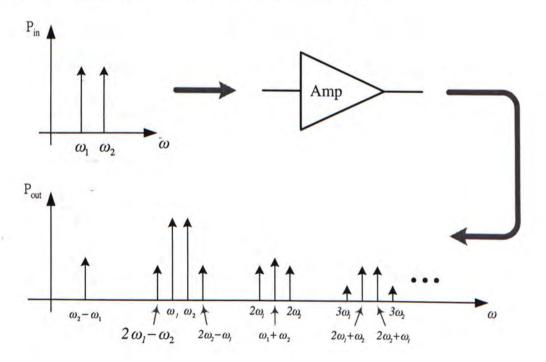

| Figure 2.2 | Non-linear effect of RF amplifier                           | 11 |

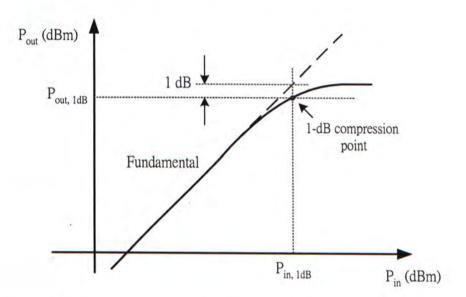

| Figure 2.3 | Determination of 1-dB compression point                     | 13 |

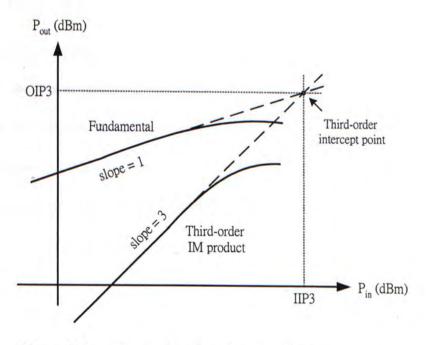

| Figure 2.4 | Determination of third-order intercept point                | 15 |

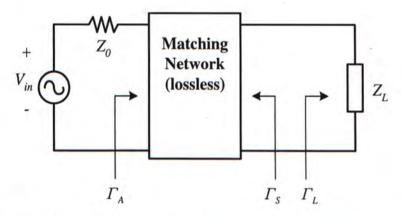

| Figure 2.5 | Impedance transformation by matching network                | 17 |

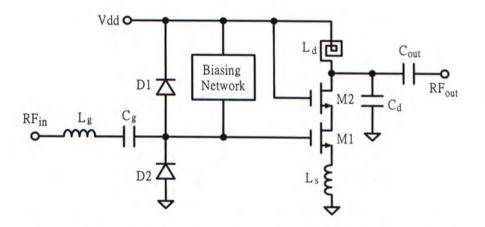

| Figure 3.1 | LNA with dual-diode ESD protection circuitry                | 22 |

| Figure 3.2 | ESD current flow in dual-diode circuitry in the case of (a) |    |

|            | positive ESD pulse; (b) negative ESD pulse                  | 23 |

| Figure 3.3 | LNA with shunt inductor as ESD protection                   | 25 |

| Figure 3.4 | ESD current flow in shunt-inductor circuitry in the case of |    |

| ŵ.         | (a) positive ESD pulse; (b) negative ESD pulse              | 26 |

| Figure 3.5 | Schematic diagram of a common-gate amplifier                | 28 |

| Figure 3.6 | Simplified circuit model of a NMOS transistor               | 29 |

| Figure 3.7 | Built-in ESD protecting mechanism of CGISM                  | 30 |

| Figure 4.1  | Small-signal model of a MOS transistor                    | 33 |

|-------------|-----------------------------------------------------------|----|

| Figure 4.2  | Input impedance matching by resistive termination         | 34 |

| Figure 4.3  | Input impedance matching by shunt-series feedback         | 34 |

| Figure 4.4  | Input impedance matching by $1/g_m$ termination           | 35 |

| Figure 4.5  | Small-signal analysis of a common-gate topology           | 35 |

| Figure 4.6  | Input impedance matching by inductive source degeneration | 36 |

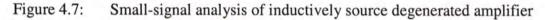

| Figure 4.7  | Small-signal analysis of inductively source degenerated   |    |

|             | amplifier                                                 | 37 |

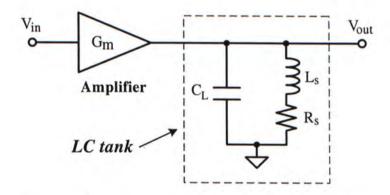

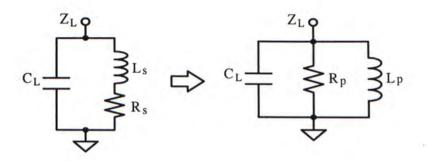

| Figure 4.8  | Tuned amplifier with LC tank circuit                      | 38 |

| Figure 4.9  | Conversion of LC tank                                     | 39 |

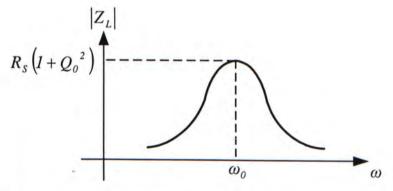

| Figure 4.10 | Frequency response of the LC tank impedance               | 39 |

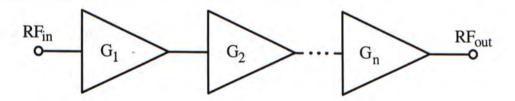

| Figure 4.11 | Multistage amplifier using cascading technique            | 40 |

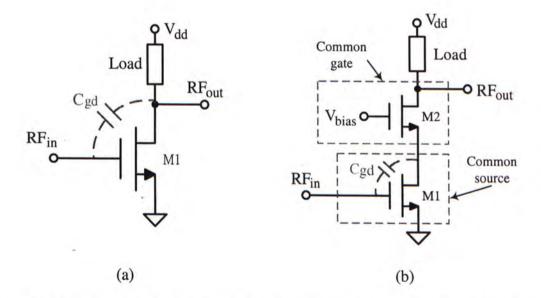

| Figure 4.12 | Small-signal model of a common-gate LNA                   | 42 |

| Figure 4.13 | Common-source LNA (a) without cascoding transistor, (b)   |    |

|             | with the cascoding transistor M2                          | 42 |

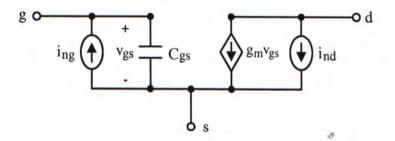

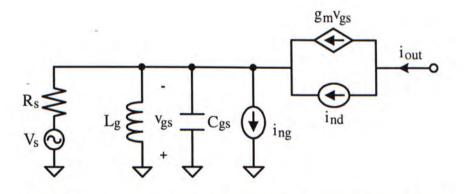

| Figure 5.1  | Noise model of MOS transistor                             | 44 |

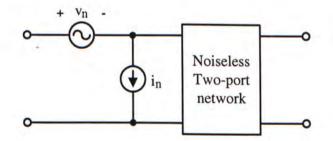

| Figure 5.2  | Representation of a noisy two-port network                | 45 |

| Figure 5.3  | Noise model for calculation of LNA noise factor           | 46 |

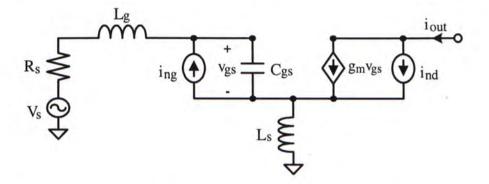

| Figure 5.4  | Small-signal noise model of an inductively source         |    |

|             | degenerated LNA                                           | 49 |

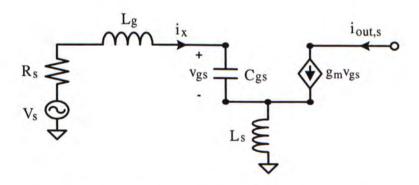

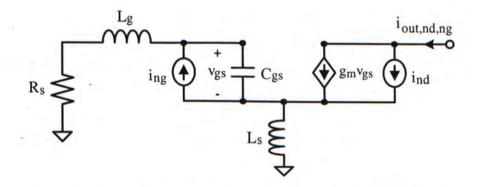

| Figure 5.5  | Small-signal noise model with $V_s$ only                  | 49 |

| Figure 5.6  | Small-signal noise model with $i_{nd}$ and $i_{ng}$ only  | 50 |

| Figure 5.7  | Small-signal noise model of a common-gate LNA             | 52 |

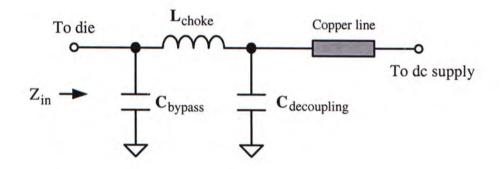

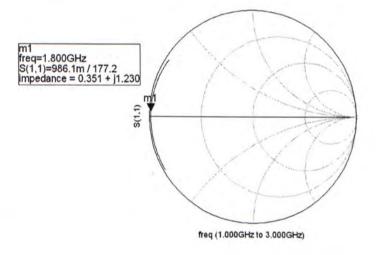

| Figure 6.1  | DC biasing circuitry of the LNA                           | 55 |

| Figure 6.2  | Simulated impedance of the DC biasing circuit              | 56 |

|-------------|------------------------------------------------------------|----|

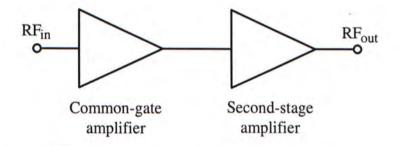

| Figure 6.3  | Architecture of the proposed LNA                           | 57 |

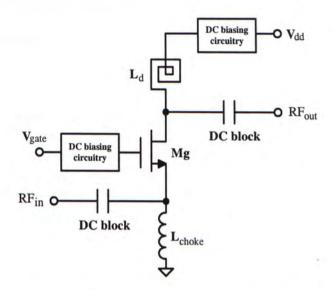

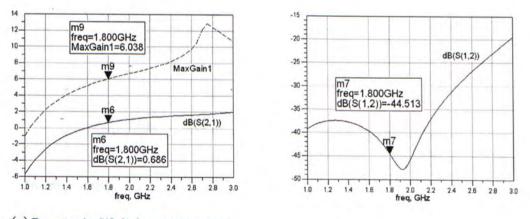

| Figure 6.4  | Schematic of the common-gate input stage                   | 58 |

| Figure 6.5  | Simulation results of the common-gate input stage          | 58 |

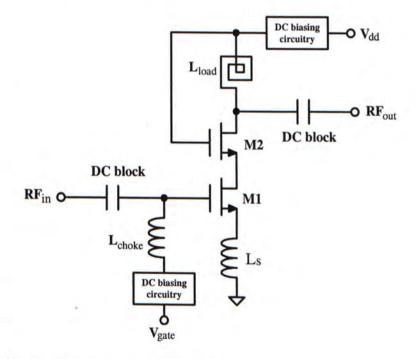

| Figure 6.6  | Schematic of the second-stage amplifier                    | 59 |

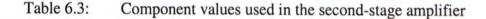

| Figure 6.7  | Simulation results of the second-stage amplifier           | 60 |

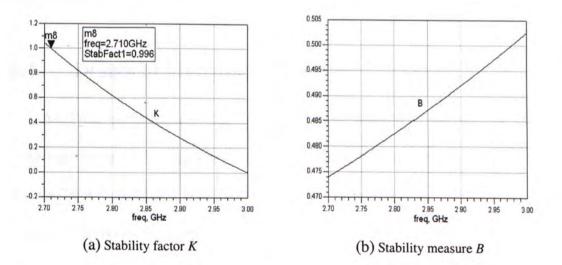

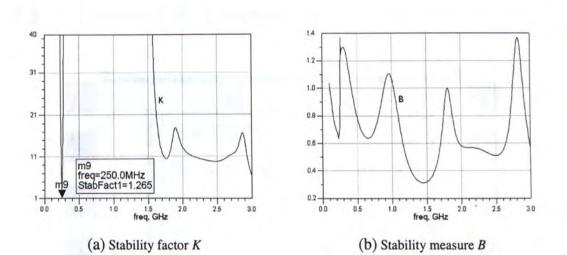

| Figure 6.8  | Unstable region of the common-gate input stage             | 61 |

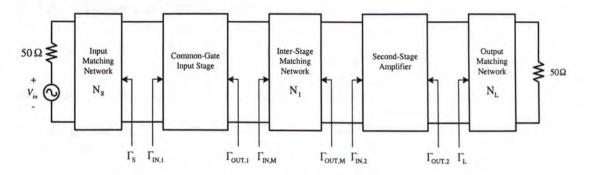

| Figure 6.9  | Block diagram of the overall proposed LNA                  | 63 |

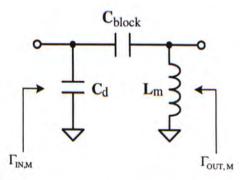

| Figure 6.10 | Schematic of the inter-stage matching network              | 64 |

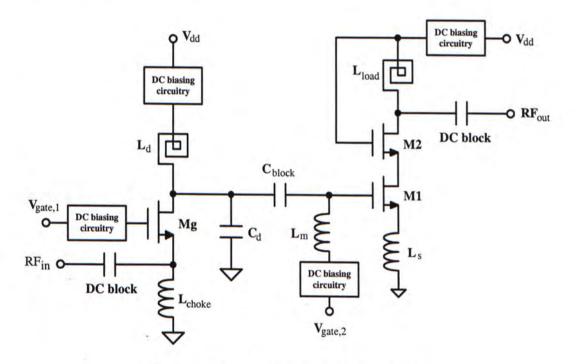

| Figure 6.11 | Schematic of the core LNA                                  | 65 |

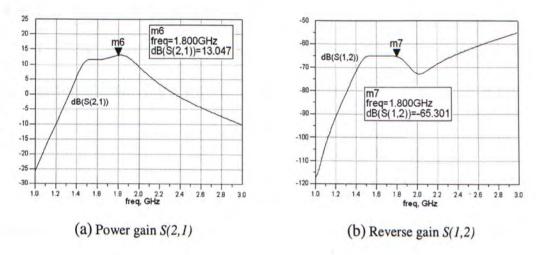

| Figure 6.12 | Simulation results of the core LNA                         | 66 |

| Figure 6.13 | Determination of the stability conditions for the core LNA | 66 |

| Figure 6.14 | Schematics of the two matching networks                    | 67 |

| Figure 6.15 | Simulation S-parameter of the proposed LNA                 | 68 |

| Figure 7.1  | Layout design of the MOS transistor                        | 71 |

| Figure 7.2  | Layout design of the poly-poly capacitor                   | 72 |

| Figure 7.3  | Schematic modeling of the poly-poly capacitor              | 73 |

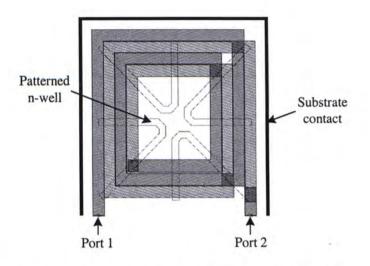

| Figure 7.4  | Layout design of the spiral inductor                       | 74 |

| Figure 7.5  | Schematic modeling of the spiral inductor                  | 75 |

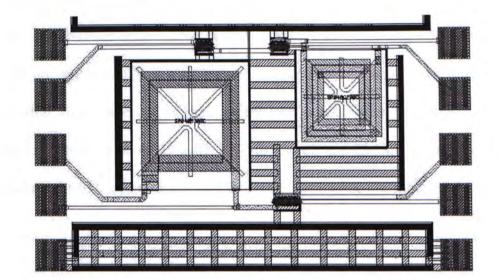

| Figure 7.6  | Layout design of the proposed LNA                          | 76 |

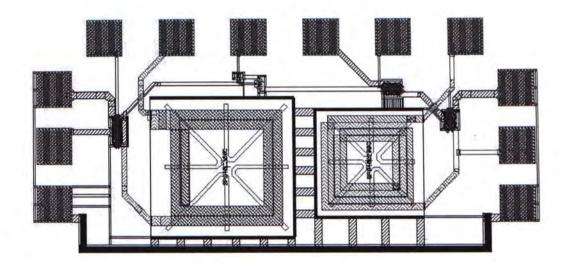

| Figure 7.7  | S-parameter of the proposed LNA in post-layout simulation  | 77 |

| Figure 7.8  | Determination of the stability conditions for the proposed |    |

|             | LNA in post-layout simulation                              | 78 |

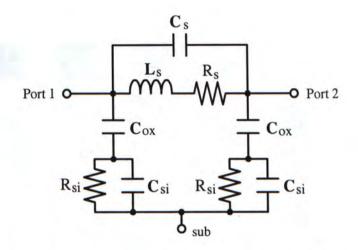

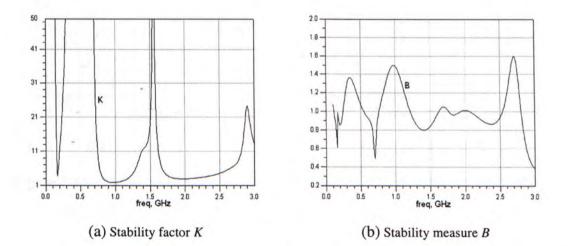

| Figure 7.9  | Layout design of the common-source LNA                     | 79 |

| Figure 7.10 | Determination of the stability conditions for the          |    |

|             | common-source LNA in post-layout simulation                     | 79 |

|-------------|-----------------------------------------------------------------|----|

| Figure 7.11 | S-parameter of the common-source LNA in post-layout             |    |

|             | simulation                                                      | 80 |

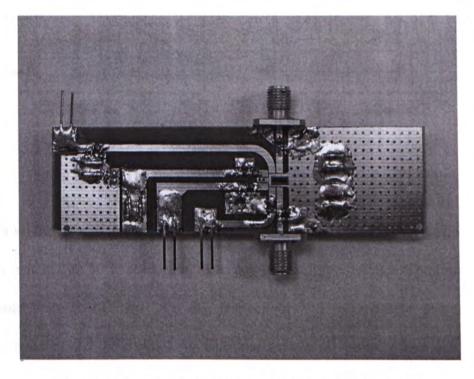

| Figure 8.1  | A testing circuit board for measurement                         | 83 |

| Figure 8.2  | The setup for the S-parameter measurement                       | 84 |

| Figure 8.3  | The setup for the noise figure measurement                      | 85 |

| Figure 8.4  | The setup for the measurement of the 1-dB compression           |    |

|             | point                                                           | 85 |

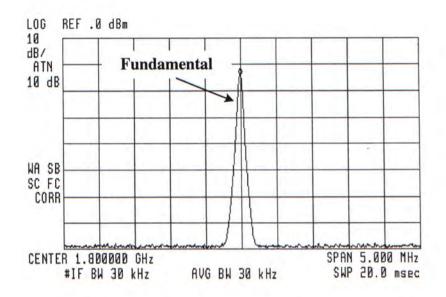

| Figure 8.5  | The output spectrum captured in the measurement of the          |    |

|             | 1-dB compression point                                          | 86 |

| Figure 8.6  | The setup for the two-tone linearity measurement                | 86 |

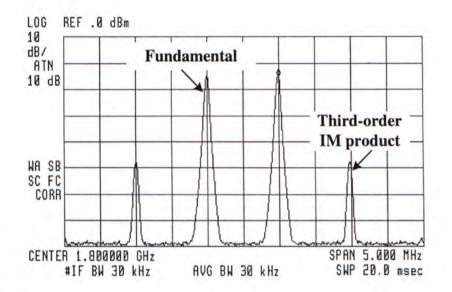

| Figure 8.7  | The output spectrum captured in the two-tone linearity          |    |

|             | measurement                                                     | 87 |

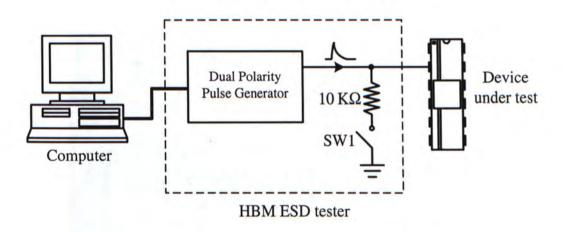

| Figure 8.8  | The setup for the HBM ESD test                                  | 88 |

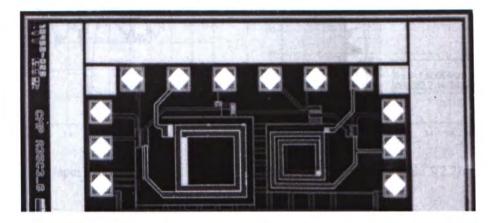

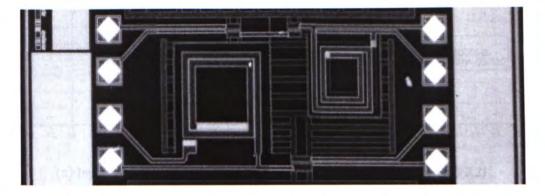

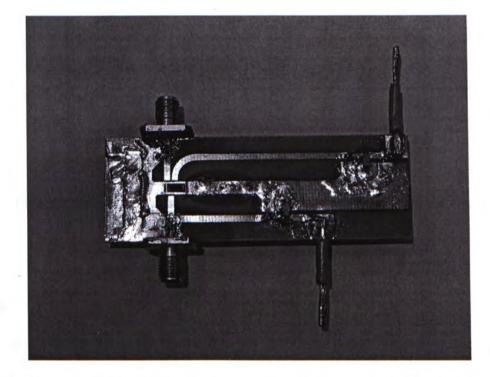

| Figure 8.9  | A microphotograph of the proposed LNA                           | 89 |

| Figure 8.10 | An evaluation board of the proposed LNA                         | 89 |

| Figure 8.11 | The measured S-parameter of the proposed LNA                    | 90 |

| Figure 8.12 | The measured noise figure of the proposed LNA                   | 91 |

| Figure 8.13 | The measured $P_{in,1dB}$ and $P_{out,1dB}$ of the proposed LNA | 92 |

| Figure 8.14 | The two-tone testing results of the proposed LNA                | 93 |

| Figure 8.15 | The I-V characteristic curves measured at the RF input of the   |    |

| N)          | proposed LNA in the negative HBM ESD test                       | 94 |

| Figure 8.16 | A microphotograph of the common-source LNA                      | 96 |

| Figure 8.17 | An evaluation board of the common-source LNA                    | 96 |

| Figure 8.18 | The measured S-parameter of the common-source LNA               | 97 |

| Figure 8.19 | The measured noise figure of the common-source LNA               | 98  |

|-------------|------------------------------------------------------------------|-----|

| Figure 8.20 | The measured $P_{in,1dB}$ and $P_{out,1dB}$ of the common-source |     |

|             | LNA                                                              | 99  |

| Figure 8.21 | The two-tone testing results of the common-source LNA            | 100 |

| Figure 8.22 | The I-V characteristic curves measured at the RF input of the    |     |

|             | common-source LNA in the positive HBM ESD test                   | 101 |

-

# **List of Tables**

| Table 2.1 | HBM ESDS component classification                                                   | 20 |

|-----------|-------------------------------------------------------------------------------------|----|

| Table 6.1 | Surface-mount components used to realize the DC biasing                             |    |

|           | circuit                                                                             | 56 |

| Table 6.2 | Component values used in the common-gate input stage                                | 58 |

| Table 6.3 | Component values used in the second-stage amplifier                                 | 60 |

| Table 6.4 | $\Gamma_{\rm IN,M},\ \Gamma_{\rm OUT,M}$ for simultaneous conjugate matches between |    |

|           | the two amplifiers and the inter-stage matching network at                          |    |

|           | 1.8 GHz                                                                             | 64 |

| Table 6.5 | Component values used in the inter-stage matching network                           | 64 |

| Table 6.6 | $\Gamma_{\rm S},\ \Gamma_{\rm L}$ for simultaneous conjugate match of the core LNA  |    |

|           | at 1.8 GHz                                                                          | 67 |

| Table 6.7 | Surface-mount components used to realize two matching                               |    |

|           | networks                                                                            | 68 |

| Table 6.8 | Simulated performance summary of the LNA                                            | 69 |

| Table 7.1 | Performance summary of the proposed LNA in post-layout                              |    |

| 1         | simulation                                                                          | 78 |

| Table 7.2 | Performance summary of the common-source LNA in                                     |    |

|           | post-layout simulation                                                              | 81 |

| Table 8.1 | The measurement results of the HBM ESD test for the                                 |    |

xvi

|           | proposed LNA                                            | 95  |  |

|-----------|---------------------------------------------------------|-----|--|

| Table 8.2 | Performance summary of the proposed LNA                 | 95  |  |

| Table 8.3 | The measurement results of the HBM ESD test for the for |     |  |

|           | the common-source LNA                                   | 102 |  |

| Table 8.4 | Performance summary of the common-source LNA            | 102 |  |

| Table 8.5 | Performance comparison between published LNA designs    |     |  |

|           | and the proposed LNA                                    | 103 |  |

| Table 8.6 | Performance comparison between the proposed LNA and the |     |  |

|           | standard LNA specifications                             | 104 |  |

|           |                                                         |     |  |

# Chapter 1

## Introduction

#### 1.1 Overview of Electrostatic Discharge

Electro-Static Discharge (ESD) is a rapid, spontaneous transfer of electrostatic charge induced by a high electrostatic field. Usually, the charge flows through a spark between two bodies at different electrostatic potentials as they approach to each other. When a charged object with a very high voltage touches a material of a low voltage, the ESD event occurs. In this situation, the electrostatic field built up across the material is very substantial. Thus, there is a sudden increase in current through the material. Even if the material is non-conductive, the hazardous ESD can lead to the insulator breakdown. Consequently, the insulator is destroyed.

#### 1.1.1 Classification of Electrostatic Discharge Models

In the investigation of the ESD events, it is found that they can be classified into three groups of models [1], depending on the characteristics of the current pulses discharged. The three categories are: 1) Human Body Model, 2) Machine Model and 3) Charged-Device Model.

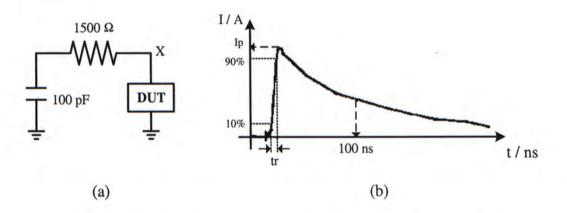

1) The Human Body Model (HBM) represents a charged human body, which discharges accumulated static charge through a device to ground. It is defined by the ESD association standard *ANSI/ESD STM5.1* [2]. Figure 1.1 shows the

1

schematic of HBM and the waveform of the ESD current pulse generated from the pre-charged capacitor, which discharges to device under test (DUT). Actually, HBM is a simple RC first-order circuit, so its current pulse is an approximate curve of exponential decay. The important parameters that are used to characterize the HBM ESD pulse are its peak current  $I_p$  and rise time tr, which are 1.33 A and 10 ns, respectively when the capacitor is pre-charged to 2 kV.

Figure 1.1: (a) The schematic of HBM and (b) the pulse waveform at X

The HBM ESD event is the most common scenario that is always considered in integrated circuit design. In practice, there are well-defined procedures for guiding the HBM ESD test, so that the maximum ESD level that the circuits can survive can be measured.

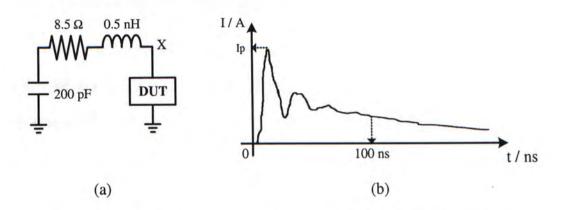

2) The Machine Model (MM) represents a charged machine body, which discharges accumulated static charge through a device to ground. It is defined by the ESD association standard *ANSI/ESD STM5.2* [3]. Since this model is composed of a resistor, inductor and a pre-charged capacitor, the ESD pulse generated by it is an underdamped oscillatory waveform. Figure 1.2 depicts the schematic and the waveform of the ESD current pulse produced from the MM ESD event.

2

Figure 1.2: (a) The schematic of MM and (b) the pulse waveform at X

Typically, the peak current  $I_p$  and the rise time tr of the MM ESD pulse are 3.7 - 7 A and 15 - 30 ns, respectively when the capacitor is pre-charged to 400 V. 3) The Charged-Device Model (CDM) represents a device self-charging and then self-discharges directly to ground. It is defined by the ESD association standard *ANSI/ESD STM5.3.1* [4]. The modeling circuit and the corresponding ESD pulse produced from the CDM ESD event are shown in Figure 1.3.

Figure 1.3: (a) The schematic of CDM and (b) the pulse waveform at X

Usually, the self-charging of an electronic device is due to field induction. In the case when DUT is charged to 1 kV by induced, the peak current  $I_p$  and the rise time tr of the resultant CDM ESD pulse are 10 A and 1 ns, respectively. This pulse is impulsive and disastrous that it is the hardest to protect against.

#### **1.2 Electrostatic Discharge in CMOS RF Circuits**

Traditional RF integrated circuit is dominated by GaAs and bipolar technologies. Due to the high speed and low noise properties, these technologies are widely used to implement RF front-end in wireless communication systems [5, 6]. As CMOS technology scales down to submicron process, it becomes possible to implement giga-hertz CMOS integrated circuits. It leads to an attractive solution of integrating a complete low cost receiver using CMOS [7, 8].

Unfortunately, the continuous down scaling in CMOS transistor makes the gate oxide layer becoming very thin. The thin oxide layer can be damaged easily by a high electrostatic field. Theoretically, the breakdown voltage of gate oxide layer  $(SiO_2)$  is 76 mV/Å. Therefore, the supply voltage should be reduced in order to avoid the gate oxide breakdown of the transistor. For example, TSMC 0.18- $\mu$ m CMOS can only operate with a supply voltage of 1.5 V.

ESD damage is a serious concern in the semiconductor industry. It can degrade or destroy the electrical characteristics of a semiconductor device. In CMOS integrated circuit, ESD is a common source that causes the gate oxide breakdown. Usually, when human being touches the transistor gate terminal, the HBM ESD pulse discharged can lead to the gate oxide breakdown, which can damage the circuit forever.

In recent years, ESD protection has been a popular research topic in CMOS RF integrated circuits [9, 10, 11]. The objective is to provide a reliable single chip receiver solution for wireless communications. Figure 1.4 depicts an integrated RF CMOS front-end.

4

Figure 1.4: An RF front-end for wireless communications

To consider ESD protection of the whole RF integrated front-end, dual-diode circuits can be employed for taking care of all its DC and low frequency input and output terminals. A conventional dual-diode protection circuit is shown in Figure 1.5. This is a reliable ESD protection circuit for CMOS digital and mixed-signal circuits [12]. It is capable of removing the incoming ESD pulses, so that the integrated circuit can be protected.

Figure 1.5: Dual-diode circuitry used in CMOS digital and mixed-signal circuits

However, the dual-diode ESD protection circuit is not suitable for RF applications, because of the large parasitic capacitances generated from the bulky protection diodes. At radio frequency, the shunt capacitances become a low impedance path that will short the RF input signal to ground. Consequently, the power gain and the noise figure of the LNA will be degraded [13, 14]. An ideal ESD protection circuit should be transparent to RF signal. Hence, most of the published CMOS RF receivers are operated without an ESD protection circuits. The yield and long-term

reliability of unprotected CMOS RF circuits are extremely low that prohibits single chip CMOS receiver from entering the commercial market.

#### 1.3 Research Goal and Contribution

This research project is aimed to improve the ESD protection of CMOS RF LNA. The new design should not cause any degradation to LNA performance. It should operate at low supply voltage. Furthermore, it should be integrated in standard commercial CMOS process.

In this thesis, a new ESD protection method, called Common-Gate Input Stage Method (CGISM), is presented. This method uses a common-gate amplifier as an input stage for a LNA, so as to reduce the possibility of the gate oxide breakdown. In addition, the method does not degrade the performance of the new LNA. To demonstrate the feasibility of CGISM, a CGISM LNA is fabricated with a standard 0.35-µm CMOS technology. From the measurement results (Chapter 8), it shows that CGISM can improve the ESD immunity of the new LNA. Moreover, the new LNA can provide comparable performance as standard LNAs [15], even at low supply voltage of 1.5 V.

#### 1.4 Thesis Outline

This thesis is divided into nine chapters. Chapter 2 defines the performance parameters of an RF amplifier. Chapter 3 reviews some ESD protection methodologies for LNA. The proposed CGISM will also be introduced. In Chapter 4, the theory and techniques used for the LNA design is explained. Chapter 5 derives the noise factor equations for LNA under two different noise analysis methods. The details of the proposed LNA design are described in Chapter 6. Then, the considerations of the layout design are discussed in Chapter 7. The measurement results of two fabricated LNA circuits are reported in Chapter 8. Finally, Chapter 9 concludes this thesis and provides the recommendations for future work.

### Chapter 2

## **Performance Parameters of Amplifier**

In performance analysis of RF amplifiers, hardware functionality is described by a specification. The parameters included in the specification give a variety of information such as amplifier gain, noise, linearity, etc. According to these performance parameters, designers can justify whether the amplifier meets the application requirements or not [15, 16]. In this chapter, we will introduce some standard RF amplifier parameters.

#### 2.1 Amplifier Gain

Figure 2.1: A microwave amplifier block diagram

Amplifier Gain refers to the ratio of the output power to the input power of an amplifier. It is one of the most important performance parameters for a microwave amplifier. In wireless communication, incoming signal to a receiver front-end is

(2 1)

always too weak to be processed. Therefore, amplifier is employed to increase the signal power level.

Figure 2.1 shows a typical microwave amplifier design diagram. In the design of an amplifier, there are three types of amplifier gains, including Transducer power gain  $G_T$ , Operating power gain  $G_P$  and Available power gain  $G_A$ . Their corresponding definitions are listed as follows [17]:

$G_T = \frac{\text{Power delivered to the load}}{\text{Power available from the source}}$

$$=\frac{1-|\Gamma_{s}|^{2}}{|I-\Gamma_{IN}\Gamma_{s}|^{2}}|S_{2I}|^{2}\frac{1-|\Gamma_{L}|^{2}}{|I-S_{22}\Gamma_{L}|^{2}}=\frac{1-|\Gamma_{s}|^{2}}{|I-S_{II}\Gamma_{s}|^{2}}|S_{2I}|^{2}\frac{1-|\Gamma_{L}|^{2}}{|I-\Gamma_{OUT}\Gamma_{L}|^{2}}$$

(2.1)

$$G_{P} = \frac{\text{Power delivered to the load}}{\text{Power input to the network}} = \frac{1}{1 - |\Gamma_{IN}|^{2}} |S_{2I}|^{2} \frac{1 - |\Gamma_{L}|^{2}}{|1 - S_{22}\Gamma_{L}|^{2}}$$

(2.2)

$$G_{A} = \frac{\text{Power available from the network}}{\text{Power available from the source}} = \frac{I - |\Gamma_{s}|^{2}}{|I - S_{II}\Gamma_{s}|^{2}} |S_{2I}|^{2} \frac{I}{1 - |\Gamma_{OUT}|^{2}}$$

(2.3)

Different definitions apply to the design of different amplifiers. For example, Equation (2.1) is used for high gain amplifier design. Equation (2.2) is used for power amplifier (PA) design. It is because the input of PA is assumed to be perfectly matched. In contrast, the output matching is assumed to be perfect in  $G_A$ definition, which is usually applied to LNA design. Nevertheless, all three gain variables will be identical for their maximum values, i.e.

$$G_{T,max} = G_{P,max} = G_{A,max} = G_{MAX}$$

(2.4)

#### 2.2 Noise Factor

Noise Factor (NF) is a measure of the degradation in signal-to-noise ratio that an amplifier introduces. Noise figure is defined as noise factor in dB. To express quantitatively this performance parameter, the following equation is defined.

$$NF = \frac{\text{Input SNR}}{\text{Output SNR}} = \frac{\frac{S_{in}}{N_{in}}}{\frac{S_{out}}{N_{out}}}$$

(2.5)

where  $S_{in}$  and  $S_{out}$  are the input and output signal power, respectively

$N_{in}$  and  $N_{out}$  are the input and output noise power, respectively

Hence,

$$NF = \frac{S_{in}}{S_{out}} \frac{N_{out}}{N_{in}}$$

$$= \frac{N_{out}}{GN_{in}}$$

(2.6)

where G is the gain of the amplifier.

From the equation derived above, another definition of noise factor is obtained, which is:

$$NF = \frac{\text{Total output noise power}}{\text{Output noise power due to input source}}$$

(2.7)

The total output noise power is composed of the output noise power due to input source and circuit noise of the amplifier [18]. In transistor amplifier, the major contributions of the circuit noise are the active components such as transistor and diode. The passive components that contain a certain amount of parasitic resistance can also generate thermal noise.

Standard mobile communication requires a minimum value of noise factor for a receiver front-end, so as to provide a reasonable signal-to-noise ratio at the output. As most of the receiver front-ends use a cascaded architecture, Friis formula can be applied to calculate the overall noise factor. This formula is given by

$$NF = F_1 + \frac{F_2 - 1}{G_1} + \frac{F_3 - 1}{G_1 G_2} + \frac{F_4 - 1}{G_1 G_2 G_3} + \dots$$

(2.8)

where  $F_i$  and  $G_i$  are the noise factor and the power gain of i-th stage, respectively. LNA is often placed in front of other RF modules in a receiver circuit. Thus, it requires high gain and low noise factor to keep the overall NF to a relatively low level.

#### 2.3 Linearity

Linearity is an important issue in RF amplifier. Circuit designer will like the RF amplifier to be a linear system, i.e.  $y(t) = \text{Gain} \cdot x(t)$ . However, most RF transistor amplifiers are non-linear [19]. It means that when two sinusoidal signals are injected into the amplifier, the output signal not only contains these two fundamental frequencies, but also generates many additional harmonics and high-order frequency terms the output spectrum (see Figure 2.2).

Figure 2.2: Non-linear effect of RF amplifier

In order to model the non-linear system mathematically, the following power series will be used.

$$y(t) = c_1 x(t) + c_2 x^2(t) + c_3 x^3(t)$$

(2.9)

where  $c_1, c_2$  and  $c_3$  are constants with  $c_1$  and  $c_3$  are opposite in sign. By using this formula, the following derivation can help us to understand the non-linear phenomenon. Suppose a two-tone input signal is  $x(t) = A \cos \omega_1 t + B \cos \omega_2 t$ , then

$$y(t) = c_{1} (A \cos \omega_{1}t + B \cos \omega_{2}t) + c_{2} (A \cos \omega_{1}t + B \cos \omega_{2}t)^{2} + c_{3} (A \cos \omega_{1}t + B \cos \omega_{2}t)^{3}$$

$$= c_{1} (A \cos \omega_{1}t + B \cos \omega_{2}t) + c_{2} (A^{2} \cos^{2} \omega_{1}t + 2AB \cos \omega_{1}t \cos \omega_{2}t + B^{2} \cos^{2} \omega_{2}t) + c_{3} (A^{3} \cos^{3} \omega_{1}t + 3A^{2}B \cos^{2} \omega_{1}t \cos \omega_{2}t + 3AB^{2} \cos \omega_{1}t \cos^{2} \omega_{2}t + B^{3} \cos^{3} \omega_{2}t)$$

$$= \frac{c_{2}(A^{2} + B^{2})}{2} + \left( c_{1}A + \frac{3c_{3}A^{3}}{4} + \frac{3c_{3}AB^{2}}{2} \right) \cos \omega_{1}t + \left( c_{1}B + \frac{3c_{3}}{4}B^{3} + \frac{3c_{3}}{2}A^{2}B \right) \cos \omega_{2}t + c_{2} AB \left[ \cos (\omega_{1} + \omega_{2})t + \cos (\omega_{2} - \omega_{1})t \right] + \frac{c_{2}A^{2}}{2} \cos 2\omega_{1}t + \frac{c_{2}B^{2}}{2} \cos 2\omega_{2}t + \frac{3c_{3}AB^{2}}{4} \cos (2\omega_{2} - \omega_{1})t + \frac{3c_{3}A^{2}B}{4} \cos (2\omega_{1} - \omega_{2})t + \frac{3c_{3}AB^{2}}{4} \cos (2\omega_{2} - \omega_{1})t + \frac{3c_{3}A^{2}B}{4} \cos (2\omega_{1} + \omega_{2})t + \frac{3c_{3}AB^{2}}{4} \cos (2\omega_{2} + \omega_{1})t + \frac{c_{3}A^{3}}{4} \cos 3\omega_{1}t + \frac{c_{3}B^{3}}{4} \cos 3\omega_{2}t$$

Based on Equation (2.10), the output contains many high frequency harmonics, which included a DC term, fundamental, second and third-order intermodulation (IM) products of the input signals. Using Equation (2.10), the two linearity parameters, *1-dB compression point* and *third-order intercept point* are derived as follows [20].

#### 2.3.1 1-dB Compression Point

When an input signal with low drive level is applied to a non-linear amplifier, its output power is directly proportional to its input power. However, as the power increases beyond a significant level, the contact gain relationship cannot keep linear and gain compression occurs. Eventually, the output power becomes saturated. The point at where the small-signal gain of the amplifier reduces from the expected linear gain by 1 dB is called 1-dB Compression Point. Figure 2.3 indicates the location of the 1-dB compression point in the graph of input-output power.

Figure 2.3: Determination of 1-dB compression point

From the mathematical point of view, when an input signal  $x(t) = Acos\omega_0 t$  is injected into an amplifier, by modifying Equation (2.10), the output signal becomes

$$y(t) = \frac{c_2 A^2}{2} + \left(c_1 A + \frac{3c_3 A^3}{4}\right) \cos \omega_0 t + \frac{c_2 A^2}{2} \cos 2\omega_0 t + \frac{c_3 A^3}{4} \cos 3\omega_0 t$$

(2.11)

We can observe from Equation (2.11) that the gain of the fundamental frequency is  $(c_1 + 3c_3A^2/4)$ , instead of a constant. At small input amplitude A,  $3c_3A^2/4$  is

small compared to  $c_1$  and can be neglected. So, the input-output power relationship remains linear. However, when A is large,  $3c_3A^2/4$  becomes significant. Since  $c_1$  and  $c_3$  are opposite in sign, the gain decreases with A. The gain compression effect will become more series if the value of A becomes very larger. Finally, the gain will be equal to zero and the amplifier is said to reach the saturation region. Therefore, 1-dB compression point is a critical value used to characterize the power handling capabilities of an amplifier.

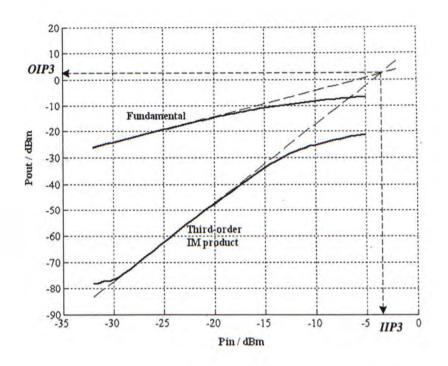

#### 2.3.2 Third-Order Intercept Point

Another standard parameter employed to assess the linearity of an amplifier is Third-Order Intercept Point (IP3). When a two-tone signal, with the same power levels at slightly different frequencies  $(\omega_1, \omega_2)$ , is applied to an amplifier, intermodulation distortion (IMD) appears at the output spectrum as shown in Figure 2.2. For the output frequency components that are far away from the fundamental frequencies, they can be removed by filtering. Unfortunately, there are two output IM products  $(2\omega_1 - \omega_2)$  and  $(2\omega_2 - \omega_1)$  caused by the third-order nonlinearities of the amplifier. They appear closely to the expected output frequencies and it is difficult to suppress them by simple filtering technique.

Equation (2.12) describes the content of the output signal y(t) when the two-tone signal  $x(t) = A(\cos \omega_1 t + \cos \omega_2 t)$  is applied to the amplifier.

$$y(t) = c_{2}A^{2} + \left(c_{1}A + \frac{9c_{3}A^{3}}{4}\right)(\cos\omega_{1}t + \cos\omega_{2}t) + c_{2}A^{2}\left[\cos(\omega_{1} + \omega_{2})t + \cos(\omega_{2} - \omega_{1})t\right] + \frac{c_{2}A^{2}}{2}\left(\cos 2\omega_{1}t + \cos 2\omega_{2}t\right) + \frac{3c_{3}A^{3}}{4}\left[\cos(2\omega_{1} - \omega_{2})t + \cos(2\omega_{2} - \omega_{1})t\right] + \frac{3c_{3}A^{3}}{4}\left[\cos(2\omega_{1} + \omega_{2})t + \cos(2\omega_{2} + \omega_{1})t\right] + \frac{c_{3}A^{3}}{4}\left(\cos 3\omega_{1}t + \cos 3\omega_{2}t\right)$$

(2.12)

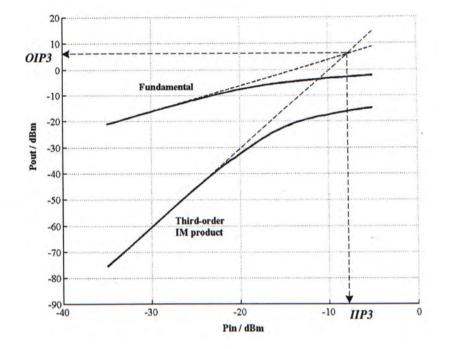

Similar to the single-tone input, gain compression occurs and the small-signal gains of the fundamental frequencies are equal to  $(c_1 + 9c_3 A^2/4)$ . So, the output powers are approximately proportional to the corresponding input powers at small amplitude A. For the third-order IM products, the output amplitudes are  $3c_3A^3/4$ . This means that the output powers are the cube of the input powers. Therefore, if the fundamental and the third-order IM product are plotted on the input power verse output power graph in log scale, the slope of the third-order IM product will be three times that of the fundamental in the linear region. This property is depicted in Figure 2.4.

Figure 2.4: Determination of third-order intercept point

From Figure 2.4, IP3 is the point where the linear extension of the Third-order IM product curve intersects the linear extension of the Fundamental curve.

IP3 indicates how well an amplifier performs in the presence of strong nearby interference, because the gain of the fundamental component is dependent of interferer's amplitude. Also, the IMD performance determines the extent to which the generated interference corrupts the adjacent channels.

In a multistage amplifier, the total IIP3 power  $P_{IIP3,tot}$  can be calculated by the following formula:

$$\frac{1}{P_{IIP3,tot}} = \frac{1}{P_{IIP3,1}} + \frac{G_1}{P_{IIP3,2}} + \frac{G_1G_2}{P_{IIP3,3}} + \dots$$

(2.13)

where  $P_{IIP3,i}$  and  $G_i$  are the IIP3 power and the power gain of i-th stage, respectively. It implies that the linearity of a multistage amplifier is limited by the number of stages and their corresponding power gains.

#### 2.4 Return Loss

Return Loss (RL) is a measure of the ratio of signal power transmitted into a system to the power reflected. This parameter indicates the amount of impedance mismatch between the source and the system. In fact, any variation in impedance from the source results in some returned power. Therefore, large RL means that there is less energy reflected and the impedance mismatch is less.

For the system impedance  $Z_A$  with the source impedance  $Z_0$ , RL is defined as:

$$RL(dB) = -20 \log_{10} |\Gamma_A|$$

(2.14)

where

$$\Gamma_A = \frac{Z_A - Z_0}{Z_A + Z_0} = \text{Reflection Coefficient}$$

(2.15)

When  $Z_A$  is equal to  $Z_0$ ,  $\Gamma_A$  will be zero and RL becomes infinity. In this condition, the system is said to perfectly match the source. As a result, all the power transfers to the system and there is no power reflection.

Figure 2.5 demonstrates how the matching network helps to improve RL.

Figure 2.5: Impedance transformation by matching network

Since the impedance  $Z_L$  is connected to a lossless matching network, its reflection coefficient is transformed from  $\Gamma_L$  to  $\Gamma_A$  which is expressed as:

$$\left| \Gamma_{A} \right| = \left| \frac{\Gamma_{L} - \Gamma_{S}^{*}}{1 - \Gamma_{L} \Gamma_{S}} \right|$$

(2.16)

On the other hand, the matching network transforms the source impedance to  $Z_s$  with the reflection coefficient of  $\Gamma_s$ . By tuning the matching network in such a way that  $\Gamma_s$  is equal to  $\Gamma_L^*$ ,  $|\Gamma_A|$  will be zero and RL seen from the source impedance becomes infinity. This technique is called conjugate matching.

In microwave amplifier design, the matching networks are usually constructed at both input and output terminals for impedance transformation (see Figure 2.1). Thus, there are two parameters for measuring how well the matching networks transform both input and output impedances to  $Z_0$ , they are:

Input RL

$$(dB) = -20 \log_{10} \left| \frac{\Gamma_{IN} - \Gamma_s^*}{1 - \Gamma_{IN} \Gamma_s} \right|$$

(2.17)

and

$$Output RL(dB) = -20 \log_{10} \left| \frac{\Gamma_{OUT} - \Gamma_{L}^{*}}{1 - \Gamma_{OUT} \Gamma_{L}} \right|$$

(2.18)

respectively. The minimum acceptable value is 15 dB. In some applications, a passive filter is required to precede a LNA, so it is necessary for the LNA to present a high RL at the input terminal, because the filter transfer characteristic is very sensitive to the mismatch of the termination impedance.

#### 2.5 **Power Consumption**

During the operation of an RF circuit, a current  $i_{dd}(t)$  is drawn from the battery of  $V_{DD}$  and there is some power dissipated. The amount of power consumed is calculated by:

$$P_{av} = V_{DD} I_{av} \tag{2.19}$$

where

$$I_{av} = \frac{1}{T} \int_{T} i_{dd}(t) \partial t$$

(2.20)

In an RF amplifier circuit,  $i_{dd}(t)$  is composed of AC and DC signals, i.e.  $i_{dd}(t) = i_{ac}(t) + i_{dc}$ . From Equation (2.20),  $I_{av}$  will be equal to  $i_{dc}$  and Equation (2.19) is simplified as:

$$P_{av} = V_{DD} i_{dc} \tag{2.21}$$

Most of the current portable mobile communication devices have the feature of long battery lifetime. In circuit design aspect, power consumption becomes a challenge issue. To attain this feature, designer can [21]:

1. use low  $V_{DD}$  to reduce the low power consumption and battery size;

2. design the circuit with low  $i_{dc}$ .

However, these methods will affect the performance of an amplifier, such as lower power gain, higher noise figure, poorer linearity and so on. There is always a trade-off between power consumption and performance.

#### 2.6 HBM ESD Withstand Voltage

In the design of an ESD-protected LNA, HBM ESD Withstand Voltage is a well-known parameter to indicate the ESD protection capability. According to ESD Association standard test method for HBM component level [2], HBM ESD withstand voltage is defined as the maximum ESD level that does not cause component failure. The component can be a resistor, diode, transistor, integrated circuit or hybrid. When component failure occurs, the component under test does not meet one or more specified data sheet parameters, including:

- static parameters input leakage current, input breakdown voltage, output drive current and supply current;

- dynamic parameters full functionality, output rise and fall times under a specified load condition and dynamic current drawn.

In this condition, the component is said to be permanently destroyed and never functions again.

19

HBM ESD withstand voltage is measured in term of a pair of experimental data, one comes form the positive ESD voltage stress, another comes form the testing for negative ESD voltage stress. Based on the HBM ESD withstand voltage, ESD sensitive components are classified, regardless of polarity. Table 2.1 shows the HBM ESD sensitive (ESDS) component classification levels under ESD Association standard.

| Class | Voltage Range (V) |

|-------|-------------------|

| 0     | <250              |

| 1A    | 250 to < 500      |

| 1B    | 500 to <1000      |

| 1C    | 1000 to < 2000    |

| 2     | 2000 to < 4000    |

| 3A    | 4000 to < 8000    |

| 3B    | ≥8000             |

Table 2.1: HBM ESDS component classification

In IC industry, most manufacturers specify the highest HBM ESD voltage level that a device can withstand. Use another word, the device must undergo testing with the HBM discharge waveform under the ESD Association standard requirements.

## **Chapter 3**

# ESD Protection Methodology for Low Noise Amplifier

ESD protection circuit is required to protect the input gate oxide of CMOS integrated circuits. In this chapter, two well-known ESD protection methods realized in the LNA are reviewed. They are dual-diode circuitry and shunt-inductor method. At the beginning, their working principles and major limitations associated with each method are discussed. After that, we will present a new ESD protection method for LNA that uses a common-gate amplifier as an input stage. The basic concept of this novel ESD protecting mechanism will be introduced at the end of this chapter.

Ideally, ESD protection circuitry designed for CMOS RF LNA should have the following features:

- It should provide an effective path for removing all ESD current without damaging the core circuit;

- It should be long-lasting and not be destroyed during a normal ESD protection process;

- 3. It should be transparent to RF signal and does not affect the LNA performance.

#### 3.1 Dual-Diode Circuitry

Dual-diode circuitry is the most common ESD protection circuit that is used in CMOS digital and mixed-signal circuits [12]. As CMOS technology scales down to submicron process, the implementation of CMOS RF integrated circuits becomes possible. The dual-diode circuitry is adopted to CMOS RF LNA for ESD protection [10].

#### 3.1.1 Working Principle

Figure 3.1: LNA with dual-diode ESD protection circuitry

The dual-diode circuitry consists of two diodes (D1 and D2) connected in reverse bias. One of them is connected from RF input of LNA to the power supply  $V_{dd}$ , another is connected from ground to the RF input, as illustrated in Figure 3.1. Since these diodes are reversely biased under normal operation, they behave like an open circuit that will not affect the performance of the LNA. However, when a hazardous static voltage is applied to the input terminal, one of the two diodes will turn on and short the input to ground. Thus, the CMOS circuits are protected from the ESD current. The detailed operation of the protection circuit is described in the following section.

When there is a positive ESD pulse at the RF input port, the potential of  $RF_{in}$  increases. As the voltage across D1 reaches its threshold  $V_{th}$ , it will turn on as illustrated in Figure 3.2(a). As a result, the gate potential is clamped to a safe level. In contrast, when there is a negative ESD pulse at the RF input port, the potential of  $RF_{in}$  decreases. In this case, D2 turns on as the voltage across D2 reaches its threshold  $V_{th}$ . The ESD current passes through D2 in the direction as illustrated in Figure 3.2(b). Similarly, the gate potential is also clamped to a safe level.

(b)

Figure 3.2: ESD current flow in dual-diode circuitry in the case of (a) positive ESD pulse; (b) negative ESD pulse

In both cases, the gate potential is clamped to either  $V_{dd} + V_{th}$  or  $-V_{th}$  to protect the gate oxide of M1 from breakdown. In particular, the ESD protection capability of the dual-diode circuitry is related to the sizes of the two diodes. The amount of ESD current that can be bypassed to ground is proportional to the diode size. That is why most of the ESD protection diodes occupy thousands of square micron of area.

#### 3.1.2 Drawbacks

Although the dual-diode protection circuit works well with low frequency CMOS circuits, we are facing the following problems when it is applied to RF CMOS:

- The clamping diodes are the bulky devices in CMOS process. They generate large shunt parasitic capacitances at the LNA input port. At radio frequency, the shunt capacitances become a low impedance path that will short the input RF signal to ground. Consequently, the power gain and the noise figure of the LNA will be degraded [13, 14]. Even though numerous researches have proposed modified circuitries to reduce the degradation, however, none of these methods have been proved feasible [22, 23].

- 2. In standard protection circuit, there is a series resistor of few hundred ohms between the dual-diode circuit and the LNA input. This resistor provides additional time delay to the ESD pulse, which serves as a secondary protection circuit. However, this small resistor will cause performance degradation to the RF circuit. Therefore, it must be omitted that will reduce the protection efficiency of the dual-diode circuit.

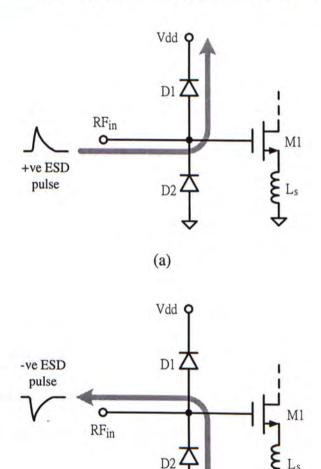

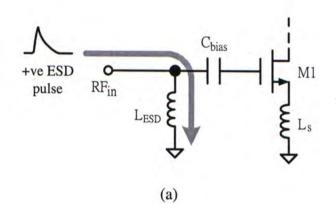

#### 3.2 Shunt-Inductor Method

Shunt-inductor method is a modified ESD protection technique [11]. Figure 3.3 demonstrates a CMOS LNA using this protection method. Basically, this method uses the shunt inductor  $L_{ESD}$  at the RF input to provide a low impedance path to the high frequency ESD current. At the same time, it can tune out all the parasitic capacitance  $C_p$  that comes from the input bonding pad and normal ESD protection network. As a result, the LNA performance is improved. Practically,  $L_{ESD}$  should be realized by the on-chip inductor so as to provide a stand-alone chip protection.

Figure 3.3: LNA with shunt inductor as ESD protection

#### 3.2.1 Working Principle

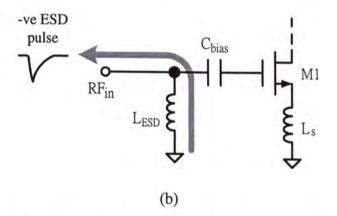

This method makes use of the natural property of ESD current pulse to design an inductor-based protection circuitry. Under normal condition, the frequency of most ESD pulses is much lower than the RF input signal. Thus,  $L_{ESD}$  acts as a low pass filter and provides a low impedance path at the ESD frequency. In contrast, since the blocking capacitor  $C_{bias}$  is selected under the consideration of RF signal frequency, its value is usually in the order of 0.1 pF. Hence, it behaves as a high pass filter and impedes the ESD current from entering the transistor M1. The incoming ESD current is forced to pass through  $L_{ESD}$  to ground, instead of passing through  $C_{bias}$ . Consequently, the entire ESD current is removed by  $L_{ESD}$  and M1 is protected.

Figure 3.4: ESD current flow in shunt-inductor circuitry in the case of (a) positive ESD pulse; (b) negative ESD pulse

Figure 3.4(a) and (b) illustrates the protecting mechanism of the shunt-inductor method for positive and negative ESD pulses, respectively.

#### 3.2.2 Drawbacks

General speaking, shunt-inductor method has the following problems:

- The on-chip inductor realized in CMOS integrated circuit is a low-Q passive component. This inevitably leads to some power loss and performance degradation.

- 2. Since the shunt inductor connects directly to ground, any DC biasing voltage at the input terminal will be shorted to ground. To prevent this problem, blocking capacitors should be added at both sides that makes the input matching network bulky and introduces high power loss.

- 3. The ESD protection capability of this method is dependent on the metal width of the shunt inductor  $L_{ESD}$ . Wider metal track can handle higher ESD current and improves the ESD withstand voltage. However, the inductance of  $L_{ESD}$ is pre-defined by the matching network, thus, the designers have very little control to the width of the metal tracks.

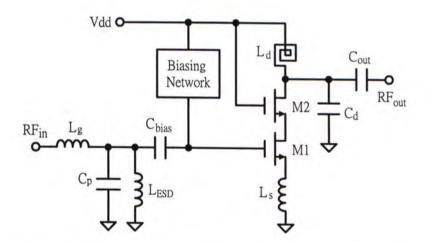

#### 3.3 Common-Gate Input Stage Method

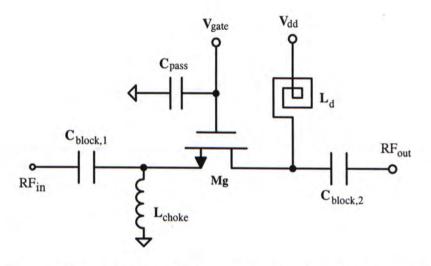

In this project, a new ESD protection method has been developed which is called Common-Gate Input Stage Method (CGISM). This proposed method eliminates all the drawbacks listed in the preceding methods. Besides, there is no any additional ESD protection circuitry required. It is because the circuit used to implement CGISM is a single-stage LNA. Figure 3.5 shows a typical common-gate amplifier that is used to achieve the project goal.

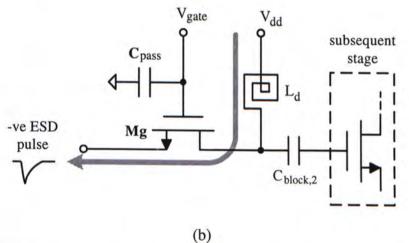

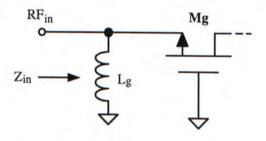

Figure 3.5: Schematic diagram of a common-gate amplifier

The major advantage of the common-gate amplifier is that its RF input is connected to the source terminal of the transistor Mg. For conventional LNA, its RF input is connected to NMOS gate terminal. Any ESD current can attack its gate oxide layer easily. Thus, its ESD immunity is quite low. However, by using CGISM, it greatly improves the ESD immunity of the LNA by preventing the hazardous ESD current from discharging through the thin gate oxide of Mg. Moreover, there is a built-in ESD protecting mechanism that can effectively take off all the ESD current at the RF input. In the following section, this built-in mechanism is introduced.

#### 3.3.1 Built-In ESD Protecting Mechanism

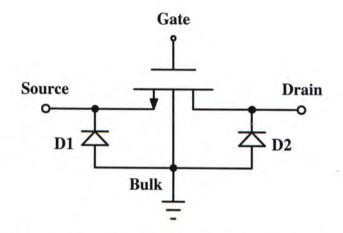

A normal NMOS transistor has two diodes (D1 and D2) at its drain-substrate and source-substrate junctions as illustrated in Figure 3.6.

Figure 3.6: Simplified circuit model of a NMOS transistor

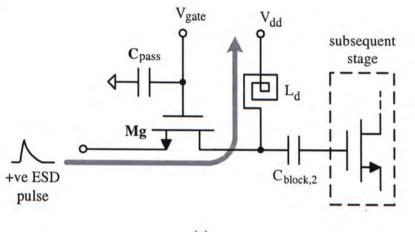

When there is a positive ESD pulse at the source terminal of a common-gate amplifier, the transistor Mg turns off initially because both its gate-to-source voltage  $V_{gs}$  and gate-to-drain voltage  $V_{gd}$  are negative. In this case, D1 is reversely biased and a space-charge layer is formed at the source-substrate junction. However, as the source terminal is forced to a high ESD potential, D1 will reach the breakdown potential. Near the breakdown potential, D1's space-charge layer generates a large amount of electron-hole pairs. The free electrons drift to the source region while the free holes drift to the substrate, which increases the substrate's potential with respect to the drain junction. Eventually, D2 switches on by the increasing substrate potential and all the ESD current passes through the transistor substrate from source-to- substrate -to-drain.

On the other hand, when a negative ESD pulse is applied to the input port, the transistor Mg and the diode D1 turn on because of the positive  $V_{gs}$ . Therefore, all the ESD current flows through the channel from drain-to-channel-to-source and from

substrate-to-source. Figure 3.7 shows the scenarios of how the hazardous ESD can be removed by a common-gate amplifier.

(-)

Figure 3.7: Built-in ESD protecting mechanism of CGISM

In summary, common-gate LNA can provide higher ESD immunity than conventional common-source LNA because of the built-in ESD protecting mechanism.

For an ESD pulse with a fast rise time, its high frequency components may leak off to the successive stage through the output capacitor  $C_{block,2}$ . To tackle this problem, an on-chip spiral inductor  $L_d$  is placed before  $C_{block,2}$  as illustrated in Figure 3.5. Its working principle is similar to how the shunt-inductor method does. Under normal condition, the ESD frequency is lower than the RF input signal.  $L_d$ and  $C_{block,2}$  form a high pass filter to force the ESD signal to  $V_{dd}$  through  $L_d$ . Furthermore, there is no ESD signal coupling to the gate of the transistor Mg through the gate-to-source capacitor  $C_{gs}$ . It is because the capacitance of  $C_{gs}$  is in the order of 0.1 pF that it gives high impedance at the ESD frequency. Therefore, the LNA is completely saved against all ESD.

#### 3.3.2 Competitiveness

By comparing with the preceding ESD protection methods, CGISM has many competitive factors that can enhance the ESD immunity of CMOS RF LNA to protect CMOS RF receiver chip.

- The method is simple, there is no additional clamping device required to install at the LNA input. Thus, it does not increase the production cost.

- There is no any bulky parasitic capacitance associated at the RF input. The performance is not degraded.

- Besides the ESD protection functionality, the common-gate input stage can provide a certain amount of power gain. The amplification requirement of the subsequent-stage amplifier can be reduced. It benefits the low voltage design.

- The ESD handling capability is proportional to the size of the transistor Mg. Larger width can support higher channel current. More ESD current can be handled as a result.

- 5. Mg controls the amount of current passing through its channel. The shunt inductor and the blocking capacitor form a high pass filter to prevent the ESD current from leaking off to the subsequent transistor.

### **Chapter 4**

## **Design Theory of Low Noise Amplifier**

Low noise amplifier (LNA) is the first stage in the receiving path of a receiver. Typically, its function is to provide enough gain to overcome the noise of subsequent stages. According to Friis formula of Equation (2.8), its noise figure directly adds to that of the receiver. Thus, the LNA should generate as little noise as possible.

Aside from the noise consideration, linearity is another parameter that should be concerned. At normal power range, the LNA should amplify the incoming signal without any distortion. On the other aspect, the LNA needs to present a well-defined input impedance, such as 50  $\Omega$ . It is due to the transfer characteristic of the antenna preceding the LNA that is very sensitive to the LNA termination.

In this chapter, we will present some basic LNA design techniques. These include the methods of input termination, gain enhancement and improvement of reverse isolation. By mastering these techniques, a variety of LNA designs can be developed to meet the system specifications.

#### 4.1 Small-Signal Modeling

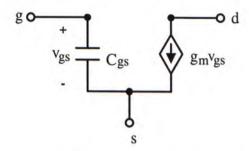

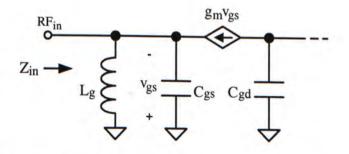

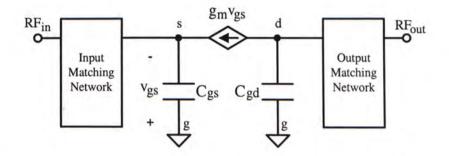

Figure 4.1: Small-signal model of a MOS transistor

For the purpose of small-signal analysis, active devices are usually modeled with a number of lumped elements, including RLC passive elements, dependent and independent sources, which give the necessary approximation in frequency domain. Figure 4.1 gives the simplified small-signal model of a MOS transistor, where  $g_m$ is the transistor transconductance.

#### 4.2 Method of Input Termination

Presentation of a good match to the external world is a critical requirement in RF design. Since the input impedance of MOS transistor is inherently capacitive, providing a 50- $\Omega$  input impedance without degrading noise performance is always a challenging topic. Fortunately, there are four common circuit topologies that are able to accomplish this goal [24]. In the section, the fundamentals of these four topologies are reviewed.

#### 4.2.1 Resistive Termination

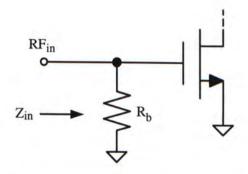

Figure 4.2: Input impedance matching by resistive termination

Resistive termination is a straightforward approach to present a broadband 50- $\Omega$  impedance at an amplifier input. Simply speaking, when a 50- $\Omega$  shunt resistor  $R_b$  is connected across the input terminal, the stable input impedance can be realized. Figure 4.2 illustrates this technique applied to a common-source amplifier.

However, the resistor  $R_b$  not only adds thermal noise to the amplifier, but also leads to high power loss at the input. The amplifier performance will be greatly degraded if this topology is implemented at high frequency. Therefore, this topology is not recommended for RF LNA design.

#### 4.2.2 Shunt-Series Feedback

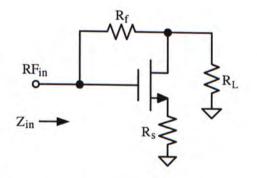

Figure 4.3: Input impedance matching by shunt-series feedback

Figure 4.3 shows the schematic of a shunt-series amplifier that employs the

feedback technique to provide a broadband real input impedance. Since there is no any shunt resistor that attenuates the input signal, its noise figure is expected to be better than the previous approach. Nevertheless, the resistor  $R_f$  still contributes some thermal noise to the amplifier. The resistive feedback network also limits the gain of the amplifier. Therefore, this topology is not recommended to implement in RF LNA.

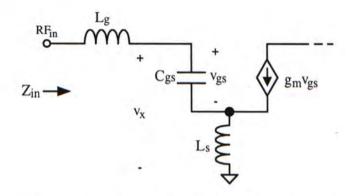

#### 4.2.3 $1/g_m$ Termination

Figure 4.4: Input impedance matching by  $1/g_m$  termination

The third method used to realize a stable 50- $\Omega$  input impedance is  $1/g_m$  termination. Its working principle is to use a common-gate topology to achieve this goal. Figure 4.4 demonstrates the implementation of this method. The shunt inductor  $L_g$  is tuned to resonate with the capacitor  $C_{gs}$  at the operating frequency.

Figure 4.5: Small-signal analysis of a common-gate topology

From the small-signal circuit shown in Figure 4.5,

$$\frac{1}{Z_{in}} = \frac{1}{j\omega L_g} + j\omega C_{gs} + \frac{g_m v_{gs}}{v_{gs}}$$

$$= \frac{1 - \omega^2 L_g C_{gs}}{j\omega L_g} + g_m$$

(4.1)

At resonance,  $\omega_0^2 L_g C_{gs} = 1$ , then

$$Z_{in}(\omega_0) = \frac{1}{g_m} \tag{4.2}$$

where  $\omega_0$  is the operating frequency. By a proper selection of the transistor size and bias current, the desired 50- $\Omega$  input impedance appears at  $\omega_0$ .

Different from the preceding approaches that rely on the resistor,  $1/g_m$  termination provides the desired input impedance with acceptable noise performance. Therefore, it becomes one of the most common methods in LNA implementation [25, 26].

#### 4.2.4 Inductive Source Degeneration

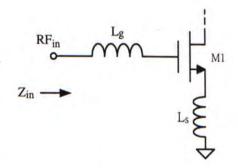

Figure 4.6: Input impedance matching by inductive source degeneration

Another popular method employed used to design standard input impedance is called Inductive Source Degeneration [27]. Figure 4.6 illustrates a common-source amplifier with this method. Actually, the advantage of this method is that the resistive part of the input impedance is generated by the source inductor  $L_s$ , instead of using noisy resistor. Theoretically, inductor does not introduce any thermal noise, which satisfies the noise requirement of LNA. Figure 4.7 shows the small-signal model of an inductively source degenerated amplifier.

From the figure,

$$v_x = v_{gs} + j\omega L_s \left( j\omega C_{gs} v_{gs} + g_m v_{gs} \right)$$

=  $\left( 1 - \omega^2 L_s C_{gs} + j\omega g_m L_s \right) v_{gs}$  (4.3)

$$Z_{in} = j\omega L_g + \frac{\left(1 - \omega^2 L_s C_{gs} + j\omega g_m L_s\right) v_{gs}}{j\omega C_{gs} v_{gs}}$$

$$= j\omega \left(L_g + L_s\right) + \frac{1}{j\omega C_{gs}} + \frac{g_m L_s}{C_{gs}}$$

$$= \frac{1 - \omega^2 \left(L_g + L_s\right) C_{gs}}{j\omega C_{gs}} + \frac{g_m L_s}{C_{gs}}$$

(4.4)

At resonance,  $\omega_0^2 (L_g + L_s) C_{gs} = 1$ , then

$$Z_{in}(\omega_0) = \frac{g_m L_s}{C_{es}}$$

(4.5)

Therefore, by choosing the suitable values of  $L_s$ ,  $L_g$ , the transistor size and bias current, the input impedance can be adjusted to 50  $\Omega$ .

#### 4.3 Method of Gain Enhancement

Amplifier gain is an important parameter in CMOS LNA specifications. High gain LNA provides sufficient amplification to the incoming signal. Moreover, it overcomes the noise of the subsequent stages, such as mixer. As a result, the overall noise figure of the receiver front-end can be reduced. Conventionally, tuned amplifier and multistage amplifier are usually implemented in CMOS LNA to enhance its amplifier gain. These methods are described in this section.

#### 4.3.1 Tuned Amplifier

Figure 4.8: Tuned amplifier with LC tank circuit

Tuned amplifier is an amplifier that uses a LC resonant tank to accomplish high-gain performance [28]. At the resonance frequency, the LC tank becomes a high impedance load that will enhance the amplifier gain. From Figure 4.8, the gain of the tuned amplifier at a given frequency  $\omega$  is given by

$$Gain = \frac{V_{out}(\omega)}{V_{in}(\omega)} = G_m Z_L(\omega)$$

(4.6)