## An Asynchronous Forth Microprocessor

## Ping-Ki TSANG

A Thesis Submitted in Partial Fulfilment of the Requirements for the Degree of Master of Philosophy

in Computer Science & Engineering

> Supervised by: Prof. Philip LEONG

## © The Chinese University of Hong Kong Jan 2000

The Chinese University of Hong Kong holds the copyright of this thesis. Any person(s) intending to use a part or whole of the materials in the thesis in a proposed publication must seek copyright release from the Dean of the Graduate School.

#### 摘要

低功率、高代碼密度、有好的軟件開發工具、高性能及細小是嵌入系統(特別是以電池作電源)裏的微處理器的必要條件。因此,我們開發了一枚異步微處理器以探索異步邏輯在低電量應用的潛力及示範以異步邏輯來迎合嵌入市場的低成本與低電量的要求。

以堆疊機器作嵌入式微處理器是十分合適的。我們開發了一個堆疊架構的微處理器(MSL16)。MSL16 擁有一個很細小的指令集及面積,我們以現場可編程門陣列(FPGA)實施了一個同步的原型。其後,我們再以馬田合成方法(Martin's synthesis method)實施一個異步微處理器,MSL16A。

我們以高速超大規模集成電路硬體描述語言(VHDL)描述 MSL16,發現它的最高運行時頻為 33MHz,而此同步原型只佔據 175 Xilinx 4000 系列可重 構邏輯塊(CLBs)。此設計的異步實施(MSL16A)擁有 66,500 個晶體管, 以 1.2 微米互補金屬氧化物半導體(CMOS)技術來實施,我們預期它的平 均性能為 33MIPS 而功率則為 95mW。

## An Asynchronous Forth Microprocessor

submitted by

Ping-Ki TSANG

for the degree of Master of Philosophy at the Chinese University of Hong Kong

## Abstract

Microprocessors for embedded battery powered applications require low power consumption, good code density, good software development tools, high performance, and small area. An asynchronous delay-insensitive implementation of an asynchronous processor, which directly addresses these issues, was developed to explore the potentials of asynchronous logic for low-power applications and to demonstrate the feasibility and practicability of using asynchronous circuits to meet the cost and power constraints of the embedded market.

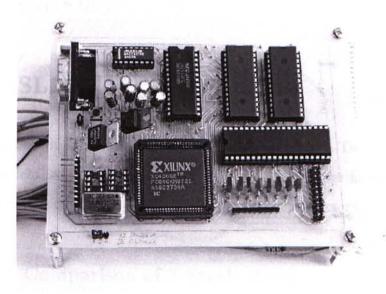

Stack machines meet all of the requirements of embedded processors and a stack based architecture, called the minimal instruction set, small and low power **16** bit microprocessor (MSL16) was developed. A synchronous prototype implementation of the architecture was successfully tested on a field programmable gate array device. The design was then reimplemented using Martin's synthesis method to produce MSL16A, a 16-bit asynchronous microprocessor.

MSL16 was synthesized from a VHDL description and was found to be operational at 33MHz. This synchronous prototype occupies merely 175 Xilinx 4000 series configurable logic blocks (CLBs) which is particularly small for it performance. The asynchronous implementation, MSL16A, contains about 66,500 transistors and the expected performance is 33 MIPS, using  $1.2\mu$ m CMOS technology, for a power consumption of 95mW. Comparisons with previous asynchronous and commercial low power microprocessors, are included. When scaled to the same technology, MSL16A performs better in terms of size, power consumption and energy efficiency because of its high code density and simple architecture. This makes MSL16A very competitive for battery powered portable or embedded applications.

## Acknowledgments

I would firstly like to acknowledge the support of my advisor, Prof. Philip Leong and Prof. Tony Lee, for the useful weekly discussions and their inspired leadership of this project. Their insights gave me many ideas, inspiration, and guidance to this work. I warmly thank Prof. Philip Leong for proof reading and commenting on this thesis. Without him, this thesis would not have been completed.

I have received a great deal of support and encouragement from my colleagues in Ho Sing Hang Engineering Building Room 1026, especially, Philip, Ken, Thomas, Oldfield, Fei, Peter and Small Keung. I would like to thank everyone of them for the daily gathering, endless discussions and, above all these, the fun and precious moments we all shared.

Finally, I wholeheartedly thank my mother, Nancy Wang for her lifelong chore of bringing me up, her warmth and invaluable lifelong support.

# Contents

| $\mathbf{A}$ | bstra | $\mathbf{ct}$                          | i   |

|--------------|-------|----------------------------------------|-----|

| A            | cknov | wledgments                             | iii |

| 1            | Intr  | oduction                               | 1   |

|              | 1.1   | Motivation and Aims                    | 1   |

|              | 1.2   | Contributions                          | 3   |

|              | 1.3   | Overview of the Thesis                 | 4   |

| 2            | Asy   | nchronous Logic                        | 6   |

|              | 2.1   | Motivation                             | 6   |

|              | 2.2   | Timing Models                          | 9   |

|              |       | 2.2.1 Fundamental-Mode Model           | 9   |

|              |       | 2.2.2 Delay-Insensitive Model          | 10  |

|              |       | 2.2.3 QDI and Speed-Independent Models | 11  |

|              | 2.3   | Asynchronous Signalling Protocols      | 12  |

|              |       | 2.3.1 2-phase Handshaking Protocol     | 12  |

|   |     | 2.3.2 4-phase Handshaking Protocol  |

|---|-----|-------------------------------------|

|   | 2.4 | Data Representations                |

|   |     | 2.4.1 Dual Rail Coded Data          |

|   |     | 2.4.2 Bundled Data                  |

|   | 2.5 | Previous Asynchronous Processors    |

|   | 2.6 | Summary                             |

| 3 | The | MSL16 Architecture 21               |

|   | 3.1 | RISC Machines                       |

|   | 3.2 | Stack Machines                      |

|   | 3.3 | Forth and its Applications          |

|   | 3.4 | MSL16                               |

|   |     | 3.4.1 Architecture                  |

|   |     | 3.4.2 Instruction Set               |

|   |     | 3.4.3 The Datapath                  |

|   |     | 3.4.4 Interrupts and Exceptions     |

|   |     | 3.4.5 Implementing Forth primitives |

|   |     | 3.4.6 Code Density Estimation       |

|   | 3.5 | Summary                             |

| 4 | Dec | an Mothodologu                      |

| 4 | Des | gn Methodology 37                   |

|   | 4.1 | Basic Notation                      |

|   | 4.2 | Specification of MSL16A                 |

|---|-----|-----------------------------------------|

|   | 4.3 | Decomposition into Concurrent Processes |

|   | 4.4 | Separation of Control and Datapath      |

|   | 4.5 | Handshaking Expansion                   |

|   |     | 4.5.1 4-Phase Handshaking Protocol      |

|   | 4.6 | Production-rule Expansion               |

|   | 4.7 | Summary 48                              |

| 5 | Imr | blementation 49                         |

| 0 |     |                                         |

|   | 5.1 | C-element                               |

|   | 5.2 | Mutual Exclusion Elements               |

|   | 5.3 | Caltech Asynchronous Synthesis Tools    |

|   | 5.4 | Stack Design                            |

|   |     | 5.4.1 Eager Stack Control               |

|   |     | 5.4.2 Lazy Stack Control                |

|   |     | 5.4.3 Eager/Lazy Stack Datapath         |

|   |     | 5.4.4 Pointer Stack Control             |

|   |     | 5.4.5 Pointer Stack Datapath            |

|   | 5.5 | ALU Design                              |

|   |     | 5.5.1 The Addition Operation            |

|   |     | 5.5.2 Zero-Checker                      |

|    | 5.6                  | Memory Interface and Tri-state Buffers | 64 |

|----|----------------------|----------------------------------------|----|

|    | 5.7                  | MSL16A                                 | 65 |

|    | 5.8                  | Summary                                | 66 |

| 6  | $\operatorname{Res}$ | ults                                   | 67 |

|    | <mark>6</mark> .1    | FPGA based implementation of MSL16     | 67 |

|    | 6.2                  | MSL16A                                 | 69 |

|    |                      | 6.2.1 A Comparison of 3 Stack Designs  | 69 |

|    |                      | 6.2.2 Evaluation of the ALU            | 73 |

|    |                      | 6.2.3 Evaluation of MSL16A             | 74 |

|    | 6.3                  | Summary                                | 81 |

| 7  | Con                  | clusions                               | 83 |

|    | 7.1                  | Future Work                            | 85 |

| Bi | bliog                | graphy                                 | 87 |

| Ρı | iblica               | ations                                 | 95 |

# List of Tables

| 2.1 Categorization of A   | synchronous Circ   | cuits     |          |        | · · · · · | 9  |

|---------------------------|--------------------|-----------|----------|--------|-----------|----|

| 2.2 Four states of a cha  | nnel               | • • • • • |          |        |           | 15 |

| 2.3 Characteristics of e  | ight previous asy  | nchronous | s micro  | proce  | ssors     | 16 |

| 3.1 The MSL16 instruc     | tion set $\ldots$  | • • • • • |          |        |           | 31 |

| 3.2 Translation of Forth  | 1 primitives       |           |          |        |           | 34 |

| 3.3 Code Density Calcu    | llation            |           |          |        | • • • • • | 35 |

| 5.1 Truth table of a C-e  | element            |           | • • • •  | • • •  |           | 51 |

| 5.2 Carry Output of a l   | Full Adder         | • • • • • | • • • •  |        |           | 63 |

| 6.1 Simulated cycle tim   | e for different St | ack Desig | ;n       |        |           | 70 |

| 6.2 Power-Delay Produ     | ct Comparison .    | · · · · · |          | • • •  |           | 71 |

| 6.3 Size of a single 16-b | it stack element(  | automati  | cally ge | enerat | ted)      | 72 |

| 6.4 Performance of the    | ALU                |           |          | • • •  |           | 73 |

| 6.5 MSL16A chip summ      | nary               |           | • • • •  | • • •  |           | 77 |

| 6.6 Characteristics of M  | ISL16A, ASPRO      | -216 and  | TITAC    | C-2 .  |           | 79 |

6.7 Scaled performance of MSL16A, ASPRO–216 and TITAC–2  $\ldots$  79

# List of Figures

| 2.1 | Fundamental-mode circuit structure                                           | 10 |

|-----|------------------------------------------------------------------------------|----|

| 2.2 | CMOS inverter                                                                | 11 |

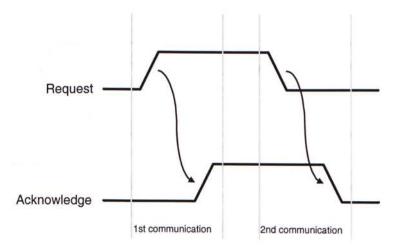

| 2.3 | 2-phase handshaking protocol                                                 | 13 |

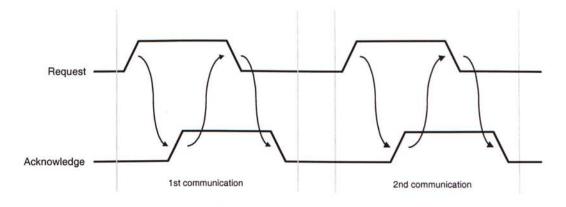

| 2.4 | 4-phase handshaking protocol                                                 | 14 |

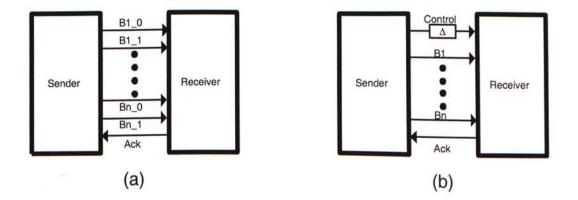

| 2.5 | Data transfer via (a)<br>dual-rail encoding and (b)<br>bundled data $\ldots$ | 14 |

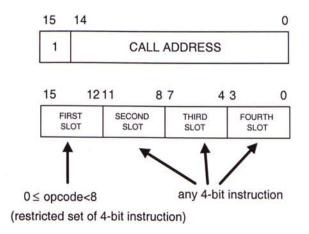

| 3.1 | Instruction format for MSL16                                                 | 30 |

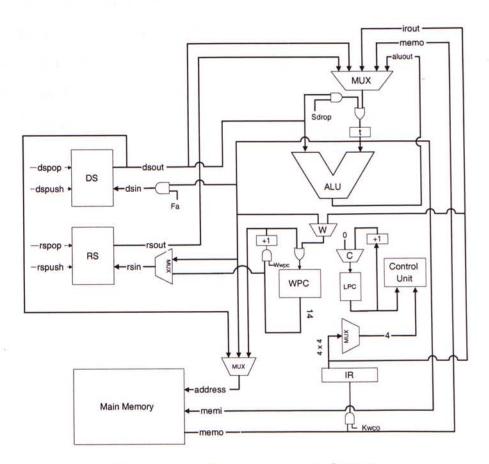

| 3.2 | The datapath of MSL16                                                        | 32 |

| 4.1 | Bare Communication on Channel $E$                                            | 46 |

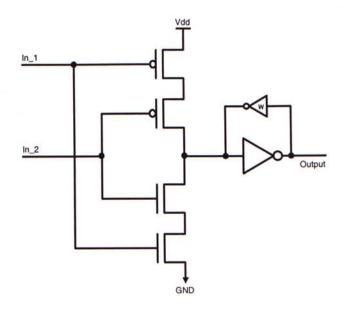

| 5.1 | The C-element                                                                | 50 |

| 5.2 | A Simple Arbitration System                                                  | 51 |

| 5.3 | A basic arbitration circuit                                                  | 52 |

| 5.4 | The Stack                                                                    | 55 |

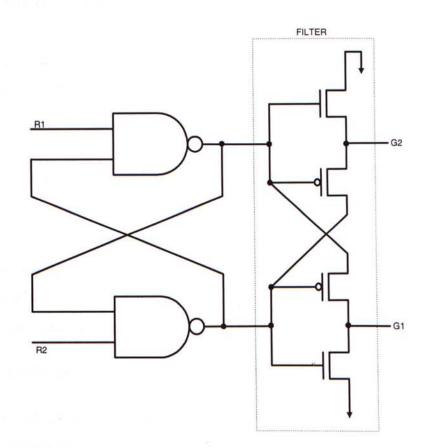

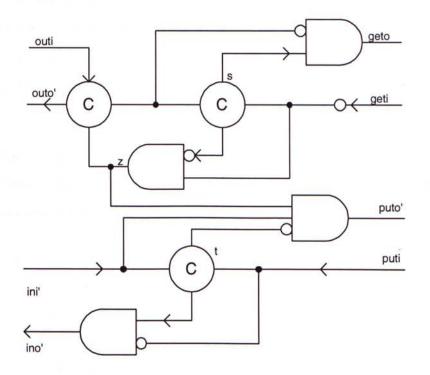

| 5.5 | Implementation of the Eager Stack's control process                          | 57 |

| 5.6 | Implementation of the Lazy Stack's control process                           | 59 |

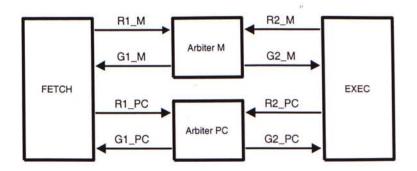

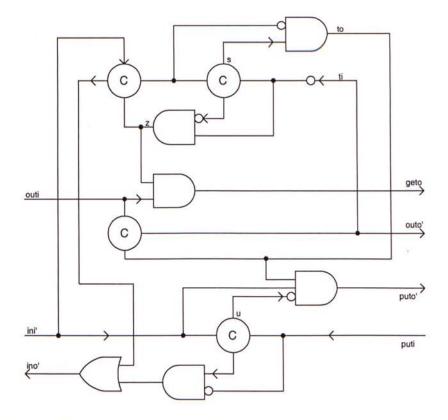

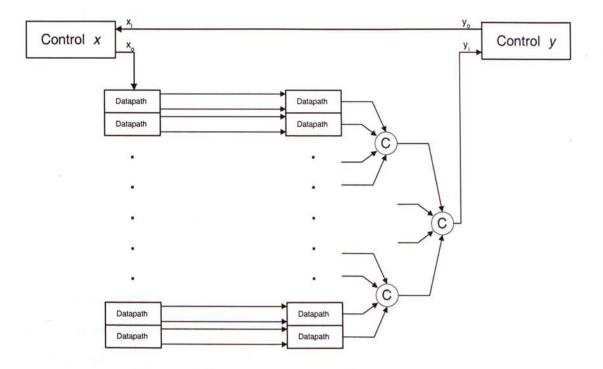

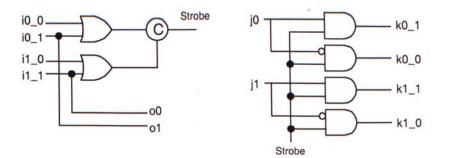

| 5.7 | Implementation of communication                                      | 60 |

|-----|----------------------------------------------------------------------|----|

| 5.8 | Dual-rail to single-rail and single-rail to dual-rail converters $\$ | 64 |

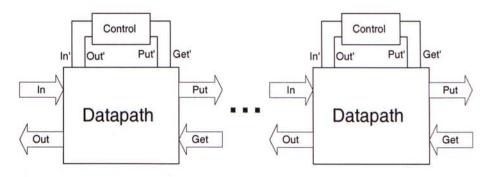

| 5.9 | The datapath of MSL16A                                               | 65 |

| 6.1 | MSL16 prototype board                                                | 68 |

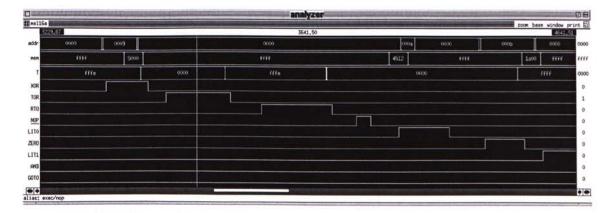

| 6.2 | IRSIM simulation of test program (Part 1)                            | 76 |

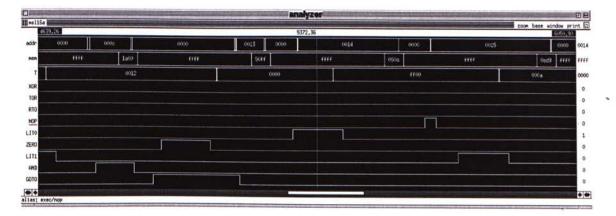

| 6.3 | IRSIM simulation of test program (Part 2)                            | 76 |

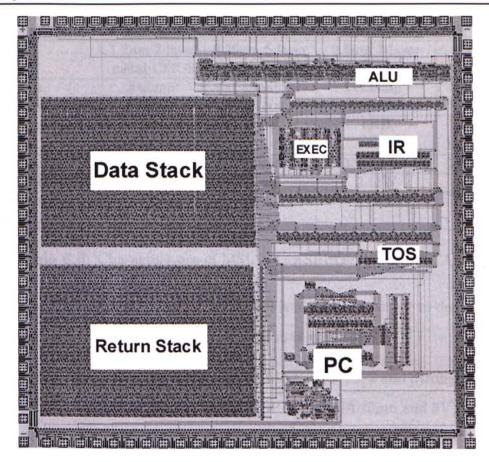

| 6.4 | MSL16A chip image                                                    | 78 |

## Chapter 1

## Introduction

## 1.1 Motivation and Aims

Driven by the growing market for portable battery operated computation devices, performance was no longer the single most important feature of a microprocessor. Today, many embedded applications employ a microprocessor which has requirements of being low power and small area with performance merely a secondary issue. Power efficiency is becoming increasingly important as portable systems are becoming physically smaller and battery weight is becoming more critical. Longer battery life can only be obtained by improving the capacity of the battery or by optimizing the power efficiency of a portable system. The advancement of battery technology is slow, digital designers must address this issue by lowering the power requirements of portable devices.

Asynchronous designs are believed to be ideal for low power applications as they only dissipate power when and where they are active. Previous work has shown that the clock power can be twice the logic power for static logic and about three times the logic power for dynamic logic [1]. Asynchronous circuits do not require global synchrony and thus eliminate the need for global clocks. Moreover, the handshaking protocol of asynchronous circuits removes spurious transitions and each transition has its own meaning which saves power by nature. Recent research has demonstrated that asynchronous circuits techniques have matured and implementations of asynchronous processors have been reported [2, 3, 4, 5, 6, 7, 8, 9, 10, 11].

Code density is crucial as it relates directly to the requirements of cache and memory sizes. The power consumption in memory and related parts of a system is inversely proportional to the code density of processor embedded in it. A processor with a higher code density means it requires a smaller cache and memory to run at equivalent performance than a lower code density processor. It has been shown that a processor does not dominate a system's total power consumption, about 50% is dissipated by the memory [12]. In addition, large caches can occupy 90% of the total chip area and dissipate about 43% of the total chip power [13]. As a result, the code density of a processor must also be optimized for low power applications.

The aim of this thesis was to address these issues in low power system design by developing a minimal instruction set, small and low power 16 bit microprocessor (MSL16 [14]), which was an architecture having desirable features like good performance, high code density and small area. High code density and small area were achieved by utilizing a stack architecture with a minimal instruction set, simple datapath and control. It was designed to directly execute Forth, which is a stack based portable integrated programming environment, operating system and programming language having code density typically higher than that of C or assembly language. Forth has been successfully used in many well known embedded applications [15, 16, 17, 18] and several commercial microprocessors have been designed to run Forth [19, 20]. A synchronous prototype implementation of the MSL16 architecture was successfully tested on a field programmable gate array device, which was found to be small, fast and power efficient.

An asynchronous re-implementation of the MSL16 microprocessor, called

MSL16A, has been developed to investigate the potential advantages that asynchronous designs may enjoy, namely average-case performance instead of worstcase performance and low power consumption. MSL16A was also developed to demonstrate the feasibility and practicability of using asynchronous circuits to meet the cost and power constraints in low power embedded applications.

### **1.2** Contributions

This thesis presents an architecture, called MSL16, which was developed to directly execute the Forth language. MSL16 (which stands for minimal instruction set, small and low power 16 bit microprocessor) was designed to support the development of complex software and designed to be included as a coprocessor inside an embedded system. MSL16 has a minimal instruction set of 17 instructions, a 16 bit datapath and very simple control and datapath. This architecture has desirable features like high speed, small number of gates and high code density. Code density is critical in power efficiency as memory and large caches may consume up to half of the total system power [12, 13]. The above features lead to an FPGA implementation that was fast, small and power efficient which is presented in Chapter 6.

Stacks are a fundamental building block in microprocessors, microcontroller and DSPs. However, to the best of the author's knowledge, there have not been any reported quantitative comparisons between different delay-insensitive stack designs and implementations. Three different asynchronous stack designs and implementations, the Eager Stack, the Lazy Stack and the Pointer Stack, were developed in this thesis. The tradeoff among the three different designs were analyzed in terms of performance, power and silicon area to justify the use of the chosen stack design when re-implementing MSL16 asynchronously. The three designs are competitive in size but the Pointer Stack was finally employed as it was found to be the most energy efficient.

An asynchronous re-implementation of MSL16, called MSL16A, was successfully developed based on Martin's synthesis method [21] to demonstrate the feasibility of using asynchronous circuits in low power embedded systems. The processor was realized both by manual layout and using the Caltech Asynchronous Synthesis Tools (CAST). The work described in this thesis includes the development of this asynchronous re-implementation and its performance estimation. MSL16A was compared with two other previous asynchronous microprocessors, ASPRO-216 [22] and TITAC-2 [9], as well as the commercially available synchronous StrongARM 110 [13]. When scaled to the same technology, MSL16A was found to be smaller, dissipates less power and was more energy efficient than the other designs.

### 1.3 Overview of the Thesis

The thesis is arranged as follows:

Chapter 2 considers asynchronous logic, the potential benefits asynchronous designs can bring, the signalling protocols and different data representation techniques. A brief description of different asynchronous design styles and previous asynchronous processors are also presented. Chapter 3 gives a brief introduction to stack machines and the programming language Forth which explains why they are particularly suitable to embedded applications, followed by a presentation of architecture of MSL16. The instruction set architecture and its datapath components are also examined, explaining how the architecture of MSL16 improves the code density of Forth programs which can greatly enhance the power efficiency of a low power system.

Chapter 4 describes Martin's synthesis method which was the design method-

ology used for MSL16A. Chapter 5 describes the implementation of MSL16A. The stack design is critical for the overall performance of the processor, and three different asynchronous stack designs were compared. Evaluations of the three stack designs and the ALU, together with other interesting implementation issues are discussed. In Chapter 6, results from simulation of the processor are presented. The synchronous FPGA based implementation is first presented, followed by the evaluation procedure and the performance comparison of MSL16A with other processors. In Chapter 7, concluding remarks about this work are presented.

## Chapter 2

# Asynchronous Logic

MSL16A uses asynchronous logic as this approach is believed to have benefits over standard synchronous designs in terms of energy efficiency, speed and robustness [23]. The first section of this chapter explains the motivation for using asynchronous logic in low power system. Different asynchronous design styles are presented in the subsequent section. The final section reviews eight recent asynchronous microprocessors.

As a complete treatment of asynchronous design styles is beyond the scope of this thesis, only a brief description of current asynchronous design styles is presented here. The design methodology adopted in building MSL16A, Martin's synthesis method, will be detailed in Chapter 4. More in-depth surveys on asynchronous design styles can be found in [24, 23]

### 2.1 Motivation

The MSL16A processor uses asynchronous circuit because of the following potential benefits.

No clock skew Clock skew is the difference in arrival times of the global clock

signal at different parts of the system. Synchronous circuits usually rely on an externally generated clock signal which is distributed to all of its circuit elements. The clock period is dependent on the maximum clock skew. With today's VLSI circuits exceeding 15mm per side, several nanosecond of clock skew is not unusual. With a fixed 5 nanosecond (200MHz) clock period, several nanoseconds of clock skew is disastrous.

Clock deskewing methods are available (like the balanced H-tree) but the costs are extremely high. The designer of the DEC<sup>1</sup> ALPHA took another approach [25] but the result is a clock driver chip that occupies about 10% of the chip area and consumes more than 40% of the total power generated by the chip. The price to pay for keeping the clock skew under control is very high. Asynchronous circuits, by definition, do not have a globally distributed clock, and the clock skew problem is eliminated automatically.

Low power Asynchronous circuits consumes power only in areas involved in computation. Idle components waste negligible power. The global clock in standard synchronous circuit keeps on toggling all the time and power is dissipated along the long clock lines. Previous work [1] has shown that clock power is about twice the logic power for static logic and about three times the logic power for dynamic logic. Some power management mechanisms can shut down the idle parts of advanced synchronous systems with extra circuitry but asynchronous system have this efficiency by nature.

In addition, in response to a clock edge, a number of signals in a synchronous system change several times before reaching a stable value. These spurious transitions do not cause the circuit to fail but every transition, useful or not, consumes power. On the other hand, every transition in an asynchronous circuit is meaningful. Any glitches will cause the circuit to malfunction. They generally make fewer transitions and hence consume

<sup>&</sup>lt;sup>1</sup>Digital Equipment Corporation

less power.

- Average-case performance A fixed clock period is chosen depending on the worst-case timing analysis of a synchronous circuit. However, worst-case situation rarely occurs but still it has to be clocked so that the rare worstcase condition is accommodated. Asynchronous circuits take advantage of the best- and average-case computation situations as they sense when a computation has completed. Substantial savings can be gained for circuits like ripple-carry adders where the worst-case delay is much worse than the average-case delay.

- **Robustness** Asynchronous circuits operates over a wide range of temperature and supply voltage. They are more tolerant to variations in physical or electrical parameters. They adapt to those variations automatically as they sense computation completion, and will run as quickly as the current physical and electrical properties allow.

Circuitry which guarantee correct mutual exclusion of independent signals are subject to metastability [26], which a system can remain in an unstable equilibrium state for an unbounded amount of time [27]. There is a chance for such a mutual exclusion circuit to fail in synchronous systems as all elements have to exhibit bounded response time. Asynchronous systems can wait for an arbitrary long time, allowing robust mutual exclusion.

Along with the advantages described above, it is worth noting that asynchronous circuits have several problems as well. Asynchronous circuits are more difficult to design as hazards must not be introduced in the circuit to avoid incorrect results. Moreover, the signalling protocol and dual-rail data representation in asynchronous systems work against energy efficiency and silicon area. Asynchronous circuits require extra time for synchronization, thus increasing the average-case delay. As a result, further investigation is needed to see to what extent the potential benefits of asynchronous circuits can be realized.

### 2.2 Timing Models

Asynchronous design styles can be categorized by the timing models they assume. As shown in Table 2.1, they can be divided into four groups according to the assumptions made on gate and wire delays. The timing models will be discussed in this section.

| Model                         | Gate delay assumption | Wire delay assumption |

|-------------------------------|-----------------------|-----------------------|

| Fundamental-mode              | Bounded               | Bounded               |

| Delay-insensitive             | Unbounded             | Unbounded             |

| Speed-independent             | Unbounded             | Negligible            |

| Quasi-delay-insensitive (QDI) | Unbounded             | Isochronic fork       |

Table 2.1: Categorization of Asynchronous Circuits

#### 2.2.1 Fundamental-Mode Model

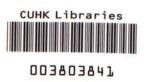

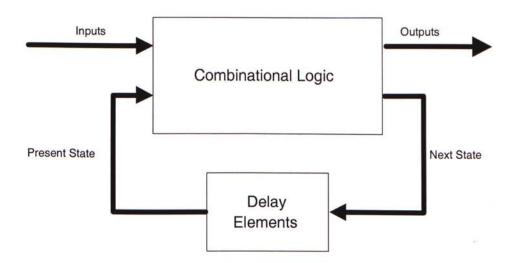

The fundamental-mode model, also called the Huffman model [28, 29], assumes that both gate and wire delays are bounded. In this model, the asynchronous circuit is decomposed into two parts, the combinational logic part and the feedback part. The fundamental-mode model asynchronous circuit structure is shown in Figure 2.1. The environment must be able to control the timings of inputs such that input transitions only occur when the circuit is in either the present state or the next state. This means that the next input transition cannot take place until the entire system settles into a stable state.

Figure 2.1: Fundamental-mode circuit structure

#### 2.2.2 Delay-Insensitive Model

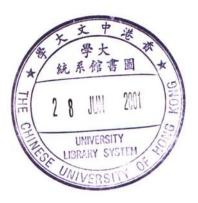

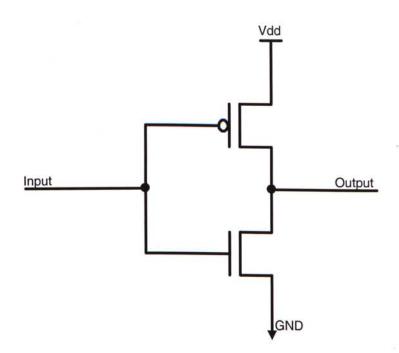

The delay-insensitive model assumes that both gate and wire delays are unbounded but finite. This model imposes the least restrictions on circuit delays and a delay-insensitive circuit works correctly as long as all gate and wire delays are finite. This is an attractive property for synthesis and testing but it has been proved that the class of delay insensitive circuit is very limited [30]. A simple example in [31] has shown that even the simplest CMOS inverter is delay sensitive. The inverter circuit shown in Figure 2.2 would fail if there is a large delay difference from the input to the pMOS and nMOS transistors as both may turn on at the same time. As a result, it is often assumed that the skew between the wire delays after the forking is less than one gate delay in practice.

Moreover, the delay-insensitive timing model has a great impact on the resulting circuit structure. It is assumed that given enough time a subcircuit will have settled in a bounded-delay model. On the other hand, in a delay-insensitive model, a subcircuit may not be settled even after a long time as delays are unbounded. The recipient must send a signal to inform the sender when it has received the data. This function relies on the completion detection circuit in the receiver which requires a new way of passing data also. The protocol and data representation techniques will be discussed in Section 2.3.

Figure 2.2: CMOS inverter

#### 2.2.3 QDI and Speed-Independent Models

These two models differentiate themselves in their choice of compromise to delay insensitivity. The speed-independent model, also called the Muller model, makes the assumption that while gate delays are unbounded but finite, all wire delays are negligible. Quasi-delay-insensitive circuits adopt the delay-insensitive assumption (both wire and gate delays are unbounded but finite) but forks are isochronic. An isochronic fork [21] is a set of interconnecting wires where the difference in delays between destinations is negligible.

While quasi-delay-insensitive and speed-independent models allow more im-

plementation alternatives than the pure delay-insensitive model, the delay assumptions they require can sometimes be difficult to realize in practice. In custom designs delay elements can be added to balance the delay to different fork ends. However, in field-programmable gate arrays and deep submicron technologies, wire delays can often dominate logic delays and the automatic routing tools may not be able to handle the isochronic constraint.

In addition, some parts of a fork may cross a chip boundary in large designs and matching the delays between on-chip and off-chip destinations is almost impossible. To avoid this problem, Martin's synthesis method [21] restricts isochronic forks to small localized areas.

### 2.3 Asynchronous Signalling Protocols

With an unbounded model, communications between blocks in an asynchronous system require some sort of handshaking mechanism. Pairs of wires called *request* and *acknowledge* are generally used to indicates when an action should be initiated and when an operation is completed. Two signalling protocols have been proposed for handshaking using the *request* and *acknowledge* signals. They are classified based on the number of transitions passing through the handshaking wires.

### 2.3.1 2-phase Handshaking Protocol

The 2-phase handshaking protocol is a non return to zero protocol. Figure 2.3 shows an example of 2-phase communication. In a 2-phase communication, the sender makes a single transition on the request wire to initiate the communication. The receiver senses the request, services the request and then responds by making a single transition on the acknowledge wire. Note that only a transition

Figure 2.3: 2-phase handshaking protocol

is important and the rising and falling edges are both significant and equivalent.

If the first communication starts with a transition from Low to High, the next communication will start with a transition from High to Low as there is no intermediate recovery stage.

## 2.3.2 4-phase Handshaking Protocol

The 4-phase handshaking protocol is a return to zero protocol and is illustrated in Figure 2.4. The first two phases are active phases while the other two phase are recovery phases. The rising edge of request initiates the communication and the receiver responds by changing the acknowledge wire to a High level also. The falling edges of request and acknowledge wires are inserted to return the *request* and *acknowledge* signals to a logical Low level and indicates a successful communication.

Figure 2.4: 4-phase handshaking protocol

## 2.4 Data Representations

In asynchronous designs, the transfer of data must be handled carefully as there is no global clock signal to indicate when a computation can start or when it is completed. Additional wires must be used for synchronization. The two commonly used approaches are described below.

Figure 2.5: Data transfer via (a)dual-rail encoding and (b)bundled data

#### 2.4.1 Dual Rail Coded Data

By using a single wire per bit to transfer data, the receiver will not be able to differentiate between a wire that will not change and one that has not yet changed. Thus, every bit of information needs to be encoded with two separate wires representing a logic '1' and a logic '0'. Initially, both of them are zero. To transmit a '1' (refer to Figure 2.5a), the wire representing logic '1' is raised and vice versa. It follows that a dual-rail encoded binary communication channel can have four states (see Table 2.2). Hence, it is possible to detect when a data bit is valid.

| wire_1 | wire_2 | meaning       |

|--------|--------|---------------|

| 0      | 0      | idle          |

| 1      | 0      | a valid one   |

| 0      | 1      | a valid zero  |

| 1      | 1      | invalid state |

Table 2.2: Four states of a channel

Unlike bundled data, the timing information is mixed with the data. The main advantage of this approach is that the resulting circuits are delay-insensitive but at the cost of increasing the number of wires and chip area.

#### 2.4.2 Bundled Data

Bundled data allows a single wire for each data bit and associates one control wire to indicate the validity of all of the data (as illustrated in Figure 2.5b). The delay in the extra control wire must be guaranteed to be longer than that of each of the data wires. This bundling constraint requires that a transition on the control wire does not occur until after the data lines are stable at the receiver.

The main advantage of this technique is that standard datapath components or cell libraries can be used. Bundled data allows fewer wires to be used but violates the delay-insensitive model as it is inherently delay-bounded. It can save considerable area at the cost of meeting the bundling constraints.

## 2.5 Previous Asynchronous Processors

Many asynchronous microprocessors have been previously implemented or proposed [2, 3, 4, 5, 6, 7, 8, 9, 10, 11]. This section briefly describes the design styles and architectures of eight asynchronous processors which are summarized in Table 2.3.

| Processor | Design Style                                                               | Instruction Set         | Organization                              |

|-----------|----------------------------------------------------------------------------|-------------------------|-------------------------------------------|

| CAP       | 4-phase, dual rail,<br>quasi delay insensitive                             | Own 16–bit<br>RISC like | Fetch-execute<br>pipeline                 |

| AMULET1   | 2-phase, bundled data                                                      | ARM                     | Pipelined,                                |

| AMULET2e  | 4-phase, bundled data                                                      | ARM                     | no forwarding<br>Pipelined,<br>forwarding |

| ECSTAC    | Fundamental mode                                                           | Own,<br>variable length | Pipelined,<br>no forwarding               |

| TITAC     | 4-phase,dual rail                                                          | Own 8-bit               | No pipelining                             |

| TITAC-2   | quasi delay insensitive<br>4-phase dual rail<br>scalable delay insensitive | MIPS R2000              | pipelined,<br>forwarding                  |

| FAM       | 4-phase, dual rail<br>quasi delay insensitive                              | Own RISC like           | Pipelined                                 |

| ASPRO-216 | 4-phase, dual rail                                                         | 16–bit RISC like        | pipelined                                 |

|           | quasi delay insensitive                                                    | 64 custom instructions  | no forwarding                             |

Table 2.3: Characteristics of eight previous asynchronous microprocessors

#### The Caltech Asynchronous Processor (CAP)

Professor Alain Martin at Caltech built the first asynchronous processor in 1989 [2]. The processor is delay insensitive and its datapath is dual rail encoded. It was built based on Martin's synthesis method [21]. The processor was described using a language that is based on Hoare's model of *Communicating Sequential Processes (CSP)* [32] and then complied to a circuit by means of program transformations.

The instruction set is a conventional 16-bit-word of the RISC-like load/store type with 16 registers. It consists of several concurrent processes responsible for instruction fetch, manipulating the program counter, ALU operation, memory access...etc. The processor was implemented in a  $1.6\mu$ m CMOS process. In room temperature, it operates at 18 millions of instructions per second(MIPS) at 5V. The circuit is functional at very low supply voltage with optimum powerdelay product at around 2V. Its performance reaches 30MIPS in liquid nitrogen at 77K.

#### AMULET1 and AMULET2e

The AMULET group led by Steve Furber at the University of Manchester built the first asynchronous implementation of the ARM instruction set, AMULET1 [33]. AMULET2e [8] is a similar processor which achieved full code-compatibility with the ARM6 processor.

The ARM instruction set was designed for synchronous processors [34] with some of its features only convenient in the synchronous system. AMULET1 and AMULET2 implements this instruction set completely including the difficult areas of interrupts and exceptions.

AMULET1 was designed using a 2-phase bundled data design style based on [35] It has a 5-stage pipeline without result forwarding. A locking mechanism is used to stall the register read stage until their operands have been written by previous instructions. It also permits out of order completion of load instruction relative to normal ALU instructions.AMULET1 was implemented in a  $1.2\mu$ m CMOS process with a peak performance of 5.3MIPS.

AMULET2e was designed using a 4-phase bundled design style as the CMOS implementation of 2-phase control elements in AMULET1 was inefficient. The pipeline of AMULET2e is slightly shorter and employs both branch prediction and result forwarding to increase the pipeline utilization. AMULET2e was implemented in a  $0.5\mu$ m 3-layer metal CMOS process and its performance reaches 40MIPS at 3.3V.

#### ECSTAC

ECSTAC is an asynchronous processor designed by researchers at the University of Adelaide [7]. It was implemented using fundamental mode circuits. It is deeply pipelined with 8-bit registers and ALU. It has a complex variable length instruction format with a total of 113 distinct instruction types including mode variants. There is no result forwarding scheme in the datapath and, like AMULET1, a register locking mechanism is employed to stall instructions until their operands are available. The anticipated throughput was 40MIPS.

The designers reported that the variable length instructions and the mismatch between the datapath width and address size made the processor more complex and slower.

#### TITAC and TITAC-2

TITAC is a simple asynchronous microprocessor built by a group at the Tokyo Institute of Technology [5]. TITAC is an asynchronous version of an 8-bit von Neumann microprocessor based on the quasi delay insensitive timing model. It has a straightforward architecture without any pipelining and a simple accumulatorbased instruction set. The datapath design uses a dual rail, multi-level AND-OR scheme with a binary decision diagram for efficient signal generation.

TITAC-2's [9] instruction set is based on the MIPS R2000. It is a 32-bit asynchronous microprocessor with an architecture which is very similar to the MIPS R2000 processor. It has a five stage pipeline and was designed using 4-phase dual rail encoding scheme. It was fabricated in a  $0.5\mu$ m 3-layer metal CMOS process and operates at 52.3MIPS at 3.3V at room temperature. TITAC-2 runs correctly from 1.5V to 6.0V.

#### FAM

FAM [11] is a 32-bit dual rail asynchronous processor with RISC like load-store instruction set. The datapath contains 32 general purpose registers, 32-bit ALU, multiplier and 32-bit barrel shifter. It has a four stage pipeline but register read, ALU operation and register write fit in a single stage to eliminate the need for result forwarding. FAM was implemented in  $0.5\mu$ m CMOS process and its performance is about 300MIPS.

#### ASPRO-216

ASPRO-216 [22] is a 16-bit quasi delay insensitive asynchronous microprocessor. It was built based on Martin's synthesis method. It is a scalar processor which issues instructions in-order while completing their instructions out-of-order. The processor includes sixteen 16-bit general purpose registers together with two two distinct on-chip memories, one for data and the other for program. In addition, there are 64 possible custom instruction slots and the processor is heavily pipelined. ASPRO-216 was implemented in a  $0.25\mu$ m five metal-layer CMOS process and a peak processing rate of 200MIPS was expected.

### 2.6 Summary

In this chapter, an introduction to asynchronous logic and asynchronous design styles was presented. MSL16A uses asynchronous circuits as this approach is believed to have benefits in terms of energy efficiency, speed and robustness. In addition, asynchronous circuits eliminate the clock skew problem found on synchronous circuits, exhibit average-case performance and allow robust mutual exclusion. MSL16A adopts the quasi-delay-insensitive timing model which assumes that wire and gate delays are unbounded but finite while forks are isochronic. Handshaking protocols and data representation techniques generally used in asynchronous systems were discussed. Dual-rail coded data are required to satisfy the unbounded delay timming assumption while bundled data are simpler and smaller but violates the delay-insensitive model. Finally, a review of earlier work on asynchronous microprocessors was also presented.

## Chapter 3

## The MSL16 Architecture

This chapter presents the architecture of the MSL16 processor. MSL16A shares the same architecture with different design methodology and implementation techniques. The first section describes RISC machines. The next two sections give a brief introduction to stack machines and the Forth programming language, explaining why they are ideal for low power systems. The pipelining of MSL16, its instruction format, its instruction set and the datapath will be discussed in the last section. This section also presents how MSL16 was designed to meet the tightly constrained power and cost requirements of low power portable applications. The code density of MSL16 are also estimated as code density relates directly to power consumption of a complete system.

## 3.1 **RISC** Machines

The basic principles behind the original RISC (Reduced Instruction Set Computer) processors are reviewed below:

- A simple instruction set is faster than a complicated one

- Complicated addressing mode for instructions are unnecessary

- A large register file facilitates software

- Let the compiler handles complicated functions

- Simple processors are easy to design

Some of these principles are still valid today but RISC processors tend to be very complicated nowadays, some are even more complicated than their CISC (Complex Instruction Set Computer) counterparts. Pipelining was introduced to increase the throughput but the pipeline still has to be flushed and refilled whenever a branch is taken. Modern RISC architectures follow the principles of making the common case fast, reducing the instruction set to simplify hardware implementation, having a uniform instruction encoding so that it is easily decoded, supporting a small number of addressing modes, using large register files and relying on caches to provide high memory bandwidth [36]. These design criteria were chosen to maximize the performance of the machine with power consumption and chip area being secondary concerns.

Large amount of cache memory is needed to buffer instructions if the core speed of a RISC processor is much faster than the main memory because of its lower code density. The associated cache control circuitry will increase the system complexity and large caches may take up to 90% of the total chip area [13]. Moreover, RISC processors does not utilize cache memory efficiently as program size for RISC machine is usually larger. A large register file is windowed to facilitate subroutine call and return but the large register file will slow down the processor for context switches.

In portable and battery operated applications, the design criteria are different as the system cost and power consumption are highly constrained. There is normally no cache, the amount of memory used should be minimized, and some performance can be sacrificed for code density, which relates directly to the total power dissipation of a system. These issues have influenced the architecture of MSL16.

## 3.2 Stack Machines

Stack machines are simpler than other CISC or RISC machines since their instruction sets do not need to encode operands. For example, in a RISC machine a 3-operand addition requires the two source and the destination registers to be encoded in the instruction. In a stack machine, however, an addition always operates on the top two elements of the stack and leaves the result on the stack so no operands are required in the instruction encoding. A stack architecture in general achieves a much higher code density than that of a RISC machine with a lower system complexity and smaller program memory requirements [19].

A stack machine can achieve high computational power at a low cost because of its low processor complexity [19]. The cost of a chip relates directly to the number of transistors, a lower complexity processor will lower the total system cost, which is tightly constrained in small embedded systems. An especially favorable application area for stack machines is in real time embedded control applications, where small size, high performance and excellent support for interrupt handling are required [19].

Besides, it is easier to write compilers for stack machines since they have very few exceptional cases and, most of the time, the operands are just the top element of the stack and the T (top of stack) register. Writing a compiler can take up a significant amount of development time, and an efficient and error-free compiler is essential for testing the system.

# **3.3** Forth and its Applications

Although the C language appears to be the ubiquitous high level programming language for RISC machines, the development effort for a programming environment including assembler, compiler and operating system is rather large, and the code density is not particularly good. Forth is an obvious language to consider using on a stack machine. This is because Forth forms both a assembly and high level language for a stack processor with two stacks, one for expression evaluation and parameter passing, the other for storing subroutine return addresses. The Forth language basically defines a stack based computer architecture which will be emulated by the stack processors while executing Forth programs [19].

A Forth system is an interactive development environment which usually combines an assembler, stand-alone operating system, interpreter and compiler. A Forth system is typically built upon a small number of primitives, and the higher level routines call the lower level primitives to implement the rest of the system. The system (which bundles the operating system and compiler) is very simple and can be ported in a matter of several weeks, compared to man years of development effort for a reasonable C compiler.

Forth encourages reuse of code, all primitive functions being compiled into subroutines and all high level functions being compiled to lists of addresses (which point either to functions or primitive functions). It has been estimated that Forth machines typically have 2.5 to 8 times better code density than CISC designs and another 1.5 to 2.5 over RISC architectures [37].

Forth is interactive in nature and is widely used in embedded applications. Forth programs work by extending the language to include the functions needed to implement a given application. Unlike languages such as C or Fortran, control instructions (such as conditionals and loops) can also be extended by the user [38]. Enhanced functionality (e.g. object oriented features) can be added

25

to the language by the users. Forth's functionality is achieved with binary sizes usually measured in kilobytes. As an example, the public domain eForth 1.0 system [39] for the Intel 8086 microprocessor is less than 5K in size and the entire system can be ported to another microprocessor by rewriting the 31 primitive instructions upon which the system is based.

Forth programs are characterized by a high frequency of subroutine calls and returns, these instructions dominating all other operations. For a set of benchmark Forth programs, Koopman found a static frequency of approximately 33% and a dynamic frequency of 22% for call/return instructions [19]. This makes it very important to make the CALL and RETURN instructions as fast and compact as possible.

ANS Forth is an American National Standards Institute (ANSI) standard language [40]. Originally developed for the interactive control of telescopes in observatories using small computers [18], Forth has been successfully used in many well known embedded applications. Some notable examples are that Forth is used in the boot firmware for all Sun (and many other) workstations (IEEE 1275–1994 standard [16]), the Federal Express SuperTracker scanner/terminal [15], and in many space applications [17] such as the Galileo probe, space shuttle and Hopkins Ultraviolet Telescope. Several commercial microprocessors have been designed to run Forth such as Novix NC4016 [19], Harris RTX 2000 [19], Silicon Composers SC32 [19] and the Computer Cowboys MuP21 [20]. These chips achieved high performance, low power consumption and small area using very simple hardware designs.

## 3.4 MSL16

Microprocessors are being used in an extremely diverse range of applications from low cost simple applications to extremely high performance real-time ones. Incorporating a microprocessor enables embedded systems to perform more complex tasks without requiring an external microprocessor. On the other hand, the market for portable computing is growing rapidly as new generations of personal digital assistants (PDAs), intelligent cellular phones and other handheld devices are now available to consumers. These applications are characterized by their high performance computation power requirments within an exteremely constrained cost and power budget. Energy efficiency is critical as most portable devices are battery powered. A more energy efficient system will give a longer battery life for the same capacity. A larger battery is highly undesirable since it increases the size of a device, and a smaller device are naturally more favorable.

Traditional embedded processors which match the power and cost limitation cannot deliver the performance required by new applications. Incredible performance improvements have been made at the other end of the processor spectrum, with increased power dissipation and system cost that are not compatible with portable systems. This called for a new class of microprocessor which gives high computation power with small area, low power and energy efficient.

In [14], a microprocessor design and implementation called MSL16 (which stands for minimal instruction set, small and low power 16 bit microprocessor) which was developed to directly address these issues was presented. MSL16 has the following features:

- high speed

- small number of gates

- high code density

- a high level language programming language and operating system

- highly customizable for different applications

- portable to different FPGA devices and vendors (for FPGA based implementation)

MSL16 is a MISC (Minimum Instruction Set Computer) architecture. The basic idea behind MISC is simplicity and the principle of simplicity in RISC is strictly enforced. MSL16 has a minimal instruction set of 17 instructions, a 16– bit datapath and very simple control and datapath. Most instructions are 4 bits in length, contributing to a high instruction density and low memory bandwidth requirements. Unlike RISC machines, MSL16 does not require cache memory as the use of a slower memory will not severely degrade the system performance. It has been shown that large caches may take up to 90% of the total chip area and dissipate about 43% of the total chip power [13].

MSL16 is a stack architecture which in general achieves a higher code density than RISC machines. Additionally, MSL16 was designed to execute the programming language "Forth". Forth machines typically have a higher code density than CISC and RISC designs [37]. Code density relates directly to system power consumption and with battery operated devices such as mobile phones, PDAs and laptop computers becoming increasingly popular, power consumption is becoming increasingly important. In a portable application such as the Berkeley Infopad project [12], the total system's power consumption (1.2 W) is dominated by the power consumption of a static RAM memory (600 mW) rather than that of the ARM60 microprocessor (120 mW). A processor with higher code density requires less memory to operate without lowering its performance. This implies a processor with higher code density is more power efficient.

Without incorporating any cache inside the processor, having a high code density and simple architecture, MSL16 can be fast and yet very small and low power. These characteristics tightly match the requirments of the portable market. The MSL16 architecture is presented below, and how it improves the code density of Forth program is detailed in Section 3.4.6. MSL16A is the asynchronous re-implementation of MSL16 which shares the same architecture and it is a small, fast, low power and high code density microprocessor. The design methodology and implementation detail of MSL16A are presented in Chapter 4 and Chapter 5 respectively.

#### 3.4.1 Architecture

The architecture of MSL16 is similar to that of MuP21 [20]. The MuP21 is a 20-bit CPU which has 25 5-bit instructions and implemented in  $1.2\mu$ m CMOS process, uses 7000 CMOS transistors and has a peak execution rate of 100 MIPS. The synchronous prototype of the MSL16 architecture was synthesized from a VHDL description. It was highly portable and was designed to be easily customized for particular applications and/or retargeted for different FPGA devices and vendors. Compared with the MuP21, the MSL16 architecture has 16 4-bit instructions, and when implemented using a Xilinx Inc, 4000 series FPGA, occupies 175 configurable logic blocks (CLBs) at a peak execution rate of 33 MIPS on a 4006E-1 device. The results of this prototype is presented in Chapter 6.

MSL16 is a dual stack machine with 16-bit data and memory buses. The data stack is used for temporary variable storage and subroutine parameter passing, and the return stack is used mainly to hold subroutine return addresses. The data and return stack are implemented internally which allows them to be accessed in parallel with instruction fetches on the memory bus. A two stage FETCH/EXECUTE pipeline is employed so that the following two steps operate in parallel

```

FOREVER

ł

1. Fetch a 16-bit word from memory

and latch in the instruction

register (IR)

2. If the most significant bit of IR set

{

CALL instruction - other 15 bits

form the subroutine address

}

else

{

IR contains four instructions -

execute in sequence (first slot

can only use the lower 3 bits so

must have 0 <= opcode < 8).

}

```

}

With the exception of the CALL instruction, MSL16 instructions are encoded with 4 bits, allowing four instructions to be packed in one 16 bit word. A 16-bit instruction fetch generally obtains 4 instructions, excluding those with CALL or LIT instructions, reducing the required memory bandwidth and overall system power consumption. As a result, the effect of starvation of the pipeline on performance is reduced and hence using a memory 4 times slower than the average cycle time would not significantly reduce the performance of the processor. This could also reduce the cost of building an embedded system with MSL16A. A pipeline stage is said to be starved if it is forced to wait for the previous stage

Figure 3.1: Instruction format for MSL16

to complete.

The execution speed of MSL16 is high because of its simple instruction set, and a short critical delay path. The two stage pipeline has a low latency so the effect of stalling the pipeline during memory operations and branches is reduced. The top of stack is implemented as a separate register, the  $\mathbf{T}$  register. Operands to the ALU are normally the two top elements of the stack and the result is usually stored in the  $\mathbf{T}$  register. This scheme virtually eliminates the instruction decoding and register fetch process normally required in a RISC machine.

#### 3.4.2 Instruction Set

The instruction format used for MSL16 is shown in Figure 3.1. All of the instructions with the exception of CALL and LIT expect their operands to be on the stack. If the most significant bit of the instruction register is set, it is a CALL instruction and the remaining 15 bits form the subroutine address. In other words, the first slot can only contain a limited set of instructions with opcode<8. If LIT appears in the first or second slot of the IR, its operand will be loaded from the least significant byte of the IR. However, if LIT appears in the final slot, the processor status word containing system flags will be loaded into the T register. To load a full 16-bit literal into the T register, 2 successive LITs, one placed in the first slot and the other in the second slot, followed by an XOR instruction are required. The operand of the first LIT instruction contains the most significant byte of the literal while the operand of the second LIT instruction contains the least significant byte of the literal. The XOR instruction will merge them correctly into a single 16-bit value stored in T.

| Opcode | Instruction | Action                                              |

|--------|-------------|-----------------------------------------------------|

| 0      | NOP         | no operation                                        |

| 1      | AND         | $T \Leftarrow T$ AND DS, pop DS                     |

| 2      | XOR         | $T \Leftarrow T XOR DS, pop DS$                     |

| 3      | +           | $T \Leftarrow T + DS$ , pop DS                      |

| 4      | 0=          | $T \Leftarrow -1$ if (T=0) else                     |

|        |             | $T \Leftarrow 0$                                    |

| 5      | LIT         | push T to DS,                                       |

|        |             | if LPC = 0, T $\leftarrow$ LSB(IR)&"00000000"       |

|        |             | if LPC = 1, T $\Leftarrow$ "00000000"&LSB(IR)       |

|        |             | if $LPC = 3$ , T $\Leftarrow$ processor status word |

| 6      | 2/          | $T \Leftarrow T / 2$                                |

| 7      | -           | $T \Leftarrow DS - T$ , pop DS                      |

| 8      | DUP         | push T to DS                                        |

| 9      | DROP        | pop DS to T                                         |

| 10     | GOTO        | Jump to T if $T \neq 0$ , pop DS to T               |

| 11     | R>          | push T to DS, pop RS to T                           |

| 12     | >R          | push T to RS, pop DS to T                           |

| 13     | 0           | LOAD mem[T] to T                                    |

| 14     | !           | STORE T to mem[ds]                                  |

| 15     | SWAP        | Swap T with DS                                      |

|        |             | •                                                   |

| MSB=1  | CALL        | PUSH PC to RS, jump to IR                           |

Table 3.1: The MSL16 instruction set

The instruction set of MSL16 is given in Table 3.1. For the synchronous version, instructions involving a memory reference (@ and !), change the flow of execution, (CALL and GOTO) and SWAP take two cycles and the remaining

instructions are single cycle. However, for MSL16A, all instructions are completed in a single cycle with different cycle time and the pipeline will adjust automatically. Some instructions just take longer to complete.

In MSL16A, the fetch and execute stages do not have fixed cycle times. The fetch cycle depends on the speed of the external memory while the execute cycle depends on the instructions executed and their operands as well. For example, 1-1 (implemented as 1 + (-1)) will take longer to complete than 1+1 in the ALU.

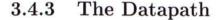

The datapath of MSL16 is shown in Figure 3.2. The main components in the datapath of MSL16 are

- A data stack (DS) for temporary variables and subroutine parameters. The very top element of the stack is stored in a separate register T so that the top two stack elements are available to the ALU.

- A return stack (RS) to store subroutine return addresses

- An instruction register(IR) which holds the four 4-bit instructions to be executed

- A PC (Program Counter) which stores the address of the next instruction

- An IR (Instruction Register) which stores the instruction being executed

- An ALU which takes operands from T and the top element of DS or RS the result will be returned to T.

The data stack and return stack are both  $32 \times 16$  bits in size. A study has shown that a stack depth of 32 is sufficient for most reasonable programs [37]. The PC is actually composed of a 2-bit nibble PC(LPC) and and a 14-bit word PC(WPC). The WPC stores the address of the next instruction while the LPC is used to keep track of which of the four instructions in the IR is currently being executed. The LPC will be reset to zero automatically when a LIT, CALL or GOTO instruction is encountered.

#### 3.4.4 Interrupts and Exceptions

MSL16 does not currently support interrupts or exceptions. Stack machines generally have good interrupt performance since there are no registers to save. The cause of the interrupt is easy to determine since the simple pipelining means there is only a single instruction being executed at any time.

#### 3.4.5 Implementing Forth primitives

All Forth primitives must be represented by the 17 instructions of MSL16 if the stack architecture defined by Forth are to be emulated. AND, XOR, +, -, 0=, DUP, DROP, SWAP, R>, >R, 2/, @ and ! are directly supported. The most frequently used Forth primitives which are not directly implemented are translated in Table 3.2. The first column lists the most frequently used but not included Forth primitives and the corresponding translation in MSL16's instructions are shown in the second column. The equivalent instruction sizes in bits are included for the estimation of code density of MSL16 to compare with a 16-bit Forth reference machine [19].

| Forth Primitive | Translated Instructions                                  | Instruction Size (bits)         |

|-----------------|----------------------------------------------------------|---------------------------------|

| 0BRANCH         | 0=, LIT addr_msb, LIT addr_lsb<br>XOR, AND, GOTO         | $4 \times 4 + 16 \times 2 = 48$ |

| 2*              | DUP, +                                                   | 4 + 4 = 8                       |

| BRANCH          | LIT addr_msb, LIT addr_lsb<br>XOR, GOTO                  | $16 \times 2 + 4 \times 2 = 40$ |

| DDROP           | DROP, DROP                                               | $4 \times 2 = 8$                |

| OVER            | >R, DUP, R>, SWAP                                        | $4 \times 4 = 16$               |

| EXIT            | R>, GOTO                                                 | $4 \times 2 = 8$                |

| LIT             | LIT const_msb, LIT const_lsb, XOR $16 \times 2 + 4 = 36$ |                                 |

Table 3.2: Translation of Forth primitives

#### 3.4.6 Code Density Estimation

By translating the most frequently used Forth primitives, the code density of Forth programs implemented with MSL16A's own instruction set could be estimated. In [19], the static instruction frequencies of all Forth primitives for a 16-bit Forth system are listed. The list was compiled with four benchmark programs. The average static frequencies (of the four benchmark programs) are used to calculate the average instruction size for MSL16.

| Forth Primitive | Static Frequency<br>(X%) | Instruction<br>size (Y bits) | X*Y    | average instruction size |

|-----------------|--------------------------|------------------------------|--------|--------------------------|

|                 |                          |                              |        |                          |

| !               | 2.32                     | 4                            | 9.28   | $798.07 \div 76.17$      |

| +               | 2.90                     | 4                            | 11.60  | =10.48 bits              |

| -               | 1.52                     | 4                            | 6.08   |                          |

| <b>OBRANCH</b>  | 3.10                     | 48                           | 148.80 |                          |

| 2*              | 1.49                     | 8                            | 11.92  |                          |

| >R              | 1.36                     | 4                            | 5.44   |                          |

| 0               | 5.59                     | 4                            | 22.36  |                          |

| BRANCH          | 1.73                     | 40                           | 69.2   |                          |

| CALL            | 25.87                    | 1                            | 25.87  |                          |

| DDROP           | 1.42                     | 8                            | 11.36  |                          |

| DROP            | 1.86                     | 4                            | 7.44   |                          |

| DUP             | 3.28                     | 4                            | 13.12  |                          |

| EXIT            | 7.47                     | 8                            | 59.76  |                          |

| LIT             | 9.41                     | 36                           | 338.76 |                          |

| OVER            | 2.49                     | 16                           | 39.84  |                          |

| R>              | 1.50                     | 4                            | 6.00   |                          |

| SWAP            | 2.81                     | 4                            | 11.24  |                          |

| TOTAL           | 76.17                    | TOTAL                        | 798.07 |                          |

Table 3.3: Code Density Calculation

The first column in Table 3.3 contains the most frequently used Forth primitives and the average static frequencies listed in [19] are shown in the second column. The third column lists the number of bits required to translate the primitive into MSL16's own instructions. The average instructions size of MSL16 was found to be about 10.48 bits long. This means that the same Forth program compiled for MSL16 can be 34.5% smaller than that for the 16-bit reference system. Because of its high code density, a system built with MSL16 can utilize a smaller external memory to store program codes. This also implies that MSL16 required smaller caches to improve system performance although no cache is incorporated in MSL16 currently.

As illustrated in the Berkeley InfoPad project [12], a processor does not dominate a system's total power dissipation, the memory itself can consume 50% of the total power. Similarly, the two large caches in the StrongARM 110 [13] consume 43% of the total chip power and fill up 90% of the total chip area. As a result, for extremely low power systems, it is crucial to optimize the whole system instead of just making a low power processor. A 34.5% smaller main memory and a smaller cache can lower the total system power consumption and size remarkably. This will be particularly beneficial to battery operated embedded systems.

### 3.5 Summary

A brief introduction to RISC machines, stack machines and the Forth language was presented in this chapter. Stack machines are simple, small and fast which are critical in real time systems and many stack machines were designed to run Forth. The Forth language is based on a set of primitives that execute on a stack machine architecture. It has been estimated that Forth machines have 1.5 to 2.5 times better code density than RISC designs [37]. Code density relates directly to power efficiency as it affects the memory and cache sizes, which can consume up to 50% of the total system power, in a low power system.

Also developed in this chapter was the architecture of MSL16. MSL16 is a dual stack machine with 16-bit data and memory buses designed to run Forth. A two stage pipeline is employed and the instruction set is minimal. MSL16 is fast and power efficient because of its simple architecture, doesn't require fast memory or caches and its high code density. The code density of MSL16 was estimated to be 34.5% higher than a 16-bit Forth reference system which makes it highly desirable for low power applications like battery operated portable systems.

# Chapter 4

# Design Methodology

MSL16A was implemented based on Martin's synthesis method [21]. An advantage of such compilation-based method over other methods is that complex concurrent systems can be described concisely in high level constructs without low-level timing concerns, which makes modification and verification of the system behavior easier. The asynchronous circuits used are called *quasi-delayinsensitive*(QDI) circuits which do not use any assumption on delays in operators and wires [21]. The asynchronous control logic was designed using the Caltech Asynchronous Synthesis Tools (CAST), which is discussed in Chapter 5, while the datapath components were realized by manual layout with the layout editor Magic [41].

This chapter details how MSL16A was implemented based on Martin's synthesis method. The first section gives the basic notations used in the higher level description of the processor while subsequent sections describe the compilation methods. For a more complete explanation of the algorithm, readers are suggested to read [21].

### 4.1 Basic Notation

The notation used in describing the processor at a high level, is based on C.A.R. Hoare's Communicating Sequential Processes (CSP) [32]. A full description of the notation used in this paper can be found in [21].

An assignment of an expression e to a variable b is "b := e". If x is a Boolean variable,  $b \uparrow$  and  $b \downarrow$  represents b :=true and b :=false respectively.

A selection statement is of the form  $[G_1 \to S_1 \ ] \dots \ ] G_n \to Sn]$ .  $G_i \to S_i$  a "guarded command" where  $G_1$  through  $G_n$  are Boolean expressions (the guards of the commands) and  $S_1$  through  $S_n$  are program parts. The operational semantics of the selection statement is: "Wait until one of the  $G_i$ 's is **true**, then choose a guarded command with a **true** guard non-deterministically and execute the corresponding program part." [G] is equivalent to  $[G \to \text{skip}]$ , which means "wait until G is **true**".

A loop statement is of the form  $*[G_1 \to S_1 \ ] \dots \ ] G_n \to Sn]$ . The operational semantics is: "Choose a guarded command with a **true** guard, execute the corresponding program part and then repeat until all  $G_i$ 's are **false**". \*[S] stands for  $*[\mathbf{true} \to \mathbf{S}]$  and means "repeat S forever".

For a communication channel X, X!u means the communication action of sending the value of expression u through channel X. Similarly, X?v denotes the communication action of receiving the value from channel X and storing it in variable v. The combined effect of the two statements is to assign the value u from a process to variable v of another process. X!u cannot complete and its native process suspends unless X?v is executed in the corresponding process. Thus, dataless channels can be used to enforce synchronization between processes. A communication action on such a channel is expressed by naming the action with the channel's name. The boolean expression  $\overline{X}$ , the probe of channel X, is **true**  if a communication action over channel X is pending, i.e. communication action X can be completed without suspension.

Moreover, sequential composition is represented by a ";" and parallel composition, which is weakly fair, is denoted by "  $\parallel$ ". Finally, " $X \bullet Y$ ", *coincident execution*, means communication actions over channels X and Y are to complete at the same time.

## 4.2 Specification of MSL16A

At the top-most level, MSL16A was described by a high level sequential program which is a non-terminating loop containing the FETCH and EXECUTE stages of the pipeline. The complete sequential program for the microprocessor is shown below:

$$\begin{aligned} *[FETCH:i,pc:=mem[pc],pc+1;\\ EXECUTE:[alu(i.op) \rightarrow tos:=aluf(tos,ds[k],i.op)\\ & \left[nop(i.op) \rightarrow skip\right]\\ & \left[lit(i.op) \rightarrow [lpc=0 \rightarrow tos:=lsb(ir) \& "0000000"\\ & \left[lpc=1 \rightarrow tos:="00000000"\& lsb(ir)\right]\\ & \left[lpc=3 \rightarrow tos:="sw\right]\\ & \left[lpc=3 \rightarrow tos:=psw\right]\\ & \left[dup(i.op) \rightarrow ds[k]:=tos\\ & \left[drop(i.op) \rightarrow tos:=ds[k]\right]\\ & \left[goto(i.op) \rightarrow [tos!=0 \rightarrow pc:=tos\\ & \left[ltos=0 \rightarrow skip\right]\\ & \left[rto(i.op) \rightarrow ds[k]:=tos;tos:=rs[k]\\ & \left[tor(i.op) \rightarrow rs[k]:=tos;tos:=ds[k]\right]\\ & \left[at(i.op) \rightarrow tos:=mem[tos]\end{aligned}$$

]

$$\begin{aligned} \|store(i.op) \to mem[ds[k]] &:= tos \\ \|swap(i.op) \to tos \Leftrightarrow ds[k] \\ \|call(i.op) \to rs[k] &:= pc; pc := ir \\ ] \end{aligned}$$

The sequential program is basically a loop statement which denotes the FETCH and EXECUTE stages of MSL16A are repeated forever. The *FETCH* and *EX*-*ECUTE* inside the program are labels inserted simply for illustration purpose. Variable i contains the instruction which is currently being executed. It is described in the **PASCAL** record notation as a structured variable consisting of several fields. All instructions contain an *op* field for *opcode* while the parameter fields depend on the types of the instructions, which were described in Chapter 3.

The array mem describes the external memory and the indexes pc to it describe the program counter. The data stack and return stack are described by the arrays ds[k] and rs[k] while variable k points to the currently active element in the stacks. The design and implementation of the stacks are discussed in Chapter 5.

Variable tos represents a separate top-of-stack register which allows concurrent access to tos and ds[k] (top element of data stack) for the ALU. The instruction register is described as *ir* and, similarly, the least-significant-byte of the instructions, which is used by **LIT**, is represented as lsb(ir). For example,  $dup(i.op) \rightarrow ds[k] := tos$  means if the instruction currently being executed is **DUP**, the value of the top-of-stack register will be pushed into the data stack. In **SWAP**,  $tos \Leftrightarrow ds[k]$  indicates the value of the top-of-stack register and the value of the currently active data stack elements is swapped.

## 4.3 Decomposition into Concurrent Processes

The previous sequential program was then decomposed into a set of concurrent processes, which operate in parallel, communicate and synchronize with each other through *channels*, based on Hoare's CSP (Communicating Sequential Processes) model [32]. A channel connects two processes and the two ends of a channel are called *ports*. Attempts were made to convert each process into smaller sub-processes until it was simple enough such that no further decomposition is necessary. The final program of MSL16A is discussed below in two parts.

/\* FETCH : continuously fetches instructions \*/  $FETCH \equiv *[JR1; PCI1; JR2; PCI2]$

/\* JR : temporary instruction holder will discard instructions when necessary pre-decode for CALL, ISCALL stalls the pipeline \*/  $JR \equiv *[[\overline{JR1} \rightarrow JR1; DOUT?i; JR2; [\overline{INST1} \& !call \rightarrow INST1!i; INST2]$   $[]\overline{INST1} \& call \rightarrow INST1!i; INST2; ISCALL$   $[]\overline{NEXTa} \rightarrow NEXTa]$ ]

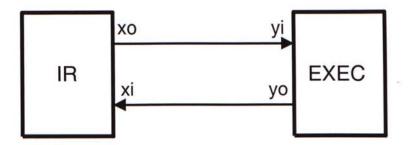

/\* IR : instruction register

fetch instruction from JR and pass to EX 4-bit at a time  $*/IR \equiv *[INST1?i; INST2;$

$E1!i \bullet LPI1; [\overline{E2} \to LPI2; E2; E1!i \bullet LPI1; [\overline{E2} \to LPI2; E1]; [\overline{E2} \to LP$

$\left[\overline{NEXTb} \to E2; LPI2\right]$

$$\begin{bmatrix} \overline{NEXTb} \to E2; LPI2 \end{bmatrix}$$

$$\begin{bmatrix} \overline{NEXTb} \to E2; LPI2 \end{bmatrix}$$

$$\begin{bmatrix} \overline{NEXTb} \to E2; LPI2 \end{bmatrix}$$

/\* LPC : nibble pc

]

controls the mux to EX also \*/

$$LPC \equiv (*[[\overline{LPI1} \rightarrow LPI1; x := lpc + 1; [\overline{LPI2} \rightarrow lpc := x \bullet LPI2$$

$$[]\overline{LZ} \rightarrow lpc := 0 \bullet LZ; LPI2$$

$$]$$

$$]|*[[[\overline{LPI1} \& lpc = 0 \rightarrow LPI1 \bullet Na1; LPI2 \bullet Na2$$

$$[]\overline{LPI1} \& lpc = 1 \rightarrow LPI1 \bullet Nb1; LPI2 \bullet Nb2$$

$$[]\overline{LPI1} \& lpc = 2 \rightarrow LPI1 \bullet Nc1; LPI2 \bullet Nc2$$

$$[]\overline{LPI1} \& lpc = 3 \rightarrow LPI1 \bullet Nd1; LPI2 \bullet Nd2$$

$$]]$$

)