# Bus-Driven Floorplanning

#### LAW Hoi Ying

A Thesis Submitted in Partial Fulfillment of the Requirements for the Degree of Master of Philosophy

in

Computer Science & Engineering

©The Chinese University of Hong Kong August 2005

The Chinese University of Hong Kong holds the copyright of this thesis. Any person(s) intending to use a part or the whole of the materials in this thesis in a proposed publication must seek copyright release from the Dean of the Graduate School.

## Abstract

As technology advances, the complexity of VLSI circuit design grows rapidly. Interconnect-driven floorplanning has become a major concern in modern floorplanning. Bus is a collection of wires running over a set of modules. It is favorable to align the set of modules that a bus goes through in such a way that routing can be done easily. In this thesis, the bus-driven floorplanning problem in 2D and 3D chips is considered. Besides, a 3D floorplan representation is proposed to solve the 3D floorplanning problem.

The bus-driven floorplanning problem involves the placement of blocks and buses. Given a set of blocks and bus specifications (the width of each bus and the blocks that the bus need to go through), we will generate a floorplan solution such that all the buses go through their blocks in less than or equal to 2-bends, with the area of the floorplan and the total area of the buses minimized. The approach proposed is based on a simulated annealing framework. Using the sequence pair representation, we derived and proved some necessary conditions for feasible buses, for which we allow 0-bend, 1-bend, or 2-bend. Then, we check whether there are buses that cannot be placed at the same time. Finally, a solution is generated giving the coordinates of the modules and the buses. Comparing with the most updated previous work by Xiang et al., our algorithm can handle buses going through many blocks and the dead space of the floorplan obtained is also reduced.

3D chips are useful in reducing interconnect lengths. However, there is not much previous work done in 3D floorplanning. In this thesis, we have proposed a 3D floorplan representation called Layered Transitive Closure Graph (LTCG), based on the Transitive Closure Graph (TCG) representation for non-slicing floorplans, in addition with some layer information. A method is introduced to align blocks (of the same bus) on different layers. A floorplanner is implemented using the LTCG representation. Experimental results have shown that LTCG is a promising representation for 3D floorplans and can handle bus planning in 3D floorplan effectively.

# 摘要

隨著科技進步,超大規模集成電路的複雜性正在迅增長。互連電路主導的佈局規劃成為了現代佈局的一個重要課題。匯流排是一組需要經過數個組件的電線。如果那些組件在佈局規劃時已被排列成可以讓匯流排容易通過的序列,會令到整個設計過程更流暢。在本論文中,我們將會發表一個有效的匯流排主導佈局規劃方案。此外,由於三維電路可以有效解決互連電路的問題,我們將會發表一個三維的佈局規劃表示法。

匯流排主導佈局規劃問題牽涉組件和匯流排。已知一組組件和匯流排規格(包括匯流排的寬度和匯流排須要經過哪些組件),我們要計算出一個可以讓所有匯流排經過組件的佈局規劃,而匯流排最多可以屈曲兩次,同時要令整個佈局規劃的面積縮到最少。我們提出的方案用了模擬降溫法。根據序列組的表示法,我們衍生出和證明了一些可行匯流排的必要條件,而我們只允許匯流排零屈曲、一次屈曲、或是兩次屈曲。然後,我們會檢查是否有些匯流排不能同時存在。最後,我們會得到一個包含所有組件座標和匯流排座標的佈局規劃。與Xiang等提出的方案發表的結果比較,我們的方案可以處理一些經過很多組件的匯流排,而無效位置也比他們的少。

三維晶片對於減少互連電線長度很有效。然而,在這個範疇沒有很多前人的工作。在這論文中,我們根據Transitive Closure Graph (TCG)提出了一個三維的佈局規劃表示法名為Layered Transitive Closure Graph (LTCG),加入了層的資訊。我們提出了一個方法去排列同一個匯流排在不同層要經過的組件。我們研究了一個佈局規劃配置器。實驗結果證明了LTCG是一個大有可為的三維佈局規範表示法,而且能夠效率地處理匯流排

# Acknowledgments

First of all, I must thank my supervisor, Professor Evangeline Fung Yu Young. She has helped me a lot in my research. Throughout the two years studies, she has given me guidances, encouragements, ideas, and advices. She is considerate and understanding. Without her, I am not possible to finish this work.

I would like to express my thanks to my marker, Professor David Yu Liang Wu. He has given me invaluable advices and constructive suggestions, which are very helpful for improvement of my work.

I would also like to thank the authors of [1] who have kindly given us their program and test cases, such that we can conduct the experiments and compare our results with theirs.

Finally, I would like to thank my colleagues. They have supported me and bolstered me. Without them, I would not have such an enjoyable and memorable school life in my memory.

# Contents

| 1 | Intr | oduction                                        | 1  |

|---|------|-------------------------------------------------|----|

|   | 1.1  | VLSI Design Cycle                               | 2  |

|   | 1.2  | Physical Design Cycle                           | 6  |

|   | 1.3  | Floorplanning                                   | 10 |

|   |      | 1.3.1 Floorplanning Objectives                  | 11 |

|   |      | 1.3.2 Common Approaches                         | 12 |

|   |      | 1.3.3 Interconnect-Driven Floorplanning         | 14 |

|   | 1.4  | Motivations and Contributions                   | 15 |

|   | 1.5  | Organization of the Thesis                      | 17 |

| 2 | Lite | rature Review on 2D Floorplan Representations 1 | 18 |

|   | 2.1  | Types of Floorplans                             | 18 |

|   | 2.2  | Floorplan Representations                       | 20 |

|   |      | 2.2.1 Slicing Floorplan                         | 21 |

|   |      | 2.2.2 Non-slicing Floorplan                     | 22 |

|   |      | 2.2.3 Mosaic Floorplan                          | 30 |

|   | 2.3  | Summary                                         | 35 |

| 3 | Lite | rature Review on 3D Floorplan Representations 3 | 7  |

|   | 3.1  | Introduction                                    | 37 |

|   | 3.2  | Problem Formulation                             | 38 |

|   | 2 2  | Provious Work                                   | 22 |

|   | 3.4  | Summa   | ary                                       | 12 |

|---|------|---------|-------------------------------------------|----|

| 4 | Lite | rature  | Review on Bus-Driven Floorplanning 4      | 4  |

|   | 4.1  | Proble  | m Formulation                             | 14 |

|   | 4.2  | Previo  | us Work                                   | 15 |

|   |      | 4.2.1   | Abutment Constraint                       | 15 |

|   |      | 4.2.2   | Alignment Constraint                      | 19 |

|   |      | 4.2.3   | Bus-Driven Floorplanning                  | 2  |

|   | 4.3  | Summ    | ary                                       | 3  |

| 5 | Mu   | lti-Ben | d Bus-Driven Floorplanning 5              | 5  |

|   | 5.1  | Introd  | $\operatorname{uction}$                   | 5  |

|   | 5.2  | Proble  | em Formulation                            | 6  |

|   | 5.3  | Metho   | dology                                    | 57 |

|   |      | 5.3.1   | Shape Validation                          | 8  |

|   |      | 5.3.2   | Bus Ordering                              | 5  |

|   |      | 5.3.3   | Floorplan Realization                     | 2  |

|   |      | 5.3.4   | Simulated Annealing                       | 3  |

|   |      | 5.3.5   | Soft Block Adjustment                     | 5  |

|   | 5.4  | Exper   | imental Results                           | 5  |

|   | 5.5  | Summ    | ary                                       | 7  |

| 6 | Bu   | s-Drive | en Floorplanning for 3D Chips 8           | 0  |

|   | 6.1  | Introd  | luction                                   | 0  |

|   | 6.2  | Proble  | em Formulation                            | 1  |

|   | 6.3  | The R   | Representation                            | 2  |

|   |      | 6.3.1   | Overview                                  | 2  |

|   |      | 6.3.2   | Review of TCG                             | 3  |

|   |      | 6.3.3   | Layered Transitive Closure Graph (LTCG) 8 | 4  |

|   |      | 6.3.4   | Aligning Blocks                           | 5  |

| Bi | bliog | aphy 10                    | <b>)1</b> |

|----|-------|----------------------------|-----------|

| 7  | Con   | usion                      | 99        |

|    | 6.8   | acknowledgement            | 95        |

|    | 6.7   | ummary                     | 94        |

|    | 6.6   | Experimental Results       | 93        |

|    | 6.5   | oft Block Adjustment       | 92        |

|    | 6.4   | imulated Annealing         | 92        |

|    |       | .3.5 Solution Perturbation | 87        |

# List of Figures

| 1.1  | The VLSI Design Cycle.[2]                                     | 3  |

|------|---------------------------------------------------------------|----|

| 1.2  | A Physical Design Cycle.[2]                                   | 7  |

| 1.3  | Pseudo Code of Simulated Annealing                            | 14 |

| 1.4  | Pseudo Code of Genetic Algorithm                              | 15 |

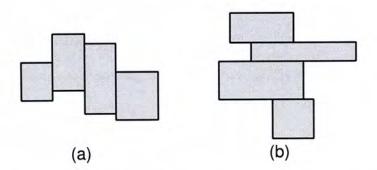

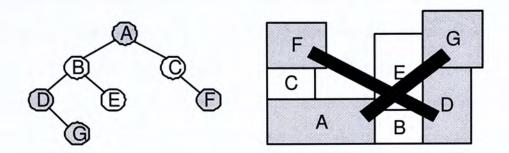

| 2.1  | Examples of the Three Main Kinds of Floorplans                | 18 |

| 2.2  | One of the Properties of Mosaic Floorplan                     | 19 |

| 2.3  | Floorplans Categories                                         | 20 |

| 2.4  | An Example of a Slicing Tree and Its Normalized Polish Ex-    |    |

|      | pression                                                      | 21 |

| 2.5  | Constraint Graphs for the Sequence Pair $(ABDECF, CBFADE)$ .  | 23 |

| 2.6  | (a) An Example of a BSG. (b) A Domain $BSG_{p\times q}$       | 24 |

| 2.7  | Representing a Floorplan Using BSG                            | 26 |

| 2.8  | An Admissible Placement and Its Horizontal Constraint Graph.  | 27 |

| 2.9  | A Floorplan and Its Corresponding B*-Tree Representation      | 28 |

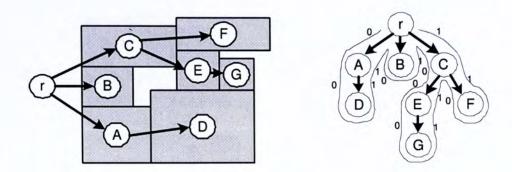

| 2.10 | A Floorplan and Its Corresponding TCG Representation          | 29 |

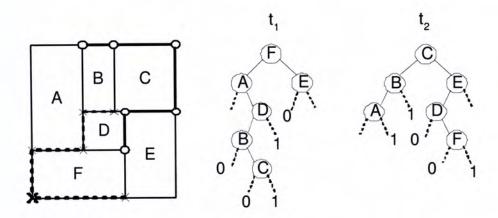

| 2.11 | Constructing a CBL from A Floorplan                           | 31 |

| 2.12 | A Non-Slicing Floorplan and Its TBT Representation            | 32 |

| 2.13 | A Floorplan Realization Example using TBS                     | 34 |

| 3.1  | (a) A 3D Slicing Tree. (b) The 2D Slicing Tree and the Floor- |    |

|      | plans of Each Layer                                           | 40 |

| 3.2  | A Floorplan Represented by CBA                                | 42 |

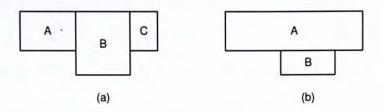

| 4.1  | (a) A Feasible Partitioning. (b) An Infeasible Partitioning                  | 46 |

|------|------------------------------------------------------------------------------|----|

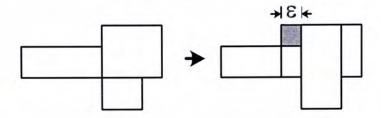

| 4.2  | A Rectilinear Block That Cannot Be Decomposed into Two L-                    |    |

|      | Shape Sub-Blocks and Its $\epsilon$ -Approximation                           | 46 |

| 4.3  | (a)<br>Block $A$ is Abutted With Block $B, C,$ and<br>D. (b)<br>Block $A$ is |    |

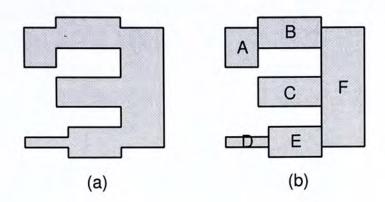

|      | Abutted With Block $D$ , Block $C$ is Abutted With Block $F.$                | 47 |

| 4.4  | Abutment Constraint Alone is Not Enough to Form a L-Shape.                   | 48 |

| 4.5  | (a) A H-Sequential Rectilinear Block. (b) A V-Sequential Rec-                |    |

|      | tilinear Block                                                               | 48 |

| 4.6  | (a) A Non-Sequential Rectilinear Block. (b) It is Partitioned                |    |

|      | into Several Sub-Blocks                                                      | 49 |

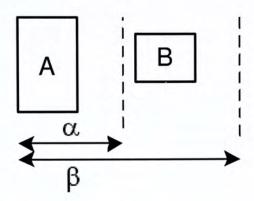

| 4.7  | Relative Placement Constraint: $h(A, B) = [\alpha, \beta]$                   | 50 |

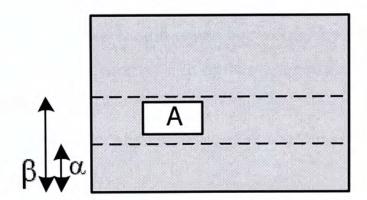

| 4.8  | Absolute Placement Constraint: $v(BB, A) = [\alpha, \beta] \dots \dots$      | 50 |

| 4.9  | A Twisted-Bus Structure                                                      | 53 |

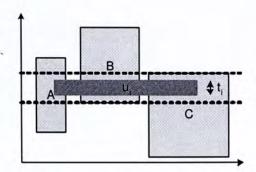

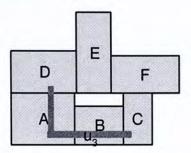

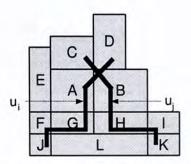

| 5.1  | Bus $u_i$ Goes Through $A$ , $B$ , and $C$                                   | 57 |

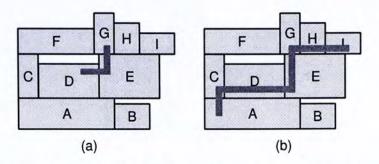

| 5.2  | (a) A 1-Bend Bus. (b) A 3-Bend Bus                                           |    |

| 5.3  | Two Valid 0-Bend Buses, $\{A,B,C\}$ and $\{C,F\}$                            | 59 |

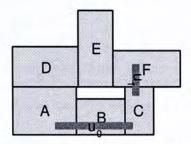

| 5.4  | A Valid 1-Bend Bus $\{A,B,C,D\}$                                             | 62 |

| 5.5  | Bus $u_4$ Cannot Be Realized as A 1-Bend Bus                                 | 63 |

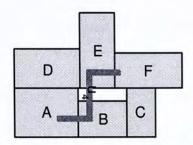

| 5.6  | In Some Cases, A T-Shaped Bus Can Be Changed into A Valid                    |    |

|      | 2-Bend Bus                                                                   | 63 |

| 5.7  | The Necessary Conditions for The Position Sets to Form A Valid               |    |

|      | 2-Bend Shape                                                                 | 65 |

| 5.8  | Pseudo Code of Shape Validation                                              | 66 |

| 5.9  | Pseudo Code of 1-Bend Checking                                               | 67 |

| 5.10 | Pseudo Code of 2-Bend Checking                                               | 68 |

| 5.11 | Bus $u_i$ Has to Be Placed on The Left of $u_j$ and Bus $u_j$ Has to         |    |

|      | Be Placed on The Left of Bus $u_i$                                           | 69 |

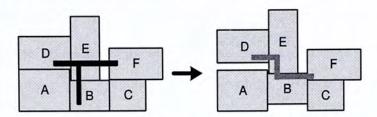

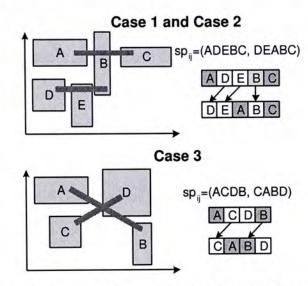

| 5.12 | A 2-Bend Bus is Broken Down into Three 0-Bend Components                        |    |

|------|---------------------------------------------------------------------------------|----|

|      | for Checking The Ordering Constraints                                           | 70 |

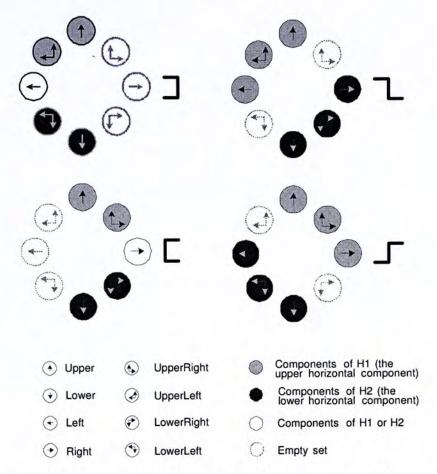

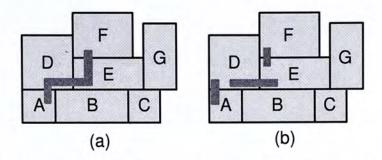

| 5.13 | Different Cases of The Bus Ordering Constraint                                  | 70 |

| 5.14 | Adding Bend to Resolve Bus Ordering Conflict                                    | 72 |

| 5.15 | Pseudo Code of The Basic Alignment Step for Horizontal Buses.                   | 73 |

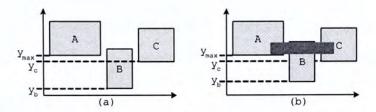

| 5.16 | (a) $y_{max}$ , $y_b$ , and $y_c$ are Calculated Correspondingly. (b) $y_b$ Has |    |

|      | to Be Moved Up to Let The Bus Go Through                                        | 73 |

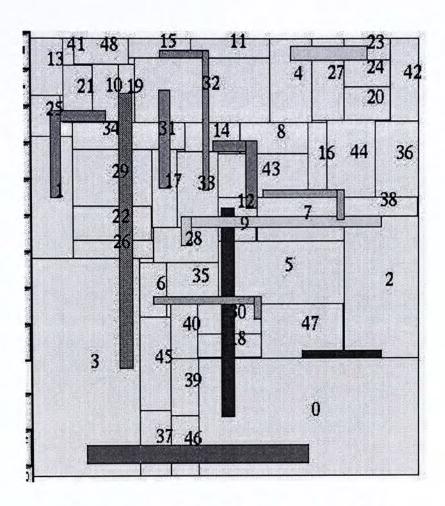

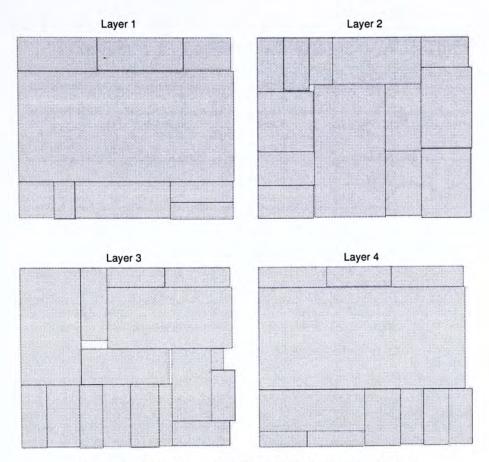

| 5.17 | Result Packing of ami49-2                                                       | 78 |

| 5.18 | Result Packing of ami49-3                                                       | 78 |

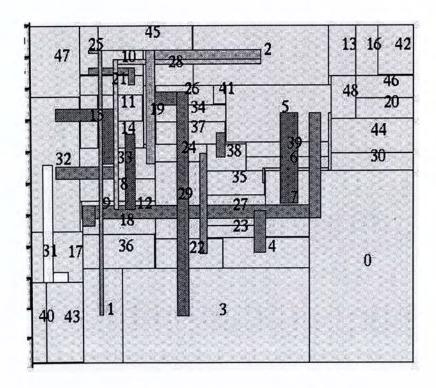

| 5.19 | Result Packing of ami49-6                                                       | 79 |

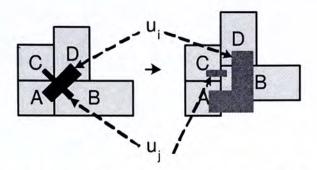

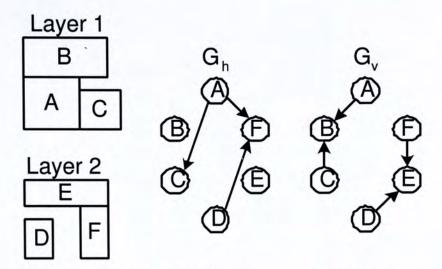

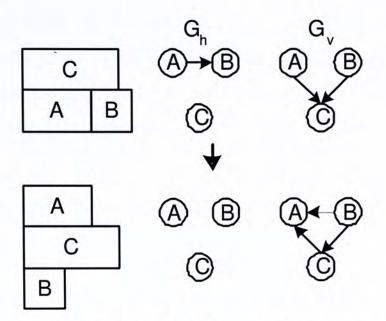

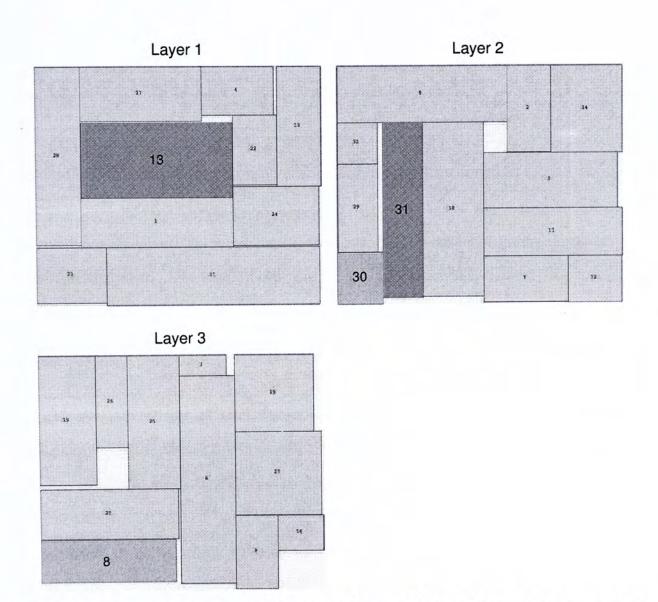

| 6.1  | A Layered Floorplan and Its LTCG Representation                                 | 85 |

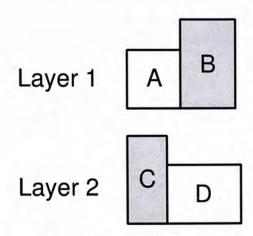

| 6.2  | Block $A,D$ and Block $B,C$ cannot be aligned simultaneously                    | 86 |

| 6.3  | Cycle Exists if The Two Pair of Edges are Added Simultaneously.                 | 87 |

| 6.4  | Pseudo Code of Aligning Blocks                                                  | 88 |

| 6.5  | A Floorplan Before And After Applying "Move" to Edge $(A,$                      |    |

|      | B) in $G_h$                                                                     | 89 |

| 6.6  | A Floorplan Before And After Applying "Reverse" to Edge $(A,$                   |    |

|      | C) in $G_v$                                                                     | 91 |

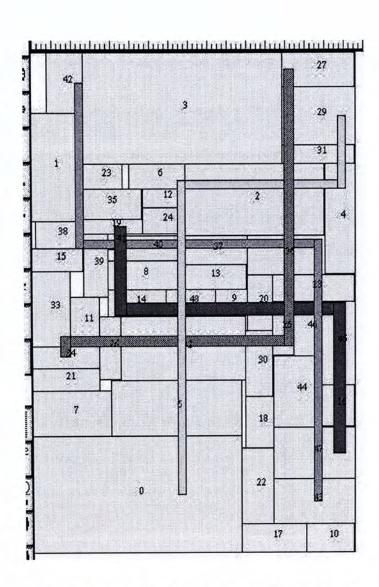

| 6.7  | Result of ami49 in Data Set 1                                                   | 94 |

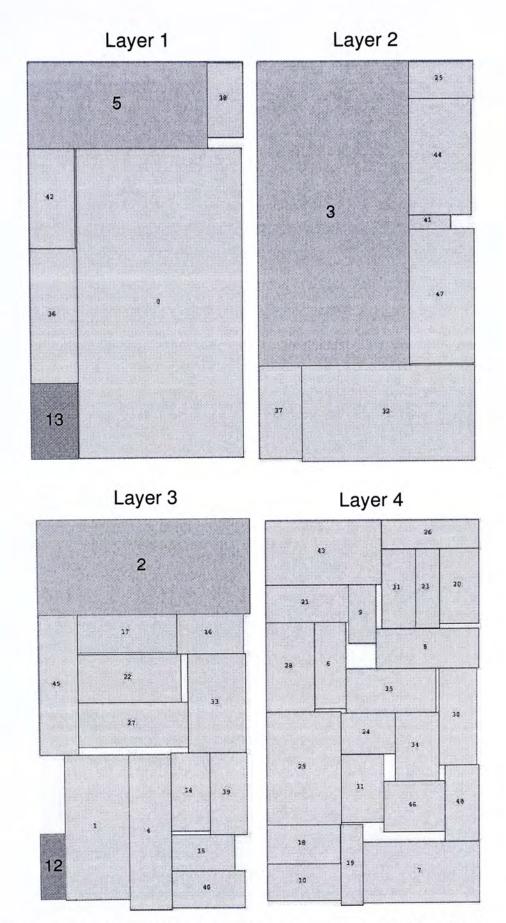

| 6.8  | Result of ami49 in Data set 3 ( $B_1 = \{0.5, 32, 33, 44\}, B_2 =$              |    |

|      | $\{6-11\}, B_3 = \{12-17\}). \ldots$                                            | 97 |

| 6.9  | Result of ami33 in Data set 3 ( $B_1 = \{6-9, 26, 29, 30\}, B_2 =$              |    |

|      | $\{10-14, 18, 24, 31\}$ )                                                       | 98 |

# List of Tables

| 1.1 | Technology Roadmap [3]                                      | 2  |

|-----|-------------------------------------------------------------|----|

| 2.1 | Comparison between Different Kinds of Floorplan Representa- |    |

|     | tions                                                       | 36 |

| 5.1 | Data Set One                                                | 76 |

| 5.2 | Data Set Two                                                | 76 |

| 5.3 | Results of Data Set One                                     | 76 |

| 5.4 | Results of Data Set Two                                     | 77 |

| 6.1 | Characteristics of Data Set 1                               | 93 |

| 6.2 | Comparisons between [4] and LTCG                            | 93 |

| 6.3 | Characteristics of Data Set 2                               | 95 |

| 6.4 | Characteristics of Data Set 3                               | 95 |

| 6.5 | Experimental Results of Data Set 2                          | 96 |

| 6.6 | Experimental Results of Data Set 3                          | 96 |

# Chapter 1

# Introduction

The technology of integrated circuit (IC) was widely adopted for computing devices like microprocessors, memory modules, and many other interface chips since 1960s. It is not surprising to find that we are surrounded by a huge number of computing devices in daily life, such as our personal computers, the ATM machines we use to withdraw cash, and many other electronic appliances. IC is one of the core components of those computing facilities.

As the Very Deep Sub-Micron (VDSM) technology advances, IC has evolved from Small Scale Integration (SSI) to Very Large Scale Integration (VLSI). The former consists of a few transistors only, where the latter consists of billions of transistors. According to Moore's Law [5], it was predicted that the number of transistors in a single IC will double in every 1.5 years. Table 1.1 show the predicted technology roadmap from 1997 to 2009 [3]. In the foreseeable future, the technology of VLSI will continue to scale down, to produce faster, more complicated yet more powerful ICs. As a side effect, the interconnections will hence become longer and denser, and it will be desirable to keep the sizes of the chips as small as possible. This growing trend has brought many new challenges to VLSI design automation, and make the design process more difficult and complicated.

| Technology $(\mu m)$      | 0.25 | 0.18 | 0.15 | 0.13 | 0.1  | 0.07 |

|---------------------------|------|------|------|------|------|------|

| Year                      | 1997 | 1999 | 2001 | 2003 | 2006 | 2009 |

| Number of Transistors     | 11M  | 21M  | 40M  | 76M  | 200M | 520M |

| Across Chip Clock $(MHz)$ | 750  | 1200 | 1400 | 1600 | 2000 | 2500 |

| Area $(mm^2)$             | 300  | 340  | 385  | 430  | 5.20 | 6.20 |

| Wiring Levels             | 6    | 6-7  | 7    | 7    | 7-8  | 8-9  |

Table 1.1: Technology Roadmap [3].

Producing a tiny chip is a time consuming process. There are many steps to go through, and many of them are computationally expensive. Many algorithms have been developed in CAD (Computer Aided Design) tools to help accomplishing the task, but there are still many unresolved problems and new challenges to be explored. In the following sections, the VLSI design cycle and the physical design cycle will be described briefly. After that, the floorplanning problem will be introduced and discussed.

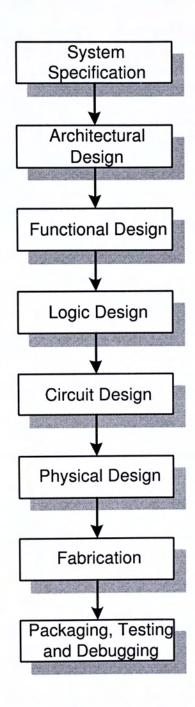

## 1.1 VLSI Design Cycle

To design a VLSI circuit, a series of steps has to be gone through. The process starts with a formal specification, and the final product is a fabricated chip. Figure 1.1 shows a VLSI design cycle. In this section, the key steps leading to a packaged chip will be described briefly.

#### System Specification

The first step in the design cycle is to prepare a formal specification of the system. This specification should state clearly the performance, functionality, physical dimension, power consumption, and other requirements of the VLSI system. Once the specification is laid down, the design process can proceed and the requirements stated has to be satisfied.

Figure 1.1: The VLSI Design Cycle.[2]

#### Architectural Design

Architectural decisions will be made in this step. For example, whether RISC (Reduced Instruction Set Computer) or CISC (Complex Instruction Set Computer) will be adopted, the number of ALUs (Arithmetic Logic Unit) or floating point units, or the number and structure of pipelines. After architectural design, engineers can predict the performance or power consumption of the system accurately. The prediction can help determining whether the design is likely to meet the specification.

#### Functional Design

In functional design, the behavior of the system, in terms of input, output, and timing requirement, will be specified, in which the internal structure is not concerned. The behavior of a system refer to the functionality that the system is capable of. Besides, interconnections between different units will also be defined in this step.

#### Logic Design

In this step, logic operations that represent the functional design of the system are derived and tested. Boolean expressions will be used to describe the logic operations. The logic operations include the control flow, arithmetic operations, and register allocation. The logic design has to be conformed to the functional design, and will be simulated to verify its correctness.

#### Circuit Design

Based on the logic design, a circuit representation can be derived. The circuit representation is a detailed circuit diagram. It shows clearly the cells, gates, transistors, and other circuit elements, together with the interconnections between them. During the design process, the speed and power requirements are also taken into account.

#### Physical Design

The step of transforming a circuit representation into a geometric representation is called physical design. The geometric representation of a circuit is called a *layout*. During physical design, problems like where to place the modules, how the interconnections between the modules should be made etc., will be addressed. As physical design is a crucial yet complex step in the design cycle, it can be further broken down into sub-steps, such as partitioning, floor-planning, placement, routing, and compaction.

#### **Fabrication**

Once the layout is produced and verified, it is ready for fabrication. The layout data is converted into photo-lithographic masks. There are several steps of the fabrication process, including deposition and diffusion of various materials on the wafer. A large wafer can be used to produce many chips. A prototype is made before the mass production of a chip.

#### Packaging, Testing and Debugging

The fabricated chip is tested in this step. Each chip is tested to ensure that all the requirements in the specification are met, and it can function properly. After that, the chips will be mass produced and packaged.

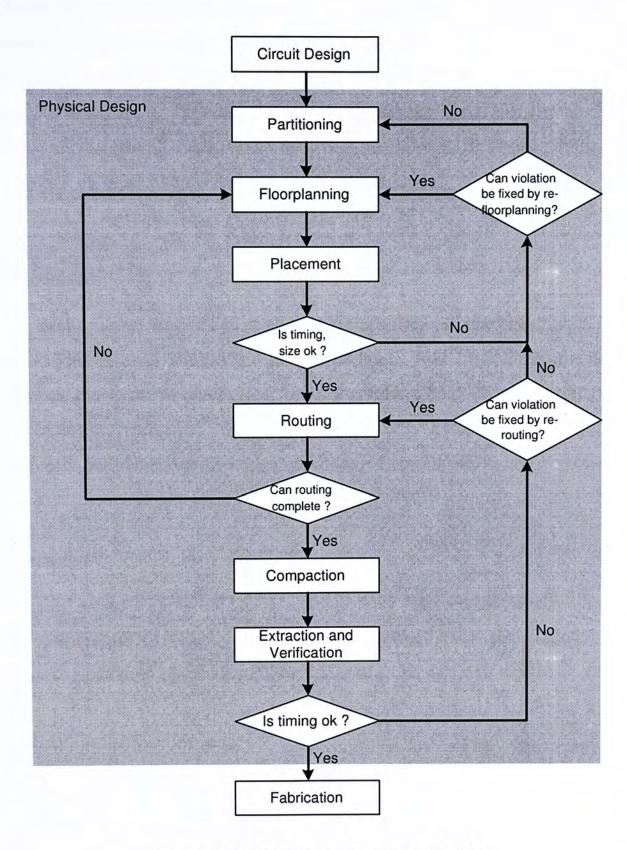

## 1.2 Physical Design Cycle

As mentioned before, a circuit representation will be transformed into a layout in the physical design step. It is usually broken down into several sub-steps. A physical design cycle is shown in Figure 1.2. The details of each step will be discussed in this section.

#### **Partitioning**

In order to achieve complicated functionalities, a chip may actually be comprised of millions of transistors. Breaking down a big problem into smaller sub-problems is always a good strategy to solve complicated problems. As huge circuits are hard to be managed efficiently and cannot be layout all at once, decomposition into finer sub-systems is a must in the design cycle. The step of decomposition is called partitioning, and the sub-circuits partitioned are called *blocks*. After partitioning circuits into blocks, each of them can then be designed effectively, independently, and simultaneously so as to ease the design process. Factors like the block sizes, block dimensions and interconnections between different blocks should be taken into account.

Figure 1.2: A Physical Design Cycle.[2]

#### Floorplanning

During the step of floorplanning, the blocks are positioned on the chip roughly, so as to optimize the circuit size and performance according to the circuit specification. A compact design is favorable, but there are many other important aspects that have to be taken care of. For example, issues like the block dimensions and overall delay should be taken into account. In floorplanning, the decisions on block shapes and pin positions are made.

#### Placement

The exact positions of the blocks are determined in the placement step. The layout should meet the performance constraints, allow the interconnections between blocks to be made, and meet the timing goal. Floorplanning and placement are vital to the design process as it affects the ultimate design significantly and determines whether the required specifications can be met.

#### Routing

Routing means completing the interconnections between blocks according to the specified netlist. The space not occupied by the blocks, the routing space, is partitioned into channels and switchboxes. Connections are made within them. Routing can be further broken down into two phases, namely global routing and detailed routing.

1. Global Routing: Planning different routes from a global point of view, without fixing the exact path of each route yet. It is a rough plan to check whether completion of all interconnections is possible.

2. **Detailed Routing:** Complete each connection by computing the exact positions of the wires on the metal layers. After detailed routing, the geometric layouts of all the nets will be known.

There may be cases that some of the connections are not able to be routed. In those situations, the technique *rip-up and re-route* will be used, which means removing some of the routed connections and re-routing them in a different order. If the problem cannot be solved by this technique, engineers may need to go back to the earlier design phases in the physical design cycle, or even to the logic design step and start the whole process all over again.

#### Compaction

Compaction means making the chip design as small as possible. During this step, the layout is compressed from different directions so as to reduce the total area. Note that during compaction, it is necessary to ensure that no design rules or constraints are violated.

#### **Extraction and Verification**

The layout is verified in this step, to ensure that all the design rules and performance constraints are satisfied, before proceeding to the fabrication step. Design rules, such as wire separation rule, which is the minimum separation between two adjacent wires, have to be fulfilled. Besides, the functionality of the layout is also verified. If problem is found, engineers may need to go back to the earlier designing steps to fix the problem.

## 1.3 Floorplanning

As technology advances into the deep submicron era, circuit sizes and complexity increase dramatically. A good planning in the early design phase is crucial, in order to avoid unnecessary iteration in the design cycle. Floorplanning has become an important step in the physical design cycle.

The input to the floorplanning phase is a set of blocks, the area of each block, the possible shapes of each block, the number of terminals of each block, and the interconnections between blocks. In the floorplanning phase, we are going to plan the position and shape of each block, together with the pin positions. The shapes for some blocks are fixed and cannot be altered. We called those blocks hard blocks. For other blocks, the shapes can be altered as long as they are within the pre-set aspect ratios. Those blocks are called soft blocks. A formal definition of the floorplanning problem is given as followed:

#### Definition 1.1 The problem floorplanning is defined as:

Given a set of n modules  $\{M_1, M_2, \dots, M_n\}$ , where each module  $M_i$  is associated with an area  $A_i$ , together with two aspect ratio bounds  $r_i$  and  $s_i$  such that  $r_i \leq h_i/w_i \leq s_i$ , where  $h_i$  and  $w_i$  is the height and the width of module i respectively. The output of the problem is a packing of the set of modules, i.e. the x- and y-coordinates and the dimension  $(h_i, w_i)$  of each module. There should be no overlapping between modules, and the circuit performance should be optimized.

In this section, some floorplan objectives will be discussed. Besides, some approaches adopted today to solve the floorplanning problem will be presented.

### 1.3.1 Floorplanning Objectives

There are several objectives to be optimized in floorplanning, like the total chip area, the total wire length, the critical path delay etc. In this section, some common floorplanning objectives will be discussed.

#### Chip Area

Area minimization is one of the most commonly adopted objectives. Minimizing the chip area implies minimizing the wire length, and hence reducing the circuit delay.

#### Total Wire Length

In addition to minimizing the chip area, minimizing the total wire length directly is also another important goal. Beside the timing issues, using less wires to connect the modules means consuming less resources, and thus reducing the production cost.

#### Delay

In some cases, minimizing the total wire length is not enough. Timing is an important issue. The final circuit performance can be optimized by minimizing the delay on the critical path.

#### Routability

Routability refer to the possibility of completing all the connections. A non-routable floorplan is of no use even if it is area-optmized and delay-optimized.

Enhancing the routability of a floorplan means to reduce the chance of encountering routing problems in the downstream designing steps.

#### Others

There are still some other objectives in floorplanning, like minimizing heat dissipation, minimizing power consumption, etc. In our work, we focus on the bus-driven floorplanning problem to minimize interconnect delay by arraying the modules on the same bus in such a way that routing can be done effectively.

#### 1.3.2 Common Approaches

The floorplanning problem is proved to be NP-complete. Thus, different heuristics are developed to solve the problem, which includes analytical approach, simulated annealing, genetic algorithm, force directed approach, constraint based approach, and other stochastic searching approaches.

#### Analytical Approach

In 1991, the author of [6] proposed that the floorplanning problem can be formulated as a mixed integer linear program (MILP), such that the objective is a linear function, all constraints are linear functions, and some variables are real numbers while others are integers. However, the MILP problem itself is a NP-complete problem, and the run time of the best known algorithm is exponential to the number of variables and equations. Thus, this modelling can only solve problems of small scales. In 1998, a convex formulation [7] is proposed to reduce the number of variables and constraints used, by handling the aspect ratios of the blocks in an indirect way.

#### Simulated Annealing (SA)

Simulated Annealing is a widely adopted heuristic to solve NP-complete problem. It belongs to the probabilistic and iterative class of algorithms. The algorithm was originally proposed in [8] for finding the equilibrium configuration of a collection of atoms at a given temperature. The idea of using SA as an optimization tool is introduced in [9]. After that, it is suggested in [10] that SA can be used as a general technique for different optimization problems. This technique is used in [11][12][13][14][15] to solve the floorplanning problem.

SA mimics the process of metal cooling and freezing into a highly ordered crystalline structure with minimum energy (the annealing process). The framework of a simulated annealing based floorplanner can be described as follows: each floorplan in the solution space is represented by a representation (e.g., sequence representation, o-tree, etc.). The quality of each candidate floorplan is evaluated according to a cost function, which may take area, wirelength, etc. into consideration. The process starts with an initial solution  $x_0$  and an initial temperature  $T_0$ . In each iteration, the candidate solution is changed a little, and is evaluated by the cost function. If the newly formed solution is better than the old one, it is accepted. Otherwise, the solution is accepted according to a probability depending of the temperature. If the temperature is high, the chance of accepting a worse solution will also be high. The temperature T will be cooled down at a cooling rate c. Finally, the process will terminate when the temperature is lower than a threshold  $T_t$ . The pseudo code is shown in Figure 1.3.

#### SIMULATED\_ANNEALING (ITER, $T_0$ , $T_t$ , c)

```

1 x \leftarrow x_0

2 T \leftarrow T_0

3 WHILE T > T_t

FOR i from 1 to ITER

4

5

x_{new} \leftarrow move(x)

\Delta f \leftarrow \text{cost}(x_{new}) - \text{cost}(x)

6

7

r \leftarrow \text{random number between 0 to 1}

8

IF \Delta f < 0 OR r < \exp(-k\Delta f/T)

9

x \leftarrow x_{new}

10

END IF

11

END FOR

T \leftarrow T \times c

12

13 END WHILE

14 RETURN x

```

Figure 1.3: Pseudo Code of Simulated Annealing.

#### Genetic Algorithm

Genetic algorithm [16][17] is another stochastic searching approach to solve NP-complete problems. A pseudo code of the general genetic algorithm approach is described in Figure 1.4. The process starts with a set of initial solutions namely population. By using two types of genetic operators, mutation and crossover, better populations can be obtained iteratively by means of evolution. Mutation means modifying one solution by applying a small change to itself. Crossover means forming a new solution by combing two solutions in the population.

#### 1.3.3 Interconnect-Driven Floorplanning

Traditional floorplanners [18][11][13][17][19][20][21][22] aim at minimizing the chip area so as to increase the yield. However, as technology advances, the number of transistors and the number of interconnections involved increase dramatically. Interconnections between modules become longer and denser.

```

GENETIC_ALGORITHM (P, R_c, R_m)

1 X \leftarrow \{x_1, x_2, \cdots, x_P\}

2 WHILE stopping criteria not met

3

X_{new} \leftarrow \phi

WHILE number of children created < P \times R_c

4

select two solutions x_i and x_j from X

5

6

x_{new} \leftarrow crossover(x_i, x_j)

7

X_{new} \leftarrow X_{new} \cup \{x_{new}\}

8

END WHILE

select P solutions from X \cup X_{new}, and call it X

9

WHILE number of children mutated < P 	imes R_m

10

select a solution x_k from X

11

x_{new} \leftarrow \mathtt{mutate}(x_k)

12

X_{new} \leftarrow X_{new} \cup \{x_{new}\}

13

END WHILE

14

X \leftarrow X_{new}

15

16 END WHILE

17 RETURN the best solution in X

```

Figure 1.4: Pseudo Code of Genetic Algorithm.

According to [3], a significant portion of about 80% of the clock cycle is consumed by interconnections in some advance systems. As there are a lot of wires to be connected, routing becomes more and more difficult. If this is not considered in early design phrases, like floorplanning, unroutable layouts may be resulted. To avoid unnecessary iteration of the design cycle, modern floorplanners always take interconnections into account.

#### 1.4 Motivations and Contributions

In VLSI system design, it is common that a system is consisted of millions of transistors. A good planning in the early design phase is of vital importance as it sets up a ground work for a good layout.

As the functionality of chips increases, chip designs become more and more complicated and involve a huge number of transistors. Beside functionality, chip designs are expected to meet many other requirements, like timing, power consumption, etc. On the other hand, it is favorable to keep the chip size as small as possible. This makes the design process much more difficult than ever.

In the deep submicron era, the number of transistors and interconnections are growing rapidly. The wires are becoming longer and denser. More routing space is needed to ensure design convergence. Bus is a collection of wires to carry a set of signals among different modules. As the complexity of chip design increases, bus routing becomes more and more important. If we do not carefully plan the routes of the buses and reserve sufficient space for them in the layout, there will be a high chance to have a lot of unroutable buses. In order to ease bus routing and avoid unnecessary iteration in the design cycle, we incorporate bus planning in the early designing phase. This is our motivation to solve the bus-driven floorplanning problem.

Our research focused on bus-driven floorplanning, in both 2D and 3D chip design. We have reviewed literatures on floorplanning, which include different floorplan representations and bus planning methods. We used the sequence pair (SP) representation and the transitive closure graph (TCG) representation for 2D and 3D floorplanning respectively.

For 2D floorplanning, we made use of the characteristics of SP and proposed a novel algorithm [23] to solve the bus-driven floorplanning problem, allowing buses with bendings. Given a SP, the topological relationships between the blocks can be found. We have proposed a method to check if buses can be placed in a specific floorplan by studying the relative positions between the blocks as represented by a SP. Simulated annealing was used to find a good solution. We have compared our work with [1], and significant improvement were made.

3D chips are useful in reducing interconnect lengths. However, there is not much previous work done in 3D floorplanning. In this thesis, we have proposed a 3D floorplan representation called Layered Transitive Closure Graph (LTCG). It is based on the Transitive Closure Graph (TCG) representation for non-slicing floorplans, together with some layer information. We proposed a method to align blocks of the same bus on different layers, by adding edges into the LTCG. A floorplanner is implemented using the LTCG representation. Experimental results have shown that LTCG is a promising representation for 3D floorplans and can handle bus planning in 3D floorplans effectively.

## 1.5 Organization of the Thesis

The rest of this thesis is organized as follows. After giving a brief introduction to the background information in this chapter, a literature review on different 2D floorplan representations will be given in Chapter 2. After that, a literature review on 3D floorplan representations will be given in Chapter 3. In Chapter 4, a literature review on previous approaches to solve the bus-driven floorplanning problem will be presented. Our proposed algorithm to solve the multi-bend bus-driven floorplanning problem in 2D floorplan will be presented in Chapter 5, followed by our proposed representation for 3D floorplans and our approach to perform bus-driven floorplaning for 3D chips in Chapter 6. Finally, a conclusion will be given in Chapter 7.

# Chapter 2

# Literature Review on 2D Floorplan Representations

## 2.1 Types of Floorplans

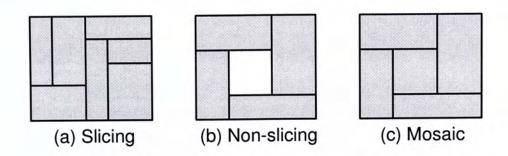

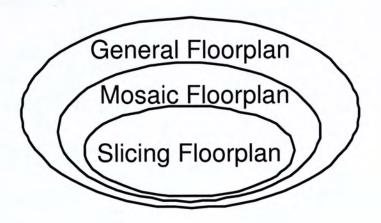

Floorplans can be classified into three main categories: slicing [24][25][26], non-slicing [12][20][27][28][11][19][29], and mosaic [18][30][13][31] as shown in Figure 2.1.

Figure 2.1: Examples of the Three Main Kinds of Floorplans.

A slicing structure can be obtained by recursively dividing a rectangle into smaller rectangles using a horizontal or a vertical cut. An example is shown in Figure 2.1(a). A widely adopted slicing floorplan representation is proposed by Wong and Liu in 1986 [25], which is called normalized Polish expression. One of

the advantages of the slicing structure is that the solution space is smaller, implying faster runtime for some search-based floorplanning algorithms. Solution space refer to how many different solutions can one representation represent. However, the representation is not general enough, as most of the real designs are not in slicing structure.

A non-slicing floorplan is a floorplan that is not necessarily slicing (Figure 2.1(b)). It is the most general kind of floorplans. Much work has been done on non-slicing floorplan representation recently, e.g., sequence pair [11], BSG [29], O-Tree [20], B\*-Tree [12], and TCG [32].

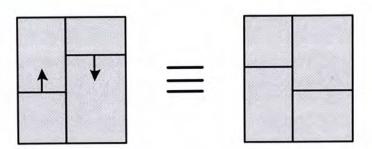

Mosaic floorplan is first proposed in 2000 [18], to represent a new class of packing structure. Mosaic floorplan is similar to non-slicing floorplan except that there is no empty room in the floorplan (Figure 2.1(c)). Each module corner is formed by a T-junction (no +-junction), except those at the four corners of the floorplan. Besides, the non-crossing segment of a T-junction can slide along the crossing segment to represent the same floorplan as shown in Figure 2.2.

Figure 2.2: One of the Properties of Mosaic Floorplan.

According to [13], the categories of floorplans can be summarized as in Figure 2.3, where slicing floorplan is a proper subset of mosaic floorplan, and mosaic floorplan is a proper subset of general(non-slicing) floorplan.

Figure 2.3: Floorplans Categories.

## 2.2 Floorplan Representations

A good floorplan representation should have the following qualities: small solution space, quick floorplan realization procedure, and being P-admissible.

The notion of *P-admissible* is first proposed by Murata et al. in [11]. For a representation to be P-admissible, it has to satisfy the following four requirements:

- 1. The solution space is finite,

- 2. Every solution is feasible,

- 3. Evaluation for each solution is possible in polynomial time and so is the realization of the corresponding packing,

- 4. The packing corresponding to the best evaluated solution in the space coincides with an optimal placement solution.

Different representations for different kinds of floorplans will be discussed in the following sections.

### 2.2.1 Slicing Floorplan

#### Normalized Polish Expression

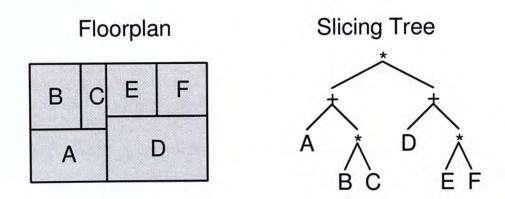

According to Wong and Liu in [25], A slicing structure is a rectangle dissection that can be obtained by recursively cutting rectangle into smaller rectangles. The authors suggested to use an oriented rooted binary tree called *slicing tree* to represent the hierarchical structure of a slicing floorplan. Each internal node of such a slicing tree is labelled by a '\*' (corresponds to a vertical cut) or a '+' (corresponds to a horizontal cut), while each leaf is labelled by the module name. An encoding to the tree can be obtained by traversing the slicing tree in a post-order, called a *Polish expression*. A Polish expression is said to be normalized if the Polish expression contains no consecutive '\*'s nor '+'s. In Figure 2.4, an example of a slicing tree together with its normalized Polish expression is shown.

Normalized Polish Expression: ABC\*+DEF\*+\*

Figure 2.4: An Example of a Slicing Tree and Its Normalized Polish Expression.

In [25], it is shown that there is a one-to-one correspondence between the normalized Polish expressions and the slicing floorplans. The size of the solution space is  $O(n!2^{3n-3}/n^{1.5})$ [13] where n is the number of modules. A slicing floorplan can be realized from a normalized Polish expression in O(n) time. The representation is P-admissible. Normalized Polish expression is a widely adopted, elegant representation for slicing structures.

### 2.2.2 Non-slicing Floorplan

#### Sequence Pair (SP)

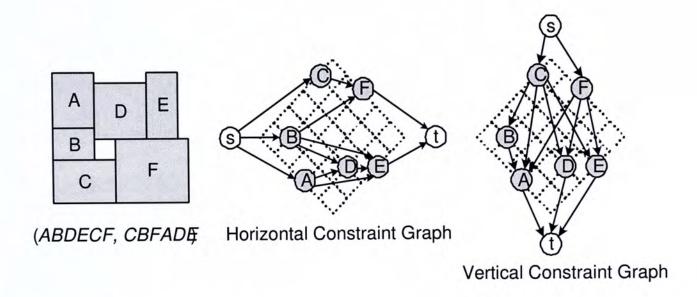

Sequence Pair (SP) was first proposed in 1995 by Murata et al [11]. In the representation, two sequences  $(\Gamma_+, \Gamma_-)$  are used to represent a floorplan. For example, (ABDECF, CBFADE) is a sequence pair of the set of modules  $\{A, B, C, D, E, F\}$ . The relationship between every two blocks is governed by the following rules:

- If two blocks A and B appear in the sequence pair as  $(\cdots A \cdots B \cdots, \cdots A \cdots B \cdots)$ , block B is on the right of block A.

- If two blocks A and B appear in the sequence pair as  $(\cdots A \cdots B \cdots, \cdots B \cdots A \cdots)$ , block B is below block A.

To realize a floorplan from a sequence pair representation, a pair of graphs, the horizontal constraint graph  $G_H$  and the vertical constraint graph  $G_V$  can be constructed. Each constraint graph has a source s and a sink t to denote the floorplan boundaries. In  $G_H$ , the source and the sink correspond to the leftmost and the rightmost boundaries of the floorplan respectively, while in  $G_V$ , the source and the sink correspond to the bottommost and uppermost boundaries of the floorplan respectively. The constraint graphs are vertex-weighted, and the set of vertices V is  $\{s\} \cup \{t\} \cup \{v_1, v_2, \dots, v_n\}$ , where n is the number

of modules, and each  $v_i$  corresponds to a module. The vertex-weight is zero for s and t in both graphs, and is the width(height) of the corresponding module in  $G_H(G_V)$ . The constraint graphs can be constructed as follows (Figure 2.5):

- If block A is on the left of block B, add an edge (A, B) in  $G_H$ .

- If block A is below block B, add an edge (A, B) in  $G_V$ .

Figure 2.5: Constraint Graphs for the Sequence Pair (ABDECF, CBFADE).

Sequence pair is a P-admissible representation. The time complexity of realization of a floorplan from a SP is  $O(n^2)$  according to [11], where n is the number of modules, and is improved to O(nloglogn) in [33]. The size of the solution space of SP is  $O((n!)^2)$ .

#### Bounded-Sliceline Grid (BSG)

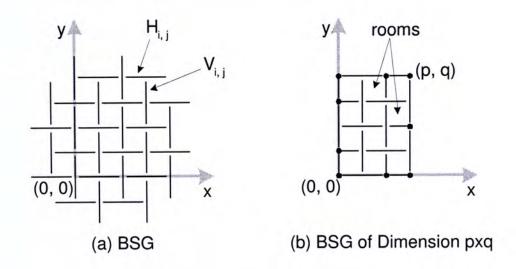

BSG refers to *Bounded-Sliceline Grid*. It is a non-slicing floorplan representation proposed in 1996 by Nakatake et al. in [19] based on the topological relationships between blocks. A meta-grid is defined on a plane without any

physical dimension. Different segments in the grid create rooms to place different blocks. The unit segment on the (x, y)-coordinate system is defined by:

$$H_{i,j} = \{(x, y) \mid i - 1 < x < i + 1, y = j\}$$

$$V_{i,j} = \{(x, y) \mid x = i, j - 1 < y < j + 1\}$$

A BSG consists of a set  $U_{BSG}$  of the unit segments as defined above. An example is shown in Figure 2.6.

$$U_{BSG} = \{V_{i,j} \mid i, j : integers, i + j : even\} \cup \{H_{i,j} \mid i, j : integers, i + j : odd\}$$

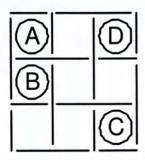

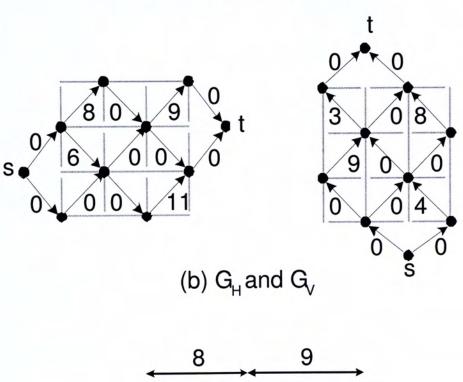

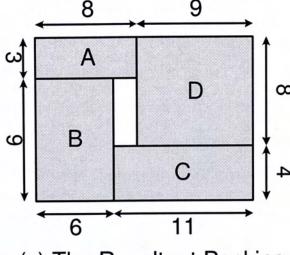

Figure 2.6: (a) An Example of a BSG. (b) A Domain BSG<sub> $p \times q$ </sub>

A pair of graphs, the horizontal unit adjacency graph  $G_H$  and the vertical unit adjacency graph  $G_V$ , can be constructed to realize the floorplan. In  $G_H$ , each vertex corresponds to a horizontal segment. Edges are added between adjacent segments and thus, each edge crosses one room. If an edge e crosses a non-empty room where block A is placed, the weight of e will be the width of block A. If e crosses an empty room, the weight of e will be 0.  $G_V$  can be built in a similar fashion. With the constructed graphs, the layout of the

floorplan can be found by performing longest path search for every block. An example of representing a floorplan using BSG is shown in Figure 2.7.

According to [19], BSG is beneficial when packing blocks into a chip of non-rectangular shape. BSG is a P-admissible representation. To realize a floorplan from its BSG representation, the time complexity is  $O(n^2)$ . The size of the solution space of BSG is  $O(n^2!/(n^2-n)!)$ .

#### O-Tree

In 1999, Guo et al. proposed an *O-tree* representation for non-slicing floorplan in [20]. They defined an *admissible placement* as a compacted placement where all blocks can neither move down nor move left. O-tree is devised to represent admissible placement.

Given a floorplan, two different ordered trees can be built, one with the root corresponding to the left boundary of the floorplan and one with the root corresponding to the bottom boundary of the floorplan. Given an O-tree, its orthogonal correspondent can be built. An example of an admissible placement and its corresponding O-tree is shown in Figure 2.8. The root node in the figure corresponds to the left boundary of the floorplan.

The authors proposed to encode the rooted ordered tree into two sequences  $(T, \pi)$ . The sequence T indicates the structure of the tree: a '0' represents a descending edge and a '1' represents an ascending edge. The sequence  $\pi$  is a sequence of module labels obtained by performing a depth-first search. Thus, the floorplan in Figure 2.8 is represented by (00110100011011, ADBCEGF).

This representation is not P-admissible. The size of the solution space of

# (a) Assignment of Rooms

(c) The Resultant Packing

Figure 2.7: Representing a Floorplan Using BSG.

Figure 2.8: An Admissible Placement and Its Horizontal Constraint Graph.

O-tree is  $O(n!2^{2n-2}/n^{1.5})$ , and the runtime to transform an O-tree to its packing is linear, i.e., O(n).

### B\*-Tree

B\*-tree[12] is proposed in 2000 by Chang et al. which is similar to O-tree, with some modifications and enhancements.

Each admissible placement has a corresponding  $B^*$ -tree T. Each node in T corresponds to a module. The root node of T corresponds to the module at the bottom-left corner of the floorplan. Let R be the set of modules on the right-hand side of and adjacent to a block x. The left child of the node x in T is the lowest unvisited block in R. Similarly, let U be the set of modules above and adjacent to x, the right child of x in T is the leftmost unvisited block in U. According to [12], there is a one-to-one correspondence between admissible placement and  $B^*$ -tree. An example of a placement and its  $B^*$ -tree representation is shown in Figure 2.9.

B\*-tree is advantageous over O-tree, as B\*-tree is a binary tree and it can be implemented easily with a static data structure such that node searching

Figure 2.9: A Floorplan and Its Corresponding B\*-Tree Representation.

and insertion can be done in constant time, i.e., O(1). Similar to O-tree, B\*-tree is not P-admissible. The size of its solution space is  $O(n!2^{2n-2}/n^{1.5})$ , and floorplan realization takes O(n) time.

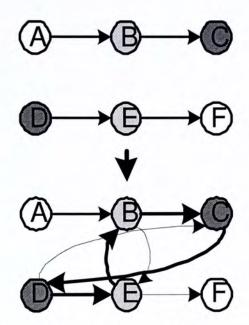

### Transitive Closure Graph (TCG)

In 2001, Transitive Closure Graph (TCG) is proposed by Lin and Chang in [32] to represent non-slicing floorplan. A TCG is a pair of directed acyclic graph, the horizontal transitive closure graph  $C_h$  and the vertical transitive closure graph  $C_v$ . The authors defined the transitive closure G' in of a directed acyclic graph G = (V, E) as follows: G' = (V, E'), where  $E' = \{(n_i, n_j) : \text{there is a path from node } n_i \text{ to node } n_j \text{ in } G\}$ .

The authors made use of the topological relationships between blocks to represent a floorplan. For two non-overlapping modules  $b_i$  and  $b_j$ , they must bear one of the following three relationships: (1) horizontal relation, (2) vertical relation, or (3) diagonal relation. The first two relationships are easy to understand: the two modules are overlapped in one dimension but not the other. For the third one,  $b_i$  is said to be diagonally related to  $b_j$  if the projections of the two modules do not overlap in either dimension. For simplicity, a diagonal relationship will be treated as a horizontal one, unless there exists

a chain of vertical relations (e.g. if A is diagonally related to C, but A is above B and B is above C, then A must be above C). For two blocks bearing a horizontal relationship, an edge will be added in  $C_h$  between the nodes representing the two blocks, while edges in  $C_v$  will correspond to vertical relationships. The graphs are vertex-weighted, where the weights correspond to the widths (heights) of the blocks. Figure 2.10 shows an example of representing a floorplan using TCG.

Figure 2.10: A Floorplan and Its Corresponding TCG Representation.

Realizing a floorplan from its TCG representation is easy. It can be done by performing a longest path search on the two constraint graphs. It is claimed that TGC has several advantages over some published work: TGC is P-admissible, TGC does not need sequence encoding, cost can be evaluated directly basing on the representation, and geometric relationship is transparent to its operations, etc. The size of the solution space of TGC is  $O((n!)^2)$  and floorplan realization can be done in  $O(n^2)$  time.

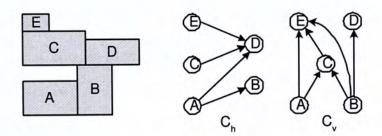

## 2.2.3 Mosaic Floorplan

### Corner Block List (CBL)

Corner Block List (CBL) is a topological representation for mosaic floorplan. It is first proposed by Hong et al. in 2000 [18]. A corner block is the upper-rightmost block in a floorplan. A CBL is a three tuple (S, L, T), that can be obtained by repeatedly deleting the corner block of the floorplan.

The sequence S is a sequence of block names. It records the order of the blocks being deleted. L is a list of orientations. The orientation of a block is defined according to the T-junction at its bottom left corner. There are two kinds of orientations: a 'T' rotated by 90 degrees anticlockwise ( $\vdash$ ) or by 180 degrees ( $\bot$ ). In the former case, a '0' will be recorded in L and in the latter case, a '1' will be recorded. The list T records the number of T-junctions on the left or bottom boundary of the corner blocks. The number of consecutive '1's in T corresponds to the number of T-junctions on the left or bottom boundary of a corner block. A '0' is added to separate this information for different blocks. The orientation and the T-junction information of the last block will not be recorded as there is only one block left at the end of the deletion process. An example is shown in Figure 2.11 to illustrate the process of obtaining the CBL from a packing.

Floorplan realization for CBL can be done in a similar fashion as in CBL construction. It can be done by checking the orientation of the corner block, and determining whether the horizontal segment or the vertical segment of the corner block should be pushed to make a room. According to [13], the size of the solution space of CBL is  $O(n!2^{3n}/n^{1.5})$ . The computation complexity to convert a CBL to a floorplan is O(n). However, CBL is not a P-admissible representation.

Figure 2.11: Constructing a CBL from A Floorplan.

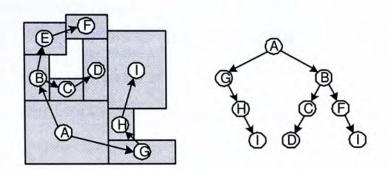

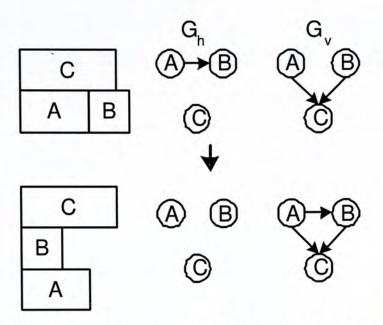

### Twins Binary Trees (TBT)

Twins Binary Tree (TBT) is first proposed to be used as a floorplan representation by Yao et al. in 2001 [30]. It is proved that there exists an one-to-one mapping between TBT and mosaic floorplan. According to [30], the set of twins binary trees  $TBT_n \subseteq Tree_n \times Tree_n$  is defined as followed:

$$TBT_n = \{(b_1, b_2)|b_1, b_2 \in Tree_n \text{ and } \Theta(b_1) = \Theta^c(b_2)\}$$

where  $Tree_n$  is the set of binary trees with n nodes, and  $\Theta(b)$  is the labelling of a binary tree.

The labelling of a tree can be obtained by carrying out an in-order walk on the tree. Beginning with an empty sequence, a '0' is added to the sequence if a node with no left child is being visited, and a '1' is added to the sequence if a node with no right child is being visited. The first '0' and the last '1' in the sequence are omitted. The complement  $\Theta^c(t_1)$  of  $\Theta(t_1)$  is obtained by

interchanging the '0' and '1' bits.

Given a mosaic floorplan, its TBT representation  $(t_1, t_2)$  can be obtained by traversing along the slicelines. Both trees contain n nodes, where n is the number of modules in the floorplan. The root of  $t_1$  is the bottom-left corner block of the floorplan. The tree  $t_1$  is built by connecting the bottom-left corners of all the blocks. The left tree edge of a node represents the vertical sliceline, and the right tree edgerepresents the horizontal sliceline.  $t_2$  is built similarly: the root is the upper-right corner block of the floorplan, and the tree is built by connecting the upper-right corners of all the blocks. The left tree edge of a node represents the horizontal sliceline, and the right tree edge of a node represents the vertical sliceline. It is proved that the pair of trees constructed in this way must be twin binary to each other. An example of a floorplan and its TBT representation is shown in Figure 2.12. The solution space of TBT is  $O(n!2^{3n}/n^{1.5})$ .

Figure 2.12: A Non-Slicing Floorplan and Its TBT Representation.

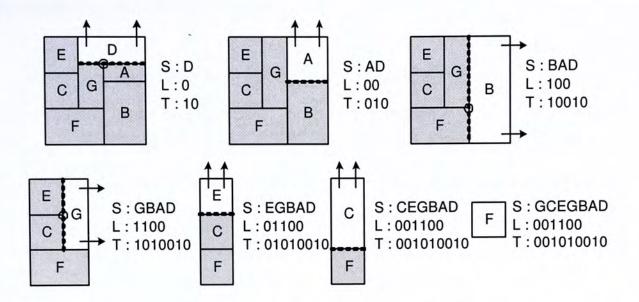

### Twins Binary Sequences (TBS)

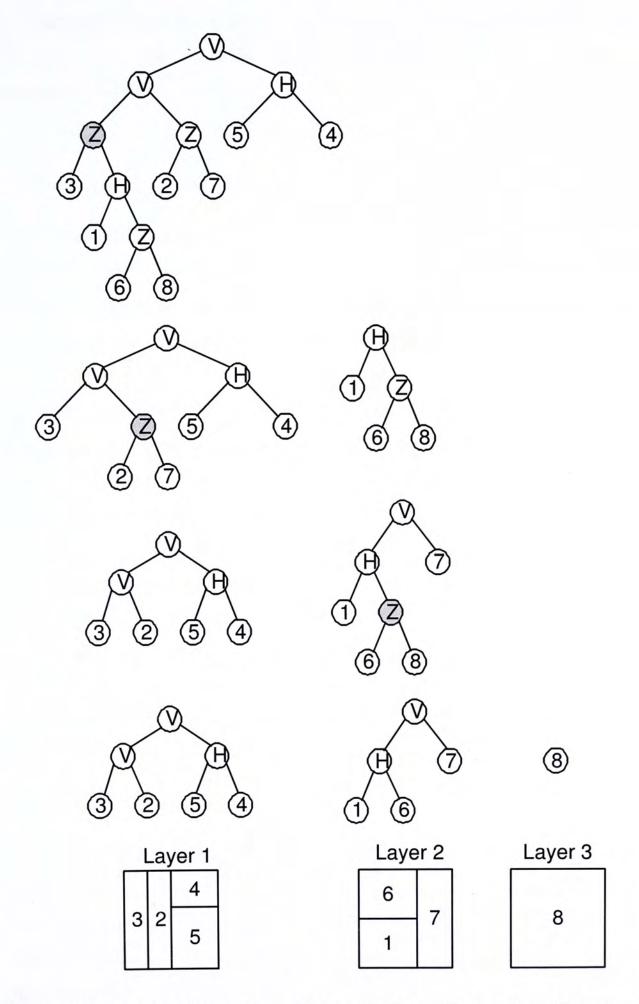

In 2002, Young et al. proposed a Twins Binary Sequences (TBS) representation for mosaic floorplan in [13] basing on TBT. The idea of using TBT to represent mosaic floorplans was proposed in [30] but the exact modelling was not mentioned. For example, it is not known that how the nodes in the TBT should be labelled so that it corresponds to a feasible floorplan. In view of this, the authors in [13] proposed a TBS representation to cope with the problems. The authors proposed to use a 4-tuple  $s = (\pi, \alpha, \beta, \beta')$  to represent a floorplan. We call s the TBS representation of a floorplan.

$\pi$  is the in-order traversals of the twin binary trees, and  $\alpha$  is the labelling of them. The authors claimed that a pair of twins binary trees will correspond to a feasible packing if and only if their in-order traversals are the same. However, these two pieces of information solely are not enough to represent a floorplan uniquely. Thus, two more bit sequences  $\beta$  and  $\beta'$  are needed. These two sequences record the structural information of the trees: a bit '0' represents the root of a tree and a node that is the right child of its parent, and a bit '1' represents a node that is the left child of its parent.  $\beta$  is used to represent the directional information of  $t_1$ , where  $\beta'$  is used to represent the directional information of  $t_2$ . An example is shown in Figure 2.13.

To make TBS more general, the authors proposed to include in the input some dummy zero-area blocks. They have proved that a tight bound of  $\theta(n)$  dummy blocks are needed to obtain general non-slicing floorplan from mosaic floorplan.

Realizing a floorplan from its TBS representation is very efficient according to [13]. It can be done by scanning the sequences only once from right to left.

Figure 2.13: A Floorplan Realization Example using TBS.

It is also proved that there is a one-to-one mapping between TBS and TBT, and thus a one-to-one mapping between TBS and mosaic floorplan. The size of the solution space of TBS is the same as that of TBT,  $O(n!2^{3n}/n^{1.5})$ .

# 2.3 Summary

In this chapter, different types of floorplan are introduced, which are slicing, non-slicing, and mosaic floorplan. Slicing floorplans are obtained by recursively dividing a rectangle into smaller rectangles. Though the solution space is small, slicing floorplans are not general enough, as most floorplans are not slicing practically. Mosaic floorplans are not necessarily obtained by dividing rectangles and thus are more general but they contain no empty space. Non-slicing floorplan is the most general one.

Current state-of-the-art representations of each type of floorplan are presented. Table 2.1 is a table summarizing the characteristics of these representations. For slicing floorplans, the most popular representation used is the normalized Polish Expression [25]. The representation is simple and elegant, and floorplan realization can be done in linear time.

For non-slicing floorplans, there are several representations such as sequence pair (SP), bounded-sliceline grid (BSG), O-Tree, B\*-Tree, and transitive closure graph (TCG). The sizes of their solution spaces and the floorplan realization runtimes are different. SP, BSG, and TCG are P-admissible where O-Tree and B\*-Tree are not.

Mosaic floorplans can be represented using corner block list (CBL), twins binary tree (TBT), or twins binary sequences (TBS). The solution space of

CBL is small, but not all CBL corresponds to a floorplan. In TBT and TBS, the solution is one-to-one mapped to the representation and the realization process can be done in linear time.

| Representation | Size of Solution Space  | Time Complexity of    |

|----------------|-------------------------|-----------------------|

|                |                         | Floorplan Realization |

| Normalized PE  | $O(n!2^{5n-3}/n^{1.5})$ | O(n)                  |

| SP             | $O((n!)^2)$             | O(nloglogn)           |

| BSG            | $O(n^2!/(n^2-n)!)$      | $O(n^2)$              |

| O-Tree         | $O(n!2^{2n-2}/n^{1.5})$ | O(n)                  |

| B*-Tree        | $O(n!2^{2n-2}/n^{1.5})$ | O(n)                  |

| TCG            | $O((n!)^2)$             | $O(n^2)$              |

| CBL            | $O(n!2^{3n})$           | O(n)                  |

| TBT            | $O(n!2^{3n}/n^{1.5})$   | O(n)                  |

| TBS            | $O(n!2^{3n}/n^{1.5})$   | O(n)                  |

Table 2.1: Comparison between Different Kinds of Floorplan Representations.

# Chapter 3

# Literature Review on 3D Floorplan Representations

### 3.1 Introduction

As the VLSI design complexity increases, both the number of blocks and the number of interconnects involved have increased dramatically. Interconnect awareness in every step of the design cycle has become a major concern as technology advances into the deep submicron era. In view of this, 3D chip is proposed. Interconnect lengths can be reduced greatly in 3D chips and thus making it easier to meet the timing requirements and to reduce the interconnect cost. Unlike the traditional packing problem of 3D blocks, there are several layers available for placing modules in 3D floorplanning. Thus, 3D floorplans are also known as multi-layer floorplans.

Though 3D chips are advantageous in solving the interconnect problem, there are still a lot of design challenges and there are not yet enough EDA tools to assist 3D chip design. In this chapter, some previous work on floorplanning for 3D chips will be discussed.

## 3.2 Problem Formulation

The formal definition of the floorplanning problem for 3D design are given as followed:

**Definition 3.1** The input is a set of n modules  $\{M_1, M_2, \dots, M_n\}$  and a value K that represents the number of layers, where each module  $M_i$  is associated with an area  $A_i$ , together with two aspect ratio bounds  $r_i$  and  $s_i$  such that  $r_i \leq h_i/w_i \leq s_i$ , where  $h_i$  and  $w_i$  are the height and the width of module i respectively. The output of the problem is a packing of the set of modules, i.e., the x- and y-coordinates and the dimensions  $(h_i, w_i)$  of modules i, and the layer  $l_i$ , where  $1 \leq l_i \leq K$ , on which module i lies. There should be no overlapping between modules in each layer, and the circuit performance should be optimized.

# 3.3 Previous Work

Several researchers have worked on floorplanning for 3D chips recently. They have proposed different representations for 3D floorplans. Their work will be reviewed in this section.

### Slicing Tree

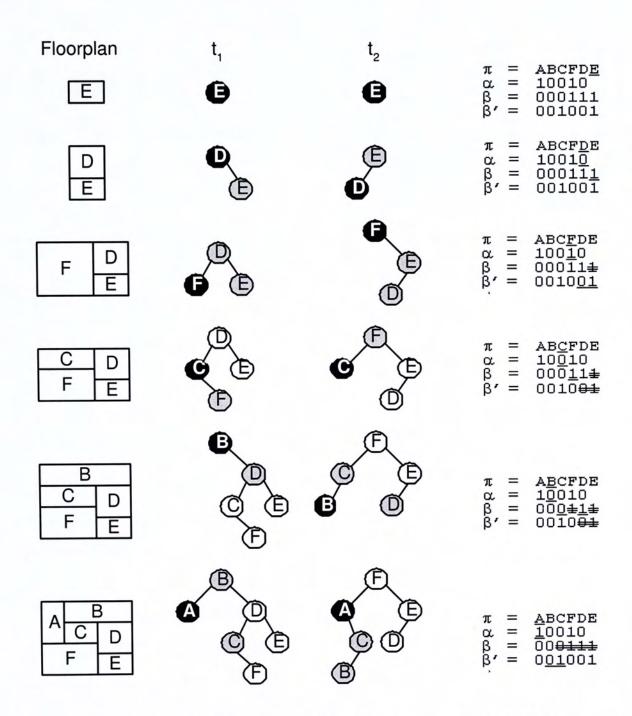

In 2004, the authors of [4] proposed a slicing structure representation for multilayer floorplans. In 2D floorplan representation, a floorplan is said to be a *slic*ing structure if it can be obtained by recursively dividing a rectangle into two by vertical or horizontal lines. The authors extend this idea into three dimensions, and adopted the Normalized Polish Expressions to represent multi-layer floorplans. Similar to Normalized Polish Expressions for 2D floorplans, a slicing tree is constructed for multi-layer floorplans. There are three kinds of internal nodes, 'H', 'V', and 'Z', representing horizontal, vertical, and lateral cuts respectively, while each leaf is labelled by a module name.

To realize the floorplan, the slicing tree has to be broken down. Each layer is represented by a slicing sub-tree. This is done by removing all the 'Z' nodes in the tree, leaving behind those 'V' and 'H' nodes only.

Given a slicing tree, we will construct the slicing sub-tree for each layer one by one from the top to the bottom. At each layer, the 'Z' node is replaced by its left child, and the right sub-tree is put to the lower layer. To put a sub-tree to the lower layer, it is checked whether the lower layer is empty first. If so, the sub-tree becomes the slicing sub-tree of that layer. Otherwise, a new root node is created to join the current slicing sub-tree and the newly added sub-tree and the label on the new root is either 'V' or 'H' depending on the lowest common ancestor of these two subtrees in the original slicing tree. An example showing a multi-layer floorplan and its slicing tree representation is illustrated in Figure 3.1.

### An Array of 2D Representations

To make things easy and strict forward, some researchers have proposed to use an array of 2D representations to represent multi-layer floorplans [34][35]. In [34], the authors proposed to use an array of Base Slice-line Grid (BSG) to represent a multi-layer floorplan, where each BSG represents the 2D floorplan on each layer. In [35], the same approach is used, but sequence pair is selected as the 2D floorplan representation.

Figure 3.1: (a) A 3D Slicing Tree. (b) The 2D Slicing Tree and the Floorplans of Each Layer.

This kind of representations is strict forward and easy to understand. However, the relationships between blocks in different layers can not be reflected by the representation solely.

### Combined Bucket and 2D Array (CBA)

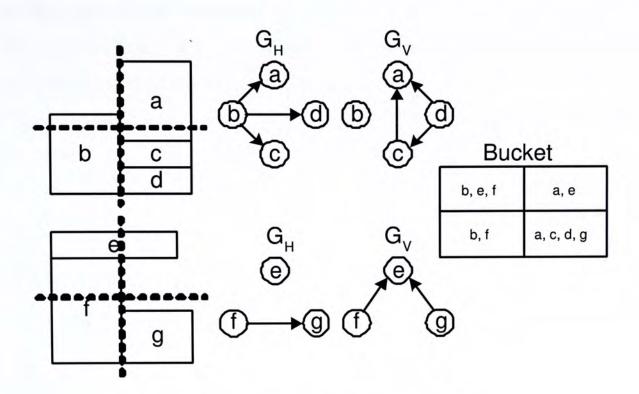

To represent multi-layer floorplans, we can use a 2D representation to represent each layer. However this is not good as the relationships between blocks in different layers are not stored. In view of this, the authors of [36] proposed a multi-layer representation called Combined Bucket and 2D Array (CBA).

CBA is consisted of two parts, a 2D representation to represent each layer, and a bucket structure to store the relationships between blocks in different layers. In [36], TCG is selected as the 2D representation but in fact, any 2D floorplan representation like Sequence Pair or Corner Block List can be used.

A bucket represents a rectangular region on the x-y plane. It stores the relationships between blocks in different layers. For each bucket, indexes of the blocks that intersect with that bucket are stored. Besides, for each block, the indexes of the buckets that intersect with that block are also recorded. Thus, if two block i and j, locating in different layers, intersect with the same bucket k, it is likely that they are placed close to each other. In Figure 3.2, a multi-layer floorplan and its CBA representation is shown.

Simulated annealing is used in [36] to search for a good floorplan. The authors have proposed different kinds of moves. Apart from some intra-layer moves like 'rotation', 'swap', 'reverse', and 'move', the authors suggested three more inter-layer moves namely 'interlayer swap', 'z-neighbor swap', and 'z-neighbor move'. The first one means swapping two blocks in different layers.

Figure 3.2: A Floorplan Represented by CBA.

The second one means swapping two blocks in different layers, but they must be close to each other. The third one means moving a block to another layer, and the destination must be close to its original position. Experimental results showed that the performance of [36] is better than that of [35].

## 3.4 Summary

In this chapter, the mutli-layer floorplanning problem is defined. It is different from the traditional floorplanning problem, as it allows blocks to be placed on more than one layer. Multi-layer floorplan design is beneficial as it can reduce the interconnect cost significantly, making the routing step easier, and making it easier to meet the timing requirements.

Several previous work on multi-layer floorplan representation is reviewed.

In [4], a slicing tree representation is proposed and in [34] [35], an array of 2D floorplan representations is proposed. However, for both of them, the relationships between blocks in different layers are neglected. Thus, the authors of [36] proposed a Combined Bucket and 2D Array representation to extend the state-of-the-art 2D representations to multi-layer.

# Chapter 4

# Literature Review on Bus-Driven Floorplanning

### 4.1 Problem Formulation

Bus-Driven Floorplanning problem is a floorplanning problem with bus planning taken into consideration. Bus is a collection of interconnections between a set of modules. The problem of bus-driven floorplanning (BDF) can be defined as follows [1]:

### Definition 4.1 Bus-Driven Floorplanning (BDF)

Given the following:

- 1. A set of n blocks  $B = \{b_0, b_1, ..., b_{n-1}\}$ , where each block  $b_i$  is associated with a width  $w_i$  and a height  $h_i$ , where  $w_i$ ,  $h_i \in \mathbf{R}^+$ .

- 2. A set of m buses  $U = \{u_0, u_1, ..., u_{m-1}\}$ , where each bus  $u_i$  has a width  $t_i, t_i \in \mathbf{R}^+$ , and goes through a set of blocks  $B_i, B_i \subseteq B$ .

Our task is to decide the position of each block and the route of each bus, such that each bus  $u_i$  can go through all its blocks. There should be no overlapping between any two blocks. The goal is to minimize the chip area and the total bus area.

Some recent approaches used to solve the bus-driven floorplanning problem will be discussed in the coming sections.

### 4.2 Previous Work

Many algorithms have been proposed to enforce different kinds of placement constraints in floorplan design. For example, the authors in [37][38][39][40][41] had considered alignment and abutment constraints in floorplan design. In [1][42], the bus-driven floorplanning problem is addressed. These approaches will be discussed in details in the following sections.

#### 4.2.1 Abutment Constraint

The authors of [37] enforce abutment constraint in floorplanning in order to handle rectilinear block placement. The sequence pair representation is adopted. To take care of rectilinear blocks, the authors proposed to partition each rectilinear block into a set of rectangular sub-blocks. Each block is partitioned in one direction only, and all neighboring sub-blocks are orthogonally aligned (Figure 4.1). Some rectilinear blocks with complicated shape may need to be partitioned into L-shaped sub-blocks, and then into rectangular shapes. In order to employ the approach proposed, the partitioning has to be done in such a way that the neighboring sub-blocks can be grouped into a L-shape block. However, some rectilinear blocks cannot be partitioned according to the above requirements. Then, an  $\epsilon$ -approximation is performed to divide it into two L-shape sub-blocks. An example is illustrated in Figure 4.2.

After partitioning, the sub-blocks have to be abutted to maintain the original rectilinear shape. For example, if a block X is partitioned into three sub-blocks as in Figure 4.1(a)), they have to be abutted horizontally or vertically in the final floorplan in order to get back the original rectilinear shape.

Figure 4.1: (a) A Feasible Partitioning. (b) An Infeasible Partitioning.

Figure 4.2: A Rectilinear Block That Cannot Be Decomposed into Two L-Shape Sub-Blocks and Its  $\epsilon$ -Approximation.

There is a key observation: the sub-blocks should maintain their initial relative positions in any feasible placements, e.g., the blocks should appear in the sequence pair as (...A...B...C..., ...A...B...C...), (...A...B...C..., ...C...B...A...), (...C...B...A..., ...C...B...A...), or (...C...B...A..., ...A...B...C...) for the example in Figure 4.1(a). Simulated annealing is used. Infeasible candidate solutions, e.g., the sub-blocks are not abutted, will be penalized in the cost function.

In 2001, the authors of [38] have proposed an algorithm to enforce abutment constraints to blocks in a floorplan. L-shaped and T-shaped blocks are first partitioned into rectangular sub-blocks, and the sub-blocks are then forced to obey the abutment constraints and the rectilinear blocks can thus be placed.

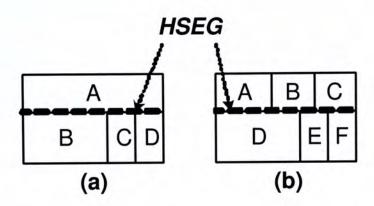

Unlike [37], Corner Block List (CBL) is used to represent a floorplan. The authors have showed that the abutment information of the blocks can be deduced from the CBL representation. Let HSEG be a horizontal segment in a

floorplan P,  $B_{HSEG} = \{B_1, B_2, \dots, B_p\}$  denotes the p blocks lying immediately below HSEG, and  $T_{HSEG} = \{T_1, T_2, \dots, T_q\}$  denotes the q blocks lying immediately above HSEG. If q equals one, every block in  $B_{HSEG}$  is lying immediately below the block  $T_1$ , implying an abutment information. The case of p equaling one is similar. If both p and q are greater than or equal to two,  $B_1$  will abut with  $T_1$ , and  $B_p$  will abut with  $T_q$  (Figure 4.3).

Figure 4.3: (a)Block A is Abutted With Block B, C, and D. (b)Block A is Abutted With Block D, Block C is Abutted With Block F.

To place L-shape or T-shape blocks, they are first partitioned into rectangular sub-blocks. However, enforcing only the abutment constraints to the sub-blocks is not enough. An example is illustrated in Figure 4.4. Thus, the authors introduced the align-abutment constraints, which means the blocks has to be aligned and abutted at the same time. Then, simulated annealing is used to search for a good solution. A penalty will be given to the candidate floorplan solutions in which the align-abutment constraints is violated.

An algorithm to handle arbitrarily shaped rectilinear blocks were proposed in 2004 by Tang et al in [41]. They also used the sequence pair representation.

According to the paper, a rectilinear block is said to be H-sequential if

Figure 4.4: Abutment Constraint Alone is Not Enough to Form a L-Shape.

no single vertical line can cut the block into more than two parts. Similarly, a rectilinear block is said to be *V-sequential* if no single horizontal line can cut the block into more than two parts. An example is illustrated in Figure 4.5. A block is said to be *non-sequential* if it is neither H-sequential nor V-sequential (Figure 4.6). If a block is H-sequential, it can be partitioned into a set of horizontally-abutted sub-blocks, the set of sub-blocks are called a H-sequential sequence. For the set of sub-blocks, the relative position of them has to be the same in both sequence of the sequence pair representation. V-sequential sequence can be defined in a similar fashion. An orthogonal link list is proposed to store the information of the rectilinear blocks.

Figure 4.5: (a) A H-Sequential Rectilinear Block. (b) A V-Sequential Rectilinear Block.

Simulated annealing will then be applied to search for a good solution. Experimental results showed that the performance of the approach is promising.

Figure 4.6: (a) A Non-Sequential Rectilinear Block. (b) It is Partitioned into Several Sub-Blocks.

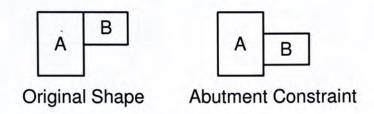

However, the algorithms proposed cannot be applied directly in the busdriven floorplanning problem, as for a bus to go through a set of blocks, it is not necessary for the blocks to abut with one another. Besides, the order in which a bus goes through its blocks is not known beforehand. Nevertheless, their novel notion of checking relative positions between blocks in a representation is helpful.

### 4.2.2 Alignment Constraint

In [39], the authors proposed a unified method to handle different kinds of placement constraints, like pre-placed constraint, range constraint, boundary constraint, alignment, abutment, and clustering constraint, etc.

The authors proposed that all the constraints mentioned above can be modelled as a collection of relative placement constraint and absolute placement constraint. Relative placement constraints are vertical or horizontal distance restriction (a certain range of values) between two modules. For example,  $h(A, B) = [\alpha, \beta]$  means that the horizontal distance between the lower left corners of block A and block B has to be greater than  $\alpha$ , but cannot exceed  $\beta$  (Figure 4.7). Absolute placement constraints are similar, except that one of the two modules in the relationship is a boundary of the chip. The left, right,

bottom, and top boundary of a chip are denoted by LL, RR, BB, and TT. An example is illustrated in Figure 4.8.

Figure 4.7: Relative Placement Constraint:  $h(A, B) = [\alpha, \beta]$

Figure 4.8: Absolute Placement Constraint:  $v(BB, A) = [\alpha, \beta]$

Sequence pair representation is adopted. After modelling different kinds of placement constraints as a collection of relative and absolute placement constraints, they can be enforced by inserting pairs of edges in the constraint graphs. If adding of edges produces positive cycles in the constraint graphs, the packing is infeasible (cannot satisfy all placement constraints). Then, a penalty will be added in the cost function of the simulated annealing process.

Based on the sequence pair representation, the authors of [40] proposed a

method to enforce the alignment constraint and some other placement constraints in 2002.

An intuitive idea of deducing the approximate positions of a set of blocks by looking at the sequence pair is proposed in [40]. In the paper, a set of blocks are said to be H-aligned if they are abutting with each other horizontally. V-alignment can be defined in a similar fashion. After that, the authors defined strictly ahead as follow: Given two blocks a and b and a sequence pair (X, Y) =  $(X_1aX_2bX_3, Y_1aY_2bY_3)$ , a is strictly ahead of b in (X, Y) if and only if the length of the longest common subsequence of  $(X_2, Y_2) = 0$ .

It is shown that if a set of blocks are *H-aligned*, the relative positions of the blocks in both sequences of the sequence pair should be the same, and the *strictly ahead* relationship should exists between every pair of consecutive neighboring blocks. The method of finding the approximate positions of the blocks by looking at the sequence pair is very helpful. In [1], the authors have made use of this to design an algorithm to solve the bus-driven floorplanning problem.

These kinds of approaches to enforce alignment constraint in a floorplan are again not suitable for solving the bus-driven floorplanning problem, as for a bus to go through a set of blocks, it is not necessary for them to align. Forcing them to align will impose some needless restrictions to the solution. Besides, for a bus to go through a set of blocks, the order in which the blocks are placed is not fixed.

### 4.2.3 Bus-Driven Floorplanning