# On FPGA Implementations for Bioinformatics, Neural Prosthetics and Reinforcement Learning Problems

MAK Sui Tung Terrence

A Thesis Submitted in Partial Fulfillment of the Requirements for the Degree of Master of Philosophy

in

Systems Engineering and Engineering Management

©The Chinese University of Hong Kong

June 2005

The Chinese University of Hong Kong holds the copyright of this thesis. Any person(s) intending to use a part or the whole of the materials in this thesis in a proposed publication must seek copyright release from the Dean of the Graduate School.

#### **Abstract**

Along with the remarkable success of Human-Genome-Project and the launch of Genome-to-Life project, voluminous biological data was accumulated and the secrets of life were yet to be deciphered. Innovations and implementations of high performance computing infrastructure to support the computational analysis of large-scale data set, complex model simulations and achieving effective access to biological data are considered to be equally important as continuing to generate new biological data from pipelining biotechnological machineries.

In parallel with the development of the computational bioinformatics, neural prosthetics, on the other hand, emerges as an innovative and interdisciplinary subject, in which the need of real-time performance is critical. Neuron-machine interfaces such as dynamic clamp and brain-implantable neuro-prosthetic devices require real-time simulations of neuronal ion channel dynamics, in which silicon devices mimic the living cell mechanics. A hardware-based, application-specific implementation of the neuronal ion channel dynamics would circumvent the limitations of computational speed and flexibility in general-purpose computers.

Further, for future combat to reduce human causalities, gathering scientific data from distant planets or in extreme environments, intelligent robots such as Unmanned Aerial Vehicles (UAVs), and Mars Rover, should be equipped with capability learning and real-time decision making, which are both computational intensive tasks. Delay in the decision making, due to heavy computational burden, would be disastrous. The distributed and parallel computational learning architecture could circumvent the limitation of the sequential computation machineries.

Field programmable gate array (FPGA) has emerged as a high-speed digital platform for application-specific computation devices. However, it is a challenge to have efficient design with good mapping from algorithms to hardware logics, due to the design complexity and the algorithm complexity. The objective of this thesis is to investigate and develop efficient methods to address the computational and implementation challenges in FPGA The research covers area from computational genomics, neural prosthetics applications to theoretical reinforcement

learning implementation in a distributed environment, with a goal to improve existing softwarebased implementation methodologies and sequential computational framework.

In light of the advance programmable distributed logics technology, we have worked on the FPGAs designs based on three different application-oriented examples. Firstly, we propose a novel approach for searching equivalence set from genetic network and offer an efficient FPGAs implementation. The approach is beneficial to genetic network dynamics development. Secondly, we propose a FPGA-based architecture for computational intensive phylogenetic tree topology evaluation. Significant acceleration for the tree evaluation can be obtained based on the proposed hardware architecture. Thirdly, we present an FPGA design of a neuromorphic Hebbian synapse which mimics the NMDA and non-NMDA ion channel dynamics observed experimentally in hippocampal neurons. The proposed design can be readily extended to high-speed implementations of dynamic clamp and neuro-prosthetics as replacements for damaged neurons in the brain.

In addition, we consider a distributed computational framework for continuous-time inference network for solving dynamic programming problems. It is a computational intensive task which becomes the bottleneck of real-time reinforcement learning and decision making. We offer an FPGAs implementation scheme with distributed arithmetic with adaptation of the embedded multipliers and logics. We also consider an analog Very Large Scale Integrated (VLSI) design for the realization and verification of the theoretical formulation. We show that the inference network converges to the optimal Bellman optimality condition, for which the convergence rate can be made arbitrarily fast and is practically independent of the problem size. Lastly, based on the framework of the Bellman Inference Network, a novel *Q*-learning network architecture is proposed. We introduce the exploration and memory components to the original Bellman inference network to form a connectionist network with the capability of parallel learning and optimization. We found that the *Q*-learning network significantly outperforms the conventional *Q*-learning algorithm under a distributed unknown environment. We also proposed two design alternatives for the realization of *Q*-learning network using FPGAs with the network dedicated to fit different applications.

#### 摘要

隨著「人類基因組計劃」革命性的成功和近期展開的大規模微生物基因排序「從基因研究了解生命」,國際基因庫屯積了大量生物數據,但是我們對生命密碼的破解還是處於起步的階段。高效能計算分析、複雜模型運算,及有效存取生物數據的創新性實現方法研究應和繼續採集生物數據有相同的重要性。在生物計算高速發展的同時,腦一機界面(或稱神經義肢)成爲對實時計算有高要求的新興學科。當中,以動態鉗和腦部可植入晶片的研究對高效能實時運算有最高要求。通過在專用硬件上實現,此研究可用作模擬真細胞的運作和模擬腦細胞離子通道運作並可改善普通電腦在運算速度和彈性上的限制。另外,爲應付未來戰爭或到外星極地進行科學研究,智能機械人,例如無人駕駛飛機,火星挑戰者號,應具備實時學習及決策的能力。但這些都是需要大量運算的。如果因要應付大量運算而延誤了決策,可能導致嚴重的後果。

近年,現場可編程門陣列已成爲現代專門高速運算硬件平台。但因爲硬件設計和算法的複雜性,令算法在硬件實現上出現很大的困難。本論文的目的是研究在生物信息、腦一機界面、及機器學習的問題上如何有效地實現分佈式硬體以達到提高單以軟體爲基礎的實現方法。我們針對三個不同的領域的問題進行現場可編程問陣列硬件實現的研究。第一,我們提出遺傳算法及動態規劃的綜合算法以解決同類基因搜索的問題。此新算法對建造基因動態模形有很大幫助。此外,我們還對算法提供了硬體的實現方法,以大大縮短所需計算時間。第二,我們提出了以並行硬件實現模式以加快基因遺傳樹重建的密集計算。第三,我們提出一套對腦細胞離子通道模擬的硬件實現方法。硬件設計對高速互動鉗和腦一機介面的建造有極大的幫助。

除此以外,本論文也針對增強式學習問題提出了間斷性和連續性推理網絡的理論基礎及實現方法。該方法可以突破實時學習的計算速度瓶頸。我們提供了現場可編程門陣列及模擬電路在超大規模集成電路的實現。最後爲解決在信息不全的情況下增強學習的問題,我們提出了 Q-學習網絡的構想。從初步的模擬測試中,Q-學習網絡表現了較有效率的學習及優化計算。此外,我們也提出了不同的硬件實現方法以應付不同的需求。

#### **List of Tables**

| Table 3.1 | able 3.1 Dynamic range comparison between Simplified Floating Point (SFPT), Fixed- |            |

|-----------|------------------------------------------------------------------------------------|------------|

|           | point and Single Precision Floating Point (FPT)                                    | 42         |

| Table 3.2 | Timing analysis based on the number of multiplications                             | 53         |

| Table 3.3 | Hardware resource consumption with increasing number of taxa                       | 57         |

| Table 4.1 | Comparison of resource utilization on different FPGAs                              | 71         |

| Table 6.1 | Comparison between the two approaches on the consumption of logic                  | slice with |

|           | respect to the number of actions and bit length                                    | 126        |

| Table 6.2 | Maximum updating rate                                                              | 127        |

| Table C.1 | Main system component in the circuit fabrication                                   | 160        |

### **List of Figures**

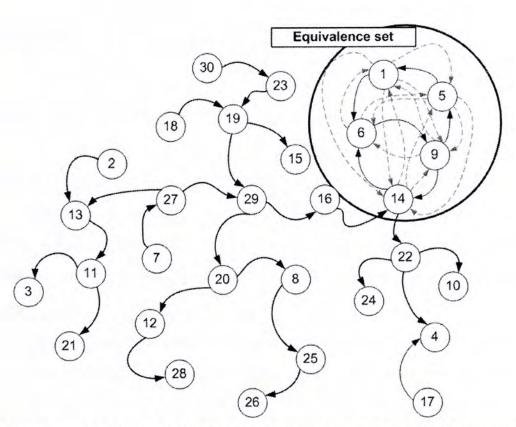

| Figure 2.1  | An example of genetic network with equivalence sets.                         | 17        |

|-------------|------------------------------------------------------------------------------|-----------|

| Figure 2.2  | Steps to compute the equivalence set.                                        | 19        |

| Figure 2.3  | Pseudo-code of bounded mutation.                                             | 23        |

| Figure 2.4  | Pseudo-code of the conditional crossover                                     | 24        |

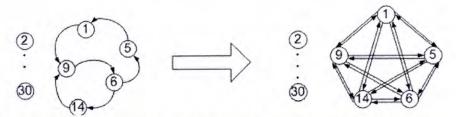

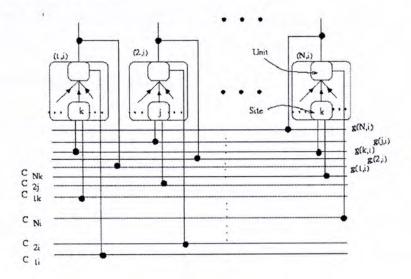

| Figure 2.5  | GA-DP hardware architecture                                                  | 25        |

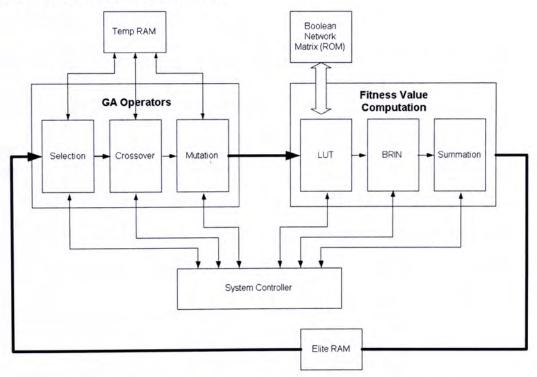

| Figure 2.6  | Network topology diagram of Binary Relation Inference Network.               | 27        |

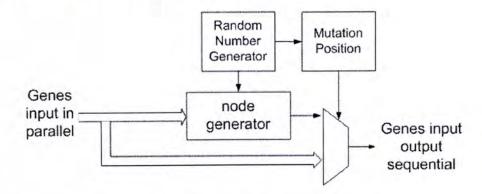

| Figure 2.7  | Data flow diagram of the mutation operator                                   | 28        |

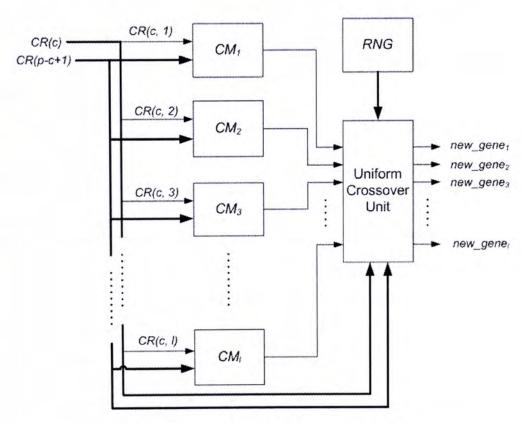

| Figure 2.8  | Data flow diagram of the Crossover operation                                 | 29        |

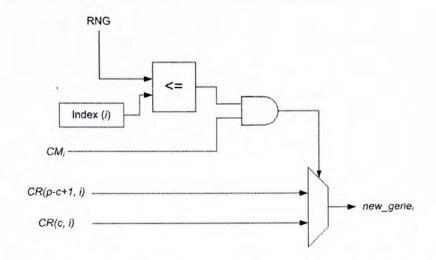

| Figure 2.9  | The schematic diagram of the crossover unit                                  | 30        |

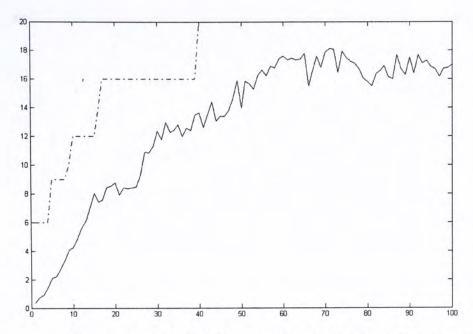

| Figure 2.10 | Software simulation result for searching equivalence genes using GADP        | 31        |

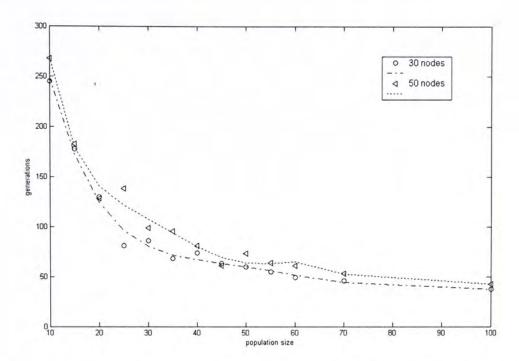

| Figure 2.11 | Simulation study for the number of generations versus population size of     | the GA-   |

|             | DP                                                                           | 32        |

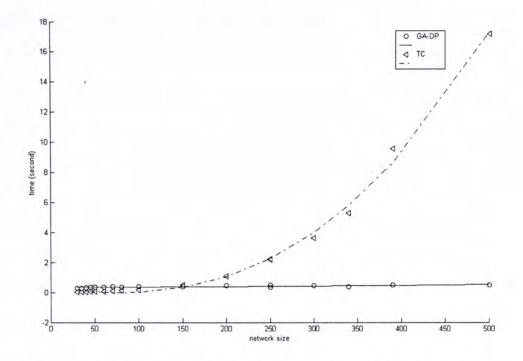

| Figure 2.12 | Comparison of computational time between the GA-DP and the transitive        | e-closure |

|             | approach from (Maki, Tominaga et al. 2001)                                   | 33        |

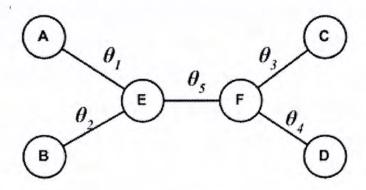

| Figure 3.1  | A 4-taxa unrooted bifurcating tree                                           | 37        |

| Figure 3.2  | Illustration of the idea using hardware to accelerate phygenetic tree recons | struction |

|             |                                                                              | 38        |

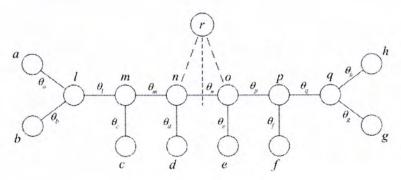

| Figure 3.3  | An example of 8-node unrooted phylogenetic tree                              | 44        |

| Figure 3.4  | An example of tree representation using a ROM/RAM                            | 44        |

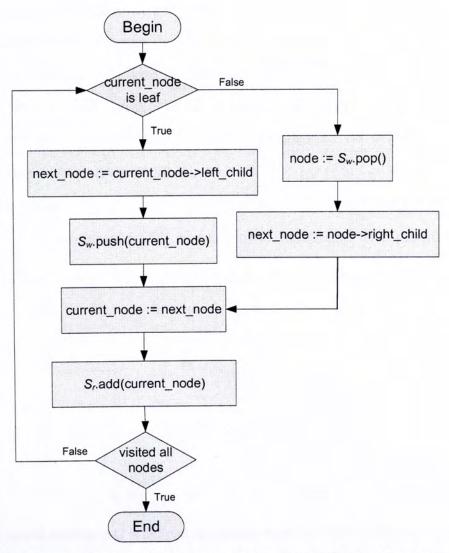

| Figure 3.5  | Flowchart for pre-order tree traversal with using stack                      | 45        |

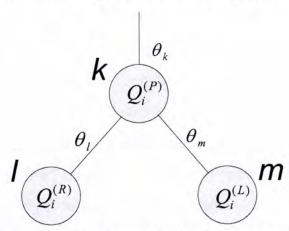

| Figure 3.6  | The partial likelihood definition                                            | 46        |

| Figure 3.7  | Pseudo-code of four basic routines to compute the partial likelihood         | 48        |

| Figure 3.8  | Pseudo-code of the recursive maximum-likelihood evaluation algorithm         | 49        |

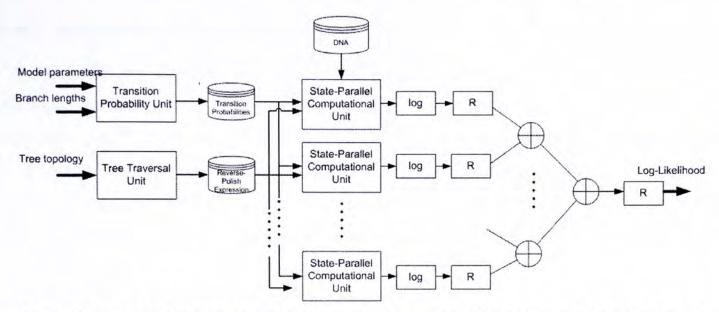

| Figure 3.9  | Data path diagram of likelihood evaluation for a given tree topology,        | , branch  |

|             | lengths and model parameters                                                 | 50        |

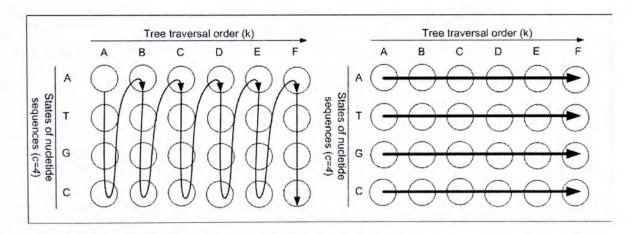

| Figure 3.10 | Illustration the idea of the parallel partial likelihood computation         | 51        |

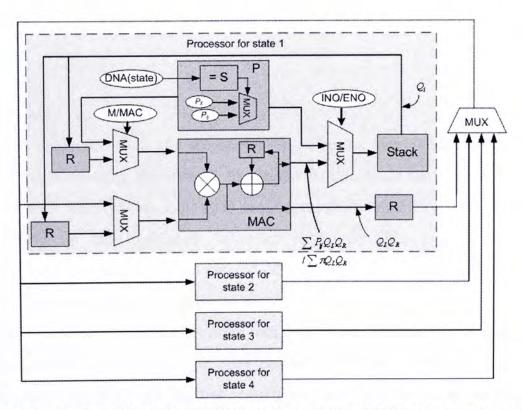

| Figure 3.11 | FPGAs architecture of the State-Parallel Computational Unit (SPCU)           | 52        |

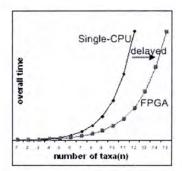

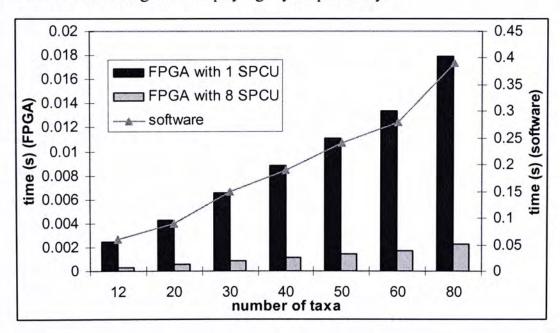

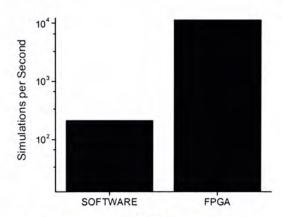

| Figure 3.12 | Comparison of the computational time between software and                    | FPGA      |

|             | implementation                                                               | 58        |

| Figure 4.1  | Biological synapse with glutamate activating AMPA and NMDA chan            | nels, and   |

|-------------|----------------------------------------------------------------------------|-------------|

|             | generating an EPSP                                                         | 63          |

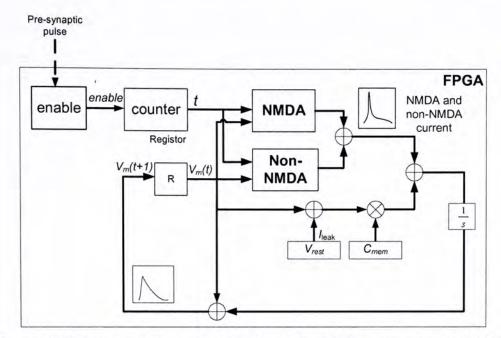

| Figure 4.2  | Schematic design of the NMDA and non-NMDA synapse using FPGA               | 67          |

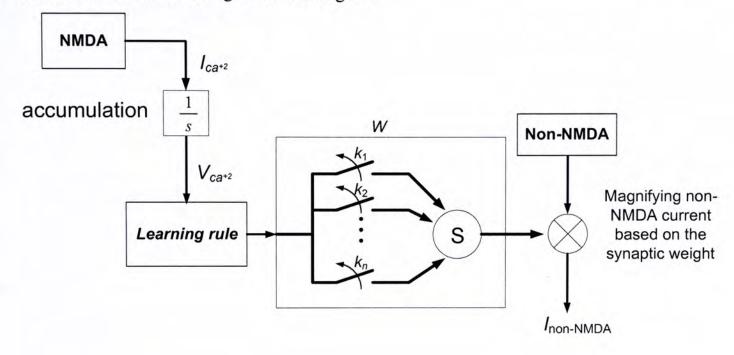

| Figure 4.3  | Schematic design of learning and adaptation of plasticity using FPGA       | 68          |

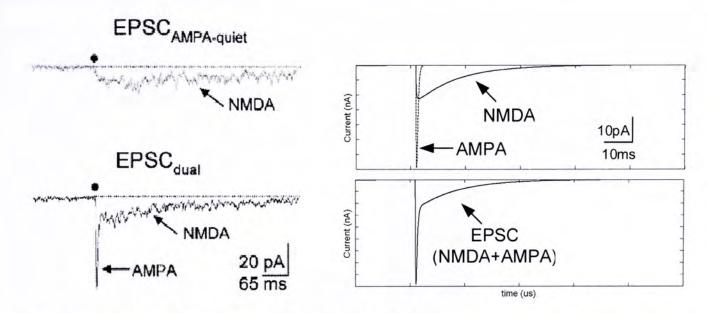

| Figure 4.4  | a.) Biological Recordings of individual NMDA channels, and miniatur        | e EPSCs     |

|             | which sum AMPA and NMDA currents, adapted from [22]. b.) Simu              | lation of   |

|             | FPGA circuit for the AMPA and NMDA current (upper) and the EPSC            | (below),    |

|             | which are qualitatively similar to the experimental data in (Renger, Eg    | gles et al. |

|             | 2001) in a.)                                                               | 69          |

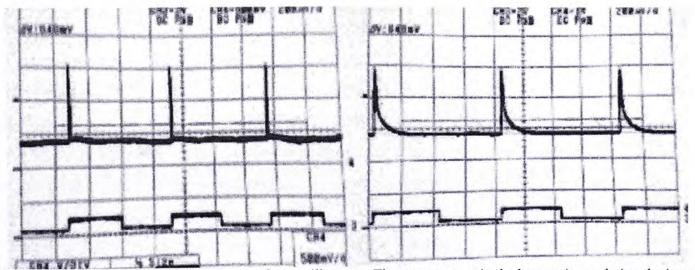

| Figure 4.5  | Screen capture from oscilloscope for FPGAs real-time computation of ion    | n channel   |

|             | dynamics                                                                   | 69          |

| Figure 4.6  | Comparison between software and FPGA for the post-synaptic ion             | channel     |

|             | simulation                                                                 | 70          |

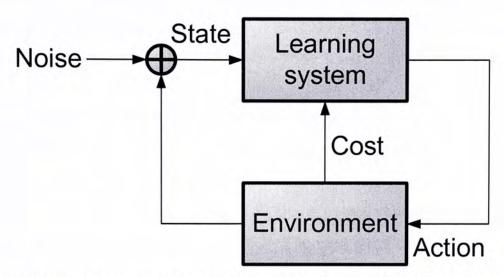

| Figure 5.1  | Learning system interacting with its environment                           | 78          |

| Figure 5.2  | A typical step in reinforcement learning problem                           | 78          |

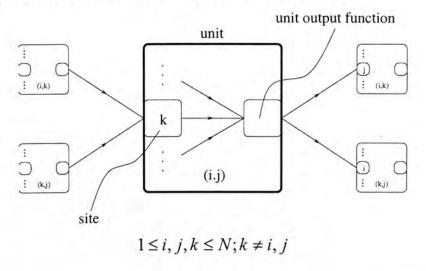

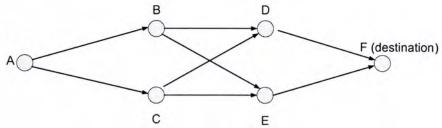

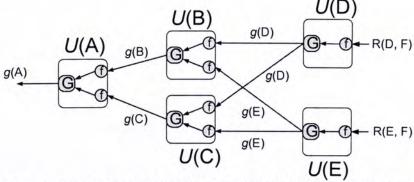

| Figure 5.3  | Unit interconnection in a general binary relation inference network        | 84          |

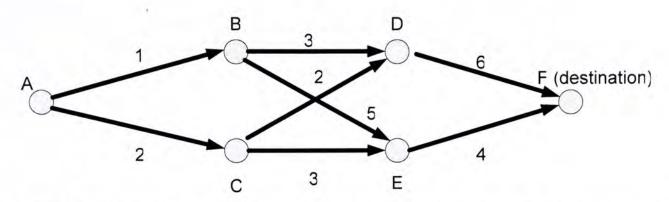

| Figure 5.4  | a.) Original problem state graph b.) inference network for solving graph i | n a.)       |

|             |                                                                            | 86          |

| Figure 5.5  | A small Markov process for generating random walks                         | 90          |

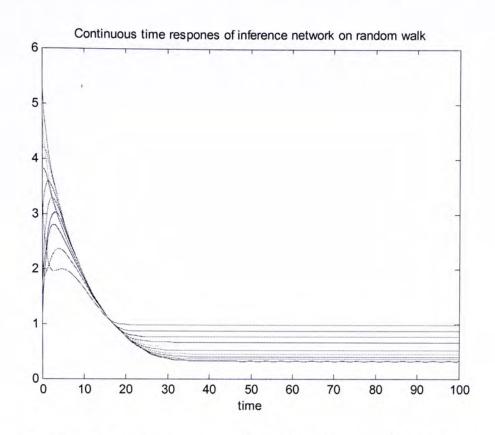

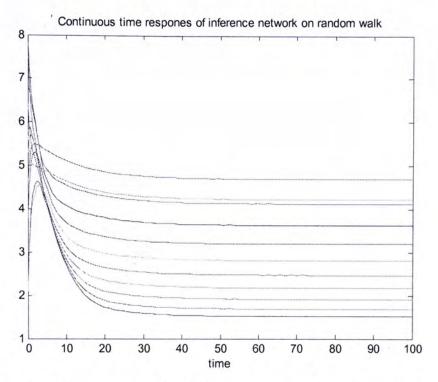

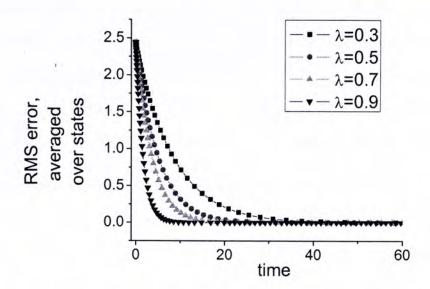

| Figure 5.6: | Convergence of the differential equations                                  | 92          |

| Figure 5.7: | Convergence of the differential equations another case                     | 93          |

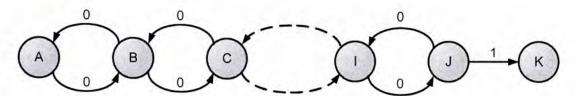

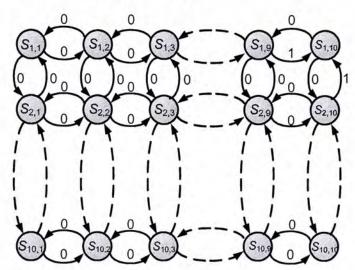

| Figure 5.8  | Simulation of a 10-unit inference network for 10-state random walk         | 93          |

| Figure 5.9  | A small Markov process for generating random walks on grid                 | 94          |

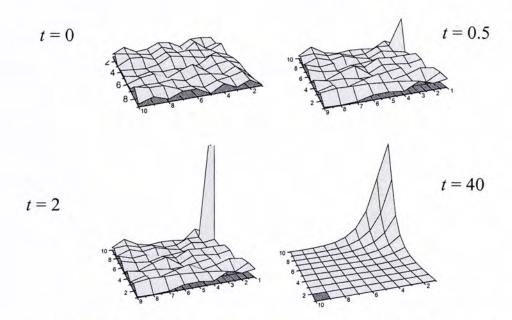

| Figure 5.10 | Computation of state-value functions for the random walk in the grid-wor   | ·ld         |

|             |                                                                            | 96          |

| Figure 5.11 | Learning curves for continuous-time inference network for random wa        | lk in the   |

|             | grid-world problem                                                         | 97          |

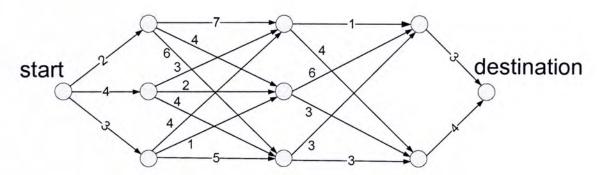

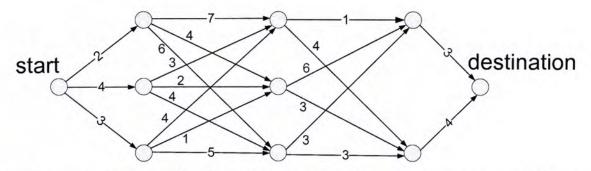

| Figure 5.12 | The flow-graph for stagecoach problem (Haykin 1999)                        | 97          |

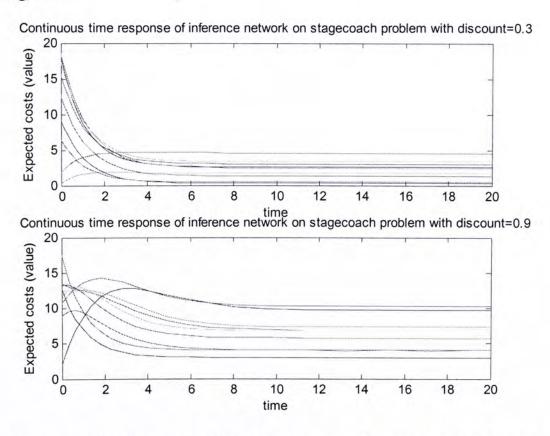

| Figure 5.13 | Simulation of a inference network for the stagecoach problem               | 98          |

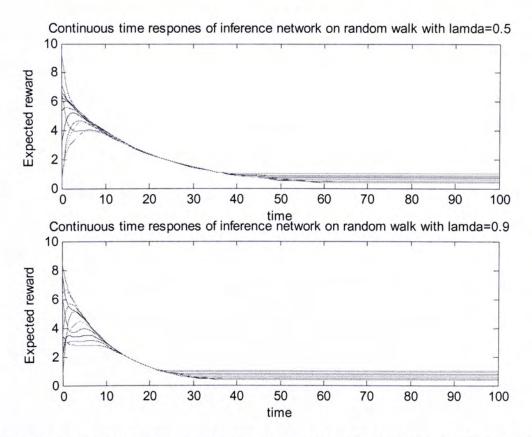

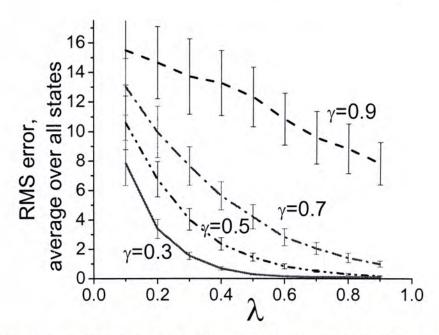

| Figure 5.14 | Convergence speed for continuous-time inference network for the rand       |             |

|             | problem                                                                    | 99          |

| Figure 5.15 | Comparison of convergence speed for continuous-time inference netwo      | ork for the |

|-------------|--------------------------------------------------------------------------|-------------|

|             | random walk problem                                                      | 100         |

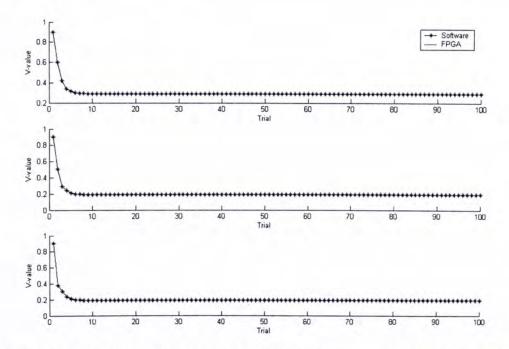

| Figure 5.16 | Verification of the network convergence on FPGAs implementation with     | referring   |

|             | to the software computation                                              | 101         |

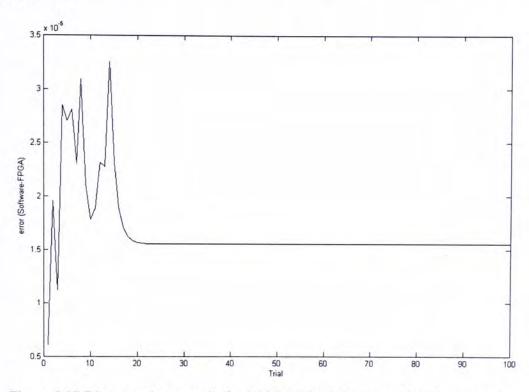

| Figure 5.17 | Bit truncation error in the 16-bit FPGA inference network computation    | 102         |

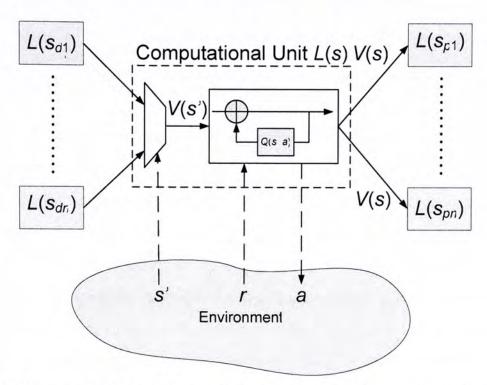

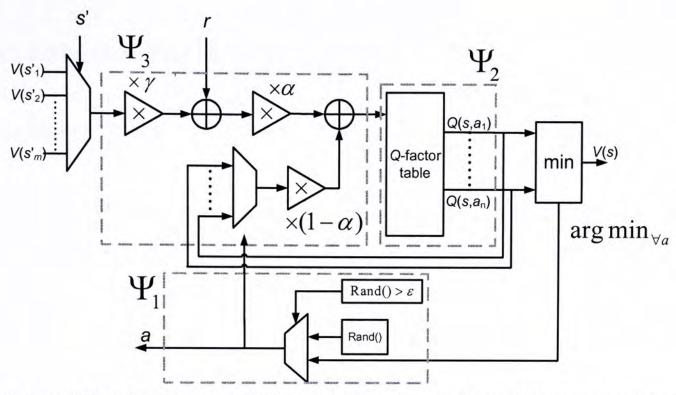

| Figure 6.1  | A typical computational unit in the learning network depicts the input a | and output  |

|             | of the learning network architecture                                     | 111         |

| Figure 6.2  | Schematic of a typical computational unit in Q-learning network          | 113         |

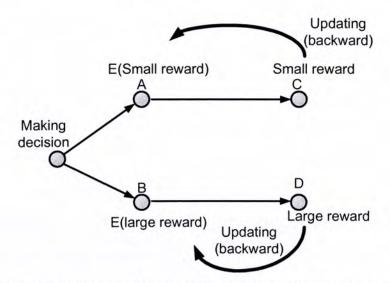

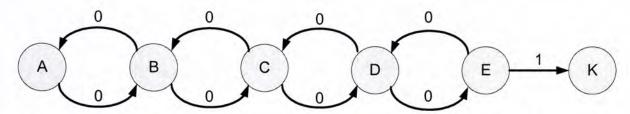

| Figure 6.3  | A small Markov process for generating random walks                       | 114         |

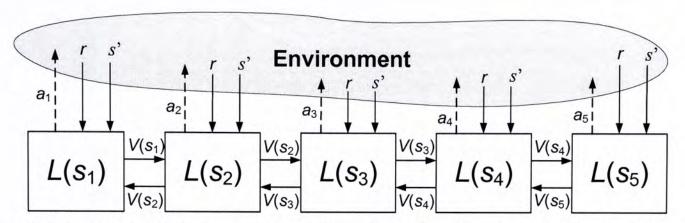

| Figure 6.4  | A distributed Q-learning framework to solve the random walk problem      | 115         |

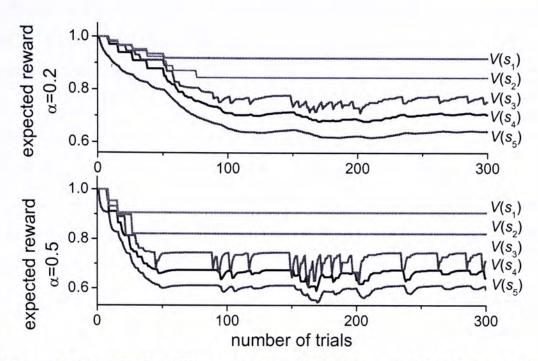

| Figure 6.5  | Learning curve of the distributed Q-learning network                     | 116         |

| Figure 6.6  | The flow-graph for stagecoach problem (Haykin 1999)                      | 116         |

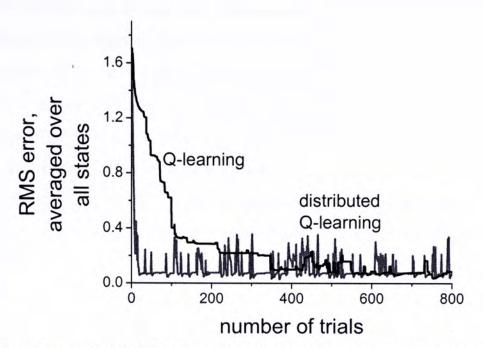

| Figure 6.7  | Comparison between typical Q-learning and the distributed Q-learning     | g network   |

|             | approach                                                                 | 118         |

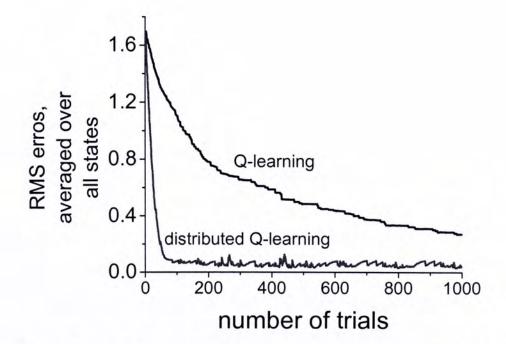

| Figure 6.8  | This is the experiment for comparison of convergence between Q-lea       | rning and   |

|             | distributed Q-learning the with smaller learning rate                    | 118         |

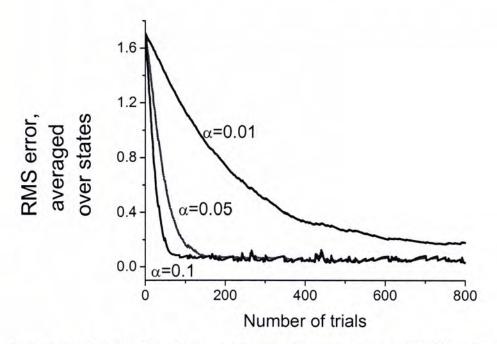

| Figure 6.9  | Convergence of the distributed Q-learning network can be varied with     | different   |

|             | learning rate                                                            | 119         |

| Figure 6.10 | For the Bellman inference network, the network needs longer converg      | ence time   |

|             | for a larger discount factor                                             | 120         |

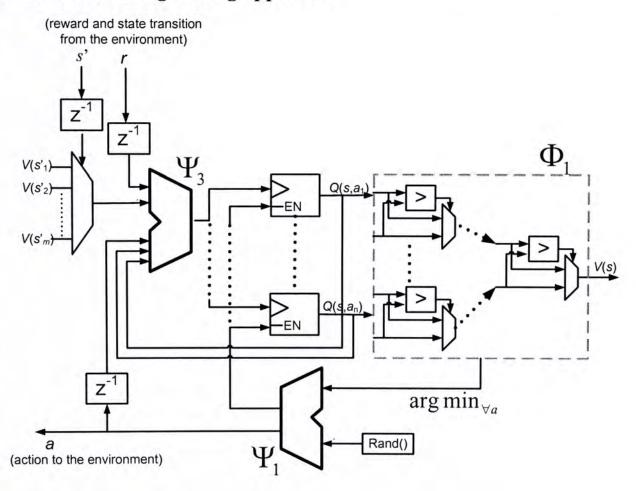

| Figure 6.11 | Schematic design for the computational unit which represents state s and | n actions   |

|             |                                                                          | 123         |

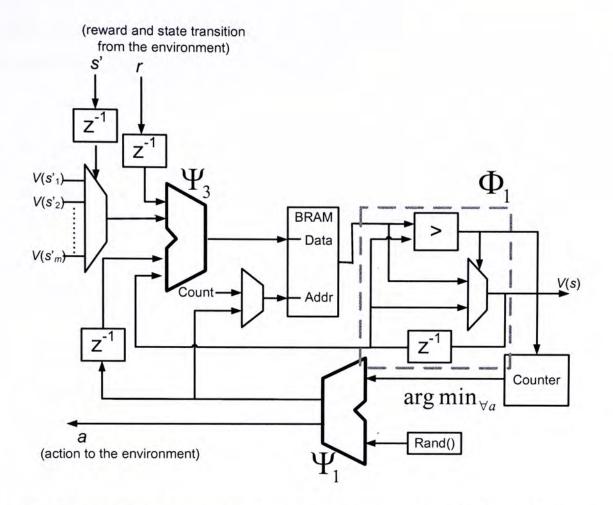

| Figure 6.12 | Q-factor table are mapping to the internal RAM and addressed by the act  | ion index   |

|             |                                                                          | 125         |

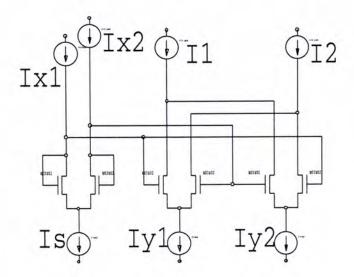

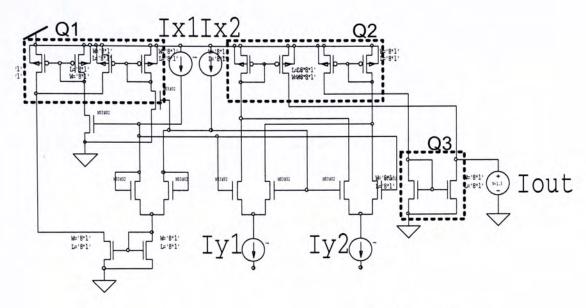

| Figure C.1. | Four-quadrant current-mode multiplier cell (Chan, Ling et al. 1995)      | 151         |

| Figure C.2. | Current-mode multiplier cell                                             | 152         |

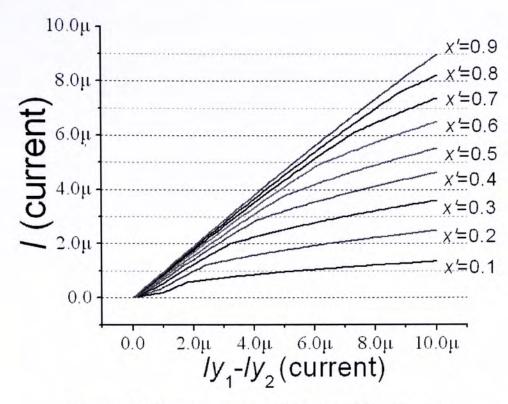

| Figure C.3  | Current-mode multiplier cell response                                    | 153         |

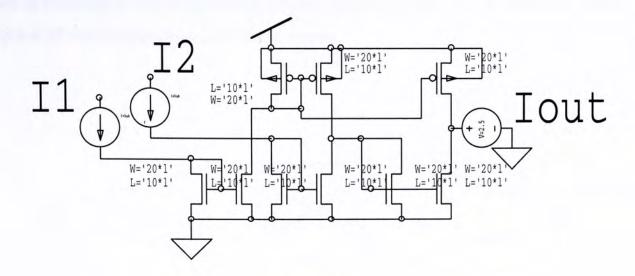

| Figure C.4  | Current-mode minimum circuit                                             | 154         |

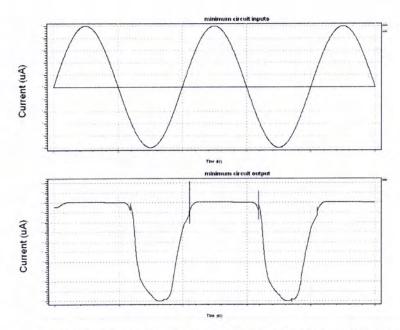

| Figure C.5  | Minimum circuit response to a sinusoid and constant inputs. The circuit  | delay can   |

|             | be found at around 80ns                                                  | 154         |

| Figure C 6  | A typical 6-state MDPs problem                                           | 155         |

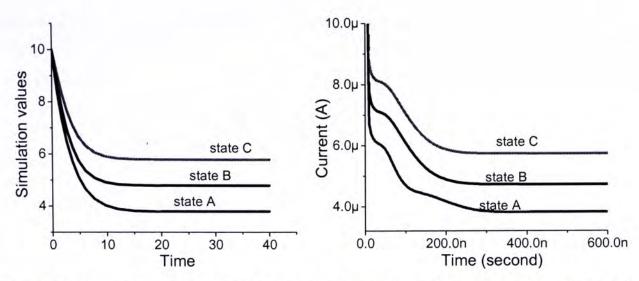

| Figure C.7  | (left) Numerical simulation of the 6-node single-destination inference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | network   |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|             | based on solving first-order ordinal differential equation (right) Inference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | network   |

|             | circuit simulation for the same problem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 156       |

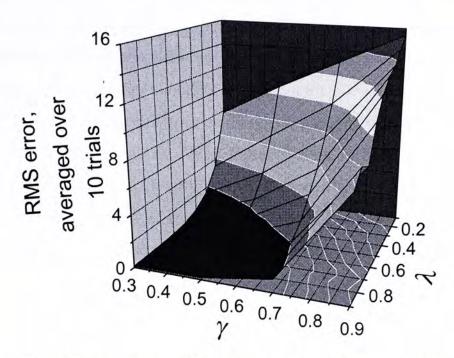

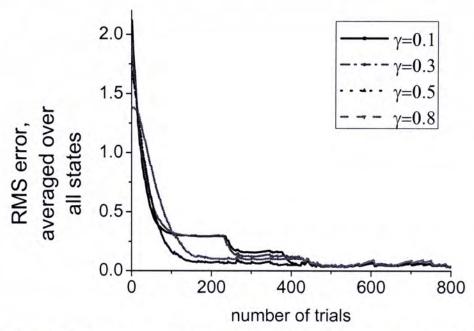

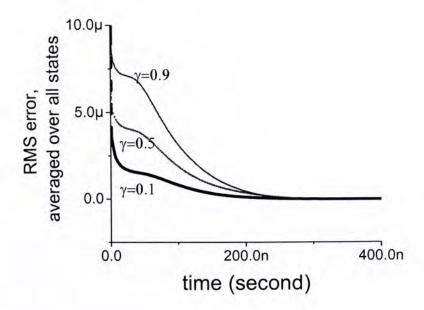

| Figure C.8  | Root-mean-square (RMS) errors with averaged over all states are compared to the compared to th | puted for |

|             | the inference network with different discount factor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 156       |

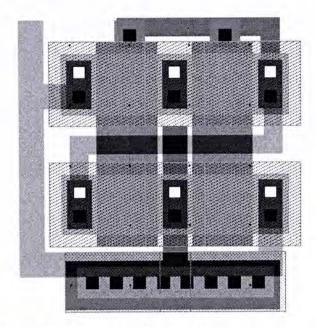

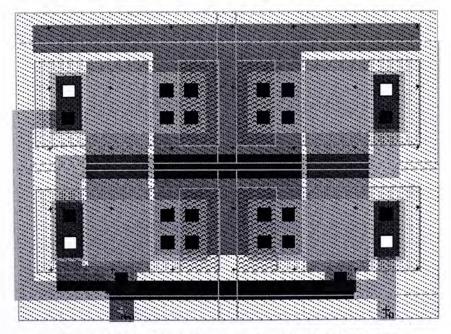

| Figure C.9  | Layout of a n-type current mirror                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 157       |

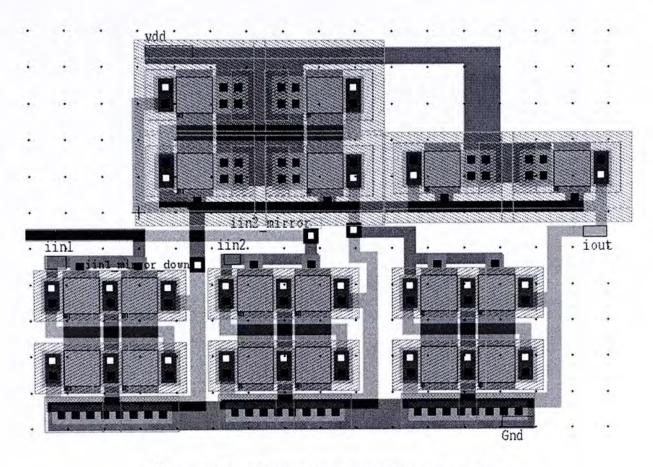

| Figure C.10 | Layout of a p-type current mirror                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 157       |

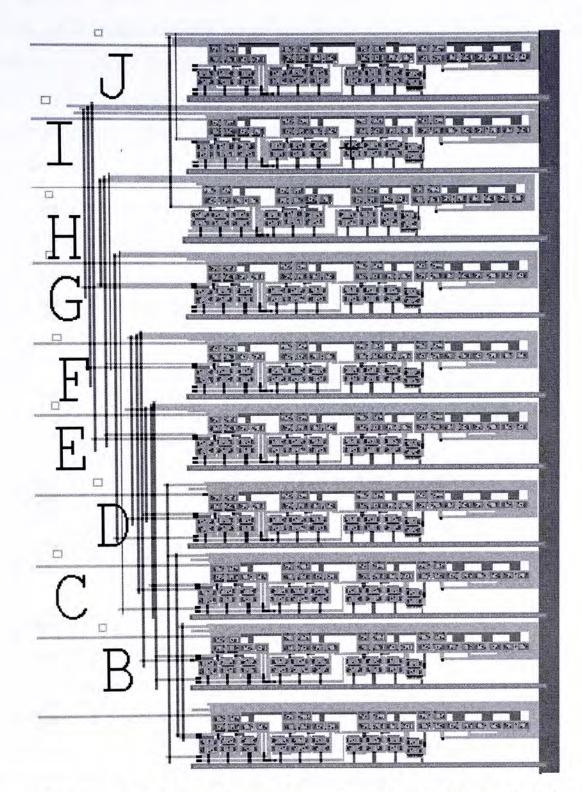

| Figure C.11 | The two-input minimum operator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 158       |

| Figure C.12 | Binary Relation Inference Network for 10-node Shortest Path Problem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 159       |

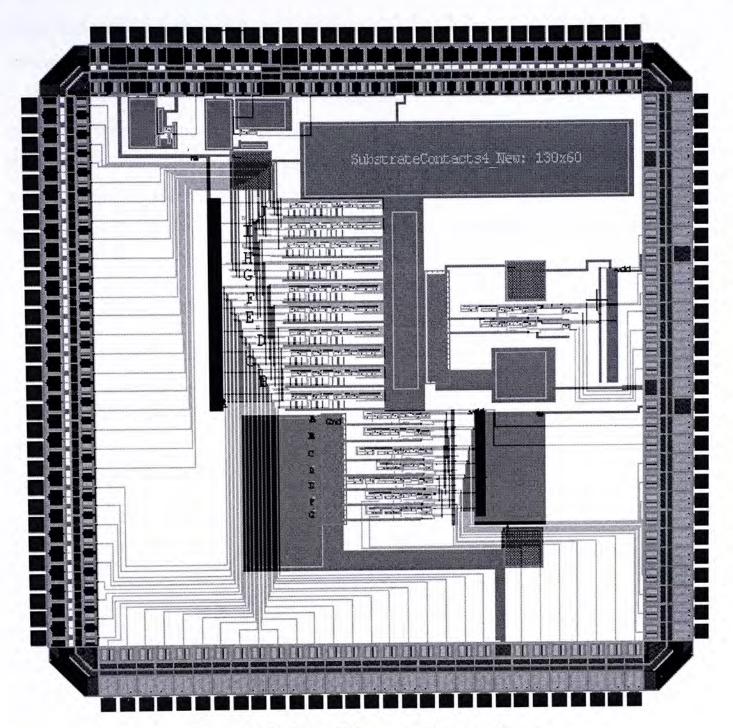

| Figure C.13 | Overall design with the Pad Frame                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 161       |

#### Acknowledgements

First of all, I would like to express my greatest gratitude to my supervisor, Professor Kai-Pui Lam, for his invaluable suggestions and comments on this thesis. More importantly, he had showed me the philosophy of engineering and the basic elements that a researcher should be equipped with during the last two years. Also, I have learnt a lot through our discussions on different research aspects. Specifically, I would also like to thank for his kind support and arrangement for my visiting study at MIT.

I would also like to express my gratefulness to Dr. Chi-Sang Poon, my supervisor when I was a visiting student at MIT. I was greatly impressed by his passionate and meticulous research attitude and his confident and cheerful personality. I have learnt a lot about research through our discussion. Also, I would like to thank Shirley, Guy, Yunguo, Chung, Armon, Dr. Song, Shawnon, Mary, Andy, Vera, Louis, Ricky and friends at Boston for their kind support and accompany at the time when I was in Boston. I would like to specially thank Guy Rathmuth for teaching me analog VLSI design, layout and fabrication technical techniques.

I greatly appreciate the members of my dissertation committee, Professor Peter Cheung, Professor Kam-Fai Wong and Professor Wai Lam for their useful feedback and suggestions.

I am also greatly indebted to Professor Shuzhong Zhang and Professor Duan Li on behalf of Department of Systems Engineering and Engineering Management to support my visiting study at MIT during my M.Phil study. I would also like to thank the graduate school of The Chinese University of Hong Kong to support the MIT visit.

My greatest gratitude goes to my parents for their endless love and encouragement. Most importantly, I would express my love to my girlfriend, Miss Ophelia Tsui for her love and support.

## **Table of Contents**

| Ab | stract                            |                                                  | i  |

|----|-----------------------------------|--------------------------------------------------|----|

| Li | st of Tabl                        | les                                              | iv |

| Li | st of Figu                        | res                                              | v  |

| Ac | knowled                           | gements                                          | ix |

| 1. | Introduc                          | ction                                            | 1  |

|    | 1.1 Bioinf                        | formatics                                        | 1  |

|    | 1.2 Neural                        | l Prosthetics                                    | 4  |

|    | 1.3 Learni                        | ing in Uncertainty                               | 5  |

|    | 1.4 The Fi                        | ield Programmable Gate Array (FPGAs)             | 7  |

|    | 1.5 Scope                         | of the Thesis                                    | 10 |

| 2. | A Hybri                           | id GA-DP Approach for Searching Equivalence Sets | 14 |

|    | 2.1 Introd                        | uction                                           | 16 |

|    | 2.2 Equiv                         | alence Set Criterion                             | 18 |

|    | 2.3 Genet                         | ic Algorithm and Dynamic Programming             | 19 |

|    | 2.3.1                             | Genetic Algorithm Formulation                    | 20 |

|    | 2.3.2                             | Bounded Mutation                                 | 21 |

|    | 2.3.3                             | Conditioned Crossover                            | 22 |

|    | 2.3.4                             | Implementation                                   | 22 |

|    | 2.4 FPGAs Implementation of GA-DP |                                                  | 24 |

|    | 2.4.1                             | System Overview                                  | 25 |

|    | 242                               | Parallel Computation for Transitive Closure      | 26 |

|    | 2.4.3       | Genetic Operation Realization                          | 28         |

|----|-------------|--------------------------------------------------------|------------|

|    | 2.5 Discuss | sion                                                   | 30         |

|    | 2.6 Limitat | ion and Future Work                                    | 33         |

|    | 2.7 Conclu  | sion                                                   | 34         |

|    |             |                                                        |            |

| 3. | An FP       | GA-based Architecture for Maximum-Likelihood           | Phylogeny  |

|    | Evaluati    | on                                                     | 35         |

|    | 3.1 Introdu | action                                                 | 36         |

|    | 3.2 Maxim   | um-Likelihood Model                                    | 39         |

|    | 3.3 Hardw   | are Mapping for Pruning Algorithm                      | 41         |

|    | 3.3.1       | Related Works                                          | 41         |

|    | 3.3.2       | Number Representation                                  | 42         |

|    | 3.3.3       | Binary Tree Representation                             | 43         |

|    | 3.3.4       | Binary Tree Traversal                                  | 45         |

|    | 3.3.5       | Maximum-Likelihood Evaluation Algorithm                | 46         |

|    | 3.4 System  | n Architecture                                         | 49         |

|    | 3.4.1       | Transition Probability Unit                            | 50         |

|    | 3.4.2       | State-Parallel Computation Unit                        | 51         |

|    | 3.4.3       | Error Computation                                      | 54         |

|    | 3.5 Discus  | esion                                                  | 56         |

|    | 3.5.1       | Hardware Resource Consumption                          | 56         |

|    | 3.5.2       | Delay Evaluation                                       | 57         |

|    | 3.6 Concl   | usion                                                  | 59         |

| 4  | . Field Pr  | ogrammable Gate Array Implementation of Neuronal l     | on Channel |

|    | Dynami      | cs                                                     | 61         |

|    | 4.1 Introd  | uction                                                 | 62         |

|    | 4.2 Backg   | ground                                                 | 63         |

|    | 4.2.1       | Analog VLSI Model for Hebbian Synapse                  | 63         |

|    | 122         | A Unifying Model of Bi-directional Synaptic Plasticity | 64         |

|    | 4.2.3      | Non-NMDA Receptor Channel Regulation                        | 65          |

|----|------------|-------------------------------------------------------------|-------------|

|    | 4.3 FPGA   | s Implementation                                            | 65          |

|    | 4.3.1      | FPGA Design Flow                                            | 65          |

|    | 4.3.2      | Digital Model of NMDA and AMPA receptors                    | 65          |

|    | 4.3.3      | Synapse Modification                                        | 67          |

|    | 4.4 Result | S                                                           | 68          |

|    | 4.4.1      | Simulation Results                                          | 68          |

|    | 4.5 Discus | ssion                                                       | 70          |

|    | 4.6 Conclu | asion                                                       | 71          |

|    |            |                                                             |             |

| 5. | Continu    | ous-Time and Discrete-Time Inference Networks for           | Distributed |

|    | Dynami     | c Programming                                               | 72          |

|    | 5.1 Introd | uction                                                      | 74          |

|    | 5.2 Backg  | round                                                       | 77          |

|    | 5.2.1      | Markov decision process (MDPs)                              | 78          |

|    | 5.2.2      | Learning in the MDPs                                        | 80          |

|    | 5.2.3      | Bellman Optimal Criterion                                   | 80          |

|    | 5.2.4      | Value Iteration                                             | 81          |

|    | 5.3 A Cor  | nputational Framework for Continuous-Time Inference Network | 82          |

|    | 5.3.1      | Binary Relation Inference Network                           | 83          |

|    | 5.3.2      | Binary Relation Inference Network for MDPs                  | 85          |

|    | 5.3.3      | Continuous-Time Inference Network for MDPs                  | 87          |

|    | 5.4 Conv   | ergence Consideration                                       | 88          |

|    | 5.5 Nume   | erical Simulation                                           | 90          |

|    | 5.5.1      | Example 1: Random Walk                                      | 90          |

|    | 5.5.2      | Example 2: Random Walk on a Grid                            | 94          |

|    | 5.5.3      | Example 3: Stochastic Shortest Path Problem                 | 97          |

|    | 5.5.4      | Relationships Between $\lambda$ and $\gamma$                | 99          |

|    | 5.6 Discr  | ete-Time Inference Network                                  | 100         |

|    | 5.6.1      | Results                                                     | 101         |

|    | 5.7 Conc   | lusion                                                      | 102         |

| 6. | On Dist     | ributed <i>Q</i> -Learning Network          | 104 |

|----|-------------|---------------------------------------------|-----|

|    | 6.1 Introd  | luction                                     | 105 |

|    | 6.2 Distri  | buted Q-Learning Network                    | 108 |

|    | 6.2.1       | Distributed Q-Learning Network              | 109 |

|    | 6.2.2       | Q-Learning Network Architecture             | 111 |

|    | 6.3 Exper   | rimental Results                            | 114 |

|    | 6.3.1       | Random Walk                                 | 114 |

|    | 6.3.2       | The Shortest Path Problem                   | 116 |

|    | 6.4 Discu   | assion                                      | 120 |

|    | 6.4.1       | Related Work                                | 121 |

|    | 6.5 FPGA    | As Implementation                           | 122 |

|    | 6.5.1       | Distributed Registering Approach            | 123 |

|    | 6.5.2       | Serial BRAM Storing Approach                | 124 |

|    | 6.5.3       | Comparison                                  | 125 |

|    | 6.5.4       | Discussion                                  | 127 |

|    | 6.6 Conc    | lusion                                      | 128 |

| 7. | Summa       | nry                                         | 129 |

| В  | ibliograp   | ohy                                         | 132 |

| A  | ppendix     |                                             |     |

| A  | . Simplific | ed Floating-Point Arithmetic                | 143 |

| В  | . Logarith  | nm, Exponential and Division Implementation | 144 |

|    | B.1 Intro   | oduction                                    | 144 |

|    | B.2 App     | roximation Scheme                           | 145 |

|    | B.2.1       | l Logarithm                                 | 145 |

|    | B.2.2       | 2 Exponentiation                            | 147 |

|    | B.2.3       | 3 Division                                  | 148 |

| 0  | . Analog    | VLSI Implementation                         | 150 |

| C.1 Site Function                     | 150 |

|---------------------------------------|-----|

| C.1.1 Multiplication Cell             | 150 |

| C.2 The Unit Function                 | 153 |

| C.3 The Inference Network Computation | 154 |

| C.4Layout                             | 157 |

| C.5 Fabrication                       | 159 |

| C.5.1 Testing and Characterization    | 161 |

who as a rule have vesey measurement also at our care

## Chapter 1

#### Introduction

#### 1.1 Bioinformatics

February 2001, it was the landmark of human technological advance, the remarkable success of Human Genome Project (Baltimore 2001; Consortium 2001; Venter et al. 2001), by raveling the underpinning of numerous genomes and DNA sequences from microbes to plants to mammals, have created a revolution in biology that has no equal in the history of science. Genomics is now the starting point for studies in biology, making tractable for the first time a systematic and deep understanding of life's process. While stunning in the impact of the human genome project, our foray into genomes has touched upon only the tiniest fraction of life on earth. The diversity and range of the environment adaptations of microbes mean that they long ago evolved solutions to many problems that scientists must now address. Comprising about fifty percent of the earth's biomass (Whitman, Coleman et al. 1998), microbes are in consequence the foundation of the biosphere, controlling earth's biogeochemical cycles and affecting the productivity of the soil, quality of water, and global climate. The desire and aspiration of understanding the life in the microbe's would, leads to the launch of another project, Genome to Life, with scale equivalent to the Human Genome Project (Frazier, Thomassen et al. 2003).

The advent of the Human Genome Project and Genome to Life projects have impacted all of the biomedical research and brought the exhilaration and celebration of the entering of postgenomic era. However, the development of large sets of genomic data has challenged biologists who as a rule have never encountered data of this scale. The secrets of life are yet to be deciphered. Implementations of conventional statistical techniques have brought a level of order and results to the biologist's desktop. But significant problems remain to be solved. The challenge remains to extract the maximum useful information from genomic data. Consider biology is awash by the amount of data and its complexity, which demands increasing computation power. In addition to generation new data from pipelining biotechnological machineries, innovations and implementations of computing infrastructure to support the computational analysis of large-scale data set, complex model simulations and achieving effective access to biological data are equally important.

Starting from gene sequencing, the combination of DNA base pairs of thousands genes can be identified, and clues for a variety of structural and functional features might be provided. However, to our knowledge, only molecular machinery of the cell can interpret the encrypted sequences to determine the complex biochemical mechanism and to define the organism behavior (D'haeseleer, Liang et al. 2000). Analysis of genomic sequences aims to understand mechanisms of molecular machinery. Data mining and modeling approaches try to conceptualize and unravel the functional relationships implicitly indicated in the genetic data set. Clustering algorithms are typically popular on automatically grouping of genes based on their expression measure and prior knowledge of the biological experiments. Some of these techniques, such as Singular Value Decomposition (SVD) for genes clustering (Alter, Brown et al. 2000; Wall, Dyck et al. 2001), expectation-maximization algorithm to cluster yeast data (Mjolsness, Mann et al. 1999), standard agglomerative hierarchical clustering algorithm for average-linkage analysis on gene expression data (Eisen, Spellman et al. 1998), are considered as popular unsupervised learning methods, from the engineering perspective.

Still, clustering approach typically only tells us correlative information, but not causality and regulating models about genes, though it is a relatively easy way to extract useful information out of large-scale gene expression data sets (D'haeseleer, Liang et al. 2000). More advance analysis aims to infer causal connections between genes and network dynamics. One way to make progress in understanding the principles of network dynamic is to radically simplify the individual molecular interactions, and focus in the collective outcome (D'haeseleer, Liang et al. 2000; Maki, Tominaga et al. 2001). Boolean network (Kauffman 1969) represents such a simplification: each gene is considered as a binary variable – either ON or OFF – regulated by other genes through logical or Boolean functions. Although there are effective measurements of

genetic data from the microarray experiments, computational analysis is complex and is a serious bottleneck in the study of genetic network using contemporary computing technology. New computational paradigm of massive parallel and high performance computers are therefore in great demand.

Among the computational genomic examples, evolutionary studied of different organisms, through the judicious evaluation of DNA or protein sequences, is still the main stream in biology. This is because an organism is best understood in the light of its evolutionary relationship to other organisms (Karp 2003). Comparative study based on the theory of evolution can be traced back to Charles Darwin (Darwin 1929). Instead of comparing the phenotype, such as size of eye ball, or palm and height, nowadays, metrics based on DNA sequences are applied for evolutionary studies. Computational model and methods to infer (or reconstruct) the evolutionary history of organism, namely phylogentic tree reconstruction, becomes everyday practices of biologists in many laboratories.

Phylogenetic tree study is one of the most fundamental bases in biology. It has been shown that phylogeny analysis has its profound implication in pharmaceutical research which focus on the evolution of virus for the purposes of drug-resistance prediction, immune-escape of mutations (Rambaut, Posasa et al. 2004), etc. Also the strong drug adaptation of HIV virus can be explained by its fast mutation rate. In (Worobey, Santiago et al. 2004), the origin of HIV is using meticulous phylogeny analysis. To decipher HIV interaction with the immune system and to develop effective control strategies, close relatives of the virus are studied using phylogeny (Rambaut, Posasa et al. 2004). Besides virology and pharmaceutical applications of phylogeny, recently, it has been shown that evolutionary studies of species can benefit the genomic studied and the regulatory genetic network prediction as well (Eisen and Fraser 2003).

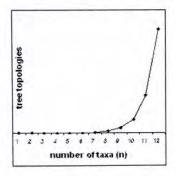

Phylogenetic tree reconstruction is computational intensive. Especially for recent advance probabilistic-based model, phylogeny computation becomes a challenging engineering issue and considered intractable for desktop computers. It is a difficult task to find the optimal solution based on the maximum likelihood criterion, simply because of the exponentially growth of the possible tree topologies with the number of taxa<sup>1</sup>. The possible unrooted, bifurcating n-taxa tree topologies is corresponding to nearly 16 billion different trees for 12 taxa and  $3\times10^{84}$  trees for 55 taxa. The optimal phylogenetic tree search problem is regarded as NP-hard (Lemmon and

<sup>&</sup>lt;sup>1</sup> Taxa is a general term referring to any kind of taxonomic unit including DNA sequences and nucleotide site.

Milinkovitch 2002) which implies that no known algorithm can find the optimal solution in polynomial time. Heuristics are often used to search the near optimal tree within a reasonable time, which essentially applies hill climbing or genetic algorithm approaches as the search strategies (Strimmer and Haeseler 1996; Swofford, Olsen et al. 1996; Lewis 1998; Lemmon and Milinkovitch 2002). The heuristics can reduce the search space for a near-optimal solution. The tree evaluation is computationally demanding and is used repeatedly in the search. In general, the computational cost of likelihood, accounts for the greatest portion of the execution time (i.e. 95% in sequential execution) (Stamatakis, Ludwig et al. 2002). The computational intensive fixed-topology tree evaluation is time consuming and this would result in the reduction of the overall search speed.

#### 1.2 Neural Prosthetics

In parallel with the success of computational genomics, neural science, is another important subject in biology and medical science. Tremendous efforts have been put on innovation and development in this area in the past two decades (Kandel, Schwartz et al. 2000). One of the frontiers is repair of the human brain: developing prosthetics for the central nervous systems to replace higher thought processes that have been lost due to damage or disease. The type of neural prosthetic that performs or assists a cognitive function is qualitatively different from the cochlear implant or artificial retina, in which transducer converts physical energy from the environment into electrical stimulation or nerve fibers (Loeb 1990), and qualitatively different from functional electrical stimulation (FES), in which preprogrammed electrical stimulation protocols are used to activate muscular movement (Mauritz and Peckham 1987). Although there is still a long way before the ultimate goal is achieved, neural prosthetic silicon neurons would have functional properties specific to those of the damaged neurons, and would both receive as inputs and send as output electrical activities to regions of the brain with which the damaged region previously communicated (Berger et. al.2001).

Real-time simulation is an important step in the implementation of brain-machine interaction (BMI), and is fundamental to several emerging neuromorphic, biomimetic and prosthetics applications. For example, in electrophysiological studies of neuronal membrane properties using the dynamic clamp technique (Sharp et. al. 1993; Butera et. al. 2004), a digital computer is used

to generate virtual ion channel conductance which continuously interacts with a biological neuron in real time. Such software-based experimental applications are highly computation-intensive and often require judicious choice of operating system (Sharp et. al. 1993) and numerical procedures (Butera et. al. 2004) to improve the computational speed and flexibility. A hardware-based, application-specific implementation of the dynamic clamp technique would circumvent the limitations of general-purpose computers.

Another example of neural prosthetics brain-machine-interface (BMI) is real-time neuronal ion channel dynamics computation. For example, a robotic arm controlled by central brain activities have been shown to be capable of generating complex motions (Taylor 2002), and such capability may find important applications in patients with Parkinson's disease, Essential Tremor, and dystonia (Isaacs et. al. 2000). One such technology is neuromorphic analog VLSI circuits (Mead 1990). Towards this end, Rachmuth and Poon have previously proposed neuromorphic Hebbian synapse design using analog CMOS circuits operating in subthreshold regime (Rachmuth and Poon 2003; Rachmuth and Poon 2004). However, the relatively long design and fabrication cycle for analog CMOS circuits is a bottleneck in the development of such devices.

#### 1.3 Learning in Uncertainty

Besides the real-time requirement of the brain-machine-interface application, rapid learning under stochastic and uncertainty is also important. This is widely used in knowledge acquisition for making time-critical decision in real-time. Autonomous robots and vehicles are assigned to perform missions in highly hazardous and extreme environments. In most of the time, good path planning and quick reaction to avoid dangerous spots can increase the chance to reach the target or accomplish a mission, as in the cases of gathering scientific information from a distant planets or searching and rescuing life from a mass casualty incident site (Team 1997; Volpe, Estlin et al. 2000; Casper and Murphy 2003). One of the examples is the design of Mars rover, which is used for exploration of Mars. Robust navigation through rocky terrains by small mobile robots is challenging as little information about the uncertain environment at extreme conditions and there is only limited number of communication with earth controller, i.e. twice a day (Volpe, Estlin et al. 2000). Highly autonomous robots with intelligent and capability of learning and making decision for path planning, execution are acquired for maximizing scientific data return from the

Mars exploration mission. Sojourner, the Mars Pathfinder rover was sent to Mars making observations on the rocks and other deposits at the Ares site to collect information and prior knowledge to increase the chance for latter rover success (Rover Team 1997).

Since the environment is highly dynamic and unpredictable, path planning relying only on the prior knowledge is risky. Several real-time and on-line planning navigation techniques are proposed to enhance the intelligence and on-line decision making capability of the rover for the coming projects (Williams, Kim et al. 2001). On the other hand, exploration of the surface of a distant planet by networks of autonomous cooperating vehicles would be an effective alternative approach. Collective information from a distributed environment would increase the content of the information and increase the chance of survival of the autonomous robots. Given this option, distributed approaches for rapid learning in an uncertain environment and for making real-time decision is important (Williams, Kim et al. 2001).

Among the examples of real-time path planning and decision making is the development of intelligent Unmanned Aerial Vehicles (UAVs) for future combats to reduce human causalities. The major challenge for intelligent UAVs development is path planning in uncertain and even adversarial environments, for which the objective is to complete the given mission, to arrive at the given target within a pre-specified time, while maximizing the safety of the UAVs. The problem can be modeled as a typical stochastic learning and sequential decision problem (Jun and D'Andrea 2003). However, in practice, UAV path planning is difficult because of two main reasons. Firstly, in the adversarial environment, information is always incomplete and is highly uncertain. It is difficult to acquire knowledge to decide on a reasonably well trajectory of the flight. Secondly, the computational load grows quickly as the number of radar sites increases. Delay in decision making, due to heavy computational burden, would be disastrous. The distributed and parallel computational learning architecture could circumvent the limitation of the sequential computation machineries (Tin 2004).

#### 1.4 The Field Programmable Gate Array (FPGAs)

The latest high-end microprocessors utilize 90nm complementary metal oxide semiconductor (CMOS) technology with 64-bit data bus, multiple functional units and megabytes of integrated

cache packed on a single die with up to a hundred million transistors operations at clock frequencies over 3 GHz (Intel 2005). Although the computational abilities of these advanced microprocessors are useful to a wide range of civil, business and engineering applications, they cannot always fulfill the needs of real-time signal processing, high-throughput computational genomic systems and large-scale optimization, which require even higher computational power. High power requirements and large heat dissipation are also shortcomings of microprocessors. Essentially, the limitation of microprocessor system is due to the nature that software programs executing follows a sequential operation within a microprocessor (Leong 2001). In contrast, hardware implementation would utilize hardware parallelism and dedicated logic leading to performance improvement over a microprocessor. The dedicated hardware architecture can be designed to be more power and computational efficient.

Field Programmable Gate Array (FPGAs) becomes unique, power efficient, robust and high performance computation engine. Originally FPGAs simply regarded as a fast prototyping tool for microprocessor design in early 80's. Evolution of silicon reconfiguration technology leads to revolutionary replacement of legacy microcontroller. When comparing to traditional microprocessors, the FPGA allow parallel implementation of computational logics and arithmetic. Given a judicious design, throughput of the applications can be greatly enhanced. For example, FPGA-based computing platform called a Programmable Active Memory (PAM) machine (Bertin and Touati 1994; Mencer, Morf et al. 1998) achieved the fastest reported encryption/decryption rate in history. In their work, it has been shown that an implementation of the International Data Encryption Algorithm (IDEA) on a Xilinx Virtex-XCV300 FPGA achieved 10 times faster than software implementation on a Sun Enterprise E4500 machine equipped with twelve 400 MHz processors. In (Trimberger, Pang et al. 2003), implementation of the Data Encryption Standard (DES) on a Xilinx XCV-300 device achieved 12Gbits/sec encryption rate while only 9.3Gbits/sec was reported in the fastest ASIC implementation.

The technological advancement of FPGAs does not limited to civil applications. but aeronautic and military applications are abounded. Mars Exploration Rover mission utilizes Xilinx FPGAs in critical applications for both the lander and rover vehicles. According to NASA's Jet Propulsion Laboratory in Pasadena, the Spirit Mars Exploration Rover (MER) launched June 10, 2003 and the Opportunity MER launched July 7, 2003 employed some of the most advanced radiation tolerant Xilinx Virtex FPGAs once they reached Mars. The Xilinx

devices was used to control the pyrotechnic devices on the lander, and several motor control functions on the rover, including controllers for the wheels, steering, and antenna gimbals (Xilinx 2003). In (Burke, Cozy et al. 2004), it was found that the operation of FPGAs, both Actel and Xilinx parts, is in good condition at very low temperatures e.g. down to -165°C. Investigation and implementation of control logics using FPGAs would greatly enhance its robustness and speedup the development cycle. This would greatly benefit the autonomous robotic and aeronautic machineries design application for distant planet exploration.

The capacity, functionalities and efficiency of FPGAs technologies does not stop evolving in recent years. The earliest architecture XC4000 FPGAs had up to 180 thousands system gates. Programmable floating gate transistor can be programmed becomes non-volatile memory together with programmable switches form a network of programmable logics. Thousands of logic operators could be connected together. Early architecture performance was limited by its capacity. The later Xilinx Virtex series FPGAs had up to 4 millions system gates and 832 Kbytes embedded memory. It was the first reconfigurable architecture with embedded memories, which had greatly enhanced the competitiveness of FPGA to other signal processing and ASIC processors. Later, Virtex-II series architectures were proposed. It was considered that signal processing performance required large volume of arithmetic operator. Introduction of 18-bit embedded multipliers increased the computational speed of the application. Further, it facilitated higher robustness, power efficiency and logic utilization. More recently, Virtex-II Pro and Virtex-4 FPGAs series enabled with IBM PowerPC immersed into the FPGAs fabric while high performance internal bus architecture dedicating for the communication between the distributed logics, embedded memory, multipliers and the embedded microprocessor (Xilinx 2002). The platform offers great flexibility for users to define task partitioning between the FPGA hardware logic and software running on the embedded microprocessor. It also provides a tightly-coupled HW/SW computing environment and supports a high-speed internal bus, which significantly reduces communication overhead. A central bus infrastructure with dedicated sub-buses and interconnected bridges is essential for providing a high throughput communication gateway connecting the microprocessor and FPGA. More specifically in (IBM 2002), the PowerPC core accesses high-speed system resources (such as instructions and data) through the Processor Local Bus (PLB); and On-Chip Peripheral Bus (OPB) provides the connectivity to the FPGA. As

integrated circuit technology continue to improve at a noticeable rate, one could be assured that even more powerful FPGA devices would be available in the future.

Accumulation of biological data, leads scientists and biologists to look for effective alternatives to process the stacking data and to circumvent the computational problem attributed to desktop computers. FPGAs, on the other hand, would be an effective implementation platform for tackling the computational problem by its distributed architecture and effective use of parallelism. It is only the beginning to apply FPGA technology on biomedical, bioinformatics and even neural prosthetics. Pioneer TimeLogic Inc. commercially provides solutions to the problem of searching genetic databases (TimeLogic 2002), in which 160 FPGAs are used to form a powerful cluster of computational system. Although the system is only one fifth of the computational speed of the machines used in the Human Genome Project, it is more power efficient and inexpensive. (Guccione and Keller 2002) found that, over ten times acceleration achieved for using more advance FPGA processors. In that case 4000 processing units were used to match gene sequences in parallel. This showed that FPGAs was an excellent solution to the bioinformatics applications. Few of the latest achievements in DNA sequence alignment were presented in (Yu, Kwong et al. 2003; Dydek and Bala 2004), where different systolic array parallelization schemes were adopted to gain higher acceleration.

In addition, FPGA implementation is an effective solution to neural prosthetics and reinforcement learning problems mentioned above. Based on the programmable distributed logic cells and other embedded resources, algorithms can be mapped to FPGA. The reconfigurable nature of FPGAs enables multiple designs to be programmed on the same hardware device at different times. Thus the costly design and fabrication process delay associated with Very Large Scale Integration (VLSI) design are avoided. The continuous improvement in silicon technology offers faster and larger FPGA devices over time. Design based on FPGA is versatile. With improved density and shorter design time in the future, designers may implement more sophisticated algorithms leading to further improvement in system performance.

Unfortunately, the FPGAs design and mapping of algorithms to FPGAs are always not straightforward. It is challenging to have efficient design with good mapping from the algorithms to the hardware logics. This is always due to the design complexity and the algorithm complexity. Efficient and simple algorithms are not necessarily efficient to be executed in hardware with trivial implementation. Besides, one difficulty in designing FPGA applications is that hardware

resources are strictly limited. Hardware area efficiency is still a major issue, even though density of FPGA devices has improved substantially. Very often, performance is sacrificed to fit a design into a given FPGA device. It is important to able to explore the tradeoff between area and performance, and a single design description can lead to multiple implementations with area and performance tradeoff.

#### 1.5 Scope of the Thesis

The objective of this thesis is to investigate and develop efficient methods to address the computational challenges, from bioinformatics, neural prosthetics problems to theoretical reinforcement learning implementation in a distributed environment. Our goal are to explore new applications and to improve the performance based on software-based implementation methodologies and sequential computational framework.

Reverse engineering of genetic network is one of the greatest challenges in today's bioinformatics. In (Akutsu, Kuhara et al. 1998; Maki, Tominaga et al. 2001; Kimura, Hatakeyama et al. 2003), the idea of partitioning genes into equivalence sets, from a large genetic network and with reference to a Boolean matrix obtained from the gene expression patterns resulted from microarray experiments was proposed. The equivalence sets facilitate effective grouping of "closed-loop" genes, and can be derived from transitive-closure computation. Subsequently, dynamic models are estimated from the identified equivalence sets for capturing network behavior. Therefore, computation of the transitive-closure for the equivalence sets is as an important step for building static and dynamic models of genetic network (Maki, Tominaga et al. 2001). In Chapter 2, we present a hybrid method, which integrates genetic algorithm (GA) with dynamic programming approach address the computational intensive equivalence sets search problem. This approach converts a high dimension computation problem into a search problem which is solved by GA using dynamic programming. The computation of transitive-closure forms the basic fitness evaluation in GA. This is used for selecting candidate chromosomes generated by applying basic genetic operators. Small transitive-closure equivalence sets can be found from large genetic network with less computational effort. We also offer an efficient Field Programmable Gate Array (FPGAs) implementation platform for the required computation. Application of FPGA processors for

searching equivalence set minimizes experimental delay due to computational intensive data analysis.

Chapter 3 addresses the computational problem in the evolutionary study of DNA sequences. We specifically study different approaches to speedup the phylogenetic tree reconstruction. Phylogeny (phylogenetic tree) is a meaningful representation for the evolutionary history of different organisms and it had been shown tremendous impact to the biological and medical science. Due to the exponentially increasing search space for the optimal Maximum Likelihood (ML) criterion, the phylogeny inference is classified as NP-hard. Heuristic search makes use of the likelihood evaluation function extensively to give score for the candidate solutions. This tree evaluation process is a critical but computationally demanding task. We present the design of a dedicated FPGA-based hardware system that performs ML tree evaluation in a more efficient manner than a software implementation. With simplification of the ML function, a recursive ML evaluation algorithm is proposed. This algorithm can be mapped to FPGAs using digital logics. In addition, based on the DNA state and nucleotide site independence, fine-grained parallelism is introduced into the proposed FPGA-based architecture to provide significant speed-up.

In Chapter 4, we study the FPGAs implementation for one of the basic mechanisms in neural prosthetics. Neuron-machine interfaces such as dynamic clamp and brain-implantable neuro-prosthetic devices require real-time simulations of neuronal ion channel dynamics. We present an FPGA design of a neuromorphic Hebbian synapse, which mimics NMDA and non-NMDA ion channel dynamics observed experimentally in hippocampal neurons. The proposed design can be readily extended to high-speed implementations of dynamic clamp and neuro-prosthetics for replacements of damaged neurons in the brain.