# UNIFIED ON-CHIP MULTI-LEVEL CACHE MANAGEMENT SCHEME USING PROCESSOR OPCODES AND ADDRESSING

MODES

By Stephen Siu-ming Wong

Supervised By Dr. Chi-hung Chi

Submitted to the Dept. of Computer Science & Engineering

In Partial Fulfillment of the Requirements for the Degree of

Master of Philosophy

At the Chinese University of Hong Kong

June 1996

# Abstract

As new generations of microprocessors are to be developed, the speed gap between main memory and new processors is widened. To bridge the gap, fast but small size of cache memory was introduced. When the feature size of transistor in microprocessor is reduced, CPU designers can pack the cache memory into the same silicon die as the processor, they labeled the cache memory as first level (L1) cache. On the circuit board holding the microprocessor, system designers added another level of cache memory on the circuit board to reduce apparent memory latency, and it is labeled second level (L2) cache. The next logical step should be the integration of second level cache on the same chip as the microprocessor.

The conventional usage of cache memory is by storing frequently used data in the cache, and when later retrieval is performed, the speed will be that of the fast cache memory, instead of the slower main memory. This behavior is termed "on-demand fetch". The saving in waiting time occurs only when the same data is referenced the second and later times.

Rather than fetching on-demand, there are useful signals on the CPU which both the first and second level caches can make use of, in order to make predictions about future memory references of the processor, the cache memory can fetch those data from the main memory in advance, this introduces the notion of Cache Prefetching. Prefetching is risky, as if the prefetch is wrong, it does not only cost a waste of time for the prefetch, but, the wrong prefetch may replace a piece of useful data that will be referenced by the processor later, because the cache memory is small in size. Therefore, an accurate prefetching is desirable. The reference pattern of the processor ultimately depends on the running program, therefore, with sufficient information from the running program, the cache system should be able to make accurate prefetching.

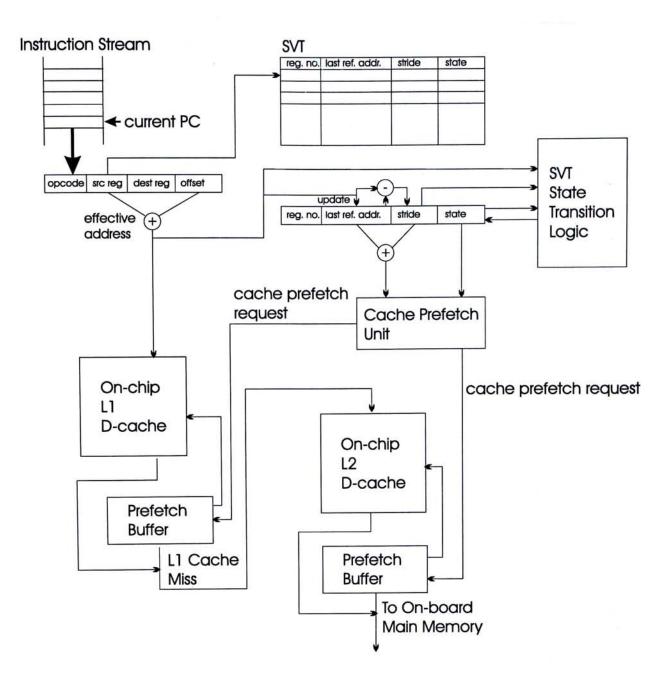

In this dissertation, 13 different prefetching algorithms would be presented, among them five are new prefetching algorithms proposed in this thesis, with the reminding eight were proposed by other papers. One of the new prefetching algorithms proposed in this dissertation is Source Index Register Prefetching, it is a hardware prefetching algorithm which does not depend on the support of language compiler. Source Index Register Prefetching has similar or better performance compare with one of the regarded hardware prefetching algorithms proposed by Dr. Chen Tien-Fu and others in [CB92] called RPT. Source Index Register Prefetching has a substantial improvement on hardware overhead compare with RPT. One of the major achievements from the Source Index Register Prefetching is the choice of index register in a machine instruction as index to the stride value table, instead of instruction address as used by the RPT. The selection of index register in Source Index Register Prefetching lowers the hardware overhead and guarantees the good performance of that algorithm.

The memory access time by using the new prefetching algorithms can be reduced by more than 90% of the "on-demand fetch". The average saving in memory access time for the new prefetching algorithms is around 30%.

Another major achievement in this study was the inclusion of Cache Line Concept in managing on-chip level one and level two cache. The use of line concept takes into consideration the different block sizes as commonly found on L1 and L2 cache. By using a single prefetching unit, and combined with Cache Line Concept, the prefetch behaviors for L1 and L2 cache will be different, and they are tuned to the parameters for that particular level of cache. The single cache management unit actually ties both L1 and L2 cache together, and they work coherently to serve data that will be referenced in a short span of time.

The unified cache management is beneficial to CPU designers as the prefetching algorithm used depends on CPU signals, that electrical loading is limited. One cache management unit means there will be just a single set of CPU signals running from the CPU core to the unit, and the inclusion of second level cache will not add further electrical loading to the CPU core logic.

# Acknowledgment

I must express my gratitude to my advisor, Dr. C H Chi, for his support and guidance throughout my course of research. Dr. Chi introduced me to the wonderland of Computer Architecture, and the realm of cache world in particular. Without Dr. Chi's valuable inspiration, encouragement and insight, I would not be able to complete this study. I would also thank Dr. C Lu and Dr. G Young, who are my markers, Prof. Zheng Wei-min in Tsinghua University, who is the external examiner of my thesis. They have given me helpful suggestions and constructive criticism in polishing my dissertation.

Without fellow graduate students Vincent Yiu, Siu-chung Lau, Wai-wai Chan, Xue-jie Zhang, Siu-ching Sze, and many others, my college life would not be as memorable. I would never forget the very useful brain storming sessions with Wai-wai Chan, the happy atmosphere created by Vincent, Chung, and Siu-ching. Without Xue-jie Zhang, I would not have chance to learn a bit in Mandarin.

I have to thank Dr. P C Wong in the department of Information Engineering, although we did not meet very often, Dr. Wong was the one who activated me to think about the possibility to pursue postgraduate study.

Lastly, I have to give special thanks to my parents, Mika and her parents for their love and support. They are so thoughtful to support me to go back to school. Without them, I would not be able to put down my burdens and go one step further to my goal.

# Contents

| 1 | Intr           | roduction 1                                                                                    |  |  |

|---|----------------|------------------------------------------------------------------------------------------------|--|--|

|   | 1.1            | Cache Memory                                                                                   |  |  |

|   | 1.2            | System Performance                                                                             |  |  |

|   | 1.3            | Cache Performance                                                                              |  |  |

|   | 1.4            | Cache Prefetching                                                                              |  |  |

|   | 1.5            | Organization of Dissertation                                                                   |  |  |

| 2 | $\mathbf{Rel}$ | ted Work 8                                                                                     |  |  |

|   | 2.1            | Memory Hierarchy                                                                               |  |  |

|   | 2.2            | Cache Memory Management                                                                        |  |  |

|   |                | 2.2.1 Configuration $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ 10 |  |  |

|   |                | 2.2.2 Replacement Algorithms                                                                   |  |  |

|   |                | 2.2.3 Write Back Policies                                                                      |  |  |

|   |                | 2.2.4 Cache Miss Types                                                                         |  |  |

|   |                | 2.2.5 Prefetching                                                                              |  |  |

|   | 2.3            | Locality                                                                                       |  |  |

|   |                | 2.3.1 Spatial vs. Temporal                                                                     |  |  |

|   |                | 2.3.2 Instruction Cache vs. Data Cache                                                         |  |  |

|   | 2.4            | Why Not a Large L1 Cache?                                                                      |  |  |

|   |                | 2.4.1 Critical Time Path                                                                       |  |  |

|   |     | 2.4.2  | Hardware Cost                     | 27 |

|---|-----|--------|-----------------------------------|----|

|   | 2.5 | Trend  | to have L2 Cache On Chip $\ldots$ | 28 |

|   |     | 2.5.1  | Examples                          | 29 |

|   |     | 2.5.2  | Dedicated L2 Bus                  | 31 |

|   | 2.6 | Hardw  | vare Prefetch Algorithms          | 32 |

|   |     | 2.6.1  | One Block Look-ahead              | 33 |

|   |     | 2.6.2  | Chen's RPT & similar algorithms   | 34 |

|   | 2.7 | Softwa | are Based Prefetch Algorithm      | 38 |

|   |     | 2.7.1  | Prefetch Instruction              | 38 |

|   | 2.8 | Hybrid | d Prefetch Algorithm              | 40 |

|   |     | 2.8.1  | Stride CAM Prefetching            | 40 |

| 3 | Sim | ulator |                                   | 43 |

| Ū | 3.1 |        | level Memory Hierarchy Simulator  | 43 |

|   | 5.1 | 3.1.1  |                                   |    |

|   |     |        | Multi-level Memory Support        | 45 |

|   |     | 3.1.2  | Non-blocking Cache                | 45 |

|   |     | 3.1.3  | Cycle-by-cycle Simulation         | 47 |

|   |     | 3.1.4  | Cache Prefetching Support         | 47 |

| 4 | Pro | posed  | Algorithms                        | 48 |

|   | 4.1 | SIRPA  | A                                 | 48 |

|   |     | 4.1.1  | Rationale                         | 48 |

|   |     | 4.1.2  | Architecture Model                | 50 |

|   | 4.2 | Line ( | Concept                           | 56 |

|   |     | 4.2.1  | Rationale                         | 56 |

|   |     | 4.2.2  | Improvement Over "Pure" Algorithm | 57 |

|   |     | 4.2.3  | Architectural Model               | 59 |

|   | 4.3 | Comb   | ined L1-L2 Cache Management       | 62 |

|   |      | 4.3.1  | Rationale                             | 62  |

|---|------|--------|---------------------------------------|-----|

|   |      | 4.3.2  | Feasibility                           | 63  |

|   | 4.4  | Combi  | ine SIRPA with Default Prefetch       | 66  |

|   |      | 4.4.1  | Rationale                             | 67  |

|   |      | 4.4.2  | Improvement Over "Pure" Algorithm     | 69  |

|   |      | 4.4.3  | Architectural Model                   | 70  |

|   | 1000 |        |                                       | 70  |

| 5 | Res  |        |                                       | 73  |

|   | 5.1  | Bench  | marks Used                            | 73  |

|   |      | 5.1.1  | SPEC92int and SPEC92fp                | 75  |

|   | 5.2  | Config | gurations Tested                      | 79  |

|   |      | 5.2.1  | Prefetch Algorithms                   | 79  |

|   |      | 5.2.2  | Cache Sizes                           | 80  |

|   |      | 5.2.3  | Cache Block Sizes                     | 81  |

|   |      | 5.2.4  | Cache Set Associativities             | 81  |

|   |      | 5.2.5  | Bus Width, Speed and Other Parameters | 81  |

|   | 5.3  | Validi | ty of Results                         | 83  |

|   |      | 5.3.1  | Total Instructions and Cycles         | 83  |

|   |      | 5.3.2  | Total Reference to Caches             | 84  |

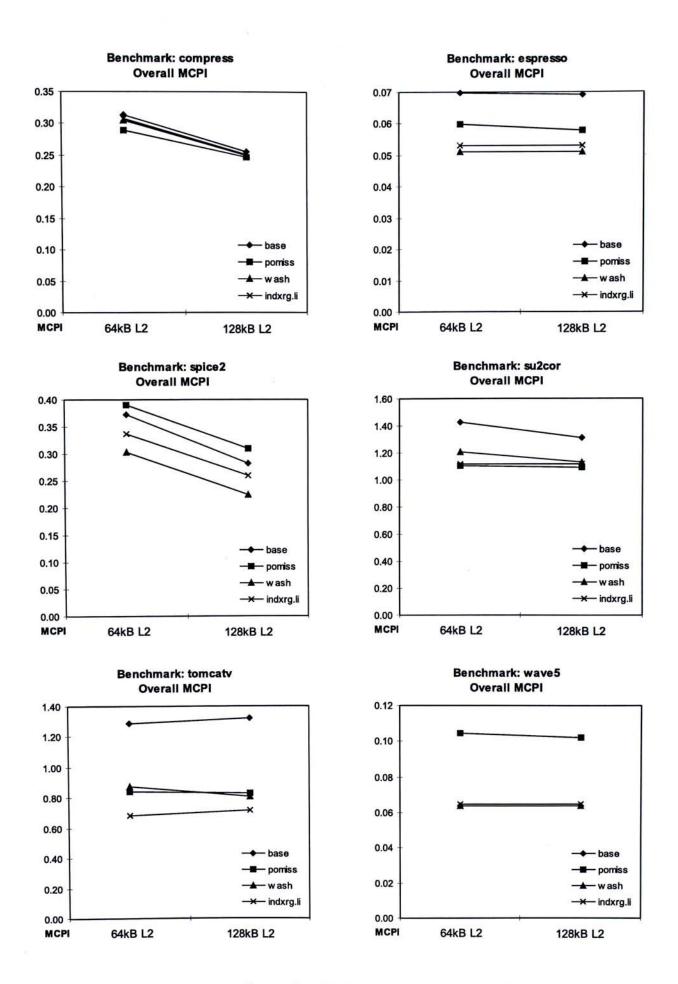

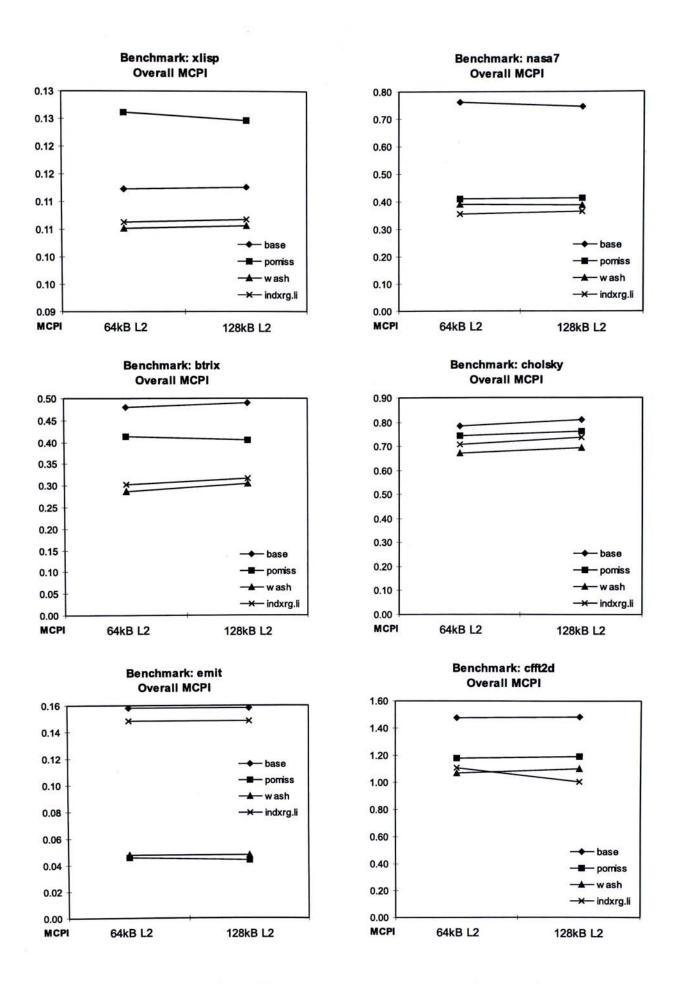

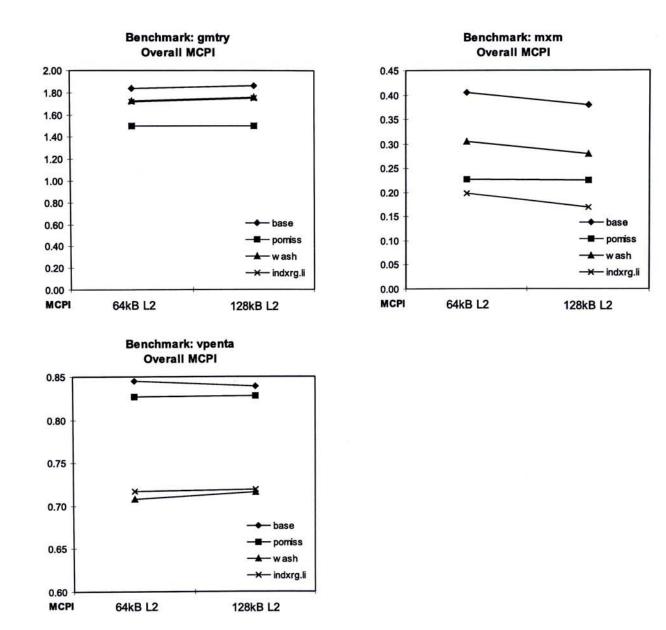

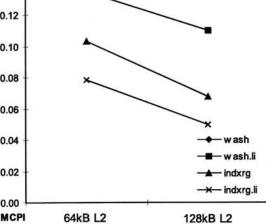

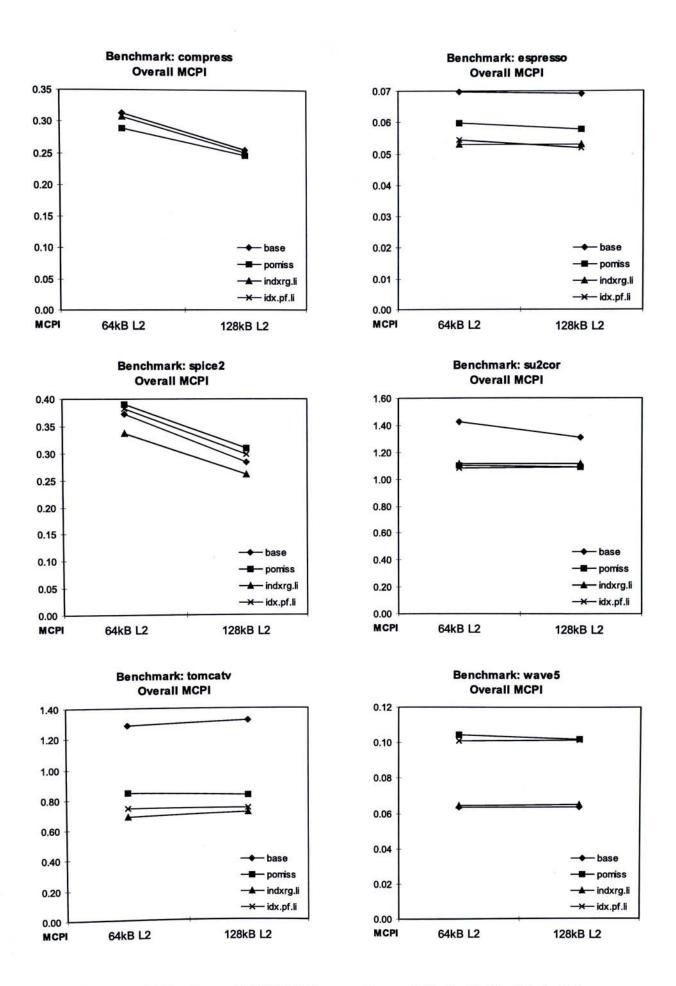

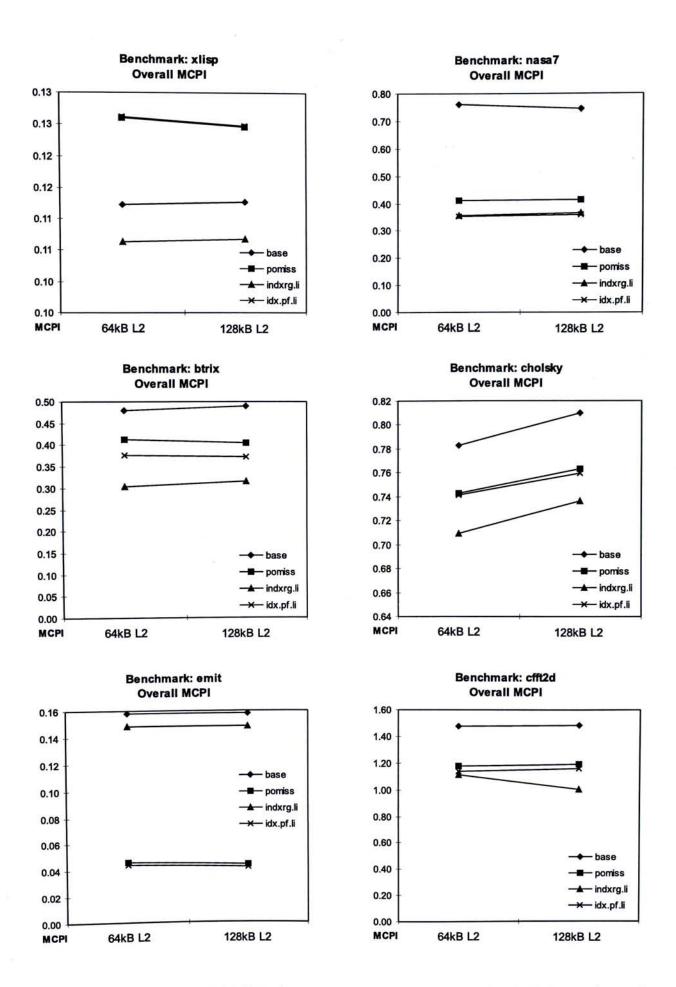

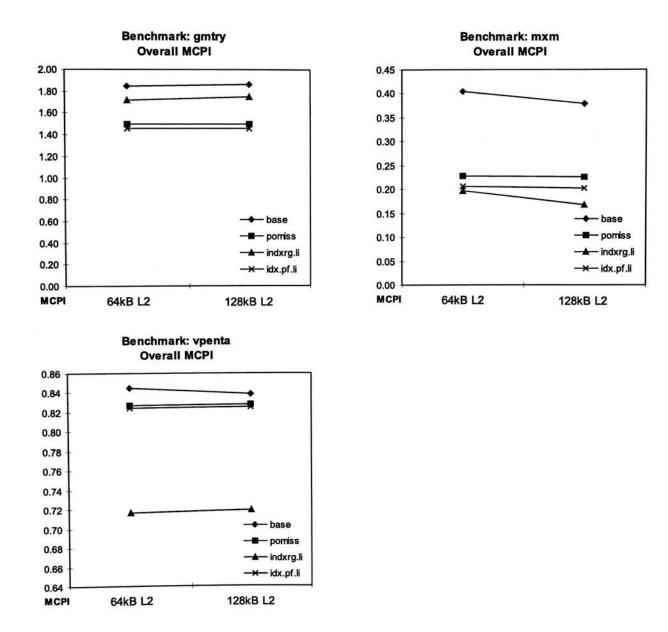

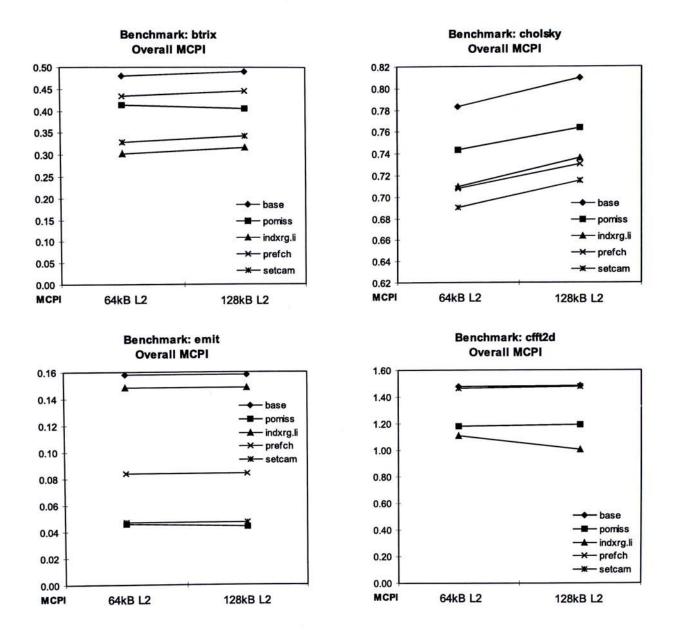

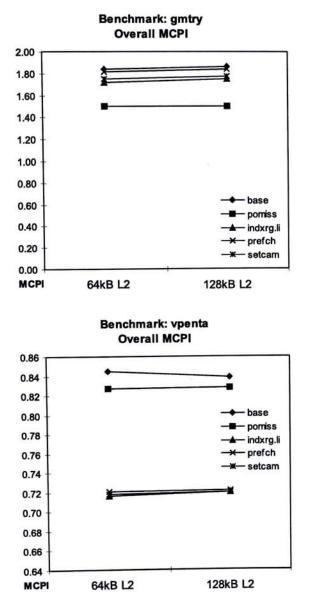

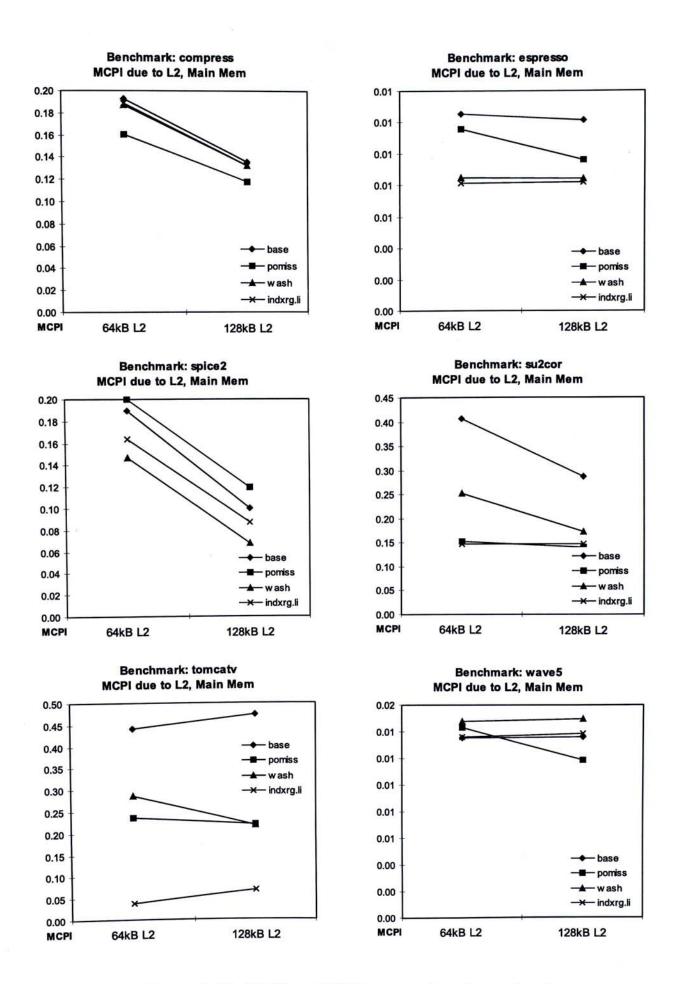

|   | 5.4  | Overa  | all MCPI Comparison                   | 86  |

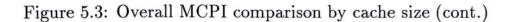

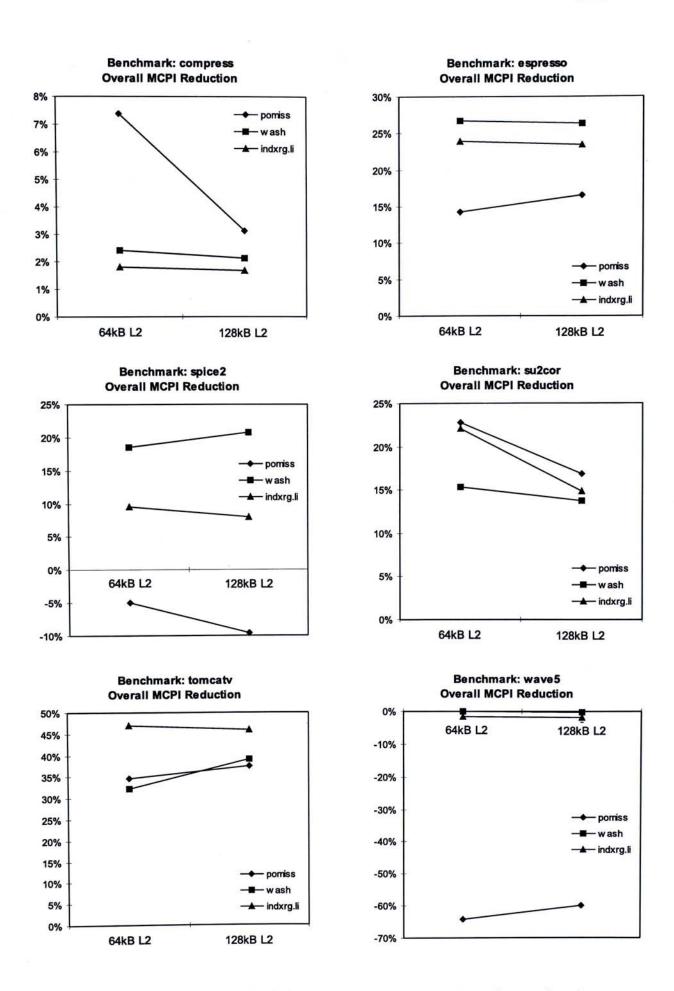

|   |      | 5.4.1  | Cache Size Effect                     | 87  |

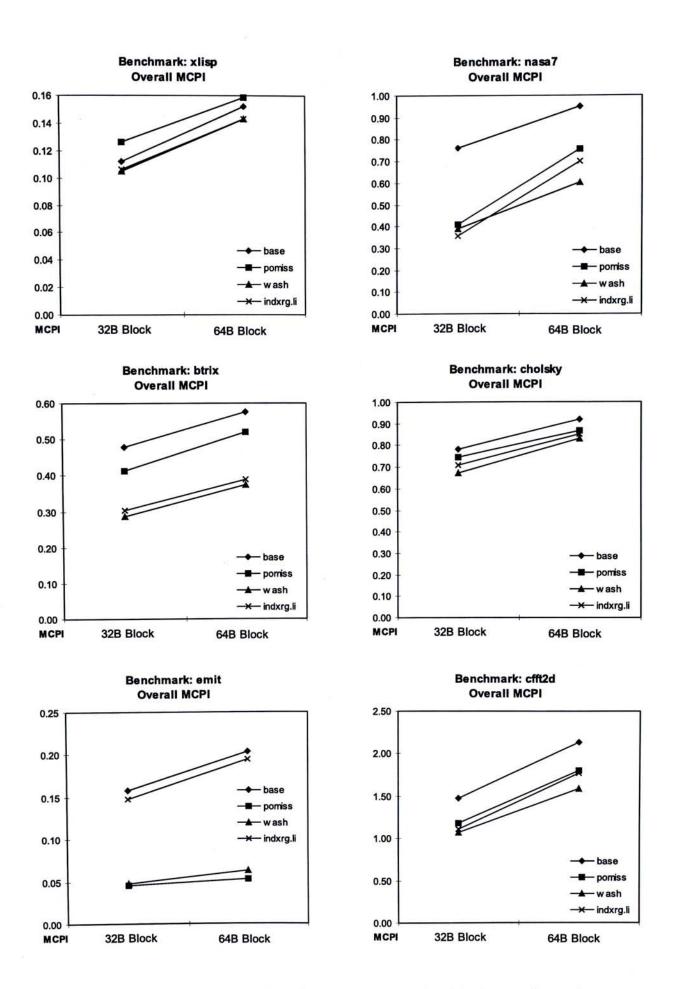

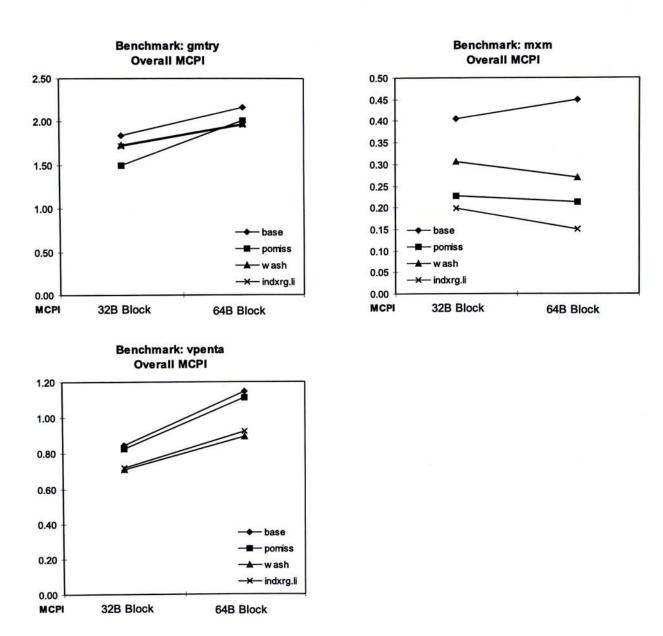

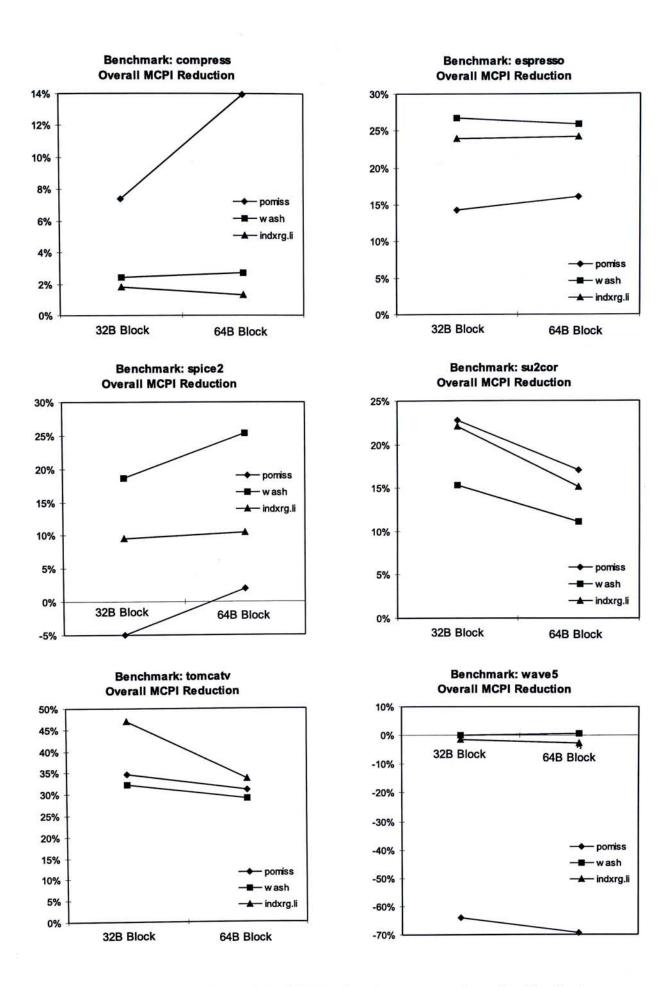

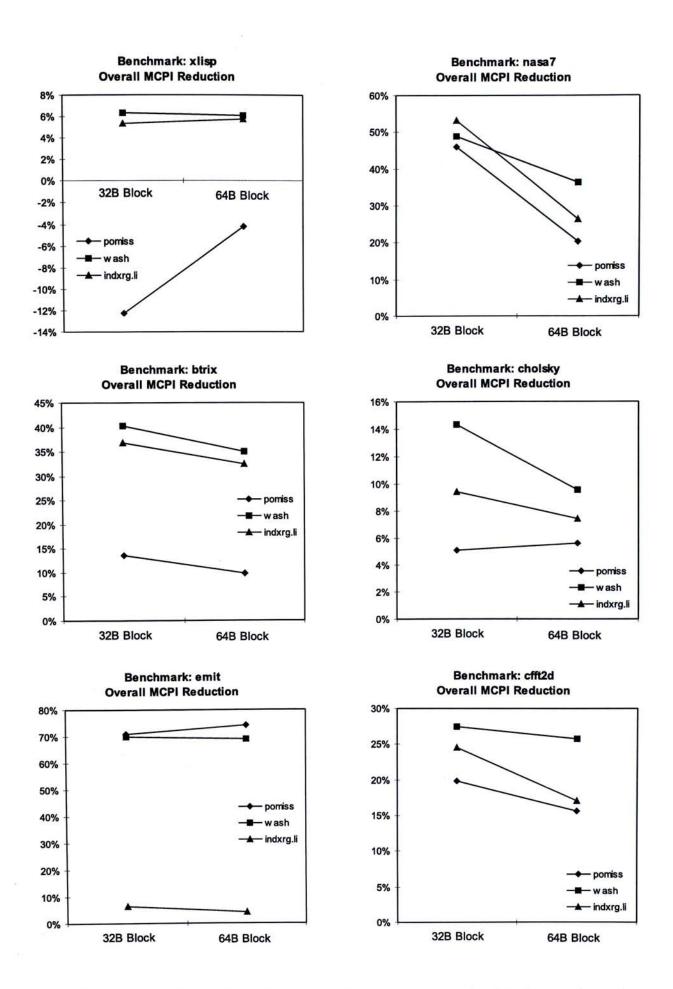

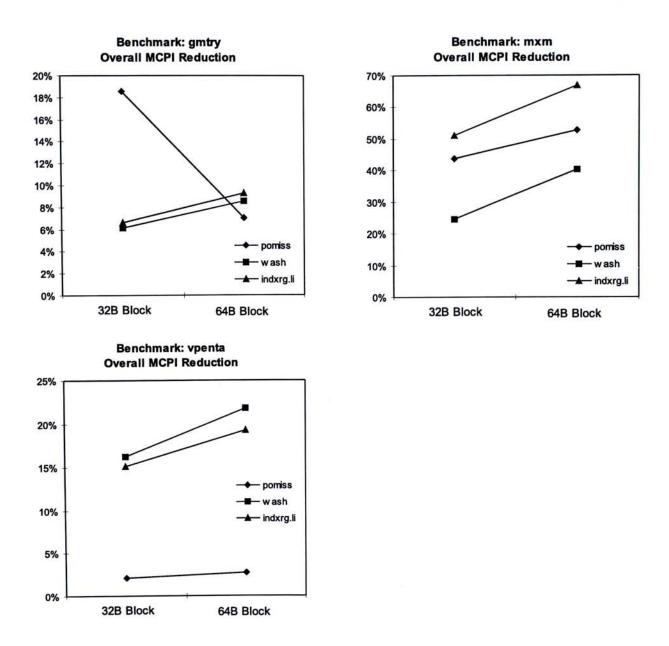

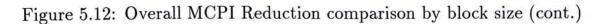

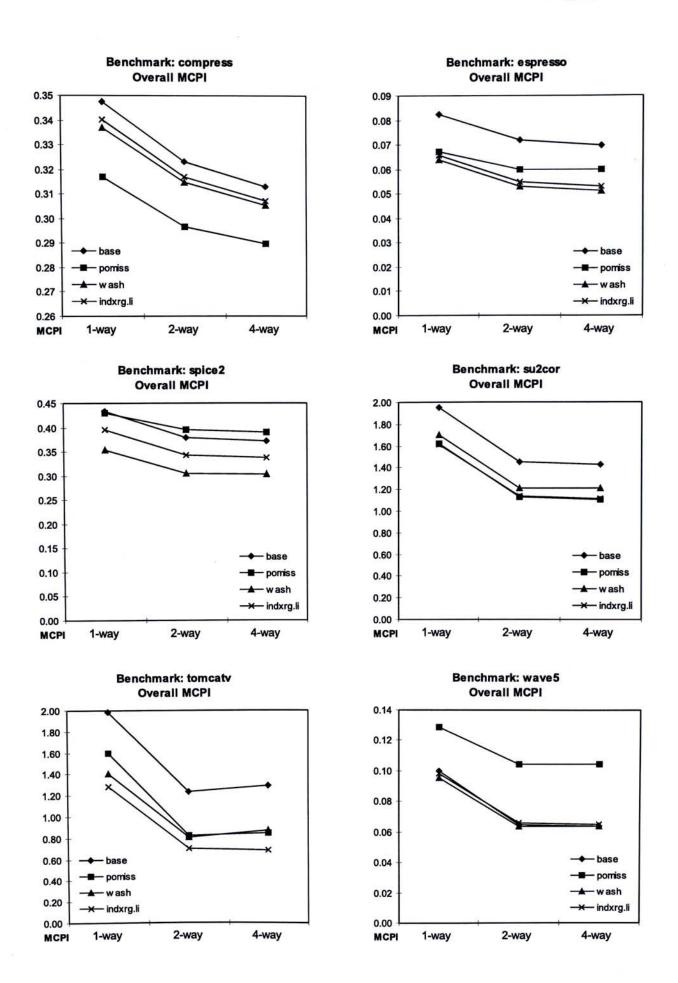

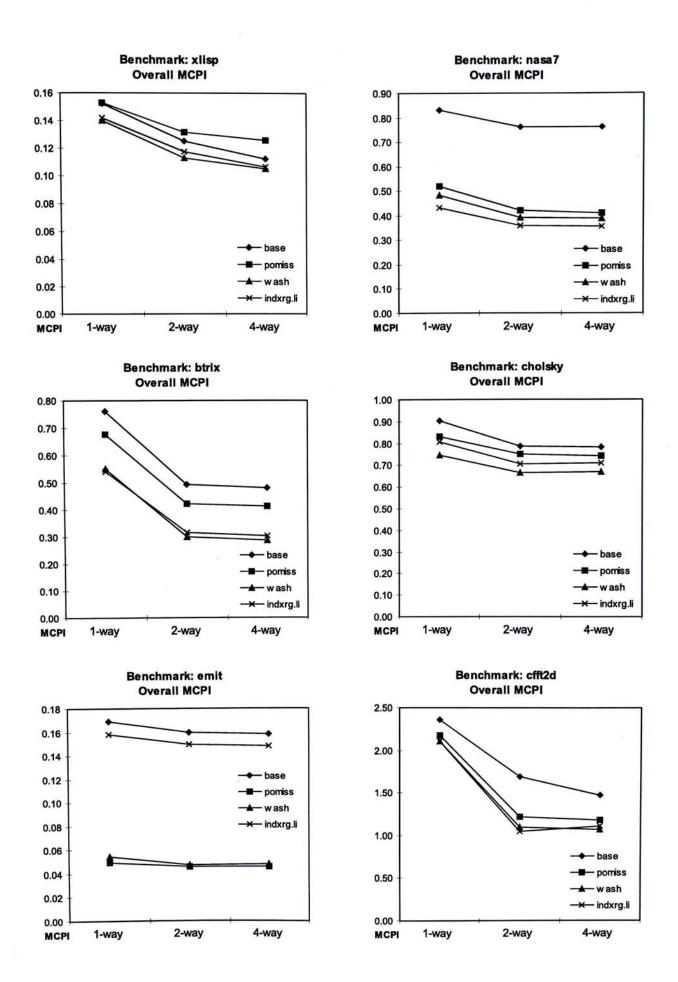

|   |      | 5.4.2  | Cache Block Size Effect               | 91  |

|   |      | 5.4.3  | Set Associativity Effect              | 101 |

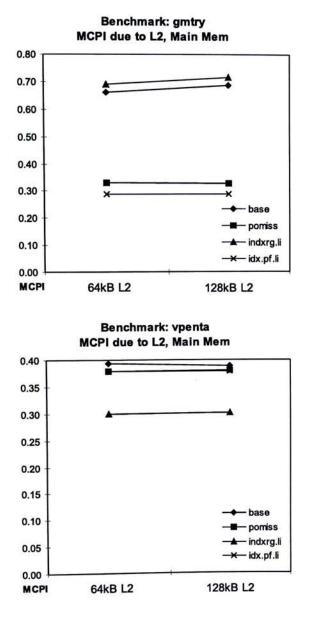

|   |      | 5.4.4  | Hardware Prefetch Algorithms          | 108 |

|   |      | 5.4.5  | Software Based Prefetch Algorithms    | 119 |

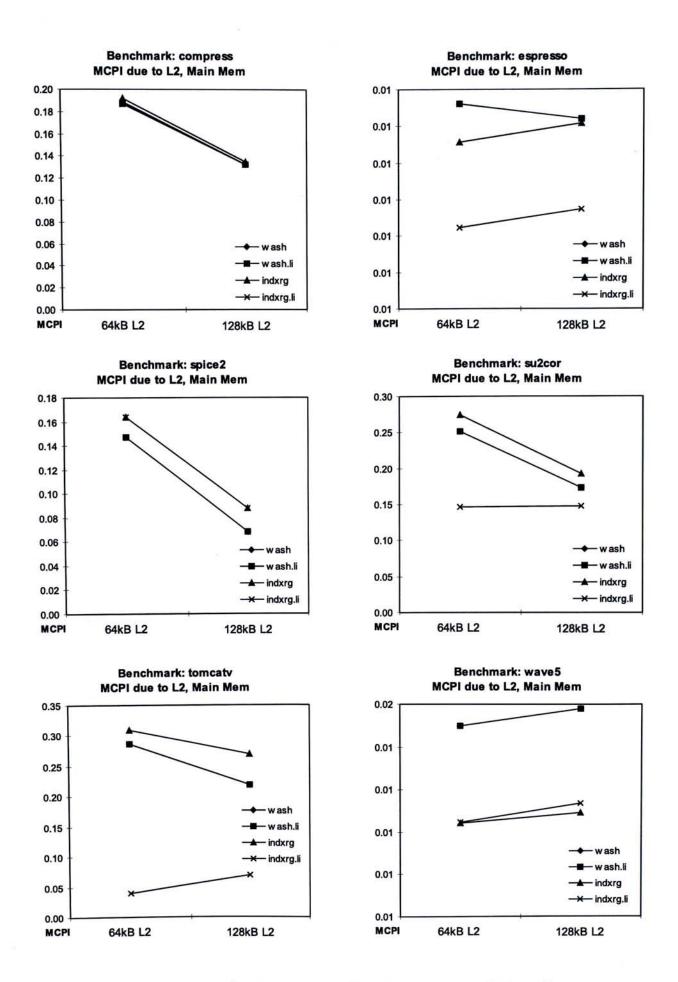

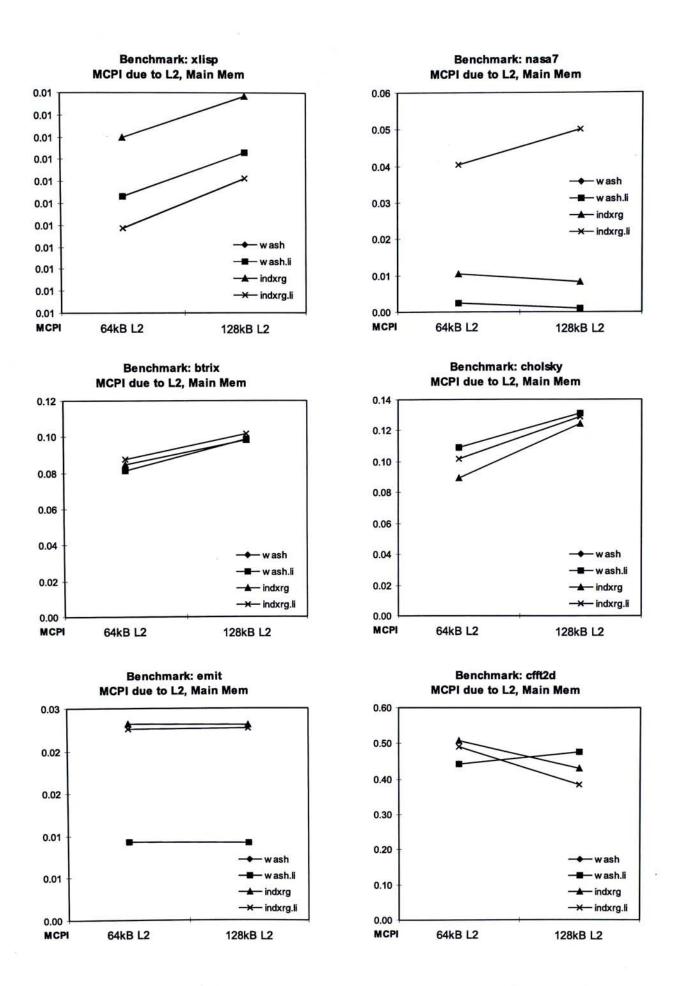

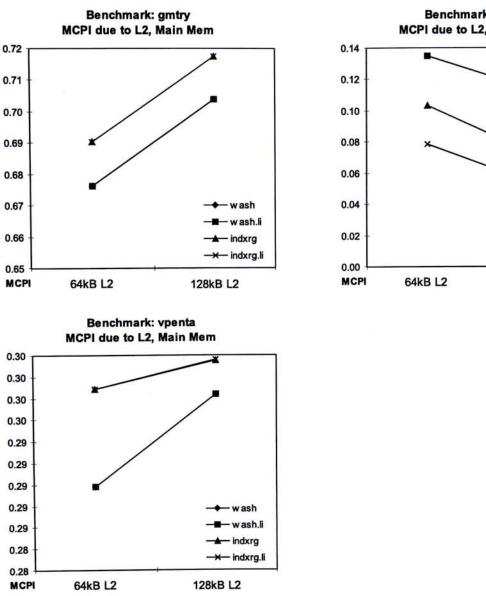

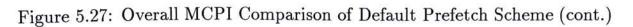

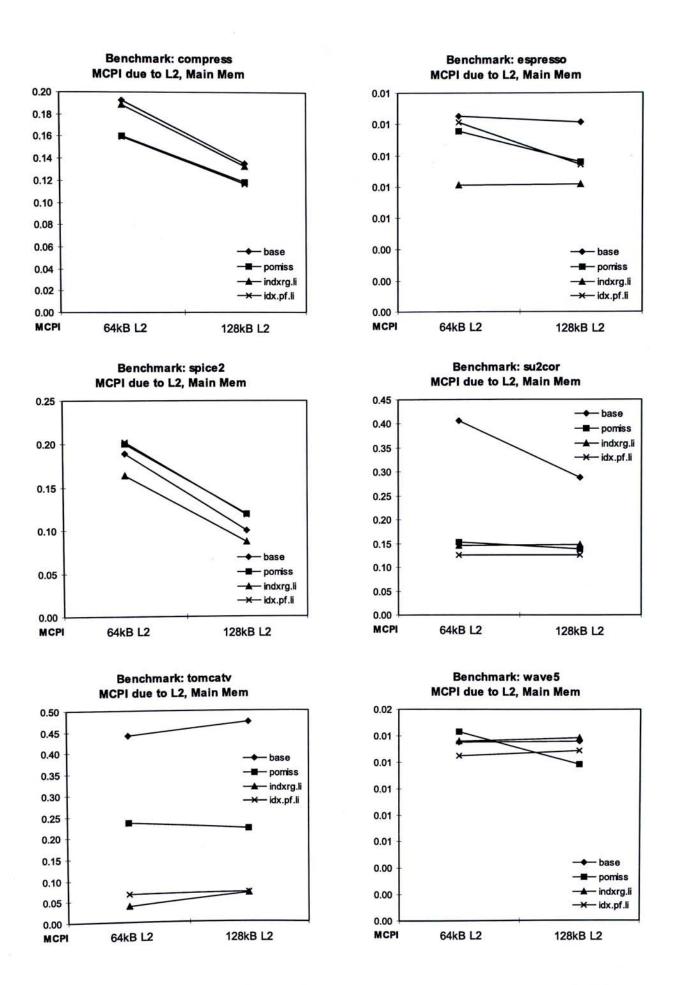

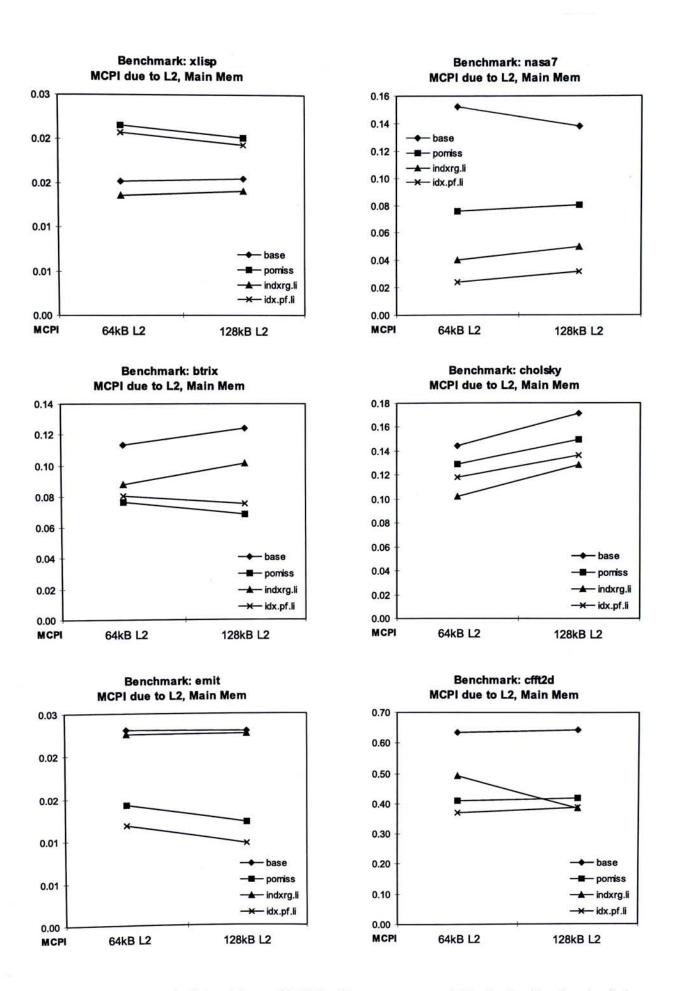

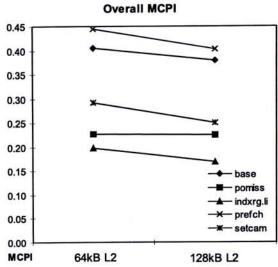

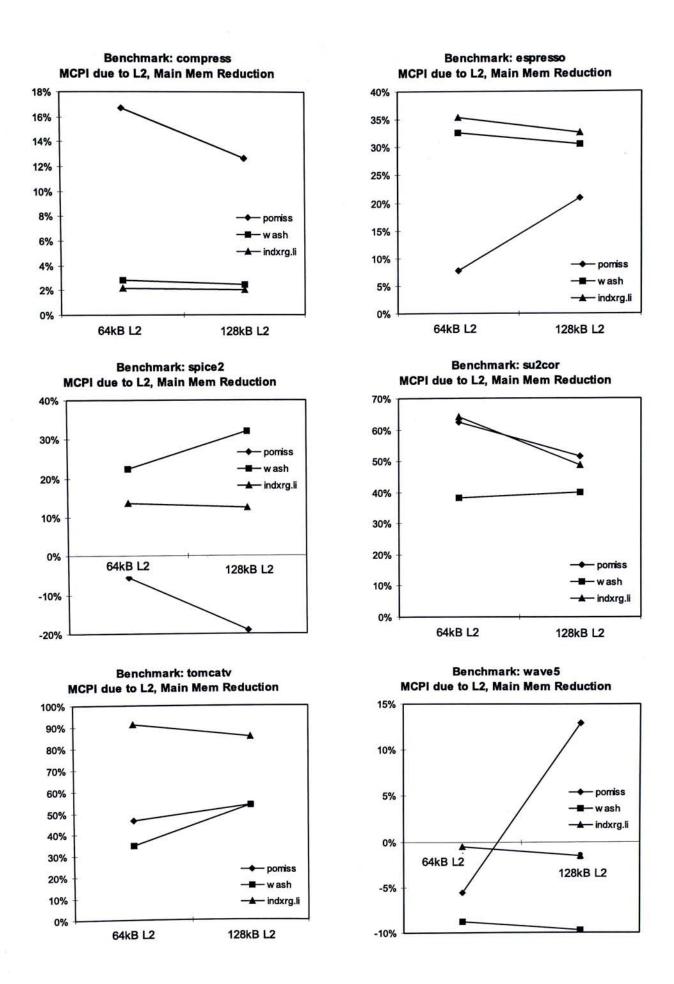

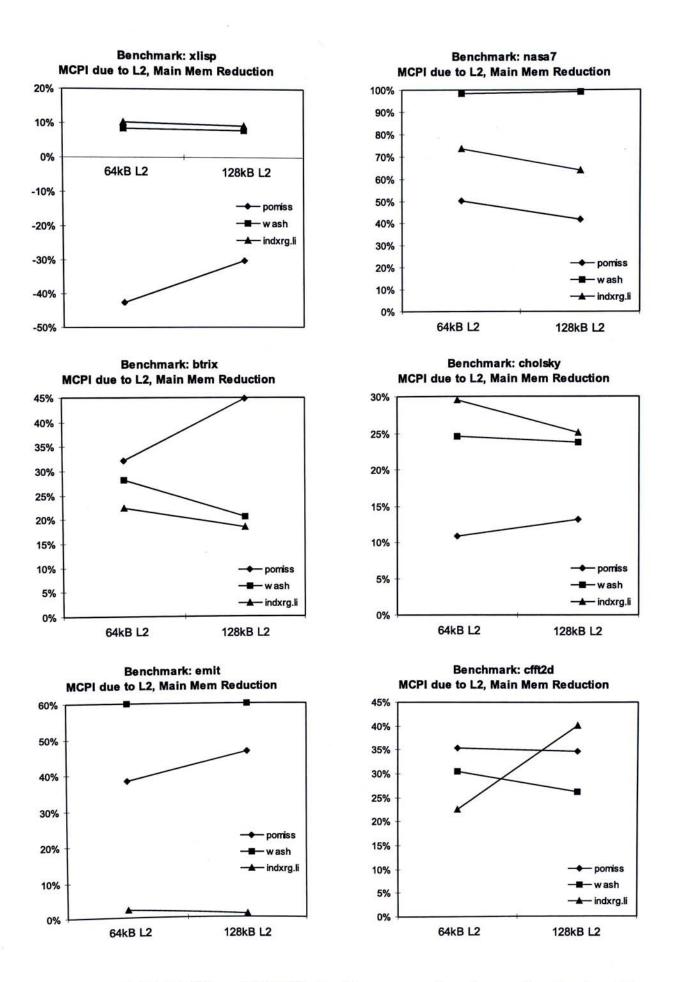

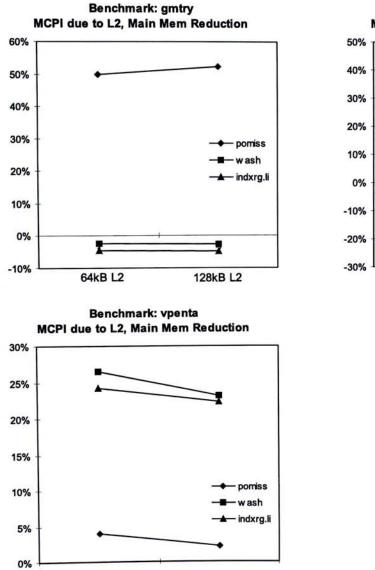

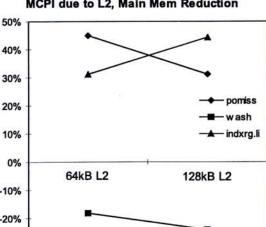

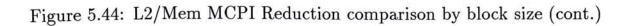

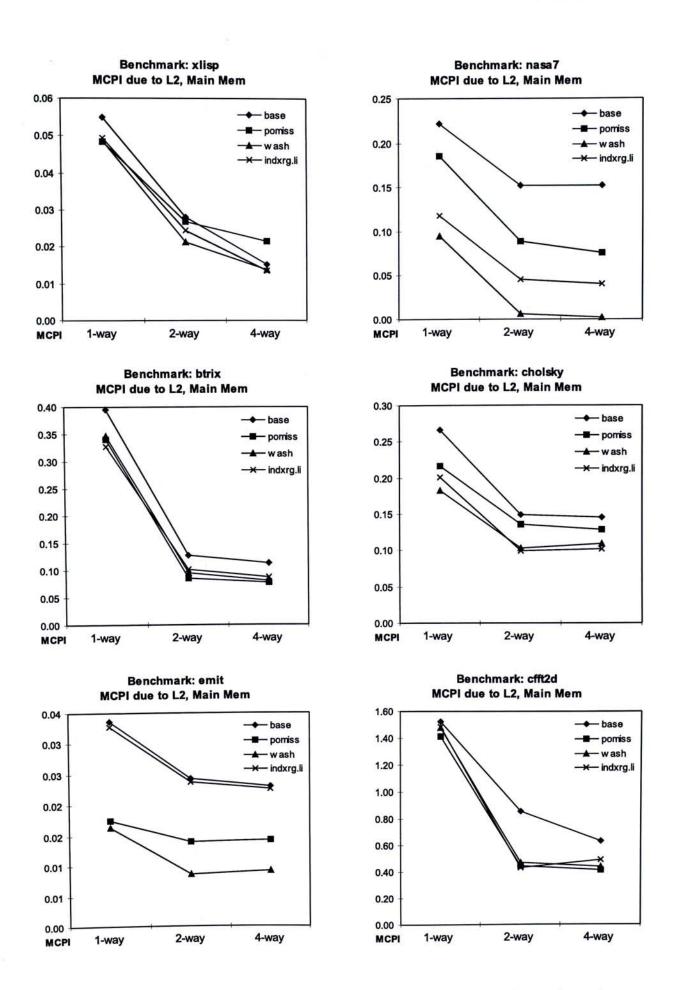

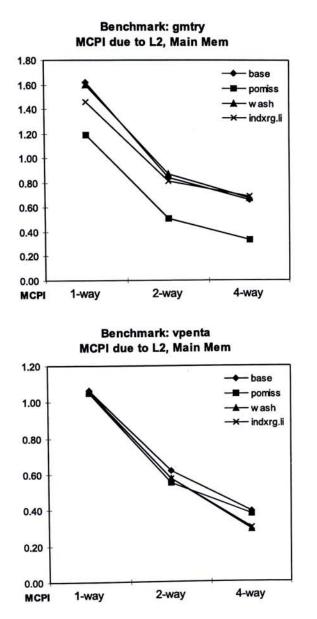

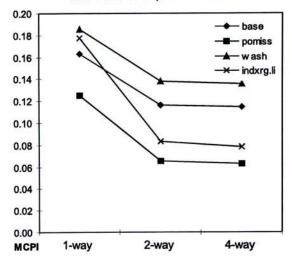

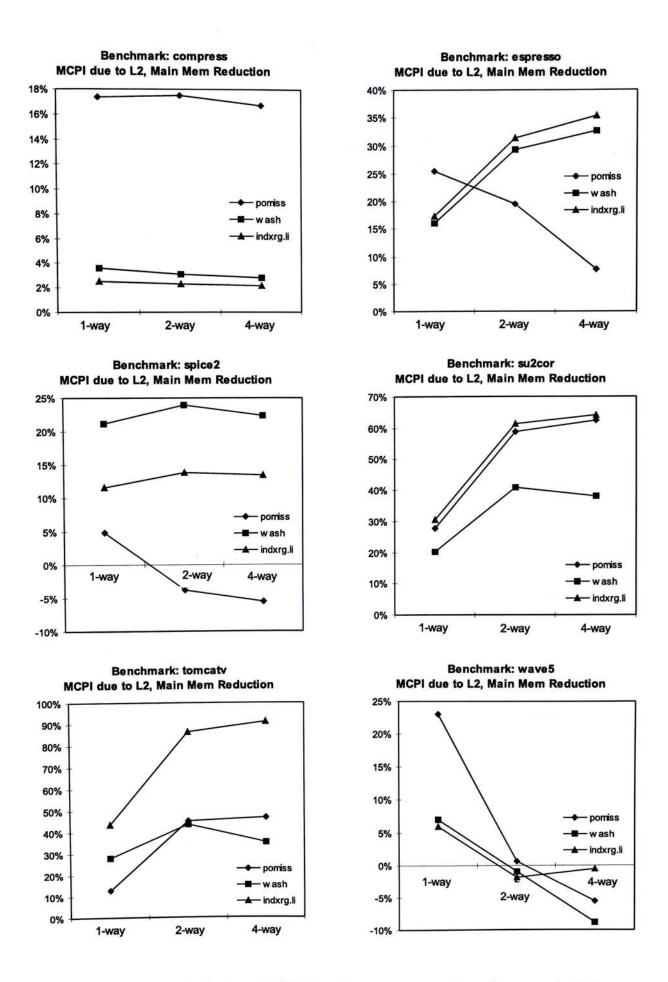

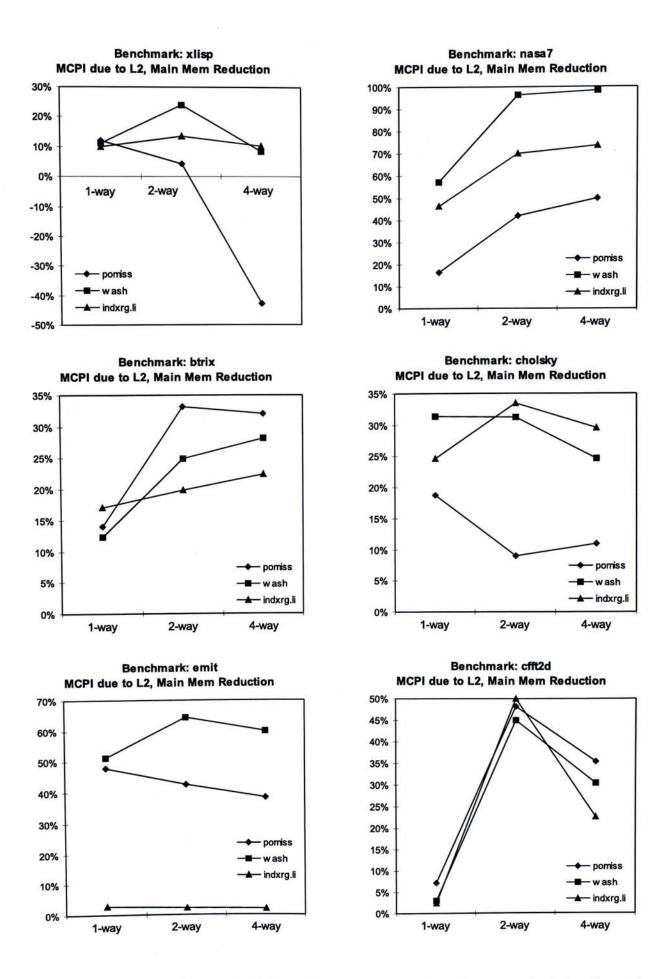

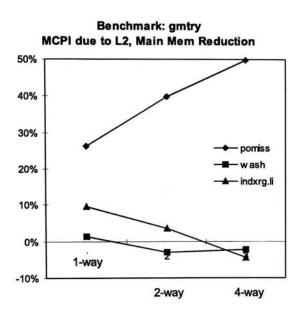

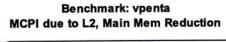

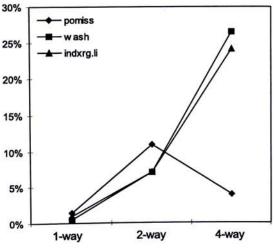

|   | 5.5  | L2 C   | ache & Main Memory MCPI Comparison    | 127 |

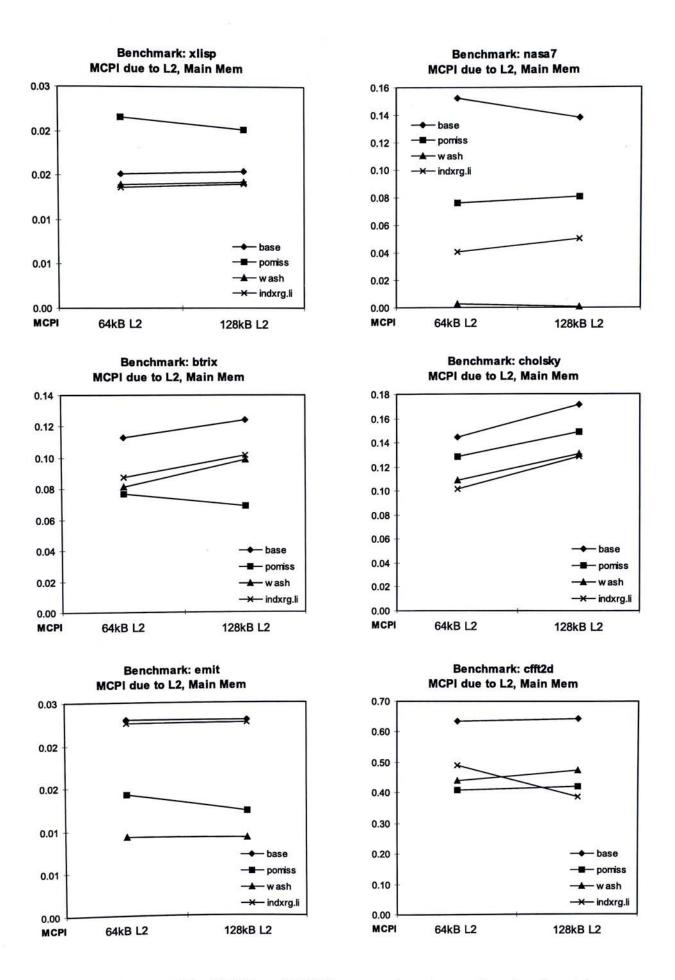

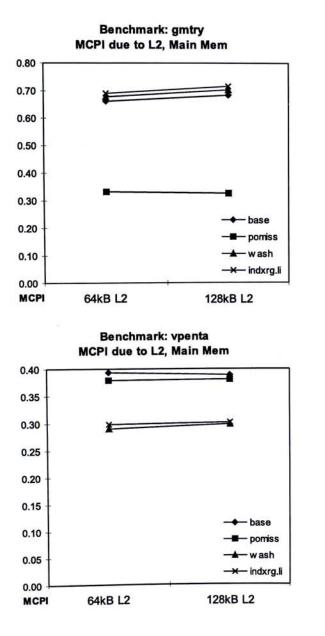

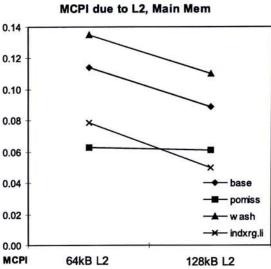

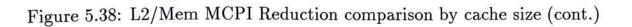

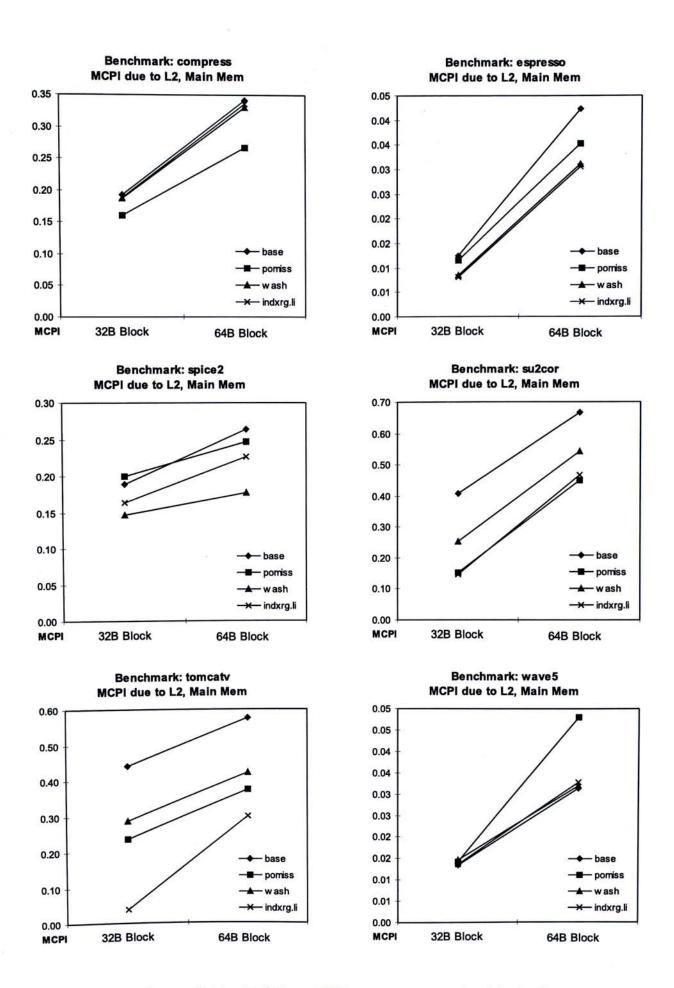

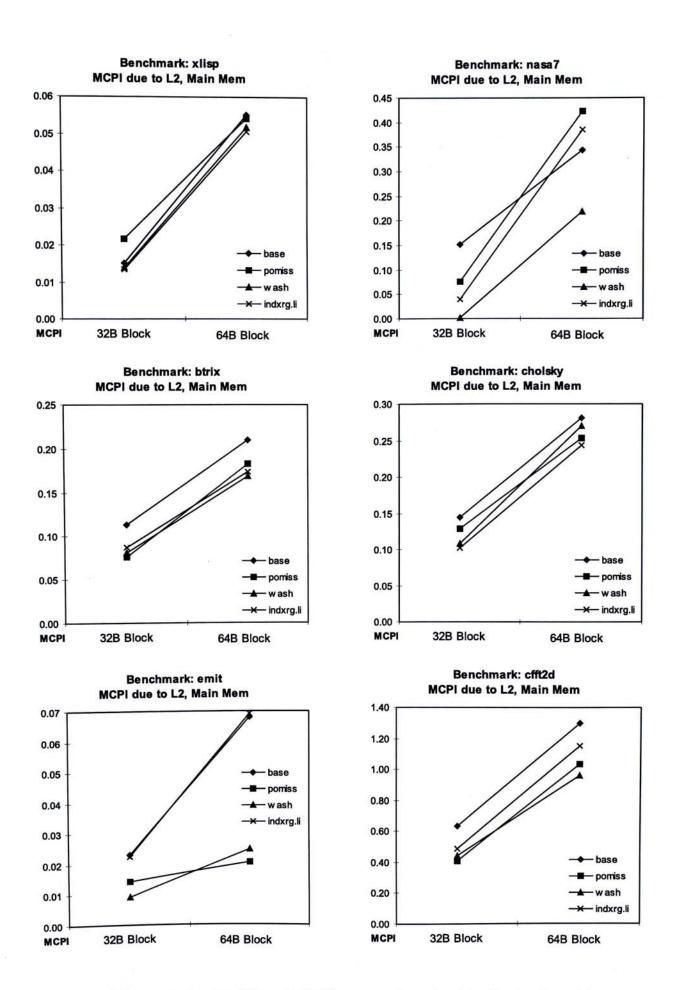

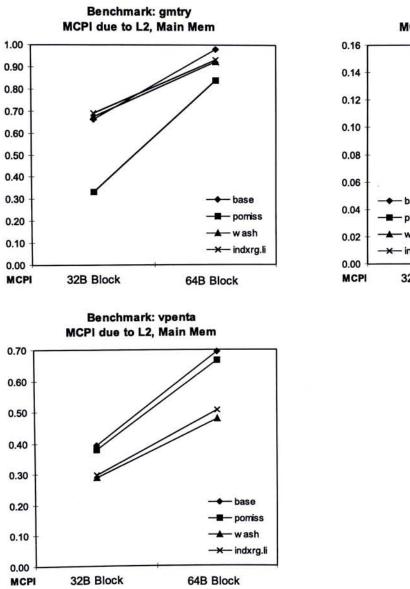

|   |      | 5.5.1  | Cache Size Effect                     | 130 |

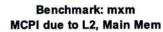

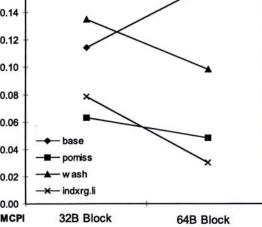

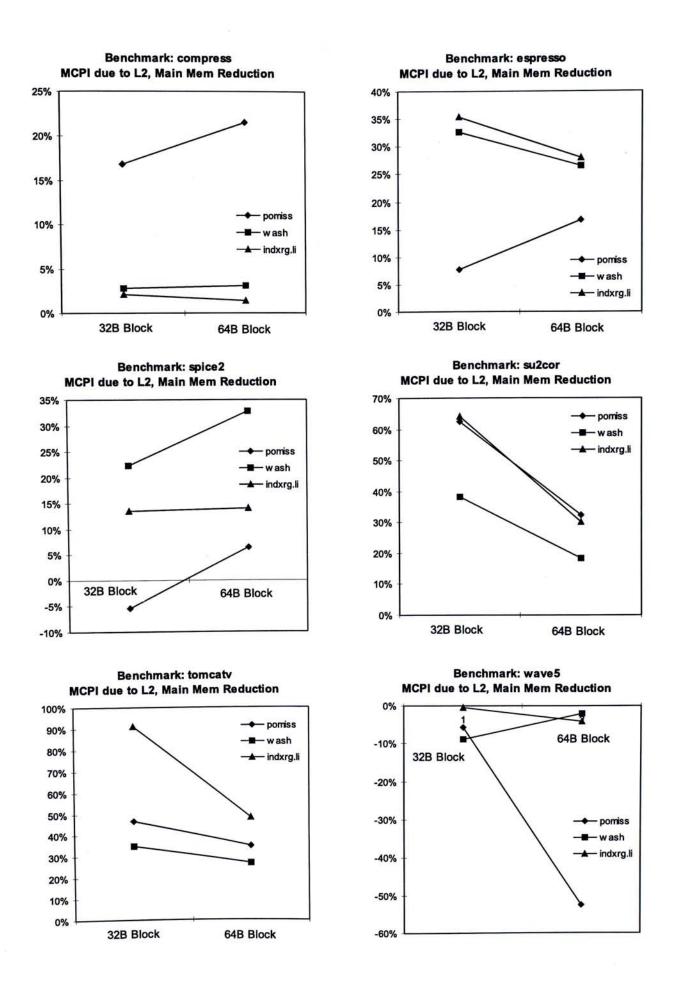

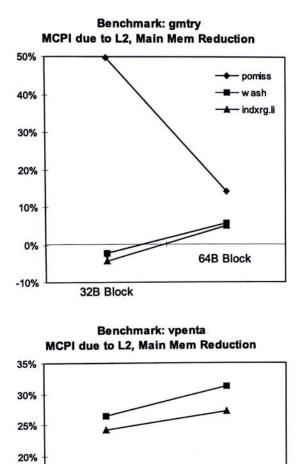

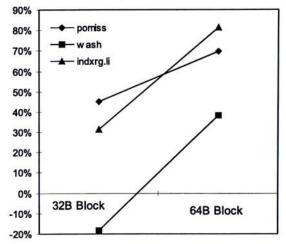

|   |      | 5.5.2  | Cache Block Size Effect               | 130 |

|   |     | 5.5.3 Set Associativity Effect      | 143 |

|---|-----|-------------------------------------|-----|

| 6 | Con | clusion                             | 154 |

| 7 | Fut | ure Directions                      | 157 |

|   | 7.1 | Prefetch Buffer                     | 157 |

|   | 7.2 | Dissimilar L1-L2 Management         | 158 |

|   | 7.3 | Combined LRU/MRU Replacement Policy | 160 |

|   | 7.4 | N Loops Look-ahead                  | 163 |

# List of Figures

| 2.1         | Probability Distribution for Spatial Locality                        | 19        |

|-------------|----------------------------------------------------------------------|-----------|

| 2.2         | Probability Distribution for Temporal Locality                       | 21        |

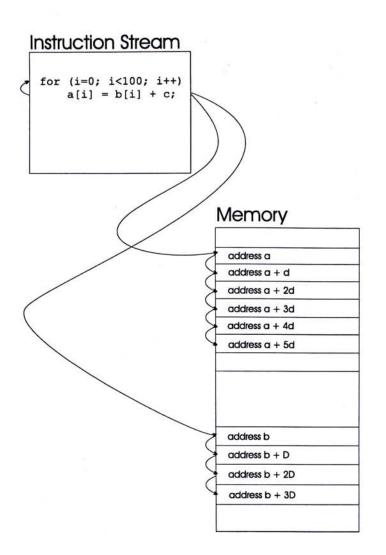

| 2.3         | Constant Stride Reference Patterns                                   | 25        |

| 2.4         | Content Associative Memory                                           | 41        |

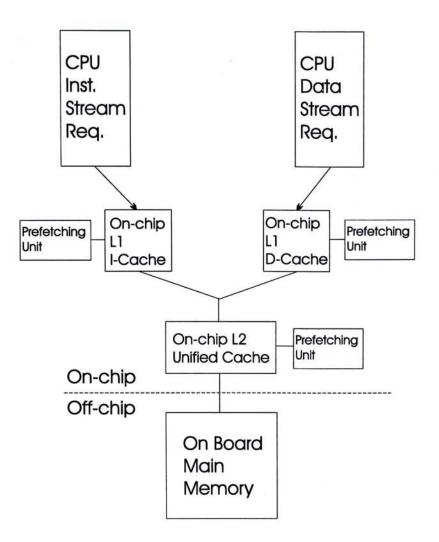

| <b>3.</b> 1 | Multi-level Memory Hierarchy Simulator Configuration                 | <u>46</u> |

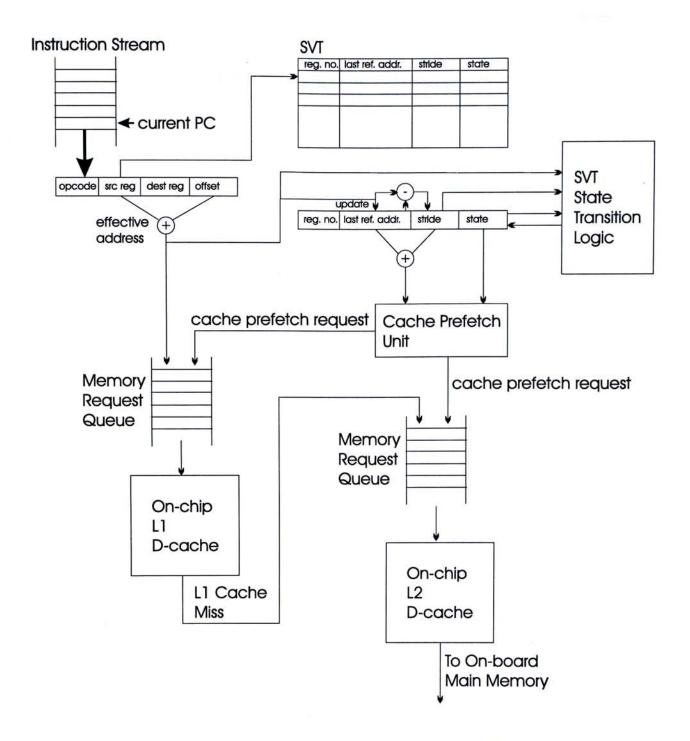

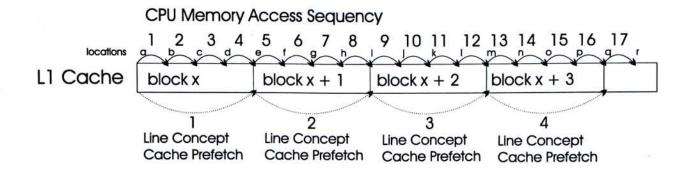

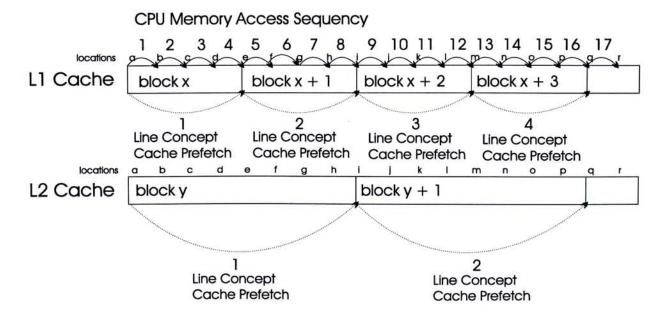

| 4.1         | Block Diagram for Processor with SIRPA scheme                        | 53        |

| 4.2         | Source Register Indexed Stride Values Table                          | 54        |

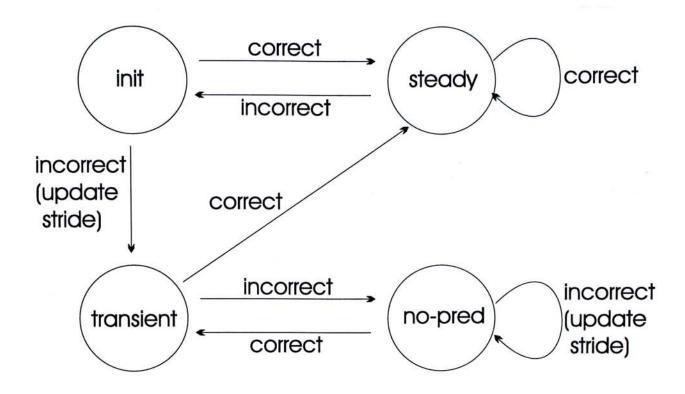

| 4.3         | SVT State Field State Transition Diagram                             | 55        |

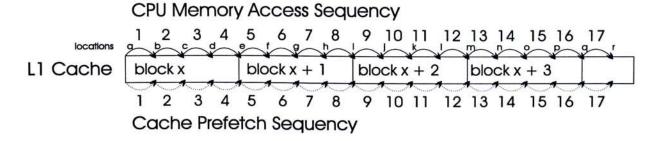

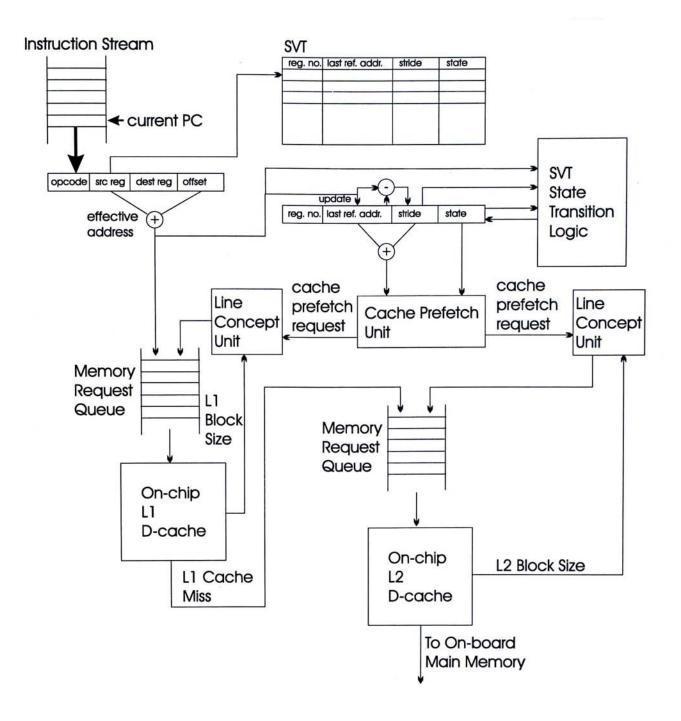

| 4.4         | CPU Access Sequence on Cache Blocks                                  | 57        |

| 4.5         | CPU Access Sequence with Line Concept Prefetch                       | 58        |

| 4.6         | Processor using SIRPA and Line Concept scheme                        | 60        |

| 4.7         | CPU Access Sequence on L1, L2 cache blocks w/Line Concept $\ .$ .    | 61        |

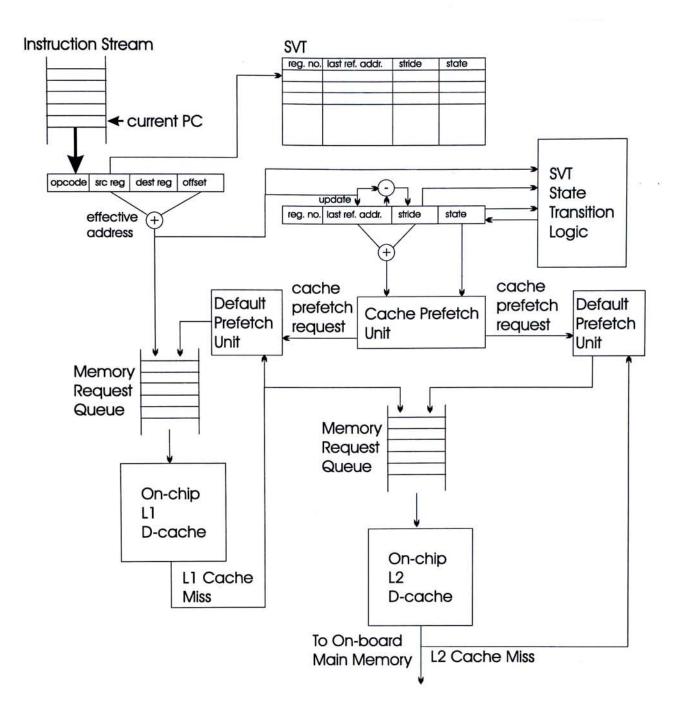

| 4.8         | Combined Prefetch Scheme                                             | 71        |

| 5.1         | Overall MCPI comparison by cache size                                | 88        |

| 5.2         | Overall MCPI comparison by cache size (cont.)                        | 89        |

| 5.3         | Overall MCPI comparison by cache size (cont.) $\ldots \ldots \ldots$ | 90        |

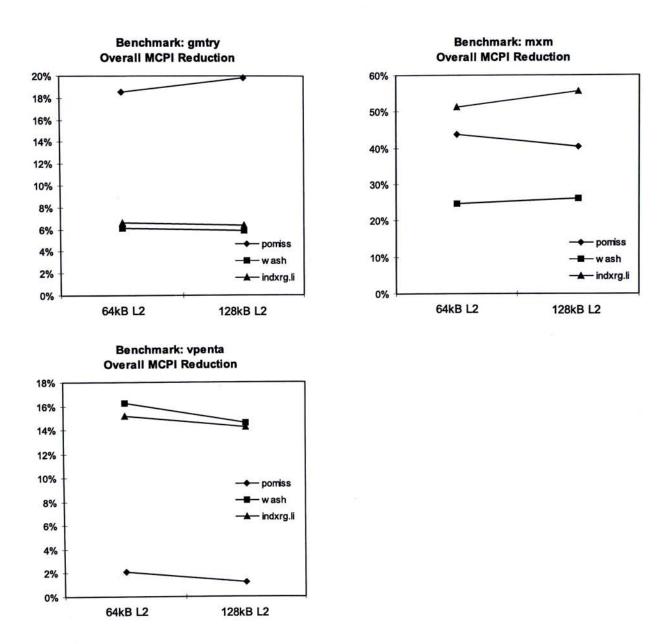

| 5.4         | Overall MCPI Reduction comparison by cache size                      | 92        |

| 5.5         | Overall MCPI Reduction comparison by cache size (cont.) $\ldots$     | 93        |

| 5.6         | Overall MCPI Reduction comparison by cache size (cont.)              | 94        |

| 5.7  | Overall MCPI comparison by block size                                   |

|------|-------------------------------------------------------------------------|

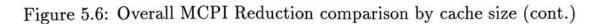

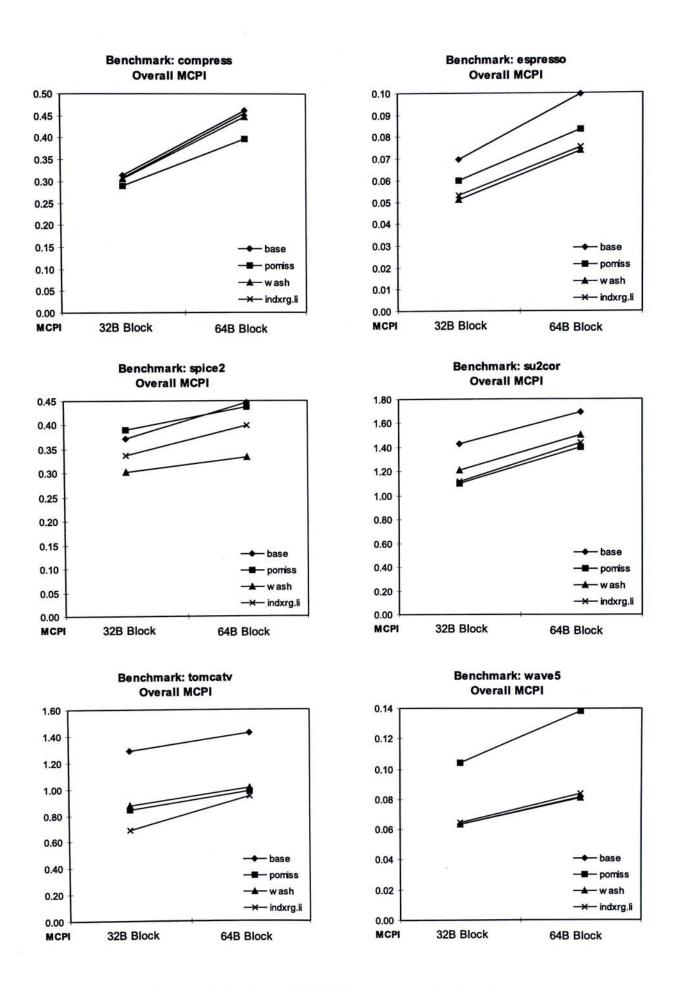

| 5.8  | Overall MCPI comparison by block size (cont.)                           |

| 5.9  | Overall MCPI comparison by block size (cont.)                           |

| 5.10 | Overall MCPI Reduction comparison by block size                         |

| 5.11 | Overall MCPI Reduction comparison by block size (cont.) 99              |

| 5.12 | Overall MCPI Reduction comparison by block size (cont.) 100             |

| 5.13 | Overall MCPI comparison by associativity                                |

| 5.14 | Overall MCPI comparison by associativity (cont.)                        |

| 5.15 | Overall MCPI comparison by associativity (cont.)                        |

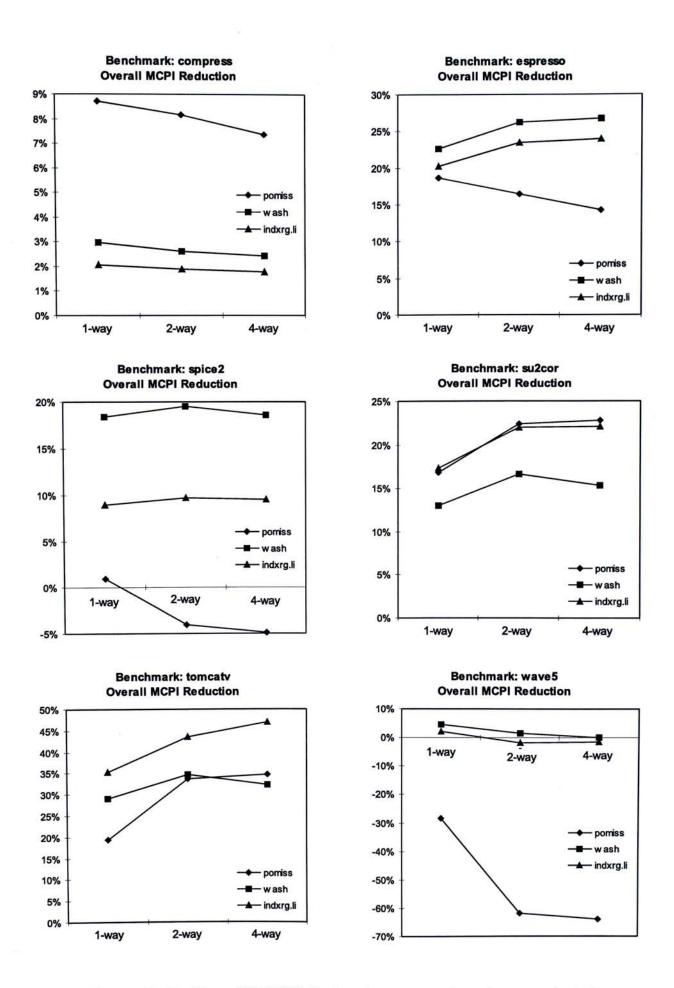

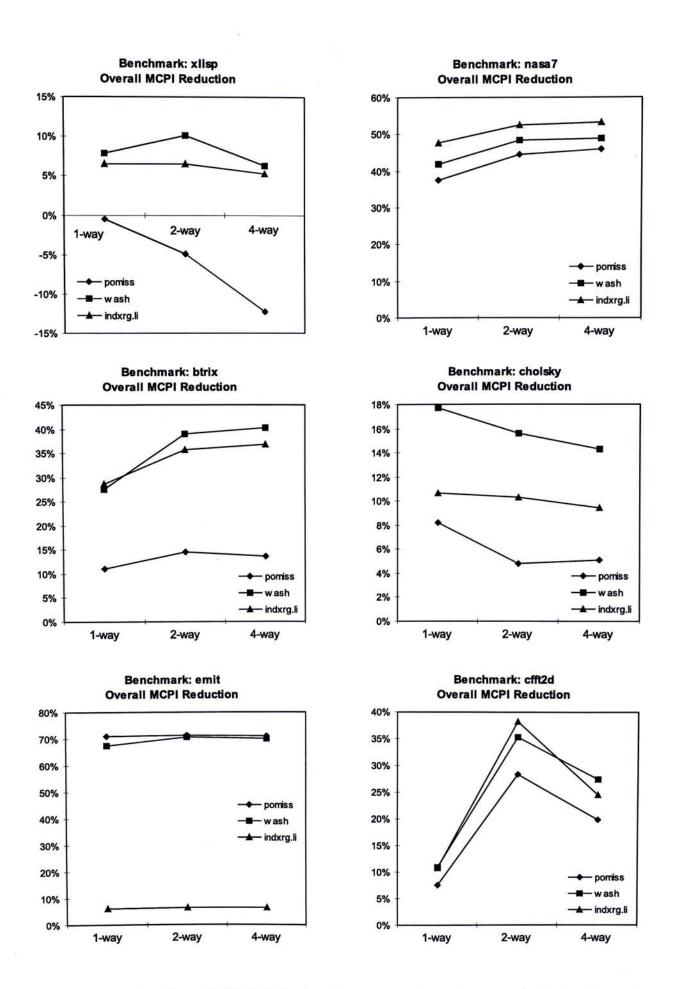

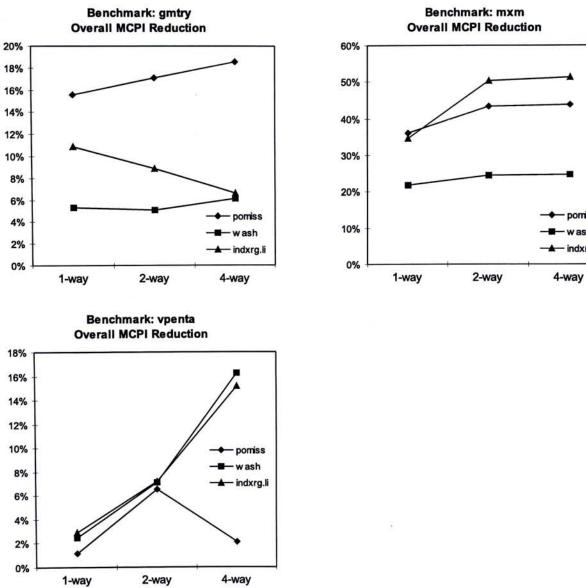

| 5.16 | Overall MCPI Reduction comparison by associativity 105                  |

| 5.17 | Overall MCPI Reduction comparison by associativity (cont.) 106          |

| 5.18 | Overall MCPI Reduction comparison by associativity (cont.) 107          |

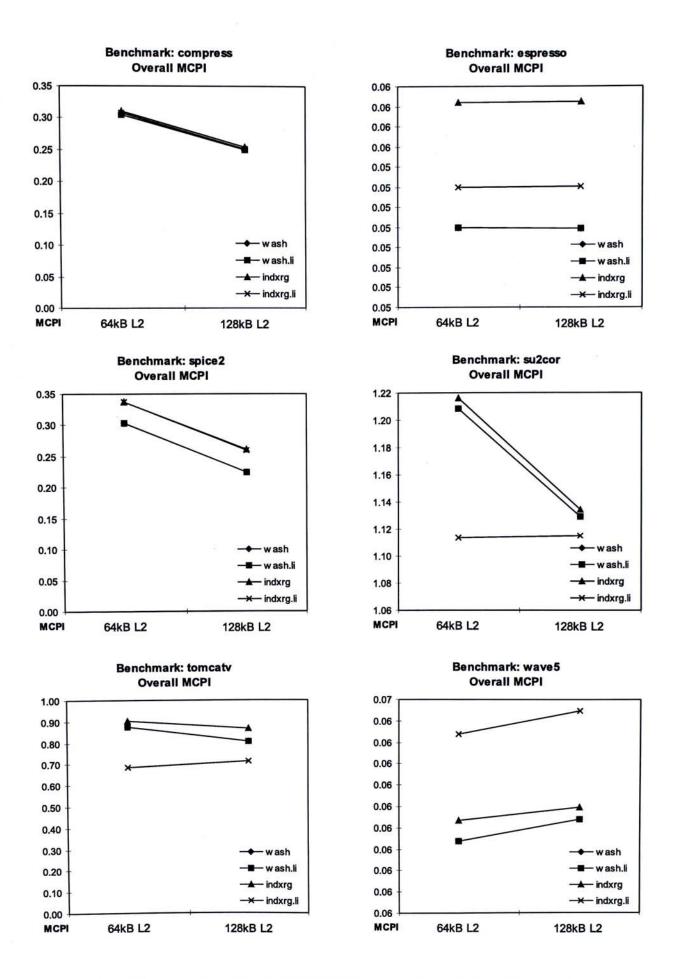

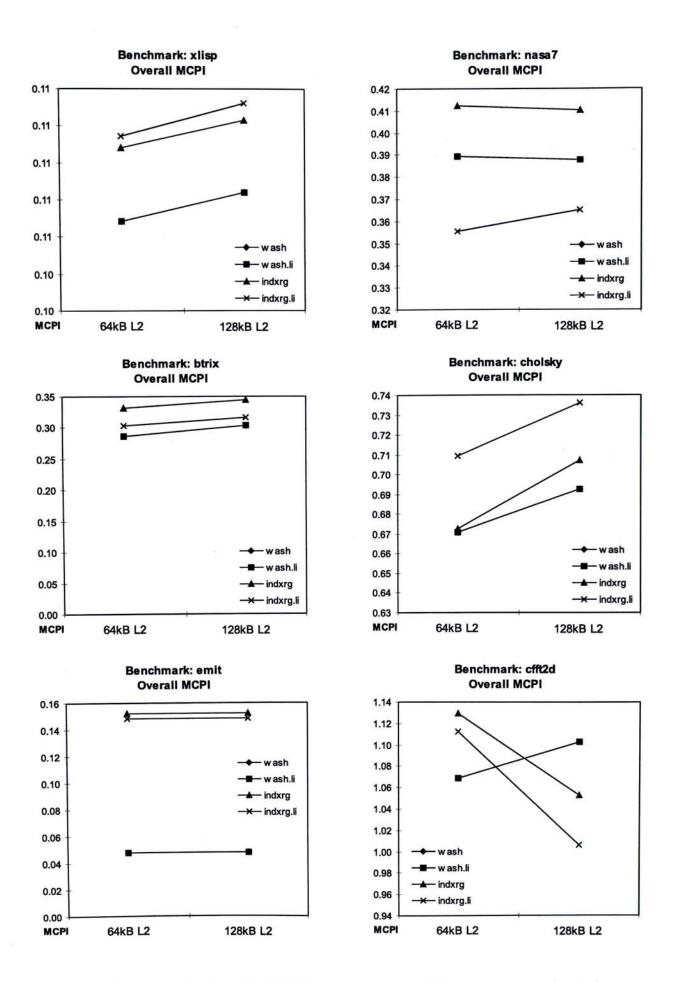

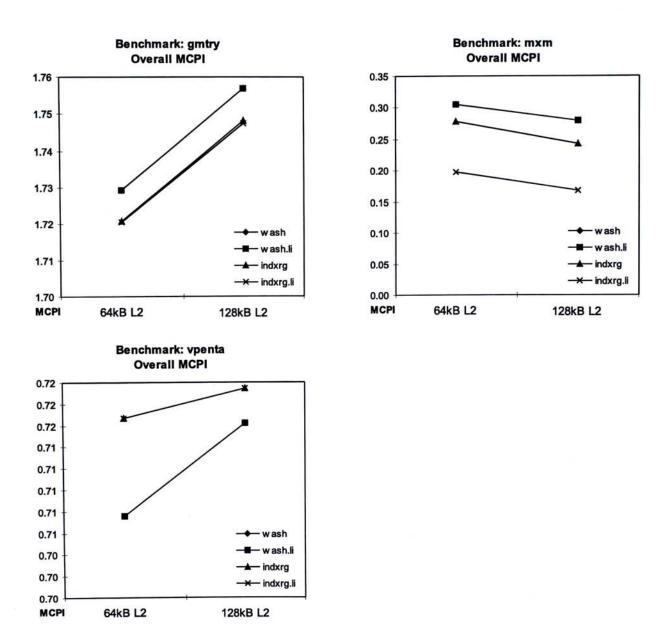

| 5.19 | Overall MCPI Comparsion of Line Concept                                 |

| 5.20 | Overall MCPI Comparsion of Line Concept (cont.) 114                     |

| 5.21 | Overall MCPI Comparsion of Line Concept (cont.)                         |

| 5.22 | L2/Main Mem MCPI Comparsion of Line Concept 116                         |

| 5.23 | L2/Main Mem MCPI Comparsion of Line Concept (cont.) 117                 |

| 5.24 | L2/Main Mem MCPI Comparsion of Line Concept (cont.) 118                 |

| 5.25 | Overall MCPI Comparison of Default Prefetch Scheme 120                  |

| 5.26 | Overall MCPI Comparison of Default Prefetch Scheme (cont.) 121          |

| 5.27 | Overall MCPI Comparison of Default Prefetch Scheme (cont.) 122          |

| 5.28 | L2/Main Mem MCPI Comparison of Default Prefetch Scheme $\therefore$ 123 |

| 5.29 | L2/Main Mem MCPI Comparison of Default Prefetch Scheme (cont.)124       |

| 5.30 | L2/Main Mem MCPI Comparison of Default Prefetch Scheme (cont.)125       |

| 5.31 | Overall MCPI Comparison by Software/Hardware Prefetch Algo-             |

|      | rithms                                                                  |

# 5.32 Overall MCPI Comparison by Software/Hardware Prefetch Algo-

| rithms (cont.) $\ldots \ldots 129$ |

|-------------------------------------------------------------------------------------------------------------------------------|

| 5.33 L2/Mem MCPI comparison by cache size                                                                                     |

| 5.34 L2/Mem MCPI comparison by cache size (cont.)                                                                             |

| 5.35 L2/Mem MCPI comparison by cache size (cont.)                                                                             |

| 5.36 L2/Mem MCPI Reduction comparison by cache size                                                                           |

| 5.37 L2/Mem MCPI Reduction comparison by cache size (cont.) 135                                                               |

| 5.38 L2/Mem MCPI Reduction comparison by cache size (cont.) 136                                                               |

| 5.39 L2/Mem MCPI comparison by block size                                                                                     |

| 5.40 L2/Mem MCPI comparison by block size (cont.)                                                                             |

| 5.41 L2/Mem MCPI comparison by block size (cont.)                                                                             |

| 5.42 L2/Mem MCPI Reduction comparison by block size                                                                           |

| 5.43 L2/Mem MCPI Reduction comparison by block size (cont.) 141                                                               |

| 5.44 L2/Mem MCPI Reduction comparison by block size (cont.) 142                                                               |

| 5.45 L2/Mem MCPI comparison by associativity                                                                                  |

| 5.46 L2/Mem MCPI comparison by associativity (cont.)                                                                          |

| 5.47 L2/Mem MCPI comparison by associativity (cont.)                                                                          |

| 5.48 L2/Mem MCPI Reduction comparison by associativity 147                                                                    |

| 5.49 L2/Mem MCPI Reduction comparison by associativity (cont.) 148 $$                                                         |

| 5.50 L2/Mem MCPI Reduction comparison by associativity (cont.) 149                                                            |

| 7.1 Processor with Prefetch Buffer                                                                                            |

# List of Tables

| 5.1 | Best Prefetch Algorithm Producing Smallest Overall MCPI 109         |

|-----|---------------------------------------------------------------------|

| 5.2 | Best Overall MCPI by using SIRPA & RPT family Algorithms 150 $$     |

| 5.3 | Best Overall MCPI by using PFONMISS/SIRPA/RPT Algorithms 151        |

| 5.4 | Benchmarks with high reduction in MCPI by using Default Prefetch152 |

| 5.5 | Best Software Based Prefetch Algorithm                              |

| 5.6 | Overall MCPI by using SETCAM & SIRPA family Algorithms 153 $$       |

| 7.1 | LRU Replacement Example                                             |

| 7.2 | MRU Replacement Example                                             |

# Chapter 1

# Introduction

The disparity between speed of microprocessors and main memory has been worsened in the last decade. With today's technology, typical CPUs like UltraSparc runs at 167MHz [Gwe94], MIPS R10000 processor runs at 275MHz [AC95], Digital's Alpha 21164 runs at 333MHz [Ban95]. These clock rates correspond to cycle time of 5.9ns, 3.6ns and 3ns respectively. However, the random access time for typical transistor based dynamic memory is about 60ns [Bol94]. If a datum is to be retrieved from main memory, the processor will be stalled for 10-20 cycles. That means a degradation of performance in one order of magnitude. The situation would be even more demanding when UltraSparc, MIPS R10000 and DEC Alpha 21164 can execute at most four instructions [Gwe94] [AC95] [Ban95] per cycle.

To bridge the speed gap between microprocessors and main memory, fast memory is inserted between the processor bus and the main memory. This type of memory is called cache memory [Smi82]. However, due to high cost to produce cache memory, its size is usually limited. The performance of the overall computer system can be improved if instructions and data that are to be referenced are kept in the cache memory [Prz90]. The less frequently used data are stored in the main memory.

# 1.1 Cache Memory

In order to feed a processor with enough instructions and data without stalling, it is typical to include cache memory in the system design. Most modern microprocessors have on-chip cache memory implemented. UltraSparc has a 16k Bytes cache memory for instruction and a 16k Bytes cache memory for data [Gwe94]. Intel's Pentium has 8k Bytes instruction cache and 8k Bytes data cache [CTR93]. MIPS R10000 has 32k Bytes instruction cache and 32k Bytes data cache [AC95]. These on-chip cache memory designs match the speed of the microprocessor [AC95] in general. If all instructions and data can be accessed from the on-chip cache, the processor can execute programs in high speed.

The working principle of cache memory depends on locality, and there are two kinds of them. Temporal locality refers to the expectation that instructions and data that are currently in use, will be referenced again in the near future. Spatial locality refers to the likelihood of adjacent access to memory in a short span of time [Prz90]. The locality feature in a program depends on the general sequential execution flow and loops inside it. When requested instructions or data can be found in the cache, the processor can retrieve from the cache instead of from the main memory. There will be a saving of time, which is equal to the difference of access timing between the cache and the main memory. If the majority of processor memory requests can be satisfied from the cache, the memory latency as experienced by the processor will be that of the access time of the cache, instead of the slower main memory.

Another layer of cache memory can be implemented on the system board level, which is called second level cache. Second level cache is usually larger in size but with a slower access time compare with the on-chip first level cache. There are newer generation processors with on-chip second level cache, such as DEC Alpha 21164 and Intel Pentium Pro, whereas other processors have on-chip second level cache controller, such as MIPS R10000, Sun UltraSparc I, and IBM/Motorola PowerPC 620.

### **1.2** System Performance

The performance of a computer system depends on the length of time that the CPU spent on computation and the time spent on moving data to/from memory. The total of the above adds up to a figure in number of clock cycles that the computer system used to execute a program. This figure can be used to show the performance of a computer system [HP90]. However, in order to compare performance across different programs, another measurement, which should be independent of the running program, is necessary. Cycles Per Instruction (CPI) is such a measurement that is independent of the complexity of the running program. CPI is defined as the number of CPU clock cycles for a program to run divided by the instruction count for that program [HP90].

For non-superscalar processor, the upper limit of CPI is 1. When CPI is 1, that means the processor can finish an instruction every cycle. For superscalar processor, as there are more than one function units in the CPU, it can process a few instructions in parallel. In theory, the upper limit of CPI of superscalar processor can be smaller than one, the limit should be the inverse of the maximum number of instructions that can be issued per cycle.

### **1.3** Cache Performance

There are a few quantities which can be used to measure cache performance. One of them is cache hit ratio (or hit rate, if the quantity is expressed as a pure number). Hit ratio is defined as the percentage of memory requests that can be found (a hit) in the cache [Prz90]. The upper limit of hit ratio is 100%, at that time, all memory references can be satisfied by the cache memory, and the memory latency will be the access time of the cache. However, as the cache size is small compare with the main memory, it is seldom to have 100% hit ratio. For hit ratio lower than 100%, the memory latency can be calculated by the following formula:

latency = hit rate \* cache access time

+(1 - hit rate) \* lower level memory access time

Hit rate can be used as a rough comparison guideline for memory hierarchy performance. The higher the hit rate, it is expected the system will have a higher performance. Hit rate is inherently easy to find by simulation, as the system has only to determine whether a memory reference is a hit or a miss in a cache.

Due to the fact that the memory latency depends not solely on the hit rate, but also the cache access time, and lower level memory access time, for different computer systems, it will be misleading to compare hit rate for performance comparison. Eventhough a system may have a higher hit rate, we cannot conclude that it will have a higher performance, because the lower level memory access time is unknown. In [BC91], another measurement called Memory CPI (MCPI) was proposed. Memory CPI is the average number of cycles that the processor spent to retrieve a word from the memory hierarchy. For the MCPI figures reported in this dissertation, they are calculated by the following formula:

MCPI = CPI - CPI with infinite fast memory

CPI with infinite fast memory was found by stimulating a computer system with a 100% first level cache hit ratio, and the latency for the first level cache is zero cycle. That means, whenever the processor requests a word from the memory, the requested word will be presented to the processor without delay. The CPI with infinite fast memory shows the processing computation overhead of the program, which that figure depends on the complexity of the running program. MCPI is a fair comparison for cache performance, because it does not depend on the number of instructions in the program, and it does not depend on the time required by the processor to do arithmetic calculations also. Assumed, the clock rate of two systems are equal, their MCPIs can be compared directly, whereas, the lower the MCPI, the faster the memory response.

MCPI is harder to find by simulation compare with the hit rate, as the simulation has to be done in a cycle-by-cycle basis. Not only whether a memory access is a hit or a miss has to be determined, but the exact number of cycles that spent to fetch that memory request is required. When there are a number of memory levels in the system, and all these memory levels can initiate transfer in parallel, the demand on resolution of the simulator is great.

There was an analytical model presented in [MeM92], which used a simplified model to calculate the CPI with certain cache configuration parameters. However, that model is hard to extend to cover a system with cache prefetching algorithm. Chang and Hsu in [ChH94] had proposed a method to reduce the overhead in simulating hit ratio. Obaidat and Khalid in [ObK95] refined hit ratio into Solo Hit Ratio, Local Hit Ratio and Global Hit Ratio. Lim, Bae, Jang, etc. did an analysis on worst case timing for a RISC processor using cache memory in [LBJ95].

### 1.4 Cache Prefetching

The performance of cache memory can be improved by cache prefetching. Cache prefetching is cache system initiated memory transfer, which the cache system predicts that the processor will access certain memory location in the near future. When the cache prefetches are accurate, the hit rate of the cache system will be increased, and hence the MCPI can be reduced, because, more processor memory requests can be satisfied from the cache memory, instead of from the slower main memory.

In general, the memory location to be prefetched can be found by two categories of methods. One is from cache hint instruction embedded in the running programming. These hint instructions are inserted by the language compiler. When the compiler detects a loop, the compiler can insert hint instructions to prefetch those data that will be used in the next iteration. Because, those hint instructions are inserted by compiler, this category of prefetching is called software based prefetching. The accuracy of software prefetching is very high, as the compiler can perform rigorous analysis on the original source program, and the data to be accessed can be predicted with high precision. However, software based prefetching suffers from big overhead, as hint instructions are inserted in the program, they will in themselves increase the memory traffic and the processor has to spend time to fetch those cache hint instructions, although it will perform nothing on those instructions.

The other cache prefetching category uses pattern information from historical memory accesses. The cache management system keeps track of memory reference locations, and if a regular pattern is found, the later memory accesses can be predicted, and hence prefetching can be performed on those locations. This category is called hardware prefetching. Because there is no extra hint instruction in the program stream, there is no software overhead in hardware prefetching schemes. However, the performance of hardware prefetching algorithms depend on the ability to discover memory access patterns. It is one of the main goal of this dissertation to propose hardware prefetching algorithms for high performance cache system.

### **1.5** Organization of Dissertation

Related studies of cache memory and multi-level cache hierarchy will be reported in the next chapter. Previous works on software based and hardware prefetching algorithms for cache will also be discussed.

A multi-level memory hierarchy simulator was built to test prefetching algorithms studied in this dissertation. A brief discussion of the features of the simulator will be presented in the third chapter.

A few hardware prefetching algorithms for cache system are proposed in the forth chapter. The rationale to have a combined level one and two cache management system will be presented also in that chapter.

Eight benchmark tests in the SPEC92 suite were used to measure the performance of cache prefetching algorithms. In a particular benchmark, NASA7, as there are seven different programs inside it, a detail study on each program was done, and results gathered. All the benchmark results are to be presented in the fifth chapter. Total cycles consumed by each benchmark programs, Overall MCPI, partial MCPI due to Second Level Cache/Main Memory and hit rate for both level 1 and level 2 cache are included in that chapter.

A conclusion on the achievement of this dissertation will be presented in the sixth chapter, and future directions are proposed in that chapter also.

In the Appendix, data from the simulations are included there, and detail graphs of each benchmark tests can be found in that chapter.

7

# Chapter 2

# **Related Work**

In this chapter, research works done by other people would be summarized. Firstly, an introduction to the memory hierarchy used in a computer system would be discussed. Then, the configuration parameteres affecting the performance of cache memory would be presented. One of the important properties that made cache memory works is the locality principle. The classification of it would be discussed.

When cache memory does prove to work well in a broad range of programs, the reason why processor designers do not opt for a large on chip first level cache would be discussed. The trend is instead to implement on chip second level cache. Finally, three categories of cache prefetch algorithms would be presented at the end of this chapter.

### 2.1 Memory Hierarchy

If the memory references made by a processor to the memory system is truly random, the gain in performance by employing a small amount of faster memory complement with a large pool of slower memory will be minimal. Because the probability that the next memory reference will fall into the area contained in the fast memory depends solely on the ratio of size of the faster memory to the slower memory. The assumption that the faster memory is small in size, makes the above probability small, and therefore, it will not be useful to improve system performance.

From actual trace studies, we found that memory references are with patterns. We can make prediction to the forthcoming memory reference by history of previous memory references. Because of this property, if all the to-be-referenced data are stored in the faster memory, and the processor can access all the required data from that memory, there will be an appearance that the whole system is running out of the faster memory without knowing the existence of the slower memory.

The faster memory is small in size, we still need the large pool of slower memory to hold programs and data. We just have to devise an algorithm to decide when we should promote a piece of data from the slower memory to the faster memory, and in turns, which piece of data in the faster memory is to be replaced. The algorithm is simply a comparison on the probabilities that which memory address will going to be accessed, and take the content of that memory address into the faster memory.

By using similar arguments as above, we can have a hierarchy of memory layers, with the fastest memory and the smallest size at the top of the hierarchy, and each lower layer with progressively slower access time and larger in size. A hierarchy of layers is better than a two-layer architecture because system designers usually have more than two choices of memory with different cost/performance ratio and other physical characteristics. In general, the faster the memory, the higher the manufacturing cost and the converse is true for slower memory. Multilayer hierarchy is also desirable to minimize the penalty paid when a piece of data is requested by the processor but that cannot be found in the fastest memory. With the backup of layers of progressively slower memory, it will have a high chance that the required data can be found in an intermediate layer instead of the lowest one.

# 2.2 Cache Memory Management

The configuration of cache memory can be classified by a few parameters.

### 2.2.1 Configuration

#### **Block Size**

In order to manage a cache, it is seldom to use byte as unit to allocate memory in it, instead the whole cache is divided into *cache blocks*. The smallest unit to occupy in a cache is usually a block, although there are implementations of cache with sub-blocks. The size of a block is called *block size*, and in some literature, it is called *line size*. With a large block size, the number of blocks in a cache will be small, and vice versa. The hardware overhead to manage a cache, including the tag memory, valid bits, dirty bits, depends on the number of blocks. Therefore with a smaller block size, the overhead will be higher.

It is common to have block size in a cache selected to be integer multiples of its data bus width. With a 64-bit data bus, the block size in a cache may be 8 Bytes, 16 Bytes, 32 Bytes. The larger the block size, the higher the penalty when there is a cache miss. Because, the cache block allocated has to be fully filled from the lower level memory before the CPU can proceed to process, although there are implementations with "early available" feature, which the cache will selectively to load the portion of memory in the block that is requested by the processor.

A block in a cache will act as a small look ahead buffer, because when the

CPU access a memory location in a block, the bytes ahead will also be fetched into the cache. If the memory access is going forward, the next reference can be done in the cache. Therefore, in general, a large block size will gives a higher hit rate for the cache. However, a large block size will decrease the number of available blocks in a cache, and more conflicts in allocating blocks are expected, this will decrease the usefulness of the cache.

#### Set Associativity

When there is a cache miss, a cache block will be allocated from the cache to hold the data to be transferred from memory. Which blocks can be selected to use depend on the associativity of the cache. For cache with associativity of one, or called *direct mapped cache*, there is only one block that can be selected. The block number is found by a simple modulus calculation from the miss address. When the set associativity is larger than one, the cache is called a *set associative cache*, the mapping function from address to cache block number will be one-to-many.

When the processor requests a memory location, the same mapping function will be performed to find out the potential block which may hold the requested datum. The exact address of the memory reference will be compared with the tag value stored in the cache block, if there is a match, then that will be a cache hit. Because there is only one potential cache block per memory address in a direct mapped cache, the address comparison to be done is minimal.

Direct mapped cache is the simplest to be implemented in hardware [Hil88], however, because there are many addresses in the main memory that will be mapped to a single cache block, there will be conflicts in using a cache block. The situation is bad especially when two data to be used in a program loop maps to the same cache block, then, these two data will replace each other in turns and causing a lot of cache misses. The situation can be improved by allowing more than one cache blocks to serve a memory address. The number of blocks available to be used is called the associativity of the cache. With a cache of associativity two, that means, for every memory address, there are two blocks in the cache that can hold the data. The two blocks are termed a set, in a set associative cache.

Set associative cache poses difficulties in hardware implementation. When the processor requests a memory location, the cache has to check all the blocks that are allowed to serve that location in order to determine whether it is a cache hit [Hil88]. In order to speed up the access, all the address comparisons have to be done in parallel. With a 4-way set associative cache, there should be four comparators in the cache to make address comparisons. It is a hardware difficulty to have a high number of cache blocks in a set, because each comparator will impose electrical loading on the CPU address bus, and the maximum loading allowed is usually a limited figure.

In general, for first level cache, due to it is in the time critical path, the set associativity will not be a large number. However, in second level cache, it may be possible to implement set associative cache there. Yang and Adina in [YaA94] suggested an innovative method to choose the set associativity for cache, in order to minimize the chance for conflict miss.

#### Cache Size

The size of the cache memory is usually small. The *cache size* is determined by the block size, number of sets and associativity of the cache. The apparent cache size that can be utilized by programs can be found by the following formula:

cache size = block size \* associativity \* number of sets

The larger the cache size, usually, it will give the better performance. However with the same cache size, the difference in block size, associativity and number of sets will give different cache performance [PHH88]. Moreover, there is hardware overhead in implementing the cache tag memory, which is the area to hold the memory address of where the data in the cache block are come from. And additional memory has to be reserved to implement valid bits and dirty bits if the cache is a write back cache. These overheads are usually not reported in the cache size, but they do consume area in the CPU die.

When the first level cache is partitioned into two parts, namely *Instruction* cache (I-cache), and *Data cache* (D-cache), the optimal size for them are not necessarily the same. Stone, Turek, etc. in [STW92] studied the conditions to find out a good allocation of size to respective caches. Boleyn, Debardelaben, etc. in [BDT93] studied the usage of a split data cache designed for superscalar processors, in particular how the integer unit and the floating point unit in the CPU can access the data cache in parallel.

### 2.2.2 Replacement Algorithms

With direct mapped cache, if a piece of data is requested by the processor, and the memory location is not currently held in the cache, there is only one block suitable to hold that data. If the cache block selected is occupied by some other memory locations, the original data will be replaced. As there is no choice for which block is going to be replaced, there is no alternate replacement algorithm. However, with set associative cache, there are more than one blocks which can hold the requested data, the replacement algorithm determine which block is selected for replacement. In general, there are two types of replacement algorithm for set associative cache.

#### Least Recently Used

Least Recently Used replacement algorithm depends on the belief that the cache block which is least recently accessed will also have the least chance to be used again in the future. This assumption is usually true except in wield situations where the number of blocks required is larger than the set associativity of the cache.

In order to implement LRU replacement algorithm, the cache system has to keep track to the last access time of each cache block. By using a time tag for each cache block, when it is necessary to do a block replacement, the block in a set with the smallest time tag will be selected. To memorize a big time tag field is usually a waste of memory space, therefore, most processors implements pseudo LRU replacement algorithm. The size of the time tag field is small, and the cache memory will periodically clear out all time tags in the cache. Then, only a running counter with a few values is used to mark the last access time. With 3 to 4 bits of time tag fields, the performance of the cache will be very close to the true LRU replacement algorithm.

#### **Random Replacement**

Another category of replacement algorithm is *random replacement*. When a cache block has to be selected for replacement in a set associative cache, the cache system will select a random block in the set for replacement. Random replacement does not depend on the time tag field, and therefore to use it, the time tag field is not required in the cache system. With a sufficiently large cache, the performance of random replacement is very close to LRU algorithm.

There are other replacement algorithms designed for specific situations, such as *First In First Out*, or *Last In First Out*. Westerholz and Honal, etc. proposed in [WHP95] three methods to use processor runtime information to control the cache replacement algorithms. These replacement algorithms are not covered in this thesis.

#### 2.2.3 Write Back Policies

When a processor does only read operations on memory, the data content kept in the main memory will be the same as those kept in the cache. There is nothing to do when a cache block has to be replaced, the data content in the cache block can simply be discarded, because the main memory still has a copy of the latest value. However, when there are processor updates to certain memory locations, we have to deal with how the updated values are to be propagated to the main memory. Jouppli in [Jou93] studied the effect of different write policies including Write Through and Write Back cache.

#### Write Through Cache

Write Through is the simpler type of update policy. For every processor update to memory location, even when it is a cache hit, the updated value will write both to the cache memory and the main memory. The processor will only be allowed to proceed when both the cache update and main memory update are completed. In this type of update policy, the values kept in main memory are always the most update version, and the cache does not have to keep track whether there is processor update. On cache block replacement, the block selected to be replaced can simply be discarded.

The benefit of Write Through cache is a simpler hardware implementation, however it suffers from the fact that the cache will only be useful to shorten memory latency for read operations. Write operations are always treated as cache miss in terms of memory latency. From trace analysis, we found that there were a lot cases that the same memory address is repeatedly updated and only the last value is useful to the result. The processor performance can be improved if the cache writes to the main memory only when that cache block is replaced.

#### Write Back Cache

Write Back cache handles memory updates from processor more gracefully than the Write Through scheme. The updated values are stored only in the cache blocks and at the same time, a flag in the cache block called *Dirty Bit* is set. When that cache block is selected to be replaced, if the block is dirty as indicated by the Dirty Bit, the content in the cache block will be transferred to the main memory. If the processor updates a particular memory location in the cache for many times, all the updates will be made in the cache memory and the latency will be the speed of the cache.

The Write Back scheme should give a superior performance compare with Write Through one. However, if there are multiple processors sharing the same main memory but they have corresponding private cache, there will be coherence problem. That is, the content in the main memory is not always the most updated version, and the private cache in each processor may have their own copy of 'updated' values.

### 2.2.4 Cache Miss Types

Mark D. Hill in [Hil87] classifies cache miss into three categories.

#### **Compulsory Miss**

Compulsory Miss occurs when the processor references a memory location the first time. Assumed the cache memory supports on-demand fetch only, compulsory miss cannot be avoided, as it is the time when the data are read from the main memory and stored into a cache block.

#### **Conflict** Miss

Conflict Miss occurs when two data are mapped to the same cache set, and they replace each other from the cache. With direct mapped cache, only one cache block is available to each memory address, and if two memory addresses which mapped to the same cache block are accessed, they will incur conflicts. With set associative cache, where there are more than one cache blocks in a set, the conflict miss will only occur when the number of data items mapped to the same cache set is greater than the set associativity of the cache.

#### **Capacity Miss**

Capacity Miss refers to the situation that the cache memory is not large enough to hold the working set of the program. The only way to reduce capacity misses is to increase the cache size.

#### 2.2.5 Prefetching

Cache using on-demand fetching reduces the memory latency when the processor references a memory location the second time, when the content of that memory location is contained in the cache, then the access time for that location is of the speed of the cache. In order to further improve the memory access time, the cache system can initiate pro-active prefetching from the main memory. If the prefetched data are used by the processor in the future, the memory latency for the first access will also be the speed of the cache. Prefetching is workable as the processor does not access memory in constant pace. Usually, there are idle cycles when the processor is doing computation, and the memory bus is free. Prefetching algorithm makes use of these idle bus cycles, and transfer data from main memory to the cache.

Just the same as processor initiated memory request, cache prefetching usually

consumes more than one cycle to complete the transfer of a cache block. There will be a situation when the cache is performing prefetching but the processor would make a memory request. In order to let the processor has the highest priority to retrieve the requested data, most cache prefetching algorithms will abort the prefetch transfer in place and give way to the processor memory request.

Prefetching algorithm is one of the focus in this thesis, in later paragraphs, we will discuss some common cache prefetching algorithms. We are going to discuss the properties of memory reference pattern, including the nature of them, and the classification of patterns.

### 2.3 Locality

From program trace analysis, when a processor accesses a certain memory address, there is a high probability that the memory references in the near future will fall into close vicinity of the current memory access, we call this property locality. Locality can be further classified into two types, one of them is related to space and is called *Spatial Locality*. The other one is related to time and is called *Temporal Locality*.

#### 2.3.1 Spatial vs. Temporal

For machine instruction execution, there is very high tendency that the instruction reference pattern will be linear, which the memory address following the current one will be referenced in the next cycle. The exception will be some branch instructions. For conditional branches, the backward branch has a more than 80% of chance to be a taken branch due to most backward branches are actually the last statement in program loops. Whereas for a forward branch, the chance for the branch to be taken is around 50%. These forward branches are usually instructions used in if-then statements.

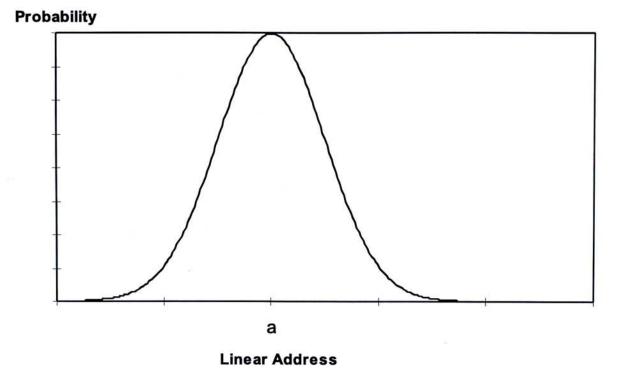

In general, with a current access to memory address a, the probability that a future memory access to address  $a + \delta$ , where  $\delta$  is a small integer, is very high. As  $\delta$  becomes larger, the probability for that address to be accessed will be diminished. The probability distribution across the memory address will have the shape as in figure 2.1.

**Probability Distribution of Future Access**

Figure 2.1: Probability Distribution for Spatial Locality

When the processor accesses memory address a, the cache memory should hold the contents from memory around a, then, the probability that the processor can find the future memory references in the cache will be high. We termed this kind of property Spatial Locality. The block size in a cache serves the spatial locality property by retrieving in advance some bytes around the referenced location.

Other than instruction reference, data reference also exhibits spatial locality. In programs using matrices or arrays, it is common to have program loops to process the whole matrix or array. The memory access pattern for data reference will follow the prediction of spatial locality.

For instructions in a program loop, these instructions have a high chance to be used again in the next loop iteration. The probability depends on the loop iteration count. For some constants used in a program, the same data may be reused in the future. With the following code fragment:

for (i=0; i<100; i++)

a[i] = b[i] + c;</pre>

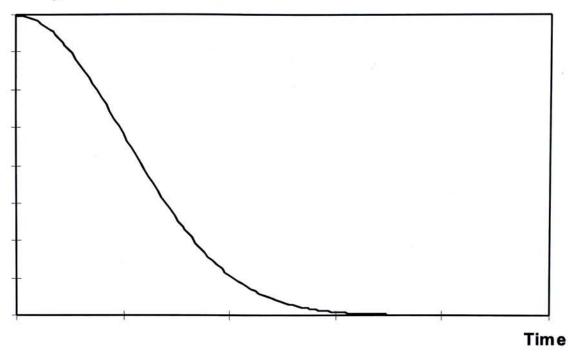

The content in c is reused for 100 times and so do the instructions to be performed in the loop. When a memory location is accessed, the same location has a high probability to be accessed again in a short span of time. The probability for that location to be accessed will be decreased with time, that means, when a memory address is not accessed for a long time, that address will have a lower chance to be called in the near future. That property of memory reference is called *Temporal Locality*. The probability distribution of future access to the same address will have a shape of figure 2.2.

When the processor accesses memory address a, the cache memory should hold the content in address a for future reference. When there is a short of space in the cache, the cache should replace the datum with the lowest chance to be accessed in the future. In general, the selected datum to be replaced will be that of the least recently used.

#### 2.3.2 Instruction Cache vs. Data Cache

In order to make a fast processor, it is common to have separate instruction cache and data cache. There are a few reasons to support the split cache configuration. The first one is for memory transfer bandwidth consideration, with two separate

#### Probability Distribution of Future Access

Figure 2.2: Probability Distribution for Temporal Locality

caches serving instruction and data separately, the available memory transfer bandwidth is doubled compare with a unified cache. For machine instruction with data access, the processor has to fetch the instruction code and data to be accessed from memory. If the access path to instruction code and data is separated, both accesses can be carried out in parallel. In particular, the separation of instruction and data paths is called Harvard Architecture [Goo89].

The parameters for cache configuration that will give the best performance are not the same for instruction and data cache in general.

From the above discussion, it is evident that for instruction cache, both the spatial locality and temporal locality will have dominant effect, and it will be seldom to have programs jumping around randomly in the code. The instruction cache should hold the next instructions to be needed, and the size of an instruction is processor dependent. With today's RISC processor, the instruction size is usually 32-bit in length, the block size for instruction cache is best to be multiples of 32-bit.

For data cache, the best block size depends on the data structure used in the program, and it will be varied from program to program. When a program uses small data, such as integers and floating point numbers, the optimal block size can be smaller, just to be enough to hold these small data. On the other hand, when a program processes big data records, the data cache block cache should be correspondingly larger. Therefore, in order to achieve optimal performance, the separation of instruction and data cache will allow for different parameters to be used.

The third reason to have separate instruction and data cache is to avoid inter-displacement between instruction and data. The number of instructions in a program loop varies together with the data to be processed in that loop. In general, the size of instructions that will be frequently reused added to the size of data that will be referenced in a short span of time constitutes the *working set* for a program. If instruction and data cache is mixed together, it will have a situation that the fetching of some instructions may displace a portion of data already in the cache. By separation of instruction and data cache, these two types of memory will not be in conflict fighting for space in a cache.

As data reference in a program may not exhibit the same locality property as instruction reference, Chen in [BC91] further classified the data access pattern into the following categories:

#### Scalar Stride

Stride is defined as the distance in address between a previous memory access and the current one. *Scalar Stride* refers to the situation when a simple variable is used inside a program loop. In general, scalar access will occur when a constant is used, or a running total is accumulated to a memory address. The following program fragments show a scalar access to memory location holding variable c.

```

for (i=0; i<100; i++)

a[i] = b[i] + c;</pre>

```

```

for (i=0; i<100; i++)

c += a[i];</pre>

```

### Zero Stride

Zero stride refers to the situation when an element in an array is referenced repeatedly within a program loop. The difference between zero stride and scalar is that the subscript in the array of a zero stride access will not be changed in the program loop, but it may be changed outside the loop. The following program fragments show a zero stride access to memory location holding array c.

```

for (i=0; i<100; i++)

a[i] = b[i] + c[j];</pre>

```

```

for (i=0; i<100; i++)

c[j] += a[i];</pre>

```

Zero stride and scalar access show the property of temporal locality, however, with sufficient number of registers in a CPU, the repeatedly referenced datum will usually be set aside in a CPU register, and the memory system will only be updated when the final result is saved. The repeat memory reference pattern will only be visible when the CPU cannot hold all the temporary results in registers and some of them has to be written out to memory.

### **Constant Stride**

Constant Stride means the address distance to the next memory reference is a constant compare with the previous memory access. This kind of pattern is typical for array or record access. As the current program loop may process only a single member in records, the data reference will jump in the forward direction with a constant distance between accesses. With the following code fragment, the memory access to array a and b shows the constant stride feature.

for (i=0; i<100; i++)

a[i] = b[i] + c;</pre>

From main memory, the constant stride reference pattern can be shown in figure 2.3.

The variable d is termed as the stride of the memory reference to array a (and D is the stride for array b). If d is smaller than the block size of the cache, that means in each cache block, there are more than one elements in it, then the transfer of the cache block provides prefetching property for the memory reference. If data consumption rate for the processor is slower than a cache block filling time, the memory latency for each reference will be that of the cache block, at that location, the memory latency will be that of a cache block, or the main memory access time.

When the stride d is larger than the cache block size, for every memory reference, if the content of the memory location is not already in cache, there will be a cache miss, the memory latency will be very poor for this type of memory accesses. In order to improve the situation, we can make use of a larger block size, in order to encapsulate more than one elements in a cache block, however, it may be impractical, as the stride d may be a very large number, approaching

Figure 2.3: Constant Stride Reference Patterns

or even larger than the cache size, it will not be good to have a small number of blocks in a cache, as the granularity is too coarse.

Another method to improve memory latency for large stride access is through prefetching. In this thesis, most prefetching algorithms target on the constant stride access pattern, and their effect will be highly visible in large stride cases.

### **Irregular Stride**

The third type of memory access pattern is *irregular stride*. In programs using linked list or memory pointer operation, the stride value will vary from time to time. The following code fragment shows an irregular stride access on ptr.

```

for (ptr=start; ptr!=NULL; ptr=ptr->next)

```

```

ptr->member1 = ptr->member2 + ptr->member3;

```

As a particular record address depends on the previous record's next pointer, we cannot make prediction on where the next record is until that one is accessed by the processor. There are studies to tackle irregular stride access pattern with prefetching, but they are out of the scope of this thesis.

# 2.4 Why Not a Large L1 Cache?

When today's processors can have tens of millions of transistors on a single die, it will be natural to use part of the available transistors to implement on-chip cache [Mel95]. On-chip cache has a few benefits over off-chip cache. On-chip cache has a shorter physical distance to the CPU core, and the transmission time spent on electrical wires is shortened. On-chip cache usually has a wider bus width compare with off-chip one, because there is lesser constrain in wiring inside a chip, then to go off-chip. The current generation of processors already has hundreds of pins to connect with the main board, it will be very difficult to add more pins to the packaging of chips. On-chip cache can make use of dedicated bus to communicate with CPU core, but for the same reason as the above, it may not be possible to reserve a large number of pins for dedicated off-chip cache bus.

Whereas on-chip is justifiable, but why not to build a large on-chip single level cache? In fact, it is impractical to build single level cache up to certain size with some technologies (eg. GaAs) [BW88]. We will discuss two considerations in the following paragraphs.

## 2.4.1 Critical Time Path

From a hardware perspective, a large size cache is actually made up of smaller size memory chips. All these memory chips exert electrical loading onto the address bus, data bus, and control bus of the CPU core. However, the CPU core is usually designed to drive a specific number of electrical loadings only. In order to drive a large number of chips, a component called bus driver can be inserted between the bus and the memory chips. Bus driver can boast the driving power of the bus to a few times of the original value. But bus driver incurs timing delay. With today's processor of running frequency around 100MHz, each cycle is merely 10ns, and the timing delay of bus driver is in the range of a few nano second. With a really large cache, it may require a two-tier or more bus drivers, which a clock cycle may already be spent in them. This factor limits the size of first level cache, because the memory latency will be significantly increased by inserting one more cycle per memory access.

A better solution is to use multi-level cache hierarchy. The first level cache is kept to be small in size, and serving the most likely requested data. Another layer of cache serves the less likely requested data. Then, the number of chips on the first level cache can be kept to a minimum, the number of bus drivers and hence the timing delay can be reduced.

### 2.4.2 Hardware Cost

To build memory cells with access time in the nano second range is expensive. For dynamic memory cell, only a capacitor is required to hold a binary bit of datum. But dynamic memory cell is slow in access time, with current technology, the access time is around 50-70 nano second. Static memory cell has a faster access time. With 2 transistors per binary bit, they can build a memory cell with access time in the range of 20 nano second. In order to build still faster memory cells, a 6-transistor architecture can be used. However, the number of transistor count will be tripled.

The first level cache is usually multiple-ported in current design, in order to let different units in the CPU to access the first level cache in parallel. To build multiple-ported cache, one way is to duplicate the memory cells, then each bank of memory cells can serve a request from different units. The result is that, in order to make a very fast first level cache matching the cycle time of the CPU and to be multiple-ported, a lot of transistors are used to build memory cells. The number of transistor count to build a single memory cell for first level cache may be a few times the required number of transistor to build a second level cache. Therefore, only the most frequently requested data are justified to be placed into the first level cache. Other data will be best to be placed into slower, but cheaper to build, second level cache or main memory [Wan89].

# 2.5 Trend to have L2 Cache On Chip

The above discussion shows why a large on-chip level one cache is not practical, instead with enough transistor budget, CPU designers tend to build multi-level cache on the CPU die. On chip second level cache is beneficial to the processor performance, as firstly, the total cache size can be increased without adding extra electrical loading on the CPU core. Secondly, the second level cache can be made of cheaper but slower design, because the majority of memory references are expected to be served by the first level cache. Thirdly, the on chip second level cache can make use of CPU signals that will not be available off chip. These CPU signals include current program counter, instruction type, addressing mode, name of CPU registers in use for the current instruction, branch prediction from the branch unit, prefetch queue information, etc. These CPU signals will be too cumbersome to be available off chip, as the number of pins required will be too large. These signals can help in making prediction for future CPU memory access. New prefetching algorithms can be devised for the cache to prefetch memory locations to be required in the future. There were previous studies ([SL88], [MeM95], [TaS94], [Liu94], [HaJ92], [NeA91], [Sez93], [ChK91], [BuK90], [APB92], [OyW92], [JoW94]) for performance on multi-level cache hierarchy, although they may not focus on the on chip second level cache design. For on chip second level cache, there were studies in [HuO94], they tried to find out the best configuration parameters for on chip multi-level cache, but not suggesting cache prefetching algorithm. The necessity to have more than a single level of cache to bridge the speed disparity is there for a long time.

The following are a few examples that commercially available processors have on-chip second level cache.

## 2.5.1 Examples

### DEC Alpha 21164

Digital's Alpha 21164 CPU has an 8k Bytes on-chip first level instruction cache, with 32 Bytes blocks. The first level instruction cache is direct mapped. There is also an 8k Bytes on-chip first level data cache. The block size is 32 Bytes, and the update policy is write through. There are two read ports on the data cache, that means two memory references can be outstanding simultaneously.

The Alpha 21164 CPU also contains a second level cache of 96k Bytes. The second level cache is a mixed cache shared by instruction and data. The on chip second level cache uses write back update policy. The on-chip second level cache uses 64 Bytes blocks and it has a set associativity of 3.

The following is an extraction from the designers of Alpha 21164 CPU to justify the reason to have two level cache architecture instead of a large single level cache.

"Two-level Data Cache. Many workloads benefit more from a

reduced latency in the data cache than from a large data cache. We considered a single-level design for a large data cache. For circuit reasons, physically large caches are slower than small caches. To achieve a reduced latency, we chose a fast primary cache backed by a large second-level cache. As a result, the effective latency of reads is better in the Alpha 21164 CPU chip than it would have been in a single-level design.

The two-level data cache has other benefits. The two-level design makes it reasonable to implement set associativity in the second-level cache. Set associativity enables power reduction by making data set access conditional on a hit in that set. The two-level design also allows the second-level cache to hold instructions, which makes a larger instruction cache unnecessary."

The Alpha 21164 CPU also contains logic to control off-chip cache. If that level of cache is implemented, it will become third level cache. The off-chip cache can have size range from 1MBytes to 64MBytes. The third level cache is direct mapped, as the number of pins available on the CPU package is limited. The third level cache uses write back update policy.

#### Intel Pentium Pro

The Intel Pentium Pro contains an 8k Bytes on-chip instruction cache and an 8k Bytes on-chip data cache. The two on-chip first level caches are non-blocking, means the processor can proceed to process other instructions even when there is a cache miss. Only when there is dependency on the cache miss data that the processor has to stall and wait for the cache miss to be served.

The Intel Pentium Pro processor also contains a 256k Bytes or a 512k Bytes on-package second level cache. The second level cache is actually implemented on a separate die as the CPU core, however, all the CPU core together with the second level cache dies are housed in a single package. The 2-die approach is a tradeoff between size of second level cache and the ease of manufacturing. The 256k Bytes second level cache is made of 15.5 million transistors and the CPU core is made of 5.5 million transistors. If all these 21 million transistors are made on the same die, the yield will not be commercially feasible for current technology. On the other hand, in order to make a large second level cache, a large number of transistors is required. The same packaging technique to house the CPU core and the second level cache makes the communication between them as fast as possible. And due to wire bondings are used to connect the 2 dies, there are more signals that can be propagated from the CPU die to the second level cache, because connection pins are not required.

## 2.5.2 Dedicated L2 Bus

There are some current microprocessors with on-chip second level cache control logic, but there is no memory cell implemented on chip. This can be a balance point to have the benefits of on-chip CPU signals for second level cache management but does not incur the production difficulties to implement a large number of memory cells. The following are examples of this category of processors.

### **MIPS R10000**

The MIPS R10000 processor has a 32k Bytes 2-way set associative, 2-way interleaved on-chip first level data cache with LRU replacement policy. The block size of the on-chip data cache is 32 Bytes. The update policy of the on-chip data cache is write back. The MIPS R10000 also has a 32k Bytes 2-way set associative instruction cache. The block size of the on-chip instruction cache is 64 Bytes. There is also a dedicated 128-bit second level cache bus with all required signals to drive off-chip static memory chips. The cache management logic for the second level cache is built on chip. The cache implemented on the MIPS R10000 processor is non-blocking.

### PowerPC 620

The IBM/Motorola PowerPC 620 processor has a 32k Bytes 8-way set associative, non-blocking data cache. The on-chip data cache can be configured to use write back or write through update policy. There is a separate 32k Bytes 8-way set associative on-chip instruction cache. In the CPU die, there is second level cache management logic, the external interface is a dedicated second level cache bus with 128-bit bus width, and implementing a direct mapped mixed instruction and data off-chip cache.

#### Nexgen Nx6x86

The Nexgen Nx6x86 is an Intel Pentium compatible processor with 32k Bytes 2way set associative, dual-ported on-chip first level data cache. The Nx6x86 also contains a 16k Bytes 2-way set associative on-chip first level instruction cache. There is on-chip second level cache management logic, and the interface to the off-chip memory chips is a dedicated second level cache bus with bus width of 64 bits. The off-chip second level cache is a mixed instruction and data cache using write back update policy.

# 2.6 Hardware Prefetch Algorithms

Due to locality property, it is possible to make predictions to future processor memory references by observing the memory access pattern. *Hardware Prefetching* makes use of historical data to deduce future memory access locations. In order to reduce the memory latency for compulsory miss, prefetching can be performed on cache memory when the memory bus is idle. If the prediction of future memory reference is accurate, the memory access time will be that of the cache memory instead of the slower main memory.

## 2.6.1 One Block Look-ahead

Alan Jay Smith in [Smi82] studied a general algorithm for hardware prefetching. The idea is when the processor accesses a cache block i, due to spatial locality, cache block i + 1 will also likely to be referenced in a short time. The prefetching algorithm is to trigger the transfer of cache block i + 1 from main memory if it is not already in cache. This type of prefetching algorithm is called *One Block Lookahead* (OBL). There are three variations in OBL that in [Smi82] had studied. The variation depends on when the prefetch will be performed. One way is to prefetch cache block i + 1 if reference to cache block i causes a cache miss, it is called *Prefetch On Miss.* The other way is to prefetch cache block i + 1 if reference to cache block i causes a cache hit, it is called *Prefetch On Hit.* The third way is to prefetch cache block i + 1, no matter reference to cache block i is a cache hit or miss, it is called *Always Prefetch.*

The effect of OBL is similar to a cache system with larger cache block size. Just the memory transfer is broken down into smaller pieces in OBL case, whereas large cache block size initiates a lengthy transfer when there is a cache miss. However OBL improves over large cache block size by maintaining the larger number of blocks in a fixed size cache. The access to cache block i is treated as a confirmation that the cache block may be accessed again in the future due to locality.

OBL and large cache block size work well in instruction cache, as the reference pattern has high sequentiality. However, in data cache, the stride value varies from case to case. In order for large cache block size to reduce compulsory miss, the stride value should be smaller than the cache block size, or every access to a new datum will cause a cache miss. For OBL, the stride value has to be smaller than twice the block size, because whenever cache block i is referenced, cache block i + 1 will be fetched, this effectively doubles the apparent block size. With large stride value, both OBL and large cache block size will perform very poor, as the prefetching in OBL and the large cache block size will bring in pollution to the cache, the cache hit rate will be decreased.

In [DDS95], Dahlgren, Dubois, etc. enhanced the OBL scheme to work on a shared memory multiprocessor environment. They proposed a method to adjust the look ahead level to tune the cache prefetch algorithm behavior.

With a splitted instruction and data cache design, there were studies ([YoS93], [YeP93]) of cache prefetch algorithm for the instruction cache. They focused on how the cache prefetch algorithm can continue to prefetch when there are branch instructions in the program.

### 2.6.2 Chen's RPT & similar algorithms

Baer and Chen in [BC91] proposed a hardware prefetching algorithm basing on a *Reference Prediction Table* (RPT), a *Branch Prediction Table* (BPT) and a *Look-ahead Program Counter* (LA-PC). The RPT keeps track of CPU instructions to issue memory accesses, the difference in memory address from previous access and a state field. The LA-PC works with the BPT to make prediction to future *Program Counter* (PC) value, if the predicted PC address has a corresponding entry in the RPT, the future memory access location can be calculated by the formula

future memory access location = previous memory access location + stride That future memory access location will be prefetched into the cache memory, and if the LA-PC keeps a far enough distance from the actual PC, the prefetch may have time to complete the memory transfer before the datum is actually requested by the processor.

The state field in each RPT entry is to filter out non-constant stride memory accesses and prevent the prefetching algorithm to issue erratic prefetches to pollute the cache memory. The state field has the following possible values:

- initial

- transient

- steady

- no prediction

Cache prefetch will only be issued for RPT entry in steady state.

Fu and Patel in [FP91] studied the stride values for memory access in vector processors. They measured the miss rate with no-prefetch, sequential-prefetch, and stride-prefetch algorithms. The sequential-prefetch and stride-prefetch algorithms reduced the cache miss rate over no prefetch case. Between the sequential prefetch and stride prefetch algorithms, the later one had a better performance due to that one can make accurate predictions to large stride access pattern.

Fu etc. in [FPJ92] further the above architecture to support non-vector processor by using a Stride Prediction Table (SPT). The structure of SPT is similar to the RPT proposed by Chen. in [BC91].

### Issues in Chen's RPT