#### REPLACEMENT AND PLACEMENT POLICIES FOR PREFETCHED LINES

By Sze Siu Ching

#### A DISSERTATION

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF PHILOSOPHY DIVISION OF COMPUTER SCIENCE AND ENGINEERING THE CHINESE UNIVERSITY OF HONG HONG JUNE 1998

Copyright © 1998 by Computer Science and Engineering, the Chinese University of Hong Kong All right reserved.

### Acknowledgements

I want to give my hearty thanks to my family.

I also want to give my hearty thanks to Dr. Gilbert H. Young, Mr. S. C. Lau, Mr. S. Y. Yiu and especially to Ms. Priscilla K. Chan.

It is clear there are many to whom I owe my thanks and acknowledgments. In order not to miss anyone of them, I just want to say thanks.

Thanks for those who have helped me, taught me, carried me and supported me during my studies. Thanks a lot.

### Abstract

As a result of technology advance, there is a widening gap between the rate at which a processing unit can consume operands and the rate at which the memory system can supply them. The introduction of cache helps alleviate this problem, and the design of cache memory is very critical to the overall system performance. Due to the limited space on the processors, on-chip caches are usually small. Therefore, the cache space should be used carefully and efficiently. Accurate prefetching and careful replacement of cache lines <sup>1</sup> are essential to improve the performance. In order to further improve the cache performance, different prefetching algorithms for cache have been proposed[BaC91] [KlL91] [Smi78a]. With prefetching, data could be available before their actual use. However, due to the large volume and the random behaviour of data usage, it is difficult to prefetch data accurately and this results in cache pollution.

Lau [Lau96] has proposed an accurate prefetching scheme, the Instruction Opcode and Addressing Mode Prefetching (**IAP**), which makes use of the future reference patterns embedded in certain instructions. Further to their study, it is also found that most prefetched data by the IAP scheme are likely to be referenced only once. Therefore, we proposed to use a mixed replacement policy to use together with the IAP scheme, to minimize the number of thrashing misses. Using both Least Recently Used (**LRU**) and Instant Zero (**IZ**) replacement algorithms with the IAP scheme outperforms the result of using LRU only.

Furthermore, in order to optimize the benefit of temporal locality and minimize

<sup>&</sup>lt;sup>1</sup>A line is a block of data in context of the cache. Usually, line size is the same as block size. In our paper, *block* refers to data located in memory or lower-level caches, *line* refers to the data in level 1 cache. However, they are interchangeable.

the cache pollution problem, another hardware replacement design is presented in this thesis. We propose a priority pre-updating scheme, which is used to update the priorities of cache lines prior to their normal updating situation. Simulation experiments are done wit this priority pre-updating scheme in cache model with prefetch-on-miss prefetching scheme. From the results, it is found that priority pre-updating helps minimizing the number of thrashing misses, optimizes the benefit of temporal locality and reduces cache pollution. In order to obtain promising cache performance improvement, we add a victim cache to hold those fresh prefetched lines that displaced from the data cache. The experimental results show that using priority pre-updating with the victim cache can achieve up to 50% reduction in memory delay.

Beside the research on replacement of cache lines, we propose another hardware design, which concerns the placement of IAP lines. The cache lines prefetched by the Instruction Opcode and Addressing Mode Prefetching pose a referenced-once property, i.e., most of them are referenced one and only one time before the program terminates. Owing to this special reference behavior, a prefetch cache, which is dedicated to prefetched lines by Instruction Opcode and Addressing Mode Prefetching scheme, is implemented separately. The prefetch cache can reduce memory delay time up to 99%.

# Contents

| 1        | Introduction                     |                                                      |           |  |

|----------|----------------------------------|------------------------------------------------------|-----------|--|

|          | 1.1                              | Overlapping Computations with Memory Accesses        | 3         |  |

|          | 1.2                              | Cache Line Replacement Policies                      | 4         |  |

|          | 1.3                              | The Rest of This Paper                               | 4         |  |

| <b>2</b> | ΑB                               | Brief Review of IAP Scheme                           | 6         |  |

|          | 2.1                              | Embedded Hints for Next Data References              | 6         |  |

|          | 2.2                              | Instruction Opcode and Addressing Mode Prefetching   | 8         |  |

|          | 2.3                              | Chapter Summary                                      | 9         |  |

| 3        | Mo                               | Motivation                                           |           |  |

|          | 3.1                              | Chapter Summary                                      | 14        |  |

| 4        | $\mathbf{Rel}$                   | ated Work                                            | 15        |  |

|          | 4.1                              | Existing Replacement Algorithms                      | 16        |  |

|          | 4.2                              | Placement Policies for Cache Lines                   | 18        |  |

|          | 4.3                              | Chapter Summary                                      | 20        |  |

| 5        | $\operatorname{Re}_{\mathbf{I}}$ | placement and Placement Policies of Prefetched Lines | <b>21</b> |  |

|          | 5.1                              | IZ Cache Line Replacement Policy in IAP scheme       | 22        |  |

|          |                                  | 5.1.1 The Instant Zero Scheme                        | 23        |  |

|          | 5.2                              | Priority Pre-Updating and Victim Cache               | 27        |  |

|          |                                  | 5.2.1 Priority Pre-Updating                          | 27        |  |

|          |                                  | 5.2.2 Priority Pre-Updating for Cache                | 28        |  |

|   |     | 5.2.3                                       | Victim Cache for Unreferenced Prefetch Lines                | 28 |

|---|-----|---------------------------------------------|-------------------------------------------------------------|----|

|   | 5.3 | Prefeto                                     | ch Cache for IAP Lines                                      | 31 |

|   | 5.4 | Chapte                                      | er Summary                                                  | 33 |

| 6 | Per | forman                                      | ce Evaluation                                               | 34 |

|   | 6.1 | Metho                                       | dology and metrics                                          | 34 |

|   |     | 6.1.1                                       | Trace Driven Simulation                                     | 35 |

|   |     | 6.1.2                                       | Caching Models                                              | 36 |

|   |     | 6.1.3                                       | Simulation Models and Performance Metrics                   | 39 |

|   | 6.2 | Simula                                      | ation Results                                               | 43 |

|   |     | 6.2.1                                       | General Results                                             | 44 |

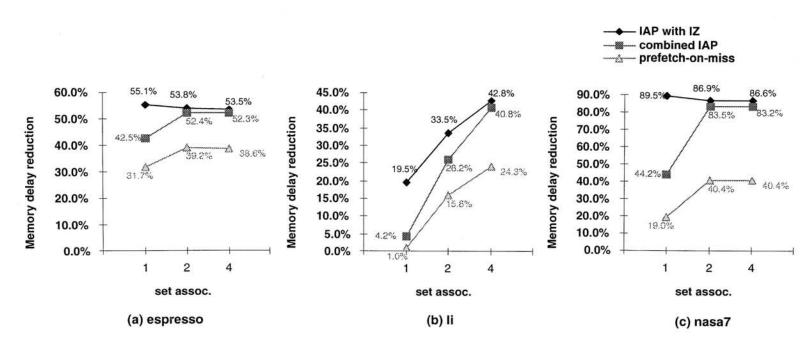

|   | 6.3 | Simulation Results of IZ Replacement Policy |                                                             |    |

|   |     | 6.3.1                                       | Analysis To IZ Cache Line Replacement Policy                | 50 |

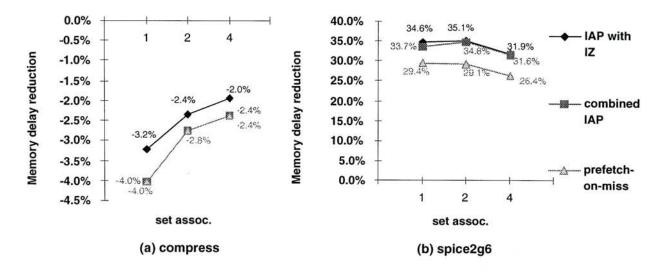

|   | 6.4 | Simula                                      | ation Results for Priority Pre-Updating with Victim Cache . | 52 |

|   |     | 6.4.1                                       | PPUVC in Cache with IAP Scheme                              | 52 |

|   |     | 6.4.2                                       | PPUVC in prefetch-on-miss Cache                             | 54 |

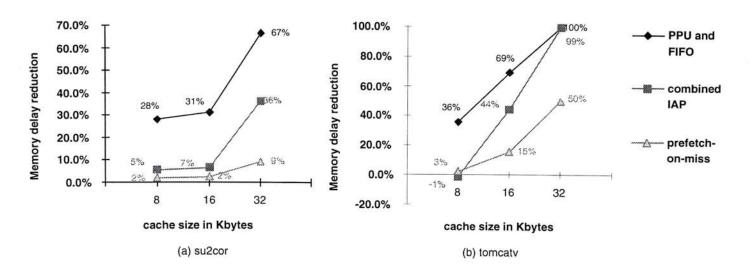

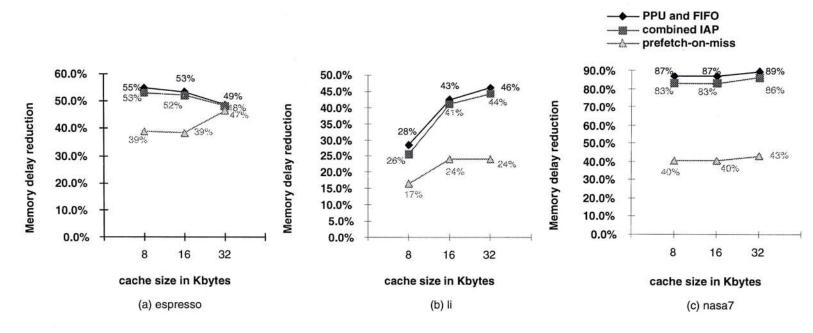

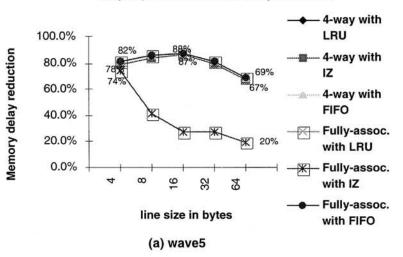

|   | 6.5 | Prefet                                      | ch Cache                                                    | 57 |

|   | 6.6 | Chapt                                       | er Summary                                                  | 63 |

| 7 | Arc | hitectu                                     | are Without LOAD-AND-STORE Instructions                     | 64 |

|   |     |                                             |                                                             |    |

| 8 | Co  | nclusio                                     | n                                                           | 66 |

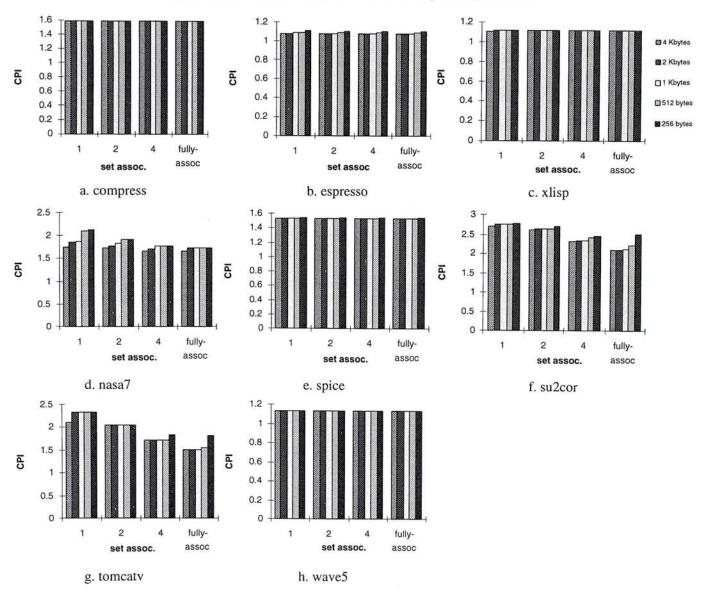

| A | CP  | I Due                                       | to Cache Misses                                             | 68 |

|   | A.1 | Varyii                                      | ng Cache Size                                               | 68 |

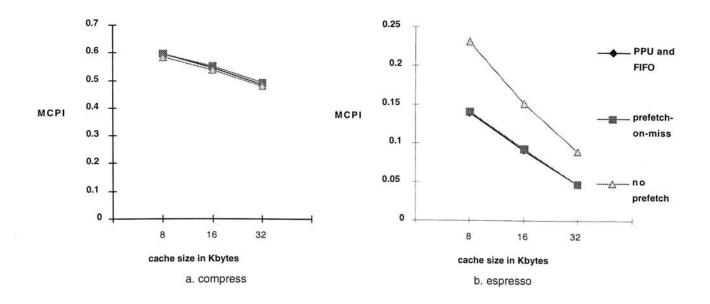

|   |     | A.1.1                                       | Instant Zero Replacement Policy                             | 68 |

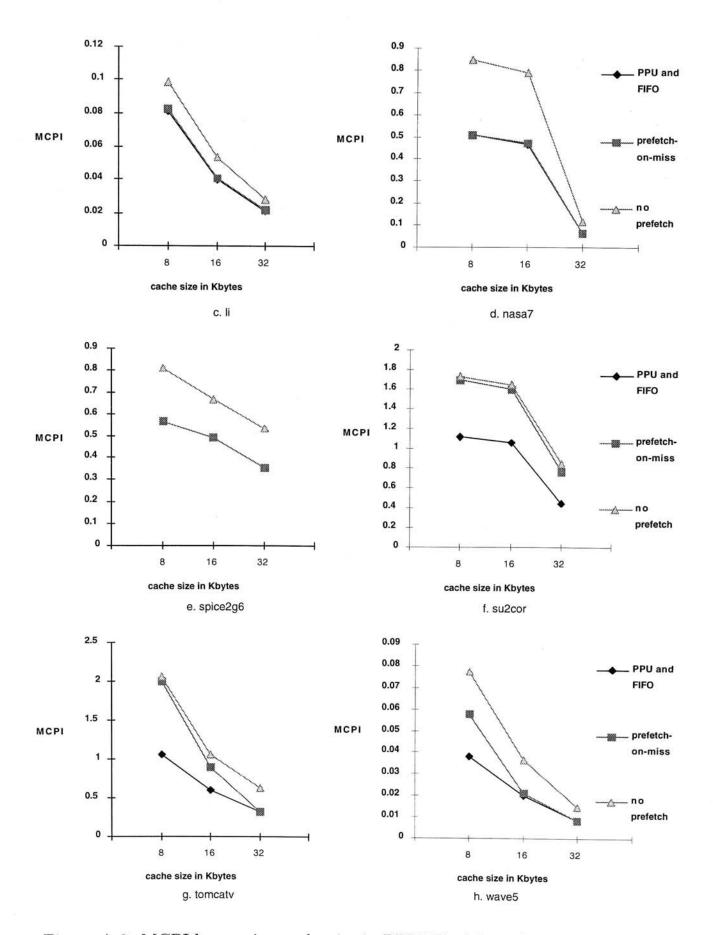

|   |     | A.1.2                                       | Priority Pre-Updating with Victim Cache                     | 70 |

|   |     | A.1.3                                       | Prefetch Cache                                              | 73 |

|   | A.2 | Varyi                                       | ng Cache Line Size                                          | 75 |

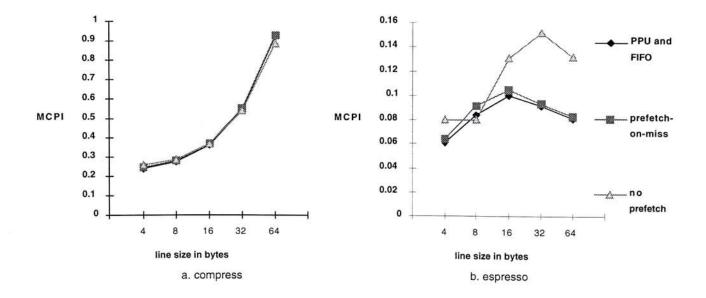

|   |     | A.2.1                                       | Instant Zero Replacement Policy                             | 75 |

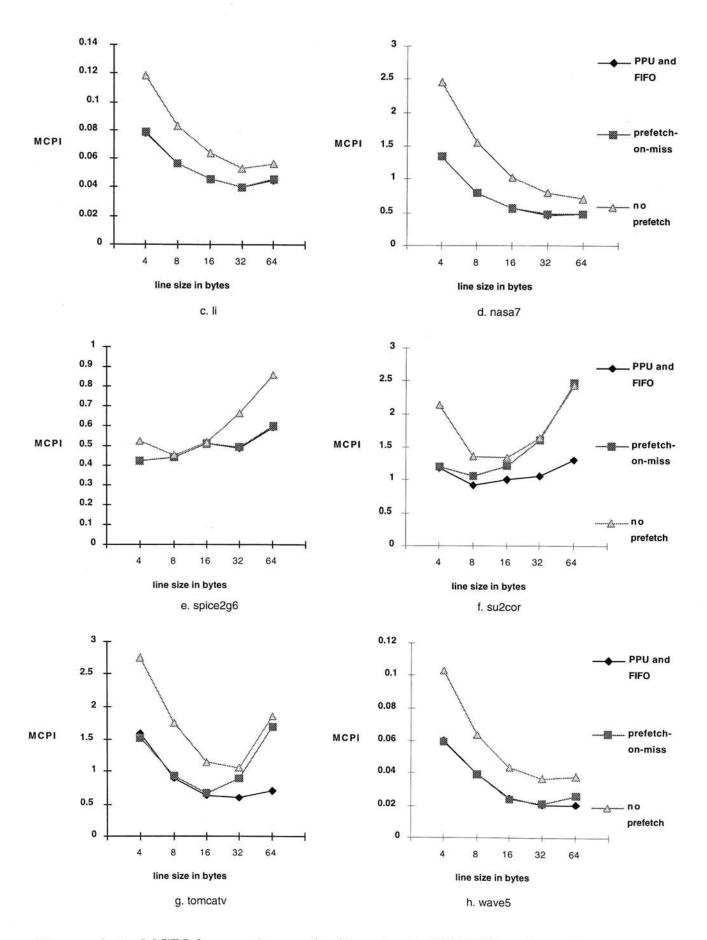

|   |     | A.2.2                                       | Priority Pre-Updating with Victim Cache                     | 77 |

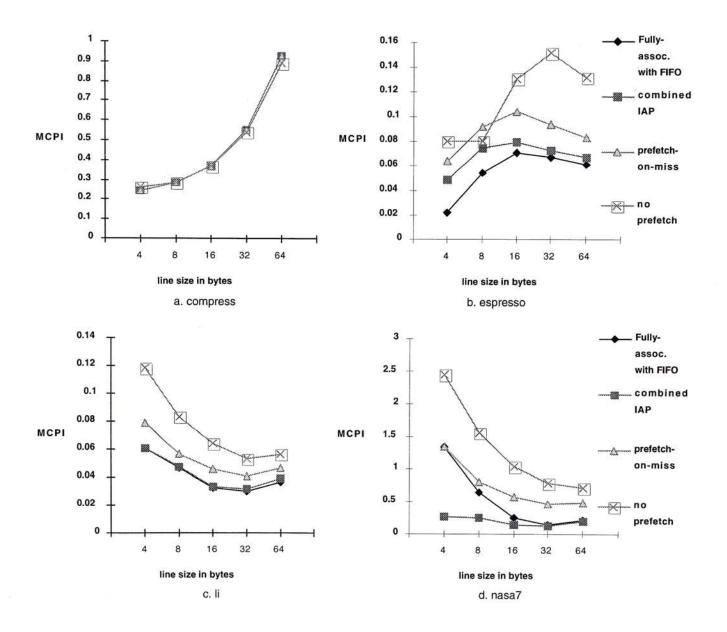

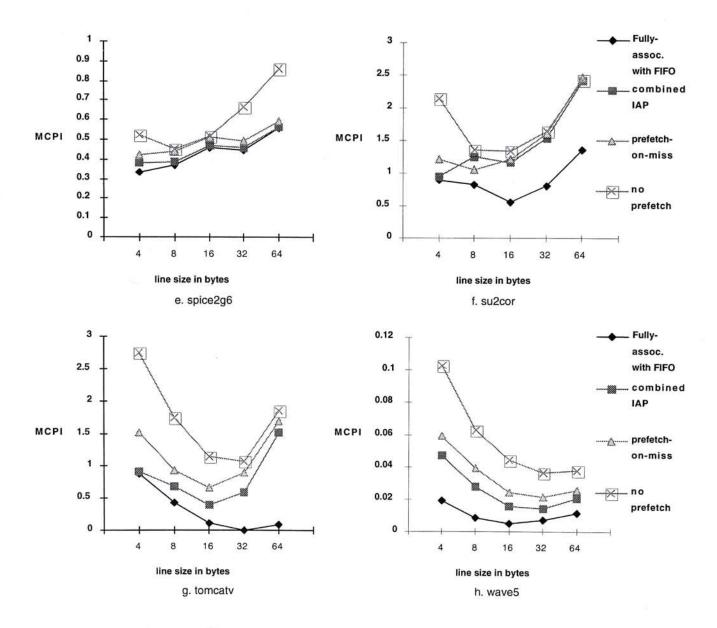

|   |     | A.2.3                                       | Prefetch Cache                                              | 80 |

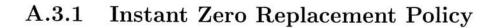

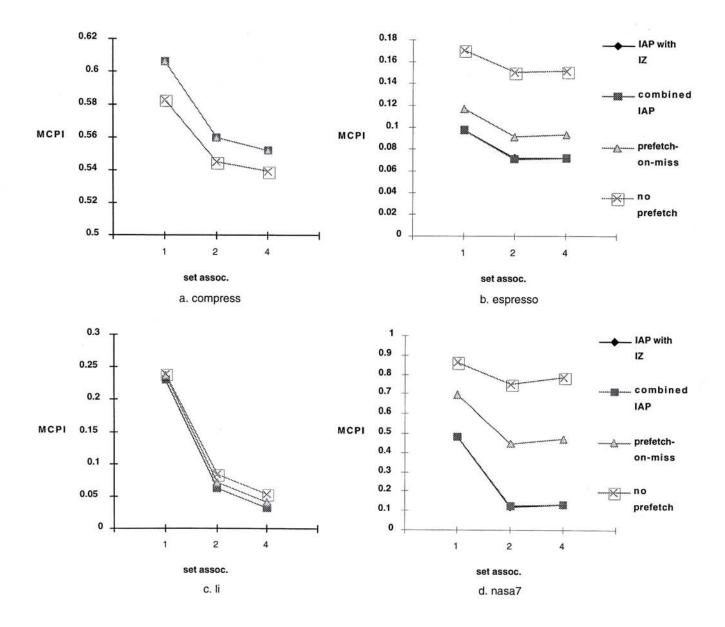

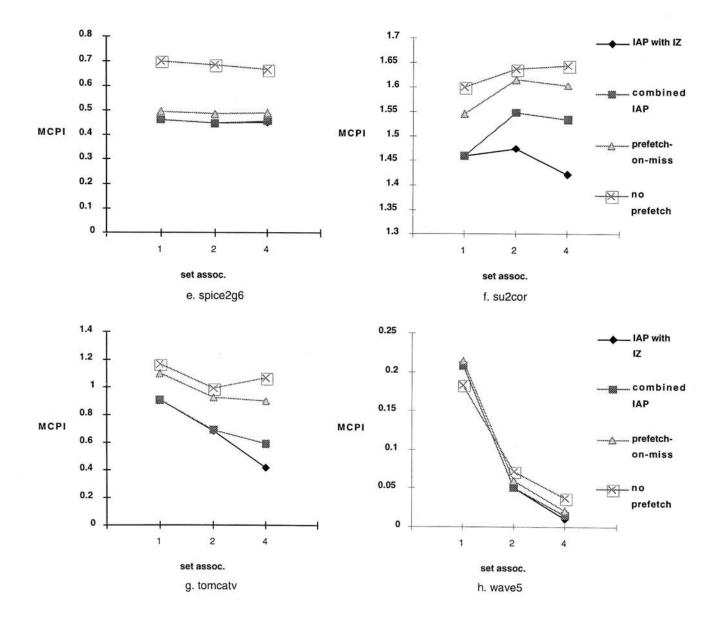

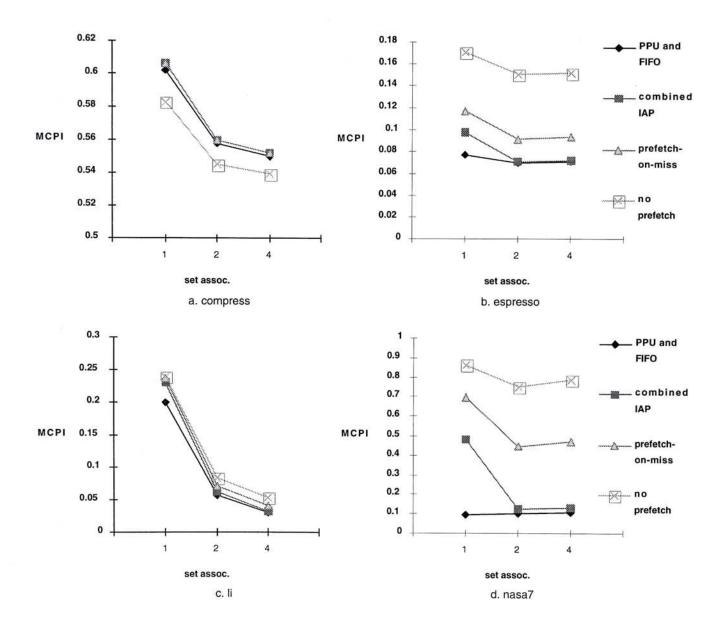

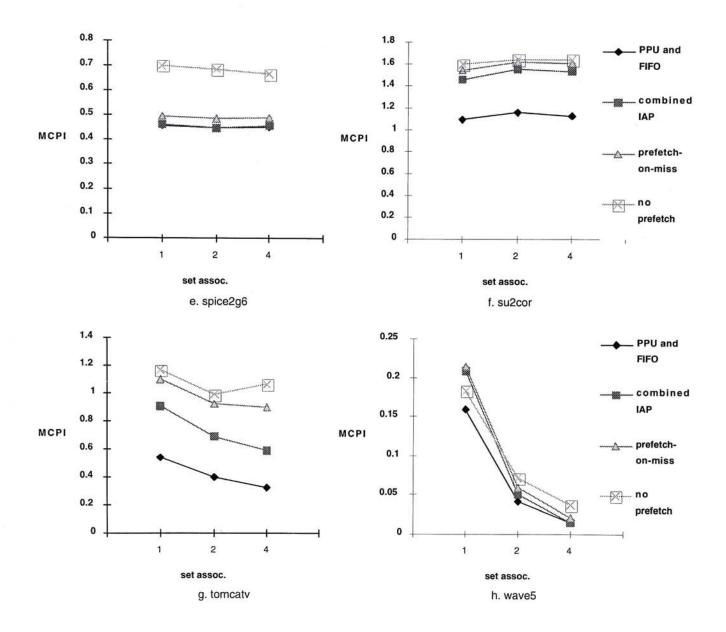

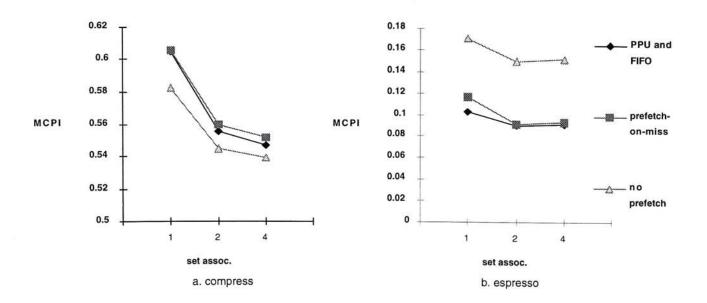

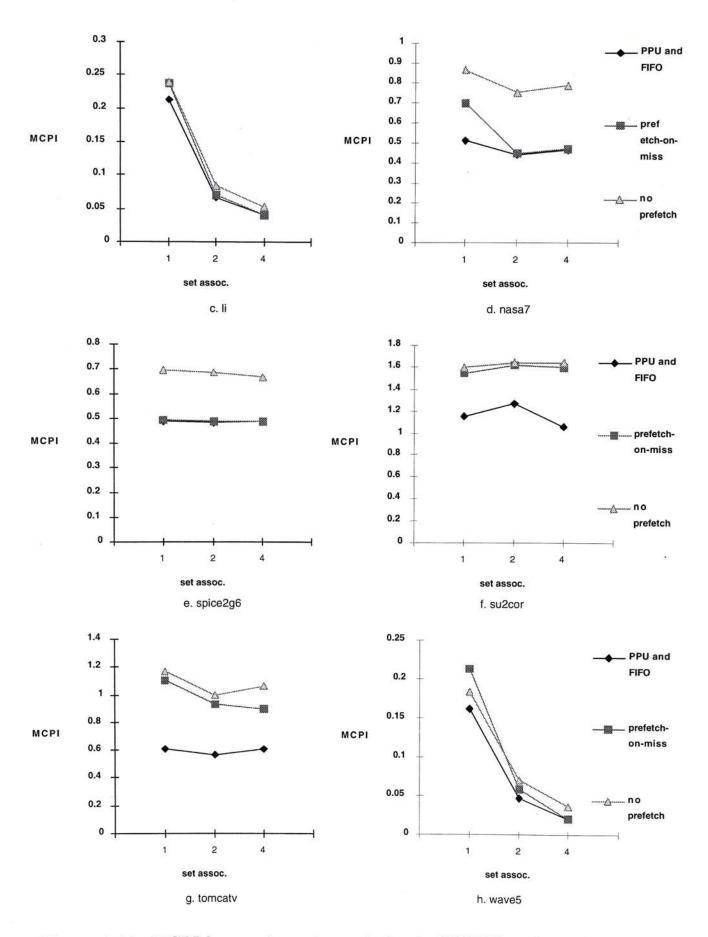

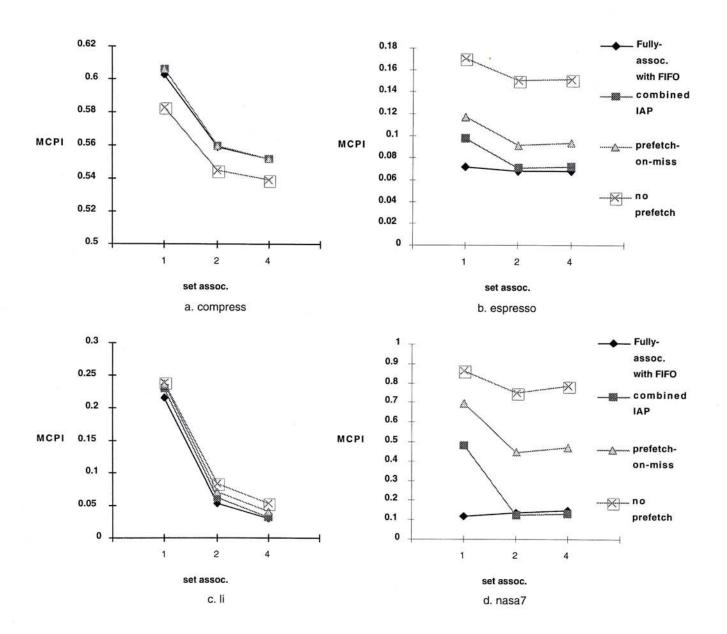

|                                                                    | A.3 Varying Cache Set Associative     |         |                                         | 82  |

|--------------------------------------------------------------------|---------------------------------------|---------|-----------------------------------------|-----|

|                                                                    | A.3.1 Instant Zero Replacement Policy |         |                                         | 82  |

|                                                                    |                                       | A.3.2   | Priority Pre-Updating with Victim Cache | 84  |

|                                                                    |                                       | A.3.3   | Prefetch Cache                          | 87  |

| в                                                                  | Sim                                   | ulatior | n Results of IZ Replacement Policy      | 89  |

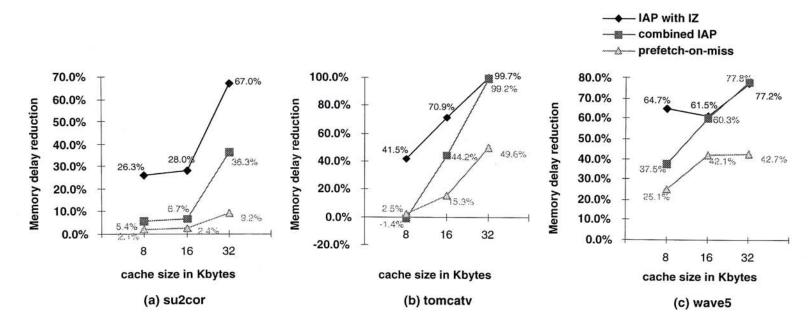

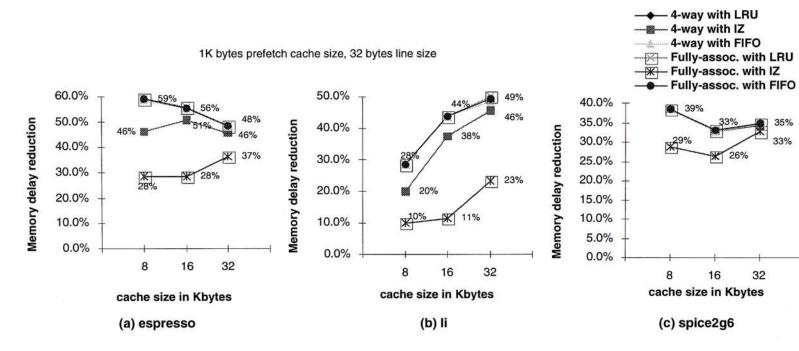

|                                                                    | B.1                                   | Memo    | ry Delay Time Reduction                 | 89  |

|                                                                    |                                       | B.1.1   | Varying Cache Size                      | 89  |

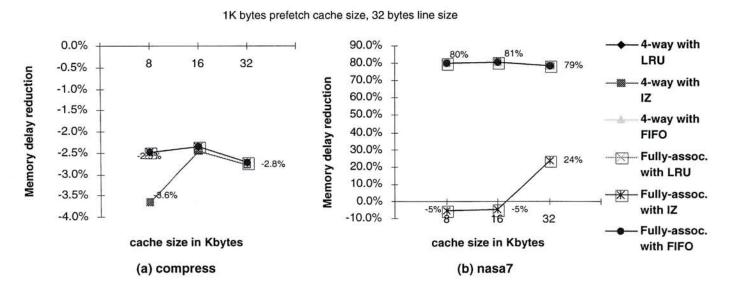

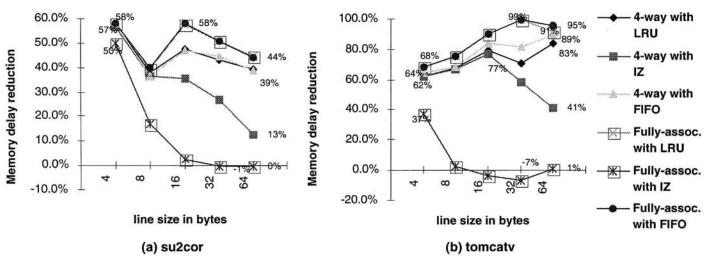

|                                                                    |                                       | B.1.2   | Varying Cache Line Size                 | 91  |

|                                                                    |                                       | B.1.3   | Varying Cache Set Associative           | 93  |

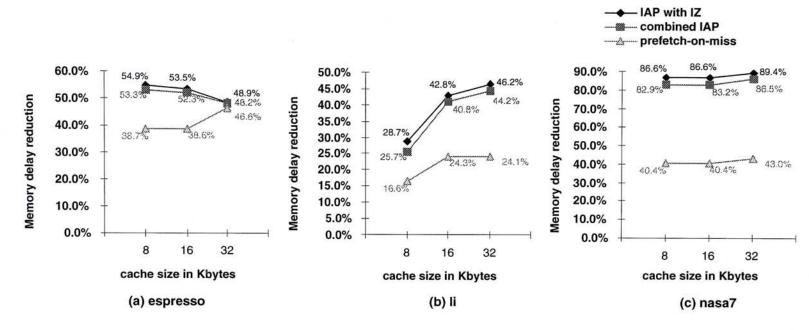

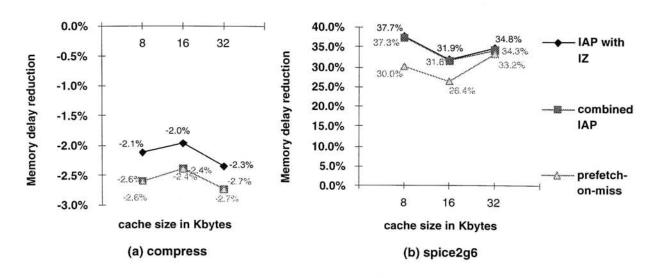

| C Simulation Results of Priority Pre-Updating with Victim Cache 95 |                                       |         |                                         |     |

|                                                                    | C.1                                   | PPUV    | C in IAP Scheme                         | 95  |

|                                                                    |                                       | C.1.1   | Memory Delay Time Reduction             | 95  |

|                                                                    | C.2                                   | PPUV    | C in Cache with Prefetch-On-Miss Only   | 101 |

|                                                                    |                                       | C.2.1   | Memory Delay Time Reduction             | 101 |

| D                                                                  | $\mathbf{Sim}$                        | ulatio  | n Results of Prefetch Cache             | 107 |

|                                                                    | D.1                                   | Memo    | ory Delay Time Reduction                | 107 |

|                                                                    |                                       | D.1.1   | Varying Cache Size                      | 107 |

|                                                                    |                                       | D.1.2   | Varying Cache Line Size                 | 109 |

|                                                                    |                                       | D.1.3   | Varying Cache Set Associative           | 111 |

|                                                                    | D.2                                   | Resul   | ts of the Three Replacement Policies    | 113 |

|                                                                    |                                       | D.2.1   | Varying Cache Size                      | 113 |

|                                                                    |                                       | D.2.2   | Varying Cache Line Size                 | 115 |

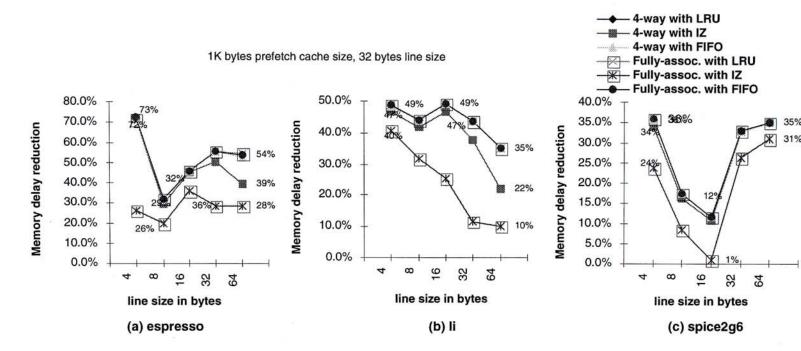

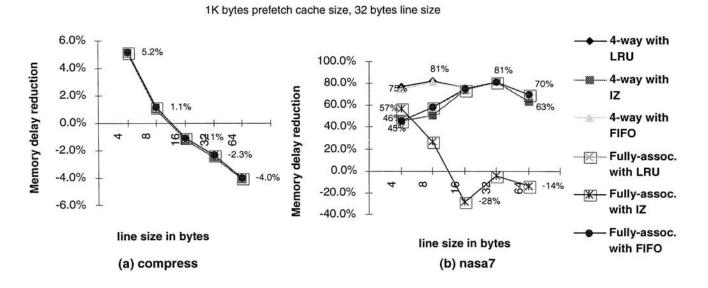

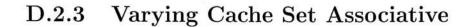

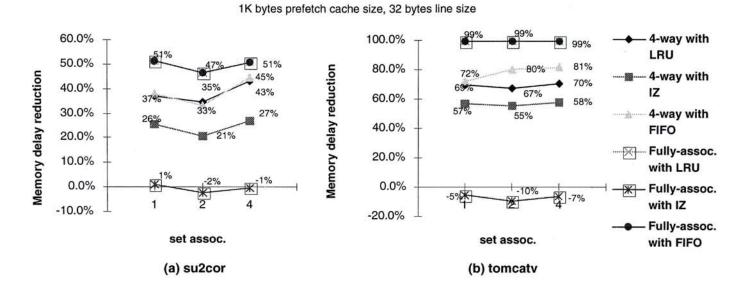

|                                                                    |                                       | D.2.3   | Varying Cache Set Associative           | 117 |

| в                                                                  | iblio                                 | graphy  |                                         | 119 |

# List of Figures

| 2.1 | Operations of $LOAD$ - $UPDATE$ and $STORE$ - $UPDATE$ (a) using              |    |  |

|-----|-------------------------------------------------------------------------------|----|--|

|     | the <i>index-displacement</i> addressing mode and (b) using the <i>index-</i> |    |  |

|     | based registers addressing mode                                               | 7  |  |

| 2.2 | Control flow for IAP scheme                                                   | 10 |  |

| 3.1 | Percentage of Prefetch-On-Miss lines that are not referenced in IAP           |    |  |

|     | scheme                                                                        | 14 |  |

| 5.1 | A theoretical representation of a set in a four-way set associative           |    |  |

|     | cache                                                                         | 24 |  |

| 5.2 | Before a reference to an IAP line                                             | 25 |  |

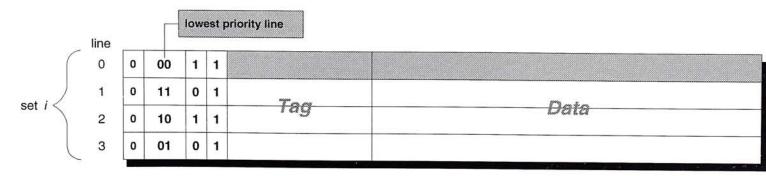

| 5.3 | After reference to an IAP line                                                | 25 |  |

| 5.4 | Control Flow of the IZ Replacement Policy                                     | 26 |  |

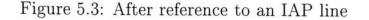

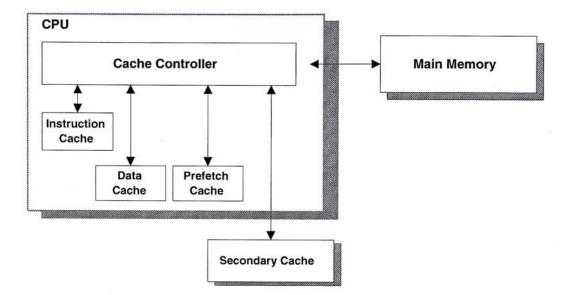

| 5.5 | Architectural model of IAP scheme with PPU                                    | 28 |  |

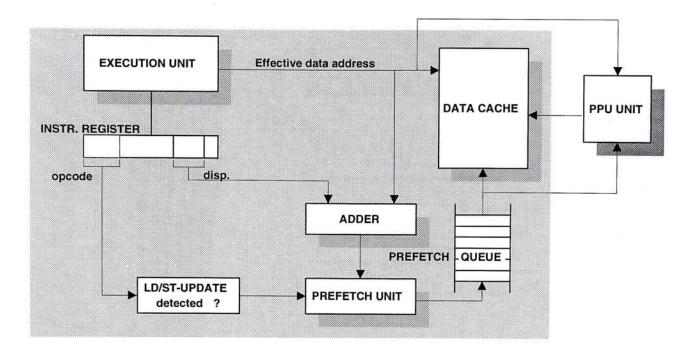

| 5.6 | Illustration of PPU                                                           | 29 |  |

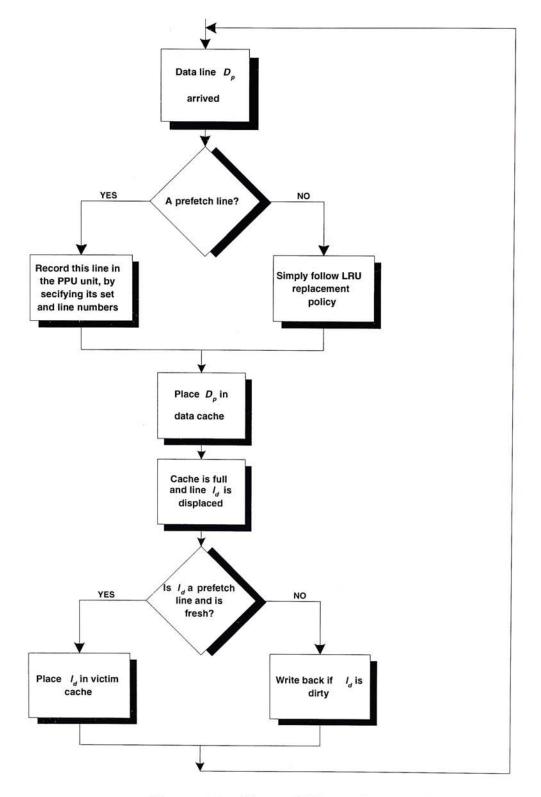

| 5.7 | Control Flow of PPUVC                                                         | 30 |  |

| 5.8 | Cache Support in the IAP architecture                                         | 32 |  |

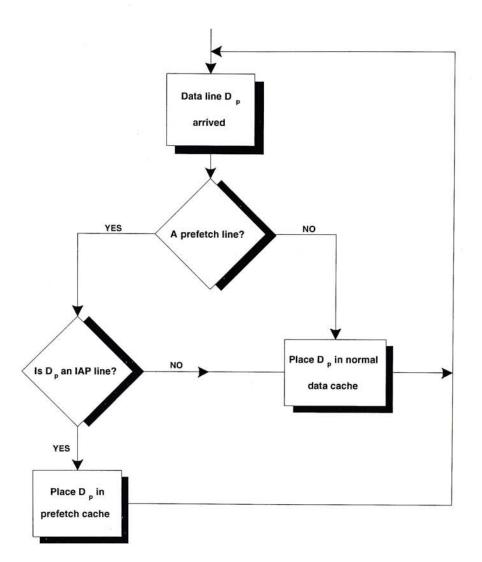

| 5.9 | Control Flow of the Prefetch Cache Scheme                                     | 33 |  |

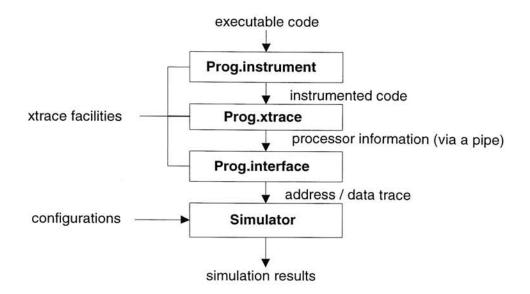

| 6.1 | Trace-driven simulator using <i>xtrace</i>                                    | 35 |  |

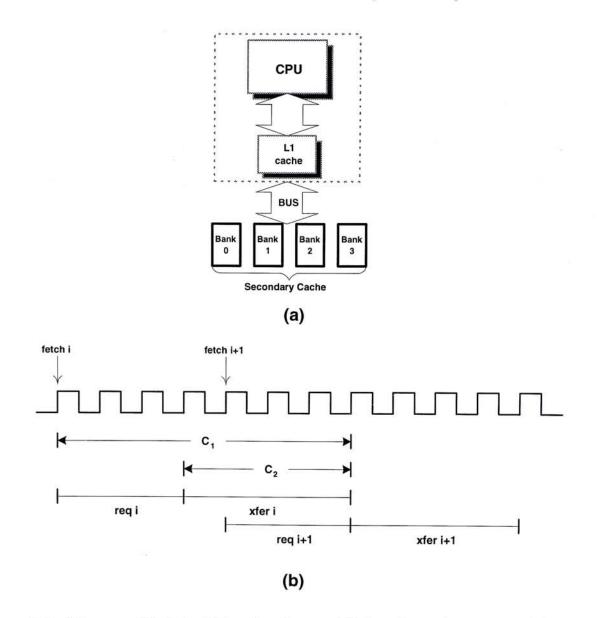

| 6.2 | Memory Model of the simulator: (a) Interleaved memory (b) Tim-                |    |  |

|     | ing of data access                                                            | 38 |  |

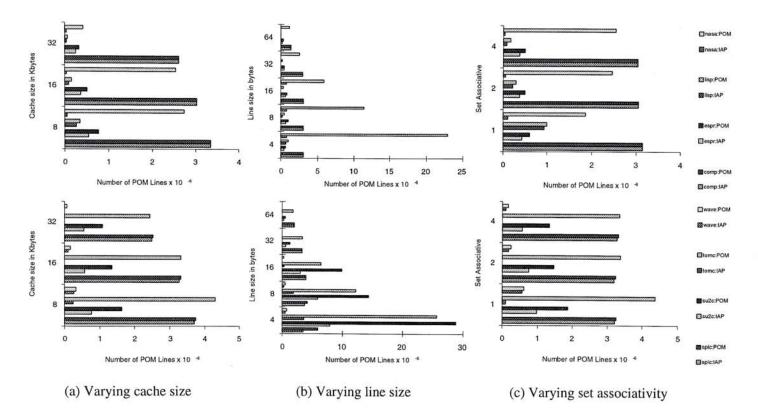

| 6.3 | Comparison of number of prefetch-on-miss lines in IAP cache and               |    |  |

|     | prefetch-on-miss-only cache                                                   | 53 |  |

| 6.4  | Percentage of prefetch-on-miss lines referenced in total number of    |    |  |

|------|-----------------------------------------------------------------------|----|--|

|      | prefetched lines                                                      | 54 |  |

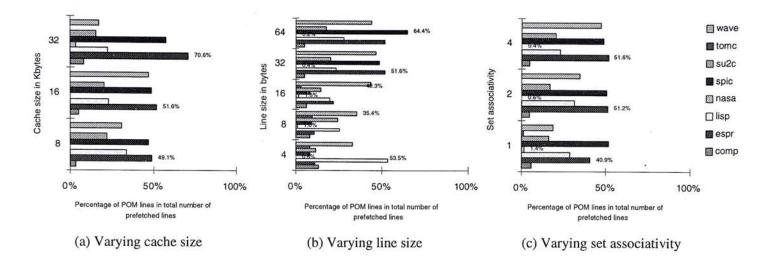

| 6.5  | The effect of Prefetch Cache size on cache performance                | 58 |  |

| 6.6  | An illustration of the performance difference between LRU and FIFO    | 61 |  |

| 6.7  | An instance of line activities in IZ prefetch cache                   | 63 |  |

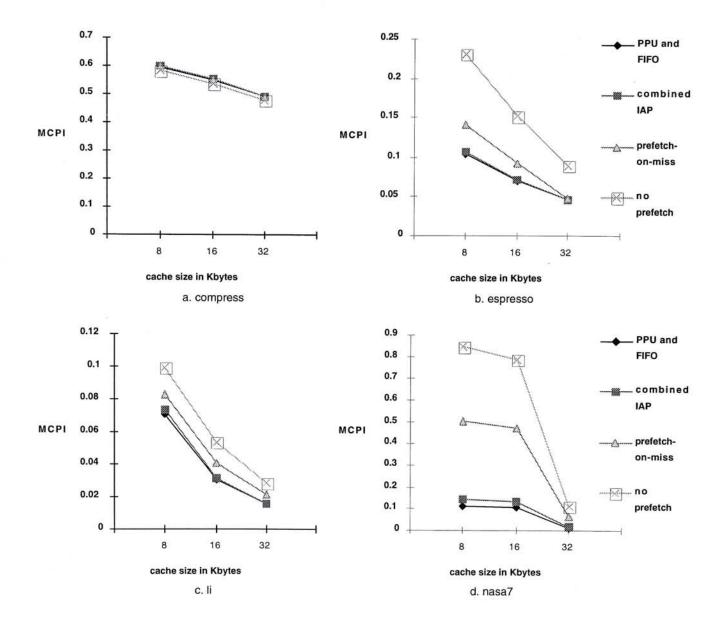

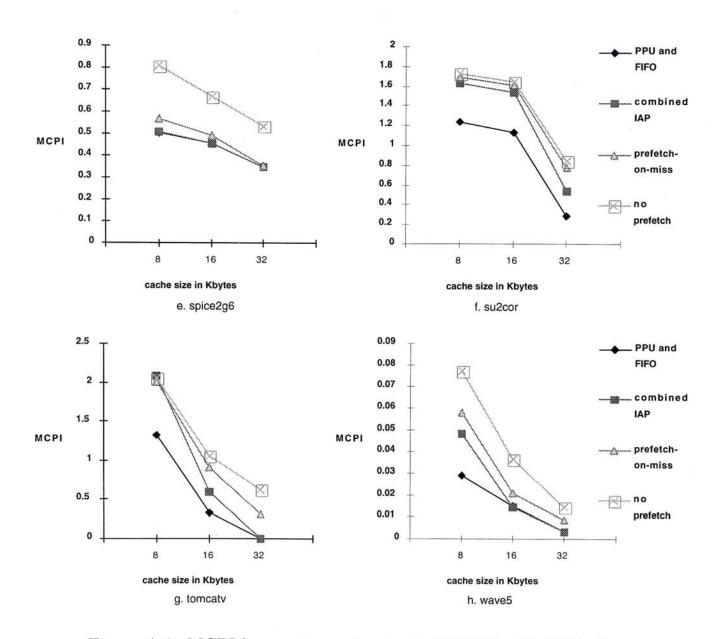

| A.1  | MCPI by varying cache size in IZ scheme                               | 69 |  |

| A.2  | MCPI by varying cache size in PPUVC with IAP scheme                   | 71 |  |

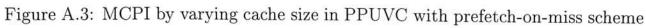

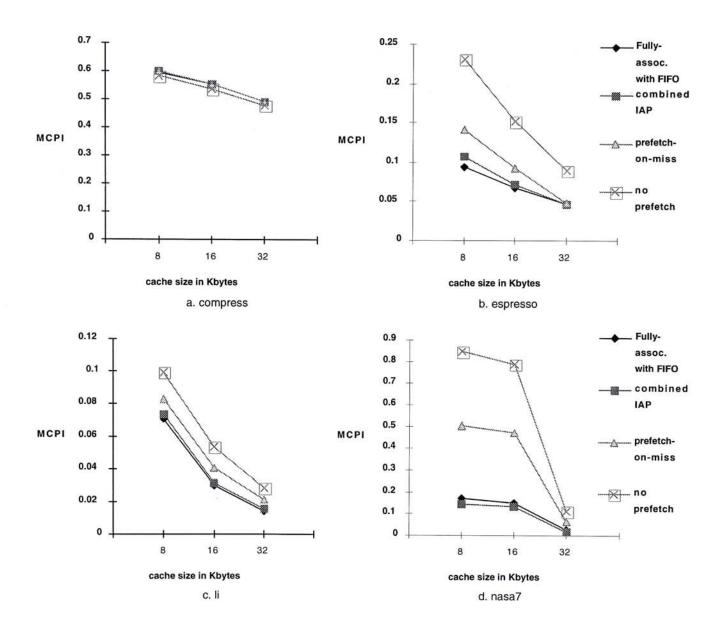

| A.3  | MCPI by varying cache size in PPUVC with prefetch-on-miss scheme      | 72 |  |

| A.4  | MCPI by varying cache size in prefetch cache scheme                   | 74 |  |

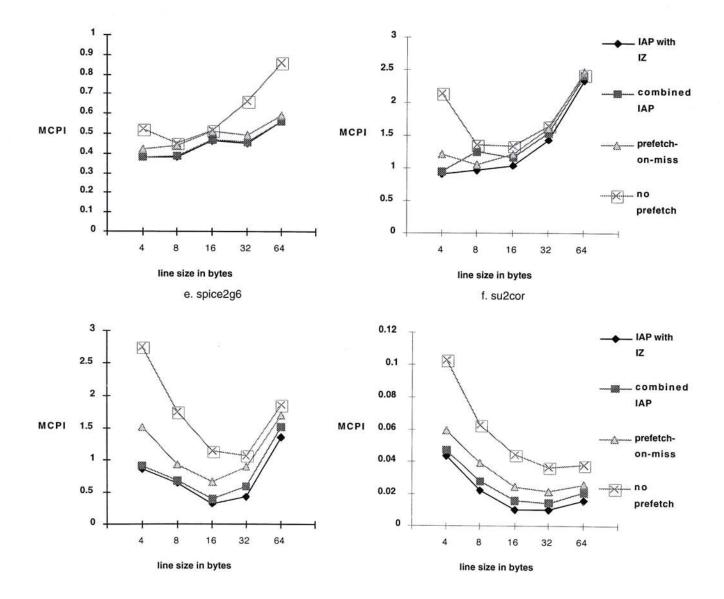

| A.5  | MCPI by varying cache line size in IZ scheme                          | 76 |  |

| A.6  | MCPI by varying cache line size in PPUVC with IAP scheme $\therefore$ | 78 |  |

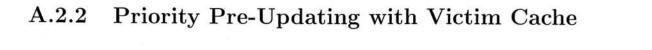

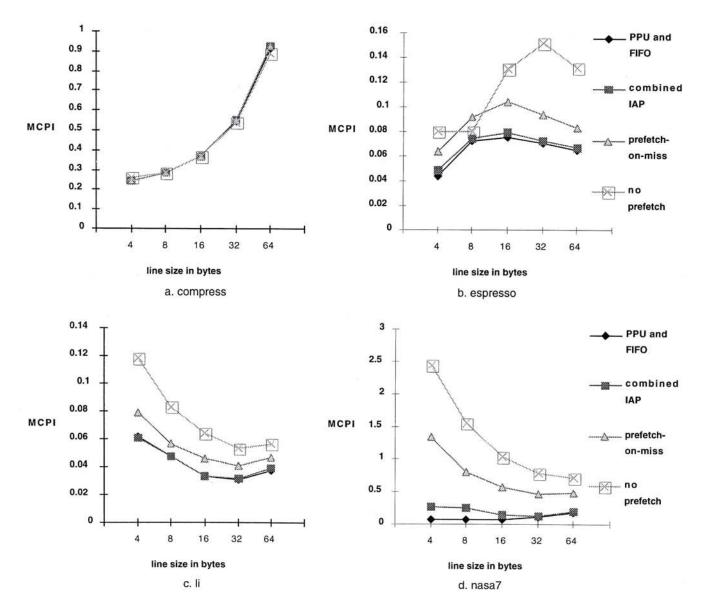

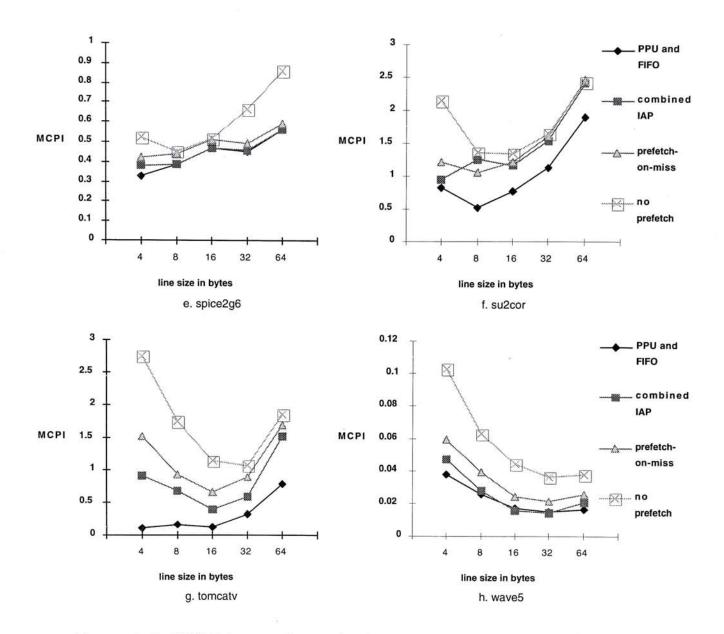

| A.7  | MCPI by varying cache line size in PPUVC with prefetch-on-miss        |    |  |

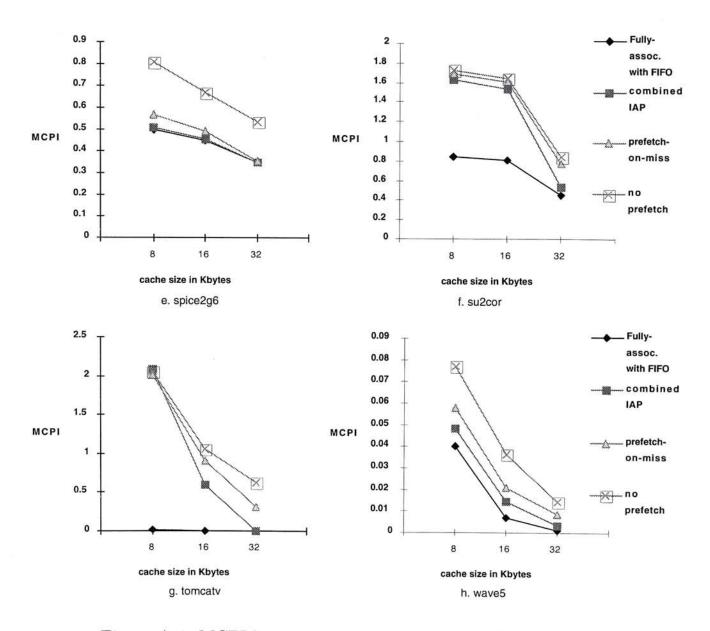

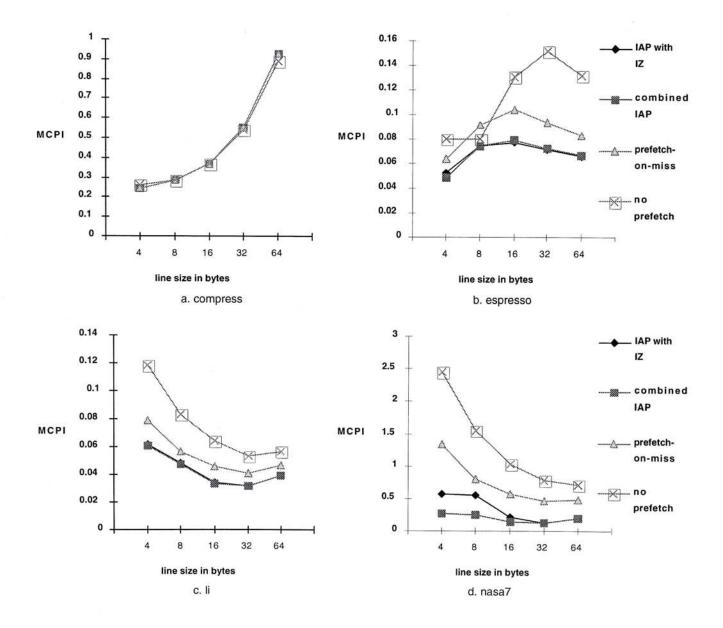

|      | scheme                                                                | 79 |  |

| A.8  | MCPI by varying cache line size in prefetch cache scheme              | 81 |  |

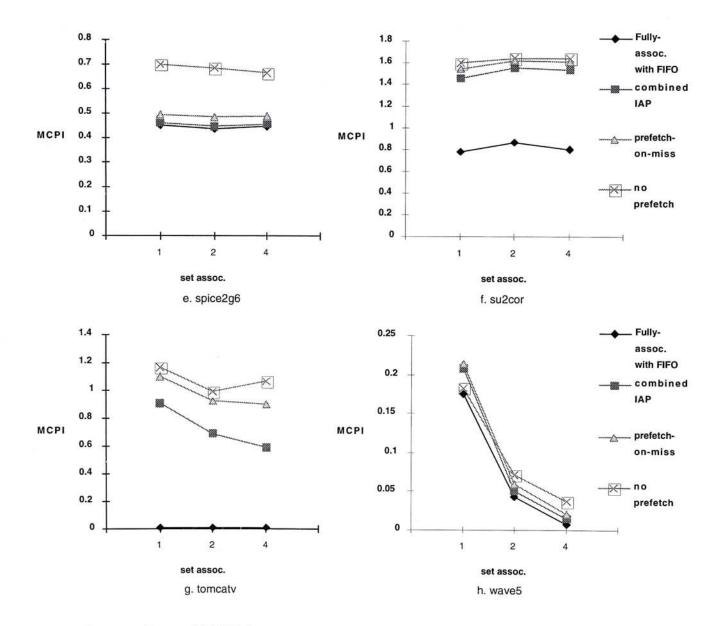

| A.9  | MCPI by varying set associative in IZ scheme                          | 83 |  |

| A.1( | ) MCPI by varying set associative in PPUVC with IAP scheme            | 85 |  |

| A.11 | 1 MCPI by varying set associative in PPUVC with prefetch-on-miss      |    |  |

|      | scheme                                                                | 86 |  |

| A.1  | 2 MCPI by varying set associative in prefetch cache scheme            | 88 |  |

| B.1  | Results of the first group programs in IZ                             | 89 |  |

| B.2  | Results of the second group programs in IZ                            | 90 |  |

| B.3  | Results of the third group programs in IZ                             | 90 |  |

| B.4  | Results of the first group programs in IZ                             | 91 |  |

| B.5  | Results of the second group programs in IZ                            | 91 |  |

| B.6  | Results of the third group programs in IZ                             | 92 |  |

| B.7  | Results of the first group programs in IZ                             | 93 |  |

| B.8  | Results of the second group programs in IZ                            | 93 |  |

| B.9  | Results of the third group programs in IZ                             | 94 |  |

| C.1  | Results of the first group programs in PPUVC  | 95  |

|------|-----------------------------------------------|-----|

| C.2  | Results of the second group programs in PPUVC | 96  |

| C.3  | Results of the third group programs in PPUVC  | 96  |

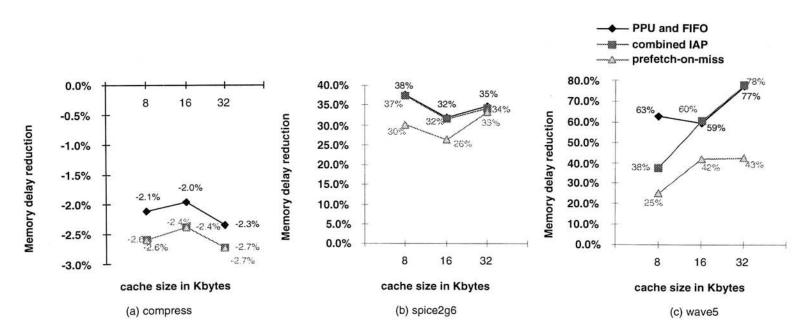

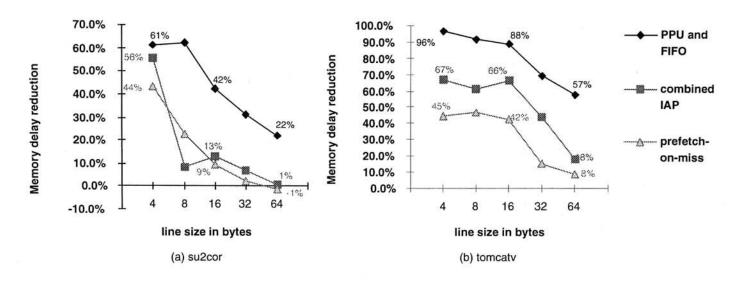

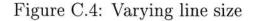

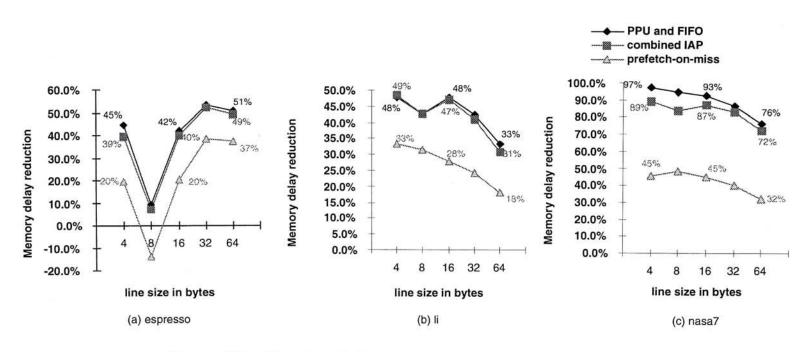

| C.4  | Varying line size                             | 97  |

| C.5  | Results of the second group programs in PPUVC | 97  |

| C.6  | Results of the third group programs in PPUVC  | 98  |

| C.7  | Varying set associative                       | 99  |

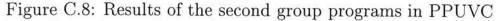

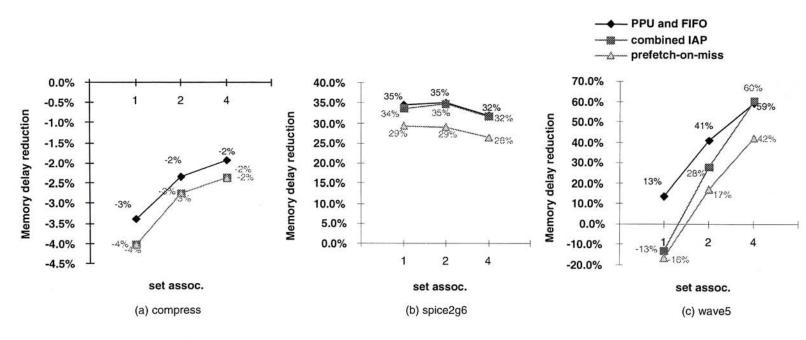

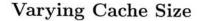

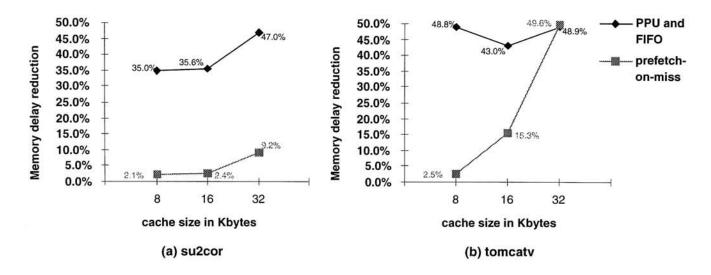

| C.8  | Results of the second group programs in PPUVC | 99  |

| C.9  | Results of the third group programs in PPUVC  | 100 |

| C.10 | Results of the first group programs in PPUVC  | 101 |

| C.11 | Results of the second group programs in PPUVC | 101 |

| C.12 | Results of the third group programs in PPUVC  | 102 |

| C.13 | Results of the first group programs in PPUVC  | 103 |

| C.14 | Results of the second group programs in PPUVC | 103 |

| C.15 | Results of the third group programs in PPUVC  | 104 |

| C.16 | Results of the first group programs in PPUVC  | 105 |

| C.17 | Results of the second group programs in PPUVC | 105 |

| C.18 | Results of the third group programs in PPUVC  | 106 |

| D.1  | Results of the first group programs           | 107 |

| D.2  | Results of the second group programs          | 108 |

| D.3  | Results of the third group programs           | 108 |

| D.4  | Results of the fourth group programs          | 108 |

| D.5  | Results of the first group programs           | 109 |

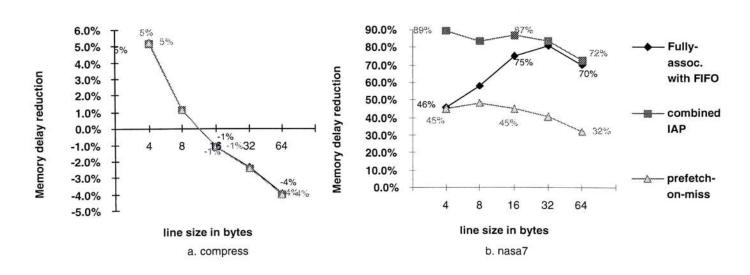

| D.6  | Results of the second group programs          | 109 |

| D.7  | Results of the third group programs           | 110 |

| D.8  | Results of the fourth group programs          | 110 |

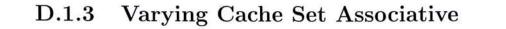

| D.9  | Results of the first group programs           | 111 |

| D.10 | Results of the second group programs          | 111 |

| D.1  | 1 Results of the third group programs         | 112 |

| D.12 Results of the fourth group programs | 112 |

|-------------------------------------------|-----|

| D.13 Results of the first group programs  | 113 |

| D.14 Results of the second group programs | 113 |

| D.15 Results of the third group programs  | 114 |

| D.16 Results of the fourth group programs | 114 |

| D.17 Results of the first group programs  | 115 |

| D.18 Results of the second group programs | 115 |

| D.19 Results of the third group programs  | 116 |

| D.20 Results of the fourth group programs | 116 |

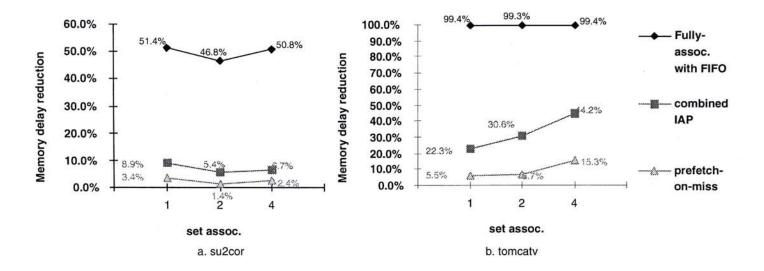

| D.21 Results of the first group programs  | 117 |

| D.22 Results of the second group programs | 117 |

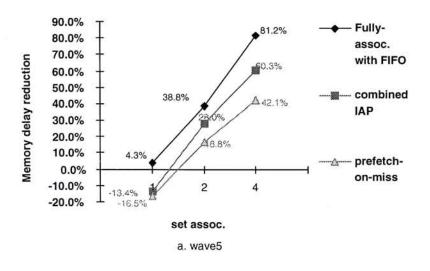

| D.23 Results of the third group programs  | 118 |

| D.24 Results of the fourth group programs | 118 |

# List of Tables

| 6.1 | SPEC Benchmark Applications used                      | 34 |

|-----|-------------------------------------------------------|----|

| 6.2 | Percentages of LOAD/STORE-UPDATEs in SPEC92 Benchmark |    |

|     | Suite                                                 | 39 |

| 6.3 | Baseline CPIs of SPEC92 Benchmark Suite               | 43 |

### Chapter 1

### Introduction

Cache memory is a special high speed memory designed to supply the processor with the most frequently requested instructions and data. Instructions and data located in cache memory can be accessed many times faster than instructions and data located in main memory. The more instructions and data the processor can access directly from cache memory, the faster the computer runs as a whole.

Memory caching is effective because most programs access the same data or instructions over and over. By keeping as much of this information as possible in cache memory (which is usually implemented with faster SRAM), the computer avoids accessing the slower main memory (which is usually implemented with slower DRAM). Some memory caches are built into the architecture or microprocessors. Such internal on-chip caches are often called Level 1 (L1) caches. Cache memory makes use of the principal of locality. Locality of reference states basically that even within very large programs with several megabyte of instructions, only small portions of this code generally get used at once. Programs tend to spend large periods of time working in one small area of the code, perform the same job many times with slightly different operands, and move on to another area of code for another batch of routine jobs. This occurs because of *loops*, which are what programs use to do work many times in a rapid succession.

Generally, there are two kinds of localities – temporal locality and spatial locality. Temporal locality describes the likelihood that a recently-referenced address will be referenced again soon, while spatial locality describes the likelihood that a close neighbor of a recently-referenced address will be referenced soon. Conventional cache memories rely on a program's temporal and spatial localities to reduce the average memory access latency.

The gap between main memory and processor clock speeds is growing at an alarming rate. As a result, the system performance is increasingly dominated by the latency of servicing memory accesses, particularly those accesses which are not easily predicted by the temporal and spatial localities captured by conventional cache memory organizations [Smi82] [HeP95].

One obvious way to reduce number of the cache misses is enlarging the cache as much as possible, however, it is often difficult to achieve practically. There are two main reasons that limit the size of Level 1 cache: [1] The performance gained is not enough to compensate the cost for cache, which typically uses fast but expensive static RAM chips. The speed for SRAM is approximate 4 times faster than DRAM, however, SRAM chips cost more than six times as much as the DRAM chips normally used for main memory. Besides, the performance improvement is not linearly proportional to the size of cache, that is, a 512K bytes cache memory may not obtain 2 times better performance than a 256K bytes one. [2] The CPU chip is usually small while SRAM size is comparable large, thus only limited space for Level 1 cache, while maintaining a reasonable processor chip size.

Due to the large speed gap between the processor and main memory, it is obvious that performance of the system will then be largely determined by [1] how effectively the on-chip memory is able to manipulate operands, minimize the frequencies of off-chip accesses, and [2] the rate at which the external memory system can supply operands.

The main aim of cache memory is to reduce the CPU's idle waiting time. Improving cache performance of programs is one way of increasing the systems throughput. The effectiveness of the on-chip cache to maintain useful operands and minimizing the frequencies of off-chip accesses is one of the main factor to determine the performance of the system. In order to reduce the disparity between processor speed and memory access time, many solutions have proposed to tackle this problem. Some have proposed adding additional features such as non-blocking fetches [Kro81], victim caches [Jou90], and sophisticated hardware prefetching [ChB92] to alleviate the access penalties for those references that have locality characteristics that are not captured by most conventional designs.

# 1.1 Overlapping Computations with Memory Ac-

#### cesses

Many solutions have been proposed to reduce the memory access and/or hide memory latency. An important approach is cache prefetching[Smi78a][Smi78b] [Smi82][HeP95], that is, the action of bringing data to the cache before they are actually needed. Prefetching is similar to speculative loads in the sense that it is non-blocking and behaves like a hint without incurring semantic faults. The main difference between prefetching and speculative loads is that data are loaded into the caches rather than registers.

Depending on how prefetch requests are determined and initiated, prefetching can be either hardware-controlled [BaC91][FuP91][FuP92] or software-directed[Por89] [KlL91][MoL92]. The hardware approach detects accesses with regular patterns and issues prefetches at the run time of the programs, whereas the software approach relies on the compiler to analyze programs and to insert prefetch instructions during compilation of the programs.

However, because of the low accuracy of some prefetching algorithms, there is a risk that the prefetched data that are never used before they are displaced from the cache. This leads to waste of memory space and bandwidth, thus poorer performance results. The problem become worse when the prefetched data displace some useful data in the cache. The phenomenon is called *cache pollution*.

3

#### **1.2** Cache Line Replacement Policies

Different replacement policies are employed to manage operands in the memory. Replacement takes place when a particular cache line or a set of cache lines is already full, and the line has to be evicted its contents to make room for the new incoming line. There is still no ideal replacement policy being invented, and it is unlikely that one would exist. Replacement policy in cache is different from the problem of replacement in paged main memories because the cache replacement algorithm must be implemented entirely in hardware and must execute very quickly so as to catch up with the processor speed.

Least Recently Used and First-In-First-Out are two most commonly used replacement policies. Beside these two well-known algorithms, there are Random, Pseudo-Least Recently Used which are used in some special systems.

Not knowing whether a line will be accessed soon, *Least Recently Used* strategy is usually used in conventional cache as the replacement scheme. However, if the displaced line is referenced by the processor again, a thrashing miss <sup>1</sup> will occur. The situation may become worse, since one thrashing miss can lead to another thrashing miss. A good cache line replacement policy should try to find out the best candidate to be displaced and will help minimize these thrashing misses.

#### 1.3 The Rest of This Paper

In this dissertation, we focus on techniques on better management of the prefetched lines for cache with the IAP scheme and that with a traditional prefetch scheme – prefetch-on-miss only.

IAP is an accurate prefetching scheme, in which it makes use of the information provided by the instruction opcodes and addressing modes for prediction. A brief review on IAP scheme will be given in Chapter 2.

Chapter 3 will briefly describe the cache pollution problem brought by conventional prefetching schemes, the reference-once property of IAP lines and how

$<sup>^{1}</sup>$ A thrashing miss occurs when the line which was replaced must itself be reloaded

IAP works.

Chapter 4 will briefly describe previous research on prefetching, and stream buffers.

The implementation of the replacement policy, Instant Zero (**IZ**) cache line replacement policy, will be discussed in Chapter 5. The details of another replacement policy, Priority Pre-Updating (**PPU**), which is designed to be used with different types of prefetching algorithms, will be given in the same chapter. The effect of using Priority Pre-Updating with victim cache (**PPUVC**) is also discussed in this chapter.

In the same chapter, details on the placement policy of prefetched lines, prefetch cache, will be given.

Chapter 6 will present the simulation methodology, performance metrics that used and the results of performance evaluation. The designs are evaluated by simulating the some benchmark program in a uniprocessor environment. The results show that either IZ, PPU with victim cache and prefetch cache alone can obtain significant improvement in system performance.

Finally, Chapter 7 will give an insight on future directions, and we will conclude this paper in Chapter 8.

### Chapter 2

## A Brief Review of IAP Scheme

#### 2.1 Embedded Hints for Next Data References

In the design of latest processor architectures, instruction opcodes and the addressing modes of the architecture definition usually have built-in mechanism to support the address calculation of future data references while the current datum is being referenced. It is also found that compound instructions are commonly used in RISC architecture to reduce the program execution path length. As it can be found from program instrumentation and tracing, certain simple RISC instructions are executed in pair. So it might be useful to define a single compound or extended opcode to execute the instruction pair, and this is particular useful if the new instruction opcode does not affect the processor clock cycle. Up to now, there are several machines have such kind of opcodes. For example, ADD-AND-BRANCH, COMPARE-AND-BRANCH, LOAD-WORD-AND-UPDATE, etc. in HP's Precision Architecture 1.1 [HP94]. IBM and PowerPC has LOAD-UPDATE, LOAD-MULTIPLE[IBM89] [Mot92] [IBM94] [WeS94], etc.. The total number of instructions defined in current RISC processors range from 150 and 200, which is much larger than that of early RISC processors (about 50 to 70 instructions). The reason is that latest processors find these compound or extended opcodes to be very useful, and this embedded them into the instruction set. Among these compound instructions, it is found that the LOAD/STORE-UPDATE (or

LOAD/STORE-MODIFY), are very helpful to manage on-chip cache activities.

Array or pointer references to a large set of data are one of the major types of data references in typical programs. Data will be referenced one after another successively, *index-displacement* and *index-based register* addressing modes are usually employed for this type of accesses. Because these accesses occur very frequently, as a result, many systems tend to use compound opcodes like *LOAD-UPDATE* and *STORE-UPDATE* for the accesses. Beside loading or storing a datum into the register, the content of the index register, which is used in the address calculation of current data reference, will be updated by each of these instructions. The operations of the *LOAD-UPDATE* and *STORE-UPDATE* instructions using either *index-displacement* or *index-based* registers addressing mode are shown in Figure 2.1.

| $LOAD \ R_T(R_x + Disp)$                                                  | $LOAD \ R_T(R_x + R_y)$                                                    |

|---------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Equivalent to                                                             | Equivalent to                                                              |

| $Eff. \ Addr. = (R_x) + Disp$ $R_T = (Eff. \ Addr.)$ $R_x = Eff. \ Addr.$ | $Eff. \ Addr. = (R_x) + (R_y)$ $R_T = (Eff. \ Addr.)$ $R_x = Eff. \ Addr.$ |

| (a)                                                                       | (b)                                                                        |

Figure 2.1: Operations of *LOAD-UPDATE* and *STORE-UPDATE* (a) using the *index-displacement* addressing mode and (b) using the *index-based registers* addressing mode

The updating action of the LOAD-UPDATE or the STORE-UPDATE instruction is the preparation of the content of register  $R_x$  which is used in calculating of the effective address of the next expected datum.  $R_x$  is equal to the sum of the current data reference address Eff. Addr. (or the updated content of register  $R_x$ ) and the displacement Disp (in the *index-displacement* addressing mode) or the register content  $R_y$  (in the *index-based register* addressing mode). Thus, accurate data cache prefetching can be carried out and the address of prefetched data is equal to (Eff. Addr.+Disp) or  $(Eff. Addr.+R_y)$ . It should be noted that values of Eff.Addr. and Disp (or  $R_y$ ) are available to the cache prefetching unit during the execution of LOAD  $R_T(R_x + Disp)$  or LOAD  $R_T(R_x + R_y)$  instruction.

## 2.2 Instruction Opcode and Addressing Mode Prefetching

By using these hints of data references provided by the instruction opcode and addressing modes, Instruction Opcodes and Addressing Mode Prefetching (**IAP**) scheme which provides accurate data prefetching for on-chip cache is proposed by Lau [Lau96]. In Lau's study, IBM POWER architecture ( or the PowerPC architecture) is used as an example to show how IAP scheme should be designed and implemented.

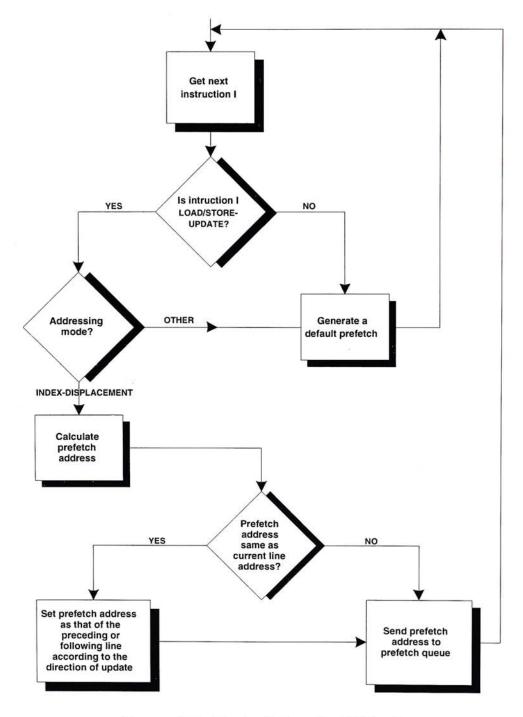

Figure 2.2 shows the control flow of IAP scheme. For each instruction i that is decoded and executed, its opcode will be checked first to determine if it belongs to LOAD-UPDATE or STORE-UPDATE instruction. If such a case is detected, the address of next datum expected to be referenced in the near future will be re-calculated. Using the same addressing mode as i but with the updated contents of all registers used in the address calculation of i. Afterwards, this new address will be sent to the cache prefetch unit for accurate data prefetching. Beside these basic ideas, two enhancements have been integrated into the IAP scheme:

• Default Prefetching vs. Selective Prefetching

When executing each LOAD/STORE instruction *i*, if this instruction *i* belongs to LOAD/STORE-UPDATE instructions group, then the IAP scheme will be used for data prefetching, else the prefetch-on-miss is used as the default prefetching scheme for data prefetching.

• Cache Block Prefetching vs. Next Data Reference Prefetching For each data prefetch requested by IAP scheme, if the target prefetched block *j* containing the candidate datum is not the same as current data referencing line i, then a prefetch of block j will be issued. If they are the same, then a prefetch request of block i + 1 will be issued.

The above IAP scheme together with the two enhancements are the *combined* IAP that we use in this paper.

#### 2.3 Chapter Summary

In this chapter, a general design for hardware controlled prefetching, which was proposed by Lau [Lau96], is introduced. By using information embedded in the instruction opcodes, Lau's design is able to single out the data references with constant strides from the pool of all data references and also able to find the corresponding stride values. With this valuable information, accurate prefetching can be accomplished and consequently, the CPU stall time due to data cache misses can be reduced. The cache block prefetching is introduced to tackle the problem of limited memory bus bandwidth. In order to exploit the spatial locality, the combined IAP scheme is equipped with default prefetching to issue prefetch requests for the non-LOAD/STORE UPDATE instructions.

Figure 2.2: Control flow for IAP scheme

### Chapter 3

### Motivation

Over the last two decades, the CPU clock cycle time has been decreasing at a much faster rate than the main memory access time. The average number of cycles per instruction has also been decreasing dramatically. The effect is more obvious for RISC machines with higher clock speed and data consumption rate.

Unfortunately, a high bandwidth of the microprocessor is meaningless unless it is matched by a similarly powerful memory subsystem. Most of current microprocessors rely on caches to reduce their effective memory access time. However, cache miss affects the overall performance of a system, i.e., if either the instruction or the operand required by the operations is not found in cache(s), the actual performance would decline for the large amount of cache misses.

With current VLSI developments, several functional units, instruction and data caches, and some special hardware functional units can be included on the processor chip. Therefore, a first obvious method for reducing the average memory access time is to implement multi-level cache hierarchies [BaW89] with an on-chip first level cache. However, under the usual caching mechanism, the processor will still be stalled on a first-level cache miss and of course also on misses on any of the next levels of the memory hierarchy with an even larger penalty time, until the miss is resolved. Since a processor must stall on a cache miss, caches do not totally hide memory latency but, instead, they eliminate many off-chip memory accesses. In order to make further progress towards the reduction of memory latency, memory accesses due to cache misses must proceed in parallel with the processor execution. As a result, a number of different solutions have been proposed to allow computations to be overlapped with memory accesses. They basically provide efficient mechanisms to allow buffering and pipelining of memory references.

Various data prefetching algorithms exist, some are hardware-assisted, some are software-directed and others are hybrid. The main fault of many of these algorithms is that they do not integrate replacement algorithms with prefetching methods. There is often a large penalty for prefetching into the cache because the wrong line was replaced.

When incorporating the prefetching algorithms in a processor, several things have to take into consideration. First, it is possible to prefetch data into the cache that will never be used by the processor. This not only pollutes the cache, but also increases memory traffic. Second, if the data is prefetched too early, it can become stale before it is referred, this may also increase memory traffic. Therefore, in designing a processor with prefetching, careful balance between performance gains and tradeoff like cache pollution and memory traffic increase are required.

From a different viewpoint, a conventional cache's hardware does not know the likelihood of whether a line will be accessed soon. A blind strategy is usually used to choose the line to be replaced when a miss has occurred, e.g. choose the *least recently used* line. However, if it happens that the displaced line is referenced by the processor again, a thrashing miss will occur. The problem becomes more serious since one thrashing miss can lead to another thrashing miss.

It is estimated that 50% of all misses are thrashing misses, and that most of these can be avoided. A good cache replacement policy will help minimize these thrashing misses.

There exists an accurate prefetching, the Instruction Opcodes and Addressing Modes Prefetching, which is proposed by Lau [Lau96]. IAP, which making use of the run-time information provided by the instruction opcodes and addressing modes, prefetches data accurately. However, it is found that data prefetched by IAP scheme have not posed the temporal locality property, a large portion of the data prefetched by the IAP scheme <sup>1</sup> are likely to be referenced one and only one time <sup>2</sup> before the program terminates. In order to handle the replacement of the data lines in the cache, a new strategy, tentatively termed as *Instant Zero* (**IZ**), is proposed. This new strategy aims at replacing the IAP lines intelligently, which will be explained in detail later.

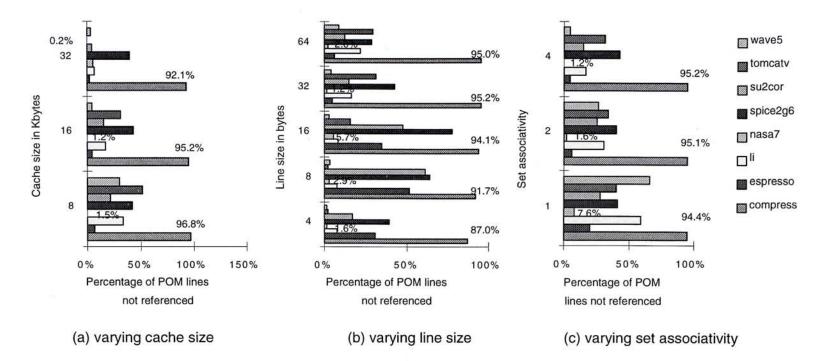

On-chip cache is usually small <sup>3</sup>, thus the precious cache space should be used carefully. Cache pollution problem highly affects the system performance, one obvious solution to solve the cache pollution problem is to kick out useless data in case of conflict or capacity misses. However, which data is useless and how to determine which should be kicked out is really a difficult problem. A poorly designed prefetching algorithm aggravates cache pollution problem, and wrong displacement of useful data degrades system performance. From Figure 3.1, we can find out that in some benchmark programs, more than 90% of prefetch-on-miss lines are unreferenced. It is obvious that most prefetch-on-miss lines are useless, i.e., they are not referenced before the program terminates. It is beneficial to shorten the life time of those possibly erroneously prefetched lines in the cache to minimize cache pollution. We propose a *Priority Pre-Updating* (**PPU**) scheme to tackle the problem, PPU helps determining the data to be kicked out and reduce cache pollution.

As mentioned above, IAP lines are likely to be referenced one and only one time before the program terminates. Therefore, placing them in a separate cache space can localize their effects and minimize the cache pollution problems. As a result, we proposed to use an on-chip *prefetch cache* to hold all those data prefetched by IAP scheme.

<sup>&</sup>lt;sup>1</sup>lines prefetched by IAP scheme will tentatively called IAP lines in later sections.

<sup>&</sup>lt;sup>2</sup>Termed as reference-once property

$<sup>^3 \</sup>rm Usually$  ranging from 4K bytes to 32K bytes. Though large on-chip cache is also found in current architecture, it is not common.

Chapter 3 Motivation

Figure 3.1: Percentage of Prefetch-On-Miss lines that are not referenced in IAP scheme

#### 3.1 Chapter Summary

Cache pollution is a side-effect of data prefetching, a poorly designed prefetching algorithm aggravates cache pollution problem. This problem has diverse effect on cache performance. A blind replacement strategy increase the thrashing misses, reduce the utilization of cache and indirectly cause cache pollution. The techniques, *Instant Zero* replacement policy and *Priority Pre-Updating with victim cache*, tend to alleviate this problems and improve the cache performance. The cache lines prefetched by IAP scheme have a reference-once property, and placing them in a separate cache space, prefetch cache, is able to localize their influence and also reduce the cache pollution problem.

## Chapter 4

## **Related Work**

For recent computer applications, it is common that there are many matrix manipulations with highly regular and sequential data references, and a lot of data are needed in performing computation. If the operands are not found in cache, the actual performance of the system would decline for the large amount of cache misses.

In order to reduce the number of cache miss penalty, data should be prefetched into the cache before their actual usage. Prefetching techniques consist of both hardware and software approaches. Existing cache prefetching schemes, either hardware-driven [BaC91] [Smi78b] or software-assisted [Tha81][Bre87][Por89] [GoG90][CaK91][ChM91][KlL91][MoG91][MoL92], are not very effective in reducing the processor idle time due to memory accesses.

Hardware prefetching typically uses dynamic stride detection to perform runtime calculation of prefetch addresses to be issued[ChB92] [FuP91] [FuP92]. The overheads of hardware prefetching are the cost for the additional hardware, and the limited ability of the dynamic units to perform any prefetching other than through arrays with linear strides.

The prefetching accuracy of traditional hardware driven data prefetching schemes is low (though it is relatively easier to be implemented), thus cannot get significant improvement in data cache performance. Though we can find some accurate

#### Chapter 4 Related Work

hardware-driven prefetching schemes of constant stride array elements, they usually require some complicated add-on hardware such as a prediction table. As a result, they are not suitable to be implemented as the first-level on-chip cache as the space on the CPU chip is very limited. Chen and Baer [ChB94] evaluated the effectiveness of lockup-free caches and hardware prefetching, and proposed a hybrid scheme based on a combination of these approaches.

Software prefetching is more flexible than hardware prefetching, having the advantage of compile-time knowledge, but pays the price of software overhead, both in instructions issued and code size[CaK91] [KlL91] [MoL92]. Software-assisted cache prefetching schemes can also achieve high accuracy in prefetching array data references with constant strides, but the runtime overhead introduced is a big obstacle to their popularity. Furthermore, architectural and compiler supports are needed for the software-assisted prefetching schemes. These also restrict the usage of software prefetching scheme in current processors and computer systems. Beside these, some promising approaches use hybrid hardware and software techniques, issuing limited instructions that provide hints to the prefetch hardware[Chi94].

When the cache or a particular set is full, and information is requested by the CPU from the lower level memory, some information in the cache must be selected for replacement. This implies that a cache miss needs not only a fetch but also a replacement. Cache replacement policies should implement totally in hardware and execute very quickly, so it will not have bad influence on the system performance. The replacement algorithms are mainly classified into usage-based and non-usage-based. Section 4.1 will give a brief description of some known replacement policies.

#### 4.1 Existing Replacement Algorithms

In brief, cache misses can occur for three reasons: [1] the requested data have never been accessed before (*compulsory miss*), [2] the requested data have been accessed before, but the size of the working data set exceeds the cache size (*capacity miss*), or [3] the requested data had been in the cache but was displaced by an intervening reference to another address (*conflict miss*). Information resident in the cache has to be removed to bring in future information in the event of cache misses. The replacement algorithm determines the information to be discarded. The algorithm may be *Least Recently Used* (LRU), *First In First Out* (FIFO), *Random, Pseudo-LRU*, etc.

A truly random strategy is completely unacceptable for production test reasons, as it is difficult to run test vectors on a chip that does not have completely deterministic behavior. Some relatively common replacement algorithms are as follows:

- 1. Least Recently Used (LRU): An usage-based algorithm under which the line which has not been accessed for the longest time is replaced with the hope of reducing the chance of throwing out information that will soon be needed again. Its implementation requires every line to have extra bits to keep track of the age of its contents thus making the controller design more complicated.

- 2. First in First Out (FIFO): The First In-First Out replacement policy chooses the page which has been in the memory the longest to be the one replaced, i.e., the page to be replaced is the *oldest* page in the cache, the one which was loaded before all the others. A pointer into the line space is maintained. On replacement, the line pointed by the pointer is ejected, and the pointer is incremented. The pointer is set to zero when the end of the line space is reached.

- 3. Clock (or Second-chance): A pointer in the line space is maintained. On replacement, the used bit of the line pointed to by the pointer is checked. If it is set, it will be cleared and the pointer is incremented. The last step is repeated until a line with the used bit cleared is found and that line is ejected. The used bit is set on every access, and is cleared periodically. This method can be used to approximate LRU, but the periodicity of the clearing needs to be carefully set. It will be difficult to find an eject-able

line if the period is too long. If the period is too short, locality will be lost and thrashing will occur frequently.

- 4. Least Recently Modified: The LRU bits of lines is modified only on writes.

- 5. Not-Most-Recently-Used: The most recently used line is kept in the cache, one of the remaining lines is selected and replaced.

- 6. Least Frequently Used (LFU)

The page to be replaced is the one used least often of the pages currently in the cache.

7. Last In First Out (LIFO)

The page to be replaced is the one most recently loaded into the cache.

8. Optimal (OPT or MIN)

The page to be replaced is the one that *will not be* used for the longest period of time. This algorithm requires future knowledge of the reference string which is not usually available. Thus, this policy is used for comparison studies.

Among all of the above algorithms, the usage-based LRU is most commonlyused in current memory design. As mentioned above, implementation for LRU has to keep track of the age of every cache line, and thus requires every cache line to have extra bits. Though this makes the controller design more complicated and expensive, it works well in most architecture. FIFO and Random are nonusage-based algorithms, non-usage-based algorithms use basis other than usage for replacement decision. It is shown that non-usage-based algorithms all yield comparable performance [Smi82].

#### 4.2 Placement Policies for Cache Lines

Techniques on holding prefetched data in intermediate space other than the firstlevel cache has also been proposed. Jouppi [Jou90] proposed to use a stream buffer to hold the prefetched data. Stream buffers prefetch cache lines starting at a cache miss address. The prefetched data is placed in the buffer instead of the cache. Stream buffers are useful in removing capacity and compulsory cache misses, as well as some instruction cache conflict misses. However, the stream buffer that proposed is actually a simple FIFO queues, and thus each time only the *oldest* element is visible to the processor. However, the newest replaced lines instead of older one are needed sometimes. As a result, the expected performance improvement in data cache is slight or nil. Therefore, multi-way stream buffer, which consists of four parallel stream buffers in a multi-way stream buffer and with LRU replacement policy, is proposed to solve the limited ability of stream buffer. When a miss occurs in the data cache that does not hit in any stream buffer, the least recently hit stream buffer is cleared and it is started fetching at the miss address. However, the utilization of buffer is still low, as only the first entry in each buffer can be searched.

Jouppi [Jou90] has proposed another technique, miss caching, to minimize the miss penalty during a cache miss. A miss cache is a small fully-associate cache containing two to five cache lines of data. When a miss occurs, data is returned not only to the normal (upper) cache, but also to the miss cache under it, where it replaces the least recently used item. Each time the upper cache is probed, the miss cache is probed as well. If a miss occurs in the upper cache but the address hits in the miss cache, then the directed mapped cache can be reloaded in the next cycle from the miss cache. This replaces a long off-chip miss penalty with a short one-cycle on-chip miss.

To make better use of the miss cache, victim caching is further proposed by Jouppi [Jou90]. Victim caching use a different replacement algorithm for the small fully-associative cache. Instead of loading the requested data into the miss cache on a miss, load the fully-associative cache with the victim line from the direct-mapped cache instead. With victim caching, no data line appears both in direct-mapped cache that hits in the victim cache, the contents of the directmapped cache line and the matching victim cache are swapped.

#### 4.3 Chapter Summary

In this chapter, a brief review on different prefetching algorithms is given. Besides, review on existing replacement and placement policies is also introduced.

### Chapter 5

# Replacement and Placement Policies of Prefetched Lines

In order to minimize the cache pollution and localize the influences brought by prefetched lines, we have tried different approaches. The different schemes try to focus on handling the life time of prefetched lines in the cache, and placement of IAP lines. Firstly, we propose to use a mixed replacement policy with both IZ and LRU replacement policies, this scheme helps to shorten the life time of referenced and useless IAP lines and it retains the temporal locality of demandfetched lines. Secondly, the Priority Pre-Updating scheme (PPU) is proposed to shorten the life time of possibly erroneously prefetched lines. In addition to IAP scheme, we found that PPU can work well on caches employing different prefetching algorithms. Thirdly , we use a on-chip prefetch cache to hold the prefetched data to localize the influences of IAP lines, Following sections will give details on these three schemes.

### 5.1 IZ Cache Line Replacement Policy in IAP scheme

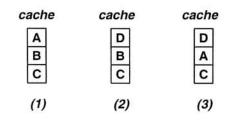

Least Recently Used (LRU) is the most commonly used cache line replacement policy in both traditional cache designs and the IAP scheme mentioned in previous chapters. Though LRU is very popular in current cache designs, it still has many drawbacks. It is known that LRU cannot always replace the best line in the cache, and replace a wrong candidate line may cause cache miss afterwards. For example, consider the following code segment:

for(count = 0; count < 3; count++)

for(i = 0; i < 4 ; i++)

a[i] += b[i];</pre>

let blocks A, B, C and D contain the data b[0], b[1], b[2] and b[3] respectively. If the cache is fully associated, with LRU chosen as the replacement policy, then the data blocks will be loaded into the cache in the following sequences:

In (2), due to limited capacity, A is replaced by D as it is the least recently used one. However, block A is immediately in need after D when the outer loop is entered again (in (3)), and thus a cache miss follows. This situation continues until the end of the loops. The same situation occurs when FIFO policy is used.

Though there is no prefect cache line replacement scheme found so far, a good replacement algorithm should try to reduce the probability of wrongly replacing a useful cache line.

Although the IAP scheme can prefetch data accurately, the cache may not large enough to accommodate all lines brought in by demand fetch and prefetch

#### Chapter 5 Replacement and Placement Policies of Prefetched Lines

requests. As a result, conflict misses occur frequently when the working set of the program is larger than the cache size, so we have proposed the Instant Zero replacement policy [SzY97] is proposed to handle the problem. IZ scheme is aimed at managing the cache replacement more efficiently and reducing the thrashing misses. It is found that the data in IAP lines are most likely to be referenced once only. If these prefetched lines are placed in the cache and obey the LRU cache line replacement policy, as they have lost the benefit of referencing in the near future once after being referenced, they are just occupying the precious space in cache without any contribution. As a result, most of them should be the best candidate to be replaced when either capacity or conflict misses occur. That is the reason why the proposed IZ replacement policy is used to handle these IAP lines. As a result, after the requested data of an IAP line has been referenced, it should be the best candidate to be discarded when there are conflicts among the cache lines.

## 5.1.1 The Instant Zero Scheme

In the IAP scheme, conflict misses are the main concern. If a line (say line i) is being referenced, and was not found in the cache, then a miss occurs. The idea of IZ is not to reduce the miss penalty caused by the reference to line i, but to minimize the probability of cache misses in the future. We can easily observe that most cache lines that generated by demand fetch or prefetch-on-miss possess certain degrees of localities, and those lines prefetched by the IAP scheme are likely to be referenced once only. As a result, the IAP lines that have been referenced should be the best candidate to be discarded if conflicts on the cache lines occur. Therefore, the replacement strategy in the IAP scheme is a mixed strategy by using both IZ and LRU.

The mixed replacement policy of LRU and IZ can be summarized as follows. [1] The replacement policy for non-IAP scheme cache lines (either by demand fetch or by default prefetching) still obey the LRU policy. [2] For those lines prefetched by the IAP scheme will follow either LRU or IZ according to the following rule : • If the prefetch address is not the same as the current data reference line, then this prefetched line will follow the LRU policy. On the other hand, if the prefetch is the same as current data reference line, then as mentioned before, the block preceding it or following it will be prefetched. And this prefetched line will obey the IZ policy, in which the priority of the line will set to 0 immediately after its reference.

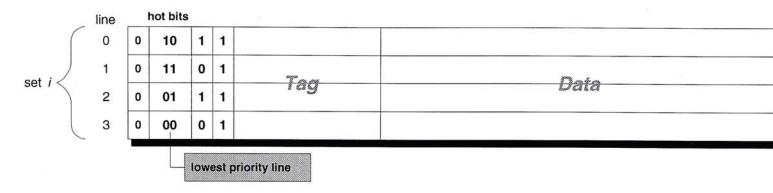

To indicate whether a line is prefetched by the IAP scheme, 1 extra bit for each cache line is needed. The cache lines in a four-way set associative cache will look like Figure 5.1.

| D <sub>1</sub> | H <sub>1</sub> | I,                                                                   | S <sub>1</sub> | PTag 1            | Data 1            |  |  |  |  |

|----------------|----------------|----------------------------------------------------------------------|----------------|-------------------|-------------------|--|--|--|--|

| D <sub>2</sub> | H <sub>2</sub> | I <sub>2</sub>                                                       | S <sub>2</sub> | PTag <sub>2</sub> | Data 2            |  |  |  |  |

| D3             | H <sub>3</sub> | I <sub>3</sub>                                                       | S <sub>3</sub> | PTag <sub>3</sub> | Data 3            |  |  |  |  |

| D4             | $H_4$          | I <sub>4</sub>                                                       | S4             | PTag <sub>4</sub> | Data <sub>4</sub> |  |  |  |  |

| 1              | 2              | 1                                                                    | 1              |                   |                   |  |  |  |  |

| D Dirty bit    |                |                                                                      |                |                   |                   |  |  |  |  |

| Ŧ              |                | Hot bit, which indicates the priority of the corresponding data line |                |                   |                   |  |  |  |  |

|                |                | IAP bit, set if the line is prefetched by the IAP scheme             |                |                   |                   |  |  |  |  |

| 5              |                | Line status bit (Valid bit):                                         |                |                   |                   |  |  |  |  |

| РТар           | )              | Physical tag                                                         |                |                   |                   |  |  |  |  |

| Data           |                | Cache Data                                                           |                |                   |                   |  |  |  |  |

Figure 5.1: A theoretical representation of a set in a four-way set associative cache

The hot bits are used to indicate the priorities of the lines following LRU replacement policy. When a line in the cache is referenced or a new line is brought into the cache, the hot bits of the lines will be updated. In the former case, the referenced line will have the hot bits updated to the largest number within the same set. Those lines with hot bits value larger than the original value of that of the referenced line will have their hot bits decreased by 1, while others remain unchanged. In the latter case, the hot bits value of each cache line will be decreased by 1, and the one with new value equal to 0 will be displaced. The new line will have its hot bits value set to the highest number within the set. Therefore, lines

with a lower priority are more likely to be kicked out, as they are the *Least Recently Used* one. In case of conflict in the cache lines, the line with hot bits equal to 0 will be displaced in order to bring in a new line.

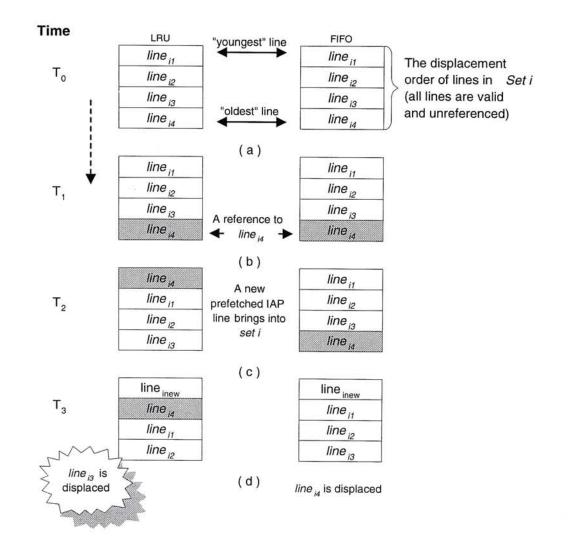

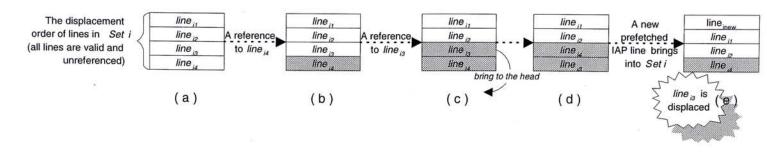

Figure 5.2: Before a reference to an IAP line

Now, let us have a look on how the IZ works within a set (say set i). Refer to Figure 5.2, if there has a miss to set i, then line 3 will be displaced. Since it is the one with lowest priority (the *least recently used* one). Suppose there is a reference go to line 0 before such a miss occurs, as it is an IAP line (with IAP bit set), it is then considered useless and will be the most likely one to be kicked out in future conflicts. Other than setting the priority of line 0 to 0, those lines with priorities lower than the original priority of line 0 should be incremented by 1. Those lines with priorities higher than the original priority of line 0 remain unchanged. As a result, the lines in the set with the priorities updated will look like Figure 5.3. Therefore, if there is a miss now, then line 0 instead of line 3 is the first one to be displaced.

The control flow of the proposed scheme is shown in Figure 5.4.

Figure 5.4: Control Flow of the IZ Replacement Policy

#### Chapter 5 Replacement and Placement Policies of Prefetched Lines

If a line is prefetched by the IAP scheme, then the IAP bit in the corresponding entry will be set to 1. These IAP lines will be treated as normal cache lines until there is a reference to it. When an IAP line is referenced, its priority will be set to 0 immediately after its reference to obey the IZ replacement policy.

# 5.2 Priority Pre-Updating and Victim Cache

In order to minimize the cache pollution and localize the influences brought by prefetched lines, we propose the Priority Pre-Updating scheme (**PPU**) to shorten the life time of possibly erroneously prefetched lines. The effect of adding a small fully-associative victim cache to hold the unreferenced prefetched lines ejected from cache is also discussed here.

## 5.2.1 Priority Pre-Updating

A PPU unit is added to keep track of all the prefetched lines according to their time of prefetching. Whenever there is a reference to a prefetched line, priorities of those former prefetched lines, which are unreferenced and precede the current referenced line in the PPU unit, will be decremented by a constant stride. Normally, the priority of a line updates only when there are references to any lines within the *same set*. However, under the PPU scheme, the priorities of other lines in different sets may also be changed.

In fact, the PPU aims at reducing the cache pollution problem as well as retaining the potential temporal locality of other lines. Figure 5.5 shows the overview of the architectural model of the cache under the PPU scheme.

As shown in Figure 5.6, each entry in PPU maps to a prefetched line in the cache. When there is a reference go to a cache line, say  $line_{03}$  (entry 3 in PPU), since  $line_{01}$  and  $line_{10}$  precede  $line_{03}$  in PPU, their priorities will be decreased by 1. The cache lines following  $line_{03}$  in PPU, such as  $line_{n0}$ , will not be affected.

Figure 5.5: Architectural model of IAP scheme with PPU

# 5.2.2 Priority Pre-Updating for Cache

The basic rules of PPU are - [1] All prefetch-on-miss lines will be recorded in PPU unit, and [2] When there is a reference, if the requested line is found in PPU unit, those preceding *unreferenced* lines will have their priority decrement by 1. [3] The corresponding entry in the PPU unit for this reference line will be deleted.

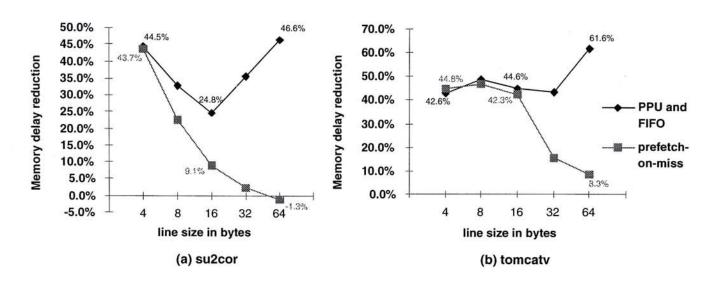

# 5.2.3 Victim Cache for Unreferenced Prefetch Lines

Owing to the long delay between references of successive data, the priority preupdating scheme cannot obtain significant improvement in the cache performance, Data which have high potential to be referenced in the near future, are sometimes trashed out before their actual reference. In order to minimize the influence of this situation, we use a small victim cache with few entries as a secondary buffer for the unreferenced prefetch line. Therefore, a small fully-associative victim cache with four entries, each with the same size as a cache line, is integrated with cache. As experimental results show that victim caches with FIFO and LRU replacement policies have similar performance, FIFO is chosen as replacement policy in victim cache, for the ease of implementation in hardware.

Figure 5.6: Illustration of PPU

For each prefetched line discarded from the cache, it will first be checked if this line is unreferenced. If such a case is detected, this line will be placed in the victim cache. When the victim cache is full, the *oldest* line will be displaced. When there is a data reference to the cache, it will first check if the data appears in the data cache. If the data is not found in data cache, then it will check if the data is in the victim cache. If such a case happens, then one extra clock cycle will be spent to fetch the data from victim cache.

Actually, the victim cache itself does not prefetch data but act as a secondary buffer to store prefetched data. Experimental results show that the cache performance is significantly improved by using PPU with victim cache (PPUVC). Figure 5.7 gives a summary of the control flow of the PPUVC.

Figure 5.7: Control Flow of PPUVC

#### Chapter 5 Replacement and Placement Policies of Prefetched Lines

When a data line arrives, it will first check if it is a prefetched line. If so, then a record will be kept in the PPU unit. When there is a reference to any cache line, then priorities of the lines will be checked and updated. If there is any conflict occurs in the cache and a line has to be replaced, then the one with lowest priority will be discarded. If the line to be discarded from cache is an unreferenced prefetched line, then it will be placed to the victim cache. On the other hand, the lines that have been referenced will not be placed in the victim cache. These lines will be written back to lower level memory if they have been modified. Otherwise, they will be simply discarded from cache.

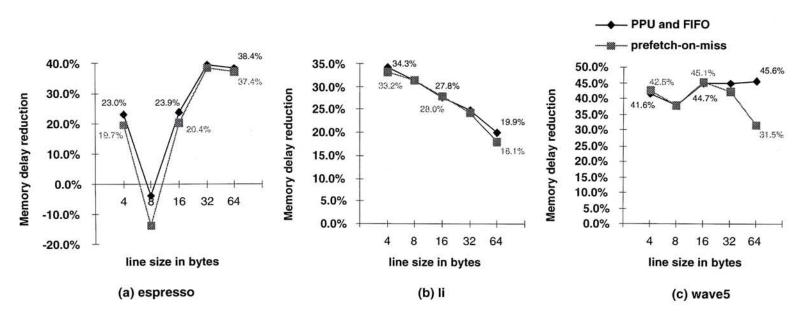

# 5.3 Prefetch Cache for IAP Lines

IAP lines have quite different property as compared to demand-fetch lines and prefetch-on-miss lines, since they are likely to reference only once during the entire program execution time. In order to localize their effects and minimize their influences to normal cache lines, a small on-chip prefetch cache is added [YoS98]. All IAP lines will be placed in the prefetch cache instead of the on-chip cache. A prefetch cache has the same structure as a cache, which consists of a series of entries with a tag, an valid bit, a dirty bit, a hot bit and a data line. Prefetch cache functions independently from the data cache. When there is a reference, both data cache and prefetch cache will be checked in parallel for any potential hits. Figure 5.8 gives the general picture of cache support in IAP architecture.

Through the on-chip cache controller, the processor attempts to access the data in the primary cache. If the data is there, then the processor will retrieve it. If a primary cache miss occurs, i.e., the data is not found in the primary cache, the cache controller checks to see if the data is in the secondary cache. If the data is found in the secondary cache, it is fetched into the primary cache. If the data is not present in the secondary cache, it is fetched as a cache line from main memory and is written into both the secondary cache and the primary cache before the processor retrieves it. For the sake of simplicity, we assumed these is no secondary

Figure 5.8: Cache Support in the IAP architecture

cache misses. In other words, the secondary cache is assumed to be infinitely large to hold all data. It is possible for the data to appear in different levels of memory. The data is kept consistent through the use of write back methodology, in which modified data is not written back to memory until the cache line is replaced. For any data prefetched by the prefetch unit, if this prefetch is generated by the IAP scheme, then it will be placed in the prefetch cache instead of the normal data cache. The data in prefetch cache is also kept consistent through write back methodology.

In addition to implementing LRU, the conventional cache replacement policy, in the prefetch cache, we also try using the IZ and FIFO replacement policies in it. We have just implemented one non-usage-based algorithm, FIFO, since nonusage-based algorithms are found to have similar performance as mentioned by Smith [Smi82].

Similar to the victim cache, the prefetch cache itself does not prefetch data but only keep prefetched data available for use. Figure 5.9 gives a summary of the control flow of the prefetch cache.

For each data line arrived in cache, it will be checked if it is a prefetched line. If the data line is a demand fetch line, then place it in the normal data cache. Otherwise, it will be further checked to see if it is prefetched by the IAP scheme. If such a case is detected, then it will be placed in the prefetch cache, and all

32

Figure 5.9: Control Flow of the Prefetch Cache Scheme

other types of prefetched lines will placed in the normal data cache.

# 5.4 Chapter Summary

In this chapter, two designs for hardware controlled replacement schemes and one replacement policy are proposed. By careful selection of data line to be replaced when a cache miss occurs, our replacement policies, IZ and PPUVC, will be able to reduce the cache pollution problem and retain the benefit of localities pose by normal cache lines. With the reference-once property of IAP lines, the placement design, prefetch cache, is able to localize the influence of IAP lines. Again, it helps to alleviate the cache pollution problem.

# Chapter 6

# **Performance Evaluation**

# 6.1 Methodology and metrics

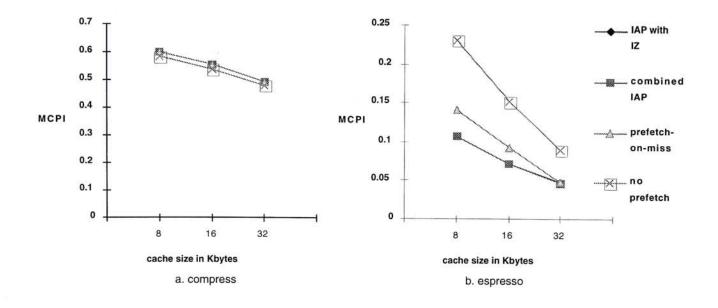

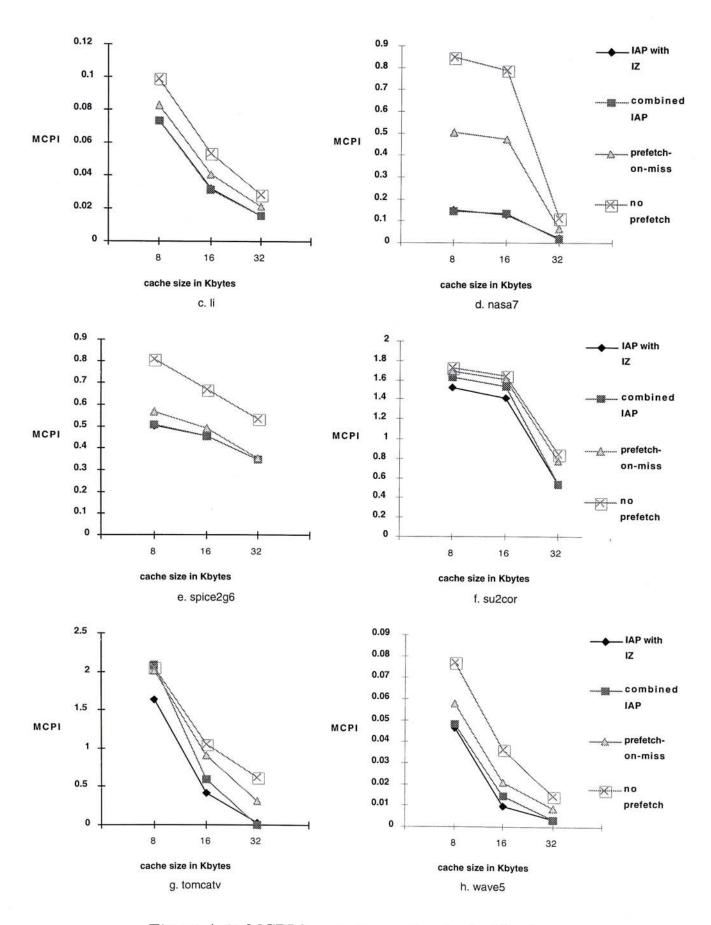

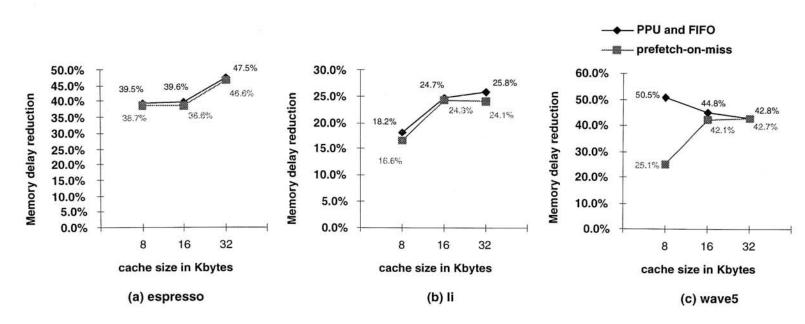

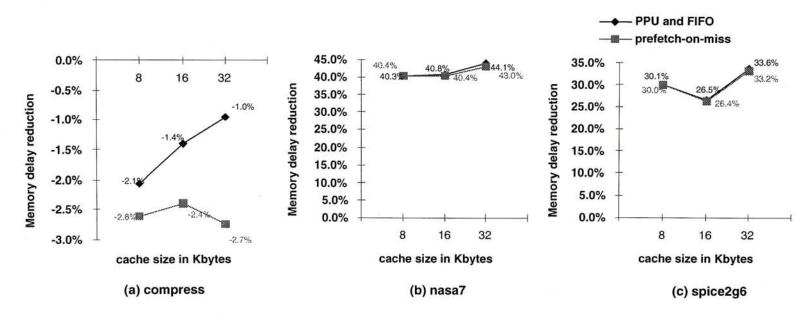

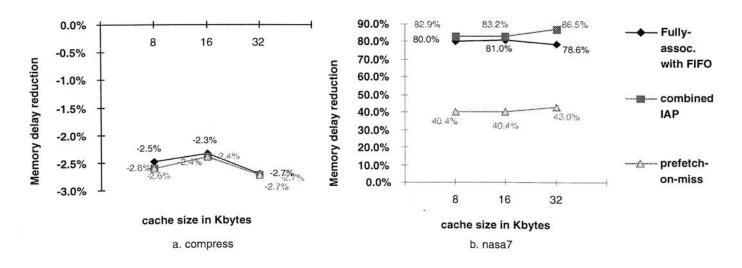

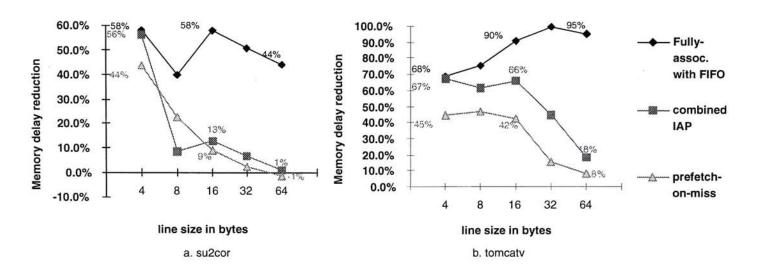

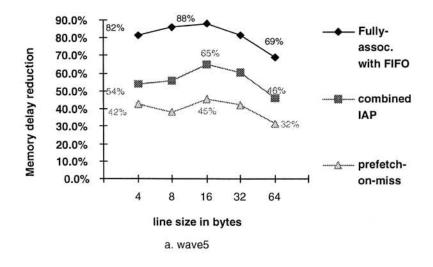

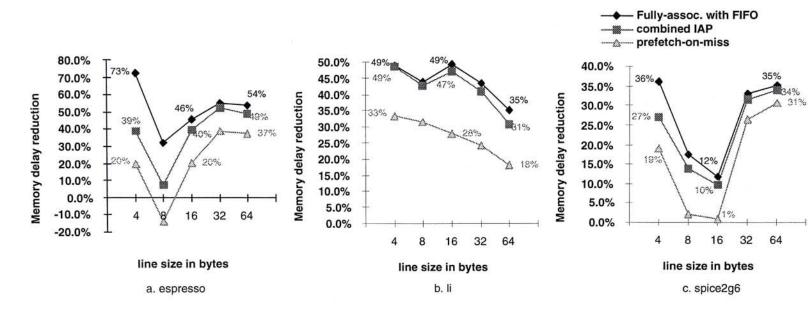

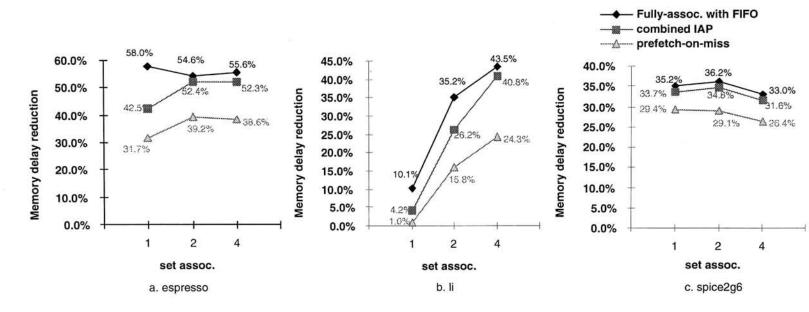

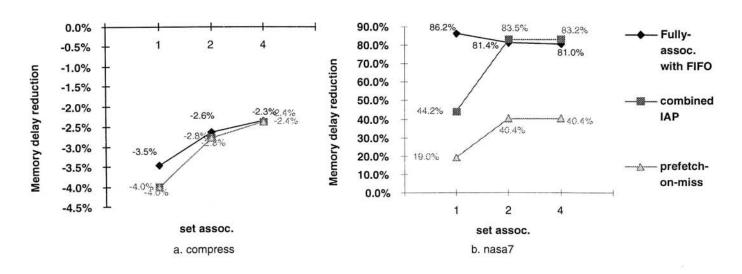

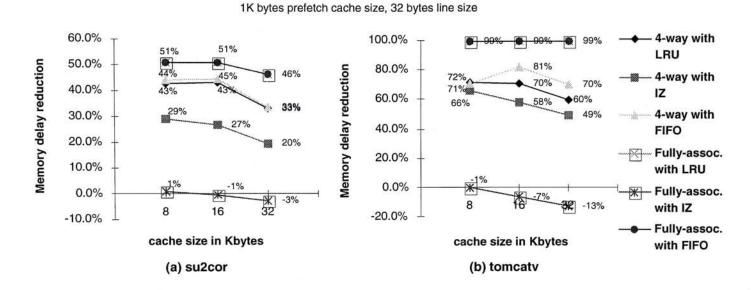

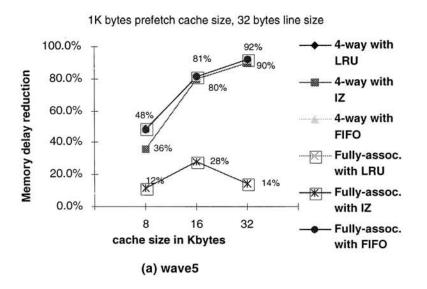

In order to have a deeper understanding of the algorithms proposed, and to show their potentials, we evaluate our proposed architecture using detail trace-driven cache simulation. We use eight SPEC92<sup>1</sup> benchmarks to generate traces for our study. They include three integer-intensive programs: compress, espresso and li, and five floating-point intensive programs: nasa7, spice2g6, su2cor, tomcatv and wave5. Table 6.1 gives a brief description of the benchmarks used.

| SPEC Benchmark Suite |          |                                                  |  |  |

|----------------------|----------|--------------------------------------------------|--|--|

| Program              | Language | Description                                      |  |  |

| compress             | С        | Adaptive Lempel-Ziv compression                  |  |  |

| espresso             | C        | Boolean function minimization                    |  |  |

| li                   | C        | Lisp interpreter solving the nine queens problem |  |  |

| nasa7                | Fortran  | Seven floating-point synthetic kernels           |  |  |

| spice2g6             | Fortran  | Analog circuit simulator                         |  |  |

| su2cor               | Fortran  | Quantum physics mass computation                 |  |  |

| tomcatv              | Fortran  | Mesh generation program                          |  |  |

| wave5                | Fortran  | Maxwell's equation solver                        |  |  |

Table 6.1: SPEC Benchmark Applications used

<sup>1</sup>SPEC is a trademark of the Standard Performance Evaluation Corporation

# 6.1.1 Trace Driven Simulation

Clearly, the type of jobs (i.e., the *job mix* or *instruction mix*) will be important to the cache simulation, since the cache performance can be highly data and code dependent.

For example, given a cache size of 8K lines with an anticipated miss rate of 10%, (1 miss in 10 memory references) we would require about 80K lines to be fetched from memory before it could reasonably be expected that each line in cache was replaced. To determine reasonable estimations of actual cache miss rates, each cache line should be replaced a number of times (the *accuracy* of the determination depends on the number of such replacements.) This net effect is a memory trace of some factor larger is required, say another factor of 10, or about 800K lines. That is, the trace length would be at least 100 times the size of the cache. Therefore, we chose to collect 100 millions instructions for each benchmark programs.

With the help of *xtrace* facilities, each of the chosen benchmark programs in the SPEC92 suite was traced on the IBM RS/6000 workstation and 100 million instructions for each benchmark were collected. The process of trace-driven simulation is summarized in Figure 6.1.

Figure 6.1: Trace-driven simulator using *xtrace*

The benchmarks were firstly compiled on the RS/6000 workstation. The executable codes were then instrumented by the program *instrument*, which inserted extra codes into the executable codes in order to extract the processor information during the program execution. The instrumented codes were then handled by *xtrace* and executed on the RS/6000 machine. The extracted processor information was then passed to the program *interface* via an explicit pipe. The program *interface* could be defined by the users to produce the desired trace format. The following information was recorded for each instruction that was traced:

$Inst\_Address, Inst\_Content, < Data\_Ref\_Address \, if \, any >, < No\_of\_Bytes\_Ref \, if \, any > ddress \, if \, any > ddress \, if \, any > ddress \, and \, a$

The simulator is designed such that it can read in the configuration descriptions such as cache size, set-associativity, line size etc., and simulation objects such as the CPU and the memory system are created based on these parameters. The trace data were stored in hard disk, such that a number of simulators could be run in parallel on different machines to speed up the simulations. The simulator read in the trace recorded one by one. Then the content of each instruction was decoded and the opcode, the addressing mode together with the register(s) used in the address calculation were found.

### 6.1.2 Caching Models

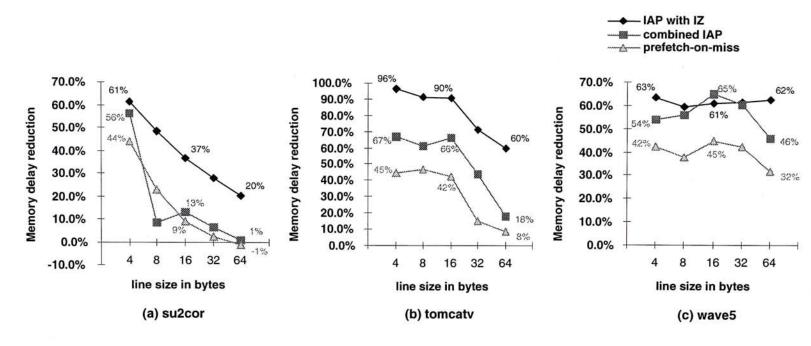

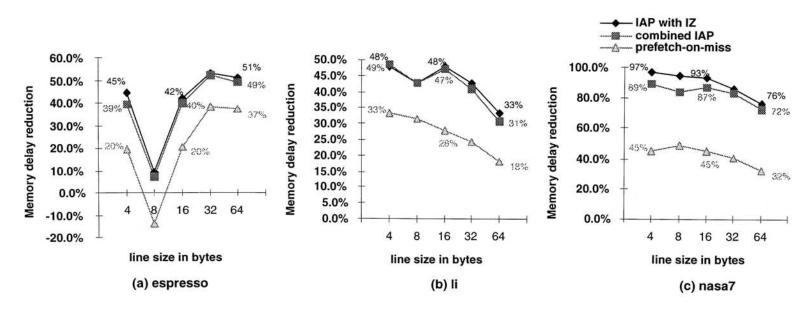

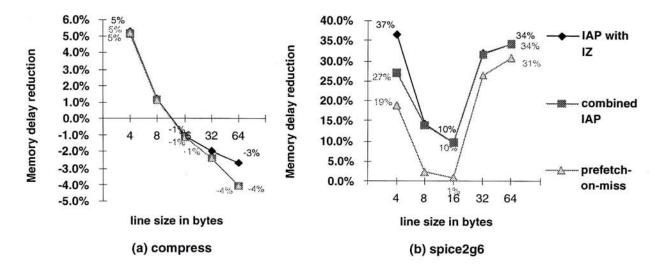

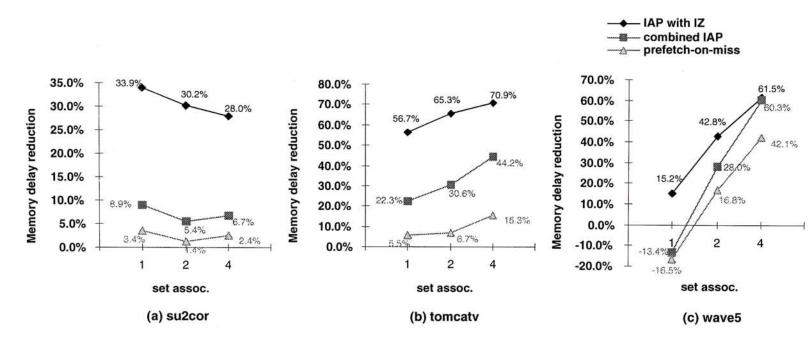

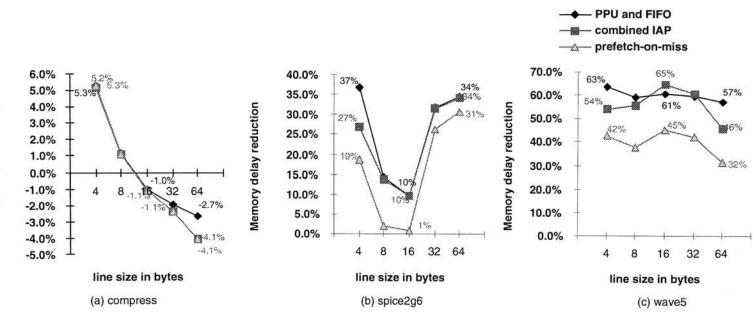

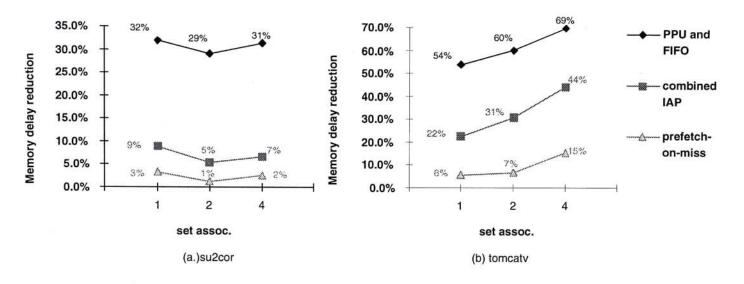

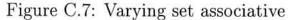

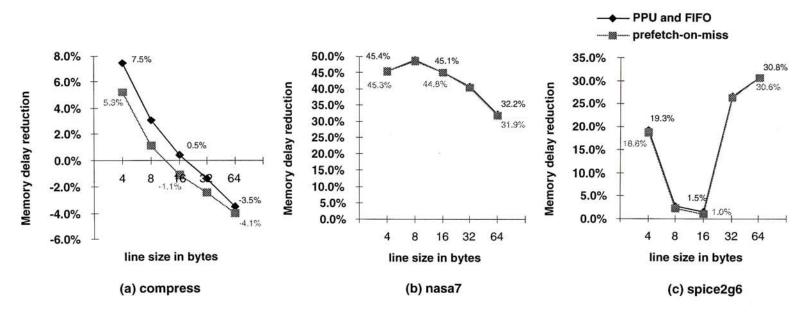

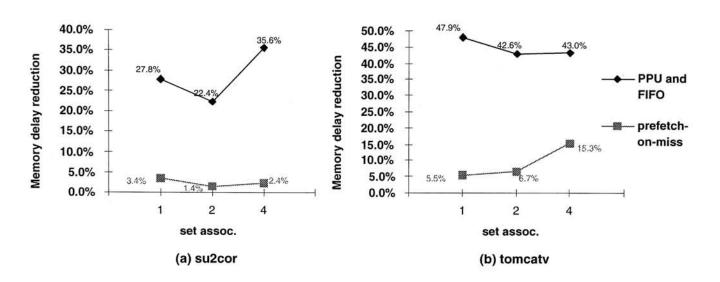

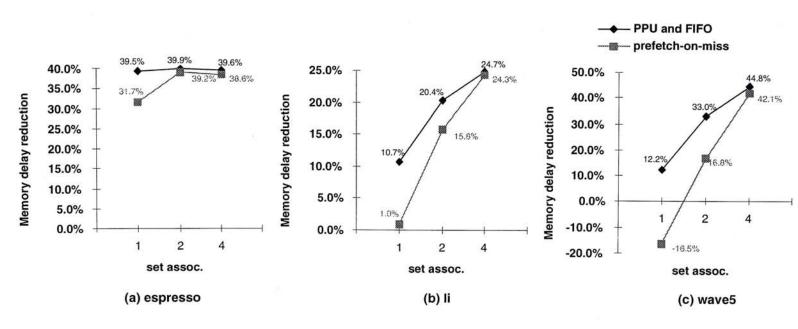

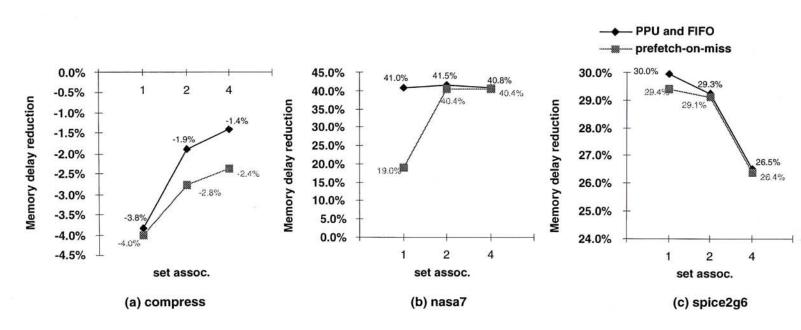

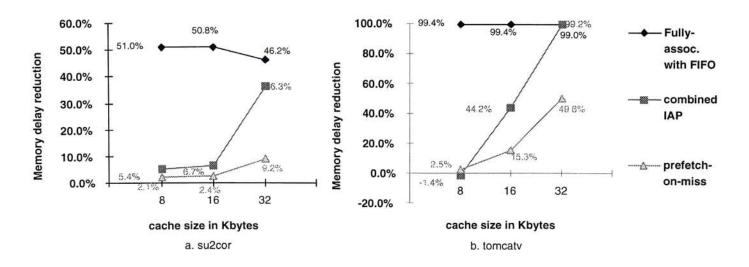

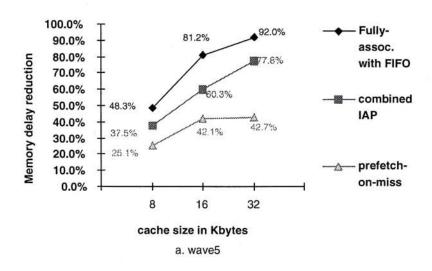

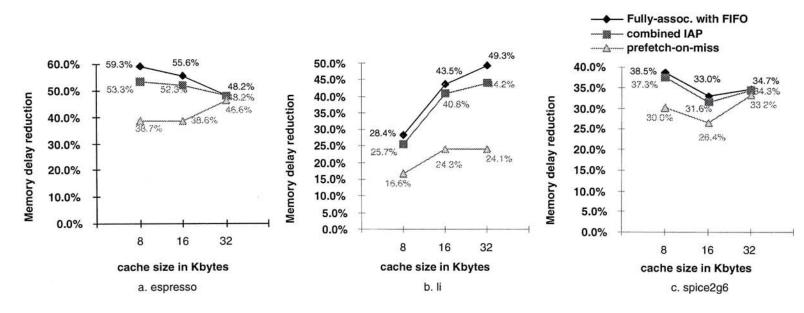

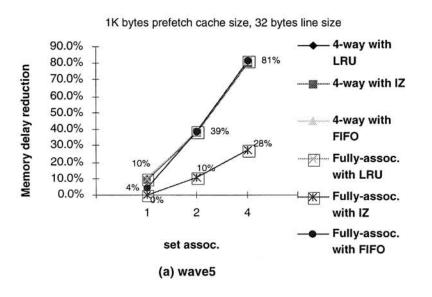

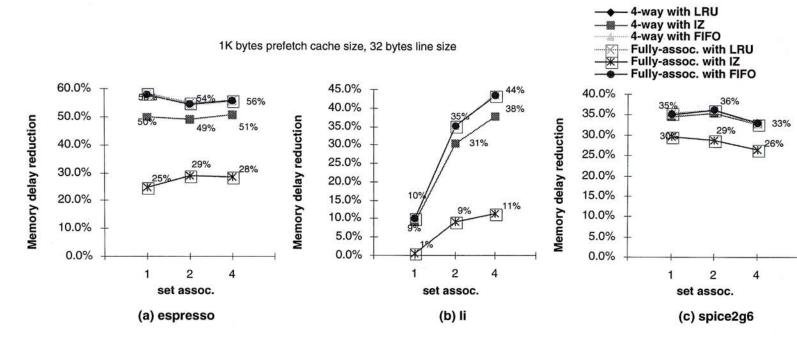

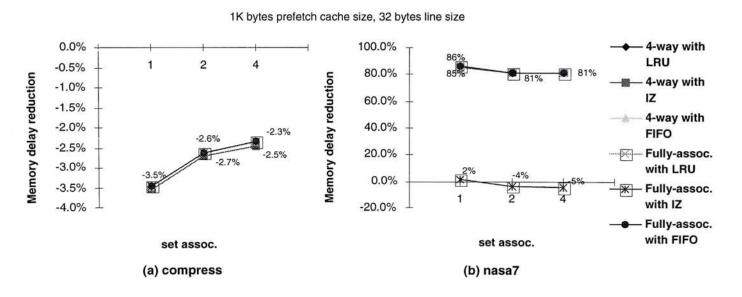

The baseline cache and the proposed caches use a write-back, write-allocate policy, and an 8-entry prefetch queue. We assumed that the processor has an ideal instruction cache with no instruction cache miss incurred. An elementary architectural model, which consists of a processor with perfect pipelined and a 4-way associative data cache with a line size of 32 bytes and a total size of 16K bytes, is defined for the simulations and the replacement algorithm is assumed to be LRU (Least Recently Used). For comparison, each dimension of the cache (cache size, line size and set associativity) is varied respectively for different simulations (cache sizes range from 8K bytes to 32K bytes, line size from 16 bytes to 64 bytes, and set associativities simulated from 1 to 4) while the other two are kept constant.