# VLSI Implementation of Discrete Cosine Transform Using a New Asynchronous Pipelined Architecture

LEE Chi-wai

A Thesis Submitted in Partial Fulfillment of the Requirements for the Degree of Master of Philosophy

> in Electronic Engineering

© The Chinese University of Hong Kong February 2002

The Chinese University of Hong Kong holds the copyright of this thesis. Any person(s) intending to use a part or whole of the materials in the thesis in a proposed publication must seek copyright release from the Dean of the Graduate School.

# Abstract of this thesis entitled: VLSI Implementation of Discrete Cosine Transform Using a New Asynchronous Pipelined Architecture

Submitted by LEE Chi-wai

for the degree of Master of Philosophy in Electronic Engineering

at The Chinese University of Hong Kong in June 2001

This thesis presents two different asynchronous VLSI implementations of Discrete Cosine Transform (DCT). Although asynchronous design has potential advantages over the synchronous design, the handshaking overhead and the design difficulties limit the speed performance of asynchronous design. In order to break through the barrier, a new asynchronous pipelined architecture is described in this thesis. It relaxes the handshaking protocol and has a simpler architecture, the performance of asynchronous design is improved. Since the new architecture employs dynamic logic, a new technique called Refresh Control Circuit is also introduced to reduce the performance degradation associated with the traditional technique.

The first DCT implementation is realized in a programmable DSP processor. This programmable processor makes use of asynchronous pipeline, dataflow architecture and parallelism, a reasonable but encouraging result of 22Mpixel/sec in DCT operation is obtained with a limited number of arithmetic units.

The second DCT implementation is performed on a dedicated 2D DCT/IDCT processor. It is a fully pipelined design and can operate at 76Mpixel/sec for 2D DCT/IDCT operation. It is capable of processing the high quality MPEG-2 and baseband HDTV signal in real-time, and is competitive to other synchronous designs even less arithmetic units are included in this processor.

The results of the two implementations demonstrate the high performance of the new asynchronous pipelined architecture and the advantages of the asynchronous technique in system design. It also encourages further development in asynchronous design.

本論文介紹了兩個可應用於離散餘弦變換 (Discrete Cosine Transform) 的異步 (asynchronous) 超大規模集成電路。雖然相對於同步設計 (synchronous design), 異步設計 (asynchronous design) 擁有潛在的優點,但因聯絡額外開銷 (handshaking overhead) 和設計上的困難而限制了異步設計的速度。為了突破這 個界限,本論文描述了一個新的異步管線式架構 (asynchronous pipelined architecture)。它放寬了聯絡協定 (handshaking protocol) 及擁有更簡單的架構, 令到異步設計的效能得以提升。因為這個新的架構應用了動態邏輯 (dynamic logic),本論文亦提出了一個名叫更新控制電路 (Refresh Control Circuit) 的新技 術。這技術能減少因使用傳統技術而導致的效能降格。

第一個離散餘弦變換設計是建於一個可程序數碼訊號處理器 (programmable DSP processor)。這個可程序處理器應用了異步管線、數據流程架構 (dataflow architecture) 及並聯 (parallelism),在執行離散餘弦變換時能夠在一秒中計算二十二萬素象。在有限的運算部件條件下,這是一個合理而且有鼓勵性的結果。

第二個離散餘弦變換設計是一個專用的二維離散餘弦變換處理器。這處理器是 完全管線式設計及能夠在二維離散餘弦變換運作中達到每秒七十六萬素象的運 算速度。這結果顯示這處理器能夠實時處理高質素的 MPEG-2 及高清晰度電視 (High Definition Television) 訊號。即使這處理器是使用了比較少的運算部件, 但在性能上仍可和其他同步設計競爭。

由這兩個設計所得出的結果可看出新的異步管線式架構的高效能表現及異步技術在系統設計上的好處。另外這結果亦對將來異步設計的發展起鼓舞作用。

## Acknowledgements

I would like to express my deepest gratitude to various individuals who provided me with sincere assistance in this research.

First of all, I would like to thank my supervisor, Prof. Oliver, C.S. Choy, for his invaluable guidance, advice, and support during the course of this research work. Notwithstanding his busy schedule, he has worked with me throughout the lengthy and demanding project, providing me continuous comments, patience, supervision, and encouragement. Without his endless help and assistance, this thesis would never have been possible. I would also like to express my gratitude to Prof. C.F. Chan who has given me insightful suggestions during my research work. In addition, a special expression of thanks goes to the research assistant, Mr. Jan Butas, for their kind assistance during my study.

Thanks are also due to my colleagues Mr. Cheng Wan Chi, Mr. Hon Kwok Wai, Mr. Leung Lai Kan, Miss Mak Wing Sum, Mr. Siu Pui Lam and Mr. Tang Tin Yau, the laboratory technician Mr. Yeung Wing Yee, and who have always been my sources of fun and encouragement.

I would also like to thank my close friend, Miss Vivian Tsoi, for her kind assistance and concern throughout the process of this study. Her constant encouragement and

v

everlasting patience and support were my strength, motivation, and inspiration all along. With her cordially support, I could exert my best effort on this study.

At last, I would also like to express my truly gratitude to my parents and my sisters for their understanding and devoted love throughout my whole course of studies. Without their concerns and support, I would not finish my study successfully. I am once again indebted to all of these people.

> Lee Chi Wai June 2001

# **Table of Contents**

| Abstract of this thesis entitled: | i   |

|-----------------------------------|-----|

| 摘要                                |     |

| Acknowledgements                  | v   |

| Table of Contents                 | vii |

| List of Tables                    | X   |

| List of Figures                   | xi  |

## Chapter 1

| Introdu | ction                      | 1 |

|---------|----------------------------|---|

| 1.1     | Synchronous Design         | 1 |

| 1.2     | Asynchronous Design        |   |

| 1.3     | Discrete Cosine Transform  |   |

| 1.4     | Motivation                 | 5 |

| 1.5     | Organization of the Thesis | 6 |

|         |                            |   |

## Chapter 2

| Asynch | ronous Design Methodology     | 7 |

|--------|-------------------------------|---|

| 2.1    | Overview                      |   |

| 2.2    | Background                    | 8 |

| 2.3    | Past Designs                  |   |

| 2.4    | Micropipeline                 |   |

| 2.5    | New Asynchronous Architecture |   |

## Chapter 3

| D | CT/ID | OCT Processor Design Methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|---|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|   | 3.1   | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|   | 3.2   | Hardware Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|   | 3.3   | DCT Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|   | 3.4   | Used Architecture and DCT Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|   | 3.4   | 동, 사람 전에서 집에서 잘 같아요. 이 것 같아요. 이 것 같아요. 그는 것 것 같아요. 것 같아요. 것 같아요. 것 같아요. 가지 않는 것 같아요. 이 것 같아요. 것 같아요. 이 것 같아요. 가지 않는 것 같아요. ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? |  |

|   | 3.4   | 같았는데 그 이 이것은 특별 방법은 것을 확여 성장을 받았다. 친구가 있는 것을 잘 들어오셨다. 물건을 가지 않는 것이 가지 않는 것이 가지 않는 것이 가지 않는 것이 하는 것이 있다.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|   |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

## Chapter 4

| New Te | chniques for Operating Dynamic Logic in Low Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | y |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 4.1    | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |

| 4.2    | Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |

| 4.3    | Traditional Technique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |

| 4.4    | New Technique – Refresh Control Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |

| 4.4    | 지 않는 것 같아요. 그는 것 같아요. 그는 것은 것 같아요. 그는 것은 것 같아요. 이 것 같아요. 그는 것 같아요. 그는 것 같아요. 이 것 같아요. 이 것 같아요. 이 것 같아요. 그는 것 같아요. 그는 것 같아요. 이 것 않아요. 이 것 같아요. 이 것 이 것 않아요. 이 집 이 집 이 집 이 집 이 집 이 집 이 집 이 집 이 집 이 |   |

| 4.4    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |

| 4.4    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |

| 4.4    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |

| 4.4    | 그렇게 이번 것 같아요. 그는 것 같아요. 그는 것 것 같아요. 그는 것이 아주 아무 아주 아주 가지 않는 것이 가지 않는 것이 가지 않는 것이 같아요. 이 가지 않는 것이 같아요. 이 가지 않는 것                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |

| 4.4    | 4.6 Operation Monitoring Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |

| 4.4    | . 2014년 - 11월 2017년 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |

## Chapter 5

| DCT | Implen | nentation on Programmable DSP Processor |  |

|-----|--------|-----------------------------------------|--|

| 5.  |        | verview                                 |  |

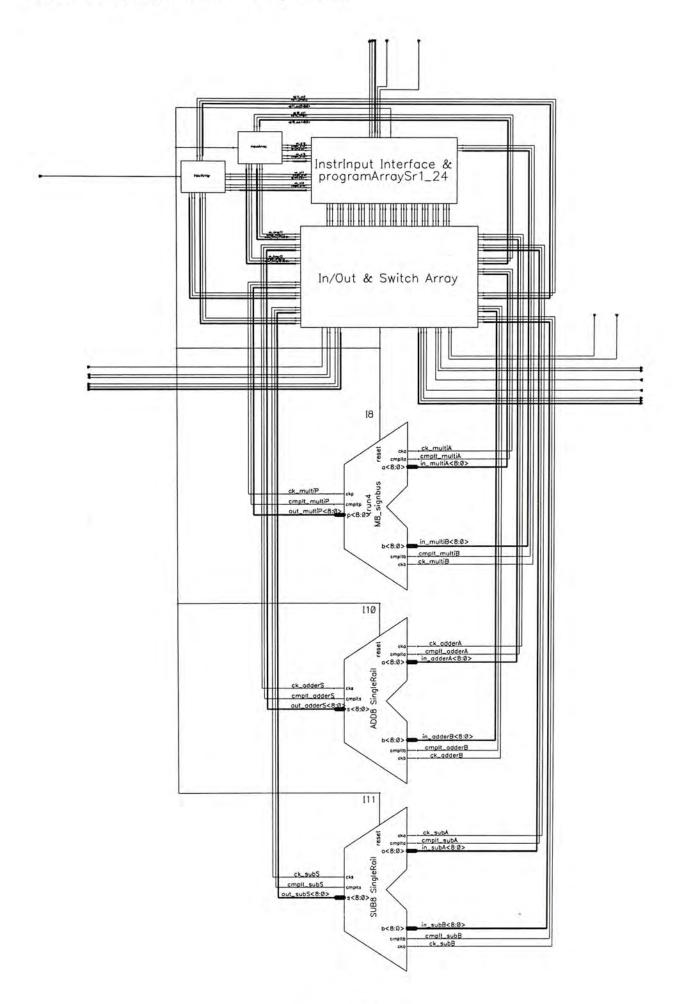

| 5.3 |        | ocessor Architecture                    |  |

|     | 5.2.1  | Arithmetic Unit                         |  |

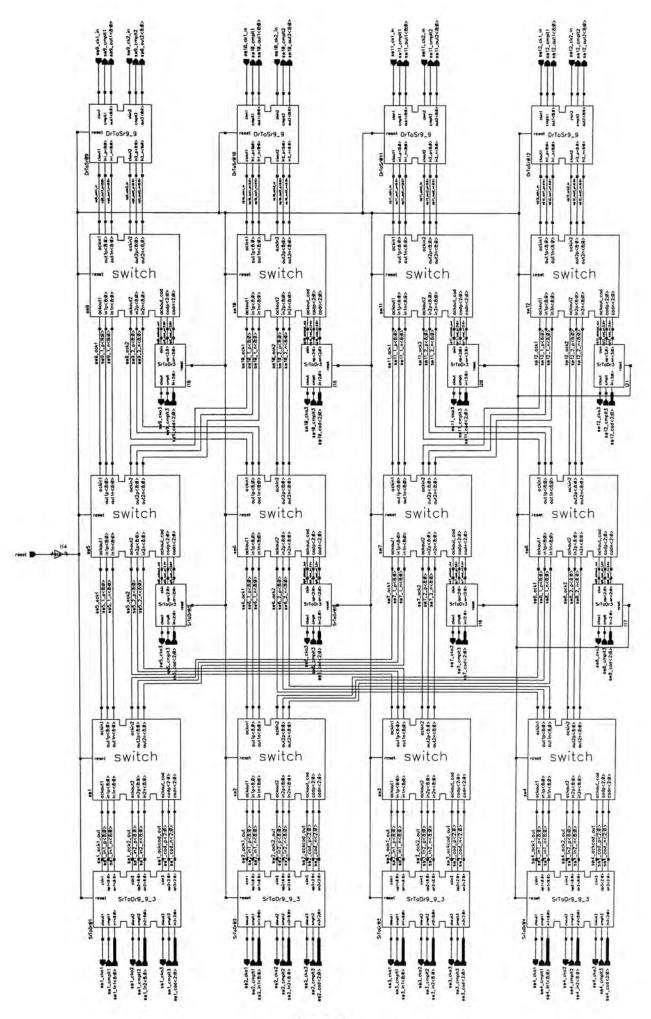

|     | 5.2.2  | Switching Network                       |  |

|     | 5.2.3  | FIFO Memory                             |  |

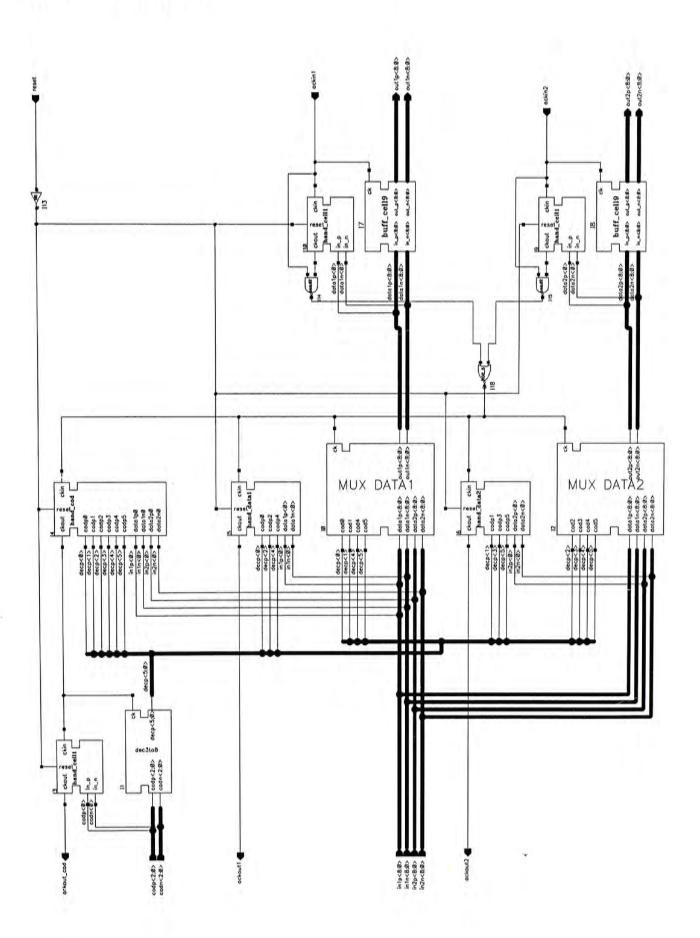

|     | 5.2.4  | Instruction Memory                      |  |

| 5.  | 3 Pr   | ogramming                               |  |

| 5.  |        | CT Implementation                       |  |

## Chapter 6

| DCT Implem | entation on Dedicated DCT Processor                                                              |    |

|------------|--------------------------------------------------------------------------------------------------|----|

|            | erview                                                                                           |    |

|            | T Chip Architecture                                                                              |    |

| 6.2.1      | 그는 정말은 이렇게 잘 못 하는 것이 같은 것이 있는 것이 같은 것이 있는 것이 같은 것이 같이 있는 것이 없는 것이 같이 많이 많이 많이 많이 많이 많이 많이 많이 없다. |    |

| 6.2.1.     | 1 Core Architecture                                                                              |    |

| 6.2.1.     | 2 Flow of Operation                                                                              |    |

| 6.2.1.     |                                                                                                  |    |

| 6.2.1.     |                                                                                                  |    |

| 6.2.2      | Combination of IDCT to 1D DCT core                                                               |    |

| 6.2.3      | Accuracy                                                                                         |    |

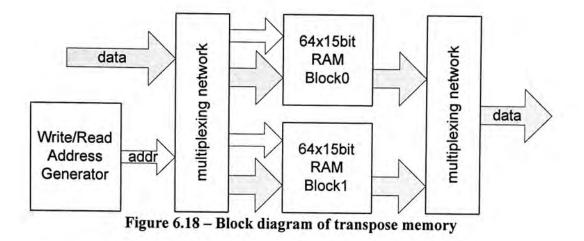

| 6.3 Tra    | anspose Memory                                                                                   |    |

| 6.3.1      | Architecture                                                                                     | 89 |

| 6.3.2      | Address Generator                                                                                |    |

| 6.3.3      | RAM Block                                                                                        |    |

## Chapter 7

| Results and | Discussions                            |  |

|-------------|----------------------------------------|--|

|             | verview                                |  |

|             | efresh Control Circuit                 |  |

| 7.2.1       | Implementation Results and Performance |  |

| 7.2.2       | Discussion                             |  |

| 7.3 Pr      | ogrammable DSP Processor               |  |

| 7.3.1       | Implementation Results and Performance |  |

| 7.3.2       | Discussion                             |  |

| 7.4 11      | D DCT/IDCT Core                        |  |

| 7.4.1       | Simulation Results                     |  |

| 7.4.2       | Measurement Results                    |  |

| 7.4.3       | Discussion                             |  |

| 7.5 Tr      | anspose Memory                         |  |

| 7.5.1       | Simulated Results                      |  |

| 7.5.2       | Measurement Results                    |  |

| 7.5.3       | Discussion                             |  |

## Chapter 8

| Conclusions | ) |

|-------------|---|

|-------------|---|

| Operations of switches in DCT implementation of programmable DS |  |

|-----------------------------------------------------------------|--|

| C Program for evaluating the error in DCT/IDCT core             |  |

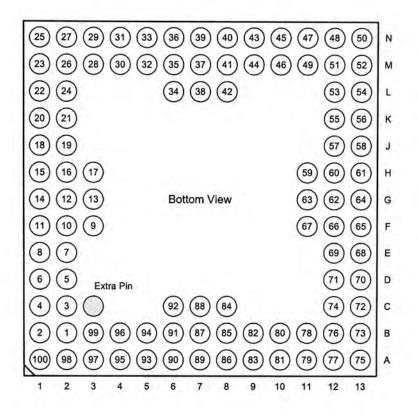

| Pin Assignments of the Programmable DSP Processor Chip          |  |

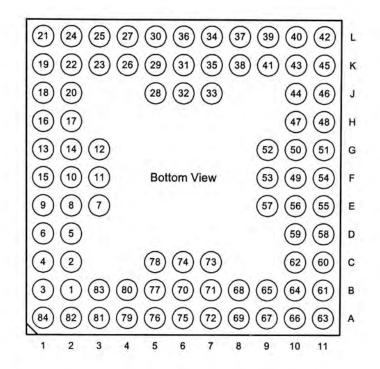

| Pin Assignments of the 1D DCT/IDCT Core Chip                    |  |

| Pin Assignments of the Transpose Memory Chip                    |  |

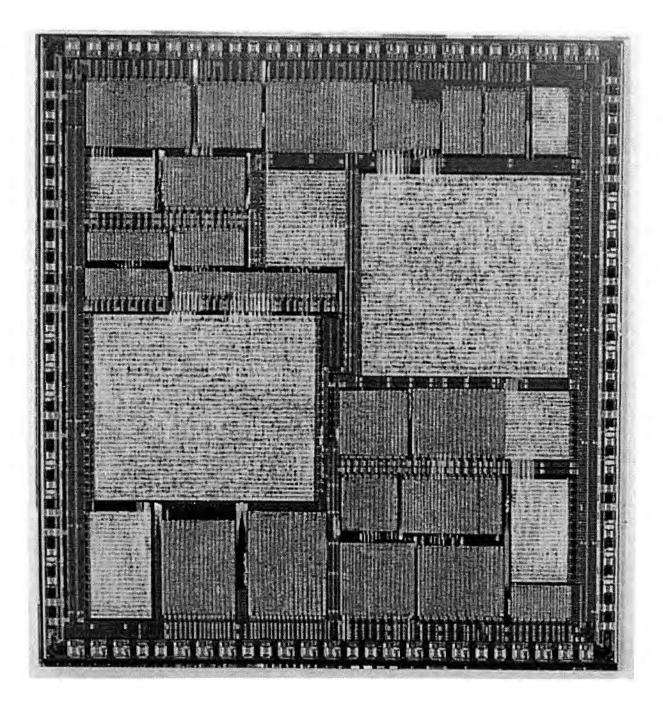

| Chip microphotograph of the 1D DCT/IDCT core                    |  |

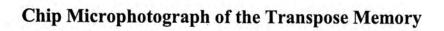

| Chip Microphotograph of the Transpose Memory                    |  |

| Measured Waveforms of 1D DCT/IDCT Chip                          |  |

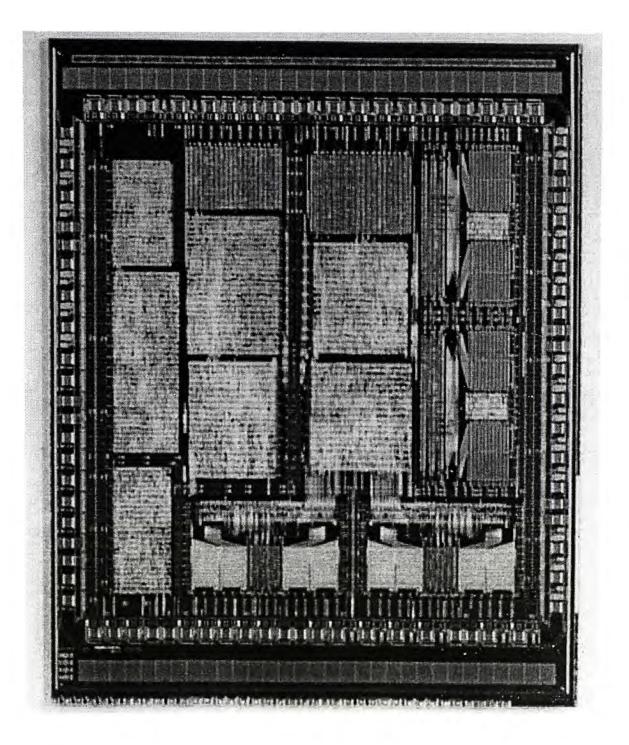

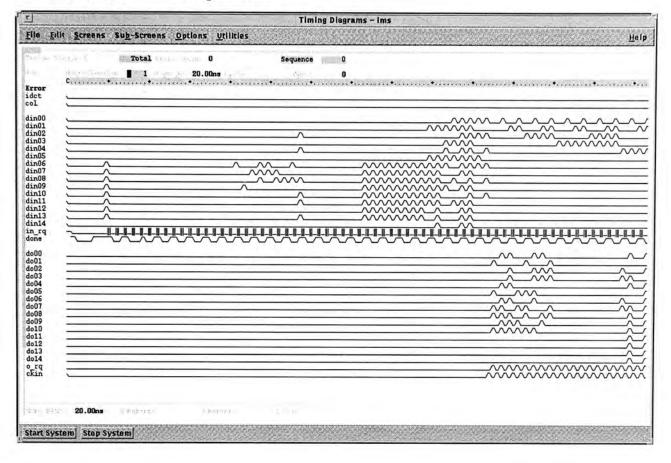

| Measured Waveforms of Transpose Memory Chip                     |  |

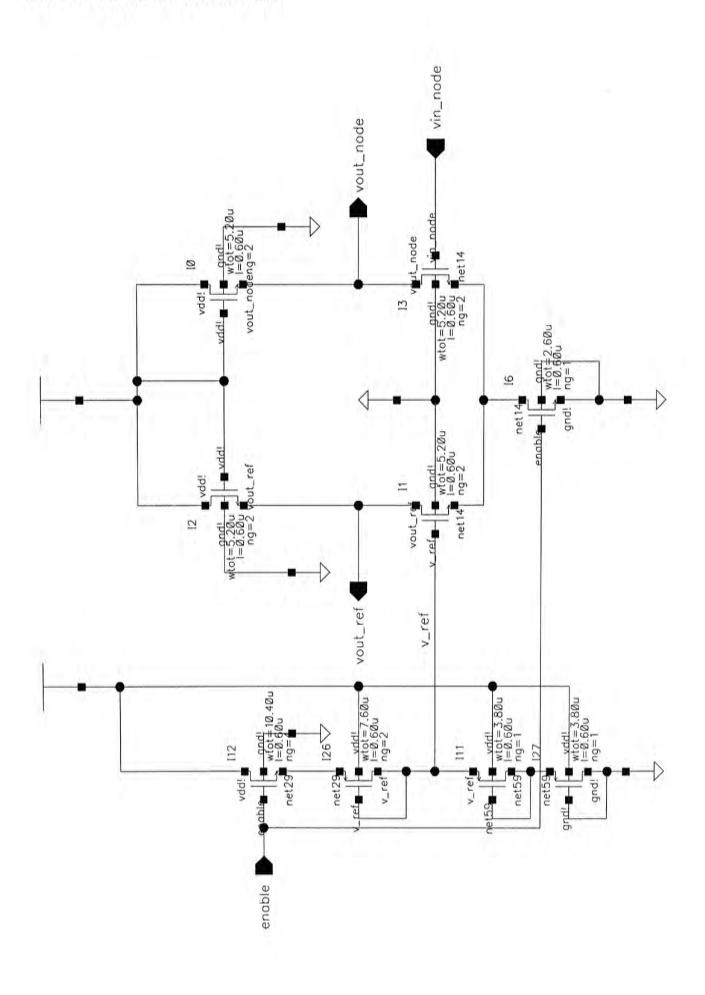

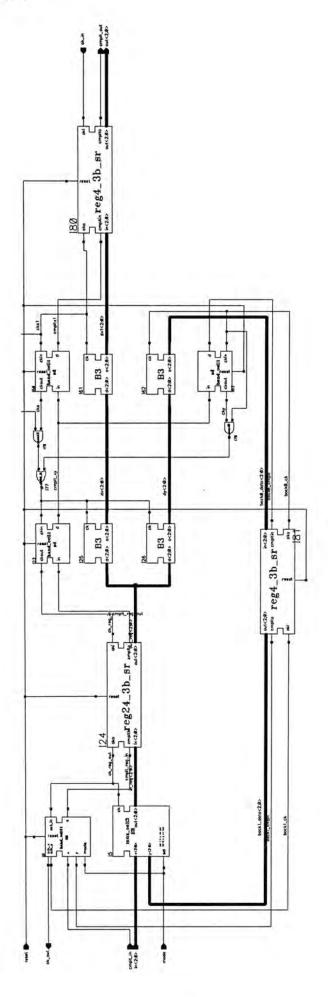

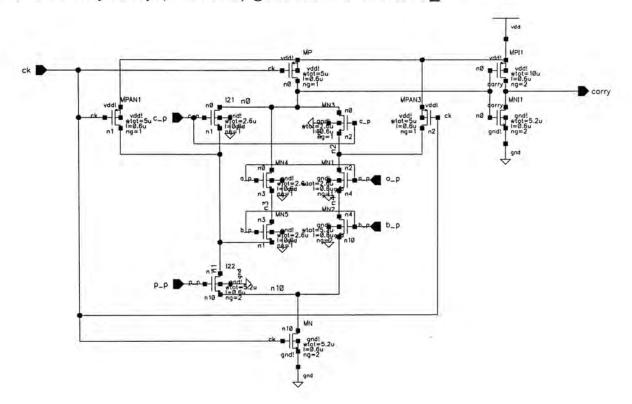

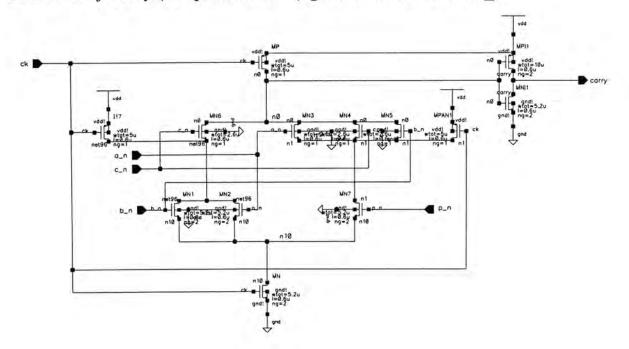

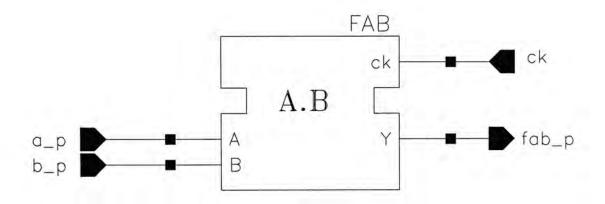

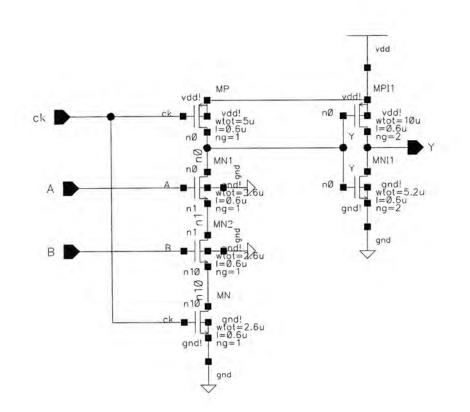

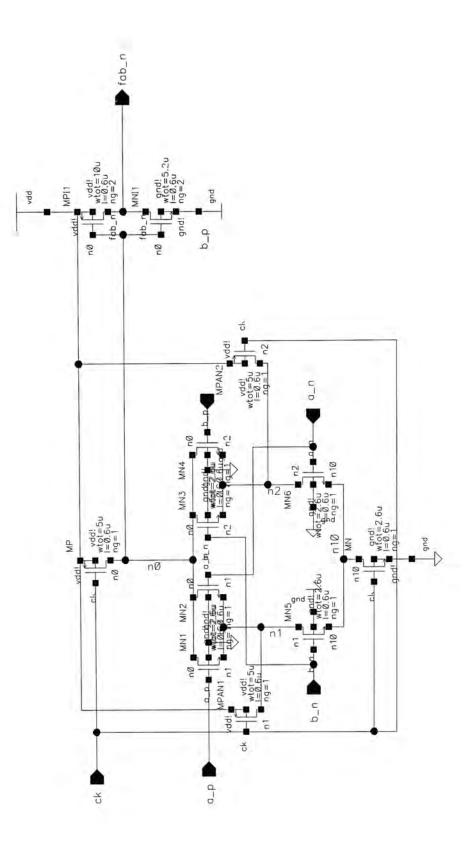

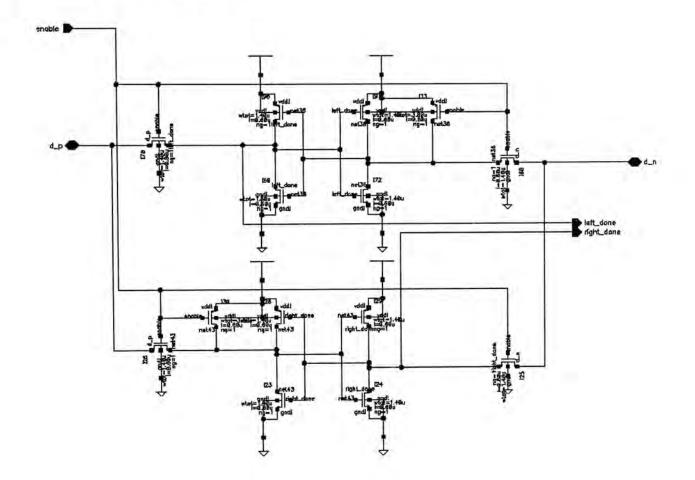

| Schematics of Refresh Control Circuit                           |  |

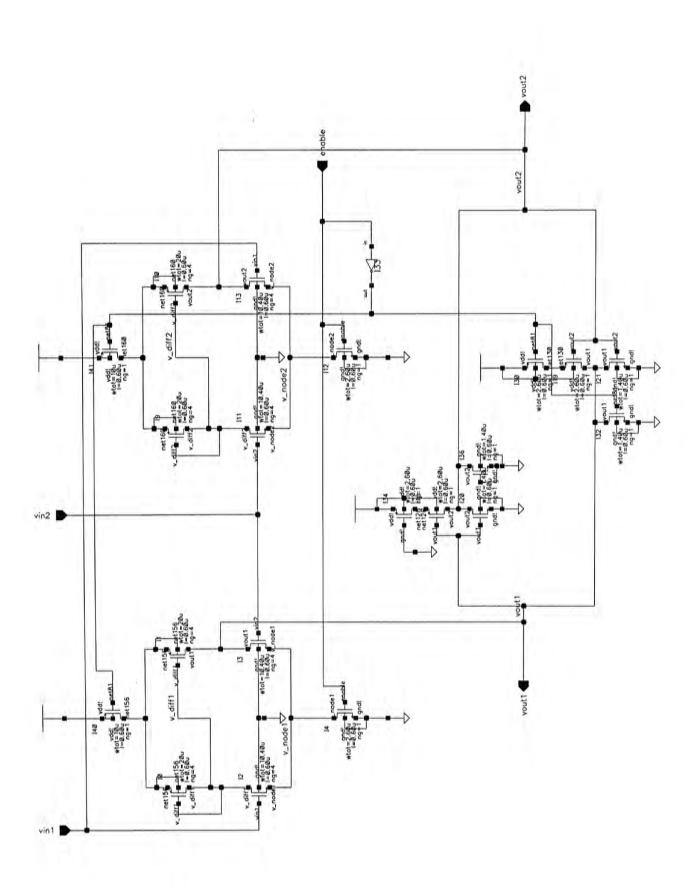

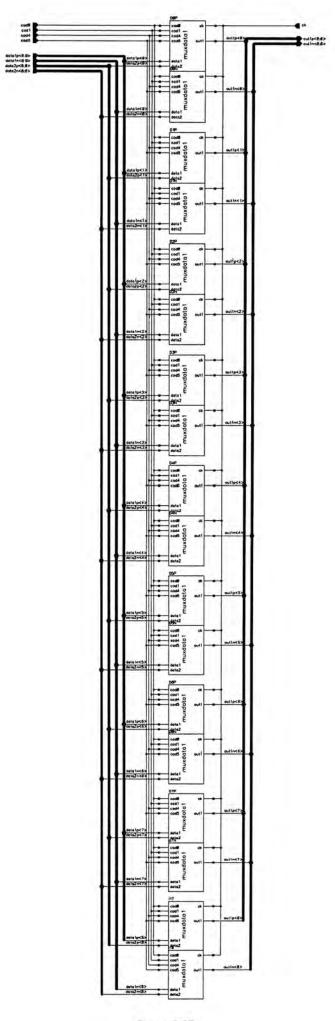

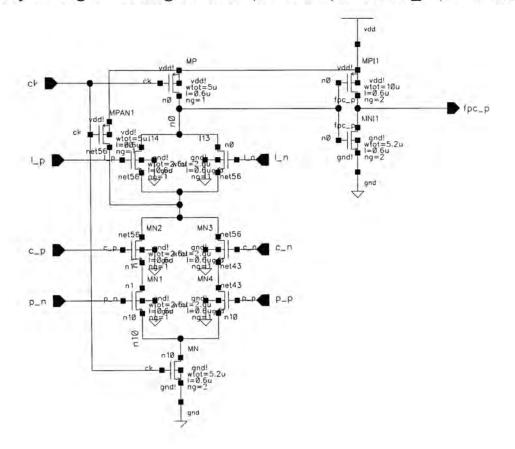

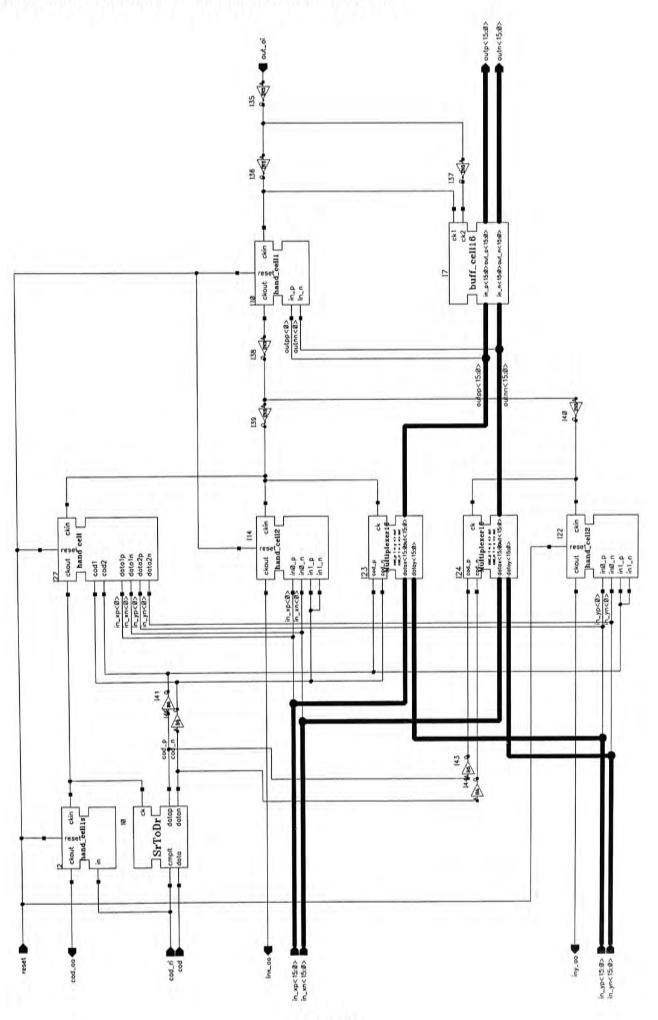

| Schematics of Programmable DSP Processor                        |  |

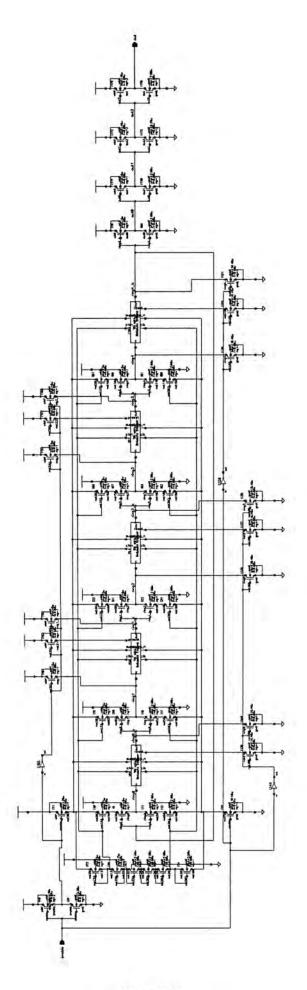

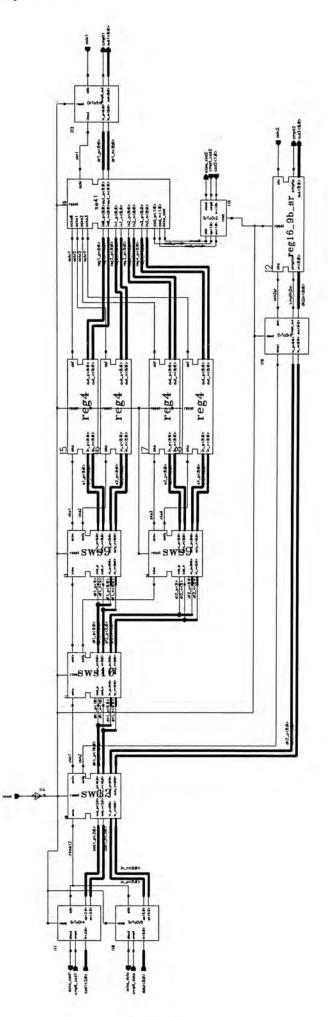

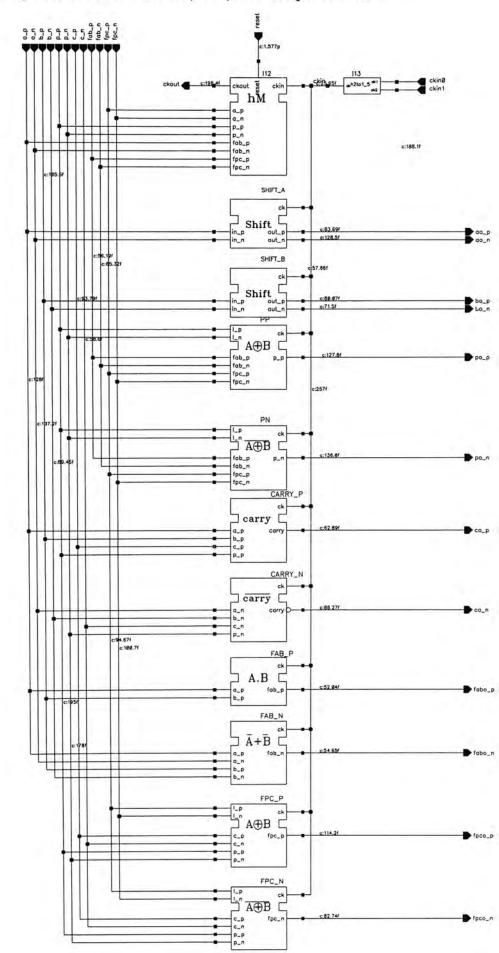

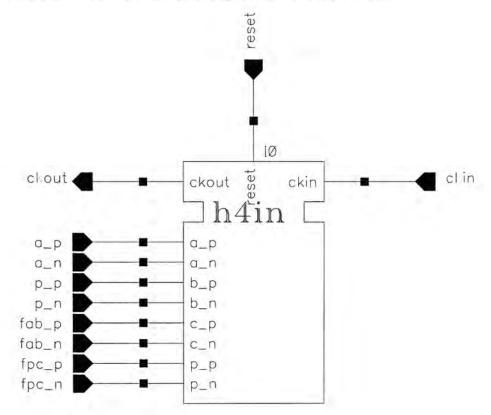

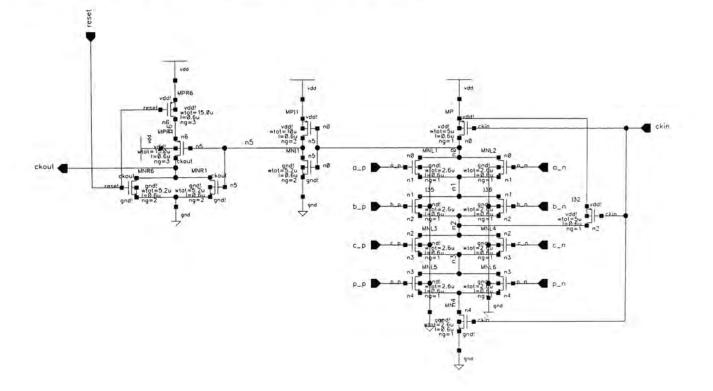

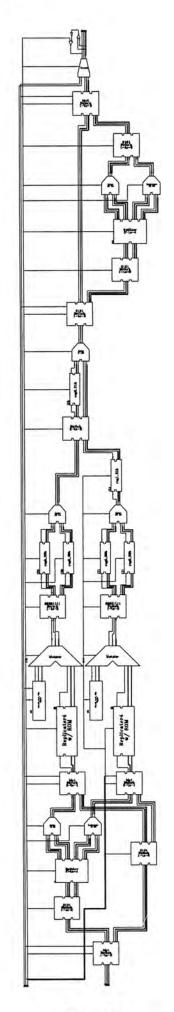

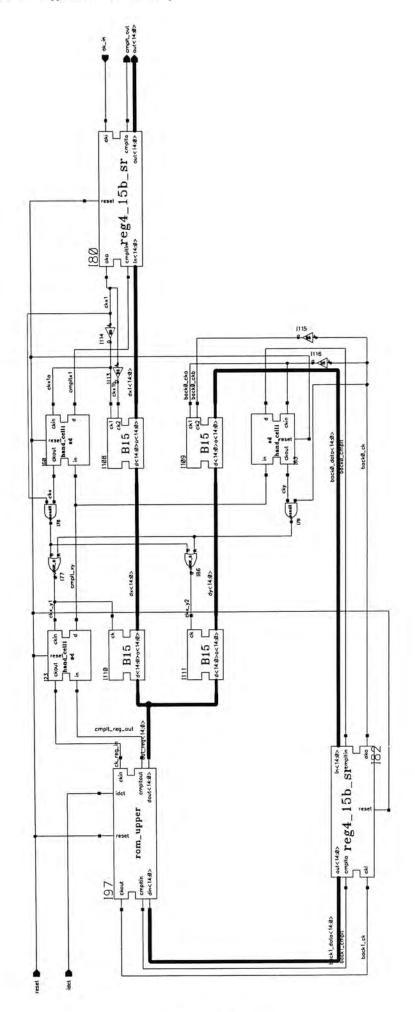

| Schematics of 1D DCT/IDCT Core                                  |  |

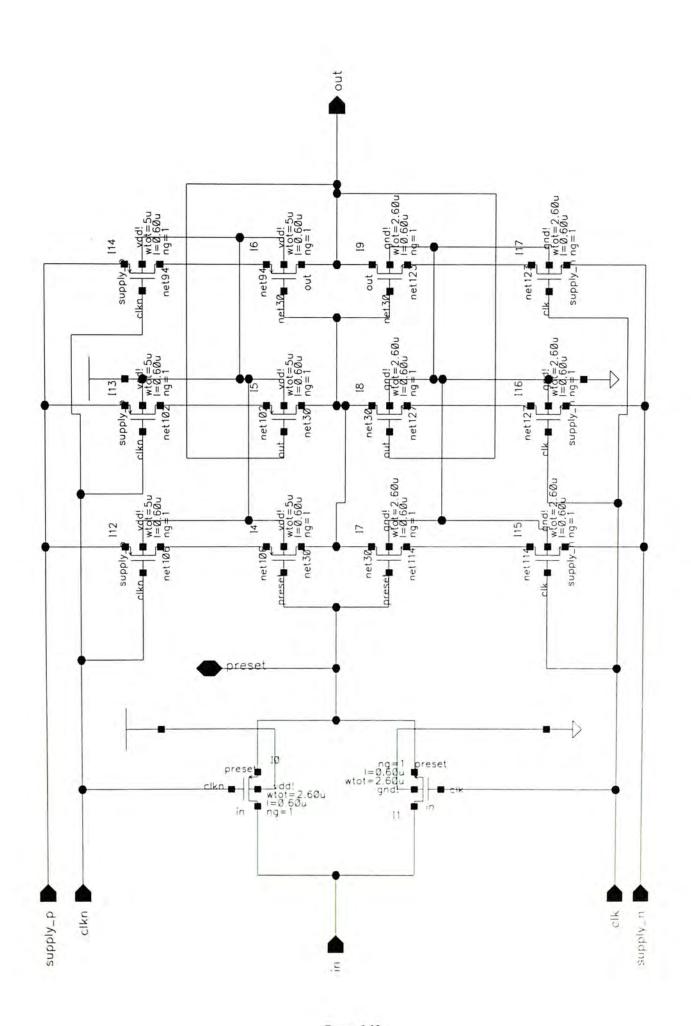

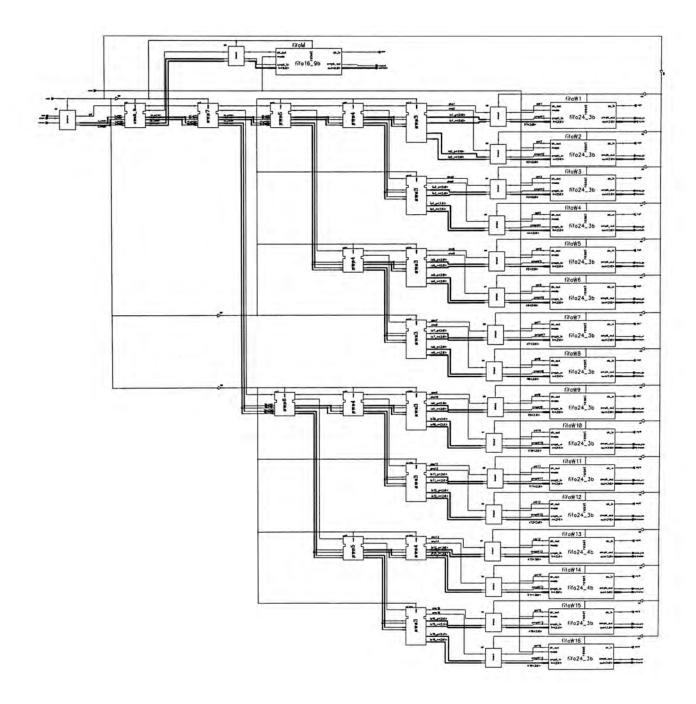

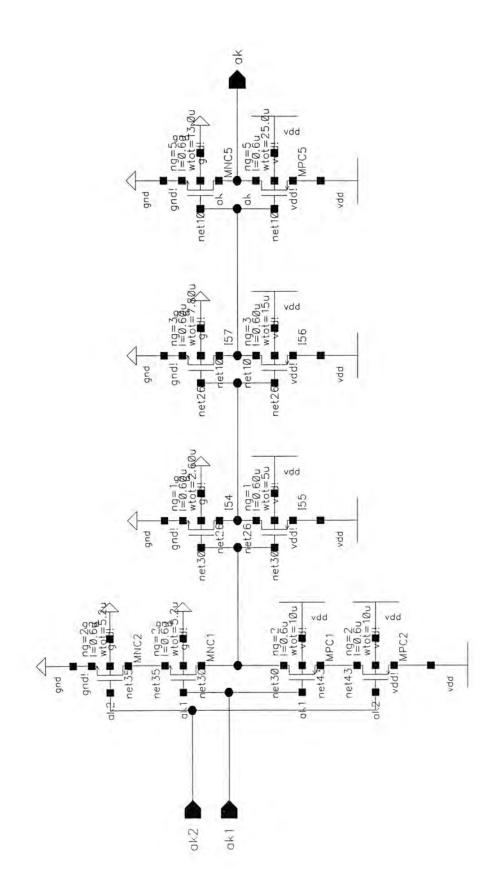

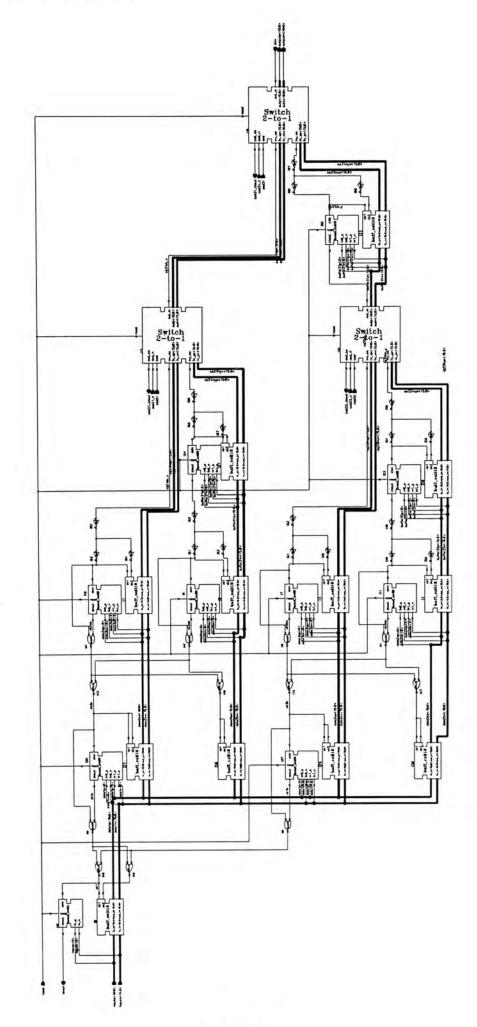

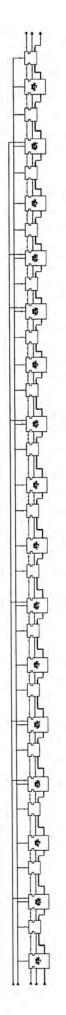

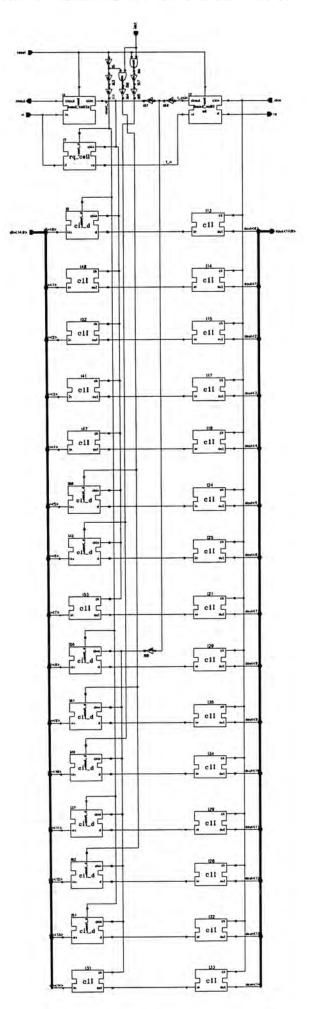

| Schematics of Transpose Memory                                  |  |

|                                                                 |  |

| References                                                      |  |

| Destau I thursday  | CD DOM | 107 |

|--------------------|--------|-----|

| Design Libraries - | CD-ROM | 191 |

# **List of Tables**

| Table 5.1 – Instructions of switch                                                   |

|--------------------------------------------------------------------------------------|

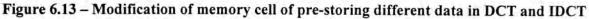

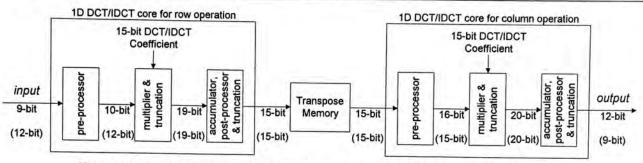

| Table 6.1 – Data rate at different stages of the 1D DCT core                         |

| Table 6.2 – Bit length in different parts of the 2D DCT/IDCT processor               |

| Table 6.3 – Accuracy of the 2D DCT/IDCT processor                                    |

| Table 6.4 – Four different operation modes of the unified ID DCT/IDCT core 87        |

| Table 7.1 – Transistor count on different units of Refresh Control Circuit           |

| Table 7.2 – Current drawn by the each parts of the Refresh Control Circuit           |

| Table 7.3 – Performance of multipliers by different techniques                       |

| Table 7.4 – Bit length information of the 9-bit programmable DSP processor 102       |

| Table 7.5 – Performance comparison of different 1D DCT implementations 103           |

| Table 7.6 – Performance comparison of 2D DCT implementation on different             |

| programmable processors106                                                           |

| Table 7.7 – Performance of different processing units on the 1D DCT/IDCT core 107    |

| Table 7.8 – Input data, measured result and calculated result of the DCT row         |

| operation                                                                            |

| Table 7.9 – Performance comparison of different 2D DCT implementations 113           |

| Table 7.10 – Simulation results of power consumption of different operation units in |

| the 1D DCT/IDCT core118                                                              |

| Table 7.11 – Comparison of power consumption on DCVSL and single-rail adder 120      |

| Table 7.12 – Performance of different units in the transpose memory                  |

|                                                                                      |

# List of Figures

| Figure 2.1 – Communications between sender and receiver in an asynchronous              |

|-----------------------------------------------------------------------------------------|

| circuit7                                                                                |

| Figure 2.2 – Timing diagram of (a)two-phase, (b)four-phase handshaking protocol.8       |

| Figure 2.3 - (a) connections in asynchronous circuit, (b) operation in asynchronous     |

| circuit9                                                                                |

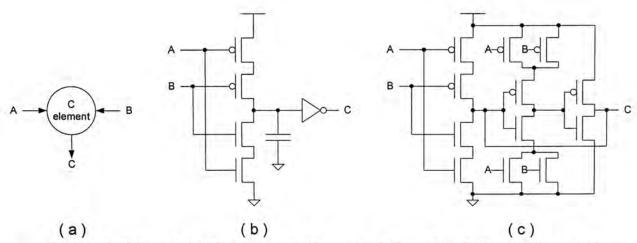

| Figure 2.4 – (a) symbol of C-element, (b) dynamic C-element and (c) static C-           |

| element                                                                                 |

| Figure 2.5 – Basic control FIFO sequence in Micropipeline structure                     |

| Figure 2.6 – Micropipeline with computation                                             |

| Figure 2.7 – Domino Logic                                                               |

| Figure 2.8 – Asynchronous architecture by using dynamic logic                           |

| Figure 2.9 – (a) new handshake cell, (b) timing diagram of a pipeline stage             |

| Figure $2.10 - (a)$ new asynchronous pipeline connection, (b) flow of operations in the |

| new asynchronous pipeline                                                               |

| Figure 2.11 – Differential Cascode Voltage Switch Logic (DCVSL)                         |

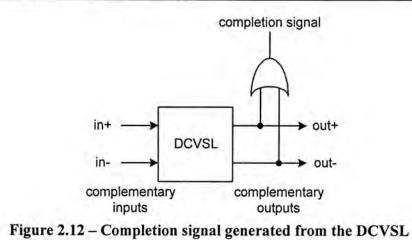

| Figure 2.12 – Completion signal generated from the DCVSL                                |

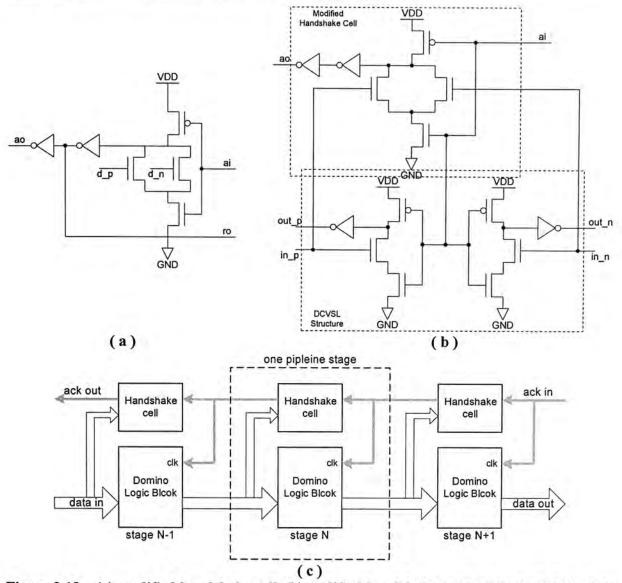

| Figure 2.13 – (a) modified handshake cell, (b)modified handshake cell and basic         |

| FIFO cell in DCVSL structure, (c) connection of the asynchronous pipeline 23            |

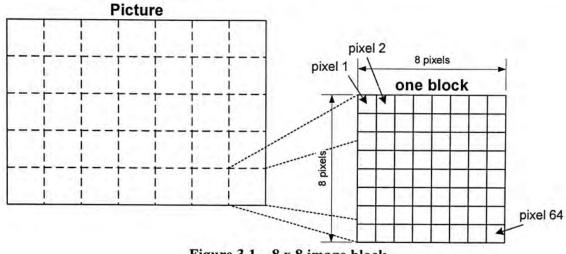

| Figure 3.1 – 8 x 8 image block27                                                        |

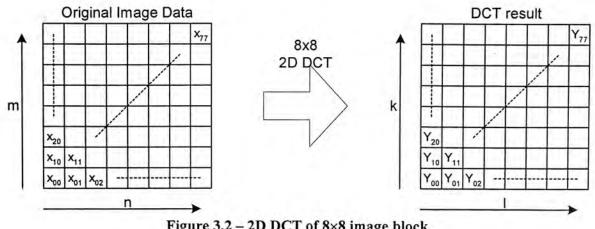

| Figure 3.2 – 2D DCT of 8×8 image block                                                  |

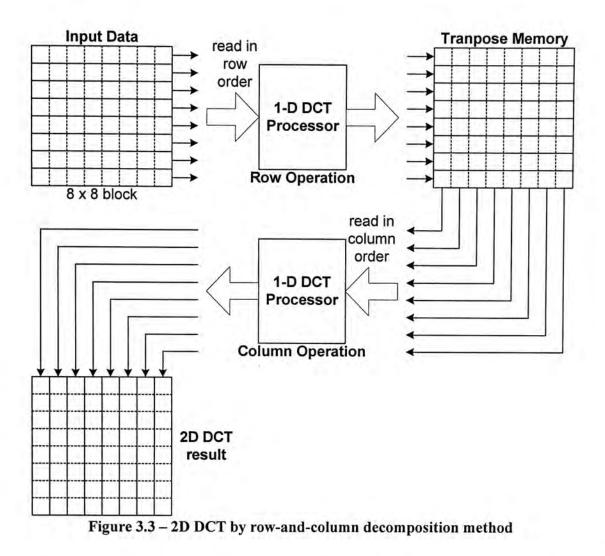

| Figure 3.3 – 2D DCT by row-and-column decomposition method                              |

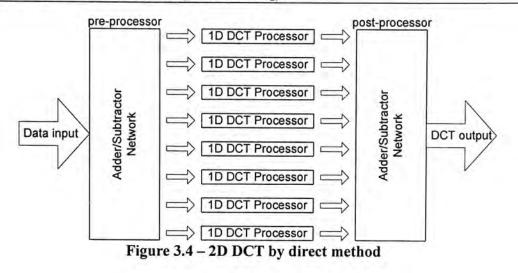

| Figure 3.4 – 2D DCT by direct method                                                    |

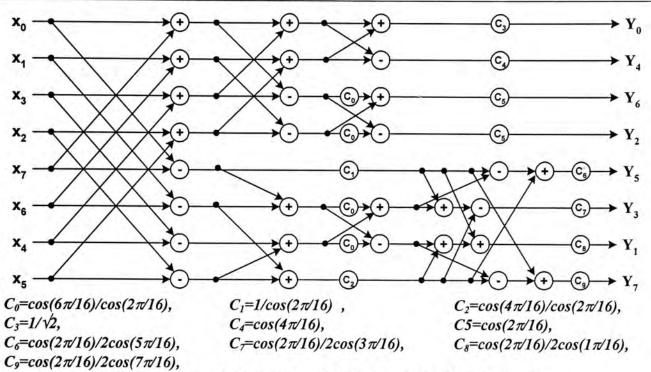

| Figure 3.5 – Signal flow diagram of the Jeong's 1D DCT fast algorithm                   |

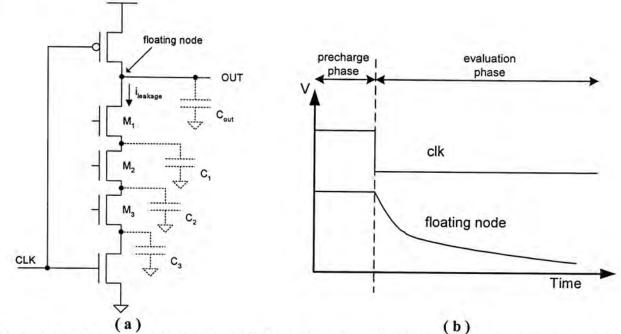

| Figure 4.1 – (a) 3-input NAND dynamic logic, (b) voltage in the floating node of the    |

| dynamic logic                                                                           |

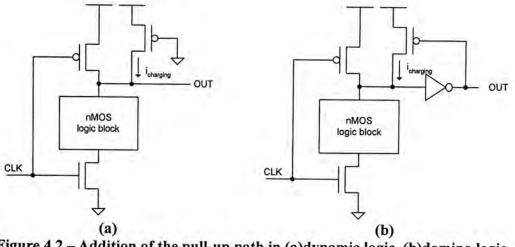

| Figure 4.2 – Addition of the pull-up path in (a)dynamic logic, (b)domino logic 39       |

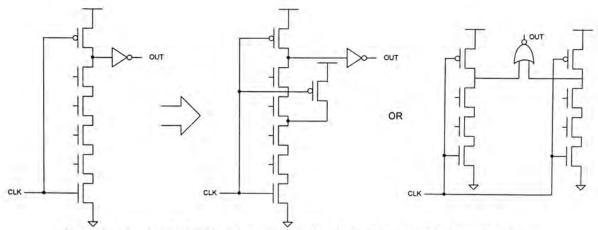

| Figure 4.3 – Techniques of overcome the charge redistribution problem                   |

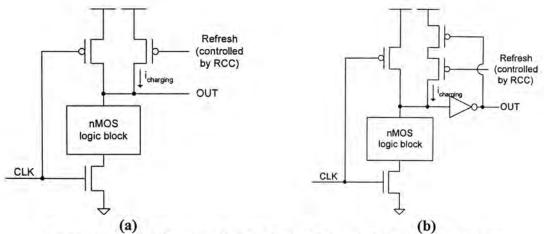

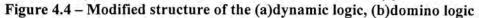

| Figure 4.4 – Modified structure of the (a)dynamic logic, (b)domino logic41              |

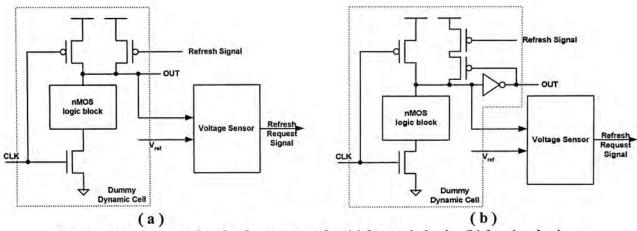

| Figure 4.5 – Proposed refresh structure for (a)dynamic logic, (b)domino logic 42        |

|      | voltage generator, (b)two-stage sense amplifiers as the second stage                    |

|------|-----------------------------------------------------------------------------------------|

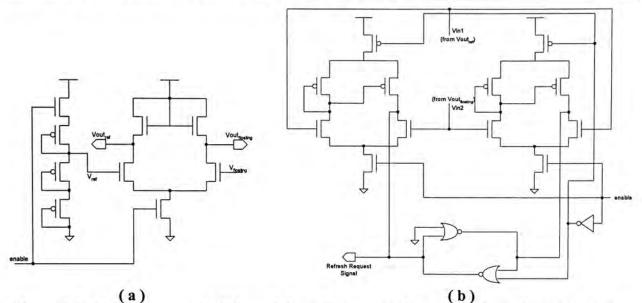

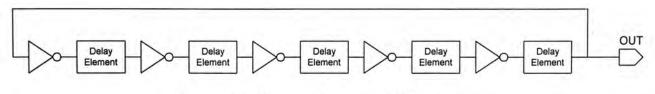

| Figu | re 4.7 – Ring oscillator                                                                |

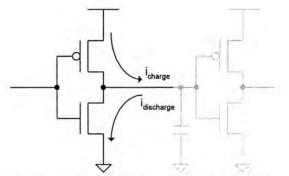

| Figu | are 4.8 – Charging and discharge current in the inverter chain                          |

| Figu | are 4.9 – Ring oscillator with delay elements                                           |

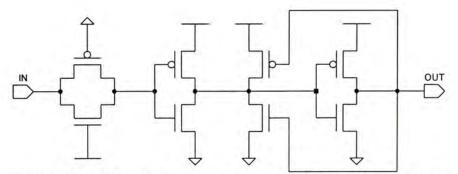

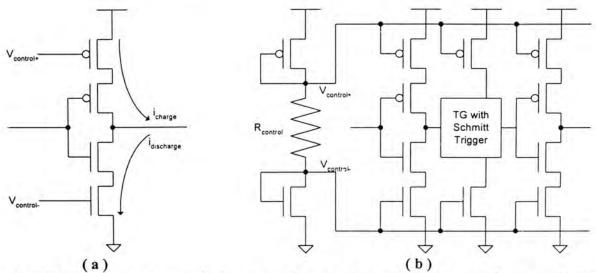

| Figu | are 4.10 – Delay element, transmission gate with Schmitt trigger                        |

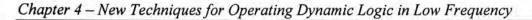

| Figu | are $4.11 - (a)$ a voltage controlled inverter, (b) part of the voltage controlled ring |

|      | oscillator4                                                                             |

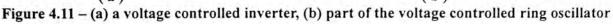

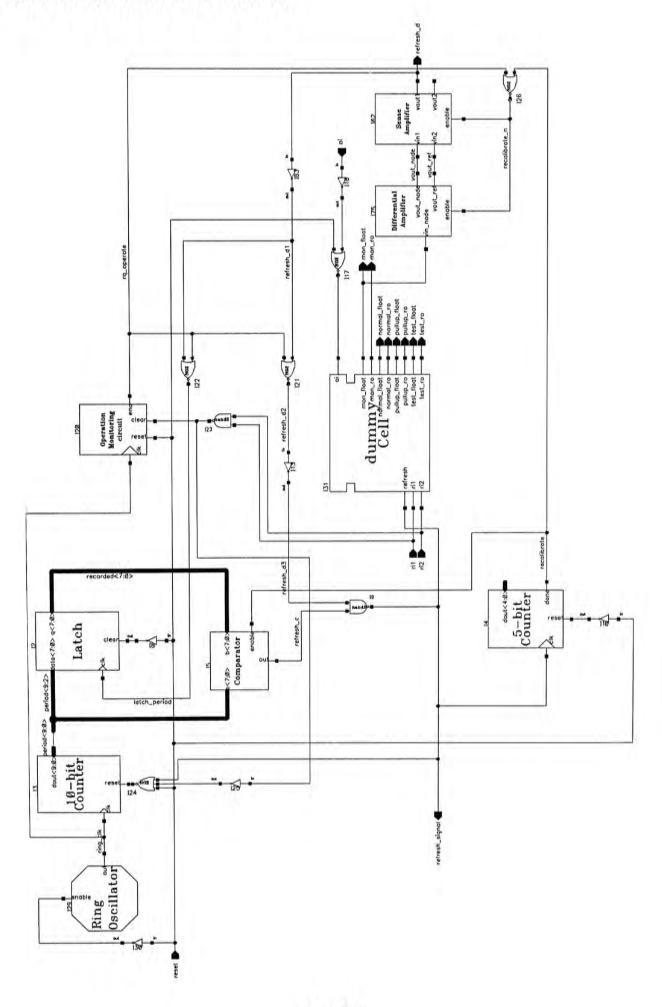

| Fig  | are 4.12 – Block diagram of the Refresh Control Circuit                                 |

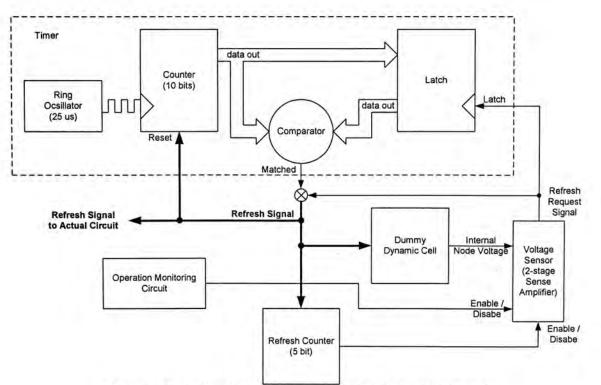

|      | are 4.13 – Timing diagram of the Refresh Control Circuit                                |

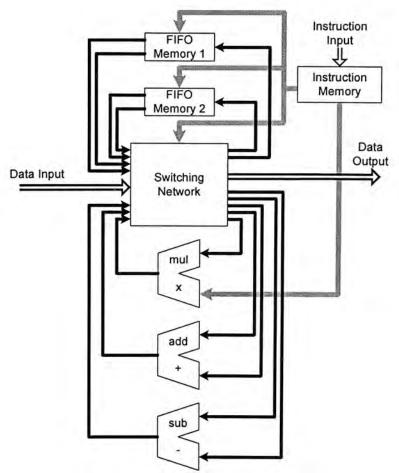

| Fig  | ure 5.1 – Dataflow architecture of the programmable DSP processor                       |

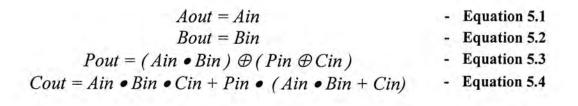

| Fig  | ure 5.2 – Product Full Adder (PFA) of the multiplier                                    |

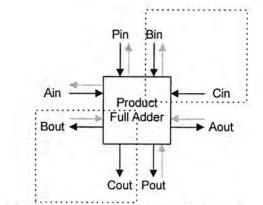

| Fig  | ure 5.3 – The 8x8 multiplier core                                                       |

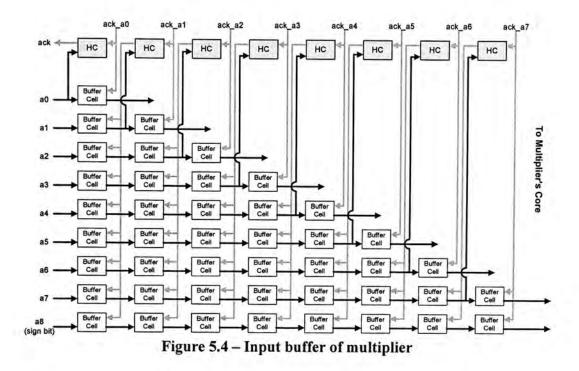

| Fig  | ure 5.4 – Input buffer of multiplier5:                                                  |

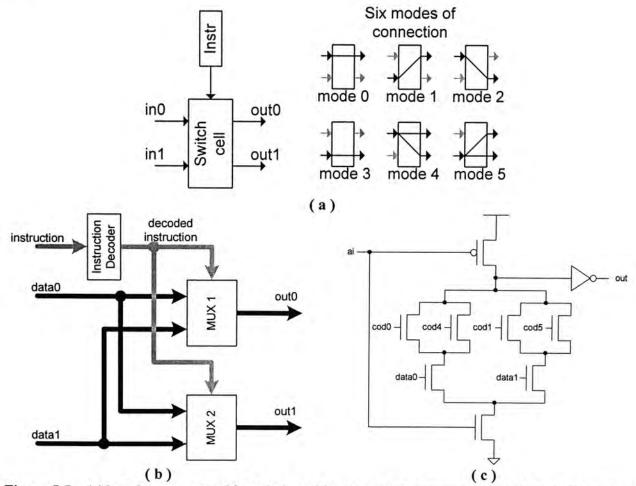

| Fig  | ure 5.5 – (a)2-to-2 programmable switch and its six modes of connection,                |

|      | (b)block diagram of the internal structure of switch, (c)CMOS structure of basic        |

|      | multiplier cell of the MUX 157                                                          |

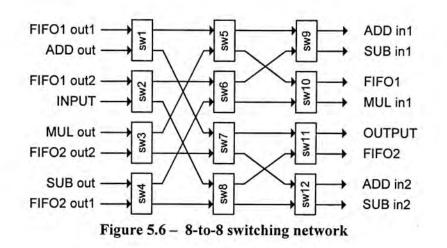

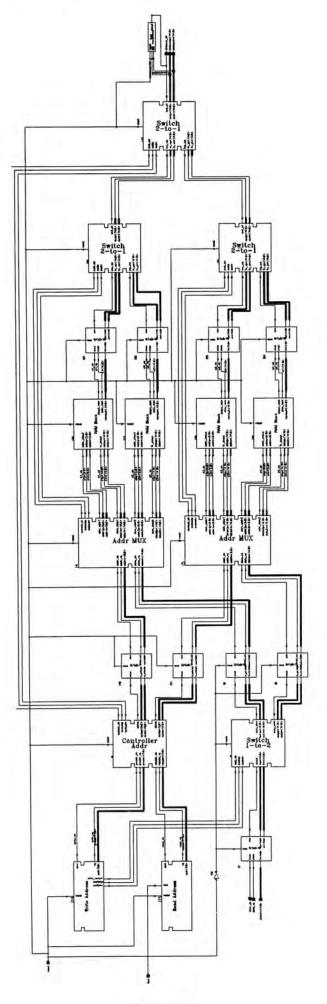

| Fig  | ure 5.6 – 8-to-8 switching network                                                      |

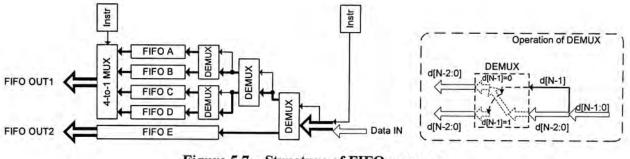

| Fig  | ure 5.7 – Structure of FIFO memory                                                      |

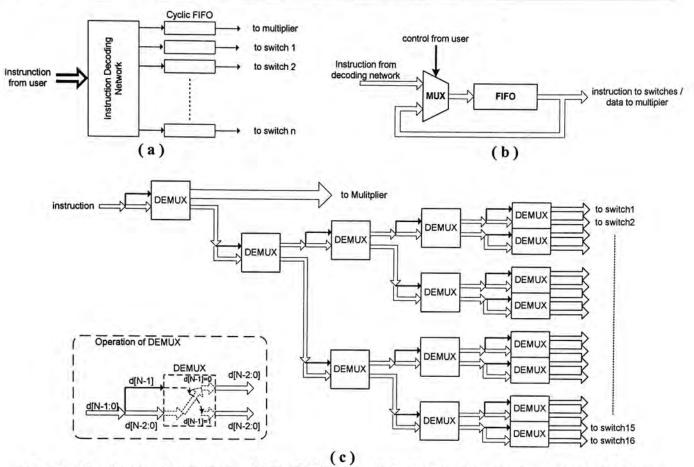

| Fig  | ure 5.8 – Instruction memory, (a) block diagram of the instruction memory, (b)          |

|      | the structure of cyclic FIFO, (c) structure of the instruction decoding network 6       |

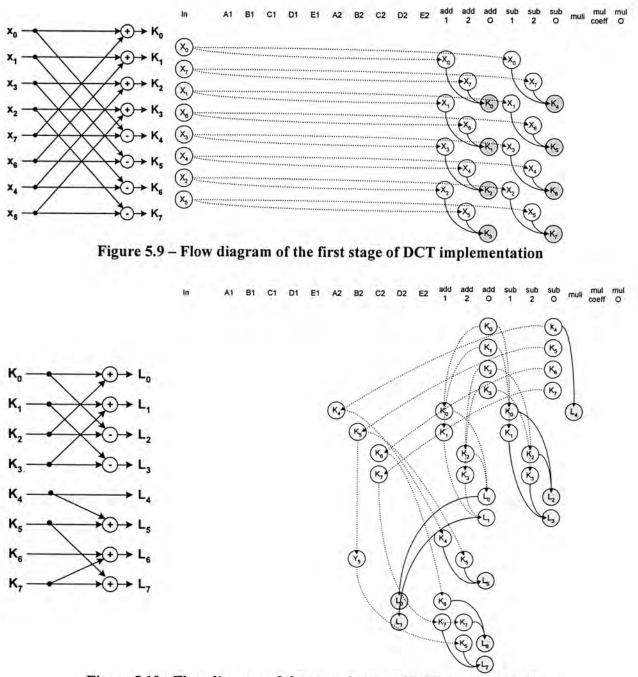

| Fig  | ure 5.9 – Flow diagram of the first stage of DCT implementation                         |

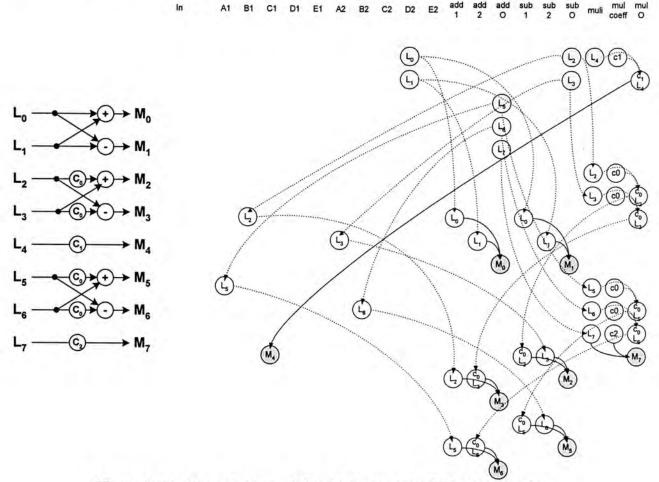

| Fig  | ure 5.10 - Flow diagram of the second stage of DCT implementation                       |

| Fig  | gure 5.11 – Flow diagram of the third stage of DCT implementation                       |

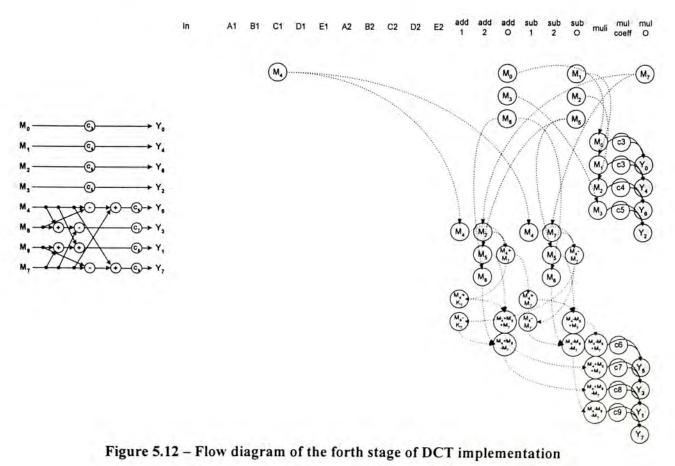

| Fig  | gure 5.12 – Flow diagram of the forth stage of DCT implementation                       |

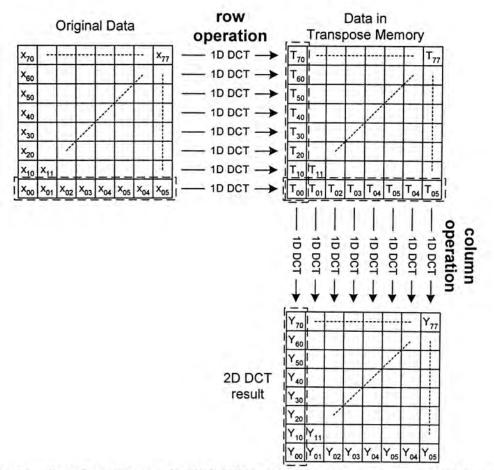

| Fig  | gure 6.1 – Dataflow diagram in 2D DCT by row-and-column decomposition                   |

|      | method67                                                                                |

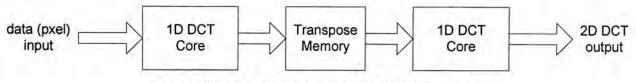

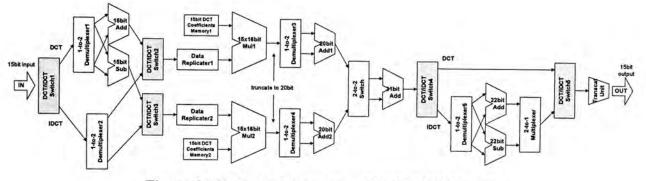

| Fig  | gure 6.2 – Block diagram of 2D DCT processor                                            |

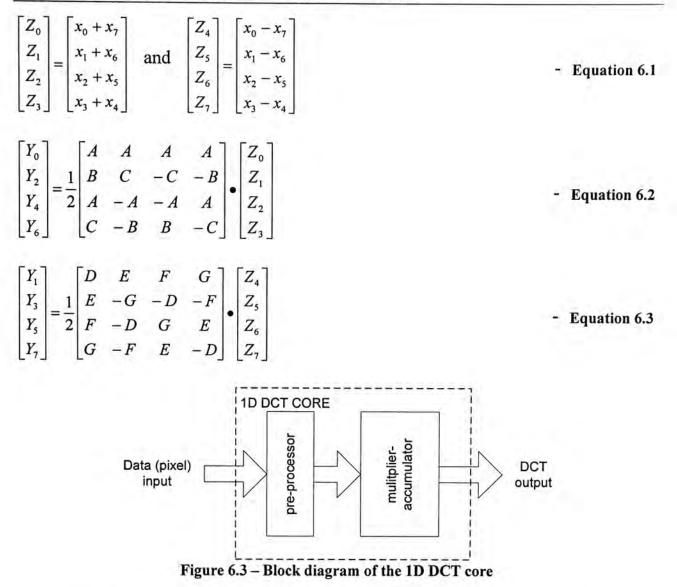

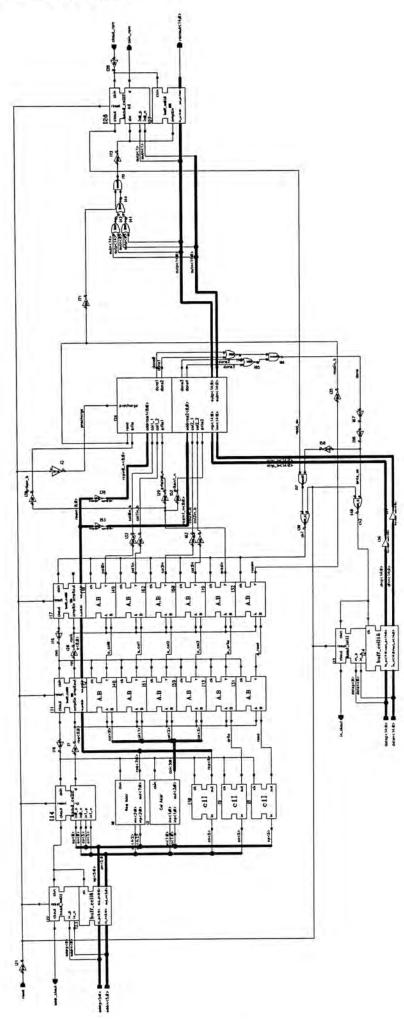

| Fig  | gure 6.3 – Block diagram of the 1D DCT core                                             |

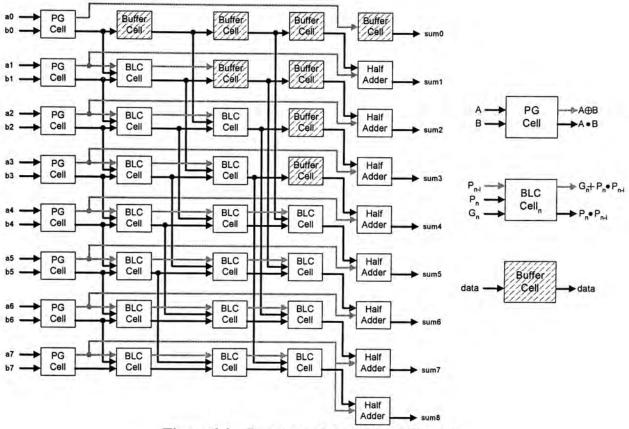

| Fig  | gure 6.4 – Structure of the 8-bit BLC adder70                                           |

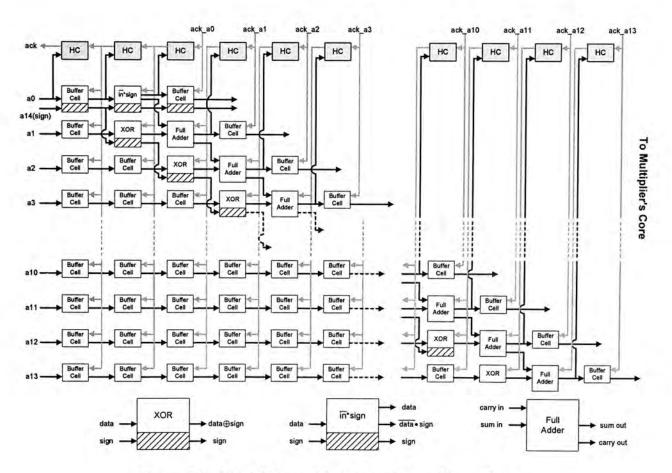

| Fig  | gure 6.5 – Modified input buffer for 2 complement input                                 |

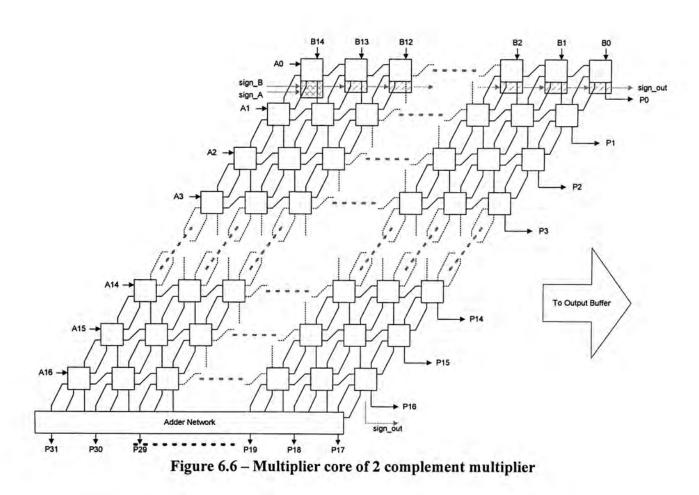

|      | gure 6.6 – Multiplier core of 2 complement multiplier                                   |

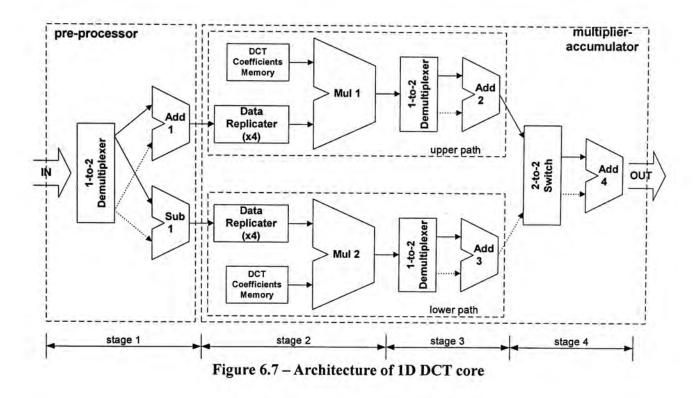

| Fi   | gure 6.7 – Architecture of 1D DCT core                                                  |

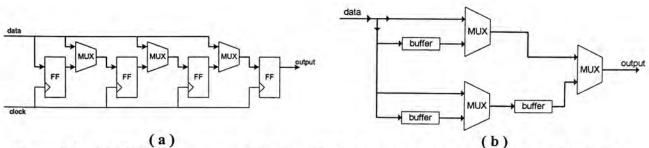

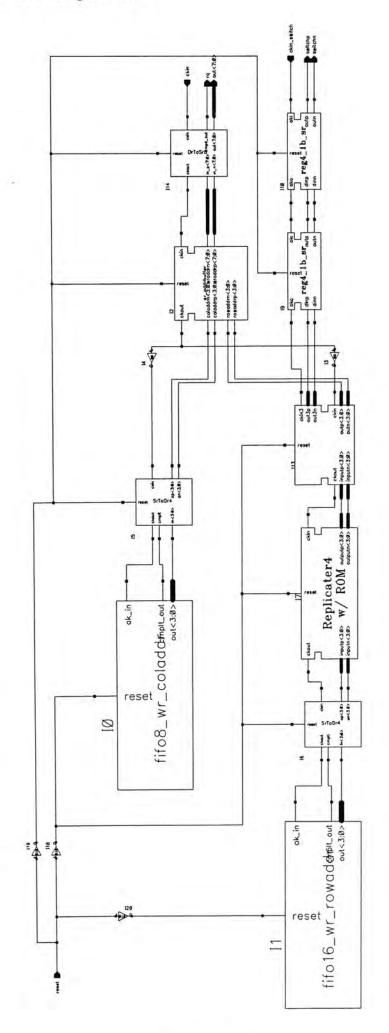

| Figure $6.8 - (a)$ block diagram parallel-to-serial shift register in synchronous desig | n, |

|-----------------------------------------------------------------------------------------|----|

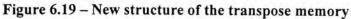

| (b) block diagram of data replicator                                                    | 79 |

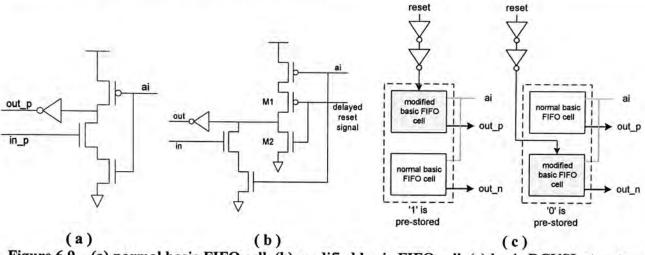

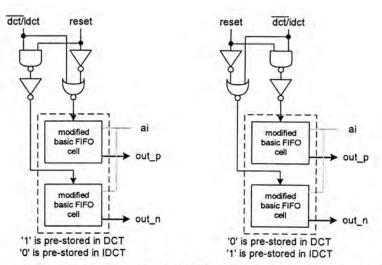

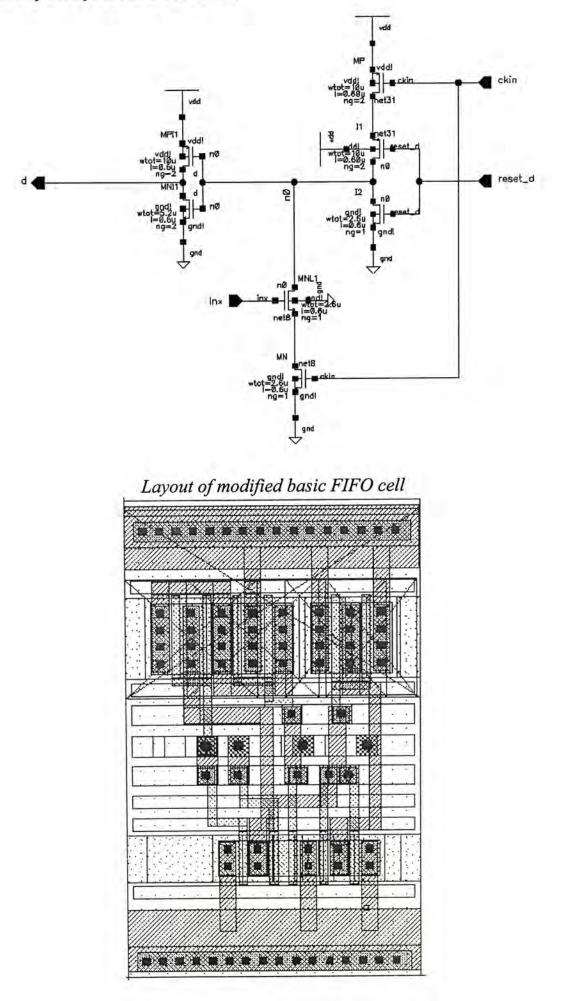

| Figure 6.9 – (a) normal basic FIFO cell, (b) modified basic FIFO cell, (c) basic        |    |

| DCVSL structure of pre-storing data                                                     | 81 |

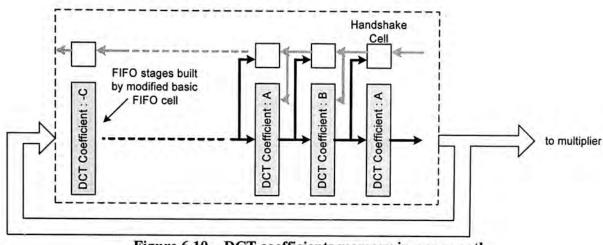

| Figure 6.10 – DCT coefficients memory in upper path                                     | 82 |

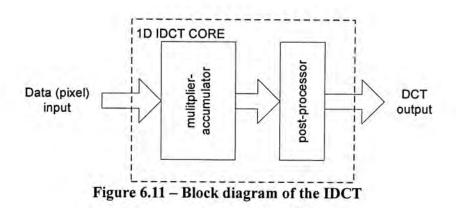

| Figure 6.11 – Block diagram of the IDCT                                                 | 83 |

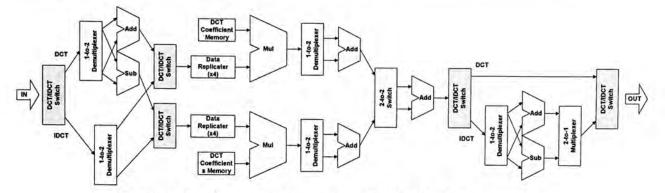

| Figure 6.12 – Overall architecture of the 1D DCT/IDCT processor                         | 84 |

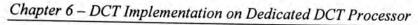

| Figure 6.13 – Modification of memory cell of pre-storing different data in DCT and      | d  |

| IDCT                                                                                    | 84 |

| Figure 6.14 – Bit length in different parts of the 2D DCT/IDCT processor                | 86 |

| Figure 6.15 – Unified structure of 1D DCT/IDCT core                                     | 87 |

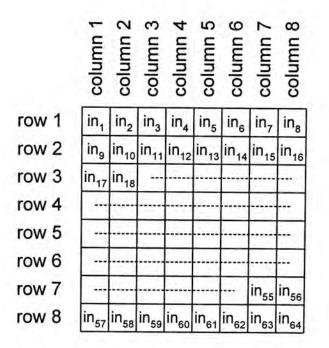

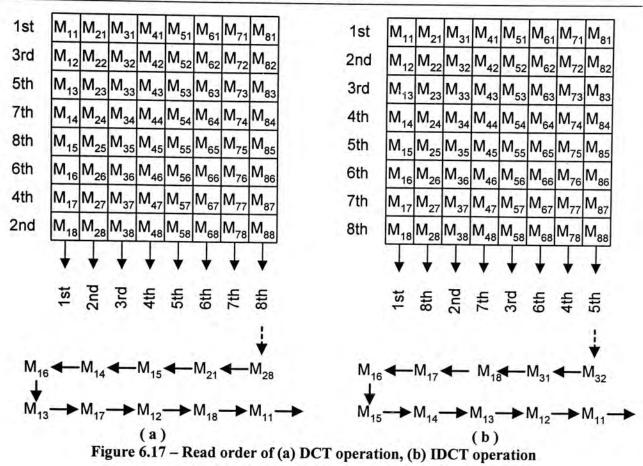

| Figure 6.16 – Write order of the transpose memory                                       | 88 |

| Figure 6.17 – Read order of (a) DCT operation, (b) IDCT operation                       | 89 |

| Figure 6.18 – Block diagram of transpose memory                                         | 90 |

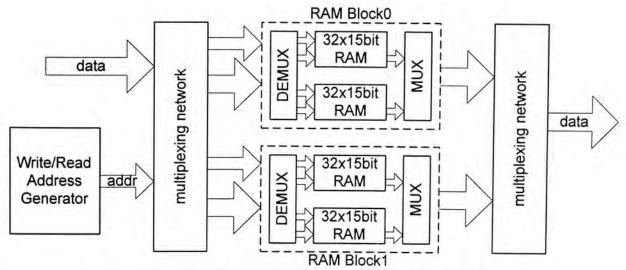

| Figure 6.19 – New structure of the transpose memory                                     | 90 |

| Figure 6.20 – Write address generator                                                   | 92 |

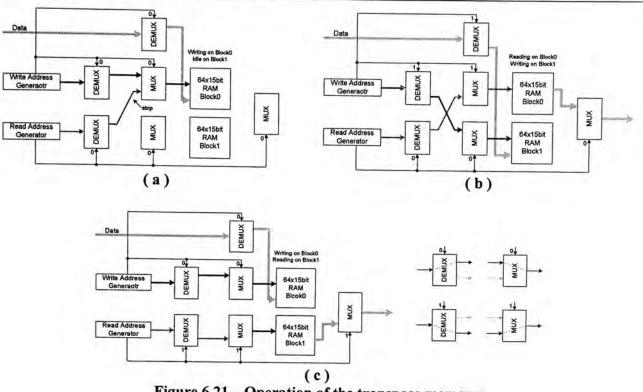

| Figure 6.21 – Operation of the transpose memory                                         | 93 |

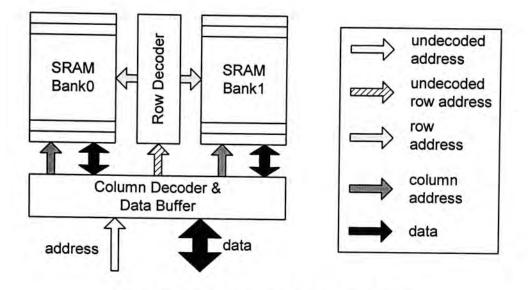

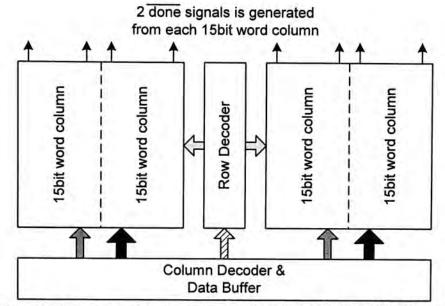

| Figure 6.22 - Block diagram of the RAM block                                            | 94 |

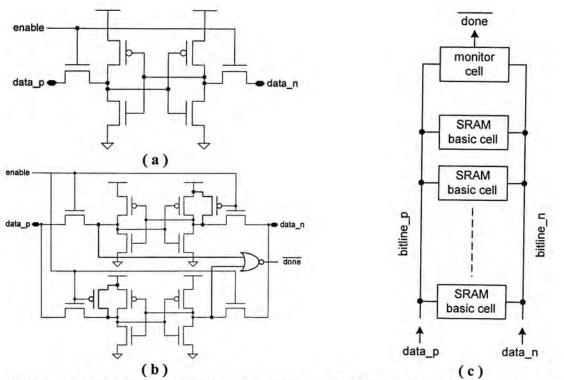

| Figure 6.23 – (a) SRAM basic cell, (b) monitor cell, (c) monitor cell in a bit column   | n  |

| of SRAM                                                                                 | 95 |

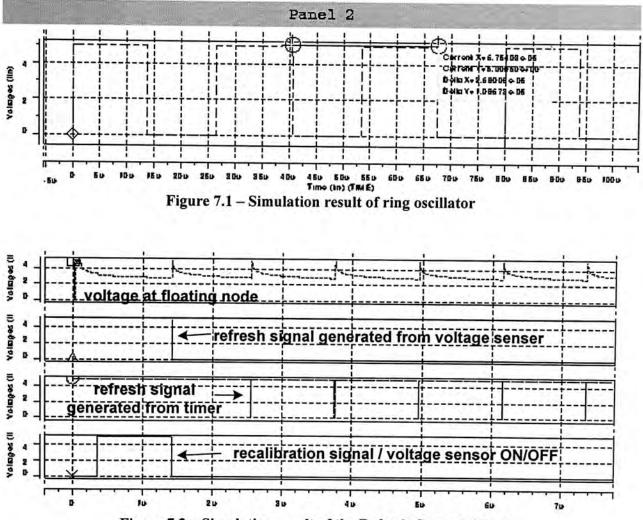

| Figure 7.1 – Simulation result of ring oscillator                                       |    |

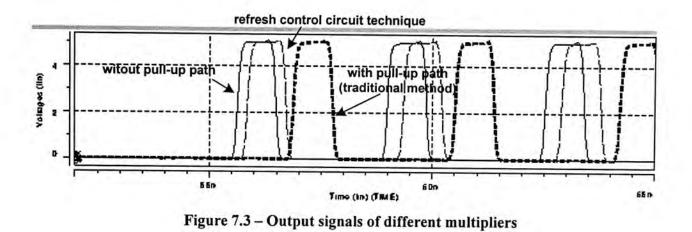

| Figure 7.2 – Simulation result of the Refresh Control Circuit                           | 98 |

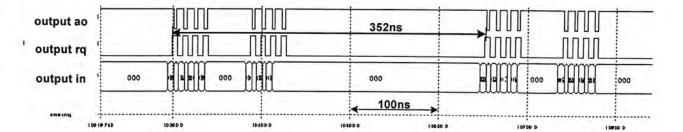

| Figure 7.3 – Output signals of different multipliers1                                   | 00 |

| Figure 7.4 – Simulation result of the programmable DSP processor1                       | 02 |

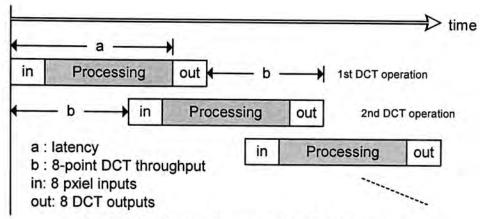

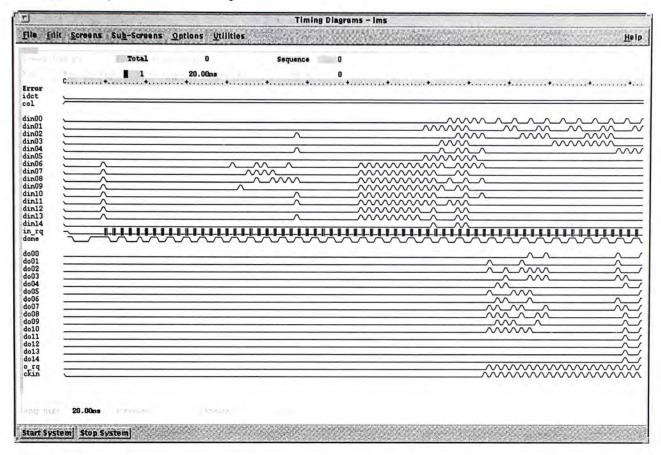

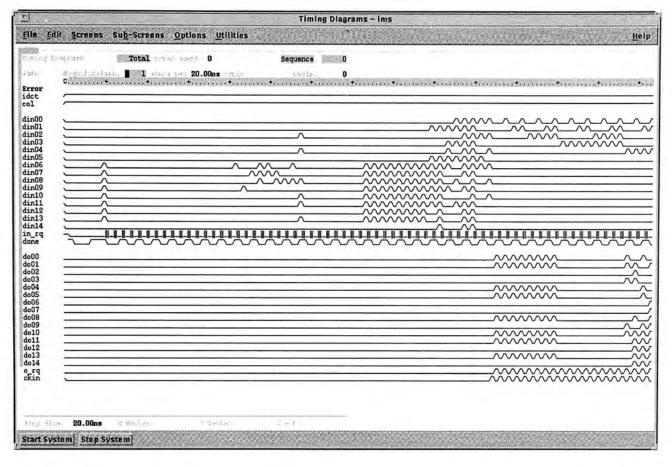

| Figure 7.5 – Timing diagram of the DCT operation1                                       | 03 |

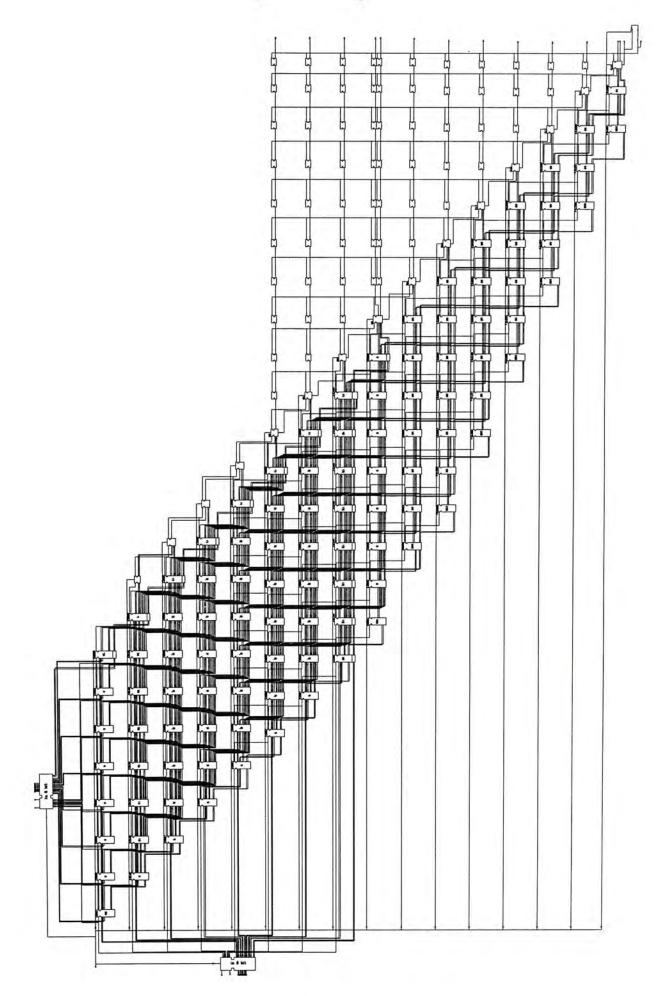

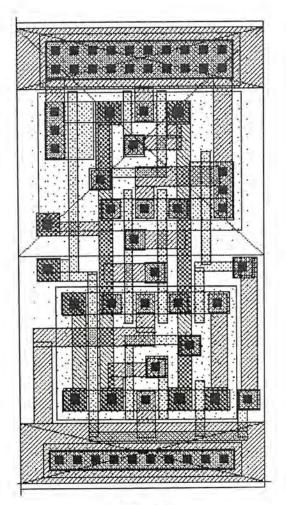

| Figure 7.6 – Layout of the 9-bit programmable DSP processor1                            | 04 |

| Figure 7.7 – Simulation result of the DCT coefficients memory                           | 08 |

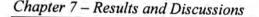

| Figure 7.8 – Layout of the 1D DCT/IDCT core processor                                   | 09 |

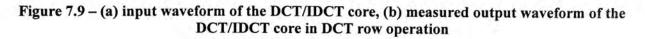

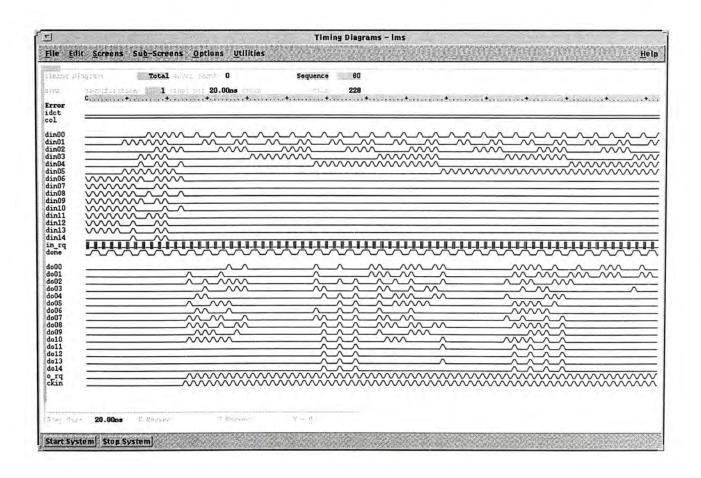

| Figure 7.9 – (a) input waveform of the DCT/IDCT core, (b) measured output               |    |

| waveform of the DCT/IDCT core in DCT row operation1                                     | 10 |

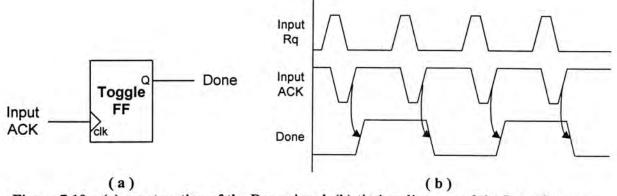

| Figure $7.10 - (a)$ construction of the Done signal, (b) timing diagram of the Input    |    |

| Request, Acknowledgement and Done signal1                                               | 11 |

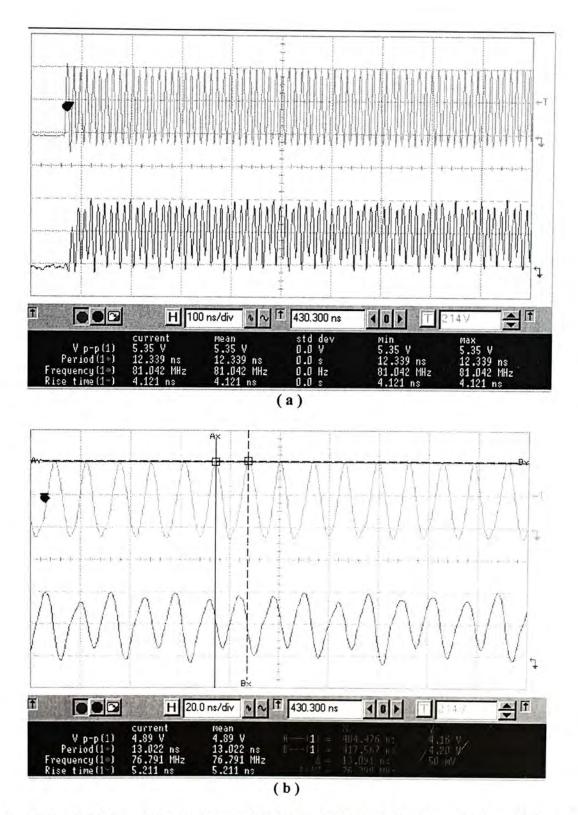

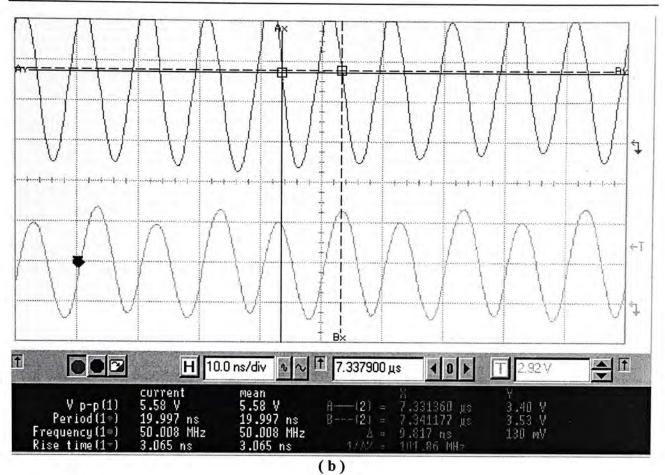

| F | Figure $7.11 - (a)$ measured waveforms of the Output Request (lower) and                 |

|---|------------------------------------------------------------------------------------------|

|   | Acknowledgement (upper) signal, (b) zoomed waveforms which shows the                     |

|   | average throughput is 76MHz112                                                           |

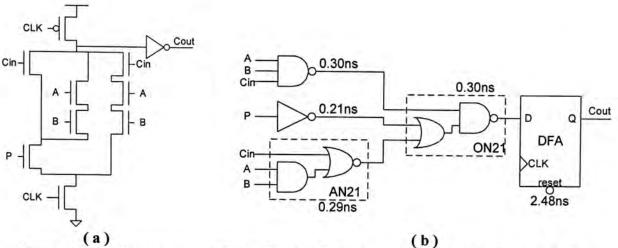

| F | Figure 7.12 – (a) carry generation in domino logic, (b) carry generation in static logic |

|   |                                                                                          |

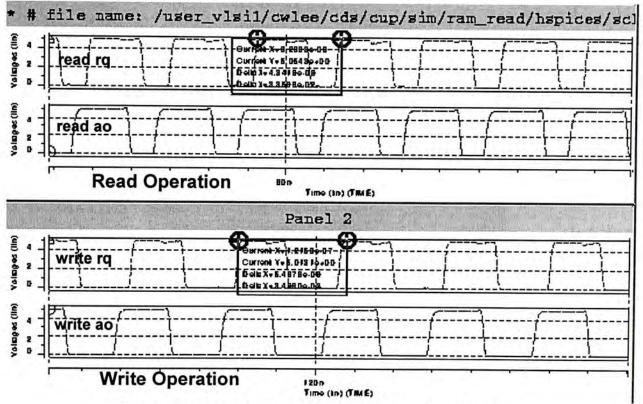

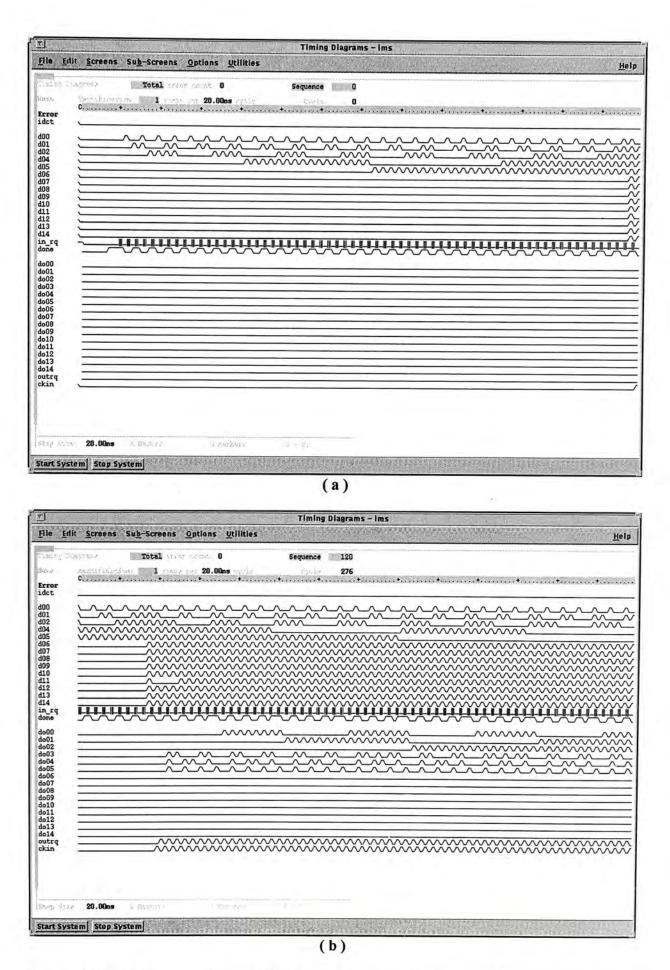

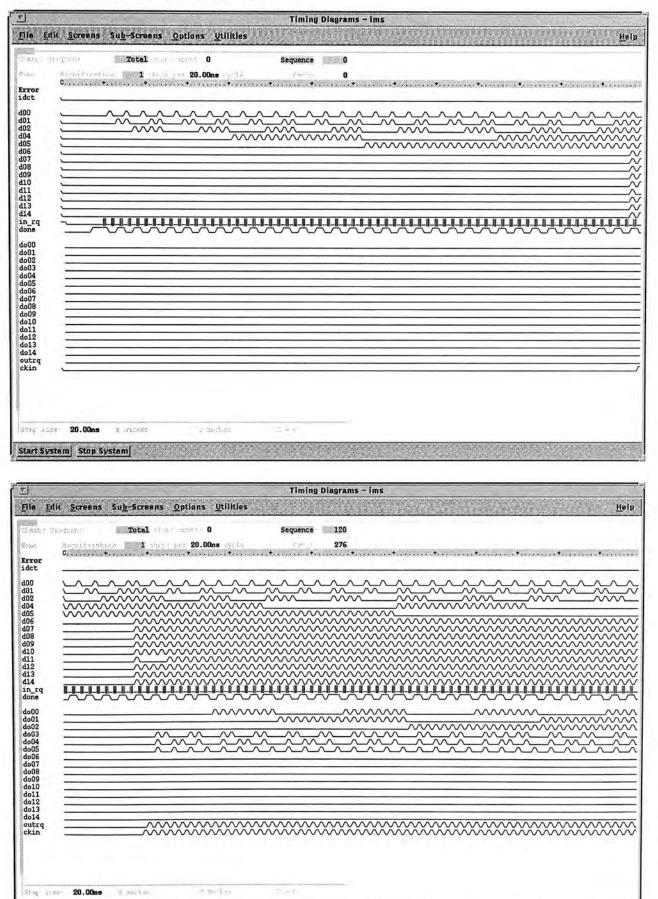

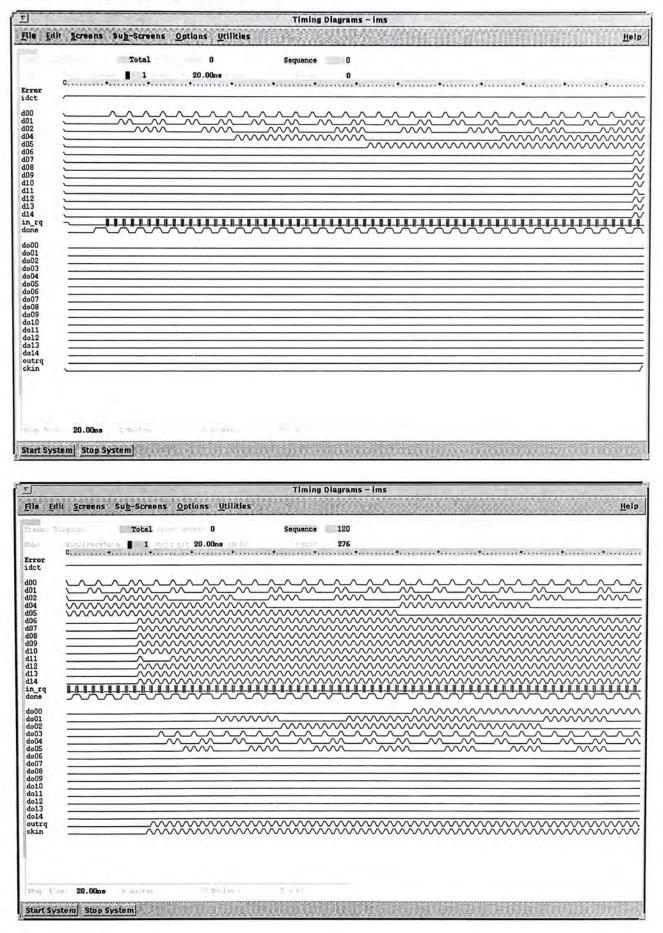

| H | Figure 7.13 – Simulation result of the write and read operation                          |

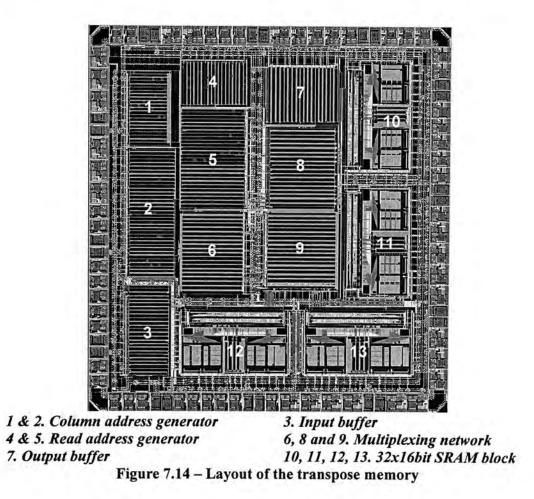

| H | Figure 7.14 – Layout of the transpose memory 123                                         |

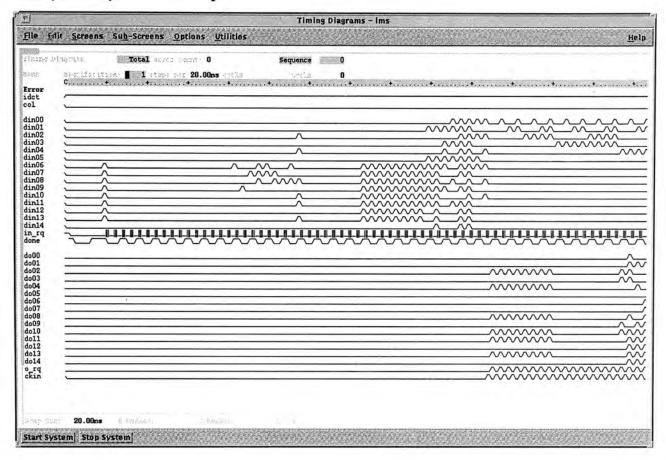

| ł | Figure 7.15 – (a) input waveform of the transpose memory, (b) measured output            |

|   | waveform of transpose memory in DCT operation mode124                                    |

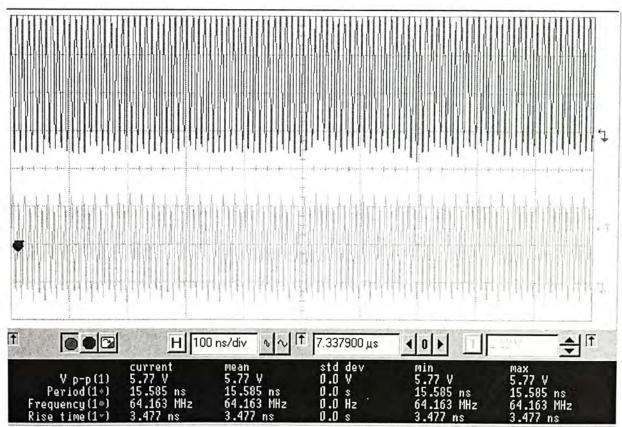

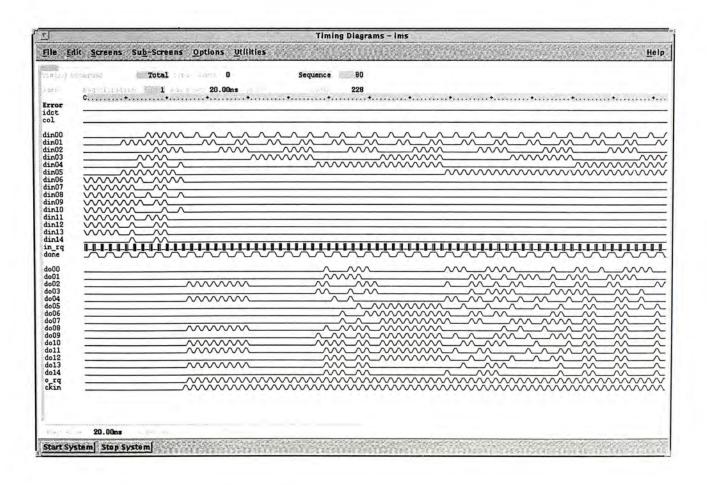

| ] | Figure 7.16 – (a) measured waveforms of the Output Request (upper) and                   |

|   | Acknowledgement (lower) signal, (b) zoomed waveforms which shows the                     |

|   | average throughput is 100MHz126                                                          |

| ] | Figure 7.17 – Done signals generated from the 32×15bit RAM block                         |

## Chapter 1

## Introduction

### 1.1 Synchronous Design

Synchronous design is the most popular digital circuit design technique today in the VLSI world. In a synchronous circuit, global clock is used to synchronize and trigger all the operations. As the technology of VLSI grows towards higher speed, smaller feature size and larger chip size, the performance of synchronous circuit is limited due to its global clock approach.

The main reason of the limitation is the clock skew problem [1][2]. Clock skew is the difference in the arrival time of clock signal at different parts of the circuit. As the chip size gets larger, it is difficult to manage the global clock signal to arrive at different parts of the design at the same time. Also, as the clock speed becomes higher, the global clock period becomes shorter and thus the transition time needs to be shorter comparing with the clock period. However, the transition time can only be reduced to a limited extent. As a result, the operating speed is forced to slow down so as to accommodate the problem.

In addition, frequency of the global clock is also restricted by the slowest part of the whole design. The period between two consecutive active clock edges must be long enough for all computations to be completed before latching the result. As a result, the clock period is determined by the slowest stage such that every stage is given enough time to fully process a data, thus yielding a worst-case performance.

It is believed that by eliminating the restrictions, a design can reach a higher level of performance, and this is the motivation of the development of asynchronous circuit.

## 1.2 Asynchronous Design

The main difference between the synchronous and asynchronous design is the use of the global clock and the local handshake signals. In asynchronous design, operations on a functional unit are controlled by the communications between neighbouring units. When there is an event occurred on the communication wire, an operation will be started or stopped by the triggering of the event.

Since the global clock signal is removed, there is no clock skew problem existed in the asynchronous design. Also, without the restriction of the global clock signal, different parts in an asynchronous circuit can operate at their own intrinsic speeds and thus the average-case performance can be achieved rather than worst-case performance in the synchronous circuit. Therefore, the problems of the synchronous design can be eliminated and higher speed can be achieved in asynchronous design. In addition, asynchronous design offers other potential advantages such as low power consumption, automatic adoption to physical properties, high modularity and less electromagnetic emission, these make the asynchronous design attractive. Despite of all the potential advantages motivating the development of asynchronous circuit, it has yet to achieve widespread use. This is because asynchronous circuit suffers from several problems as well.

The major problem of the asynchronous circuit is hazards [1]. In the synchronous design, hazards can be easily removed by adding more registers or slowering the clock rate. However, designers of the asynchronous circuit must remove all hazards to prevent incorrect operation. At the same time, there are little supports from CAD tools, design automation and optimization of the asynchronous design has still not been fully achieved. As a result, extra attention and extensive simulations are required and thus the development cost is increased.

Furthermore, an additional handshake circuitry is required in asynchronous design in order to handle the communication signals. This circuitry is usually complex and leads to a larger area in asynchronous design. Also asynchronous circuit generally requires extra time for handshaking protocol and thus an operation requires more time to be completed due to the communication overhead. As a result, the expected average-case performance is not fully realized. These two reasons cause an asynchronous circuit running at a speed even slower than the synchronous circuit.

Due to the maturity in synchronous design methodologies and the difficulties of asynchronous design as mentioned above, designers still prefer synchronous design in most of their system development today.

#### 1.3 Discrete Cosine Transform

The Discrete Cosine Transform (DCT), proposed by Ahmed et. al. in 1974 [3], and its inverse (IDCT) have become an important tool for image and video signal processing applications due to their adoption in standards such as CCITT H.261 [4] for video telephony and teleconference, JPEG (Joint Photographic Experts Group) [5] for colored still image transmission and MPEG (Moving Picture Experts Group) [6] for moving pictures on the storage media. The advantages of DCT are that its performance closes to the optimal Karhunen-Loeve transform (KTL) for highly correlated signals and the existence of the fast algorithms [7][8][9] which reduce the number of operations.

The role of DCT is providing a data compression on the picture while a reasonable quality can still be maintained. It helps to reduce memory size and transmission bandwidth in the image and video applications. DCT basically involve additions and multiplications. The operation of 1D N-point DCT and IDCT can be described by following equations,

$$DCT: Y_{n} = \frac{1}{2}c(n)\sum_{i=0}^{N-1} x_{i} \cos \frac{(2i+1)n\pi}{2N} - \text{Equation 1.1}$$

$$IDCT: x_{i} = \frac{1}{2}\sum_{i=0}^{N-1} c(n)Y_{n} \cos \frac{(2i+1)n\pi}{2N} - \text{Equation 1.2}$$

$$where \quad i, n = 0, 1, \dots, N-1$$

$$c(0) = 1/\sqrt{2} = 1 \text{ for } i \neq 0$$

----

In recent year, the increasing demand of high image and video quality signal, such as MPEG-2 and High Definition Television (HDTV), requires higher and higher To meet with the real-time computation computation in signal processing.

requirement, a processor which rapidly computes DCT has become a key component in image compression VLSI.

#### 1.4 Motivation

Up to now, most of the past asynchronous circuits are not good in performance in terms of speed. Together with the difficulties discussed in the previous section, it discourages the development of asynchronous design. However, there are methods exist so that full performance potential of the asynchronous design can be realized. The worse speed performance of the asynchronous circuit is mainly due to the complicated handshaking circuitry and slow communication protocol. It is believed that by developing a new asynchronous architecture having simpler handshaking circuitry, more aggressive handshaking protocol and together with a careful circuit arrangement, the hazard can be removed and a competitive asynchronous design can be obtained. This is the motivation of this project.

DCT is chosen for the realization of a new asynchronous architecture. This is because digital signal processing (DSP) algorithm is suitable to be implemented by asynchronous technique as the process is data-dependent that fits the style of the asynchronous design. Among various DSP algorithms, DCT is a widely used algorithm in many image and video applications and high throughput is required. It helps to demonstrate the practicality of the new asynchronous architecture and the fulfillment of the requirement of image and video applications today.

#### 1.5 Organization of the Thesis

This thesis is organized into eight chapters. The first chapter describes the background of the asynchronous design, Discrete Cosine Transform, and the motivation of this project. The second chapter introduces the basic operation and past methodologies in the asynchronous circuit design, and the new asynchronous pipelined architecture is presented at the end of this chapter. In chapter 3, various methods and algorithms of DCT implementation and two different approaches of the asynchronous implementation of DCT processor are described. Since dynamic logic is employed in the new asynchronous pipelined architecture, a new technique of operating dynamic logic in low frequency is presented in chapter 4. Chapter 5 describes the detailed architecture of the programmable DSP asynchronous processor, and the DCT implementation is given as well. Chapter 6 presents another implementation of DCT on a dedicated DCT processor. The architecture and flow of operations on the processor, and the design of the transpose memory are all provided. In chapter 7, all the implementation results and performance of the designs proposed in this thesis are given. Based on the results, the performance comparisons, discussions and suggestions are also provided in the same chapter. Finally, conclusion of the thesis is given in the last chapter.

## Chapter 2

## **Asynchronous Design Methodology**

#### 2.1 Overview

The operation of an asynchronous circuit is not based on the global clock signal, which is used in the synchronous circuit, but on its local handshake signals. The handshake signals are the controlling signals in the communication between the sender and receiver. For most of asynchronous circuits, they usually make use of similar handshaking protocol involving requests and acknowledgements.

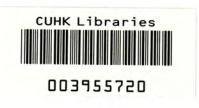

Figure 2.1 - Communications between sender and receiver in an asynchronous circuit

Figure 2.1 shows a basic communication interface in asynchronous circuit. This kind of communication style is called the bundled data approach [1][10]. In this approach, the interface between sender and receiver consists of a bundle of data which carries information (using one wire for each bit) and two control wires. When the data from the sender side is ready, a transition will occur on the request wire to inform the receiver, and acknowledgement wire from the receiver to the sender carries a transition when the data has been processed. Also the data will be maintained constantly during the receiver's active phase preventing wrong operation.

There are many types of handshaking protocol and different kinds of circuit for implementing this asynchronous communication interface. In this chapter, a brief introduction to different handshaking protocols will be given. In addition, some of the past designs and the micropipeline structure will be introduced. At last, the new asynchronous architecture will be presented.

#### 2.2 Background

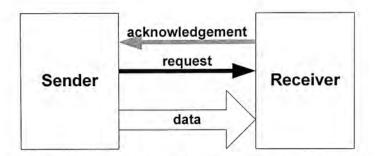

Figure 2.2 - Timing diagram of (a)two-phase, (b)four-phase handshaking protocol

There are 2 classes of handshaking protocol, one is the two-phase and the other is the four-phase [1][10][11] and their timing diagram is shown in Figure 2.2. Two-phase handshaking protocol means that any transition in the handshake signal represents an event occurred. Different from the two-phase, the four-phase handshaking protocol is a level-triggered protocol. The occurrence of an event is represented by an active

level, and the return to non-active level is required after the event has been finished. In general, the two-phase handshaking protocol has better performance than the fourphase one as it makes use of all transitions of the signal to represent an event, it leads to a faster communication rate.

Compared to the synchronous circuit, the request and acknowledgement signals are additional signals. As a result an extra control circuit is required in asynchronous design so as to handle these two signals, and usually this circuit is called handshake control circuit or handshake cell.

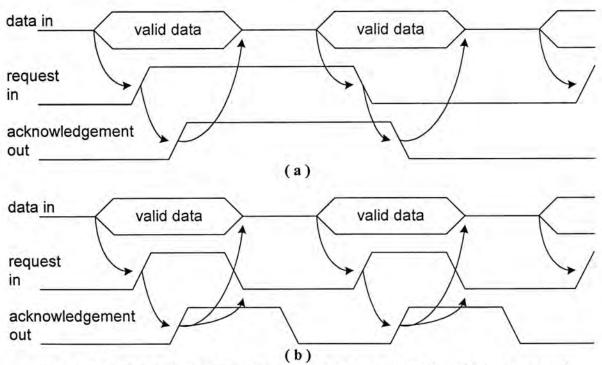

Figure 2.3 - (a) connections in asynchronous circuit, (b) operation in asynchronous circuit

Figure 2.3(a) shows the basic connection in asynchronous design using the handshake cell. In this connection, the operations depend totally on the handshake signals, and that can be explained with the help of Figure 2.3(b). Initially when the operation of functional block in stage N-1 is completed, the output data will be passed to the functional block in stage N. At the same time, the handshake cell in

#### Chapter 2 - Asynchronous Design Methodology

stage N-1 will detect the completion of computation and generate a request signal for stage N. This request signal is used to indicate that the operation of stage N-1 is completed, and the output data of stage N-1 is held and ready for the stage N to process. Starting from this moment, stage N-1 needs to hold the output data until stage N finishes the computation.

The handshake cell in stage N detects the request signal from the previous stage, and then allows the functional block in stage N to process the data. After the computation is completed, the handshake cell in stage N will generate two signals. The first one is the acknowledgement signal which is used to inform stage N-1 that the data has been processed. As a result, stage N-1 becomes idle and wait for the data from stage N-2 for the next operation. The second signal is the request signal to the stage N+1 for further processing of data.

This communication interface and protocol exist between all the stages and its neighbouring stages in the asynchronous circuit. Since all the operations are controlled by the handshake signals, the performance of the handshake cell becomes the main factor of determining the speed of the asynchronous circuit.

## 2.3 Past Designs

The design of the handshake cell and the use of the handshaking protocol are important as they determine the throughput and latency of the whole asynchronous system. For the handshake cell, an accurate detection of the completion of the operation and a quick generation of the request signal are the most important issues as they are used to guarantee the circuit operating correctly and quickly. If the

#### Chapter 2 – Asynchronous Design Methodology

request signal is generated before the functional block finishes its computation process or before data is valid, hazard will occur as incorrect data will be latched by the next stage and incorrect result will be obtained. If the request signal is generated a long time after the end of computation, it is secure to have a correct output but the whole circuit will be slowed down. However, to generate the request signal just in time while maintaining simple structure is really a difficult task. By using a suitable handshake cell, the complexity of the handshaking protocol can be reduced and thus, the communication time can be reduced too. As a result, the speed and performance of the whole circuit can be enhanced.

In the past decades, there were many kinds of handshake cell developed [12][13][14][15]. And the most famous and commonly used one is the C-element. C-element is firstly introduced by D.E. Muller in 1956 [16]. It is a rendezvous element, or an event-driven element. Figure 2.4 shows the symbol and 2 different CMOS structures of the C-element.

The operation of the C-element is that, when both inputs are the same, then the data will be copied to the output, else the previous output will be maintained. Therefore,

the output will only be toggled when there are events occurred at the both inputs of the C-element.

C-element is usually incorporated in the two-phase handshaking protocol with the bundled data approach. In applying the C-element in the asynchronous circuit, the input A and B are served as the inputs of request or completion signal from previous stage and acknowledgement signal from next stage. The output C has 3 functions. The first one is to control the operation of the function block. The second one is acted as the acknowledgement signal which is sent back to the previous stage, and the last one is acted as the request signal sending to the next stage. A more detailed operation of C-element in asynchronous circuit will be discussed in the next part.

### 2.4 Micropipeline

No matter synchronous or asynchronous design, pipeline is an important methodology to improve the performance of a circuit or system. The principle of the pipeline is to divide a single operation into several sub-operations, and allows them to operate simultaneously [10]. For the asynchronous circuit, pipeline can be done by breaking down the complex functional block into several simpler functional blocks, and each of them is governed by a dedicated handshake cell. The widely known pipeline methodology in asynchronous circuit is micropipeline.

Micropipeline was introduced in Ivan Sutherlands' Turing Award lecture [10] primarily as an asynchronous alternative to synchronous elastic pipelines. From the definition by Ivan, micropipeline means a simple form of event-driven elastic pipeline with or without internal processing.

#### Chapter 2 - Asynchronous Design Methodology

The basic operation of the micropipeline can be explained by the control first-infirst-out (FIFO) sequence structure as shown in Figure 2.5. The control FIFO sequence is operated in two-phase handshaking protocol. Assuming that all the wires are initially set at zero, when there is a transition in the request input, then output of the first C-element will be changed from zero to one. This transition will be sent out of the control sequence as an acknowledgement signal, and also will be propagated to the input of the second C-element. Since the input is toggled, same situation will occur in the second C-element, as well as the third C-element. As a result, the request signal passes through all the C-elements in series, and emerges on request out.

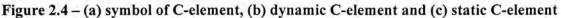

Figure 2.5 - Basic control FIFO sequence in Micropipeline structure

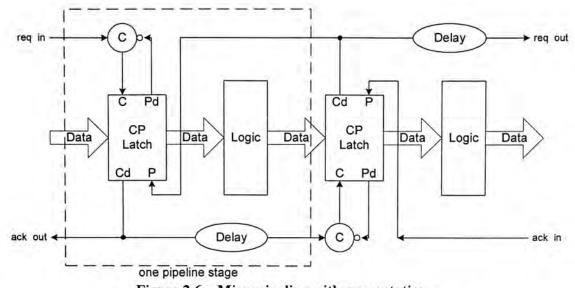

However, when there is another request signal coming from the request input, this new request signal may not be emerged on the request out this time. This is because the control FIFO sequence may still not received the acknowledgement from the output side, as a result no transition has been made in the acknowledgement input terminal and thus the output of the third C-element cannot be toggled. However, this phenomenon is normal as no transition on acknowledgement input means that the output side, or the recipient side, still has not processed the previous request, the new request should not pass to it before the previous event is completed. Figure 2.6 shows the block diagram of the Sutherland's micropipeline system. The connections are actually similar to the previous FIFO sequence, but a storage element and a logic block are included in each stage. The storage element used is called Capture and Pass latch (CP latch), which is an event-controlled storage element. The inputs C and P are responsible for controlling the capture and pass function, and the outputs Cd and Pd are just simply the delayed version of the inputs C and Prespectively. In this micropipeline structure, when there is a transition occurred in the request input, data will be captured and stored in the CP latch. However, the stored data will not be passed out from the output of the CP latch until there a transition occurs at input P. If the CP latch in the next stage has captured the previous data, the phase of acknowledgement signal will be changed and passed back to the first CP latch. Then the first CP latch will pass the stored data to the logic block to perform the logic operation. This operation will be repeated when the next request signal arrives. The delay element is used to delay the arrival of the request (capture) signal to the next stage so as to ensure the logic operation have been completed, therefore it needs to be the worst-case delay of the corresponding logic block.

Figure 2.6 – Micropipeline with computation

Page 14

#### Chapter 2 – Asynchronous Design Methodology

There are several benefits of using the micropipeline structure. First, the architecture is simple and effective, it is easy to implement and a good throughput can be easily achieved. Also, the latches moderate the flow of data through the pipeline and can be used to filter out hazards. Thus, any logic structure can be used in the logic blocks, including the straightforward structures used in synchronous designs. At last, micropipeline is automatically elastic [10], data can be sent to and received from a micropipeline at arbitrary times.

Although micropipeline is a powerful implementation strategy which elegantly implements elastic pipelines, it delivers worst-case performance in each stage by adding delay elements to the control path to match with the worst-case computation time of the corresponding function block. Besides from this, the circuit of its CP latch is rather complicated, and delays are added on the capture and pass signal to make sure the data has been latched. Therefore the performance is degraded.

#### 2.5 New Asynchronous Architecture

As previously discussed, although Micropipeline is a powerful and widely used methodology in the asynchronous circuit design, it still has some areas for improvement.

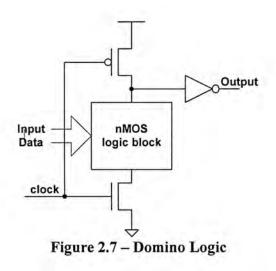

The first improvement from the micropipeline is the use of dynamic logic, and in our design, domino logic [18] is used. Domino logic is one of the logic types in the dynamic logic family, and its basic structure is shown in Figure 2.7. The logical function of the domino logic is characterized by the nMOS logic block. There are two phases for the operation of the domino logic, one is the Precharge phase and the

other is the Evaluation phase. When the clock signal is low, then the domino logic is in the Precharge phase. At this moment the output must be low as a pull-up path is connected to the floating node. When the clock signal is high, then it is in the Evaluation phase and the output depends on the input data. If the input data creates a pull-down path in the nMOS tree, then the floating node will be discharged and the output will go high. Otherwise the output will be kept in low.

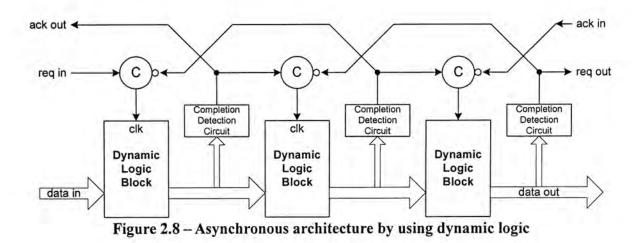

The advantage of the dynamic logic is that it has lower processing delays and more compact in size in comparison to conventional CMOS data-paths. Due to these, many asynchronous circuits [11][19][20][21][23][25] also adopted the dynamic logic in their micropipeline design. However most of them have not utilized all the functions of dynamic logic. One of the interesting properties of the dynamic logic is its ability of temporary storage [17][19]. Dynamic Logic is actually a combination of the logic and storage elements, the output data can be held even though the input data have been changed under some conditions. As a result, the complex CP latch in the micropipeline can be omitted if the dynamic logic (domino logic in our case) is used. This implementation of dynamic logic in asynchronous circuit has been proven by Renaudin et. al. [17], and its pipeline structure is shown in Figure 2.8. In this architecture, the completion detection is no longer relied on the worst-case delay, it is

done by a dedicated circuit. It monitors the output of the logic block and provides a faster and accurate response when the output is ready. Although dynamic logic brings benefits for the asynchronous circuit, it introduces other problems of charge leakage and charge redistribution. These problems limit the dynamic logic to have a minimum operating frequency from preventing the logic error. As a result, extra attention must be paid in using dynamic logic. A further discussion on this problem and some possible solutions will be given in chapter 4.

Besides from the dynamic logic, another improvement is on the handshaking protocol and handshake cell. Referring to the previous implementation shown in Figure 2.8, a very restrictive handshaking protocol is used to guarantee secure operation of the asynchronous pipeline. For a certain stage in this pipeline architecture, a new operation, either precharge or evaluate, can only be carried out when both the previous and next stage finished their current operation. This strict protocol limits the performance of the handshake signal.

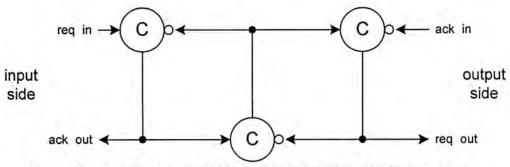

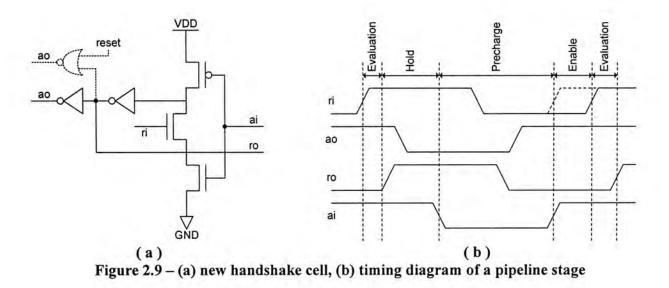

In the new asynchronous architecture, some improvements on the protocol have been made. First a current stage is allowed to go into the Evaluation phase when the next stage goes into the Precharge phase, i.e. no need to wait for the precharge confirmation from the Precharge phase. Second, a current stage is allowed to finish the Precharge phase even the previous stage is still in Evaluation phase. This introduces a flexible "Enable" period between the Precharge and Evaluation period. In order to carry out this new handshaking protocol, a new handshake cell is used and it is shown in Figure 2.9(a).

The new handshake cell is also in domino style. Compared with the classical architecture, this handshake cell is faster due to its simplicity, low input capacitance from the request and using simple transistor in pull-up. In this new structure, the handshake cell and the domino logic cell will enter the Precharge phase and Evaluation phase respectively at the same time. As a result, the handshake cell can be seen as a logic element of the pipeline stage and the throughput of the system can be minimized [30]. The handshake cell can be easily modified to receive more than one request signal by connecting more nMOS transistors in series in the nMOS tree, which is similar to the dynamic AND structure. The difference in speed will be more significant in logically joining handshake signals as the classical C-element with many inputs is very slow.

#### Chapter 2 – Asynchronous Design Methodology

One of the disadvantages of this handshake cell is the requirement of the four-phase handshaking protocol which requires longer communication time. However, this four-phase fits the operation of dynamic logic as the non-active phase can be used for the precharge of the dynamic logic.

Based on the new handshake cell, the operation of this new asynchronous pipeline architecture can be divided into 4 phases: Evaluation, Hold, Precharge and Enable. The timing diagram is shown in Figure 2.9(b). In the Evaluation phase, the current stage processes the data, which is valid at the input. After the current stage has finished its process, it will enter the Hold phase. In this phase, the input data may become invalid but the output should be held for the process in the next stage. After that, the stage will enter the Precharge phase, and will enter the Enable phase afterwards. In this phase, the stage is waiting for the valid data appearing at the input. This phase can be omitted when the valid input data has already appeared during the Precharge phase. Since all the handshake cells and logic cells should be precharged first during the power up, a NOR gate will be used, as shown in Figure 2.9(a), in the handshake cell. In this configuration, one of NOR gate inputs connects to the Reset signal thus that the all the cells in previous stage can be precharged initially.

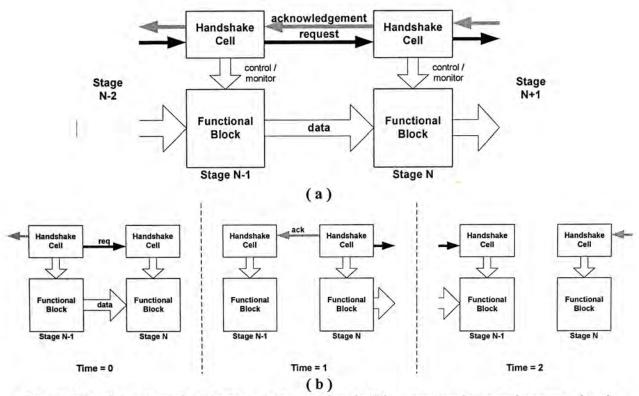

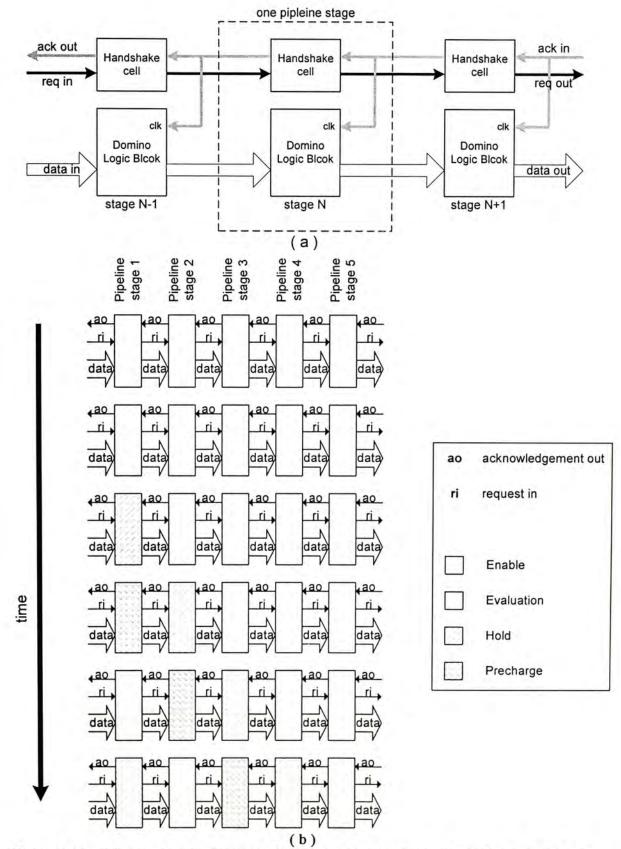

Figure 2.10 shows the connection and the flow of the pipeline operations of this new asynchronous architecture. When data arrives, the current stage will enter the Evaluation phase to process the data. Afterward, it will enter the Hold phase to hold the data for the next pipeline stage to process. At this moment, it will send a request signal to the following stage and acknowledgement signal to the previous stage.

After the following stage has processed the data, the current stage enters the Precharge phase. And at last it will enter the Enable phase to wait for a new data from the previous stage.

Figure 2.10 – (a) new asynchronous pipeline connection, (b) flow of operations in the new asynchronous pipeline

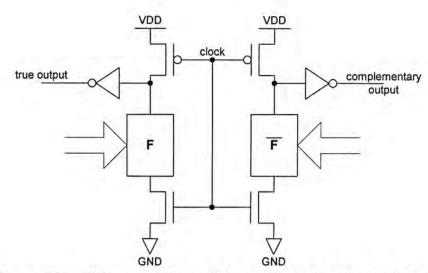

The use of Differential Cascode Voltage Switch Logic (DCVSL) [24], a type of domino logic, can also improve the speed of the circuit. Figure 2.11 shows the basic structure of a DCVSL cell. Its operation is similar to that of the domino logic. In the Precharge phase, both of the true and complementary outputs will be kept at low. When in the Evaluation phase, the computation is enabled. Due to the complementary structure of the nMOS logic blocks in DCVSL, one and only one of the outputs will go high.

Figure 2.11 – Differential Cascode Voltage Switch Logic (DCVSL)