# Implementation of an FPGA Based Accelerator for Virtual Private Networks

CHEUNG Yu Hoi Ocean (B. Eng.)

A Thesis Submitted in Partial Fulfillment of the Requirements for the Degree of Master of Philosophy

in

Computer Science and Engineering

©The Chinese University of Hong Kong July, 2002

The Chinese University of Hong Kong holds the copyright of this thesis. Any person(s) intending to use a part or the whole of the materials in this thesis in a proposed publication must seek copyright release from the Dean of the Graduate School.

# **Abstract**

Virtual Private Networks (VPN) are becoming increasingly popular network architectures for corporate networks. They enable corporations to connect Local Area Networks (LAN) in main and branch offices as if they were in the same network. As VPNs are built on the Internet infrastructure, the data exchange among different local area network will be passed through the Internet and thus can be easily eavesdropped, masqueraded, etc. Therefore, certain security measures must be used to deal with these privacy issues.

The Internet Protocol Security (IPSec) by the Internet Engineering Task Force (IETF) addresses the above mentioned security issues. A project called the Free Secure Wide Area Network (FreeS/WAN) was developed to provide an open source IPSec based VPN solution. This application use Triple-DES as default encryption mode for IPSec. Results show that the bottleneck in FreeS/WAN comes from encryption and decryption of the data.

As shown in this dissertation, the performance of FreeS/WAN with IPSec is 50% of that without FreeS/WAN. In order to improve performance of encryption, field programmable gate array (FPGA) based accelerators were built on a reconfigurable computing development platform called Pilchard. An implementation of Triple-DES on Pilchard was built to replace the current Triple-DES software based library (LibDES) used in FreeS/WAN. To compare performance of Triple-DES with that of another cipher, a Pilchard based accelerator for the International Data Encryption Algorithm (IDEA) was developed.

The resulting implementations achieved 120 Mb/sec for Triple-DES in CBC

mode and 248 Mb/sec for IDEA in ECB mode. These ciphers were used as a new cryptographic library for FreeS/WAN. Measurements show that this FPGA-based FreeS/WAN offers a 30% speedup on Triple-DES CBC mode over the original software library.

# 現場可編程門陣虛擬私有網路的加速器

#### 作者 張如海

## 摘要

虛擬私有網路(VPN)正成爲商業機構愈來愈普遍採用的網路結構。商業機構可以利用虛擬私有網路將在總部和分部的局域網(LAN)連成一體。因爲虛擬私有網路架設在互聯網上,不同的局域網之間需要通過互聯網來進行資料交換。所以必須使用某些安全措施來處理這些保密性問題。

爲解決上述安全問題,由互聯網工程小組(IETF)提出了互聯網安全協定(IPSec)。 FreeS/WAN 的開發提供了一種在使用互聯網安全協定和開放來源碼的 VPN 應用程式。這應用程式使用三重數據加密標準(Triple-DES) 作爲 IPSec 的主要加密方式。 其結果顯示在 FreeS/WAN 的瓶頸來自於資料的加密和解密。

在這份學術論文中, FreeS/WAN 的性能表現爲沒有 FreeS/WAN 50%。爲了改進加密的性能,在可重構的發展平臺-Pilchard 上發展了現場可編程門陣 (FPGA)的加速器。三重數據加密標準在 Pilchard 上實施以取代在 FreeS/WAN 的三重數據加密標準的軟體庫(LibDES)。

三重數據加密標準的加速器在 CBC 方式下性能可達 120 Mb/sec。而國際數據加密演算法(IDEA) 的加速器在 ECB 方式下可達 248 Mb/sec。這些加速器成爲 FreeS/WAN 的一個新的加密庫。測量結果顯示使用 FPGA 加速器的 FreeS/WAN 應用程式在三重數據加密標準下的性能比原來使用的軟體庫提升 30%。

# Acknowledgments

This thesis would not be possible to completed without help of many people. I would like to take this opportunity to thank them.

Firstly, I would like to thank my final year project and Master Degree supervisor, Prof. Leong Heng Wai Philip, for his guidance and encouragement in the past two years. He show his generosity and gave me numerous ideas for my research work.

I would like to thank Prof. Lee Kin Hong and Prof. Wei Keh Wei Victor for suggestions and comments for improving this work.

I would like to specially thank Mr. K.H. Tsoi and Mr. M.P. Leong. They gave me a lot of advices in completing this thesis.

I would like to thank my colleagues, Mr. C.K. Fung, Mr. C.H. Ho, Mr. Y.M. Lam, Ms. Ng Anny, Mr. C.W. Ng, Mr. C.W. Sham and Mr. W.C. Wong for their help in my research and bring me a pleasant working atmosphere.

I would like to thank my family for their endless support. This thesis is dedicated to my family.

# **Contents**

| 1 | Intr | roduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1  |

|---|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | 1.1  | Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1  |

|   | 1.2  | Aims                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2  |

|   | 1.3  | Contributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3  |

|   | 1.4  | Thesis Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3  |

| 2 | Virt | tual Private Network and FreeS/WAN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4  |

|   | 2.1  | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4  |

|   | 2.2  | Internet Protocol Security (IPSec)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4  |

|   | 2.3  | Secure Virtual Private Network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6  |

|   | 2.4  | LibDES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 9  |

|   | 2.5  | FreeS/WAN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 9  |

|   | 2.6  | Commercial VPN solutions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 9  |

|   | 2.7  | S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 11 |

| 3 | Cry  | ptography and Field-Programmable Gate Arrays (FPGAs)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12 |

| v | 3.1  | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 12 |

|   | 3.2  | The Date of the Control of the Contr | 12 |

|   |      | 201 Th Til DEG () ()                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 14 |

|   |      | 222 P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 16 |

|   | 3.3  | The IDEA At 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 17 |

|   |      | 2.2.1 Multiplication M. I. I. On                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 20 |

|   |     | 3.3.2         | Previous work on IDEA             | 21 |  |

|---|-----|---------------|-----------------------------------|----|--|

|   | 3.4 | Block         | Cipher Modes of angusting         | 23 |  |

|   |     | 3.4.1         | Flactronic Code Deals (FCD)       | 23 |  |

|   |     | 3.4.2         | Ciphon block Chairing (CDC)       | 25 |  |

|   | 3.5 | Field-        | Drogrammahla Cata A               | 27 |  |

|   |     | 3.5.1         | Viling Vietor ETM EDG A           | 27 |  |

|   | 3.6 | Pilcha        | ard                               | 30 |  |

|   |     | 3.6.1         | Mamory Cooks Control M. 1         | 31 |  |

|   | 3.7 | Electr        | onic Design Automotion To-1       | 32 |  |

|   | 3.8 |               | nary.                             | 33 |  |

| 4 | Imp | mplementation |                                   |    |  |

|   | 4.1 | Introd        | uction                            | 36 |  |

|   |     | 4.1.1         | Hardware Platform                 | 36 |  |

|   |     | 4.1.2         | Reconfigurable Hardware Committee | 36 |  |

|   |     | 4.1.3         | Pilchard Coffman                  | 38 |  |

|   | 4.2 | DES in        | n ECR made                        | 39 |  |

|   |     | 4.2.1         | Hardware                          | 39 |  |

|   |     | 4.2.2         | Software Interface                | 40 |  |

|   | 4.3 | DES in        | n CRC mode                        | 42 |  |

|   |     | 4.3.1         | Hardware                          | 42 |  |

|   |     | 4.3.2         | Software Interface                | 42 |  |

|   | 4.4 | Triple-       | DES in CRC mode                   | 45 |  |

|   |     | 4.4.1         | Hardware                          | 45 |  |

|   |     | 4.4.2         | Software Interface                | 45 |  |

|   | 4.5 | IDEA :        | in ECB mode                       | 48 |  |

|   |     | 4.5.1         | Multiplication Madula 916 + 1     | 48 |  |

|   |     | 4.5.2         | Hardware                          | 48 |  |

|   |     | 4.5.3         | Coftware Tut. C                   | 50 |  |

|    | 4.6    | Triple-DES accelerator in LibDES               |   |

|----|--------|------------------------------------------------|---|

|    | 4.7    |                                                |   |

|    | 4.8    |                                                | 3 |

|    | 4.9    |                                                | ļ |

| 5  | Res    | sults 55                                       | ; |

|    | 5.1    | Introduction                                   | ; |

|    | 5.2    | Benchmarking environment                       | ; |

|    | 5.3    | Performance of Triple-DES and IDEA accelerator |   |

|    |        | 5.3.1 Performance of Triple-DES core           |   |

|    |        | 5.3.2 Performance of IDEA core                 |   |

|    | 5.4    | Benchmark of FreeS/WAN                         |   |

|    |        | 5.4.1 Triple-DES                               |   |

|    |        | 5.4.2 IDEA                                     |   |

|    | 5.5    | Summary                                        |   |

| 6  | Con    | aclusion 62                                    |   |

|    | 6.1    | Future development                             |   |

|    |        | 1 ditare development                           |   |

| Bi | bliogr | raphy 65                                       |   |

|    |        |                                                |   |

# **List of Figures**

| 2.1  | Virtual Private Network                                              | 8  |

|------|----------------------------------------------------------------------|----|

| 3.1  | Data Encryption Standard algorithm                                   | 15 |

| 3.2  | Triple-DES algorithm                                                 | 16 |

| 3.3  | Block diagram of the IDEA algorithm                                  | 18 |

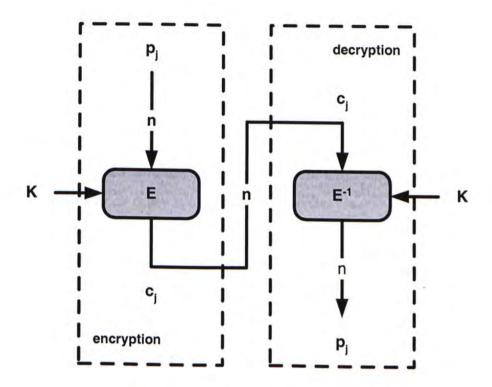

| 3.4  | Electronic Codebook mode                                             | 24 |

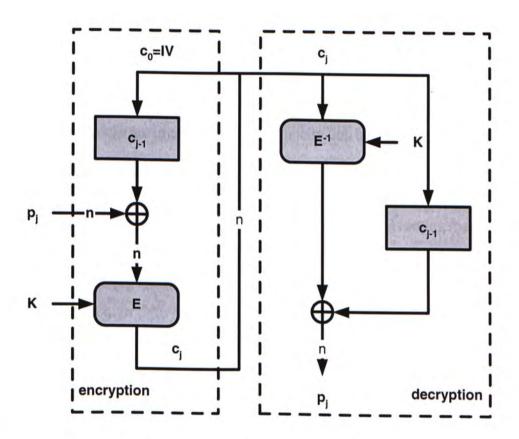

| 3.5  | Cipher Block Chaining mode                                           | 26 |

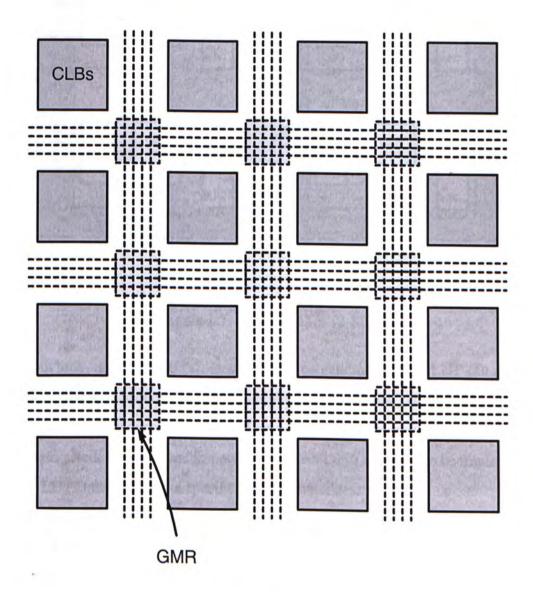

| 3.6  | Architecture of FPGAs                                                | 28 |

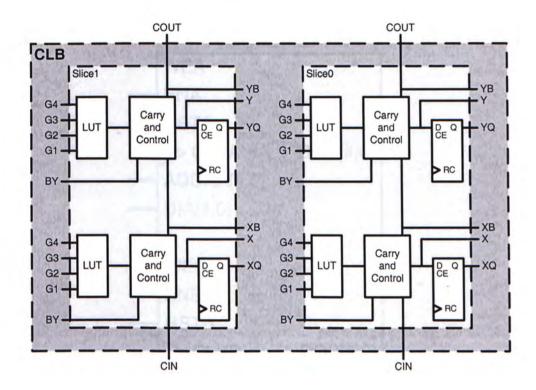

| 3.7  | Virtex-E CLB (2-Slice)                                               | 29 |

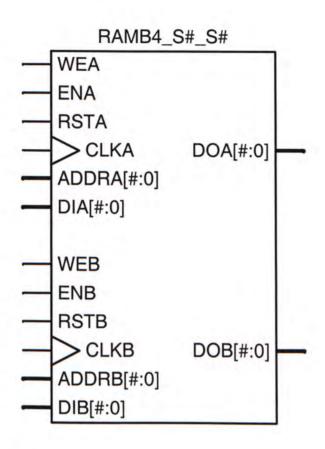

| 3.8  | Dual-Port Block SelectRAM                                            | 30 |

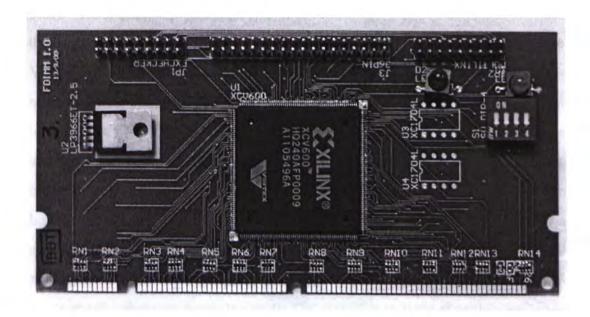

| 3.9  | Picture of Pilchard                                                  | 32 |

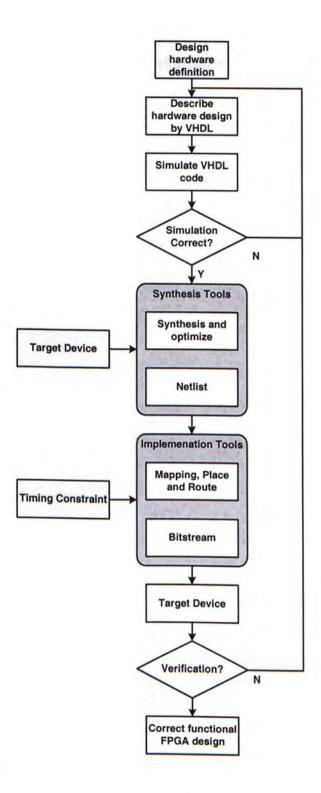

| 3.10 | Development cycles for FPGA design using VHDL                        | 34 |

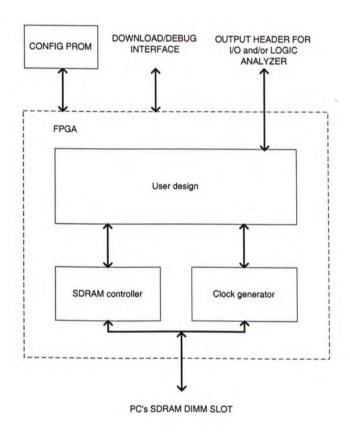

| 4.1  | Block diagram of the Pilchard board                                  | 37 |

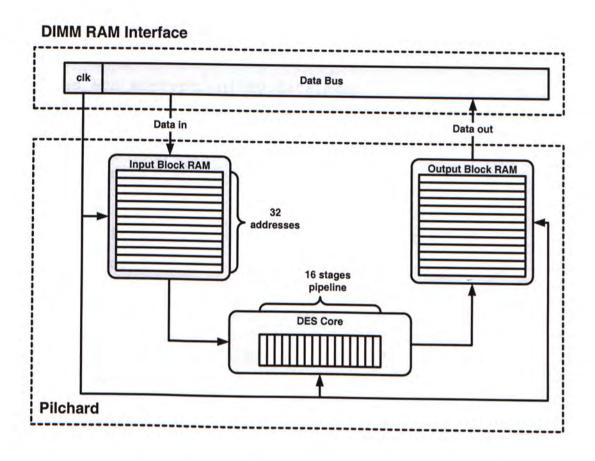

| 4.2  | System architecture of DES accelerator in ECB mode                   | 40 |

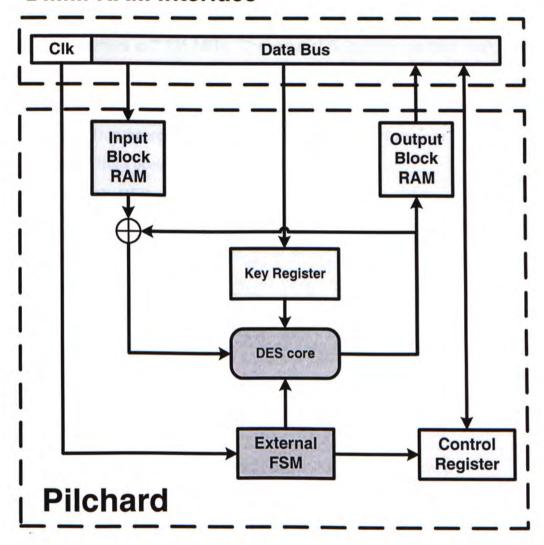

| 4.3  | System architecture of DES accelerator in CBC mode                   | 44 |

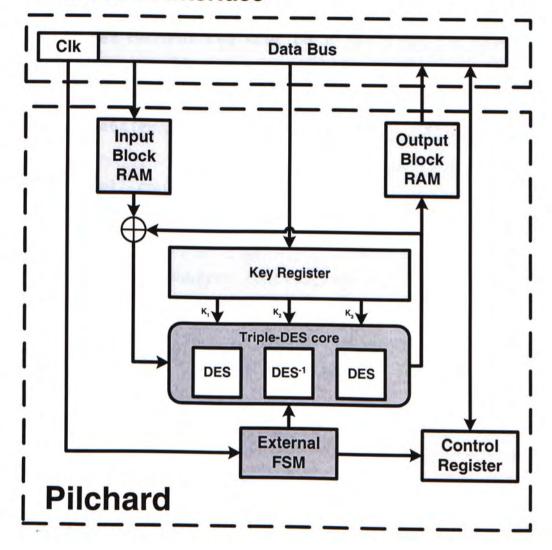

| 4.4  | System architecture of Triple-DES accelerator                        | 46 |

| 4.5  | Architecture of the IDEA core                                        | 49 |

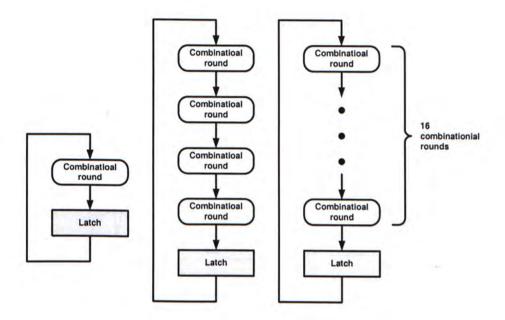

| 5.1  | Architecture of the DES core with different number of combina-       |    |

|      | tional rounds                                                        | 57 |

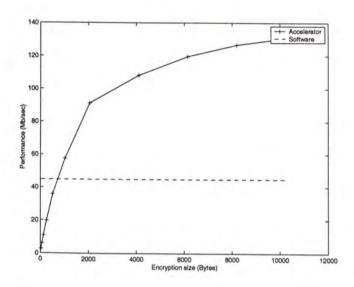

| 5.2  | Performance of Triple-DES accelerator with different encryption size |    |

# **List of Tables**

| 2.1 | Comparison of VPN solutions using software encryption                                  | 10 |

|-----|----------------------------------------------------------------------------------------|----|

| 2.2 | Comparison of VPN solutions using hardware encryption                                  |    |

| 3.1 | Initial bit permutation (IP)                                                           | 14 |

| 3.2 | Inverse of initial bit permutation $(IP^{-1})$                                         | 14 |

| 3.3 | Comparison of DES implementations                                                      |    |

| 3.4 | IDEA decryption subkeys $Z_r^{(i)}$ derived from encryption subkeys                    | 17 |

|     | $Z_r^{(i)}$ . $-Z_i$ and $Z_i^{-1}$ denote additive inverse modulo $2^{16}$ and multi- |    |

|     | plicative inverse $2^{16} + 1$ of $Z_i$ respectively                                   | 20 |

| 3.5 | Comparison of IDEA implementations                                                     | 22 |

| 5.1 | Configuration of machine for benchmark                                                 | 55 |

| 5.2 | Area and Speed Tradeoff among DES core with different rounds                           | 56 |

| 5.3 | Benchmark of ttcp with/without FreeS/WAN                                               |    |

| 5.4 | Benchmark of ttcp with FreeS/WAN using Pilchard based accelerator                      |    |

|     |                                                                                        |    |

# Chapter 1

# Introduction

#### 1.1 Motivation

In a private network of a business, information and resource are shared. Information flow is very important nowadays, for example, the operational costs of a business can be cut down if a better supply chain model is employed. The business can improve its services by sharing information internally and with its business partners. Also due to the globalization of business environments, corporations have offices all over the world. The different geographical locations make connections among different private networks difficult.

The Virtual Private Network is an architecture to realize the connections among different private networks over a public network. For example, the Internet can be used as a convenient and low cost channel for a virtual private network. Internet is a public channel and is not secure. Cryptographic algorithms can provide a way to secure channel between private networks over Internet.

Field-Programmable Gate Arrays (FPGAs) are hardware devices which are reconfigurable, i.e. programming an FPGA can change its functionally. Implementations of cryptographic hardware using FPGAs offer higher performance than software implementations. Software implementations of cryptographic algorithms are sequential in nature. However, in cryptographic hardware, algorithms can execute in parallel, offering a more efficient implementation. There are several advantages to use FPGAs as the choice of hardware device for a virtual private network accelerator:

- most network applications offer various encryption standards as options. With FPGAs, it is possible to reconfigure the chip for different encryption standards.

- FPGAs offer lower costs for small volumes, shorter development times and faster time to market over application specific integrated circuit (ASIC) technology.

- the technology and capacity of FPGAs continue to improve over previous years. The performance of FPGA accelerator can be improved once a faster device is available without any further engineering.

#### 1.2 Aims

The main aim of this work was to develop an FPGA based accelerator for Virtual Private Networks. The following features were desired.

- develop a hardware accelerator which is integrated into a real network application.

- design various cryptographic hardware accelerators to widen the choice of algorithm.

- devise a hardware interface which is fully compatible with an existing software cryptographic library for usage in other applications.

- provide a high performance hardware accelerator for Triple Data Encryption Standard in Cipher-Block Chaining mode and the International Data Encryption Algorithm (IDEA) in Electronic Code Book (ECB) mode by using a new reconfigurable hardware environment - Pilchard.

#### 1.3 Contributions

This thesis presents a FPGA based cryptographic accelerator for virtual private network. The work presented in this thesis has the following features that distinguishes it over all previous designs:

- a study of tradeoffs in parallel and serial implementations of the International

Data Encryption Algorithm was made [CTLL01]. In this work, the bit-serial

implementation of IDEA was implemented by M.P. Leong [LCTL00]. In the

bit-parallel implementation of IDEA, the pipelined IDEA core was my work

and the control section was implemented by K.H. Tsoi.

- improvements to the device driver for the Pilchard reconfigurable hardware environment were made in order to improve the bandwidth between the PC and the FPGA.

- a high performance cryptographic accelerator was integrated in a real VPN

application and its performance measured. Although hardware based cryptographic accelerators (summized in Section 2.6) exist in commercial products,

to the best of my knowledge, detailed reports of their design and performance

have not been published.

#### 1.4 Thesis Outline

Background information concerning virtual private network are presented in Chapter 2. Chapter 3 provides a description of previous work on the IDEA and DES algorithms as well as their implementation in hardware. Also the tools and reconfigurable hardware that were used in this research are introduced. Chapter 5 introduce the architectural details of an FPGA based Virtual Private Network. Chapter 6 contains the results and benchmarks for this research. In Chapter 7, conclusions and further directions for work are given.

# Chapter 2

# Virtual Private Network and

# FreeS/WAN

#### 2.1 Introduction

In this chapter, background knowledge about virtual private networks and a VPN solution - FreeS/WAN are given. This chapter begins with a brief introduction to Virtual Private Networks using IPSec. A section discussing the Internet Protocol Security protocol (IPSec) is included, followed by information about LibDES which is a popular software cryptographic library. Finally, the details about FreeS/WAN is given.

# 2.2 Internet Protocol Security (IPSec)

IP packets are not secure over the Internet. It is trivial to fake the identity of an IP address, modify the content of packets, replay packets and intercept packets. In addition, we cannot guarantee that IP packets received are either coming from the original source or that the content is the original content.

Therefore, the IPSec protocol [KA98c] was introduced to solve the following problems:

- Eavesdropping: an adversary eavesdrops on the Internet, capturing data packets, e.g. credit card numbers, login names and passwords, etc. can be obtained by eavesdropping. Using the IPSec protocol, data traffic is encrypted so that it is difficult to obtain useful information by eavesdropping.

- 2. Masquerading: an adversary fakes his IP address to masquerade as a trusted host when address-based authentication is used. The IPSec protocol provides a cryptographic authentication method to protect against masquerading. With the IPSec Authentication Header Protocol, a receiver can make sure the source of data is as claimed.

- 3. Session hijacking: an adversary takes over a connection after the source has been authenticated. This scenario will not occur with IPSec protocol since the adversary have no knowledge about the session keys, which is negotiated in the IPSec Internet Key Exchange protocol, so they cannot encrypt or decrypt the data packets.

- 4. Denial-of-service: An adversary sends a huge sequence of connection requests to the target in order to make the target system overflow the buffer space. For example, email bombing, TCP SYN flooding, etc. Although this kind of attack is still possible with the use of IPSec protocol, the adversary will expose his real IP address due to the fact that all data packets should be properly authenticated.

The IPSec protocol provides three functionalities using three different protocols:

- the Authentication Header (AH) protocol

- the Encapsulating Security Payload (ESP) protocol

- the Internet Key Exchange (IKE) protocol

The Authentication Header (AH) protocol [KA98a] can authenticate the source of data packets, protect the completeness of the data packets and protect against

replay attacks. ESP (Encapsulation Security Payload) protocol [KA98b] shares all properties that AH has and it can also protect data from unauthorized disclosure and provide protection against traffic flow analysis. The security provided by IPSec needs to use shared keys in order to authenticate and encrypt the data streams. The Internet Key Exchange (IKE) protocol [HC98] is used to dynamically authenticate parties involved in IPSec, negotiate the encryption method used, and produce shared keys.

#### 2.3 Secure Virtual Private Network

In this work, the term Virtual Private Network (VPN) [DH99] is use to refer to the architecture that a private network constructed within a public network infrastructure. The connection of this network architecture can be either encrypted or unencrypted. Also it is possible to implement Virtual Private Networks on other networks, in this project, the Internet is assumed. IPSec is one of the protocol that may use in VPN architecture that provide security and privacy by cryptographic algorithms and hash functions. Another term, Secure Virtual Private Network (SVPN) refers to a VPN with IPSec.

The key concept of Virtual Private Network is tunneling. With tunneling, VPNs provide connection and protocol transparency among different Intranets of same organization or even different parties. For connection transparency, different parties are connected together as if they were on the same network. They do not need to know the mechanism and the details of connections. For protocol transparency, different parties using different protocol can be connected together as if they were using the same protocol. This is achieved by encapsulation of data packets at the end-points of a tunnel with a different protocol.

Although there are many advantages associated with using a VPN over the Internet, the data would be transmitted in plaintext over an insecure channel. The Intranet of a party is exposed to attacks from Internet which violates the major aim of VPN to be a private network.

There are two major in common protocols for VPNs.

- 1. IPSec

- 2. PPTP

PPTP is the protocol used in Microsoft's VPN product and is proprietary. Thus, this work will focus on IPSec which will documented by the IETF in RFCs [iet].

Internet Protocol Security (IPSec) is a protocol proposed to solve the concerns about security and privacy. IPSec provide mechanisms to authenticate different parties and data packets are protected by encryptions.

To summarize here are some VPN characteristics:

- 1. The VPN uses the Internet as the underlying public network infrastructure.

- The VPN uses the IPSec as protocol to ensure privacy at the network layer.This means encryption is done as per every packet.

- Private addressing schemes can be used in Intranets and IP address is only used on communication of end-points of tunnel.

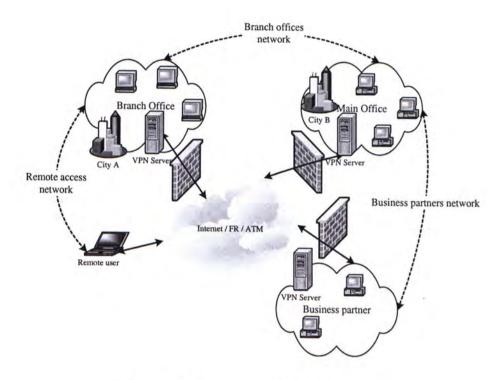

As suggested by most vendors of VPN solutions [vpnc], there are three scenarios that should be deal with in order to meet the requirements of a business. Three different types of users should be able to grant access to the VPN of a corporation. They are remote users, branch offices and business partners.

1. Remote access network - A remote user at home or on road needs access to his/her company's resources. The VPN should enable the remote users to work as if (s)he was at a workstation in the office. Different connections method should be provided in order to achieve the remote access into the network, e.g. dialup, ISDN, mobile IP, etc.

Figure 2.1: Virtual Private Network

- 2. Branch offices network Two or more trusted Intranets, which represent different branch and remote offices of a corporation, are interconnected together by a VPN. Very often, Intranets are protected by firewalls which can act as secure gateway connect to the Internet. Client workstations do not have to worry about the security between Intranets since this is ensured by the VPN.

- 3. Business partners network This is referred to as an Extranet by many VPN solution vendors. It should be the most recent trend for VPN usage; however, it is the scenario with least knowledge. Corporations can grant their business partner temporal and limited access to their Intranet. Electronic business applications among business partners include online quotations, order fulfillment, etc.

#### 2.4 LibDES

LibDES is a publicity available software library for DES and Triple-DES, written by Eric Young [lib]. It offers a large variety of highly optimized DES and Triple-DES functions in different modes. For example, DES in Electronic Codebook Mode (ECB), DES in Cipher Block Chaining Mode (CBC), 3DES in ECB mode, 3DES in CBC mode, etc. LibDES is a common standard library which is used in various application such as openSSL.

#### 2.5 FreeS/WAN

In this work, the baseline software used for the implementation of the VPN accelerator was FreeS/WAN. FreeS/WAN [Nap00, Fre00] stand for Free Secure Wide Area Network. FreeS/WAN is currently the most complete open source VPN solution available on Linux. In here, the version of FreeS/WAN used in this project is 1.5. It is currently built for Linux IPv4 network stack and work has commenced to integrate into the IPv6 network stack.

FreeS/WAN supports both remote access network and branch office network, however, it does not support business partner networks because the software does not have any mechanism for temporal and limited access to network.

LibDES is used in FreeS/WAN as the DES and Triple-DES library. In LibDES, DES and triple-DES in different modes are performed in software. Replacing the software DES with a hardware based implementation is the main focus of this work. The version of LibDES used in FreeS/WAN v1.5 is version 4.04.

# 2.6 Commercial VPN solutions

There are commercial VPN solutions using either software or hardware implementations for different cryptographic algorithms. Although different solutions may

have different build-in cryptographic algorithm options, Triple-DES is available for all VPN solutions. Performance of VPN solutions using Triple-DES from different vendors is compared in Table 2.1 and Table 2.2.

Cisco Systems Inc. has a wide range of VPN solutions with different specifications. Cisco 3015 uses software encryption method and hence a relatively low throughput of 4 Mb/sec is obtained. In Cisco 5000 series VPN solutions, different numbers of encryption processors can be used. For the highest throughput VPN solution in this series, 760 Mb/sec is achieved by using eight encryption processors. Intel provides two VPN solutions using software encryption with throughputs of 8 Mb/sec and 20 Mb/sec. They also have a VPN solution using a PCI encryption processor with a throughput of 85 Mb/sec.

| Vendor | VPN Solution           | Maximum throughputs (Mb/sec) | Reference |

|--------|------------------------|------------------------------|-----------|

| Cisco  | Cisco 3015             | 4                            | [vpna]    |

| Intel  | Intel 3110 VPN gateway | 8                            | [vpne]    |

| Intel  | Intel 3105 VPN gateway | 20                           | [vpnd]    |

Table 2.1: Comparison of VPN solutions using software encryption

| Vendor | VPN Solution           | Maximum throughputs (Mb/sec) | Scalability | Reference |

|--------|------------------------|------------------------------|-------------|-----------|

| Cisco  | Cisco VPN 5001         | 45                           | 1           | [vpnb]    |

|        | Cisco VPN 5002         | 190                          | 2           | [vpnb]    |

|        | Cisco VPN 5008         | 760                          | 8           | [vpnb]    |

| Intel  | Intel 3125 VPN gateway | 85                           | 1           | [vpnf]    |

Table 2.2: Comparison of VPN solutions using hardware encryption

## 2.7 Summary

In this chapter, virtual private networks and the details about FreeS/WAN were discussed. The Virtual Private Network is an architecture to connect two separate LANs over a public network. The Internet is the most popular choice as the channel due to its accessibility and cost. Since the Internet is insecure, IPSec is used to deal with privacy issues. FreeS/WAN is an open source VPN solution using IPSec on Linux.

# Chapter 3

# Cryptography and Field-Programmable Gate Arrays (FPGAs)

#### 3.1 Introduction

This chapter introduces the basic concepts of cryptography and Field-Programmable Gate Arrays. Firstly, DES, Triple-DES and IDEA algorithms and previous implementations are introduced. This is followed by description of different block cipher modes of operation. The architecture of FPGAs is discussed, in particular, information on the architecture of Xilinx Virtex-E FPGAs are given. The details concerning the reconfigurable computing environment, Pilchard, is then presented. Finally, Electronic Design Automation Tools and the FPGAs design flow is detailed.

## 3.2 The Data Encryption Standard Algorithm (DES)

The Data Encryption Standard (DES) [Nat94, Uni77] algorithm has been a popular secret key encryption algorithm and is used in many commercial and financial applications. Also, it was the first commercial cryptographic algorithm with fully

specified implementation details. It is defined by ANSI FIPS46-2. Although introduced in 1976, it has proved resistant to all forms of cryptanalysis. However, its 56-bit key is not large enough by today's standards. A DES key search engine called "Deep Crack" could search 88 billion keys per second and this machine solve RSA laboratories DES-III challenge [RSA99] on January 1999 in 22 hours.

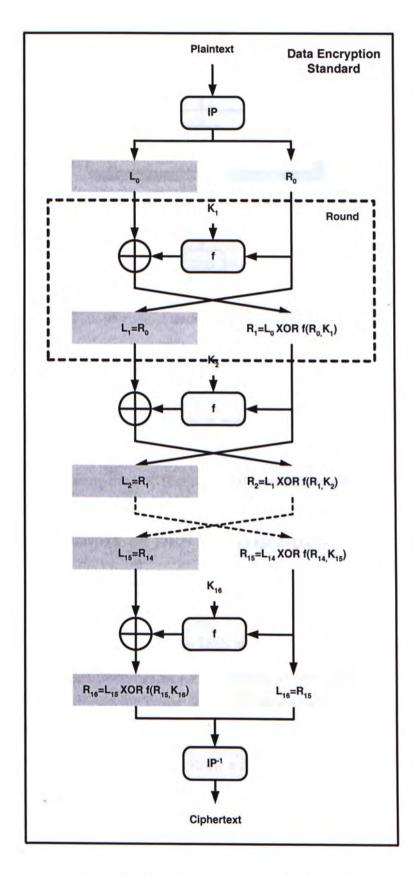

DES is a block cipher as shown in Figure 3.1 which processes 64-bit plaintext blocks and produces 64-bit ciphertext blocks. The effective portion of the secret key is 56-bit out of 64-bit since although the key is 64-bit, 8-bits are used as parity bits.

Encryption of DES proceeds in 16 identical rounds. From the input key, sixteen 48-bit subkey  $K_i$  are generated, one for each round. Within each round, 8 fixed 6 to 4-bit substitution mappings known as S-Boxes are used.

The plaintext have an initial bit permutation (IP) as shown in Table 3.1 and are then divided into left  $L_0$  and right halves  $R_0$ , each 32-bit. Each round takes 32-bit inputs  $L_{i-1}$  and  $R_{i-1}$  from previous rounds and produces 32-bit outputs  $L_i$  and  $R_i$  for  $1 \le i \le 16$ , as follows:

$$L_i = R_{i-1}$$

$L_i = L_{i-1} \oplus f(R_{i-1}, K_i), where f(R_{i-1}, K_i) = P(S(E(R_{i-1}) \oplus K_i))$

E is a fixed expansion permutation mapping  $R_{i-1}$  from 32-bit to 48-bit. P is another fixed permutation on 32-bits. The equation shows the right half of each round go through an expansion permutation from 32-bits to 48-bits and is then exclusive-ored with the subkey of that round. The temporary result is passed through the S-Box and forms the new 32-bit product of the right half. For each round, right half and left half are exchanged. Finally both halves are combined together in the 16th round and permutated by the inverse of the initial bit permutation shown in Table 3.2 to form the ciphertext. Decryption uses the same key and algorithm, however, the subkeys in internal rounds are applied in reverse order. For encryption, the key schedule order is  $K_1, K_2, K_3, \ldots, K_{16}$ . For decryption, the decryption key

schedule is  $K_{16}, K_{15}, K_{14}, \dots, K_1$ .

```

58

50

42

34

26

2

18

10

52

44

36

28

20

12

60

4

22

62

54

46

38

30

14

6

56

48

40

32

24

16

64

8

25

17

57

49

41

33

9

1

59

51

43

35

27

19

3

11

21

61

53

45

37

29

13

5

63 55

47

39

31

23

15

7

```

Table 3.1: Initial bit permutation (IP)

```

40

24

8

48

16

56

64

32

39

55

23

63

47

15

31

6

38

46

14

54

22

62

30

37

5

45

13

53

21

61

29

36

4

44

12

52

20

60

28

3

35

43

11

51

19

59

27

2

34

42

10

50

18

26

58

33

1

41

9

49

17

157

25

```

Table 3.2: Inverse of initial bit permutation  $(IP^{-1})$

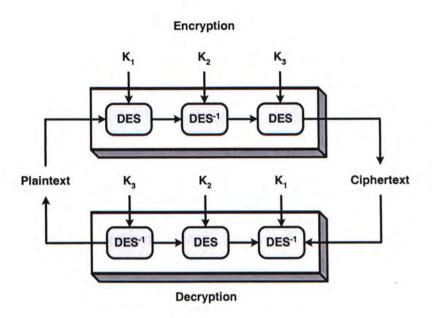

#### 3.2.1 The Triple-DES Algorithm (3DES)

Triple-DES algorithm [Nat99] was introduced to increase the key size of DES and maintaining compatibility with legacy DES software and hardware systems. For encryption, the plaintext is processed by three cascaded DES cores as shown in Figure 3.2, the first and the last DES cores are in encryption mode and the middle one is in decryption mode. If the same key is used for  $K_1$  and  $K_2$ , Triple-DES is the same as DES with key  $K_3$ . For decryption of Triple-DES, the modes of three cascaded DES cores are inverted so that the first and the last DES cores are in

Figure 3.1: Data Encryption Standard algorithm

Figure 3.2: Triple-DES algorithm

decryption mode and the middle one is in encryption mode. Triple-DES algorithm increase the key size three times compared to DES, which is from 56-bit to 168-bit. However, the processing time of Triple-DES increase three times as well.

#### 3.2.2 Previous work on DES and Triple-DES

A software implementation of DES and Triple-DES by Biham in 1997 in ECB mode achieved 46 Mb/second 22 Mb/sec respectively on an 300 MHz Alpha, which is a 64-bit processor. The most common DES software LibDES [lib] achieves 121.5 Mb/sec for DES ECB mode on an Intel Pentium III 866 MHz machine. LibDES also achieves 42.9 Mb/sec for Triple-DES CBC mode on the same machine.

Hardware implementations offer much higher performance than DES software implementation. In 1999, Free-DES [fre], a 3656 Mb/sec implementation of DES algorithm on Xilinx Virtex XCV400-6 with 60 MHz clock rate was reported. A 1280 Mb/sec implementation of IDEA was reported in 1999 [WPR+99] by Wilcox et. al. The Sandia National Laboratories developed an ASIC implementation of DES [WPR+99]

which achieves 6700 Mb/sec. The fastest hardware DES hardware implementation [Pat00] is proposed by Patterson which achieves 10752 Mb/sec. This implementation fully unrolls and pipeline the DES rounds and operates at a 168 MHz clock rate. It employs dynamic circuit specialization in an FPGA to achieve high performance.

Previous high performance implementation of DES in hardware fully maximize their throughput by unrolling and pipelining the design in Electronic Code Book mode (see Section 3.6). Due to the data dependencies, pipelined DES implementations cannot have the same performance.

| Year | Implementation         | Throughput (Mb/sec) | Reference |

|------|------------------------|---------------------|-----------|

| 1997 | software               | 121.5               | [fre]     |

| 1999 | Xilinx Virtex XCV400-6 | 3656                | [fre]     |

| 1999 | 4 × Altera 10K100      | 1280                | [WPR+99]  |

| 1999 | ASIC 0.6 µm CMOS       | 9280                | [WPR+99]  |

| 2000 | Xilinx Virtex XCV150-6 | 10752               | [Pat00]   |

Table 3.3: Comparison of DES implementations

### 3.3 The IDEA Algorithm

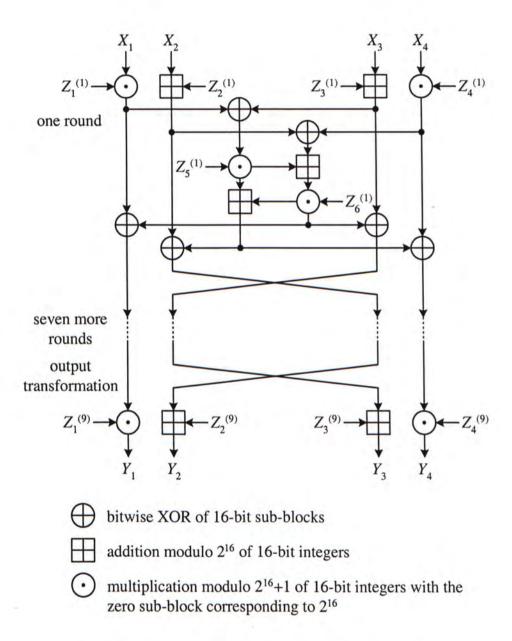

IDEA takes 64-bit plaintext inputs and produces 64-bit ciphertext outputs using a 128-bit key.

The design philosophy behind IDEA is mixing operations from different algebraic groups including XOR, addition modulo  $2^{16}$ , and multiplication modulo the Fermat prime  $2^{16} + 1$ . All these operations work on 16-bit sub-blocks.

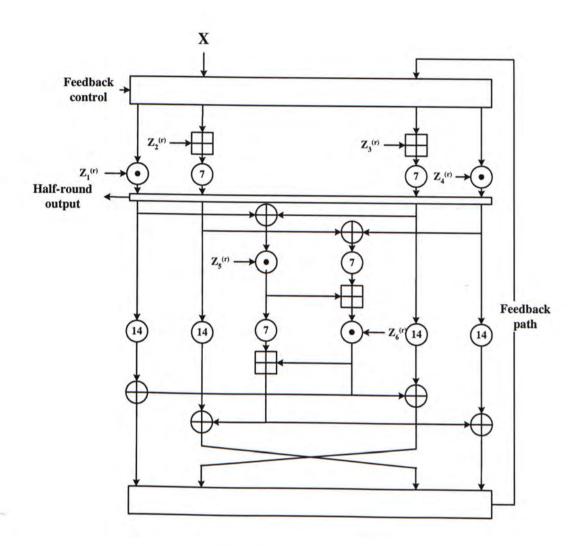

The IDEA block cipher [Sch96] (depicted in Figure 3.3) consists of a cascade of eight identical blocks known as rounds, followed by a half-round or output transformation. In each round, XOR, addition and modular multiplication operations are applied. IDEA is believed to possess strong cryptographic strength because

Figure 3.3: Block diagram of the IDEA algorithm.

- its primitive operations are of three distinct algebraic groups of 216 elements

- ullet multiplication modulo  $2^{16}+1$  provides desirable statistical independence between plaintext and ciphertext

- · its property of having iterative rounds made differential attacks difficult.

The encryption process is as follows. The 64-bit plaintext is divided into four 16-bit plaintext sub-blocks,  $X_1$  to  $X_4$ . The algorithm converts the plaintext blocks into ciphertext blocks of the same bit-length, similarly divided into four 16-bit sub-blocks,  $Y_1$  to  $Y_4$ . 52 16-bit subkeys,  $Z_i^{(r)}$ , where i and r are the subkey number and round number respectively, are computed from the 128-bit secret key. Each round uses six subkeys and the remaining four subkeys are used in the output transformation. The decryption process is essentially the same as the encryption process except that the subkeys are derived using a different algorithm [Sch96].

The algorithm for computing the encryption subkeys (called the key-schedule) involves only logical rotations. Order the 52 subkeys as  $Z_1^{(1)}, \ldots, Z_6^{(1)}, Z_1^{(2)}, \ldots, Z_6^{(2)}, \ldots, Z_6^{(8)}, Z_1^{(9)}, \ldots, Z_4^{(9)}$ . The procedure begins by partitioning the 128-key secret key Z into eight 16-bit blocks and assigning them directly to the first eight subkeys. Z is then rotated left by 25 bit, partitioned into eight 16-bit blocks and again assigned to the next eight subkeys. The process continues until all 52 subkeys are assigned. The decryption subkeys  $Z_i^{(r)}$  can be computed from the encryption subkeys with reference to Table 3.4.

In Electronic Codebook (ECB) mode [Sch96], the data dependencies of the IDEA algorithm have no feedback paths. Additionally, in practice, latencies of order of microseconds are acceptable. These features make deeply pipelined implementations possible.

|                     | r = 1                 | $2 \le r \le 8$       | r = 9                 |

|---------------------|-----------------------|-----------------------|-----------------------|

| $Z_1^{\prime(r)}$   | $(Z_1^{(10-r)})^{-1}$ | $(Z_1^{(10-r)})^{-1}$ | $(Z_1^{(10-r)})^{-1}$ |

| $Z_{2}^{\prime(r)}$ | $-Z_2^{(10-r)}$       | $-Z_3^{(10-r)}$       | $-Z_2^{(10-r)}$       |

| $Z_{3}^{\prime(r)}$ | $-Z_3^{(10-r)}$       | $-Z_2^{(10-r)}$       | $-Z_3^{(10-r)}$       |

| $Z_4^{\prime(r)}$   | $(Z_4^{(10-r)})^{-1}$ | $(Z_4^{(10-r)})^{-1}$ | $(Z_4^{(10-r)})^{-1}$ |

| $Z_{5}^{\prime(r)}$ | $Z_5^{(9-r)}$         | $Z_5^{(9-r)}$         | N/A                   |

| $Z_{6}^{\prime(r)}$ | $Z_6^{(9-r)}$         | $Z_6^{(9-r)}$         | N/A                   |

Table 3.4: IDEA decryption subkeys  $Z_r^{(i)}$  derived from encryption subkeys  $Z_r^{(i)}$ .  $-Z_i$  and  $Z_i^{-1}$  denote additive inverse modulo  $2^{16}$  and multiplicative inverse  $2^{16} + 1$  of  $Z_i$  respectively.

#### **3.3.1** Multiplication Modulo $2^n + 1$