# Design and Implementation of Fully Integrated Low-Voltage Low-Noise CMOS VCO

YIP Kim-fung

A Thesis Submitted in Partial Fulfilment

of the Requirements for the Degree of

Master of Philosophy

in

**Electronic Engineering**

©The Chinese University of Hong Kong June 2002

The Chinese University of Hong Kong holds the copyright of this thesis. Any person(s) intending to use a part or whole of the materials in the thesis in a proposed publication must seek copyright release from the Dean of the Graduate School.

### Abstract

Voltage-controlled oscillators (VCOs) are critical components for signal generation in RF transceivers. Recently, there has been considerable interest in monolithic integration of inductance-capacitance (LC) tank oscillators for highly integrated RF transceivers. Technologies such as Si CMOS and Si/SiGe BiCMOS are of interest in light of the potential for integration with digital functions. However, in Si technologies, the Q of the inductor is usually the limiting factor. Traditionally, inductors have been incorporated as discrete components located off-chip, often as small surface-mount parts. Alternatively, some VCO designs have utilized bonding wires as hybrid inductors. While bonding wires can offer a relatively high Q, they also suffer from large variations in inductance value.

In this thesis, the design and implementation of low phase noise fully integrated CMOS LC differential voltage-controlled oscillators is presented. The new circuit topology offers: (1) Resonator with enhanced quality factor; and (2) Reduction of noise up-conversion coefficient. The proposed design is verified experimentally by the fabrication of 1.5 GHz LC VCO circuits using 0.6 micron standard CMOS technology. The phase noise and frequency tuning performances of the oscillators are also shown for comparison.

摘要

在無線電收發機內,電壓控制振盪器是其中一個較為重要的部分。近年, 有關把電感電容差分電壓控制振盪器整合於單晶片無線電收發機上的研究,引 起了極大關注。藉著利用互補金屬氧化物半導體或雙極互補金屬氧化物半導體 技術,更可把振盪器與數位電路結合在一單晶片上。但是,在矽技術當中,電 感器的Q值往往是一個限制。

本論文將會講述有關如何利用嶄新的共振器結構,設計出低相位雜訊的電 感電容差分電壓控制振盪器。這技術不但能提高共振器的Q值,並且能減少振 盪器的嘈音上載指數。

本論文所提出的電感電容差分電壓控制振盪器設計,是透過標準零點六微 米互補金屬氧化物半導體技術的研製下,電路運作在一千五百兆頻,並在相位 雜訊和頻率調整的性能上作出分析及比較。

# Acknowledgement

I would like to express my sincere thanks to my supervisor, Prof. K. K. Cheng, for his generous, guidance and continued support throughout my research study. I also thank my family for their love and encouragement. My associate examiner, Prof. K. L. Wu, and my colleagues have also helped in many ways. I would like to single out Mr. C. W. Fan, Ms. W. Y. Leung, Mr. P. Y. Lin for their assistance and helpful suggestions.

## **Table of Contents**

| Abstract                |                                                                                                                                                                                                                                                                                                            | Ι                                |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Acknowled               | lgement                                                                                                                                                                                                                                                                                                    | ш                                |

| Table of Co             | ontents                                                                                                                                                                                                                                                                                                    | IV                               |

| Chapter 1<br>1.1<br>1.2 | Introduction<br>Motivation<br>Objective                                                                                                                                                                                                                                                                    | 1<br>1<br>6                      |

| Chapter 2<br>2.1        | Theory of Oscillators<br>Oscillator Design<br>2.1.1 Loop-Gain Method<br>2.1.2 Negative Resistance-Conductance Method<br>2.1.3 Crossed-Coupled Oscillator                                                                                                                                                   | 7<br>7<br>7<br>8<br>10           |

| Chapter 3<br>3.1        | Noise Analysis<br>Origin of Noise Sources<br>3.1.1 Flicker Noise<br>3.1.2 Thermal Noise<br>3.1.3 Noise Model of Varactor                                                                                                                                                                                   | 15<br>16<br>16<br>17<br>18       |

| 3.2<br>3.3              | <ul> <li>3.1.4 Noise Model of Spiral Inductor</li> <li>Derivation of Resonator</li> <li>Phase Noise Model</li> <li>3.3.1 Leeson's Model</li> <li>3.3.2 Phase Noise Model defined by J. Cranincks and M. Steyaert</li> </ul>                                                                                | 19<br>19<br>22<br>23<br>24       |

| 3.4                     | <ul> <li>3.3.3 Non-linear Analysis of Phase Noise</li> <li>3.3.4 Flicker-Noise Upconversion Mechanism</li> <li>Phase Noise Reduction Techniques</li> <li>3.4.1 Conventional Tank Circuit Structure</li> <li>3.4.2 Enhanced Q tank circuit Structure</li> <li>3.4.3 Tank Circuit with parasitics</li> </ul> | 26<br>31<br>33<br>33<br>35<br>37 |

|                         | 3.4.4 Reduction of Up-converted Noise                                                                                                                                                                                                                                                                      | 39                               |

| Chapter 4        | CMOS Technology and Device Modeling                                                                | 42       |

|------------------|----------------------------------------------------------------------------------------------------|----------|

| 4.1              | Device Modeling                                                                                    | 42       |

|                  | 4.1.1 FET model                                                                                    | 42       |

|                  | 4.1.2 Layout of Interdigitated FET                                                                 | 46       |

|                  | 4.1.3 Planar Inductor                                                                              | 48       |

|                  | 4.1.4 Circuit Model of Planar Inductor                                                             | 50       |

|                  | 4.1.5 Inductor Layout Consideration                                                                | 54       |

|                  | 4.1.6 CMOS RF Varactor                                                                             | 55       |

|                  | 4.1.7 Parasitics of PMOS-type varactor                                                             | 57       |

| Chapter 5        | Design of Integrated CMOS VCOs                                                                     | 59       |

| 5.1              |                                                                                                    | 59       |

|                  | 5.1.1 Equivalent circuit model of differential LC VCO                                              | 59       |

|                  | 5.1.2 Reference Oscillator Circuit                                                                 | 61       |

|                  | 5.1.3 Proposed Oscillator Circuit                                                                  | 62       |

|                  | 5.1.4 Output buffer                                                                                | 63       |

|                  | 5.1.5 Biasing Circuitry                                                                            | 64       |

| 5.2              |                                                                                                    | 65       |

| 5.3              | 방향, 영상가 쉽지 않고 있었던 방법이 가지 않는 것 같아요. 것이 가지 않는 것 같아요. 그는 것이 같이 많이 | 67       |

|                  | Varactor Design                                                                                    | 68<br>69 |

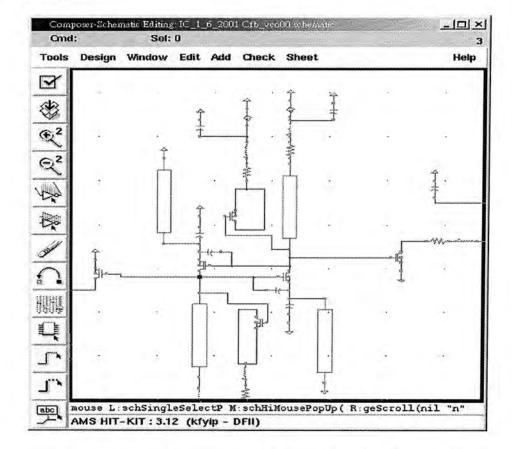

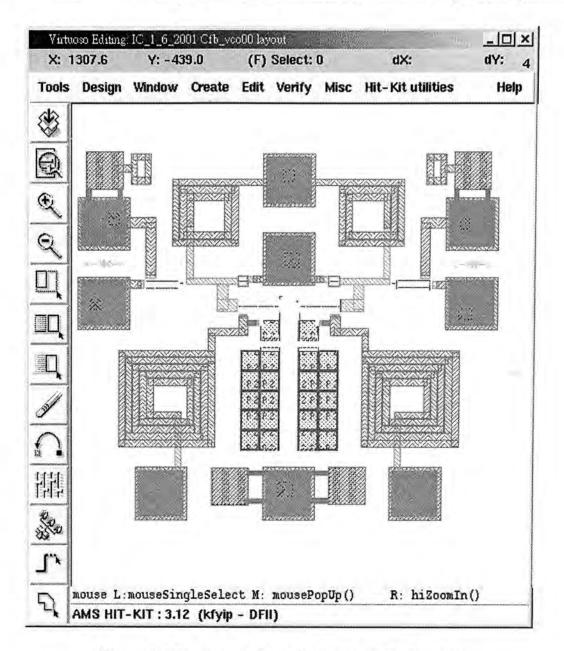

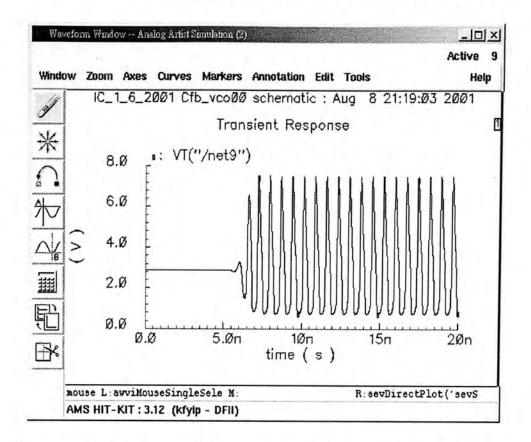

| 5.5<br>5.6       | Layout (Cadence)<br>Circuit Simulation (SpectreRF)                                                 | 74       |

| Chapter 6        | Experimental Results and Discussion                                                                | 76       |

| 6.1              | Measurement Setup                                                                                  | 76       |

| 6.2              | Measurement results: Reference Oscillator Circuit                                                  | 81       |

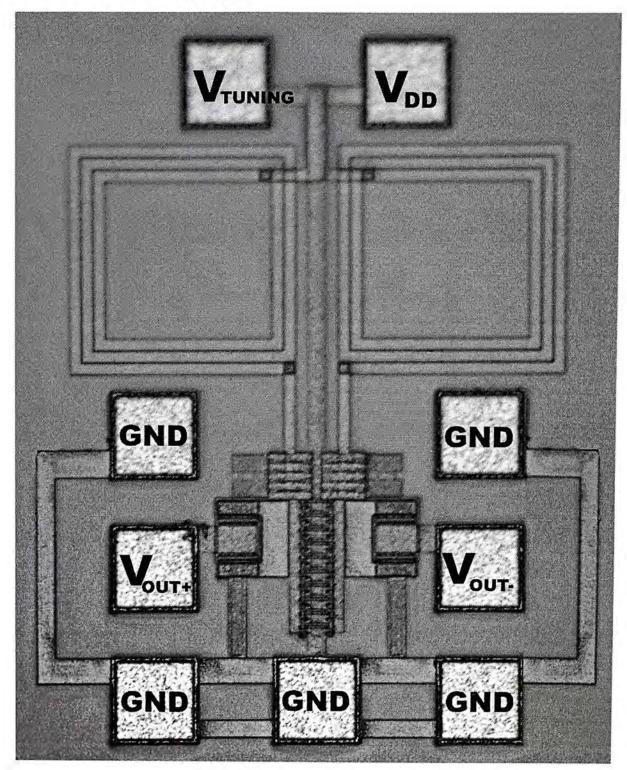

|                  | 6.2.1 Output Spectrum                                                                              | 81       |

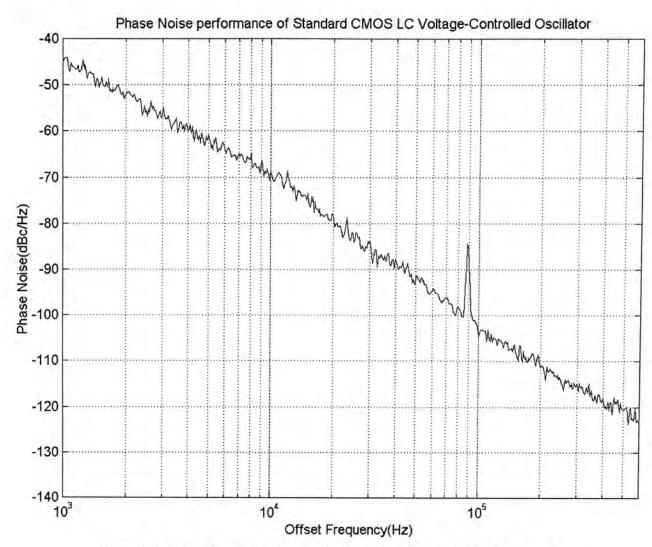

|                  | 6.2.2 Phase Noise Performance                                                                      | 82       |

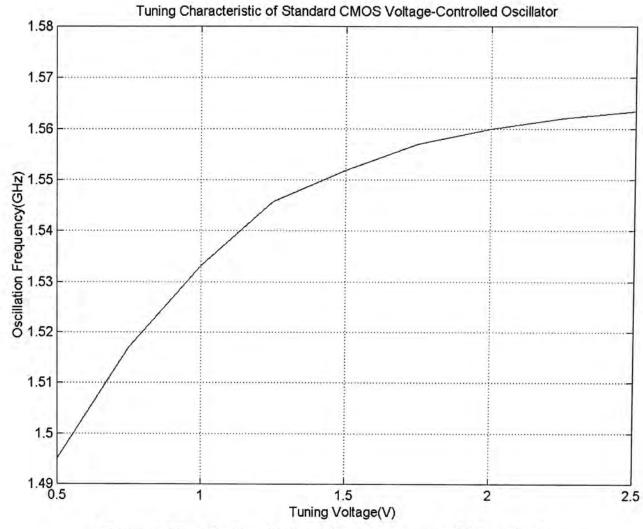

|                  | 6.2.3 Tuning Characteristic                                                                        | 83       |

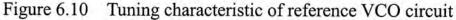

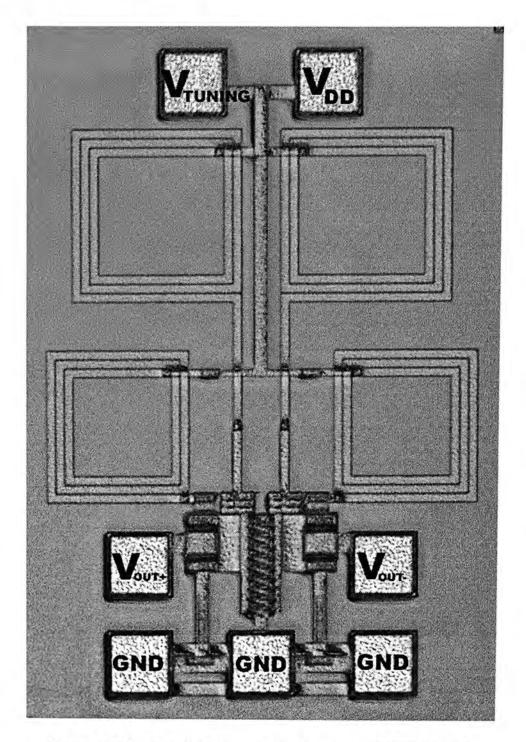

|                  | 6.2.4 Microphotograph                                                                              | 84       |

| 6.3              | Measurement results: Proposed Oscillator Circuit                                                   | 85       |

|                  | <ul><li>6.3.1 Output Spectrum</li><li>6.3.2 Phase Noise Performance</li></ul>                      | 85<br>86 |

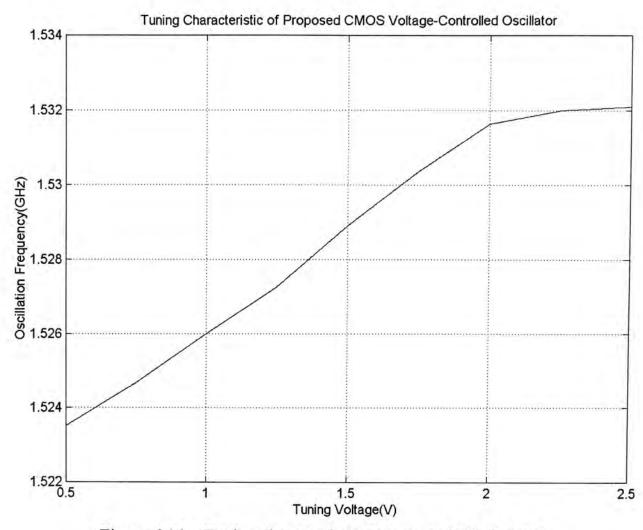

|                  | 6.3.3 Tuning Characteristic                                                                        | 87       |

|                  |                                                                                                    | 88       |

| 6.4              | 6.3.4 Microphotograph<br>Comparison of Measured Results                                            | 89       |

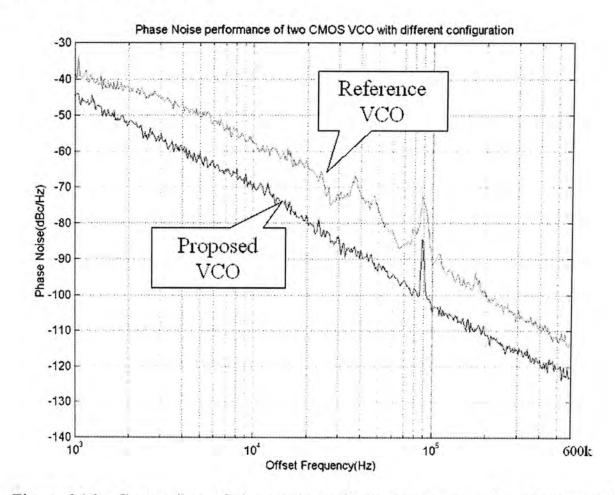

| 0.4              | 6.4.1 Phase Noise Performance                                                                      | 89       |

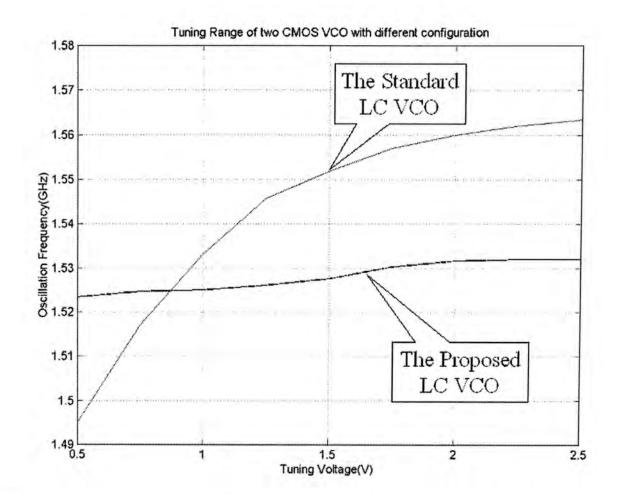

|                  | 6.4.2 Tuning Characteristic                                                                        | 90       |

| Chapter 7        | Conclusion and Future Work                                                                         | 02       |

| Chapter 7<br>7.1 | Conclusion                                                                                         | 93<br>93 |

| 7.2              | Future Work                                                                                        | 93<br>94 |

| References           | 9   |

|----------------------|-----|

| Author's Publication | 10  |

| Appendix A           | 10  |

| Appendix B           | 104 |

| Appendix C           | 100 |

X

# **Chapter 1** Introduction

### 1.1 Motivation

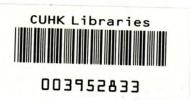

Figure 1.1 Block diagram of typical RF receiver

Oscillators are used at various places in an RF transceiver system. Figure 1.1 illustrates this with a block diagram of a superhet receiver. The local oscillator (LO) provides the mixer with a signal which is equal, in frequency, to the difference of the RF carrier and the intermediate frequency (IF). The LO is part of a phase locked loop (PLL), and uses a crystal oscillator as reference.

The LO in RF transceivers is often implemented using an LC oscillator with lumped LC resonator which can be on-chip or off-chip. Piezoelectric material is used in SAW (Surface Acoustic Wave) oscillators, which offers excellent spectral purity and also very good long-term frequency stability. Another example of a very stable resonator is a dielectric resonator (DR).

Recently, there has been considerable interest in monolithic integration of LC oscillators for highly integrated RF transceivers. Technologies such as Silicon CMOS and BiCMOS are of interest in light of the potential for integration with digital functions. In BiCMOS technologies, the bipolar device co-exists along with the MOS device on the same Si substrate. There are obvious advantages here: Since the RF system is usually implemented using bipolar transistors and the baseband subsystem is a complex digital CMOS system, the BiCMOS technology allows for the complete integration of a mobile communication system on a single chip. Disadvantages of BiCMOS technologies are the increased process cost compared to a simple CMOS process. Recent advances in CMOS technologies and in particular the continuous shrinkage in transistors' channel length, makes the MOS device comparable to the bipolar transistor in terms of speed of operation.

It is well known that the output power spectrum of an oscillator features a peak at oscillation frequency  $\omega_0$  and tails in both sidebands, decreasing as the frequency offset  $\alpha$  from  $\omega_0$ . Generally speaking, they are ascribed to the presence of noise sources in the circuit, and they are more precisely referred to as the oscillator phase noise.

The noise performance of an oscillator are quantitatively assessed by defining a suitable signal to noise ratio, i.e. the single sideband-to-carrier ratio (SSCR). This figure is the ratio between the output noise power in a 1-Hz bandwidth at the frequency offset  $\alpha$  from the carrier and the power of the carrier, and is usually expressed in dBc/Hz, i.e., decibels relative to the carrier. For instance the GSM standard asks for a SSCR of about –115dBc/Hz at 100kHz form the carrier frequency.

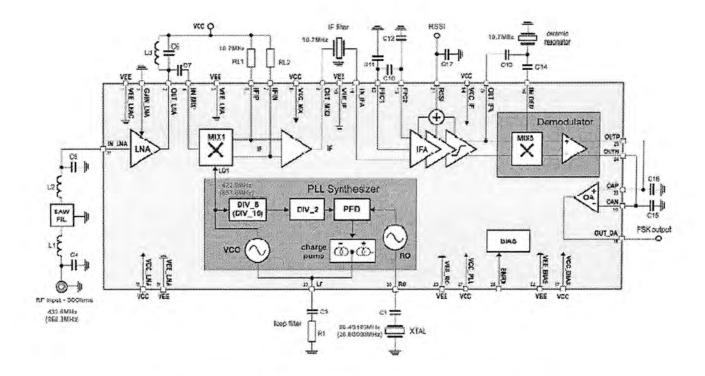

In realizing microwave oscillators, phase noise performance is usually the main concern. Suppose the receiver tunes to a weak desired signal in the presence of a strong interferer in an adjacent channel, as shown in Figure 1.2. If the local oscillator has large phase noise, the interfering signal will also be down-converted to almost the same intermediate frequency. The resulting interference will significantly degrade the dynamic range of the receiver. Note that a high Q resonator strongly reduces both the phase noise and power consumption of an oscillator.

Figure 1.2 Reciprocal Mixing

Conventionally, Resonant tanks in RF oscillators are usually implemented with high-quality discrete components located off-chip, often as small surface-mount parts. Alternatively, some oscillators have employed bonding wires as hybrid inductors. While bonding wires can offer a relatively high Q, they also suffer from large variation in inductance value. Monolithic inductors fabricated as single planar spirals are widely used on GaAs substrates with Qs in the range of 20-40. However, inductor Qs on standard Si substrates are much lower. The L of a monolithic inductor is defined solely by its geometry. Since modern photolithographic processes provide extremely tight geometric tolerances, monolithic inductors have very small variations in their performance. This is the main reason for the widespread efforts in the IC community to improve the quality of fully integrated inductors in silicon, especially in the last few years.

In addition, flicker noise is upconverted to  $\frac{1}{f^3}$  - shaped phase noise close to the carrier. When the oscillator is not carefully designed, flicker noise can deteriorate the phase noise at higher offset frequencies important for communication systems, e.g., 600kHz, by several dB. This is especially true in MOS VCO's because of the higher flicker noise of MOS transistors compared to bipolar transistors. It has been shown elsewhere that upconversion is highly dependent on the symmetry of the output waveform [21].

The aim of this work is to clarify how the noise sources of the electronic devices contribute to the output phase noise of the oscillator, thus giving some guidelines for the circuit optimization.

### 1.2 Objective

This research work is to investigate, both theoretically and experimentally, the design and optimization of low phase noise voltage-controlled oscillators fabricated using standard CMOS technology. New circuit topology is proposed which offers: (1) Resonator with enhanced quality factor; and (2) Reduction of noise up-conversion factor. This thesis is divided into seven chapters. Chapter 2 covers the background theories of oscillator design. In chapter 3, we introduce the fundamentals of the nonlinear analysis of the noise and we show that the nonlinear behavior of the transconductor causes a folding of the wide-band noise sources like the thermal noise of the transistor. Moreover, noise reduction techniques, particularly for the design of differential LC VCOs, are presented. Chapter 4 describes the CMOS technology adopted and addresses the issues of device modeling. Chapter 5 details the design and implementation of CMOS VCO circuits. Measured results such as phase noise and tuning characteristics are presented in chapter 6. Finally, chapter 7 concludes this thesis and provides recommendation for future work.

### Chapter 2 Theory of Oscillators

### 2.1 Oscillator Design

This chapter deals with the analysis and design of oscillators, or more specifically, the voltage controlled oscillators (VCOs). Beginning with a general study of oscillation in feedback systems, we introduce the LC differential oscillators along with methods of varying the frequency of oscillation.

### 2.1.1 Loop-Gain Method

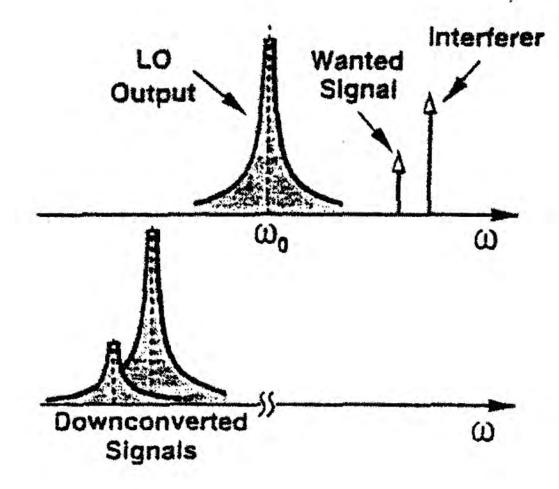

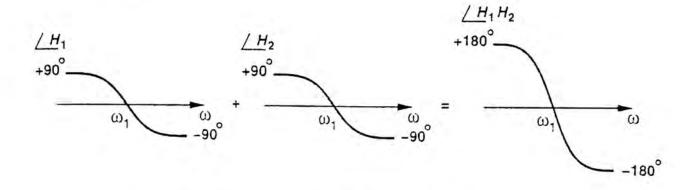

An oscillator is considered as an amplifier with feedback in the loop gain method. Figure 2.1 shows the block diagram representation which consists of an ideal amplifier with gain A, in cascaded with frequency selective networks characterized by transfer function  $H_1(f)$  and  $H_2(f)$ .

Figure 2.1 Block diagram of an amplifier with feedback

7

The overall transfer function of the feedback amplifier is given by equation 2.3.

$$\frac{V_o(s)}{V_i(s)} = \frac{A \times H_1(s)}{1 - A \times H_1(s) \times H_2(s)}$$

(2.3)

An oscillator is obtained when an output signal appears in the absence of an external input signal. This is possible only if the Barkhausen criteria[1] is satisfied:

$$|A \times H_1(j\omega) \times H_2(j\omega)| = 1$$

Phase  $[A \times H_1(j\omega) \times H_2(j\omega)] = 0$  (2.4)

It is the condition for steady state oscillation since it states that, at the frequency of oscillation, the signal must go around the loop with no attenuation and zero phase shift. In practice, due to the component tolerances and the non-linearity of the amplifier, the loop-gain value of the circuit must be greater than unity for startup of oscillation. Steady-state oscillation is reached when the signal amplitude is self-limited by the nonlinear nature of active devices. At this point, the loop-gain value equals unity and the Barkhausen criteria is met.

#### 2.1.2 Negative Resistance-Conductance Method

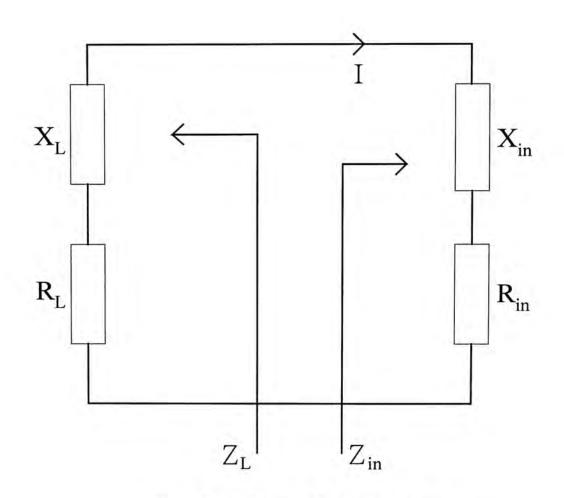

At microwave frequencies, Gunn diodes and IMPATT diodes are examples of device which exhibit negative resistance. Since a positive resistance dissipates power, it is reasonable to assume that a device which exhibits negative resistance could be used to generate an RF signal. With a potentially unstable transistor, a negative resistance can effectively be created by terminating the device with an impedance designed to drive it into the unstable region[1]. When a resonator is connected to a network exhibiting negative resistance, oscillation builds up until limiting reduces the net resistance to zero. Referring to Figure 2.2, for oscillation to occur, we have  $R_L + R_{in} = 0$  and  $X_L + X_{in} = 0$  (2.5)

Figure 2.2 Negative Resistance Circuit

In practice a value of  $R_L = |R_{in} / 3|$  is commonly used. During power on, any transient excitation or noise causes oscillation to build at frequency  $\omega_0$ . As the

current increases, the value of  $R_{in}$  becomes less negative until  $R_L + R_{in} = 0$ . The oscillator is now operating in a stable state.

### 2.1.3 Crossed-Coupled Oscillator

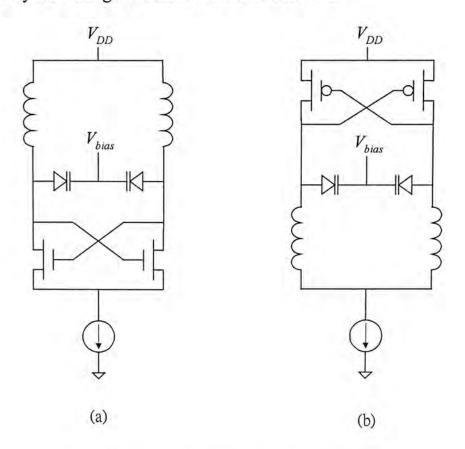

CMOS oscillators in today's technology are typically implemented as "ring oscillators" or "LC oscillators". As ring oscillators are very sensitive to noise in the switching thresholds and charging currents, it is a common practice to use LC oscillators for higher frequency stability and spectral purity. MOS differential voltage-controlled oscillator with integrated LC resonator[13], as shown in figure 2.4, are most widely used integrated oscillators in silicon ICs.

Figure 2.4 (a) NMOS VCO, (b) PMOS VCO

The above VCO use cross-coupled FETs to generate negative resistance so as to compensate for the loss of the LC tank and start-up oscillation. The current source at the bottom is used for controlling the current flowing through the cross-coupled FETs. A pair of inductors and varactors constitutes the LC tank.  $V_{bias}$  is used to control the biasing voltage of varactors, producing different capacitance value, and therefore to tune the oscillating frequency of the VCO circuits.

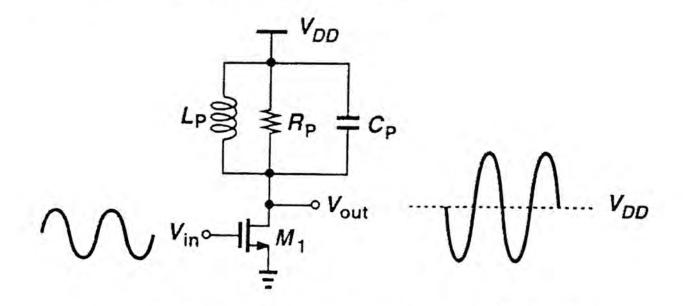

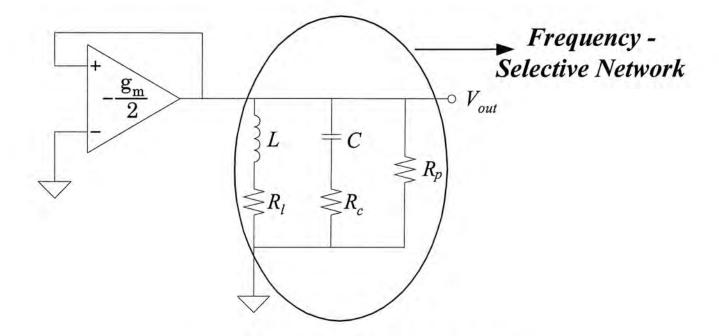

Consider another type of oscillator design, as shown in Figure 2.5, where an LC tank operates as the load. At resonance, the voltage gain should be equal to  $-g_{ml}R_p$  and  $jC_p\omega=1/(jL_p\omega)$ . When the circuit is biased at a drain current I<sub>1</sub> and small sinusoidal voltage at the resonance frequency is applied to the input. V<sub>out</sub> should be an inverted sinusoid with an average value near V<sub>DD</sub> [31].

Figure 2.5 Common-source configuration with parallel tank as load

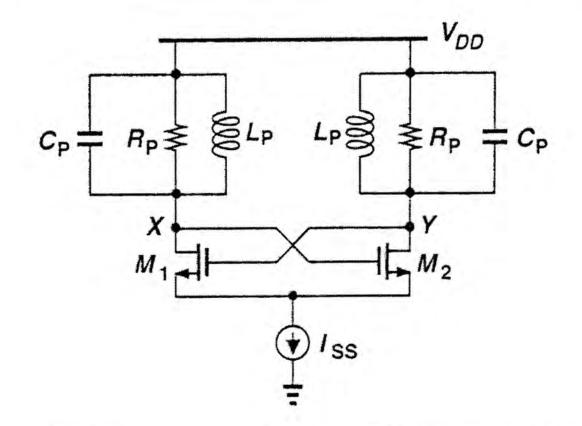

Figure 2.6 Two common-source configuration connected with positive feedback loop Suppose we place two circuit of Figure 2.5 in a cascade, as shown in Figure 2.6 [31]. Note that when  $(-g_{m1}R_p) \times (-g_{m2}R_p) > 1$ , then oscillation will take place. The output waveform of V<sub>X</sub> and V<sub>Y</sub> are differential in nature. Furthermore, at resonance, the total phase shift around the loop is zero because each stage contributes zero frequency –dependent phase shift, as illustrated in Figure 2.7.

Figure 2.7 Phase characteristics of the circuit shown in Figure 2.5

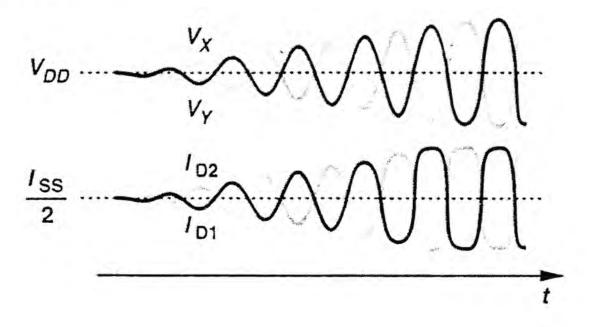

When we apply the supply voltage  $V_{DD}$  to the cross-coupled oscillator, then  $V_X = V_Y = V_{DD}$ , Two transistors share the tail current I<sub>SS</sub> equally. When  $(-g_{ml}R_p)$   $x (-g_{m2}R_p) > 1$ , noise components at the resonance frequency are continually amplified by M<sub>1</sub> and M<sub>2</sub>, allowing the oscillation to grow. The drain currents of both transistors vary according to the instantaneous value of  $V_X - V_Y[31]$ .

The oscillation amplitude will continue to grow until the voltage or current gain drops at the peaks. The voltage gain waveforms vary between zero and  $V_X$ -  $V_Y$  whereas current gain waveforms vary between zero and  $I_{SS}$ , as shown in Figure 2.8.

Figure 2.8 Transient response of V<sub>X</sub>, V<sub>Y</sub>, I<sub>D1</sub> and I<sub>D2</sub>

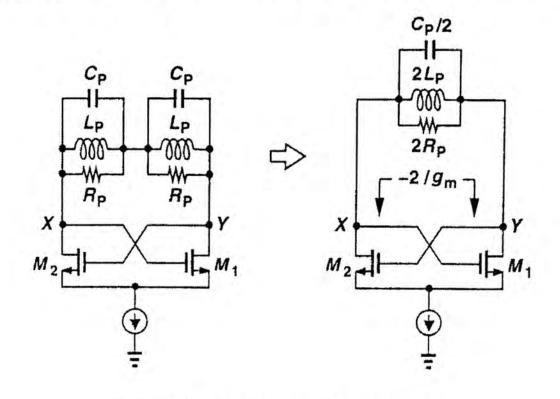

In analyzing this kind of oscillator, we can also merge two tanks into one, as shown in Figure 2.9. Note that the cross-coupled pair should provide a negative resistance of  $-R_P$  between nodes X and Y to enable oscillation. This resistance equals

to  $-2 / g_m$  [31]. That means it is necessary for  $R_P \ge 1 / g_m$  so as to start oscillation.

## Chapter 3 Noise Theory of Oscillators

The importance of oscillator phase noise in RF and other communication circuits has made it one of the most extensively studied subjects in electronics. Journal papers on the subject can be found from each of the last six decades. Experimentally, the qualitative behavior of phase noise has been well known. An oscillator's output power spectrum consists of a peak at the carrier frequency surrounded by a noise skirt symmetrical to the carrier frequency. Irrespective of the exact implementation, the noise skirt has the following characteristics:

- The noise spectral density is inversely proportional to the frequency offset from the carrier, except very close to the carrier frequency, where the influence of up-converted flicker noise dominates or the presence of the strong carrier begins to limit the measurement accuracy.

- The same noise manifests itself in the time domain as jitter around the oscillation's zero-crossing points, which can only be caused by noise in the phase of the oscillation rather than that super-imposed on its amplitude. Oscillator noise is therefore usually referred to as phase noise.

Today, RF oscillators are implemented with high-quality inductors and capacitors outside the chip containing the active devices. This is the main reason for the wide-spread efforts in the integrated circuit community to improve the quality of fully integrated inductors on silicon, especially in the last few years. Despite the avalanche of research papers, the quality factor Q of on-chip inductors at 1GHz has hardly improved by a factor of two (from  $Q \le 3$  to  $Q \le 6$ ) in the last 10 years. Reported phase noise level, however, vary by as much as 20dB at 100kHz offset. This underlines the fact that other factors than the Q of the tank also affect the oscillator phase noise strongly.

In this chapter, we will review typical existing phase noise models of oscillators. Finally, phase noise reduction techniques based on a new oscillator circuit topology is presented.

### 3.1 Origin of Noise Sources

#### 3.1.1 Flicker Noise

One of the sources of noise associated with solid-state devices, the amplitude of which varies inversely with frequency. It is also referred to as 1/f noise. The mathematical expression for flicker noise is [25],

$$\frac{\overline{i_n^2}}{\Delta f} = \Delta f \times \frac{Kg_m^2}{fWLC_{ox}^2}$$

(3.1)

where

K is Flicker noise parameter,

L and W are the effective channel length and width respectively,  $g_m$  is the transconductance of active device,

$C_{ox}$  is the intrinsic gate oxide capacitance of the active device.

For lower flicker noise generation, a large MOSFET device should be adopted since the gate capacitance of MOSFET smoothens the fluctuations in channel charge. The main drawback is the increased parasitic capacitance as the size of the device is enlarged.

### 3.1.2 Thermal Noise

In CMOS-type oscillator, the dominant thermal noise is contributed from the gate channel of FETs [25]. There are two mathematical expressions for channel thermal noise:

(3.2)

For long-channel device,

$$\frac{\overline{i_{nd}^2}}{\Delta f} = 4kT \,\gamma \,g_m$$

For short-channel device,

$$\frac{\overline{i_{nd}^2}}{\Delta f} = 4kT \frac{I_{bias}}{E_{sat}L}$$

where

k = Boltzman Constant

T = temperature in Kelvin

$\gamma = 0.67$  (long-channel devices)

= 2.5 (short-channel devices)

$I_{bias}$  = drain current of the FET

$E_{sat}$  = field strength

### 3.1.3 Noise Model of Varactor

Since a varactor can be modeled as a capacitor and a resistor connected in

series [26], hence, the noise power can be described by,

$$\frac{i_n^2}{\Delta f} = \frac{4kT}{R_{\rm var}}$$

(3.3)

where  $R_{var}$  equals the effective resistance in series with the capacitor.

### 3.1.4 Noise Model of Spiral Inductor

Spiral inductor can also be modeled as an inductor and a resistor connected in series[26] since the metal track of the spiral inductor introduces ohmic loss. The expression is shown below:

$$\frac{\overline{i_n^2}}{\Delta f} = \frac{4kT}{R_L}$$

(3.4)

where  $R_L$  equals the equivalent series resistance of the spiral inductor.

### 3.2 Derivation of Resonator

The most common definitions of quality factor Q are:

1.

$$Q = 2\pi \frac{\text{Energy Stored}}{\text{Energy Dissipated per Cycle}}$$

2.  $Q = \frac{\omega_o}{\Delta \omega}$

**3 dB**

$\Delta \omega$

$Q = \frac{\omega_o}{\Delta \omega}$

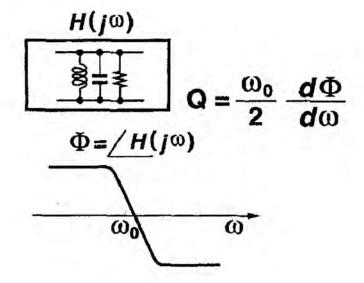

Figure 3.1 A definition of Q

3. For a simple LC shunt circuit (Figure 3.2):

$$Q=\frac{\omega_o}{2}\frac{\partial\Phi}{\partial\omega},$$

where  $\omega_o$  is the resonant frequency and  $\Phi$  denotes the phase response of the circuit admittance.

Figure 3.2 Another definition of Q

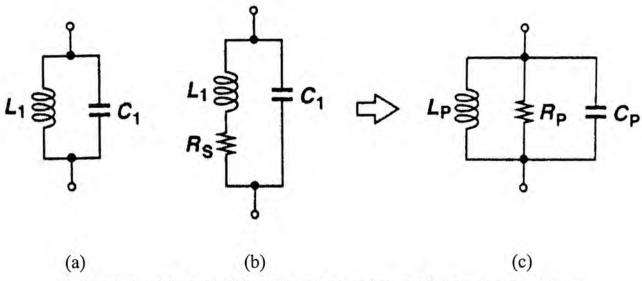

As shown in Figure 3.3(a), an inductor  $L_1$  placed in parallel with a capacitor  $C_1$  resonates at a frequency  $\omega_{res} = 1/\sqrt{L_1C_1}$ . We say the circuit has an infinite quality factor, Q. In practice, inductors (and capacitors) suffer from resistive components. For example, the series resistance of the metal wire used in the inductor can be modeled as shown in Fig. 3.3(b). We define the Q of the inductor as  $L_1 \omega / R_S$ . For this circuit, the reader can show that the equivalent impedance is given by

$$\left|Z_{eq}(s=j\omega)\right|^{2} = \frac{R_{s}^{2} + L_{1}^{2}\omega^{2}}{(1 - L_{1}C_{1}\omega^{2})^{2} + R_{s}^{2}C_{1}^{2}\omega^{2}}$$

(3.5)

20

Figure 3.3 (a) Ideal, (b) realistic LC tanks; and (c) equivalent circuit

That is, the impedance does not go to infinity at any  $s = j\omega$ . We say the circuit has a finite Q. For a narrow frequency range, it is possible to convert the circuit to the parallel configuration of Figure 3.3(c). Recall that  $L_1\omega/R_S = Q$ , a value typically greater than 3 for monolithic inductors. Thus, we have

$$L_p \approx L_1 \tag{3.6}$$

$$R_p \approx \frac{L_1^2 \omega^2}{R_s} \approx Q^2 R_s \tag{3.7}$$

The insight gained from the parallel combination is that at  $\omega_1 = 1/\sqrt{L_p C_p}$ , the tank reduces to a simple resistor; i.e., the phase difference between the voltage and current of the tank drops to zero. Note that the behavior is inductive for  $\omega < \omega_1$  and capacitive for  $\omega > \omega_1$ .

The Q defined in the preceding sections is a characteristic of the resonant circuit

itself, in the absence of any loading effects caused by external circuitry, and so is called the unloaded Q. In practice, however, a resonant circuit is invariably coupled to other circuitry, which will always have the effect of lowering the overall Q of the circuit.

### 3.3 Oscillator Phase Noise Model

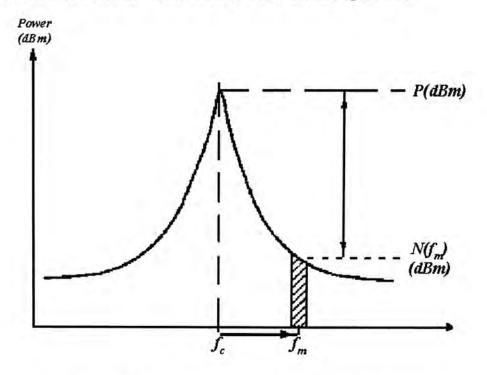

Any oscillator has noise sidebands at frequencies  $f_m$  offset from the carrier frequency. For increasing distance from the carrier the noise sidebands decay ultimately at 6dB/octave into the noise floor, as shown in Figure 3.4.

Figure 3.4 Single resonator oscillator spectrum

Thermal noise causes fluctuations in both amplitude and phase, usually denoted as AM noise and PM noise. However, all practical oscillators employ same form of amplitude limiting, as noted previously. Consequently, amplitude variations in real oscillators are attenuated and phase fluctuations dominate. Additionally, we are often more interested in how large this noise in relative to the carrier, rather than its absolute value:

$$L\{\Delta f\} = \frac{\text{Noise Power at }\Delta f \text{ offset with 1Hz Bandwidth}}{\text{Carrier Power}}$$

(3.8)

### 3.3.1 Leeson's Model

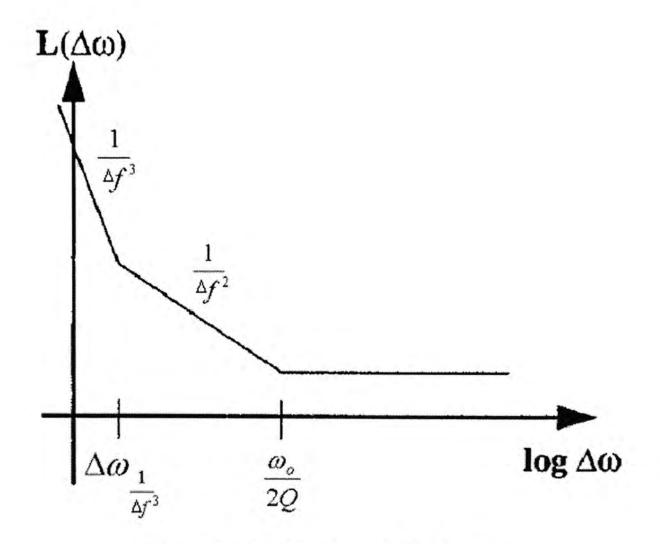

The most common phase noise model is proposed by Leeson [20]:

$$L(\Delta f) = \frac{1}{2} \frac{FkT}{C} \left[ \frac{1}{4Q^2} \left( \frac{f_o}{\Delta f} \right)^2 + 1 \right] \times \left( \frac{f_c}{\Delta f} + 1 \right)$$

(3.9)

where

Q is the quality factor of the resonator

F is an empirical parameter of noise figure

C is the output power of the oscillator

$f_o$  is the oscillation frequency

$\Delta f$  is the offset frequency

$f_c$  is the flicker noise corner of the oscillator

Equation (3.9) shows that the phase noise at a given offset improves as both the

carrier power and Q increase. Leeson's formula also includes the introduction of a factor F to account for the increased noise in the  $1/\Delta f^2$  region, an extra term of unity(inside the brackets) to account for the noise floor, and a multiplicative factor to provide a  $1/\Delta f^3$  behavior at small offset frequencies(Figure 3.5).

Figure 3.5 Phase Noise versus offset frequency

#### 3.3.2 J. Cranincks and M. Steyaert Noise Model [25]

J. Cranincks and M. Steyaert have developed a similar model for predicting the phase noise of oscillators. The expression is given by:

$$L\{\Delta f\} = 10\log\left\{\frac{kTR_{eff}[1+F]}{V_{\max}^2/2}\left(\frac{f_o}{\Delta f}\right)^2\right\}$$

(3.10)

F is a term that includes the excess noise of the oscillator's negative resistance,  $V_{max}$  is the differential output amplitude, and  $R_{eff}$  is the LC-tank's effective resistance, which is mainly determined by the inductor. The inductor's series resistance must be reduced so as to lower the phase noise as well as the power consumption. For mass production, fully integrated spiral inductors on silicon substrates without extra post-processing steps are required. The quality of these inductors is limited by the parasitic effects, such as skin effect, eddy currents in the substrate.

### 3.3.3 Non-linear Analysis of Phase Noise

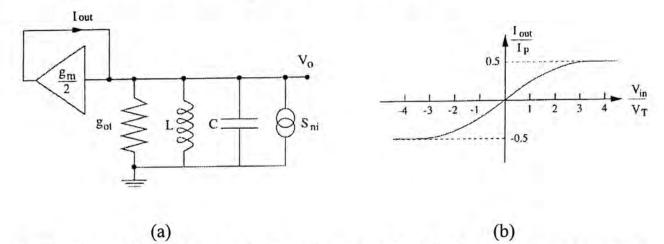

Figure 3.6 (a) Single-ended equivalent circuit with the current noise source accounting for the additive noise;

(b) The figure shows the I-V characteristics of the transconductor.

Figure 3.6 shows a single-ended equivalent of the oscillator. It is well known that in the small signal regime the cross-coupled pair features a negative resistance equal to  $-2 / g_m$ , where  $g_m$  is the transconductance of each transistor. The figure also shows the characteristic of the transconductor with the input and the output variables normalized to the thermal voltage  $V_T$  and to the tail current  $I_P$ , respectively. We denote with  $\omega_o = 1/\sqrt{LC}$  the central frequency of the bandpass loop filter, while the losses are represented by the equivalent conductance  $g_{ot}$  in parallel to the tank.

The self-sustaining oscillation occurs for  $\omega = \omega_0$ , and if the differential pair is driven well beyond the input linear range, the transconductor output current resembles a square wave at  $\omega_0$ . However, the harmonic component at  $\omega_0$  is the only component of the signal passing through the loop filter. If Q is high enough all the other harmonic components are cut-off. Therefore the transconductor transfer may be quantitatively characterized by introducing an effective transconductance  $g_{meff}$ , given by the ratio between the output current component at  $\omega_o$  and the input voltage amplitude at the same frequency. If the amplitude of the voltage signal is small, the effective transconductance is coincident with the small signal parameter  $g_m / 2 = I_p /$  $4V_T$ . As the input amplitude  $A_o$  increases beyond the input linear range, the effective transconductance decreases below  $g_m / 2$  and in the hard limiting regime, when the current output waveform is a square wave, it approaches the value  $g_{meff} = 2I_p / \pi A_o$ .

Finally, we remind that the oscillation is self-sustaining when the loop gain at  $\omega_0$  is equal to one, i.e.,  $g_{meff} / g_{ot} = 1$ . This means that the losses,  $g_{ot}$ , are perfectly balanced by the transconductance of the positively fed back transconductor and the tank reduces to a parallel connection between the inductor and the capacitor.

The noise spectral density of the output voltage,  $S_{nv}$ , is usually estimated by representing the overall circuit noise with a current noise source  $S_{ni}$  in parallel to the tank. This noise is usually referred to as additive noise. The current noise generator forces an impedance  $Z(\omega)$  given by the parallel of L and C. By taking  $\alpha$  as the frequency offset from  $\omega_0$ , for  $\alpha \ll \omega_0$ , we may write

Chapter 3 Noise Analysis

$$\left|Z(\omega_o \pm \alpha)\right|^2 \approx \frac{1}{\left(2\alpha C\right)^2} \tag{3.11}$$

Thus,

$$S_{n\nu}(\alpha) = \frac{S_{ni}}{\left(2\alpha C\right)^2} = \frac{1}{4} \frac{S_{ni}}{g_{ot}C} \frac{\omega_o}{Q} \frac{1}{\alpha^2}$$

(3.12)

Due to the sharp resonance of the LC network, the output spectrum shows tails decreasing from  $\omega_o$  as  $\alpha^2$ .

A first contribution to  $S_{ni}$  arises from the thermal noise  $2kTg_{ot}$  of the ohmic parasitics of the loop filter. In other terms, the equivalent conductance  $g_{ot}$  appears not only into the quality factor of the filter, but it also accounts for the thermal noise due to the parasitic resistances of the tank. The noise of the transconductor may be instead represented by adding a current spectral density  $2kTg_{ot}F$ , where F is a suitable noise factor. Therefore we have  $S_{ni} = 2kTg_{ot}(1+F)$ , the output voltage noise may be written as

$$S_{n\nu}(\alpha) = \frac{1}{2} \frac{kT}{C} \frac{\omega_o}{Q} \frac{1}{\alpha^2} (1+F)$$

(3.13)

All the difficulty of the noise calculations is now hidden within F, the noise factor of the differential stage.

For totally uncorrelated noise one half of the total noise power contributes to the AM and the other half gives a PM. If  $A_0 \gg 2V_T$ , the differential stage behaves as a

hard limiter and only the PM component is transmitted to the output. It follows that the noise power spectral density, must be divided by a factor 2, thus obtaining

$$S_{nv}(\alpha) = \frac{1}{4} \frac{kT}{C} \frac{\omega_o}{Q} \frac{1}{\alpha^2} (1+F)$$

(3.14)

However, the nonlinear behavior of the stage has an impact larger than the simple introduction of the above factor 2. We will show in the following that intermodulations between the carrier and wide-band noise sources cause noise folding that increases the transconductor noise factor F.

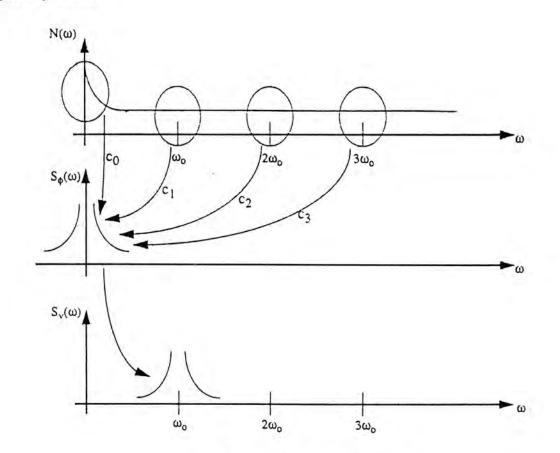

Figure 3.7 Single-ended equivalent circuit

The solution can be found analytically [23] when the transconductor behaves as a hard limiter. Each noise component,  $I_n$ , is delivered to the tank via the switching transconductor, i.e. multiplied by a square wave T(t) with a frequency  $\omega_0$ . We have

$$\left(\frac{\bar{I}_n}{2}e^{j\omega t} + \frac{\bar{I}_n^*}{2}e^{-j\omega t}\right) \sum_{n=-\infty}^{+\infty} T^{(2n+1)}e^{j(2n+1)\omega_o t}$$

(3.15)

where  $\overline{I}_n$  is the generic noise tone,  $T^{(2n+1)} = e^{jn\pi} / \pi(2n+1)$ , and  $T^{(2n+1)} = T^{-(2n+1)}$ . It

turns out that the noise tones  $I_{u}$  and  $I_{l}$ , at frequency  $\omega_{o} \pm \alpha$ , are due to the noise components around the even harmonics of  $\omega_{o}$ , i.e.  $2n\omega_{o} \pm \alpha$ . Analytically we have

$$\begin{bmatrix} \bar{I}_{l}^{*}/2\\ \bar{I}_{u}/2 \end{bmatrix} = \begin{bmatrix} T^{(-1)} & T^{(1)} & T^{(-3)} & \cdots\\ T^{(1)} & T^{(3)} & T^{(-1)} & \cdots \end{bmatrix} \begin{bmatrix} \bar{I}_{n}(\alpha)/2\\ \bar{I}_{n}^{*}(2\omega_{o}-\alpha)/2\\ \bar{I}_{n}(2\omega_{o}+\alpha)/2\\ \bar{I}_{n}^{*}(4\omega_{o}-\alpha)/2\\ \cdots \end{bmatrix}$$

(3.16)

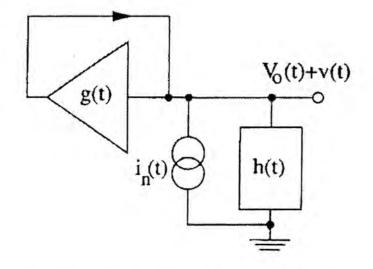

In reality the folding factor will depend on both the I(V) characteristic of the transconductor and its bandwidth. The transconductor output noise spectrum is obtained from the convolution between these delta functions and the wideband noise (Figure 3.8). The convolution gives rise to a noise folding, similar to what happens in sampled systems.

Figure 3.8 Evolution of noise

## 3.3.4 Flicker-Noise Upconversion Mechanism

Compared to bipolar transistors, MOS transistor generates more flicker noise. In oscillator, flicker noise is upconverted to  $1/f^3$  phase noise. Consequently, the  $1/f^3$  phase noise will be much higher in MOS oscillators than in bipolar oscillators and becomes an effect that has to be taken into account.

The mechanism of flicker-noise upconversion can be examined as follows. Flicker noise from the tail current source that enters the LC-tank will be upconverted due to the mixing action of the VCO circuit. Additionally, when the single differential oscillator circuit is unbalanced, the common-mode node of the current source will oscillate at twice the oscillator center frequency,  $2\omega_{o}$ , because the current source will be pulled every time one of the NMOS transistors switches on. Through channel length modulation, the noise of the trail current source is upconverted to  $2\omega_0$ . The upconverted noise enters the LC-tank and is mixed with the fundamental oscillator frequency, resulting in phase-noise sidebands at the oscillator frequency. Therefore, to minimize the upconversion of flicker noise from the tail current source, all even harmonics must be suppressed, meaning that the circuit must be as symmetric as possible. Odd harmonics have little importance for flicker-noise upconversion because they do not affect the symmetry, and noise at odd harmonics

does not result in sidebands around the fundamental frequency when mixed. Flicker noise from the tail current source will be the main contributor to  $1/f^3$  phase noise. Flicker noise is correlated noise and can only exist in systems with memory. When transistors are ideally switched, all memory and consequently the flicker noise is removed. When the switching is not ideal, a small amount of the NMOS transistor flicker noise will be upconverted.

In some oscillator designs, the main source of upconverted flicker noise is the current source. Therefore, a PMOS transistor was chosen for the tail current source because of its inherently lower flicker noise (approximately 10dB), compared to NMOS transistors. The area of the PMOS transistor is increased, by designing the transistor length larger than the minimum length, to further minimize the flicker-noise contribution. Additional circuit techniques have also been reported to further minimize the flicker-noise upconversion. A capacitance and a cascode transistor are added to the common-mode node of the tail current source to suppress all common-mode node variations. As a result, noise upconversion due to channel length modulation by higher (and especially the second) order harmonics is suppressed.

# 3.4 Phase Noise Reduction Techniques

As mentioned previously, the phase noise associated with a VCO is determined by:

(a) Q factor of the resonator

(b) Q factor of the varactor diode

(c) effective noise factor of the active devices used

(d) power supply noise

(e) external tuning voltage supply noise

The noise contribution made by (d) and (e) can be minimized by careful choice of the power supplies. The phase noise of the VCO is therefore governed primarily by the overall Q of the circuit, and the noise up-conversion factor.

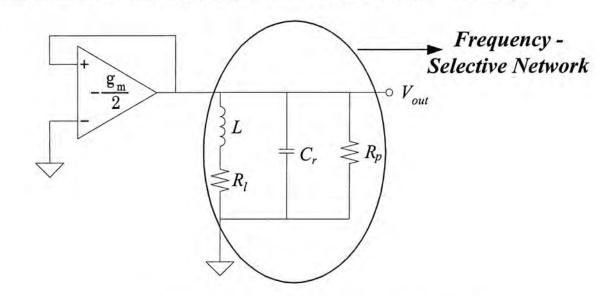

#### 3.4.1 Conventional Tank Circuit Structure

As stated in the previous sections, the standard NMOS cross-coupled differential oscillators with symmetrical structure can be transformed into a single-sided equivalent circuit, as shown in Figure 3.9. Differential topologies are advantageous in integrated circuit because they offer common-mode rejection. Therefore, differential circuits are less susceptible to supply noise present in on-chip power rails. Differential VCO topologies also avoid the need for single-ended to

differential conversion circuitry for the LO drive of a Gilbert-cell mixer.

Figure 3.9 Single-sided equivalent circuit

The frequency-selective network can be transformed into an LC tank network

with parallel loss only (Figure 3.10):

$$\frac{1}{R_{p,total}} = \frac{1}{R_l(Q_l^2 + 1)} + \frac{1}{R_p}$$

(3.17)

where  $Q_l = \frac{\omega L}{R_l}$

Figure 3.10 The resonator of single-sided equivalent circuit

Subsequently, the overall Q of the resonator can be derived as follows:

$$Y_{in} = j\omega C_r + \frac{1}{j\omega L_r} + \frac{1}{R_{p,total}}$$

$$\Rightarrow \phi = \tan^{-1} \left[ \omega R_{p,total} \left( C_r - \frac{1}{\omega^2 L_r} \right) \right]$$

$$\Rightarrow \frac{\partial \phi}{\partial \omega} \Big|_{\omega = \omega_o} = 2R_{p,total} C_r$$

By using  $Q_L = \frac{\omega_o}{2} \frac{\partial \phi}{\partial \omega} \Big|_{\omega = \omega_o}$

$$\Rightarrow \quad Q_L = \omega_o R_{p,total} C_r \tag{3.18}$$

# 3.4.2 Enhanced Q Tank Circuit Structure

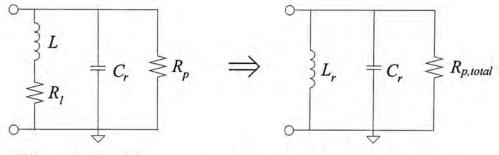

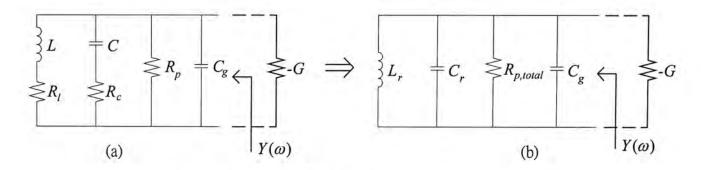

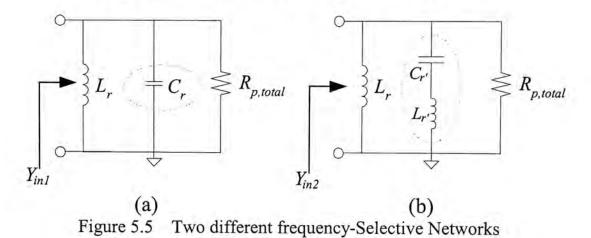

Figure 3.11 Two different frequency-selective networks

Assuming that the two resonant circuits shown in Figure 3.11 exhibit the same

resonant frequency, then the relationship between the element values is given by,

$$C_r = \frac{1}{\omega_o^2 L_r} \tag{3.19}$$

$$C_{r'} = \frac{C_r}{1 + \omega_o^2 L_{r'} C_r}$$

(3.20)

35

As a result, the loaded quality factor of circuit(b) can be derived as:

$$Y_{in2} = \frac{1}{\frac{1}{j\omega C_{r'}} + j\omega L_{r'}} + \frac{1}{j\omega L_r} + \frac{1}{R_{p,total}}$$

(3.21)

$$\Rightarrow \phi = \tan^{-1} \left[ R_{p,total} \times \left( \frac{\omega C_{r'}}{1 - \omega^2 L_{r'} C_{r'}} - \frac{1}{\omega L_r} \right) \right]$$

$$\Rightarrow \frac{\partial \phi}{\partial \omega} \Big|_{\omega = \omega_o} = 2R_{p,total} C_r + 2\omega_o^2 C_r^2 L_{r'} R_{p,total} = 2R_{p,total} C_r \left( \frac{C_r}{C_{r'}} \right)$$

(3.22)

Thus,

$$Q_{L} = \frac{\omega_{o}}{2} \frac{\partial \phi}{\partial \omega} \bigg|_{\omega = \omega_{o}} = \omega_{o} R_{p, total} C_{r} \bigg( \frac{C_{r}}{C_{r'}} \bigg)$$

Since the value of  $C_r$  is always larger than  $C_{r^\prime}$  and thus, the loaded Q of circuit(b) is always larger than the loaded Q of circuit(a). Subsequently, we can define the noise reduction factor (NRF) as,

$$NRF = 10\log\left\{\frac{Phase \ noise \ of \ circuit(a)}{Phase \ noise \ of \ circuit(b)}\right\} \approx 20\log\frac{Q_{L,b}}{Q_{L,a}}$$

$$\approx 20\log\frac{C_r}{C_{r'}}$$

(3.23)

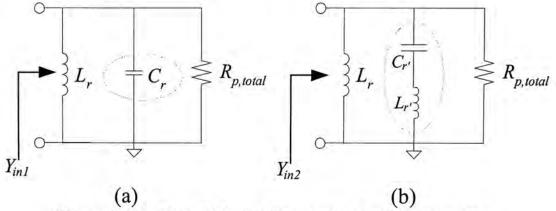

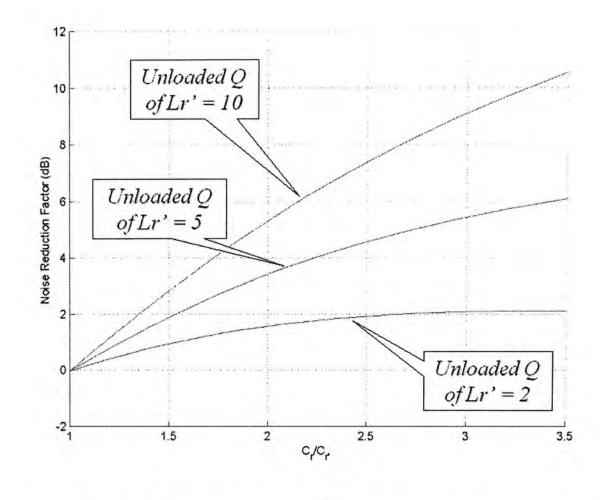

For illustration, the noise reduction performance of the proposed tank structure

versus  $\frac{C_r}{C_{r'}}$  is plotted in Fig 3.12. It indicates that a larger value of  $\frac{C_r}{C_{r'}}$  is desirable for better phase noise improvement. However, in practice, the adoption of a smaller capacitance  $C_{r'}$  leads to a higher inductance value  $(L_{r'})$  and inductor series resistance, which limits the highest attainable Q factor of the tank circuit.

Figure 3.12 Predicted noise reduction performance of the proposed VCO Circuit

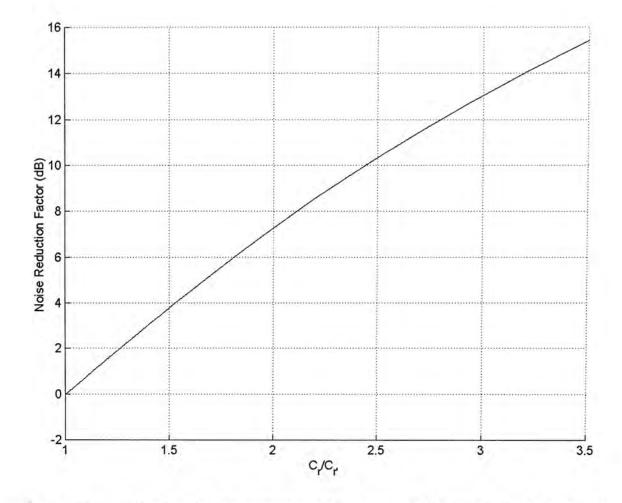

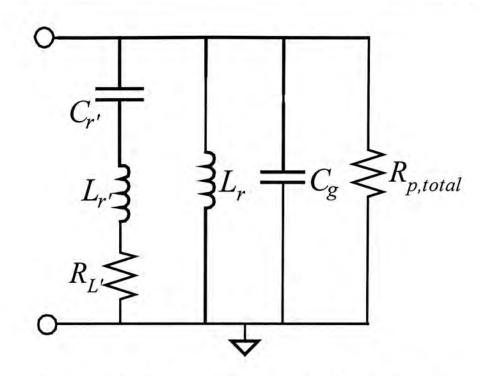

# 3.4.3 Tank Circuit with parasitics

Figure 3.13 shows the equivalent circuit of the modified tank circuit with parasitics such as inductor loss resistance  $R_{L'}$  and gate capacitance  $C_g$  of the FET.

Figure 3.13 Enhanced Q resonant tank with parasitics

The input admittance of the LC tank is given as,

$$Y_{in} = \frac{1}{\frac{1}{j\omega C_{r'}} + j\omega L_{r'} + R_{L'}} + \frac{1}{j\omega L_{r}} + j\omega C_{g} + \frac{1}{R_{p,total}}$$

$$\Rightarrow \phi = \tan^{-1} \left[ -\frac{Z_{L}}{L_{r}} \left( \frac{1 - \omega^{2}C_{g}L_{r}}{\omega} + \frac{\omega^{2}L_{r}L_{r'} - \frac{L_{r}}{C_{r'}} - R_{p,total}R_{L'}(1 - \omega^{2}C_{g}L_{r})}{\omega \left( R_{L'}^{2} + \left( \omega L_{r'} - \frac{1}{\omega C_{r'}} \right)^{2} + R_{p,total}R_{L'} \right)} \right]$$

By using the formula,  $Q_L = \frac{\omega_o}{2} \frac{\partial \phi}{\partial \omega}\Big|_{\omega = \omega_o}$ , the variation of  $Q_L$  versus

$\frac{C_r}{C_{r'}}$  is plotted in Figure 3.14. The results indicate that the noise reduction

factor deteriorates as the unloaded Q value of the inductor decreases.

Figure 3.14 Noise Reduction Factor versus  $\frac{C_r}{C_{r'}}$ , as a function of unloaded inductor Q

# 3.4.4 Reduction of Second-Harmonic Induced Up-converted Noise

In section 5.3, we have discussed the transfer of the noise sources in a differential LC tuned oscillator. We have shown that the nonlinear operation of the transconductor stage has to be properly accounted for since it introduces spectrum folding.

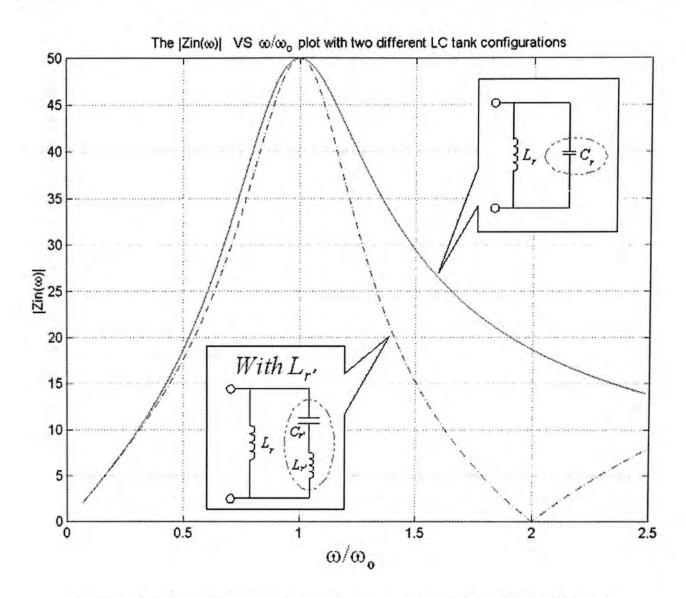

When an inductor is connected in series with the capacitor in the LC tank

(Figure 3.11), a transmission zero is introduced at a frequency given by,

$$\omega_z = \sqrt{\frac{1}{L_{r'}C_{r'}}} \tag{3.24}$$

Therefore, for the suppression of the second harmonic component, we have,

$$\omega_z = \sqrt{\frac{1}{L_{r'}C_{r'}}} = 2\omega_o \tag{3.25}$$

Combining equation (3.20) and (3.25), we get,

$$C_{r} = \frac{C_{r'}}{1 - \omega_{o}^{2} L_{r'} C_{r'}} = \frac{C_{r'}}{1 - \frac{1}{4}} = \frac{4}{3} C_{r'}$$

(3.26)

Figure 3.15 shows the plot of input impedance variations of circuit (a) and (b) as

a function of normalized frequency. It can be seen from the diagram that a short-circuit is present at the second harmonic.

Figure 3.15 Variation of Input impedance versus frequency of LC tank circuits

# Chapter 4 CMOS Device Modeling

At the dawn of its fifth decade, the semiconductor industry continues to grow at an amazing pace. High-speed and low-power CMOS integrated circuits (IC) are used in an ever expanding trend. Thus, a critical part of this technology is high-quality circuit design. In this project, all oscillators are implemented with AMS CUP 0.6 micron process technology. These oscillators are fully integrated with planar spiral inductors. This chapter describes the corresponding technologies in designing the oscillator circuits, particularly the development of device model for FET, inductor as well as varactor in CMOS process.

# 4.1 Device Modeling

#### 4.1.1 FET model

Circuit simulator is an essential tool in designing integrated circuits. The accuracy of circuit simulation highly depends on the types of transistor model used. Reduction in transistor size continually complicates the device physics and makes device modeling more challenging and sophisticated. BSIM3v3 (BSIM stands for Berkeley Short-channel IGFET Model) was selected as the industrial MOSFET model by many leading companies in the semiconductor industry such as Cadence design Systems, Hewlett Packard, Mentor Graphics, ...etc. It is a model developed by the BSIM Research Group in UC Berkeley. Details of this model can be found in the following website: http://www-device.eecs.berkeley.edu/~bsim3

This model explicitly takes into account the effects of many physical and process variables for good device scalability and predictability. The short channel and narrow width effects as well as high-field effects are well modeled. The minimum channel length that can be modeled is 0.15 micron.

| NMOS                                        | PMOS                                          |

|---------------------------------------------|-----------------------------------------------|

| *model = bsim3v3                            | *model = bsim3v3                              |

| *Berkeley Spice Compatibility               | *Berkeley Spice Compatibility                 |

| * Lmin= .35 Lmax= 20 Wmin= .6 Wmax= 20      | * Lmin= .35 Lmax= 20 Wmin= .6 Wmax= 20        |

| .model N1 NMOS                              | .model P1 PMOS                                |

| +Level= 8                                   | +Level= 8                                     |

| +Tnom=27.0                                  | +Tnom=27.0                                    |

| +Nch= 2.498E+17 Tox=9E-09 Xj=1.00000E-07    | +Nch= 3.533024E+17 Tox=9E-09 Xj=1.00000E-07   |

| +Lint=9.36e-8 Wint=1.47e-7                  | +Lint=6.23e-8 Wint=1.22e-7                    |

| +Vth0= .6322 K1= .756 K2= -3.83e-2 K        | 3=+Vth0=6732829 K1= .8362093 K2=-8.606622E-02 |

| -2.612                                      | K3= 1.82                                      |

| +Dvt0= 2.812 Dvt1= 0.462 Dvt2=-9.17e-2      | +Dvt0= 1.903801 Dvt1= .5333922 Dvt2=1862677   |

| +Nlx= 3.52291E-08 W0= 1.163e-6              | +Nlx= 1.28e-8 W0= 2.1e-6                      |

| +K3b= 2.233                                 | +K3b= -0.24 Prwg=-0.001 Prwb=-0.323           |

| +Vsat= 86301.58 Ua= 6.47e-9 Ub= 4.23e-      | 18 +Vsat= 103503.2 Ua= 1.39995E-09 Ub= 1.e-19 |

| Uc=-4.706281E-11                            | Uc=-2.73e-11                                  |

| +Rdsw= 650 U0= 388.3203 wr=1                | + Rdsw= 460 U0= 138.7609                      |

| +A0= .3496967 Ags=.1 B0=0.546 B1= 1         | +A0= .4716551 Ags=0.12                        |

| + Dwg = -6.0E-09 Dwb = -3.56E-09 Prwb =213  | +Keta=-1.871516E-03 A1= .3417965 A2= 0.83     |

| +Keta=-3.605872E-02 A1= 2.778747E-02 A2= .9 | +Voff=074182 NFactor= 1.54389                 |

The list below shows the typical SPICE circuit netlists of BSIM3v3 model.

| +Voff=-6.735529E-02 NFactor= 1.139926 Ci     | t= Cit=-1.015667E-03                       |

|----------------------------------------------|--------------------------------------------|

| 1.622527E-04                                 | +Cdsc= 8.937517E-04                        |

| +Cdsc=-2.147181E-05                          | +Cdscb= 1.45e-4 Cdscd=1.04e-4              |

| +Cdscb= 0 $Dvt0w = 0 Dvt1w = 0 Dvt2w = 0$    | + Dvt0w=0.232 Dvt1w=4.5e6 Dvt2w=-0.0023    |

| + Cdscd = 0 Prwg = 0                         | +Eta0= 6.024776E-02 Etab=-4.64593E-03      |

| +Eta0= 1.0281729E-02 Etab=-5.042203E-03      | +Dsub= .23222404                           |

| +Dsub= .31871233                             | +Pclm= .989 Pdiblc1= 2.07418E-02 Pdiblc2=  |

| +Pclm= 1.114846 Pdiblc1= 2.45357E-03 Pdiblc2 | = 1.33813E-3                               |

| 6.406289E-03                                 | +Drout=.3222404 Pscbe1=118000 Pscbe2=1E-09 |

| +Drout= .31871233 Pscbe1= 5000000 Pscbe2     | = +Pvag = 0                                |

| 5E-09 Pdiblcb =234                           | +kt1 = -0.25 $kt2 = -0.032$ prt=64.5       |

| +Pvag= 0 delta=0.01                          | +At= 33000                                 |

| + Wl = 0 Ww = -1.420242E-09 Wwl = 0          | +Ute= -1.5                                 |

| + Wln = 0 Wwn = .2613948 Ll = 1.300902E-10   | +Ua1= 4.312e-9 Ub1= 6.65e-19 Uc1= 0        |

| + Lw = 0 Lwl = 0 Lln = .316394               | +Kt11=0                                    |

| + Lwn = 0                                    |                                            |

| +kt1=3 kt2=051                               |                                            |

| +At= 22400                                   |                                            |

| +Ute=-1.48                                   |                                            |

| +Ua1= 3.31E-10 Ub1= 2.61E-19 Uc1= -3.42e-10  |                                            |

| +Kt11=0 Prt=764.3                            |                                            |

Nowadays, as transistors were scaled to submicron dimensions, it became increasingly more difficult to introduce physically meaningful equations that would be both accurate and computationally efficient. BSIM adopted a different approach: numerous empirical parameters were added in order to simplify the equations. A feature of BSIM is the addition of a simple equation to represent the geometry dependences of many device parameters. For example:

$$P = P_o + \frac{\alpha_P}{L_{eff}} + \frac{\beta_P}{W_{eff}}$$

where  $P_o$  is the value of empirical parameter of a long, wide transistor,  $\alpha_p$  and  $\beta_p$  are fitting factors. BSIM model has three generations. Each generation has some special features. They are:

#### BSIMv1:

- Using approximately 50 parameters;

- Dependence of mobility upon the vertical field includes the substrate voltage;

- Currents in the weak and strong inversion regions are derived such that their values and first derivatives are continuous;

- Simplify the drain current equations, new expressions are devised for velocity saturation, dependence of mobility upon the lateral field, and the saturation voltage.

#### BSIMv2:

- Using approximately 70 parameters;

- Employs new expressions for mobility, drain current, and subthreshold conduction;

- Suffers from large errors in the triode region for short, narrow transistors

#### BSIMv3:

- Using approximately 180 parameters;

- Returns to the physical principles of device operation while maintaining many of the useful features of BSIM and BSIM2.

- Provides reasonable accuracy for subthreshold and strong inversion operation while still suffering from large errors in predicting the output impedance for short channel length FET.

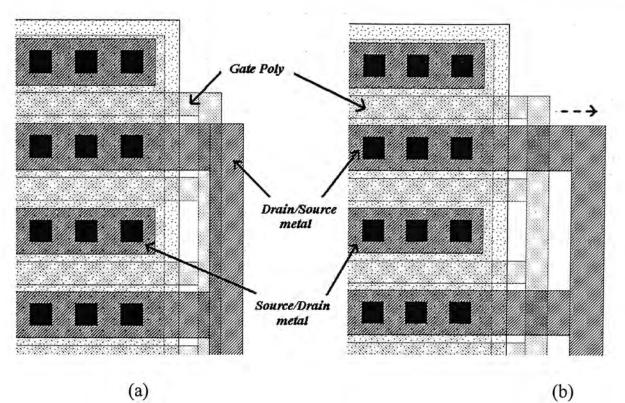

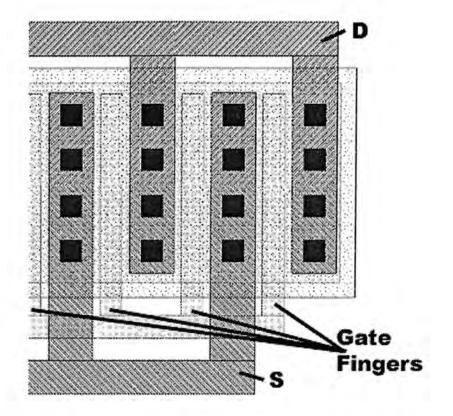

# 4.1.2 Layout of Interdigitated FET

In designing multi-finger FETs, as in figure 7.1(a), the overlapping of Drain/Source metal to gate poly will generate more parasitic loss. Figure 4.1(b) shows a common practice to move the Drain/Source metal trace far apart from the gate poly, to get rid of parasitic capacitance.

Figure 4.1 Minimize gate poly-to-drain/source metal capacitance

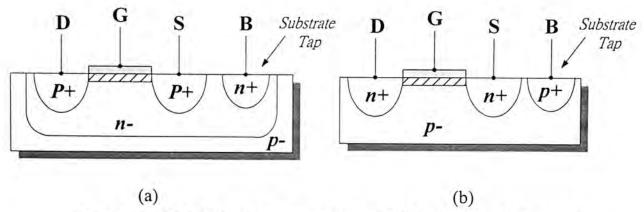

Furthermore, for the proper operation of FETs in CMOS process, it is necessary to provide a substrate tap. In Figure 7.2 shows the example of adding substrate tap to NMOS and PMOS. In order to eliminate the bulk resistance of the FETs, extra substrate taps should be placed close to the FETs.

Figure 4.2(a) NMOS with substrate tap, (b) PMOS with substrate tap

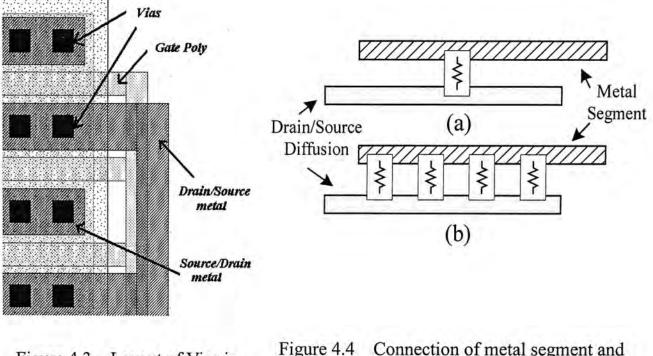

Moreover, vias are needed to connect the source/drain diffusion region to the metal segment (Figure 4.3). As a rule of thumb, via are added at equal distance to reduce the internal resistance associated with the interconnect, as depicted in Figure 4.4.

Figure 4.3 Layout of Vias in FETs

re 4.4 Connection of metal segment and drain/source diffusion with (a) a via, (b) four vias

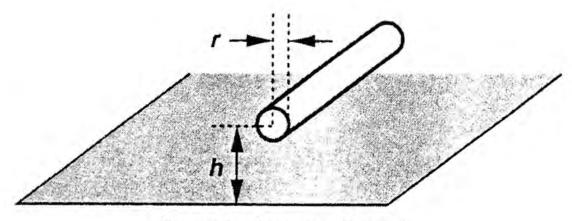

#### 4.1.3 Planar Inductor

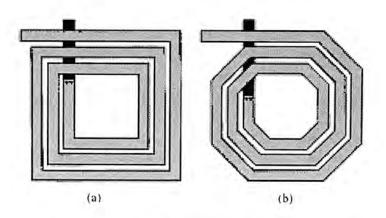

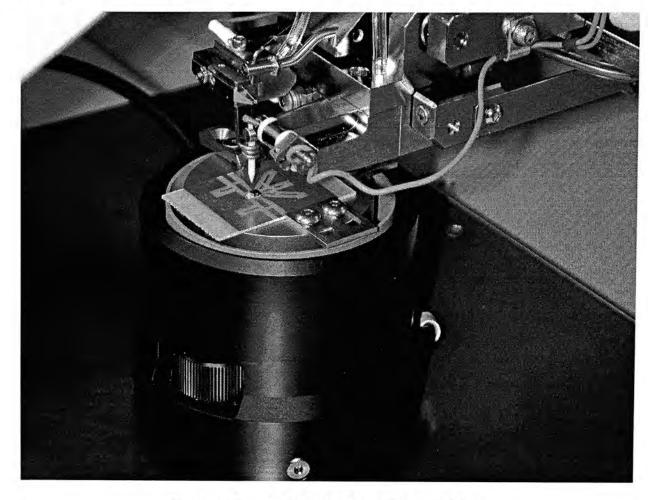

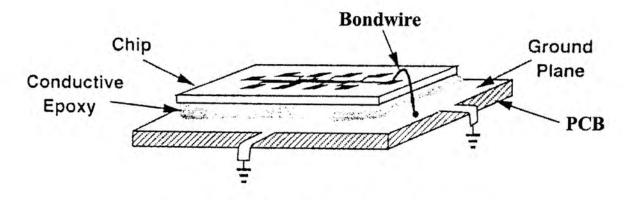

Recently, bonding wire is used as inductor in CMOS process due to its low series resistance. A typical use of bonding wire is to connect the bond pad on top of the wafer die to the lead of the package or to another bond pad. Unfortunately, these hybrid inductors suffer from large variations in inductance value due to manufacturing tolerances. Monolithic inductors fabricated as simple spirals on Si substrate, are often associated with lower Q factor due to resistive loss and substrate loss. The inductance of a monolithic inductor is defined solely by its geometry. Since modern photolithographic processes provide extremely tight geometric tolerances, monolithic inductors have very small variations in their performance. There are many ways to layout a planar spiral inductor. The optimum structure is a circular spiral. This structure places the largest amount of conductors in the smallest possible area, reducing the series resistance of the spiral. This structure, however, is often not used because it is not supported by many mask generation systems. For the CMOS process used here, the standard square spiral structure are recommended, as shown in Figure 4.5(a).

Figure 4.5 Spiral Inductor Layout: (a)square and (b)octagonal.

The total inductance value of the spiral can be computed by using Greenhouse's method [17]. Basically, the spiral square inductor is split up into sections consisting of straight conductors, and the self-inductance of the sections is calculated and summed.

#### 4.1.4 Circuit Model of Planar Inductor

The self-inductance for a straight conductor is,

$$L = 0.0021 \left[ ln \left( \frac{21}{GMD} \right) - 1.25 + \frac{AMD}{1} + \left( \frac{\mu}{4} \right) \Gamma \right]$$

(4.1)

where L is the self-inductance in  $\mu$ H, l is the conductor length in cm, m is the conductor permeability, and T is the frequency correction parameter.

Geometric Mean Distance (GMD) is the distance between two infinitely thin imaginary filaments whose mutual inductance is equal to the mutual inductance between the two original conductors. The GMD is equal to 0.44705 times a side in the case of a square cross section.

Arithmetic Mean Distance (AMD) is the average of all the distances between the points of one conductor and the points of another. For a single conductor, the arithmetic mean distance is the average of all possible distances within the cross section.

If the top layer of metal is used for the layout of the spiral inductor, we can consider it as a thin-film inductor with rectangular cross section. Thus, equation(4.1) can be simplified as,

$$L = 0.0021 \left[ ln \left( \frac{21}{a+b} \right) + 0.50049 + \frac{a+b}{31} \right]$$

(4.2)

where a, b are the rectangular dimension of the cross section. The magnetic permeability m is 1, and the skin-depth phenomenon has little effect on thin film, T is an empirical parameter, which should be considered to have a value of 1 for

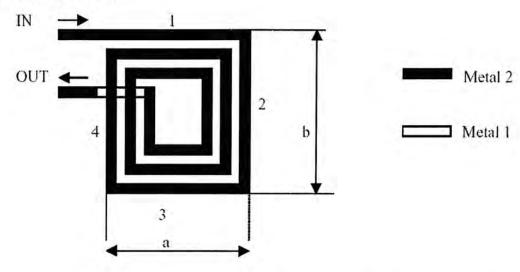

Figure 4.6 Layout of a typical rectangular spiral inductor.

There are several sources of loss in a spiral inductor. The most obvious loss mechanism is the series winding resistance. The interconnect metal used in most CMOS processes has typically been aluminum. Depending on the metalization thickness and particular aluminum alloy used, the sheet resistivity can be anywhere from 30-70 m $\Omega$  /  $\Box$ . However, at higher frequencies, the resistance of the spiral increases due to the skin effect and "current crowding" at the corners of each turn. On the other hand, standard CMOS substrate losses ultimately remain the limiting factor, even when the conductivity of the spiral windings is no longer an issue.

In an CMOS process, the windings of the spiral are separated from the substrate by a thin layer of Silicon dioxide. This creates capacitance between the spiral and the surface of the substrate. Thus, the heavily doped p-type substrate appears as a

microwave frequencies.

grounded resister in series with this capacitance.

There are also losses due to the magnetic field in the inductor structure. The magnetic field extends around the windings of the spiral and into the substrate. This field forces an image current to flow in the substrate. These currents can account for 50% or more of the losses in a CMOS inductor. Use of non-standard high-resistivity Si substrates, or a post-process to etch the substrate away under the inductor, can minimize these losses.

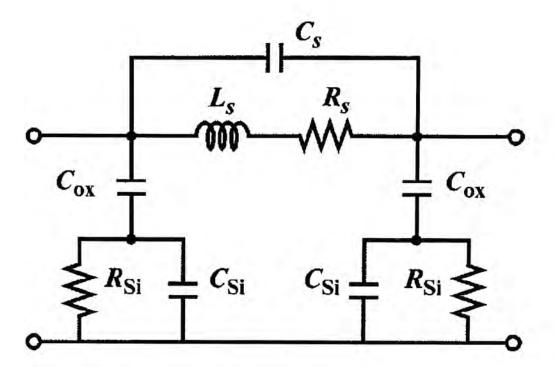

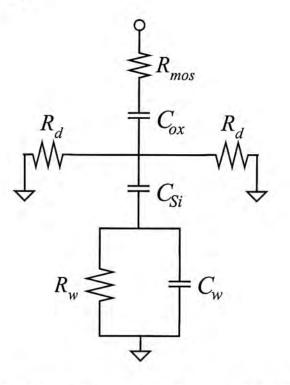

Figure 4.7 Lumped physical model of spiral inductor on Silicon

A general circuit model for a monolithic inductor on a low-resistivity substrate is

shown in Figure 4.7 [15]. This model includes circuit elements that model the winding less as well as the substrate loss. The model parameters can be evaluated by the following equations:

$$R_{s} = \frac{\rho \times l}{w \times \delta \times (1 - e^{-t/\delta})}$$

$$C_{s} = n \times w^{2} \times \frac{\varepsilon_{ox}}{t_{ox_{metal}}}$$

$$C_{ox} = \frac{1}{2} \times l \times w \times \frac{\varepsilon_{ox}}{t_{ox}}$$

$$C_{si} = \frac{1}{2} \times l \times w \times C_{sub}$$

$$R_{si} = \frac{2}{l \times w \times G_{sub}}$$

(4.3)

where

L<sub>s</sub> stands for spiral inductance

R<sub>s</sub> stands for series sheet resistance

$C_s$  represents the capacitance due to the overlaps between the spiral and the center-tap underpass

C<sub>si</sub> models the silicon substrate capacitance

$\mathbf{R}_{si}$  models the silicon substrate resistance

n stands for number of turns of spiral trace

$\rho$  stands for metal resistivity,

l stands for total length of the spiral

w stands for metal width

$\delta$  stands for metal skin depth

t stands for metal thickness

$tox_{metal}$  represents the thickness of the oxide insulator between the spiral and underpass

tox represents the thickness of the oxide layer between the spiral and substrate.

$\epsilon_{os}$  stands for permittivity of the oxide

Gsub stands for substrate conductance

Csub stands for capacitance per unit area

# 4.1.5 Inductor Layout Consideration

In order to minimize the parasitic loss of inductors, some precaution should be taken in constructing the layout of CMOS spiral inductors [3]:

- Metal trace width should be limited: as the skin effect will reduce the current flow in the center of wide conductor. Thus, wide metal conductors are not efficient.

- Minimize the number of turns: at high frequency, generation of eddy currents will deteriorate the overall quality factor of inductors. Since the innermost turns of the coil suffer from an enormous increase in resistance, while their contribution to the inductance value is minimal.

- Area occupied by the spiral should be reduced: magnetic field generated by inductor induces currents in the substrate at high frequency, which cause a decrease in inductance value and extra resistive losses. Thus, large spirals are not efficient as the magnetic field of small coils penetrates less deep into the substrate. Large spiral inductor consumes too much substrate area and therefore, inductors with inductance value greater than 10nH is not recommanded.

# 4.1.6 CMOS RF Varactor

There are many types of CMOS varactors, such as junction diode, MOS Varactor[10], Gated Varactor[11] and Three-Terminal Varactor[12]. VCO's based on MOS varactors, a device readily available in any CMOS process, have been reported in the literature.

In the standard CMOS process, junction diode is formed by providing p+ active area in an n-well. The junction diode is operated in reverse-bias mode, and therefore its junction capacitance can be made tunable by a voltage. The disadvantages of diode varactors are:

large wafer area is needed to provide higher capacitance value,

lack of high frequency model

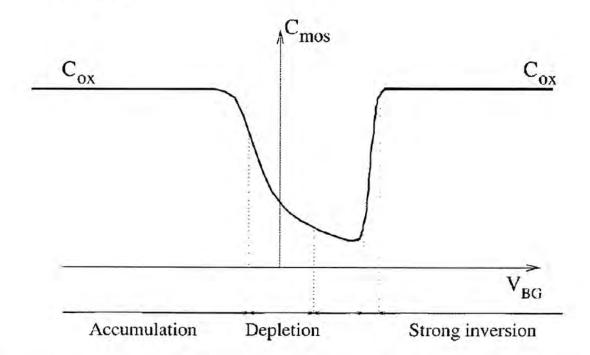

It is well known that an MOS transistor with drain, source, and bulk connected together realizes an MOS capacitor with capacitance value dependent on the voltage between the bulk and gate (Figure 4.8). The capacitance variation of a typical PMOS varactor as a function of  $V_{BG}$  is illustrated in figure 4.9.

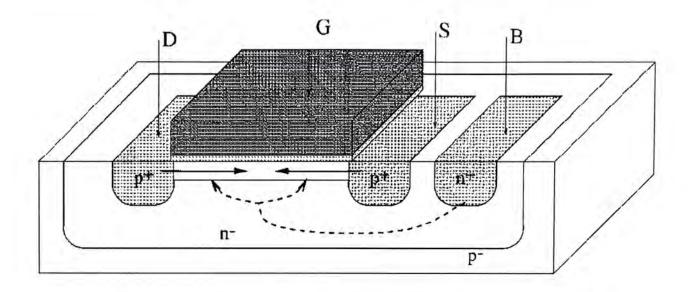

Figure 4.8 Cross-section area of PMOS varactor by connecting D, S and B together

When  $V_{BG}$  is negative and high enough to allow electrons to move freely, the concentration of surface majority carrier increases. In this case, the MOS varactor is said to be in deep accumulation, and the resulting capacitance is mainly composed of gate-body capacitance. In the accumulation region, no channel is induced between drain and source region. Thus, MOS capacitance is equal to the gate oxide capacitance:  $C_{ox} = \varepsilon_{ox} S / t_{ox}$ , where S and  $t_{ox}$  are the transistor channel area and the oxide thickness, respectively.

For  $V_{BG} > |V_T|$ , some free electrons are repelled from the channel region below the gate and pushed downward into the substrate. Depletion layer is formed under the gate oxide layer, and the MOS capacitance can be modeled as  $C_{ox}$  in series with  $C_b//C_i$ .  $C_b$  accounts for the modulation of the depletion region, while  $C_i$  is related to the variation of the number of holes at the gate oxide interface. As the value of  $V_{BG}$  increases, the depletion region widens and the capacitance is reduced further until it reaches its minimum.

When  $V_{BG}$  becomes very much larger than  $|V_T|$ , more free holes are attracted into the channel region. As a result, an inversion layer with mobile holes is formed in the channel area. MOS capacitance equals the gate oxide capacitance  $C_{ox}$ , as in the accumulation region.

Figure 4.9 Capacitance variation versus tuning voltage of typical PMOS varactor

### 4.1.7 Parasitics of PMOS-type varactor

It is well-known that the quality factor Q of the MOS varactor has a strong influence on the phase noise performance of VCOs. As a result, the layout design of the PMOS varactor must be done with care as the parasitics are directly associated with the device geometry. In [19], the parasitic resistance of a PMOS varactor working in strong inversion is given by,

$$R_{mos} = \frac{L}{12k_{p}W(V_{BG} - |V_{T}|)}$$

(4.4)

where W, L, and  $k_p$  are the width, length, and gain factor of the PMOS transistor. Thus, it is seen that a transistor with large W/L ratio should be chosen in order to minimize  $R_{mos}$  (Figure 4.10).

Figure 4.10 Equivalent model of typical PMOS varactor

# Chapter 5 Design and Implementation of Integrated CMOS VCO

The Local Oscillator is one of the most fundamental blocks in a telecommunication transceiver. The voltage-controlled oscillator is an integral part of the LO, characterized by very stringent design requirements. Today, the VCO circuits are usually realized using one of the semiconductor technologies: GaAs, bipolar, BiCMOS, SiGe or CMOS. Recent advances in CMOS technology and in particular the continuous shrinkage in transistors' channel length, makes the MOS device comparable to the bipolar transistor in terms of the highest frequency of operation. This chapter deals with the design of CMOS LC oscillators by using two pairs of NMOS/PMOS transistors coupled in positive feedback [9].

# 5.1 1.5 GHz CMOS VCO Design

#### 5.1.1 Equivalent circuit model of differential LC VCO

Figure 5.1 and 5.2 show the equivalent single-sided model of the differential LC VCO, equivalent model of the resonant tank circuit with all associated losses. The parameters are defined by,

Figure 5.1 Single-sided equivalent circuit

Figure 5.2 (a) LC Tank including all parasitic loss (b) equivalent LC tank with all losses represented by parallel losses

$$R_{p,total} = \frac{1}{\frac{1}{R_{l}(Q_{l}^{2}+1)} + \frac{1}{R_{c}(Q_{c}^{2}+1)} + \frac{1}{R_{p}}}$$

(5.1)

$$Y(\omega) = j\omega C_{r} + \frac{1}{j\omega L_{r}} + \frac{1}{R_{p,total}} + j\omega C_{g}$$

$$C_{r} = C \left(\frac{Q_{c}^{2}}{Q_{c}^{2}+1}\right)$$

$$L_{r} = L \left(\frac{Q_{l}^{2}+1}{Q_{l}^{2}}\right)$$

where  $C_g$  is the gate capacitance of the FET; C is the varactor capacitance.

Therefore, the frequency of oscillation can be approximated by:

$$f_o = \frac{1}{2\pi\sqrt{L_r(C_r + C_g)}}$$

(5.2)

# 5.1.2 Reference Oscillator Circuit

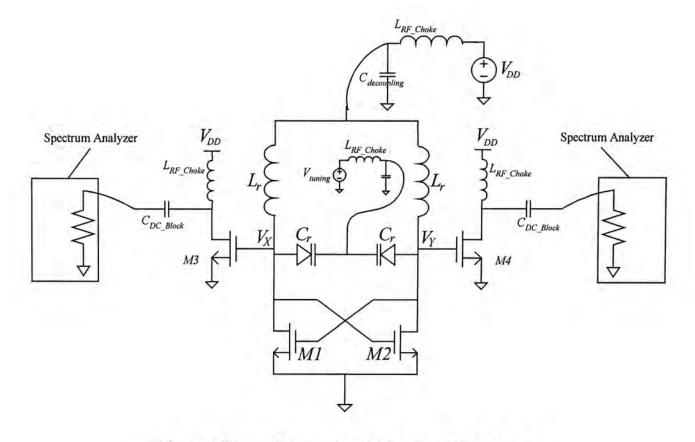

Figure 5.3 Schematic of reference VCO design

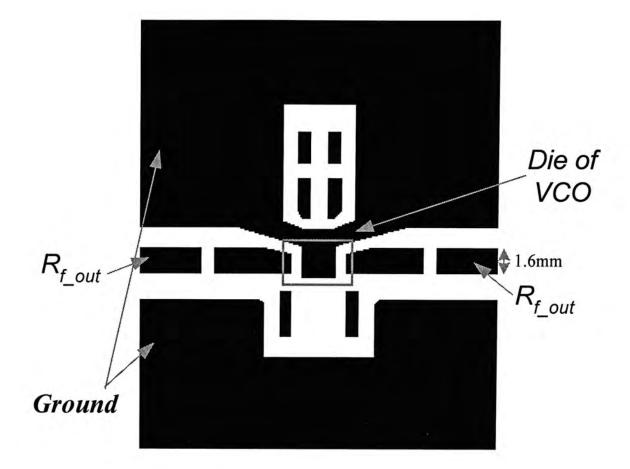

In the reference design, two NMOS transistors (M1 and M2) are coupled in positive feedback to provide a negative resistance. The on-chip spiral inductor and PMOS varactor ( $L_r$  and  $C_r$ ) together forms a resonant tank. The oscillating frequency is made variable by using PMOS varactor with the drain, source and substrate all connected to the tuning voltage  $V_{tuning}$ , while the gate poly of the varactor is connected to the drain terminals of the NMOS transistor. According to equation (5.2), with  $L_r = 3.2$ nH, the capacitance associated with the tank circuit must be set equal to 3.5pF in order to give an oscillation frequency of 1.5GHz. This capacitance is mainly composed of the inductor-to-substrate capacitance (0.2pF), the gate-source capacitance of the NMOS transistor (1pF), and the capacitance of the PMOS transistor (2.3pF at zero bias).

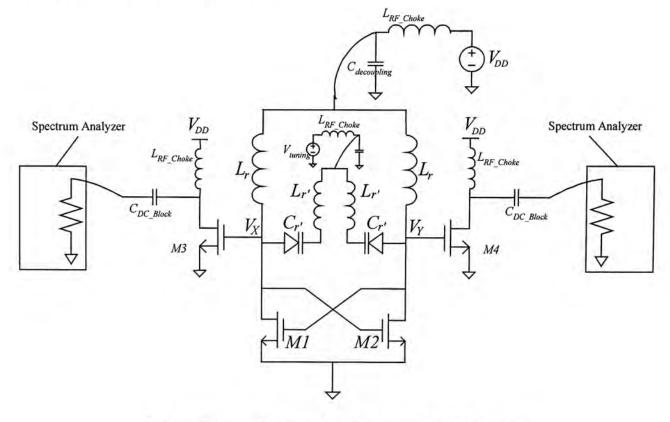

# 5.1.3 Proposed Oscillator Circuit

Figure 5.4

Schematic of proposed VCO design

Figure 5.5 shows the topology of the LC tank adopted in the reference and proposed VCO circuits. According to the formulas derived in chapter 3, the expression for the component values are simply,

$$C_{r'} = \frac{C_r}{1 + \omega_o^2 L_{r'} C_r}$$

(5.3)

$$L_{r'} = L_r \left(\frac{C_r}{C_{r'}} - 1\right) \tag{5.4}$$

Subsequently,

$$C_{r'} = \frac{3}{4}C_r = \frac{3}{4} \times 2.3\,pF = 1.72\,pF \tag{5.5}$$

Hence, if the capacitance value of the PMOS varactor is set equal to 1.5pF, we obtain,

$$L_{r'} = L_r \left(\frac{C_r}{C_{r'}} - 1\right) = 3.2 \times 10^{-9} \times \left(\frac{2.3 \times 10^{-12}}{1.5 \times 10^{-12}} - 1\right) = 1.70 \text{nH}$$

(5.6)

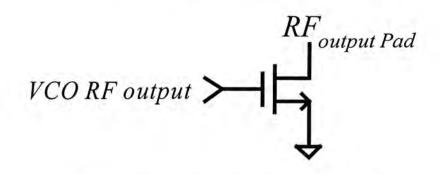

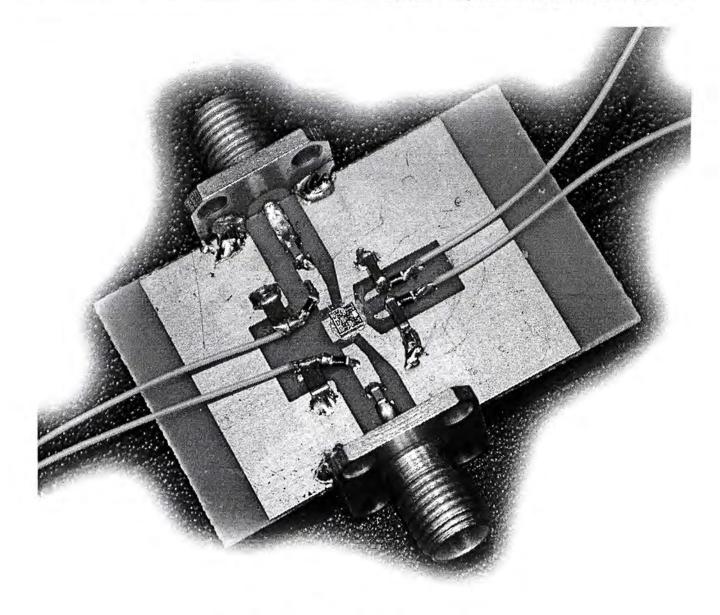

# 5.1.4 Output buffer

Note that the parasitics associated with the bond pads may affect the performance of the VCO circuits, or even preventing them from oscillation. It is a common practice to insert a common-source stage (M3 and M4) for output buffer, as depicted in Figure 5.6.

Figure 5.6 Common-source output buffer

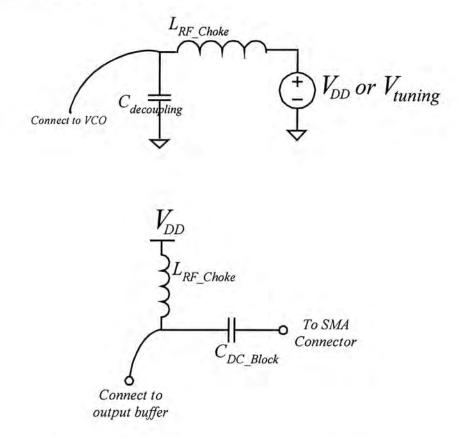

# 5.1.5 Biasing Circuitry

Figure 5.7 Biasing circuit of VCO circuits

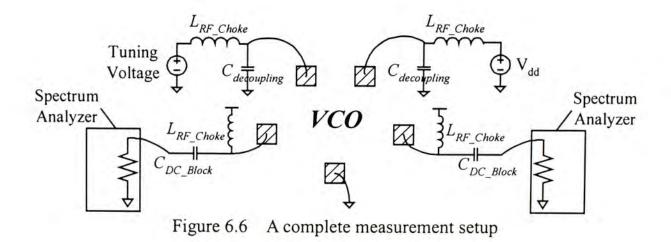

Figure 5.7 shows the biasing networks for the VCO circuits. The RF choke presents a high impedance to high frequency signal and a low impedance DC path. The decoupling capacitor provides a proper RF ground at the required frequency range. The function of  $C_{DC_{Block}}$  is to prevent any DC voltage appearing at the output

from entering the measurement equipment. Surface-mount components of 10nH, 10 $\mu$ F and 2.5pF are chosen for L<sub>RF\_Choke</sub>, C<sub>decoupling</sub> and C<sub>DC\_Block</sub>, respectively.

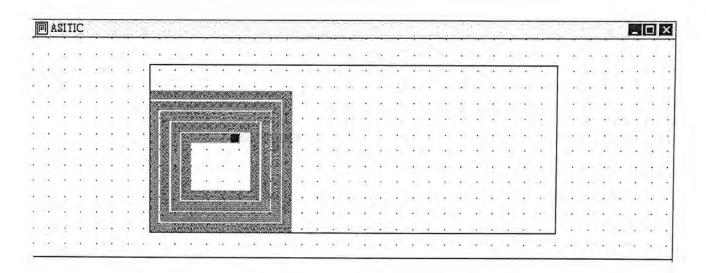

### 5.2 Spiral Inductor Design

It has been reported that the GreenHouse's Method is rather accurate in estimating the inductance value of the spiral inductor. Some computer-aided design tools are also available for solving the respective calculations. ASITIC [30] (*Analysis of Si Inductors and Transformers for ICs*), a CAD tool that can be used to optimize the design of spiral inductors, is adopted here.

Figure 5.8 Screenshot of CAD tool – ASITIC

Figure 5.8 shows the screenshot of ASITIC. The required process parameters such as the layer thickness and the resistivity of the layer, are contained in a

technology file as input data, see Appendix B. Table 5.1 summaries the basic steps in

creating the spiral inductor and extracting circuit model using ASITIC.

| Steps | Action                                                                                                                      |  |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1     | Use command "sq" to start create rectangular spiral inductor                                                                |  |  |  |  |

| 2     | Type the name, inner dimension, no. of turn, metal width, metal-to-metal spacing, etc of the spiral.                        |  |  |  |  |

| 3     | Type "ind <spiralname>" to ask for inductance of the spiral. ( i.e. The value of <math>L_s</math> )</spiralname>            |  |  |  |  |

| 4     | Type "res <spiralname>" to ask for total sheet resistance of the spiral. ( i.e. The value of <math>R_s</math>)</spiralname> |  |  |  |  |

| 5     | Type "geom. <spiralname>" to ask for all dimensions of the spiral. ( i.e. Total length (I)</spiralname>                     |  |  |  |  |

Table 5.1

Procedure of spiral inductor design using ASITIC

Once the dimensions of the spiral inductors are known, equation 4.3 can be used

to calculate all element values in the lumped equivalent model of the spiral inductor.

A matlab program is written for these calculations and the code is given in Appendix

C.

Based on the process parameter provided by the foundry, we can create a technology file suitable for use by ASITIC. For example, the dimensions of a square spiral inductor of 3.2nH are given below:

- inner dimension = 180 micron

- $\blacksquare \quad \text{number of turns} = 3$

- metal used = metal 3

- metal width = 12 micron

- metal-to-metal spacing = 1.5 micron

Then, by using the Matlab program, the parameter values in the equivalent

inductor model are simply equal to:

$$R_{s} = 15.2\Omega$$

$$C_{s} = 21.0 fF$$

$$C_{ox} = 140.2 fF$$

$$C_{si} = 11.1 pF$$

$$R_{si} = 719.7\Omega$$

### 5.3 Determination of W/L ratio of FET

Assuming the cross-coupled FETs are symmetrical, we can calculate the transconductance as follows:

$$\frac{g_{m}}{2} \ge \alpha \times \text{Real}\{Y(\omega)\}$$

$$= \frac{\alpha}{R_{p,total}}$$

$$= \alpha \times \left(\frac{1}{R_{l}(Q_{l}^{2}+1)} + \frac{1}{R_{c}(Q_{c}^{2}+1)} + \frac{1}{R_{p}}\right)$$

(5.7)

In many cases, the value of  $\alpha$  is set between 1 to 2 so as to ensure start-up oscillation. Since the quality factor of CMOS varactors(>20) is usually much higher than spiral inductors, it is reasonable to assume that  $\frac{1}{R_c(Q_c^2+1)} \approx 0.$

As a result, we have

$$g_{m} \geq \frac{2\alpha}{R_{l}(Q_{l}^{2}+1)}$$

$$(5.8)$$

At an oscillating frequency of 1.5GHz, the unloaded quality factor of the spiral

inductor is thus given by,

$$Q_l = \frac{2\pi \times (1.5 \times 10^9) \times 3.2 \times 10^{-9}}{15.2} = 1.98$$

(5.9)

For safety reason, we set  $\alpha = 1.5$ , which gives,

$$g_{\rm m} \ge \frac{2 \times 1.5}{15.2 \times (1.98^2 + 1)} = 40.1 mS$$

(5.10)

Subsequently, with  $V_{dd} = 1.5$ V, the size of the NMOS transistor can be evaluated by,

$$\frac{W}{L} = \frac{g_{\rm m}}{\mu \, C_{\rm ox} \left( V_{GS} - V_T \right)} = \frac{0.0401}{1.18 \times 10^{-4} \times (1.5 - 0.7)} = 424.92 \tag{5.11}$$

For  $L = 0.6 \mu m$ , the width of the active device should be set equal to 250  $\mu m$ .

### 5.4 Varactor Design

The physical dimensions of the PMOS varactor may be estimated from the lowest tuning capacitance value required in the VCO design. It is very difficult to determine the exact capacitance value of the varactor by using simple formulas, and therefore we will leave this calculation to the simulation program. In the reference VCO design, the total tank capacitance required is approximately 3.5pF for an oscillation frequency of 1.5GHz. This capacitance consists of the spiral inductor to substrate capacitance (0.2pF), varactor capacitance and the parasitics of the FET. For NMOS transistor with a gate-length of 0.6 $\mu$ m and a gate-width of 250 $\mu$ m, the parasitic capacitance which consists of the gate-drain, drain-bulk and gate-source capacitances may be calculated by,

$$C_{\text{FET Parasitic}} = 250 \,\mu m \times 4 \, fF \,/\,\mu m$$

$$= 1 \, pF$$

(5.12)

Consequently, the capacitance value of the varactor is simply,

$$C_{r} = 3.5pF - C_{Inductor Parasitic} - C_{FET Parasitic}$$

= 3.5pF - 0.2pF - 1pF

= 2.3pF (5.13)