# Design of Application-specific Instruction Set Processors with Asynchronous Methodology for

#### **Embedded Digital Signal Processing Applications**

KWOK Yan-lun Andy

A Thesis Submitted in Partial Fulfilment of the Requirements for the Degree of Master of Philosophy in Electronic Engineering

© The Chinese University of Hong Kong

November 2004

The Chinese University of Hong Kong holds the copyright of this thesis. Any person(s) intending to use a part or whole of the materials in the thesis in a proposed publication must seek copyright release from the Dean of the Graduate Schools.

#### **ABSTRACT**

Abstract of thesis entitled:

Design of Application-specific Instruction Set Processors with Asynchronous Methodology for Embedded Digital Signal Processing Applications

Submitted by KWOK Yan-lun Andy

for the degree of Master of Philosophy in Electronic Engineering at The Chinese University of Hong Kong in November 2004

This thesis presents a new design methodology of application-specific instruction set processors (ASIPs) using asynchronous design methodology. ASIPs are today's enabling technology for tackling increasingly complex embedded systems together with tightening time-to-market constraints. It combines the high design productivity of the software approach and the high performance of the hardware approach, which brings us programmable devices with dedicated hardware features for real-time applications. A major obstacle of ASIP design is the larger design space compared with pure hardware or pure software implementations. This makes it hard for the designers to search for large amounts of architecture alternatives in order to find an optimal implementation within a competitive design timeframe.

The platform-based design methodology using asynchronous technology is developed. A highly extensible and flexible platform is designed as the heart. Using asynchronous interfaces, components can be added to the platform rapidly to expand its functionalities without affecting the global timing. The platform can be effectively optimized for particular applications.

The proposed design methodology is proven to be effective in the case studies. It shows that the base platform can be scaled up easily to dramatically speed up different kinds of kernels, reaching the performance level of some advanced parallel DSPs. The benchmark of rotation CORDIC algorithm even illustrates further performance gain by using asynchronous design methodology for seamless cooperation between two different clock domains.

### 摘要

日益進步的半導體技術,使計算機系統得以向多樣化和高整合進化。面對越來越複雜的應用以及縮短開發周期的需求,使用專用指令集處理器(ASIP)是最佳的選擇。專用指令集處理器結合專用集成電路(ASIC)的卓越運算能力及可編程架構的高靈活性,使系統設計師能在短時間內完成產品上市。但是設計專用指令集處理器本身是一個極難解的問題。當中涉及複雜的軟硬體協調,使設計師無從入手,更遑論嘗試各種不同的軟硬體組合以求得到最合適的設計。

有鑒於此,本論文提出一個利用異步設計技術和以開發平台爲基礎的方案。利用異步設計的高度模組化和其溝通界面,不同的模組可迅速組裝在一個可延展的平台上,面向目標應用對平台進行優化。建基於平台的方案爲專用指令集處理器設計提供一個切入點,並有效將設計流程簡化。設計師因而可在有限的時間內評價不同配置的效能。

本論文所提出的方案在不同的實作中能有效面向不同的數字訊號處理核心(DSPKernel)進行優化,並帶來顯著的效能增益。其效能甚至可媲美超長指令數字處理器(VLIWDSP)。此結果令人鼓舞,亦證實本方案爲可行並有效。

**ACKNOWLEDGEMENTS**

Gratitude to The Almighty, without whose blessing nothing can be achieved.

Special thanks to my supervisor Professor Choy Chiu-Sing, who has been a constant

source of inspiration for me, and has given me invaluable support, encouragement

and guidance. My appreciation also goes to Professor Chan Cheong-Fat and

Professor Pun Kong-Pang for their constructive comments on the work.

I would also like to thank Mr Yeung Wing-Yee, who maintained our design

environment and helped me with most of the technical problems. I will not forget the

students in our research group, especially Cheng Wang-Tung, Shen Jun-Hua, Yu

Chun-Pon, Xu Ke, Leung Pak-Keung, Chan Chi-Hong and Chan Wing-Kin, whose

energy and diversity have made for many stimulating interactions. It has been a

genuine pleasure to work with them.

My heartfelt thanks to my parents for their continuing support of all kinds, and to

auntie Mavis and my friend Chan Wan-Man for their endless encouragement.

Kwok Yan Lun

2004

iii

## TABLE OF CONTENTS

| // Acknowledgements                                                                                                                                  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| List of Figures                                                                                                                                      |  |  |

| List of Tables and Examples  1. Introduction  1.1. Motivation  1.2. Objective and Approach  1.3. Thesis Organization  2. Related Work  2.1. Coverage |  |  |

| 1. Introduction                                                                                                                                      |  |  |

| 1.1. Motivation                                                                                                                                      |  |  |

| 1.2. Objective and Approach                                                                                                                          |  |  |

| 1.3. Thesis Organization  2. Related Work                                                                                                            |  |  |

| 2. Related Work                                                                                                                                      |  |  |

| 2.1. Coverage                                                                                                                                        |  |  |

|                                                                                                                                                      |  |  |

| 2.2. ASIP Design Methodologies                                                                                                                       |  |  |

|                                                                                                                                                      |  |  |

| 2.3. Asynchronous Technology on Processors                                                                                                           |  |  |

| 2.4. Summary 1                                                                                                                                       |  |  |

| Asynchronous Design Methodology                                                                                                                      |  |  |

| 3.1. Overview                                                                                                                                        |  |  |

| 3.2. Asynchronous Design Style                                                                                                                       |  |  |

| 3.2.1. Micropipelines                                                                                                                                |  |  |

|    | 3.3. | Advantages of GALS in ASIP Design                       | 27 |

|----|------|---------------------------------------------------------|----|

|    |      | 3.3.1. Reuse of Synchronous and Asynchronous IP         | 27 |

|    |      | 3.3.2. Fine Tuning of Performance and Power Consumption | 27 |

|    |      | 3.3.3. Synthesis-based Design Flow                      | 28 |

|    | 3.4. | Design of GALS Asynchronous Wrapper                     | 28 |

|    |      | 3.4.1. Handshake Protocol                               | 28 |

|    |      | 3.4.2. Pausible Clock Generator                         | 29 |

|    |      | 3.4.3. Port Controllers                                 | 30 |

|    |      | 3.4.4. Performance of the Asynchronous Wrapper          | 33 |

|    | 3.5. | Summary                                                 | 35 |

| 4. | Plat | tform Based ASIP Design Methodology                     | 36 |

|    | 4.1. | Platform Based Approach                                 | 36 |

|    |      |                                                         |    |

|    |      | 4.1.1. The Definition of Our Platform.                  |    |

|    |      | 4.1.2. The Definition of the Platform Based Design      |    |

|    | 4.2. |                                                         |    |

|    |      | 4.2.1. The Nature of DSP Algorithms                     | 38 |

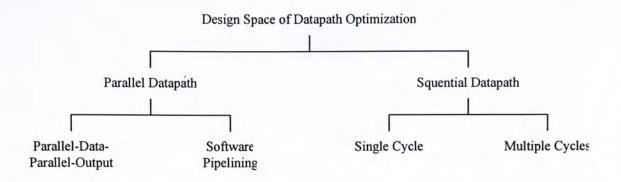

|    |      | 4.2.2. Design Space of Datapath Optimization            |    |

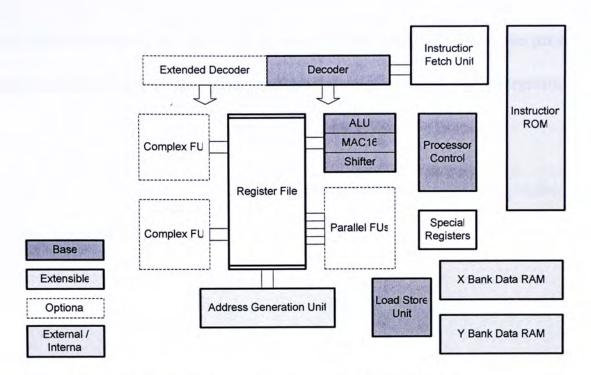

|    |      | 4.2.3. Proposed Architecture                            |    |

|    |      | 4.2.4. The Strategy of Realizing an Optimized Datapath  |    |

|    |      | 4.2.5. Pipeline Organization                            |    |

|    |      | 4.2.7. Operation Mechanism                              |    |

|    | 4.3. | Overall Design Flow                                     |    |

|    | 4.4. | Summary                                                 | 70 |

| 5. | Des  | sign of the ASIP Platform                               | 72 |

|    | 5.1. | Design Goal                                             | 72 |

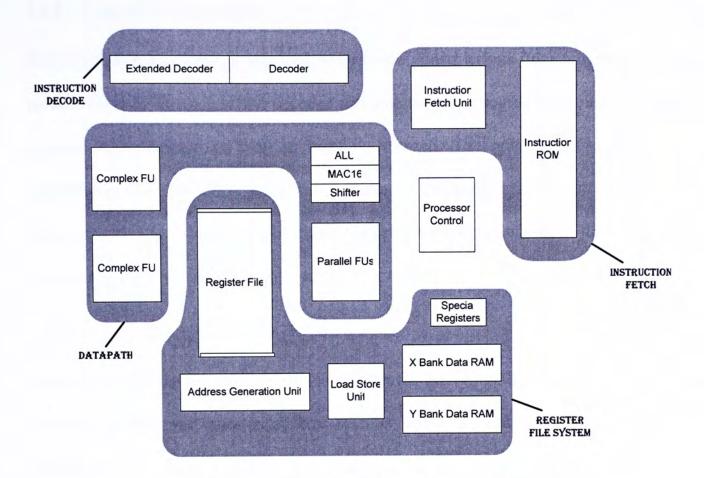

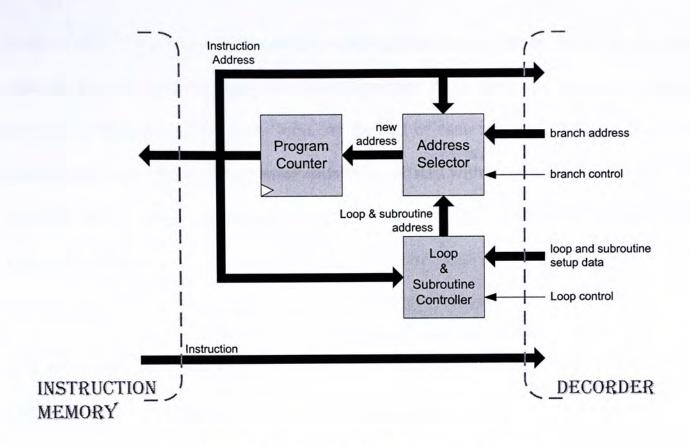

|    | 5.2. | Instruction Fetch                                       | 74 |

|    |      | 5.2.1. Instruction fetch unit                           |    |

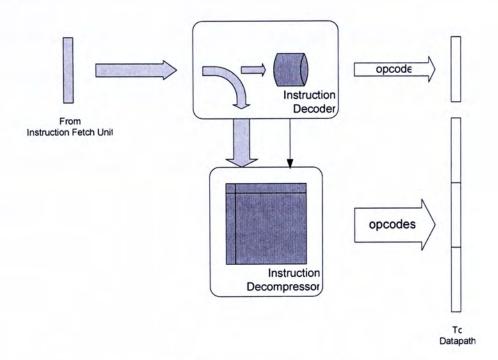

|    | 5.3. | Instruction Decode                                      | 77 |

|    |      | 5.3.1. Instruction decoder                              |    |

|    | 5.4. | Datapath                                                | 81 |

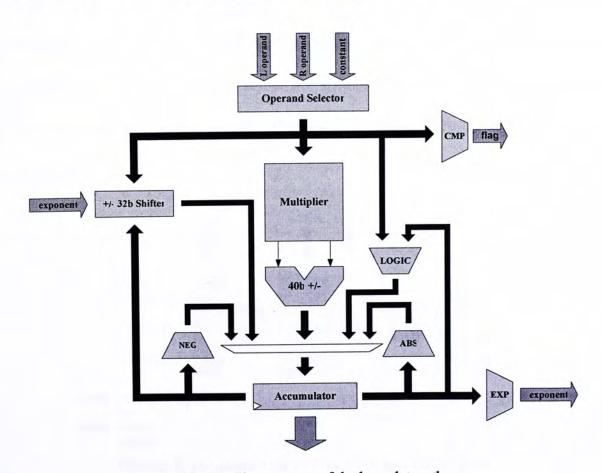

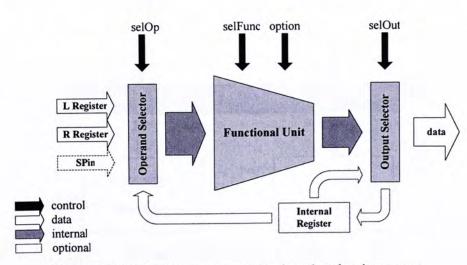

|    |      | 5.4.1. Base Functional Units                            |    |

|    | 5.5. | . Register File Systems                                 | 84 |

|    |      | 5.5.1. Memory Hierarchy                                 | 84 |

|    | 5.5.3   | . Register File Organization                | 93         |

|----|---------|---------------------------------------------|------------|

|    | 5.5.4   | . Load and Store                            | 98         |

|    | 5.6.    | Design Verification                         | 100        |

|    | 5.7.    | Summary                                     | 104        |

| 6. | Case St | udies                                       | 105        |

|    | 6.1.    | Objective                                   | 105        |

|    | 6.2.    | Approach                                    | 105        |

|    | 6.3.    | Based versus Optimized                      | 106        |

|    | 6.3.1   | . Matrix Manipulation                       | 106        |

|    | 6.3.2   | 2. Autocorrelation                          | 109        |

|    | 6.3.3   | 3. CORDIC                                   | 110        |

|    | 6.4.    | Optimized versus Advanced Commercial DSPs   | 113        |

|    |         | 1. Introduction to TMS320C62x and SC140     | 115        |

|    | 6.5.    | Summary                                     | 116        |

| 7. | Conclus | sion                                        | 118        |

|    | 7.1.    | When ASIPs encounter asynchronous           | 118        |

|    | 7.2.    | Contributions                               | 120        |

|    | 7.3.    | Future Directions.                          | 121        |

| A  | Synthes | sis of Extended Burst-Mode Asynchronous Fir | nite State |

|    | Machi   | ne                                          | 122        |

| В  | Base In | struction Set                               | 124        |

| C  | Special | Registers                                   | 127        |

| D  | Synthe  | sizable Model of GALS Wrapper               | 130        |

| Re | ference |                                             | 133        |

## LIST OF FIGURES

| Figure 1.1: ASIP bridges the performance and time-to-market gap                            |

|--------------------------------------------------------------------------------------------|

| Figure 3.1: An abstract interface of asynchronous circuits                                 |

| Figure 3.2: Micropipeline with processing. (Source: [15])                                  |

| Figure 3.3: Muller C-element with inverter. (Source: [15])                                 |

| Figure 3.4: Micropipeline for simple logics                                                |

| Figure 3.5: Micropipeline for self-timed logics                                            |

| Figure 3.6: Conventional domino logic                                                      |

| Figure 3.7: Differential cascode voltage switch logic (DCVSL)                              |

| Figure 3.8: Globally asynchronous communication between modules                            |

| Figure 3.9: Asynchronous Wrapper24                                                         |

| Figure 3.10: Pausible clock while stretching (Other control signals are not shown). 24     |

| Figure 3.11: The GALS design methodology (modified from [36])                              |

| Figure 3.12: Timing diagram of the four-phase handshake protocol                           |

| Figure 3.13: Pausible Clock Generator                                                      |

| Figure 3.14: Mutual Exclusion                                                              |

| Figure 3.15: The extended burst-mode specification and the logical implementation of       |

| the output port controller32                                                               |

| Figure 3.16: The extended burst-mode specification and the logical implementation of       |

| the input port controller32                                                                |

| Figure 3.17: The configuration of an asynchronous communication interface 33               |

| Figure 3.18: The simulated waveform of the communication channel34                         |

| Figure 4.1: A digital signal processing system                                             |

| Figure 4.2: (a) Circular addressing of size 16 and step 3 at iteration K; (b) Bit-reversed |

| addressing of 3 bits in size at iteration K                                                |

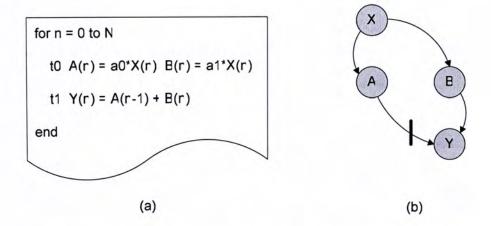

| Figure 4.3: (a) The algorithm of a two-tap FIR filter; (b) The corresponding DFG 41        |

| Figure 4.4: (a) The unfolded algorithm of a two-tap FIR filter; (b) The corresponding      |

| DFG42                                                                                      |

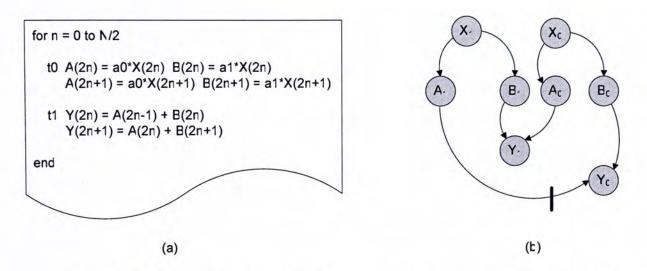

| Figure 4.5: (a) The arbitrary algorithm with heavy data dependence; (b) The                |

| corresponding DFG42                                                                        |

| Figure 4.6: (a) The reformed body of the arbitrary algorithm (b) The software              |

| pipelined arbitrary algorithm43                                                            |

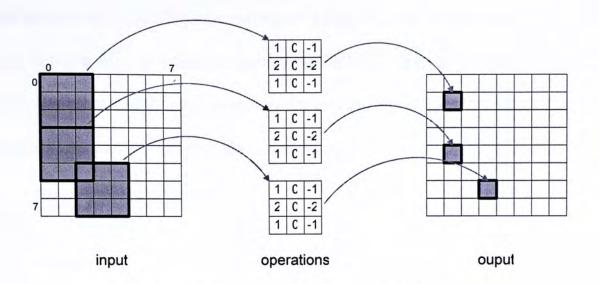

| Figure 4.7: Applying Sobel edge detectors on a 8x8 image                                   |

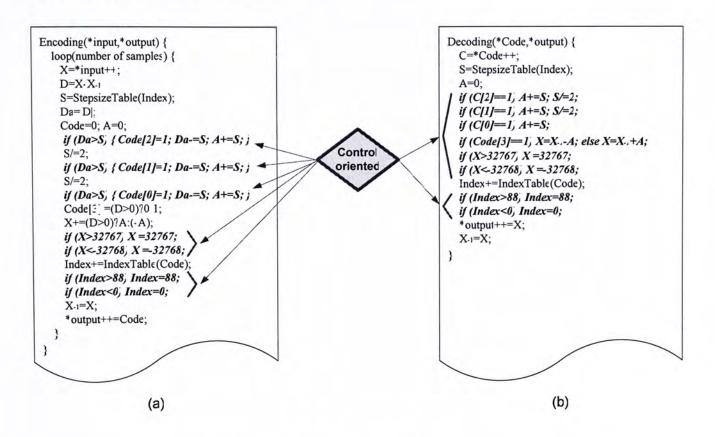

| Figure 4.8: The pesudocode of ADPCM (a) encoding and (b) decoding (Source:          | [39])  |

|-------------------------------------------------------------------------------------|--------|

|                                                                                     | 46     |

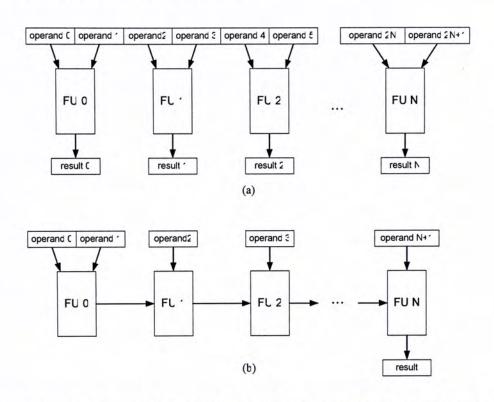

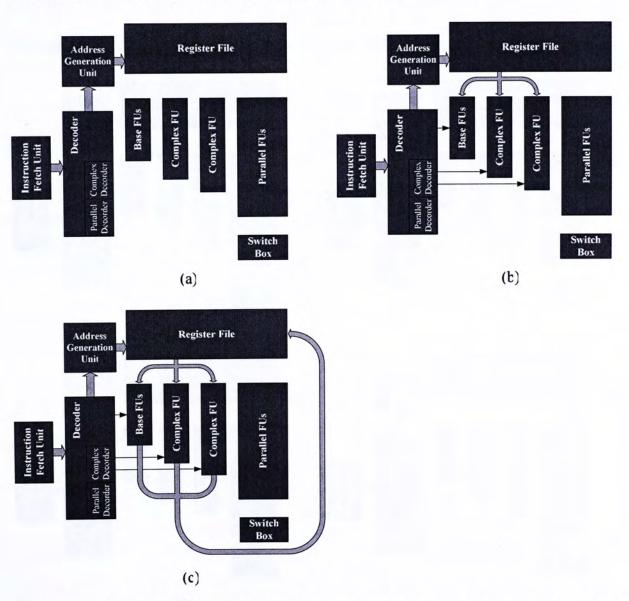

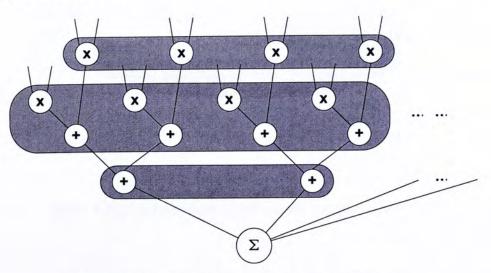

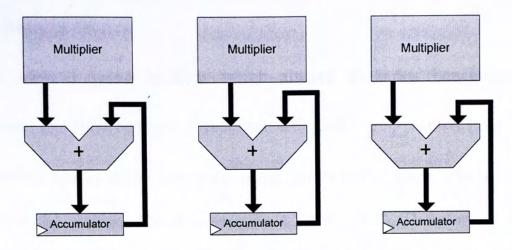

| Figure 4.9: The layout of the parallel datapath (a) for ordinary parallel operation | is (b) |

| for software pipelining                                                             | 47     |

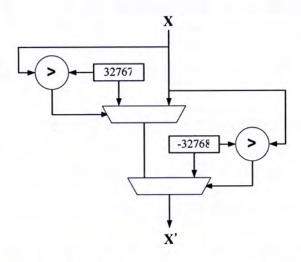

| Figure 4.10: The datapath of saturation arithmetic                                  | 48     |

| Figure 4.11: The design space of datapath optimization                              | 49     |

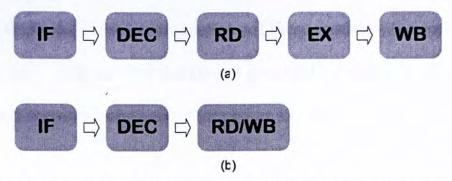

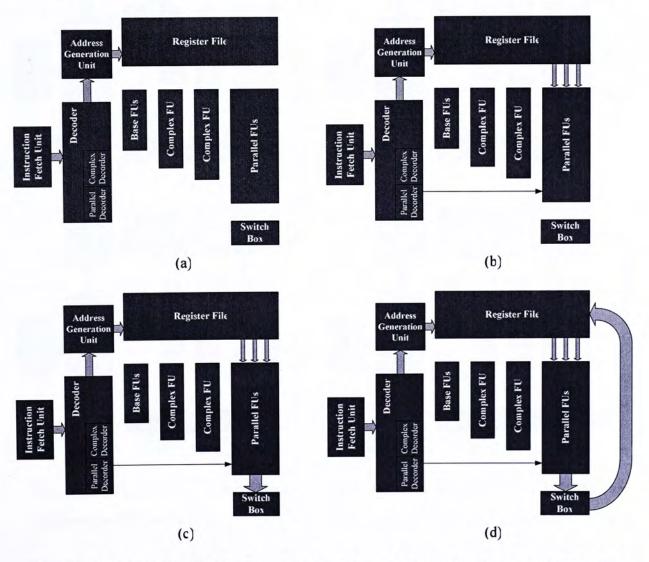

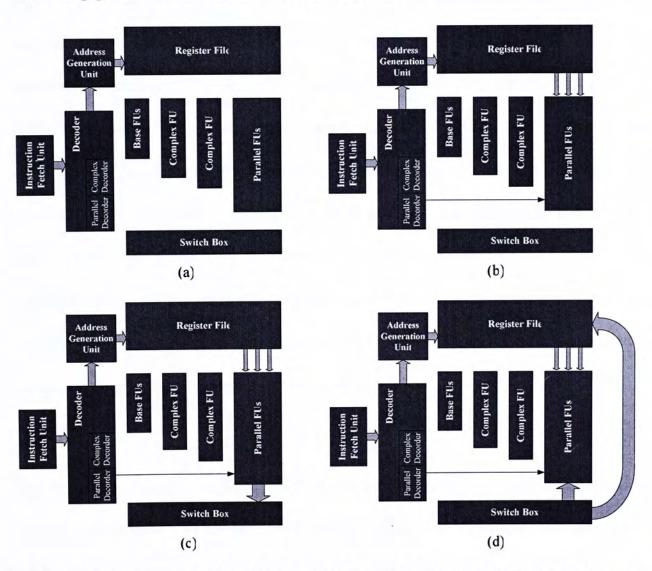

| Figure 4.12: The architecture overview of the platform                              | 50     |

| Figure 4.13: The idea of instruction decompression                                  |        |

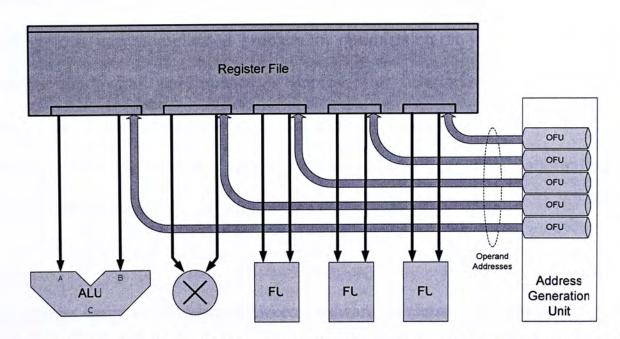

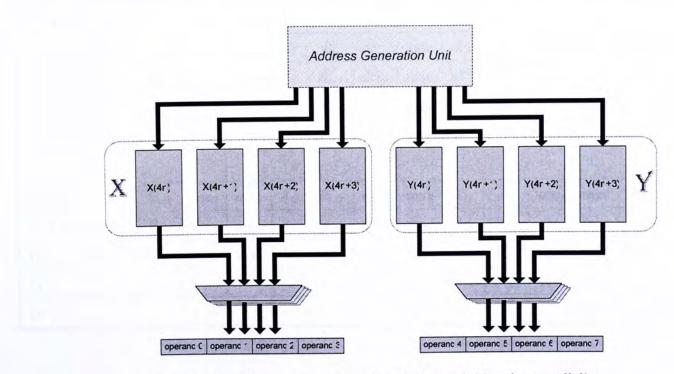

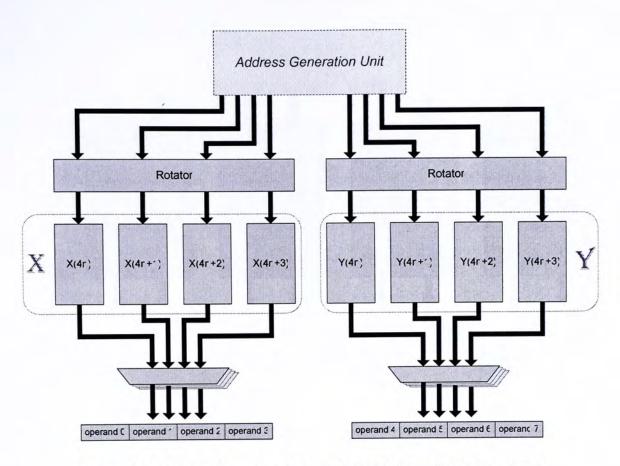

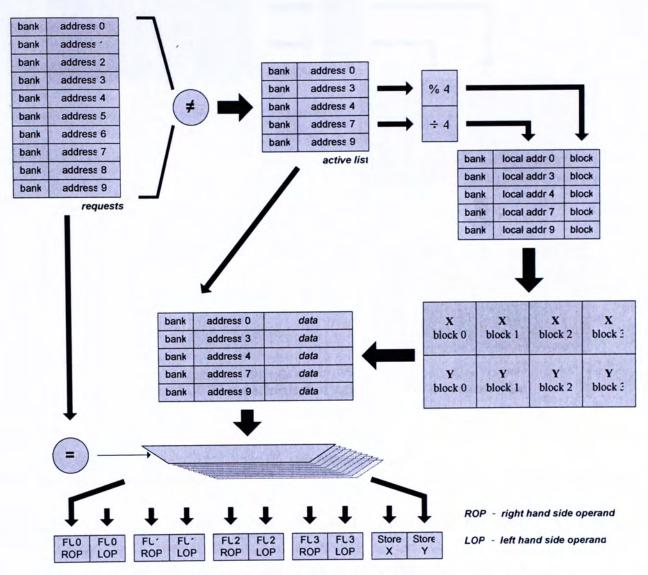

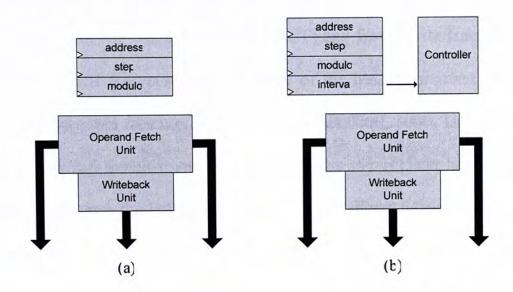

| Figure 4.14: Operand fetch units (OFU) are part of the address generation unit.     |        |

| are used to fetch operands for the functional units.                                | 55     |

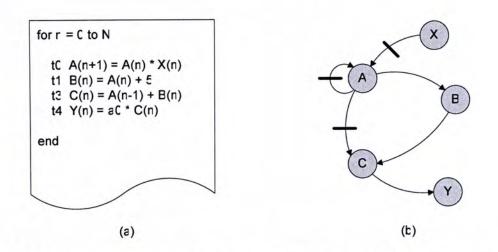

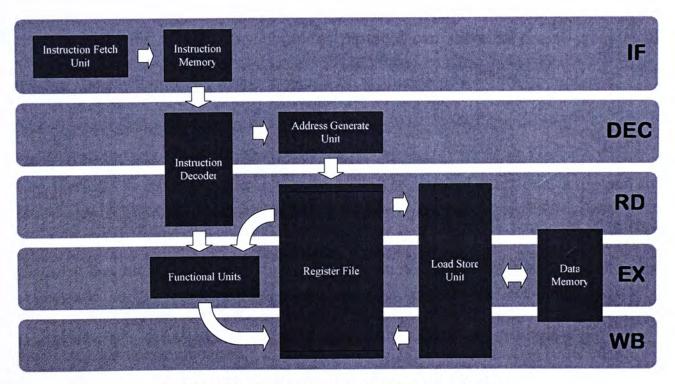

| Figure 4.15: The pipeline organization of the platform                              | 60     |

| Figure 4.16: (a) The normal flow of pipeline operation; (b) The shorten flow with   |        |

| skipping.                                                                           | 61     |

| Figure 4.17: The GALS partitioning of the platform                                  | 63     |

| Figure 4.18: The operation mechanism of simple instructions and complex instruc     | ctions |

|                                                                                     |        |

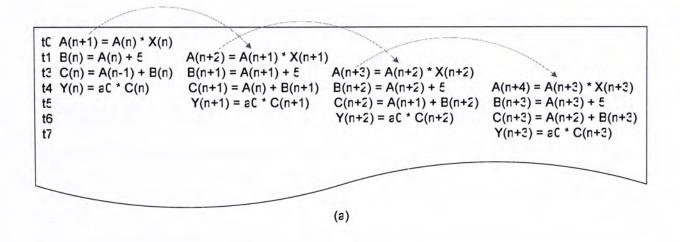

| Figure 4.19: The operation mechanism of parallel instructions                       | 65     |

| Figure 4.20: The operation mechanism of software pipelined parallel instruction     | s66    |

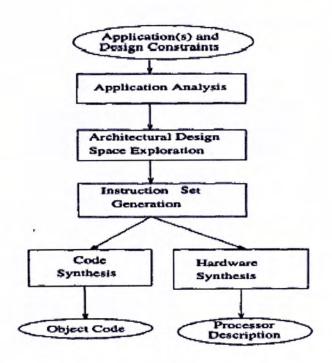

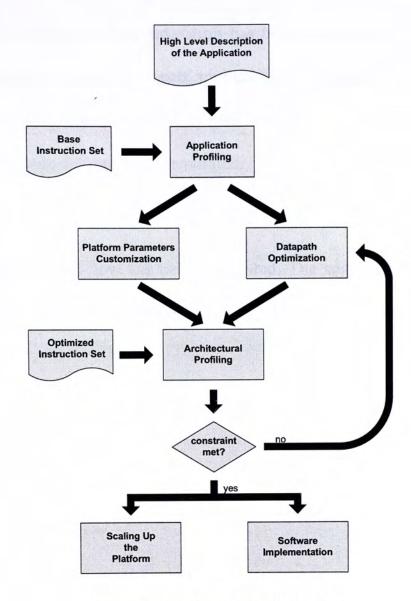

| Figure 4.21: Typical ASIP design flow (source: [40])                                | 69     |

| Figure 4.22: Platform-based design flow                                             | 70     |

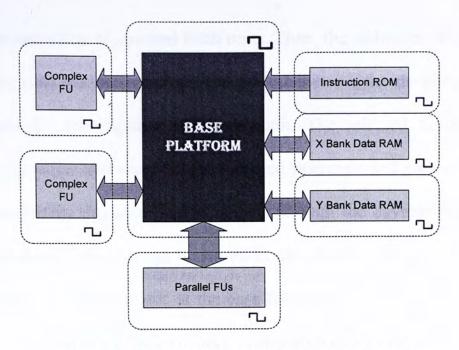

| Figure 5.1: The organization of the platform architecture                           | 73     |

| Figure 5.2: The structure of instruction fetch unit                                 |        |

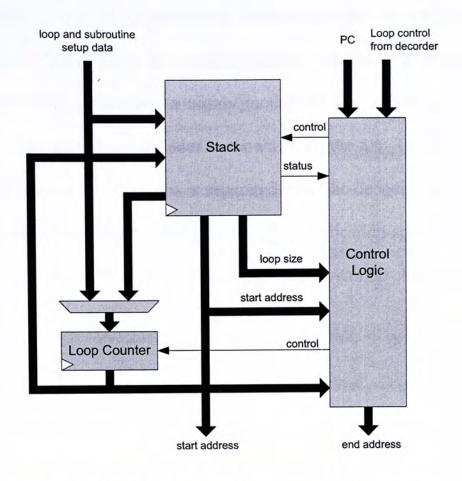

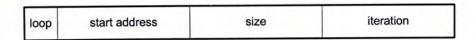

| Figure 5.3: The structure of the loop & subroutine controller                       | 77     |

| Figure 5.4: The content of the stack                                                | 77     |

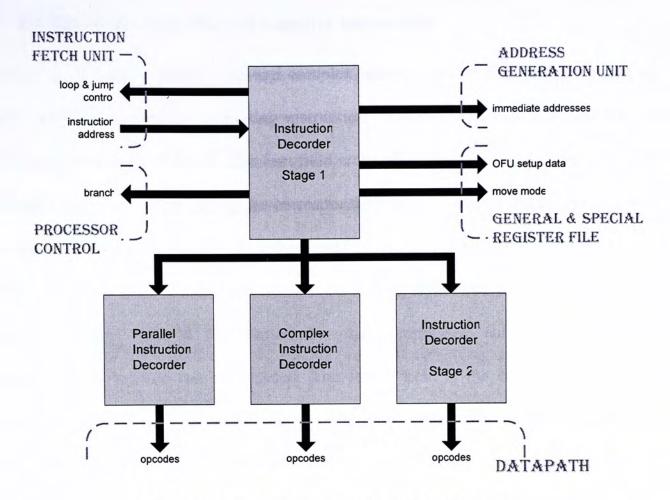

| Figure 5.5: The structure of the instruction decoder                                | 79     |

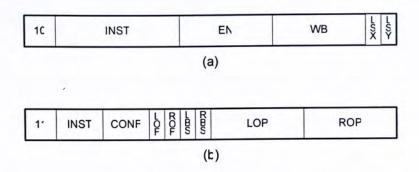

| Figure 5.6: The instruction format of (a) parallel instructions and (b) complex     |        |

| instructions                                                                        |        |

| Figure 5.7: The structure of the base datapath                                      |        |

| Figure 5.8: The abstract view of the functional unit wrapper                        |        |

| Figure 5.9: The memory hierarchy                                                    | 84     |

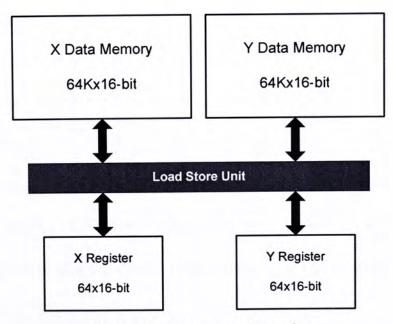

| Figure 5.10: The structure of register file for exploiting data parallelism         | 87     |

| Figure 5.11:The structure of register file for applying software pipelining         | 89     |

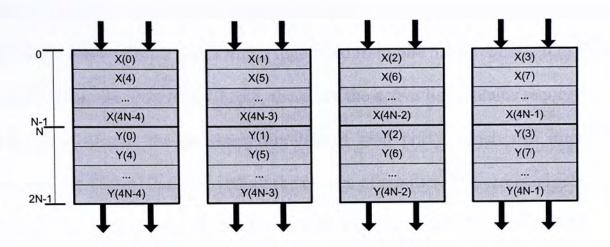

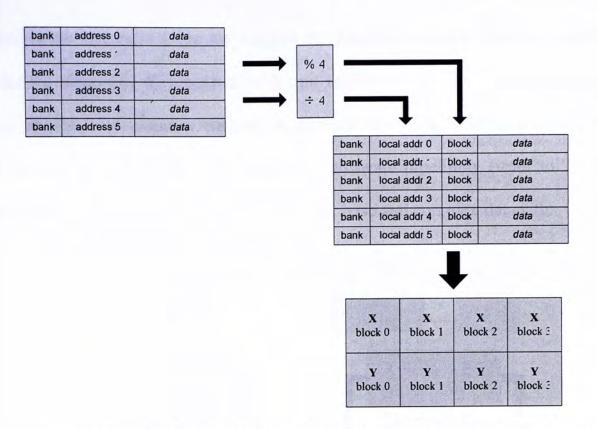

| Figure 5.12: Organize two read port register blocks to X bank and Y bank            | 90     |

| Figure 5.13: The mechanism of reading data from the register file                   |        |

| Figure 5.14: The mechanism of writing data to the register file                     |        |

| Figure 5.15: The organization of address generation engine for (a) base and comp    |        |

| datapath and (b) parallel datapath                                                  |        |

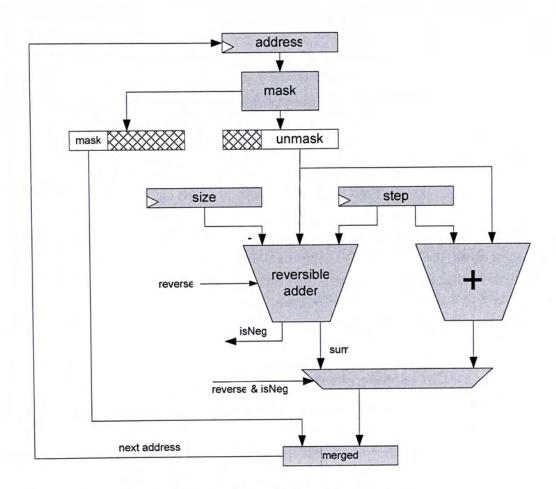

| Figure 5.16: The datapath for address generation                                    | 97     |

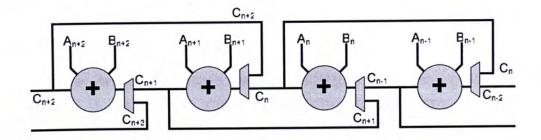

| Figure 5.17: The modified carry propagate adder                               | 97    |

|-------------------------------------------------------------------------------|-------|

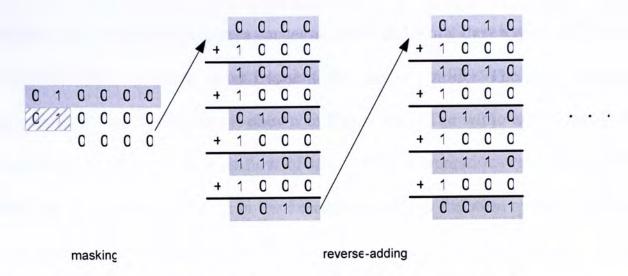

| Figure 5.18: An example of the generation of 16-bit bit-reversed address      | 98    |

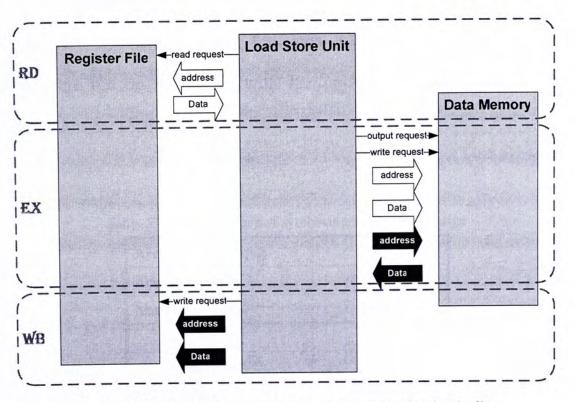

| Figure 5.19: The partitioning of load and store operation in pipeline         | 99    |

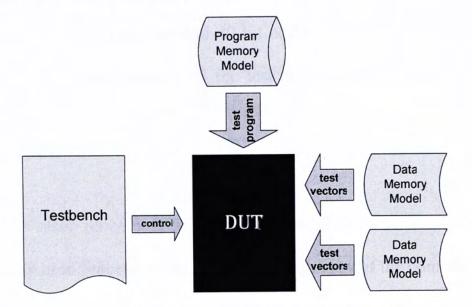

| Figure 5.20: Co-Simulation Environment                                        | 102   |

| Figure 5.21: The memory model template                                        | 102   |

| Figure 6.1: The partitioning of an optimized datapath                         | 107   |

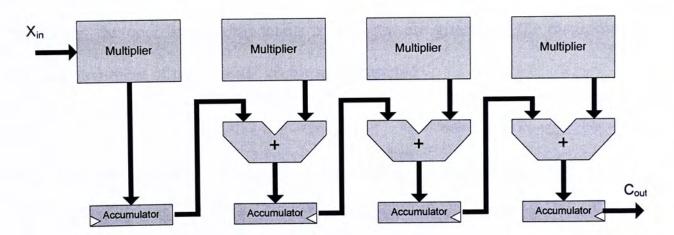

| Figure 6.2: The implementation of the optimized datapath for vector multiplic | ation |

|                                                                               | 108   |

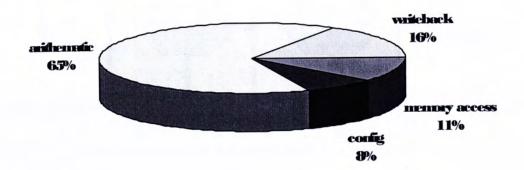

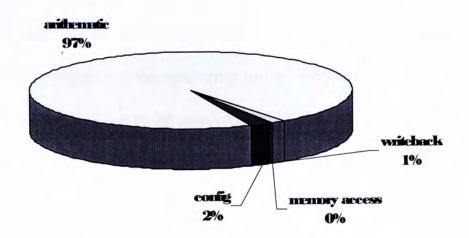

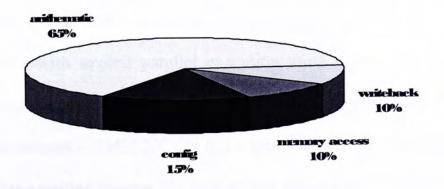

| Figure 6.3: Task breakdown of optimized vector multiplication                 | 108   |

| Figure 6.4: The implementation of the optimized datapath for autocorrelation  | 109   |

| Figure 6.5: Task breakdown of optimized autocorrelation                       | 110   |

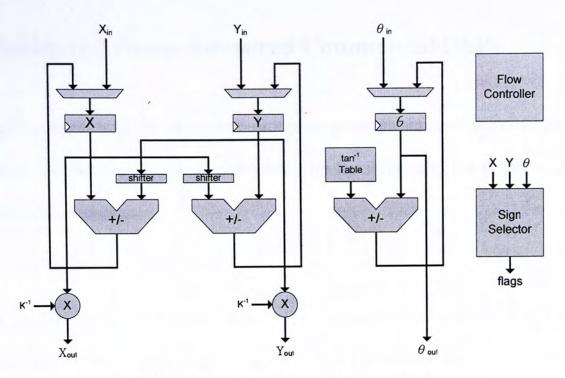

| Figure 6.6: The structure of the CORDIC accelerator                           | 112   |

| Figure 6.7: Task breakdown of optimized CORDIC                                | 112   |

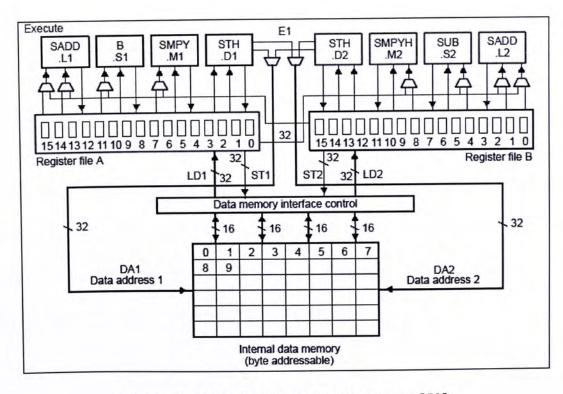

| Figure 6.8: Datapath of TMS320C62x (source: [50])                             | 114   |

| Figure 6.9: Datapath of SC140 (source: [51])                                  | 115   |

| Figure A.1: The 3D machine of the input port controller                       | 122   |

| Figure A.2: The 3D machine of the output port controller                      | 123   |

### LIST OF TABLES AND EXAMPLES

| Table 2.1: The summary of asynchronous processors designed by industry and      |       |

|---------------------------------------------------------------------------------|-------|

| academia                                                                        | 13    |

| Table 3.1: Simulation results of the asynchronous wrapper                       | 34    |

| Table 4.1: DSP primitive mathematical operations                                | 39    |

| Table 5.1: The architectural parameters of the platform for verification        | 73    |

| Table 5.2: The activity list of executing different classes of instructions     | 79    |

| Table 5.3: The data access pattern for exploiting data parallelism              | 87    |

| Table 5.4: The data access pattern for applying software pipelining             | 88    |

| Table 5.5: The summary of synthesis and physical design                         | . 100 |

| Table 5.6: Test programmes for the base platform                                | . 101 |

| Table 5.7: FIR Benchmark Results                                                | . 103 |

| Table 6.1: Results of the vector multiplication benchmark                       | . 108 |

| Table 6.2: Results of the autocorrelation benchmark                             | . 109 |

| Table 6.3: Results of the Rotation CORDIC benchmark                             | . 112 |

| Table 6.4: Processor features of TMS320C62x and SC140                           | . 114 |

| Table 6.5: The summary of benchmark results among different DSPs                | . 116 |

| Table 6.6: The summary of the results of benchmark for base and optimized platf | form  |

|                                                                                 | . 117 |

| Table B.1: The data processing instructions                                     |       |

| Table B.2: The bit manipulation instructions                                    | . 125 |

| Table B.3: The Boolean operation instructions                                   | . 125 |

| Table B.4: The flow control instructions                                        | . 125 |

| Table B.5: The configuration instructions                                       | . 126 |

| Table B.6: The memory manipulation instructions                                 | . 126 |

| Table C.1: The organization of special purpose registers                        | . 127 |

# 1. Introduction

#### 1.1. Motivation

Moore's law 0 has driven the development of technology in the silicon industry for the past three decades. The silicon gate count continues to grow; and the transistor size continues to be scaled down with the regular pace that Moore predicted. Continuing growth in silicon capability is rapidly magnifying the functionality of digital circuits, leading us into a new era of diversified applications on embedded digital devices.

However, Moore's law is found to be increasingly irrelevant. While the silicon gate count still continues to grow as Moore predicted, hardware designers find difficulties in using all the gates efficiently and effectively with the leading edge technology. The improvement of electronic design aided (EDA) tools and engineering skills cannot keep track of the growth in the capability and complexity of digital circuits.

This gap of design productivity leads to great tension in achieving time-to-market, and therefore it becomes a serious burden for realizing advanced competitive designs.

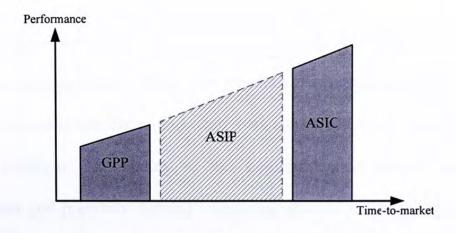

As time-to-market is primarily important, application-specific integrated circuits (ASIC) are no longer the best option although they deliver excellent performance in terms of speed, power and silicon efficiency. Shifting from hardware to software can take advantages in this scenario. Increasing the software proportion of a design improves the design productivity due both to the simple and predictable software design flow and to the high degree of reusability of the software library together with the programmable device itself. It can be expected that programmable devices, especially general-purpose processors, continue to benefit from Moore's law scaling. However, general-purpose processors show limits in meeting stringent requirements of embedded real-time applications. Compared to ASICs, general-purpose processors consume more power and offer lower performance. For this reason, the new type of programmable devices, so-called application-specific instruction-set processors (ASIP) are being developed to fill the gap between performance and time-to-market of purely hardware and purely software solutions as shown in Figure 1.1.

Figure 1.1: ASIP bridges the performance and time-to-market gap

The philosophy of ASIPs is to put to good use the optimized user-defined instruction set and datapath to gain higher performance of computation for certain target applications. From the software designers' point of view, ASIPs offer efficient macros to replace heavily loaded subroutines in software implementation. From the hardware designers' point of view, ASIPs simplify the hardware algorithms by realizing some tedious but uncritical modules in software. The advantages of this arrangement are threefold: 1) High degree of flexibility allows late design change to keep track of the evolving standards. 2) High degree of reusability facilitates rapid retargeting. 3) Tailor-made optimized features breakthrough the performance bottleneck of general-purpose processors.

Design of an efficient ASIP is not a straightforward task. On the one hand, it requires precise judgment to balance the performance and the flexibility. On the other hand, it eliminates over-design and wastage of silicon. This multi-dimensional optimization problem widely covers three areas: hardware logic design; computer architecture design; and application software design, which makes it hard for the designers to search for large amounts of architecture alternatives in order to identify an optimal implementation within a competitive design timeframe.

Another eye-catching technology, asynchronous design methodology [2][3][4] may provide a new opportunity to tackle this problem. Asynchronous design style uses handshake to accomplish communication between modules in order to solve the clock skew problem. The beauty of this communication mechanism inherently provides robust and precisely defined interfaces between modules. By having these interfaces, the specifications of the modules can be precisely defined, and can be

independent of any global timing reference. The design task of a large system is greatly simplified to smaller tasks – design of component modules and verification of their interfaces. Undoubtedly, this is a good practice for designing ASIP efficiently. In addition, this module-based design facilitates design reuse, which means it increases the degree of retargetability of the designed ASIP. By exploring suitable design space for asynchronous technology, it is possible to solve the complex optimization problem.

#### 1.2. Objective and Approach

The objective of this research is to study the way to apply asynchronous technology to ASIP design, and to provide an effective design methodology to optimize an asynchronous ASIP to meet real-time requirements of the target application.

Our work focuses on the optimization of the datapath with its associated instruction-set in order to fulfil the timing criteria for embedded digital signal processing (DSP) applications. Power efficiency is the second concern but is not a major factor in optimization. The other issues about architecture design are also addressed. However, the rest of the ASIP design issues, such as application analysis and software generation, are not covered.

As optimization of the datapath is closely related to the characteristics of the target application and some parameters of the overall architecture, such as memory bandwidth, depth of pipeline stages and degree of computational concurrency, the

following approach is taken to achieve our objective:

- 1. To find an architecture that can maximize the design space of the datapath;

- To find a parameterized extensible architecture that can take advantage of asynchronous technology;

- 3. To find a methodology to design an optimized datapath based on the characteristics of the target application.

The extensible architecture is the centre of our proposed methodology. Further datapath optimization essentially depends on that architecture. For the sake of ease of notation, this extensible architecture is called a "platform" for the rest of the thesis.

#### 1.3. Thesis Organization

The remainder of the thesis is organized as follows:

Chapter 2: Related Work. This chapter gives an outline of the related work in ASIP design methodology and some remarkable achievements in asynchronous technology research.

Chapter 3: Asynchronous Technology. This chapter briefly describes the design style of asynchronous circuits. Afterwards, there is a discussion on the best option for our platform and also on its implementation.

- Chapter 4: Platform-based ASIP Design Methodology. This chapter provides a complete description of the proposed design methodology. The exploration of the design space of the datapath, the architecture of the platform and the overall design flow are addressed.

- Chapter 5: Design of ASIP Platform. This chapter presents the microarchitecture of the platform. It includes functional description of each module, their working mechanism and the design consideration.

- Chapter 6: Case Studies. To prove this design methodology, case studies were conducted. A detailed description of the case studies is available.

- Chapter 7: Conclusion. This chapter summarizes the overall research work.

Perspectives of future work are pointed out.

# 2. RELATED WORK

#### 2.1. Coverage

Presently, there is no publication covering the design methodology that explores advantages of using asynchronous technology in ASIP design. Publications related to asynchronous ASIP design can be separated into two areas: ASIP design methodologies and asynchronous processor methodologies. In order to focus on our objective, the summary of ASIP design methodologies describes only the works that have an explicit treatment on hardware implementation, and the resulting hardware should be in the class of instruction set architecture. The design methodologies mainly on compilation technique, software generation and synthesis of dedicated hardware accelerators are not covered.

For the area of asynchronous design methodologies, we summarize some remarkable asynchronous processor designs in industry and in academia. A detailed discussion of the asynchronous design methodology is given in Chapter 3.

#### 2.2. ASIP Design Methodologies

Existing ASIP design environments can be classified into two approaches. Some design environments are based on predefined processor platforms and provide different architectural options for customization. Other environments provide architecture description languages for the designers to describe their target processor architectures.

Xtensa of Tensilica [5][6], R.E.A.L of Philips[7], ARCtangent-A5 of ARC [8] and Jazz DSP processor of Improv Systems [9] are the commercial design environments using predefined processor platforms approach.

Xtensa of Tensilica is a configurable, extensible and synthesizable RISC (reduced instruction set computer) processor with load store architecture. Its base architecture has a compact 16- and 24-bit instruction set comprising of 80 instructions. The configurable parameters include the choice of 32 or 64 general-purpose 32-bit registers, the size of cache, the write buffer size, and the availability of designer defined instruction execution unit. Designers can define the mnemonic, the encoding, and the semantics of single cycle instructions using TIE language. In addition, the development environment includes ANSI C/C++ compiler, linker, assembler, debugger, code profiler, and instruction set simulator.

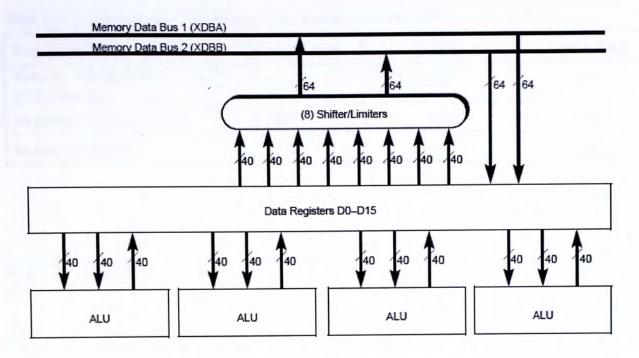

The R.E.A.L of Philips is customizable DSP having two independent 16x16 bit multipliers, four parallel 16-bit ALUs which can be combined into two 40-bit ALUs (including eight overflow bits each), and a number of parallel shifters and saturators in

base architecture. Besides a standard 16- and 32-bit instruction set, there are additional Application Specific Instructions (ASIs), which allow the full parallelism of the DSP to be exploited. The ASI concept allows up to 256 VLIW instructions in a 96-bit width look-up table inside the R.E.A.L. DSP. These are triggered by a special class of 16 bit instructions, stored in the normal programme memory. The ASI look-up table can be a RAM (for prototype chips), ROM, a synthesized netlist, or a combination of these. If the ASI table is implemented in RAM, then its contents can be modified using the JTAG port, or under DSP programme control by writing to dedicated registers within the DSP.

The ARCtangent-A5 of ARC is a four-stage 32-bit RISC processor that can be configured and extended to match the application requirements. Designers can customize the processor in two ways: configuration and extension. Configuration is the ability to change existing features of the processor, such as the main-memory and auxiliary-bus widths; the size and organization of the instruction and data caches; or the size of local memory and DSP XY memory. Extension is the ability to add entirely new features to the processor such as a 32x32-multiply instruction, a USB peripheral and user-defined application-specific extensions. The resulting core is generated to HDL code together with synthesis scripts, simulation make-files, documentation and an automated test environment.

The Jazz DSP processor of Improv Systems is a configurable VLIW processor for their proprietary Programmable System Architecture (PSA). Improv employs this architecture that can scale from a single, uniquely configured Jazz DSP processor core, to a system level platform implementation that consists of many of these uniquely configured Jazz processors in an interconnected structure defined by shared memory maps between the processors. Each processor instance can be customized by custom RTL blocks and instructions to create a designer-defined DSP core. The Jazz PSA Composer Tool Suite provides designers with automatically generated synthesizable HDL code and a full set of software design tools including the debugger, simulator and profiler.

Other design environments using architecture description languages include the design environment of Target Compiler Technologies [10], LISA Processor Design Platform [11][12], MetaCore [13] and PEAS-III [14].

The design environment of Target Compiler Technologies is based on the processor modelling language nML. nML offers designers the abstraction level for describing a processor architecture and instruction set (ISA), which serves as an input to the various tools. nML captures the specification of the processor's instruction set, together with sufficient structural information to enable efficient compilation. Processor designers can describe alternative instruction-set architectures in nML. The support-tools for corresponding architecture are automatically available. Once the architecture has been optimized in nML, the control logics of processor description can be translated automatically into an HDL model. This HDL description can be synthesized with commercially available synthesis tools, for ASIC or FPGA implementation.

The LISA Processor Design Platform (LPDP) tool-suite is based on the machine description LISA. Starting from architecture descriptions in the LISA language,

software development tools can be generated including HLL C-compiler, assembler, linker, simulator, and debugger front end. LISA is a language which aims at the formal description of programmable architectures, their peripherals, and external interfaces. The language elements of LISA enable the description of different aspects of processor architectures like behaviour, instruction set coding and syntax. The language LISA and its generic machine model can produce bit- and cycle/phase-accurate models of systems that consist of programmable architectures and peripheral hardware components. Moreover, synthesizable HDL (VHDL, Verilog, SystemC) code of the target processor can be generated and processed by the standard synthesis tools.

MetaCore is a DSP-oriented ASIP development system that can generate efficient ASIP using benchmark-driven design methodology. The heart of the MetaCore system is a predefined micro-architecture. The design style of the predefined micro-architecture is parameterized and pipelined. The architectural parameters include register file size, bus width, address space of each memory, and bit width of functional blocks. The specification of the target ASIP in the MetaCore system is described using the structural specification language MSL and behavioural specification language MBL. MSL is used to specify the data path structure of the target micro-architecture, while MBL is used to specify the architectural parameters and the behaviour of instructions for the target ASIP. The MSL description consists of declarations of hardware resources such as busses, latches, multiplexer, functional units, and interconnections among the hardware resources. A synthesis tool called SMART is used to translate the given processor specification into the corresponding HDL code of the target ASIP equipped with the user-defined application-specific instructions.

PEAS-III is an architectural level processor design environment based on a micro-operation description of instructions. In the environment, designers model the target processor with the following five items: 1) Architecture parameters such as the number of pipeline stages, the number of delayed branch slots; 2) Declarations of resources to be included in processor (e.g. ALUs, registers); 3) Instruction format definitions which include interrupt conditions and the number of execution cycles of interrupt conditions and the number of execution cycles of interrupt; 5) Micro-operation descriptions of instructions and interrupts. PEAS-III synthesizes the datapath and the control logic of the processor, and generates a simulation model and synthesizable VHDL descriptions of the processor.

#### 2.3. Asynchronous Technology on Processors

Over the past few years, industry and academia have put much effort on asynchronous circuit technology. Their achievements can be concluded by many advanced and sophisticated asynchronous processors. Table 2.1: The summary of asynchronous processors designed by industry and academia gives a summary of asynchronous processors designed by industry and academia.

Table 2.1: The summary of asynchronous processors designed by industry and academia

| Organization and<br>Reference                                | Description                                                                                                                        | Achievements                                                                                                                                                |  |

|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| University of  Manchester, [15][16][17]                      | The Amulet Series. A series of asynchronous ARM processors using self-timed micropipelined VLSI implementation.                    | Successfully delivered the asynchronous processors for commercial use.                                                                                      |  |

| Philips Electronics, [18]                                    | Asynchronous 80C51.                                                                                                                | Four times lower power than a power-optimized synchronous version. Significant reduction of EM emissions.                                                   |  |

| Intel Corporation, [2]                                       | 1) Asynchronous Pentium !!!; 2) Incorporate clockless elements in Pentium 4                                                        | The asynchronous Pentium !!! processor is three times faster and consumes half the power of synchronous counterpart.                                        |  |

| Sharp Corporation, [19]                                      | DDMP Signal Processor. A self-timed data driven multi-media processor aimed at digital television receivers and other applications | Operating at a speed of 8600 Million Operations per Second and with power consumption of less than 1 watt.                                                  |  |

| Caltech, [20]                                                | Asynchronous MIPS R3000. Using asynchronous circuits to implement a deep, fine-grained pipelined MIPS processor                    | R3000 exhibits significantly improved MIPS/watt performance over the synchronous version when scaled to account for different processes and voltages        |  |

| Asynchronous Digital Design Pasadena, Calif, [21]            | 1) Vortex processor; 2) MiniMIPS processor.                                                                                        | MiniMIPS processor is twice as fast as all other designs using the 0.6 micron process in addition to 30 percent less power consumption.                     |  |

| Tokyo Institute of Technology and Tokyo University, [22][23] | TITAC2. A full-featured 32-bit architecture.                                                                                       | Using delay-scaling techniques to improve performance by taking real circuit delays into account, rather than conservatively assuming unbounded gate delays |  |

#### 2.4. Summary

Industry and academia provided convincing demonstrations on asynchronous processors. Their works showed the feasibility and potential performance gain of using asynchronous circuits in processor design. The published ASIP design methodologies do not pay special attention to asynchronous technology. All of them are focused on synchronous designs. None of them explicitly explores the power of asynchronous circuits in ASIP design.

The differentiation of our work against the pervious works is that we consider asynchronous technology as a factor in optimization. We do not consider asynchronous ASIPs as the straightforward translation of synchronous ASIPs. We also focus on the delay insensitive nature of asynchronous circuits in order to explore the opportunity to enhance the design reusability in ASIP design.

# 3. ASYNCHRONOUS DESIGN METHODOLOGY

#### 3.1. Overview

Asynchronous circuits are fundamentally different from its well-known counterpart – synchronous circuits. The operation of asynchronous circuits does not rely on global clock signal as that of synchronous, but on local handshake signals. The handshake signals are basically the control signals in the communication between modules. Different styles of asynchronous circuit implementation may have different handshake protocols [24], for instance, two-phase protocol and four-phase protocol. In essence, all handshake protocols are the composition of request states and acknowledgement states.

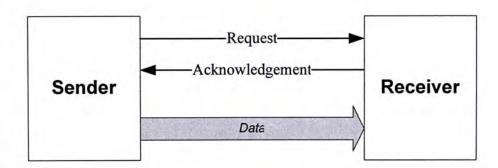

An abstract interface of asynchronous circuits is shown in Figure 3.1. This interface has three channels for communications, request, acknowledgement and data channel between two modules. For simplicity, one module is defined as sender which is a

data provider and another one defined as receiver, a data consumer. When the sender is ready to send data, a request state is asserted. A request signal is sent through the request channel to inform the receiver. (This signal can be transition sensitive, level sensitive or in binary encoded form. This is also true for acknowledgement signal). After receiving this signal, the receiver starts to process the data and sends back an acknowledgement signal when it finishes its work. Then the sender prepares another set of data for next transfer. This data transfer mechanism can safely avoid hazards. This concept is much clearer on asynchronous pipeline, which is discussed in the section on Micropipelines on page 17.

Figure 3.1: An abstract interface of asynchronous circuits

Compared to synchronous circuits, asynchronous circuits have no common or discrete reference time for all modules. There is only local reference time between two communicating modules. This was previously considered a disadvantage, because this violates the beauty of synchronous circuits – all components reference to common and discrete time defined by clock, which is believed to greatly simplify the design work. However, when the clock skew problem becomes significant due to process scaling, asynchronous circuits beat its counterpart in this arena. Besides, according to [25] asynchronous technology offers opportunities in the following areas:

- 1. High performance;

- 2. Low power consumption;

- 3. Low noise and low EMI emission;

- 4. A good match with heterogeneous system timing.

For system integration, asynchronous technology is undeniably a better option than synchronous. Its handshake-based communication mechanism provides a reliable environment for reuse of pre-designed, pre-verified, pre-characterized IP blocks. The freedom of using IP blocks with different specifications offers the highest potential for improving design productivity.

#### 3.2. Asynchronous Design Style

This section is an introduction to different asynchronous design styles. Based on different sizes of communication blocks, three styles are presented – micropipelines, fine-grain pipelining and globally-asynchronous-locally-synchronous design.

#### 3.2.1. Micropipelines

Micropipeline was first introduced in Ivan Sutherlands' Turing Award lecture [26]. Sutherlands designed micropipelines as an asynchronous alternative to synchronous pipelines. From the definition of micropipelines, this is a simple form of event-driven elastic pipeline that contains simple circuitry in each pipeline stage.

Figure 3.2: Micropipeline with processing. (Source: [15])

Figure 3.3: Muller C-element with inverter. (Source: [15])

Figure 3.2 is a typical structure of micropipelines. This circuit operates in two-phase handshake protocol which is based on the signal-transition conceptual framework proposed in [26]. To fit to signal-transition signalling control system, capture and pass latches are used as storage elements. The inputs C and P govern the capture and pass function of the latch, and the outputs Cd and Pd represent "capture done" and "pass done" respectively. When there is a transition occurring at signal C, data will be captured and held in the latch. On the other hand, the latch looks transparent while a transition is present at signal P.

The basic operation of the micropipeline can be easily explained using the events of request and acknowledgement signal. Assuming that all the wires are initially set at zero and all latches are initially transparent, when there is a transition in the request input, then output of the first C-element will be changed from zero to one. This

transition notifies the first latch to capture the data. The latch passes the captured data to the computation logic, at the same time it asserts a pair of request and acknowledgement signals from Cd. The acknowledgement signal is sent back to the data source while the request signal is sent through a delay line to the second stage. The delay line matching the computation logic to the computation is completed before the arrival of the request signal. Meanwhile, the first C-element blocks the request from the data source and waits for an acknowledgement from the second stage. After receiving the request, the second latch captures the data and sends back an acknowledgement, and then the first latch is allowed to capture data again. This operation is repeated when the next request signal arrives, and the data propagates along the pipeline to the output.

Micropipelines have a simple and effective structure. It is easy to implement and easy to achieve high throughput. Also, the latches moderate the flow of data through the pipeline, and can be used to filter out hazards. Thus, any logic structure can be used in the logic blocks, including the straightforward translation of synchronous pipelines.

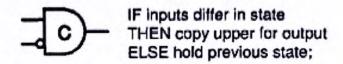

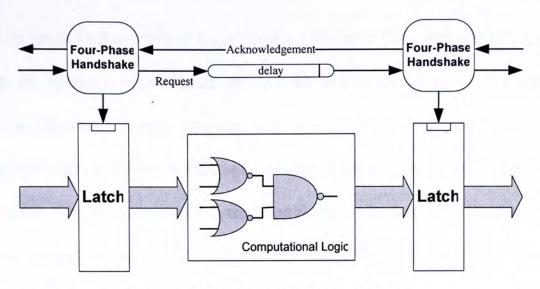

Presently, there are different derivatives of micropipelines. Some designs give up using capture and pass latches but use simple latches with four-phase latch control (Figure 3.4). Some designs involve self-timed logic, which makes the pipeline even more elastic (Figure 3.5).

Figure 3.4: Micropipeline for simple logics

Figure 3.5: Micropipeline for self-timed logics

#### 3.2.2. Fine-grain Pipelining

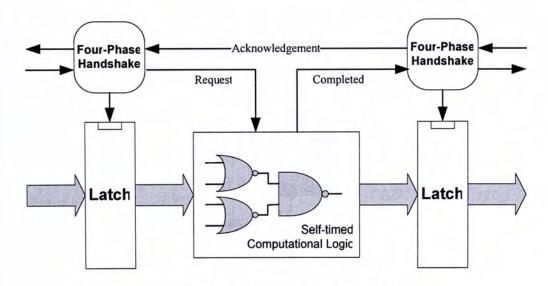

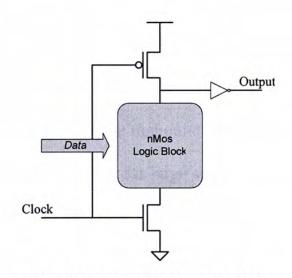

A number of design styles targets higher performance by using much smaller communicating blocks. These styles decompose the design into a fine-grain pipeline. In some aggressive approaches, the critical path of each pipeline stage is limited to a few logic gates [27]. In order to have ultimately high throughput, this kind of design styles adopt a latch-free structure in fine-grain pipelines [28][29], as the capture and pass latch is too slow compared to the computation logic. Differential cascode voltage switch logic (DCVSL) [30] is the spot of this structure.

DCVSL belongs to the dynamic logic family. Similar to the other members, DCVSL operates in alternative precharge phase and evaluation phase [31], but it has differential input and output. The structure of DCVSL is shown in Figure 3.7. It is symmetrical and comprise a pair of domino logics (Figure 3.6). An attractive characteristic for using it in latch-free applications is that DCVSL can hold the evaluated output whereas the input data is changed [32]. Thus, DCVSL can be understood as a combination of the logic and storage elements that are preferred in fine-grain pipelines.

Figure 3.6: Conventional domino logic

Figure 3.7: Differential cascode voltage switch logic (DCVSL)

The operation of DCVSL is similar to conventional dynamic logic. When the request is low, the DCVSL shifts to precharge phase. At this moment the two upper pMOS

are turned on and make the two outputs low. When the request is high, then it is in evaluation phase. Either one of the nMOS logic trees is turned on to change the output to high. A differential output is obtained when the evaluation is completed. This operation mechanism is inherently an incomplete handshake protocol, which can provide a foundation to simplify the handshake logic. On the other hand, the logic can indicate the completion of computation by the differential output. No surplus timing margin is needed in contrast to the worst-case delay line used in micropipelines. Thus, higher performance can be expected.

Fine-grain pipelining is excellent for high speed applications [33][34][35]. However, designing dynamic logic requires more manual effort and incurs much longer design cycles. This design style is not suitable for large scale designs.

#### 3.2.3. Globally-Asynchronous Locally-Synchronous (GALS) Design

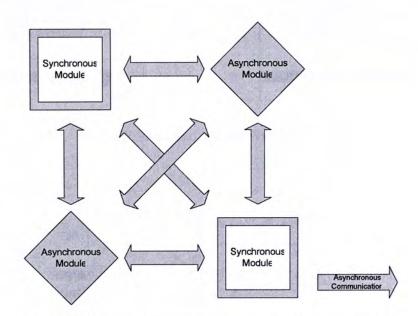

GALS uses largest communication blocks compared to the other two design styles. Its asynchronous communication scheme targets on coarse grained block level whose size can be as large as a finite state machine or an IP. The scope of GALS is also different from that of micropipelines and fine-grain pipelining. Its design philosophy focuses on the interconnection of synchronous blocks with asynchronous technology. This approach partitions the large synchronous system into smaller synchronous blocks and interconnects them with asynchronous handshake protocol. Similar to other asynchronous design styles, the communication among blocks is referenced to local handshake signals, therefore the synchronization can be spread among the system effectively and reliably.

#### Synchronous-Asynchronous Cooperation

In order to carry out asynchronous global communication with others, all synchronous modules are wrapped by an asynchronous interface. This asynchronous wrapper is potentially capable to communicate with purely asynchronous modules as long as they share the same protocol. This is a low cost way to establish synchronous-asynchronous cooperation in a system (Figure 3.8). GALS can bridge synchronous and asynchronous technology together to form a heterogeneous system that is free to make good use of synchronous and asynchronous IPs.

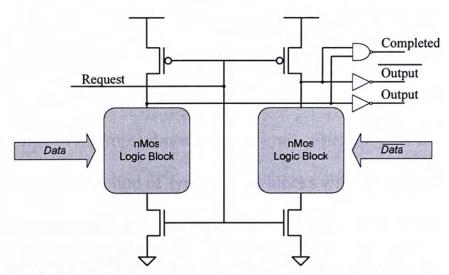

Figure 3.8: Globally asynchronous communication between modules.

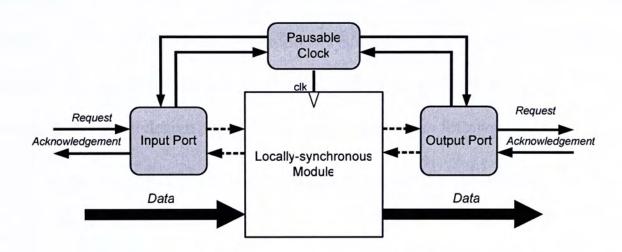

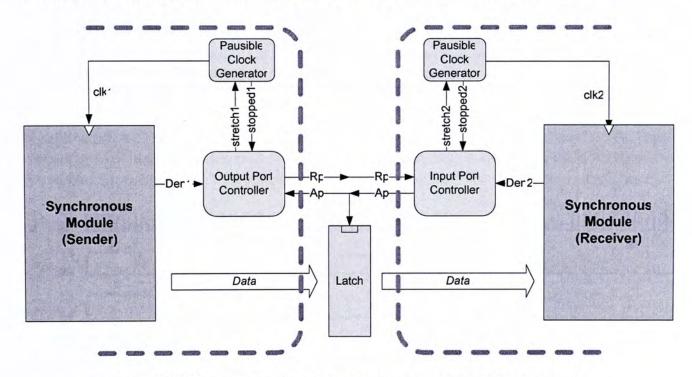

#### Asynchronous Wrappers

The structure of an asynchronous wrapper is illustrated in Figure 3.9. The asynchronous wrapper surrounds a synchronous module aiming to provide a completely asynchronous external interface. All input and output ports of the module are managed by separate port controller. When data enters or leaves the module, the controller bundles the data with handshake signals to ensure its validity in the whole transfer process. Additionally, the asynchronous wrapper provides a local clock

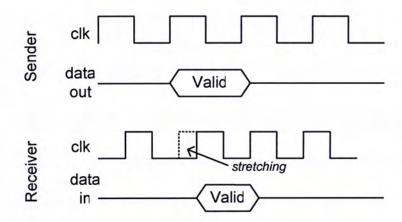

signal for the synchronous module. This clock signal is independent from outside modules in order to fully encapsulate the synchronous module. On the other hand, this clock is generated as stretchable. If incoming data arrives too close to a sampling clock edge, either the clock edge or the data transfer gets shifted to a later point in time in order to avoid being metastable (Figure 3.10).

Figure 3.9: Asynchronous Wrapper

Figure 3.10: Pausible clock while stretching (Other control signals are not shown)

#### Design Methodology of GALS Systems

While asynchronous design technology promises to solve the clock skew problem and favours reuse of IPs, hardware designers are not willing to migrate completely from synchronous to asynchronous in short. The reason is that the design of asynchronous circuits needs special design methodology that has no or very little support from commercial EDA tools. Without dedicated EDA tools, designers have to work out an asynchronous circuit in semi-custom or full-custom manner.

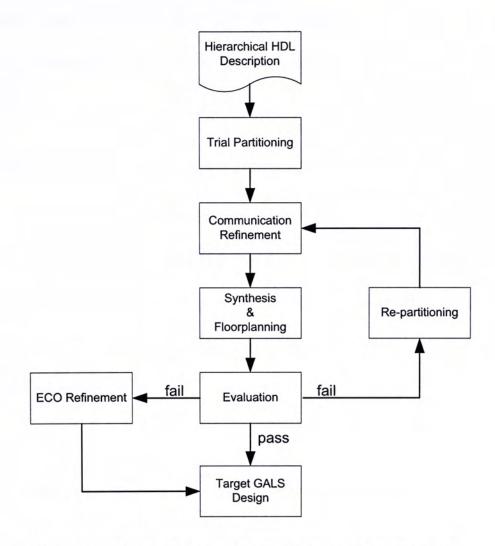

Using GALS is an easier entry point to the asynchronous world. The design methodology of GALS is an extension of the familiar synchronous design methodology. It partitions the synchronous system into optimal size of synchronous modules and redefines the communication among these modules to asynchronous manner. The overall design methodology is summarized as follows:

- At the beginning, the hierarchical description of the synchronous system has to be accomplished.

- 2. According to the structure of hierarchy, a trail partitioning is performed by separating the modules on the first level of hierarchy. If the size of module violates the system specification, that module may be further partitioned into its inner hierarchy or merged with other modules.

- 3. In the communication refinementstage, each module has to be characterized by its operating frequency, the expected throughput and the nature (push or pull mode) of its ports. By considering the requirement of each module and the communication requirement between two modules, suitable asynchronous wrappers can be identified.

- 4. The synchronous modules are synthesized and partitioned in floor planning.

- 5. Finally, the design undergoes evaluation. If the design cannot meet the timing constraints, there are two paths to go. One is to adjust the clock periods of some modules by adding delay in the layout. If the result is too bad or the

clock period of each module is already fine tuned, the design has to be re-partitioned and its communication redefined.

Figure 3.11: The GALS design methodology (modified from [36])

Hardware designers can maintain synchronous design methodology to implement the computation and control parts of the whole GALS system, and need to pay more attention to and manual effort on the asynchronous wrappers only. As time-to-market and design efficiency are the number one considerations, the GALS design style is the best among micropipelines and fine-grain pipelining.

# 3.3. Advantages of GALS in ASIP Design

Design of ASIP is not only an arena of performance, but also is an arena of time-to-market and design efficiency. To take this into account, our ASIP platform is designed with the GALS design style. There are three points to support our choice.

#### 3.3.1. Reuse of Synchronous and Asynchronous IP

Design reuse can greatly improve time-to-market. Designers are now seriously exploring opportunity for reusing IPs to compose a system. The GALS design is the pioneer in this area. It has the freedom to use the mixture of synchronous IPs and asynchronous IPs The exploration space of the GALS design in IP reuse is much wider than other design styles.

#### 3.3.2. Fine Tuning of Performance and Power Consumption

Using multiple frequency and voltage in a system is recognized to be an aggressive power saving and performance tuning strategy [36]. In GALS systems, all modules are perfectly encapsulated. All modules are isolated from one another, and do not reference to a correlated clocking system. Their communication is controlled by reliable handshakes, and therefore GALS systems are adaptive to change of timing. Using GALS, designers are empowered to use fine grained frequency and voltage scaling, even a dynamic one to compose the target system. The design space of power efficient ASIP can be further widened.

#### 3.3.3. Synthesis-based Design Flow

The push factor for using asynchronous is that designers have to work in transistor level or standard cell level to some extent. For GALS, this adverse factor no longer exists. Muttersbach reported a set of almost synthesizable asynchronous wrappers in [37]. Only one cell has to be designed at layout level. Designers are allowed to use behavioural model or register transfer level (RTL) model to describe GALS designs.

# 3.4. Design of GALS Asynchronous Wrapper

To realize a GALS processor, a set of input- and output-port controllers for asynchronous wrappers is designed based on [37]. The input port module is also reused in our design. Different from Muttersbach's design, our wrappers are fully synthesizable.

#### 3.4.1. Handshake Protocol

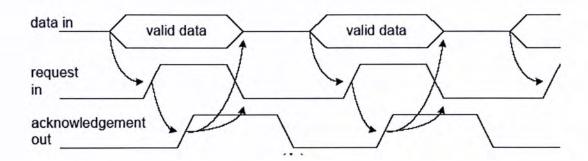

For the asynchronous communication channel, the four-phase handshake protocol is selected. The timing diagram of the protocol is illustrated in Figure 3.12. In four-phase protocol, valid data is accompanied by a pair of request and acknowledgement signals. When the data is ready for the receiver, the send sets the request signal to high. The data is guaranteed to be valid until the request is dropped. After getting the request signal, the receiver takes the data and sends back an acknowledgement signal. Then the sender can set the request to low and process another set of data.

Four-phase handshake protocol is level sensitive. It can interface with memory naturally and control the latches effectively. Compared to two-phase one, four-phase protocol is more robust because the data is wrapped by the request signal. The invalid data can also be indicated by the low request signal.

Figure 3.12: Timing diagram of the four-phase handshake protocol

#### 3.4.2. Pausible Clock Generator

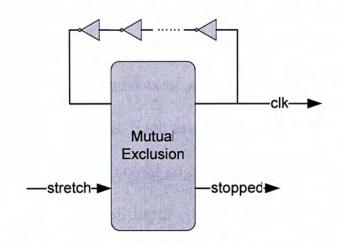

The pausible clock generator is an important component in asynchronous wrappers. The module either establishes or is requested for synchronization with another module, and the period of the clock is stretched to match the clock of another one. The port controllers are entitled to govern the stretch of the clock by sending a stretch signal to stop the clock. As the clock keeps oscillating, it is possible for the stretch signal to get too close to the clock edge leading to the state of being metastable. A mutual exclusion (ME) element is used in the pausible clock to decide which one can take over the control.

The structure of the pausible clock is shown in Figure 3.13. A ring oscillator is used instead of crystal oscillators or PLL in order to be able to have full control of the clock generation. To provide a control interface and to resolve the competition of the

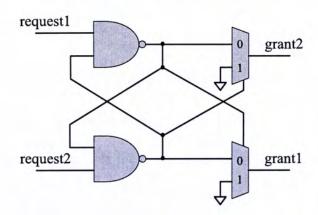

clock and the stretch signal, an ME is inserted to the inverter chain of the ring oscillator. Figure 3.14 shows the structure of ME. This element serves the request signals on a first-come-first-served basis. Only the first coming request signal can invoke the corresponding grant. If the two signals arrive concurrently, the ME selects one to pass arbitrarily. The two grant signals are guaranteed to be mutually exclusive. In the operation of the plausible clock generator, the ME is normally transparent to the ring oscillator. Once the stretch signal wins the control, the ME blocks the inverter chain and lowers the clock signal. At the same time, the stopped signal is asserted. The ring oscillator can be recovered unless the stretch signal is released.

Figure 3.13: Pausible Clock Generator

Figure 3.14: Mutual Exclusion

#### 3.4.3. Port Controllers

Another component in asynchronous wrapper is port controllers. The function of data port controllers is to handle the handshake protocol and to control the local pausible

clock. As the port controllers operate in the absence of the clock, they are designed as asynchronous finite state machines (AFSMs). Unlike synchronous finite state machines (FSM), an AFSM has the potential problem of output hazard for multiple input changes. To solve the hazard problem, our controllers are captured by the extended burst-mode specification [38]. This kind of AFSM can be triggered by input bursts – transition signalling, therefore, signals from the synchronous module can trigger the port controller in every cycle.

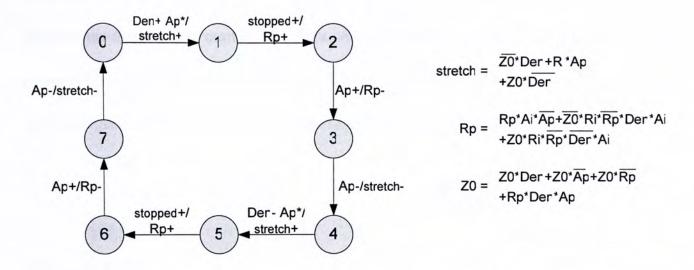

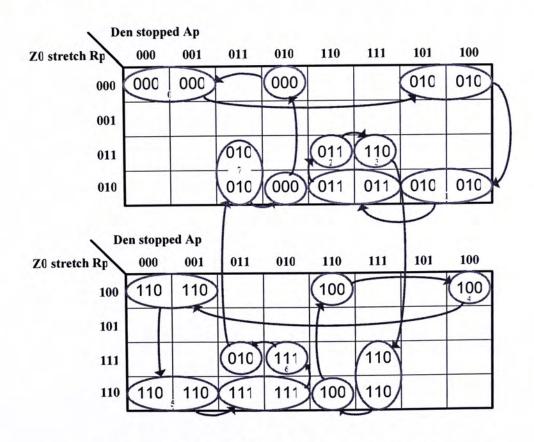

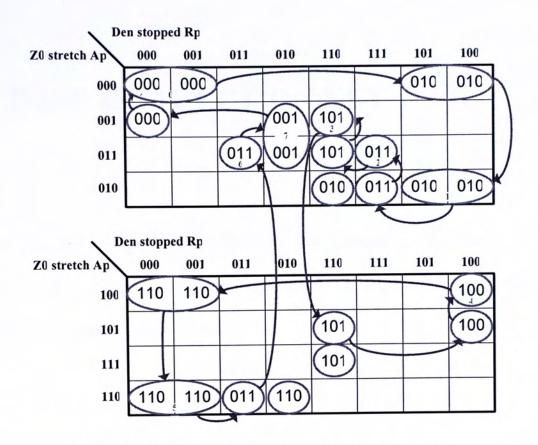

The extended burst-mode specifications of our port controllers are depicted by Figure 3.15 and Figure 3.16. An extended burst-mode asynchronous finite state machine is specified by a state diagram which consists of a finite number of states, and a set of directed arcs connecting pairs of states. Each arc indicates the transition between two states and is labelled with two sets of signal edges comprising the input burst and the output burst. In a given state, when all input edges appear, the machine generates a set of output changes and moves to a new state.

For the output port controller, *Den* is the enable signal for the start of handshake. A transition of *Den* from low to high triggers the AFSM to enter state 1 from state 0 and lift *sketch* to high. Then the AFSM moves to state 2 when there is a positive transition of *stopped*. Walking through the AFSM state by state, the handshake sequence is accomplished in state 4. The AFSM waits for the negative transition of *Den* this time. The rest of the states repeat works of state1 to 3.

To implement port controller, the specifications are translated to 3D machines and

are synthesized with the method mentioned in [38]. A detailed description of the synthesis can be found in appendix A. The results of the synthesis are available in Figure 3.15 and Figure 3.16.

Figure 3.15: The extended burst-mode specification and the logical implementation of the output port controller

Figure 3.16: The extended burst-mode specification and the logical implementation of the input port controller

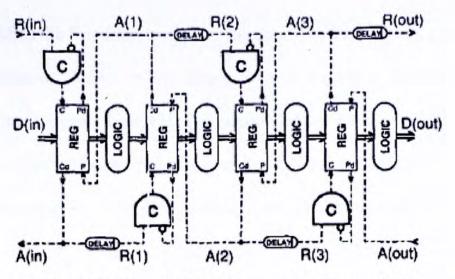

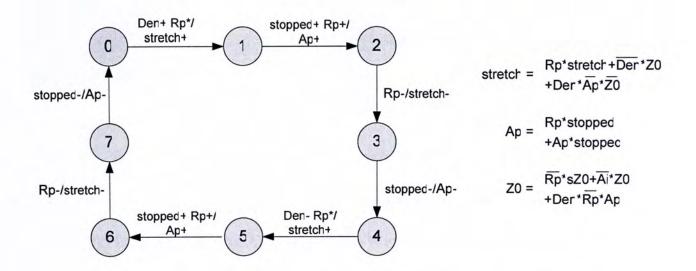

A one-way asynchronous communication channel between two modules is configured as in Figure 3.17. The input port controller and output port controller play different roles in the data transfer mechanism. Output port controller is the one to establish the communication channel. When the sender module activates the output

port controller with Den+, the local clock is stretched. An event of Rp+ is sent to the receiver module immediately after the clock is stopped. If the input port controller is already activated, it stretches the clock signal in the presence of Rp+, and replies with an Ap+ as soon as the local clock is stopped. Simultaneously, the Ap+ commands the latch to capture the data. After detecting the Ap+, the Rp+ is released to Rp-. The receiver feedbacks with an Ap- and recovers the local clock to sample the data captured in the latch. And the sender can recover its clock eventually.

Figure 3.17: The configuration of an asynchronous communication interface

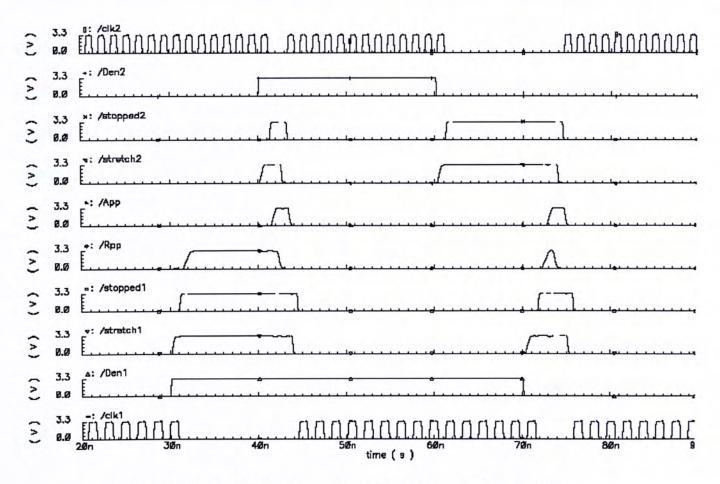

#### 3.4.4. Performance of the Asynchronous Wrapper

To evaluate our design, spice level simulations are performed using AMS 0.35um CMOS technology. The unit under simulation is configured as in Figure 3.17. The sender module runs with nominal frequency of 540MHz and the receiver with 680MHz. The waveform in Figure 3.18 shows the simulated behaviour of the communication channel. From the waveform, the transfer of data takes about 3.1ns on average. This value is the time difference between the first positive clock edge that initiates the data transfer and the sampling clock edge of the receiver, which is

defined as the communication overhead of the channel.

There are also some simulations of the mutual exclusion element and the pausible clock generator. The simulation results are summarized in Table 3.1.

Table 3.1: Simulation results of the asynchronous wrapper

| Component                | Parameter               | Value  |  |

|--------------------------|-------------------------|--------|--|

| Asynchronous Interface   | Communication Overhead  | 3.1ns  |  |

| M.A. IE-I                | Latency                 | 0.45ns |  |

| Mutual Exclusion         | Response Time           | 0.15ns |  |

| Pausible Clock Generator | Maximum Clock Frequency | 1.7GHz |  |

Figure 3.18: The simulated waveform of the communication channel

# 3.5. Summary

This chapter describes three asynchronous design styles: micropipelines, fine-grain pipelining and GALS design. The GALS design style has been chosen for our platform for three reasons: 1) It is heterogeneous and supports the mixture of synchronous and asynchronous IPs; 2) It widens the design space by allowing the designers to fine-tune the voltage and the frequency of each module. 3) It has a synthesis-based design flow.

The design of the asynchronous wrapper based on the work of [37] has been presented at the end. We have designed a set of fully synthesizable components – pausible clock generator, input- and output- port controllers. The design methodology of each component and their behaviour have been discussed. From the spice-level simulation, it is found that the communication overhead of our wrapper is about 3.1ns on average.

# 4. PLATFORM BASED ASIP DESIGN METHODOLOGY

# 4.1. Platform Based Approach

The asynchronous design style is excellent for system integration. Local handshake interfaces allow seamless communication of modules with heterogeneous timing. Modules can be put together in an ad-hoc manner on the ground of sharing common handshake protocol. In ASIP design, it is obvious that some architectural parameters, especially the datapath, have to be changed iteratively in the optimization cycle. To take full advantage of the asynchronous design style, the target processor can be realized by adding modules to expand and customize the functionality of the base processor. This approach has several advantages:

- 1. The complexity of optimization, software generation can be lowered.

- 2. Accurate application profiling is possible.

- 3. The real-time performance of the whole system can be evaluated at an early

stage.

- 4. The base processor can be reused from design to design.

- 5. The design cycle can be shortened substantially.

- 6. The target processor is capable of being modified/upgraded in order to keep track of the evolving application needs.

The effectiveness and efficiency of this approach largely depends on the base processor. The design methodology used in this research is also based on a base processor. We call the used base processor a 'platform'.

#### 4.1.1. The Definition of Our Platform

Our platform is a base processor environment that provides sufficient facilities for developing the target processor. It is a semi-finished product with general functions for the target application domain. It provides maximum freedom for application-specific customization. For this research, the platform is an extensible architecture that targets on embedded DSP applications. It supports rapid assembly and modification among synchronous and asynchronous modules. The target processor can be built on top of it.

#### 4.1.2. The Definition of the Platform Based Design

The platform based design is a design methodology based on the foundation provided by the platform. Design begins in the middle of the whole process. The design philosophy is to scale up the datapath of the platform and to customize its architectural parameters to meet the real time requirements of the target application.

It is a straightforward way to design a complex system.

# 4.2. Platform Architecture

The platform is the centre of our design methodology. Its characteristics outline the functionality and the performance of the target processor. The quality of the platform is determined by three factors: 1) the design space of its datapath; 2) the customization options; 3) the coverage of target application domain. These three factors decide how much performance can be improved in the optimization and how tight the functionality can be coupled to the target application.

In this section, we derive the architecture of our platform from the nature of DSP algorithms. By investigating the DSP applications, the maximum desired design space of the datapath and the elements needed for performance enhancement can be identified. The extensible architecture of the platform is tailored for carrying these features in order to give the largest room for optimization.

## 4.2.1. The Nature of DSP Algorithms

A generic DSP system, as shown in Figure 4.1, consists of one or more input signals being processed by a digital circuitry to produce an output with the desired characteristics. The characteristics of the system can be described by mathematical models which is the transfer function H(z) in the z-transform domain. Although a complete system can perform very complex functions, the majority of signal processing operation can be broken down into a combination of the primitive

mathematical operations listed in Table 4.1.

Figure 4.1: A digital signal processing system

Table 4.1: DSP primitive mathematical operations

Finite Impulse Response (FIR) Filter

$$y(n) = \sum_{k=0}^{N-1} a_k x(n-k)$$

Infinite Impulse Response (IIR) All-Pole Filter

$$y(n) = \sum_{k=1}^{N-1} a_k y(n-k) + x(n)$$

General Filter

$$y(n) = \sum_{k=0}^{N-1} a_k x(n-k) + \sum_{l=1}^{M-1} b_l y(n-l)$$

Cross-Correlation

$$C_{xy}(m) = \frac{1}{N} \sum_{n=0}^{N-1} x(n) y(n+m)$$

Discrete Fourier Transform

$$X(n) = \sum_{k=0}^{N-1} x(n) e^{-j2\pi k \frac{n}{N}}$$

Autocorrelation

$$C_{xy}(m) = \frac{1}{N} \sum_{n=0}^{N-1-m} x(i) x(i+m)$$

DSP has been widely used in many areas, such as speech synthesis and recognition, computer vision systems, control systems and digital communications. Many different kinds of algorithms have been devised for different applications. But most of the algorithms share some common characteristics, providing us with priori knowledge to make use of. We outline those that are closely related to the performance of a DSP application.

## Computation-Intensive Kernels

Kernels are pieces of computational algorithms that make up the heart of the DSP application. They are typically in the form of nested short loops that involve intensive computation. The kernels often occupy the largest share of the computation power, thus affecting the peak performance of the application.

## **Strong Data Locality**

DSP applications tend to access data in a relatively small block of memory. Large displacement of data address is infrequent. On the other hand, the data access pattern is regular. For filters, correlations and most of the matrix operations, the data is accessed in circular addressing with constant steps (Figure 4.2a). More sophisticated bit-reversed addition pattern (Figure 4.2b) is used for butterfly-like transformations

| K | address | K | address |     |                                        |

|---|---------|---|---------|-----|----------------------------------------|

| С | С       | С | 000     | = C |                                        |

| 1 | 3       | 1 | 100     | = 4 |                                        |

| 2 | €       | 2 | 010     | = 2 |                                        |

| 3 | ç       | 3 | 110     | = 6 |                                        |

| 4 | 12      | 4 | 001     | = 1 | Ada 1 to MSB in each iteration         |

| 5 | 15      | 5 | 101     | = 5 |                                        |

| 6 | 2       | € | 011     | = 3 | The carry                              |

| 7 | 5       | 7 | 111     | = 7 | propagates from<br>MSB to LSB          |

| 8 | 8       | 8 | 000     | = C | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ |

|   | (a)     |   |         | (b) |                                        |

Figure 4.2: (a) Circular addressing of size 16 and step 3 at iteration K; (b) Bit-reversed addressing of 3 bits in size at iteration K

#### Explicit and Implicit Instruction Level Parallelism

DSP applications possess a high degree of instruction level parallelism (ILP), especially in the kernels. For simplicity without losing generality, parallelism exploration of a two-tap FIR filter is demonstrated as an example. The mathematical formulation of a two-tap FIR filter is  $y(n) = \sum_{k=0}^{1} a_k x(n-k)$  and the algorithm and the corresponding data flow graph (DFG) are depicted by Figure 4.3. From the algorithm, it can be found that the two multiplications can operate in parallel. This is the explicit parallelism of this algorithm. However, the parallelism is not limited to this level. There is implicit parallelism that can be explored by doing transformation on the algorithm.

Figure 4.3: (a) The algorithm of a two-tap FIR filter; (b) The corresponding DFG. The vertical bar represents a delay element

One of the transformation techniques is unfolding. The summation series of the two-tap FIR can be split into two summation series:

$$y(n) = \sum_{k=0}^{1} a_k x(n-k) = \begin{cases} y(2n) = a_0 x(2n) + a_1 x(2n-1) \\ y(2n+1) = a_0 x(2n+1) + a_1 x(2n) \end{cases}$$

Each of them is represented by a new DFG. Due to the dependency of the two summation series, the two DFG can be merged as in Figure 4.4b. From this new

complete DFG, there are four parallel operations discovered  $(A_0, A_1, B_0, B_1)$  which are double the original one. The unfolded algorithm is shown in Figure 4.4a. This demonstration only unfolds the algorithm to two levels. For a higher degree of parallelism, the algorithm can be further unfolded.

Figure 4.4: (a) The unfolded algorithm of a two-tap FIR filter; (b) The corresponding DFG

Figure 4.5: (a) The arbitrary algorithm with heavy data dependence; (b) The corresponding DFG

Some algorithms carry heavy data dependence in which some synchronization is necessary between operations of various iterations. An arbitrary algorithm of this kind is shown in Figure 4.5a and its DFG in Figure 4.5b as an example. The data dependence between one iteration and the successive iteration prohibits parallelism as that in the two-tap FIR filter. Another transformation technique, software

pipelining can unveil some potential parallelism in such cases. The idea behind software pipelining is that the body of a loop can be reformed so that one iteration of the loop can start before previous iterations finish executing. The reformed body of the algorithm is shown in Figure 4.6a. The arrows indicate the data dependence of two operations. Figure 4.6b shows the result of the transformation. The maximum level of parallelism gains to four.

```

tc A(1) = A(C) * X(C)

t1 B(C) = A(C) + E A(2) = A(1) * X(1)

t2 C(C) = B(C) B(1) = A(1) + E A(3) = A(2) * X(2)

for r = C to N-2

t4 Y(n) = aC * C(n) C(n+1) = A(n) + B(n+1) B(n+2) = A(n+2) + E A(n+4) = A(n+3) * X(n+3)

end

tE Y(N-2) = aC * C(N-2) C(N-1) = A(N-2) + B(N-1) B(N) = A(N) + E

t6 Y(N-1) = aC * C(N-1) C(N) = A(N-1) + B(N)

t7 Y(N) = aC * C(N)

```

Figure 4.6: (a) The reformed body of the arbitrary algorithm (b) The software pipelined arbitrary algorithm

#### Data Parallelism

In some DSP applications, the data sets have an extremely high degree of internal parallelism, which means that all the elements of the data sets can be processed simultaneously. Matrix is an example. Matrix itself is a large data set that consists of

an array of data. There is no crucial relationship among the data. Only the spatial relationship of each data is important. Computer vision and image processing use this kind of data representation. Their computation is on images consisting of a large array of pixels.