University of Warwick institutional repository: http://go.warwick.ac.uk/wrap This paper is made available online in accordance with publisher policies. Please scroll down to view the document itself. Please refer to the repository record for this item and our policy information available from the repository home page for further information.

To see the final version of this paper please visit the publisher's website. Access to the published version may require a subscription.

Author(s): M. J. Palmer, G. Braithwaite, T. J. Grasby, P. J. Phillips, M. J. Prest, E. H. C. Parker, and T. E. Whall, C. P. Parry, A. M. Waite and A. G. R. Evans

Article Title: Effective mobilities in pseudomorphic Si/SiGe/Si p-channel metal-oxide-semiconductor field-effect transistors with thin silicon capping layers

Year of publication: 2001

Link to published version: http://dx.doi.org/10.1063/1.1354662

Publisher statement: None

APPLIED PHYSICS LETTERS VOLUME 78, NUMBER 10 5 MARCH 2001

## Effective mobilities in pseudomorphic Si/SiGe/Si *p*-channel metal-oxide-semiconductor field-effect transistors with thin silicon capping layers

M. J. Palmer, G. Braithwaite, a) T. J. Grasby, P. J. Phillips, M. J. Prest, E. H. C. Parker, and T. E. Whall

Department of Physics, University of Warwick, Coventry CV4 7AL, United Kingdom

## C. P. Parry

University of Stuttgart, Inst. Halbleitertechnik, D 70049 Stuttgart, Germany

## A. M. Waite and A. G. R. Evans

Department of Electronics and Computer Science, University of Southampton, Highfield, Southampton SO17 1BJ, United Kingdom

## S. Roy, J. R. Watling, S. Kaya, and A. Asenov

Department of Electronics and Electrical Engineering, University of Glasgow, Rankine Building, Oakfield Avenue, Glasgow G12 8QQ, United Kingdom

(Received 20 September 2000; accepted for publication 18 January 2001)

The room-temperature effective mobilities of pseudomorphic Si/Si $_{0.64}$ Ge $_{0.36}$ /Si p-metal-oxide-semiconductor field effect transistors are reported. The peak mobility in the buried SiGe channel increases with silicon cap thickness. It is argued that SiO $_2$ /Si interface roughness is a major source of scattering in these devices, which is attenuated for thicker silicon caps. It is also suggested that segregated Ge in the silicon cap interferes with the oxidation process, leading to increased SiO $_2$ /Si interface roughness in the case of thin silicon caps. © 2001 American Institute of Physics. [DOI: 10.1063/1.1354662]

Incorporation of pseudomorphic SiGe layers into Si complementary metal-oxide-semiconductor (CMOS) technology has prospects of improving the hole channel mobility to approach that of the bulk silicon electron channel. SiGe metal-oxide-semiconductor field effect transistors (MOSFETs) normally require a Si spacer between the SiO<sub>2</sub> and the SiGe layer to avoid the pile up of unoxidized Ge behind the oxide front (snow plow effect) which leads to a degradation of the oxide/semiconductor interface quality. 1-3 The maximum benefit from incorporation of SiGe in CMOS may expected to occur when the alloy layer is placed as close as possible to the oxide. Unfortunately, as Ge content or alloy growth temperature increases, strain-driven long range roughening of the upper Si/SiGe heterointerface may occur<sup>4</sup> which sets a limit on the Si cap thickness. Previously, when this type of material was oxidized to retain a 2.5 nm Si capping layer, there was a severe degradation in mobility with the observation of oxide pinholes.

Here, we report electrical measurements on pseudomorphic Si/Si<sub>0.64</sub>Ge<sub>0.36</sub>/Si *p*-metal-oxide-semiconductor (*p*-MOS) devices fabricated from solid source molecular beam epitaxial (SS-MBE) material grown using a low growth temperature (450 °C), postgrowth anneal (800 °C) technique.<sup>5</sup> The pseudomorphic Si<sub>0.64</sub>Ge<sub>0.36</sub> layers have interfaces<sup>5</sup> without the strain-induced interface roughness that is associated with higher temperature growth and thus these structures are well suited for incorporation into SiGe/MOS technology. The final Si capping layer thicknesses obtained after oxidation were measured by a combination of x ray, cross-

sectional transmission electron microscopy (TEM) and capacitance-voltage (C-V) measurements, to within an accuracy of ±0.2 nm. Devices were fabricated in a standard CMOS-type process, but with a reduced thermal budget (maximum 850 °C, 60 s) to maintain the integrity of the SiGe layer. Oxide growth was by dry thermal oxidation at 800 °C. The gate material is in situ boron doped polysilicon and source and drain contacts are conventional high doped BF<sub>2</sub> ( $5 \times 10^{15}$  cm<sup>-2</sup>, 50 keV) implants. Two different *n*-type substrate doping concentrations  $(N_{sub})$  were used,  $2\times10^{17}\,\mathrm{cm}^{-3}$  (batch A) and  $5\times10^{15}\,\mathrm{cm}^{-3}$  (batch B), to investigate punchthrough and drain induced barrier lowering effects which occur at short device channel lengths. A nominally undoped 100 nm Si buffer layer was grown on the substrate, followed by a  $Si_{0.64}Ge_{0.36}$  layer of thickness 10 nm. A range of values of the Si capping layer were chosen such that the final values after process cleans and oxidation would be between 2 and 8 nm.

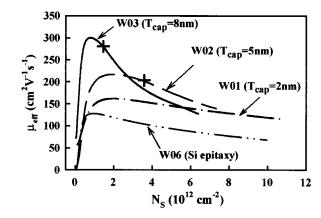

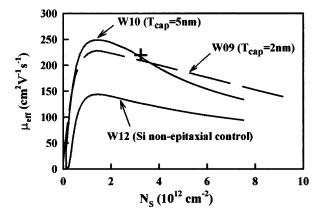

To determine the effective carrier mobility,  $\mu_{\rm eff}$ , we have used a modified "split-C-V" technique on large area FETs of length = 300  $\mu$ m and width = 50  $\mu$ m. Figures 1 and 2 show plots of  $\mu_{\rm eff}$  as a function of total carrier sheet density ( $N_S$ ) for devices fabricated in batches A and B, respectively. The crosses on the plots for W02, W03, and W10 indicate points where marked decreases in effective mobility occur as the total carrier density increases. Simulations indicate that these points are where parasitic conduction at the Si/SiO<sub>2</sub> interface begins to affect the transport characteristics of the device. It should be noted that for both W01 and W09 (nominal 2 nm Si cap), and the Si control (W06), we do not observe any such change in slope ( $d\mu_{\rm eff}/dN_s$ ) in the range of

a)Electronic mail: phseg@warwick.ac.uk

FIG. 1. Batch (A), effective mobility vs carrier sheet density for devices with a  $2 \times 10^{17}$  cm<sup>-3</sup> substrate doping punchthrough stopper. The observed onset of conduction at the SiO<sub>2</sub>/Si interface is marked by a cross (+).

measured data, and this is consistent with our simulations. There is clearly a dependence of peak effective mobility on Si capping layer thickness, with wafer W03, the 8 nm Si capped sample, exhibiting a maximum factor of 2.44 increase (305 cm $^2$  V $^{-1}$  s $^{-1}$ ) when compared to the W06 Si standard (125 cm $^2$  V $^{-1}$  s $^{-1}$ ).

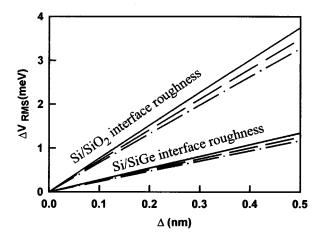

Lander et al., Whall and Parker, and Kearney and Horrell<sup>9</sup> have provided strong evidence that interface roughness rather than alloy scattering plays a dominant role in limiting the hole mobility in devices of this type. To determine the effect of thickness fluctuations,  $\Delta$ , in the SiO<sub>2</sub> insulator and Si cap, we have evaluated the associated fluctuations in the electrostatic potential<sup>10</sup> at the Si/SiGe interface using a self-consistent solution of Poisson's and Schrödinger's equations. To compare structures with different Si cap or oxide thicknesses the carrier sheet density in the channel was kept at a constant value of  $1.0 \times 10^{12} \,\mathrm{cm}^{-2}$ , low enough to ensure that the Si cap would not be populated. The rms potential fluctuation,  $\Delta V$ , is plotted as a function of rms roughness amplitude in Fig. 3 for typical values<sup>9,11</sup> of Si/ SiGe and Si/SiO<sub>2</sub> interface roughness,  $\Delta$ . It is clear that, for the current specifications, the scattering potential is more sensitive to fluctuations in oxide rather than Si capping layer thickness. In this respect, the situation is similar to the scattering of silicon inversion layer electrons by remote metal/ oxide interface roughness.<sup>12</sup> Typical oxide fluctuations of  $\Delta_{\text{oxide}} \sim 0.2$  nm will generate a rms scattering potential of

FIG. 2. Batch (B), effective mobility vs carrier sheet density for devices without a punchthrough stopper. The observed onset of conduction at the  $SiO_2/Si$  interface is marked by a cross (+).

FIG. 3. Calculated rms interface roughness scattering potential ( $\Delta V$ ) due to rms thickness fluctuations,  $\Delta$ , at the SiO<sub>2</sub>/Si interface and at the upper Si/SiGe interface for values of different Si capping layer thickness. Solid lines: 2 nm Si cap; dashed lines: 5 nm Si cap; dot–dashed lines: 8 nm Si cap.

$\sim$ 1.4 meV. To obtain the same scattering potential, the alloy thickness fluctuations ( $\Delta_{\rm SiGe}$ ) must be 0.4 nm. This difference is attributed to the lower dielectric constant in SiO<sub>2</sub>. The interface roughness limited mobility  $\mu_{\rm IR}$  is predicted to behave as  $^{10}$

$$\mu_{\rm IR}^{\alpha}(\Delta V)^{-\beta} \tag{1}$$

with  $\beta=2$ .

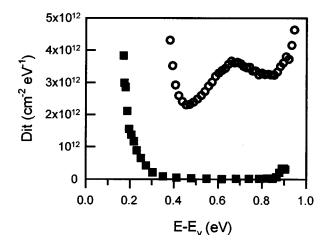

In the presence of other scattering mechanisms, e.g., phonon scattering, the resultant mobility will be expected to have a  $\beta$  value of less than 2. However, comparing our experimental results (Fig. 1) with calculated values of  $\Delta V$  using constant  $\Delta$  (Fig. 3) and constant effective field of 0.15 MV/cm<sup>-1</sup> ( $N_s$  = 1.5×10<sup>12</sup> cm<sup>-2</sup>) we deduce a value of ~3. This high value appears to be associated with the degradation of SiO<sub>2</sub>/Si interface quality with decreasing silicon cap thickness, due to segregation/diffusion of Ge into the cap.<sup>5</sup> Interface state densities,  $D_{it}$ , for these samples were deduced from quasistatic C-V measurements and from a comparison of low frequency and high frequency C-V data. Figure 4 shows plots of  $D_{it}$  versus energy (measured from the valence band edge of silicon) for wafer W01 (batch A). The

FIG. 4. Interface trapped charge density distributions vs energy measured from the valence band edge of silicon. Samples shown are W01, 2 nm Si cap (○) and W06, epitaxial Si control (■).

Downloaded 06 Jul 2009 to 137.205.202.8. Redistribution subject to AIP license or copyright; see http://apl.aip.org/apl/copyright.jsp

TABLE I. Maximum effective mobility,  $\mu_{\rm eff}({\rm max})$ , vs capping layer thickness,  $T_{\rm cap}$ . Also shown are the interface trap densities,  $D_{\rm it}$ , measured at midgap or at the peak in the energy distribution of  $D_{\rm it}$ , shown in Fig. 3. Samples marked  $\dagger$  are silicon controls.

| Wafer<br>No. | $N_{\rm sub}$ (cm <sup>-3</sup> )                        | T <sub>cap</sub> (nm) | $\mu_{\text{eff}}(\text{max})$ $\text{cm}^2  \text{V}^{-1}  \text{s}^{-1}$ | $\begin{array}{c} D_{\rm it} \\ ({\rm cm}^{-2}{\rm eV}^{-1}) \end{array}$ |

|--------------|----------------------------------------------------------|-----------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------|

| W01(a)       | $2 \times 10^{17}$                                       | 2                     | 162                                                                        | $3.8 \times 10^{12}$ $5 \times 10^{11}$                                   |

| W02(a)       | $2 \times 10^{17}$                                       | 4.5                   | 217                                                                        |                                                                           |

| W03(a)       | $2 \times 10^{17}$ $2 \times 10^{17}$ $2 \times 10^{17}$ | 8                     | 305                                                                        | $<2\times10^{11}$                                                         |

| †W06(a)      |                                                          | 24                    | 128                                                                        | $<2\times10^{11}$                                                         |

| W09(b)       | $\sim 5 \times 10^{15}$                                  | 2                     | 228                                                                        | $8 \times 10^{11}$                                                        |

| W10(b)       | $\sim 5 \times 10^{15}$                                  | 5                     | 249                                                                        | $<1 \times 10^{11}$ $5 \times 10^{10}$                                    |

| †W12(b)      | $\sim 5 \times 10^{15}$                                  | 0                     | 144                                                                        |                                                                           |

peak at  $\sim 0.7$  eV has been seen previously by Goh et al.<sup>3</sup> and has been attributed to Si dangling bonds at the oxide interface, the generation of which is enhanced in the presence of Ge. The maximum mobilities,  $\mu_{\text{max}}$ , for given silicon cap thicknesses are shown in Table I, together with the interface trap densities,  $D_{it}$ , either at an observable peak or at midband. There is a clear correlation between  $\mu_{\text{max}}$  and  $D_{\text{it}}$  for samples containing SiGe in batch A. As might be expected,  $\mu_{\rm max}$  is lower in the epitaxial Si control (W06) because of the larger effective mass, the absence of light hole/heavy hole splitting and the proximity of the SiO<sub>2</sub>/Si interface. Samples of batch B were grown at a slightly lower growth temperature ( $\sim$ 430 °C), and since we observe a higher  $\mu_{\text{max}}$  for a given cap thickness, this implies that there is less Ge segregation. Nevertheless, the SiGe samples show the same correlation with  $D_{it}$  as those in batch A. These SiO<sub>2</sub>/Si interface states, if charged, would not be expected to give rise to appreciable scattering of carriers in the buried alloy. 14 We suggest that an increased roughening of the SiO2/Si interface accompanies the generation of these interface states, possibly due to the presence of microscopic clusters of SiGe which may have a different rate of oxidation from silicon. 15 This roughness would be responsible for the decrease in mobility. A similar correlation between  $D_{it}$  values and the rms amplitude,  $\Delta$ , of the roughness has been demonstrated for Si MOS structures by Koga *et al.*, <sup>16</sup> but the underlying mechanisms which give rise to this effect are probably different from the present case.

In conclusion, we have shown that, depending on the oxide and silicon cap thickness, SiO<sub>2</sub>/Si as opposed to Si/SiGe interface roughness can limit the hole mobility in the strained SiGe channel. It is argued that this interface roughness scattering is less for devices having thicker silicon caps, not only because the magnitude of the Coulomb potential fluctuation in the channel for a given SiO<sub>2</sub>/Si interface roughness is reduced, but because the smaller amplitude of the Ge segregation tail at the SiO<sub>2</sub>/Si boundary leads to a smoother interface.

- <sup>1</sup>S. Verdonckt-Vandebroek, E. F. Crabbé, B. S. Meyerson, D. L. Harame, P. J. Restle, J. M. C. Stork, and J. B. Johnson, IEEE Trans. Electron Devices **41**, 90 (1994).

- <sup>2</sup>C. G. Ahn, H. S. Kang, Y. K. Kwon, and B. Kang, Jpn. J. Appl. Phys., Part 1 37, 1316 (1998).

- <sup>3</sup>I. S. Goh, J. F. Zhang, S. Hall, W. Eccleston, and K. Werner, Semicond. Sci. Technol. 10, 818 (1995).

- <sup>4</sup> A. J. Pidduck, D. J. Robbins, A. G. Cullis, W. Y. Leong, and A. M. Pitt, Thin Solid Films 222, 78 (1992).

- <sup>5</sup>T. J. Grasby, C. P. Parry, P. J. Phillips, B. M. McGregor, R. J. H. Morris, G. Braithwaite, T. E. Whall, E. H. C. Parker, R. Hammond, A. P. Knights, and P. G. Colemen, Appl. Phys. Lett. **74**, 1848 (1999).

- <sup>6</sup>C. G. Sodini, T. W. Ekstedt, and J. L. Moll, Solid-State Electron. 25, 833 (1982).

- <sup>7</sup> R. J. P. Lander, M. J. Kearney, A. I. Horrell, E. H. C. Parker, and T. E. Whall, Semicond. Sci. Technol. 12, 1064 (1997).

- <sup>8</sup>T. E. Whall and E. H. C. Parker, Thin Solid Films 369, 297 (2000).

- <sup>9</sup>M. J. Kearney and A. I. Horrell, Semicond. Sci. Technol. 13, 174 (1998).

- <sup>10</sup>T. Ando, A. B. Fowler, and F. Stern, Rev. Mod. Phys. **54**, 437 (1982).

- <sup>11</sup> A. Pirovano, A. L. Lacaita, G. Ghidini, and G. Tallarida, IEEE Electron Device Lett. 21, 34 (2000).

- <sup>12</sup> J. Li and T.-P. Ma, J. Appl. Phys. **62**, 4212 (1987).

- <sup>13</sup>D. K. Schröder, Semiconductor Material and Device Characterization, 2nd ed. (Wiley, New York, 1998).

- <sup>14</sup>T. Matsuoka, S. Taguchi, Q. D. M. Khosur, K. Taniguchi, and C. Hamaguchi, J. Appl. Phys. 78, 3252 (1995).

- <sup>15</sup>L. S. Riley and S. Hall, J. Appl. Phys. **85**, 6828 (1999).

- <sup>16</sup> J. Koga, S. Takagi, and A. Toriumi, Jpn. J. Appl. Phys., Part 1 35, 1440 (1996)