# **Calhoun: The NPS Institutional Archive**

# **DSpace Repository**

Theses and Dissertations

1. Thesis and Dissertation Collection, all items

2021-09

# MODELING AND TOPOLOGY EVALUATION FOR RECTIFIER CIRCUITS IN MEDIUM VOLTAGE DIRECT CURRENT SYSTEM

# Kinney, Daniel T., Jr.

Monterey, CA; Naval Postgraduate School

http://hdl.handle.net/10945/68343

This publication is a work of the U.S. Government as defined in Title 17, United States Code, Section 101. Copyright protection is not available for this work in the United States.

Downloaded from NPS Archive: Calhoun

Calhoun is the Naval Postgraduate School's public access digital repository for research materials and institutional publications created by the NPS community. Calhoun is named for Professor of Mathematics Guy K. Calhoun, NPS's first appointed -- and published -- scholarly author.

> Dudley Knox Library / Naval Postgraduate School 411 Dyer Road / 1 University Circle Monterey, California USA 93943

http://www.nps.edu/library

# NAVAL POSTGRADUATE SCHOOL

**MONTEREY, CALIFORNIA**

# THESIS

# MODELING AND TOPOLOGY EVALUATION FOR RECTIFIER CIRCUITS IN MEDIUM VOLTAGE DIRECT CURRENT SYSTEM

by

Daniel T. Kinney Jr.

September 2021

Thesis Advisor: Co-Advisor: Di Zhang Giovanna Oriti

Approved for public release. Distribution is unlimited.

| REPORT D                                                                                                                                                                                                                                                                                                                                                                                                                  | OCUMENTATION PAGE                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                   | Form Approved OM<br>No. 0704-0188                                                                                                                                                                                                                                                                                              | В                                                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| instruction, searching existing data<br>information. Send comments regard<br>for reducing this burden, to Washi                                                                                                                                                                                                                                                                                                           | lection of information is estimated to<br>sources, gathering and maintaining th<br>ling this burden estimate or any other<br>ington headquarters Services, Directo<br>gton, VA 22202-4302, and to the Off<br>03.                                                                                                                                                                                                                                | e data needed, and c<br>aspect of this collec<br>prate for Information                                                                                                                                            | completing and reviewing the control tion of information, including sum operations and Reports, 1215                                                                                                                                                                                                                           | llection of<br>uggestions<br>Jefferson                                                                                                  |

| 1. AGENCY USE ONLY<br>(Leave blank)                                                                                                                                                                                                                                                                                                                                                                                       | 2. REPORT DATE<br>September 2021                                                                                                                                                                                                                                                                                                                                                                                                                | 3. REPORT TY                                                                                                                                                                                                      | YPE AND DATES COVER<br>Master's thesis                                                                                                                                                                                                                                                                                         | ED                                                                                                                                      |

| <ul> <li>4. TITLE AND SUBTITLE<br/>MODELING AND TOPOLOG<br/>IN MEDIUM VOLTAGE DIRE</li> <li>6. AUTHOR(S) Daniel T. Kinr</li> </ul>                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                 | IER CIRCUITS                                                                                                                                                                                                      | 5. FUNDING NUMBERS                                                                                                                                                                                                                                                                                                             | >                                                                                                                                       |

| 7. PERFORMING ORGANIZ<br>Naval Postgraduate School<br>Monterey, CA 93943-5000                                                                                                                                                                                                                                                                                                                                             | LATION NAME(S) AND ADDF                                                                                                                                                                                                                                                                                                                                                                                                                         | RESS(ES)                                                                                                                                                                                                          | 8. PERFORMING<br>ORGANIZATION REPO<br>NUMBER                                                                                                                                                                                                                                                                                   | )RT                                                                                                                                     |

| 9. SPONSORING / MONITORING AGENCY NAME(S) AND<br>ADDRESS(ES)<br>N/A                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10. SPONSORING /<br>MONITORING AGENC<br>REPORT NUMBER                                                                                                                                                             | Y                                                                                                                                                                                                                                                                                                                              |                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>ES</b> The views expressed in this t<br>Department of Defense or the U.                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                   | he author and do not reflect t                                                                                                                                                                                                                                                                                                 | the                                                                                                                                     |

| <b>12a. DISTRIBUTION / AVAI</b><br>Approved for public release. Di                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                   | 12b. DISTRIBUTION COA                                                                                                                                                                                                                                                                                                          | ODE                                                                                                                                     |

| shaft through a reduction ge<br>(DC) power distribution sys<br>interfacing an alternating cu<br>Power quality and efficience<br>rectifier circuit topologies: 2<br>multi-level rectifier. Com<br>performance, and naval ship<br>Using a power electron<br>connected between a 6.6kV<br>Inside each rectifier circuit,<br>are built in and losses are cap<br>multi-level rectifier circuit<br>naval shipboard applications | design is evolving from the t<br>ear to a new architecture that is<br>stem. The goal of this thesis<br>rrent (AC) generator to a DC<br>ey of the power converters an<br>2-level converter, 3-level conv<br>verter operating principles,<br>board applicability are discuss<br>ics simulation platform, the f<br>AC generator and a regulate<br>thermal properties of the cho<br>ptured and analyzed in steady<br>is the most efficient, easiest | uses electric driv<br>is to compare d<br>bus which can p<br>e the parameter<br>erter, modular m<br>design trade-<br>ed in detail.<br>our power rectif<br>d DC bus that re-<br>osen semiconduc<br>state operation. | ves powered from a direct<br>ifferent medium voltage is<br>power the ship propulsion<br>is used to compare four of<br>nulti-level converter, and is<br>offs, modeling charact<br>ier circuits and their cont<br>epresents the shipboard p<br>tor switching devices and<br>This study shows that the<br>d the recommended topol | t current<br>rectifiers<br>n system.<br>different<br>modular<br>teristics,<br>trols are<br>blatform.<br>d diodes<br>modular<br>logy for |

| <b>14. SUBJECT TERMS</b><br>MVDC, rectifier, modular multi<br>power, converter, topologies, m                                                                                                                                                                                                                                                                                                                             | ilevel converter, thyristor, perforr<br>odeling, design                                                                                                                                                                                                                                                                                                                                                                                         | nance, metrics, sin                                                                                                                                                                                               | 87                                                                                                                                                                                                                                                                                                                             |                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                   | 16. PRICE COL                                                                                                                                                                                                                                                                                                                  |                                                                                                                                         |

| CLASSIFICATION OF<br>REPORT                                                                                                                                                                                                                                                                                                                                                                                               | 18. SECURITY<br>CLASSIFICATION OF THIS<br>PAGE<br>Unclassified                                                                                                                                                                                                                                                                                                                                                                                  | 19. SECURITY<br>CLASSIFICAT<br>ABSTRACT<br>Unclassified                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                | UN OF                                                                                                                                   |

| NSN 7540-01-280-5500                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                   | Standard Form 298 (<br>Prescribed by ANSIS                                                                                                                                                                                                                                                                                     |                                                                                                                                         |

Prescribed by ANSI Std. 239-18

#### Approved for public release. Distribution is unlimited.

### MODELING AND TOPOLOGY EVALUATION FOR RECTIFIER CIRCUITS IN MEDIUM VOLTAGE DIRECT CURRENT SYSTEM

Daniel T. Kinney Lieutenant, United States Navy BS, U.S. Naval Academy, 2012

Submitted in partial fulfillment of the requirements for the degree of

#### MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

from the

## NAVAL POSTGRADUATE SCHOOL September 2021

Approved by: Di Zhang Advisor

> Giovanna Oriti Co-Advisor

Douglas J. Fouts Chair, Department of Electrical and Computer Engineering

### ABSTRACT

Naval ship propulsion design is evolving from the traditional structure with a main engine driving a shaft through a reduction gear to a new architecture that uses electric drives powered from a direct current (DC) power distribution system. The goal of this thesis is to compare different medium voltage rectifiers interfacing an alternating current (AC) generator to a DC bus which can power the ship propulsion system. Power quality and efficiency of the power converters are the parameters used to compare four different rectifier circuit topologies: 2-level converter, 3-level converter, modular multi-level converter, and modular multi-level rectifier. Converter operating principles, design trade-offs, modeling characteristics, performance, and naval shipboard applicability are discussed in detail.

Using a power electronics simulation platform, the four power rectifier circuits and their controls are connected between a 6.6kV AC generator and a regulated DC bus that represents the shipboard platform. Inside each rectifier circuit, thermal properties of the chosen semiconductor switching devices and diodes are built in and losses are captured and analyzed in steady state operation. This study shows that the modular multi-level rectifier circuit is the most efficient, easiest to maintain, and the recommended topology for naval shipboard applications.

# **TABLE OF CONTENTS**

| I.   | INT    | RODUCTION                              | 1  |

|------|--------|----------------------------------------|----|

|      | A.     | SIGNIFICANCE OF RESEARCH               | 1  |

|      | B.     | <b>RESEARCH PROBLEM SPACE</b>          | 4  |

|      | C.     | RESEARCH QUESTION                      | 4  |

|      | D.     | APPROACH                               | 4  |

|      | Е.     | CHAPTER OVERVIEW                       | 5  |

| II.  | -      | ERATION PRINCIPLES OF ACTIVE RECTIFIER |    |

|      |        | POLOGIES                               |    |

|      | А.     | PASSIVE VS. ACTIVE RECTIFIERS          |    |

|      | В.     | ACTIVE RECTIFIER BASIC OPERATION       |    |

|      | C.     | TWO-LEVEL CONVERTER                    |    |

|      | D.     | THREE-LEVEL T-TYPE CONVERTER           |    |

|      | Е.     | MODULAR MULTILEVEL CONVERTER           |    |

|      | F.     | MODULAR MULTILEVEL RECTIFIER           | 16 |

| III. | MO     | DELING AND CONTROL                     | 21 |

|      | A.     | SYSTEM PARAMETERS                      |    |

|      | B.     | ACTIVE RECTIFIER CONTROL               |    |

|      | C.     | DEVICE THERMAL MODEL                   | 27 |

|      | D.     | KEY METRICS FOR COMPARISON             |    |

| IV.  | SIM    | IULATION RESULTS                       |    |

|      | A.     | TWO-LEVEL CONVERTER                    |    |

|      | В.     | THREE-LEVEL T CONVERTER                |    |

|      | C.     | MMC                                    | 46 |

|      | D.     | MMR                                    | 55 |

| V.   | ANA    | ALYSIS OF SIMULATION RESULTS           | 63 |

| VI.  | CO     | NCLUSION AND FUTURE WORK               | 65 |

| LIST | OF R   | REFERENCES                             | 67 |

| INIT | 'IAL D | DISTRIBUTION LIST                      | 69 |

# LIST OF FIGURES

| Figure 1.  | DC side capacitor equivalent circuit                             | 8  |

|------------|------------------------------------------------------------------|----|

| Figure 2.  | AC side equivalent circuit                                       | 9  |

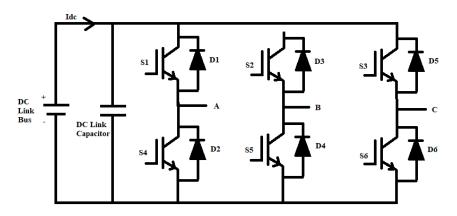

| Figure 3.  | 2- level converter diagram                                       | 10 |

| Figure 4.  | 2-level converter switching waveforms. Source: [13]              | 11 |

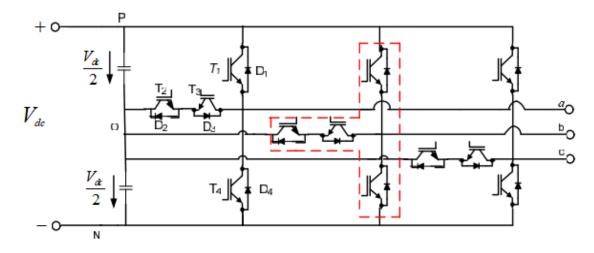

| Figure 5.  | 3-Level T-Type converter circuit diagram. Source: [13]           | 12 |

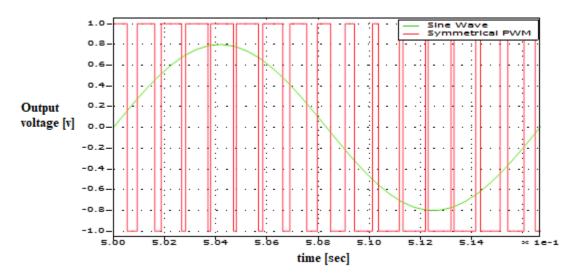

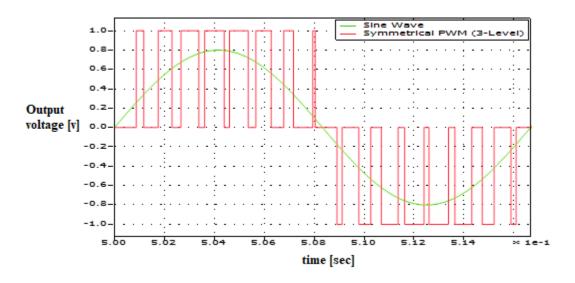

| Figure 6.  | 3-level converter waveform. Source:[13]                          | 13 |

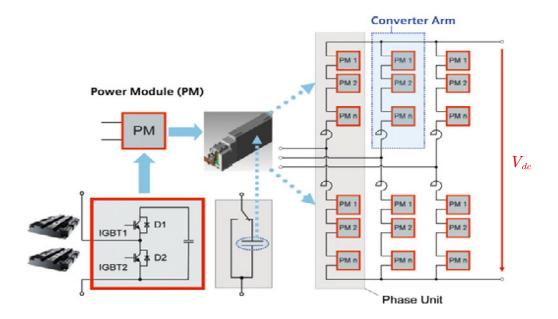

| Figure 7.  | MMC power module configuration. Source: [14]                     | 14 |

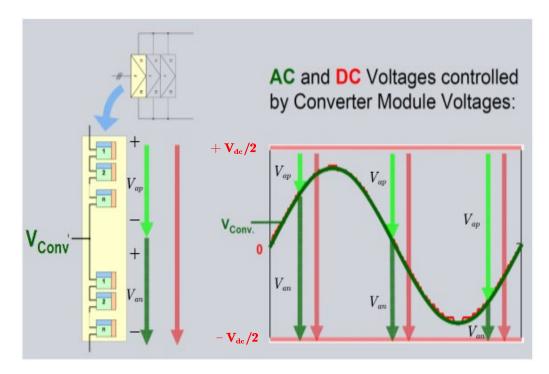

| Figure 8.  | Converter arm voltage. Source: [14]                              | 15 |

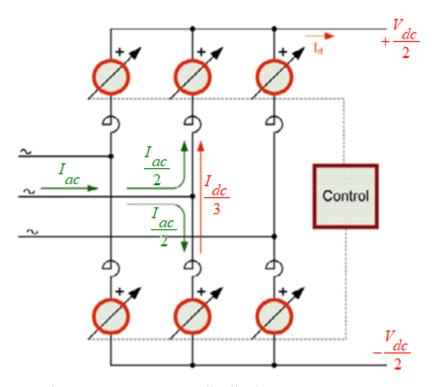

| Figure 9.  | Arm current distribution. Source: [14]                           | 16 |

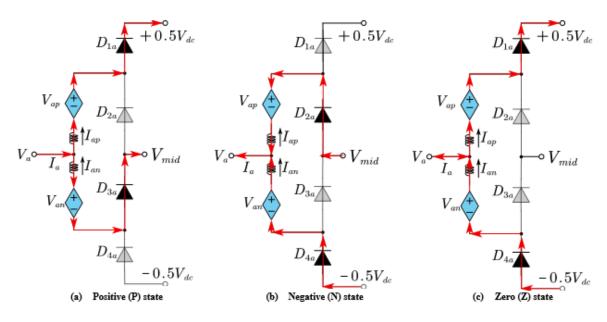

| Figure 10. | Topology of proposed modular multilevel rectifier. Source: [16]  | 17 |

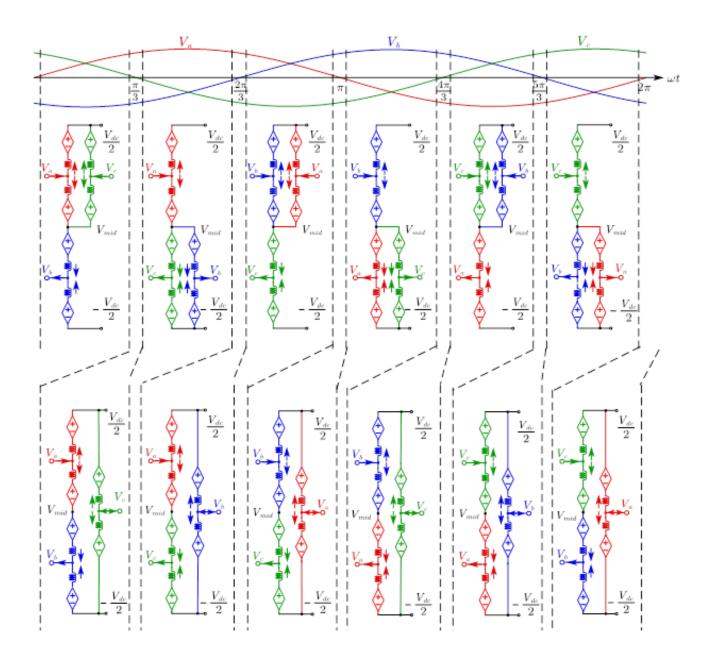

| Figure 11. | Basic states of a MMR phase leg. Source: [16]                    | 18 |

| Figure 12. | States of 3 phases in MMR over one line cycle. Source: [16]      | 19 |

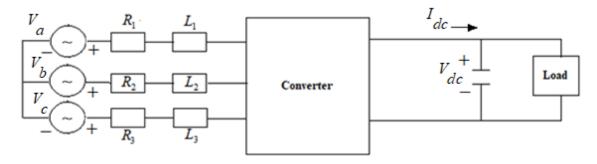

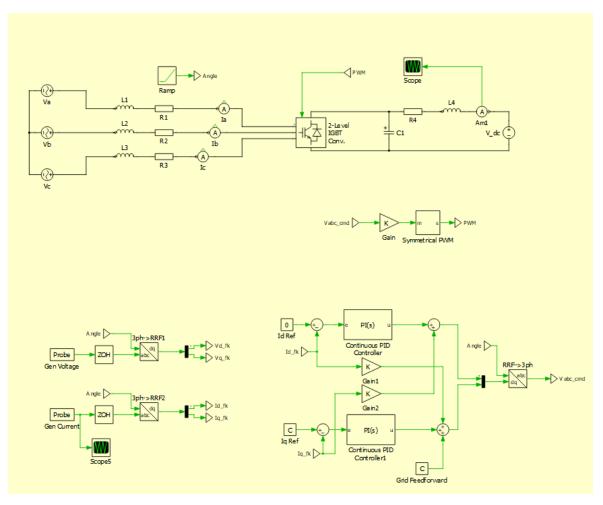

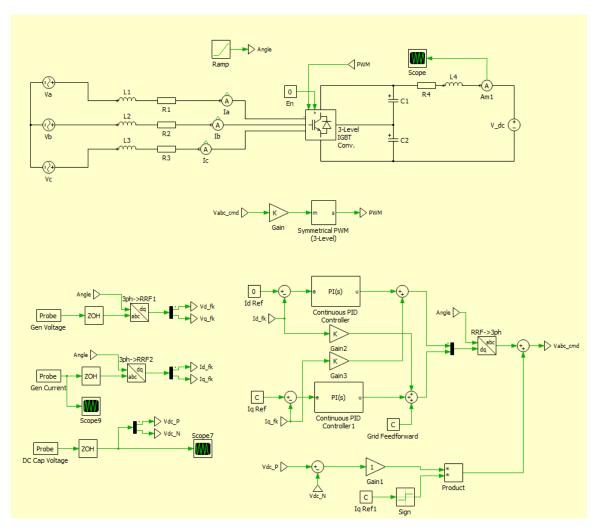

| Figure 13. | Rectifier control circuit                                        | 22 |

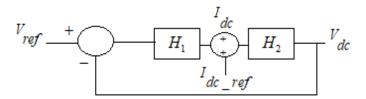

| Figure 14. | Voltage control system block diagram                             | 23 |

| Figure 15. | Rectifier AC side equivalent circuit on the d-axis               | 24 |

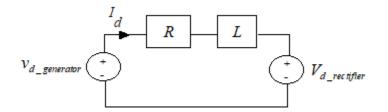

| Figure 16. | Current control system block diagram                             | 25 |

| Figure 17. | Switching loss thermal model for the Toshiba semiconductor       | 28 |

| Figure 18. | Conduction loss thermal model characteristics for Toshiba device | 29 |

| Figure 19. | 2-level rectifier as modeled in PLECS                            | 32 |

| Figure 20. | 2-level converter PLECS system configuration                     | 33 |

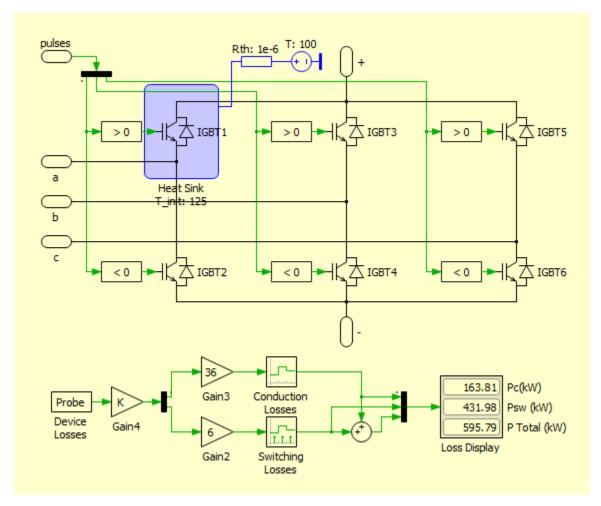

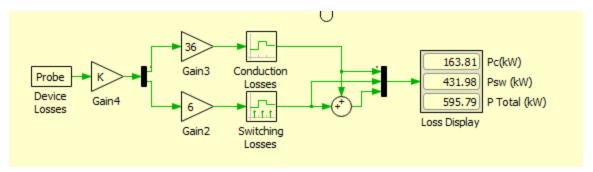

| Figure 21. | 2-level converter thermal modeling circuit configuration         | 34 |

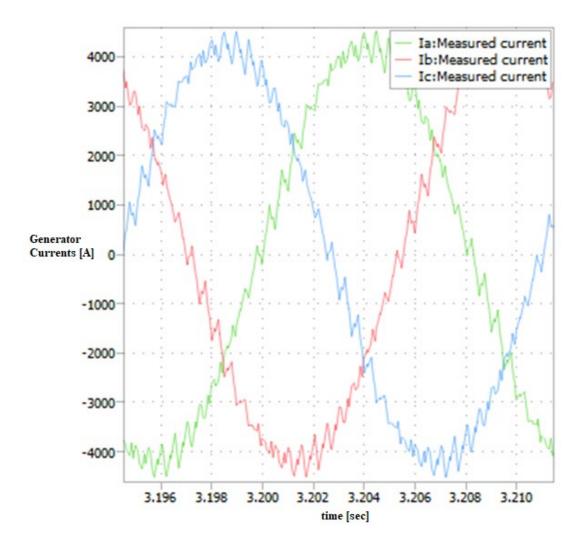

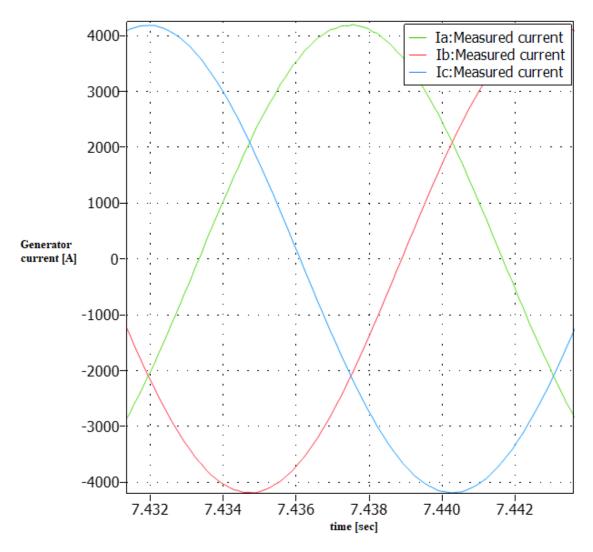

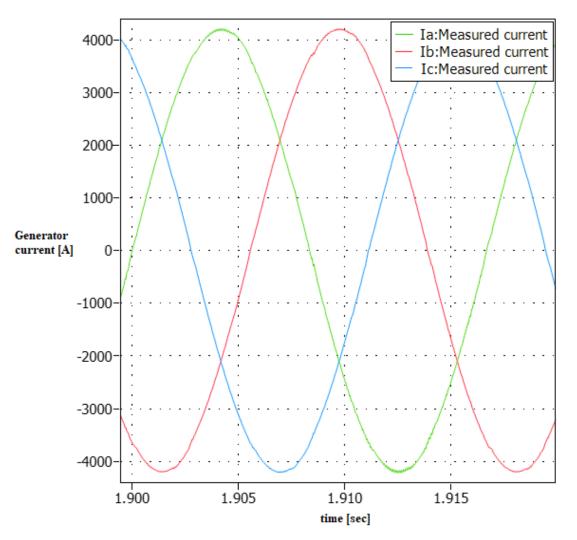

| Figure 22. | 2-level rectifier three-phase input currents                     | 35 |

| Figure 23. | 2-level converter total switching and conduction losses          | 36 |

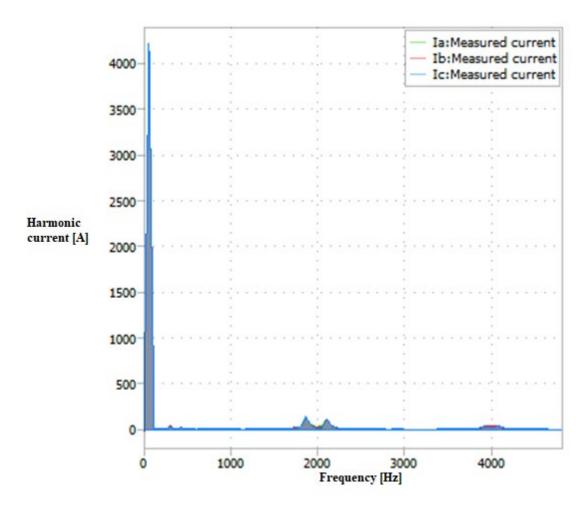

| Figure 24. | 2 level generator current Fourier analysis                       | 37 |

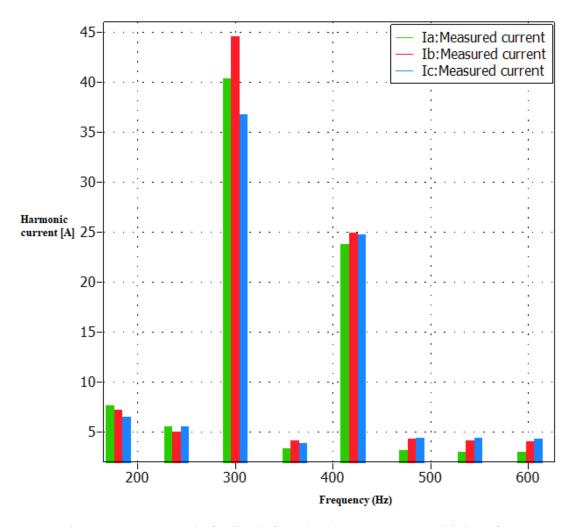

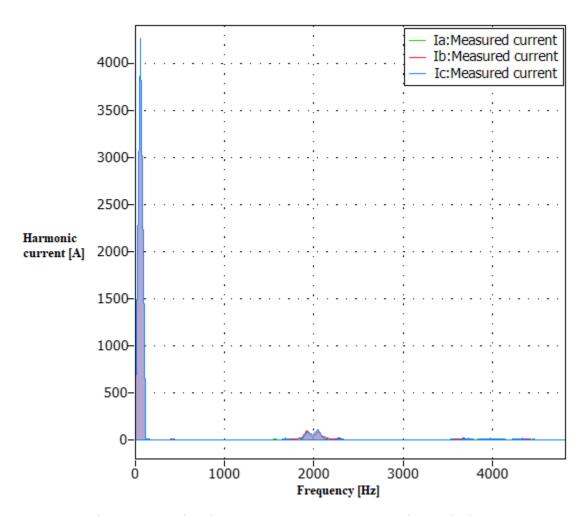

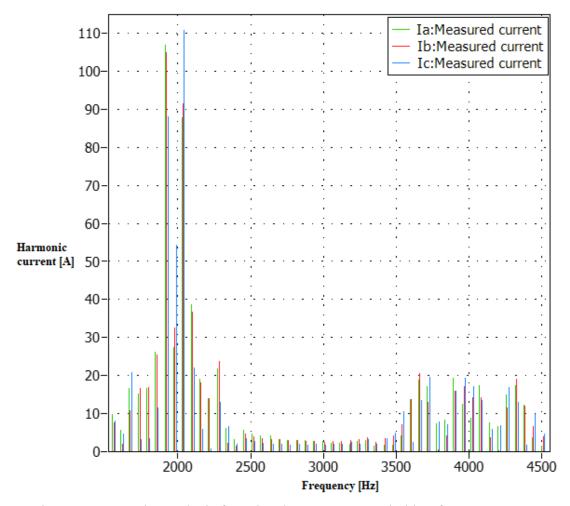

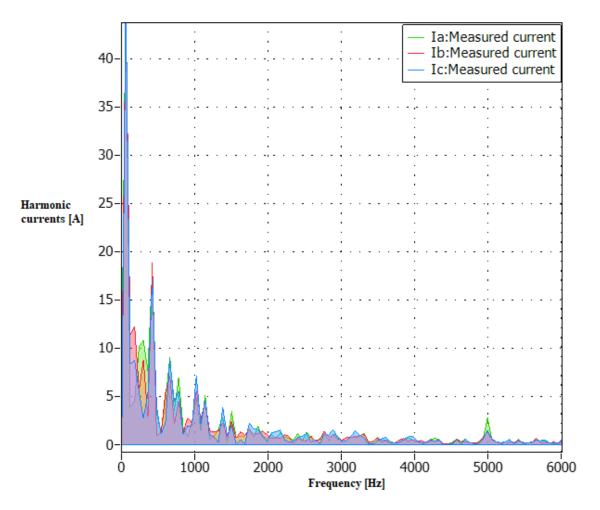

| Figure 25. | Harmonic feedback for 2-level converter at multiples of fundamental frequency | 38 |

|------------|-------------------------------------------------------------------------------|----|

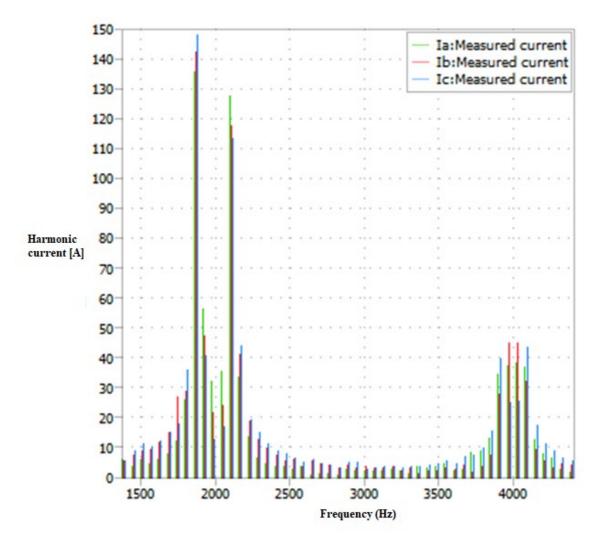

| Figure 26. | Fourier analysis for 2-level converter at multiples of switching frequency    | 39 |

| Figure 27. | 3-level T type converter PLECS topology                                       | 40 |

| Figure 28. | 3- level T type converter PLECS system configuration                          | 41 |

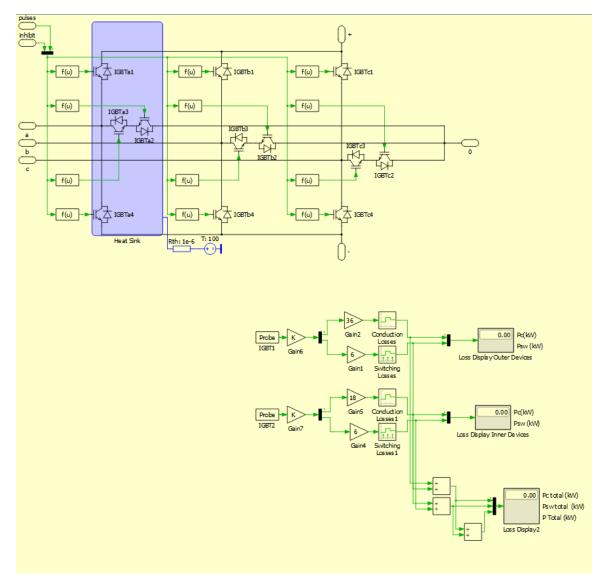

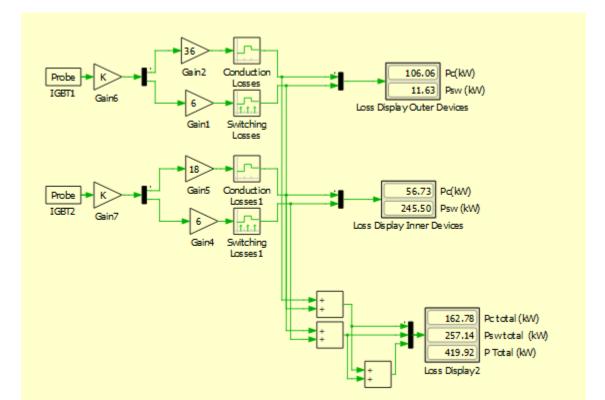

| Figure 29. | 3-level T type rectifier thermal modeling system in PLECS                     | 42 |

| Figure 30. | 3 level rectifier power loss results                                          | 43 |

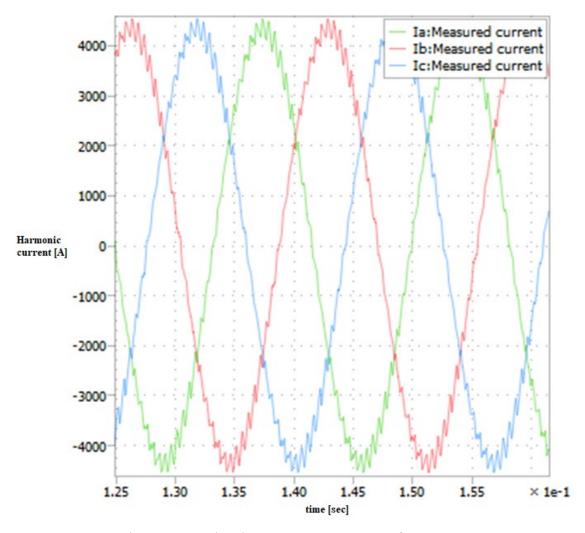

| Figure 31. | 3-level generator current waveform                                            | 44 |

| Figure 32. | 3-level T type generator current Fourier analysis                             | 45 |

| Figure 33. | Fourier analysis for 3-level converter at switching frequency                 | 46 |

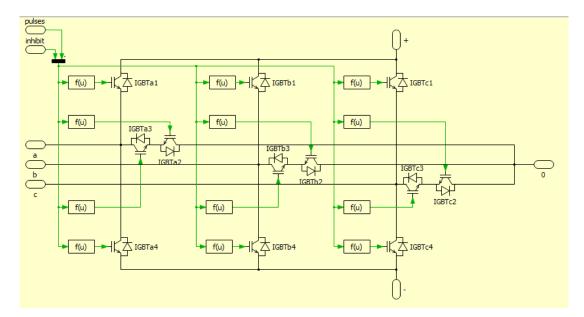

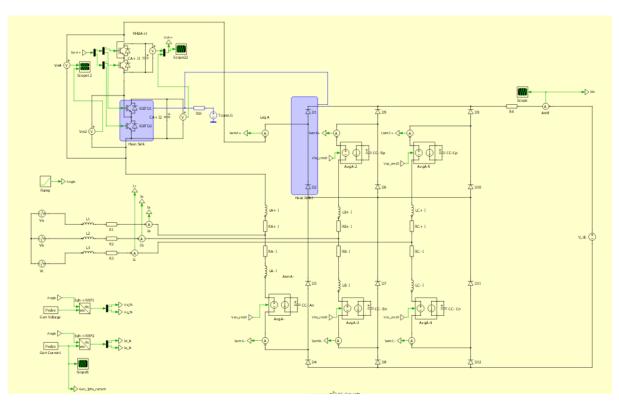

| Figure 34. | Modular multi-level converter PLECS circuit design                            | 48 |

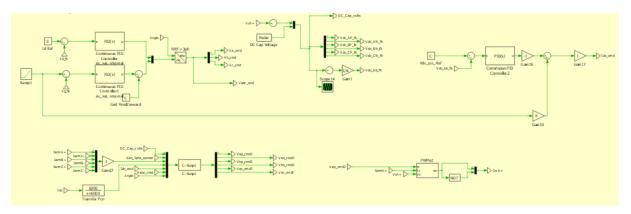

| Figure 35. | MMC control system circuits                                                   | 48 |

| Figure 36. | MMC generator current signal quality                                          | 50 |

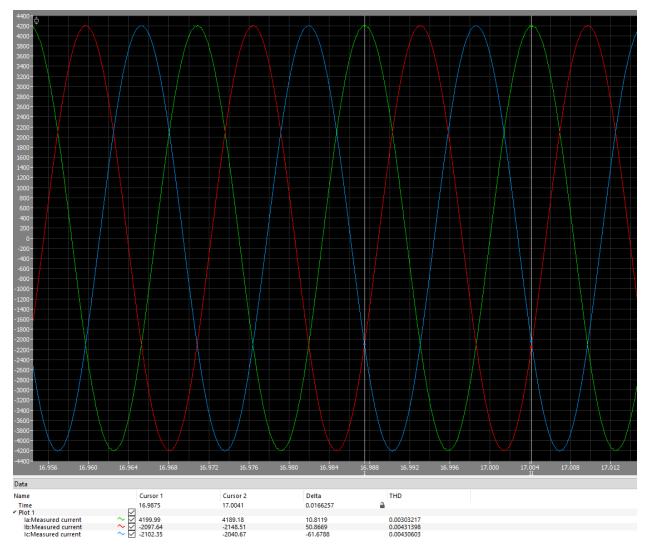

| Figure 37. | MMC THD calculation                                                           | 51 |

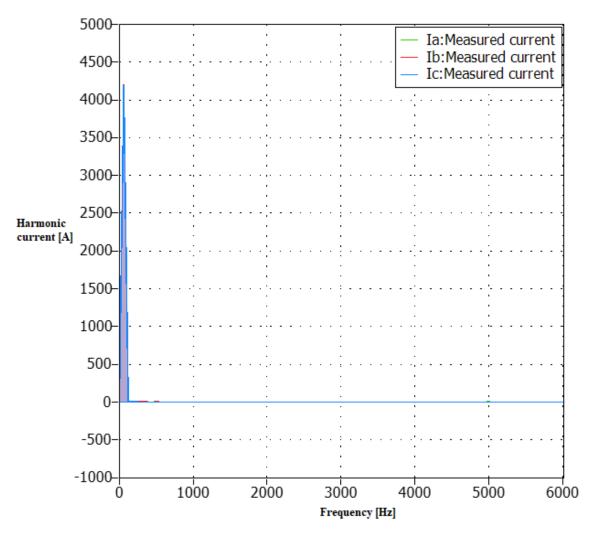

| Figure 38. | MMC Generator current Fourier analysis graph                                  | 52 |

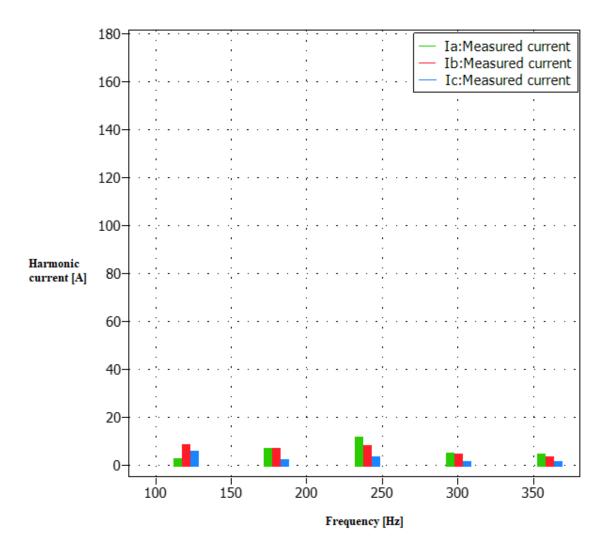

| Figure 39. | Fourier analysis at multiples of fundamental frequency for MMC                | 53 |

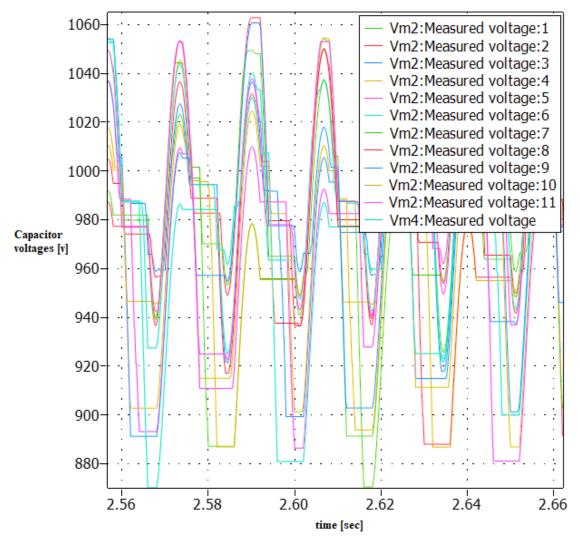

| Figure 40. | MMC capacitor balancing voltages                                              | 54 |

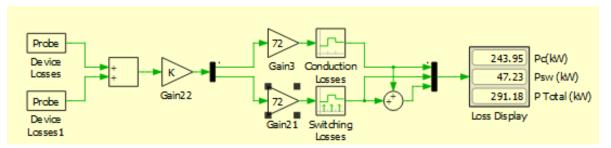

| Figure 41. | MMC power loss simulation results                                             | 55 |

| Figure 42. | Modular multi-level rectifier overview                                        | 56 |

| Figure 43. | MMR command control system                                                    | 56 |

| Figure 44. | Generator current waveform                                                    | 57 |

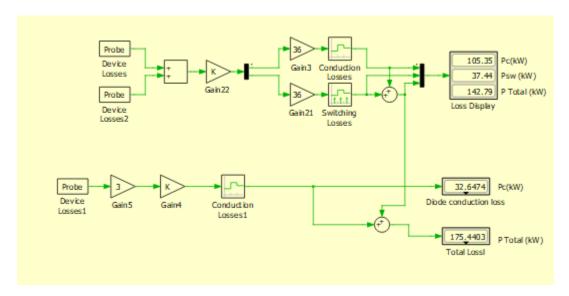

| Figure 45. | MMR simulation losses                                                         | 58 |

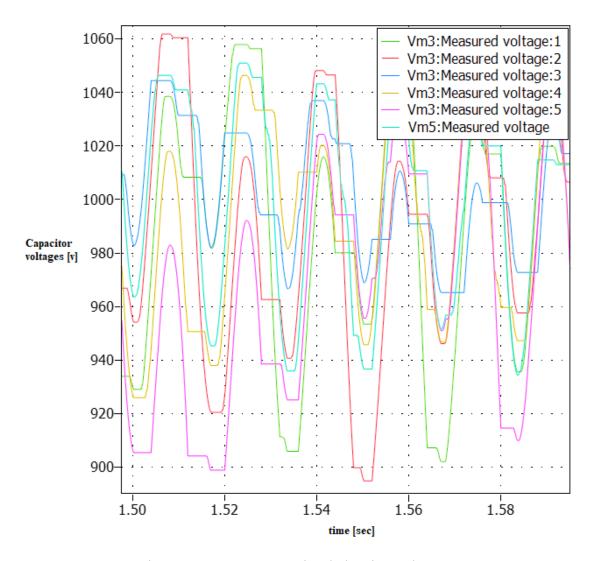

| Figure 46. | MMR Capacitor balancing voltage                                               | 59 |

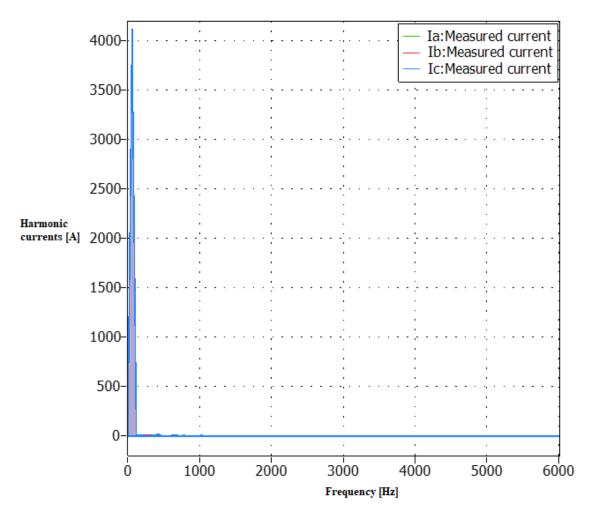

| Figure 47. | MMR Fourier analysis                                                          | 60 |

| Figure 48. | Fourier analysis at multiples of switching frequency for MMR                  | 61 |

# LIST OF TABLES

| Table 1. | Loss, efficiency, THD results for all topologies under study63 |

|----------|----------------------------------------------------------------|

| Table 2. | Topology energy storage and capacitance calculations           |

# LIST OF ACRONYMS AND ABBREVIATIONS

| AC                       | alternating current                                                                                                    |

|--------------------------|------------------------------------------------------------------------------------------------------------------------|

| DC                       | direct current                                                                                                         |

| EMI                      | electromagnetic interference                                                                                           |

| HVDC                     | high voltage direct current                                                                                            |

| IGBT                     | insulated gate bridge transistor                                                                                       |

| MMC                      | modular multi-level converter                                                                                          |

| MMR                      | modular multi-level rectifier                                                                                          |

| MVDC                     | medium voltage direct current                                                                                          |

|                          |                                                                                                                        |

| NAVSEA                   | Naval Sea Systems Command                                                                                              |

| NAVSEA<br>PF             | Naval Sea Systems Command<br>power factor                                                                              |

|                          | ·                                                                                                                      |

| PF                       | power factor                                                                                                           |

| PF<br>PI                 | power factor<br>proportional-integrational                                                                             |

| PF<br>PI<br>PLECS        | power factor<br>proportional-integrational<br>piecewise linear electrical circuit simulation                           |

| PF<br>PI<br>PLECS<br>PWM | power factor<br>proportional-integrational<br>piecewise linear electrical circuit simulation<br>pulse width modulation |

## ACKNOWLEDGMENTS

I want to offer my sincerest gratitude to Dr. Di Zhang for his constant support and guidance through all aspects of my thesis work. Thank you for the hours of video conferences and office meetings to explain converter theory. Your dedication is the reason for this thesis.

I want to give a profound thank you to Dr. Giovanna Oriti for her help in thesis editing and willingness to educate me on power electronics principles. My thesis was able to articulate the intended message more effectively because of the hours she dedicated to improving my technical writing.

Last, I'd like to thank Chloe Woida of the Graduate Writing Center. I'm extremely grateful for the hours of video conferences and your selfless devotion to helping me succeed.

## I. INTRODUCTION

As the threat to national security increases, the communications and weapon systems that the U.S. Navy employs on naval vessels present power density challenges due to the need for dedicated power conditioning systems on alternate current (AC) distribution plants [1]. The U.S. Navy predominantly uses AC electrical distribution systems aboard naval vessels, while electric drive propulsion motors are powered from a direct current (DC) distribution system. DC power is obtained using gas-powered AC generators and AC/ DC switching power converters also called rectifiers. This study provides a topology comparison of four different active rectifier circuit topologies. For each converter circuit, the principle of operation is discussed in terms of switching cycles to create a DC current from a three-phase AC input. Each topology is designed to rectify the AC power provided from a generator to a stable DC bus, which can be used for shipboard electrical distribution. Each converter was evaluated for its steady state performance, where efficiency, voltage, current quality, and power losses are all studied to determine which of the chosen four represents the best choice for use in a medium voltage direct current (MVDC) distribution system. This study shows that the modular multi-level rectifier is the best choice for this type of operating environment and offers significant benefits.

#### A. SIGNIFICANCE OF RESEARCH

A study of efficient power converters is necessary in preparation for the future of naval warship power generation requirements. Distribution systems must be ready for a higher power demand, while maintaining volume and weight limitations inherent to ships. Power electronics are more complex than traditional means of power distribution because of their control systems, but they can be designed to facilitate ease of maintenance and system repair in the event of a failure.

With advancements in communications, weapons, and propulsion, AC distribution systems present power density challenges due to the need for dedicated power conditioning systems that can adequately provide for the increased loading [1]. Because of stability that must be afforded during significant power spikes of pulsed loads, traditional shipboard AC

systems do not have the power density required to meet transient load demands without additional large and costly energy storage systems [2]. Pulsed loads consist of high-powered lasers, high-powered electromagnetic systems, and high-powered electronic warfare systems that all work in conjunction to meet the missions of self and area defense [3].

Naval Sea Systems Command (NAVSEA) has incorporated electric propulsion systems on various ships, to include the Zumwalt class destroyer, and is focused on efforts to make electric ships part of the future fleet. The NAVSEA design practices and criteria manual states "The primary aim of the electric power system design will be for survivability and continuity of the electrical power supply. To ensure continuity of service, consideration shall be given to the number, size and location of generators, switchboards, and to the type of electrical distribution systems to be installed and the suitability for segregating or isolating damaged sections of the system" [3].

The electric drive motor in comparison to gas powered main engines has benefits ranging from size, efficiency, cost, and power availability for other high-power weapons and communication applications that are paramount to the mission of a warship [4]. The use of electric propulsion maximizes efficiency of the electrical distribution by minimizing heat losses and removing reactive power in transmission due to a DC-DC link bus voltage that provides power throughout the ship. The DC electrical power is then inverted at the location on the ship where AC power is required to drive a load. Electric drive motors offer the benefit of operating without a main engine that is directly coupled to the propeller. They are also smaller than their gas engine counterparts and run at closer to 100% of rated power [5]. They have an advantage of faster acceleration at lower speeds and can reach peak torque without having to increase revolutions per minute (RPM). Controlling the current into the electric drive motor controls the torque to the propeller. Since current can be controlled very quickly using power electronics devices, the acceleration rate can be much higher than that of a main engine where the rotational speed of the engine must change to change the speed of the propeller. Electric drive propulsion also allows for removal of the reduction gears on gas- and nuclear-powered ships. According to Ronald O'Rourke in a national defense strategy prepared for Congress, another benefit for ship propulsion is the aspect of stealth by minimizing noise that comes from an AC bus transferring power throughout the ship [6].

Electric drive propulsion motors are powered from a DC distribution system where power is inverted back to an AC voltage and current at the motor. To achieve the demanded ship speed, an electric drive motor draws adequate AC current into the windings, which produces a torque and subsequently propels the ships. The electric drive configuration means that the propulsion of the ship is decoupled from the power the AC generator provides, and the AC generator will not have to change rotational speed based on a desired ship speed change. Thus, the AC generator can operate at different speeds optimized for efficiency at corresponding load conditions regardless of the motor speed. In addition, AC generator horsepower is directly proportional to its volume (rotor diameter squared multiplied by rotor active length) multiplied by its rotational speed, rotor flux, and stator [7]. In an electric propulsion system, the generator can rotate much faster and therefore theoretically provide the ability to reduce generator volume with the same power output. Lower volume corresponds to less weight and smaller machines that take up less space, which is a major advantage for ship systems.

While electric drive propulsion relies on DC power, the U.S. Navy predominantly uses AC electrical distribution systems aboard naval vessels. In traditional ship propulsion systems, an AC distribution plant is driven by three phase AC generators and the propulsion system uses a main engine to drive the shaft through a reduction gear. As the ship is commanded to speed up or slow down, the speed on the main engine is changed accordingly and the prime mover (shaft) rotates at much slower speeds than the generators for the distribution system. The operation of a motor at slower speeds means that it is heavier and takes up much more volume than machines that can rotate much faster and at constant speeds. The topologies being evaluated in this study will point to a recommended converter that can work effectively in an MVDC system and provide the necessary power requirement for the evolving needs of shipboard distribution.

#### **B. RESEARCH PROBLEM SPACE**

The system that is discussed throughout this document includes a gas-powered generator powering a stable DC bus, from which the DC voltage is inverted to AC by the motor drive unit for propulsion control [8]. With existing shipboard AC distribution systems, the frequency of the of the gas-powered generators must be adjusted to remain constant during all loading conditions. The need for frequency adjustment within existing systems greatly limits the operation of the gas generators and makes their operating points dependent on the loads, instead of operating at the most efficient condition [9].

This research is focused on MVDC distribution systems which allow the use of higher speed generators, thereby reducing their size and weight with respect to the generators currently in use. These smaller machines are not only significantly smaller and lighter but provide the additional benefits of lower torque and higher power density. Gas generators onboard military ships providing power for distribution systems have low efficiency values that are typically around 40% [9]. The decoupling of the MVDC system allows these generators to operate at a range of speeds that give greater flexibility of operation with fuel and power generation efficiency in mind.

An additional benefit of the MVDC systems is the efficiency that can be realized from the use of solid-state transformers in stepping up or down voltage levels. Solid-state transformers enabled by the semiconductor-based power electronics operate at a few kHz up to a few hundred kHz, leading to a much higher power density and a much lower weight compared to the traditional transformers used in a MVAC system [10].

#### C. RESEARCH QUESTION

In the context of an MVDC system, which converter topology is the best for efficient rectification in Naval propulsion?

### D. APPROACH

Four active front end rectifier topologies are studied in this thesis: the classic 2level converter, the T-type 3-level converter and the modular multi-level converter, which is widely used in industrial applications, and the new modular multi-level rectifier. All four topologies are transformer-less configurations that achieve high power density and efficiency. They also have a much-improved power quality compared to a diode rectifier.

## E. CHAPTER OVERVIEW

In Chapter II the benefits of using active rectifiers versus diode rectifiers are discussed together with the detailed operating principles of each converter. Chapter 3 introduces the control system architecture and its design. It also features an overview of the steps taken to model the topologies through simulations. Chapter 4 discusses simulation results for each topology and provides a comparison of benefits for use in shipboard MVDC systems. Lastly, Chapter 5 summarizes the results and suggests future work on the basis that the modular multi-level rectifier (MMR) is the most suitable choice in power conversion for naval shipboard distribution.

# II. OPERATION PRINCIPLES OF ACTIVE RECTIFIER TOPOLOGIES

In this chapter, the basic operation of an active rectifier is introduced, followed by the detailed operation of each different topology. The benefits of active rectifiers are explored, and that concept is carried into the design of each active rectifier topology. The operating principles of the four converters chosen for this study are discussed in detail in terms of how they operate, how they were be designed for simulation, and how they are controlled.

#### A. PASSIVE VS. ACTIVE RECTIFIERS

Typically, AC power from the generator is converted to DC through a rectifier. There are two types of rectifiers, passive rectifiers and active front end rectifiers. Passive rectifiers are bulky, lossy and costly [11]. Active rectifiers were utilized in this topology comparison study and provide many benefits as compared to passive rectifiers.

The passive rectifier, which is also called a diode rectifier, usually consists of a simple design of diodes arranged in a full bridge configuration. Although very unlikely to fail, they require the use of bulky and heavy capacitors for power factor (PF) correction [12]. Active rectifiers are much more complex due to the control circuitry that must be implemented into the design, but they do not require large capacitors for power factor correction, and they also provide the benefit of low harmonic current [12].

The passive rectifier consists of line-frequency transformers to improve the AC side power quality. The basic three-phase diode rectifier consists of 6 diodes, two diodes per phase. Diodes are inexpensive and simple in operation but are not controllable devices and draw currents with large harmonics of the fundamental frequency, which cause significant distortion in the source voltage [11]. In other words, even with a pure sinusoidal voltage source at the input, the diode rectifier input currents are heavily distorted. When the current is distorted, the source voltage becomes distorted, and all other loads connected at the point of common coupling are affected. Harmonics can be reduced by placing filters at the input or connecting multiple diode rectifiers in parallel or in series with transformers, but the transformers and bulky and lossy.

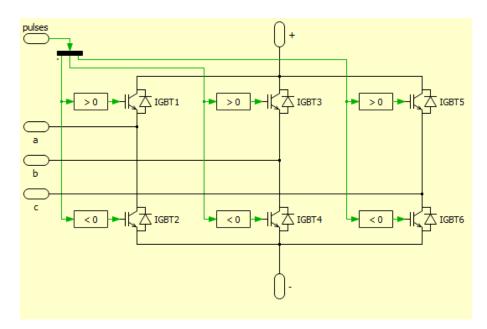

Transformer-less active front end rectifiers reduce harmonics and are small enough that they no longer become a design constraint in shipboard applications. Instead of diodes, an active front end uses controllable switching semiconductors such as insulated-gate bipolar transistors (IGBTs), which can be controlled to draw a sinusoidal input current, to minimize the total harmonic components. The rectifier input current can still contain some harmonics, but at frequencies close to the switching frequency of the IGBTs, which is much higher than 60Hz and can be eliminated by LCL filters of moderate size and weight [11]. Other than the harmonics, the power factor at the generator terminal can also be controlled by an active rectifier to be close to unity. The high-power quality is one reason why active front end rectification was chosen for this topology study.

#### **B.** ACTIVE RECTIFIER BASIC OPERATION

The active rectifier needs to accomplish two main goals:

- control the DC bus voltage

- control the active and reactive power at the AC input

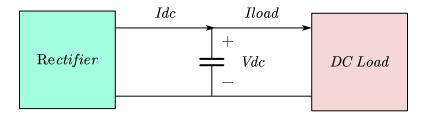

The main function of the active rectifier, like the diode rectifier, is to convert AC voltage into DC voltage. Unlike the diode rectifier, an active rectifier has the ability to keep the DC bus voltage constant. There are capacitors at the output of all rectifiers, as shown in the following figure. In Figure 1, the rectifier is on the left side providing constant current to the DC load on the right side.

Figure 1. DC side capacitor equivalent circuit

$I_{load}$  represents the load current. To keep the DC bus voltage VDC constant, the active rectifier needs to control its DC side output current  $I_{dc}$  to match  $I_{load}$ . If  $I_{dc}$  is higher than  $I_{load}$ , the capacitor or DC bus voltage increases. Otherwise, the DC bus voltage drops. Since the load current always varies, the active rectifier needs to change  $I_{dc}$  consistently.

During this regulation, the product of  $I_{dc}$  and  $V_{dc}$  equals the rectifier output power. To provide such power, the active rectifier needs to control the input power received from AC side.

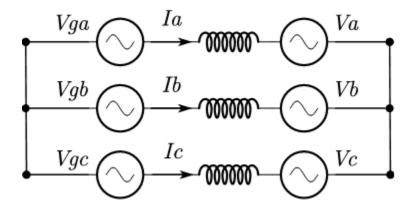

As shown in Figure 2, the three-phase AC voltage sources at the generator terminal are modeled as  $V_{ga}$ ,  $V_{gb}$  and  $V_{gc}$ . The active rectifier acts as a controlled three-phase voltage source (modeled as  $V_a$ ,  $V_b$  and  $V_c$ ). Thus, by controlling the amplitude and phase angle of the three-phase voltages, the three-phase currents  $I_a$ ,  $I_b$  and  $I_c$  can be regulated, as well as the active power and reactive power. The detailed control method is explained in chapter 3. Figure 2 shows the ac side equivalent circuit for these modeled systems.

Figure 2. AC side equivalent circuit

## C. TWO-LEVEL CONVERTER

The 2-level converter is the most basic three-phase voltage source converter topology widely used to reduce the AC input harmonic distortion compared to a 6-pulse rectifier circuit. The three-phase 2-level converters have IGBTs with anti-parallel diodes where 6-pulse rectifiers have thyristors or diodes. The anti-parallel diodes allow for current to be bi-directional. The 2-level converter can control the power flow in either way between the generator and DC bus. However, in Navy applications, where a gas turbine is used as the prime mover to drive the generator, inverted power from the DC bus to the AC turbine is unnecessary. Figure 3 shows the basic setup of the 2-level rectifier circuit configuration.

Figure 3. 2- level converter diagram

By controlling the gate signals of the switching devices, the switching devices can be turned on or off. When the top device, such as S1 is turned on and the bottom device S4 is turned off, the phase leg output voltage, such as the voltage at terminal A, is equal to the positive DC bus voltage. When the top device is turned off and the bottom device is turned on, the phase leg output voltage equals the negative DC bus voltage. Then by controlling the time distribution between the two voltage levels, i.e., using pulse width modulation (PWM), the average output voltage of such phase leg in each switching cycle is controlled to synthesize the required AC output voltage or DC output voltage.

One example is shown in Figure 4. The red waveform is the output PWM waveform of a 2-level converter, and the green wave represents the filtered sinusoidal voltage. It

should be noted that all devices in a 2-level converter must be rated at the full DC link voltage and load current because at each switching event, the IGBT switches the full DC link voltage and load current.

Figure 4. 2-level converter switching waveforms. Source: [13]

#### D. THREE-LEVEL T-TYPE CONVERTER

A 3-level T-Type converter topology is shown in Figure 5. It consists of the baseline 2-level converter with the additional bidirectional current capability devices that are placed into the circuit between the midpoint of the DC link and AC output terminals [13]. Each phase leg consists of four IGBTs with antiparallel diodes, named T1, T2, T3 and T4. When only T1 is turned on, the phase leg AC output voltage is equal to the positive DC bus voltage. When only T2 and T3 are turned on, the phase leg AC output voltage is equal to the neutral point voltage of the DC bus. When only T4 is turned on, the phase leg output voltage is equal to the negative DC bus voltage. In other words, there are three possible output voltage levels on the AC side, which is the reason for labeling this topology a 3-level converter. The 3-level converter is used in this thesis because this topology has been evaluated and the case has been made for its applicability in high-speed motor applications in [14]. There are many types of 3-level converter designs, and all have similar performance in terms of efficiency and THD. Because of the operating similarity, the analysis presented

here is valid for other 3-level converter topologies for this high-level system analysis. Figure 5 shows the 4-level T-type rectifier circuit configuration.

Figure 5. 3-Level T-Type converter circuit diagram. Source: [13]

Using pulse width modulation, the output sinusoidal voltage can be synthesized with the three voltage levels as shown in Figure 6. The red waveform is the output PWM waveform of the 3-level converter, and the green wave represents the filtered sinusoidal voltage. Compared to the 2-level converter, the sinusoidal waveform can be synthesized more accurately with the additional neutral point DC voltage level. In other words, the harmonic component in the 3-level converter is reduced compared to the 2-level converter with the same switching frequency, leading to a much lower harmonic components in the AC side current. Alternatively, a lower switching frequency can be used in a 3-level converter to achieve the same harmonic component of a 2-level converter. In this thesis, the harmonic component is quantified by total harmonic distortion (THD).

THD is the percentage of distortion of a waveform when the output is compared to the input of a sinusoidal component. A lower THD means the waveform has lower harmonic components compared with the fundamental component, or in other word, the waveform is closer to an ideal sinusoidal waveform. In addition, it should be noted that in each switching event, the IGBT only needs to switch half of the total DC link voltage. Since the switching loss is roughly proportional to the voltage that the device blocks at each switching cycle, the switching losses in a 3-level converter can be reduced by half in comparison to a 2-level converter, at the same switching frequency, which is displayed in Figure 6.

Figure 6. 3-level converter waveform. Source:[13]

#### E. MODULAR MULTILEVEL CONVERTER

The modular multilevel converter (MMC) is a mature topology which is very popular in high voltage DC (HVDC) application. Compared to the classic 2-level and 3level converters, MMCs can generate theoretically unlimited voltage levels, i.e., hundreds of levels in HVDC application, which are used to synthesize the AC sinusoidal waveform accurately and without additional harmonic filters. On top of the extremely low harmonic level, the MMC also features low switching losses because each device only needs to be rated for a small fraction of the DC voltage.

The basic MMC topology is shown in Figure 7.

Figure 7. MMC power module configuration. Source: [14]

Each MMC phase leg includes two arms. Each arm consists of a few cascaded power modules and one arm inductor. Each power module has the same structure as a 2-level converter phase leg, including two IGBTs with anti-parallel diodes and one capacitor. By controlling the gates of the two IGBTs in one power module, the terminal output voltage of such power module can be either 0V or the voltage of the capacitor inside the module. Assuming the power module capacitor voltage is  $V_{cap}$  and there are N power modules in one arm, then by controlling all the gates of the power modules in the arm, the total voltage across such arm can be controlled to be any value between 0 and  $N \cdot V_{cap}$ .

One key benefit of MMC is that if one submodule fails in one arm, it can be bypassed and the system can continue operating at rated power if additional redundant modules are included.

Since there are two arms in each phase leg, the AC output voltage can be controlled if the top arm outputs the voltage difference between  $+\frac{V_{dc}}{2}$  and the AC output voltage. The bottom arm outputs the voltage difference between the AC output voltage and  $-\frac{V_{dc}}{2}$ . The total voltage of the two arms in one phase equals the DC side voltage as illustrated in Figure 8.

Figure 8. Converter arm voltage. Source: [14]

The relationship between the top arm voltage  $(V_{ap})$ , the bottom arm voltage  $(V_{an})$ , the DC bus voltage  $(+/-\frac{V_{dc}}{2})$  and the AC side voltage  $V_{conv}$  can be summarized by the following:

$$V_{an} = V_{dc}/2 + V_{conv} \tag{1}$$

$$V_{ap} = V_{dc}/2 - V_{conv} \tag{2}$$

$$V_{an} + V_{ap} = 2 * V_{dc} \tag{3}$$

One key challenge related to MMCs is how to keep the capacitor average voltage constant, which means the net energy flowing into the capacitors inside each arm must be

zero during a fundamental cycle. To achieve this goal, the steady state current distribution is summarized in Figure 9 where the converter arms are represented as six controlled voltage sources. The AC side phase current in each phase is split evenly between the two arms and the DC side current is shared evenly among the three phase legs.

Figure 9. Arm current distribution. Source: [14]

With such current distribution, it can be proven that the net power of each arm is zero during a line cycle. However, each arm is in essence a single-phase system, which offers no way to eliminate 2nd order harmonics. So, the MMC requires a large capacitor for energy storage. Its internal storage requirement is determined by the AC fundamental frequency (60 Hz) and is approximately 40 kJ/MW for a 60 Hz system. [16]

## F. MODULAR MULTILEVEL RECTIFIER

The MMR topology is depicted in Figure 10, and it consists of two components: 1) half bridge modules with Si IGBTS and Si diodes and 2) diode stacks. It should be noted

that, as in MMC, no harmonic filter or DC side capacitors are required and the failed module can be bypassed to keep the system operating at full power.

As seen in Figure 10, four diode stacks are added to each phase of the MMC topology, which consist of an upper arm and a lower arm. Each arm is built with series connected half bridge modules. Three phase midpoints are connected to construct a neutral point so that the arm voltage is no longer determined by only  $V_{ac}$  and  $V_{dc}$  as in the MMC. Instead, the midpoint voltage  $V_{mid}$  can be utilized to reshape the arm voltage, which makes it possible to reduce the maximum arm voltage. While a controlled switching device can turn off the current actively, the state of each diode is determined by the current polarity. Therefore, there are three possible working states for a single-phase MMR, as shown in Figure 11.

Figure 10. Topology of proposed modular multilevel rectifier. Source: [16]

Figure 11. Basic states of a MMR phase leg. Source: [16]

As shown in Figure 11(a), when both the AC output voltage  $V_a$  and AC current  $I_a$  are positive,  $D_{1a}$  and  $D_{3a}$  are turned on and the phase leg is defined as being in a positive state. As shown in Figure 11(b), when both the AC output voltage  $V_a$  and AC current  $I_a$  are negative, both  $D_{2a}$  and  $D_{4a}$  are turned on and the phase leg is defined as being in a negative state. As shown in Figure 11(c), when the polarity of the AC output voltage and the AC output current are not determined, such as when the AC output voltage  $V_a$  or AC output current  $I_a$  cross zero, the diodes  $D_{1a}$  and  $D_{4a}$  turn on and the phase leg is defined as being as being in zero state. The switching between different states is controlled via the output voltages of the different arms. The states of the three phase legs over one line cycle is illustrated in Figure 12.

Figure 12. States of 3 phases in MMR over one line cycle. Source: [16]

From Figure 12, it can be found that, not like in an MMC, where all three phases are connected in parallel across the DC bus, at least two phases, in an MMR are connected in series between the DC bus. In other words, four arms are connected in series to block the DC bus voltage instead of two arms as in an MMC. So, the voltage rating or the total number of submodules of each arm in an MMR is only half as in an MMC. For example,

in a 12kV (+/-6kV) DC system, if the DC capacitor voltage of each submodule is 1kV, a MMC will require 12 submodules per arm or 72 submodules in total without additional redundancies. But for an MMR, only 6 submodules are required per arm or 36 submodules in total. Since the output AC voltage is synthesized by the submodules, both MMC and MMR can generate the same AC side voltage with 13 voltage levels (1kV per level between +/-6kV). With such high number of voltage levels, the harmonics current flowing on the AC side can be negligible without any filters and the electromagnetic interference (EMI) issues can be significantly mitigated due to much lower dv/dt in the MVDC system compared with the traditional 2-level and 3-level converters mentioned above. Please note that, even lower submodule voltages can be used to further improve the system harmonic performance with the penalty of higher system complexity since more submodules are needed. Compared to the MMC topology, the number of power modules is reduced by half, so the energy storage requirement is also reduced by half.

# III. MODELING AND CONTROL

This chapter presents the system parameters, device thermal model, and performance evaluation criteria which is applied to the four active front end rectifier topologies.

## A. SYSTEM PARAMETERS

In modeling a shipboard system for this comparison study, the parameters chosen for base calculations are as follows:

- 1. The total apparent power of the system is 35 MVA.

- 2. The three-phase AC line-to-line voltage at the generator output  $V_{ac}$  is 6.6 kV rms.

- 3. The DC output voltage of the rectifier  $V_{dc}$  is 12 kV.

- 4. The fundamental frequency is 60 Hz.

The AC rms phase voltage is

$$V_{ac\_rms} = \frac{V_{ac}}{\sqrt{3}} = 3810.51\nu$$

(4)

and the rms AC current is

$$I_{ac\_rms} = \frac{\frac{35MVA}{3}}{V_{ac\_rms}} \approx 3kA$$

<sup>(5)</sup>

Finally, the system base impedance is

$$Z_b = \frac{V_{ac\_rms}}{I_{ac\_rms}} = 1.2446\Omega \tag{6}$$

Assuming the generator equivalent impedance is 0.3 pu, which is an estimated value for the generators in Naval shipboard operations, the synchronous inductance of the machine can be calculated as

$$L_{gen} = \frac{0.3 * Z_b}{(2\pi * 60)} = 1mH \tag{7}$$

#### **B.** ACTIVE RECTIFIER CONTROL

The system topology of a generic active rectifier is shown in Figure 13. The input AC voltage source is modeled as an ideal voltage source in series with resistors and inductors, modeling its resistance and inductance per phase. The DC output has a DC capacitor.

Figure 13. Rectifier control circuit

The goal of the rectifier control system is to regulate the output voltage  $V_{dc}$  to a constant value. The DC link voltage must be constant or vary within a specified limited range to meet the standard, no matter what the load requirement is. To achieve this target, the current  $I_{dc}$  is regulated to control  $V_{dc}$ . To achieve these control functions, a voltage control loop must be implemented, as shown in Figure 14.

Figure 14. Voltage control system block diagram

In Figure 14,  $H_2$  is describing the transfer function of the physical system on the DC side and  $H_1$  represents the control system transfer function.

The relationship between the DC side current, DC side voltage and DC capacitor in frequency domain can be represented as

$$V_{dc} = \frac{I_{dc}}{sC} \tag{8}$$

where s is the Laplace variable used as derivative operator in this capacitor voltage equation. Then

$$H_2 = \frac{V_{dc}}{I_{dc}} = \frac{1}{sC} \tag{9}$$

$H_1$  is the transfer function of the control system and this design uses a proportional – integral (PI) controller for the control system in the rectifier. The PI control transfer function is represented by  $H_1$ , where  $K_{p_v}$  is the proportional gain and  $K_{i_v}$  is the integral control gain

$$H_1 = K_{p_v} + \frac{K_{i_v}}{s}$$

(10)

To control the system response as a first order control system (the input-output relationship is a first order differential equation) with bandwidth  $\omega$ , the overall DC side open loop transfer function (T), which is calculated as the control system gain multiplied by the physical system gain, is represented by

$$T = H_1 * H_2 = \frac{\omega}{s} = (K_{p_v} + \frac{K_{i_v}}{s}) * (\frac{1}{sC})$$

(11)

where  $K_{p_v}$  and  $K_{i_v}$  are the proportional and integral gains for the voltage control loop.

$$K_{p-v} = \omega C \text{ and } K_{i-v} = 0 \tag{12}$$

The control gains in equation (12) can achieve the closed loop voltage control required to keep the DC voltage constant.

Since the converters cannot generate or absorb energy, to control  $i_{dc}$ , the AC side active power needs to be controlled to match the active power delivered to the DC side, as shown in the following power equation:

$$P = I_{dc}V_{dc} = \frac{3}{2}I_dV_d \tag{13}$$

where  $i_d$  and  $v_d$  are variables on the direct axis (d-axis) of the quadrature-direct-zero (qd0) synchronous reference frame. This reference frame is used to rotate the reference of the AC sinusoidal voltage and current waveforms so that they are stationary and can be represented as DC signals. The *abc* to qd0 transformation simplifies the control system used for the rectifiers analyzed in this thesis. The d-axis reference current on the AC side can be derived and utilized to control the rectifier voltage and current. Figure 15 shows how the three-phase voltage and current are represented as DC signals on the d-axis of the qd0 reference frame.

Figure 15. Rectifier AC side equivalent circuit on the d-axis

In Figure 15 the input voltage  $V_{d_{generator}}$  represents the d-axis component of the gas turbine generator voltage transformed from *abc* to *qd0*, and  $V_{d_{rectifier}}$  is the d-axis rectifier voltage on *qd0* reference frame.

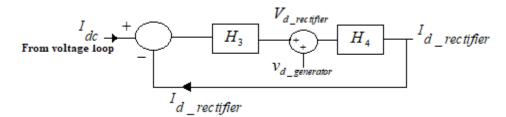

The control system for the AC side current is shown in Figure 16, where  $H_4$  represents the transfer function of the physical system on the d-axis of the qd0 reference frame and  $H_3$  represents the transfer function of the control system.  $V_{d_generator}$  is used as the feedforward term to achieve a faster dynamic response.

Figure 16. Current control system block diagram

To control rectifier current,  $I_{d\_rectifier}$ , the following equations are used to derive the values for the proportional and integral gains for the current control loop  $K_{p_i}$ ,  $K_{i_i}$ .

The AC side system can be modeled in time domain in Eq. (14) or in frequency domain in Eq. (15) to (17).

$$V_{d\_rectifier} = L \frac{dI_{d\_rectifier}}{dt} + I_{d\_rectifier} R + V_{d\_generator}$$

(14)

$$V_{d\_rectifier} - V_{d\_generator} = LsI_{d\_rectifier} + I_{d\_rectifier}R$$

(15)

$$V_{d\_rectifier} - V_{d\_generator} = (Ls + R)I_{d\_rectifier}$$

(16)

$$\frac{V_{d\_rectifier} - V_{d\_generator}}{Ls + R} = I_{d\_rectifier}$$

(17)

The voltage  $V_{d_{generator}}$  is constant DC, therefore it has no effect on the transfer function  $H_4$  and Eq (17) can be rewritten as

$$V_{d\_rectifier} = Lsi_{d\_rectifier} + I_{d\_rectifier}R$$

(18)

The transfer function of the physical system in the current loop,  $H_4$  is

$$H_4 = \frac{1}{Ls + R}.\tag{19}$$

Similar to the voltage control loop, the overall AC side current open loop transfer function ( $T_2$ ), the system response is also controlled as a first order control system with bandwidth  $\omega_i$ .

$$T_2 = H_3 * H_4 = \frac{K_{p\_i}s + K_{i\_i}}{s} * \frac{1}{Ls + R} = \frac{\omega_i}{s}$$

(20)

$$K_{p_i}s + K_{i_i} = \omega_i(Ls + R)$$

(21)

$$K_{p-i}s + K_{i-i} = Ls\omega_i + R\omega_i \tag{22}$$

So,

$$K_{p-i} = Ls\omega_i \tag{23}$$

$$K_{i-i} = R\omega_i \tag{24}$$

When  $V_{d\_generator}$  is added to the  $V_{d\_rectifier}$ , a feed forward system is created.  $V_{d\_generator}$  is a value that is set to be close to the value that we know  $V_{d\_rectifier}$  needs to be. As the control system begins making corrections to the signal, having a baseline close to the desired result makes finding the correct answer happen much more quickly. This allows the controller to reach steady state much faster.  $V_{d\_generator}$  is a voltage signal that is close to the typical value of the control target. Knowing this allows the system to speed up the process of current correction to control the converter more quickly.

Following the design rule to decouple the voltage control loop from the current control loop, the control bandwidth is picked so that  $\omega_i >> \omega_v$  and the measured current can follow the current command very quickly. In other words, when controlling the AC side current, the DC side voltage can be assumed to be constant, so in the simulation model the DC side is modeled as a constant DC voltage source. This can significantly simplify the control system design and speed up the simulation time.

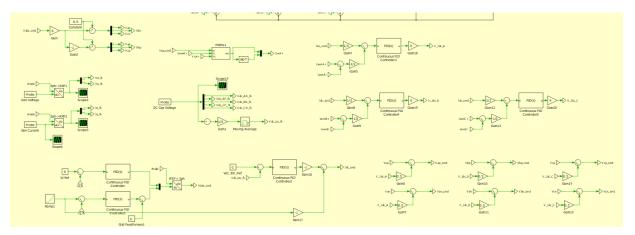

The control system presented in this section is the basic control which is used for all rectifiers analyzed in this study. As the complexity of the converter topology increases with additional levels, there is a need for additional control circuitry specific to each converter design, which is briefly covered in Ch. 4.

#### C. DEVICE THERMAL MODEL

In this study, we used the piecewise linear electric circuit simulation (PLECS) software to evaluate the performance of each topology. PLECS is a software program that allows for system level analysis of power electronics. PLECS provides the ability to build the converter topologies, then easily analyze their performance. The software has pre-made features that facilitate efficient evaluation of power electronic circuit operation.

The heat sink tool in PLECS was utilized to calculate the losses in the semiconductor devices during the steady state operation of each rectifier topology. Data can be taken directly from the semiconductor data sheet and uploaded into the PLECS thermal library as characteristics that were feed into the heat sink tool. Thermal models were developed for the 2-level and 3-level converter from the data sheet of the TOSHIBA SILICON N-CHANNEL IEGT ST2100GXH22A [17] and their anti-parallel diodes (Infineon D2700) [18], which are rated 4.5kV 2100A. In the thermal imaging wizard of the PLECS software, the diode conduction losses are included. This concept is shown in the conduction loss graph for the two semiconductor devices used in the topology simulations. Turn-on losses, turn-off losses, and conduction losses were imported into the PLECS thermal imaging library and assigned to the switching devices in the converter circuit in the PLECS simulation. Figure 17 and Figure 18 capture the thermal inputs for the switching devices and respective diodes. As the PLECS software simulates the thermal models, the

semiconductor losses are calculated and scaled up for the number of devices used in the system. This is explained in further detail in the simulation results section of this study.

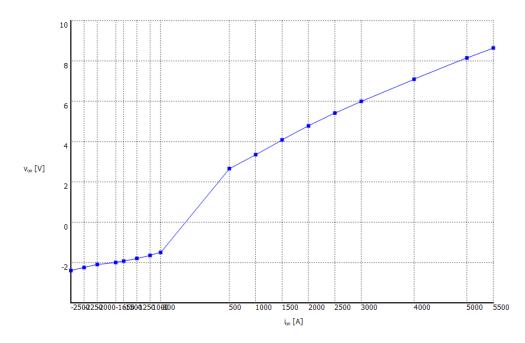

Figure 17 shows the final switching loss profile for the semiconductor switching device after the data has been uploaded into the thermal library. Figure 18 shows the conduction loss profile for the semiconductor device and anti-parallel diodes. The conduction power losses are calculated as the current multiplied by the voltage. All devices used in this study had thermal profiles built into the simulation software.

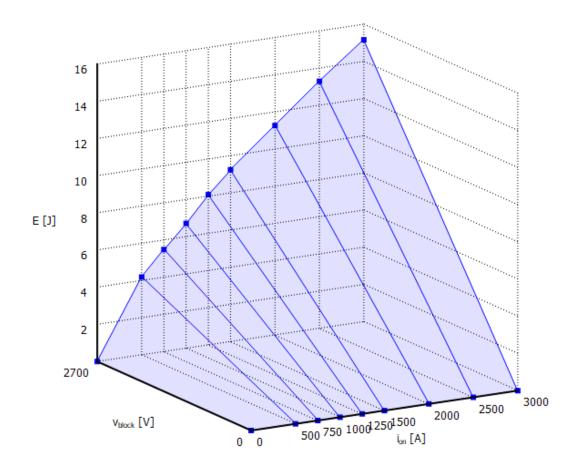

Figure 17. Switching loss thermal model for the Toshiba semiconductor

Figure 18. Conduction loss thermal model characteristics for Toshiba device

For the MMC and MMR topologies, the voltage that the switches need to block is 1kV, which is considerably lower than the 2 and 3-level converters, where the switches must block 4.5kV. Therefore, a different semiconductor was chosen; an Infineon dual IGBT module which has a large power density and more efficient power and thermal cycling capability than the devices used for the 2- and 3-level topologies [19]. The semiconductor device chosen for the MMC and MMR topologies was the Infineon FF1200R17KP4\_B2. This device can block up to 1700V and has a current handling capability of 1200 A. Due to the limited current handling capability of the device, when the IEGT is used in 2 and 3-level converter circuits, two paralleled devices must be used so that the total current rating is doubled. Using the device datasheet [20], conduction loss and switching loss graphs were loaded into the thermal wizard as was done for the Toshiba device and diode for the 2-level and 3-level converter model.

For the switching devices in the MMC and MMR topologies, current values from the data sheet are doubled to simulate the case with two devices in parallel.

For the MMR topology design, a diode thermal model had to be defined for the diode stack which is rated at half of the DC bus voltage. For this, the same diode used in

the 2-level converter was used. Since these diodes switch at the fundamental frequency, when the current flowing through them is close to zero, the diode stack switching losses are ignored. Only the conduction losses are included in the thermal property for the diodes used in the diode stack.

#### D. KEY METRICS FOR COMPARISON

All four rectifier topologies were compared based on three performance metrics: the efficiency or power losses, the AC current harmonics, and the total energy storage requirements. The efficiency is obtained based on the simulated converter losses at rated power operating conditions (35MVA). The total energy storage was calculated based on the total energy stored in the capacitors. The harmonic performance is evaluated based on the THD of the AC side current.

Total harmonic distortion is a measurement of how much the voltage or current is distorted due to harmonics in the system in integer multiples of the fundamental frequency. It is defined as the ratio of the equivalent root mean square (RMS) voltage of all the harmonic frequencies (from the 2nd harmonic on) over the RMS voltage of the fundamental frequency. While the voltage at the fundamental frequency is the desired output voltage, its multiples cause unwanted distortion in the waveform. In (25) the squared harmonic voltages are added together, and the square root is taken. The result is then divided by the voltage at the fundamental and the THD given is a percentage of the output signal representing percent distortion of the voltage waveform.

$$THD = 100 \cdot \frac{\sqrt{\sum_{n=2}^{\infty} (V_{n_rms})^2}}{V_{rms_fundamental}}$$

(25)

Power electronics systems must be designed to produce voltages and currents with THD as low as possible because higher THD negatively impact system performance by reducing the power factor and overall efficiency.

The PLECS software includes a tool to calculate the THD which accounts for all harmonics and provides a realistic representation of power quality in the system.

# **IV. SIMULATION RESULTS**

The models of the four active rectifier topologies are built using the PLECS software with the goal to compare their performance and the simulation results are presented in this chapter. It should be noted that, since one important metric to compare the four topologies is the efficiency, and the power electronic device conduction losses and switching losses are dependent on the device junction temperature, a dedicated thermal management system design is required for each converter system in the real application. So the device junction temperatures are set high enough to fully leverage the device power capability, but with sufficient margin from the maximum junction temperature for safety and reliability. However, since this thesis compares the four topologies at a high level, the ambient temperature is set to 125 degrees Celsius and very low thermal impedance between the device and ambient are used in all simulations. In other words, all thermal loss data is calculated with the assumption that the device junction temperature is 125 degrees Celsius for all four rectifiers.

#### A. TWO-LEVEL CONVERTER

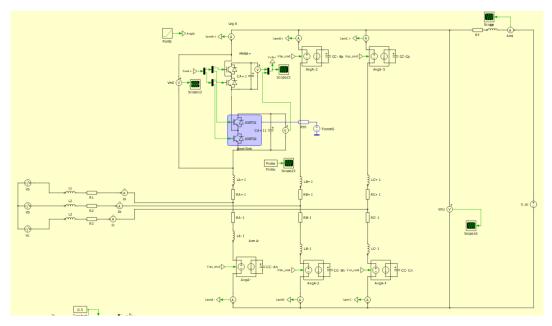

The 2-level converter design consists of 3 legs (one leg per phase), with 12 semiconductor switching devices per leg. The devices chosen for this study are Toshiba IGBT rated 4.5 kV and 2.1 kA. Since each device in the 2-level converter must be able to handle  $+\frac{V_{dc}}{2}$  to  $-\frac{V_{dc}}{2}$ , or 12 kV with additional transient overvoltage during switching and additional margin is necessary to cover the unbalanced voltage distribution among series connected devices, 6 IGBTs in series are designed per each device position with 26kV voltage blocking capability. Figure 19 shows a standard 2-level configuration with two devices per phase. Once the thermal characteristics are captured during simulation, results are then multiplied by the number of devices used in the system to achieve the 12 kV DC bus.

The switching frequency in the 2-level converter is 2kHz to achieve a good balance between power losses and harmonic performance. The current control bandwidth is set to 10% of the switching frequency. Figure 19 shows the circuit configuration as designed in PLECS.

Figure 19. 2-level rectifier as modeled in PLECS