# THE UNIVERSITY of EDINBURGH

This thesis has been submitted in fulfilment of the requirements for a postgraduate degree (e.g. PhD, MPhil, DClinPsychol) at the University of Edinburgh. Please note the following terms and conditions of use:

- This work is protected by copyright and other intellectual property rights, which are retained by the thesis author, unless otherwise stated.

- A copy can be downloaded for personal non-commercial research or study, without prior permission or charge.

- This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author.

- The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author.

- When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

## Composite Power Semiconductor Switches for High-Power Applications

Ross Ellis Mathieson

A thesis presented for the degree of Doctor of Philosophy

> School of Engineering University of Edinburgh 2020

## Declaration

I declare that this thesis has been composed solely by myself and that it has not been submitted, in whole or in part, in any previous application for a degree. Except where states otherwise by reference or acknowledgement, the work presented is entirely my own.

Date:

Signed:

### Abstract

It is predicted that 80 % of the world's electricity will flow through power electronic based converters by 2030, with a growing demand for renewable technologies and the highest levels of efficiency at every stage from generation to load. At the heart of a power electronic converter is the power semiconductor switch which is responsible for controlling and modulating the flow of power from the input to the output. The requirements for these power semiconductor switches are vast, and include: having an extremely low level of conduction and switching losses; being a low source of electromagnetic noise, and not being susceptible to external Electromagnetic Interference (EMI); and having a good level of ruggedness and reliability. These high-performance switches must also be economically viable and not have an unnecessarily large manufacturing related carbon footprint.

This thesis investigates the switching performance of the two main semiconductor switches used in high-power applications — the well-established Silicon (Si)-Insulated-Gate Bipolar Transistor (IGBT) and the state-of-the-art Wide-Bandgap (WBG) Silicon-Carbide (SiC)-Metal–Oxide–Semiconductor Field-Effect Transistor (MOSFET). The SiC-MOSFET is ostensibly a better device than the Si-IGBT due to the lower level of losses, however the cost of the device is far greater and there are characteristics which can be troublesome, such as the high levels of oscillatory behaviour at the switching edges which can cause serious Electromagnetic Compatibility (EMC) issues. The operating mechanisms of these devices, the materials which are used to make them, and their auxiliary components are critically analysed and discussed. This includes a head-to-head comparison of the two high-capacity devices in terms of their losses and switching characteristics. The design of a high-power Double-Pulse Test Rig (DPTR) and the associated high-bandwidth measurement platform is presented. This test rig is then extensively used throughout this thesis to experimentally characterise the switching performance of the aforementioned high-capacity power semiconductor devices.

A hybrid switch concept — termed "The Diverter" — is investigated, with the motivation of achieving improved switching performance without the highcost of a full SiC solution. This comprises a fully rated Si-IGBT as the main conduction device and a part-rated SiC-MOSFET which is used at the turn-off. The coordinated switching scheme for the Si/SiC-Diverter is experimentally examined to determine the required timings which yield the lowest turn-off loss and the lowest level of oscillatory behaviour and other EMI precursors. The thermal stress imposed on the part-rated SiC-MOSFET is considered in a junction temperature simulation and determined to be negligible. This concept is then analysed in a grid-tied converter simulation and compared to a fully rated SiC-MOSFET and Si-IGBT. A conduction assistance operating mode, which solely uses the part-rated SiC-MOSFET when within its rating, is also investigated. Results show that the Diverter achieves a significantly lower level of losses compared to a Si-IGBT and only marginally higher than a full SiC solution. This is achieved at a much lower cost than a full SiC solution and may also provide a better method of achieving high-current SiC switches.

## Acknowledgements

Firstly, I would like to express my gratitude to my supervisor Prof. Stephen Finney for this opportunity and for his support and guidance over the past four years. I would also like to thank Dr. Michaël Merlin for the numerous technical discussions and Dr. Paul Judge for all his knowledge and collaborations on my research.

I am very grateful for the friendships I have made during my PhD and I would like to express my thanks to all those who have helped and supported me. I would especially like to mention: Zehong, Zoe, Alyx, Marlee, Agatha, Peng, Nina, Richard, Dimitrios, Max, Darwish, and Atef. Additional thanks must also go to the various technicians at the School of Engineering who helped make our ambitious hardware plans possible.

My appreciation also goes out to my family for the unconditional support and belief in me.

And finally, to Alison for the patience and motivation, particularly during the final few months.

# Contents

| D  | eclar | ration                                              | ii    |

|----|-------|-----------------------------------------------------|-------|

| A  | bstra | act                                                 | iii   |

| A  | cknov | wledgements                                         | v     |

| C  | onter | $\mathbf{nts}$                                      | vi    |

| Li | st of | f Figures                                           | xii   |

| Li | st of | f Tables                                            | xviii |

| Li | st of | f Acronyms                                          | xx    |

| N  | omer  | nclature                                            | XXV   |

| 1  | Intr  | roduction                                           | 1     |

|    | 1.1   | The Role of Power Electronics                       | 1     |

|    | 1.2   | Semiconductor Devices in a Power Converter          | 2     |

|    |       | 1.2.1 Half-Bridge in Voltage-Source Converter (VSC) | 3     |

|    |       | 1.2.2 Effective High-Capacity Semiconductor Devices | 6     |

|    | 1.3   | Research Motivations and Objectives                 | 8     |

|   | 1.4 | Thesis | Structure                                                    | 8  |

|---|-----|--------|--------------------------------------------------------------|----|

| 2 |     |        | niconductor Devices Technology Review: Traditional<br>andgap | 10 |

|   | 2.1 | Chapt  | er Introduction                                              | 10 |

|   | 2.2 | Power  | Semiconductor Technologies                                   | 11 |

|   |     | 2.2.1  | Basic Solid-State Physics                                    | 11 |

|   |     | 2.2.2  | Wide-Bandgap Semiconductor Materials                         | 15 |

|   | 2.3 | Power  | Semiconductor Devices                                        | 18 |

|   | 2.4 | The D  | iode                                                         | 19 |

|   |     | 2.4.1  | Ideal Power Diode                                            | 19 |

|   |     | 2.4.2  | pn Junction                                                  | 19 |

|   |     | 2.4.3  | $pn$ Junction Diode $\ldots$                                 | 21 |

|   |     | 2.4.4  | Diode Transient Behaviour                                    | 23 |

|   |     | 2.4.5  | Power Diodes                                                 | 25 |

|   | 2.5 | The T  | ransistor                                                    | 29 |

|   |     | 2.5.1  | Ideal Power Switch                                           | 29 |

|   |     | 2.5.2  | Metal–Oxide–Semiconductor Field-Effect Transistor (MOS-FET)  | 30 |

|   |     | 2.5.3  | Insulated-Gate Bipolar Transistor (IGBT)                     | 40 |

|   | 2.6 | Wide-  | Bandgap (WBG) Power Semiconductor Devices                    | 47 |

|   |     | 2.6.1  | Silicon Carbide Devices                                      | 48 |

|   |     | 2.6.2  | Other WBG Devices                                            | 51 |

|   |     | 2.6.3  | WBG Device Considerations                                    | 52 |

|   | 2.7 | Real F | Power Devices                                                | 56 |

|   |     | 2.7.1  | Semiconductor Die                                                                  | 56  |

|---|-----|--------|------------------------------------------------------------------------------------|-----|

|   |     | 2.7.2  | Device Packaging                                                                   | 58  |

|   |     | 2.7.3  | WBG Packaging                                                                      | 61  |

|   |     | 2.7.4  | Advanced WBG Packaging in Literature                                               | 62  |

| • | Ð   |        |                                                                                    |     |

| 3 |     |        | n of High-Power Double-Pulse Test Rig & Measure-<br>pment for Wide-Bandgap Devices | 67  |

|   | 3.1 | Chapte | er Introduction                                                                    | 67  |

|   | 3.2 | Double | e-Pulse Test Rig (DPTR)                                                            | 69  |

|   |     | 3.2.1  | Double-Pulse Test                                                                  | 69  |

|   |     | 3.2.2  | Methodology                                                                        | 70  |

|   | 3.3 | DPTR   | Power Circuit Realisation & Theory                                                 | 72  |

|   |     | 3.3.1  | Charging Circuitry                                                                 | 73  |

|   |     | 3.3.2  | DC Busbar and Capacitors                                                           | 74  |

|   |     | 3.3.3  | Inductive Load                                                                     | 87  |

|   | 3.4 | DPTR   | Full System & Associated Components                                                | 92  |

|   |     | 3.4.1  | System Architecture                                                                | 92  |

|   |     | 3.4.2  | Gate-Drivers                                                                       | 95  |

|   |     | 3.4.3  | DPTR Commissioning Tests                                                           | 100 |

|   | 3.5 | Effect | of Parasitic Elements on Device Switching                                          | 102 |

|   |     | 3.5.1  | Current Overshoot at Turn-On (Reverse Recovery) $\ . \ . \ .$                      | 103 |

|   |     | 3.5.2  | Voltage Overshoot at Turn-Off                                                      | 104 |

|   |     | 3.5.3  | Oscillations in Voltage & Current                                                  | 105 |

|   |     | 3.5.4  | Further Experimental Results on Parasitic Effects                                  | 107 |

|   |     | 3.5.5  | Electromagnetic Interference (EMI) Impact of Device Tran-<br>sients                     | 112      |

|---|-----|--------|-----------------------------------------------------------------------------------------|----------|

|   | 3.6 | High-l | Bandwidth Measurement Equipment                                                         | 116      |

|   |     | 3.6.1  | Oscilloscope                                                                            | 117      |

|   |     | 3.6.2  | Voltage Measurement                                                                     | 120      |

|   |     | 3.6.3  | Current Measurement                                                                     | 124      |

|   |     | 3.6.4  | Radiated EMI Probes                                                                     | 130      |

|   | 3.7 | Switch | ning Loss Calculations                                                                  | 131      |

|   |     | 3.7.1  | Data Processing                                                                         | 131      |

|   |     | 3.7.2  | Switching Loss Estimations                                                              | 132      |

| 4 |     |        | FETs & Si-IGBTs: Characterising High-Capacity De<br>onsiderations for full Exploitation | -<br>134 |

|   | 4.1 | Chapt  | er Introduction                                                                         | 134      |

|   | 4.2 | Head-  | to-Head: Si-IGBT & SiC-MOSFET                                                           | 135      |

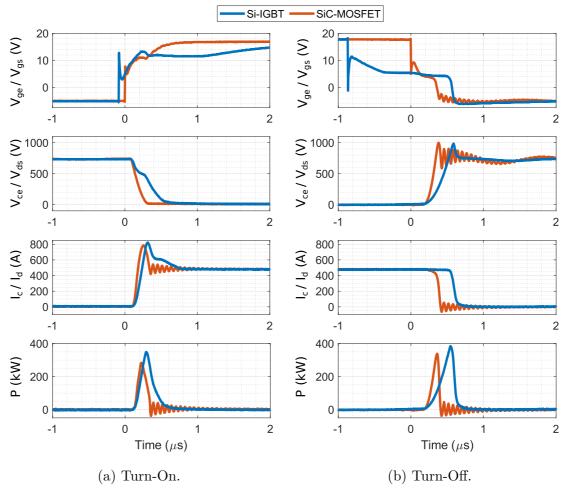

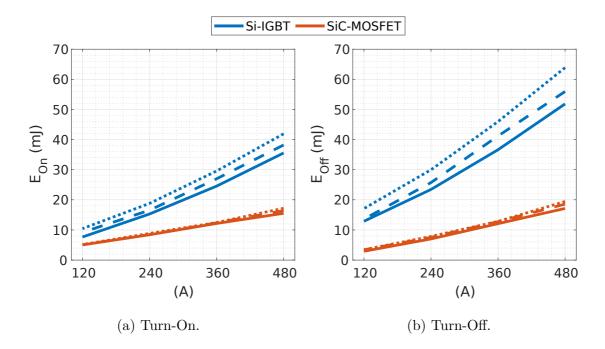

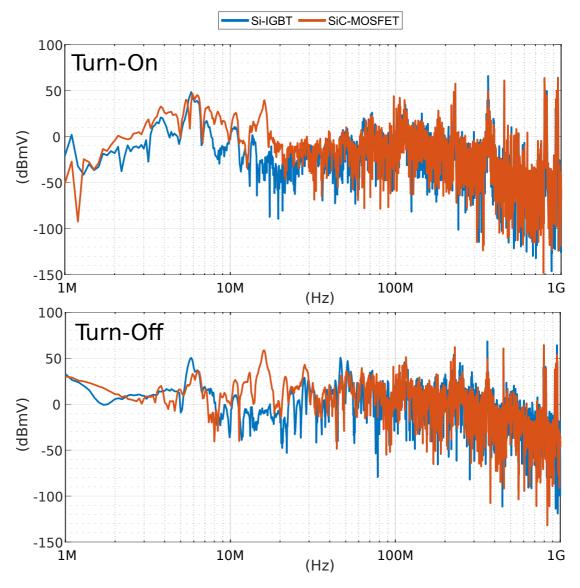

|   |     | 4.2.1  | Experimental Comparison of Switching Transients                                         | 136      |

|   |     | 4.2.2  | Further Comparison                                                                      | 140      |

|   | 4.3 | Requi  | red Measurement Bandwidth for SiC                                                       | 144      |

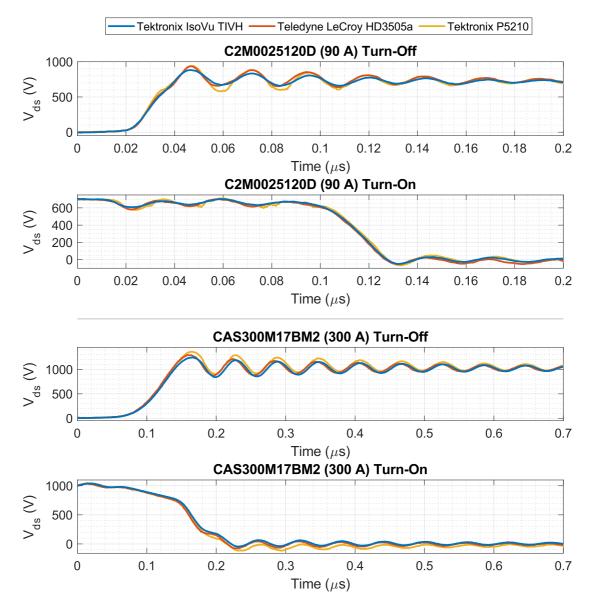

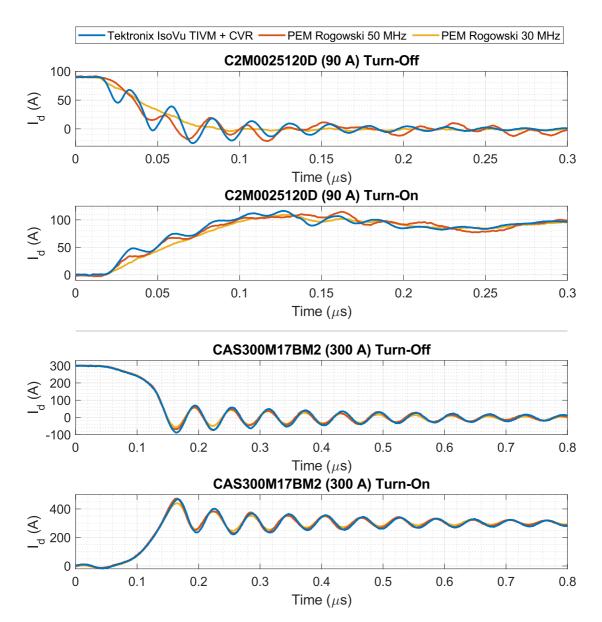

|   |     | 4.3.1  | Voltage Probe Measurements                                                              | 145      |

|   |     | 4.3.2  | Current Probe Measurements                                                              | 146      |

|   |     | 4.3.3  | Discussion on the Probes                                                                | 147      |

|   | 4.4 | Hybrid | d IGBT                                                                                  | 148      |

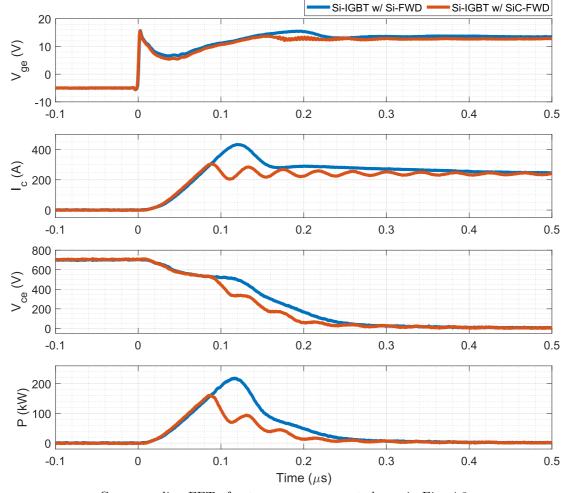

|   |     | 4.4.1  | Si-IGBT with SiC-FWD                                                                    | 148      |

|   |     | 4.4.2  | Snappy Diode Recovery Behaviour                                                         | 151      |

|   | 4.5 | Slowin | ng Down SiC-MOSFET Transients                                                           | 154      |

|   | 4.6 | Manag  | ging Switching Transients                                                            | 161 |

|---|-----|--------|--------------------------------------------------------------------------------------|-----|

|   |     | 4.6.1  | Snubber Circuits                                                                     | 161 |

|   |     | 4.6.2  | Active Gate-Drivers (AGD)                                                            | 163 |

| 5 | The | Diver  | ter: A Si/SiC Hybrid Switch                                                          | 170 |

|   | 5.1 | Chapt  | er Introduction                                                                      | 170 |

|   | 5.2 | Divert | er: Principle of Operation                                                           | 171 |

|   |     | 5.2.1  | Previous Work in Literature                                                          | 171 |

|   |     | 5.2.2  | Diverter: This Study                                                                 | 175 |

|   |     | 5.2.3  | Diverter: Overview of Coordinated Switching at Turn-Off                              | 176 |

|   |     | 5.2.4  | Diverter: Selection of SiC-MOSFET & Si-IGBT                                          | 178 |

|   | 5.3 | Divert | er: Determining Delay Period for Minimum Turn-Off Loss .                             | 179 |

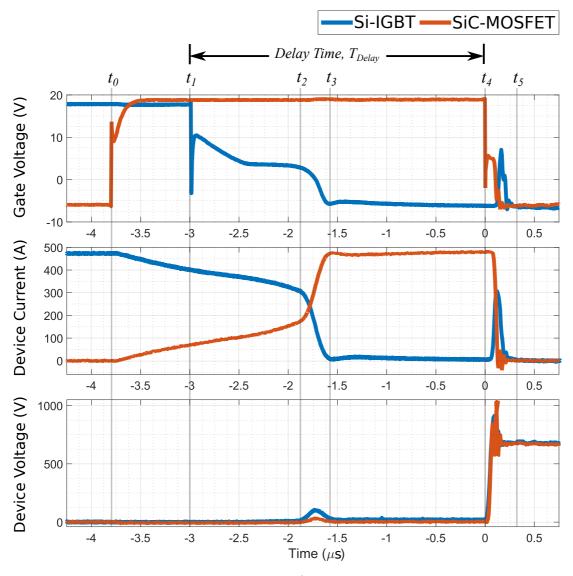

|   |     | 5.3.1  | Current Commutation from IGBT to MOSFET                                              | 180 |

|   |     | 5.3.2  | MOSFET Conduction Period                                                             | 184 |

|   |     | 5.3.3  | Turn-Off Event                                                                       | 185 |

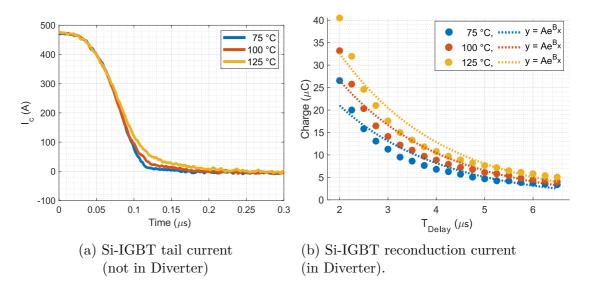

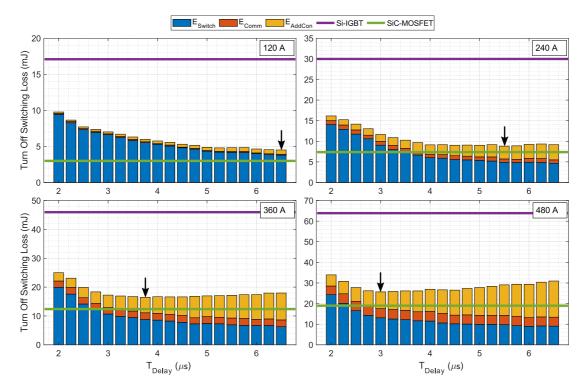

|   |     | 5.3.4  | Overall Turn-Off Switching Loss                                                      | 189 |

|   | 5.4 | Divert | er: Further Analysis on Turn-Off                                                     | 192 |

|   |     | 5.4.1  | Influence of Parallel Connected SiC-MOSFET on Si-IGBT<br>Turn-On Behaviour           | 192 |

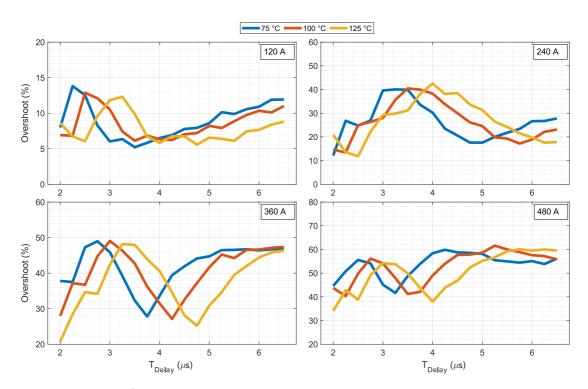

|   |     | 5.4.2  | Naturally Damped Oscillations and Overshoot                                          | 195 |

|   |     | 5.4.3  | Relating Damping to Radiated EMI                                                     | 201 |

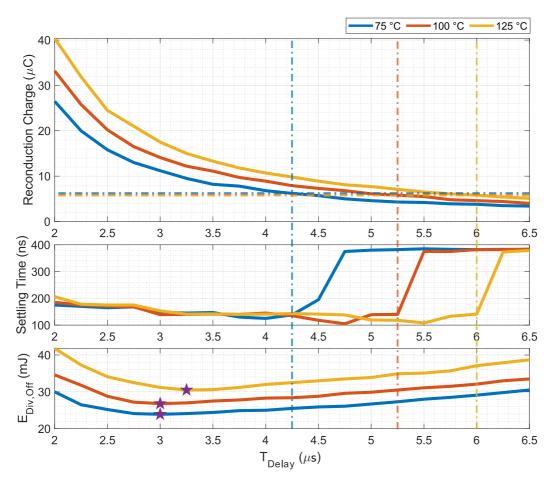

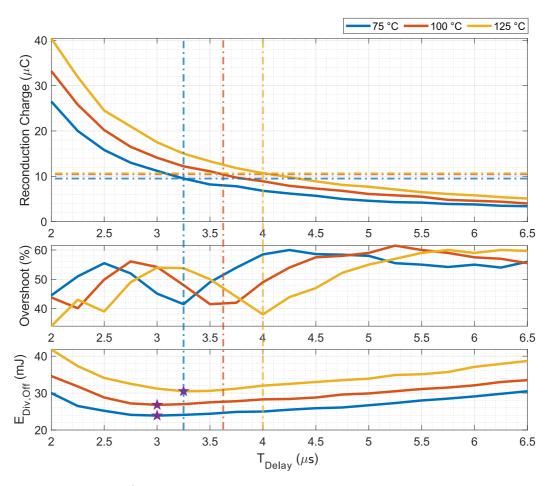

|   |     | 5.4.4  | Delay Period for Minimum Switching Loss, Voltage Over-<br>shoot, and/or Oscillations | 202 |

|   | 5.5 | Discus | sion: Si/SiC-Diverter vs. SiC-MOSFET vs. Si-IGBT                                     | 203 |

|   |     | 5.5.1  | Turn-Off Loss                                                                        | 204 |

|    |       | 5.5.2   | Oscillatory Behaviour and Overshoot Voltage                         | 206 |

|----|-------|---------|---------------------------------------------------------------------|-----|

|    |       | 5.5.3   | Justification for the Diverter                                      | 208 |

| 6  | The   | Diver   | ter: Converter Losses & Thermal Stress Simulations                  | 212 |

|    | 6.1   | Chapte  | er Introduction                                                     | 212 |

|    | 6.2   | Divert  | er: Use in a Converter                                              | 213 |

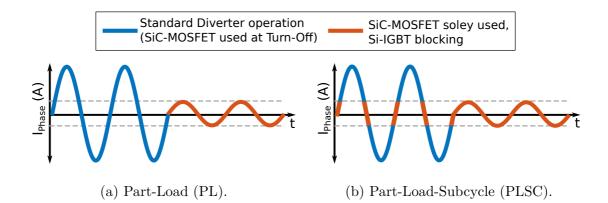

|    |       | 6.2.1   | Part-Load                                                           | 213 |

|    |       | 6.2.2   | Converter Simulation                                                | 215 |

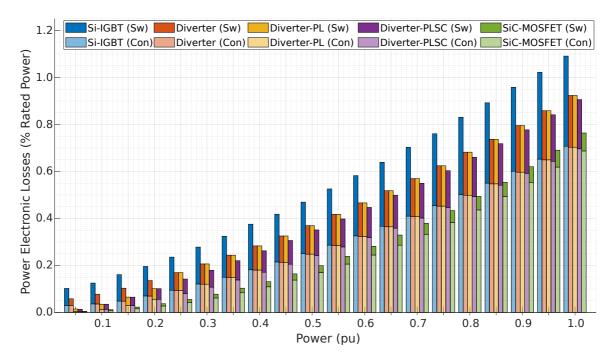

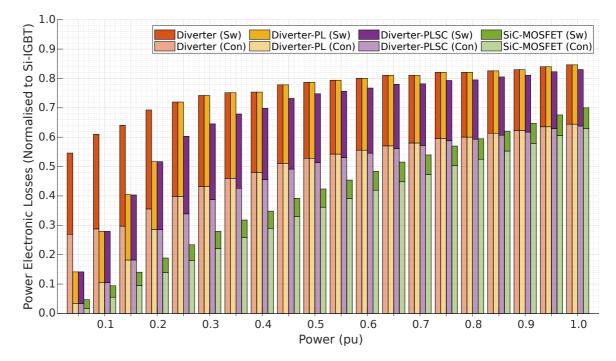

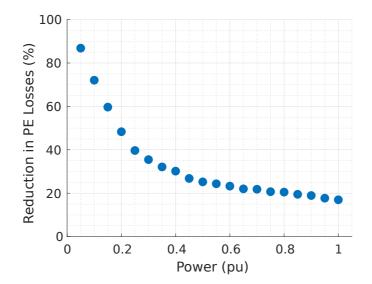

|    |       | 6.2.3   | Power Electronic Efficiency Estimates & Discussion                  | 218 |

|    | 6.3   | Divert  | er: Thermal Stress on SiC-MOSFET                                    | 221 |

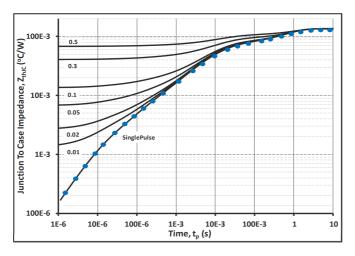

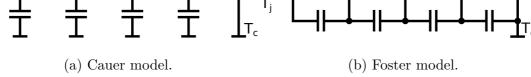

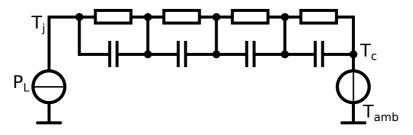

|    |       | 6.3.1   | Thermal Impedance                                                   | 221 |

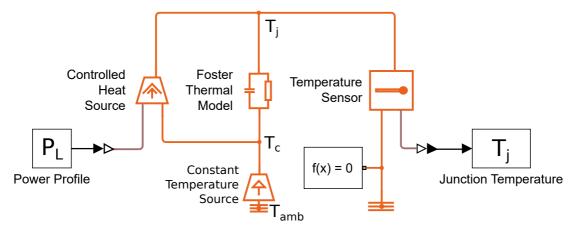

|    |       | 6.3.2   | Thermal Simulink Model                                              | 224 |

|    |       | 6.3.3   | Thermal Simulation: Constructing the Power Profile for Steady-State | 226 |

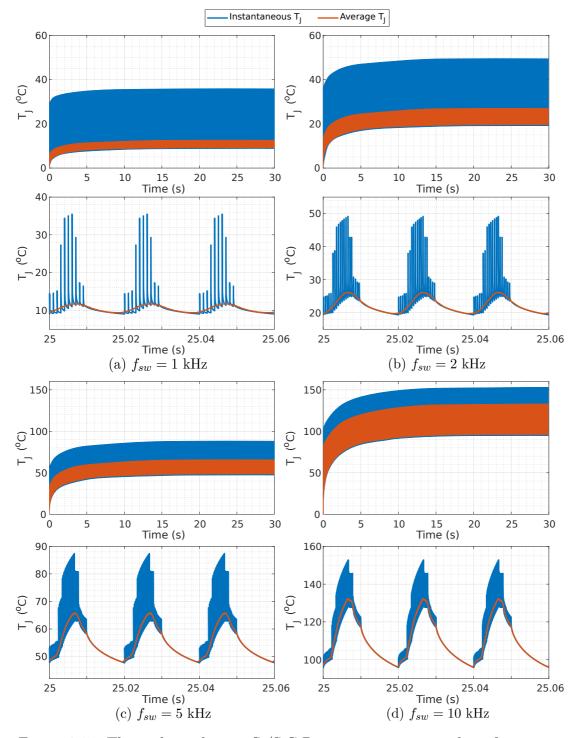

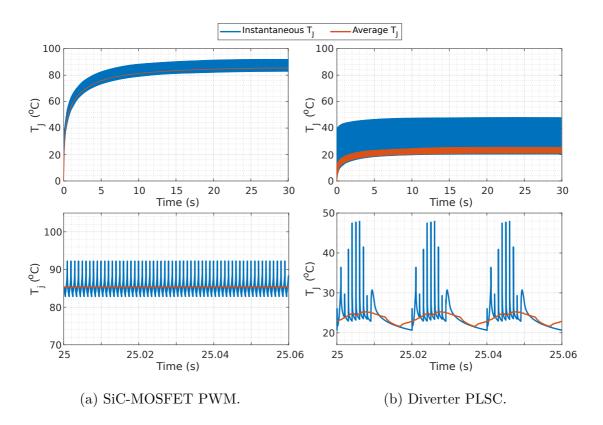

|    |       | 6.3.4   | Thermal Simulation: Steady-State                                    | 228 |

|    |       | 6.3.5   | Discussion on Thermal Stress                                        | 230 |

| 7  | Con   | clusior | 18                                                                  | 236 |

|    | 7.1   | Conclu  | usions on Hybrid Switching & The Si/SiC Diverter $\ldots$ .         | 236 |

|    | 7.2   |         | of the Art High-Capacity Transistors - Literature Review            | 239 |

|    | 7.3   | Recom   | umendations for Future Work                                         | 242 |

|    | 7.4   | Impact  | t of High-Power Double Pulse Test-Rig                               | 243 |

|    | 7.5   | Public  | ations Arising from this Thesis                                     | 244 |

| Bi | bliog | graphy  |                                                                     | 245 |

# List of Figures

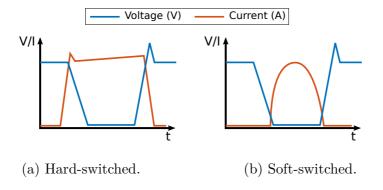

| 1.1  | Device switching classification                                                | 2  |

|------|--------------------------------------------------------------------------------|----|

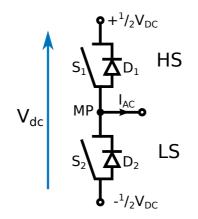

| 1.2  | Half-bridge (HB) configuration for VSC                                         | 3  |

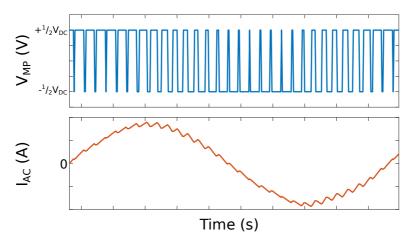

| 1.3  | Two-level inverter voltage and current waveforms                               | 4  |

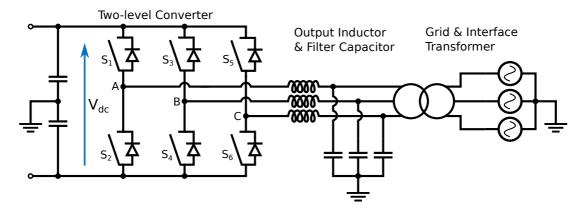

| 1.4  | Three-phase inverter example (circuit diagram)                                 | 5  |

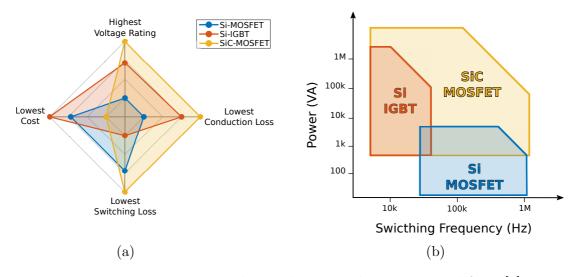

| 1.5  | Power semiconductor device qualities                                           | 7  |

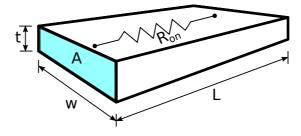

| 2.1  | Semiconductor material resistance.                                             | 13 |

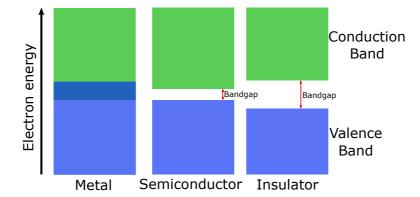

| 2.2  | Conduction and valence bands of metal, semiconductor, and insulator materials. | 14 |

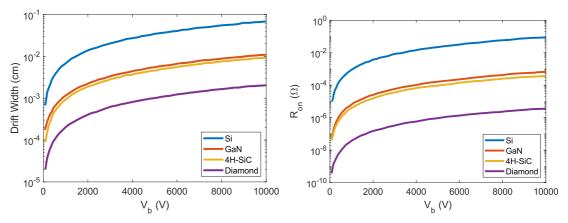

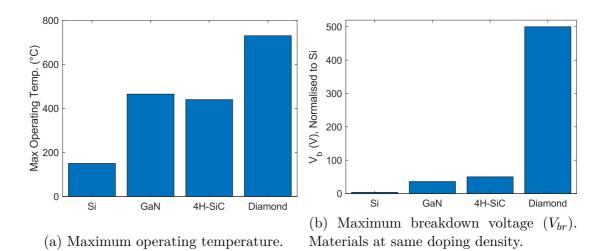

| 2.3  | Drift region width and on-resistance of Si and WBG semiconductors.             | 17 |

| 2.4  | Maximum operating conditions of Si and WBG semiconductors                      | 17 |

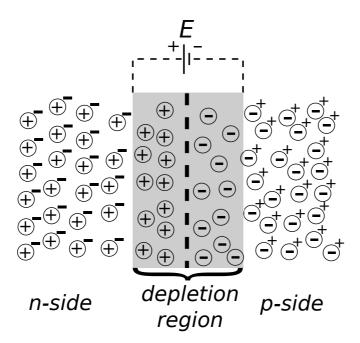

| 2.5  | pn junction and depletion region                                               | 20 |

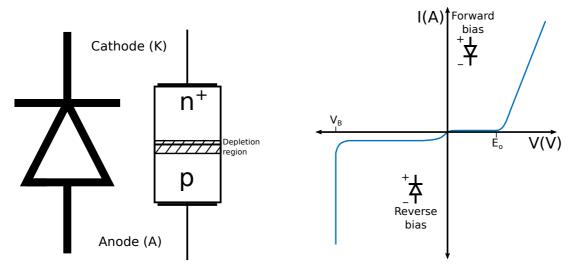

| 2.6  | pn Junction Diode                                                              | 22 |

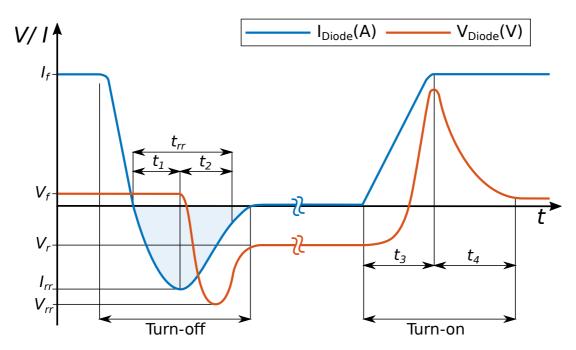

| 2.7  | Turn-off and turn-on transients of diode                                       | 24 |

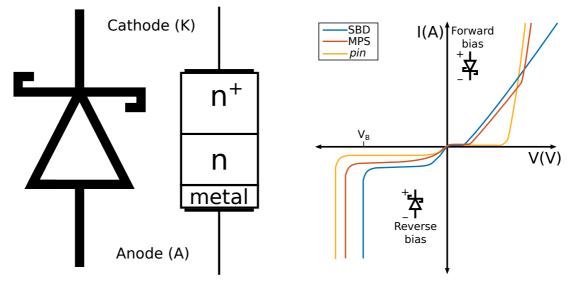

| 2.8  | Schottky Diode                                                                 | 27 |

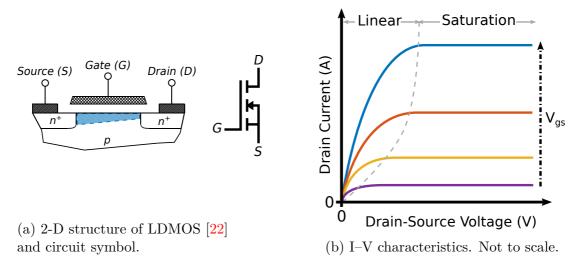

| 2.9  | Metal–Oxide–Semiconductor Field-Effect Transistor (MOSFET)                     | 31 |

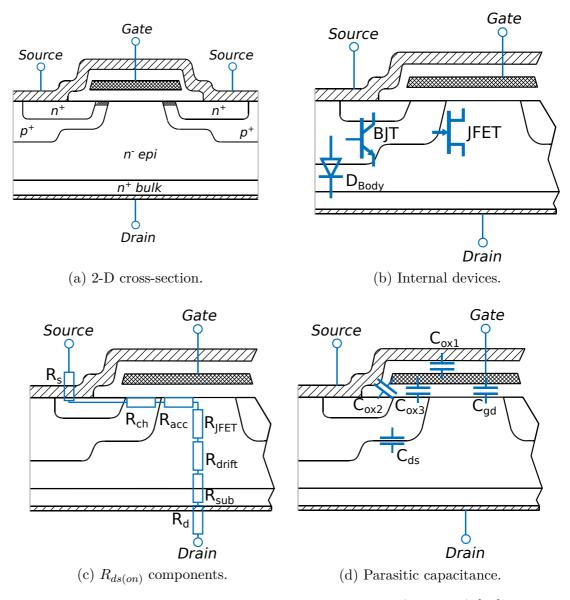

| 2.10 | Vertical Double-Diffused MOSFET (VDMOS)                                        | 33 |

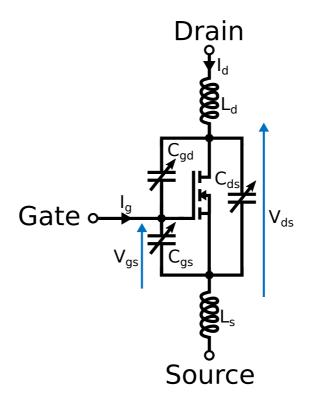

| 2.11 | Parasitic capacitance and inductance of MOSFET                                 | 35 |

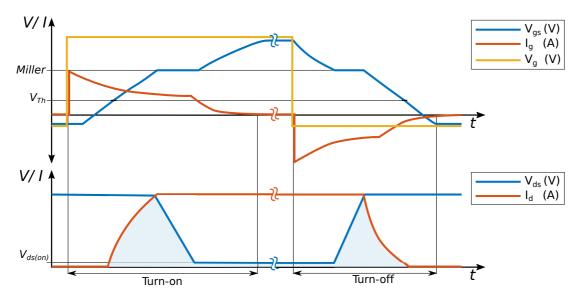

| 2.12 | Turn-off and turn-on transients of MOSFET                                      | 36 |

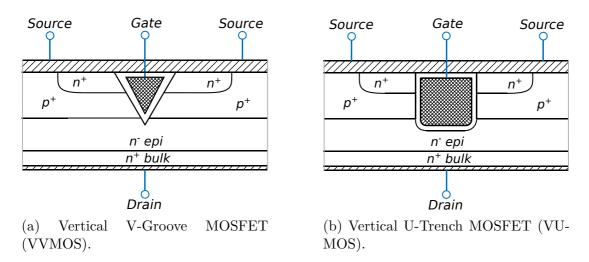

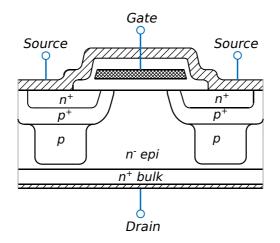

| 2.13 | 2-D cross-section of trench-gate MOSFET structures                      | 38 |

|------|-------------------------------------------------------------------------|----|

| 2.14 | 2-D cross-section of Superjunction MOSFET structure                     | 40 |

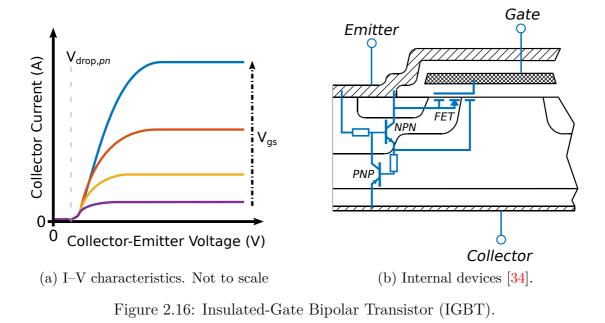

| 2.15 | Insulated-Gate Bipolar Transistor (IGBT)                                | 41 |

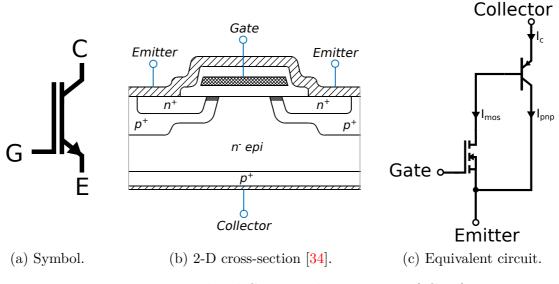

| 2.16 | Insulated-Gate Bipolar Transistor (IGBT)                                | 42 |

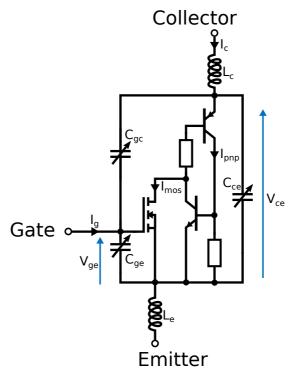

| 2.17 | IGBT internal devices and parasitic elements                            | 43 |

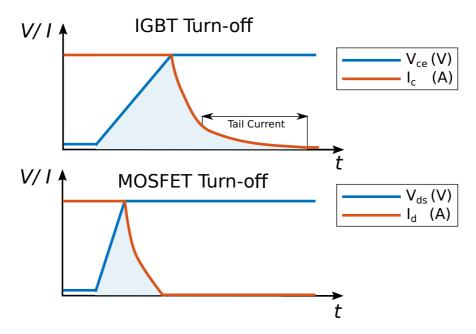

| 2.18 | IGBT turn-off transient compared to MOSFET                              | 44 |

| 2.19 | 3-D structure of vertical power transistor with trench-gates. $\ . \ .$ | 56 |

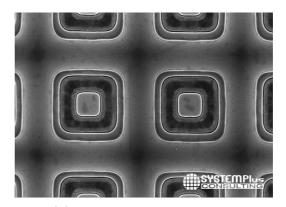

| 2.20 | Scanning electron microscope images of SiC-MOSFET die                   | 56 |

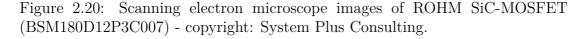

| 2.21 | MOSFET bare die images                                                  | 57 |

| 2.22 | Selection of power semiconductor packages.                              | 59 |

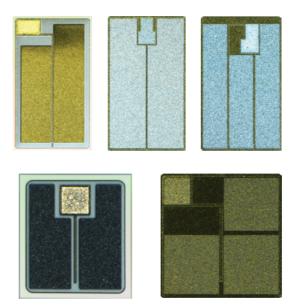

| 2.23 | Kelvin-Source (KS) connection of MOSFET                                 | 60 |

| 2.24 | Cree XM3 SiC MOSFET power module                                        | 61 |

| 2.25 | STMicroelectronics low inductance SiC-MOSFET package                    | 63 |

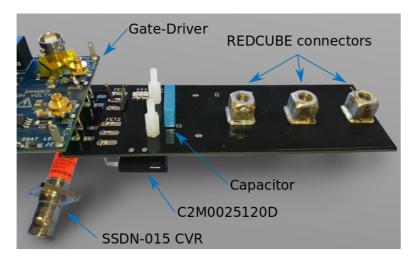

| 3.1  | Photograph of the Double-Pulse Test Rig (DPTR)                          | 69 |

| 3.2  | Double-pulse test methodology.                                          |    |

|      |                                                                         |    |

| 3.3  | Double-pulse test waveforms.                                            | 71 |

| 3.4  | DPTR full circuit diagram.                                              | 72 |

| 3.5  | High-voltage optically controlled relay PCB                             | 73 |

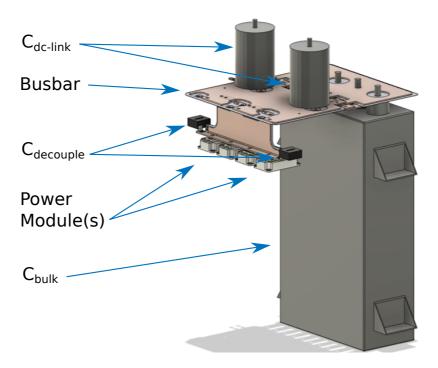

| 3.6  | Render of the main power circuit in the DPTR                            | 75 |

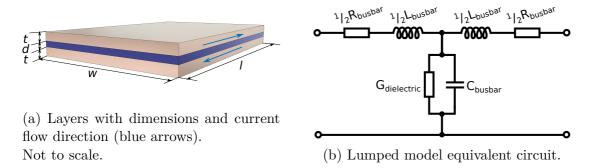

| 3.7  | Planar two layer busbar.                                                | 78 |

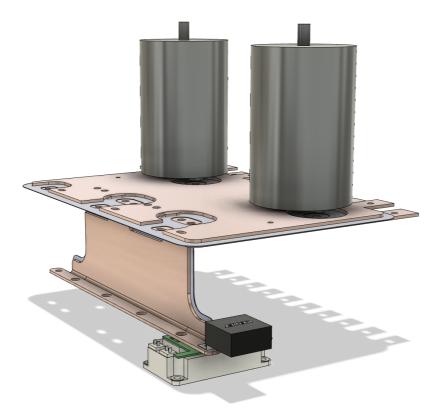

| 3.8  | Render of the main DC busbar and decoupling capacitors                  | 83 |

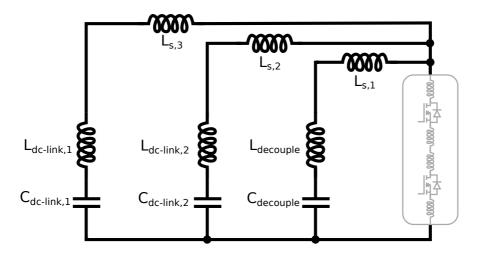

| 3.9  | Parasitic schematic diagram of DPTR busbar.                             | 84 |

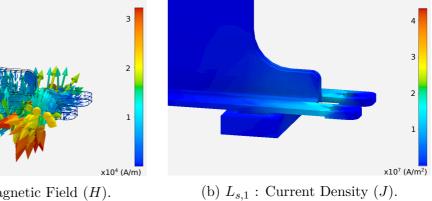

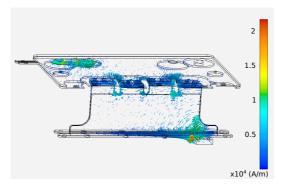

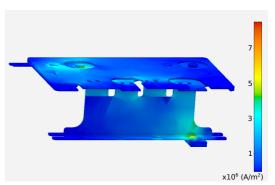

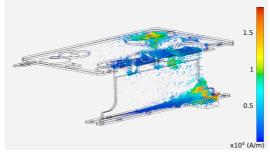

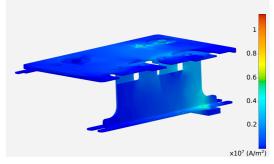

| 3.10 | FEM modelling of $L_s$                                                  | 85 |

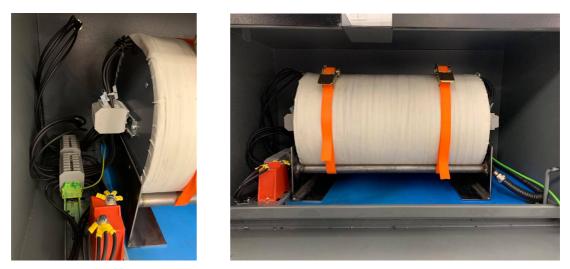

| 3.11 | Photograph of DPTR inductive load $(L_{Load})$                                                   | 87  |

|------|--------------------------------------------------------------------------------------------------|-----|

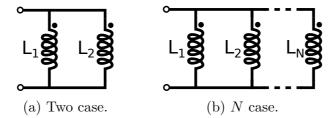

| 3.12 | Mutually-coupled parallel inductors.                                                             | 89  |

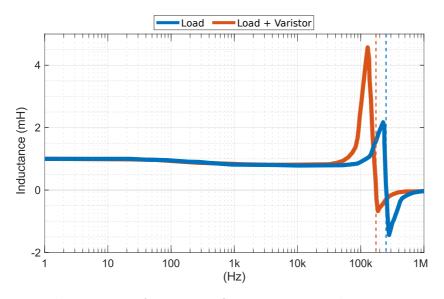

| 3.13 | Inductance vs. Frequency of $L_{Load}$                                                           | 90  |

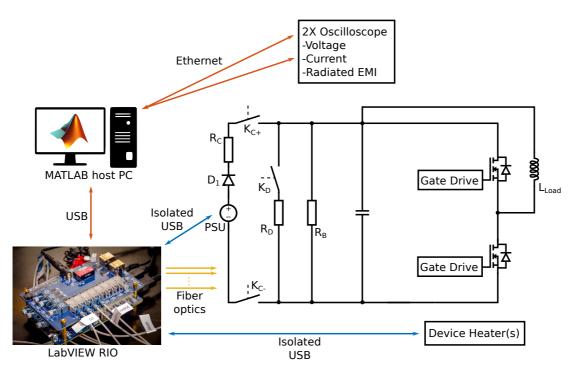

| 3.14 | Overview of the full DPTR platform                                                               | 92  |

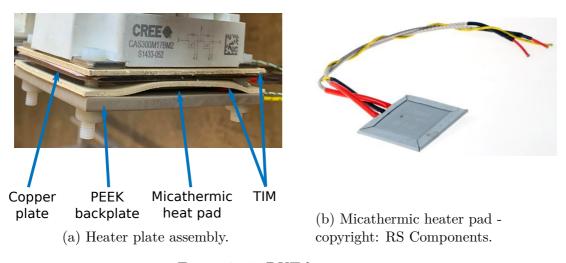

| 3.15 | DUT heat source                                                                                  | 94  |

| 3.16 | Basic gate-drive functionality                                                                   | 95  |

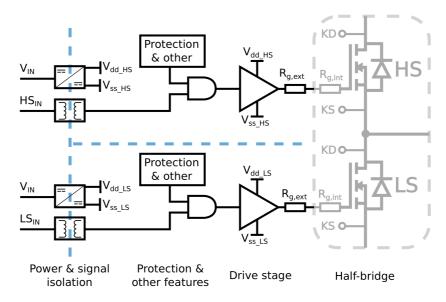

| 3.17 | Half-bridge gate-drivers used in DPTR                                                            | 99  |

| 3.18 | Photograph of device failures from commissioning tests                                           | 101 |

| 3.19 | Intentional failure commissioning tests                                                          | 102 |

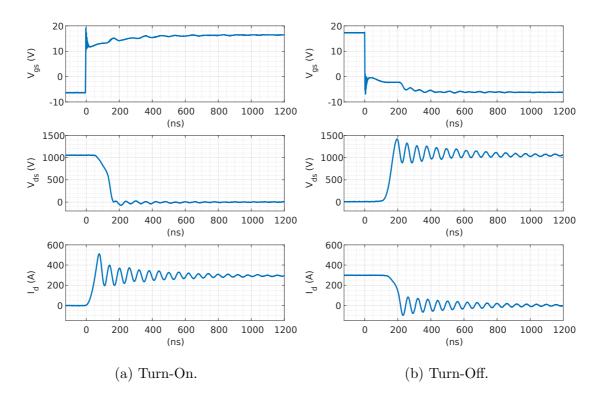

| 3.20 | Experimental measurements of SiC-MOSFET transient behaviour.                                     | 103 |

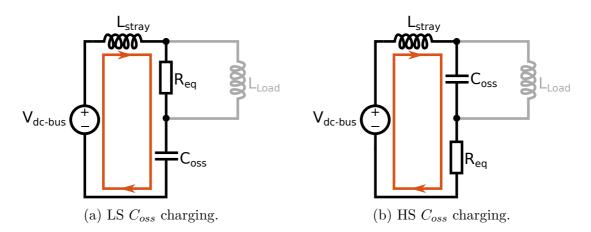

| 3.21 | Half-bridge resonant charging circuit                                                            | 105 |

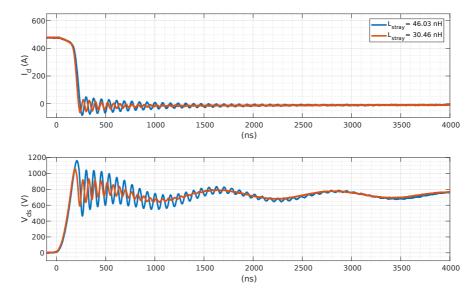

| 3.22 | Experimental measurements of SiC-MOSFET, showing impact of increased $L_{stray}$                 | 107 |

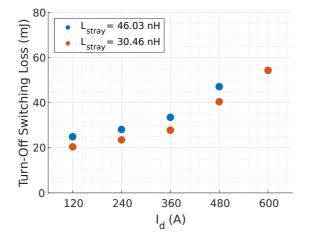

| 3.23 | Turn-off switching loss energy of SiC-MOSFET, showing impact of increased $L_{stray}$ .          | 108 |

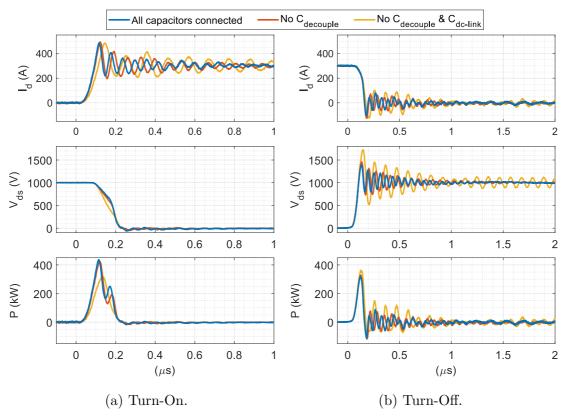

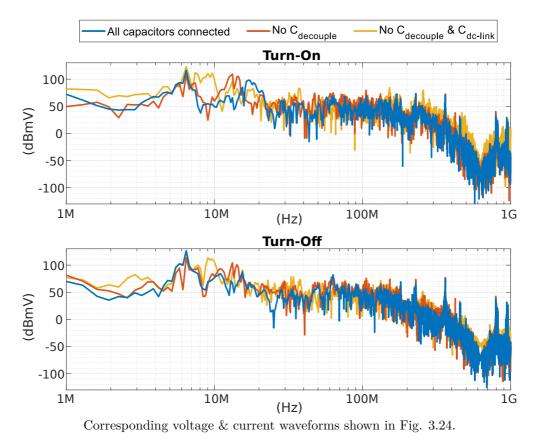

| 3.24 | Experimental measurements of SiC-MOSFET, showing impact of removing decoupling capacitors.       | 109 |

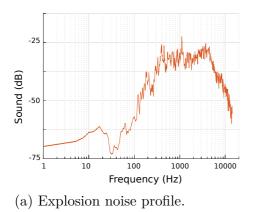

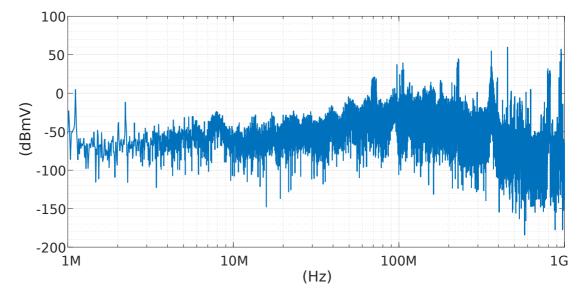

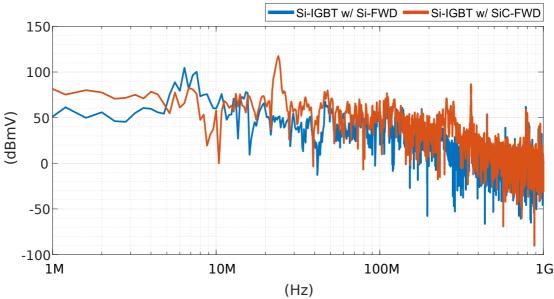

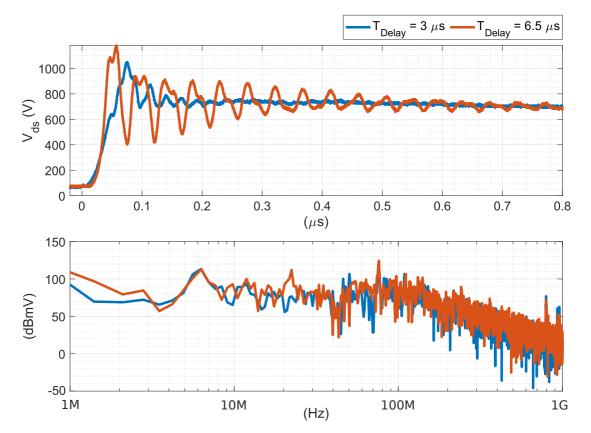

| 3.25 | FFT of antenna measurements                                                                      | 110 |

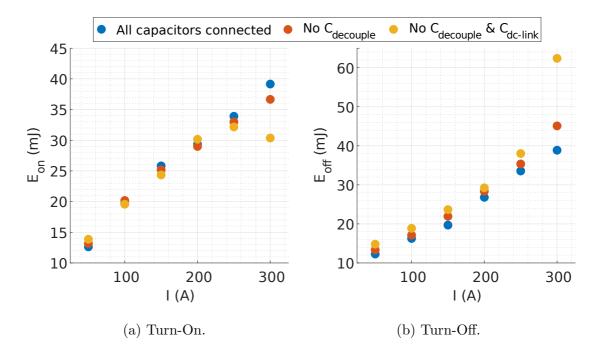

| 3.26 | Switching loss energy of SiC-MOSFET, showing impact of remov-<br>ing decoupling capacitors.      | 111 |

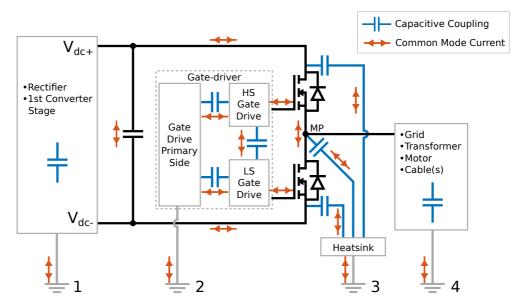

| 3.27 | Capacitive coupling paths and common-mode current paths in a typical two-level converter system. | 113 |

| 3.28 | Measurement probes used in this study                                                            | 119 |

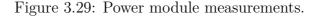

| 3.29 | Power module measurements                                                                        | 122 |

| 3.30 | Power module measurements                                                                        | 123 |

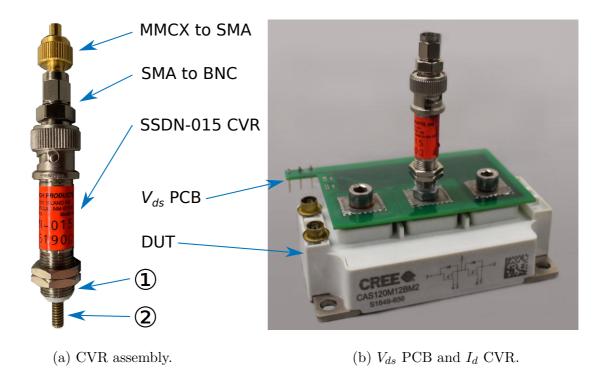

| 3.31 | Coaxial Current Viewing Resistor (CVR).                                                          | 125 |

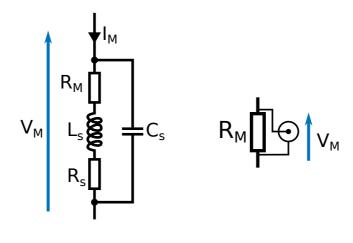

| 3.32 | Diagram of Rogowski coil principle                                                                                                                            | 127 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.33 | BicoLOG 20100 X from Aaronia.                                                                                                                                 | 130 |

| 3.34 | FFT plot of background EMI                                                                                                                                    | 131 |

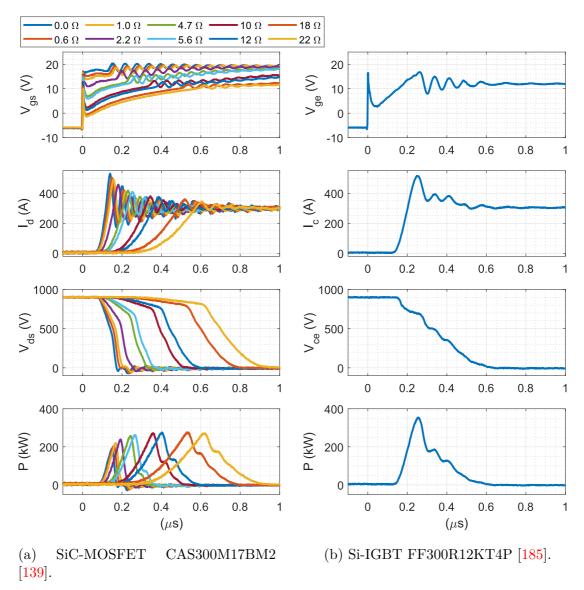

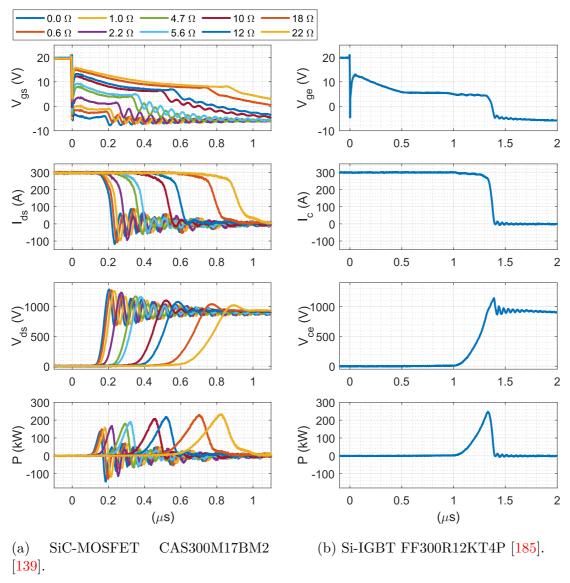

| 4.1  | Experimental waveforms of switching transitions, Si-IGBT com-<br>pared to SiC-MOSFET.                                                                         | 137 |

| 4.2  | Switching energy of Si-IGBT and SiC-MOSFET                                                                                                                    | 138 |

| 4.3  | FFT of antenna measurements                                                                                                                                   | 139 |

| 4.4  | TO-247-3 busbar interface PCB                                                                                                                                 | 144 |

| 4.5  | $\label{eq:high-bandwidth} \mbox{High-bandwidth experimental equipment} \ - \mbox{voltage measurements}.$                                                     | 145 |

| 4.6  | eq:High-bandwidth experimental equipment - current measurements.                                                                                              | 146 |

| 4.7  | Experimental waveforms of turn-on switching transition, standard Si-IGBT with Si-FRD compared to Si-IGBT with SiC-SBD                                         | 149 |

| 4.8  | FFT of antenna measurements                                                                                                                                   | 150 |

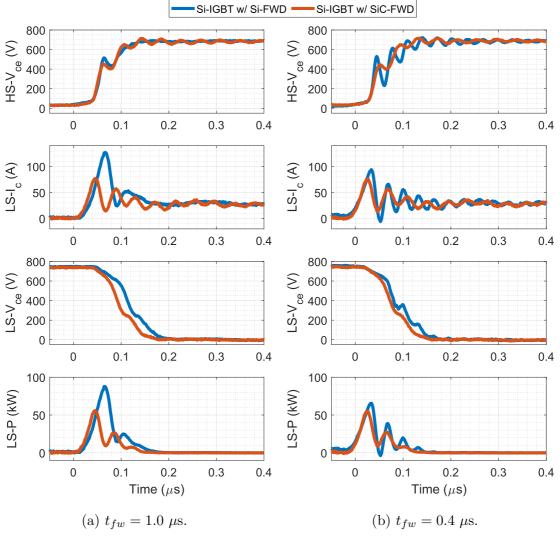

| 4.9  | Experimental waveforms of turn-on switching transition showing<br>snappy diode behaviour, standard Si-IGBT with Si-FRD com-<br>pared to Si-IGBT with SiC-SBD. | 152 |

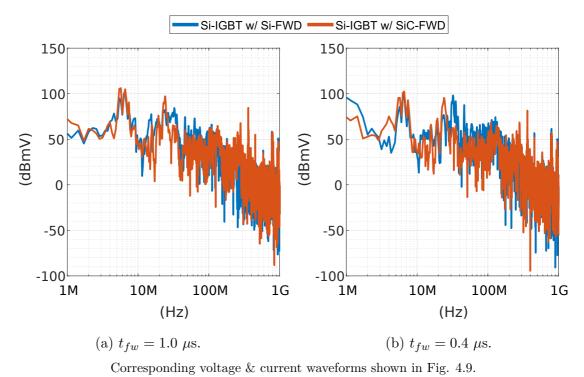

| 4.10 | FFT of antenna measurements                                                                                                                                   | 153 |

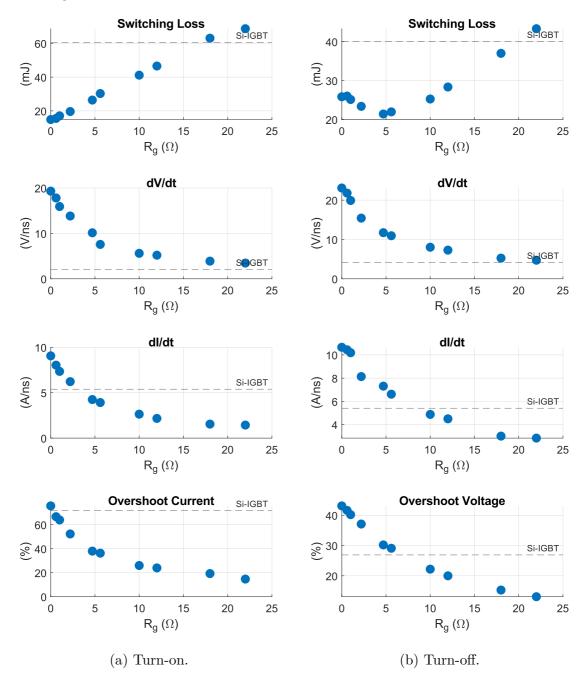

| 4.11 | Experimental waveforms of SiC-MOSFET turn-on transient, vary-<br>ing gate resistance.                                                                         | 155 |

| 4.12 | Experimental waveforms of SiC-MOSFET turn-off transient, vary-<br>ing gate resistance.                                                                        | 156 |

| 4.13 | Slowing down SiC-MOSFET, current and voltage waveform analysis.                                                                                               | 157 |

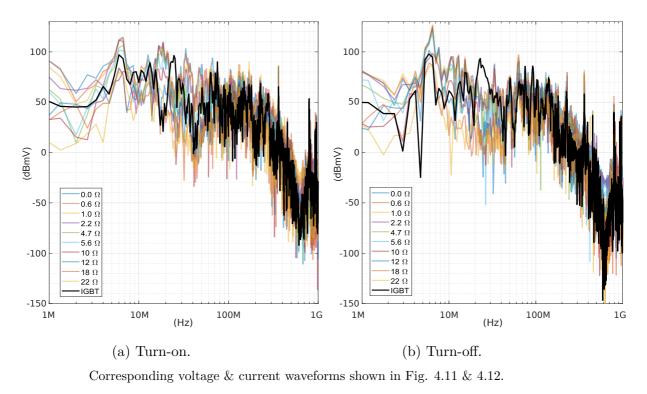

| 4.14 | FFT of antenna measurements                                                                                                                                   | 160 |

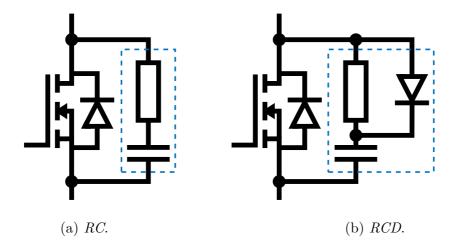

| 4.15 | Transistor snubber circuits.                                                                                                                                  | 162 |

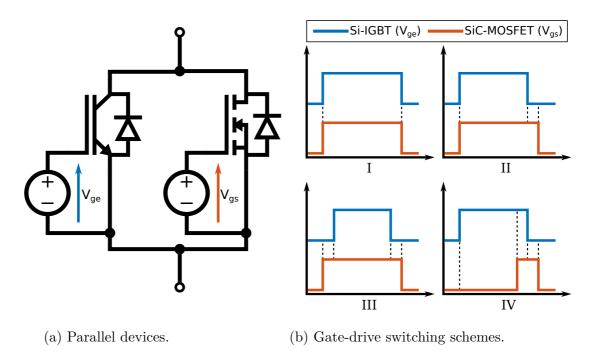

| 5.1  | Hybrid switching.                                                                                                                                             | 171 |

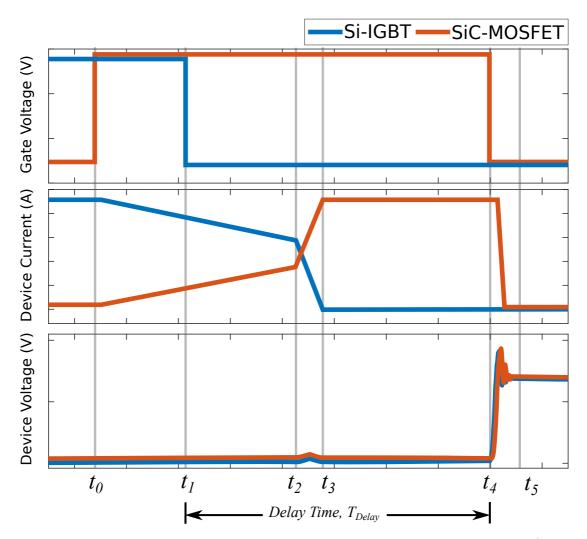

| 5.2  | Illustration of coordinated turn-off switching scheme for Si/SiC-<br>Diverter                                             | 177 |

|------|---------------------------------------------------------------------------------------------------------------------------|-----|

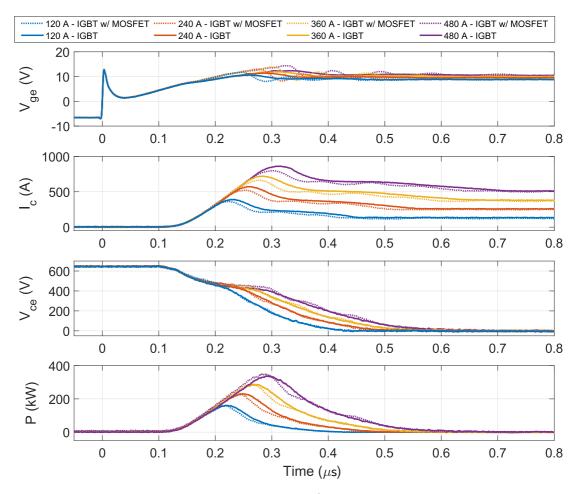

| 5.3  | Experimental waveforms of Si/SiC-Diverter                                                                                 | 180 |

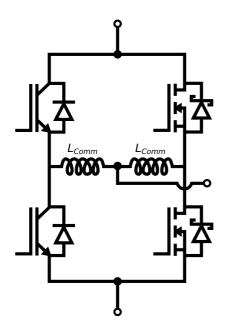

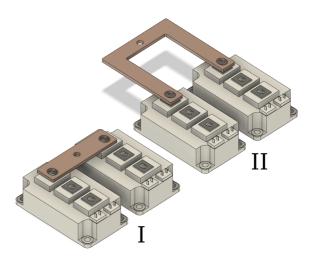

| 5.4  | Inter-device stray inductance $(L_{Comm})$                                                                                | 181 |

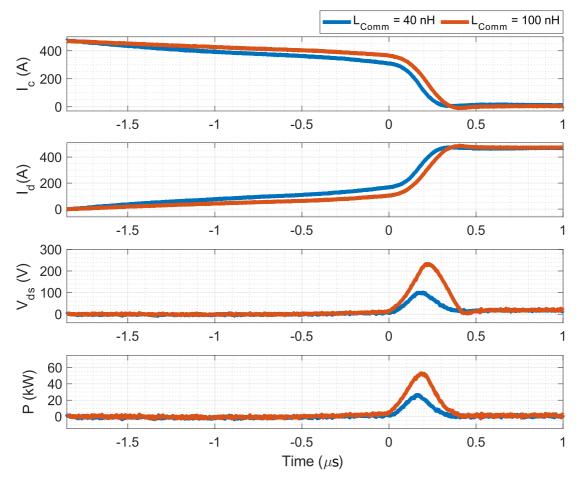

| 5.5  | Experimental waveforms of Si/SiC-Diverter showing the impact of $L_{Comm}$                                                | 182 |

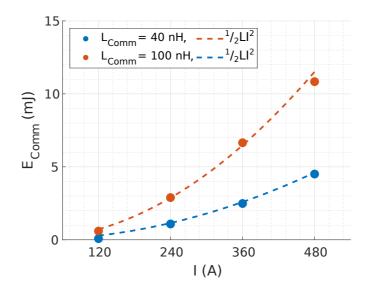

| 5.6  | Measured $E_{Comm}$ of Si/SiC-Diverter at two values of $L_{Comm}$                                                        | 183 |

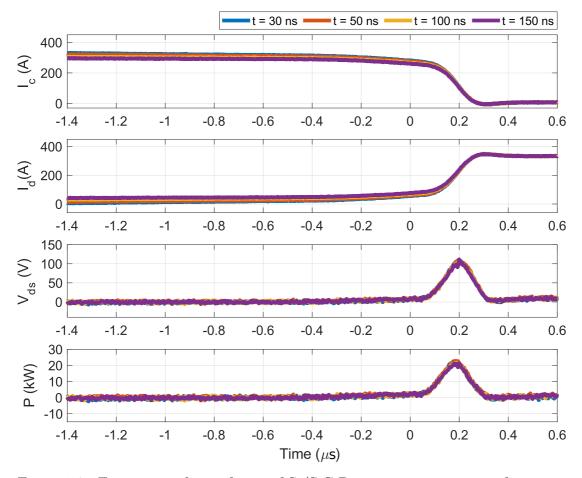

| 5.7  | Experimental waveforms of Si/SiC-Diverter, varying time of $t_0 \rightarrow t_1$ .                                        | 184 |

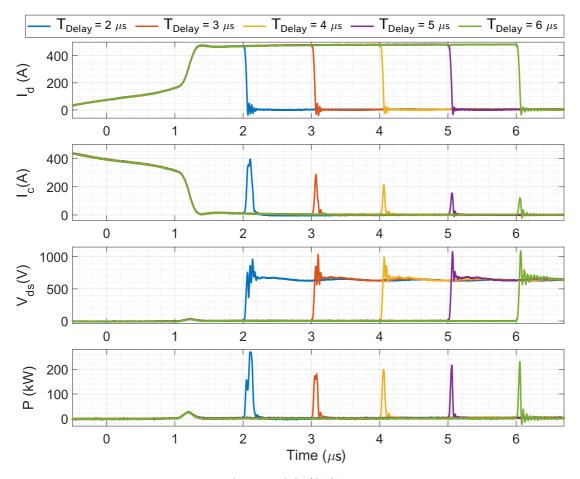

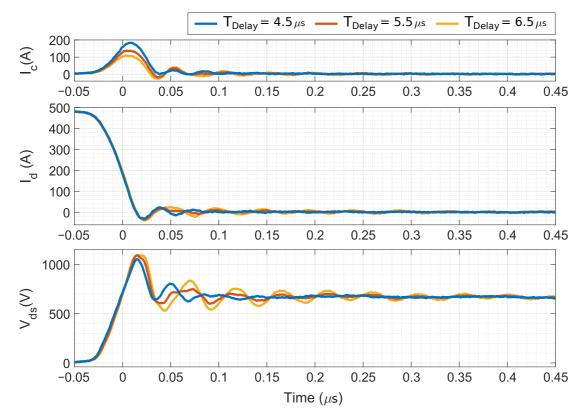

| 5.8  | Experimental waveforms of Si/SiC-Diverter, varying $T_{Delay}$                                                            | 186 |

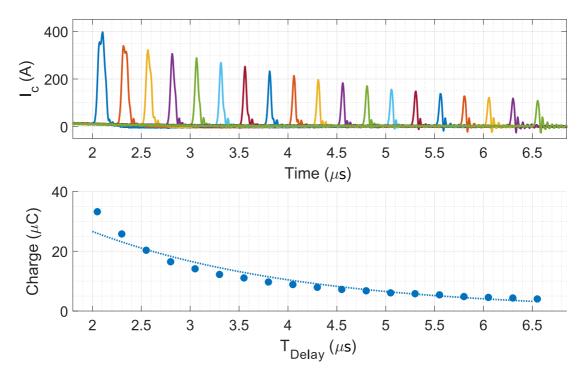

| 5.9  | Si-IGBT reconduction current analysis                                                                                     | 187 |

| 5.10 | Effect of temperature on recombination rate of minority carriers                                                          | 189 |

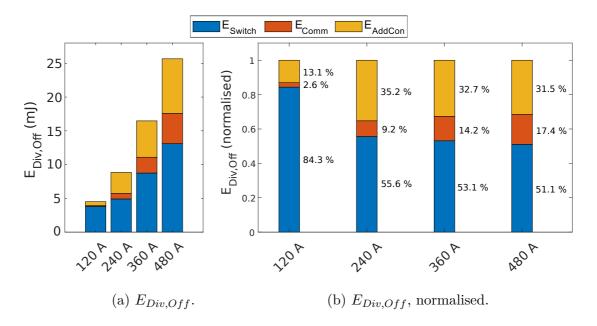

| 5.11 | Breakdown of Si/SiC-Diverter $E_{Div,Off}$ with respect to $T_{Delay}$                                                    | 190 |

| 5.12 | Minimum $E_{Div,Off}$ for each current set point                                                                          | 191 |

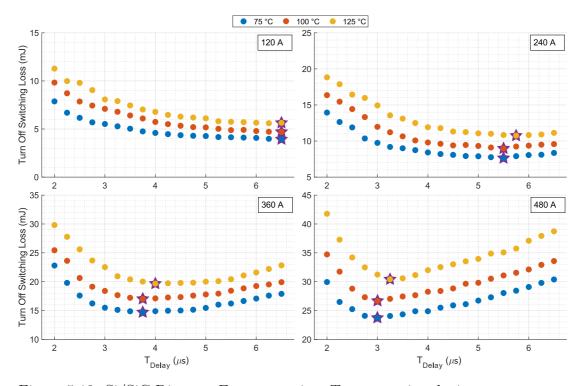

| 5.13 | Si/SiC-Diverter $E_{Div,Off}$ against $T_{Delay}$ , varying device temperature.                                           | 192 |

| 5.14 | Experimental waveforms of Si/SiC-Diverter at turn-on                                                                      | 193 |

| 5.15 | Experimental waveforms of Si/SiC-Diverter, showing damping of oscillatory behaviour and voltage overshoot.                | 196 |

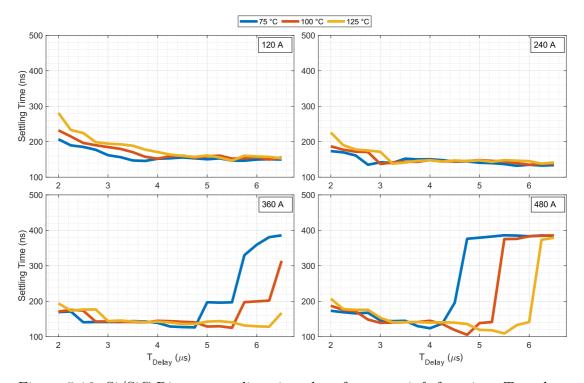

| 5.16 | Si/SiC-Diverter settling time data.                                                                                       | 197 |

| 5.17 | Si/SiC-Diverter settling time analysis.                                                                                   | 198 |

| 5.18 | Si/SiC-Diverter overshoot data.                                                                                           | 199 |

| 5.19 | Si/SiC-Diverter overshoot analysis.                                                                                       | 200 |

| 5.20 | Experimental waveforms of Si/SiC-Diverter showing correlation of damping of oscillatory behaviour with radiated emissions | 201 |

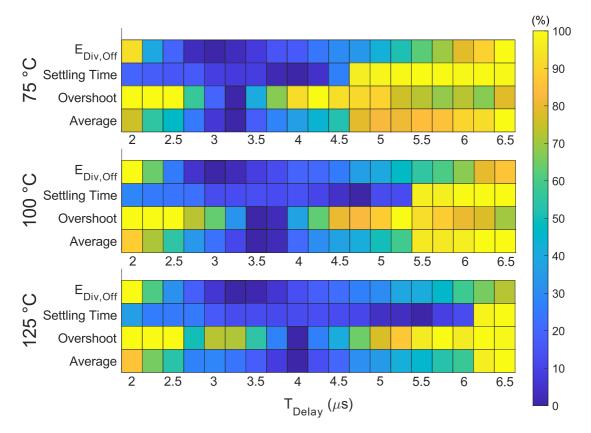

| 5.21 | Heat map showing spread of best $T_{Delay}$ .                                                                             | 202 |

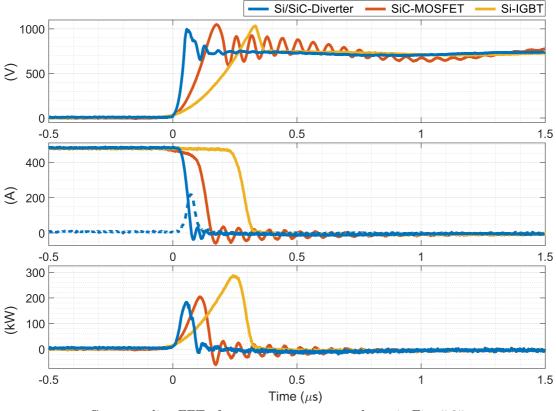

| 5.22 | Experimental waveforms of the Si/SiC-Diverter compared to fully rated Si-IGBT and SiC-MOSFET.                             | 204 |

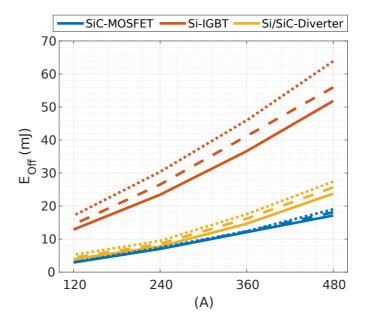

| 5.23 | Comparison of turn-off switching energy for Si/SiC-Diverter, SiC-MOSFET, and Si-IGBT         | 205 |

|------|----------------------------------------------------------------------------------------------|-----|

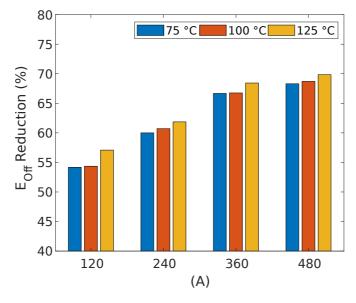

| 5.24 | Reduction in turn-off switching energy from Si-IGBT to Si/SiC-<br>Diverter                   | 206 |

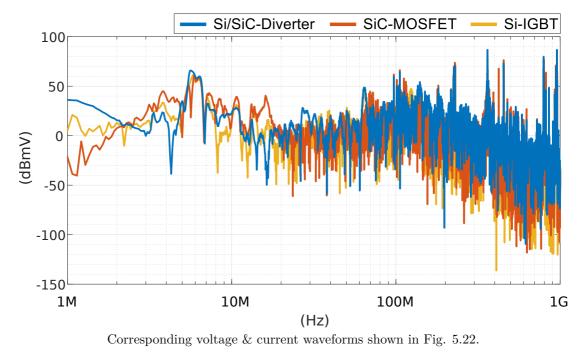

| 5.25 | FFT of antenna measurements.                                                                 | 207 |

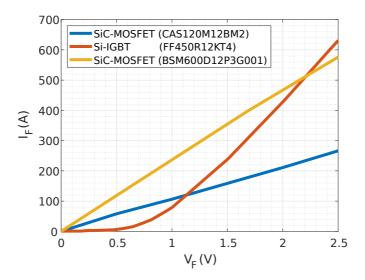

| 6.1  | I–V forward conduction loss curves of MOSFET and IGBT. $\ . \ .$                             | 214 |

| 6.2  | Diverter conduction assistance modes of operation                                            | 215 |

| 6.3  | Power electronic losses from inverter simulation. Losses as a per-<br>centage of rated power | 218 |

| 6.4  | Power electronic losses from inverter simulation. Losses normalised to Si-IGBT               | 219 |

| 6.5  | Power electronic loss reduction                                                              | 220 |

| 6.6  | Junction to case thermal impedance of SiC-MOSFET. $\ . \ . \ .$                              | 222 |

| 6.7  | Thermal network equivalent circuits                                                          | 222 |

| 6.8  | Foster thermal network                                                                       | 223 |

| 6.9  | Junction temperature Simulink model                                                          | 224 |

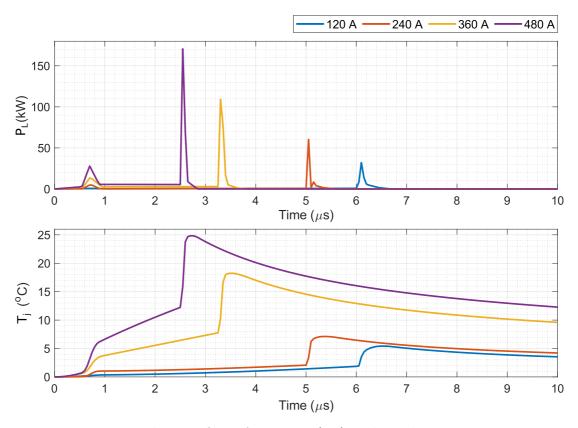

| 6.10 | Power loss profiles of Diverter and resultant junction temperature response                  | 225 |

| 6.11 | Junction temperature response, on logarithmic scale.                                         | 226 |

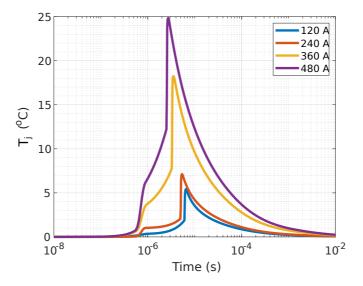

| 6.12 | Continuous thermal stress simulation                                                         | 227 |

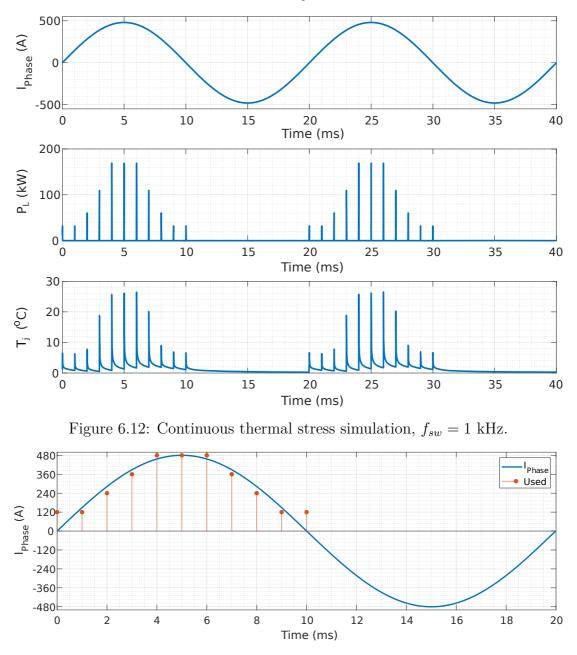

| 6.13 | Thermal simulation scheme                                                                    | 227 |

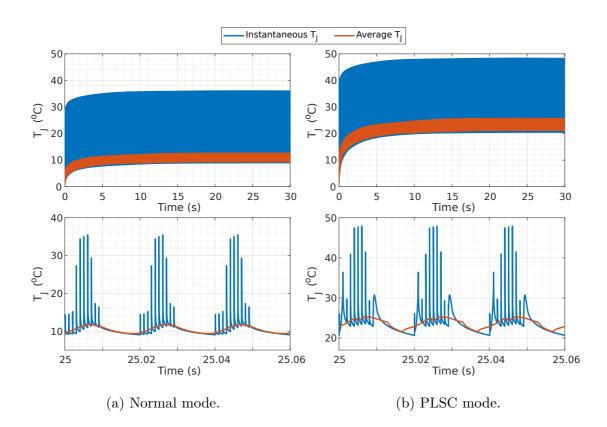

| 6.14 | Thermal simulation: Si/SiC-Diverter mode of operation                                        | 228 |

| 6.15 | Thermal simulation: Si/SiC-Diverter, varying switching frequency.                            | 230 |

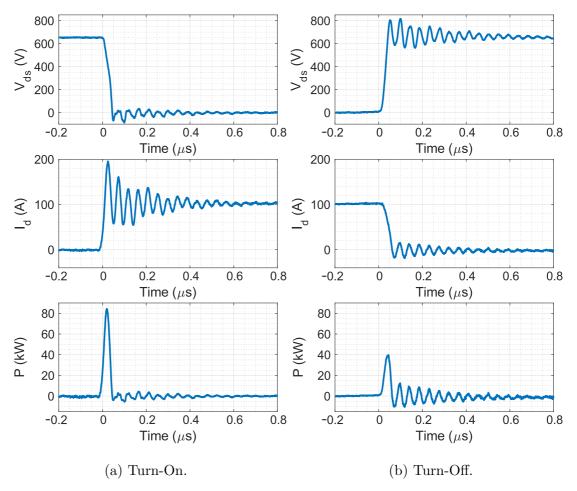

| 6.16 | Experimental waveforms of 120 A SiC-MOSFET switching tran-<br>sients                         | 233 |

| 6.17 | Thermal simulation: Si/SiC-Diverter vs. standard PWM on SiC MOSFET                           | 234 |

# List of Tables

| 1.1  | Switching states of half-bridge (HB)                          | 4  |

|------|---------------------------------------------------------------|----|

| 1.2  | Limitations and shortcomings of power semiconductor devices   | 6  |

| 2.1  | Properties of $n$ -type and $p$ -type semiconductor materials | 12 |

| 2.2  | Notable properties of Si and WBG materials                    | 15 |

| 2.3  | Power semiconductor switching device families                 | 18 |

| 2.4  | Transistor bare die comparison                                | 57 |

| 3.1  | Capacitors used in the high-power DPTR                        | 77 |

| 3.2  | PETG dielectric properties                                    | 83 |

| 3.3  | Busbar stray inductance $(L_s)$                               | 86 |

| 3.4  | Characteristics of DPTR inductive load $(L_{Load})$           | 89 |

| 3.5  | LabVIEW FSM for DPTR                                          | 93 |

| 3.6  | Required oscilloscope bandwidth for SiC-MOSFETs               | 17 |

| 3.7  | Oscilloscopes used in experimental work                       | 18 |

| 3.8  | Differential voltage probes used in experimental work         | 20 |

| 3.9  | CVR used in experimental work                                 | 25 |

| 3.10 | Current probes used in experimental work                      | 29 |

| 3.11 | EMI antenna used in experimental work                         | 30 |

| 4.1 | Gate resistance required for SiC-MOSFET to achieve level of Si-<br>IGBT in EMI precursors in Fig. 4.13 | 159 |

|-----|--------------------------------------------------------------------------------------------------------|-----|

| 5.1 | Power semiconductor devices used in experimental work                                                  | 178 |

| 5.2 | Curve fitting exponent coefficients.                                                                   | 189 |

| 5.3 | $T_{Delay}$ for minimum overall turn-off loss                                                          | 192 |

| 5.4 | $\Delta E_{on}(\%)$ for different currents and temperatures                                            | 195 |

| 5.5 | Best $T_{Delay}$ for each performance trait                                                            | 203 |

| 5.6 | Headline characteristics from comparison in Fig. 5.22                                                  | 205 |

| 6.1 | Power electronic loss categories/mechanisms                                                            | 216 |

| 6.2 | SiC-MOSFET junction temperature, varying switching frequency.                                          | 229 |

# List of Acronyms

| $\mathbf{AC}$          | Alternating Current                     |

|------------------------|-----------------------------------------|

| ACC                    | Active Current Control                  |

| ADC                    | Analogue-to-Digital Converter           |

| AGD                    | Active Gate-Drivers                     |

| ASIC                   | Application-Specific Integrated Circuit |

| AWG                    | American Wire Gauge                     |

| AVC                    | Active Voltage Control                  |

| BFoM                   | Baliga's Figure of Merit                |

| BJT                    | Bipolar Junction Transistor             |

| BNC                    | Bayonet Neill–Concelman                 |

| $\mathbf{BW}$          | Bandwidth                               |

| С                      | Carbon                                  |

| CAD                    | Computer Aided Design                   |

| $\operatorname{CCL}$   | Current Commutation Loop                |

| CE                     | Conducted Emissions                     |

| $\mathbf{C}\mathbf{M}$ | Common-Mode                             |

| CMOS                   | Complementary Metal-Oxide-Semiconductor |

| CMRR                   | Common-Mode Rejection Ratio             |

| CMTI                   | Common-Mode Transient Immunity          |

| CoC                    | Chip on Chip                            |

| $\mathbf{CSR}$         | Charge Storage Region                   |

$\mathbf{CT}$ Current Transformer CVR Current Viewing Resistor DAC Digital-to-Analogue Converter DC Direct Current DLB Direct Lead Bonding  $\mathbf{D}\mathbf{M}$ Differential-Mode DPTR Double-Pulse Test Rig DUT Device Under Test  $\mathbf{E}\mathbf{M}$ Electromagnetic EMC Electromagnetic Compatibility EMI Electromagnetic Interference ESL Equivalent Series Inductance  $\mathbf{ESR}$ Equivalent Series Resistance  $\mathbf{EV}$ Electric Vehicle FACTS Flexible Alternating Current Transmission System FCC Federal Communications Commission FEM Finite Element Method FET Field-Effect Transistor Fast Fourier Transform FFT FIT Failure in Time **FPGA** Field Programmable Gate Array FRD Fast Recovery Diode FSM Finite State Machine FWD Freewheeling Diode GaN Gallium Nitride HEMT High-Electron-Mobility Transistor HS High-Side HVDC High-Voltage Direct Current

| IGBT   | Insulated-Gate Bipolar Transistor                               |

|--------|-----------------------------------------------------------------|

| IC     | Integrated Circuit                                              |

|        | Integrated Circuit<br>International Electrotechnical Commission |

| IEC    |                                                                 |

| JBS    | Junction Barrier Schottky                                       |

| JFET   | Junction Field-Effect Transistor                                |

| JFoM   | Johnson's Figure of Merit                                       |

| KC     | Kelvin-Collector                                                |

| KD     | Kelvin-Drain                                                    |

| KE     | Kelvin-Emitter                                                  |

| KS     | Kelvin-Source                                                   |

| LCoE   | Levelised Cost of Energy                                        |

| LDMOS  | Laterally Diffused MOSFET                                       |

| LED    | Light-Emitting Diode                                            |

| LS     | Low-Side                                                        |

| MLCC   | Multi-Layer Ceramic Capacitor                                   |

| MELF   | Metal Electrode Leadless Face                                   |

| MMC    | Modular Multi-Level Converter                                   |

| MMCX   | Micro-Miniature Coaxial                                         |

| MOS    | Metal–Oxide–Semiconductor                                       |

| MOSFET | Metal–Oxide–Semiconductor Field-Effect Transistor               |

| MOV    | Metal-Oxide Varistor                                            |

| MP     | Midpoint                                                        |

| MPS    | Merged PIN Schottky                                             |

| NPC    | Neutral Point Clamped                                           |

| NPT    | Non-Punch Through                                               |

| NTC    | Negative Temperature Coefficient                                |

| Op-Amp | Operational Amplifier                                           |

| OVLO   | Over-Voltage Lockout                                            |

|        |                                                                 |

PCB Printed Circuit Board  $\mathbf{PE}$ Power Electronic PEEK Polyether Ether Ketone PETG Polyethylene Terephthalate Glycol-modified  $\mathbf{PL}$ Part-Load PLSC Part-Load-Subcycle PoF Power-over-Fiber **PSU** Power Supply Unit  $\mathbf{PT}$ Punch Through PTC Positive Temperature Coefficient  $\mathbf{PV}$ Photovoltaic PVC Polyvinyl Chloride **PWL Piece-Wise Linear** Pulse-Width Modulation **PWM** RC **Reverse-Conducting**  $\mathbf{RE}$ **Radiated Emissions**  $\mathbf{RF}$ **Radio Frequency** RFI Radio Frequency Interference **SBD** Schottky Barrier Diode SCC Short Circuit Capacity SEB Single-Event Burnout SEE Single-Event Effect Si Silicon SiC Silicon-Carbide SJBT Superjunction IGBT SJMOS Superjunction MOSFET SMA Sub-Miniature Version-A **SMPS** Switched-Mode Power Supply

| SOASafe Operating AreaSoCSystem on a ChipSPICESimulation Program with Integrated Circuit EmphasisSPTSoft-Punch ThroughSSRSolid-State RelayTIMThermal Interface MaterialTSEPTemperature Sensitive Electrical Parameters |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPICESimulation Program with Integrated Circuit EmphasisSPTSoft-Punch ThroughSSRSolid-State RelayTIMThermal Interface MaterialTSEPTemperature Sensitive Electrical Parameters                                          |

| SPTSoft-Punch ThroughSSRSolid-State RelayTIMThermal Interface MaterialTSEPTemperature Sensitive Electrical Parameters                                                                                                  |

| SSRSolid-State RelayTIMThermal Interface MaterialTSEPTemperature Sensitive Electrical Parameters                                                                                                                       |

| TIMThermal Interface MaterialTSEPTemperature Sensitive Electrical Parameters                                                                                                                                           |

| <b>TSEP</b> Temperature Sensitive Electrical Parameters                                                                                                                                                                |

| 1                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                        |

| UV Ultraviolet                                                                                                                                                                                                         |

| UVLO Under-Voltage Lockout                                                                                                                                                                                             |

| <b>VDMOS</b> Vertical Double-Diffused MOSFET                                                                                                                                                                           |

| VSC Voltage-Source Converter                                                                                                                                                                                           |

| <b>VUMOS</b> Vertical U-Trench MOSFET                                                                                                                                                                                  |

| <b>VVMOS</b> Vertical V-Groove MOSFET                                                                                                                                                                                  |

| WBG Wide-Bandgap                                                                                                                                                                                                       |

| <b>XS</b> Cross-Switch                                                                                                                                                                                                 |

| <b>ZCS</b> Zero Current Switching                                                                                                                                                                                      |

| <b>ZTC</b> Zero Temperature Coefficient                                                                                                                                                                                |

| <b>ZVS</b> Zero Voltage Switching                                                                                                                                                                                      |

# Nomenclature

### Symbols

| $\delta_{skin}$       | Skin Depth                                  | [m]                           |

|-----------------------|---------------------------------------------|-------------------------------|

| $\epsilon_r$          | Dielectric Constant (Relative Permittivity) |                               |

| λ                     | Wavelength                                  | [m]                           |

| $\lambda_T$           | Thermal Conductivity                        | [W/cmK]                       |

| $\mu_n$               | Electron Mobility                           | $[\mathrm{cm}^2/\mathrm{Vs}]$ |

| $\mu_p$               | Hole Mobility                               | $[\mathrm{cm}^2/\mathrm{Vs}]$ |

| $\mu_r$               | Relative Permeability                       |                               |

| $\phi$                | Magnetic Flux                               | [Wb]                          |

| ρ                     | Resistivity                                 | $[\Omega{\cdot}m]$            |

| σ                     | Conductivity                                | [S/m]                         |

| $\sigma_{dielectric}$ | Dielectric Conductivity                     | [S/m]                         |

| $	au_{HL}$            | Charge Carrier High-Level Lifetime Constant | $[\mathbf{s}]$                |

| ζ                     | Damping Factor                              |                               |

| $A_{busbar}$          | Busbar Area                                 | $[m^2]$                       |

| В                     | Magnetic Flux Density                       | [T]                           |

| BW                    | Bandwidth                                   | [Hz]                          |

| C                     | Capacitor/Capacitance                       | [F]                           |

| $C_{bulk}$            | DC Bulk Capacitance                         | [F]                           |

| $C_{busbar}$          | Busbar Capacitance                          | [F]                           |

| $C_{dc-link}$         | DC-Link Capacitance                         | $[\mathbf{F}]$                |

| $C_{decouple}$                                               | High-Frequency Decoupling Capacitance                                                                                                                          | [F]                                        |

|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| $C_{ds}$                                                     | Drain-Source Capacitance                                                                                                                                       | [F]                                        |

| $C_{gd}$                                                     | Gate-Drain Capacitance                                                                                                                                         | [F]                                        |

| $C_{gs}$                                                     | Gate-Source Capacitance                                                                                                                                        | [F]                                        |

| $C_{iss}$                                                    | Transistor Input Capacitance                                                                                                                                   | [F]                                        |

| $C_{oss}$                                                    | Transistor Output Capacitance                                                                                                                                  | [F]                                        |

| $C_{ox}$                                                     | Gate Oxide Capacitance                                                                                                                                         | $[\mathrm{F/cm^2}]$                        |

| $C_{par}$                                                    | Parasitic Capacitance                                                                                                                                          | [F]                                        |

| $C_{rss}$                                                    | Transistor Reverse Transfer Capacitance                                                                                                                        | [F]                                        |

| D                                                            | Diode                                                                                                                                                          |                                            |

| $D_{EM}$                                                     | Planar EM Wave Formation Distance                                                                                                                              | [m]                                        |

| E                                                            | Energy                                                                                                                                                         | [J]                                        |

| $E_0$                                                        | Junction Potential                                                                                                                                             | [V]                                        |

| $E_{AddCond}$                                                | Diverter Additional Conduction Energy Loss                                                                                                                     | [J]                                        |

| $E_{Comm}$                                                   | Diverter Commutation Energy Loss                                                                                                                               | [J]                                        |

| $E_{crit}$                                                   | Critical Electric Field                                                                                                                                        | [kV/cm]                                    |

| $E_{Div,Off}$                                                | Diverter Turn-Off Switching Energy                                                                                                                             | [J]                                        |

| $E_{Off}$                                                    | Turn-Off Switching Energy                                                                                                                                      | [J]                                        |

|                                                              |                                                                                                                                                                | [0]                                        |

| $E_{On}$                                                     | Turn-On Switching Energy                                                                                                                                       | [J]                                        |

| $E_{On}$<br>$E_{Switch}$                                     | Turn-On Switching Energy<br>Diverter Switching Event Energy Loss                                                                                               |                                            |

|                                                              |                                                                                                                                                                | [J]                                        |

| $E_{Switch}$                                                 | Diverter Switching Event Energy Loss                                                                                                                           | [J]                                        |

| $E_{Switch}$<br>$E_{sw}$                                     | Diverter Switching Event Energy Loss<br>Switching Energy                                                                                                       | [J]                                        |

| $E_{Switch}$<br>$E_{sw}$<br>f                                | Diverter Switching Event Energy Loss<br>Switching Energy<br>Frequency                                                                                          | [J]<br>[J]<br>[Hz]                         |

| $E_{Switch}$<br>$E_{sw}$<br>f<br>$f_{3dB}$                   | Diverter Switching Event Energy Loss<br>Switching Energy<br>Frequency<br>Corner/Cutoff/-3dB Frequency                                                          | [J]<br>[J]<br>[Hz]<br>[Hz]                 |

| $E_{Switch}$<br>$E_{sw}$<br>f<br>$f_{3dB}$<br>$f_n$          | Diverter Switching Event Energy Loss<br>Switching Energy<br>Frequency<br>Corner/Cutoff/-3dB Frequency<br>Natural Resonant Frequency                            | [J]<br>[J]<br>[Hz]<br>[Hz]<br>[Hz]         |

| $E_{Switch}$<br>$E_{sw}$<br>f<br>$f_{3dB}$<br>$f_n$<br>$f_o$ | Diverter Switching Event Energy Loss<br>Switching Energy<br>Frequency<br>Corner/Cutoff/-3dB Frequency<br>Natural Resonant Frequency<br>Self Resonant Frequency | [J]<br>[J]<br>[Hz]<br>[Hz]<br>[Hz]<br>[Hz] |

| Ι              | Current                                            | [ \ ]          |

|----------------|----------------------------------------------------|----------------|

|                |                                                    | [A]            |

| $I_{CM}$       | Common Mode Current                                | [A]            |

| I <sub>c</sub> | Collector Current                                  | [A]            |

| $I_{d,sat}$    | Drain Current (saturation region)                  | [A]            |

| $I_{DM}$       | Differential Mode Current                          | [A]            |

| $I_d$          | Drain Current                                      | [A]            |

| $I_F$          | Forward Current                                    | [A]            |

| $I_g$          | Gate Current                                       | $[\mathbf{A}]$ |

| $I_L$          | Load Current                                       | [A]            |

| $I_{mos}$      | MOSFET Unipolar Current (IGBT)                     | [A]            |

| $I_{Phase}$    | Phase Current                                      | $[\mathbf{A}]$ |

| $I_{pnp}$      | BJT Bipolar Current (IGBT)                         | $[\mathbf{A}]$ |

| $I_{rr}$       | Peak Reverse Recovery Current                      | [A]            |

| $I_s$          | Saturation Current                                 | [A]            |

| $K_C$          | Charging Contactor                                 |                |

| $K_D$          | Discharge Contactor                                |                |

| L              | Inductor/Inductance                                | [H]            |

| $L_{busbar}$   | Busbar Parasitic Inductance                        | [H]            |

| $L_{Comm}$     | Diverter Inter-Device Stray Commutation Inductance | [H]            |

| $L_C$          | Channel Length                                     | [m]            |

| $L_{eq}$       | Equivalent Inductance                              | [H]            |

| $L_e$          | Busbar External Inductance                         | [H]            |

| $L_G$          | Gate Stray Inductance                              | [H]            |

| $L_i$          | Busbar Internal Inductance                         | [H]            |

| $L_{KS}$       | Kelvin-Source Stray Inductance                     | [H]            |

| $L_{Load}$     | Load Inductor                                      | [H]            |

| $L_{stray}$    | Stray Inductance                                   | [H]            |

| $L_s$          | Stray Inductance                                   | [H]            |

|                |                                                    |                |

| $M_L$         | Mutual Inductance                            | [H]             |

|---------------|----------------------------------------------|-----------------|

| N             | Number of Turns                              |                 |

| $N_A$         | Acceptor Impurity Concentration              | $[cm^{-3}]$     |

| $N_D$         | Donor Impurity Concentration                 | $[cm^{-3}]$     |

| $n_i$         | Intrinsic Carrier Concentration              | $[cm^{-3}]$     |

| Р             | Power                                        | [W]             |

| $P_{IGBT}$    | Instantaneous Power Loss in IGBT             | [W]             |

| $P_{L\_cond}$ | Instantaneous Device Conduction Power Losses | [W]             |

| $P_{L\_sw}$   | Instantaneous Device Switching Power Losses  | [W]             |

| $P_L$         | Instantaneous Device Power Losses            | [W]             |

| $P_{MOSFET}$  | Instantaneous Power Loss in MOSFET           | [W]             |

| Q             | Charge                                       | [C]             |

| $Q_{gs}$      | Required Gate Charge                         | [C]             |

| $Q_{rr}$      | Reverse Recovery Charge                      | [C]             |

| R             | Resistor/Resistance                          | $[\Omega]$      |

| r             | Radius                                       | [m]             |

| $R_{\Box}$    | Sheet Resistance                             | $[\Omega/\Box]$ |

| $R_{acc}$     | Accumulation Region Resistance               | $[\Omega]$      |

| $R_{busbar}$  | Busbar Resistance                            | $[\Omega]$      |

| $R_B$         | Bleed Resistor                               | $[\Omega]$      |

| $R_{ch}$      | Channel Resistance                           | $[\Omega]$      |

| $R_{crit}$    | Critical Resistance (for critical damping)   | $[\Omega]$      |

| $R_C$         | Charging Resistor                            | $[\Omega]$      |

| $R_{Drift}$   | Epitaxial-Layer/Drift Region Resistance      | $[\Omega]$      |

| $R_{ds(on)}$  | MOSFET On-State Resistance                   | $[\Omega]$      |

| $R_D$         | Discharge Resistor                           | $[\Omega]$      |

| $R_d$         | Resistance of Drain Connection               | $[\Omega]$      |

| $R_{eq}$      | Equivalent Resistance                        | $[\Omega]$      |

| $R_{g,int}$       | Gate Resistance (internal)              | $[\Omega]$     |

|-------------------|-----------------------------------------|----------------|

| $R_{g\_off}$      | Turn-Off Gate Resistance                | $[\Omega]$     |

| $R_{g\_on}$       | Turn-On Gate Resistance                 | $[\Omega]$     |

| $R_g$             | Gate Resistance (external)              | $[\Omega]$     |

| $R_{JFET}$        | JFET Pinching Resistance                | $[\Omega]$     |

| $R_M$             | CVR Measurement Resistance              | $[\Omega]$     |

| $R_{on}$          | On-Resistance                           | $[\Omega]$     |

| $R_{sub}$         | Substrate Layer Resistance              | $[\Omega]$     |

| $R_s$             | Resistance of Source Connection         | $[\Omega]$     |

| $T_{amb}$         | Ambient Temperature                     | [K]            |

| $t_{charge}$      | Double-Pule Test Charging Time          | [s]            |

| $T_c$             | Case Temperature                        | [K]            |

| $T_{Delay}$       | Diverter Delay Time                     | [s]            |

| $t_{dielectric}$  | Thickness of Dielectric Material        | [m]            |

| $t_{fw}$          | Diode Freewheeling Time                 | $[\mathbf{s}]$ |

| $t_f$             | Fall Time                               | $[\mathbf{s}]$ |

| $T_j$             | Junction Temperature                    | [K]            |

| $t_{rr}$          | Reverse Recovery Time                   | [s]            |

| $t_r$             | Rise Time                               | [s]            |

| V                 | Voltage                                 | [V]            |

| $V_{br}$          | Breakdown Voltage                       | [V]            |

| $V_{bus,+\Delta}$ | DPTR Pre-Charge DC Bus Voltage          | [V]            |

| $V_{bus}$         | DC Bus Voltage                          | [V]            |

| $V_{ce(sat)}$     | IGBT On-State Collector-Emitter Voltage | [V]            |

| $V_{ce}$          | Collector-Emitter Voltage               | [V]            |

| $V_{CM}$          | Common Mode Voltage                     | [V]            |

| $V_{DM}$          | Differential Mode Voltage               | [V]            |

| $V_{drop,pn}$     | Diode Voltage Drop (IGBT)               | [V]            |

| $V_{ds(on)}$  | MOSFET On-State Drain-Source Voltage | e [V]                                       |

|---------------|--------------------------------------|---------------------------------------------|

| $V_{ds}$      | Drain-Source Voltage                 | [V]                                         |

| $V_F$         | Forward Voltage Drop                 | [V]                                         |

| $V_{ge}$      | Gate-Emitter Voltage                 | [V]                                         |

| $V_{gs}$      | Gate-Source Voltage                  | [V]                                         |

| $V_g$         | External Gate Voltage                | [V]                                         |

| $V_{ind.}$    | Induced Voltage                      | [V]                                         |

| $V_L$         | Instantaneous Inductor Voltage       | [V]                                         |

| $V_M$         | Voltage Measurement                  | [V]                                         |

| $V_{os}$      | Voltage Overshoot                    | [V]                                         |

| $V_{rr}$      | Peak Reverse Recovery Voltage        | [V]                                         |

| $v_{sat}$     | Charge Carrier Saturation Velocity   | $[\mathrm{cm/s}]$                           |

| $V_{Th}$      | Threshold Voltage                    | [V]                                         |

| $W_C$         | Channel Width                        | [m]                                         |

| $X_C$         | Capacitor Reactance                  | $[\Omega]$                                  |

| $x_{j}$       | Junction Depth                       | [m]                                         |

| $X_L$         | Inductor Reactance                   | $[\Omega]$                                  |

| Ζ             | Impedance                            | $[\Omega]$                                  |

| $Z_{busbar}$  | Busbar Characteristic Impedance      | $[\Omega]$                                  |

| $Z_{th(j-c)}$ | Junction to Case Thermal Impedance   | $[^{\rm o}C/W]$                             |

| $Z_{th}$      | Thermal Impedance                    | $[^{\circ}C/W]$                             |

| $\beta_{pnp}$ | BJT Current Gain                     |                                             |

| Physics (     | Constants                            |                                             |

| $\epsilon_0$  | Permittivity of Free Space           | $8.85418782 \times 10^{-12} \ \mathrm{F/m}$ |

| $\mu_o$       | Permeability of Free Space           | $1.25663706\times 10^{-6}~\rm{H/m}$         |

| $\pi$         | Pi                                   | 3.14159265359                               |

| $\pi$ | Pi                   | 3.14159265359                           |

|-------|----------------------|-----------------------------------------|

| eV    | Electronvolt         | $1.602176634 \times 10^{-19} \text{ J}$ |

| k     | Boltzmann's Constant | $1.380649 \times 10^{-23} \text{ J/K}$  |

| q     | Electron Charge      | $1.60217662 \times 10^{-19} \text{ C}$  |

## 1 Introduction

### 1.1 The Role of Power Electronics

Power Electronic (PE) based converters are becoming ubiquitous in almost every aspect of how we generate, distribute and consume electricity. This technology provides the necessary functions that support applications such as: gigawatt scale High-Voltage Direct Current (HVDC) transmission and Flexible Alternating Current Transmission System (FACTS); megawatt scale grid-tied converters for renewable sources, such as wind and solar; kilowatt scale chargers and motor drives that are necessary for the forthcoming Electric Vehicle (EV) revolution; low-power converters found in consumer electronics, wireless power transfer and lighting; and many more. As we move toward a low-carbon society, the requirements for PE will be twofold in terms of efficiency and flexibility. It is these technologies that will enable future renewable energy sources and facilitate energy storage solutions whilst helping to maintain grid stability. It is predicted that 80 % of electricity will flow through PE based converters by 2030, more than double the current figure [1].

Power converters are capable of interfacing with either Direct Current (DC) or Alternating Current (AC), either single-phase or multi-phase, and range in complexity from circuits that operate using tens of components to those that use thousands. The principal role of these systems is to convert one form of electrical energy into another. These power converters are able to achieve efficiencies of >95 % [1]. At the heart of a PE converter are the power semiconductor devices. Their job is to manage the flow of power round a converter and, with the aid of an external controller, supply or source the correct voltage and current levels. They achieve this by rapidly switching between an on and off state, typically at frequencies in the kHz range, in a controlled manner. Using a wide variety of modulation techniques, along with passive filtering components, the desired power flow can be realised.

### 1.2 Semiconductor Devices in a Power Converter

The way in which power semiconductor devices are used in a power converter can be generally classified as either hard-switched or soft-switched.

Figure 1.1: Device switching classification.

Hard-switching describes when the device's current and voltage overlap during the switching transitions resulting in an appreciable amount of switching loss  $(P_{switch} = V_{switch} \times I_{switch})$  – this overlap is illustrated in Figure 1.1a. Whereas soft-switching behaviour occurs when the devices turn on or off with either zero voltage or zero current, known as Zero Voltage Switching (ZVS) and Zero Current Switching (ZCS) respectively, resulting in essentially zero switching loss. However, soft-switching circuits can become complex and usually employ resonant techniques to achieve ZVS or ZCS. The conversion techniques which employ soft-switching of transistors are mainly found in low-power converters.

In high-power applications, the transistor is predominantly used in the hardswitched manner. This leads to switching losses which significantly contribute to total PE losses. Therefore, hard-switching will only be considered in this thesis.

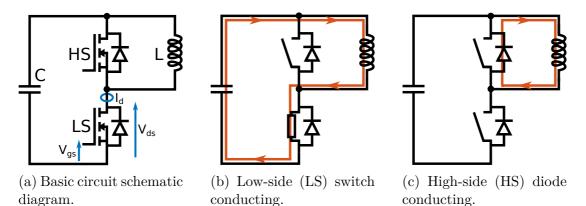

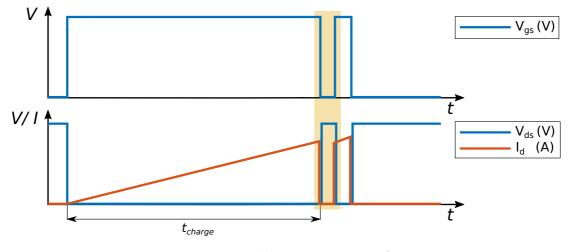

#### 1.2.1 Half-Bridge in Voltage-Source Converter (VSC)

In high-power applications, a hard-switched Voltage-Source Converter (VSC) is typically used — the most fundamental being the two-level converter. The basic structure of the two-level converter is formed using two power semiconductor switches  $(S_1 \& S_2)$  in series, with diodes  $(D_1 \& D_2)$  in parallel to each of them. This basic structure is termed a half-bridge, or phase-leg, and is shown in Figure 1.2. The top device is referred to as the High-Side (HS) and the bottom the Low-Side (LS).

Figure 1.2: Half-bridge (HB) configuration for VSC.

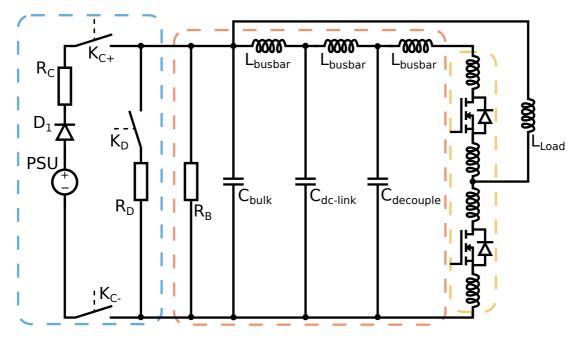

The half-bridge is used to connect its Midpoint (MP) connection to either the positive or negative side of the DC voltage ( $V_{DC}$ ) that is connected to its terminals. The available switching states are shown in Table 1.1. The HS and LS devices are switched in a complimentary manner such that both are not on at the same time. If they were to simultaneously conduct, a short-circuit would be created and the devices would exhibit an over-current and fail. To avoid this happening when transitioning between HS conduction and LS conduction, a small delay period (dead-time) is used.

| S2 | S1 | MP                                    |

|----|----|---------------------------------------|

| 0  | 0  | Floating                              |

| 0  | 1  | $+ 1/2V_{DC}$                         |

| 1  | 0  | $- \frac{1}{2}V_{DC}$                 |

| 1  | 1  | Not allowed <sup><math>a</math></sup> |

<sup>a</sup> Would result in a short-circuit.

Table 1.1: Switching states of half-bridge (HB).

Figure 1.3: Two-level inverter voltage and current waveforms.

The top plot in Figure 1.3 shows how the half-bridge configuration is used to rapidly switch between  $+1/2V_{DC}$  and  $-1/2V_{DC}$ . When this is done using modulation techniques, it can be used, with the aid of additional filtering, to produce an AC output. Figure 1.4 shows the system diagram for a typical three-phase grid-tied inverter — using three half-bridge's to realise the three-phases — with the required output LC stage (inductor and capacitor). The filter stage is connected to each phase output (MPs A, B, & C) and is used to average out the high-frequency switching to a smooth sinusoid. The switching frequency  $(f_{sw})$  of the converter is related to the time constant of the filter stage, with an increase in  $f_{sw}$  allowing for a reduction in the value and hence physical size of the filter. The anti-parallel diode, referred to as a Freewheeling Diode (FWD), is used for reverse inductive current flow. It also allows for rectification in the opposite direction for the inverter example shown.

Figure 1.4: Three-phase inverter example (circuit diagram).

The "two-level" name of this converter class arises from the two voltage levels  $(+ \frac{1}{2}V_{DC} \& - \frac{1}{2}V_{DC})$  that the half-bridge can achieve. However, the half-bridge can be used to realise multi-level VSCs for high-power applications. For example; the three-level Neutral Point Clamped (NPC) converter; various multi-level flying-capacitor converters; and the Modular Multi-Level Converter (MMC) which is used in High-Voltage Direct Current (HVDC) applications.

Megawatt scale grid-tied converters that are used in, for example, wind turbine AC–AC converters, utility-scale solar farm inverters, and large-scale energy storage interfacing converters require high-capacity semiconductor devices. These high-capacity devices are required to operate at voltages in excess of 1–2 kV and conduct currents of 100s if not 1000s of amps.

## **1.2.2** Effective High-Capacity Semiconductor Devices

The semiconductor devices are instrumental in the efficient operation of the converter, however they do have some limitations and shortcomings. These are listed in Table 1.2.

| Power Losses           | A significant amount of power converter losses<br>can be attributed to them, both when they switch<br>and conduct. |

|------------------------|--------------------------------------------------------------------------------------------------------------------|

| Electromagnetic Noise  | They can give rise to serious EMC issues, in the form of radiated and conducted.                                   |

| Electrical Limitations | They have limited voltage, current and temperature operating capabilities.                                         |

Table 1.2: Limitations and shortcomings of power semiconductor devices.

For VSC converters, the switching devices used must be fully controllable such that they can be turned on and off — a transistor offers this functionality. More than 30 years of research and development efforts have lead to the Silicon (Si)-Insulated-Gate Bipolar Transistor (IGBT) (with Si-based FWD) being the device of choice for high-power applications due to its high level of maturity. Even though further improvements are achieved with each new generation of Si-IGBT technology (however, these gains are becoming smaller with each iteration), the relatively poor switching performance of the Si-IGBT limits converter switching frequencies to  $\sim 20$  kHz for low-power converters and 2–4 kHz for high-power converters [2].