#### University of Massachusetts Amherst

# ScholarWorks@UMass Amherst

**Masters Theses**

Dissertations and Theses

October 2021

# Internet Infrastructures for Large Scale Emulation with Efficient HW/SW Co-design

Aiden K. Gula University of Massachusetts Amherst

Follow this and additional works at: https://scholarworks.umass.edu/masters\_theses\_2

Part of the Computer and Systems Architecture Commons, and the Digital Communications and Networking Commons

#### **Recommended Citation**

Gula, Aiden K., "Internet Infrastructures for Large Scale Emulation with Efficient HW/SW Co-design" (2021). *Masters Theses*. 1138.

https://doi.org/10.7275/24549961.0 https://scholarworks.umass.edu/masters\_theses\_2/1138

This Open Access Thesis is brought to you for free and open access by the Dissertations and Theses at ScholarWorks@UMass Amherst. It has been accepted for inclusion in Masters Theses by an authorized administrator of ScholarWorks@UMass Amherst. For more information, please contact scholarworks@library.umass.edu.

### University of Massachusetts Amherst

# ScholarWorks@UMass Amherst

**Masters Theses**

Dissertations and Theses

# Internet Infrastructures for Large Scale Emulation with Efficient HW/SW Co-design

Aiden K. Gula

Follow this and additional works at: https://scholarworks.umass.edu/masters\_theses\_2

Part of the Computer and Systems Architecture Commons, and the Digital Communications and Networking Commons

# INTERNET INFRASTRUCTURES FOR LARGE SCALE EMULATION WITH EFFICIENT HW/SW CO-DESIGN

A Thesis Presented

by

AIDEN GULA

Submitted to the Graduate School of the University of Massachusetts Amherst in partial fulfillment of the requirements for the degree of

# MASTER OF SCIENCE IN ELECTRICAL AND COMPUTER ENGINNERING

September 2021

Electrical and Computer Engineering

© Copyright by Aiden Gula 2021 All Rights Reserved

# INTERNET INFRASTRUCTURES FOR LARGE SCALE EMULATION WITH EFFICIENT HW/SW CO-DESIGN

| A Thesis Presented |

|--------------------|

| by                 |

| AIDEN GULA         |

| Approved as to style and content by: |  |

|--------------------------------------|--|

|                                      |  |

| Russell Tessier, Chair               |  |

|                                      |  |

| Fatima Anwar, Member                 |  |

|                                      |  |

| Paul Siqueira, Member                |  |

|                                      |  |

Christopher V. Hollot, Department Chair Electrical and Computer Engineering

### **DEDICATION**

I want to dedicate this thesis work to my late father, who always stressed the importance of an education. Thank you for providing your guidance and wisdom throughout the years, which helped shape me into the person I am today.

### **ACKNOWLEDGMENTS**

I want to express my gratitude to my advisor Professor Russell Tessier, for his support and guidance throughout my thesis work. I want to thank Professor Fatima Anwar and Professor Paul Siqueira for serving on my thesis committee and providing their expertise. Finally, I would like to thank former graduate students Xuzhi Zhang and Narendra Prabhu for their collaboration on a portion of this thesis work.

#### ABSTRACT

# INTERNET INFRASTRUCTURES FOR LARGE SCALE EMULATION WITH EFFICIENT HW/SW CO-DESIGN

#### SEPTEMBER 2021

#### AIDEN GULA

B.Sc., UNIVERSITY OF MASSACHUSETTS DARTMOUTH M.S.E.C.E, UNIVERSITY OF MASSACHUSETTS AMHERST

Directed by: Professor Russell Tessier

Connected systems are becoming more ingrained in our daily lives with the advent of cloud computing, the Internet of Things (IoT), and artificial intelligence. As technology progresses, we expect the number of networked systems to rise along with their complexity. As these systems become abstruse, it becomes paramount to understand their interactions and nuances. In particular, Mobile Ad hoc Networks (MANET) and swarm communication systems exhibit added complexity due to a multitude of environmental and physical conditions. Testing these types of systems is challenging and incurs high engineering and deployment costs. In this work, we propose a scalable MANET emulation framework using virtualized internet infrastructures that generalizes an assortment of application spaces with diverse attributes. We then quantify the architecture using various evaluation techniques to determine both feasibility and scalability. Finally, we developed a hardware offload engine for virtualized network systems that builds upon recent work in the field.

# TABLE OF CONTENTS

|    |                                 |                         | Pag                                                                                    | $\mathbf{ge}$     |

|----|---------------------------------|-------------------------|----------------------------------------------------------------------------------------|-------------------|

| A  | CKN                             | OWL                     | EDGMENTS                                                                               | $\mathbf{v}$      |

| Al | BST                             | RACT                    |                                                                                        | vi                |

| LI | ST (                            | OF TA                   | ABLES                                                                                  | x                 |

| LI | ST (                            | OF FIG                  | GURES                                                                                  | xi                |

| CI | нлр                             | TER                     |                                                                                        |                   |

| CI | паг                             | IER                     |                                                                                        |                   |

| 1. | INT                             | ROD                     | UCTION                                                                                 | 1                 |

|    | 1.1<br>1.2<br>1.3               | Netwo                   | er Simulation Infrastructure                                                           | . 2               |

| 2. | $\mathbf{EM}$                   | ULAT                    | TION ARCHITECTURE                                                                      | 4                 |

|    | 2.1<br>2.2<br>2.3<br>2.4<br>2.5 | Docke<br>Node<br>Conta  | e Ad hoc Networks  er  Infrastructure  inerized SDN Connectivity  nical User Interface | . 5<br>. 6<br>. 9 |

|    | 2.6                             | 2.5.1<br>2.5.2<br>2.5.3 | Main Control Panel                                                                     | 14<br>15          |

|    | 2.0                             | 2.6.1<br>2.6.2          | Node Hardware Emulation                                                                | 16                |

| 3. | QU                       | ANTII                            | FYING SYSTEM PERFORMANCE                          | 18           |

|----|--------------------------|----------------------------------|---------------------------------------------------|--------------|

|    | 3.1                      | Simula                           | ation Performance                                 | . 18         |

|    |                          | 3.1.1<br>3.1.2                   | Single Stream Bandwidth                           |              |

|    | 3.2<br>3.3               |                                  | rk Coverage                                       |              |

| 4. | SIL                      | ICON                             | OPENFLOW SWITCH                                   | 30           |

|    | 4.1<br>4.2<br>4.3<br>4.4 | Switch<br>Heade                  | Flow Fundamentals  Architecture  r Parsing  Table | . 31<br>. 33 |

|    |                          | 4.4.1                            | FPGA Content Addressable Memory                   | . 36         |

|    | 4.5                      | Action                           | n Processor                                       | . 37         |

| 5. | PC                       | IE SR-                           | IOV VIRTUAL NETWORK ACCELERATOR                   | 39           |

|    | 5.1<br>5.2<br>5.3        | High-Level Acceleration Solution |                                                   | . 42         |

|    |                          | 5.3.1<br>5.3.2<br>5.3.3<br>5.3.4 | Network Drivers and PCIe Support                  | . 45<br>. 47 |

|    | 5.4                      | PCIe l                           | Hardware Implementation                           | . 50         |

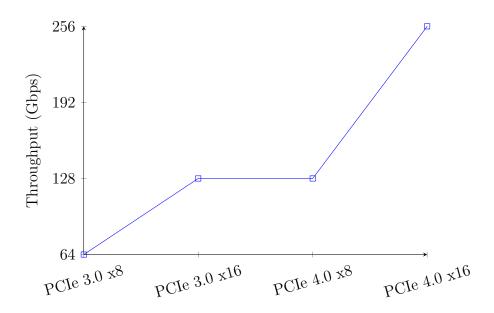

|    |                          | 5.4.1<br>5.4.2<br>5.4.3          | PCIe Specification Overview                       | . 52         |

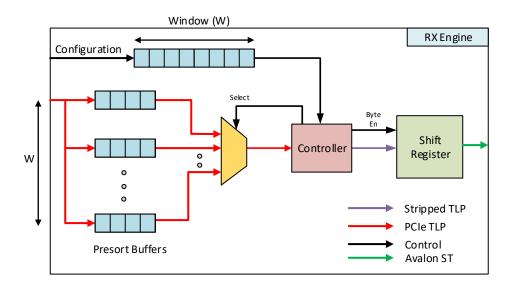

|    |                          |                                  | 5.4.3.1 Receive Engine                            | . 56         |

|    |                          | 5.4.4                            | System Memory and Programming Models              | . 58         |

| 6. |                          |                                  | ΓΙΟΝ OF PCIE SR-IOV VIRTUAL NETWORK LERATOR       | 61           |

|    |                          |                                  | mance for Containerized Applications              | 61           |

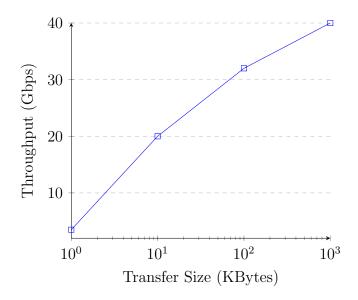

|    |               | 6.1.1  | Bandwidth Capabilities of Direct Memory Access 61      |

|----|---------------|--------|--------------------------------------------------------|

|    |               | 6.1.2  | Performance Quantification of Network Communication 63 |

|    | <i>c</i> o    | MANIE  |                                                        |

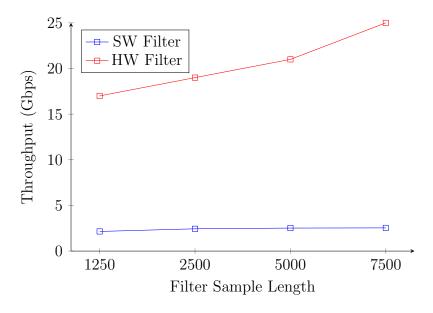

|    |               |        | T Emulation HW/SW Performance                          |

|    | 6.3           | Edge A | Application Specific Acceleration                      |

|    | 6.4           | Limita | tions for Memory Bound Computation                     |

|    |               |        |                                                        |

| 7. | $\mathbf{CO}$ | NCLU   | SION 76                                                |

|    |               | _      |                                                        |

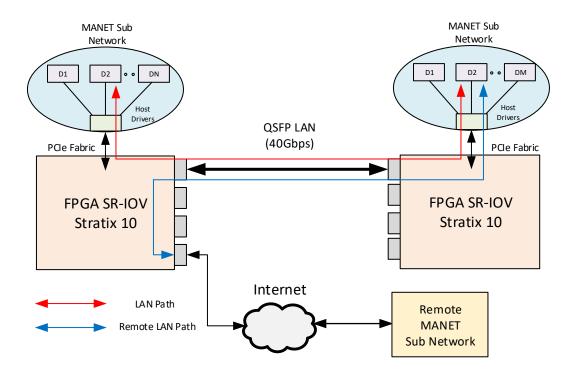

|    | 7.1           | Future | Work                                                   |

|    |               | 7.1.1  | Scatter Gather I/O                                     |

|    |               |        | FPGA Offload with OVS                                  |

|    |               | 7.1.3  | Distribute Computation Across Hosts                    |

|    |               | 7.1.4  | Interconnected CPU and FPGA                            |

|    |               |        |                                                        |

|    |               |        |                                                        |

| BI | BLI           | OGR.A  | PHY 81                                                 |

# LIST OF TABLES

| Table | Page                               |

|-------|------------------------------------|

| 3.1   | Traffic Model Grid (Mbps)          |

| 3.2   | Network Coverage                   |

| 3.3   | Network Resiliency                 |

| 6.1   | Repeated TCP/IP Connections (Kpps) |

# LIST OF FIGURES

| Figure | Page                                            |

|--------|-------------------------------------------------|

| 2.1    | Example MANET                                   |

| 2.2    | Node Architecture                               |

| 2.3    | Master Coordinator Architecture                 |

| 2.4    | Routing Endpoint Architecture                   |

| 2.5    | Emulation Architecture                          |

| 2.6    | Visibility File                                 |

| 2.7    | Topology in respect to time                     |

| 2.8    | Emulation Manager Main Control Panel            |

| 2.9    | Emulation Manager Control Processor Panel       |

| 2.10   | Emulation Manager Graph Utility                 |

| 2.11   | Hardware Based Environment                      |

| 3.1    | Inter-Node Bandwidth                            |

| 3.2    | Intra-Node Bandwidth                            |

| 3.3    | Full Message Bandwidth                          |

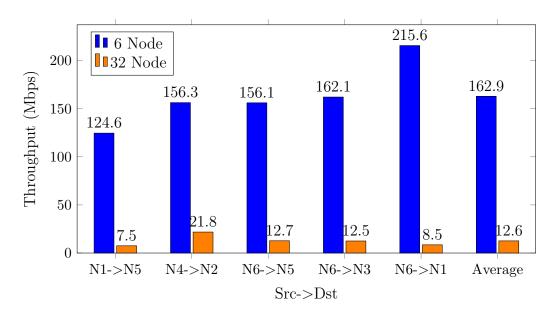

| 3.4    | Traffic Model Bandwidth                         |

| 3.5    | Connectivity Graph for Traffic Model Simulation |

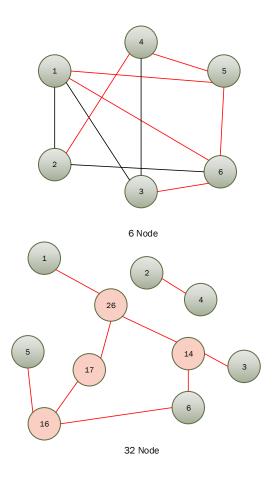

| 4.1    | Open Flow Architecture                          |

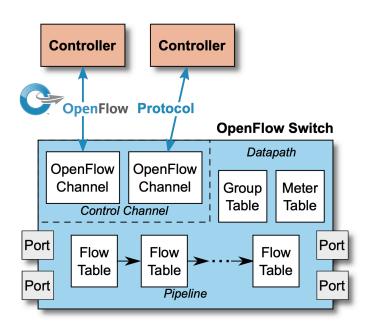

| 4.2    | OpenFlow Pipeline                               |

| 4.3  | Ethernet Header Parser in the Interpreter                  |

|------|------------------------------------------------------------|

| 4.4  | Flow Table                                                 |

| 4.5  | CAM FPGA Emulation                                         |

| 4.6  | Action Processor                                           |

| 5.1  | CPU Utilization                                            |

| 5.2  | SR-IOV Architecture for Containerized Applications         |

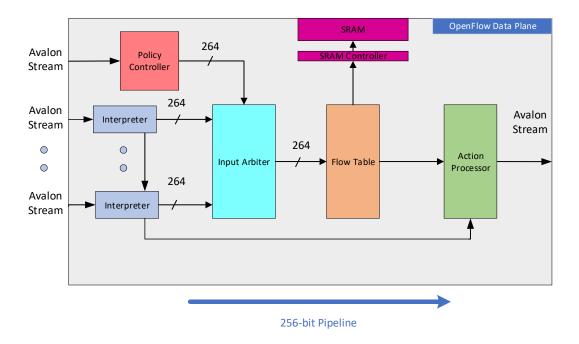

| 5.3  | PCIe SR-IOV Accelerator                                    |

| 5.4  | Socket Buffer Kernel Structure                             |

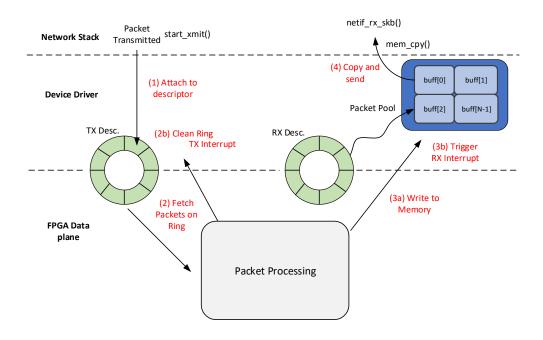

| 5.5  | Linux Kernel Packet Lifecycle HW/SW                        |

| 5.6  | PCI Express Interconnect Network                           |

| 5.7  | Theoretical PCIe 3.0 Bandwidth                             |

| 5.8  | PCIe Read Request Comparison                               |

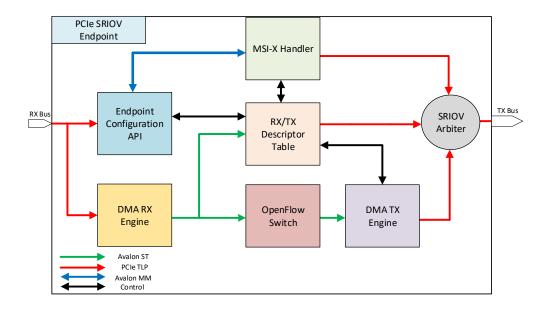

| 5.9  | PCI SRIOV Architecture                                     |

| 5.10 | Receive DMA Engine                                         |

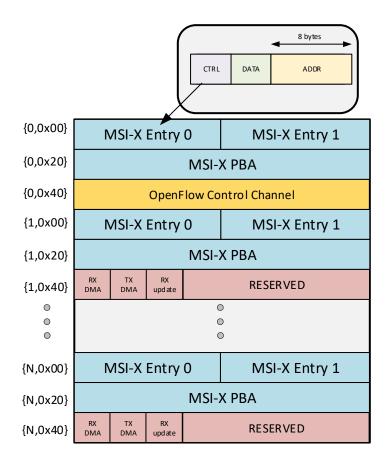

| 5.11 | PCIe SR-IOV Address Space                                  |

| 6.1  | DMA Throughput for OpenFlow                                |

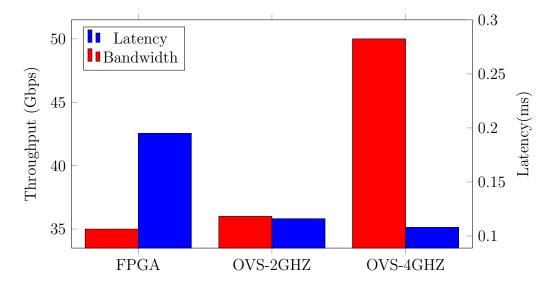

| 6.2  | Performance Comparison between OVS and FPGA64              |

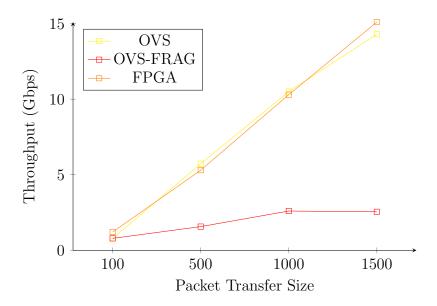

| 6.3  | Small Payload Bandwidth Comparison between Mobile Nodes 65 |

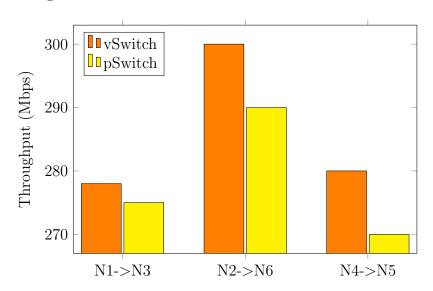

| 6.4  | MANET Emulation FPGA vs OVS                                |

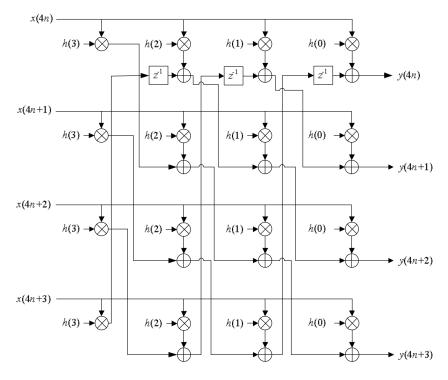

| 6.5  | Parallel FIR Filter Transposed                             |

| 6.6  | Edge Acceleration Speedup over UDP Protocol                |

| 6.7  | PCIe Spec Comparison                                       |

| 7 1  | Distributed Emulation with SR-IOV enabled FPGAs 79         |

#### CHAPTER 1

#### INTRODUCTION

In recent years, the number of connected computing devices has increased drastically. This growth has been predominantly driven by IoT and cellular technologies, including 4G, LTE, and 5G standards. The number of connected devices in 2030 is projected to be approximately 24 billion, with revenue exceeding 1.5 trillion dollars across the globe [32]. As the number of connected devices increases, so does the need for networked distributed systems' evaluation infrastructures. These infrastructures are particularly needed to support rapid prototyping and extensions in both algorithm development and routing protocols [8].

Network emulation and virtualization helps alleviate the need for expensive hardware testing and evaluation. Instead of utilizing multiple hardware devices, one can virtualize a compute host on a single Operating System (OS) and run directed tests to evaluate algorithms, routing protocols, and performance metrics [27]. Network virtualization flexibility helps assess potential future systems and determine system specifications, feature requirements, and costs before hardware acquisition and deployment. Obtaining this information early in the development process allows engineers to make informed design decisions for hardware and software sub-systems. This, in turn, decreases the need for expensive changes after the hardware has been acquired. Network emulation allows the infrastructure to behave the same way as it would on a physical device. Network emulation provides guarantees that the system software will run the same when deployed on distributed networked systems in the

field. This thesis discusses our network virtualization approach and emulation and describes how it integrates with specific applications and hardware-based acceleration.

#### 1.1 Docker Simulation Infrastructure

The field of network virtualization is vast and complex with a myriad of approaches [38][40] each with its own pros and cons for specific application spaces. Network virtualization systems are even more challenging when considering MANETs (mobile area networks), in which the network topology changes as a function of time due to real-time position updates. The network connectivity relies on the nodes' relative position in 3D space, which is enforced by the communication medium range. In this work, we propose a network virtualization infrastructure that supports MANET topologies at a proper abstraction while closely emulating the functionality of distributed embedded testbeds. The virtualized system utilizes Docker [1] containers to simulate mobile communication nodes. Mobile node can communicate with each other using an external virtual switch called Open vSwitch (OVS) [3]. The external OVS instance allows dynamic traffic forwarding based on a set of rules to help support MANET topologies. The work in this thesis builds up this virtualization infrastructure to support a wide range of applications and system performance quantification tools while increasing usability to allow rapid prototyping and evaluation.

### 1.2 Network Offload Engine

Software-based network virtualization offers customization and flexibility at a low cost, but it suffers from performance degradation due to sequential packet processing. In software-based virtualized systems, user space programs, kernel space programs, hypervisors, switches, and daemons run on a Central Processing Unit (CPU). This implementation leads to large context switching overheads [26] for virtualized infrastructures since the number of processes often exceeds the number of CPU cores.

Researchers [37][39] have recently shown great interest in developing acceleration infrastructures that support end-to-end virtual networking stacks. For this thesis project, we propose an Field Programmable Gate Array (FPGA) based offload solution that is enabled by state-of-the-art virtualization technology standards such as Peripheral Component Interconnect Express (PCIe) Single Root Input/Output Virtualization (SR-IOV) [18]. The infrastructure supports the OpenFlow protocol for packet processing, matching, and forwarding.

#### 1.3 Thesis Outline

This thesis work is divided into four major sections. The first section discusses our MANET emulation environment. We describe the architecture, capabilities, interfaces, and extensions that support various applications and use cases. The second section discusses the emulation performance metrics. We explain how system performance is quantified and discuss the implications of these results. The third section examines Software Defined Networking (SDN) solutions at the hardware level. This section describes hardware architectures at the Register Transfer Level (RTL) and a full software-defined networking switch on an FPGA is presented. The final section discusses how a network hardware data plane was integrated into our emulation infrastructure for hardware offloading. This chapter includes discussions of relevant PCIe specifications, kernel-level drivers, and hardware infrastructures for efficient HW/SW co-design.

#### CHAPTER 2

#### EMULATION ARCHITECTURE

#### 2.1 Mobile Ad hoc Networks

Mobile Ad hoc Networks (MANET) are a type of decentralized network, where the topology of the network is determined autonomously based on each node's relative position. The network connectivity can experience drastic changes based on the environment, making modeling and simulation challenging. The nodes of a MANET are constrained by limited transmission ranges forcing each node within a network to act as a router to achieve multi-hop communication [23]. Network topologies like this are most prevalent in the IoT space that operates on mesh networking protocols such as ZWave or Zigbee [6].

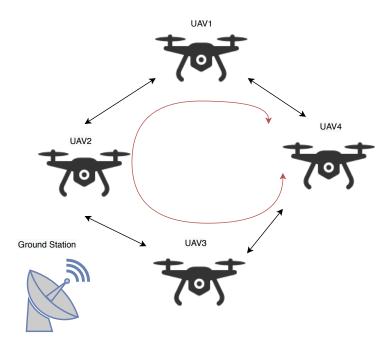

An application space that is most prevalent in military operations is demonstrated in Figure 2.1. Each node within the network is an Unmanned Aerial Vehicle (UAV). The black arrows represent direct connections between nodes, while the red arrow demonstrates a virtual network substrate achieved by multi-hop routing. The ground station acts as a special purpose node that initiates traffic used for inter-node communication. It is important to note that the ground station can be generalized to represent any node within the system. Throughout the rest of the document, the ground station will be referred to as the master coordinator. The following sections will discuss how this type of scenario is emulated using modern technologies and frameworks.

Figure 2.1: Example MANET

#### 2.2 Docker

Docker is a framework that can be used in the development, shipping, and execution of applications. A Docker platform [1] provides isolation and security, allowing many containers to be virtualized on a single host. Docker operates similar to a Virtual Machine (VM), but runs directly in the host machine's kernel and avoids the need for a complete hypervisor. In this project, we leverage Docker to instantiate multiple containers where each container represents one node within the network. The Docker infrastructure uses an *image* to determine the functionality embedded within a container. In our case, each node is an Ubuntu operating system that contains its own network stack, device drivers, kernel, and most importantly, user space programs.

Furthermore, each container can support nested containers through Docker's standard Docker in Docker (DinD) [11] image. The DinD image allows any Docker infrastructure to be realized within an already existing container. This implies that each node can host complex network infrastructures, where each piece is its own nested virtual host. The proposed architecture allows each node to act as a virtual distributed system. Each component within a node emulates its own compute environment with an isolated network stack and user space programs. The significance of this architecture will be further discussed in Section 2.6.

#### 2.3 Node Infrastructure

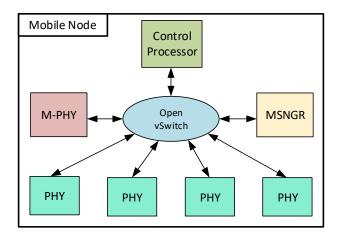

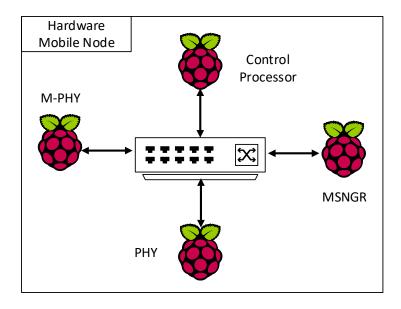

In section 2.1, we introduced a hypothetical scenario where the nodes of the MANET network represent a single UAV. For the purposes of this discussion, a mobile node can be thought of as one of the UAVs in that scenario. A mobile node must make local decisions, initiate remote connections between nodes, and maintain global routing information. Figure 2.2 shows an architectural diagram of the components that make up a mobile node to achieve this functionality.

Figure 2.2: Node Architecture

A mobile node comprises three distinct components: the control processor, the messenger (MSNGR), and PHYs. The control processor is considered to be the brain of the node. This component maintains global information such as the state of all other components and all remote connections. The control processor manages all routing tables and distributes relevant information to all components within a

mobile node. This routing information is used to forward traffic from source to destination during intermediate hops. The messenger component is used to generate traffic models. In this context, the traffic model is a stream of data from source to destination of various sizes. The supported traffic types are image, command, and telemetry data, which all have a set payload size ranging from 100 to 65k bytes.

The final internal component is a PHY, which is derived from the physical layer of a communication stack. The component acts as a software abstraction that handles all connections and transmissions to remote mobile nodes. Each PHY component can initiate and manage one active connection at a time through a Transmission Control Protocol (TCP) socket. The TCP socket is necessary due to its connection-oriented nature; each PHY must be able to recognize that a connection has been made or broken to notify and update the control processor's internal routing tables. Therefore, the number of remote connections for each mobile node is limited by the number of PHYs. Figure 2.2 is capable of four remote mobile node connections due to the number of PHYs inside of the container. The M-PHY component is almost identical to the others but can only maintain remote connections with a master coordinator component, hence the M designator. The Open vSwitch in the container is utilized to route packets between components using Media Access Control (MAC) based forwarding. All internal components dynamically discover each other using a variation of the Address Resolution Protocol (ARP) protocol.

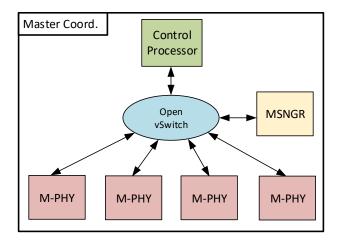

The master coordinator uses a control processor and a messenger but only utilizes M-PHYs. The M-PHY component in the master coordinator only makes remote connections with other M-PHY components. The control processor component has a unique identifier that restricts its connections to the correct component type. Internal identification allows other mobile nodes to identify a master coordinator node's messages. Figure 2.3 shows a high-level view of the master coordinator.

Figure 2.3: Master Coordinator Architecture

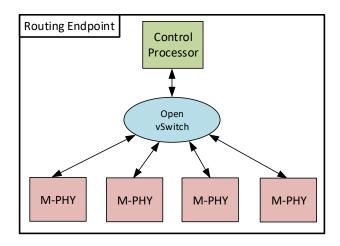

The final type of supported node infrastructure is a routing endpoint. This node type acts as an adapter that can expand connectivity between nodes. The routing endpoint's components are useful when connecting a master coordinator to other mobile nodes, expanding routing capabilities. The routing endpoint can be viewed as an antenna that extends communication when transmission distances are too far. For example, if a master coordinator cannot make a connection to a mobile node due to limited range, a routing endpoint can be used as an intermediate connections between source and destination. Section 3.2 will discuss how these components can be leveraged for network coverage. The routing endpoint does not require a MSNGR component because no messages are received or transmitted. Components in the node behave in the same manner as similar components in a master coordinator node. Figure 2.4 shows a high-level diagram of a routing endpoint with multiple M-PHY instances.

Figure 2.4: Routing Endpoint Architecture

#### 2.4 Containerized SDN Connectivity

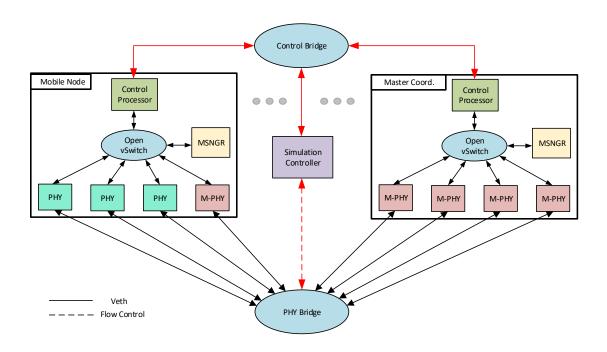

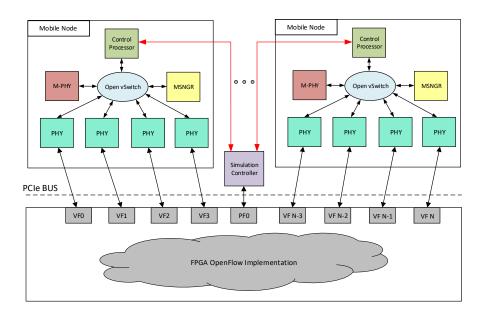

To emulate a MANET network, a network substrate that can dynamically change network topologies based on geo-spatial distances must exist. An external OVS (PHY Bridge) is utilized to connect PHYs within each node to implement network topologies. The OVS instance uses the OpenFlow protocol [28], which supports SDN. SDN decouples the control and data plane, allowing software to dictate how traffic is forwarded between ports. Chapter 4 provides protocol and implementation-specific details for SDN implementation. Figure 2.5 shows a high-level depiction of the infrastructure utilized to connect nodes represented as Docker containers.

The Simulation Controller (SC) is a component within the emulation infrastructure that helps manage connections through the external OVS. The switch allows a set of programmable rules to be defined to control how data is handled at each input port. In this architecture, the SC programs flow rules into the switch that manages which nodes can communicate with each other. The SC component can also communicate with all control processors through the control bridge, a switch that provides IP based forwarding. The SC has a global view of all mobile nodes, master coordinators, and routing endpoints and helps facilitate network topology changes

Figure 2.5: Emulation Architecture

based on visibility data. The visibility data in a JavaScript Object Notation (JSON) file defines which mobile nodes can be connected and the X, Y, Z distances between the nodes. Figure 2.6 shows the structure of visibility data that defines the network topology during a simulation. The communication medium range can be adjusted to help model Radio Frequency (RF) protocols.

Figure 2.6: Visibility File

The visibility file includes a node's position, identifier, and name. The visibility graph object key provides a list of all visible nodes indicated by the Boolean line of sight (LoS) key. Furthermore, the distance between the current node and the visible node is available. The connection is only made if the distance is less than a certain threshold dictated by the communication medium being modeled. The same structure is repeated for every valid time step over the simulation time frame. A simulation time step is the unit of time where the current network topology is guaranteed to be correct. After a simulation time step is over, new position data is evaluated. The network is modified if the distance between nodes is no longer supported based on the range of the communication medium. The opposite is also true; new connections can be made if the range between nodes is shortened to a supported distance. The SC manages this visibility data and reevaluates the network topology at each new time step. If links need to be broken or added, each respective node's control processor is

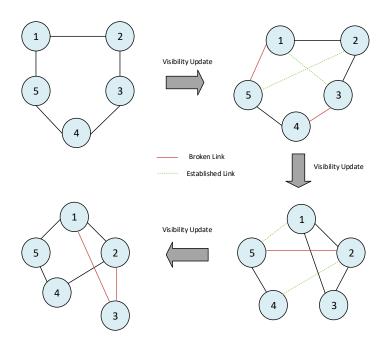

notified so all internal routing tables can be updated appropriately. Figure 2.7 shows an example simulation, where the node connectivity changes based on visibility time steps. The red lines indicate links that have been broken, while the green lines indicate newly established connections.

Figure 2.7: Topology in respect to time

The example shows a simple four-node environment with four different time step evaluations of 10 minutes each. The time step can vary depending on the application space. For example, a UAV may update positions multiple times per minute, but GPS satellites may update much more slowly. The topology changes show that the network is self-organizing, allowing nodes to be disconnected and connected based on visibility data based on relative positions.

### 2.5 Graphical User Interface

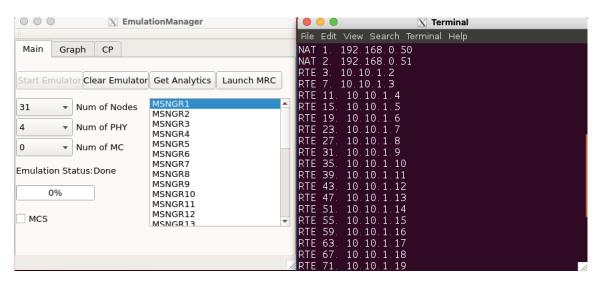

The emulation environment can be controlled through a command-line interface using a set of scripting tools. The environment can be built, deleted, and run from the scripting tools but modifications require an understanding of the architecture. To utilize all features of the environment, a general knowledge of Docker and OVS commands is needed. Furthermore, the data produced and displayed to the user can be difficult to interpret and visualize, making emulator operation less intuitive and interactive. To provide a cohesive user experience with proper technical abstraction, a Graphical User Interface (GUI) was developed using the Qt framework [35] to operate, manage, and interact with the emulation environment. The GUI allows the environment to be easily controlled, providing responsive feedback enabling rapid prototyping, evaluation, and data visualization. Figure 2.8 shows the main control panel and supported tabs.

Figure 2.8: Emulation Manager Main Control Panel

#### 2.5.1 Main Control Panel

The main control panel allows a user to build a Docker-based emulation environment with nodes, PHYs, and master coordinators. The GUI uses low-level operating system primitives to manage Docker container instantiation processes, OVS instances, and virtual networking. The GUI uses User Datagram Protocol (UDP) sockets to communicate with all control processors to manage and monitor internal statistics.

The control panel also allows MSNGR components to be dynamically spawned inside a node, enabling the user to generate traffic between mobile nodes of varying payload sizes. The user can also view each node's internal routing tables to gauge the routing algorithms' connectivity. The control panel mainly provides a means to abstract the Docker specific tasks needed to manage and run a simulation. A progress bar is utilized to provide user feedback during the environment construction since this can be quite time consuming for large scale emulation.

#### 2.5.2 Control Processor Panel

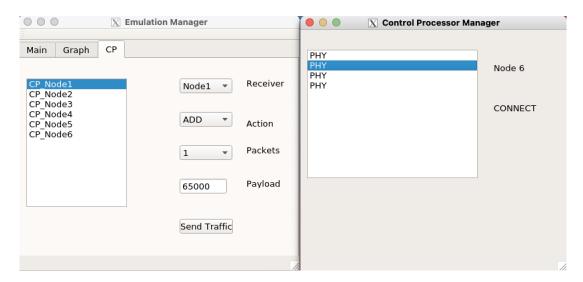

The control processor panel allows the GUI to communicate with all mobile nodes to check internal statistics and dispatch commands to the environment. The feature enables a user to query a mobile node to check PHY statistics and external mobile node connections. This allows a user to verify external connectivity and check which nodes have direct connections. The panel also enables traffic models to be generated from source to destination, making the feature useful for evaluating single-hop communication performance. Figure 2.9 shows how the panel is used to view connectivity and the form used to generate arbitrary traffic model streams.

Figure 2.9: Emulation Manager Control Processor Panel

#### 2.5.3 Graphing Utility

The graphing utility allows real-time data visualization, which provides system performance feedback to the user. The display statistics show the latency of inter-node communication links using small payload sizes and the average bits per second (bps) flowing through each communication link. This feature allows a user to visualize data flow through the MANET emulation environment and provide real-time performance metrics when deploying and evaluating traffic models. Figure 2.10 shows the two data displays. These data displays can be toggled by pressing the space bar when the graphing utility is in focus. The graphing utility dynamically scales based on the number of nodes within the environment. For example, a six node environment will have 24 active links, while a 32 node environment will have 128.

Figure 2.10: Emulation Manager Graph Utility

## 2.6 Hardware Emulation Support

To support hardware emulation, the environment must function the same way as a distributed embedded testbed. Leveraging nested Docker containers provides a flexible deployment environment while maintaining a network infrastructure that can be realized on hardware devices.

#### 2.6.1 Node Hardware Emulation

A mobile node is comprised of many components that help represent a MANET capable node, such as a MSNGR, Control Processor, and multiple PHYs. Each of these components is represented using a user space program that operates using socket-based communications. The Docker infrastructure allows the program to be run in a secure and isolated operating system with a separate network stack. The virtual Ethernet interface then communicates with all other components using Linux network primitives. The virtualized environment operates in the same way as an operating system on a physical computing device. This allows each component to run transparently on a Raspberry Pi with the Ubuntu operating system. When a component tries to initiate a connection, a low-level driver will translate packets out of the physical Network Interface Card (NIC). This abstraction allows each component to behave similarly to an embedded device. This approach allows a mobile node to be emulated in hardware using multiple Raspberry Pi's. A physical switch can be represented as a cluster of Raspberry Pis.

#### 2.6.2 System Hardware Emulation

Each hardware-based mobile node can be evaluated in a MANET simulation system. The emulated PHY using a Raspberry PI can be connected to an OpenFlow switch using its onboard NIC. Thus, any arbitrary sized network can be emulated in hardware as long as there are enough available computing and networking devices. The software SC can be instantiated on a Raspberry Pi and connected directly to the OpenFlow switch to program flow rules into the device.

Furthermore, the environment can operate in a para-virtualized manner where it only partially represents the underlying hardware. In this scenario, each Raspberry PI acts as one mobile node where the node's internals are abstracted using Docker and

Figure 2.11: Hardware Based Environment

OVS. The external connections between mobile nodes would still be hardware-based with an OpenFlow capable switch controlled by a software entity.

The deciding factor in deployment is based on cost and hardware acquisition. A hardware-based system would require (2 + PHY) \* Nodes embedded devices, while a para-virtualized environment would only require an embedded device count equivalent to the number of nodes being emulated. Of course, this type of hardware-based simulation is not entirely scalable because the number of necessary devices becomes high when emulating anything more than a few nodes. Another limiting factor is the number of ports available on an OpenFlow capable switch. For example, a 32 Node environment with 4 PHY devices would require a 128 port OpenFlow switch, which is not available commercially.

#### CHAPTER 3

#### QUANTIFYING SYSTEM PERFORMANCE

The emulation infrastructure helps model, prototype, and explore networked distributed systems. The infrastructure emulates a distributed system's interactions and communication by virtualizing a CPU. This compromise leads to a disparity in system performance between the emulation infrastructure and an implemented distributed system. In a distributed system, all system processes can be run concurrently across many CPUs. There is no need for context switching, synchronization methodologies, hypervisors, or resource overhead for virtualized interfaces. This chapter will discuss how system performance is quantified for the emulation environment. The evaluation is split into three broad categories: simulation performance, network reachability, and resiliency. The server used for performance evaluation is a Dell PowerEdge T640 with 192 GB of memory and a 20-core Intel Xeon processor with 40 virtual threads. The server operating system is Ubuntu 16.04 LTS [36] with kernel version 4.4.0-138.

#### 3.1 Simulation Performance

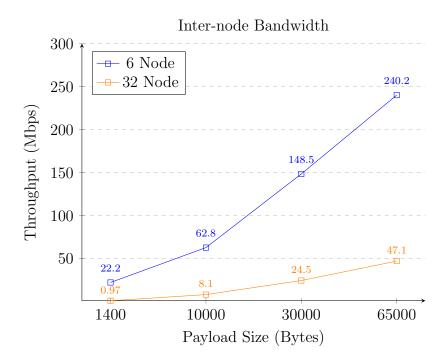

In the emulation environment shown in Figure 2.5, there are two distinct types of network links, inter-node and intra-node communication links. These communication links operate on two distinct transport level protocols, TCP and UDP, respectively. This section evaluates the emulated bandwidth for both types of communication links during a simulation. This analysis highlights which communication link acts is a bottleneck for message passing. Two simulation environments are evaluated, one environment with six mobile nodes and another with 32 mobile nodes. Each

Figure 3.1: Inter-Node Bandwidth

simulation environment runs both a simple point-to-point communication network and a traffic model with multiple streams transmitting simultaneously.

#### 3.1.1 Single Stream Bandwidth

Single stream bandwidth is defined as the total number of bits per second transmitted from source to destination, when only one active node is transmitting data. The same tests are evaluated for both a TCP link used to communicate with components inside a mobile node and a UDP link used to communicate between nodes.

Figure 3.1 shows the performance metrics for inter-node communications using the TCP protocol. In each environment, there is only one active link being used for data transmission. The initial results highlight the discrepancy of performance between six- and 32-node systems. For example, in a distributed hardware-based system, processes running on node C will not affect the bandwidth of data transfer between nodes A and B. In our emulation environment, every process on the system competes

Figure 3.2: Intra-Node Bandwidth

for cycle time on one CPU, which degrades performance. Larger payload sizes yield better bandwidth utilization of the links. This result is attributed to TCP's windowing and the associated overhead enforced by collision detection, retransmission, and sequencing. For small payloads, this transmission overhead becomes a significant percentage of the payload size, reducing link utilization.

Figure 3.2 shows the intra-node communication link bandwidth. This data shows that UDP based payloads have a higher overall bandwidth between the two emulation environments. The UDP protocol can achieve higher bandwidth due to its simplicity but does not guarantee delivery, collision detection, or in-order retrieval. The protocol header of UDP is more simplistic and has less overhead and impact on overall throughput. The results show that the TCP link acts as a major bottleneck for message passing capabilities, especially for smaller payload sizes. The difference in bandwidth is more than 10x when evaluating payloads of 1400 bytes.

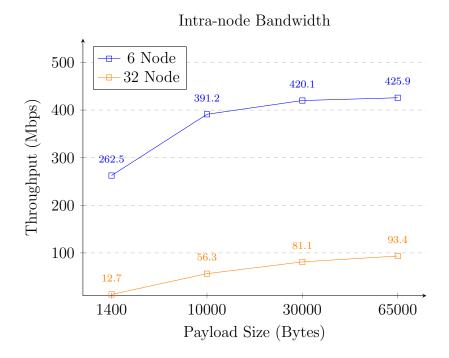

Figure 3.3: Full Message Bandwidth

The previous tests showed inter-node and intra-node communication link performance for point-to-point connections. However, they do not measure performance across entire communications paths. In Figure 2.5, there are a total of three communication links and two virtual switches between the MSNGR components of two mobile nodes. The combination of these links and switches form a full source-destination communication path. Since MSNGR components generate and receive traffic in each mobile node, the path bandwidth determines the message passing capability of the system. Figure 3.3 shows the message passing bandwidth between messenger nodes in both six- and 32-node environments with varying payload sizes.

Higher bandwidth can be seen at larger payload sizes, influenced by the TCP bandwidth for inter-node communication links. Limited inter-node bandwidth is the dominant effect since TCP packets have considerable overhead and limit total performance. In TCP protocol schemes, lower level kernel drivers have multiple quality assurance checks to help enforce arrival guarantees, which UDP does not provide at

the transport level. Additionally, the external switch has many connections in a 32-node environment, which drastically slows down packet processing, classification, and forwarding. Overall, the results show that the total bandwidth is much closer to the inter-node communication link bandwidth, demonstrating that these links limit system performance. The limiting factor for system performance is the overhead of the TCP protocol and virtual OVS switch used to connect mobile nodes. The overhead is even more significant with larger sized environments as the external switch scales with the number of ports.

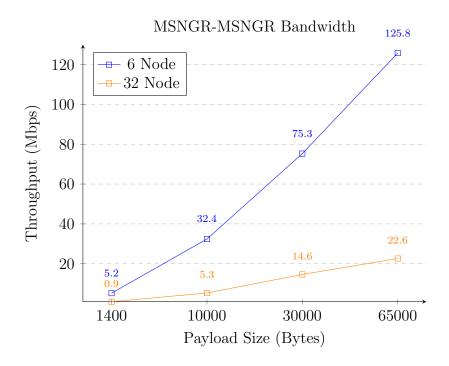

#### 3.1.2 Traffic Model Bandwidth

MANET communication is typically not limited to one message stream within an entire network. Therefore, the tests in the previous subsection do not evaluate message passing bandwidth under typical conditions. The tests described in this subsection quantify message passing bandwidth in the presence of multiple data streams. Our traffic model allows the emulation environment to evaluate realistic MANET payloads with command, image, and telemetry data. In the previous subsection, it was shown that maximum link utilization is achieved with larger payload sizes. The tests in this section use payloads at the limit of TCP transmission, roughly 65k bytes. Traffic stream types that support these payload sizes include image data, a common payload type in MANET based networks including those consisting of UAVs. Emulation environments with six and 32 mobile nodes are evaluated in the traffic model. Figure 3.4 shows traffic model performance for five image data streams for both six and 32 node environments. The performance data highlights the bandwidth of each stream.

Figure 3.5 shows the connectivity for six- and 32-node systems. The red nodes indicate those reached through intermediate hops, and the gray indicate those that are a source or destination. The red edges represent links with active traffic based on

Figure 3.4: Traffic Model Bandwidth

the five image data streams. All of the six-node streams are transmitted in a single hop, while the 32-node environment is transmitted across 4, 1, 2, 2, and 3 hops, respectively, for the results in Figure 3.4. The number of hops is defined as the number of intermediate links needed for a packet to reach its destination from its respective source. From this data, we can see that each image stream has a different performance profile. In this environment, all five traffic streams run concurrently. The number of processes that compete for CPU cycles is greater than the number of cores and virtual threads. Performance deviation is attributed to the overhead caused by context switching and the importance of each process in the Linux scheduling algorithm. All user-space processes in the emulation infrastructure are given the highest priority, effectively making them real-time. The variance between test runs is high due to the number of high priority processes running concurrently, including kernel-space processes. If higher priority is given to specific mobile nodes, a performance shift is seen, favoring processes with higher priority.

Figure 3.5: Connectivity Graph for Traffic Model Simulation

The variation is even more significant in the 32-node environment due to multi-hop routes. In the six-node environment, most data streams reach their destination in a single hop. For example, in an environment with four PHYs, Node 1 communicates directly with all but one node. In a 32-node environment, Node 1 can only directly reach four distinct nodes, 13% of the entire network. Therefore, most communication is made through multi-hop routes, degrading system performance, and increasing the variance between test runs. Our routing algorithms are optimized to choose the shortest path from a traffic stream's source to a destination.

The 32-node environment has 28x more possible communication paths than a sixnode environment. To test system performance in the larger environment, the number of active traffic models was increased to span a more complete subset of mobile nodes. The traffic models were intentionally overlapped to demonstrate how performance is impacted when nodes receive or transmit streams concurrently.

Table 3.1: Traffic Model Grid (Mbps)

|     | N15     | N16    | N17     | N18    | N21     | N22     | N23     | N24    | N25    | N26     |

|-----|---------|--------|---------|--------|---------|---------|---------|--------|--------|---------|

| N1  | X       | X      | 11.1(2) | X      | 12.3(3) | X       | X       | X      | X      | X       |

| N2  | X       | X      | X       | 6.2(4) | 8.5(5)  | X       | X       | X      | X      | X       |

| N3  | X       | X      | X       | X      | X       | X       | X       | 7.2(4) | 9.4(2) | 12.5(2) |

| N4  | 14.1(2) | 9.5(3) | X       | X      | X       | X       | X       | X      | X      | X       |

| N5  | X       | X      | X       | X      | X       | X       | X       | X      | 8.8(3) | X       |

| N6  | X       | X      | X       | X      | X       | X       | X       | 7.6(4) | X      | X       |

| N7  | X       | X      | X       | X      | 20.5(1) | 12.6(2) | X       | X      | 8.3(3) | X       |

| N8  | X       | X      | X       | 5.5(5) | X       | X       | X       | X      | 8.7(3) | 12.6(2) |

| N9  | X       | X      | X       | X      | X       | X       | X       | 8.1(3) | X      | X       |

| N10 | X       | X      | X       | X      | X       | 13.1(2) | 22.5(1) | X      | X      | X       |

Table 3.1 shows performance metrics for 20 source-destination streams. The vertical rows represent the destination nodes for a traffic stream, while the horizontal rows represent the source nodes. The table entry where a horizontal and vertical row meet is the performance and (hop count) of that traffic stream from the respective source to destination. An x in the entry represents that there is no stream with that source and destination pairing. All bandwidth results in a vertical row indicate competition between receiving streams on the destination MSNGR component. All bandwidth results on a horizontal row indicate competition between sending streams on the source MSNGR component. The results demonstrate that the system performance scales well with a larger number of traffic streams. However, the variance from different links is even greater due to increased competition when multiple streams are sent or received from the same node. Similarly, performance is lower when a receiving node handles traffic from multiple sources. An example is the traffic stream from node 10 to node 23. This route has a bandwidth of 22.5 Mbps with one hop from source to destination. However, the bandwidth from node 7 to node 21 is only 20.5 Mbps for

one hop. The only difference between these two routes is that node 21 receives two traffic streams while node 23 only receives one.

## 3.2 Network Coverage

In a MANET, nodes cannot always communicate with each other, since the network topology relies on distance, communication medium, and environmental factors. In this section, we introduce the concept of network coverage. In this context, network coverage is defined as the percentage of nodes that can be reached by a central master coordinator component. Figure 2.3 demonstrates the architecture of this node.

In the following tests, the number of PHYs within a mobile node will be varied, limiting the number of remote connections that can be made from a mobile node. The number of routing endpoints will also be varied. These iterative tests aim to find the minimum configuration of components such that full network coverage is maintained. The more components within a system, the more resources utilized. Therefore, minimizing the number of components within the system will allow larger environments to be emulated with similar network coverage. Table 3.2 shows the iterative test results to determine the minimum number of components needed so that full network coverage is maintained.

Table 3.2: Network Coverage

| PHY per Node | PHY per Endpoint | PHY per MC | Coverage (T/F) |

|--------------|------------------|------------|----------------|

| 4            | 0                | 1          | Т              |

| 3            | 0                | 1          | T              |

| 2            | 1                | 1          | Т              |

| 1            | 4                | 4          | F              |

| 1            | 3                | 3          | F              |

| 1            | 2                | 2          | F              |

| 1            | 1                | 1          | F              |

| 0            | 0                | 0          | F              |

Table 3.2 shows the results from a 32-node simulation. Three components are deployed in the environment: mobile nodes, routing endpoints, and master coordinators (MCs). Each of these components is tested with varying numbers of PHYs per node to allow remote connections. The master coordinator must have enough PHYs to connect to every routing endpoint. Additional PHYs can be used to connect to remote mobile nodes to expand connectivity. The column containing the number of PHYs in the MC excludes those allocated for connections to routing endpoints. Similarly, the column containing the number of PHYs in an endpoint excludes those allocated to the master coordinator. The number of PHYs within a routing endpoint constrains how many nodes can be connected externally. Fewer PHYs in a routing endpoint indicates fewer connectivity capabilities. The number of PHYs in a master coordinator indicates how many external connections can be made to mobile nodes.

The data shows that the minimum configuration of PHYs for full coverage contains two PHYs per mobile node, one PHY per endpoint, and one PHY per MC. Thus the mobile nodes can connect to two other mobile nodes, the endpoints can connect to one node, and the master coordinator can connect to one other node. The results show that the routing endpoints help expand network coverage and allow fewer PHYs to be used in each mobile node. This demonstrates a trade-off between memory utilization and performance. The routing endpoint approach decreases the total number of containerized components at the cost of performance. Each message sent from the master coordinator using this approach will need to go through extra hops from source to destination, impacting total bandwidth. The difference in memory and resources becomes more apparent in larger sized emulation environments. For example, in a 32-node environment eliminating two PHYs per node yields a reduction of 64 components.

## 3.3 Network Resiliency

Our final performance evaluation involves network resiliency, which is defined as the amount of network coverage maintained in the presence of link failure. In MANET environments, link failures can happen due to hardware/software issues, environmental factors such as transmission distances, and noise. A robust MANET should still be able to provide coverage in the presence of link failure. Recent research has shown significant interest in simulating and evaluating algorithms and protocols relevant to MANET in the context of wireless communications. These efforts include link repair in Ad-hoc On Demand Distance Vector (ADOV) algorithms [33] and failure prediction in MANET based systems using statistical methods [25]. These efforts aim to increase state of the art in MANET based systems by increasing network coverage during navigation of various topologies and predicting potential failures for more efficient routing.

In this section, we quantify network resiliency in the emulation environment when one or more links fail using a variation of ADOV for route exploration. The emulation environment supports link jamming to simulate link failure, which allows a user to disconnect any active link. When a link is jammed, the SC will attempt to find a connection to another PHY on the same or a different node to preserve network connectivity. In these simulations, we assume that only one PHY is rendered useless when a link is jammed, giving another PHY an opportunity to initiate a connection.

Network resiliency evaluations were performed for a 32-node emulation environment. The six-node system has insufficient connectivity to provide meaningful results in the case of link failure. In our experiments, links are jammed in a randomized fashion. The evaluation baseline assumes zero jammed links and 100% network coverage. The test starts with four links jammed, and each successive experiment iteration assumes an additional four jammed links, up to 24 links total. Table 3.3 shows the incremental coverage data. The first column shows the number of links deleted, the

Table 3.3: Network Resiliency

| Number of Links | Coverage       | Links Recovered |

|-----------------|----------------|-----------------|

| 0               | 100%           | 0               |

| 4               | 96.5%          | 1               |

| 8               | 82.7%          | 4               |

| 16              | 58.6%<br>44.8% | 8               |

| 24              | 44.8%          | 10              |

second column shows achieved coverage, and the third column shows the number of links that were recovered by dynamic re-routing using new PHY connections.

The table shows that coverage does not decrease linearly. This result indicates that the MANET framework is a self-healing network, in which damaged links can be repurposed for other connections to maintain coverage and network performance. The amount of recovered links increases significantly when the number of jammed links exceeds 20%. This result is attributed to how negotiation is handled; when a link is rendered inactive, one PHY is allowed to connect to another unused node. If only one link breaks, it is unlikely that its PHY can be re-purposed because the pool for available links is small. When more links are broken, the collection of available links increases, and the probability of re-initiation increases considerably. It is important to note that links within a MANET typically do not have uniform importance. It is often the case that one link rendered useless could have a drastic effect on coverage while a different link could have none. The results demonstrate that the MANET emulation environment can handle some link failures but cannot recover from all of them due to the non-uniform nature of link importance.

## CHAPTER 4

### SILICON OPENFLOW SWITCH

## 4.1 OpenFlow Fundamentals

The emulation environment uses an OpenFlow capable virtual switch called OVS to connect inter-node communication links. Figure 2.5 shows the external OVS instance and its relation to the emulation environment. The switch allows software to configure how traffic is forwarded from port to port. This functionality enables the decoupling of the data and control planes. In this chapter, the characteristics of OpenFlow capable switches are discussed and an implementation in digital hardware is presented.

Figure 4.1: Open Flow Architecture [28]

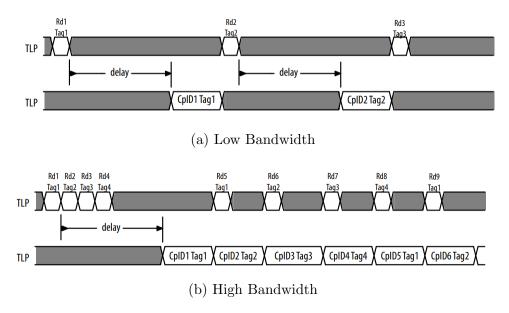

Figure 4.1 depicts a switch that can support OpenFlow functionality. The architecture includes a control channel and a data path. The control channel allows an OpenFlow controller to modify the hardware's switching capabilities. The data path is compromised of N levels of flow tables which hold information on how packets should be processed. For example, a flow table can hold an entry that specifies that all TCP packets to be forwarded out of port 2. Similarly, a flow table can also hold an entry that specifies that all ARP packets should be dropped. The OpenFlow controller is typically located outside of the switch. The configuration channel is generally interfaced through a secure TCP socket. In this work the OpenFlow control port is accessed via a PCIe bus to allow user space software to control and manage flow entries and packet statistics. An OpenFlow switch's data path contains a group table and a meter table to store internal statistics on how flow tables are accessed. For example, statistics that specify how many times a flow entry has been hit or how many packets have been processed on a specific port can be stored in local Static Random-Access Memory (SRAM).

The OpenFlow protocol specifies how packets should be parsed and classified. Packets with Virtual Local Area Network (VLAN) tags are classified differently from those without tags. Packets at different layers of the Open Systems Interconnection (OSI) [10] model also must be handled differently. ARP packets reside on level 2 (L2) and do not have an IP level header. TCP packets have both IP and transport-level headers. Therefore, an ARP packet is classified and output in fewer cycles than a TCP or UDP packet. A packet with L4 fields can be classified in two cycles while L2 fields are done in one, assuming a 256-bit bus width.

#### 4.2 Switch Architecture

A preliminary version of an OpenFlow switch has been developed to support packet offloading for matching, classification, and forwarding. Here, we describe the

Figure 4.2: OpenFlow Pipeline

hardware data path written in RTL that supports the OpenFlow protocol. Figure 4.2 shows a block-level design for the OpenFlow pipeline. The diagram shows stream interfaces for data transfer. These interfaces are currently implemented using the Avalon Stream protocol. The protocol is a standardized bus specification in Intel FPGA systems that allow multiple writes from software-based sub-systems to be translated into a data stream for high performance applications [19].

In this design, there are N Avalon stream interfaces allowing network traffic to be processed externally. Each interface has a TX (transmit) queue and RX (receive) queue that reside inside the interpreter modules. The interpreter module parses incoming Ethernet frames and constructs a match-field tuple, which is utilized during packet lookup and classification. The match-field tuple is a 264-bit tag that contains various fields from the packet which helps provide a unique identification. At the top left of the figure, an Avalon Stream interface to a policy controller is shown. The policy controller receives messages from the OpenFlow controller to add/delete/modify

flows or perform packets' actions. The policy controller receives messages from the host machine through the PCIe bus through a first-in-first-out (FIFO) queue. The PCIe bus provides an Avalon Stream interface for data communication, which allows a convenient interface mechanism to this design. The policy controller operates like the interpreter, except that it constructs a match-field tuple to write into the flow table instead of a lookup. These outputs go into an input arbiter that utilizes a round-robin scheduling policy without time slices to allow fair access into the data pipeline.

The data pipeline includes a flow table, a content addressable memory that initiates an action based on packet match fields. Typical actions specified by the flow table include packet drop, packet forward, and packet modification. After an action has been retrieved, the packet is forwarded to an action processor, where the corresponding action is performed. A local SRAM is utilized as a buffer. The data plane's width is 256-bits wide, which is constrained by the bus width of the PCIe IP provided by Intel.

# 4.3 Header Parsing

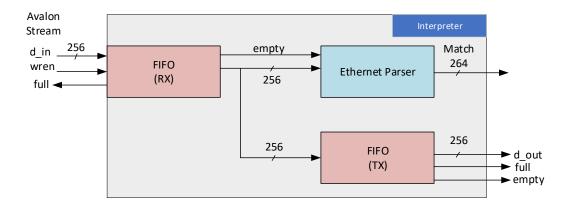

The Ethernet interpreter design reads and parses incoming Ethernet packets. These packets encapsulate a complete frame that can consist of L2, L3, or L4 headers of the OSI model. Header matching must support the following protocols from the OpenFlow specification: IPV4 [16], ICMP [15], ARP [31], TCP [17], UDP [21], and VLAN [5]. Figure 4.3 shows a block diagram of the Ethernet interpreter module.

In the figure, there are two FIFO memory elements. The RX FIFO is used to store incoming data from the Avalon stream interface. The TX FIFO is used to re-buffer the data as the parser reads from the RX FIFO. The Avalon stream interface has a data bus, a write enable signal, and a full signal, which allows back pressure so useful data will not be overwritten if an overflow occurs.

Figure 4.3: Ethernet Header Parser in the Interpreter

The Ethernet parser module within the interpreter sequentially reads 256-bit payloads and interprets the fields within them. The parser is a state machine that constructs a 264-bit match field based on packet header. The FSM determines packet type and specifies appropriate packet processing actions.

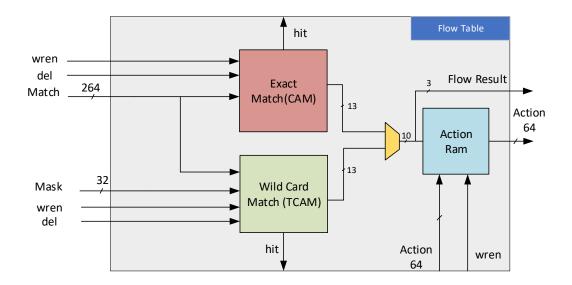

#### 4.4 Flow Table

The flow table design includes three groups of memory elements. An OpenFlow switch performs two types of matching: exact and wild card. An exact match requires that all 264 bits of the input match an entry within the table. The exact match is implemented using a Content Addressable Memory (CAM). The wild card match allows a mask to be provided, which signifies which bits can be ignored in the match process. A Ternary Content Addressable Memory (TCAM) must be utilized to extend the memory to handle don't care bits to achieve this functionality. The TCAM is a special type of CAM that allows matching on three input fields: '1', '0', and 'X'. For example, if only the port the packet came on is of interest, a mask can be provided to disregard all other fields. In this configuration, all packets would be matched on the specified input port regardless of the other fields. Figure 4.4 shows the flow table

Figure 4.4: Flow Table

general architecture. Pipeline stages and most of the control logic are omitted for simplicity.

The CAM and TCAM memory elements handle packet lookup when incoming messages are parsed from the OpenFlow or Ethernet Interpreter modules. Both memory elements can handle entry writes and deletes. This functionality allows entries to be added, deleted, or modified when an OpenFlow message is received from the controller. If a received packet matches one of the CAM entries, the hit flag is asserted, and the corresponding address of the match is given to the priority encoder. The priority encoder determines which address is given to the action RAM, which holds information about how packets are handled when a match occurs. If both the TCAM and CAM have a match, the priority encoder will use the CAM address. The CAM's also specify the flow result signal based on the input port of the incoming packet. In this case, the flow result signal is 3-bits indicating a total of 3 input ports. This can be generalized to an N-bit signal for a total of N input ports. The action RAM then fetches the action associated with the matched packet. The action

Random-Access Memory (RAM) stores where the packet should be forwarded based on the hit flow entry along with an action, if any. Each valid CAM address has a corresponding entry in the action RAM. The action processor then performs data movement adhering to the received action.

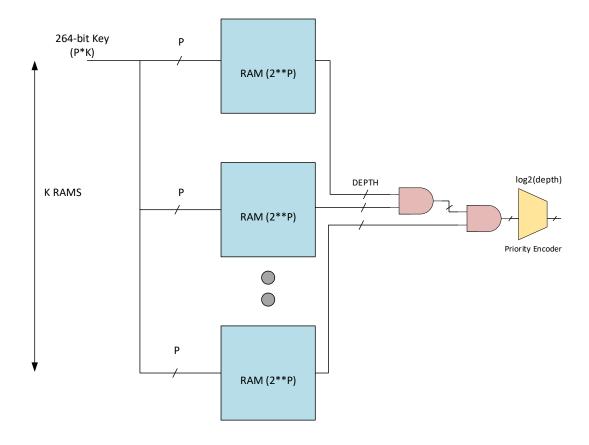

#### 4.4.1 FPGA Content Addressable Memory

Modern FPGAs do not contain CAM cell memory, although they can be emulated using logic [24]. The CAM key can be used as an address into RAM. The data at the location will consist of a '1' if there is a valid entry. The drawback of this implementation is memory utilization when using large keys. In this design, a 264-bit key must be used for the CAM. This means that we must have a total of  $2^{264}$  locations in memory, which no FPGA can support. To address this issue, multiple smaller memories can be utilized. The 264-bit key can be split up into K different RAMs, in which the number of address bits for each is P. The equation shown below indicates the total number of memory bits required to realize a CAM in an FPGA using this approach. Each RAM has  $2^P$  locations, and there is a total of 264/P total RAMS in parallel. Then each location has a width proportional to the number of entries within the CAM.

$$\frac{264}{P}*(2^P)*CAMEntries$$

A bit-wise AND can then be performed on the outputs of the RAMs and then converted into an address using a simple priority encoder. The encoder translates the resulting one hot encoding into a valid address for lookup. The basic architecture of the CAM can be found in Figure 4.5. The same concept can be applied to the TCAM, except at most  $2^P$  writes are needed for each address specified in the TCAM mask. For example, a mask of all zeros indicates that all bits are don't cares, which translates to valid data at every RAM location. An FSM based model is used to

Figure 4.5: CAM FPGA Emulation

perform sequential writes based on an input mask to determine don't care encoding [22].

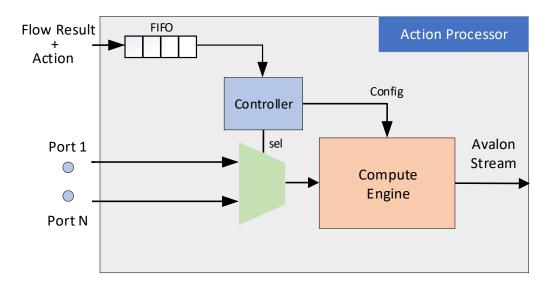

### 4.5 Action Processor

The action processor module performs packet processing options supported by the OpenFlow protocol. These actions include setting, modifying, or removing network packet fields and forwarding or dropping packets. In the current implementation, the module is used for forwarding traffic, dropping traffic, and setting MAC addresses. Figure 4.6 shows the architecture for the action processor.

The port inputs are connected directly to the TX queues located in the interpreter module. The flow result and action input signals indicate which input port has a

Figure 4.6: Action Processor

packet and the action needed to be performed, respectively. For example, if the flow result indicates no flow match, the packet is dropped, and the action field is ignored. Conversely, if the flow has a valid match, the port is connected to the compute engine through the multiplexer, and the action is performed. The controller facilitates the data transfer between the TX queues and the compute engine. The compute engine is configured based on buffered flow results and action data provided by the flow table. The Avalon Stream output interface connects to downstream logic used to transmit packets over PCIe which will be discussed in Chapter 5.

### CHAPTER 5

## PCIE SR-IOV VIRTUAL NETWORK ACCELERATOR

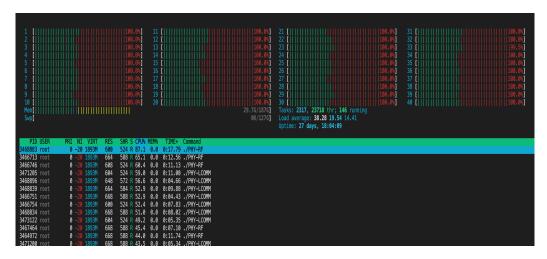

Processor-based networked virtualized systems are flexible for prototyping and algorithm exploration. However, there is an inherent limitation in system performance due to the threaded nature of CPU resources. In our software-only emulation environment, processes utilize CPU cycles and incur large overheads for context switching. The server currently used for testing includes 20 CPU cores, each with two threads per core. When running a 32-node simulation with four PHYs, 188 user-space processes, each with multiple threads, are created. This does not consider the processes for the virtual infrastructure such as OVS, Docker, and Linux based primitives. Therefore, context switching must frequently occur to guarantee fair access to resources. Figure 5.1 shows the CPU utilization using the htop command during a simulation run.

Figure 5.1: CPU Utilization

The CPU utilization shows that all cores and virtual threads are running at high capacity, demonstrating the emulation environment's CPU-bound computation.

Based on this information, the overall performance may be improved by offloading computation from the CPU to a custom hardware data plane. By offloading computation, the CPU will be freed up to work on other tasks, while packets are matched, classified, and transferred into user space memory. The http results show that reducing CPU utilization could allow more processes to be quickly serviced allowing more concurrency to be exploited in the simulation.

Using the design from the previous chapter as a basis, we developed an end-to-end FPGA based acceleration stack for software-defined networking. The hardware-based OpenFlow switch designed in Chapter 4 was integrated into a PCIe acceleration engine using kernel-level drivers to abstract network operations. The following sections will discuss the design decisions involved at various levels of the HW and SW stack.

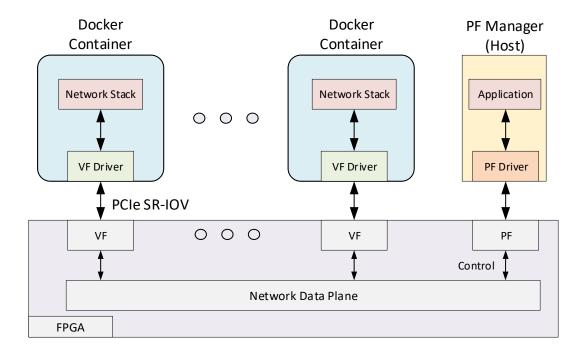

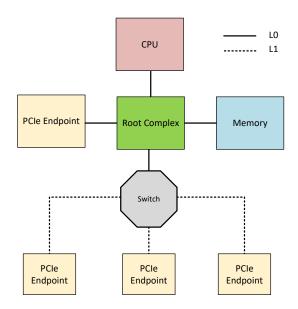

## 5.1 SR-IOV Virtualization Specification

SR-IOV [18] is a specification that supports efficient HW/SW co-design for scalable networked infrastructures that sits on top of traditional PCIe. The SR-IOV specification allows a device such as a network adapter to separate access to its resources through PCIe hardware functions [7]. There are two types of functions enabled by SR-IOV: Virtual Functions (VF) and Physical Functions (PF). The PF advertises the device's SR-IOV capabilities. It configures and manages all enabled VFs. Each VF is typically a memory region or network interface. Each PF and VF is assigned a unique requester ID so that each can initiate reads, writes, and Direct Memory Access (DMA) requests through the host PC software. The specification allows network traffic to bypass the software switch layer of the virtualization stack so that these environments can get near line-rate performance. Figure 5.2 shows an abstract representation of a SR-IOV network stack.

In this scenario, an application-specific process manages the PF while the network stack sends and receives data from the VFs. The PF manager that runs within the

Figure 5.2: SR-IOV Architecture for Containerized Applications

host controls the SR-IOV system configuration and the compute engine in the physical hardware. For example, in a networked system, the PF manager would configure the switching substrate to the handle operation of N VFs. The Docker containers are virtualized operating systems that each gets their own dedicated PCIe function as if there were N physical hardware devices. The virtualization standard allows the host software to mimic how a system operates under the conditions mentioned earlier. Thus, each driver within a Docker container communicates with the hardware as if it has its own I/O device and associated memory resources. The configuration allows data to be transferred from the Docker container to the hardware very efficiently with minimal CPU overhead.

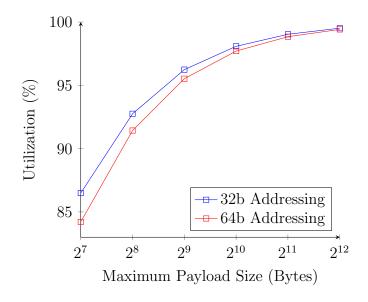

## 5.2 High-Level Acceleration Solution

To develop a general-purpose accelerator for scalable network interfaces, the PCIe SR-IOV specification was utilized to interface with a custom logic design on an Intel Stratix 10 FPGA [34]. Figure 5.3 shows an abstract representation of how the custom FPGA design interacts with the emulation environment through the facilities supported by the SR-IOV specification. The OpenFlow data plane from Chapter 4 was integrated into the custom HW solution to achieve packet classification capabilities.

Each network interface acts as a port on the external OpenFlow switch used in the emulation environment. The SR-IOV specification supports up to 2048 Virtual Functions (VFs) across all Physical Functions (PFs). Thus an SR-IOV enabled FPGA can support hardware offloading for virtual switches with up to 2048 ports assuming no other physical functions are utilized. Every configuration in our emulation environment can be supported by this offload infrastructure. The theoretical limit for hardware acceleration would be a total of 512 mobile nodes, where each node has 4 PHYs (2048 total ports). This count is subject to FPGA resources that are constrained by memory utilization for base address registers, descriptor tables, and configuration space for PCIe capabilities.

In this solution, each PHY within the emulation environment is connected to a VF through Linux network name spaces and virtual Ethernet interfaces. Each PHY can initiate a TCP-based socket connection using low-level Application Programming Interface (API) primitives. The VF kernel drivers initiate DMA transfers to the physical hardware data plane when the Ethernet device wants to send a packet. When the hardware transfer is complete, an MSIx interrupt will be triggered, allowing the VF driver to reallocate the DMA descriptor and memory space for new incoming packets. After matching and classification of a packet, the data plane will either drop or forward the packet to the correct memory space associated with its corresponding

Figure 5.3: PCIe SR-IOV Accelerator

VF driver. The driver will then receive this packet through another MSIx interrupt and then transfer the data to the receiving PHY component's socket connection. This abstraction allows the emulation environment to operate and function in the same manner as the virtual switching solution.

The Simulation Controller can directly program the OpenFlow data plane through kernel-level drivers and basic user-space API calls on the host machine. The role of the simulation controller is to manage which mobile nodes can communicate with each other during a simulation as visibility changes as a function of time. A Linux character driver provides these capabilities, allowing user-space programs to communicate to the hardware devices on-chip memory through the kernel's file system. In addition, the abstraction allows flows to be programmed in the hardware using file I/O, which fits nicely into the existing emulation environment with few modifications. Unfortunately, the programming channel in out system is not compliant with commercial OpenFlow controllers since communication is not facilitated through TCP with SSL.

### 5.3 Linux Device Driver

A device driver acts as an interface between system-level software and the physical hardware data plane, such as a NIC or Graphics Processing Unit (GPU). Unlike userspace programs, device drivers can be dynamically loaded at run-time or during program execution using the modprobe utility [2]. The device driver allows system software developers to work at an abstract level without understanding the device's physical hardware and associated architecture. The kernel driver is the only piece of code that should interact directly with the hardware register interfaces to guarantee the correctness and atomic execution. There are three main types of device drivers: character, block, and network interfaces [9]. The virtual network accelerator design predominantly uses network drivers to interact with the Linux network stack. Thus, we will cover the operations of these types of interfaces exhaustively in the following sections.

### 5.3.1 Network Drivers and PCIe Support

In this system, network drivers are used to model the operation of a NIC. A network device driver creates an interface on the host machine that can be assigned an IP address, MAC address, and various packet processing options and protocols. The device driver will dictate how asynchronous events are handled, such as command-line utilities, packet receiving, and packet transmitting. The following initialization steps occur to set up a network device to transmit and receive packets over PCIe.

- Probe PCIe bus components for device ID, and function number. Allocate memory regions for each base address register configured by the hardware.

- Attach interrupts to PCIe hardware functions and provide associated event callbacks.

- Initialize network interface with name, MAC, IP, queue structures, and setup function callbacks for asynchronous events.

Allocate DMA memory address regions and allocate ring-buffers for transmit and receive descriptors.

The SR-IOV specification allows for a different device driver to be attached to each VF or PF. The device driver attached to the PF will enable SR-IOV capabilities and will receive messages through a character driver to manage the hardware data plane. The PF will be written to and read from similar to how a file operates, through a stream of bytes. Each VF will be attached to a network device driver to facilitate socket communication from the upper-level network stack. The network driver provides the necessary abstraction to integrate hardware into a network infrastructure that spans the OSI model. These mechanisms allow less software intervention during packet transfer from source to destination allowing a reduction of CPU utilization typically leading to an increase in performance.

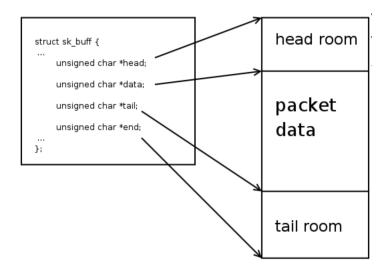

### 5.3.2 Packet Representation in the Linux Kernel