Dieses Dokument ist eine Zweitveröffentlichung (Postprint) / This is a self-archiving document (accepted version):

Manu Viswambharan Thayyil, Songhui Li, Niko Joram, Frank Ellinger

## WA 4-32 GHz SiGe Multi-Octave Power Amplifier With 20 dBm Peak Power, 18.6 dB Peak Gain and 156% Power Fractional Bandwidth

### Erstveröffentlichung in / First published in:

*IEEE Microwave and Wireless Components Letters.* 2019, 29(11), S. 745 - 748 [Zugriff am: 11.11.2021]. IEEE Xplore Digital Library. ISSN 1558-1764.

DOI: https://doi.org/10.1109/LMWC.2019.2942189

Diese Version ist verfügbar / This version is available on: https://nbn-resolving.org/urn:nbn:de:bsz:14-qucosa2-766128

# A 4-32 GHz SiGe Multi-Octave Power Amplifier with 20 dBm Peak Power, 18.6 dB Peak Gain and 156 % Power Fractional Bandwidth

Manu Viswambharan Thayyil, Songhui Li, Niko Joram and Frank Ellinger, Senior Member, IEEE

Abstract—This letter presents the design and characterization results of a multi-octave power amplifier fabricated in a 0.13 µm SiGe-BiCMOS technology. The single stage power amplifier is implemented as the stack of a cascode amplifier combining broadband input matching network with resistive feedback, and a common-base amplifier with base capacitive feedback. Measurement results show that the design delivers a peak saturated output power level of 20.2 dBm, with output 1 dB compression at 19.4 dBm. The measured 3 dB power bandwidth is from 4 GHz to 32 GHz, covering three octaves. The corresponding power fractional bandwidth is 156 %. The measured peak power added efficiency is 20.6 %, and peak small signal gain is 18.6 dB. The fabricated integrated circuit occupies an area of 0.71 mm<sup>2</sup>. To compare state-of-the-art multi-octave power amplifiers, the power amplifier figure of merit defined by the international technology roadmap for semiconductors is modified to include power fractional bandwidth and area. To the knowledge of the authors, the presented design achieves the highest figure of merit among multi-octave power amplifiers in a silicon based integrated circuit technology reported in literature.

*Index Terms*—Power amplifier, broadband matching networks, feedback, SiGe-BiCMOS technology, figure of merit.

#### I. INTRODUCTION

ANDWIDTH is an important performance parameter **B** along with output power, power added efficiency (PAE) and gain for power amplifiers (PA). Silicon based integrated system applications like positioning and localization radars, imaging systems, and communication transceivers have been instrumental in pushing both the maximum frequency and bandwidth of all components including PAs to microwave, millimeter wave and beyond. To address this demand, several wideband power amplifiers implementations are reported in literature. These include predominantly silicon germanium (SiGe) BiCMOS implementations [1]-[4], while CMOS implementations are catching up [5], [6]. Most PAs reporting a high power fractional bandwidth (PFBW) are based on the distributed amplifier (DA) topology [1], [4], [5], occupying large area, having low gains, often requiring pre-amplifiers when used in a system and having low PAE. Whereas PAs based on other topologies [2], [3], [6] have relatively lower PFBW than DA based PAs.

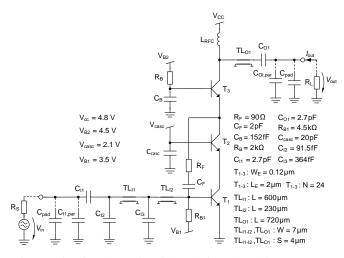

Fig. 1: Circuit schematic of the designed multi-octave PA .

A single stage multi-octave power amplifier (MOPA), completely covering the frequency bands  $K_u$  and K, which includes the 24 GHz ISM band and 28 GHz 5G frequency bands, and partially covering the UWB and  $K_a$  bands is presented in this letter. The MOPA uses a novel combination of resistive feedback to enable broadband input matching of low-ohmic, highly capacitive input impedances, and transistor stacking for high output power with better output transfer network efficiency across a wide frequency range. The design is optimized to maximize the PFBW and gain, and to minimize the occupied area, while maintaining an output power and PAE comparable to the state-of-the-art in these frequency ranges.

The circuit design of the single gain stage multi-octave PA, including the implementation of matching networks are discussed in Section II. Characterization results and comparison of results with the state-of-the-art are discussed in Section III. Section IV summarizes the letter, highlighting key features of the design and results.

#### II. DESIGN

The single stage MOPA shown in Fig. 1 is implemented using heterojunction bipolar transistors (HBTs) in a 0.13 µm SiGe-BiCMOS technology with with  $f_t / f_{max}$  of 250 GHz/340 GHz from IHP microelectronics. The design target output power level of 20 dBm corresponds to a peak-to-peak voltage swing  $V_{out,pp} \approx 6.3$  V on load resistance  $R_{\rm L} = 50 \,\Omega$ , calculated using  $P_{\rm out} = V_{\rm out,pp}^2/(8R_{\rm L})$ , for

Manuscript received March 15, 2019; revised July 15, 2019; accepted September 6, 2019. This work has received funding from the European Unions Horizon 2020 research and innovation programme under grant agreement No. 636286 (Lynceus2Market).(*Corresponding author : Manu V. Thayyil*)

The authors are with the Chair for Circuit Design and Network Theory, Technische Universität Dresden, 01069 Dresden, Germany (email: manu.thayyil@tu-dresden.de)

an output network transformation ratio of 1. For a single HBT used in this design, the collector-emitter breakdown voltage when the base is open amounts to  $V_{\rm BVCEO} \approx 1.7 \, {\rm V}$ . However, it can be seen from [7] that, when the base resistance is optimized to lower values, the corresponding breakdown voltage  $V_{\rm BVCER}$  is much higher, and close to the collectorbase breakdown voltage  $V_{\rm BVCBO}$  with open emitter. Using this approach along with technology process documentation, it is determined that base resistance values less than  $5 k\Omega$ , are required for  $V_{\text{BVCER}} > 3.5 \text{ V}$ . The base resistance values used in the design as shown in Fig. 1 are optimized as a trade-off between breakdown voltage and sensitivity to bias voltage variations. Now using  $V_{\text{out,pp}} = n(V_{\text{BVCER}} - V_{\text{knee}})$ , where  $V_{\rm knee} \approx 350 \,{\rm mV}$  is the knee voltage, the number of transistors in the stack is calculated as n = 2. This means that a stack of two HBTs, T<sub>2.3</sub> is sufficient to generate the required output power to be delivered directly into  $R_{\rm L}$ . The common base stage consisting of T<sub>3</sub>, base feedback capacitance  $C_{\rm B} \approx 152 \, {\rm fF}$  and resistance  $R_{\rm B} \approx 2 \, {\rm k}\Omega$  distributes  $V_{\rm out,pp}$ equally among the HBTs T<sub>2.3</sub> using the stacking principle described in [8]. The optimum load required to generate the maximum output power can then be obtained from the load line as  $R_{\text{opt}} = V_{\text{out,pp}} / I_{\text{out,pp}} = 6.3 \text{ V} / 129 \text{ mA} \approx 49 \Omega$ . To generate the target power with high gain, T<sub>1-3</sub> in Fig. 1 are dimensioned as 24 parallel HBTs with a total emitter area  $A_E = 24 \times 0.12 \,\mu{

m m} \times 2 \,\mu{

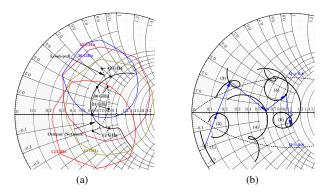

m m}$ , and biased near the maximum  $f_t$  current density at  $2 \text{ mA} / \mu \text{m}$ . Load-pull simulations are done over the frequency range to obtain the optimum load required to generate the maximum power as shown in Fig. 2(a). The impedance transformation network required to present the optimum load to the collector of  $T_3$  is implemented using the combination of the grounded coplanar waveguide (GCPW) transmission line TL<sub>01</sub> with characteristic impedance  $Z_0 = 50 \Omega$  and length 720 µm, the capacitance  $C_{01} \approx 2 \,\mathrm{pF}$ , which also functions as a dc block, and the equivalent shunt capacitance formed by the parasitics and pad capacitance  $C_{\rm O1,par} + C_{\rm pad} \approx 80\,{\rm fF}$ . The output impedance transformation network is optimized such that, across the frequency range of interest, the MOPA generates an output power within 2 dB of the maximum possible output power that can be generated at each frequency. The corresponding simulated impedance trajectory across the frequency range is shown in Fig. 2(a).

The large HBT emitter area used to generate the required output power results in a very low-ohmic and highly capacitive input impedance,  $\underline{Z}_{in} = R_{in} - jX_{in} \approx 1.8 - j9.5 \Omega$  at  $f_c = 24 \,\text{GHz}$  as shown in curve (1) of Fig. 2(b). The corresponding nodal quality factor  $Q_{in} = \frac{|X_{in}|}{R_{in}} = 5.3$ , the equivalent parallel resistance  $R_{p,in} = (1 + Q_{in}^2)Rs \approx 50 \Omega$ , and equivalent parallel capacitance of  $C_{p,in} = 674 \,\text{fF}$ . The Bode-Fano matching network bandwidth limit [9], for an  $|\underline{S}_{11}| = -10 \,\text{dB}$  and corresponding input reflection coefficient  $|\Gamma|_{\text{max}} = 0.32$ , can be then calculated as  $f_{\text{BW,limit}} \leq \frac{1}{2R_{p,in}C_{p,in}\ln\frac{1}{|\Gamma|}} \approx 12.3 \,\text{GHz}$ . The introduction of the negative feedback resistor  $R_{\text{F}}$  increases this limit by a factor of 80, making  $|\underline{Z}_{in}|$  predominantly resistive to  $\underline{Z}_{in,\text{fb}} \approx 7.3 \,\Omega$  as shown in curve (2) of Fig. 2(b). The

Fig. 2: (a) Optimum load at different frequencies obtained from load-pull simulations, 2 dB load-pull contours and the impedance looking into the output transformation network. (b) Shows the design trajectories for the input matching network.

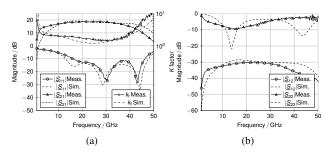

Fig. 3: Measured and simulated small signal parameters.

$R_{\rm F}$  required to obtain this  $\underline{Z}_{\rm in,fb}$  can be calculated at  $f_c$  as  $R_{\rm F} \approx (1 - \underline{a}_{\rm v}) \frac{R_{\rm p,in} \ \underline{Z}_{\rm in,fb}}{(R_{\rm p,in} - \underline{Z}_{\rm in,fb})} \approx 90 \,\Omega$ , where the voltage gain of the cascode stage  $\underline{a}_v$  has a magnitude  $|\underline{a}_v| \approx 10$ . The transformation of this  $Z_{in}$  to source impedance  $R_s = 50 \Omega$ is done using a two section matching network, confining the impedance transformation trajectory to a Q = 0.8 curve and the real axis, as shown in Fig. 2(b).  $Q = \frac{f_{\rm C}}{f_{\rm BW}} \approx 0.8$  is calculated using  $f_c = 24 \text{ GHz}$ , and small signal bandwidth  $f_{\rm BW} = 30 \, \text{GHz}$ . The impedance transformation trajectory in Fig. 2(b) from curve (2) through curves (3), (4) and (5) to  $R_{\rm s}$  is implemented using GCPW transmission lines TL<sub>11</sub> and TL<sub>I2</sub> with  $Z_0 = 50 \Omega$ , capacitors  $C_{I1} = 2.7 \text{ pF} \ C_{I2} = 91.5 \text{ fF}$ and  $C_{I3} = 364 \,\text{fF}$ . TL<sub>I1</sub> has a length of 600  $\mu$ m, and TL<sub>I2</sub> has a length of 230  $\mu$ m. The parasitic capacitance  $C_{I1,par}$  and  $C_{\text{pad}}$  are also included in the network. The MOPA is also unconditionally stable across the frequency range from post layout K-factor  $(K_f)$  simulations and stability circles.

#### III. CHARACTERIZATION

The inset of Fig. 4 shows the fabricated MOPA IC, occupying an area of  $845 \,\mu\text{m} \times 845 \,\mu\text{m} = 0.71 \,\text{mm}^2$  including pads. The bias voltages shown in Fig. 1 are used to set the operating point, and the corresponding bias current measured is 98 mA. S-parameters and large signal parameters as a function of frequency are characterized using a test setup mainly consisting of a R&S 67 GHz vector network analyzer (VNA) ZVA67. S-parameter measurements confirm that the small signal parameters including input matching and Final edited form was published in "IEEE Microwave and Wireless Components Letters. 2019, 29(11), S. 745 - 748. ISSN 1558-1764. https://doi.org/10.1109/LMWC.2019.2942189

| Ref. | $f_{ m u,3dB}$    | $PBW_{3dB}$       | PFBW             | $P_{\rm L,sat}$ | $P_{\rm L,OP1dB}$ | Peak Gain | Peak PAE | Area               | $FoM_{ m MOPA}{}^{ m a}$ | Tech.        |

|------|-------------------|-------------------|------------------|-----------------|-------------------|-----------|----------|--------------------|--------------------------|--------------|

|      | (GHz)             | (GHz)             | (%)              | (dBm)           | (dBm)             | (dB)      | (%)      | (mm <sup>2</sup> ) | $(W  GHz^2/mm^2)$        |              |

| [6]  | 33                | 15.0              | 59               | 19.5            | 16                | 15.2      | 10.2     | 0.86               | 224                      | 0.18 µm CMOS |

| [1]  | 40                | 30.0              | 120              | 15.4            | 11.4              | 17.1      | 10       | 2.00               | 171                      | 0.18 µm SiGe |

| [2]  | 35                | 10.7              | 36               | 11.1            | 9.6               | 16.3      | 55.9     | 0.72               | 189                      | 0.18 µm SiGe |

| [3]  | 18                | 13.5              | 120              | 23.7            | 19.5              | 15.7      | 31.9     | 0.73               | 1476                     | 0.13 µm SiGe |

| [5]  | 23.8 <sup>b</sup> | 22.8 <sup>b</sup> | 184 <sup>b</sup> | 16.7            | 14.5              | 11.9      | 10       | 1.7                | 44 <sup>b</sup>          | 0.18 µm CMOS |

| [4]  | 40                | 28.0              | 108              | 21.5            | 19.8              | 13.9      | 20.1     | 1.19               | 1009                     | 0.13 µm SiGe |

| This | 32                | 29.0              | 156              | 20.2            | 19.4              | 18.6      | 20.6     | 0.71               | 3423                     | 0.13 µm SiGe |

TABLE I: Comparison with state-of-the-art multi-octave power amplifiers.

<sup>a</sup>  $FoM_{MOPA} = P_{sat} \cdot G \cdot PAE \cdot f_{u,3dB}^2 \cdot PFBW / Area.$  <sup>b</sup> Power bandwidth not reported, small-signal bandwidth used.

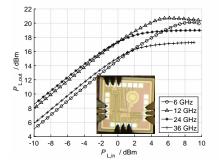

Fig. 4: Measured output power as function of input power levels from  $-10 \,d\text{Bm}$  to  $10 \,d\text{Bm}$  at different frequencies. The fabricated IC occupying an area of  $0.71 \,\text{mm}^2$  is shown in inset.

gain are in good agreement with simulations as shown in Fig. 3. Also the three characteristic dips due to multi-band input matching network can be clearly seen in the  $|\underline{S}_{11}|$  plots in Fig. 3(a). Small signal peak gain is measured as 18.6 dB around 24.6 GHz, and the 3 dB bandwidth is measured as 31.9 GHz from the frequency range of 6.6 GHz to 38.5 GHz.

Input power is swept from  $-10 \,\text{dBm}$  to  $10 \,\text{dBm}$  in the 2 GHz to 42 GHz frequency range, and the measured output power as a function of input power for frequencies 6 GHz, 12 GHz, 24 GHz and 36 GHz are shown in Fig. 4. The corresponding

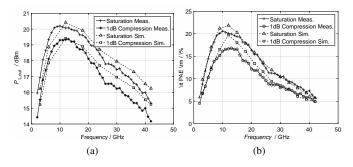

Fig. 5: Comparison of large signal measurements with simulation. (a) Output power. (b) PAE.

saturated output power level P<sub>L,sat</sub> along with output 1 dB compression point  $P_{\text{L,OP1dB}}$  are plotted in Fig. 5(a), and the measured PAE is plotted in Fig. 5(b). It can be seen from Fig. 5(a) that the maximum  $P_{L,sat} = 20.2 \text{ dBm}$  and  $P_{L,1dB} = 19.4 \text{ dBm}$ are obtained at a frequency of 10 GHz, and the small-signal gain at 10 GHz is 17 dB from Fig. 3(a). At mid-band, near 24 GHz,  $P_{L,sat} = 18.4 \text{ dBm}$  and  $P_{L,OP1dB} = 17.1 \text{ dBm}$ . Also from the data in 5(a), the 3 dB power bandwidth is measured as 29 GHz from the frequency range of 3 GHz to 32 GHz. The measured maximum PAE of the design is 20.6% at 10 GHz, 13.3% at 24 GHz and the minimum of 9.8% at the 3 dB frequency of 32 GHz. The power fractional bandwidth of a PA [6] is defined as,  $PFBW = (PBW_{3dB} / f_c) \times 100 \%$ , where  $f_c = f_{u,3dB} - (PBW_{3dB} / 2)$ , and  $f_{u,3dB}$  is the 3 dB upper cut off frequency. From Fig. 5(a), it can be seen that PFBW = 156% for the presented MOPA.

Table I shows the comparison with similar state-of-the-art PAs. It can be clearly seen that this work has the best *PFBW*, peak gain and lowest area. A modified international technology roadmap for semiconductors (ITRS) power amplifier figure of merit (FoM) is used to compare PAs in [6]. Here we are incorporating *PFBW* and area into the FoM for better comparison of multi-octave power amplifiers as shown in the footnote <sup>a</sup> of Table I. The  $FOM_{MOPA} \approx 407 \text{ W} (\text{GHz/mm})^2$  is the highest when compared to other PAs in Table I.

#### IV. CONCLUSION

A single stage integrated multi-octave power amplifier is implemented in a  $0.13 \,\mu\text{m}$  SiGe-BiCMOS technology using a novel combination of resistive feedback to enable broadband input matching of low-ohmic, highly capacitive input impedances, and transistor stacking for high output power with better output transfer network efficiency across a wide frequency range. Measurement results show a maximum saturated output power level of 20.2 dBm, a peak PAE of 20.6% and a 3 dB power upper cut-off frequency of 32 GHz. To the knowledge of the authors, this design has one of the best reported  $FOM_{\text{MOPA}}$ , a modified ITRS figure of merit which includes the measured power fractional bandwidth of 156%, peak gain of 18.6 dB and area of 0.71 mm<sup>2</sup>.

#### References

- K. Kim and C. Nguyen, "A concurrent *Ku/K/Ka* tri-band distributed power amplifier with negative-resistance active notch using SiGe BiC-MOS process," *IEEE Trans. Microw. Theory Techn.*, vol. 62, no. 1, pp. 125–136, Jan 2014.

- [2] K. Ma, T. B. Kumar, and K. S. Yeo, "A reconfigurable K/Ka band power amplifier with high PAE in 0.18 μm SiGe BiCMOS for multiband applications," *IEEE Trans. Microw. Theory Techn.*, vol. 63, no. 12, pp. 4395–4405, Dec 2015.

- [3] E. Kerherve, N. Demirel, A. Ghiotto, A. Larie, N. Deltimple, J. Pham, Y. Mancuso, and P. Garrec, "A broadband 4.5 - 15.5 GHz SiGe power amplifier with 25.5 dBm peak saturated output power and 28.7% maximum PAE," *IEEE Trans. Microw. Theory Techn.*, vol. 63, no. 5, pp. 1621–1632, May 2015.

- [4] S. Li, D. Fritsche, C. Carta, and F. Ellinger, "Design and characterization of a 12 - 40 GHz power amplifier in SiGe technology," in 2018 IEEE Topical Conf. RF/Microw. Power Ampl. Radio Wireless Appl. (PAWR) Dig. Tech. Papers, Jan 2018, pp. 23–25.

- [5] Y. Zhang and K. Ma, "A 2 22 GHz CMOS distributed power amplifier with combined artificial transmission lines," *IEEE Microw. Wireless Compon. Lett.*, vol. 27, no. 12, pp. 1122–1124, Dec 2017.

- [6] C. Kuo, H. Chiou, and H. Chung, "An 18 to 33 GHz fully-integrated darlington power amplifier with Guanella-type transmission-line transformers in 0.18 μm CMOS technology," *IEEE Microw. Wireless Compon. Lett.*, vol. 23, no. 12, pp. 668–670, Dec 2013.

- [7] T. S. D. Cheung and J. R. Long, "A 21-26 GHz SiGe bipolar power amplifier MMIC," *IEEE J. Solid-State Circuits*, vol. 40, no. 12, pp. 2583– 2597, Dec 2005.

- [8] D. Fritsche, R. Wolf, and F. Ellinger, "Analysis and design of a stacked power amplifier with very high bandwidth," *IEEE Trans. Microw. Theory Techn.*, vol. 60, no. 10, pp. 3223–3231, Oct 2012.

- [9] R. M. Fano, "Theoretical limitations on the broadband matching of arbitrary impedances," J. Franklin Institute, vol. 249, no. 1, pp. 57–83, 1950.