# INTEGRATION OF ALIGNED ARRAYS OF SINGLE-WALLED CARBON NANOTUBES IN ELECTRONIC DEVICES

$\mathbf{B}\mathbf{Y}$

# XINNING HO

# DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Materials Science and Engineering in the Graduate College of the University of Illinois at Urbana-Champaign, 2011

# Urbana, Illinois

Doctoral Committee:

Professor John A. Rogers, Chair and Director of Research Professor Moonsub Shim Professor John R. Abelson Assistant Professor Xiuling Li Assistant Professor Eric Pop

### ABSTRACT

Aligned arrays of single-walled carbon nanotubes (SWNTs) are an attractive format for macroelectronics and RF analog electronics with exceptional electrical, mechanical and optical properties. Unlike isolated SWNT, the presence of many SWNTs in the aligned arrays increases the current output and statistical averaging in many SWNTs is expected to reduce the device to device variations. The SWNTs in aligned arrays do not intersect one another, unlike in networks of SWNTs. Hence, tube/tube contacts, which limit the transport in SWNT networks due to tunneling barriers or electrostatic screening at the contacts to prevent effective gate modulation at those specific points, are absent.

Nonetheless, challenges still remain for these aligned arrays of SWNTs before their successful integration into electronic devices for large scale commercial use. The main challenges include (1) selective elimination of m-SWNTs, (2) increasing the density of SWNTs, (3) achieving electronic uniformity across devices fabricated and (4) understanding their mode of operation and the role of contacts in their operation.

In this dissertation, I present a study that aims to tackle the 3<sup>rd</sup> and 4<sup>th</sup> challenges aforementioned. We integrated these arrays of SWNT thin films into field effect transistors to study the electronic uniformity of the devices. We examined the effect of variation in density and diameter distributions of the aligned arrays of SWNTs on the variation in the electrical performance of the transistors. We also analyzed the properties of the contacts at the SWNT/metal interface. We found Pd to be a good Ohmic contact and Ca to be a Schottky contact to the aligned arrays of SWNTs and went on to fabricate Schottky diodes. Using these Schottky diodes, we demonstrated light emitting diodes with aligned arrays of SWNTs which could be used in novel applications that require solid state and nano-scale infra-red emitters. Work done to selectively eliminate m-SWNTs (1<sup>st</sup> challenge) via selective laser ablation is also archived in this dissertation.

These results represent important steps in understanding the device performance of transistors and Schottky diodes based on aligned arrays of SWNTs; which may have a large impact in large area RF analog electronics.

# ACKNOWLEDGEMENTS

I would like to express my deep gratitude to my thesis advisor, Prof. John A. Rogers who made this work possible. It is my great fortune to be able to learn under his tutorship. He teaches me how to think analytically in the face of difficult research problems and provides the resources for me to learn and benefit from other top researchers in the field. Prof. Rogers' contribution to this work and his support and guidance for me throughout my PhD program is beyond what words can describe.

I am deeply indebted to Prof. Slava Rotkin at Lehigh University, Dr. Jana Zaumseil at Argonne National Laboratory, Shuaib Salamat and Prof. Muhammad Alam at Purdue University and Prof. Subodh Mhaisalkar at Singapore Nanyang Technological University for extensive discussions and collaborations. I would like to thank Prof. Moonsub Shim, Prof. John Abelson, Prof. Eric Pop and Prof. Xiuling Li for serving on my committee and providing insightful suggestions.

It is my great pleasure to be able to work in a conducive research environment created at Materials Research Laboratory, with generous help from Prof. Coskun Kocabas, Dr. Qing Cao, Dr. Xiaoyu Zhang, Dr. Taner Ozel, Dr. Ahmad Islam, Simon Dunham, Lina Ye, Frank Du, Xu Xie, Sakulsuk Unarunotai, Tony Banks and Kevin Colravy. Finally I want to thank my family and friends for their support in my work.

This work was carried out in part in the Frederick Seitz Materials Research Laboratory Central Facilities, University of Illinois, which are partially supported by the U.S. Department of Energy under grants DE-FG02-07ER46453 and DEFG02-07ER46471. I acknowledge fellowship support from ASTAR (Singapore).

# **TABLE OF CONTENTS**

| CHAP | TER 1: Introduction                                           |    |

|------|---------------------------------------------------------------|----|

| 1.1  | Introduction to Carbon Nanotubes                              | 1  |

| 1.2  | Alignment in Aligned Arrays of Single-walled Carbon Nanotubes | 2  |

| 1.3  | Nanotube Field Effect Transistors and Diodes                  | 3  |

| 1.4  | Construction of this Thesis                                   | 5  |

| 1.5  | References                                                    | 7  |

| 1.6  | Figures                                                       | 10 |

CHAPTER 2: Statistical Analysis Of The Electrical Performance Variability In Transistors That Use Aligned Arrays Of Single Walled Carbon Nanotubes

| 2.1 | Introduction                                       | 13 |

|-----|----------------------------------------------------|----|

| 2.2 | Methods for Fabricating Single and Array SWNT FETs | 15 |

| 2.3 | Characteristics of Single SWNT FETs                | 15 |

| 2.4 | Statistics of Array SWNT FETs                      | 20 |

| 2.5 | Conclusions                                        | 25 |

| 2.6 | References                                         | 25 |

| 2.7 | Figures                                            | 28 |

CHAPTER 3: Intrinsic Performance Variability In Aligned-Array Carbon Nanotube Field Effect Transistors

| 3.1 | Introduction                                                           | .38 |

|-----|------------------------------------------------------------------------|-----|

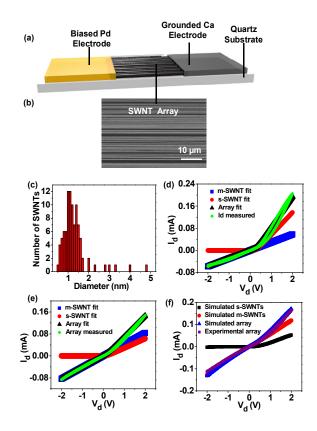

| 3.2 | Fabrication of Nanotube Arrays and Devices                             | .39 |

| 3.3 | Modeling of the Effect of Diameter Distribution on I-V Characteristics | .41 |

| 3.4 | Conclusion                                                             | 45  |

| 3.5 | References                                                             | .46 |

| 3.6 | Figures                                                                | 49  |

CHAPTER 4: Scaling Properties In Transistors That Use Aligned Arrays Of Single Walled Carbon Nanotubes

| 4.1 | Introduction            | 53 |

|-----|-------------------------|----|

| 4.2 | Methods                 | 54 |

| 4.3 | Results and Discussions | 54 |

| 4.4 | Conclusions             | 59 |

| 4.5 | References              | 59 |

| 4.6 | Figures                 | 62 |

CHAPTER 5: Electroluminescence From Electrolyte-Gated Carbon Nanotube Field-Effect Transistors

| 5.1 | Introduction            | 67 |

|-----|-------------------------|----|

| 5.2 | Methods                 | 70 |

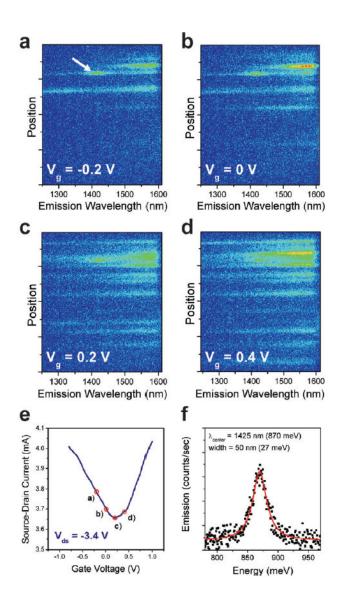

| 5.3 | Results and Discussions | 71 |

| 5.4 | Conclusions             | 78 |

| 5.5 | References              | 79 |

| 5.6 | Figures                 |    |

CHAPTER 6: Complementary Theoretical And Experimental Study Of Schottky Diodes That Use Aligned Arrays Of Single Walled Carbon Nanotubes

| 6.1 | Introduction            | .88 |

|-----|-------------------------|-----|

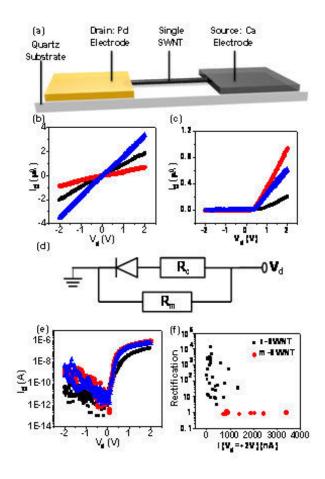

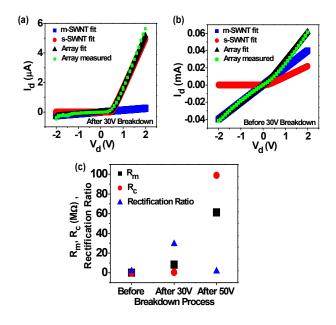

| 6.2 | Results and Discussions | 89  |

| 6.3 | Conclusions             | .93 |

| 6.4 | References              | .94 |

| 6.5 | Figures                 | .97 |

CHAPTER 7: Electroluminescence From Schottky Diodes That Use Aligned Arrays Of Single Walled Carbon Nanotubes

| 7.1 | Introduction | 100 |

|-----|--------------|-----|

|-----|--------------|-----|

| 7.2 | Methods                 |     |

|-----|-------------------------|-----|

| 7.3 | Results and Discussions | 102 |

| 7.4 | Conclusions             | 105 |

| 7.5 | References              |     |

| 7.6 | Figures                 |     |

CHAPTER 8: Selective Elimination Of Metallic Single Walled Carbon Nanotubes Via Selective Laser Ablation

| 8.1 | Introduction            | 113 |

|-----|-------------------------|-----|

|     | Methods                 |     |

| 8.3 | Results and Discussions | 116 |

| 8.4 | Conclusions             | 117 |

| 8.5 | References              | 117 |

| 8.6 | Figures                 |     |

# CHAPTER 9: Conclusions And Outlook

| 9.1 | Conclusions and Outlook | 125 |

|-----|-------------------------|-----|

| 9.2 | References              | 126 |

### **CHAPTER 1:**

# **INTRODUCTION**

The main objective of my doctoral research is to study the integration of thin films of aligned arrays of single-walled carbon nanotubes (SWNT) into field effect transistors and diodes. We examined the effect of variation in density and diameter distributions of the aligned arrays of SWNTs on the scatter in the electrical performance of the transistors based on these thin films and analyzed the properties of the contacts at the SWNT/metal interface in these transistors. We found Pd to be a good Ohmic contact and Ca to be a Schottky contact to the aligned arrays of SWNTs and went on to fabricate Schottky diodes. We studied the theoretical and experimental aspects of these Schottky diodes based on aligned arrays of SWNTs and found that a simple physical model, taking into account the basic physics of current rectification, can adequately describe the devices. Using these Schottky diodes, we demonstrated light emitting diodes which could be used in novel applications that require solid state and nano-scale infra-red emitters.

## **1.1 Introduction to Carbon Nanotubes**

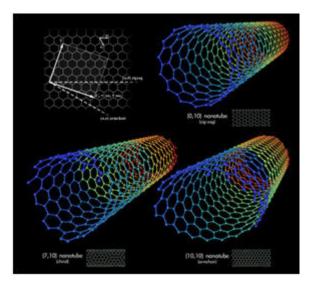

SWNTs can be perceived as rolled-up cylinders of graphene sheets. The way a graphene sheet is rolled up is represented by a pair of indices (n,m), as shown in Figure 1.1. This pair of indices determines the chirality and diameter of a SWNT which in turn determines the bandgap as well as the mobility of the SWNT [1,2]. SWNTs are an interesting class of materials to study because of their exceptional electrical [1,2] and optical properties [3]. Semiconducting SWNTs have been considered for use as the active channels in field effect transistors and diodes due to their high mobility (up to  $10,000 \text{ cm}^2/\text{Vs}$ )[2] while metallic SWNTs, for use as transparent metal contacts because of their low resistivity [4-6], optical transparency and high current carrying capability (up to  $10^9 \text{A/cm}^2$ ) [7].

Two promising areas of potential application are flexible macroelectronics and RF analog electronics. Flexible macroelectronics, involving large scale electronics beyond the size of a semiconductor wafer, demands materials and processes to be cost effective, flexible and portable. Applications include rollable displays, printable solar cells or other novel applications that require large scale electronics on non-conventional substrates. SWNTs with their very high mobility [2], mechanical flexibility [8-10] and the ability to deposit solution-based SWNTs directly on polymeric substrates or transfer printed from conventional substrates to other forms of substrates make them attractive for flexible macroelectronics applications. Aligned arrays of SWNTs, which have low intrinsic capacitance and high linearity, have been considered for use in RF analog electronics. Transistors based on aligned arrays of SWNTs have been demonstrated to be able to operate up to GHz frequency with further improvements possible via device optimization, increasing the density of the SWNTs and selectively eliminating the m-SWNTs [11-14].

Transistors based on a single semiconducting SWNT have been demonstrated. They are found to display high mobility (up to  $10,000 \text{cm}^2/\text{Vs}$ ) [2], high transconductance (up to  $3\text{mS}/\mu\text{m}$ ) [15] and high on/off ratio (up to  $\sim 10^6$ ) [15]. However, these single SWNTs are difficult to integrate into devices as one needs to know precisely where the single SWNTs are in order to deposit contacts on them. Furthermore, these single SWNTs have different chirality, resulting in non uniformity of electrical performance in devices fabricated. Finally, transistors based on single SWNTs have low current output. The obvious solution of which is to grow thin films of SWNTs.

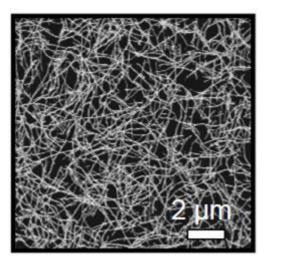

Thin films of SWNTs can be grown in two different formats: random network or aligned arrays. Scanning electron micrographs of random network of SWNTs and aligned arrays of SWNTs are shown in figure 1.2a and 1.2b respectively. As evident in figure 1.2, there are many tube-tube contacts in the random network which are absent in the aligned arrays. These tube/tube contacts limit the transport in SWNT networks due to tunneling barriers or electrostatic screening at the contacts to prevent effective gate modulation at those specific points [16]. Hence, aligned arrays of SWNTs display superior electrical performance relative to random network of SWNTs, which is essential for RF applications [17,18].

# 1.2 Alignment in Aligned Arrays of Single-walled Carbon Nanotubes

Carbon nanotubes can be synthesized via arc-discharge [19], laser ablation [20] or chemical vapor deposition (CVD). The first two methods of synthesis mentioned above are difficult to integrate into devices because the alignment and location of the nanotubes cannot be well controlled. On the other hand, CVD growth of carbon nanotube films provides excellent control over alignment and location of nanotubes.

The driving force for alignment in CVD can arise from electrical fields [21,22], laminar flow of feeding gas [23-25] or anisotropic interactions between SWNTs and single crystalline substrates [26-28]. Electric fields induce torques on growing SWNTs to align them [21,22] while laminar flow of the feed gas in CVD growth of SWNTs aligns them [23-25]. SWNTs grown on certain single crystalline substrates (e.g. sapphire and quartz) interact anisotropically, resulting in aligned arrays of SWNTs. In one study, the authors present combined theoretical and experimental studies of alignment of SWNTs on different orientations of quartz [28]. They find that there is an angle dependent van der Waals interaction between the SWNTs and substrate and SWNTs preferentially grow in the directions that minimize the Lennard-Jones potential energy (figure 1.3). These directions correspond to the directions of molecular scale topological grooves on the substrate. They also find that while surface roughness and any small surface relief are not crucial, the crystalline quality of the surface is extremely important. Hence, aligned arrays of SWNTs can be reproducibly grown with very high degrees of alignment on single crystalline substrates.

### **1.3 Nanotube Field Effect Transistors and Diodes**

## **1.3.1 Nanotube Field Effect Transistors**

After the formation of SWNT thin films, transistors or diodes can be fabricated. Single semiconducting-SWNT transistors have been examined and found to be Schottky transistors if a Schottky barrier exits between small diameter SWNTs and the metal electrode [28-32]. On the other hand, ohmic contacts [33,34] have been formed when palladium electrodes are contacted to s-SWNTs which have larger diameters. As current output from a single SWNT transistor is very small, thin films of SWNTs are essential to increase the current output. Thin films of SWNTs can also potentially decrease the device to device variations present in single tube transistors via statistical averaging. Studies have shown that despite the high mobility of a transistor made from a single semiconducting SWNT (up to 10,000cm<sup>2</sup>/Vs) [2], a transistor made from a network of SWNTs has a significantly lower mobility (~80cm<sup>2</sup>/Vs) [35]. This has been attributed to the tube-tube junction resistance and the screening effect between tubes which limit the charge transport in the network of tubes. On the other hand, transistors which active conducting channel is aligned arrays of SWNTs are found to retain the high mobility as in a single SWNT transistor.

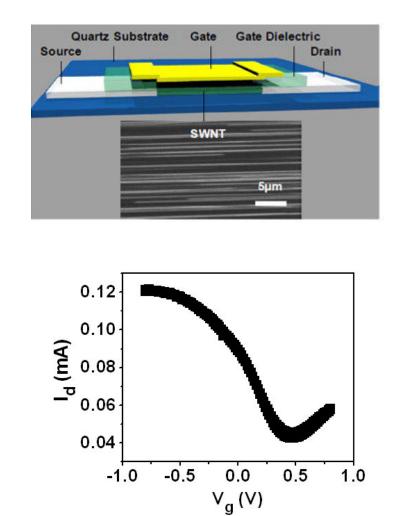

Figure 1.4a shows the schematic illustration of a top gated field effect transistor which active conducting channel is aligned arrays of SWNTs. Typical source and drain electrodes used are high work function metals, palladium or gold. Hafnium dioxide is deposited to form the dielectric between the gate electrode and SWNT array. A typical transfer curve from a transistor with palladium source and drain electrodes is shown in figure 1.4b. The transistor is predominantly p-type behaving as the Fermi level of high work function metal electrodes used is closer to the valence band. By applying a negative gate bias, the conduction and valence bands are bent upwards. Thus, the tunneling barrier between the palladium source and the valence band is narrowed, enabling holes to tunnel through the Schottky barrier easily. As the holes start to accumulate in the SWNTs, it becomes increasingly difficult for the holes to tunnel into the SWNTs. Hence, the increase in current with gate bias decreases and eventually saturates.

## 1.3.2 Nanotube Diodes

Besides nanotube transistors, nanotube diodes have been fabricated and examined. Two types of SWNT diodes have been studied; namely p-n junction diodes [36-38] and Schottky diodes [39]. P-n junction diodes can be formed by various means.

A commonly used method is electrostatic doping [36]. This is achieved by using a split-gate geometry. One part of the SWNT is gated p type while the other part is gated n type. The area between these two parts of the SWNT which is not gated forms an intrinsic region. This results in a p-i-n diode which does not suffer from severe reverse leakage. Another technique to form a p-n diode is via chemical doping [38]. One side of the junction is doped by a p-type dopant, tetracyanoquinodimethane (TCNQ) while the other side is doped by a n-type dopant, polyethylenimine (PEI).

The Schottky barrier formed at the SWNT-metal electrode interface is determined by both the diameter of the SWNT (which determines the bandgap of the SWNT) and the work function of the metal electrode used. Aluminum and titanium have been found to form Schottky contacts with SWNTs and have been used in Schottky diodes [39]. Palladium or gold is usually used to form an Ohmic contact for the other electrode in the diode.

### **1.4** Construction of this Thesis

Chapter 1 provides the outline of the thesis and provides background information about SWNTs and thin film type electronics.

Chapter 2 presents the statistical analysis of the electrical performance variability in transistors that use aligned arrays of single walled carbon nanotubes. We find that when we increase the number of SWNTs in a transistor with aligned arrays of SWNTs, the scatter in the on current, maximum transconductance, threshold voltage and off current of the devices do not decrease as rapidly as we expect based on statistical averaging. This is because of (1) the variation in the number of SWNTs in the transistors fabricated with the aligned arrays of SWNTs and (2) the different statistical distributions of diameter for different transistors having the same channel width.

Chapter 3 reports the intrinsic performance variability in aligned array SWNT field effect transistors. Using measured diameter distributions, detailed numerical simulations are performed to demonstrate that the diameter distribution of SWNTs in field effect transistors using aligned array of SWNTs plays a dominant role in the fluctuation of the electrical performance of the device at short channel length. This fluctuation in electrical performance ranges from the fluctuation in on current to that in device modulation.

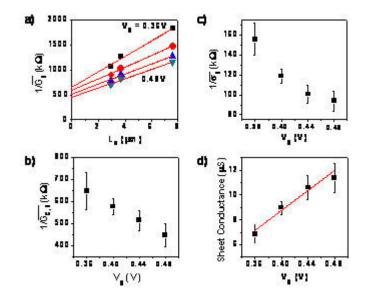

Chapter 4 reports scaling properties in transistors that use aligned arrays of single walled carbon nanotubes. Using the transmission line model, the dependence of device properties on channel length are studied, to reveal the role of contact and channel resistance in the operation. Two systems are examined; one with palladium electrodes and the other with gold electrodes.

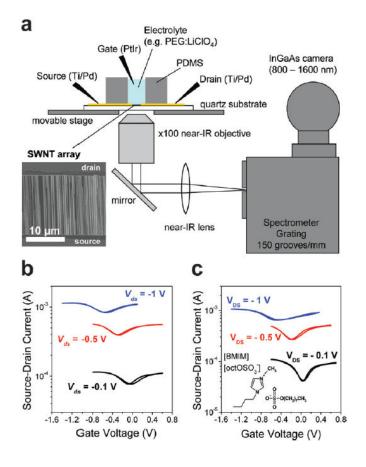

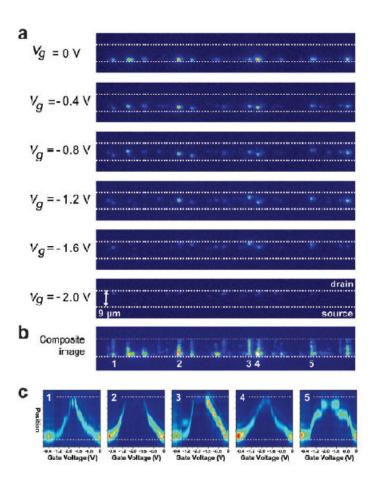

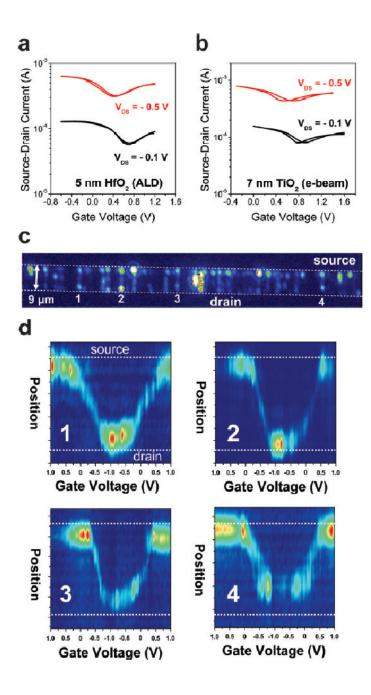

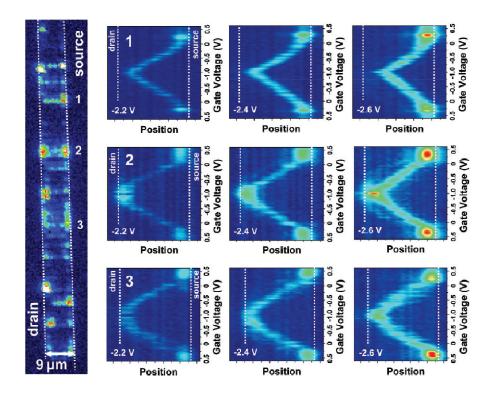

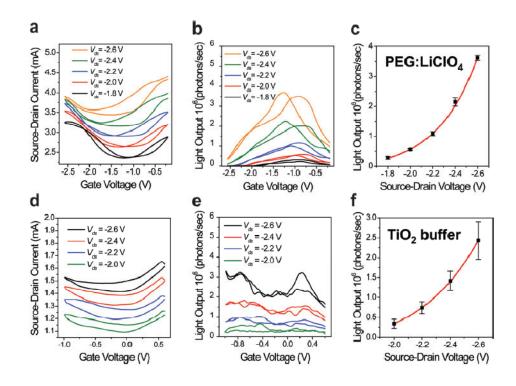

Chapter 5 demonstrates near-infrared electroluminescence from ambipolar, electrolyte-gated arrays of SWNTs. Numerous emission spots corresponding to individual SWNTs in the array are observed. When the electron and hole accumulation zones determined by the applied gate and source-drain voltages meet, these spots will emit light. The movement of emission spots with gate voltage yields information about the relative band gaps, contact resistance, defects, and interaction between carbon nanotubes within the array.

Chapter 6 presents theoretical and experimental studies of Schottky diodes that use aligned arrays of single walled carbon nanotubes. A simple physical model, taking into account the basic physics of current rectification, can adequately describe both the single-tube and array devices.

Chapter 7 demonstrates light emitting Schottky diodes based on aligned arrays of SWNTs. Electroluminescence was observed from Schottky-diode structure based on Ca and Pd asymmetric contacts. Light emission occurs spatially near the Ca/Al contact under forward biased condition. Both the current and the emission intensity increases linearly with the voltage beyond a certain threshold voltage, but the emission onset is higher. The spectral peaks observed are broad with the FWHM ranging from 80meV to 120meV. Further understanding of the causes for differences in threshold voltage for current and light emission and peak broadening is expected to be achieved through ongoing modeling. The light emission is mainly due to electron hole recombination near the Schottky contact, while impact excitation and black body radiation (BBR) may be the causes of light emission at higher voltages.

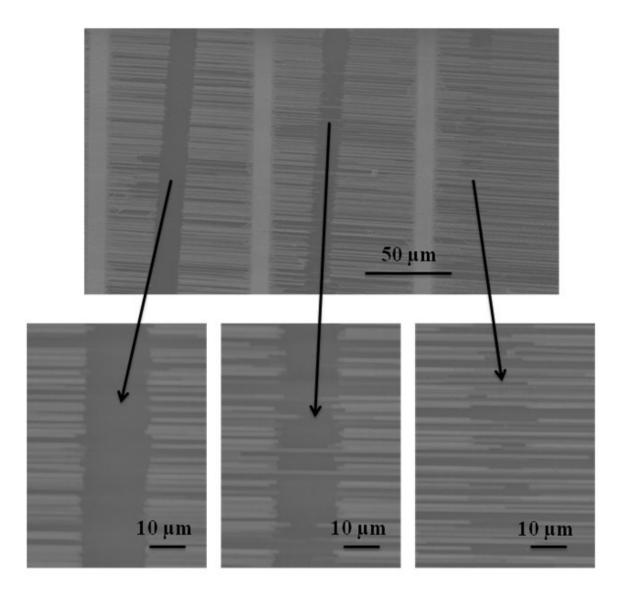

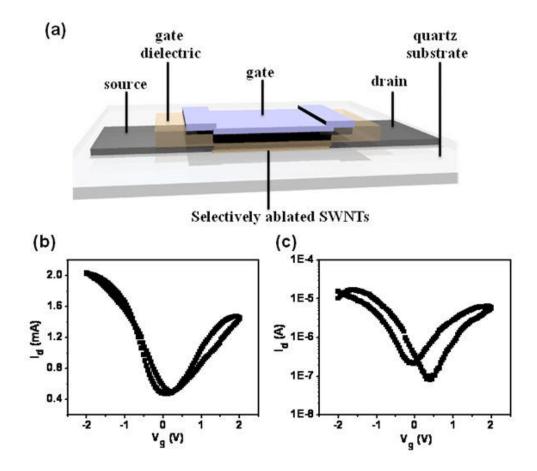

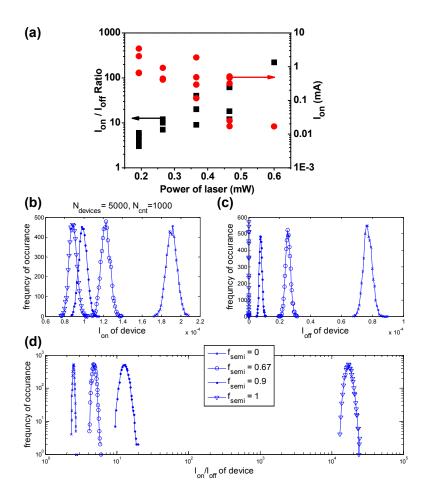

Chapter 8 archives work done to selectively remove m-SWNTs via laser ablation. This is very challenging because of the varying diameter distribution of SWNTs across the substrate which results in inconsistent electrical performance of transistors based on selectively ablated SWNTs. In addition, to achieve transistors with very high  $I_{on} / I_{off}$  ratio, very small proportion of m-SWNTs are allowed to be present. This is very difficult to achieve as not all m-SWNTs absorb the same wavelength of light very effectively. Some s-SWNTs also absorb at the same wavelength of light as certain m-SWNTs, which results in undesired ablation and / or degradation of s-SWNTs too.

Chapter 9 summarizes the results of our studies and discusses possible future work in this field.

#### 1.5 References

1. P. Avouris, Z. Chen, and V. Perebeinos, *Nature Nanotech.*, 2, 605 (2007).

2. X. Zhou, J-Y Park, S. Huang, J. Liu and P.L. McEuen, *Phys. Rev. Lett.*, 95, 146805 (2005).

3. P. Avouris, M. Freitag, and V. Perebeinos, *Nature Photonics*, 2, 341 (2008).

H. Cho, K.H. Koo, P. Kapur and K.C. Saraswat, *IEEE Electronic Device Letters*, 29, 122 (2008).

5. B.M. Quinn and S.G. Lemay, Adv. Mater., 18, 855 (2006).

6. C.T. White and T.N. Todorov, *Nature*, 393, 240 (1998).

- 7. C.L. Kane, Z. Yao and C. Dekker, *Phys. Rev. Lett.* 84, 2941 (2000).

- 8. R.S. Ruoff, D. Qian and W.K. Liu, *C.R. Physique*, 4, 993 (2003).

- 9. M-F. Yu, M.J. Dyer and R.S. Ruoff, J. Appl. Phy., 89, 4554 (2001).

- 10. S. Iijima, C. Brabec, A. Maiti and J. Bernholc, J. Chem. Phys., 104,2089 (1996).

11. C. Kocabas, S. Dunham, Q. Cao, K. Cimino, X. Ho, H-S Kim, D. Dawson, J. Payne, M. Stuenkel, H. Zhang, T. Banks, M. Feng, S.V. Rotkin and J.A. Rogers, *Nano Lett.* 9, 1937 (2009).

12. C. Kocabas, H-S. Kim, T. Banks, J.A. Rogers, A.A. Pesetski, J.E.Baumgardner, S.V. Krishnaswamy and H. Zhang, *Proc. Natl. Acad. Sci.*, 105, 1405 (2008).

13. P.J. Burke, Solid State Electronics, 48, 1981 (2004).

14. P.J. Burke, *IEEE Trans. Nanotech.*, 2, 55 (2003).

A. Javey, H. Kim, M. Brink, Q. Wang, A. Ural, J. Guo, P. McIntyre, P. McEuen,

M. Lundstrom and H. Dai, *Nat. Mater.*, 1, 241 (2002).

16. Q. Cao, M. Xia, C. Kocabas, M. Shim, J.A. Rogers and S.V. Rotkin, *Appl. Phy. Lett.*, 90, 023516 (2007).

- 17. Q. Cao and J.A. Rogers, *Adv. Mater.*, 20, 29 (2008).

- 18. Q. Cao and J.A. Rogers, *Nano Research*, 1, 259 (2008).

19. S. Iijima and T. Ichihashi, *Nature*, 363, 603 (1993).

20. A.G. Rinzler, J. Liu, H. Dai, P. Nikolaev, C.B. Huffman, F.J. Rodriguez-Macias, P.J. Boul, A.H. Lu, D. Heymann, D.T. Colbert, R.S. Lee, J.E. Fischer, A.M. Rao, P.C. Eklund and R.E. Smalley, *Appl. Phys. A*, 67, 29 (1998).

21. Y. Zhang, A. Chang, J. Cao, Q. Wang, W. Kim, Y. Li, N. Morris, E. Yenilmez, J. Kong and H. Dai, *Appl. Phys. Lett.*, 79, 3155 (2001).

22. E. Joselevich and C.M. Lieber, *Nano Lett.*, 2, 1137 (2002).

23. S.M. Huang, M. Woodson, R. Smalley and J. Liu, Nano Lett., 4, 1025 (2004).

24. S.M. Huang, X.Y. Cai and J. Liu, J. Am. Chem. Soc., 125, 5636 (2003).

25. Z. Jin, H. Chu, J. Wang, J. Hong, W. Tan and Y. Li, Nano Lett., 7, 2073 (2007).

26. J. Xiao, S. Dunham, P. Liu, Y. Zhang, C. Kocabas, L. Moh, Y. Huang, K-C. Hwang, C. Lu, W. Huang and J.A. Rogers, *Nano Lett.*, 9, 4311 (2009).

27. S. Han, X.L. Liu and C.W. Zhou, J. Am. Chem. Soc., 127, 5294 (2005).

28. C. Kocabas, S-H Hur, A. Gaur, M. Meitl, M. Shim and J.A. Rogers, *Small*, 1, 1110 (2005).

29. S.J. Wind, J. Appenzeller, and P. Avouris, *Phys. Rev. Lett.* 91, 58301 (2003).

30. J. Appenzeller, J. Knoch, V. Derycke, R. Martel, S. Wind and P. Avouris, *Phys. Rev. Lett.* 89, 126801 (2002).

31. S. Heinze, J. Tersoff, R. Martel, V. Derycke, J. Appenzeller and P. Avouris, *Phys. Rev. Lett.* 89, 106801 (2002).

32. Z. Chen, J. Appenzeller, J. Knoch, Y-M Lin, and P. Avouris, *Nano Lett.* 5, 1497 (2005).

33. A. Javey, J. Guo, Q. Wang, M. Lundstrom and H. Dai, *Nature* 424, 654 (2003).

34. Y. Yaish, J.-Y. Park, S. Rosenblatt, V. Sazonova, M. Brink and P.L. McEuen, *Phys. Rev. Lett.* 92, 46401 (2004).

35. Q. Cao, H.S. Kim, N. Pimparkar, J.P. Kulkarni, C. Wang, M. Shim, K. Roy, M.A. Alam and J.A. Rogers, *Nature* 454, 495 (2008).

36. K. Bosnick, N. Gabor, and P McEuen, Appl. Phys. Lett. 89, 163121 (2006).

37. J.U. Lee, P.P. Gipp, and C.M. Heller, Appl. Phys. Lett. 85, 145 (2004).

38. D. Abdula and M. Shim, ACS Nano 2, 2154 (2008).

39. C. Lu, L. An, Q. Fu, J. Liu, H. Zhang, and J. Murduck, *Appl. Phys. Lett.* 88, 133501 (2006).

# 1.6 Figures

http://www.nanoscienceworks.org/Members/siebo/657pxtypes\_of\_carbon\_nanotubes.png /view

Figure 1.1 Single layers of graphene sheets are rolled up to form various kinds of carbon nanotubes.

a.

Figure 1.2 Random networks (a) and aligned arrays (b) of SWNTs grown via chemical vapor deposition.

b.

Figure 1.3 Interaction energy between a SWNT and ST cut quartz, as a function of orientation angle, and experimental results. (a) Energy map for a SWNT with radius 0.6 nm on quartz. The results show a single preferred orientation, at 0°. (b) SEM image of experimental results, showing behavior consistent with theory. The orange arrow indicates the flow direction. In a typical case such as this one, more than 99.91% of the total lengths of the SWNTs lie along the preferred direction, not including the regions where the catalyst particles are located. Reproduced with permission from Ref. [26]. Copyright 2009 American Chemical Society.

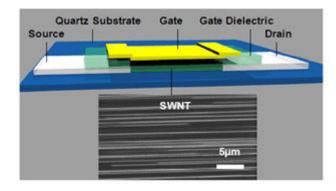

Figure 1.4 (a) Schematic illustration of a top gated thin film transistor. Bottom image shows a SEM image of an aligned array of SWNTs. (b) Transfer curve of an aligned array SWNT thin film transistor. In this case, the channel width is  $400\mu$ m and the channel length is  $5\mu$ m. Tube density is 4SWNTs/ $\mu$ m. Metal electrodes used are palladium.

b.

## **CHAPTER 2:**

# STATISTICAL ANALYSIS OF THE ELECTRICAL PERFORMANCE VARIABILITY IN TRANSISTORS THAT USE ALIGNED ARRAYS OF SINGLE WALLED CARBON NANOTUBES

## 2.1 Introduction

Transistors based on single semiconducting single walled carbon nanotubes (SWNTs) have been demonstrated. These devices are found to have high mobility up to  $10,000 \text{cm}^2/\text{Vs}$ , [1] high transconductance up to  $3\text{mS}/\mu\text{m}$  [2] and high on/off ratio,  $\sim 10^6$ . [2] This generates an interest in studying SWNTs for use in electronic devices. However, these test structures based on single SWNTs have low current output and non-uniformity in electrical performance because of the variation in diameter and chirality of SWNTs grown. [3,4] Hence, for practical use of SWNTs in transistors, thin films of SWNTs containing SWNTs of a certain high density are more attractive because the current output will be higher and statistical averaging can result in more uniform electrical performance.

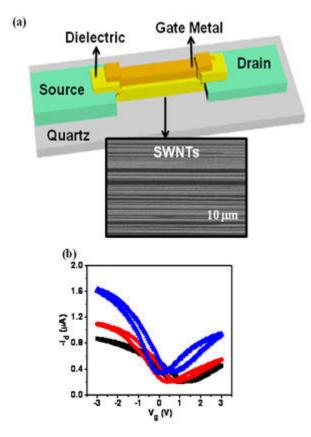

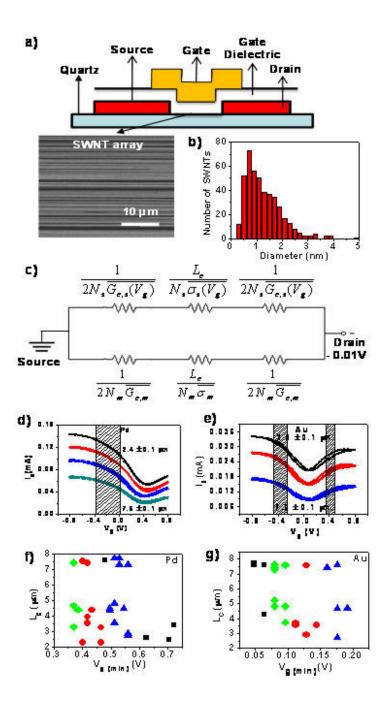

Transistors based on thin film of random SWNT networks have demonstrated attractive device performance [5] and thus, been considered as alternative semiconducting materials for use in flexible electronics [6] or transparent electronics. [7] On the other hand, transistors based on aligned arrays of SWNTs have superior electrical performance than its random counterpart, which makes aligned array SWNT transistors to be attractive in applications with high demand requirements such as RF analog electronics. [8-10] However, integration of such aligned SWNT arrays in transistors for large scale commercial use requires them to be uniform in electrical performance. Our measurement of transistors based on aligned arrays of SWNTs (schematically shown in Figure 2.1a) indicates considerable variation in its I-V characteristics (Figure 2.1b).

Our previous work [11] has indicated that variation in the on current of transistors based on aligned array of SWNTs can be attributed to variation in the diameter distribution of SWNTs. However, we did not consider the effect of SWNT density variation in the arrays, which can also potentially contribute to additional variation [12]. Reference 12 also claims that in devices with many SWNTs, the variation contributed by the diameter distribution is strongly diminished by statistical averaging. This contradicts with our previous study. Our earlier analysis was limited because we only considered the effect of diameter of SWNT on the Schottky barrier height at the SWNT-metal electrode interface. However, at relatively long channel lengths (> a few  $\mu$ m), the on current of a SWNT can instead be limited by its channel conductance instead of contact conductance. This is especially true for SWNTs with large diameters (hence small bandgap and small Schottky barrier at the SWNT-metal electrode interface). Furthermore, the contribution of SWNTs with large diameters to the overall on current of a transistor based on aligned array of SWNTs is more significant because SWNTs with larger diameters carry more current. Similarly, a previous study from another group (reference 3) has also considered the effect of contact conductance only but not channel conductance, which we will consider in this work.

This chapter seeks to examine the extent of statistical averaging in reducing the device to device variations in transistors based on aligned arrays of SWNTs very thoroughly. In this study, we fabricate and characterize field-effect transistors consisting of a single SWNT (single-SWNT FETs). Using these single-SWNT FETs as the basis, we simulate transistors consisting of aligned arrays of SWNTs (array-SWNT FETs). Later, we compare the I-V characteristics and the extracted on current and maximum transconductance of these simulated array-SWNT FETs to those of fabricated array-SWNT FETs. Our analysis suggests that the variations in fabricated array-SWNT FETs do not reduce as  $1/\sqrt{n}$  (central limit theorem) as we would expect, where n is the number of SWNTs in array-SWNT FETs. We attribute these inconsistencies to the variations in spatial density and diameter distribution of SWNTs across the wafer.

In addition, we also study in detail the dependence of the on current, maximum transconductance and threshold voltage of single semiconducting SWNT (s-SWNT) devices on the diameter of the SWNTs. The variation in on current and maximum transconductance can be attributed to variations in diameter. The threshold voltage has also previously been attributed to the diameter only [13]. However, we show that the SWNT threshold voltage statistics should consider the contributions from extrinsic factors, e.g. the variations in defect density across the wafer [14,15,16]. These results

provide key insights into the causes of variations in transistors and directions to eliminate these variations in future.

## 2.2 Methods for Fabricating Single and Array SWNT FETs

Figure 2.1a shows a schematic illustration of a transistor that uses aligned arrays of single walled carbon nanotubes (SWNTs) or a single SWNT as the semiconducting material. A scanning electron microscope (SEM) image of an aligned array of SWNTs is also shown below for illustration. To fabricate aligned array SWNT FETs, aligned SWNTs are grown via chemical vapor deposition (CVD) on ST (stable temperature) cut quartz substrate, using procedures described elsewhere. [15,16] Next, we define source and drain electrodes (60 nm Pd/ 2 nm Ti) by photolithography and lift-off and etch SWNT outside the channel regions (defined by channel length and width). The channel length of the fabricated transistors is ~10 $\mu$ m. A layer of ~35nm spin-coated and heat-treated Spin-On Glass (SOG) and a layer of ~20nm ALD-grown hafnium oxide (HfO<sub>2</sub>) are deposited on top of the contacts and SWNTs, forming the gate dielectrics. This is followed by a gate electrode (Au (60 nm)/ Ti (2 nm)) deposition, which is again defined by photolithography and liftoff to complete the transistors.

Fabrication of single SWNT FETs follows a similar process. However, we etch all but a small width of  $1.5\mu m$ , thus resulting in FETs with a small number of SWNTs. The devices are examined using SEM and the FETs with a single SWNT are selected. As a purely stochastic process, resultant yield of single SWNT FETs is low, ~3%.

# 2.3 Characteristics of Single SWNT FETs

Understanding of the statistics of an array SWNT FET requires us to comprehend the characteristics of its basic building block, i.e. the characteristics of single SWNT itself. So far, several studies [1, 11, 14, 17-24] have characterized single SWNT FETs and examined the effect of SWNT diameter and source/drain metal electrodes on their I-V properties. These studies have identified the following key features of SWNT FETs:

- SWNT FETs with Pd source/drain electrodes have p-type properties.

- Small diameter SWNT has large bandgap and p-type conduction in the corresponding FET is dictated by the Schottky barrier near the source/drain electrode.

- On the other hand, large diameter SWNT has small bandgap and the corresponding FET has no Schottky barrier near the source/drain electrode. Hence, p-type conduction in these FETs is dictated by the intrinsic properties of SWNT channel.

- P-type conduction in large diameter SWNT FET indicates linear relationship between the channel conductance and diameter (which also corresponds to a quadratic relationship between the effective mobility and diameter).

- The magnitude of conductance and effective mobility of SWNT FET strongly depends on its surrounding environment.

In this section, we study the properties of our fabricated SWNT FETs, estimate the conventional electrical parameters of SWNT FETs (like threshold voltage, maximum transconductance, ON current, etc.) and identify their dependence on SWNT diameter. In addition, we develop a simple model explaining the diameter dependence of SWNT FETs electrical parameters. In consistency with literature, we identify that most of the electrical parameters (except threshold voltage) of SWNT FETs can solely be explained by understanding their diameter dependence. Therefore, knowledge of diameter distribution and SWNT density distribution across the wafer is sufficient to study the performance statistics (except threshold voltage) of array SWNT FETs (see section 2.4.3 for details). We show that the variation of threshold voltage of SWNT FETs depends weakly on diameter and (presumably) depends on extrinsic factors like interface defect density, metal workfunction [25-27], etc. Such understanding of the SWNT's performance variation with diameter, along with the information related to diameter distribution and SWNT density distribution across the wafer, enables us to explain the statistics of array SWNT FETs, as discussed in section 2.4.

# 2.3.1 Measurement of Single SWNT FET

Figure 2.2a shows a SEM image of a single SWNT contacted to two metal electrodes to the right and left of the image, before depositing the gate dielectric and metal gate to complete the single SWNT FET. Figure 2.2b and 2.2c show typical transfer curves of transistors based on a single semiconducting SWNT (s-SWNT) and a single quasi metallic SWNT (m-SWNT), respectively, measured with the source grounded, the

drain held at a bias of -0.05 V, and the gate bias (V<sub>G</sub>) swept between  $\pm 1.5$ V. The single s-SWNT devices have high ON/OFF ratio =  $I_{ON}/I_{OFF}$  (here, the ON current  $I_{ON}$  is considered as the  $I_D$  at  $V_G = -1.5V$  and OFF current  $I_{OFF}$  is considered as the minimum I<sub>D</sub>) and show predominantly p-type behavior. On the other hand, single quasi m-SWNT devices have very small gate modulation (ON/OFF ratio of < 100) and show ambipolar behavior (with a smaller n type tail). Small gate modulation of quasi m-SWNT devices are not totally unexpected and have been reported previously. [28-29] This phenomenon has been attributed to the Mott insulating state in m-SWNTs [28] or the strain induced bandgap in m-SWNTs [29]. The difference in electrical properties of quasi m-SWNT FETs and s-SWNT FETs is more clearly visible in Figure 2.2d, where we plot I<sub>OFF</sub> vs I<sub>ON</sub> for all the 45 single (quasi metallic and semiconducting) SWNT FETs measured. The symbols representing the quasi m-SWNT FETs (having ON/OFF ratio < 100) are in the shaded maroon region, while the symbols representing the s-SWNT devices (having ON/OFF ratio > 100) are in the shaded blue region. The single s-SWNT FETs have  $I_{OFF}$ that are orders of magnitude smaller than most of the single m-SWNT FETs. Note that the measured I<sub>OFF</sub> of s-SWNT devices are limited at ~0.1-1pA, which is due to the Agilient parametric analyzer's current resolution limit. Actual I<sub>OFF</sub> of s-SWNT FETs may be significantly lower than this measured pA current.

## 2.3.2 Modeling of s-SWNT FET

Figure 2.3a replots the I-V characteristics of 25 measured s-SWNT FETs (having ON/OFF ratio >100). Here, we model the s-SWNT I-V characteristics and check if the variation in electrical parameters of s-SWNT is due to variation in diameter. We simulate the I-V characteristics of s-SWNT at small drain bias by determining the source-to-drain conductance ( $G_{DS}$ ) of s-SWNT FET, as a combination of contact conductance ( $G_C$ ) and s-SWNT channel conductance ( $G_{CNT}$ ). Later on, we calculate the drain current,  $I_D$ , at a particular gate voltage,  $V_G = E_{Fi} + Q/C_G$ , using  $I_D = G_{DS}*V_{DS}$ , where  $V_{DS}$  is the drain voltage,  $E_{Fi} = E_i - E_F$ ,  $E_i$  is the intrinsic Fermi level of s-SWNT (*i.e.*, the mid-gap energy level),  $E_F$  is the Fermi energy level in the s-SWNT,  $C_G$  is the gate capacitance, and Q is the charge density that is expressed as

$$Q = -q \int_{-\infty}^{\infty} dE * sign(E) * v(E) * f(sign(E) * (E - E_{Fi}))$$

$$\tag{1}$$

where  $v(E) = \frac{4}{\pi \hbar v_F} \frac{|E|u(E - E_{Fi})}{\sqrt{E^2 - E_{Fi}^2}}$  [30-33], v(E) is the density of states in the s-SWNT,

$f(sign(E)*(E-E_{Fi}))$  is the Fermi distribution in the s-SWNT, u(E) is the unit step function, and sign(E) is the sign of energy level E.

Once, we calculate  $E_{Fi}$ , hence  $V_G$ , for a particular value of Q, we can estimate  $G_{DS}$  using

$$G_{DS} = G_{DS,e} + G_{DS,h} = (G_{CNT,e}^{-1} + G_{C,e}^{-1})^{-1} + (G_{CNT,h}^{-1} + G_{C,h}^{-1})^{-1}$$

(2)

where G<sub>CNT</sub> within single sub-band approximation is expressed as [1],

$$G_{CNT,e(h)} = \frac{4q^2}{h} \frac{\tau_0 v_0}{L} \frac{\left[\left|Q_{e(h)}\right| / V_A\right]^2}{1 + \left[\left|Q_{e(h)}\right| / V_A\right]^2}$$

(3)

where  $V_A = \frac{8q}{3\pi d}$ , q is the electron charge, h is Planck's constant, L is channel length,  $\tau_0^{-1}$  is the scattering rate in the SWNT channel at Fermi velocity, v<sub>0</sub>. Following the expression for acoustic phonon scattering rate in [1], we express the scattering rate using,  $\tau_0^{-1} = \alpha \frac{T}{d}$ , where T is the temperature in °K, and  $\alpha$  is the scattering coefficient. d is the diameter of the SWNT and Q<sub>e(h)</sub> is the electron (hole) density within SWNT channel and can be calculated as

$$Q_{e} = -q \int_{0}^{\infty} dE * sign(E) * v(E) * f(sign(E) * (E - E_{Fi}))$$

$$Q_{h} = -q \int_{\infty}^{0} dE * sign(E) * v(E) * f(sign(E) * (E - E_{Fi}))$$

(4)

Calculation of  $G_{DS}$  in equation (2) also requires us to obtain  $G_C$ , which is considered as a multiplication of  $G_{C0}$  (the contact conductance for large s-SWNT diameter and large  $V_G$ , so that carriers can be injected barrier-free from contact into

SWNT) and contact Transmission probability  $T_C$ ; i.e.  $G_C = G_{C0}T_C$  with  $T_C = T_{therm} + T_{SB}$ +  $T_{BTBT}$ . The transmission probability through the contact has contributions from

(1) thermionic emission ( $T_{therm}$ ).  $T_{therm}$  is expressed as  $exp(-E_{barrier}/kT)$ ; where  $E_{barrier}$  is the thermal barrier for carrier injection from contact into the channel,

(2) Schottky barrier tunneling ( $T_{SB}$ ).  $T_{SB}$  is expressed as where  $k_z$  is parallel momentum related to the E-k relationship in CNT [33] at distance z from the contact into the channel,

(3) band to band tunneling  $(T_{BTBT})$ .  $T_{BTBT}$  is expressed as  $\exp(-E_G^2 / q\hbar v_0 F_z)$  [34], where  $E_G$  is the bandgap of CNT,  $F_z$  is the electric field at the location of band to band tunneling.

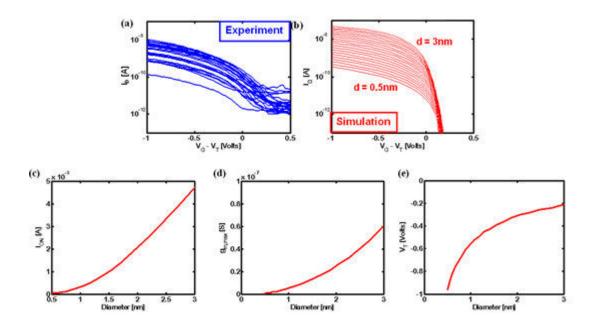

Following the approach summarized above, we calculate I<sub>D</sub>-V<sub>G</sub> of s-SWNTs for various diameters (figure 2.3b) using  $v_0 = 8 \times 10^5$  m/s,  $\alpha = 80$  m/K-s,  $G_{c0} = 1/28$  kΩ [1], T = 300 °K. The simulated transfer curves match closely with the measured transfer curves in Figure 2.3a. With these parameters, our simulation suggests a diameter range of 0.5-1.5nm for the measured transfer characteristics of Figure 2.3a. Note that the required value of scattering parameter  $\alpha$ , for matching the I-V characteristics using a reasonable diameter range of 0.5-1.5nm, is much larger than the ones reported in [1,24,35]. This can be due to the existence of more scattering in our samples. Next, we calculate  $I_{ON} \equiv$  $I_D @V_G - V_T = -1V$ , maximum transconductance  $(g_{m,max} = max(\partial I_D / \partial V_G))$  and  $V_T$  (defined as V<sub>G</sub> for I<sub>D,max</sub>/100) of single s-SWNT devices and plot them in figure 2.3c, 2.3d and 2.3e, respectively. I<sub>ON</sub> vs diameter relationship of Figure 2.3c suggests a non-linear increase of  $I_{ON}$  at smaller diameter, where  $T_C < 1$ . At larger diameter,  $T_C \sim 1$  and the source-to-drain conduction is mostly limited by the CNT channel and hence,  $I_{ON} \sim {\tau_0}^{-1} \sim$ d [1]. g<sub>m,max</sub> vs diameter relationship of Figure 2.3d suggests a non-linear relationship at smaller diameter (where,  $T_C < 1$ ) and  $g_{m,max} \sim SWNT$  mobility  $\sim d^2$  [1] relationship at larger diameter, where  $T_C \sim 1$ . Note that the diameter threshold for observing a change in the electrical-parameter vs diameter as we move from the  $T_C < 1$  to  $T_C \sim 1$  region (in Figure 2.3c and 2.3d) depends on CNT work-function ( $\Phi_{CNT}$ ), V<sub>G</sub>-V<sub>T</sub>, and contact workfunction ( $\Phi_{\rm C}$ ) used in the simulation. In general, the diameter threshold is smaller for larger V<sub>G</sub>-V<sub>T</sub> and smaller ( $\Phi_{C}$  -  $\Phi_{CNT}$ ). Figure 2.3e shows V<sub>T</sub> vs diameter relationship for single s-SWNT transistors. This relationship mainly depends on the definition of  $V_T$  being used. Since  $V_T$  is defined as the  $V_G$  for  $I_D = I_{D,max}/100$ , at smaller diameter or larger SWNT bandgap (when  $T_C < 1$ ), the non-linear conduction is dictated by the Schottky barrier at the contact and hence  $V_T$  increases rapidly with diameter. At larger diameter (when  $T_C \sim 1$ ), Schottky barrier height reduces to zero and the linear increase in  $I_{D,max}$  with diameter also results in a corresponding increase of  $V_T$ .

## 2.4 Statistics of Array SWNT FETs

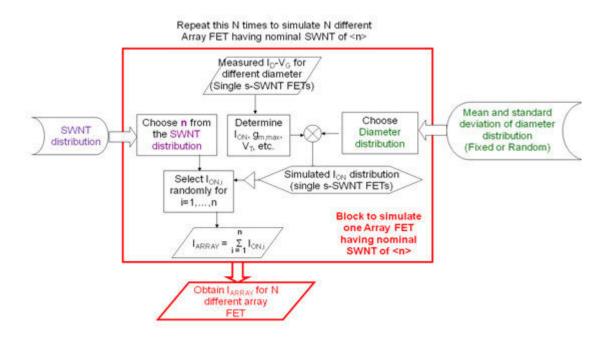

Our knowledge of s-SWNT electrical parameters and their diameter dependence enables us to estimate the statistics of array SWNT FETs by following the algorithm that is presented in Figure 2.4 for studying the ON current statistics (one can follow similar algorithm with appropriate changes for other electrical parameters) and hence compare with array SWNT FET measurements. This allows us to understand the extent of statistical averaging in reducing the device to device variations in array-SWNT FETs. The input to our algorithm is the diameter distribution and the SWNT density distribution across the wafer, which is known from measurements (see section 2.4.1 and Figure 2.5). For simulating an array SWNT FET having a nominal number of <n> SWNT,

1. We either randomly choose n from a (presumed) normal distribution of SWNT having mean  $\langle n \rangle$ , or choose n =  $\langle n \rangle$ .

2. At the same time, we also choose a diameter distribution for the same array SWNT FETs that has a mean and standard deviation of the diameter. Such mean and standard deviation are either randomly chosen from the values measured in Figure 2.5b-c or kept the same for the entire set of array SWNT FETs.

3. Choice of a particular diameter distribution, along with the diameter dependence of electrical parameters (as shown in Figure 2.3c-e), enables us to obtain the distribution of electrical parameters (one such example is shown in Figure 2.6).

4. Later, we choose n values of electrical parameters from the distribution and appropriately sum them for estimating the electrical parameters of an array SWNT FET. For simulating a different array SWNT FET, we repeat the same steps as mentioned above.

20

## 2.4.1 Diameter and Density Distributions

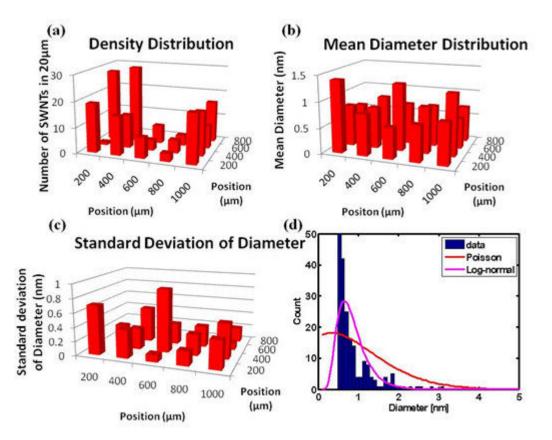

Simulation of array SWNT FET statistics uses the SWNT density distribution and diameter distribution across the wafer as an input. Therefore, we measure these values across the wafer and summarize them in Figure 2.5. Figure 2.5a show the measured SWNT density distribution (via Atomic Force Microscopy AFM) on a substrate for a scanned area of 20µm (normal to the alignment direction of SWNT) X 1.25 µm (parallel to the alignment direction of SWNT), which has average SWNT  $\langle n \rangle = 13$  and standard deviation of 69% of <n>. The SWNT density can vary significantly even though the separation between two distributions is only 200µm. Therefore, our simulation of array SWNT FET statistics should consider different n for different array SWNT FETs. Similarly, wide variation in the mean and standard deviation of the diameter distribution at different locations of the substrate (for the same scan area) is also observed in Figure 2.5b and 2.5c, respectively. Figure 2.5d shows a representative diameter distribution for a wider scanned area. The distribution is better fitted (have less sum of squares error) using a log-normal distribution compared to a Poisson distribution. Therefore, we determine the variation of log-normal distribution parameters across the wafer. In simulating different array SWNT FETs, we either randomly choose log-normal distribution parameters within the measured range (see Figures 2.8d and 2.8f) or keep the log-normal distribution parameters fixed to a measured value (see Figures 2.7b, 2.7c, 2.7e, 2.8a, and 2.8b).

# 2.4.2 Distribution of s-SWNT Electrical Parameters

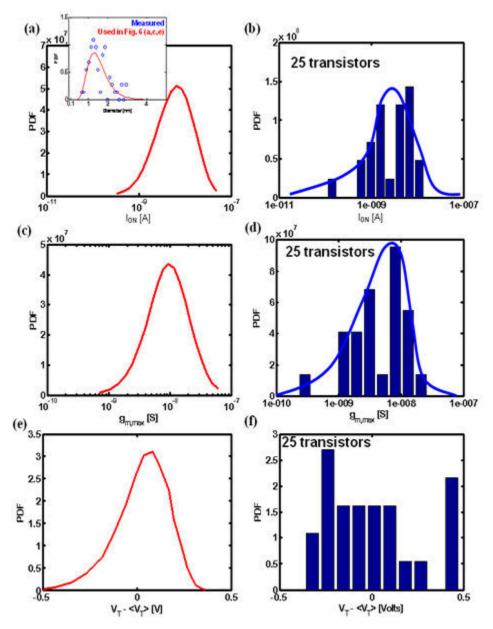

Once we obtain the dependence of s-SWNT electrical parameters on diameter (Figure 2.3c-e), we can use a particular diameter distribution to estimate the distribution of s-SWNT parameters for that diameter distribution. Later, we compare the simulated distribution of s-SWNT electrical parameters with the ones obtained from single s-SWNT FET measurements. We fit a representative statistics of diameter (inset of Figure 2.6a) using log-normal distribution and hence use Figure 2.3c to estimate the distribution of I<sub>ON</sub>  $\equiv$  I<sub>D</sub>@V<sub>G</sub>-V<sub>T</sub>=-1V (Figure 2.6a). Simulated distribution agrees reasonably well I<sub>ON</sub> distribution of Figure 2.6b, which has been derived from Figure 2.3a. We also perform similar simulation of g<sub>m,max</sub> and V<sub>T</sub> -  $\langle$ V<sub>T</sub>> distributions, as shown in Figure 2.6c and

2.6e, respectively and compare them with the measurements of Figure 2.6d and 2.6f, respectively. However, unlike the I<sub>ON</sub> and  $g_{m,max}$  distribution, measured  $V_T - \langle V_T \rangle$  distribution shows inconsistency with the simulated distribution. Therefore, diameter distribution of s-SWNTs may not be the main factor that controls the measured variations in  $V_T - \langle V_T \rangle$ . Instead, the variation in  $V_T - \langle V_T \rangle$  is expected to originate from extrinsic factors, such as variations in oxide/interface defects at the SWNT/gate dielectric interface and/or variation in metal-gate workfunction. The shape of the  $V_T$  distribution will therefore reflect the variation of these extrinsic factors in our fabricated FETs.

### 2.4.3 Comparing simulated and measured array-SWNT FETs

Once we have estimated the distribution of electrical performance parameters or I-V characteristics as a whole (for a particular diameter distribution, chosen from a set), we can simulate statistical distribution of electrical parameters or I-V characteristics for an array SWNT FET. To perform this for a particular array SWNT FET having a nominal number of  $\langle n \rangle$  SWNT, we either choose  $n = \langle n \rangle$  ('fixed n' simulation) or choose n from the expected SWNT density distribution with mean  $\langle n \rangle$  ('variable n' simulation). Next, we randomly select n values of electrical parameters like  $I_{ON}$  ( $I_{ON,i=1...n}$ ) from the distribution like Figure 2.6a. Then for estimating the ON current for the simulated array

SWNT FET (I<sub>ARRAY</sub>), we sum I<sub>ON,i</sub> and thus calculate I<sub>ARRAY</sub> =  $\sum_{i=1}^{n} I_{ON,i}$ . On the other

hand, for estimating maximum transconductance  $(g_{ARRAY})$  and threshold voltage  $(V_{T,ARRAY})$  for simulated array SWNT FET, we sum the randomly selected n I-V characteristics (I-V<sub>i</sub>) to obtain I-V characteristics of array SWNT FET (I-V<sub>ARRAY</sub>). From I-V<sub>ARRAY</sub>, we can estimate  $g_{ARRAY}$  and  $V_{T,ARRAY}$ . For simulating a different array SWNT FET, we either choose the same  $n = \langle n \rangle$  for 'fixed n' simulation or choose a different n from the SWNT density distribution for 'variable n' simulation. Input diameter distribution to our simulator can either be considered as fixed (as done in Figures 2.7b, 2.7c, 2.7e, 2.8a, and 2.8b) or variable (as done in Figures 2.8d and 2.8f).

After repeating the calculation for a number of array SWNT FETs having same <n>, we can estimate the statistics of electrical parameters like I<sub>ARRAY</sub>, g<sub>ARRAY</sub>, V<sub>T,ARRAY</sub> for the array SWNT FETs. Let us now understand the effect of the experimentally

observed distribution of SWNT density and diameter on the statistics of array SWNT FET's electrical parameters. We add the effect of one distribution at a time for studying the I<sub>ARRAY</sub> statistics in detail and later extend our analysis for other SWNT FET's electrical parameters.

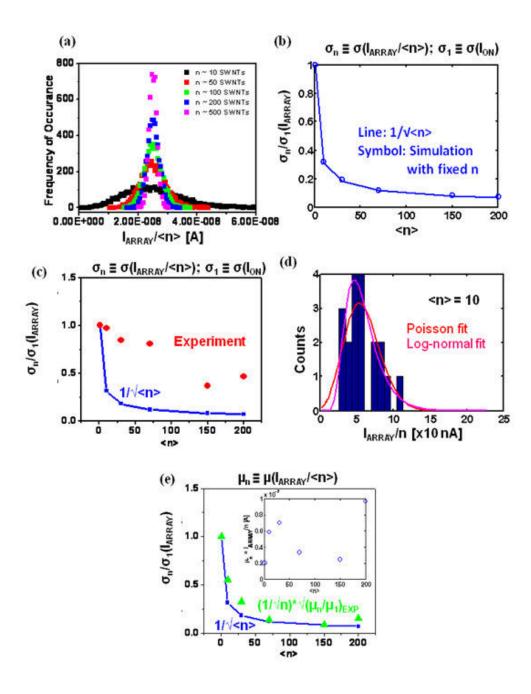

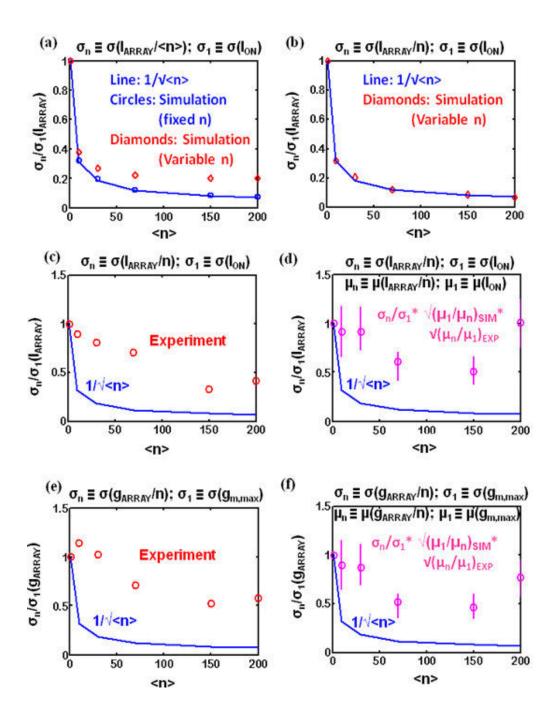

First, we consider the case for <u>no variation in SWNT density (*i.e.*, n = <n>) and input diameter distribution</u> for array SWNT FET. Using this approach, we simulate the  $I_{ARRAY}/<n>$  (Figure 2.7a) and observe gradual narrowing of the distribution with increasing <n>. Following the central limit theorem, the normalized standard deviation of  $I_{ARRAY}/<n>$  distribution, ( $\sigma_n/\sigma_1(I_{ARRAY})$ ), reduces as  $1/\sqrt{<n}$  (Figure 2.7b). Estimation of  $\sigma_n/\sigma_1(I_{ARRAY})$  of measured array SWNT FET suggests significant deviation from the  $1/\sqrt{<n}$  relationship (Figure 2.7c). This indicates the necessity to consider the variation in SWNT density and input diameter distribution for understanding the statistics of array SWNT FETs.

Next, we consider the effect of <u>variation in mean I<sub>ARRAY</sub>/<n> on the statistics of array SWNT FETs. Considering that the mean of any distribution is related to the standard deviation (for example,  $\mu \sim \sigma^2$  for the Poisson distribution), a systematic variation in mean I<sub>ARRAY</sub>/<n> might enable us to explain the deviation from 1/ $\sqrt{n}$  in Figure 2.7c. Therefore, we determine the statistics of I<sub>ARRAY</sub>/<n> for all array SWNT FETs and observe Log-normal distribution to better fit (with smaller sum of square error) the I<sub>ARRAY</sub>/<n>, compared to a Poisson distribution (Figure 2.7d). However, since Poisson distribution has a simple relationship of  $\mu \sim \sigma^2$  and has reasonable fitting for the array SWNT FET statistics, we use  $\mu \sim \sigma^2$  in the rest of our analysis for compensating the disparity of  $\mu_{n,I}$  (see the inset of Figure 2.7e) in our array transistors. Therefore, scaling  $1/\sqrt{<n}$  with  $\sqrt{(\mu_n/\mu_1)_{EXP}}$  (obtained from measurement) enables us to capture the effect of variation in mean I<sub>ARRAY</sub>/<n>. Figure 2.7e suggests that such scaling of  $1/\sqrt{<n}$  (which is consistent with simple statistical simulation of Figure 2.7a-b) cannot explain the measured  $\sigma_n/\sigma_1$ (I<sub>ARRAY</sub>) of Figure 2.7c.</u>

Later, we consider the effect of <u>SWNT density variation</u> on the statistics of array SWNT FET. Our simulation (Figure 2.8a) suggests that the consideration of SWNT density variation (variable n simulation) causes deviation from  $1/\sqrt{<n>}$ , when we use  $I_{ARRAY}/<n>$  for calculating  $\sigma_n/\sigma_1(I_{ARRAY})$ . However, a calculation of  $\sigma_n/\sigma_1(I_{ARRAY})$  using  $I_{ARRAY}/n$  (*i.e.*, calculating average ON current carried by a SWNT in array SWNT FET by dividing with the respective n, rather than <n>, for that array SWNT FET) eliminates the effect of SWNT density variation from the statistics of array SWNT FETs (Figure 2.8b). Simulated  $\sigma_n/\sigma_1(I_{ARRAY})$  for array SWNT FETs that considers the effect of SWNT density variation suggests negligible deviation from  $1/\sqrt{<n>}$ , when  $I_{ARRAY}/n$  is used for calculating  $\sigma_n/\sigma_1(I_{ARRAY})$ . However, similar calculation of measured  $\sigma_n/\sigma_1(I_{ARRAY})$  using  $I_{ARRAY}/n$  still shows significant deviation from the  $1/\sqrt{<n>}$  relationship (Figure 2.8c). This enables us to conclude that we still need to consider the effect of diameter distribution in calculating  $\sigma_n/\sigma_1(I_{ARRAY})$ , which mainly dictates the statistics of array SWNT FETs.

Finally, we consider the effect of both <u>variations in SWNT density and diameter</u> <u>distribution</u> for explaining the statistics of array SWNT FETs. Figure 2.8d suggests that the inclusion of variation in diameter distribution from one array SWNT to another (but having same  $\langle n \rangle$ ) is crucial for explaining the experiment. Since there is disparity in the chosen diameter distribution from one simulation run to another, we obtain a range of  $\sigma_n/\sigma_1(I_{ARRAY})$  for the array SWNT FETs of size  $\langle n \rangle$ . Experimental data shown in Figure 2.8c falls within this range of  $\sigma_n/\sigma_1(I_{ARRAY})$  and hence show excellent consistency with simulation. Similar to the analysis of  $I_{ARRAY}$ , our measurement of  $\sigma_n/\sigma_1(g_{ARRAY})$  also reflects deviation from  $1/\sqrt{\langle n \rangle}$  scaling, as shown in Figure 2.8e. This deviation can also be attributed to the wafer-level diameter distribution, as simulated in Figure 2.8f.

Note that our simulation of array-SWNT FET does not consider the effect of metallic-SWNTs in calculating the array-SWNT FET statistics; however, the measurements of array SWNT FETs have contribution from metallic-SWNTs and hence have much smaller ON/OFF ratio, as shown in Figure 2.1b. In spite of such differences, our statistical analysis nicely reflects the effect of statistical averaging in large <n> array SWNT FETs and the effect of variation in SWNT density and diameter distribution across the wafer. Inclusion of the effect of metallic-SWNTs should make the comparison between theory and experiment more meaningful, but will not change the essential features of array-SWNT FET statistics.

Since our theoretical analysis does not take into account the conduction through metallic SWNTs, we do not follow the same approach (as we used for analyzing  $I_{ARRAY}$  and  $g_{ARRAY}$ ) for statistical analysis of two other array-SWNT FET parameters, namely

gate voltage at minimum drain current ( $V_{G,min}$ ) and minimum drain current ( $I_{MIN}$ ). Statistics of these parameters are mainly related to the statistics of metallic SWNTs within the array-SWNT FET and shows slight deviation from 1/<n>. Our ultimate effort in commercializing SWNT electronics is to eliminate the metallic SWNTs, hence we restrain ourselves from the statistical analysis of  $V_{G,min}$  and  $I_{MIN}$ .

#### 2.5 Conclusions

We examine the variation in on current, maximum transconductance and threshold voltage of single s-SWNT FETs and find that we can attribute the variation in on current and maximum transconductance to variation in diameter distributions of SWNTs. The variation in threshold voltage of single s-SWNT transistors may be more influenced by other extrinsic factors such as variation in interface defects or gate metal workfunction. Next, we study the extent of statistical averaging in reducing the device to device variations in array-SWNT FETs. We simulate the electrical parameters of array-SWNT FETs and hence compare it with measurements of similar parameters. We find that although there is smaller device to device variation as the number of SWNTs in array FETs increases, the decrease in device to device variation does not follow the expected  $1/\sqrt{n}$  relation (according to central limit theorem) because of the non-uniformity of the density and diameter distributions across the wafer. Therefore, it is essential to control the uniformity of the density and diameter distributions of array-SWNT FETs to achieve devices with uniform electrical properties via well engineered processing, which is essential for large scale commercial use of such FETs. Clever circuit design is also another technique that has been suggested to help reduce the effects of variations in arrays of SWNTs. [12]

### 2.6 References

1. X. Zhou, J-Y Park, S. Huang, J. Liu and P.L. McEuen, *Phys. Rev. Lett.*, 95, 146805 (2005).

A. Javey, H. Kim, M. Brink, Q. Wang, A. Ural, J. Guo, P. McIntyre, P. McEuen, M. Lundstrom and H. Dai, *Nat. Mater.*, 1, 241 (2002). 3. Y.C. Tseng, K. Phoa, D. Carlton and J. Bokor, *Nano Lett.*, *6*, 1364 (2006).

4. S. Bandow and S. Asaka, *Phys. Rev. Lett.*, 80, 3779 (1998).

5. E.S. Snow, J.P. Novak, P.M. Campbell and D. Park, *Appl. Phy. Lett.*, 82, 2145 (2003).

6. Q. Cao, H-S Kim, N. Pimparkar, J.P. Kulkarni, C. Wang, M. Shim, K. Roy, M.A. Alam and J.A. Rogers, *Nature*, 454, 495 (2008).

7. S. Kim, S. Kim, J. Park, S. Ju and S. Mohammadi, *ACS Nano*, 4, 2994 (2010).

8. C. Kocabas, S. Dunham, Q. Cao, K. Cimino, X. Ho, H-S Kim, D. Dawson, J. Payne, M. Stuenkel, H. Zhang, T. Banks, M. Feng, S.V. Rotkin and J.A. Rogers, *Nano Lett.* 9, 1937 (2009).

9. C. Kocabas, H-S. Kim, T. Banks, J.A. Rogers, A.A. Pesetski, J.E.Baumgardner, S.V. Krishnaswamy and H. Zhang, *Proc. Natl. Acad. Sci.*, 105, 1405 (2008).

10. P.J. Burke, Solid State Electron., 48, 1981 (2004).

11. S. Salamat, X. Ho, J.A. Rogers and M.A. Alam, *IEEE Trans. Nanotechnol.*, PP(99), 1 (2010)

12. J. Zhang, N. Patil, A. Hazeghi and S. Mitra, Carbon nanotube circuits in the presence of carbon nanotube density variations, Proceedings of the 46th Annual Design Automation Conference, 2009, New York, New York.

13. Z. Chen, J. Appenzeller, J. Knoch, Y-M Lin and P. Avouris, *Nano Lett.*, 5, 1497 (2005).

14. V. Derycke, R. Martel, J. Appenzeller and P. Avouris, *Appl. Phys. Lett.*, 80, 2773 (2002).

15. Y. Li, S-M. Yu and H-M. Chen, *Microelectron. Eng.*, 84, 2117 (2007).

D.B. Farmer, R. Golizadeh-Mojarad, V. Perebeinos, Y-M. Lin, G.S. Tulevski,

J.C. Tsang and P. Avouris, *Nano Lett.*, 9, 388 (2009).

17. C. Kocabas, M. Shim and J.A. Rogers, J. Am. Chem. Soc., 128, 4540 (2006).

18. C. Kocabas, S-H Hur, A. Gaur, M. Meitl, M. Shim and J.A. Rogers, *Small*, 1, 1110 (2005).

19. W. Kim, A. Javey, R. Tu, J. Cao, Q. Wang and H. Dai, *Appl. Phys. Lett.*, 87, 173101 (2005).

20. J. Guo, S. Dutta and M. Lundstrom, IEEE Trans. Elec. Device, 51, 172 (2004).

21. S. Heinze, J. Tersoff, R. Martel, V. Derycke, J. Appenzeller and P. Avouris, *Phys. Rev. Lett.*, 89, 106801 (2002).

22. S.J. Wind, J. Appenzeller and P. Avouris, *Phys. Rev. Lett.*, 91, 058301 (2003).

23. J. Appenzeller, J. Knoch, V. Derycke, R. Martel, S. Wind and P. Avouris, *Phys. Rev. Lett.*, 89, 126801 (2002).

24. A. Javey, J. Guo, D.B. Farmer, Q. Wang, D. Wang, R.G. Gordon, M. Lundstrom and H. Dai, *Nano Lett.*, 4, 447 (2004).

25. V. Perebeinos, J. Tersoff and P. Avouris, *Phys. Rev. Lett.*, 94, 086802 (2005).

26. I. Polishchuk, P. Ranade, T-J. King and C. Hu, *IEEE Elec. Device Lett.*, 22, 444 (2001).

27. J.K. Efavi, T. Mollenhauer, T. Wahlbrink, H.D.B. Gottlob, M.C. Lemme and H. Kurz, *J. Mater. Sci. - Mater. Electron.*, 16, 433 (2005).

28. A.E-J. Lim, W.S. Hwang, X.P. Wang, D.M.Y. Lai, G.S. Samudra, D-L Kwong and Y-C. Yeo, *J. Electrochem. Soc.*, 154, H309 (2007).

29. V.V. Deshpande, B. Chandra, R. Caldwell, D.S. Novikov, J. Hone and M. Bockrath, *Science*, 323, 106 (2009).

30. J-C Charlier, X. Blasé, S. Roche, Rev. Mod. Phy., 79, 677 (2007).

31. J. Guo (2004) *Carbon Nanotube Electronics: Modeling, Physics, and Applications.* PhD dissertation. Purdue University.

32. A. Robert-Peillard and S.V. Rotkin, *IEEE Trans. Nanotechnol.*, 4, 284 (2005).

33. Y. Zhao, A. Liao and E. Pop, *IEEE Elec. Device Lett.*, 30, 1078 (2009).

34. X. Yang, G. Fiori, G. Iannaccone and K. Mohanram, *Physics–based semi*analytical model for Schottky–barrier carbon nanotube and graphene nanoribbon transistors, Great Lake Symposium on VLSI, 2010.

35. A. Liao, Y. Zhao and E. Pop, *Phys. Rev. Lett.* 101, 256804 (2008).

36. G. Pennington and N. Goldsman, *Phys. Rev. B*, 68, 045426 (2003).

27

# 2.7 Figures

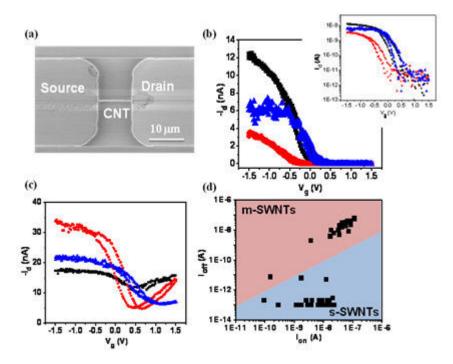

Figure 2.1: (a) Schematic illustration of a transistor based on single walled carbon nanotubes (SWNTs). A scanning electron microscope (SEM) image of the aligned arrays of SWNTs is shown below the illustration. (b) Transfer curves of array SWNT FETs with nominally 10 SWNTs.

Figure 2.2: (a) SEM image of a single SWNT contacted to two metal electrodes (source and drain) on the left and right of the image. (b) Transfer curves of representative single semiconducting SWNT (s-SWNT) devices at  $V_{ds} = -0.05V$ . Inset shows the transfer curve in semilog-y scale. (c) Transfer curves of representative single metallic SWNT (m-SWNT) devices at  $V_{ds} = -0.05V$ . (d) Distribution of measured I<sub>on</sub> and I<sub>off</sub> of single SWNT devices. Symbols representing m-SWNTs are in the area shaded maroon with I<sub>on</sub>/I<sub>off</sub> < 100 and symbols representing s-SWNTs are in the area shaded blue with I<sub>on</sub>/I<sub>off</sub> > 100.

Figure 2.3: (a) Measured transfer characteristics of single s-SWNT transistors. (b) Simulated transfer curves of single s-SWNT transistors having a diameter range of 0.5nm and 3nm. (c) Drain current when  $V_G-V_T = -1V(I_{ON})$  as a function of diameter for single s-SWNT transistors. I<sub>ON</sub> increases super-linearly at smaller diameters and increases linearly at larger diameters. (d) Maximum transconductance ( $g_{m,max}$ ) as a function of diameter for single s-SWNT transistors.  $g_{m,max}$  increases non-linearly with diameter. (e) Threshold voltage ( $V_T$ ) as a function of diameter for single s-SWNT transistors.  $V_T$  increases rapidly at smaller diameters and less rapidly at larger diameters. Here  $V_T$  is defined as the  $V_G$  at which  $I_D = I_{ON,max}/100$ .

Figure 2.4: Flowchart for simulating ON current distribution for N different array SWNT FET having nominal SWNT of <n>.

Figure 2.5: (a) Spatial distribution of the density of aligned arrays of SWNTs over an area of a substrate. Scanned area via AFM:  $20\mu m$  (normal to the alignment direction of SWNT) X 1.25 $\mu m$  (parallel to the alignment direction of SWNT); Mean SWNT,  $\langle n \rangle = 13$ . The x and y axes show the spatial locations where the distributions were measured. (b) Spatial distribution of the mean diameter of aligned arrays of SWNTs over an area of a substrate. Scanned area =  $20x1.25\mu m$ . (c) Spatial distribution of the standard deviation of the diameter distribution of aligned arrays of SWNTs over an area of a substrate. Scanned area =  $20x1.25\mu m$ . (d) A representative diameter distribution of SWNTs measured by AFM. The distribution is better fitted using a log-normal distribution (magenta line) compared to a Poisson distribution (red line).

Figure 2.6: (a) Distribution of simulated  $I_{ON}$  for single s-SWNT transistors using the diameter distribution shown in the inset. (b) Distribution of measured  $I_{ON}$  for single s-SWNT transistors. Blue line acts as guide to the eye only. (c) Distribution of simulated  $g_{m,max}$  for single s-SWNT transistors using the diameter distribution shown in the inset of Figure 2.6a. (d) Distribution of measured  $g_{m,max}$  for single s-SWNT transistors. Blue line acts as guide to the eye. (e) Distribution of simulated  $V_T - \langle V_T \rangle$  for single s-SWNT transistors using the diameter distribution of measured  $V_T - \langle V_T \rangle$  for single s-SWNT transistors. Here,  $\langle V_T \rangle$  is the mean  $V_T$  of all the single s-SWNT transistors.

Figure 2.7: (a) Distribution of  $I_{ARRAY}/n$  at  $V_G-V_T = -1V$  in simulated array transistors (single SWNT FET of Figure 2.2 are used as basis), where there are n = 10, 50, 100, 200 and 500 SWNTs in the array FETs, represented by the black, red, green, blue and magenta symbols respectively. (b) Normalized standard deviation of  $I_{ARRAY}/n$  at  $V_G-V_T = -1V$ ,  $\sigma_n/\sigma_1(I_{ARRAY})$ , as a function of n in the simulated array transistor. In the simulation,

Figure 2.7 (continued): n is fixed ( $n = \langle n \rangle$ ) for each of the array-SWNT FET.  $\sigma_n/\sigma_1(I_{ARRAY})$  follows a  $1/\sqrt{n}$  scaling, as expected in any statistical samples. Here, the transistors for any n are considered to have same  $I_{ARRAY}/n$  and  $\sigma_n \equiv \sigma(I_{ARRAY}/n)$ ,  $\sigma_1 \equiv$  $\sigma(I_{ON})$ . (c)  $\sigma_n/\sigma_1(I_{ARRAY})$  of measured array transistors as a function of <n>. The experiment deviates significantly from the  $1/\sqrt{n}$  relationship. Here,  $\sigma_n \equiv \sigma(I_{ARRAY}/\langle n \rangle)$ and  $\sigma_1 \equiv \sigma(I_{ON})$ . Therefore, for a particular n, the array-SWNT FET does not have same number of SWNT and diameter distribution, as assumed in this simulation. (d) Histogram of measured  $I_{ARRAY}/n$  for  $\langle n \rangle = 10$  (blue column bars). Measured distribution matches well with a Log-normal distribution (magenta line) than a Poisson distribution (red line). (e) There is significant deviation of mean  $I_{ARRAY}/n$ ,  $\mu(I_{ARRAY}/n)$ , in our transistors (inset). We scale  $1/\sqrt{n}$  (which is similar to the standard deviation of part b) using  $\sqrt{(\mu_n/\mu_1)}$  (where,  $\mu_n \equiv \mu(I_{ARRAY}/n)$  and  $\mu_1 \equiv \mu(I_{ON})$  to capture the effect of mean  $I_{ARRAY}$  variation (green symbols). Here, we use the Poisson relationship of  $\mu \sim \sigma^2$  for scaling the normalized standard deviation of part b. Consideration of disparity in mean ION causes deviation from the  $1/\sqrt{n}$  relationship. However, such deviation from  $1/\sqrt{n}$  is not comparable to the deviation observed in part c.

Figure 2.8: (a)  $\sigma_n/\sigma_1(I_{ARRAY})$  of simulated array transistors as a function of  $\langle n \rangle$ , where  $\sigma_n$  indicates the standard deviation of  $I_{ARRAY}/\langle n \rangle$ . Blue square symbols consider no variation of n in array SWNT FET and is consistent with  $1/\sqrt{n}$ . Red diamond symbols

Figure 2.8 (continued): consider variation of n in array SWNT FET and deviates from  $1/\sqrt{n}$ . (b)  $\sigma_n/\sigma_1(I_{ARRAY})$  of simulated array transistors as a function of  $\langle n \rangle$ , where  $\sigma_n$ indicates the standard deviation of I<sub>ARRAY</sub>/n. Simulation results (red diamond symbols) are consistent with  $1/\sqrt{n}$  (blue line), which suggests that the calculation of  $\sigma_n$  using I<sub>ARRAY</sub>/n (rather than using I<sub>ARRAY</sub>/<n>, as in part a) can eliminate the effect of n variation in array SWNT FET. (c)  $\sigma_n/\sigma_1(I_{ARRAY})$  of measured array transistors (red symbols) as a function of <n>. Measurement still deviates from  $1/\sqrt{n}$  relationship (blue line), even when the  $\sigma_n$  is calculate using  $I_{ARRAY}/n$ . (d)  $\sigma_n/\sigma_1(I_{ARRAY})$  of simulated array SWNT FET (magenta symbols) as a function of <n>. Simulation considers the effect of density distribution (like part b), wide range of diameter distribution (like Figure 2.5b,c), and  $\mu_n$  variation (like the inset of Figure 2.7e) across the wafer. The  $1/\sqrt{n}$  relation is also shown in blue. (e) Normalized standard deviation of the maximum transconductance  $(g_{ARRAY})$  per SWNT of measured array transistors  $\sigma_n/\sigma_1(g_{ARRAY})$  (where,  $\sigma_n$  is the standard deviation of  $g_{ARRAY}/n$  of array SWNT FET, and  $\sigma_1$  is the standard deviation of g<sub>m.max</sub> for single SWNT FET) of measured array transistors (red symbols) as a function of <n>. Measurement deviates from  $1/\sqrt{n}$  relationship (blue line). (f)  $\sigma_n/\sigma_1(g_{ARRAY})$  of simulated array SWNT FET (magenta symbols) as a function of <n>. Simulation considers the effect of density distribution (like part b), wide range of diameter distribution (like Figure 2.5b,c), and  $\mu_n$  variation (like the inset of Figure 2.7e) across the wafer. The  $1/\sqrt{n}$  relation is also shown in blue.

#### CHAPTER 3:

# INTRINSIC PERFORMANCE VARIABILITY IN ALIGNED-ARRAY CARBON NANOTUBE FIELD EFFECT TRANSISTORS

This chapter was accepted as "<u>Intrinsic Performance Variability in Aligned-Array</u> <u>CNT Field Effect Transistors</u>, S. Salamat, **X. Ho**, J.A. Rogers and M.A. Alam, *IEEE Transactions on Nanotechnology*, PP(99), 1 (2010)" Reproduced with permissions from the journal.

### 3.1 Introduction

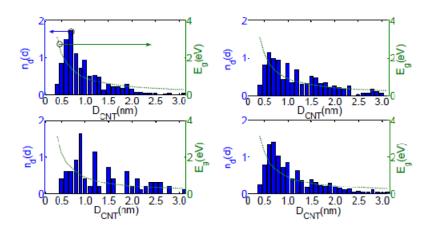

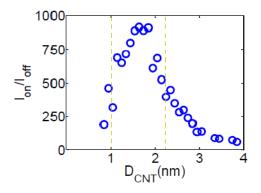

As CNT-nanonet technology explores niche applications in micro [1-5] and macroelectronics [6-10], it is increasingly important to create transistors with nominally uniform characteristics as the basis for large scale circuit integration. Studies based on single tube CNFET have shown that among various transistor parameters, control of tube diameter is most critical, because diameter dictates bandgap and injection barriers, and these two parameters in turn dictate (exponentially) the I-V characteristics of a transistor [11]. The question is: Does diameter distribution play an equally important role in multitube transistors or does the self-averaging, over various tube diameters, obviate the problem? It is well known that in long channel nanonet transistors, the sensitivity of the I-V characteristics on tube diameter is suppressed as electrons percolate through an 'ensemble-averaged' network of tubes with various diameters [7,12]. In short channel aligned-array CNFETs, however, such "path-averaging" may be absent and distribution of CNT parameters (e.g., diameter, mobility, etc.) could be directly reflected in the I-V characteristics. In principle, therefore, short-channel directly-bridging CNFETs using similar device geometries could exhibit significant variation in the on current, especially for ultra-scaled transistors appropriate for high-frequency operation. While the role of the metal/nanotube contact and its effect on device performance for FET with single CNT has been studied by many groups [11, 13-16], the effect of diameter distribution (of CNT array) on FET performance parameters (e.g., Ion, VT, Rd, and Ion/Ioff), especially in the presence of metallic-CNTs, has not been considered. In this paper, we use measured

diameter distribution and transistor characteristics along with systematic theoretical simulations to demonstrate that, of all the parameters, intrinsic process-induced diameter distribution would continue to play a dominant role in dictating the performance of short channel CNT transistors, even if the channel length was scaled to the ballistic limit. Given typical diameter distribution, we find that (i) only a fraction of the tubes carry most of the current (i.e., larger diameter nanotubes, despite being relatively small percentage of the total number of tubes, carry a significant amount of current [ $d_{CNT}$ ~1/ $E_g$ ]) and (ii) depending on the contact material (source/drain), a fraction of the semiconducting tubes behave essentially like metallic tubes (from Off-state to On-state) and must be removed for good  $I_{on}/I_{off}$  ratio.

# 3.2 Fabrication of Nanotube Arrays and Devices

As shown in the Fig. 3.1, the thin-film transistors (TFTs) used in this study are based on perfectly aligned parallel array of single walled carbon nanotubes (SWNTs) as the channel material. The SWNTs were grown directly into such configuration via chemical vapor deposition (CVD) on a specially prepared quartz substrate, using the procedures described in our earlier work [17]. The devices studied here used Palladium (Pd) for source and drain electrodes. Layers of hafnium oxide (HfO<sub>2</sub>) deposited on top of the resulting structure formed the gate dielectric (94±7 nm). Gold (Au) was used as the gate electrode. The gate was aligned to the channel and it overlapped significantly with both the source and the drain (by ~20  $\mu$  m). To study the transport characteristics, we fabricated 6 samples for each channel length of 3, 4, 5 and 8  $\mu$ m (a total of 24 devices). The widths (W) of all the transistors were kept constant at 400  $\mu$  m.

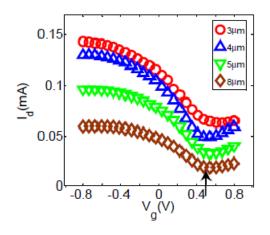

Fig. 3.2 shows typical transfer curves of one sample of each channel length. Consistent with the previous reports [14], these Pd contacted devices exhibited predominantly p-type characteristics.

Remarkably, however, even though all the devices were processed in parallel and used the same metallization scheme, Fig. 3.3 shows that even for samples with the same channel length, the devices exhibited significant variations in the  $I_{on}$ ,  $V_T$  and  $R_d$ . Here,  $I_{on}$

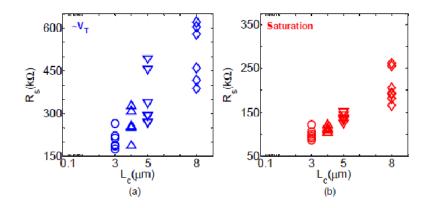

is defined as drain current (I<sub>d</sub>) at maximum applied gate bias (V<sub>g</sub>) of -0.8V, V<sub>T</sub> is defined as the gate bias (V<sub>g</sub>) at which I<sub>d</sub> is minimum [18] (This definition is different from that of MOSFET, wherein V<sub>T</sub> is traditionally defined by taking the point of maximum slope on I<sub>d</sub>-V<sub>g</sub> curve (or linear transconductance) and V<sub>T</sub> is extracted by the intercept of the tangent through the point [19]), and R<sub>d</sub> is the device resistance given by R<sub>d</sub>=V<sub>ds</sub>/I<sub>on</sub> and it includes the resistance of semiconducting as well as metallic tubes. Given that the ratio of metallic-CNTs (m-CNTs) to semiconducting-CNTs (s-CNTs) is ~1:2, we associate I<sub>off</sub> with transport through m-CNTs, and the difference of I<sub>on</sub> and I<sub>off</sub> with transport through semiconducting tubes. The average resistance of each semiconducting tube can be calculated as R<sub>s</sub> = N<sub>s</sub>xV<sub>ds</sub>/(I<sub>on</sub>-I<sub>off</sub>) where N<sub>s</sub> is the number of semiconducting tubes per device (determined from the density measurements of CNTs making up the transistor) and V<sub>ds</sub> is the applied drain bias.

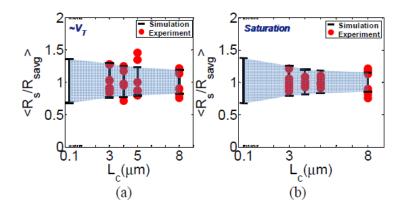

Figs. 3.3a and b summarize the observed fluctuations in the average resistance of semiconducting tubes for various channel lengths, measured at threshold and in saturation. These variations were present for all channel lengths (3, 4, 5 and 8  $\mu$  m), and were particularly large around V<sub>T</sub> (Fig. 3.3a).

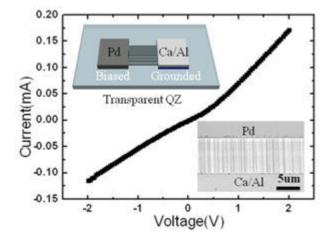

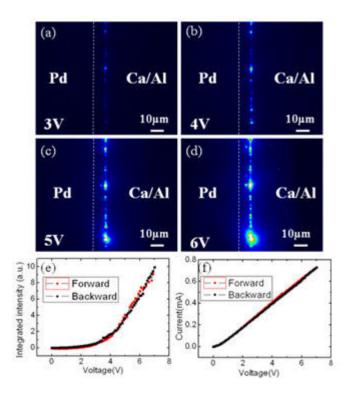

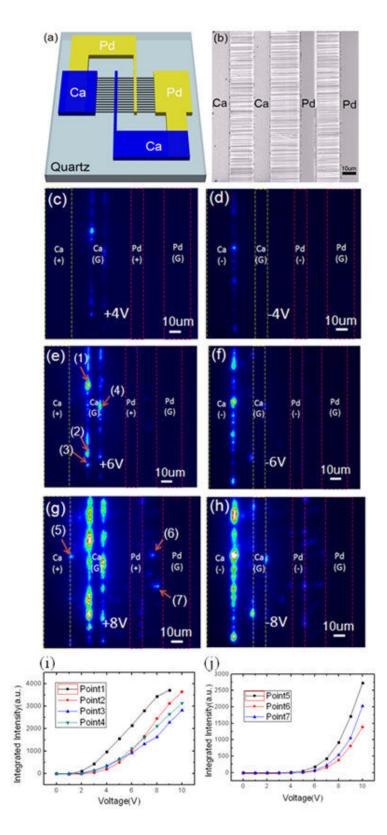

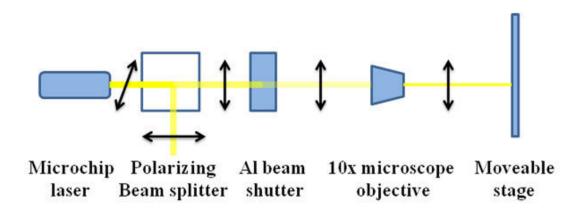

These results immediately bring into focus a number of issues regarding the variability in transistors' performance. It is conceivable that at longer channel lengths, extrinsic factors like mobility fluctuation, variability in the number of tubes able to bridge the source and the drain, length dependent scaling of defects along the tube, etc. can potentially increase device-to-device fluctuation. However, as the devices are scaled down to  $3\mu$ m or less, surprisingly the *relative* fluctuation in resistance remains almost independent of channel length (see Fig. 3.6), suggesting the possibility that this fluctuation may not be averaged out even at ultra-scaled, quasi-ballistic channel lengths (< 300nm) [14] relevant for high-speed electronic applications. While fluctuation at the longer channel lengths may be amplified by extrinsic variability, there appears to be an irreducible intrinsic variability present in all array-based CNT transistors.