Grand Valley State University ScholarWorks@GVSU

**Masters Theses**

Graduate Research and Creative Practice

7-26-2021

# Hardware Acceleration in Image Stitching: GPU vs FPGA

Joshua David Edgcombe

Follow this and additional works at: https://scholarworks.gvsu.edu/theses

Part of the Hardware Systems Commons

#### ScholarWorks Citation

Edgcombe, Joshua David, "Hardware Acceleration in Image Stitching: GPU vs FPGA" (2021). *Masters Theses.* 1018. https://scholarworks.gvsu.edu/theses/1018

This Thesis is brought to you for free and open access by the Graduate Research and Creative Practice at ScholarWorks@GVSU. It has been accepted for inclusion in Masters Theses by an authorized administrator of ScholarWorks@GVSU. For more information, please contact scholarworks@gvsu.edu.

Hardware Acceleration in Image Stitching: GPU vs FPGA

Joshua D. Edgcombe

A Thesis Submitted to the Graduate Faculty of

## GRAND VALLEY STATE UNIVERSITY

In

Partial Fulfillment of the Requirements

For the Degree of

Master of Science in Engineering Electrical & Computer Engineering

School of Engineering

August 2021

#### **Thesis Approval Form**

The signatories of the committee members below indicate that they have read and approved the thesis of Joshua David Edgcombe in partial fulfillment of the requirements for the degree of Master of Science in Engineering, Electrical and Computer Engineering.

07-19-2021 Dr. Chirag Parikh, Thesis committee chair Date 07-19-2021 Dr. Christian Trefftz, Committee member Date Vahech Komble 07-19-2021 Date Dr. Nabeeh Kandalaft, Committee member

Accepted and approved on behalf of the Padnos College of Engineering and Computing

Dean of the College

7/19/21

Date

Accepted and approved on behalf of the Graduate Faculty

Jelly M. Pott

Associate Vice-Provost for the Graduate School

7/26/2021

Date

© Copyright by Joshua D. Edgcombe 2021

All Rights Reserved

# **DEDICATION**

First and foremost, I would like to dedicate this paper to my Lord and Savior Jesus Christ. He is my strength and my rock; my life would not be what it has been without Him.

#### ACKNOWLEDGMENTS

I would like to thank my committee, including Dr. Parikh, Dr. Trefftz, and Dr. Kandalaft for their guidance and help throughout the process of developing and writing this thesis. Additionally, I would like to thank all the professors and faculty that have helped and allowed me to get to this point. Notably, Dr. Dunne, Dr. Ward, and Dr. Brakora for their assistance in achieving admission to the master's program.

I would also like to thank DornerWorks for working with me throughout my time in the master's program. Not only did they provide me time and space to balance fulltime work and thesis studies, but they also provided me access to phenomenal engineers with decades of experience in industry that were always willing to answer questions or give direction. The entire DornerWorks FPGA team was extremely helpful during the FPGA design and development process.

Finally, I would like to thank my family for always being there for me regardless of how difficult balancing my responsibilities became. I could not ask for a better and more reliable support structure than the family I was given.

#### ABSTRACT

#### Hardware Acceleration in Image Stitching: GPU vs FPGA

Image stitching is a process where two or more images with an overlapping field of view are combined. This process is commonly used to increase the field of view or image quality of a system. While this process is not particularly difficult for modern personal computers, hardware acceleration is often required to achieve real-time performance in low-power image stitching solutions. In this thesis, two separate hardware accelerated image stitching solutions are developed and compared. One solution is accelerated using a Xilinx Zynq UltraScale+ ZU3EG FPGA and the other solution is accelerated using an Nvidia RTX 2070 Super GPU. The image stitching solutions implemented in this paper increase the system's field of view and involve the end-to-end process of feature detection, image registration, and image mixing. The latency, resource utilization, and power consumption for the accelerated portions of each system are compared and each systems tradeoffs and use cases are considered.

#### AUGUST 2021

# JOSHUA D. EDGCOMBE, B.S.E., GRAND VALLEY STATE UNIVERSITY M.S.E., GRAND VALLEY STATE UNIVERSITY

Directed by: Professor Chirag Parikh

# **TABLE OF CONTENTS**

| ACKNOWLEDGMENTS                                | 5  |

|------------------------------------------------|----|

| ABSTRACT                                       | 6  |

| TABLE OF CONTENTS                              | 7  |

| LIST OF TABLES                                 | 10 |

| LIST OF FIGURES                                | 11 |

| INTRODUCTION                                   | 13 |

| 1.1 Problem Statement                          | 13 |

| 1.2 Scope                                      |    |

| 1.3 Layout of Thesis                           |    |

| Literature Review                              | 17 |

| 2.1 Field Programmable Gate Arrays             | 17 |

| 2.2 Graphical Processing Units                 |    |

| 2.3 Image Stitching                            |    |

| 2.4 Feature Detection                          |    |

| 2.4.1 Harris-Stephens Corner Detectors         |    |

| 2.4.2 Scale-Invariant Feature Transform (SIFT) |    |

| Scale-Space                                    |    |

| Feature Detection                              |    |

| Feature Description                            |    |

| 2.4.3 Speeded Up Robust Features (SURF)        |    |

| Integral Image                                 |    |

| Box Filters                                    |    |

| Feature Detection                              | 35 |

| Feature Description                            |    |

| 2.5 Image Registration [Homography]            |    |

| Homography Calculation                         |    |

| 2.5.1 Assumption Method                        |    |

| 2.5.2 SVD Method                               |    |

| 2.6 Mixing/Blending                            |    |

| Implementation                                 | 48 |

| 3.1 Development Environments                   |    |

| 3.1.1 FPGA                                     |    |

| 3.1.2 GPU                                      | 49 |

| 3.2 General Design D | ecisions                       | 49 |

|----------------------|--------------------------------|----|

| 3.2.1 Image Pr       | eprocessing                    |    |

|                      | arameters                      |    |

| Domin                | ant Orientation Parameters     |    |

| Feature              | e Description                  | 53 |

| 3.2.3 Matching       | g Parameters                   | 54 |

| 3.2.4 Homogra        | aphy Parameters                | 54 |

| 3.2.5 Image M        | lixing                         | 55 |

| 3.3 FPGA Design      |                                | 55 |

| 3.3.1 Feature I      | Detection Subsystem            | 57 |

| Integra              | l Image                        | 59 |

| Filterir             | ıg                             | 61 |

| Non-m                | aximal Value Suppression (NMS) | 66 |

| 3.3.2 Feature I      | Description                    | 69 |

| 3.4 GPU Design       |                                | 70 |

| 3.4.1 SURF Fe        | eature Detection               | 72 |

| Integra              | l Image                        | 73 |

| Filterir             | ıg                             | 74 |

| Non-m                | aximal Value Suppression (NMS) | 76 |

| 3.4.2 Feature I      | Description                    | 79 |

|                      |                                |    |

| Results & Discussion |                                |    |

|                      |                                |    |

| •                    |                                |    |

|                      |                                |    |

|                      | es                             |    |

|                      |                                |    |

|                      |                                |    |

|                      | у                              |    |

|                      |                                |    |

| Resour               | ces                            | 84 |

|                      |                                |    |

|                      | у                              |    |

|                      |                                |    |

|                      | ces                            |    |

|                      |                                |    |

| •                    |                                |    |

| FPGA                 |                                |    |

|                      | Integral Image                 |    |

|                      | SURF Filtering                 |    |

|                      | Non-maximal Value Suppression  |    |

| GPU                  |                                |    |

|                      | Integral Image                 |    |

|                      | SURF Filtering                 |    |

|                      | Non-maximal Value Suppression  |    |

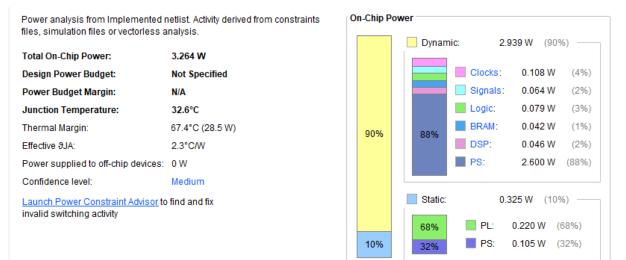

| 4.3.2 Power          |                                | 92 |

| FPGA                |                |     |

|---------------------|----------------|-----|

| GPU                 |                |     |

|                     | es             |     |

| FPGA                |                |     |

|                     | Integral Image |     |

|                     | Filtering      |     |

|                     | NMS            |     |

| GPU                 |                |     |

|                     | Integral Image |     |

|                     | Filtering      |     |

|                     | NMS            |     |

| 4.4 Summary         |                |     |

|                     |                |     |

|                     |                |     |

| 4.4.3 Resourc       | es             |     |

| Future Work         |                |     |

|                     | mprovements    |     |

| Conclusion          |                |     |

|                     | k              |     |

|                     | lts            |     |

| APPENDIX A. Figures |                | 104 |

|                     |                |     |

| Dionography         |                |     |

# LIST OF TABLES

| Table                                         | Page |

|-----------------------------------------------|------|

| Table 1. SURF Implementation Parameters       | 52   |

| Table 2. FPGA SURF Filter Constants           | 65   |

| Table 3. FPGA SURF Implementation Comparisons | 87   |

| Table 4. FPGA SURF Filtering Latencies        | 89   |

| Table 5. FPGA NMS Latencies                   | 89   |

| Table 6. GPU Filtering Latencies              | 91   |

| Table 7. GPU NMS Latencies                    | 92   |

| Table 8. Summary of Test Results              | 101  |

| Table 9. GPU Dxx Filtering Latencies          | 106  |

| Table 10. GPU Dyy Filtering Latencies         | 107  |

| Table 11. GPU Dxy Filtering Latencies         | 107  |

| Table 12. GPU SURF Filtering Latencies        | 107  |

|  | LIST | OF | FIG | URES | \$ |

|--|------|----|-----|------|----|

|--|------|----|-----|------|----|

| Figure                                                                    | Page |

|---------------------------------------------------------------------------|------|

| Figure 1. FPGA Architecture                                               | 18   |

| Figure 2. GPU Architecture                                                | 20   |

| Figure 3. SURF Feature Point Detection                                    | 22   |

| Figure 4. Image Registration (Feature Point Matching)                     | 23   |

| Figure 5. Stitched Image Output Example                                   | 23   |

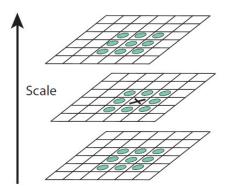

| Figure 6. Scale-Space Example                                             | 27   |

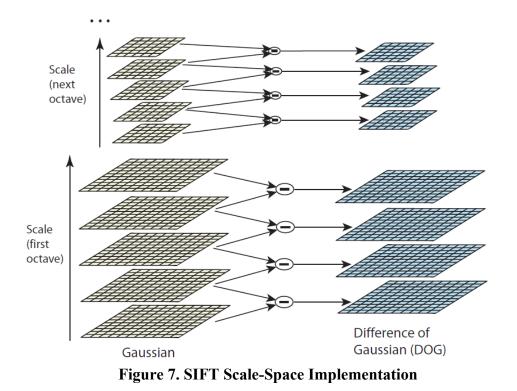

| Figure 7. SIFT Scale-Space Implementation                                 | 28   |

| Figure 8. Non-Maximal Value Suppression                                   | 29   |

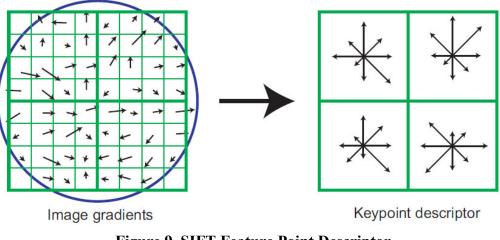

| Figure 9. SIFT Feature Point Descriptor                                   | 31   |

| Figure 10. Integral Image Calculation Example                             | 32   |

| Figure 11. First Order Gaussian Box Filter Comparison (D <sub>x</sub> )   | 34   |

| Figure 12. Second Order Gaussian Box Filter Comparison (Dyy)              | 34   |

| Figure 13. Second Order Gaussian Box Filter Comparison (D <sub>xy</sub> ) | 34   |

| Figure 14. D <sub>xx</sub> Box Filter                                     | 35   |

| Figure 15. D <sub>yy</sub> Box Filter                                     | 36   |

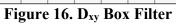

| Figure 16. D <sub>xy</sub> Box Filter                                     | 36   |

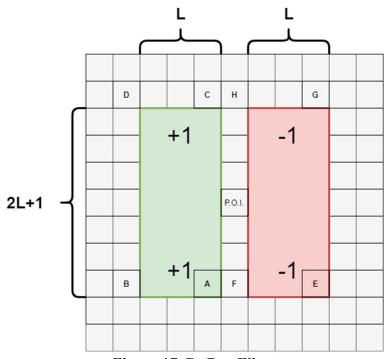

| Figure 17. D <sub>x</sub> Box Filter                                      | 37   |

| Figure 18. D <sub>y</sub> Box Filter                                      | 37   |

| Figure 19. SURF Descriptor Local Region                                   | 42   |

| Figure 20. FPGA Feature Detection High-Level Architecture                 | 56   |

| Figure 21. FPGA – SURF Feature Detection Subsystem                        | 59   |

| Figure 22. Integral Image Calculation Code                                    | 61  |

|-------------------------------------------------------------------------------|-----|

| Figure 23. Integral Image Value Calculation Function                          | 62  |

| Figure 24. D <sub>yy</sub> Filter Value Calculation Processes                 | 63  |

| Figure 25. Signed to Floating Point Standard Logic Vector Conversion Function | 64  |

| Figure 26. SURF Filtered Value Calculation Blocks                             | 66  |

| Figure 27. NMS Calculation and Output Assignment                              | 67  |

| Figure 28. Floating Point Comparison Function                                 |     |

| Figure 29. FPGA 32-bit Feature Point Row, Column, and Octave Encoding         | 69  |

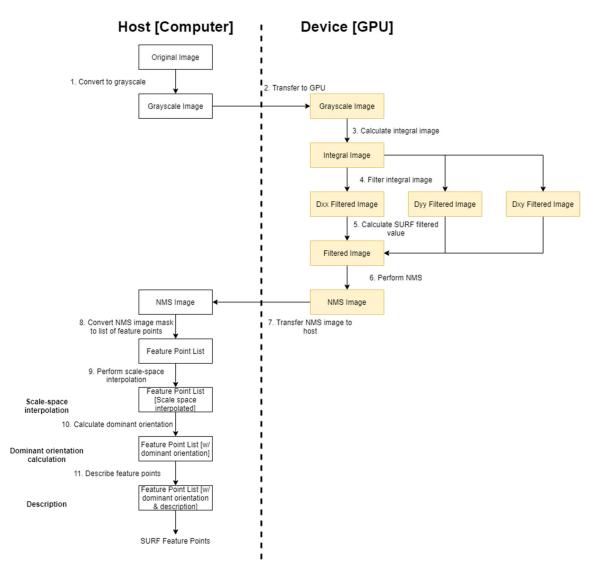

| Figure 30. GPU SURF Algorithm Dataflow Diagram                                | 72  |

| Figure 31. GPU Integral Image Calculation Kernel                              | 74  |

| Figure 32. GPU Accelerated D <sub>xx</sub> Filter Kernel                      | 75  |

| Figure 33. GPU SURF Filter Value Kernel                                       | 76  |

| Figure 34. GPU NMS Comparison Kernel                                          |     |

| Figure 35. FPGA Power Estimates                                               | 93  |

| Figure 36. Power Usage With GPU Accelerated Program Running                   | 94  |

| Figure 37. Post-synthesis resource utilization                                | 95  |

| Figure 38. Post-implementation resource utilization                           | 96  |

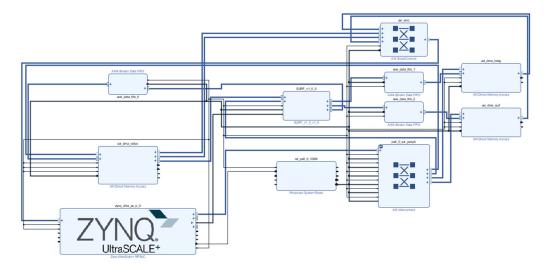

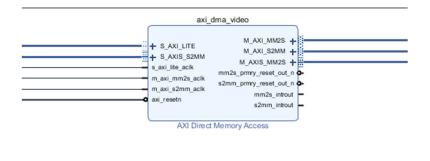

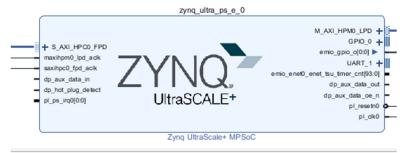

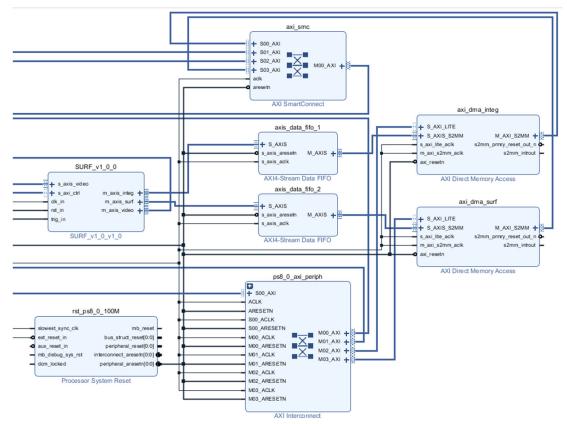

| Figure 39. FPGA Top Level Block Diagram (Full)                                |     |

| Figure 40. FPGA Top Level Block Diagram (Left)                                |     |

| Figure 41. FPGA Top Level Block Diagram (Right)                               |     |

| Figure 42. Nvprof Profiling of GPU Accel                                      | 108 |

#### **CHAPTER 1**

#### **INTRODUCTION**

Two hardware accelerated implementations of an image stitching algorithm are developed and compared in this thesis. The image stitching algorithm is composed of three main components: feature detection and description, feature matching, and image registration. The feature detection and description portion of the algorithm finds sufficiently unique points in an image in a repeatable manner and describes them in a robust and repeatable way. The feature matching portion of the algorithm matches features from one image to similar features in a second image. The image registration process converts the two separate images to a common coordinate system. These three steps make up the core of the hardware accelerated image stitching algorithm used in the image stitching solutions developed.

Looking at the two hardware accelerated image stitching solutions, the latency, resource utilization, and power consumption are analyzed and compared for the accelerated portions of the image stitching process mentioned above. Using the results of these individual comparisons, the full systems are compared and their tradeoffs discussed.

#### **1.1 Problem Statement**

Due to the computational complexity of the image stitching process, power consumption can be high to achieve real-time performance in an image stitching solution. While power is not a concern for all designs, low power solutions are often required for embedded or edge computing solutions. In the past, computationally complex image

processing has been performed using graphical processing units (GPUs), but due to advances in field programmable gate array (FPGA) technology these tasks have become more viable with lower power consumption FPGA devices. The goal of this thesis is to use two common methods of hardware acceleration, FPGAs and GPUs, to develop image stitching solutions used to increase the field of view of a system and then compare them.

#### 1.2 Scope

In this thesis, two hardware accelerated image stitching solutions are implemented and their performance compared. The two methods of hardware acceleration being compared are field programmable gate arrays (FPGAs) and graphical processing units (GPUs). The speeded up robust features (SURF) algorithm [1] is used for the feature detection and description portions of the image stitching process. An exhaustive comparison of two linked lists is used to perform feature point matching. Random sample consensus (RANSAC) is used for matched point selection to calculate the homography matrix for the image registration process. Image mixing is performed using the nearest neighbor method.

While the image stitching algorithms and methodology were kept as similar as possible between the two hardware acceleration methods, design decisions specific to each implementation are noted where they occur. Differences in the algorithms or methodology are only present where hardware limitations prevent the use of the original algorithm or methodology.

The factors to be compared are latency, resource utilization, and power consumption. Latency will be measured from the time the first pixel enters the feature detection portion of the system to the time the first possible feature point location can be

output from the feature detection portion of the system and will be measured in clock cycles. Resource utilization will look at the amount of resources required for the hardware accelerated portion of each implementation and will be measured in percentage of total resources utilized. The effects of the percentage of total resource utilization on each type of hardware will also be discussed. Power consumption will be measured for each solution in watts.

This thesis only covers the portions of the image processing pipeline that are necessary for hardware acceleration of the image stitching algorithm. Implementation details specific to the image processing pipelines for each implementation such as image encoding or decoding, pixel value preprocessing functions such as gamma correction or pixel debayering, camera initialization values and processes, DMA component specifics, and output components such as DisplayPort encoding or windowing systems used will be excluded from description and analysis in this paper to retain a focus on the accelerated image stitching algorithm performance in both systems.

#### **1.3 Layout of Thesis**

The next section of this thesis will cover the literature and background material used as a basis for the implementation of the systems. A quick introduction to FPGAs, GPUs, and the image processing algorithms used in this thesis will be covered at a theoretical level in this section. By the end of this section, the reader will have all the knowledge necessary to understand this thesis on an abstract theoretical level.

The third section will cover the implementation details and design decisions made for each form of hardware acceleration used in this paper. This section will include deeper explanations of the algorithms used to implement the theory discussed in the

previous section as well as implementation details for each form of hardware acceleration. Diagrams will be used to help visualize the high-level organization of the systems on both forms of hardware acceleration. Additionally, the methods used for measuring the performance metrics on each form of hardware acceleration will be covered in this section.

The fourth section will cover the results of the tests performed as well as general comments on the performance of each system. The effects of the differences in the implementation specific design decisions will be considered and different use cases will be discussed in this section.

The final section will discuss potential improvements for future versions of each of the systems and include a discussion of the future of the technologies used in these implementations. With a general understanding of what is included in this thesis, we can now start reviewing the technologies and theory behind the algorithm used for both implementations.

#### **CHAPTER 2**

#### LITERATURE REVIEW

#### **2.1 Field Programmable Gate Arrays**

Field programmable gate arrays (FPGAs) are a type of integrated circuit in which the physical circuitry can be modified using a hardware description language (HDL) such as VHDL or Verilog. The first FPGAs available for purchase were produced by Xilinx in 1984 [2] and were sold as a great solution for achieving near application specific integrated circuit (ASIC) performance while retaining the programmability of software. Depending on the requirements of the system, FPGA implementations are commonly targeted to increase the speed or reduce the power consumption of the device.

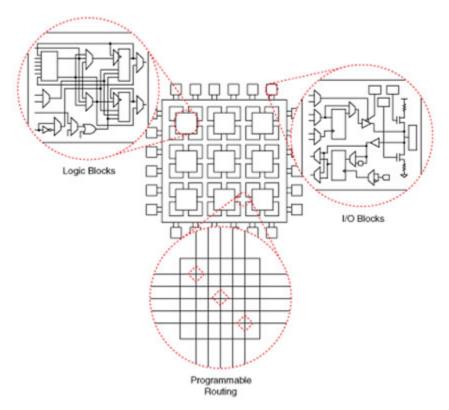

On a high level, the basic architecture of an FPGA involves the connection of input and output pins to functional cores using programmable routing lines. There are a variety of functional components that are available depending on the specific FPGA being considered, but only the most common will be discussed and considered in this paper. A graphical representation of the high-level architecture of an FPGA can be seen in Figure 1 below [3].

**Figure 1. FPGA Architecture**

While the names used to reference the pieces inside an FPGA differ between manufacturers, three main components are common in nearly all modern FPGAs. The three main components common to nearly all modern FPGAs are the memory, logic, and math components. The memory available to an FPGA generally includes on-chip memory, such as block ram (BRAM), look-up tables (LUTs), and registers. Depending on the system, an FPGA can also be given access to off-chip memory such as DDR or SRAM modules. The logic performed on an FPGA uses LUTs and flip-flops to implement any arbitrary logical function that can be defined in HDL. Due to the necessity of floating-point mathematic operations in many modern systems, most modern FPGAs also include floating-point specific algebra blocks. The floating-point algebra blocks available on Xilinx devices are called digital signal processing (DSP) slices and are named DSP slices due to how common floating-point operations are in digital signal processing applications. Modern FPGAs also often include peripherals such as serializer-deserializers (SERDES) for high-speed communication and DDR that can be used on device specific pins. While these three types of modules can generally be found on any modern microcontroller, the big advantage an FPGA provides is the ability to electronically connect these blocks together using HDL into an extremely low latency and time-efficient system.

The ability to electronically connect these blocks together in an arbitrary manner as defined by HDL provides the programmability aspect of FPGAs while providing near ASIC performance. Complex operations can be broken up into many clock cycles to achieve higher clock frequencies and throughput. This is design technique known as pipelining. Additionally, the number of clock cycles necessary to perform certain logical and mathematical operations can be reduced using custom logic, but may result in a lower clock speed for the system. The FPGA also provides cheap and easy parallelization of custom logic operations. Each operational pipeline can be duplicated as many times as the FPGA's resources allow and can all simultaneously access data in a single clock cycle without affecting the performance of the other pipelines if a common data source is used.

The areas that FPGAs can excel in are power consumption, latency, and parallelization. It is worth noting that FPGAs work best on streams of data. The main disadvantage of using an FPGA is the level of expertise required to include one in a system and the relatively low number of qualified and available engineers.

#### **2.2 Graphical Processing Units**

Graphical processing units (GPUs) are a type of integrated circuit designed specifically for accelerating common graphical operations. While different algorithms and hardware were used to accelerate graphical operations prior to GPUs, the first official GPU was produced for sale by Nvidia in 1999 [4]. The first GPUs were sold as a device capable of offloading graphical processing from the CPU and accelerating operations common to computer graphics.

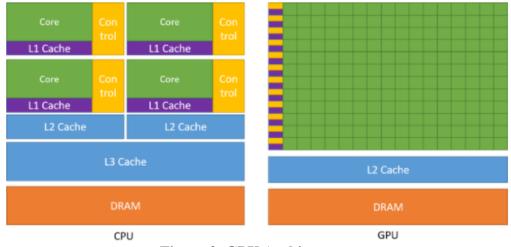

One of the main types of operations GPUs excel at performing is the floatingpoint algebraic operation, particularly when performed on large sets of data. As such, GPUs tend to provide a large amount of high-speed memory resources with many smaller distributed GPU-specific floating point and logical operation processing cores. A highlevel graphical representation of the architecture of a modern Nvidia GPU can be found in Figure 2 below [5].

Figure 2. GPU Architecture

The large memory space is commonly used for image or video frame buffers for the frames being rendered or otherwise manipulated prior to rendering when used for image processing. GPUs are built around the concept of single-instruction, multiple data (SIMD) hardware acceleration. In order to utilize this form of acceleration, latency is introduced when initializing the memory space or transferring data between the host and the GPU device. While latency is introduced when transferring data or initializing memory, performing mathematical and logical operations on the data in the memory space is highly accelerated.

One of the big disadvantages of GPUs is that the actual integrated circuit chips are not as readily available as FPGAs for hardware engineers to get their hands on. Without the ability to buy the individual chips, full personal computer systems generally need to be built to utilize the hardware acceleration that can be gained using the GPU. This increases the cost, reduces the customizability, and increases the power consumption of the system. With that being said, GPUs are relatively easy to obtain with PCI-E connectivity for applications where power is not a central concern.

GPUs are extremely good at applying a series of instructions to an exceptionally large data set in parallel. This advantage makes GPUs very well suited for large linear algebra operations. Another advantage of GPUs is the accessibility of libraries that provide a relatively easy to use programming interface. While there is a slight learning curve for using these libraries and understanding their design principles, learning to write a program to be accelerated using a GPU is much more accessible to a programmer than learning to write HDL for an FPGA.

## 2.3 Image Stitching

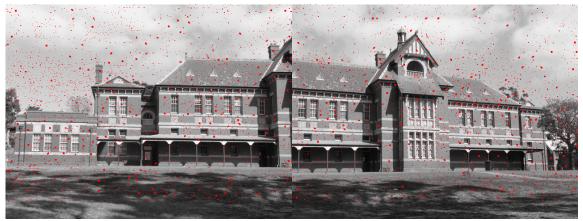

Image stitching is the process of merging together two or more images to create a single image that combines the overlapping field of view of all images to increase the field of view or image quality of a system. In this case, two or more images are being stitched together to create an image mosaic using multiple image sources. The three main steps involved in the image stitching process are feature detection, image registration, and image mixing. Feature detection is the process of finding unique points in an image and describing them in a robust and repeatable manner. Image registration is the process of using the feature points from the feature detection process to map two images to a common coordinate system. Image mixing is the process of combining the two or more images mapped to a common coordinate system in the image registration step into a single output image or video. An example of the steps involved in stitching together two images can be seen in the figures below.

**Figure 3. SURF Feature Point Detection**

Figure 4. Image Registration (Feature Point Matching)

Figure 5. Stitched Image Output Example

## **2.4 Feature Detection**

Feature detection is the process of finding unique points in an image and describing them in a robust and repeatable manner. This means that the performance of a feature detection algorithm can be determined and compared by how likely it is to find the same point in multiple images regardless of differences in lighting, rotation, translation, scale, or other forms of optical noise or transformations. The more likely an algorithm is to find and describe the same location in two or more perspectives of the same scene with a similar, or the same, feature description, the better the performance of the algorithm.

There are a variety of feature detection algorithms available in the field of computer vision and each has their own tradeoffs. For this project, the Speeded Up Robust Features (SURF) algorithm was used because it is known for having a good balance between performance and speed of execution. Originally, the Scale-Invariant Feature Transform (SIFT) algorithm [6] was planned to be used, but resource issues arose during development of the FPGA accelerated solution.

During development of the FPGA accelerated portion of the thesis, floating point resource availability required the switching of the algorithm to a less resource hungry algorithm. With performance comparable to SIFT and a significant reduction in resource usage, SURF was an obvious replacement candidate. In order to understand how SURF functions and where it came from, a quick look at Harris Corner Detectors and the SIFT algorithm is appropriate.

#### 2.4.1 Harris-Stephens Corner Detectors

The Harris-Stephens Corner Detector [7] was one of the first feature detection algorithms used in computer vision. This algorithm starts from the basic idea that the autocorrelation function applied to a region can be used to determine if a pixel is sufficiently different than neighboring pixels. The algorithm works by using the partial derivatives of the autocorrelation function to find pixel locations with high x and y partial derivatives indicating a locally unique point. This algorithm is rotation and translation invariant, but only includes the feature point detection process. Although no feature point description is associated with this algorithm, it is possible to use the SIFT or SURF

feature description algorithms with the Harris Corner Detector algorithm. A deeper explanation of this algorithm can be found in Appendix B.

While the Harris-Stephens Corner Detection algorithm provided a strong method for finding useful features in an image, it was not scale-invariant which is a significant issue for many modern applications of image processing. To achieve scale invariance, one of the best performing modern feature detection algorithms incorporates the concept of scale-space filtering and is called the SIFT algorithm.

#### 2.4.2 Scale-Invariant Feature Transform (SIFT)

SIFT is one of the best performing feature detection algorithms currently available but requires a significant amount of processing to be performed. SIFT, like SURF, can be broken down into two main components: feature detection and feature description. Feature detection is the process of finding distinct points in one or more images with high repeatability. Feature description is the process of describing the detected feature points in a way that they can be matched to other feature points that have similar regional or local pixel values. As an example, describing a point on a car tire using the SIFT feature point description process should be described similarly to, or the same as, other descriptions of the same location on a car tire in other pictures containing car tires regardless of lighting, rotation, blur, scale, etc.

While there are many factors to be considered in these algorithms, the most commonly considered transforms are scale, rotation, and translation invariance. When running multiple images through the feature detection portion of the algorithm, the same points should be found in each image regardless of how the image is rotated, shifted, or how far away the image is taken from any point of interest. Additionally, feature points

detected in regions of overlapping fields of view should be described similarly in all involved images. While rotation and translation invariance has been achieved in previous feature detection algorithms, achieving scale-invariance in the SIFT algorithm is accomplished using scale-space.

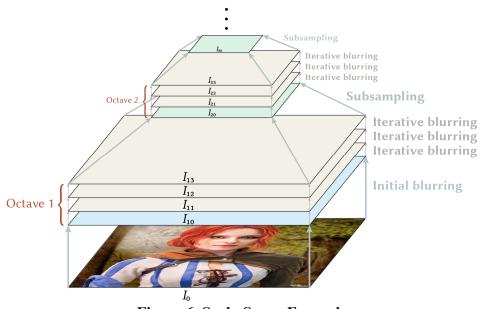

#### **Scale-Space**

The concept of scale-space is used to achieve scale-invariance in the SIFT algorithm. Scale-space was originally discussed by Andrew Witkin in 1983 [8]. The scale-space representation of an image can be used to detect objects or features in a scale-invariant manner. The method approximates how human biological vision works to recognize images at various distances or scales. A scale-space set of images is built by creating a set of images with a gaussian blur applied of up to  $\sigma$ =2. This set of successively blurred images is known as an octave. The next octave is created by subsampling the image blurred to an effective  $\sigma$ =2 value down to a scale of half and thus reducing the loss of information during subsampling to an optimal level. A visualization of the gaussian blur image pyramid used in scale-space can be seen in Figure 6 below [9].

Figure 6. Scale-Space Example

This concept can be used for any number of octaves and filtered levels within the octaves that the algorithm designer desires. The gaussian blur filters being applied to each octave can be either applied iteratively or in parallel to result in an overall gaussian blur level that reduces loss of information between octaves due to subsampling to an optimal level.

#### **Feature Detection**

SIFT accomplishes scale invariance by using a gaussian filtered image pyramid, otherwise known as scale-space. After the image is filtered for all filtered levels of the selected octaves, a difference of gaussian (DoG) calculation is made between adjacent filter levels within the same octave and a non-extrema suppression filter is used to select distinct points from the DoG images. The non-extrema value suppression filter compares the DoG values at one gaussian filter level with the DoG values associated with the neighboring DoG values immediately above and below in the scale-space image pyramid. The SIFT image pyramid can be seen graphically in Figure 7 below [10]. The difference of gaussian is used as a blob detection technique and approximates the Laplacian of the gaussian.

The non-extrema suppression looks for both local maxima and local minima. The only pixels compared are the eight pixels on the current DoG level immediately surrounding the current pixel location in question, the 3x3 DoG area directly above, and the 3x3 DoG area directly below. This results in a 3x3x3 cube determining if the middle pixel value is the local extrema. This can be seen visually in Figure 8 below [10]. This same principle is applied for all desired image scales and octaves with two exceptions per octave. The two DoG layers excluded per octave are the first and last DoG layer in each octave due to the lack of both an upper and lower DoG for comparison. After the feature points have been detected and their scale and location recorded, the feature points are then described.

Figure 8. Non-Maximal Value Suppression

## **Feature Description**

The SIFT algorithm includes the definition of a 128-value feature point descriptor. The feature point's location, scale, and orientation must first be adjusted to be as accurate as possible prior to classification. The interpolated location of the feature point is found using a method for fitting a 3D quadratic function to the feature point and its surrounding sample points [6]. Once the exact location of the feature point is found, the dominant orientation must be calculated.

The dominant orientation of the feature point is found using the magnitude m(x,y)and orientation  $\theta(x,y)$  of the points local to the feature point. The magnitudes of these local points are separated by angle into a 36-bin histogram with each bin representing a ten-degree angle of the full 360 degrees possible. The magnitudes in each bin are then summed to calculate the final bin values. The scale of the feature point is used to determine which Gaussian filtered image, L, to use for these calculations. The formulas used for the magnitude and orientation calculations can be found below.

$$m(x,y) = \sqrt{\left(L(x+1,y) - L(x-1,y)\right)^2 + \left(L(x,y+1) - L(x,y-1)\right)^2} \quad (\text{Eq. 2.4.2.1})$$

$$\theta(x,y) = \tan^{-1} \left( \frac{L(x,y+1) - L(x,y-1)}{L(x+1,y) - L(x-1,y)} \right)$$

(Eq. 2.4.2.2)

The directional bins associated with the largest summed magnitude and the summed magnitudes of the two neighboring directional bins are used as three points to fit a parabola against to determine a more accurate peak orientation. If no dominant orientation can be found due to multiple equal maximum valued directional bins, feature points will be created using the same location and scale, but with each of the different maximum valued orientations found. Once the dominant orientation for the feature point is determined, the descriptor can be calculated

To be used as a SIFT feature point descriptor, a 4x4 matrix of eight-orientation histograms are used to describe a feature point. The 4x4 matrix is created using the location, scale, and dominant orientation from the previous step and using the gradient values of the points local to the feature point. Each histogram represents a 4x4 sample subregion where the sample spacing is determined using the scale of the feature point. The histogram is the summation of magnitudes with orientation values nearest to one of the eight orientations, or nearest 45 degrees, used to describe the region. A scaled down graphical example of what the conversion to a matrix of histograms from a local subsampled region looks like in practice can be seen in Figure 9 below [10].

**Figure 9. SIFT Feature Point Descriptor**

While the figure above uses only a 2x2 array of eight-orientation histograms, the actual algorithm uses a 4x4 array of eight-orientation histograms for the regions surrounding the feature point resulting in a 128-value feature point descriptor. The subregions used to generate the 4x4 array of eight orientation histograms have a dimension of 4x4 sample locations resulting in a total sample region of 16x16 samples surrounding the feature point. All sample points in the 16x16 sample region have their gradient magnitudes binned by orientation, summed with similarly oriented samples in the same subregion, and simplified down to the 4x4 feature point descriptor array. A gaussian filter is applied to the 16x16 full sample region prior to calculating the histogram for all regions. Additionally, the descriptors are normalized to reduce the effect of low contrast regions on the descriptor.

#### 2.4.3 Speeded Up Robust Features (SURF)

The SURF algorithm functions very similarly to the SIFT algorithm but uses several approximations and a few tricks. The core speed-up provided by SURF is gained through the use of box filters instead of exact gaussian filters. These box filters approximate the gaussian filters used in SIFT, but do not result in a significant feature detection performance hit. Even though there is not a significant detection performance disadvantage to using SURF, the box filters allow calculation of a pixel's filtered value using significantly fewer calculations. However, in order to use box filters, an integral image must be created first.

### **Integral Image**

The integral image is used in the SURF algorithm as an intermediary step that greatly increases the performance of the SURF algorithm in later steps. The value of every pixel in an integral image is the sum of the current pixel's intensity and all pixel intensities above and to the left of the current pixel. To demonstrate this visually, an example of a 3x3 block of pixel values can be seen in the figure below. The left side 3x3 block represents the pixel values at each location and the right side 3x3 block represents the integral image values.

|      |   | 0 | 1 | 2 |   | 0               | 1                        | 2                         |

|------|---|---|---|---|---|-----------------|--------------------------|---------------------------|

|      | 0 | 1 | 2 | 3 | 0 | <b>1</b><br>(1) | <b>3</b><br>(2+1)        | 6<br>(3+3)                |

| Rows | 1 | 4 | 5 | 6 | 1 | 5<br>(4+1)      | <b>12</b><br>(5+5+3-1)   | 21<br>(6+12+6-3)          |

|      | 2 | 7 | 8 | 9 | 2 | 12<br>(7+5)     | <b>27</b><br>(8+12+12-5) | <b>45</b><br>(9+27+21-12) |

Columns

Figure 10. Integral Image Calculation Example

An important aspect of creating an integral image is the use of an appropriate number of bits to prevent overflow from occurring during the integral image calculation process. Equation 2.4.3.2 can be used where N represents the number of bits required to store each integral image value, n represents the number of bits used to store each normalized pixel's intensity value, and M represents the total number of values to be summed (the number of pixels in an image).

$$N = n + [\log_2(M)]$$

(Eq. 2.4.3.1)

Once the integral image has been calculated, the SURF algorithm uses the integral image for the filtering process.

#### **Box Filters**

Box filters are used by the SURF algorithm as an approximation to first and second order gaussian filters once an integral image has been calculated. Box filters provide a speed up by allowing the application of filters to be performed with significantly fewer calculations than a typical gaussian filter. While gaussian filters need to apply a different floating point multiplier to all pixels, box filters only need to use the integral image values of a filter's corner locations and don't require any floating point arithmetic.

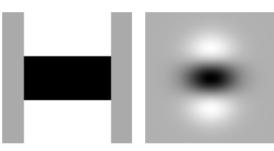

As a comparison of what the integral image will compute versus what the gaussian filters will compute, figures have been included below [10]. In Figure 11, the box filter only requires reading 6 pixel values and performing 7 integer arithmetic operations. In Figure 12, the box filter only requires reading 8 pixel values and 8 integer arithmetic operations. In Figure 13, the box filter only requires reading 9 pixel values and performing 12 integer arithmetic operations.

Figure 11. First Order Gaussian Box Filter Comparison (D<sub>x</sub>)

Figure 12. Second Order Gaussian Box Filter Comparison (Dyy)

Figure 13. Second Order Gaussian Box Filter Comparison (D<sub>xy</sub>)

Due to the use of box filters, the down sampling and filtering used in SIFT is not required to apply the filters to different scales of the image. Instead of down sampling and filtering, the size of the box filters being applied is changed using a filter width value. Only needing to change the filter width value allows the application of filters at various scale-space levels to be applied in parallel on the same base image. This greatly reduces the processing and memory resources required for this algorithm.

# **Feature Detection**

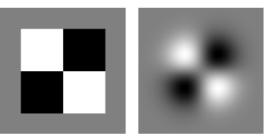

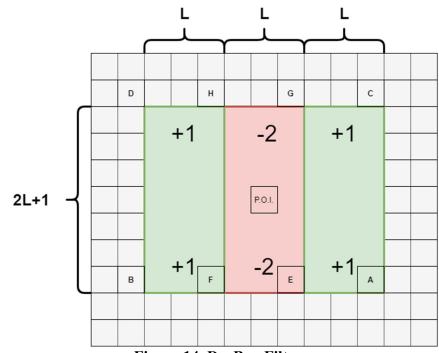

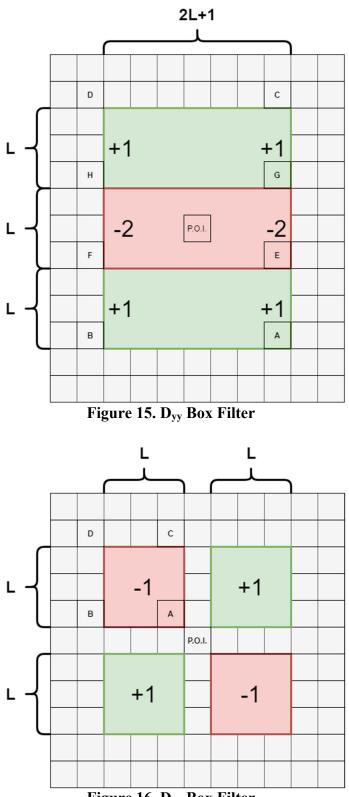

For feature detection in SURF, three box filters are used on the integral image to approximate second order gaussians and two box filters are used on the integral image to approximate first order gaussians. The dimensions of the filters vary based on the filter width parameter L chosen. Examples of the box filters used in the SURF algorithm can be seen in the figures below.

Figure 14. D<sub>xx</sub> Box Filter

Figure 18. D<sub>y</sub> Box Filter

Assuming the letters A through H act as variables to represent the values of the integral image at the location specified in the figures above for D<sub>xx</sub>, D<sub>yy</sub>, D<sub>x</sub>, and D<sub>y</sub>, the value of the filters can be found using the equations below.

$$D_{xx} = (A - B - C + D) - 3 * (E - F - G + H)$$

(Eq. 2.4.3.2)

$$D_{yy} = (A - B - C + D) - 3 * (E - F - G + H)$$

(Eq. 2.4.3.3)

$$D_x = (A - B - C + D) - (E - F - G + H)$$

(Eq. 2.4.3.4)

$$D_y = (A - B - C + D) - (E - F - G + H)$$

(Eq. 2.4.3.5)

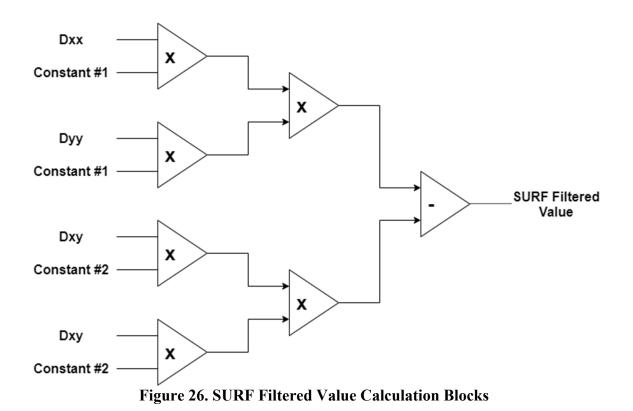

The second order box filters are used to calculate the Determinant of Hessian for a specified filter width L and applied to the integral image using equation 2.4.3.6 below. In this equation the box filters for a specified filter width L for the integral image u are represented as  $D_{xx}^{L}(u)$ ,  $D_{yy}^{L}(u)$ , and  $D_{xy}^{L}(u)$ . The coefficient  $\omega$  is specific to the filter length L and can be calculated using eq. 2.4.3.7.

$$DoH^{L}(u) \coloneqq \frac{1}{L^{4}} \left( D_{xx}^{L}(u) * D_{yy}^{L}(u) - \left( \omega * D_{xy}^{L}(u) \right)^{2} \right)$$

(Eq. 2.4.3.6)

$$\omega = \sqrt{\frac{2L-1}{2L}}$$

(Eq. 2.4.3.7)

Prior to calculating the final SURF filtered value, the values of the box filters must be scale-normalized. Scale-normalization is performed by multiplying the box filter values by constants specific to the filter width. Equation 2.4.3.8 is the constant used for the  $D_{xx}$  and  $D_{yy}$  filtered values. Equation 2.4.3.9 is the constant value used for the  $D_{xy}$ values.

$$6L(2L-1)$$

(Eq. 2.4.3.8)

$$4L^2$$

(Eq. 2.4.3.9)

After the filtered pixel values have been calculated, non-maximal value suppression (NMS) is performed. NMS in SURF, similar to SIFT, is performed on all

filtered pixel values within an octave excluding the first and last filters in the octave. The first and last filters within an octave are excluded because they do not have filters both above and below them for filtered value comparison. The NMS process also uses a minimum value threshold to ensure that noise in low contrast regions is not selected for feature points. Once NMS has been performed, scale-space interpolation is performed to find the exact location and scale at which the feature point should be located.

Scale-space interpolation is used to find the exact location and scale at which the feature point should be located. This process also drops points that are not likely to be a good fit as a feature point. Once this process is complete, the scales and locations of feature points found can be considered continuous values. After the list of feature points has been found, the feature points must be described.

#### **Feature Description**

After a feature point has been found to be sufficiently unique, it must be described. The description process works in two steps. First, the dominant orientation of the feature point is found using box filters for first order gaussian derivative approximations. Once the dominant orientation is found, a 64-value descriptor is calculated by separating the region surrounding the point into sixteen five-by-five subsections. Four values are calculated for each of the sixteen subsections resulting in the 64-value descriptor.

In order to achieve scale-invariance, a scale factor  $\sigma_k$  is used to determine the spacing between samples used for the feature point description process. The equation for the scale factor can be seen in equation 2.4.3.10 where o is the zero-based octave, i is the zero-based filter level within the octave, and L is the filter width parameter.

$$\sigma_{k(L)} = \frac{1.2}{3} (2^o * i + 1) \approx [0.4L_k]$$

(Eq. 2.4.3.10)

The first step in the feature description portion of SURF is determining the dominant orientation of the feature point. The dominant orientation of the feature point is found by binning the magnitudes calculated using the first order gaussian approximation box filters on the integral image based on their orientation. The magnitudes of each sample point are weighted using the distance the sample point is from the feature point using a gaussian function and only values within a  $6\sigma_k$  radius from the feature point's location are considered. The range of orientation angles stored in each bin is determined by the algorithm designer. The weighted magnitudes stored in each bin are then summed to find the final value associated with each bin. This process can be better understood by examining how the process works for a single feature point.

For a feature point k, each sample point within a  $6\sigma_k$  radius from the feature point at an iterative spacing of  $\sigma_k$ , the first order box filters are applied to the integral image. The x and y components found from the previous step are then multiplied by a gaussian weighting value calculated using a standard deviation of  $2\sigma_k$  and centered on the feature point. The values found at this point in the process can be represented by equation 2.4.3.11 where D<sub>x</sub> and D<sub>y</sub> are the box filters approximating the first order Gaussian derivative in the x and y directions, respectively. u(x,y) is the integral image and G is the Gaussian function. The k subscript is used to represent values associated with the feature point being iterated through and is used for determining the appropriate Gaussian weighting value to apply to the sample point of interest.

$$\phi_k(x,y) \coloneqq \begin{pmatrix} D_x \\ D_y \end{pmatrix} \circ u(x,y) \bullet G\left(\frac{x-x_k}{2\sigma_k}, \frac{y-y_k}{2\sigma_k}\right)$$

(Eq. 2.4.3.11)

After calculating and weighting the x and y components for each point within the radius of interest, the magnitudes and directions for each point in the  $6\sigma_k$  radius region are found using equations 2.4.3.12 and 2.4.3.13 below.

$$m(x, y) = \sqrt{x^2 + y^2}$$

(Eq. 2.4.3.12)

$$\phi(x, y) = \tan^{-1}\left(\frac{y}{x}\right)$$

(Eq. 2.4.3.13)

Unlike the one stage of histograms used in SIFT for determining dominant orientation, the SURF algorithm uses a second binning step. The second binning step sweeps the angles between 0 and  $2\pi$  at intervals decided on by the algorithm implementer and associates each possible dominant orientation angle with a second stage bin. The second bins store the sum of magnitude values of first stage bins that represent an angle within the range  $\pm \frac{\pi}{6}$  of the angle associated with the second stage bin being calculated. The second stage bin with the greatest magnitude is chosen as the dominant orientation.

Without the first stage of binning, calculating the summed magnitude associated with any angle  $\pm \frac{\pi}{6}$  would require examining every sample's orientation for every angle considered for dominant orientation. The two-stage binning process reduces the number of algebraic steps associated with calculating the total magnitude within a range of angles. After the dominant orientation has been determined, the 16x4 SURF descriptor vector can be computed.

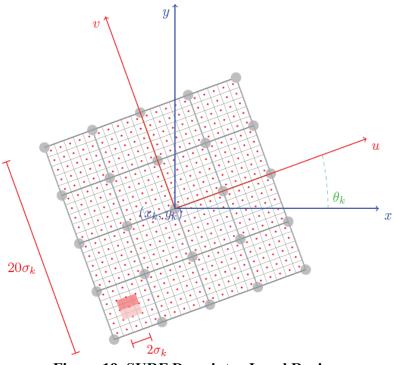

Unlike SIFT, SURF does not use histograms for the feature point descriptor vector. The region surrounding a feature point is sampled as a  $20\sigma_k x 20\sigma_k$  region which is divided into  $4\sigma_k x 4\sigma_k$  subregions, each containing 25 samples, and oriented to the previously found dominant orientation of the feature point as shown in Figure 19 below [10].

Figure 19. SURF Descriptor Local Region

The gradient components are computed by applying the first order box filters to each of the points in the  $20\sigma_k x 20\sigma_k$  region using the integral image with a sample spacing of  $\sigma_k$ . The results are then rotated using a rotation matrix to correct the results to the dominant orientation of the feature point. The rotation matrix and the differential equations to be applied to the region can be found below.

$$R_{\alpha} = \begin{pmatrix} \cos \alpha & -\sin \alpha \\ \sin \alpha & \cos \alpha \end{pmatrix}$$

(Eq. 2.4.3.14)

$$\begin{pmatrix} d_x(u,v) \\ d_y(u,v) \end{pmatrix} \coloneqq R_{-\theta_k} \begin{pmatrix} D_x^{L_k} \\ D_y^{L_k} \end{pmatrix} u(x,y) * G_1 \left( \frac{u}{3.3}, \frac{v}{3.3} \right)$$

(Eq. 2.4.3.15)

Once all the differential function values have been calculated for the full  $20\sigma_k x 20\sigma_k$  region of interest, four values must be calculated for each of the 16 subregions. The four calculated values for each subregion are the sum of the first order filters as applied to each of the points in the subregion and the sum of the absolute values

of the first order box filters applied to the subregions. The four values are combined into a vector for each subregion and ultimately combined to form a 64-value descriptor for the feature point. An example subregion descriptor vector can be found in the equation below for the subregion (i,j) within the group of  $4\sigma_k x 4\sigma_k$  subregions of interest.

$$\mu_{k}(i,j) = \begin{pmatrix} \sum_{(u,v) \in R_{i,j}} d_{x}(u,v) \\ \sum_{(u,v) \in R_{i,j}} d_{y}(u,v) \\ \sum_{(u,v) \in R_{i,j}} |d_{x}(u,v)| \\ \sum_{(u,v) \in R_{i,j}} |d_{y}(u,v)| \end{pmatrix}$$

(Eq. 2.4.3.16)

The full SURF feature point descriptor is created by concatenating all subregion descriptor vectors. The full SURF feature point descriptor is then normalized using  $l^2$  normalization. This step makes the SURF feature point descriptor less susceptible to linear contrast changes.

## 2.5 Image Registration [Homography]

A homography matrix is a matrix which converts the points in two images containing an overlapping field of view to a common coordinate system. The algorithm for calculating the homography matrix requires at least four pairs of matched feature points to be calculated. The matched points are coordinates in two images that correspond to the same physical location in the scene shared by both images. One of the core requirements of homography is that the four selected points must be located on a single plane within the scene.

The issue with homography is that while it maps a common plane from one image to a similar plane in another image, it does not consider the depth of other objects in the scene. This can result in distortion of objects in the scene which are closer or further away than the plane formed by the four matched pairs being used to calculate the homography matrix. A better stitching operation can be performed using the extrinsic camera parameters for the image sensors as well as knowledge of the depths of all objects in the scene but requires more processing to be performed and knowledge which is not always known prior to image processing.

## **Homography Calculation**

The homography matrix calculation starts with a matrix using the coordinates of one of the four matched pairs of feature points. In this matrix, the row and column locations of the first feature point of the matched pair are  $x_i$ ,  $y_i$  while the row and column locations of the second feature point in the matched pair are  $x'_i$ ,  $y'_i$ . Using these coordinates, a matrix can be constructed to represent the matched pair as seen in Eq. 2.5.1 below.

$$A_p = \begin{bmatrix} -x_i & -y_i & -1 & 0 & 0 & 0 & x_i x'_i & y_i x'_i & x'_i \\ 0 & 0 & 0 & -x_i & -y_i & -1 & x_i y'_i & y_i y'_i & y'_i \end{bmatrix}$$

(Eq. 2.5.1)

With four sets of matched feature points, the vectors are row appended to each other to get an 8x9 matrix as seen in the figure below.

$$A_{m} = \begin{bmatrix} A_{p_{1}} \\ A_{p_{2}} \\ A_{p_{3}} \\ A_{p_{4}} \end{bmatrix}$$

(Eq. 2.5.2)

When looking at this matrix as a set of equations, the set of equations is underdetermined by one equation. The homography matrix however only has eight degrees of freedom with the ninth value only representing a scaling factor. It is worth noting that while the scaling value is generally not zero, in special cases it can be zero. Using the full matrix containing all the matched pairs, the homography matrix used to convert the two images to a common coordinate system can be found. The homography matrix is computed using the matrix above in one of two ways, the assumption method or the singular value decomposition (SVD) method.

# 2.5.1 Assumption Method

The assumption method appends a ninth row to the matrix above with all zeros except the last column which contains a value of one. This effectively sets the variable associated with the ninth column, which represents a scaling factor, to one in the system of equations. Forcing the matrix to be critically constrained makes solving for the variables a trivial operation. Converting the new matrix to upper triangular form and using reverse substitution, all the variable values which correspond to the values of the homography matrix can be found.

The advantage of using the assumption method is that it requires less computations and is computationally simpler. These are important factors to keep in mind when working in a resource constrained environment like an FPGA or embedded environment.

The disadvantage of the assumption method is that it is incapable of handling transformations that result in a scale value of zero. A common example of this would be when only rotation is involved in the transformation. In this case, the resulting homography matrix would not accurately model the transformation necessary to find a common coordinate system between the two images.

## 2.5.2 SVD Method

The singular value decomposition (SVD) method uses SVD to find the homography matrix. SVD must be used because the eigenvector associated with the smallest eigenvalue of the system of equations represents the homography matrix with the lowest error that can be used to fulfill the system of equations. The smallest eigenvalue in this case is the eigenvalue closest to zero, not the most negative value. SVD must be used because the matrix is non-square.

The advantage of the SVD method is that it will always return the best approximation of the homography matrix no matter what the transformation involves. This means that a homography matrix can always be calculated and works for all cases.

The disadvantage of the SVD method is that it requires more computations and is more computationally complex. This method is best to be used when compute resources are not constrained or are plentiful.

## 2.6 Mixing/Blending

There are a variety of image mixing algorithms available with the end goal of determining the output value of each pixel. Generally speaking, there are two main methods of combining the pixel values of two or more images: blending and nearest neighbor selection.

The first method involves the blending together of pixels using weighted values based on how far each pixel is from the location of the pixel being determined. After applying a transformation matrix like a homography matrix, the coordinate locations of pixels in an image do not necessarily line up with exact integer locations ((1,0), (1,1), (1,2), etc.) so the output pixel values at each location use neighboring pixels from both

images to determine an appropriate output pixel value. Due to the necessity of calculating the distance from the nearby transformed pixel locations to the current pixel value being calculated, this method requires more arithmetic operations to be performed (resulting in a higher run time), but generally results in a more accurate combination of the images.

The second method, called the nearest neighbor method, simply selects the pixel value of the pixel in the image with a location nearest to the output pixel being determined. This method only uses the nearest pixel if it is within a reasonable distance of the output pixel value being determined. The nearest neighbor method runs much quicker because it does not have the additional step of weighting pixel values based on their distance from the pixel value being calculated. This method generally results in a sufficient quality output frame and has a greatly reduced runtime when compared to the blending method.

Now that the theory and basic pipeline architecture have been covered, the implementation can be considered. While the two forms of hardware acceleration differ greatly, the implementations are kept as similar as possible to the algorithm outlined above. The development environments and libraries used for each implementation will also be presented. Finally, any differences that exist between the implementations and their effects on the performance of each system will be discussed.

## **CHAPTER 3**

## **IMPLEMENTATION**

#### **3.1 Development Environments**

Before diving into the implementation, it is important to consider the development environments used for each implementation. The development environments used can significantly influence the performance and quality of builds for each type of hardware acceleration. Because of these effects, a description of the development environments used for each implementation, and the hardware they were implemented on, has been included in this section.

## 3.1.1 FPGA

The most significant piece of the FPGA build environment is the version of integrated development environment (IDE) used. FPGAs generally require the use of vendor-specific IDEs to utilize their FPGAs and the version of IDE used, depending on the vendor, can greatly affect builds. For this project, the Digilent Genesys ZU-3EG development board was used for implementation. The development board uses a Xilinx FPGA so the Xilinx IDE, Vivado, was required to be used. For this project, Vivado 2019.1 was used due to licensing requirements for IP that was planned to be used for this thesis. The IP that was expected to be used was removed late in the development process, but the use of Vivado 2019.1 continued throughout the remainder of the thesis.

# 3.1.2 GPU

For GPU acceleration of the algorithm, the IDE tends to be much less important than the build tools and libraries used. For general development and build automation, Visual Studio 2019 was used with CMake 3.18.4. OpenCV version 4.5.0-76 was used for image storage and image operations performed on the host computer. OpenCV was chosen because it provides a quick means of retrieving, modifying, and displaying or saving images.

The GPU accelerated implementation used an Nvidia 2070 Super. Nvidia was chosen as the vendor to be used because of the well documented CUDA library available at the time of development. The version of the CUDA compiler, known as nvcc, and its associated library are probably the most significant aspects of the GPU development environment. nvcc version 11.1.74 was used for the GPU compiler. Now that a general description of the development environment has been provided, the general design decisions made for the implementations can be considered.

#### **3.2 General Design Decisions**

In order to reduce the duplication of documentation and descriptions of portions of each implementation that are shared between the projects, a general design decision section has been included. In this section, constants that are used in both implementations as well as concepts that are applied similarly or the same between the projects are introduced and covered. This reduces duplication of information in the document and provides a central location for parameter specifics for both implementations. This section will start with the image preprocessing portion of the implementations and work all the way through to the image mixing portion of the pipeline.

#### **3.2.1 Image Preprocessing**

Prior to running the image through the feature detection portion of the image processing pipeline, the image must first be preprocessed. First, all pixels must be converted from the three value RGB colored pixel representation associated with each pixel to a single pixel intensity value associated with each pixel. For both implementations, an 8-bit average of the three color components was used to calculate the pixel intensity value.

The pixel intensity values can be normalized throughout the entire image to reduce the effects of low contrast images on feature detection. The normalization process involves finding the maximum and minimum pixel intensity values in an image and scaling all pixel intensity values in the image to reflect the maximum possible range. The normalization process was not performed for either of the acceleration methods because it requires the system to know all pixel intensity values in a system prior to normalization. This cannot be assumed for both implementations.

Methods for approximating the maximum and minimum pixel intensity values for a frame were considered, but the image stitching pipeline worked sufficiently well without the normalization step so normalization was not implemented. The equation used for normalization is included below as equation 3.2.1.1 where n is the number of bits used to store each pixel intensity value,  $i_{min}$  is the minimum pixel intensity value in the image,  $i_{max}$  is the maximum pixel intensity value in the image, i is the pixel intensity value being normalized, and I is the normalized pixel intensity value.

$$I = (2^{n} - 1) * ((i - i_{min})/(i_{max} - i_{min}))$$

(Eq. 3.2.1.1)

An integral image can be calculated directly from the pixel intensity image, but performing the SURF filtering process on the integral image calculated directly from the pixel intensity image results in an unusable region of filtered values around the border of the image. This can be solved by either padding the integral image out or excluding the unusable region from the feature detection process. Both methods were tested and a significant difference was not observed in the performance of the algorithm using either of the two methods. The exclusion region method was chosen and implemented on both forms of acceleration due to ease of implementation.

# **3.2.2 SURF Parameters**

The portion of the image stitching pipeline that was accelerated for both implementations was the SURF feature detection algorithm. The SURF implementation used in this thesis uses three octaves with three filter widths per octave. The filter width values L and the coefficient values  $\omega$  used in the filter calculations for both implementations can be found in the table below. The filter width value L is used to determine the dimensions of the box filters used in the calculation of the SURF filtered values. The  $\omega$  value functions as a coefficient within the SURF filtered value calculation. The organization of octaves, filters, and their corresponding  $\omega$  coefficient can be found summarized in Table 1 below.

| Table 1. SURF | Implementatior | <b>Parameters</b> |

|---------------|----------------|-------------------|

|---------------|----------------|-------------------|

| Octave | L  | ω(L)   |

|--------|----|--------|

| 1      | 3  | 0.9129 |

| 1      | 5  | 0.9487 |

| 1      | 7  | 0.9646 |

| 2      | 5  | 0.9487 |

| 2      | 9  | 0.9718 |

| 2      | 13 | 0.9806 |

| 3      | 9  | 0.9718 |

| 3      | 17 | 09852  |

| 3      | 25 | 0.9900 |

Following SURF filtering, non-maximal value suppression is performed. For nonmaximal value suppression, each pixel is compared with its 26 neighboring pixels in addition to a minimum hessian threshold value. A hessian threshold of 1000.0 was used for both implementations. Sample spacings of 1, 2, and 4 were used for octaves 1, 2, and 3 respectively when performing NMS. Once NMS has been performed, the remainder of both pipelines is performed in software without hardware acceleration.

## **Dominant Orientation Parameters**

When determining the dominant orientation of the feature point for feature point description, a two-step process was used. First, the  $D_x$  and  $D_y$  values for all points within a  $6\sigma_k$  radius were calculated at an interval of  $\sigma_k$ . The  $D_x$  and  $D_y$  values were used to calculate a magnitude and orientation associated with each sample point. The magnitude

values were multiplied by a gaussian filter function reducing the effects of values further away from the point of interest prior to first stage binning. The magnitude associated with each point was then grouped into 20 different equal range angular regions based on orientation. The values stored in the bins were summed which resulted in 20 angular region bins which stored the sum of all magnitudes whose dominant orientation corresponded to that angular region.

After all the magnitudes of the points within the  $6\sigma_k$  radius were categorized into their associated angular region bins, these bins were used to find the dominant orientation. To find the dominant orientation, 20 different angles were considered. For each angle being considered, all bins whose range of angles were within  $\pm \frac{\pi}{6}$  of the current orientation being examined were summed. Once all 20 different orientations had summed the angular region bins whose regions fell within the  $\pm \frac{\pi}{6}$  range of angles, the orientation with the highest summed bin value was selected as the dominant orientation.

## **Feature Description**

The remainder of the feature description process is performed using relatively similar code for both systems. Once the row-column location, scale, and dominant orientation for each feature point was found and stored, the feature point is described using the feature point description process described in section 2.4.3. Other than the number of bins used in the dominant orientation calculation, the feature point description process has no parameters specific to either implementation to be described and an indepth explanation of its functionality has been excluded from this section as such.

#### **3.2.3 Matching Parameters**

Matching is performed using a brute force method of matching one list of feature points to another. The error is calculated between each point on one list and all points on the second list. The lowest two errors are tracked for each feature point so that relative error matching can be performed. If the lowest error is lower than the second lowest error multiplied by a relative coefficient less than one, the point is treated as a match. The relative matching value of 0.15 was found to work well during testing and used for both implementations.

## **3.2.4 Homography Parameters**

Homography is calculated using four sets of matched feature locations and the assumption method. This means that an 8x9 matrix is constructed using the four sets of matched feature locations and a ninth row is appended with all zeros and a final column value of one. This matrix is solved by converting it to an upper triangular matrix and using substitution to solve for the homography matrix values. The resulting homography matrix is then normalized using the scale value in the homography matrix. The scale value in the homography matrix is the value in the last row and column of the matrix.

Once a homography matrix is found, it is applied to the location of all feature point matches from the secondary image used in the homography calculation. Error is calculated using the sum of the Euclidean distances between primary image locations and transformed secondary image locations for all matched feature points. Assuming more than four matched pairs of feature points were found, the homography calculation is performed using four randomly selected matched feature point pairs, applied to the secondary image feature point locations, and the error is calculated. The homography

matrix with the lowest error is then accepted as the best homography matrix. The repetition of these calculations and the selection of the homography matrix with the lowest associated error is how RANSAC was implemented with 2000 iterations. Once an appropriate homography matrix has been found, image mixing can be performed.

## 3.2.5 Image Mixing

To perform image mixing, the primary image was centered within the output frame and the secondary image was transformed using the best homography matrix found. The nearest neighbor method of image mixing is used so the pixel values of the image centered in the output frame always take precedence in the output frame. The pixel values associated with the transformed image then fill in the output frame outside of the non-transformed image. Both implementations use OpenCV to apply the homography matrix to the secondary image, mix the two images together, and output the mixed image to a new window.

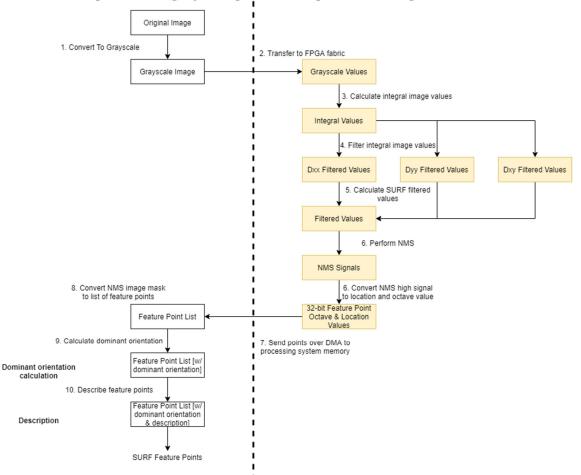

## 3.3 FPGA Design

For the FPGA accelerated portion of the thesis, acceleration was used for image preprocessing and the feature detection portion of the pipeline. The choice to accelerate only this portion of the pipeline is mainly due to the large resource utilization required for parallelizing the application of all the different SURF filters being applied to a common set of data. Once the feature point locations have been found, they are passed with the calculated integral image to the systems DDR memory via DMA. The remainder of the processing performed by the image stitching pipeline is performed using the FPGA's

integrated hardcore ARM processing subsystem. A high-level architecture of the FPGA

feature detection portion of the pipeline can be seen in the figure below.

Host [Processing System] · Device [FPGA Fabric]

Figure 20. FPGA Feature Detection High-Level Architecture

Once the processor receives the feature point locations and their associated filter widths along with the integral image, feature point description can occur. Feature points are appended to a linked list and the feature points found in the exclusionary region around the border of the image are discarded. The number of linked lists for the feature points retained during processing is equal to the number of image sources used. Once all the feature points have been described for at least two input images, the feature point lists are supplied to the feature matching code.

Feature matching is performed using a brute force comparison of all points between the two linked lists of feature points using a relative matching criterion. The brute force comparison process tracks the two lowest feature point description errors using two variables. When the two lowest errors fulfill the relative matching criteria after iterating through all possible matches, the feature point associated with the lowest error and the feature point being considered are considered a match. A match is indicated using a nonzero pointer value stored in the linked list struct associated with each feature point. Once all feature point matches have been found, the homography calculation is performed using RANSAC.

After the homography matrix is found, it is supplied to the host computer via a UART serial communication link. The mixing of the two images is then performed on the host computer using OpenCV and displayed to the user in a new window.

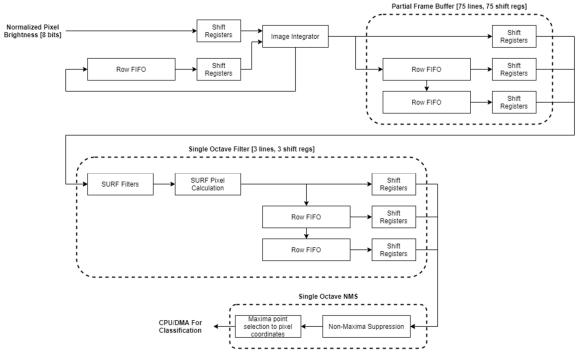

#### **3.3.1 Feature Detection Subsystem**

The accelerated feature detection portion of the FPGA image stitching pipeline can be broken down into three steps: integral image calculation, filtering, and nonmaximal value suppression. The integral image calculation takes in the image intensity value associated with each pixel and outputs the associated integral image value for that pixel. The filtering portion takes as input the integral image values and outputs SURF filtered values. The non-maximal value suppression portion takes as input the SURF filtered values and outputs a signal that goes high when a local maximum value is found.

These three steps make up the hardware accelerated portion of the FPGA image stitching pipeline.

For the integral image calculation to work on the stream of pixel intensity values, the pixel intensity of the location being calculated and the integral image values of the pixels to the left, above, and diagonally above and to the left are required. A single row buffer is used to store the integral image values from the row above the current row with two shift registers to store the integral image values directly above and diagonally above and to the left. These input values are used by the image integrator block to calculate and output the integral image values to the partial frame buffer.

The SURF filtering portion of the pipeline uses the partial frame buffer to calculate SURF filtered values. The partial frame buffer provides an area of 75 by 75 integrated image pixels. The partial frame buffer values are used by the SURF second order partial derivative box filters. There are seven unique SURF filter widths used to constitute the nine filters split between the three SURF octaves. The outputs of the filters are then used to calculate the SURF filtered pixel value in the SURF pixel calculation block. There is one SURF pixel calculation block per unique filter width.