# A new high speed charge and high efficiency Li-Ion battery charger interface using pulse control technique

# Mustapha El Alaoui<sup>1</sup>, Karim El Khadiri<sup>2</sup>, Rachid El Alami<sup>1</sup>, Ahmed Tahiri<sup>2</sup>, Ahmed Lakhssassi<sup>3</sup>, Hassan Qjidaa<sup>1</sup>

<sup>1</sup>Laboratory of Computer Science, Signals, Automation and Cognitivism (LISAC), Department of Physics, Faculty of Sciences Dhar El Mahraz, Sidi Mohamed Ben Abdellah University, Fez, Morocco

<sup>2</sup>Laboratory of Computer Science and Interdisciplinary Physics (LIPI), Normal Superior School Fez (ENSF), Sidi Mohamed Ben Abdellah University, Fez, Morocco

<sup>3</sup>Department of Computer Science and Engineering, University of Quebec in Outaouais, Gatineau, Canada

#### **Article Info**

# Article history:

Received Mar 24, 2021 Revised Sep 29, 2021 Accepted Oct 25, 2021

#### Keywords:

Constant current mode control Constant voltage mode control Li-Ion battery charger interface Low drop out based Pulse control technique Switching power supply based

## ABSTRACT

A new Li-Ion battery charger interface (BCI) using pulse control (PC) technique is designed and analyzed in this paper. Thanks to the use of PC technique, the main standards of the Li-Ion battery charger, i.e. fast charge, small surface area and high efficiency, are achieved. The proposed charger achieves full charge in forty-one minutes passing by the constant current (CC) charging mode which also included the start-up and the constant voltage mode (CV) charging mode. It designed, simulated and layouted which occupies a small size area 0.1 mm<sup>2</sup> by using Taiwan Semiconductor Manufacturing Company 180 nm complementary metal oxide semiconductor technology (TSMC 180 nm CMOS) technology in Cadence Virtuoso software. The battery voltage V<sub>BAT</sub> varies between 2.9 V to 4.35 V and the maximum battery current I<sub>BAT</sub> is 2.1 A in CC charging mode, according to a maximum input voltage V<sub>IN</sub> equal 5 V. The maximum charging efficiency reaches 98%.

This is an open access article under the <u>CC BY-SA</u> license.

## **Corresponding Author:**

Mustapha El Alaoui Laboratory of Computer Science, Signals, Automation and Cognitivism (LISAC), Department of Physics, Faculty of Sciences Dhar El Mahraz, Sidi Mohamed Ben Abdellah University B.P. 1796 Fez-Atlas, 30003, Fez, Morocco Email: mustapha.elalaoui@usmba.ac.ma

#### 1. INTRODUCTION

Battery is an assembly of electrochemical accumulators that are reversible generators. The electrical energy is stored as chemical form in the accumulator to be restored at any time on demand thanks to the reversibility of the transformation. An oxidation-reduction reaction is activated when a load is connected to the terminals of an elementary cell between two electrodes bathed in an electrolyte.

Li-Ion batteries are more usable in mobile electrical devices that require a powerful and light battery, as it produces a high storage density based on the low density. It can be divided into several types LiFePO<sub>4</sub>, LiCoO<sub>2</sub>, LiNiMnCoO<sub>2</sub> and LiMn<sub>2</sub>O<sub>4</sub> exist according to their application such as telecommunications, laptops, electric bicycles and electric vehicles, respectively. This advantage makes it possible to choose the right technology or type for the particular application required. In today's automotive industry, Li-ion batteries are the best alternative to automotive fuel because they have the potential to be the answer to the challenges faced by automakers to provide solutions to the growing oil shortage and reduce the environmental impact of vehicles. Despite still significant constraints (recharging time, energy density, cost), the competitiveness of these batteries has already revived interest in electric vehicles. The well-known charger solutions are essentially classified into two types: Low-drop-out (LDO) based charger and the switching-power-supply (SPS) based charger [1]. The choice of the technique to be used depends on the application to which it will be integrated. Table 1 provides a comparison between the two most popular types of charger solutions.

| Table 1. The LDO-based charger versus the SPS-based |                     |                   |  |  |  |  |  |  |

|-----------------------------------------------------|---------------------|-------------------|--|--|--|--|--|--|

| Performances                                        | SPS-based charger   | LDO-based charger |  |  |  |  |  |  |

| Input voltage range                                 | Large               | Low               |  |  |  |  |  |  |

| Complexity                                          | Medium              | Low               |  |  |  |  |  |  |

| Efficiency                                          | High                | Low               |  |  |  |  |  |  |

| Size                                                | Lower at high power | Small-medium      |  |  |  |  |  |  |

The use of the SPS technique with a low-pass filter to lower the input voltage, lower losses can be achieved than with LDO-based chargers [2], [3]. It gives a wide input/output voltage range [4] and also requires an advanced circuit design to achieve high efficiency. In addition, the maximum charging battery current is ranging from 300 mA to 2 A. Furthermore, the SPS chargers cost a lot of disadvantages, such as worse noise repudiation upon ripple at a SPS rate, and increased power consumption [5]. The size chip of the SPS-based chargers is smaller at high power. The several implementations of the SPS-based chargers are exposed in [6]–[12].

On the other hand, LDO-based chargers are based on a pass transistor to drop the excess input voltage in order to obtain an output regulation by modulating its resistance. Simplicity at the trouble of a poor efficiency and small size (for low to medium power) are the main advantages of it. The LDO-based charger meets these requirements due to its low ripple current and can be inserted into the chip without a descriptive component [13]. In addition, the maximum charging battery current is ranging from 350 mA to 1 A. Among the big problems for it is the low efficiency. Therefore the integration of a power-MOS is a solution to its low efficiency and also to minimize its loss [14]. The several implementations of the LDO-based chargers are exposed in [15]–[18]. To minimize the complexity of circuit design through CMOS technology improvements, LDO-based chargers and SPS-based chargers are usually inserted on a single chip. Subsequently, to reduce the noise and ripple effect, the battery charger interface (BCI) is merged into a system-on-chip (SoC) [4].

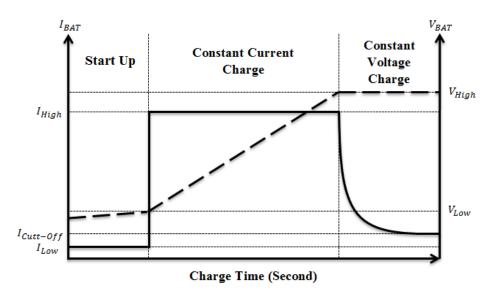

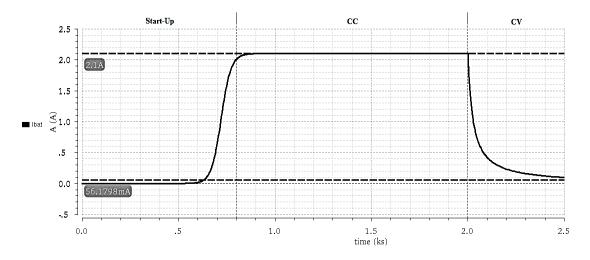

The three-step Li-Ion battery charging modes are shown in Figure 1. The first one is the start-up, the second one is the constant current (CC) charge and the last one is the constant voltage (CV) charge [19]. In the first step start-up, the battery current ( $I_{BAT}$ ) is maintained at a constant low value when the battery voltage ( $V_{BAT}$ ) is lower than the low voltage ( $V_L$ ), this helps protect the battery from damage caused by overheating. Also in the second step CC, the battery is charged with a strong constant current (which minimizes the charging time) when  $V_{BAT}$  is between  $V_L$  and high voltage ( $V_H$ ). Finally in the last step CV, the  $I_{BAT}$  drops at the cut-off (the charging process ends) when the  $V_{BAT}$  rises to the specification value of the  $V_H$ .

This paper focuses on the design of a SPS-based charger (mass charger), which is well suited for operation between CC mode and CV mode by the pulse control (PC) technique to achieve high efficiency and to ensure that the battery is quickly fully charged. We presented this article at the following: section 2 presents our proposed charger design using the PC technique; section 3 presents the simulation results of our charging circuit; and we conclude in section 4.

# 2. PROPOSED CHARGER DESIGN USING THE PULSE CONTROL TECHNIQUE

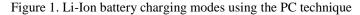

The high efficiency, the large output current and also the constant output supply voltage are the most important results to be achieved in the design and modelling of a Li-Ion BCI using Taiwan Semiconductor Manufacturing Company 180 nm complementary metal oxide semi-conductor technology (TSMC 180 nm CMOS) technology. To achieve a solution of the low efficiency, low output current and an instable output supply voltage that is the big problem for many researchers in this field, we proposed a new charger design using the PC technique illustrated in Figure 2. It depends of pulse width modulation ( $S_{CC}$ ) signal who is acting in CC charge mode and pulse frequency modulation ( $S_{CV}$ ) signal who is acting in CV charge mode. That makes balancing the efficiency between the batteries charging procedure. Also the automatic selection between  $S_{CC}$  and  $S_{CV}$  is ensured by the use of logic circuits with the reduction of the conversion loss and ensuring the average efficiency.

Figure 2. The proposed design of the Li-Ion BCI using PC technique

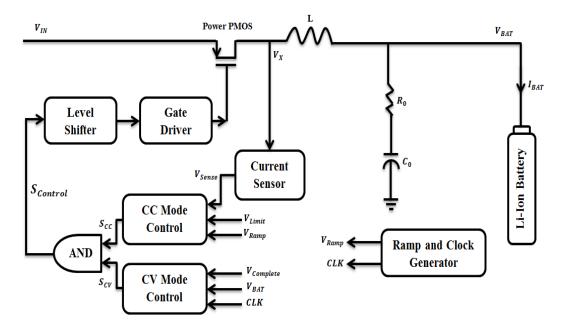

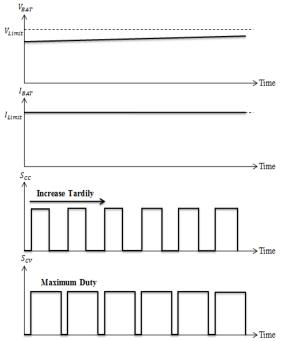

At startup, the  $S_{CV}$  signal is initially set to its maximum charge ratio to ensure that the charger operates in CC charging mode and not in CV charging mode. When the battery is empty, the  $I_{BAT}$  increases rapidly with the increasing  $S_{CC}$  signal until the  $I_{BAT}$  reaches the current limit  $I_{Limit}$  as shown in Figure 3. The  $I_{BAT}$  will gradually decrease if the  $S_{CC}$  signal is maintained at the same level due to the gradual increase in the  $V_{BAT}$  as shown in Figure 4. Therefore, the  $I_{BAT}$  remains stable, depending on the slow increase of the  $S_{CC}$ signal.

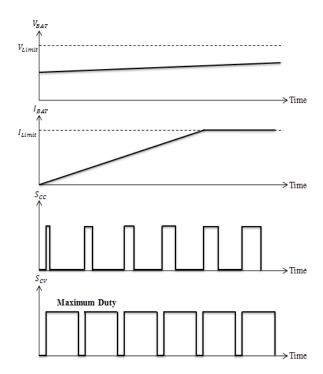

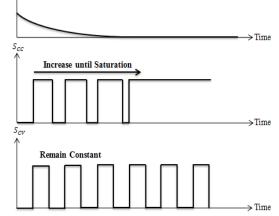

The duty-cycle of the CC-CV begins to reduce whenever the  $V_{BAT}$  approximates the  $V_{Limit}$  as shown in Figure 5.  $V_{BAT}$  and  $I_{BAT}$  reach  $V_{Limit}$  and  $I_{Limit}$ , respectively, when the  $S_{CV}$  is exactly the same as the  $S_{CC}$ . The duty-ratio of  $S_{CV}$  remains the same to keep the VBAT constant, while the  $I_{BAT}$  gradually decreases and also the duty-ratio of  $S_{CC}$  continues to increase and eventually saturates as illustrated in Figure 6. The proposed charger design of Li-Ion BCI using PC Technique is illustrated in Figure 2 which includes six subcircuits: the CC mode-control block, the CV mode-control block, the current-sensor, the level-shifter, the gate-driver and the Ramp-clock generator.

The CC mode is activated to set the signal  $S_{CC}$  by the comparison between the predefined limit voltage  $V_{Limit}$  and the sensing voltage  $V_{Sense}$  which is generated by the current sensor block. In addition The

CV mode is activated to set the signal  $S_{CV}$  by the comparison between the  $V_{BAT}$  and the predefined complete voltage  $V_{Complete}$ , it ensures the regulating of the  $V_{BAT}$ . To select either the  $S_{CC}$  or the  $S_{CV}$  as the  $S_{Control}$  signal, an AND logic gate is used. The operating principle of each block has been described.

VBAT

Figure 3. Curve forms of the  $V_{BAT}$ ,  $I_{BAT}$ ,  $S_{CC}$  signal and  $S_{CV}$  signal in start-up charge mode

$V_{Limit}$   $\rightarrow$  Time  $I_{BAT}$   $\rightarrow$  Time

Figure 4. Curve forms of the  $V_{BAT}$ ,  $I_{BAT}$ ,  $S_{CC}$  signal

and S<sub>CV</sub> signal in CC charge mode

Figure 5. Curve forms of the  $V_{BAT},\,I_{BAT},\,S_{CC}$  signal and  $S_{CV}$  signal in transition between CC and CV charge modes

A new high speed charge and high efficiency ... (Mustapha El Alaoui)

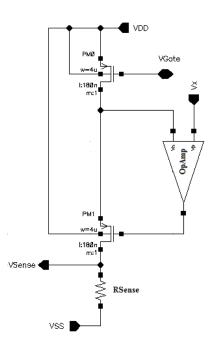

#### 2.1. The CC mode control block

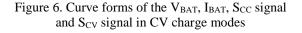

Figure 7 shows the schematic of the CC mode control block. The high speed comparator used in the input of the block to compare between  $V_{Sense}$  and  $V_{Limit}$ . Then, the Bascul-D uses as input the high-speed comparator and the descending fronts of the  $S_{Control}$  signal to trigger it. The proper comparison results are assured by the use of the Bascul-D logic gate. The charging or discharging the  $C_{CC}$  capacitor is provided by a pair of current-source and sink-pairs that are controlled by Q and NOT Q which are the outputs of the Bascul-D logic gate.

Figure 7. Schematic of the CC mode control block

Also, the use of a second high-speed comparator in the output of the CC mode control block allows determining the duty cycle of the  $S_{CC}$  signal by comparing the  $C_{CC}$  capacitor voltage  $V_{CC}$  with a sawtooth waveform  $V_{Ramp}$ . Finally, the start-up function is also performed by the control unit in CC mode control block, because the  $V_{CC}$  is charged by the  $I_{Bias}$  from zero, so that it also gradually increases from zero, for that, the increase of the  $C_{CC}$  or the decrease of  $I_{Bias}$  makes the prolongation of the start-up time. The increase rate of  $V_{CC}$  can be expressed by the (1):

$$\frac{\mathrm{d}V_{\mathrm{CC}}}{\mathrm{dt}} = \frac{\mathrm{I}_{\mathrm{B}}}{\mathrm{C}_{\mathrm{CC}}} \tag{1}$$

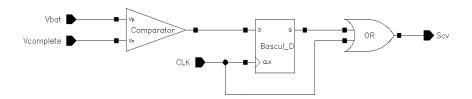

## 2.2. The CV mode control block

....

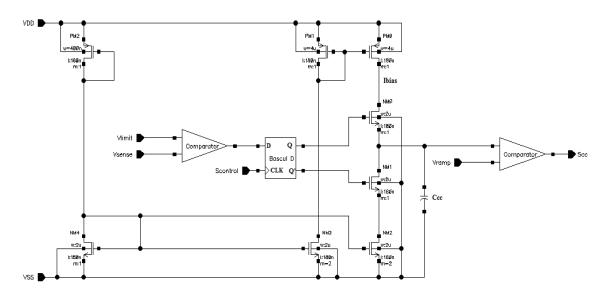

Figure 8 illustrates the circuit of the CV mode block. The charger is confronted with a light charging scenario when the  $V_{BAT}$  is about equal to the value of the  $V_{Complete}$ . However, the  $S_{CV}$  will be selected in front of the  $S_{CC}$  by using an AND logic gate as illustrated in Figure 2, this allows to maintain the light load efficiency. The high speed comparator used in the circuit to produce a low and high logic level. It produces a low logic level when either  $S_{CV}$  equals the clock signal (CLK) in case the  $V_{BAT}$  does not reach the  $V_{Complete}$ . On the other hand, it produces a high logic level when the  $V_{BAT}$  and the  $V_{Complete}$  are equal to cover CLK by  $S_{CV}$ . The power p-channel metal-oxide semiconductor (power-PMOS) is turned off due to the long operating cycle of the high-signal  $S_{CV}$ .

Figure 8. Schematic of the CV mode control block

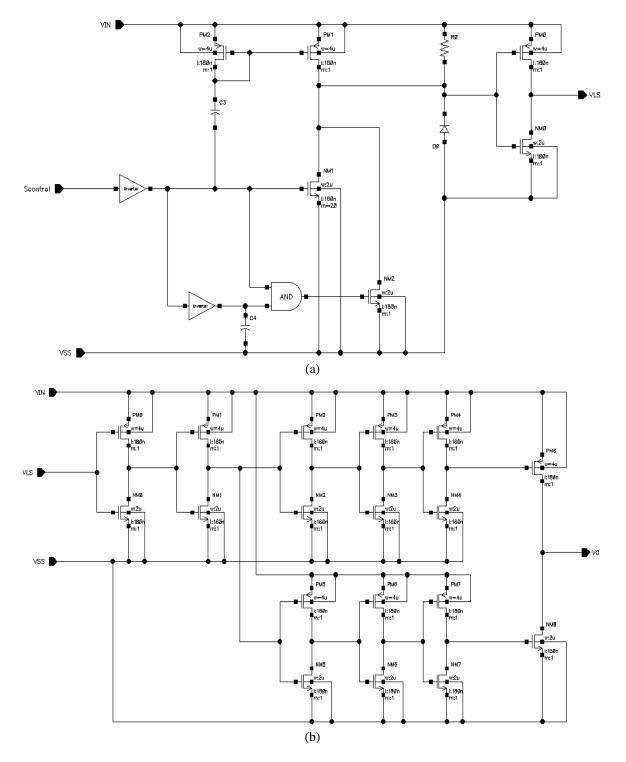

## 2.3. The level shifter and gate driver blocks

The level-shifter block is used to switch from the low-voltage of the  $S_{Control}$  to a higher-voltage to drive the power-PMOS. Its circuit is illustrated in Figure 9(a). In addition, the gate-driver block is attached to the gate of the power-PMOS which feeds the battery charge through the switching action and the convenient value of current is then regulated in the battery. Its circuit is illustrated in Figure 9(b). The level-shifter, in combination with the gate-driver, provides an ascent time of about 36 picoseconds, a descent time of about 0.25 nanoseconds [20].

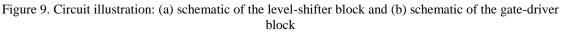

# **2.4.** The current sensor block

The OpAmp is used in the circuit as illustrated in Figure 10 to maintain the drain-voltage (V<sub>D</sub>) of the PMOS-transistor (PM0) constant and equal to the V<sub>BAT</sub>. In addition, the PMOS transistor (PM0) used in the design as a load current-sensor. This block is used to generate the V<sub>Sense</sub> which is always proportional to the V<sub>BAT</sub>.

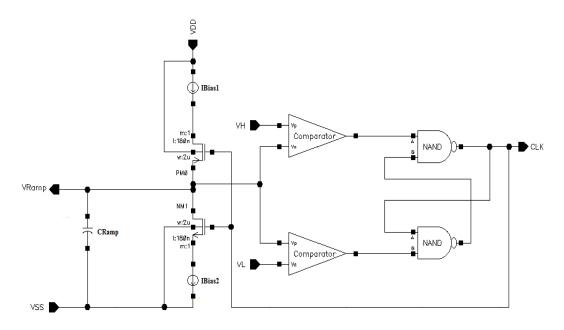

# 2.5. The ramp and clock block

The circuit of the Ramp and Clock block is illustrated in Figure 11. When the PMOS-transistor (PM0) initialized correctly, the  $I_{Bias1}$  loads  $C_{Ramp}$ . The high speed comparator in the up of circuit provided a low logic to pull up  $S_{CLK}$  when  $V_{Ramp}$  reaches the  $V_H$ . The NMOS-transistor (NM1) turned "On" when  $S_{CLK}$  equal "1" to discharge  $C_{Ramp}$ .

Figure 10. Schematic of the current-sensor block

Figure 11. Shematic of the ramp and clock block

Also, the high speed comparator in the down of circuit provided low logic for descent  $S_{CLK}$  when  $V_{Ramp}$  higher than  $C_{Ramp}$  which is also lower than another  $V_L$ . So, the Ramp signal  $S_{Ramp}$  is desired for the  $S_{CC}$  and  $S_{CV}$  controls mechanism. The operating cycles are repeated to provide the  $S_{Ramp}$  and  $S_{CLK}$  signals pending the system is sealed.

# 3. SIMULATION RESULTS AND LAYOUT

## 3.1. Simulation

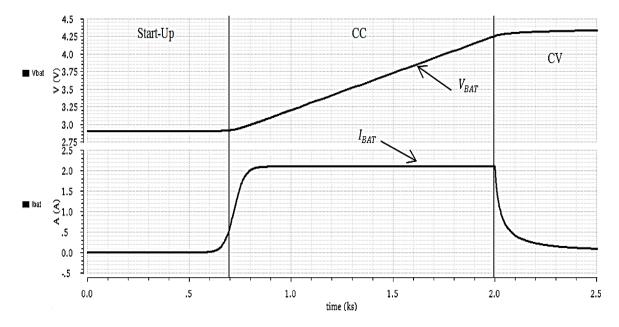

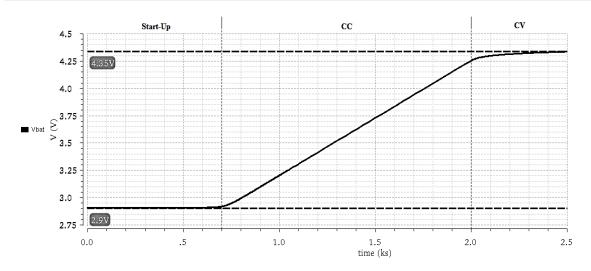

The proposed design of a Li-Ion battery charger interface using the pulse control technique is realized by the TSMC 180 nm CMOS technology under the Cadence Virtuoso software. The selected battery capacity is 5000 mAh in this simulation. The supply voltage  $V_{IN}$  is equal to 5 V. The simulation results of the  $V_{BAT}$  and the  $I_{BAT}$  in each charging mode (start-up, CC and CV) of the proposed charger using PC technique are presented in Figure 12. Also, we can observe from the simulation that the battery charges rapidly in forty-one minutes (2.5 kilo-second).

Figure 12. The waveforms of the  $V_{BAT}$  and the  $I_{BAT}$

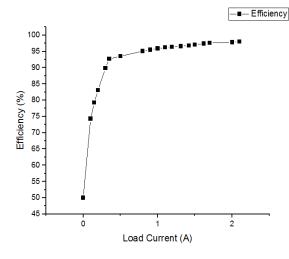

The variable value of the  $V_{BAT}$  is about 2.9 V to 4.35 V as illustrated in Figure 13. The  $I_{BAT}$  is equal 2.1 A in the CC control mode as illustrated in Figure 14. And also it reaches the  $I_{Cut-off}$  value that equals about 56 mA to terminate the charging procedure. The power efficiency of the proposed Li-Ion BCI using PC technique achieving an efficiency equal 98% of the load current 2.1 A as illustrated in Figure 15. It is determined by (2):

%Efficiency =

$$\frac{P_{Out}}{P_{In}} \times 100$$

(2)

with:

$P_{Out}$ : the output power in Watts.  $P_{In}$ : the input power consumption in watts.

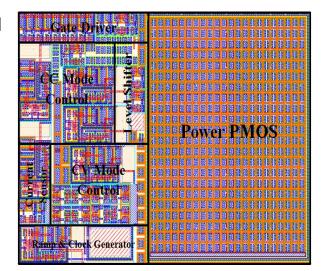

#### 3.2. Layout

The layout of the proposed fast charger is shown in Figure 16. A double layer guard ring is used in all circuits susceptible to electromagnetic interference. It is made by respecting the design rules (density, design rule manual (DRM) and mask rule checker (MRC)) and the designer constraint information (cat match, text and constraint manager). It is occupying a total area of 0.1 mm<sup>2</sup>. The comparative analysis between the results found and other works/references are summarized in Table 2.

Figure 14. The waveform of the  $I_{BAT}$

Figure 15. The resulting curve of the power efficiency

Figure 16. Layout of the proposed Li-Ion BCI using PC technique

ISSN: 2088-8708

| Table 2. Comparative analysis           |                                 |                                 |                        |                              |                       |                  |                           |                         |                                 |  |

|-----------------------------------------|---------------------------------|---------------------------------|------------------------|------------------------------|-----------------------|------------------|---------------------------|-------------------------|---------------------------------|--|

| Variable                                | [2]<br>(2021)                   | [3]<br>(2021)                   | [11]<br>(2017)         | [21]<br>(2019)               | [22]<br>(2015)        | [23]<br>(2017)   | [24]<br>(2016)            | [25]<br>(2017)          | This Work                       |  |

| Topology                                | Switching                       | Switching                       | Switching              | Switching                    | Adaptive              | LDO              | Switching                 | Switching               | Switching                       |  |

| Technology                              | Based<br>TSMC<br>180 nm<br>CMOS | Based<br>TSMC<br>180 nm<br>CMOS | +LDO<br>180 nm<br>CMOS | Based<br>500 nm<br>CMOS      | LDO<br>180 nm<br>CMOS | 130 nm<br>BICMOS | Based<br>130 nm<br>BICMOS | Based<br>350 nm<br>CMOS | Based<br>TSMC<br>180 nm<br>CMOS |  |

| V <sub>IN(max)</sub><br>(V)             | 4.5                             | 4.2                             | 5.5                    | 8.0-10.0                     | 5                     | 5                | 16                        | 5.5                     | 5                               |  |

| Output<br>Range<br>V <sub>BAT</sub> (V) | 2.7-4.2                         | 2.7-4.5                         | 2.8-4.2                | 2.5-4.2                      | 2.5-4.2               | 3-4.3            | 2.5-4.2                   | 2.3-4.2                 | 2.9-4.35                        |  |

| I <sub>BAT(max)</sub><br>(A)            | 1.7                             | 1                               | 0.5                    | 1.5                          | 0.448                 | 0.495            | 1.5                       | 0.6                     | 2.1                             |  |

| Peak<br>Efficiency<br>(%)               | 97                              | 90.9                            | 87.6                   | 87.4<br>(CC)<br>88.6<br>(CV) | 84                    | 83.9             | 90                        | 92.5                    | 98                              |  |

| Die Size<br>(mm <sup>2</sup> )          | 0.3                             | 1.5                             | 1.62                   | 7.29                         | 1.62                  | 1.41             | 12.25                     | 2.7126                  | 0.1                             |  |

# 4. CONCLUSION

A Li-Ion battery charger interface using the pulse control technique was favorably created and realized in TSMC 180 nm CMOS technology using the Cadence Virtuoso software. The proposed charger provides a battery voltage  $V_{BAT}$  ranging from 2.9 V to 4.35 V and a maximum battery current  $I_{BAT}$  of 2.1 A at a maximum input voltage  $V_{IN}$  of 5 V. The proposed charger provides a full charge in forty-one minutes. The maximum charging efficiency is also 98% and the total area occupies a small size of 0.1 mm<sup>2</sup>.

#### REFERENCES

- T. C. Huang, R. H. Peng, T. W. Tsai, K. H. Chen, and C. L. Wey, "Fast charging and high efficiency switching-based charger with continuous built-in resistance detection and automatic energy deliver control for portable electronics," *IEEE Journal of Solid-State Circuits*, vol. 49, no. 7, pp. 1580–1594, Jul. 2014, doi: 10.1109/JSSC.2014.2312411.

- [2] M. El Alaoui, F. Farah, K. El Khadiri, A. Tahiri, R. El Alami, and H. Qjidaa, "A high efficiency and high speed charge of li-ion battery charger interface using switching-based technique in 180 nm CMOS technology," *International Journal of Power Electronics and Drive Systems (IJPEDS)*, vol. 12, no. 1, pp. 374–384, Mar. 2021, doi: 10.11591/ijpeds.v12.i1.pp374-384.

- [3] F. Farah et al., "A new Li-ion battery charger with charge mode selection based on 0.18 um CMOS for phone applications," *International Journal of Electrical and Computer Engineering (IJECE)*, vol. 11, no. 3, pp. 1994–2002, Jun. 2021, doi: 10.11591/ijece.v11i3.pp1994-2002.

- [4] K. El Khadiri, H. Akhmal, and H. Qjidaa, "Li-Ion battery charging with a buck-boost DC–DC converter for a portable device power management," vol. 13, no. 2, pp. 263–270, Jun. 2017, doi: 10.1166/jolpe.2017.1479.

- [5] H. M. Nguyen, L. D. Pham, and T. Hoang, "A novel Li-ion battery charger using multi-mode LDO configuration based on 350 nm HV-CMOS," *Analog Integrated Circuits and Signal Processing*, vol. 88, no. 3, pp. 505–516, Jun. 2016, doi: 10.1007/s10470-016-0778-1.

- [6] M. Du and H. Lee, "A single-inductor dual-input dual-output buck regulator with enhanced power-delivery capability for portable battery management system," in *Midwest Symposium on Circuits and Systems*, Aug. 2010, pp. 1141–1144, doi: 10.1109/MWSCAS.2010.5548860.

- [7] R. H. Peng *et al.*, "Switching-based charger with continuously built-in resistor detector (CBIRD) and analog multiplicationdivision unit (AMDU) for fast charging in Li-Ion battery," in *European Solid-State Circuits Conference*, Sep. 2013, pp. 157–160, doi: 10.1109/ESSCIRC.2013.6649096.

- [8] R. H. Peng et al., "Robust switch-mode charger with bootstrap detector (BSD) and soft-start embedded in type III compensation (SSEC) technique," in 2012 IEEE Energy Conversion Congress and Exposition, ECCE 2012, Sep. 2012, pp. 1164–1167, doi: 10.1109/ECCE.2012.6342686.

- [9] Z. Yi, W. Xiaobo, Y. Xiaolang, and H. Shiming, "A novel switch-mode charger controller IC for VRLA batteries," in IECON Proceedings (Industrial Electronics Conference), Nov. 2007, pp. 1919–1923, doi: 10.1109/IECON.2007.4460259.

- [10] L. Huang, J. Wang, X. Fu, and F. Run, "A soft start circuit for automobile voltage regulator," in 2011 International Conference on Electronics, Communications and Control, ICECC 2011 - Proceedings, Sep. 2011, pp. 673–676, doi: 10.1109/ICECC.2011.6066545.

- [11] Y. H. Jung, S. K. Hong, and O. K. Kwon, "Highly accurate and power-efficient battery charger with charging current compensator for wearable devices," *Electronics Letters*, vol. 53, no. 7, pp. 461–463, Mar. 2017, doi: 10.1049/el.2017.0388.

- [12] R. Pagano, M. Baker, and R. E. Radke, "A 0.18 μm monolithic Li-Ion battery charger for wireless devices based on partial current sensing and adaptive reference voltage," *IEEE Journal of Solid-State Circuits*, vol. 47, no. 6, pp. 1355–1368, Jun. 2012, doi: 10.1109/JSSC.2012.2191025.

- [13] P. H. Van Quang, T. T. Ha, and J. W. Lee, "A fully integrated multimode wireless power charger IC with adaptive supply control and built-in resistance compensation," *IEEE Transactions on Industrial Electronics*, vol. 62, no. 2, pp. 1251–1261, Feb. 2015, doi: 10.1109/TIE.2014.2336618.

- [14] M. Ouremchi et al., "Li-Ion battery charger based on LDO regulator for portable device power management," in 2018 6th International Renewable and Sustainable Energy Conference (IRSEC), Dec. 2018, pp. 1–4, doi: 10.1109/IRSEC.2018.8702961.

- [15] J. A. De Lima, "A compact and power-efficient CMOS battery charger for implantable devices," in *Proceedings of the 27th Symposium on Integrated Circuits and Systems Design SBCCI '14*, 2014, pp. 1–6, doi: 10.1145/2660540.2660988.

- [16] C. C. Tsai, C. Y. Lin, Y. S. Hwang, W. T. Lee, and T. Y. Lee, "A multi-mode LDO-based Li-ion battery charger in 0.35 µM CMOS technology," in *IEEE Asia-Pacific Conference on Circuits and Systems, Proceedings, APCCAS*, 2004, vol. 1, pp. 49–52, doi: 10.1109/apccas.2004.1412688.

- [17] H. Y. Yang, T. H. Wu, J. J. Chen, Y. S. Hwang, and C. C. Yu, "An omnipotent Li-Ion battery charger with multimode controlled techniques," in *Proceedings of the International Conference on Power Electronics and Drive Systems*, Apr. 2013, pp. 531–534, doi: 10.1109/PEDS.2013.6527076.

- [18] H. Nguyen-Van, T. Nguyen, V. Quan, M. Nguyen, and L. Pham-Nguyen, "A topology of charging mode control circuit suitable for long-life Li-Ion battery charger," in 2016 IEEE 6th International Conference on Communications and Electronics, IEEE ICCE 2016, Jul. 2016, pp. 167–171, doi: 10.1109/CCE.2016.7562630.

- [19] Y. S. Hwang, S. C. Wang, F. C. Yang, and J. J. Chen, "New compact CMOS li-ion battery charger using charge-pump technique for portable applications," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 54, no. 4, pp. 705–712, Apr. 2007, doi: 10.1109/TCSI.2007.890605.

- [20] M. El Alaoui et al., "Design and analysis of new level shifter with gate driver for Li-Ion battery charger in 180 nm CMOS technology," *Iranian Journal of Electrical and Electronic Engineering*, vol. 15, no. 4, pp. 477–484, Dec. 2019, doi: 10.22068/IJEEE.15.4.477.

- [21] C. C. Wang and G. X. Liu, "A 1.5a 88.6% Li-ion battery charger design using pulse swallow technique in light load," in Proceedings - IEEE International Symposium on Circuits and Systems, May 2019, vol. 2019-May, doi: 10.1109/ISCAS.2019.8702746.

- [22] Y. Ziadi and H. Qjidaa, "A high efficiency Li-ion battery LDO-based charger for portable application," Active and Passive Electronic Components, vol. 2015, pp. 1–9, 2015, doi: 10.1155/2015/591986.

- [23] K. Chung, S. K. Hong, and O. K. Kwon, "A fast and compact charger for an Li-Ion battery using successive built-in resistance detection," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 64, no. 2, pp. 161–165, Feb. 2017, doi: 10.1109/TCSII.2016.2554839.

- [24] M. G. Jeong, S. H. Kim, and C. Yoo, "Switching battery charger integrated circuit for mobile devices in a 130-nm BCDMOS process," *IEEE Transactions on Power Electronics*, vol. 31, no. 11, pp. 7943–7952, Nov. 2016, doi: 10.1109/TPEL.2016.2514518.

- [25] C. C. Su, Y. W. Liu, and C. C. Hung, "A dual-input high-efficiency li-ion battery charger with current-mode smooth transition and ripple reduction circuits," in *Midwest Symposium on Circuits and Systems*, Aug. 2017, vol. 2017-August, pp. 468–471, doi: 10.1109/MWSCAS.2017.8052961.

## **BIOGRAPHIES OF AUTHORS**

**Mustapha El Alaoui B S S B** is born in the Old Medina, Fes, Morocco, 1994. He recieved his Master degree since 2017 in Micro-Electronics in Faculty of Sciences Dhar EL Mahraz (FSDM), Sidi Mohammed Ben Abdellah University (USMBA), Fez, Morocco. He is now a Ph.D. student in Laboratory of Computer Science, Signals, Automation and Cognitivism (LISAC), Department of Physics, FSDM, USMBA, Fez, Morocco. His research interests include Li-Ion battery charger interface (BCI) and BMS, RFID passif and actif tags, CMOS mixed mode integrated circuit design, Integrated Class-D power output stage and renewable energy. He can be contacted at email: mustapha.elalaoui@usmba.ac.ma.

Karim El Khadiri **B** S **S B** is now a Professor in Superior Normal School, ENS-FEZ, Morocco. He recieved his Master degree since 2011 in Micro-Electronics and Ph.D. degrees since 2017 in FSDM, USMBA, Fez, Morocco. His research interests include Li-Ion battery charger interface (BCI) and BMS, RFID passif and actif tags, CMOS mixed mode integrated circuit design, Integrated Class-D power output stage and renewable energy. He can be contacted at email: karim.elkhadiri@usmba.ac.ma.

**Rachid El Alami B** is a Professor in Department of Physics, FSDM, USMBA, Fez, Morocco. He received his BS degree in Electronics from Polydisciplinary Faculty of Taza, the MS and PhD degrees in Signals, Systems and Informatics in FSDM, USMBA, Fez, Morocco, in 2008 and 2013 respectively. His research interests include the channel coding/decoding (LDPC codes), FPGA implementation and image processing. He can be contacted at email: rachid.elalami@usmba.ac.ma.

Ahmed Tahiri **D** S S **D** is now a Professor in Superior Normal School, ENS-FEZ, Morocco. He recieved his graduate degree DES and Ph.D degree in Department of Physics, FSDM, USMBA, Fez, Morocco. And He has a doctoral in Didactics of Science in the University of Sherbrooke in Canada in 2010. His research interests include didactics of scientific disciplines, computer science and image processing. He can be contacted at email: ahmed.tahiri@usmba.ac.ma.

Ahmed Lakhssassi 💿 🕺 🔄 🖻 is Professor at the Department of Computer Science and Engineering University of Quebec in Outaouais, He is specializes in energy sciences and thermal aspects in integrated circuits. His main research interest includes Electronic, Electromagnetism, Thermal aspects, and Numerical methods, Energy sciences, electrothermics, Constraints and distortions, Materials Sciences. He can be contacted at email: ahmed.lakhssassi@uqo.ca.

**Hassan Qjidaa** <sup>(b)</sup> **S** <sup>(c)</sup> **(b)** is now a Professor in Department of Physics, FSDM, USMBA, Fez, Morocco. He recived his Master degree since 1984 and Ph.D. degrees since 1987 in Electrical Engineering from Nuclear Physics Institute of Lyon, France. His research interests include Li-Ion battery charger interface (BCI) and BMS, RFID passif and actif tags, CMOS mixed mode integrated circuit design, Integrated Class-D power output stage, renewable energy and image processin. He can be contacted at email: qjidah@yahoo.fr.