Technological University Dublin ARROW@TU Dublin

Doctoral

Engineering

2021

## A New MMC Topology Which Decreases the Sub Module Voltage Fluctuations at Lower Switching Frequencies and Improves Converter Efficiency

Shahab Sajedi Technological University Dublin, shahab.sajedi@mydit.ie

Follow this and additional works at: https://arrow.tudublin.ie/engdoc

Part of the Engineering Commons

#### **Recommended Citation**

Sajedi, S. (2021). A New MMC Topology Which Decreases the Sub Module Voltage Fluctuations at Lower Switching Frequencies and Improves Converter Efficiency. Doctoral Thesis, Technological University Dublin. doi:10.21427/a98s-td51

This Theses, Ph.D is brought to you for free and open access by the Engineering at ARROW@TU Dublin. It has been accepted for inclusion in Doctoral by an authorized administrator of ARROW@TU Dublin. For more information, please contact arrow.admin@tudublin.ie, aisling.coyne@tudublin.ie, gerard.connolly@tudublin.ie.

This work is licensed under a Creative Commons Attribution-Noncommercial-Share Alike 4.0 License

A New MMC Topology Which Decreases the Sub Module Voltage Fluctuations at Lower Switching Frequencies and Improves Converter Efficiency

Shahab Sajedi

A thesis submitted in fulfilment of the requirements for the degree of Doctor of Philosophy

School of Electrical and Electronic Engineering Technological University Dublin

2021

Under the Supervision of Dr. Malabika Basu, Mr. Michael Farrell & Prof. Michael Conlon

## Acknowledgement

Throughout the writing of this dissertation, I have received a great deal of support and assistance.

I would first like to thank my supervisors, Dr. Malabika Basu, Mr. Michael Farrell and Prof. Michael Conlon whose expertise were invaluable in formulating the research questions and methodology. Your insightful feedback pushed me to sharpen my thinking and brought my work to a higher level. I also would like to acknowledge my colleague, Dr. Sandipan Patra for his wonderful collaboration.

In addition, I would like to thank my parents for their wise counsel and sympathetic ear. You are always there for me. Finally, I could not have completed this dissertation without the support of Dr. Ghazal Tadayyon, who provided stimulating discussions as well as happy distractions to rest my mind outside of my research.

## Abstract

Modular Multi-level inverters (MMCs) are becoming more common because of their suitability for applications in smart grids and multi-terminal HVDC transmission networks. The comparative study between the two classic topologies of MMC (AC side cascaded and DC side cascaded topologies) indicates some disadvantages which can affect their performance. The sub module voltage ripple and switching losses are one of the main issues and the reason for the appearance of the circulating current is sub module capacitor voltage ripple. Hence, the sub module capacitor needs to be large enough to constrain the voltage ripple when operating at lower switching frequencies. However, this is prohibitively uneconomical for the high voltage applications. There is always a trade off in MMC design between the switching frequency and sub module voltage ripple.

The converter reliability is the other important issue of using MMCs as they use a lot of components in their structure. A fault of one sub module can also cause the other components in the corresponding arm to fail and lead to total system collapse. When the quantity of broken sub modules is more than the redundant ones, the MMC would work with asymmetrical operation. In the worst case, this might result in system failure. Moreover, MMC needs higher number of voltage sensors which will increase the cost of converter and deteriorate the converter reliability.

In this research, a new topology for MMC has been proposed which can maintain the sub module voltage ripples in an acceptable range without the need for large capacitor values when operating at lower switching frequencies. The main contribution is the elimination of the sub module voltage fluctuations at lower switching frequencies which will lead to improved converter efficiency and maintaining the circulating current content in the acceptable range. Moreover, the proposed design doesn't need any sub module voltage sensors which will reduce the converter cost and complexity and will improve the converter reliability. It can also improve the converter reliability during the sub module capacitor failure. Considering open circuit status for the faulty sub module capacitor, the converter can continue the normal operation. The proposed topology provides robust and fast responses to sub module capacitor faults with minor additional costs and its reliability improvement is more significant as the number of sub modules increases. The simulation results demonstrate the effectiveness of the proposed topology in decreasing the converter total losses and reliability improvement.

## Declaration

I hereby certify that this thesis which I now submit for examination for the award of Doctor of Philosophy, is entirely my own work and has not been taken from the work of others, save and to the extent that such work has been cited and acknowledged within the text of my work.

This thesis was prepared according to the regulations for postgraduate study by research of the Technological University Dublin and has not been submitted in whole or in part for another award in any Institute.

The work reported in this thesis conforms to the principles and requirements of the Technological University Dublin's guidelines for ethics in research.

Technological University Dublin has permission to keep, lend or copy this thesis in whole or in part, on condition that any such use of the material of the thesis be duly acknowledged.

# Abbreviations List

| CSC   | Current Source Converter          |

|-------|-----------------------------------|

| HVDC  | High Voltage Direct Current       |

| UHV   | Ultra-High Voltage                |

| VSC   | Voltage Source Converter          |

| IGBT  | Insulated Gate Bipolar Transistor |

| GTO   | Gate Turn-Off Thyristor           |

| BJT   | Bipolar Junction Transistor       |

| IGCT  | Integrate Gate-Commutated         |

|       | Thyristor                         |

| PWM   | Pulse Width Modulation            |

| ММС   | Modular Multilevel Converter      |

| SM    | Sub Module                        |

| НВ    | Half Bridge                       |

| FB    | Full Bridge                       |

| LCC   | Line Commutated Converter         |

| PD    | Phase Disposition                 |

| NLC   | Nearest Level Control             |

| PSC   | Phase Shifted Carrier             |

| THD   | Total Harmonic Distortion         |

| SVM   | Space Vector Modulation           |

| 3L-FC | Three-Level Flying Capacitor      |

| FCMC  | Flying Capacitor Multi Cell       |

|       | Converters                        |

| CSM   | Composite Multilevel Sub Module   |

| PMSG  | Permanent Magnet Synchronous      |

|       | Generator                         |

| WECS    | Wind Energy Conversion System                |  |  |  |  |  |

|---------|----------------------------------------------|--|--|--|--|--|

| SCSM    | Switched Capacitor Sub Module                |  |  |  |  |  |

| DZ-SM   | Double Zero Sub Module                       |  |  |  |  |  |

| МРС     | Model Predictive Control                     |  |  |  |  |  |

| CCSC    | Circulating Current Suppressing<br>Control   |  |  |  |  |  |

| PR      | Proportional Resonant                        |  |  |  |  |  |

| PTG     | Pole to Ground                               |  |  |  |  |  |

| LGF     | Line to Ground                               |  |  |  |  |  |

| SCF     | Short Circuit Fault                          |  |  |  |  |  |

| АССВ    | AC Circuit Breaker                           |  |  |  |  |  |

| ОССВ    | DC Circuit Breaker                           |  |  |  |  |  |

| DMR     | Dedicated Metallic Return                    |  |  |  |  |  |

| CDSM    | Clamp Double Sub Module                      |  |  |  |  |  |

| QRB-MMC | Quasi Reverse Blocking Modular<br>Multilevel |  |  |  |  |  |

| SPG     | Single Phase to Ground                       |  |  |  |  |  |

| CLR     | Current Limiting Reactors                    |  |  |  |  |  |

| FCL     | Fault Current Limiter                        |  |  |  |  |  |

| ТІ-НММС | Three Level Cell-Based Hybrid MMC            |  |  |  |  |  |

| FDM     | Fault Diagnosis Method                       |  |  |  |  |  |

| CA      | Clustering Algorithm                         |  |  |  |  |  |

| SRF     | Synchronous Rotating Reference<br>Frame      |  |  |  |  |  |

| ESR     | Equivalent Series Resistance                 |  |  |  |  |  |

# List of Acronyms

| $V_{dc}$          | DC bus voltage                     |

|-------------------|------------------------------------|

| V <sub>C</sub>    | Sub Module Capacitor Voltage       |

| Larm              | Arm Inductance                     |

| i <sub>SM</sub>   | Sub Module Current                 |

| VSM_out           | Sub Module Output Voltage          |

| i <sub>U</sub>    | Upper Leg Current                  |

| $i_L$             | Lower Leg Current                  |

| ic                | Circulating Current                |

| <i>is</i>         | Output Current                     |

| $R_L$             | Load Resistance                    |

| L                 | Load Inductance                    |

| Non               | Number of Inserted Sub Modules     |

| Kripplemax        | Maximum Sub Module Voltage Ripple  |

| $\Delta e_{pmax}$ | Maximum Sub Module Energy          |

|                   | Variation                          |

| $T_s$             | Switching Cycle of IGBT            |

| E                 | Ripple Factor                      |

| S                 | Three Phase Apparent Power         |

| W                 | Fundamental Frequency              |

| М                 | Modulation Index                   |

| cosØ              | Power Factor                       |

| $f_s$             | Switching Frequency                |

| Pcond             | Conduction Losses                  |

| $V_f$             | Forward Voltage Drop               |

| Iav               | Average Current                    |

| Irms              | Root Mean Square Value of Current  |

| $P_{sw}$          | Switching Losses                   |

| $X_L$             | Total Reactance of the Converter   |

|                   | Transformer and the Phase Reactor  |

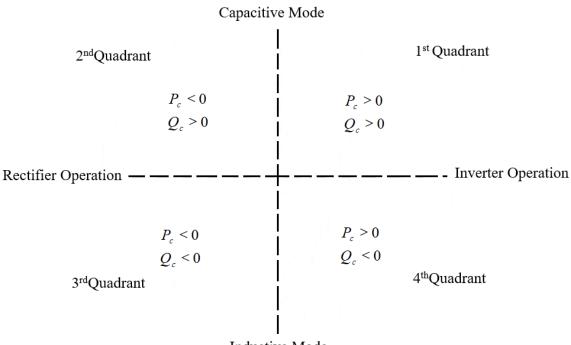

| $P_c$             | Active Power Exchanged Between the |

|                   | MMC and the AC System              |

| $Q_c$             | Reactive Power Exchanged Between   |

|                   | the MMC and the AC System          |

| РСС               | Point of Common Coupling           |

# Table of Contents

## Contents

A New MMC Topology Which Decreases the Sub Module Voltage Fluctuations at Lower Switching Frequencies and Improves Converter Efficiency Abstract.....I Declaration.....II Abbreviations List......III List of Acronyms ......V List of Figures.....IX List of Tables ......XIII Chapter 1...... 1 Introduction......1 1.2.1 Line Commutaded Converter (LCC) Based HVDC ......7 Review of The Modular Multilevel Converters and Different Challenges for HVDC System

| 2.6 Sub Module Capacitor Size and Ripple                                                                                             | 32             |

|--------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 2.7 Challenge of Switch Count and Losses with Proposing New Sub-Module Topology                                                      | 34             |

| 2.8 Circulating Currents: The Challenge of Suppressing with Different Control Methods4                                               | 13             |

| 2.9 Challenge of DC Fault and Fault Protection of DC Grid Based on Hybrid MMC 4                                                      | 18             |

| 2.10 Sub-Module Faults: Fault-Tolerant Approach for Modular Multilevel Converters Under<br>Sub-Module Faults5                        | 53             |

| 2.11 Summary of Literature Review5                                                                                                   | 58             |

| Chapter 3                                                                                                                            | 50             |

| Proposed New MMC Topology and Its Operational Principle                                                                              | 50             |

| 3.1 Research Methodology and Design                                                                                                  | 50             |

| 3.2 Sub Module Capacitance Selection Principle                                                                                       | 72             |

| 3.2.1 Definition of Sub Module Voltage Ripple Factor                                                                                 | 72             |

| 3.3 Simulation Results at Different Switching Frequencies                                                                            | 73             |

| 3.3.1 Simulation Results at 1000 Hz Switching Frequency7                                                                             | 75             |

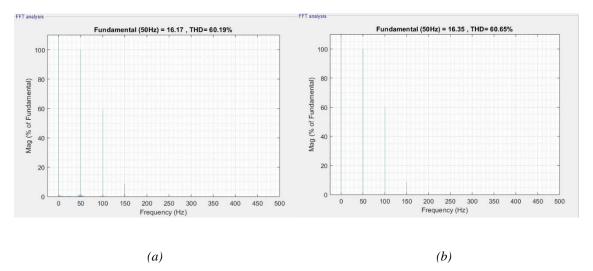

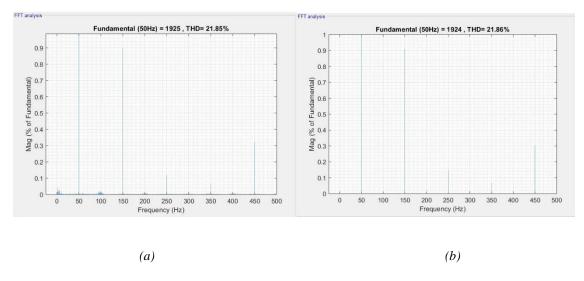

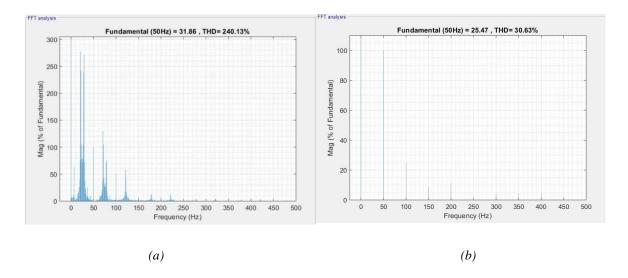

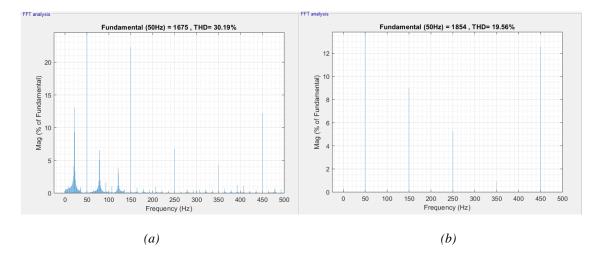

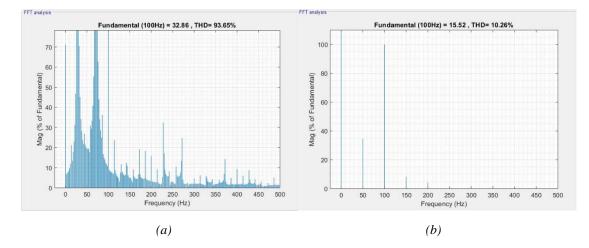

| 3.3.1.1 Harmonic Analysis of Sub Module Voltage, Output Voltage and Circulating Current<br>at 1000 Hz Switching Frequency            | 79             |

| 3.3.2 Simulation results at 400 Hz switching frequency                                                                               | 31             |

| 3.3.2.1 Harmonic Analysis of Sub Module Voltage, Output Voltage and Circulating Current<br>at 400 Hz Switching Frequency             | 34             |

| 3.3.3 Simulation results at 100 Hz switching frequency                                                                               | 35             |

| 3.3.3.1 Harmonic Analysis of Sub Module Voltage, Output Voltage and Circulating Current<br>at 100 Hz Switching Frequency             | 38             |

| 3.3.4 Simulation results at 50 Hz switching frequency                                                                                | <del>)</del> 0 |

| 3.3.4.1 Harmonic Analysis of Sub Module Voltage, Output Voltage and Circulating Current<br>at 50 Hz Switching Frequency              | €€             |

| 3.4 Loss and Efficiency Calculations                                                                                                 | <del>)</del> 5 |

| 3.4.1 Switch Selection                                                                                                               | €              |

| 3.4.2 Heat Sink                                                                                                                      | <del>)</del> 8 |

| 3.4.3 Damping Resistors                                                                                                              | <del>)</del> 9 |

| 3.4.4 Loss and Efficiency Analysis of the Classic Half Bridge MMC Versus the Proposed New Topology                                   | )1             |

| 3.5 Analysis of The New Topology Considering Hybrid MMC (Mixture of Half-bridge and Full Bridge Sub Modules)                         | )4             |

| 3.5.1 Hybrid MMC Topology10                                                                                                          | )4             |

| 3.5.2 Proposed Topology Considering Hybrid MMC10                                                                                     | )5             |

| 3.6 Chapter Summary                                                                                                                  | )8             |

| Chapter 410                                                                                                                          | )9             |

| Operation of the New Proposed Design at HVDC System Level and the Converter Reliability<br>Improvement                               | )9             |

| 4.1 Operation of the New Design at the HVDC System Level Considering the Nominal Values of East-West Inter-Connector (400 kV, 500MW) | 10             |

| 4.1.1 Simulation Results of the Proposed Topology Considering the Nominal Values of<br>East-West Inter-Connector (400 kV, 500MW)11   | 11             |

| 4.1.1.1 Simulation Results at 1000 Hz Switching Frequency11                                                                                                   | 1  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.1.1.2 Simulation Results at 400 Hz Switching Frequency11                                                                                                    | 4  |

| 4.1.1.3 Simulation Results at 100 Hz Switching Frequency11                                                                                                    | 7  |

| 4.1.1.4 Simulation Results at 50 Hz Switching Frequency12                                                                                                     | 0  |

| 4.2 THD and Harmonic Analysis of the Output Current and Voltage at Four Different<br>Switching Frequencies Considering the New Design                         | :3 |

| 4.3 Loss and Efficiency Analysis of the Classic Half Bridge MMC Versus the Proposed New<br>Topology at the HVDC System Level                                  | :4 |

| 4.4 Closed Loop Control of the Proposed Design Considering the Nominal Values of East-West Inter-Connector (400 kV, 500MW) and Point to Point HVDC Connection |    |

| 4.5 Converter Reliability Improvement Under Sub Module Capacitor Failure Condition                                                                            | 5  |

| 4.5.1 Faults in Sub Module Capacitors                                                                                                                         | 5  |

| 4.5.2 Operation of the Proposed Design Under Sub Module Capacitor Failure Condition                                                                           | 6  |

| 4.6 Impact of Applying the Proposed Design at Reducing the Number of Sub Module Voltage<br>Sensors                                                            | .8 |

| 4.6.1 Simulation of the Proposed Design Without Using Voltage Sensors                                                                                         | .9 |

| 4.7 Chapter Summary                                                                                                                                           | 2  |

| Chapter 515                                                                                                                                                   | 3  |

| Conclusions and Future Work15                                                                                                                                 | 3  |

| 5.1 Conclusions15                                                                                                                                             | 3  |

| 5.2 Future Work                                                                                                                                               | 5  |

| References                                                                                                                                                    | 7  |

# List of Figures

| Fig. 1.1 Investment costs for DC and AC transmission lines                                         | 1    |

|----------------------------------------------------------------------------------------------------|------|

| Fig. 1.2 A 12-pulse converter bridge                                                               | 2    |

| Fig. 1.3 A bipolar CSC-HVDC system with one 12-pulse bridge per pole                               |      |

| Fig. 1.4 Diagram of a two-level VSC                                                                |      |

| Fig. 1.5 Typical configuration of a DC to three-phase AC MMC system                                |      |

| Fig. 2.1 (a) Basic representation of a multilevel converter; (b) the MMC's approach                |      |

| Fig. 2.2 Typical output waveforms of MMC                                                           |      |

| Fig. 2.3 Circuit diagram of a Half-Bridge sub module                                               | 16   |

| Fig. 2.4 Six operation states of a Half-Bridge sub module                                          | 18   |

| Fig. 2.5 Full-Bridge sub module structure                                                          | 19   |

| Fig. 2.6 Topology of a single-phase MMC with 10 sub modules                                        | 20   |

| Fig. 2.7 Waveforms of phase disposition (PD) carriers                                              | 23   |

| Fig. 2.8 Principle of NLM strategy                                                                 | 24   |

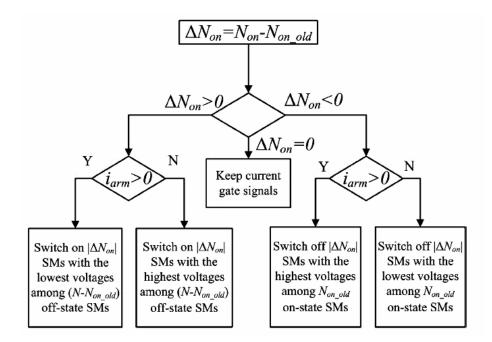

| Fig. 2.9 Reduced switching-frequency voltage-balancing algorithm                                   | - 29 |

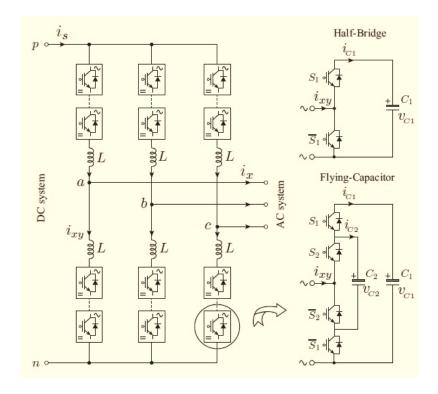

| Fig. 2.10 MMC with 3L-FC submodule                                                                 | 35   |

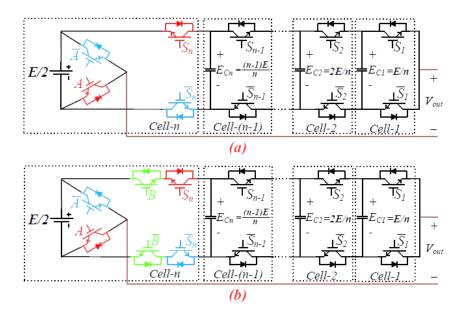

| Fig. 2.11 Sub multilevel module of n-cell-n+1-level modified FCMC based on only one DC voltage     |      |

| source with maximum peak-to-peak voltage of E                                                      |      |

| Fig. 2.12 Proposed self-blocking composite multilevel sub module topology (CSM topology)           |      |

| Fig. 2.13 Some of the known cell configurations for modular and hybrid multilevel converters       |      |

| Fig. 2.14 The DCBSSM topology                                                                      | 38   |

| Fig. 2.15 Proposed unipolar voltage full-bridge SM circuit                                         | 39   |

| Fig. 2.16 Proposed three-level cross-connected SM circuit                                          | 40   |

| Fig. 2.17 Proposed semi-full-bridge-sub module                                                     | 40   |

| Fig. 2.18 New topology of sub module in the MMC                                                    | 41   |

| Fig. 2.19 Proposed switched capacitor sub module (SCSM)                                            | 41   |

| Fig. 2.20 Diode clamp sub module                                                                   | 42   |

| Fig. 2.21 Novel Double-Zero sub module                                                             | 42   |

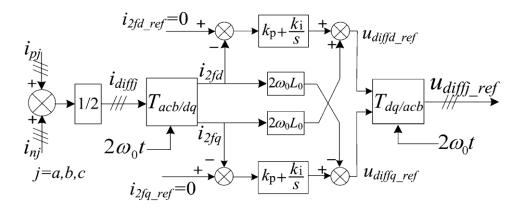

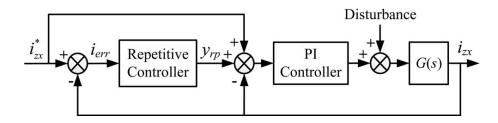

| Fig. 2.22 Control diagram of the method based on double line-frequency d-q coordinate              | 46   |

| Fig. 2.23 Diagram of repetitive-plus-PI control                                                    |      |

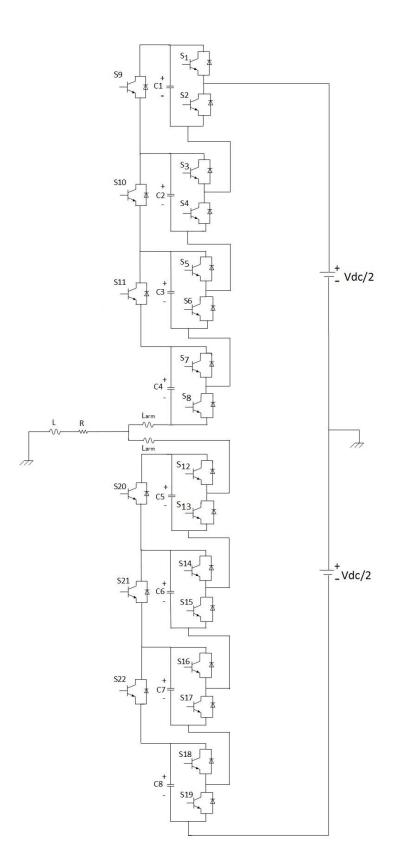

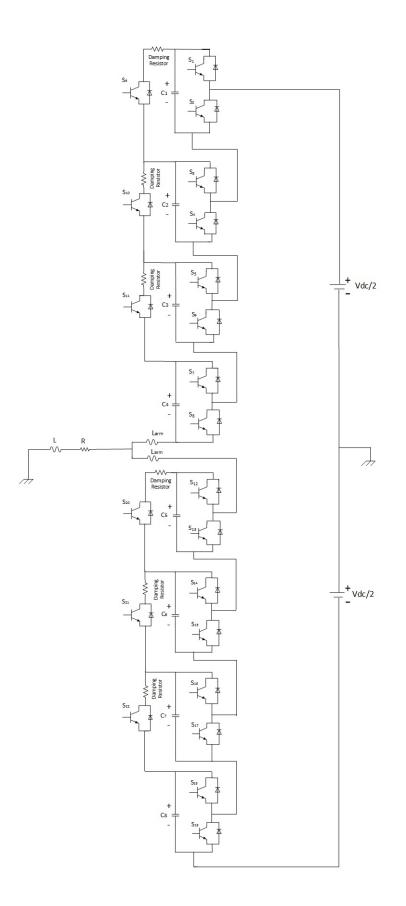

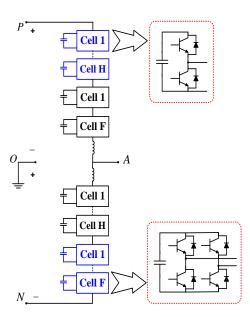

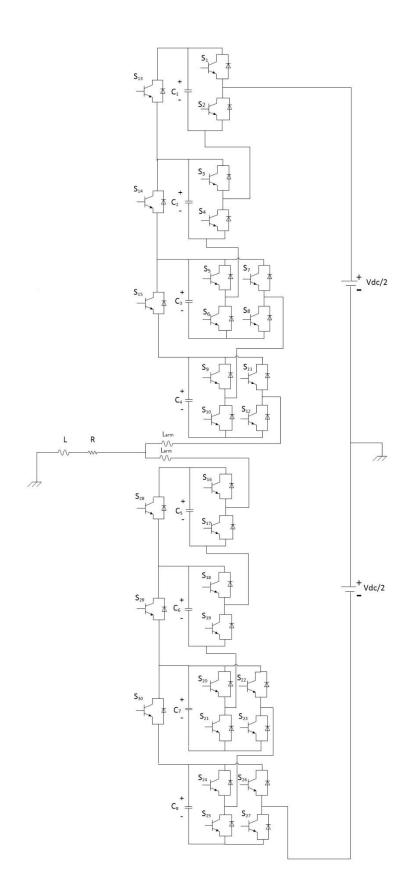

| Fig. 3.1 New proposed topology (single phase)                                                      | 64   |

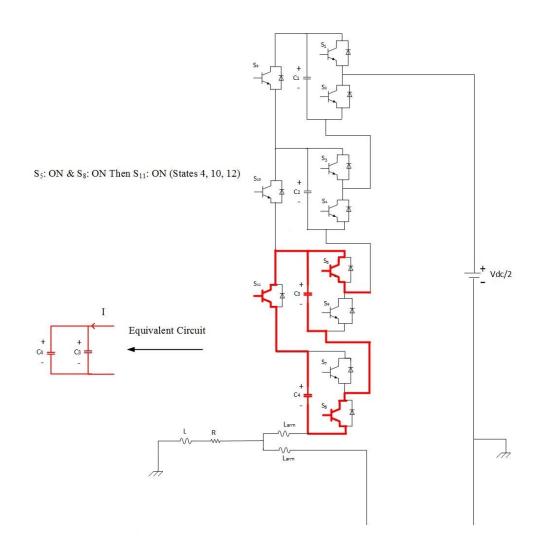

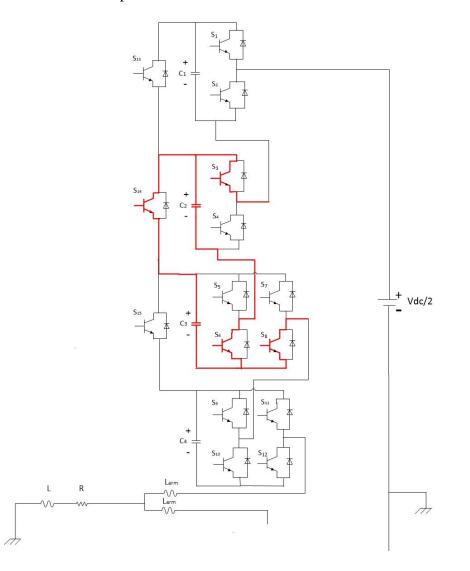

| Fig. 3.2 States 4, 10 and 12                                                                       | 65   |

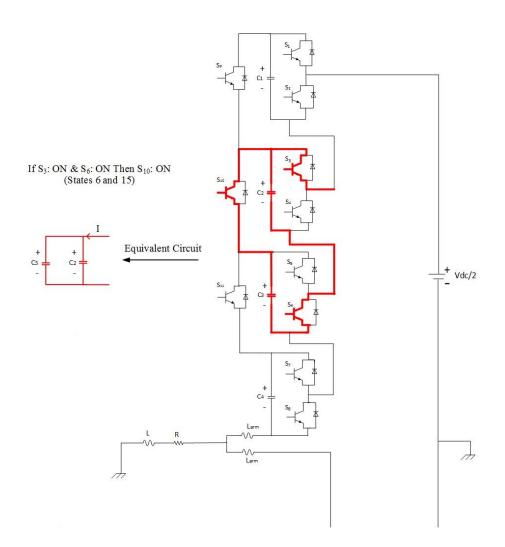

| Fig. 3.3 States 6 and 15                                                                           | 66   |

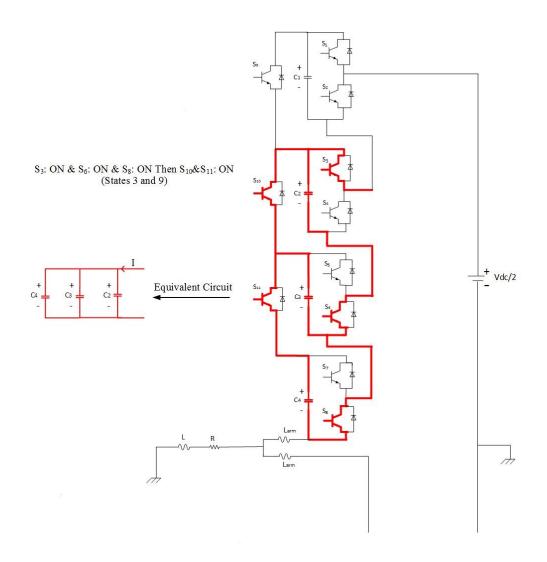

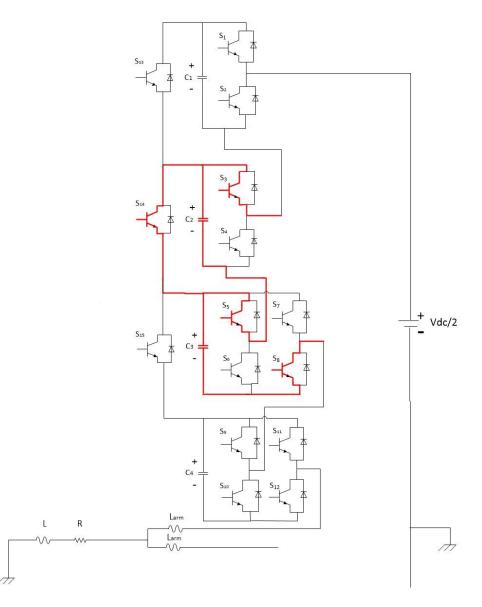

| Fig. 3.4 States 3 and 9                                                                            |      |

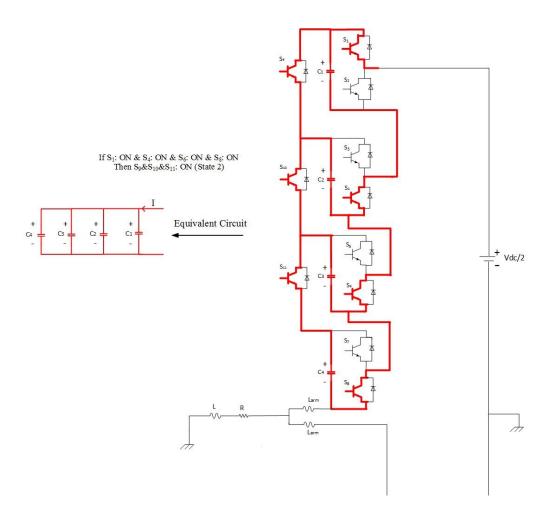

| Fig. 3.5 State 2                                                                                   |      |

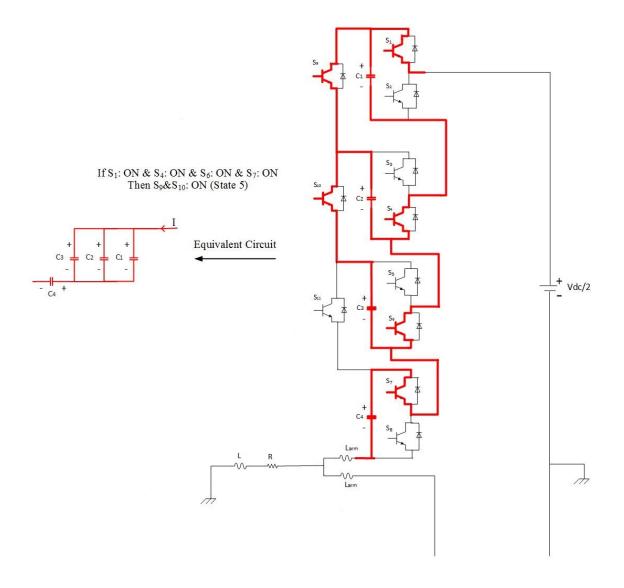

| Fig. 3.6 State 5                                                                                   | 69   |

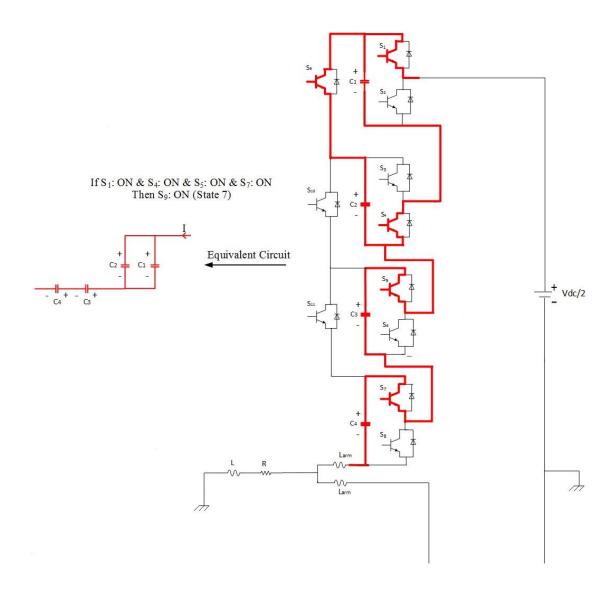

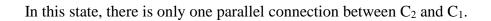

| Fig. 3.7 State 7 Fig. 3.8 State 8                                                                  | 70   |

|                                                                                                    |      |

| Fig. 3.9 Engineering Trade-off in Designing MMC System                                             |      |

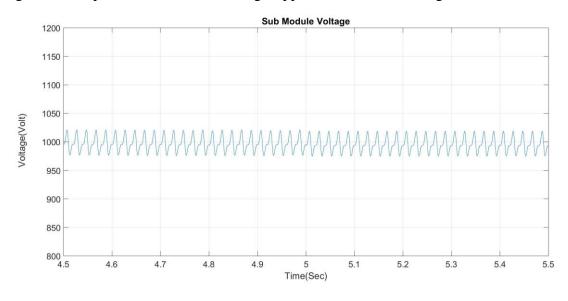

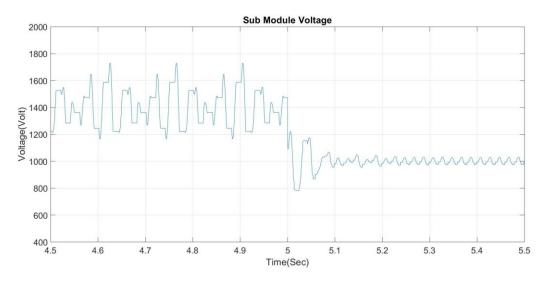

| Fig. 3.10 Sub module voltage before and after applying the proposed design at t=5 Sec and 1000 Hz  | Z    |

| switching frequency                                                                                | 76   |

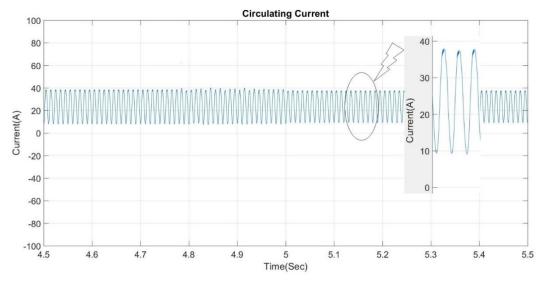

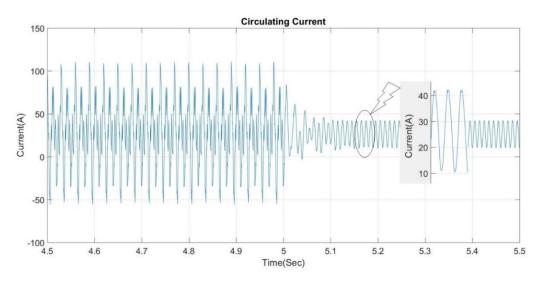

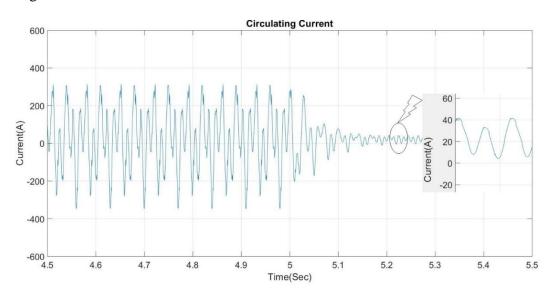

| Fig. 3.11 Circulating current before and after applying the proposed design at t=5 Sec and 1000 Hz |      |

| switching frequency                                                                                | 76   |

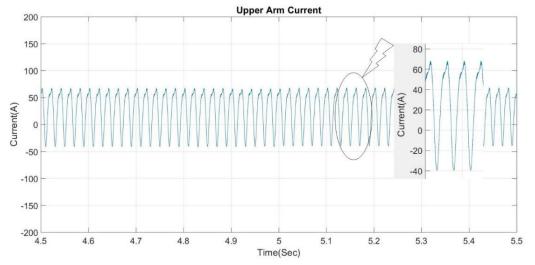

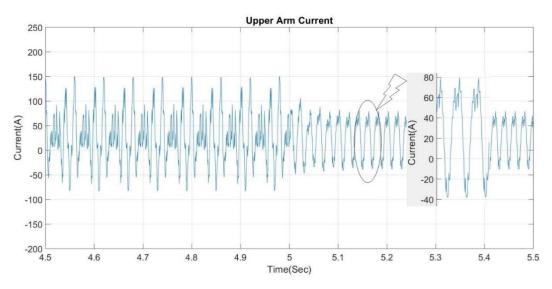

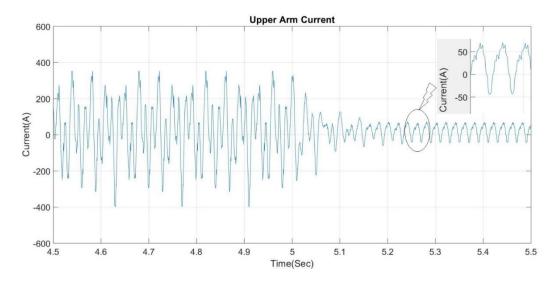

| Fig. 3.12 Upper arm current before and after applying the proposed design at t=5 Sec and 1000 Hz   |      |

| switching frequency                                                                                | 77   |

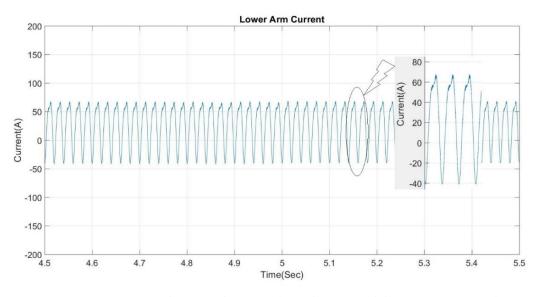

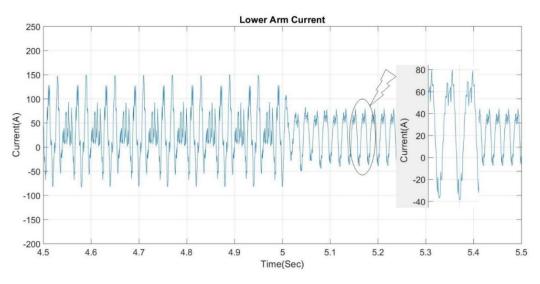

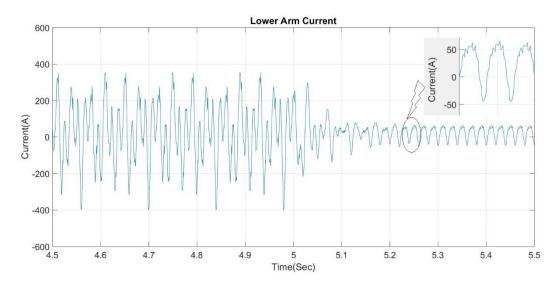

| Fig. 3.13 Lower arm current before and after applying the proposed design at t=5 Sec and 1000 Hz   |      |

| switching frequency                                                                                | 77   |

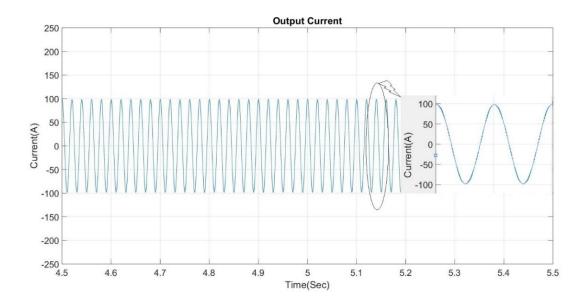

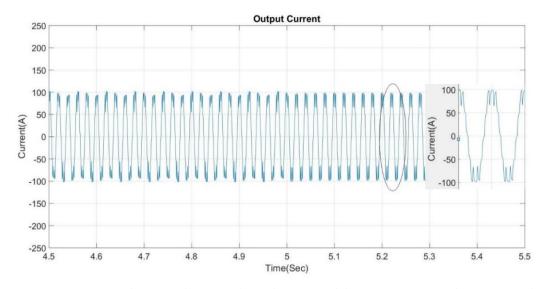

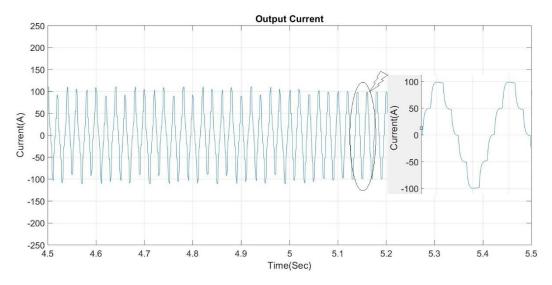

| Fig. 3.14 Output current before and after applying the proposed design at t=5 Sec and 1000 Hz      |      |

| switching frequency                                                                                | 78   |

| Fig. 3.15 Output voltage before and after applying the proposed design at t=5 Sec and 1000 Hz      |      |

| switching frequency                                                                                | 78   |

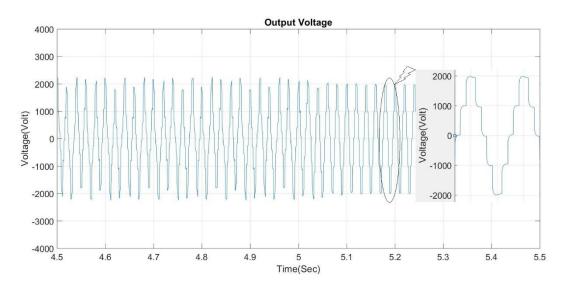

| Fig. 3.16 Harmonic analysis of sub module voltage at 1000 Hz switching frequency                   |      |

| Fig. 3.17 Harmonic analysis of output voltage at 1000 Hz switching frequency                       | 80   |

| Fig. 3.18 Harmonic analysis of circulating current at 1000 Hz switching frequency                                                                                                                            | 0      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| switching frequency                                                                                                                                                                                          | 1      |

| Fig. 3.20 Circulating current before and after applying the proposed design at t=5 Sec and 400 Hz                                                                                                            |        |

| switching frequency8<br>Fig. 3.21 Upper arm current before and after applying the proposed design at t=5 Sec and 400 Hz<br>switching frequency                                                               | 2      |

| switching frequency 82<br>Fig. 3.22 Lower arm current before and after applying the proposed design at t=5 Sec and 400 Hz<br>switching frequency 82                                                          | 2      |

| Switching frequency 82<br>Fig. 3.23 Output current before and after applying the proposed design at t=5 Sec and 400 Hz<br>Switching frequency 82                                                             | 3      |

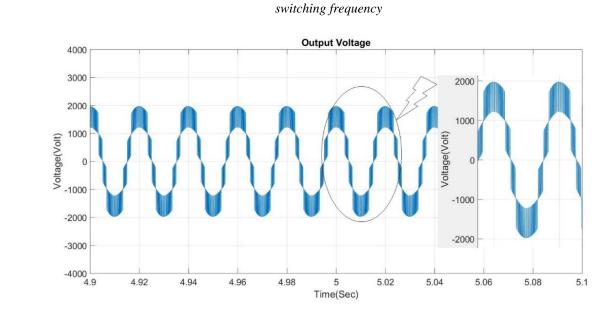

| Switching frequency 82<br>Fig. 3.24 Output voltage before and after applying the proposed design at t=5 Sec and 400 Hz<br>switching frequency 82                                                             | 3      |

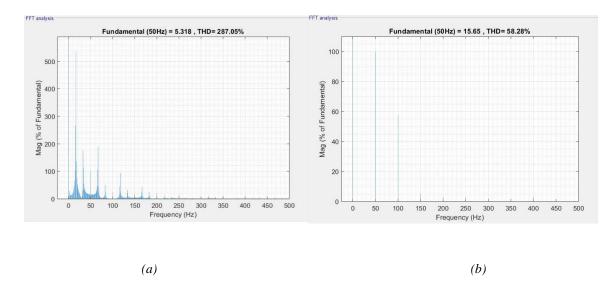

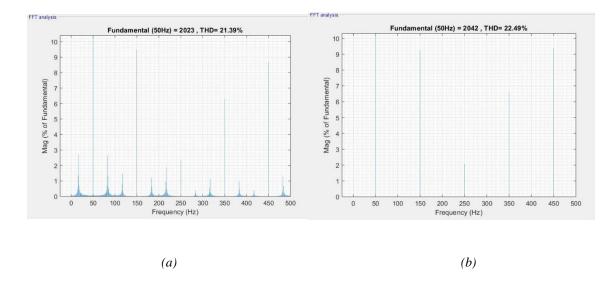

| Fig. 3.25 Harmonic analysis of sub module voltage at 400 Hz switching frequency 84                                                                                                                           | 4      |

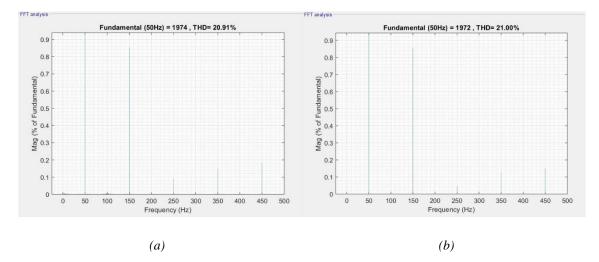

| Fig. 3.26 Harmonic analysis of output voltage at 400 Hz switching frequency 84                                                                                                                               |        |

| Fig. 3.27 Harmonic analysis of circulating current at 400 Hz switching frequency 83                                                                                                                          | 5      |

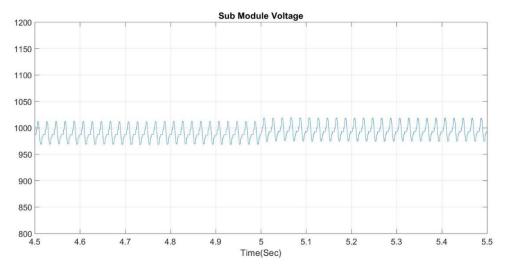

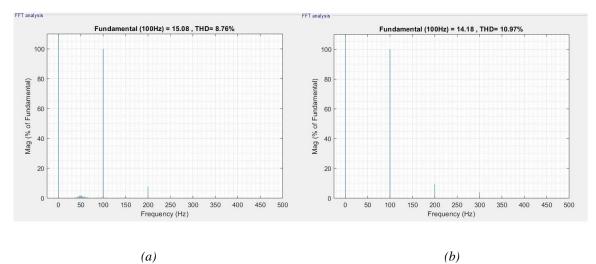

| Fig. 3.28 Sub module voltage before and after applying the proposed design at t=5 Sec and 100 Hz switching frequency 80                                                                                      | 6      |

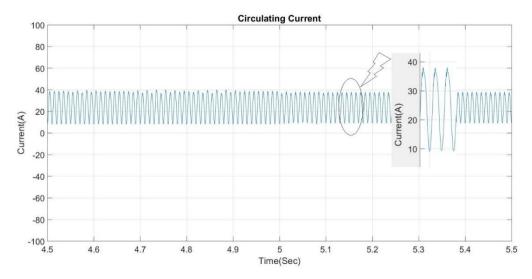

| Fig. 3.29 Circulating current before and after applying the proposed design at t=5 Sec and 100 Hz                                                                                                            |        |

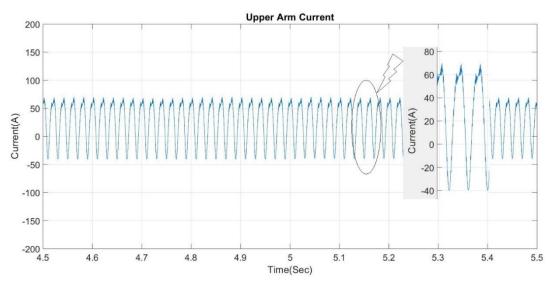

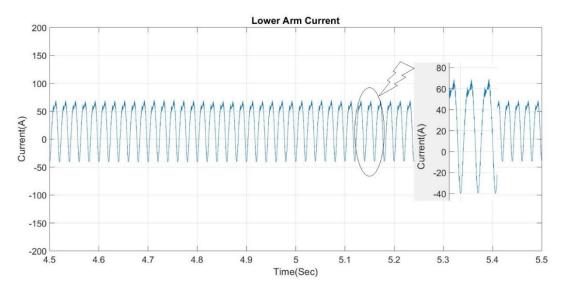

| switching frequency 86<br>Fig. 3.30 Upper arm current before and after applying the proposed design at t=5 Sec and 100 Hz<br>switching frequency 87                                                          | 7      |

| Switching frequency 8'<br>Fig. 3.31 Lower arm current before and after applying the proposed design at t=5 Sec and 100 Hz<br>Switching frequency 8'                                                          | 7      |

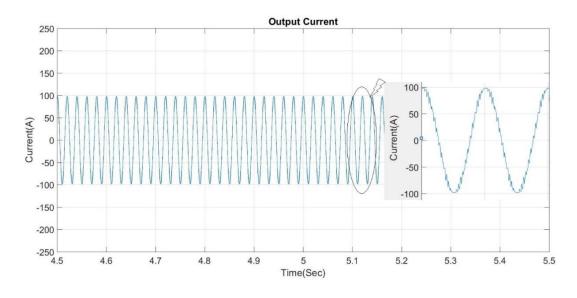

| Switching frequency 8'<br>Fig. 3.32 Output current before and after applying the proposed design at t=5 Sec and 100 Hz<br>switching frequency 8                                                              | ,<br>8 |

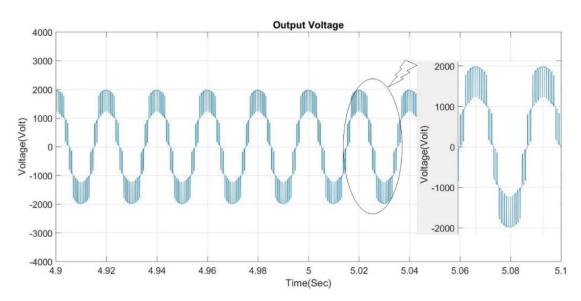

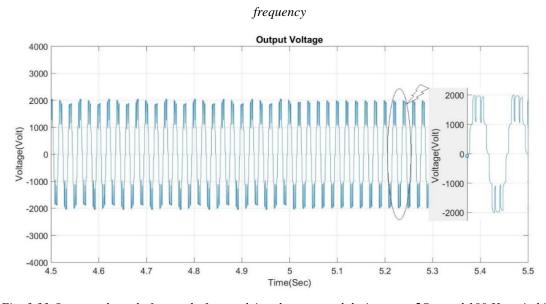

| Fig. 3.33 Output voltage before and after applying the proposed design at t=5 Sec and 100 Hz switching frequency 88                                                                                          | 8      |

| Fig. 3.34 Harmonic analysis of sub module voltage at 100 Hz switching frequency 89                                                                                                                           | 9      |

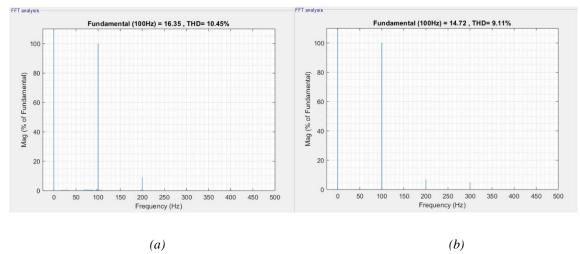

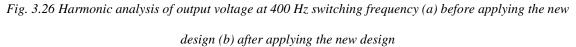

| Fig. 3.35 Harmonic analysis of output voltage at 100 Hz switching frequency                                                                                                                                  | á      |

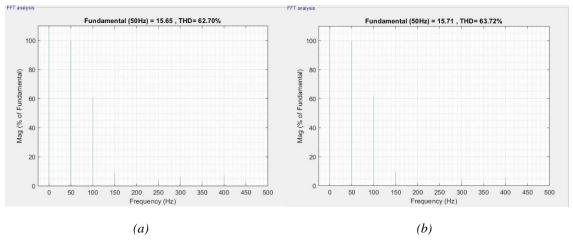

| Fig. 3.36 Harmonic analysis of circulating current at 100 Hz switching frequency99                                                                                                                           |        |

| Fig. 3.37 Sub module voltage before and after applying the proposed design at t=5 Sec and 50 Hz switching frequency 9                                                                                        | 1      |

| Fig. 3.38 Circulating current before and after applying the proposed design at t=5 Sec and 50 Hz switching frequency9                                                                                        |        |

| Fig. 3.39 Upper arm current before and after applying the proposed design at t=5 Sec and 50 Hz switching frequency92                                                                                         |        |

| Fig. 3.40 Lower arm current before and after applying the proposed design at t=5 Sec and 50 Hz switching frequency92                                                                                         |        |

| Fig. 3.41 Output current before and after applying the proposed design at t=5 Sec and 50 Hz switching frequency92                                                                                            |        |

| Fig. 3.42 Output voltage before and after applying the proposed design at t=5 Sec and 50 Hz switching frequency92                                                                                            |        |

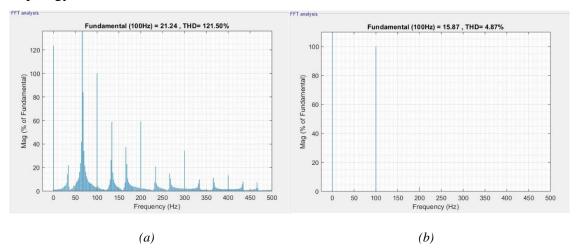

| Fig. 3.43 Harmonic analysis of sub module voltage at 50 Hz switching frequency94                                                                                                                             |        |

| Fig. 3.44 Harmonic analysis of output voltage at 50 Hz switching frequency                                                                                                                                   |        |

| Fig. 3.45 Harmonic analysis of circulating current at 50 Hz switching frequency99                                                                                                                            |        |

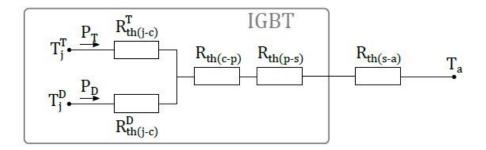

| Fig. 3.46 Thermal model of IGBT92                                                                                                                                                                            |        |

|                                                                                                                                                                                                              |        |

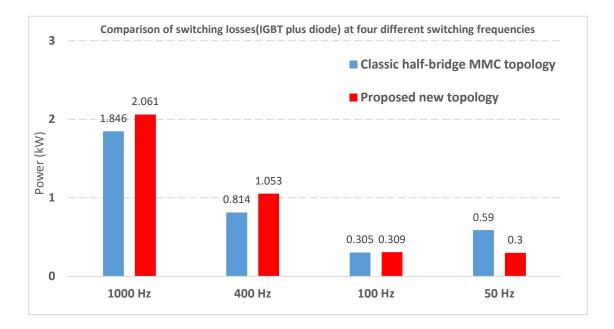

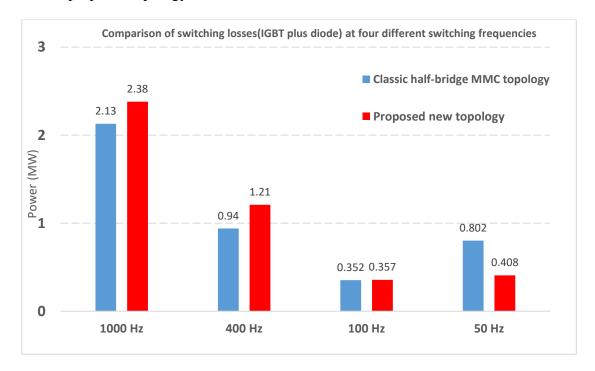

| Fig. 3.47 Circuit diagram of the proposed topology including damping resistors100 Fig. 3.48 Comparison of switching losses (IGBT plus diode) at four different switching frequencies                         |        |

| considering classic half-bridge MMC topology and proposed new topology10                                                                                                                                     | 1      |

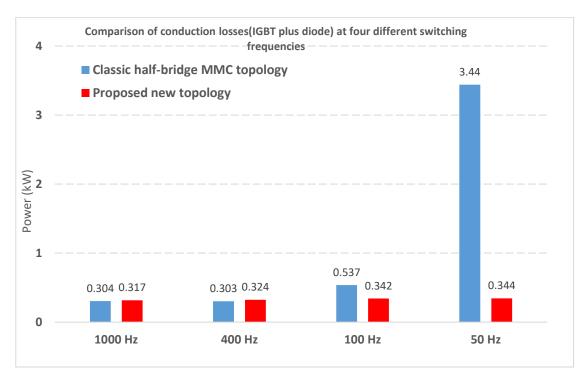

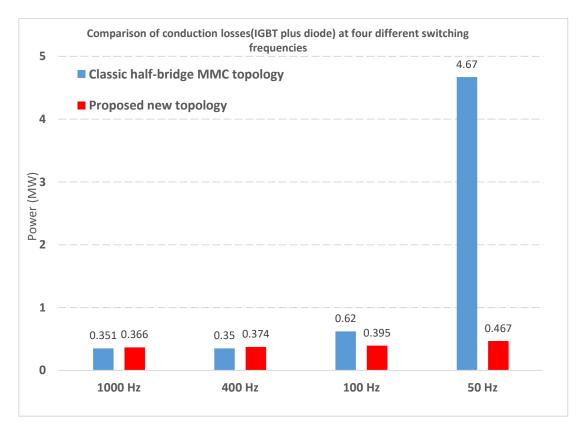

| Fig. 3.49 Comparison of conduction losses (IGBT plus diode) at four different switching frequencies                                                                                                          |        |

|                                                                                                                                                                                                              |        |

| considering classic half-bridge MMC topology and proposed new topology102                                                                                                                                    | 2      |

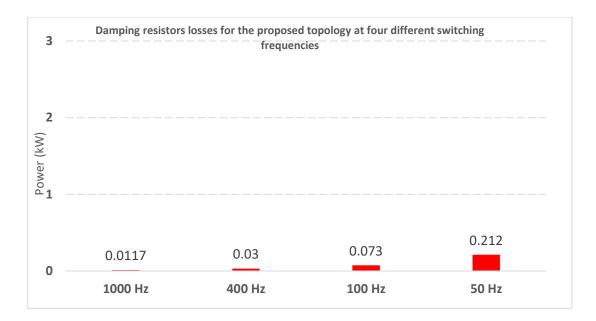

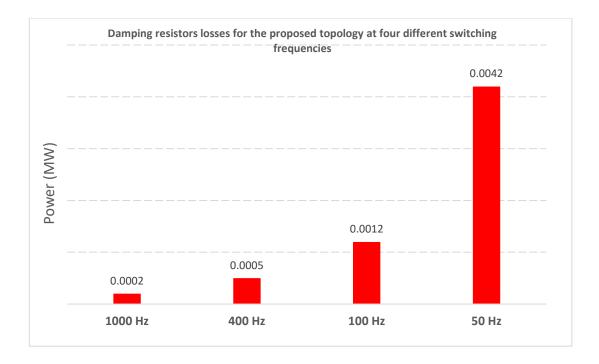

| considering classic half-bridge MMC topology and proposed new topology102<br>Fig. 3.50 Comparison of damping resistor losses at four different switching frequencies considering<br>proposed new topology102 |        |

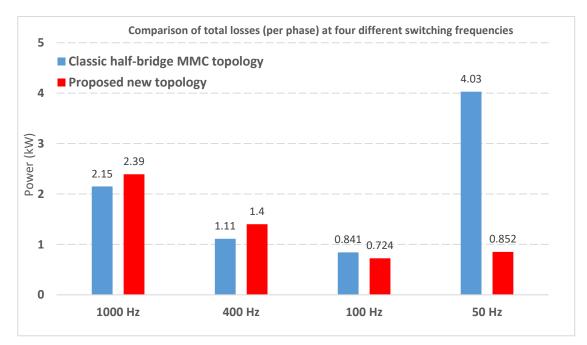

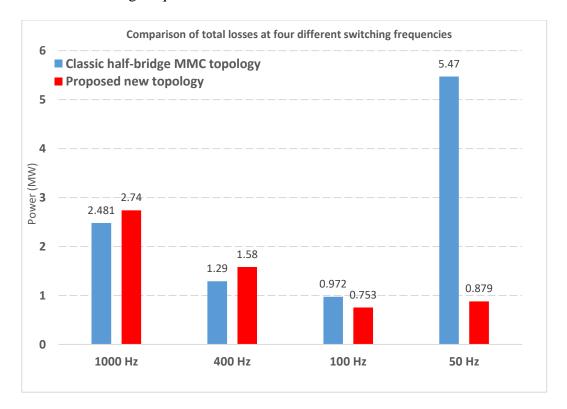

| classic half-bridge MMC topology and proposed new topology                                                                | 103      |

|---------------------------------------------------------------------------------------------------------------------------|----------|

| Fig. 3.52 One leg structure of hybrid MMC                                                                                 | 105      |

| Fig. 3.53 Circuit diagram of the proposed topology considering hybrid topology                                            | 106      |

| Fig. 3.54 One of the states                                                                                               | 107      |

| Fig. 3.55 One of the states (Impractical operation condition)                                                             |          |

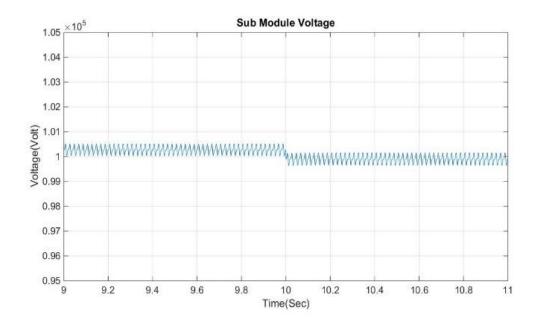

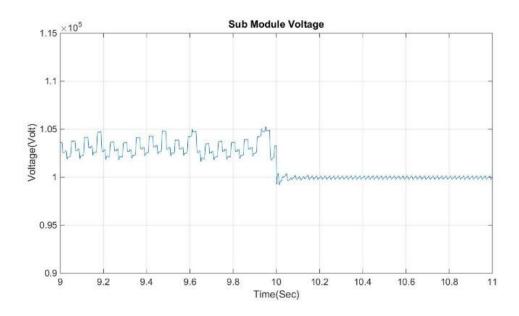

| Fig. 4.1 Sub module voltage before and after applying the proposed design at t=10 Sec and 1000 Hz                         |          |

| switching frequency<br>Fig. 4.2 Circulating current before and after applying the proposed design at t=10 Sec and 1000 Hz | 111      |

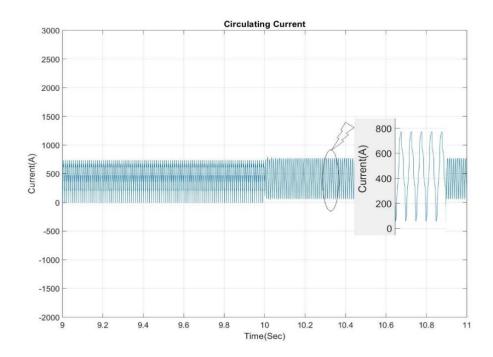

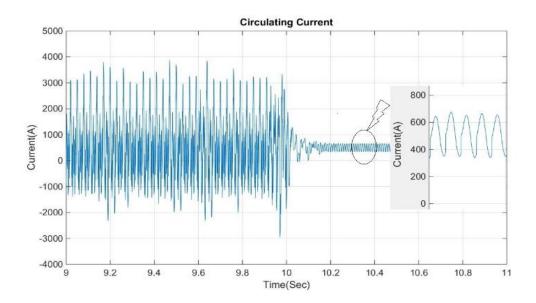

| Fig. 4.2 Circulating current before and after applying the proposed design at t=10 Sec and 1000 Hz switching frequency    | 112      |

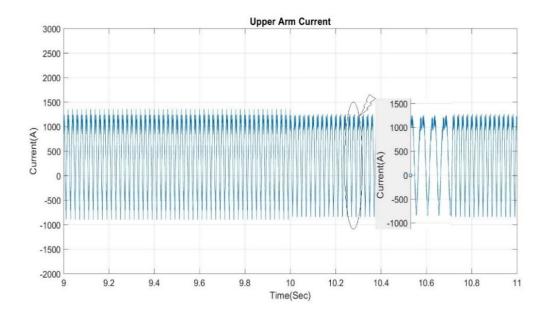

| Fig. 4.3 Upper arm current before and after applying the proposed design at $t=10$ Sec and 1000 Hz.                       |          |

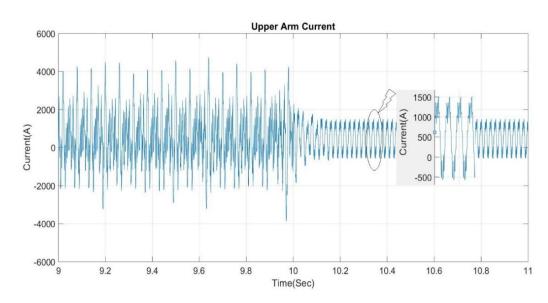

| Fig. 4.3 Upper arm current before and after applying the proposed design at t=10 Sec and 1000 Hz switching frequency      | 112      |

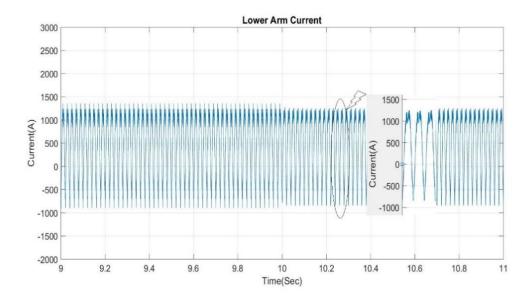

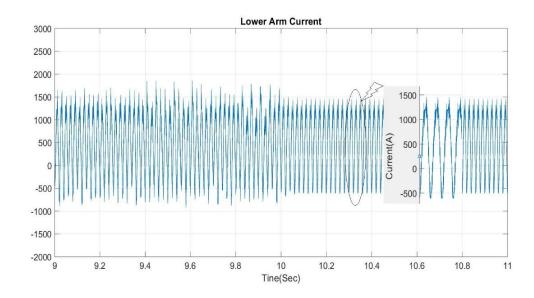

| Fig. 4.4 Lower arm current before and after applying the proposed design at $t=10$ Sec and 1000 Hz                        |          |

| switching frequency                                                                                                       | 113      |

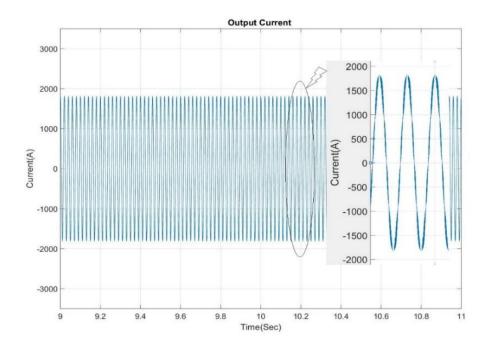

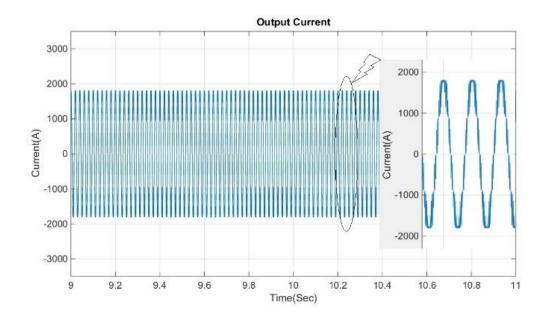

| Fig. 4.5 Output current before and after applying the proposed design at t=10 Sec and 1000 Hz switching frequency         |          |

| switching frequency                                                                                                       | 113      |

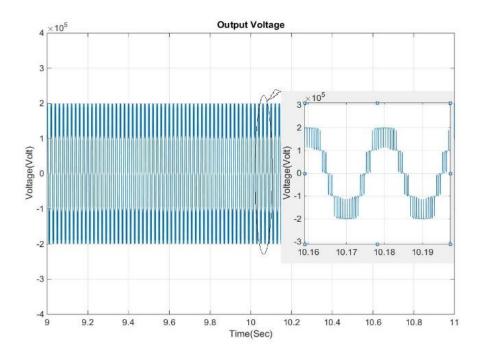

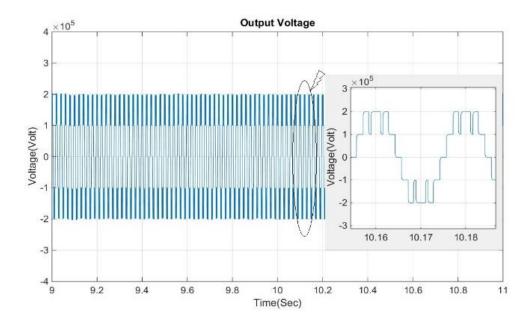

| Fig. 4.6 Output voltage before and after applying the proposed design at t=10 Sec and 1000 Hz switching frequency         |          |

| switching frequency                                                                                                       | 114      |

| Fig. 4.7 Sub module voltage before and after applying the proposed design at t=10 Sec and 400 Hz                          |          |

| switching frequency                                                                                                       | 114      |

| Fig. 4.8 Circulating current before and after applying the proposed design at t=10 Sec and 400 Hz                         |          |

| switching frequency                                                                                                       | 115      |

| Fig. 4.9 Upper arm current before and after applying the proposed design at t=10 Sec and 400 Hz                           | 115      |

| switching frequency                                                                                                       | 115      |

| Fig. 4.10 Lower arm current before and after applying the proposed design at t=10 Sec and 400 Hz                          | 116      |

| switching frequency                                                                                                       | 110      |

| switching frequency                                                                                                       | 116      |

| Fig. 4.12 Output voltage before and after applying the proposed design at t=10 Sec and 400 Hz                             | 110      |

| Fig. 4.12 Output voltage before and after applying the proposed design at t=10 Sec and 400 Hz switching frequency         | 117      |

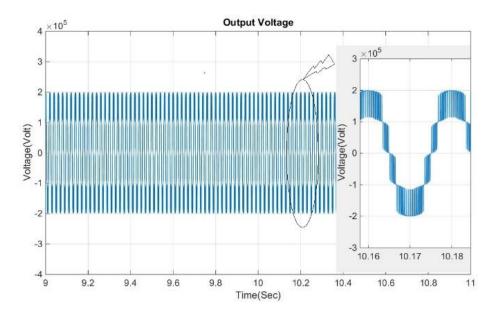

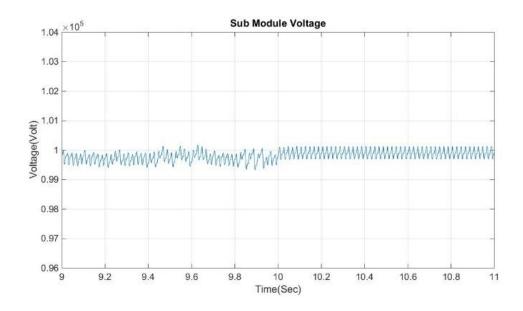

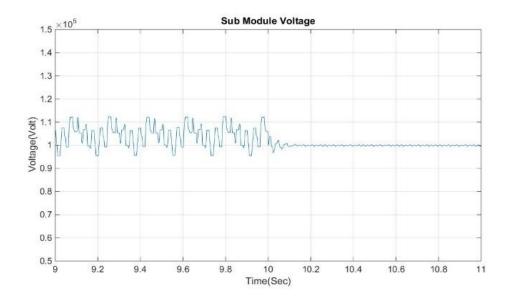

| Fig. 4.13 Sub module voltage before and after applying the proposed design at t=10 Sec and 100 Hz                         | 11/<br>Z |

| Fig. 4.13 Sub module voltage before and after applying the proposed design at t=10 Sec and 100 Hz switching frequency     | 117      |

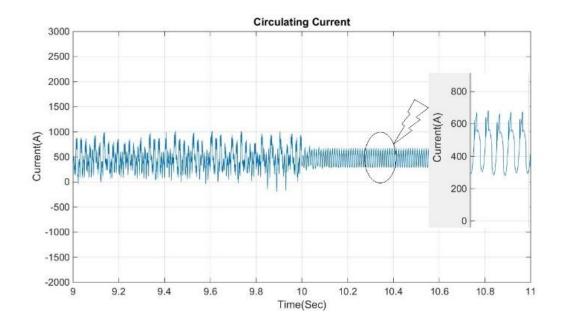

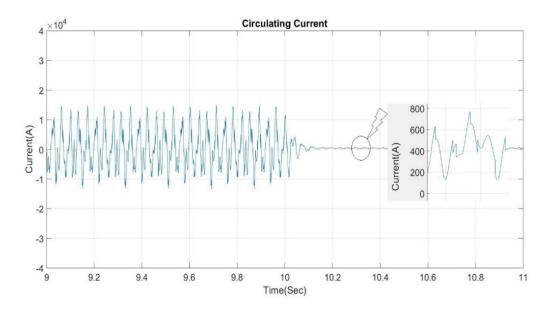

| Fig. 4.14 Circulating current before and after applying the proposed design at t=10 Sec and 100 Hz                        |          |

| switching frequency                                                                                                       | 118      |

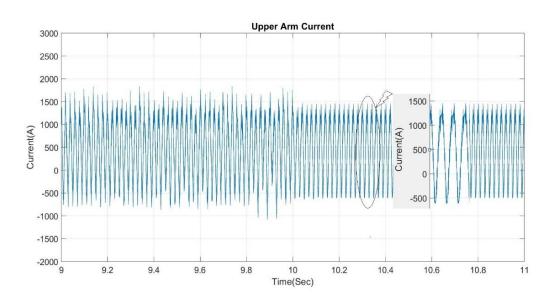

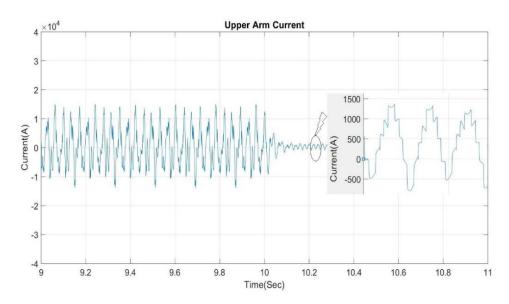

| Fig. 4.15 Upper arm current before and after applying the proposed design at t=10 Sec and 100 Hz                          |          |

| switching frequency                                                                                                       | 118      |

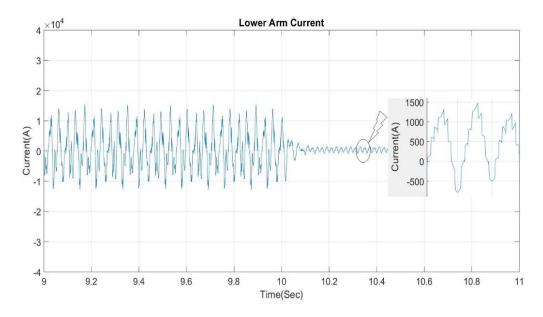

| Fig. 4.16 Lower arm current before and after applying the proposed design at t=10 Sec and 100 Hz                          |          |

| switching frequency                                                                                                       | 119      |

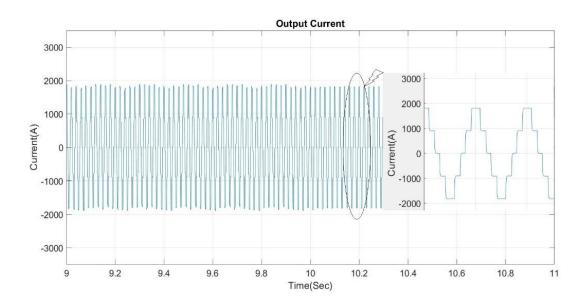

| Fig. 4.17 Output current before and after applying the proposed design at t=10 Sec and 100 Hz                             | 110      |

| switching frequency                                                                                                       | 119      |

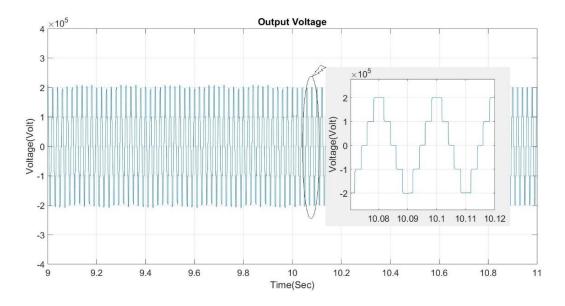

| Fig. 4.18 Output voltage before and after applying the proposed design at t=10 Sec and 100 Hz switching frequency         | 120      |

| Fig. 4.19 Sub module voltage before and after applying the proposed design at t=10 Sec and 50 Hz                          | 120      |

| switching frequency                                                                                                       | 120      |

| Fig. 4.20 Circulating current before and after applying the proposed design at t=10 Sec and 50 Hz                         | 120      |

| switching frequency                                                                                                       | 121      |

| Fig. 4.21 Upper arm current before and after applying the proposed design at t=10 Sec and 50 Hz                           |          |

| switching frequency                                                                                                       | 121      |

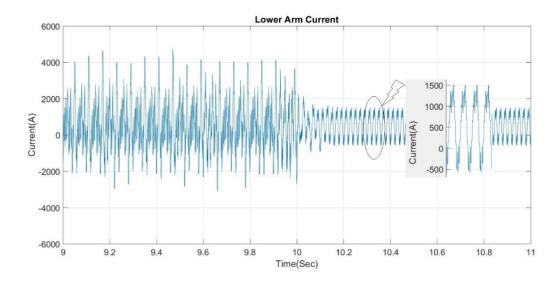

| Fig. 4.22 Lower arm current before and after applying the proposed design at t=10 Sec and 50 Hz                           |          |

| switching frequency                                                                                                       | 122      |

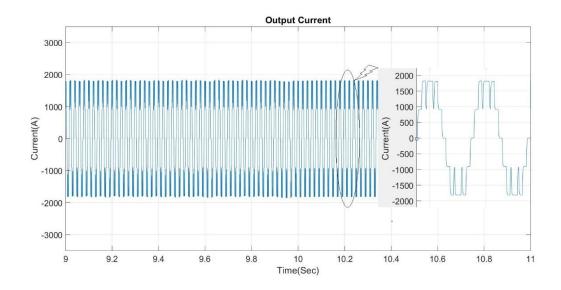

| Fig. 4.23 Output current before and after applying the proposed design at t=10 Sec and 50 Hz                              |          |

| switching frequency                                                                                                       | 122      |

| Fig. 4.24 Output voltage before and after applying the proposed design at t=10 Sec and 50 Hz                              |          |

| switching frequency                                                                                                       | 123      |

| Fig. 4.25 Comparison of switching losses (IGBT plus diode) at four different switching frequencies                        | \$       |

| considering classic half-bridge MMC topology and proposed new topology with East-West Inter-                              |          |

| Connector values1                                                                                                                                     | 125   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Fig. 4.26 Comparison of conduction losses (IGBT plus diode) at four different switching frequencies                                                   | es    |

| considering classic half-bridge MMC topology and proposed new topology with East-West                                                                 |       |

| Inter-Connector values1                                                                                                                               | 126   |

| Fig. 4.27 Comparison of damping resistor losses at four different switching frequencies considering                                                   | 5     |

| proposed new topology and East-West Inter-Connector values1                                                                                           | 127   |

| Fig. 4.28 Comparison of total losses (per phase) at four switching frequencies considering classic                                                    |       |

| half-bridge MMC topology and proposed new topology with East-West Inter-Connector values1                                                             | 127   |

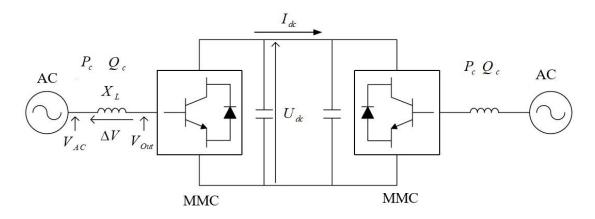

| Fig. 4.29 MMC based HVDC transmission operation1                                                                                                      | 129   |

| Fig. 4.30 Four-Quadrant Operation of MMC1                                                                                                             | 130   |

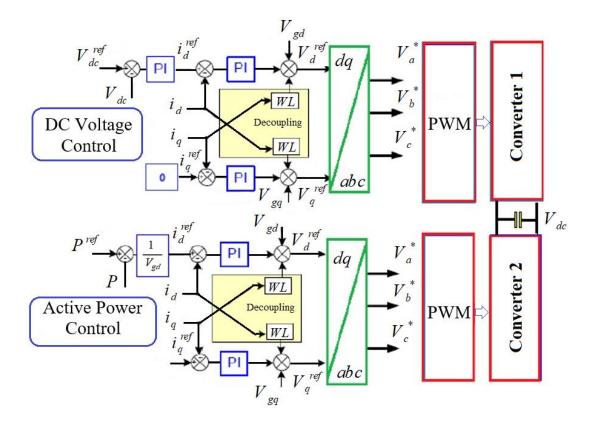

| Fig. 4.31 Control schematic of MMC-HVDC1                                                                                                              | 131   |

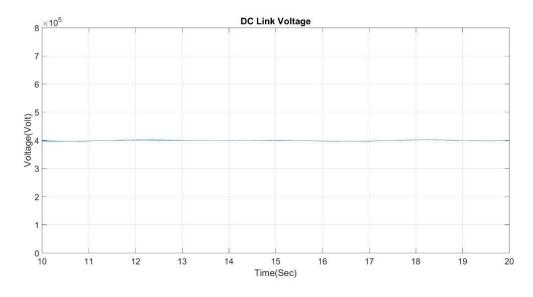

| Fig. 4.32 DC link voltage1                                                                                                                            | 132   |

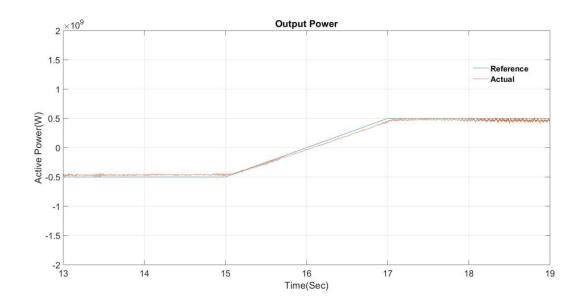

| Fig. 4.33 Dynamic change for active power1                                                                                                            | 133   |

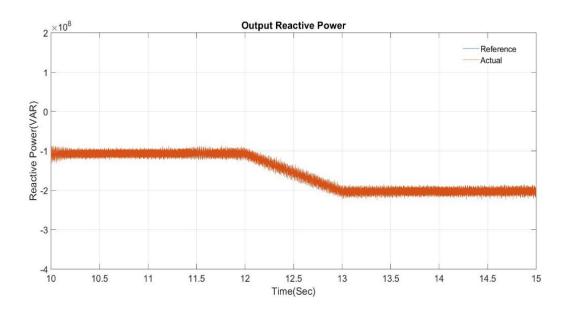

| Fig. 4.34 Dynamic change for reactive power1                                                                                                          | 133   |

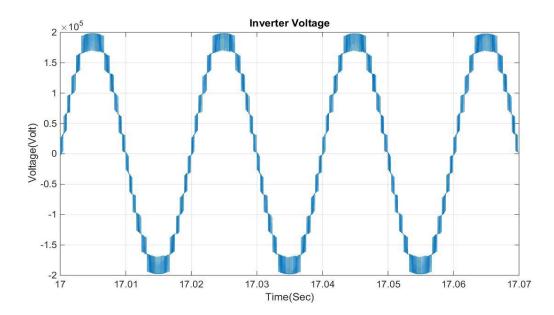

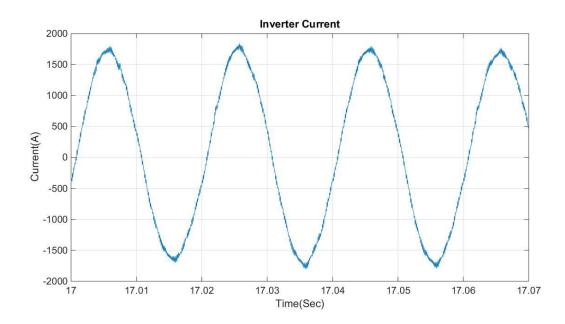

| Fig. 4.35 The inverter output voltage1                                                                                                                | 134   |

| Fig. 4.36 The inverter output current1                                                                                                                | 134   |

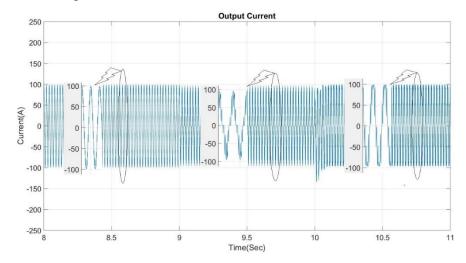

| Fig. 4.37 Output current variation with two faulty sub modules at the upper arm and two faulty sub                                                    |       |

| modules at the lower arm and considering the new design after t=10 Sec1                                                                               | 137   |

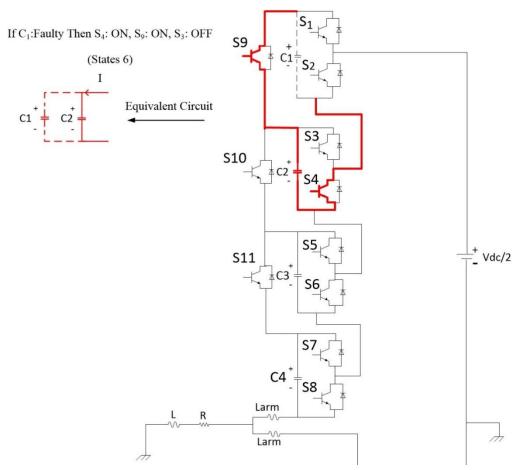

| Fig. 4.38 Fault tolerant operation at state 61                                                                                                        | 138   |

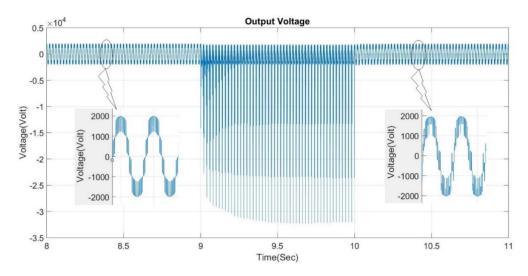

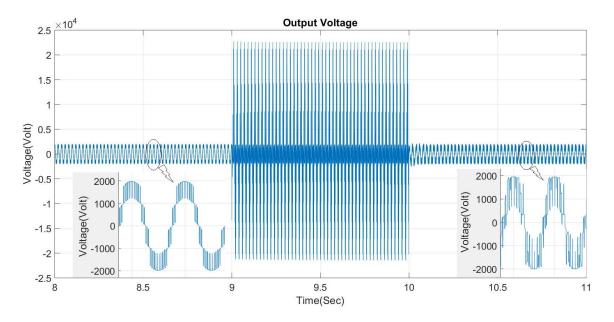

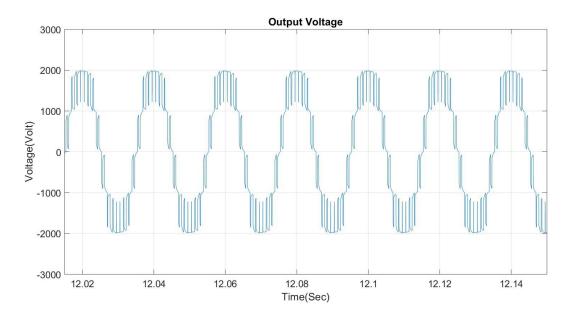

| Fig. 4.39 Output voltage at state 61                                                                                                                  | 139   |

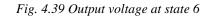

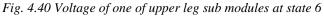

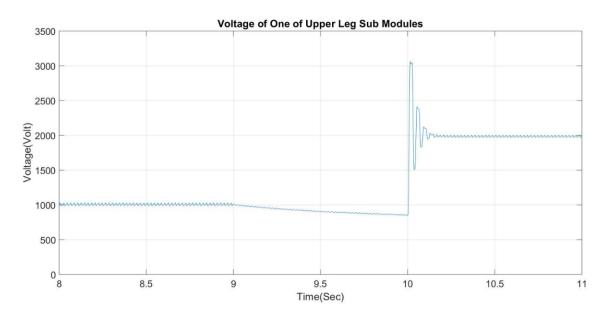

| Fig. 4.40 Voltage of one of upper leg sub modules at state 61                                                                                         |       |

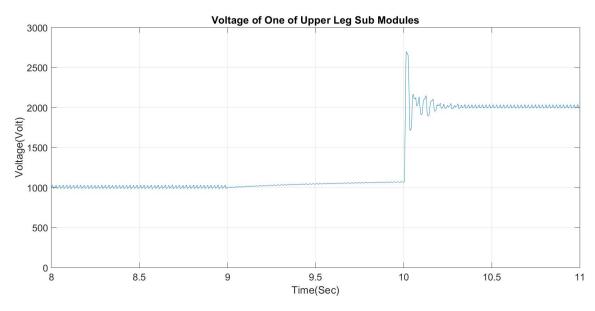

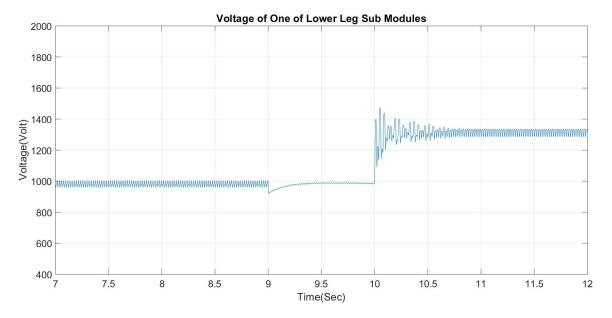

| Fig. 4.41 Voltage of one of lower leg sub modules at state 61                                                                                         |       |

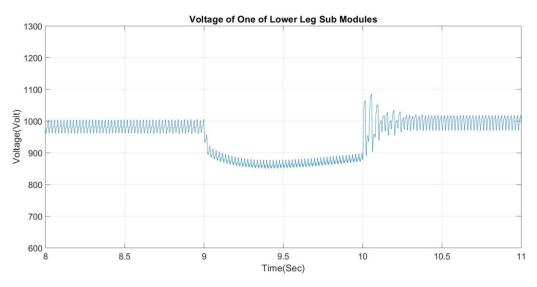

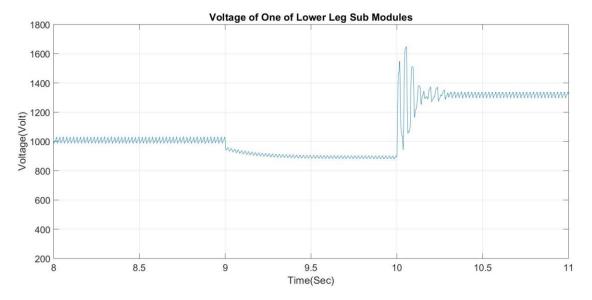

| Fig. 4.42 Fault tolerant operation at state 71                                                                                                        | 140   |

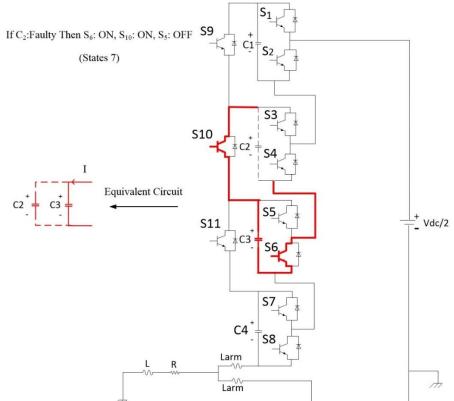

| Fig. 4.43 Fault tolerant operation at state 81                                                                                                        | 141   |

| Fig. 4.44 Fault tolerant operation at state 111                                                                                                       | 142   |

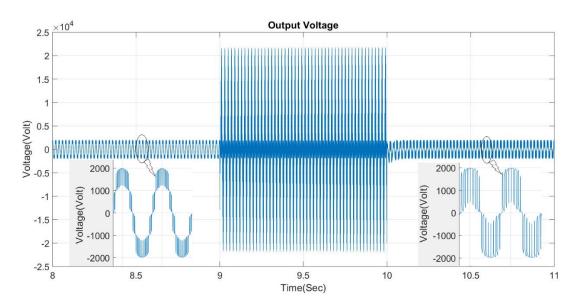

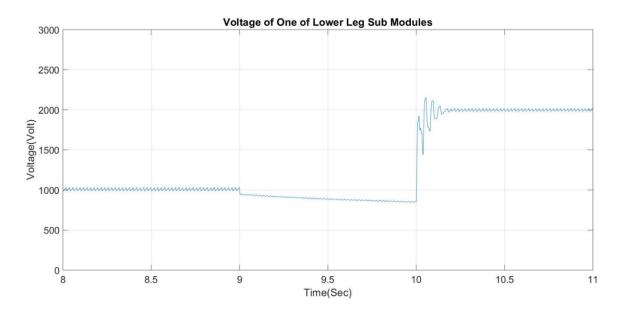

| Fig. 4.45 Output voltage at state 111                                                                                                                 | 142   |

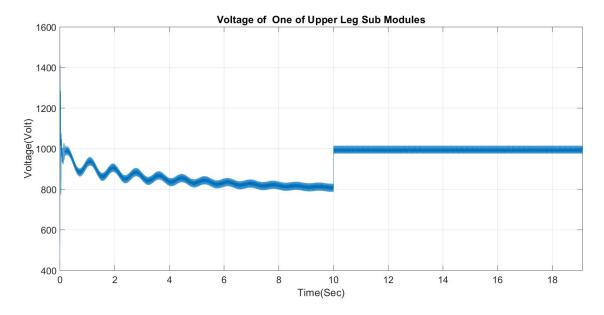

| Fig. 4.46 Voltage of one of upper leg sub modules at state 111                                                                                        | 143   |

| Fig. 4.47 Voltage of one of lower leg sub modules at state 111                                                                                        | 143   |

| Fig. 4.48 Output voltage considering two faulty sub modules at the upper arm and one faulty                                                           |       |

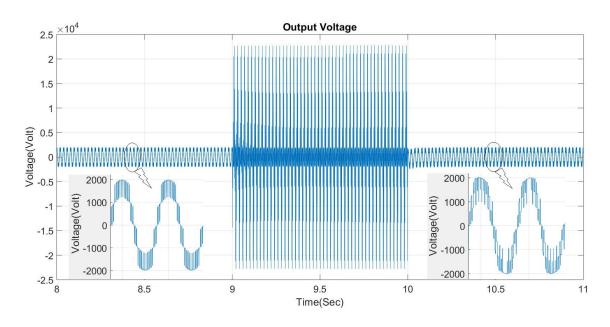

| sub module at the lower arm1                                                                                                                          |       |

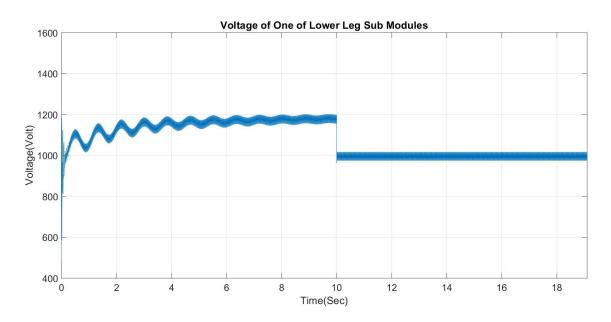

| Fig. 4.49 Voltage of one of upper leg sub modules considering two faulty sub modules at the upper arm and one faulty sub module at the lower arm1     |       |

| arm and one faulty sub module at the lower arm                                                                                                        | 144   |

| Fig. 4.50 Voltage of one of lower leg sub modules considering two faulty sub modules at the upper arm and one faulty sub module at the lower arm1     |       |

|                                                                                                                                                       | 145   |

| Fig. 4.51 Output voltage considering two faulty sub modules at the upper arm and two faulty                                                           | 1 4 7 |

|                                                                                                                                                       | 145   |

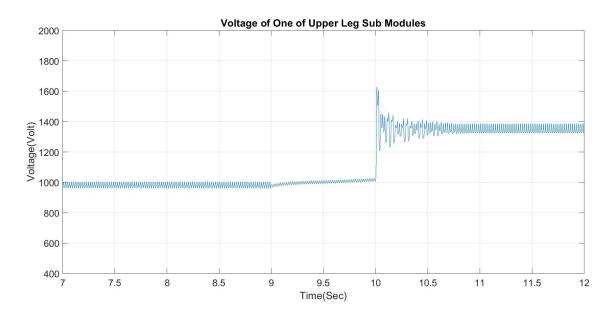

| Fig. 4.52 Voltage of one of upper leg sub modules considering two faulty sub modules at the upper                                                     |       |

| arm and two faulty sub modules at the lower arm1<br>Fig. 4.53 Voltage of one of lower leg sub modules considering two faulty sub modules at the upper | 140   |

| arm and two faulty sub modules at the lower arm1                                                                                                      |       |

| Fig. 4.54 Output voltage considering one faulty sub module at the upper arm and one faulty                                                            | 140   |

| sub module at the lower arm1                                                                                                                          | 1/7   |

| Fig. 4.55 Voltage of one of upper leg sub modules considering one faulty sub module at the upper                                                      | 14/   |

| arm and one faulty sub module at the lower arm1                                                                                                       | 147   |

| Fig. 4.56 Voltage of one of lower leg sub modules considering one faulty sub module at the upper                                                      | 17/   |

| arm and one faulty sub module at the lower arm1                                                                                                       | 148   |

| Fig. 4.57 The sub module voltage variation for one of upper arm sub modules without using voltage                                                     |       |

| sensors1                                                                                                                                              | 150   |

| Fig. 4.58 The sub module voltage variation for one of lower arm sub modules without using voltage                                                     |       |

| sensors1                                                                                                                                              |       |

| Fig. 4.59 The output voltage variation considering the new design without using voltage sensors1                                                      |       |

# List of Tables

| Table 1.1 Summary of some worldwide VSC-HVDC projects                                           | 9   |

|-------------------------------------------------------------------------------------------------|-----|

| Table 2.1 Six operating states of a Half-Bridge sub module                                      | 18  |

| Table 2.2 Comparison between different switching algorithms used for MMCs                       |     |

| Table 3.1 Switching states for the upper leg                                                    | 62  |

| Table 3.2 Voltage stresses on the added switches                                                | 63  |

| Table 3.3 Simulation parameters in unity power factor condition                                 | 74  |

| Table 3.4 The converter efficiency at four different switching frequencies                      | 104 |

| Table 4.1 Simulation parameters in unity power factor condition                                 | 110 |

| Table 4.2 Output voltage and current THD at four different switching frequencies for 5-level an | ıd  |

| 9-level output                                                                                  | 124 |

| Table 4.3 The converter efficiency at four different switching frequencies                      | 128 |

| Table 4.4 Simulation parameters considering East-West Inter-Connector nominal values            | 131 |

| Table 4.5 Faults in sub module capacitors                                                       | 135 |

| Table 4.6 Possible sub module capacitor failure states                                          |     |

| (capacitor open circuit considering the upper arm)                                              | 136 |

| Table 4.7 Simulation parameters of system without using voltage sensors                         | 149 |

### Chapter 1

## Introduction

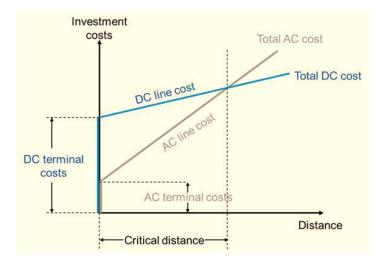

For the first half of twentieth century, AC power transmission was the preferable option due to the ability of power transformers to step up and step-down voltage levels to reduce the power losses. During the early 1950s, there was a renewed interest in the use of DC technology as it was a cost effective option for long distance overhead line transmission [1]. Where transmission distances are very long (beyond 1000 km) the AC transmission capacity is limited due to stability considerations. A high voltage drop occurs across the AC transmission lines. However, the DC transmission line is free from inductance, and hence only a small resistive voltage drop occurs across the line. The other advantage of DC transmission line is that the phenomenon of skin effect is not present on the DC transmission line. Lower insulation requirement and absence of Corona effect are the other superiorities of DC transmission line. Fig. 1.1 depicts that the initial investment cost for the DC terminal is higher than the AC one. However, for long distances the total cost for the DC transmission will be lower than the AC transmission.

Fig. 1.1 Investment costs for DC and AC transmission lines

#### 1.1 Power Converters

#### 1.1.1 Current source converter (CSC)

As the name indicates, the current source converter (CSC) likes to see a stiff DC current source at the input (ideally with infinite Thevenin impedance). The current source can be achieved by connecting a large inductor (inductance) in series with a variable voltage source that is controlled by a current feedback loop. With a stiff DC current source, the AC output currents will not be affected by load conditions. Since power semiconductor devices in a CSC must withstand reverse voltage, symmetric voltage blocking devices such as thyristors are usually used [2].

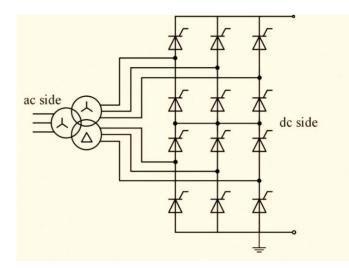

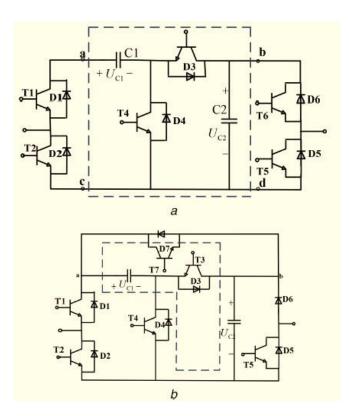

CSCs have been the only HVDC transmission solution for many decades and they are still the first choice for bulk power transmission at the GW-level [3],[4]. A CSC is usually based on a 12-pulse bridge configuration as shown in Fig. 1.2 Three AC connectors are on the left-hand side and two DC terminals are on the right-hand side. Two of such 12-pulse bridges are usually connected in series to form the positive and negative terminals of the DC bus as shown in Fig. 1.3.

Fig. 1.2 A 12-pulse converter bridge [5]

Fig. 1.3 A bipolar CSC-HVDC system with one 12-pulse bridge per pole [5]

The advantage of such a structure is that one pole can continue to transmit power in the case that the other one is out of service for whatever reason. Each system can operate on its own as an independent system with the earth return. Projects at a DC voltage of  $\pm 800$  kV are also termed ultra-high voltage (UHV) DC systems and they usually consist of two such series connected 12-pulse bridges per pole.

The advantages of the CSC-HVDC system include a high overload capability, excellent robustness, reliability and low operational losses. The total loss of an AC transmission system with 6.4 GW capacity at 1,000 kV is around 7% per 1,000 km, while the line loss of a  $\pm$ 800 kV HVDC with the same capacity is only 3.5%. Even when the 0.7% converter losses per station are included, the total loss of a CSC-HVDC system is still much lower than the HVAC option [5].

Although the CSC-HVDC serves the transmission industry well, it has several drawbacks:

• First, the AC outputs contain significant low order harmonics, which will cause various power quality problems, leading to higher losses and the malfunction of sensitive loads [2]. Massive filters are necessary on both the AC side and DC side for smooth power outputs.

• Second, due to the absence of the turn-off capability in the thyristor, the commutation of the switch is driven by the interconnected AC grid and the current is always lagging, i.e. keeps absorbing reactive power from the grid. As a result, massive reactive power compensation equipment is required on the AC side.

• Third, the direction of the power flow cannot be reversed by reversing the DC current due to the switch configuration. The change of power flow direction can only be achieved through a change in DC polarities. As a result, the relatively cheap and light polyethylene insulated DC cables are not suitable due to their poor fast polarity reversal capability. This is also one of the major obstacles to building a multi-terminal DC grid using CSC technology [6].

• Finally, the CSC-HVDC is sensitive to the strength of the inter-connected AC system. Particularly at the inverter side, slight disturbances in the AC system may lead to commutation failure in the converter. Consecutive commutation failures may lead to system breakdown.

#### 1.1.2 Voltage source converter (VSC)

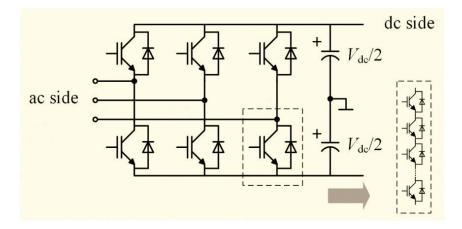

Voltage source converters (VSCs), as the name indicates, receive DC voltage at one side and convert it to AC voltage on the other. A VSC prefers a stiff DC voltage source at the input (ideally zero Thevenin impedance) which is usually achieved using large capacitors[2]. Ever since the first VSC project ( $\pm 10$  kV, Hellsjon experimental project) was built in1997, the voltage and power ratings of VSCs have steadily increased. Currently, VSC systems with ratings of up to  $\pm 320$  kV, 1 GW are technically achievable. Fig. 1.4 shows the simplest VSC topology, i.e. the two-level AC/DC converter (with IGBT/diode modules). In VSCs, the power semiconductor switches always remain forward-biased due to the DC bus voltage, and therefore, not only IGBTs, but all other self-controlled forward or asymmetric blocking switches, such as GTOs, BJTs, power

MOSFETs, and IGCTs can be used. A diode is always connected across the device to achieve free reverse current flow and ensure the four-quadrant operation of the converter.

Fig. 1.4 Diagram of a two-level VSC

Since the blocking voltage of currently available IGBT modules is only up to 6.5 kV, in order to block the voltage up to a few hundred kV, large amounts of IGBT modules are directly connected in series as shown in the dashed box in Fig. 1.4. Typically, VSCs are controlled through pulse width modulation (PWM) techniques, among which the sinusoidal PWM (SPWM) is the simplest and thus is commonly adopted for industrial converters. When compared with the thyristor-based CSC-HVDC system, the IGBTbased VSC-HVDC system has the following benefits [7]:

• Both the amplitude and phase angle of AC output voltages can be controlled independently, offering independent and rapid control of the active and reactive power. The fast dynamic can help to enhance the transient stability of the interconnected AC grid.

• Owing to the self-commutation capability of the IGBT, VSCs can operate in all four quadrants of the *P*-*Q* operating plane without external reactive power compensation.

• Power reversal can be achieved through reversing the DC current instead of the DC voltage polarities, which is critical for a multi-terminal DC grid.

• Due to the high frequency of switching, the harmonics that need to be filtered are at high frequencies and thus the filtering demands are largely reduced.

On the other hand, two and three-level VSCs have their own disadvantages [8]:

• In order to achieve the high voltage rating, large amounts of IGBTs are connected in series, demanding very complex gating and protection schemes.

• The PWM process requires the simultaneous switching of series-connected devices at high frequencies (one to a few kHz), leading to significant power losses (typically 1.6% per station). This is one major reason why the CSC-HVDC is still preferable for bulk power transmissions.

The situation began to change with the advent of the modular multilevel converter (MMC), which was a milestone in VSC technology and in 2010 the first MMC project started commercial operations, i.e. the Trans Bay Cable in the United States rated at  $\pm 200 \text{ kV}$ , 400 MW.

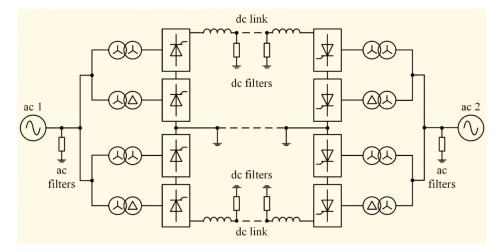

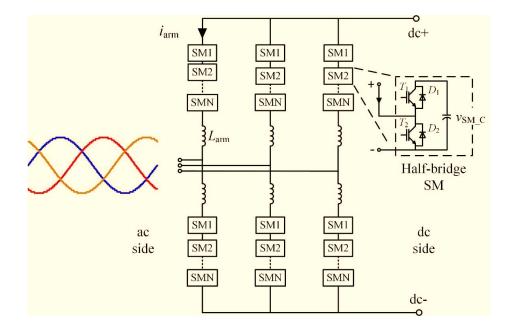

Fig. 1.5 shows a typical configuration of a DC to three-phase AC MMC system. Valve in the converter arms is no longer a single IGBT/diode module but a controllable VSC itself, which is usually referred to as sub module (SM) or cell.

A SM can be a half-bridge (HB) converter as shown in the dashed line box (Fig. 1.5), a full-bridge (FB) converter, or it can appear in other forms. Direct series connection of power switches is no longer needed. Each SM can be switched as low as the AC line frequency leading to increased efficiency and reduced cooling demands. Typical losses for one MMC station can be less than 1.0%. The large number of steps in the synthesized AC voltage waveform provides low distortion and good EMC performance. Hence, harmonic filters become a thing of the past for both the AC side and DC side [6].

Fig. 1.5 Typical configuration of a DC to three-phase AC MMC system

## 1.2 High Voltage DC transmission

In recent times, High Voltage DC (HVDC) transmission is becoming more popular for the interconnection of remote renewable energy resources to the grid. Installation of HVDC transmission lines are increasing in China, Europe and North America. For long transmission distances, the lifetime cost for HVDC system is lower than HVAC system and this makes HVDC system the more appropriate option for long distance large-scale offshore wind energy transmission [9].

#### 1.2.1 Line Commutated Converter (LCC) Based HVDC

The LCC HVDC system is a classic solution for the DC transmission system, in use since mid-20th century, which employs high power thyristors in converters. It is also called a Current Source Converter (CSC) as it acts as a current source to the grid. By regulating the firing angle ( $\alpha$ ), rectifier and inverter terminals control DC current and voltage respectively [10]. The LCC-HVDC transmission line can operate only in AC grids with established or live AC voltages as it requires these live AC voltages to commutate currents from outgoing to incoming arm. The direction of real power flow is

from rectifier to inverter and both converters consume reactive power. The LCC station has large footprint as it uses large switched capacitor banks and AC side harmonic filters to supply its reactive power consumption, which varies with the magnitude of DC or real power transfer, particularly, at inverter terminal. The need for the fast-acting mechanical switches during the power reversal is one of the drawbacks of the LCC MTDC system. The other issue is the commutation failure at inverter terminal during asymmetric AC faults or generally during operation in weak AC grids [11]. The Sardinia-Corsica-Italy (SACOI) interconnection and the Hydro-Quebec-New England interconnection are examples of existing LCC MTDC systems. Currently, an increase in the rated power, nominal voltage and length of transmission distance is observed. The power capacity can exceed 5000 MW, at voltage of 800 kV and transmission distances via overhead line up to 3000 km. Work is underway on the use of 1100 kV voltage for the transmission of 10-12 GW power over the distance of 2000 km. The largest, so far, LCC HVDC systems have been built in China and India. An important application of LCC HVDC technology are subsea connections of non-synchronous areas. Many such connections have been implemented in Europe. The largest are the NorNed connection, between Norway and the Netherlands, with the following parameters: rated power 700 MW, cable length 580 km, voltage  $\pm$ 450 kV. Under construction is a connection between Norway and the UK with a length of 750 km and a rated power of 1400 MW.

#### 1.2.2 Voltage Source Converter (VSC) Based HVDC

The application of voltage source converters in HVDC transmission system has been developing since 1997. VSC technology uses IGBTs with antiparallel diodes in the converter bridge to allow current flow in both directions and voltage blocking in forward and backward directions. The most beneficial advantage of VSC based HVDC over LCC based HVDC is independent control of active and reactive powers, which is achieved by

exploiting two available control degree of freedom. Moreover, because of less filtering and reactive power requirements, the footprint of a VSC is much smaller than an equivalent LCC station. The main disadvantage of VSC technology is the high switching losses due to the use of high frequency pulse width modulation (PWM) [12].

| Name           | <b>Converter Station 1</b> | <b>Converter Station 2</b> | Cable (km)   | Voltage (kV) | Power | Year |

|----------------|----------------------------|----------------------------|--------------|--------------|-------|------|

|                |                            |                            |              |              | (MW)  |      |

| Hellsjön-      | Sweden – Hellsjoen         | Sweden –                   | 10, Overhead | 180          | 3     | 1997 |

| Grängesberg    |                            | Graengesberg               | line         |              |       |      |

|                |                            |                            |              |              |       |      |

| Terranora      | Australia –                | Australia – Bungalora      | 59           | 80           | 180   | 2000 |

| interconnector | Mullumbimby                |                            |              |              |       |      |

| (Direktlink)   |                            |                            | 10           | 1.50         | 220   |      |

| Cross Sound    | USA – New Haven,           | USA – Shoreham,            | 40           | 150          | 330   | 2002 |

| Cable          | СТ                         | Long Island                |              |              |       |      |

| HVDC Troll     | Norway – Kollsnes          | Norway – Offshore          | 70           | 60           | 80    | 2004 |

|                |                            | platform                   |              |              |       |      |

| Estlink        | Estonia – Harku            | Finland – Espoo            | 105          | 150          | 350   | 2006 |

| NordE.ON 1     | Germany – Diele            | Germany – Borkum 2         | 203          | 150          | 400   | 2009 |

|                |                            | platform                   |              |              |       |      |

| Trans Bay      | USA – East Bay –           | USA – San Francisco,       | 88           | 200          | 400   | 2010 |

| HVDC           | Germany – Dörpen           | Germany – DolWin           | 165          | 320          | 800   | 2013 |

| DolWin1        |                            | Alpha platform             |              |              |       |      |

| HVDC           | Sweden – Nybro             | Lithuania – Klapeida       | 450          | 300          | 700   | 2015 |

| NordBalt       |                            |                            |              |              |       |      |

| DolWin3        | Germany – Heede            | Germany – DolWin           | 160          | ±320         | 900   | 2017 |

| Caithness      | UK – Spittal               | UK – Blackhillock          | 160          | 320          | 1200  | 2018 |

| Moray HVDC     | - ~ <b>r</b>               |                            |              |              |       |      |

|                |                            |                            |              |              |       |      |

| Nemo Link      | Belgium –                  | UK – Richborough           | 140          | 400          | 1000  | 2019 |

|                | near Bruges                | Energy Park                |              |              |       |      |

| IFA-2          | France – Tourbe,           | UK -Pilling,               | 240          | 400          | 1000  | 2020 |

|                | Normandie                  | Hampshire                  |              |              |       |      |

Table.1.1 Summary of some worldwide VSC-HVDC projects [13]

Currently, point-to-point systems up to 1200 MW with cross-linked polyethylene cables and 500 kV voltage are used. Table. 1.1 summarizes the installed VSC HVDC projects in the world. Research into the most appropriate converter bridge topology design is ongoing. One of the most advanced voltage source converters is the Modular Multi-Level Converter (MMC) and it is the converter technology that this research is based on.

Among the existing MMC topologies for the HVDC, an MMC structure consisted of Half-Bridge Sub Module (HBSM)s has characteristics such as reduced system cost and low operation loss. The main disadvantage of the Half-Bridge Sub Module MMC is its fault blocking capability during the DC fault condition. To cope this issue, Full-Bridge Sub Module (FBSM)s could be added to the MMC structure. However, balancing the sub module capacitor voltages where each arm of the MMC is consisted of mixed (HBSM)s and (FBSM)s, is very difficult. Chapter 2, investigates about different challenges for HVDC system considering modular multi-level converters and also design aspects for the MMC.

### **1.3 Research Motivation**

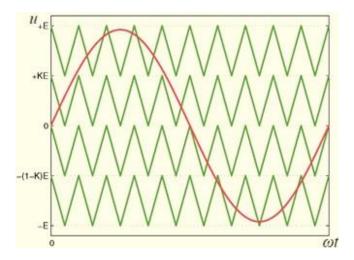

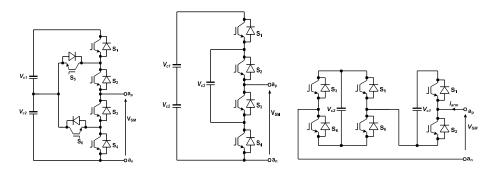

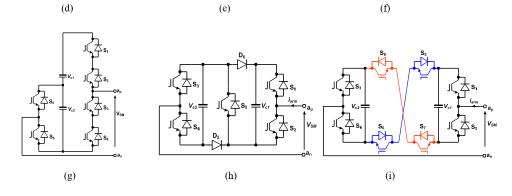

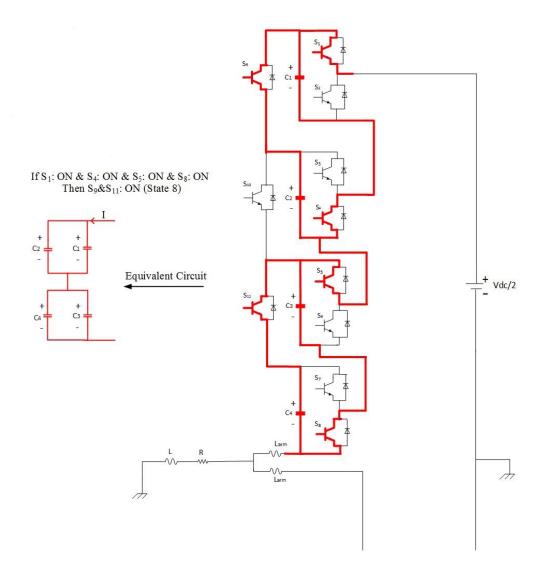

Modular multilevel converters have become popular in recent years because of their high efficiency, low harmonic distortion without using output filters, low switching frequency and high modularity [14]. Several multilevel topologies have been proposed, including a hybrid multilevel converter with AC side cascaded H-bridge cells, an alternative arm modular multilevel converter and a DC side cascaded multilevel with half bridge or full bridge cells connected across the DC link [15, 16]. The presented MMC topologies have several disadvantages which affect their performance. The circulating current which occurs mainly due to the sub module voltage fluctuations is one of the challenges of the DC side cascaded MMC topology. Several control methods are proposed in the literature to suppress and eliminate the circulating current and most of the proposed methods are complex and difficult to implement [17-19]. The sub module voltage fluctuation is the main reason for the appearance of the circulating currents. It should be noticed that choosing a higher switching frequency will lead to a less sub module voltage ripple as well as a smaller sub module capacitor size but it will increase the converter losses. So the ideal working point could be a lower switching frequency with an acceptable voltage ripple (less than 10%) for each sub module which will necessitate the large sub module capacitor to constrain the voltage ripple. However, the ideal point is prohibitively uneconomical for the high voltage applications because the ideal point can only be achieved with extremely large sub module capacitance.

Converter reliability is the other important challenge in modular multilevel converters, since they include many components. For this reason, the development of fault-tolerant converter topologies and strategies are relevant research topics nowadays. Multiple studies analyse the reliability and provide solutions to faults. However, these techniques imply a high increase in the converter cost and complexity [20, 21].

In this research, a new topology for the MMC has been proposed which can maintain the sub module voltage ripples in an acceptable range even with lower switching frequencies without the need for large sub module capacitors. Moreover, the proposed design has more reliability in case of sub module capacitor failure and can operate without sub module voltage sensors. The main contribution is providing the acceptable voltage regulation (less than 10%) for each sub module and minimum switching losses during switching period by adding additional switches to connect idle capacitors in parallel with active sub modules. The other contribution is converter reliability improvement which is achievable by the elimination of using voltage sensors and fault tolerant operation.

### 1.4 Research Questions and Objectives

Based on the discussion of the previous sections, the research questions and aims are defined as follows:

• How to eliminate the sub module voltage fluctuations with smaller sub module capacitor values at low switching frequencies? This issue also will be addressed by proposing a new MMC topology.

• How the MMC can operate at lower switching frequencies? The proposed design implements idle capacitors in parallel with sub modules. Consequently, the sub module capacitor size will be increased without the need to large sub module capacitors and the MMC will operate at lower switching frequencies with acceptable sub module ripple.

• What will be the converter efficiency with the new proposed topology? The new design uses some extra switches during the switching period. So, the MMC loss analysis at the lower switching frequencies will be done to calculate the efficiency of the new design.

• What will be the content of circulating current after applying the new design? After applying the new design at the low switching frequency (100 Hz), the amount of circulating current will be comparable to the achieved value at higher switching frequency of 1000 Hz.

• How the reliability of converter can be improved applying the new design? Operation without using any sub module voltage sensors will reduce the converter cost and complexity and will improve the converter reliability. Moreover, the proposed

12

topology can be kept in operational condition and work with more reliability in the case of the sub module capacitor failure.

The proposed topology is validated in simulation by modelling in MATLAB/Simulink. The simulation speed is the main limitation for this research, specially when the higher number of switches are utilized in the MMC design.

## 1.5 Thesis Outline

The thesis is divided into 5 Chapters. The first Chapter is a brief introduction about the HVDC transmission with LCC and VSC technologies. Research motivation and questions are also presented at the end of this Chapter. Review of the modular multilevel converters and different challenges for HVDC system considering modular multilevel converters is presented in Chapter 2. Chapter 3 explains about the proposed new MMC topology and its operational principle. In Chapter 4, Operation of the new proposed design at HVDC system level, sub module capacitor failure condition and impact of applying the proposed design at reducing the number of sub module voltage sensors are investigated. The proposal for the future work and conclusions is presented in the final Chapter.

## Chapter 2: Review of The Modular Multilevel Converters and Different Challenges for HVDC System Considering Modular Multilevel Converters

This chapter reviews about the operational principle and different modulation techniques of the MMC. Design considerations and challenges considering modular multilevel converters also are discussed in this chapter. The mathematical model of Half-Bridge MMC is investigated in section 2.2 and section 2.5 explains about the design considerations of MMCs. Submodule capacitor size and ripple, challenge of switch count, challenge of circulating currents, DC fault and protection and sub module faults are discussed in section 2.5, 2.7, 2.8, 2.9 and 2.10.

## 2.1 Basic Operation Principles of MMC

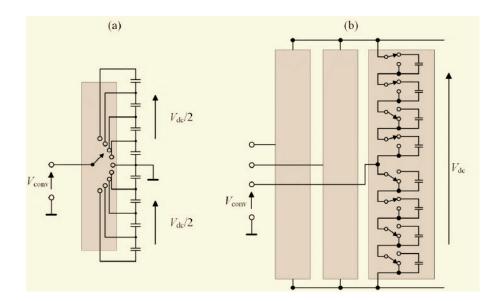

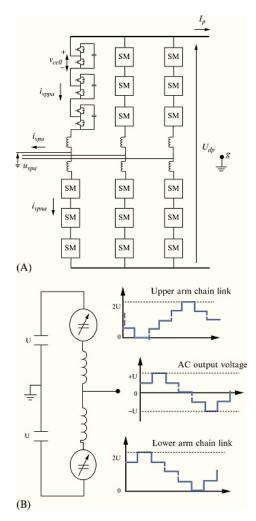

Fig. 2.1 shows the basic idea of a multilevel converter [22]. The AC output voltage  $V_{dc}$  is achieved by an appropriate number of series-connected pre-charged capacitors. The higher number of capacitors (sub modules) leads to smaller size of voltage steps and lower proportion of harmonics and high frequency noises.

Fig. 2.1 (a) Basic representation of a multilevel converter; (b) the MMC's approach [22]

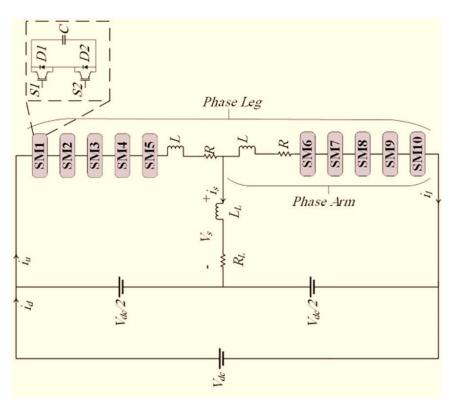

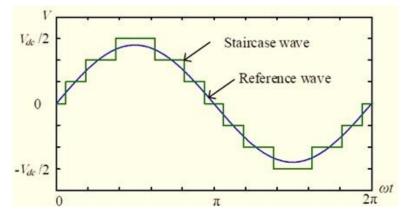

Fig. 2.1 (b) shows the MMC's approach to multilevel operation. There are three phase units corresponding to the three phases in the interconnected AC grid. Each phase unit has two converter arms, namely an upper arm and lower arm. Each converter arm consists of tens to a few hundred sub modules (SMs) connected in series. Each sub module itself is an independent VSC with usually a floating reservoir DC capacitor. Sub modules in each arm in total can withstand the entire converter DC bus voltage ( $V_{dc}$ ). Each sub module can output either positive or zero voltage (sometimes negative with certain sub module topologies) to the arm circuit in order to synthesize the desired arm voltage. As shown in Fig. 2.2, through appropriate sub module switching strategies, the arm voltage is usually a sinusoidal waveform with a DC offset equal to half the DC bus voltage.

Fig. 2.2 Typical output waveforms of MMC [23]

#### 2.1.1 Basic Operation Principles of Half-Bridge MMC

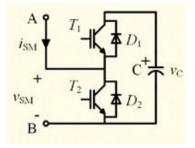

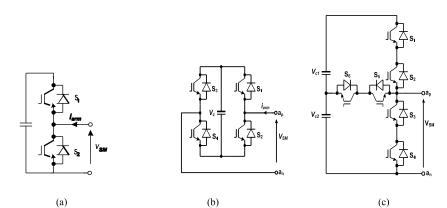

The basic operation principles of the Half-Bridge MMC are introduced in this section. The duty of each sub module is to output the desired voltage (usually positive or zero) when requested to synthesize the desired arm voltage. Among all the sub module topologies, the Half-Bridge sub module has been the most popular topology adopted for the MMC [24]. This is due to the presence of only two semiconductor switches in each sub module, leading to a lower number of devices, simpler circuit configuration, reduced control complexity, and higher system efficiency. Hereafter, the basic operation principles of the Half-Bridge sub module will be firstly introduced. Other sub module topologies will be discussed and compared at this Chapter.

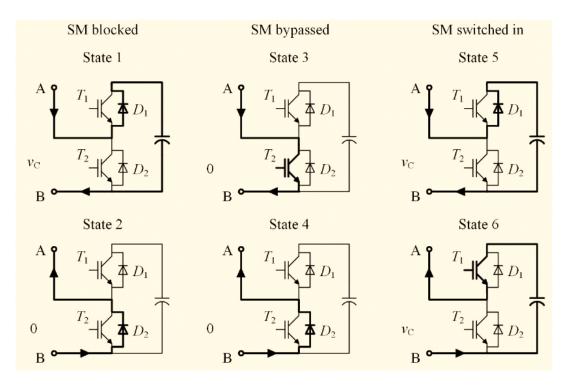

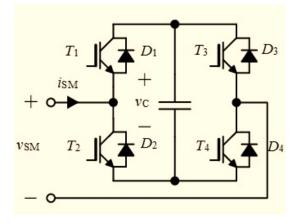

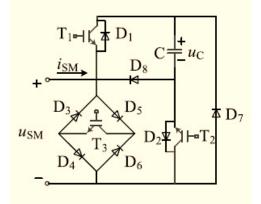

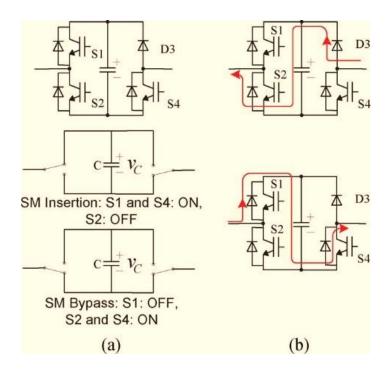

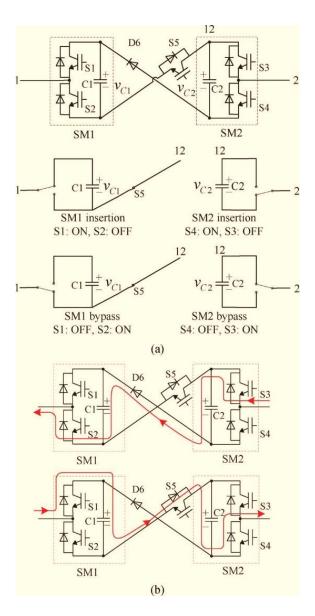

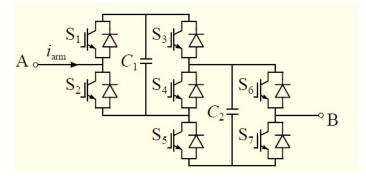

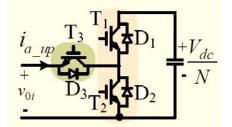

Fig. 2.3 shows the circuit diagram of a Half-Bridge sub module, where  $T_1/D_1$  represents the upper IGBT/diode module and  $T_2/D_2$  stands for the lower IGBT/diode module. In normal operations, through switching the upper and lower power switches, the sub module capacitor C is either connected to the output port AB or bypassed, and the sub module output voltage  $v_{SM}$  will be equal to either the capacitor voltage  $v_C$  or 0. There are a total of six operating states for each Half-Bridge sub module as shown in Fig. 2.4 and Table. 2.1 depending on the switching states of  $T_1/D_1$  and  $T_2/D_2$  ( '1' means ON and '0 means OFF) as well as the direction of the sub module current  $i_{SM}$ .

Fig. 2.3 Circuit diagram of a Half-Bridge sub module

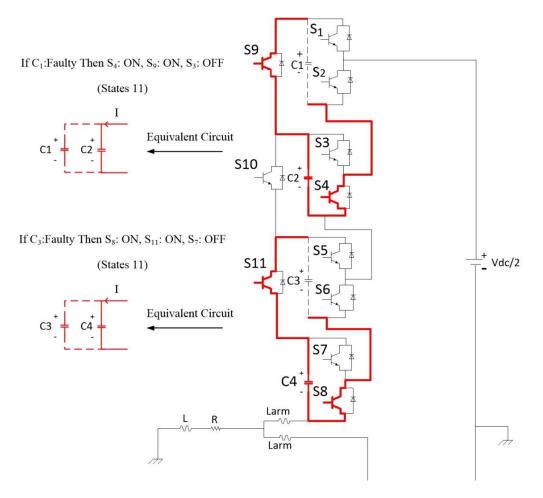

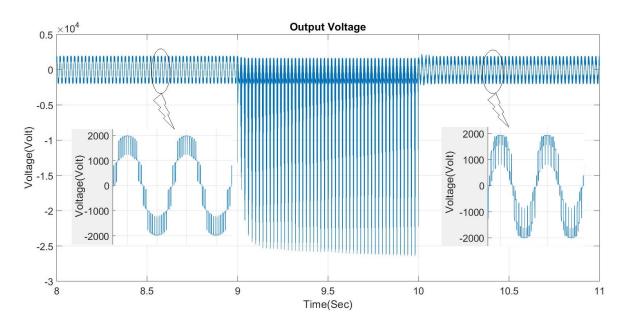

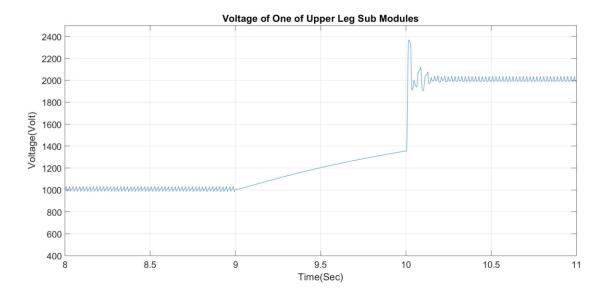

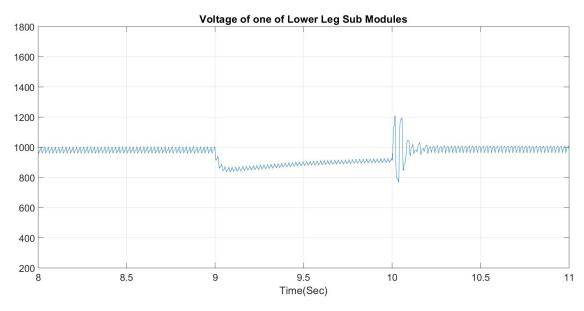

#### "Sub Module blocked" – both switches are OFF