# Design of an ATM Switch and Implementation of Output Scheduler

Jun Fang, **B.Sc.**

Thesis submitted for the degree of

Master of Engineer Science

in the department of Electrical and Electronic Engineer

The University of Adelaide

Adelaide, Australia

15 March 1999

## Contents

| Abs | stract                                                  | VII  |

|-----|---------------------------------------------------------|------|

| Dec | claration                                               | VIII |

| Acł | knowledgments                                           | IX   |

| Lis | st of Figures                                           | X    |

| Lis | st of Tables                                            | XII  |

| Cł  | hapter 1 Introduction                                   | 1    |

| 1.1 | Trends in the development of telecommunication network. |      |

| 1.2 | 2 The advantage of ATM                                  | 1    |

| 1.3 | 3 ATM switching system                                  | 2    |

|     | 1.3.1 Switch matrix                                     |      |

|     | 1.3.2 Port controller                                   |      |

|     | 1.3.3 Multi-stage switching                             | 9    |

| 1.4 | 4 A time scheduling ATM switch                          | 10   |

| 1.4.1 Structure                                  | 10 |

|--------------------------------------------------|----|

| 1.4.2 Input port controller and header processor | 12 |

| 1.4.3 Scheduler                                  | 12 |

| 1.5 Description of a Time scheduling Algorithm |

|------------------------------------------------|

| 1.5.1 Basic algorithm                          |

| 1.5.2Enhancement                               |

| 1.5.2.1 Priority                               |

| 1.5.2.2 Multicasting 19                        |

| 1.6 Summary 19                                 |

20

# Chapter 2 The Design of ATM switch

| 2.1 | Overview of the ATM switch 20                   |

|-----|-------------------------------------------------|

|     | 2.1.1 Design Objective                          |

|     | 2.1.2 Switching process                         |

|     | 2.1.3 Interface definition                      |

| 2.2 | Switch Matrix25                                 |

| 2.3 | Design of the input port controller             |

|     | 2.3.1 Overview of the input port controller. 28 |

|     | 2.3.2 The function of the header processor      |

|     | 2.3.3 The operation of the buffers              |

|     | 2.3.3.1 Temporary buffers                       |

|     | 2.3.3.2 The structure of the main buffers       |

| 2.3.3.3 Operation of the main | buffers | 33 |

|-------------------------------|---------|----|

|-------------------------------|---------|----|

| 2.4 Design of the output scheduler           |  |

|----------------------------------------------|--|

| 2.4.1 The structure of the output scheduler. |  |

| 2.4.2 Operation of the output scheduler      |  |

| 2.4.2.1 Data flow of the output scheduler.   |  |

| 2.4.2.2 Structure analysis.                  |  |

| 2.4.2.3 Defeating unfairness                 |  |

| 2.5 | Summary. |  |  |  | 8 <b>11 1</b> 3 | e. 163 |  |  |  |  |  | •• | •• |  | • • |  | • • |  |  | • • |  | •• | • | 19 |  | • • | •• | 102 | 53 | į |

|-----|----------|--|--|--|-----------------|--------|--|--|--|--|--|----|----|--|-----|--|-----|--|--|-----|--|----|---|----|--|-----|----|-----|----|---|

|-----|----------|--|--|--|-----------------|--------|--|--|--|--|--|----|----|--|-----|--|-----|--|--|-----|--|----|---|----|--|-----|----|-----|----|---|

## Chapter 3 Investigating Basic

## Functional Blocks of the Output Scheduler54

| 3.1.1 Structure                             |

|---------------------------------------------|

| 3.1.2 Operation of the comparison unit      |

| 3.1.3 Modifications for Priority            |

| 3.1.4 Operation of the schedule register    |

| 3.1.5 Input address generation              |

| 3.1.6 Circuit design of the comparison unit |

| 3.1.6.1 Generating the schedule.          | .64  |

|-------------------------------------------|------|

| 3.1.6.2 Updating the output status.       | 67   |

| 3.1.6.3 Interfacing with subsequent units | . 71 |

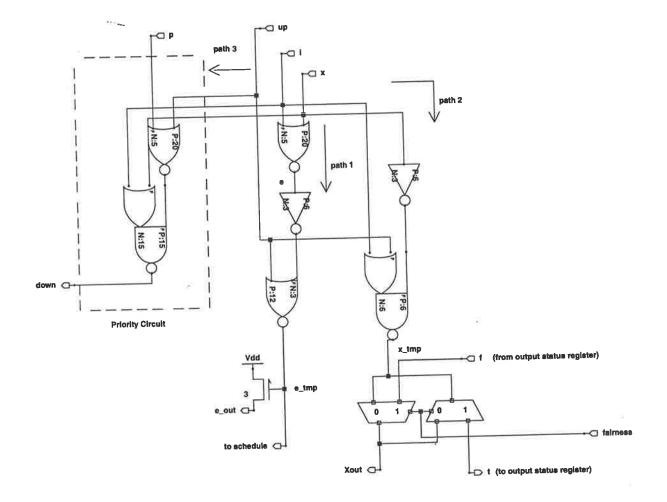

| 2 Input status register                          |

|--------------------------------------------------|

| 3.2.1 The structure of the input status register |

| 3.2.2 Operation of the input status register     |

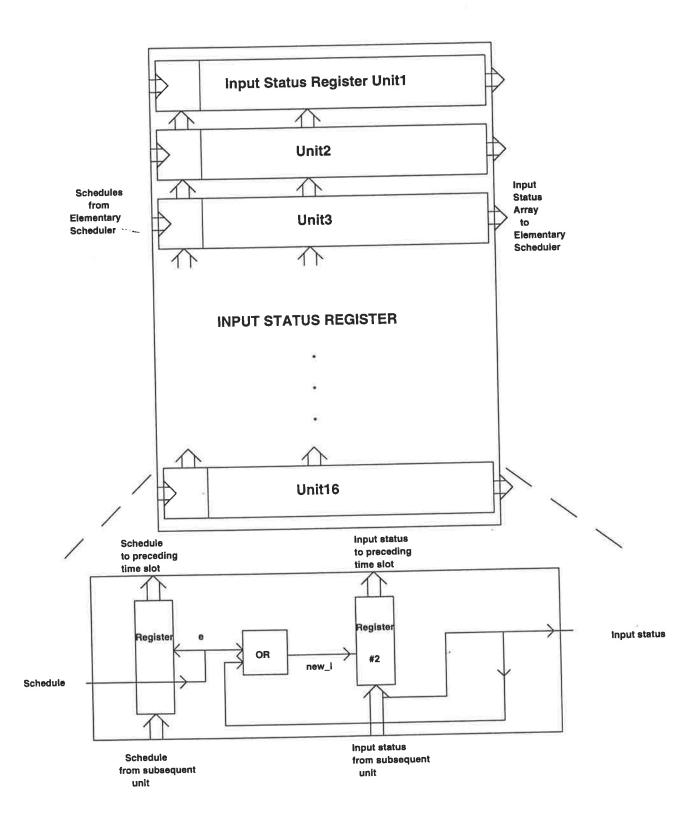

| 3.3 Output status register |  | 77 |

|----------------------------|--|----|

|----------------------------|--|----|

| 3.4 Clock generator. |    |

|----------------------|----|

| <u>e</u>             |    |

| 3.5 Summary          | 82 |

## Chapter 4

| Physical Design of the Output Scheduler            | 83   |

|----------------------------------------------------|------|

| 4.1 The design methodology                         | . 83 |

| 4.2 Techniques for high performance digital design |      |

| 4.2.1 Design specification.                        | .86  |

| 4.2.2 Design requirements                          | 87   |

| 4.2.3 Design techniques for high speed            |

|---------------------------------------------------|

| 4.2.3.1 Floorplanning                             |

| 4.2.3.2 Clock distribution and skew               |

| 4.2.3.3 Critical path analysis and optimisation   |

| 4.2.3.4General techniques to decrease delay       |

| 4.2.4 Design techniques for low power dissipation |

| 4.2.4.1 Logic family selection                    |

| 4.2.4.2 Reducing the effective capacitance        |

| 4.2.5 Techniques for reducing the area            |

| 4.2.6 I/O system Design                           |

| 4.2.7 Power distribution                          |

|                                                   |

| 4.3 The simulation result of output scheduler     |

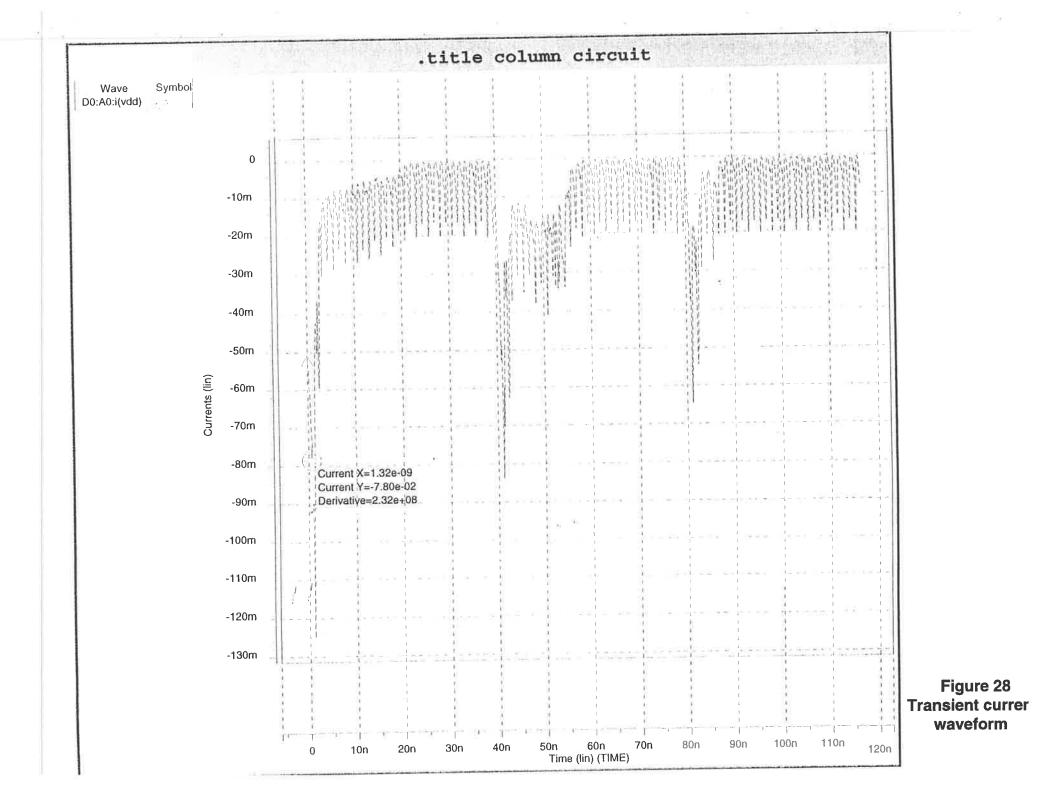

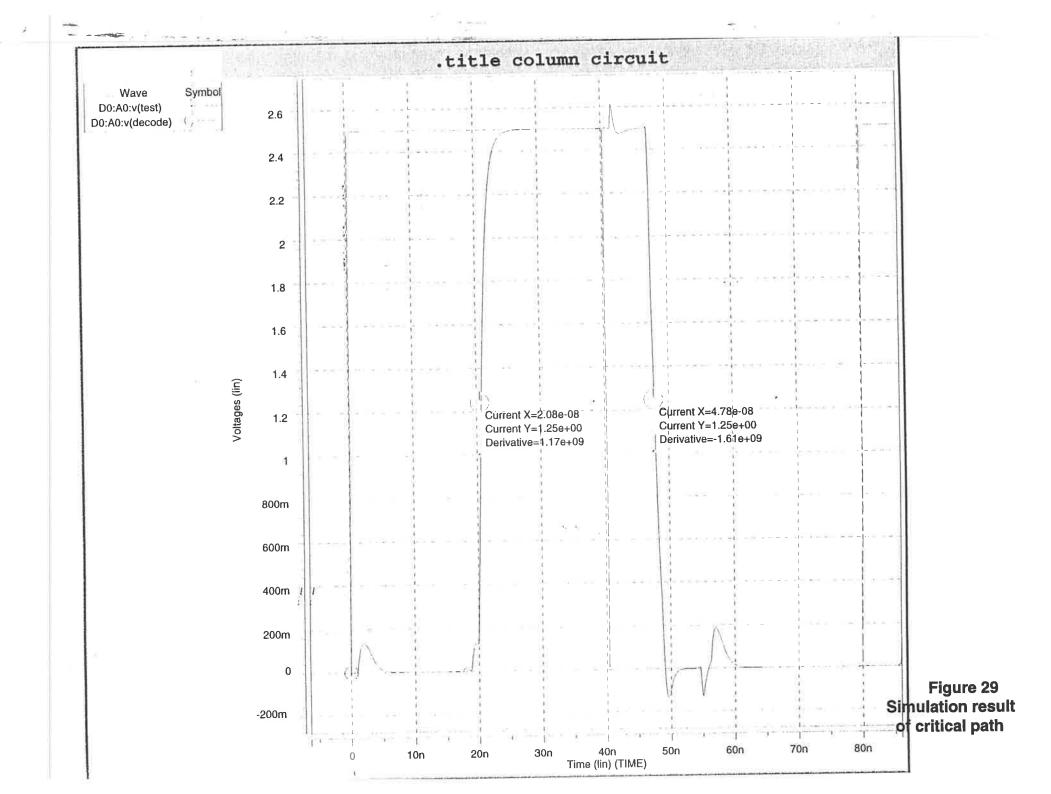

| 4.3.1 Delay and power dissipation 114             |

|                                                   |

| 4.3.1.1 Simulation environment.  | 114 |

|----------------------------------|-----|

| 4.3.1.2 Selection of the stimuli | 115 |

| 4.3.1.3 Simulation result.       |     |

| 4.3.2 Size and area              | 118 |

| 4.4 Summary |  | 118 |

|-------------|--|-----|

|-------------|--|-----|

# **Chapter 5 Discussion**

| 5.1 Speed-up two                            |

|---------------------------------------------|

| 5.2 A possible way to improve the speed 124 |

| 5.3 Challenges on packaging 127             |

| 5.4 Summary 129                             |

# Chapter 6 Conclusion 131

| Reference 13 | 33 |

|--------------|----|

|--------------|----|

#### Abstract

ATM (Asynchronous Transfer Mode) is regarded as the solution for next generation telecommunication network. ATM switches are the critical parts of an ATM network. In this project, an experimental 16 x 16 input buffered ATM switch is developed, which employs a time scheduling algorithm developed by Sarkies and Main. The ATM switch discussed in this thesis contains four basic functional blocks: switch matrix, output scheduler, input port controller and output port controller. The output scheduler is the key part of the project, which is designed to the chip-level. The other parts of the switching system that interface with the output scheduler are designed to the architecture level. The objective of this research project is not only to design a high-speed output scheduler that can support the switch matrix working at 10Gb/s/channel, but also to design the output scheduler that can provide variable priority threshold and multicast to improve the performance.

The output scheduler described in this thesis is designed with TSMC 0.25 $\mu$ m CMOS technology. The entire chip contains over 600,000 transistors. The simulation results show that delay of the critical path is 20.8ns, which is much less than the design requirements, 40ns. The estimated power dissipation of the circuits is 0.785w with a 2.5v power supply at 100°C. The circuit area is 4.9 mm<sup>2</sup> and chip area is about 12mm<sup>2</sup>.

We demonstrate the output scheduler can coordinate with the other parts in the ATM switch to provide high quality service.

## Declaration

This work contains no material which has been accepted for the award of any other degree or diploma in any university or other tertiary institution and, to the best of my knowledge and belief, contains no material previously published or written by another person, except where due reference has been made in the test.

I give consent to this copy of my thesis made, when deposited in the University Library, being available for loan and photocopying.

SIGNED: .

DATE: ... 23 30/08/99

### Acknowledgments

I would like to express my appreciation to the people who made their contributions to the completion of this research. First of all, I would like to thank my supervisor, Dr. Kenneth Sarkies. He not only gave me invaluable guidance and continued support in the course of my research, but also gave me many comments on the structure, contents and grammar of my thesis. Secondly, I also wish to extend my sincere gratitude to Mr Kiet N. To. He patiently taught me the usage of the CAD tools used in VLSI design. Last but not least my thanks go to Mr Andrew Beaumont-Smith, Mr Said Al-Sarawi, Dr. Alireza Moini and Mr. Michael Liebelt for many discussions in various stages of design.

# List of Figures

| 1  | A general model for ATM switch                                    |

|----|-------------------------------------------------------------------|

| 2  | Architecture of crosspoint switch developed by Lowe               |

| 3  | Architecture of crosspoint switch developed by Savara and Turudic |

| 4  | Structure of an input buffered ATM switch                         |

| 5  | Diagram to illustrate the time scheduling algorithm 15            |

| 6  | Flow chart of operation switching process                         |

| 7  | High-level architecture of an input buffered ATM switch           |

| 8  | Architecture of crosspoint switch used in this ATM switch         |

| 9  | Diagram of input port controller                                  |

| 10 | Structure of write controller                                     |

| 11 | Operation of the write controller                                 |

| 12 | Structure of output scheduler 41                                  |

| 13 | Detailed structure of output scheduler 44                         |

| 14 | Flow chart of operation of output scheduler 45                    |

| 15 | Diagram of the elementary scheduler 55                            |

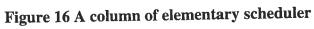

| 16 | A column of elementary scheduler                                  |

| 17 | Circuit of comparison unit                                        |

| 18 | Diagram of input status register                                  |

| 19 | Diagram of output status register                                 |

| 20 | Diagram of clock generator                                        |

| 21 | Timing diagram of signal generator                                |

| 22 | Floorplan of elementary scheduler                                 |

| 23 | Structure of buffer distribution                               |

|----|----------------------------------------------------------------|

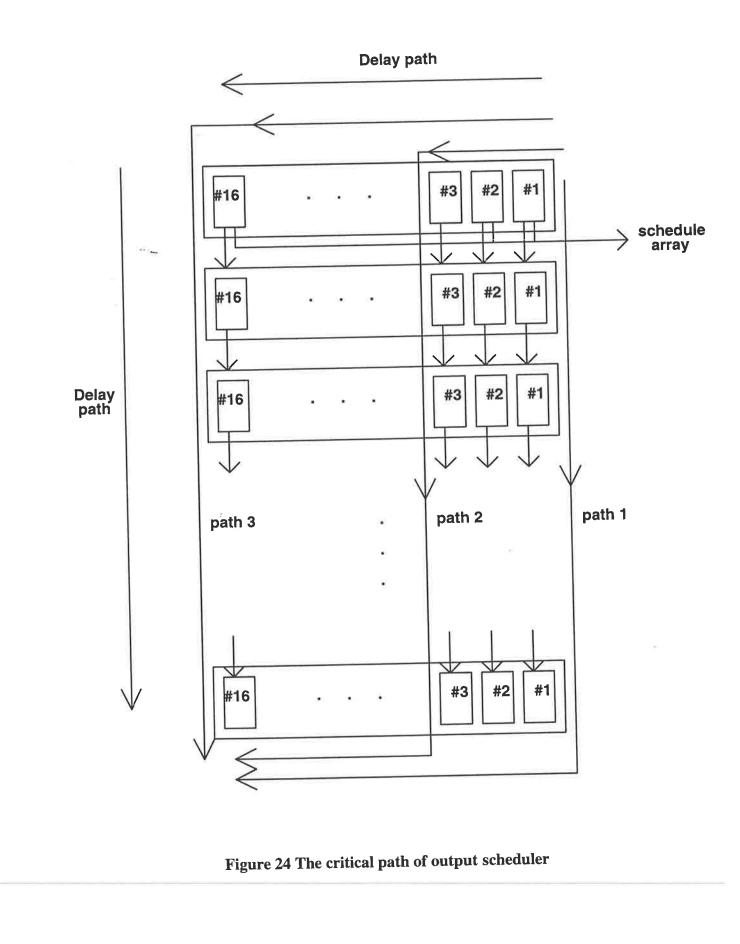

| 24 | The critical path of output scheduler                          |

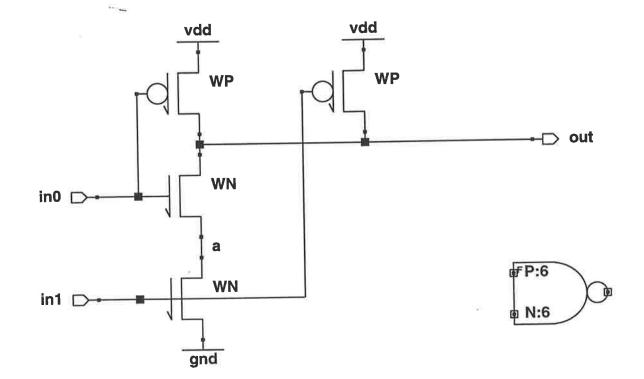

| 25 | Circuit of an NAND gate                                        |

| 26 | Avoid extensive bus sharing                                    |

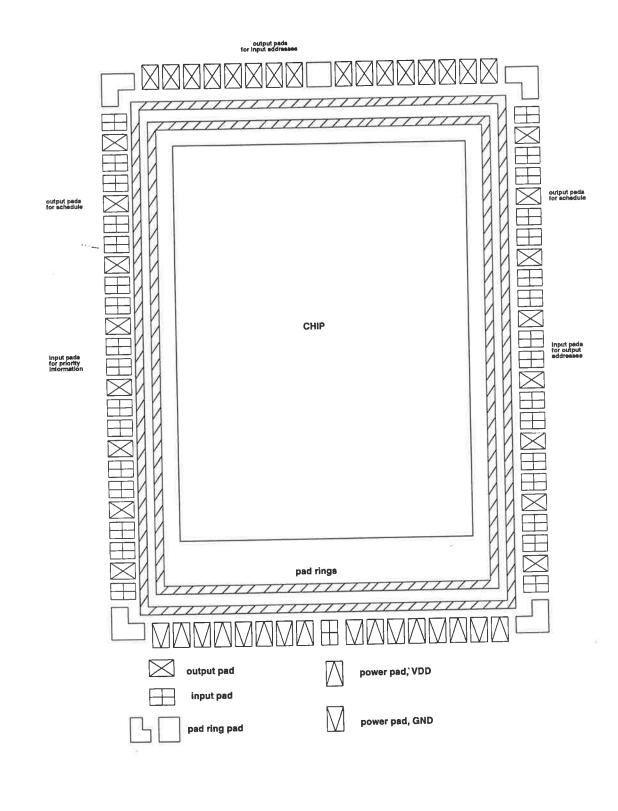

| 27 | Placement of pads                                              |

| 28 | Transient current wave form                                    |

| 29 | Simulation of critical path                                    |

| 30 | Architecture of an input buffered ATM switch with speed-up two |

| 31 | Diagram for an elementary scheduler group                      |

| 32 | Structure and circuit of elementary scheduler with lookahead   |

## List of Figure

| 1. | Truth table of schedule generation         | . 67 |

|----|--------------------------------------------|------|

| 2. | Truth table of output status updating      | 69   |

| 3. | Truth table of generating fairness signal  | 70   |

| 4. | Truth table of generating interface signal | 74   |

# LIBRARY

## **Chapter One** Introduction

## 1.1 Trends in the Development of Telecommunication Network

Nowadays, computers have infiltrated all walks of life, such as the home, banks, manufacturing industries and so on. Although stand-alone computers are still widely used, in more and more instances they are networked. As a result, both computer and telecommunication networks are developing rapidly.

Recently, the telecommunication network has acquired two new characteristics: one is the need to support services of different characteristics, for example digitised video and image; the other is the need to support all of these services on a single network [1]. Hence, a new telecommunication network standard is being established, namely B-ISDN (Broadband Integrated Services Digital Network). A great deal of research work is taking place to find a solution for the B-ISDN. Eventually, ATM (Asynchronous Transfer Mode) was agreed as the *target transfer mode* for implementing a B-ISDN [2].

#### **1.2** The Advantage of ATM

ATM is a type of packet switching system that operates at high speed. In an ATM network, the information is transferred asynchronously in the form of cells, a type of small, fixed length packet. Cells have a length of 53 octets and are comprised of two

parts: one is the header that contains the routing information, the other is the information field that is the cell payload. On the sending end the information is organised into cells, on the receiving end the information in the cells is recombined together. Such a technique provides great flexibility, so that the ATM network is very suitable for new high-bit-rate services. Real-time video is a typical example for this kind of service, which is known as variable bit-rate (VBR) service. It is intuitively obvious that the bit rate generated by a video picture of static scenery is certainly different from that of a racing fox. When the scene switches from the scenery to the fox, there is a large burst of information to be transferred. ATM can allow this variable rate of information generation to be transferred effectively across the network. Moreover, another inherent advantage of ATM network is multiplexing of cells. Cells from different services can be transferred onto one link. That means the network operator need only provide one connection to the customers and all services can be provided over this link. Also, as described previously, a significant characteristic of modern telecommunication networks is to support multimedia services. ATM networks use a standard size of cell for all media, which means that switching of the cell streams can be performed at very high rate and this simplifies the design of the ATM switch considerably. Clearly, ATM offers great ease of integration of sources. It was for this reason that ATM was selected as the transfer mode for the new generation of high-speed telecommunication network.

#### 1.3 ATM Switching system

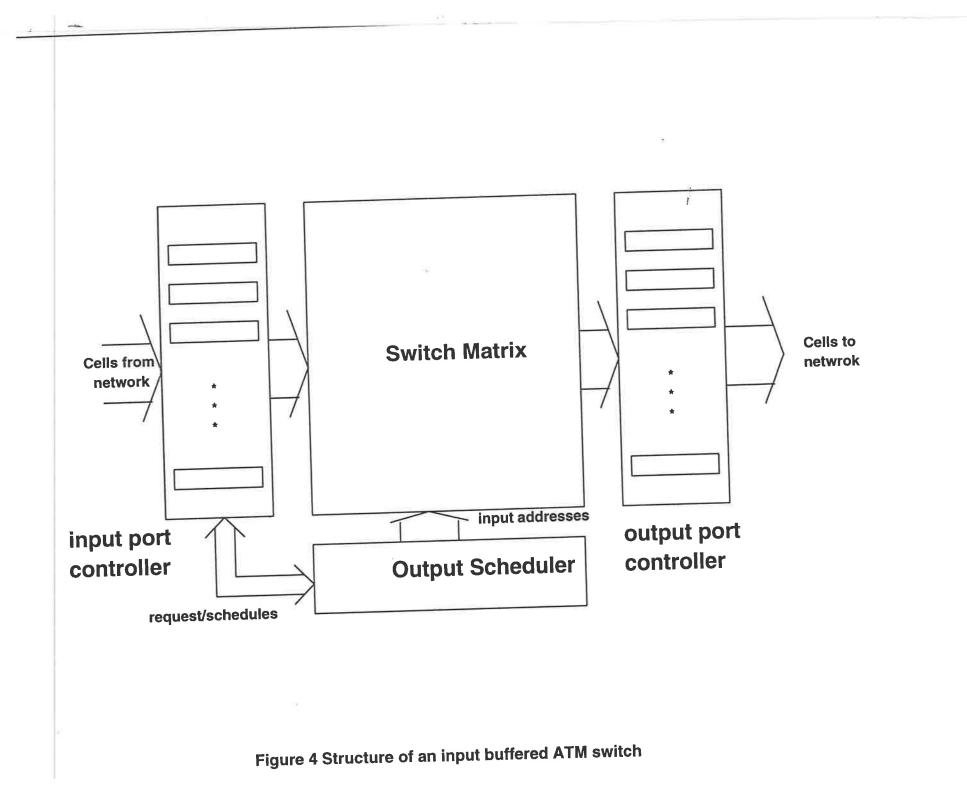

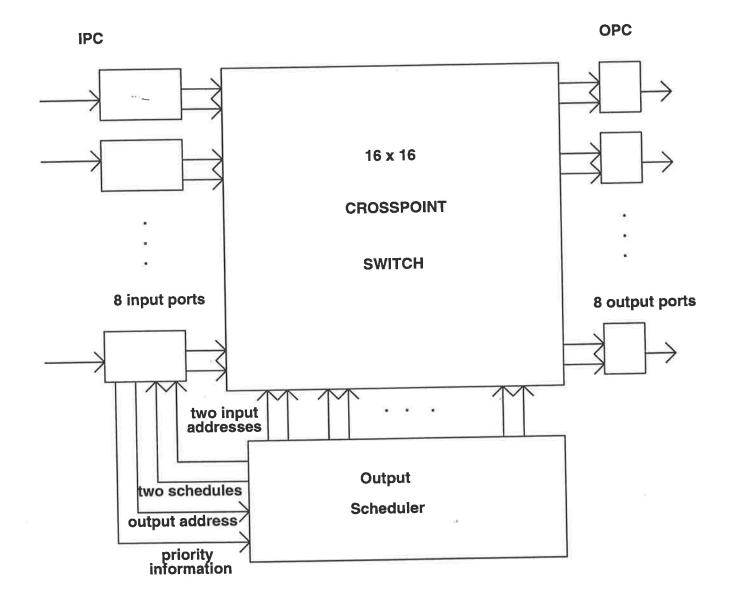

Generally, an ATM switching system is comprised of three elements: switch matrix, an input port controller (IPC) for each input port and an output port controller (OPC)

for each output port [3]. A diagram that shows these three modules is sketched in figure 1.

Figure 1: A general model for ATM switch

#### 1.3.1 Switch Matrix

Clearly, the switch matrix is the core of this switching system, in which the data path is developed between any input-output-pair. Hence, matrix will significantly affect the capability of the whole switch. The increasing traffic and multiple services in the modern telecommunication network raise the requirement for high-capability switches. High-performance switches should present such characteristics as very high speed, versatility of switching mode (selective and broadcast), ease of control, small loss, small delay, good signal integrity with little noise and so forth. Furthermore, for the ATM network the capability of handling asynchronous data is of importance. The crosspoint switch has proven to be a competent candidate to meet

these rigorous requirements.

In the past few years, much work has been done to implement the high-speed crosspoint switches that can support ATM switch. We shall describe two different architectures used in giga-bit crosspoint switches.

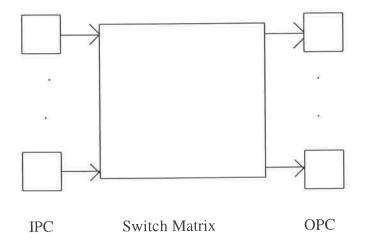

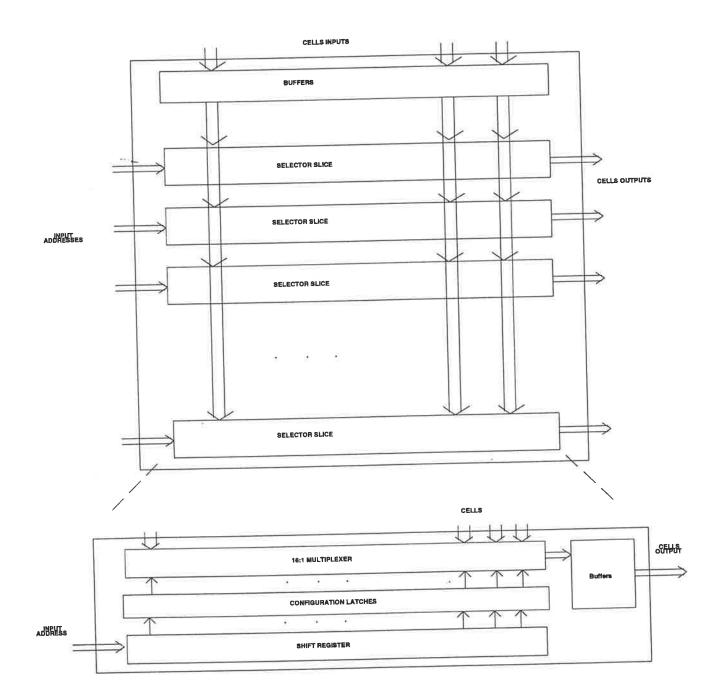

In 1997, Lowe reported a 10Gb/s/channel crosspoint switch [4], which employs a multiplexer/decoder type of architecture. The architecture of this crosspoint switch is shown in figure 2. As shown in the diagram, the switch consists of 16 selector slices. In each selector, there is a 4-bit register for the input address, a 16:1 multiplexer and an output buffer. The 4:16 decoder selects the desired output among the 16 selector slices according to the output address. In each input port there are sixteen input data buffers and input address buffers. They are used to drive the cells and addresses to all the selector slices.

When a cell arrives at the switch, its input address and output address are sent to the input address buffers and decoder respectively. According to the output address the decoder selects one of the 16 outputs, namely one of 16 selector slices. Note that the decoded output address is latched by a load pulse. That means that only when the load pulse is asserted can the output address enter the selector slice. On the other hand, the input address is buffered with low impedance amplifiers and driven to all the slices. The cell is also broadcast to all the slices. Referring to the detailed structure of each slice, we note that the input address is stored in a register and it will not be sent to the multiplexer until it receives a clock signal from the decoder. When the load pulse is asserted, the output address is loaded into each selector slice and the

Figure 2 Architecture of crosspoint switch developed by Lowe

asserted bit will activate the register to send the input address to the multiplexer. According to this address, the multiplexer connects one of the cells to the buffer. Finally, the buffers drive the cell out of the switch.

This broadcast-and-select architecture needs a relatively simple structure, so it can be implemented in one chip. This characteristic is significant as it improves the speed of the switch and decreases the cost of production. However, this architecture also has some disadvantages. This switch can set up only one data path at one time, so it needs 16 consecutive load pulse to fully reconfigure the whole switch. That means in one time slot the switch must be programmed 16 times. This increases the complexity of external control and the complexity of interactions with the data flow.

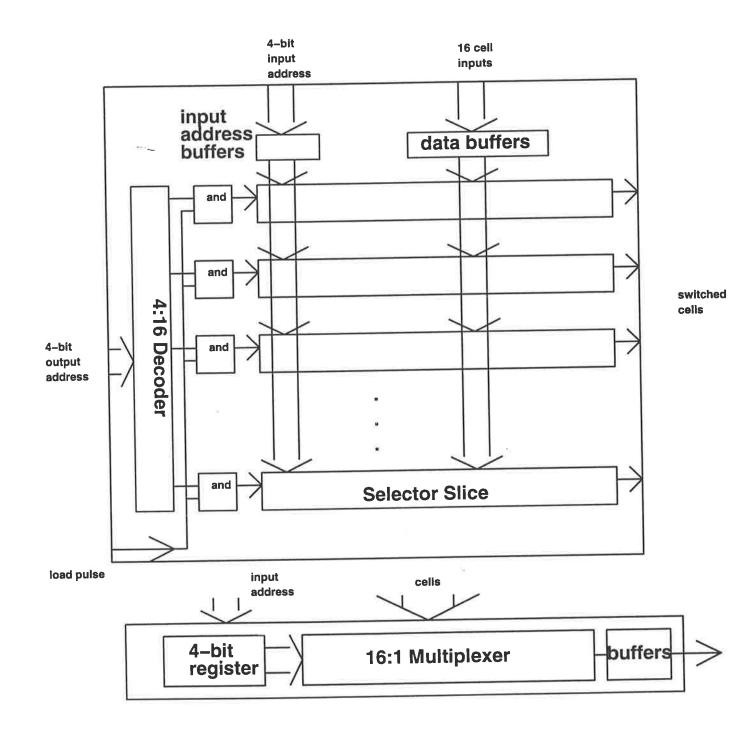

Savara and Turudic developed another architecture for a crosspoint switch in 1995[5] (see figure 3). As normal switch, it has input buffers, output buffers and a crosspoint switch matrix. There are only sixteen 16:1 multiplexers in the switch matrix and each multiplexer corresponds to one output port. A characteristic of this switch is the utilisation of configuration latches and sixteen 4-bit shift registers to deal with the input addresses.

The incoming cells are stored in the input buffers, and the 4-bit input addresses are sent to the address registers. Each address register corresponds to one multiplexer. The addresses are shifted into registers serially. When all the sixteen 4-bit binary numbers are stored into the shift registers, the switch control centre sends a signal to turn on the configuration latch. Each shift register loads the input address into the

Figure 3 Architecture of crosspoint switch developed by Savara and Turudic

multiplexer in parallel. With the input addresses, the multiplexer will select one of the 16 inputs and connect it to the output. Thus, 16 nonblocking data paths are established at the same time in the switch matrix.

Clearly this architecture is more efficient than the last one, as the cells that asynchronously arrive at the 16 input ports within one time slot are transferred through the switch simultaneously. The switch is configured only once per time slot, which makes its control easy. Hence, this architecture presents a significant advantage when used in an ATM network.

#### 1.3.2 Port Controller

San Incon

In order to avoid excessive cell loss in the case of internal collisions, buffers have to be provided in the switching system. Basically, there are two possibilities for the buffer location:

- located in the output port controllers

- located in the input port controllers.

Different buffer location of buffers results in different performance.

For the output buffered ATM switch, if the switch matrix can not work fast enough contention may occur. In this case several cells are requesting the same output port simultaneously. In order to achieve collision free switch, the speed-up factor of N must be reached for an N x N switch matrix. That is, it must be possible for each output to pass N cells simultaneously to the buffers. Thus very high speed buffers are

needed. This characteristic makes the output buffered ATM switch undesirable from a performance viewpoint.

The input buffered switch would not suffer from the speed limitations of the output buffered switch, but it has its own problems as well. When first-in-first-out buffers are used in the input port controller, a collision occurs when two or more head-ofthe-line cells compete for the same output simultaneously. If so, one cell passes and the others are blocked. All cells in the blocked queues will be blocked, even if they are requesting other possibly unused outputs. Consequently the throughput of the input buffered switch is comparatively low. In order to overcome this disadvantage, some controller module or scheduler must be employed to manage the input queues intelligently. Thus, the input buffered switch is more practical but harder to control.

#### 1.3.3 Multi-stage Switching

For a large switching system, a single stage switch can not provide enough inputs and outputs, so a multi-stage network is used. A multi-stage network is built of several stages which are interconnected by internal links in such a way that any output can be reached from any input. According to the number of paths which are available for a cell to reach a destination output from a given input, these networks can be subdivided into two groups: single-path and multiple-path networks. For the single-path network, due to the fact that only one path exists from an input to an output, routing is very simple. The disadvantage is that when an internal link is used by two inputs simultaneously internal blocking is inevitable. For the multi-path network, due to the existence of alternative paths for reaching the destination output

from a given input, internal blocking can be reduced or avoided. However, the possibility exist for cell streams to arrive at the outputs with cells placed out of sequence.

#### **1.4** A Time Scheduling ATM Switch

In this thesis, we will discuss an input buffered ATM switch using a time scheduling algorithm.

#### 1.4.1 Structure

As stated above, for a high-performance input buffered ATM switch, a controller or scheduler should be employed to manage the queuing. As shown in the figure 4, such an ATM switch consists of these four parts:

- **1** The switch matrix is the core of a switch. The data path between the input and output is set up in it;

- 2 The scheduler selects a suitable time slot in which both the input and output are available to send the cells so that no conflict could occur within the switch matrix;

- **3** The input port controller is the interface between the switch matrix and the scheduler. The controller should coordinate with the scheduler to manage the cell flow. For an input buffered switch, the data buffers are used here to store the incoming cell temporarily;

#### 1.5.1 Basic Algorithm

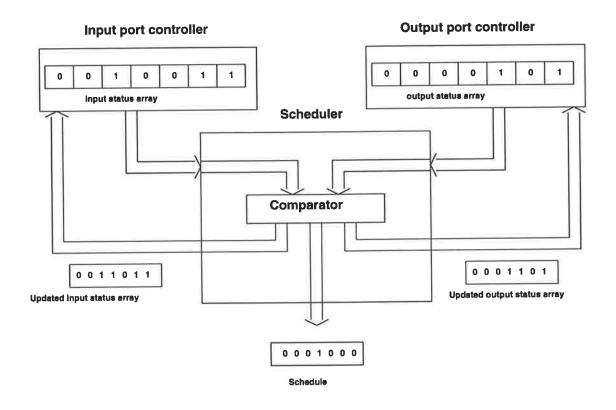

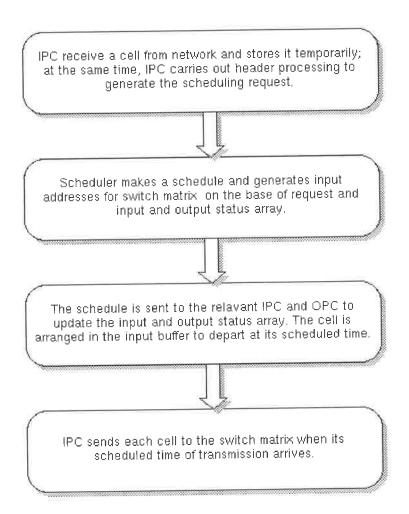

A block diagram is shown in figure 5 to illustrate this algorithm. The basic idea of this algorithm is that in the input port controller and output port controller an input status array and an output status array are maintained and updated respectively. These indicate the usage of the input ports and output ports in successive time slots. Specifically, a status array records which time slots have been scheduled to send a cell for this port and which slots are available for new cell. Referring to figure 5, here we take 7 time slots as an example. Both the input status array and the output status array are maintained in the form of binary number array. In these arrays, *I* represents a time slot that has been scheduled out, while *O* represents a time slot that is available for scheduling. When a cell is to be switched from an input to an output, the corresponding input and output port controller will send the status arrays to the scheduler. The scheduler compares these two status arrays so as to find the first time slot that both input port and output port are available. Finally, the scheduler sends the scheduling results to the input port controller and output port controller, respectively.

## Figure 5 Diagram to illustrate the time scheduling algorithm

We can use a flow chart (Figure ) to describe this algorithm.

Figure 6 Flow chart of operation of switching process.

To make this a bit clearer, let us study such two arrays shown in the diagram. The input status array is "0010011" and the output status array is "0000101". We assume that the least-significant bits of these arrays represent the first time slot. When this input-output pair is requested by a cell, these two arrays are sent to the comparator in the scheduler. The comparator compares the two arrays starting from the first time

slot until a schedule is found. For the first bit, both of the arrays are I which means neither of them is available for a schedule. Then the scheduler compares the second bit, for this bit the input port has been allocated, so no schedule can be made. For the  $3^{rd}$  time slot, although the input port is available the output will be busy, so there is still no schedule. For the  $4^{th}$  one, both ports are available, so a schedule is made. Since the purpose of the comparator is to find the first time slot available for switching, the comparator stops as soon as a schedule is found.

The comparator generates a schedule result and sends the updated input status array to the input port controller. As show in the diagram, the schedule result is an array of binary numbers, in which the binary *I* represents the schedule. Also, the 4<sup>th</sup> bit of the input status array is updated to *I*. In addition, the comparator sends an updated output status array to the output port controller. In a similar way to the input status array, the 4<sup>th</sup> bit of the output status array is changed to *I* which means that this time slot has been scheduled out. This new output status array will be stored in the output port controller. After this time slot, both the input and output status arrays are shifted by one bit so that the second time slot becomes the first and so on. The bit corresponding to the 1<sup>st</sup> time slot is used to guide the input port controller to send the cell to the switch matrix. The bit corresponding to the 16<sup>th</sup> time slot is fed a *0* that means a new time slot is available.

This scheduling algorithm can effectively avoid conflict among cells that may otherwise use the same output port at the same time slot. This can decrease the loss rate and improve the delay performance significantly. Sarkies and Main [6] showed that this algorithm makes a throughput of greater than 90% achievable, when the status length is sufficiently large. Therefore, this time scheduling algorithm can ensure high performance of the switch.

#### 1.5.2 Enhancement

The algorithm can be enhanced by adding priority and multicasting.

#### 1.5.2.1 Priority

Basically, there are two types of priority algorithm, namely delay priority and discard priority. For the first case, the cell with a low priority may suffer more delay, because the network always serves the high-priority cell first. Discard priority means that a cell with lower priority will be more likely to be discarded when compared with a high-priority cell. Usually, the discard priority is very simple and is easily implemented. The priority used by this algorithm is discard priority.

Specifically, for this algorithm a priority threshold is associated with each time slot. The high priority cell can use any time slot for scheduling, while the low priority cell can only be scheduled within the time slots that occur before the threshold. If a cell with a low priority can not make a schedule within the time slots permitted for it, the cell will be discarded.

Clearly, this approach is very simple to implement, but the penalty for it is less flexibility. In different ATM networks the threshold for the priority may need to be set to a different value. Therefore, to achieve the best flexibility and simplicity, the scheduler should be designed to be able to support a variable threshold. In other words, the threshold value can be set to any point and this value is decided by the priority level.

#### 1.5.2.2 Multicasting

The algorithm also supports multicasting. Multicasting means a cell from one input can be switched through a number of outputs simultaneous. In order to support multicast, the switch matrix should broadcast a cell to all the 16 outputs. Then input addresses are sent to their corresponding output ports, which select and connect one of the inputs to the output. Clearly, if a number of selector slices select the same input, the cell from this input will be multicast. We will discuss the crosspoint switch architecture that supports multicast in a later section.

#### 1.6 Summary

In this chapter, we introduced the basic structure of an ATM switch. The switch matrix is the core of the ATM switching system. Therefore, we reviewed the crosspoint switch architecture. Then, we discussed particularly the structure of an input buffered ATM switch with a time scheduling algorithm. Finally, the time scheduling algorithm employed by this ATM switch is discussed.

In the next chapter, we take up these basic concepts and carry out the design of an ATM switch scheduler and its interfaces to the rest of the switch.

Eigure 7 High-level architecture of an input buffered ATM switch

#### 2.1.3 Interface Definition

The simulation results [6] of the time scheduling algorithm used in this switch show that the switch can achieve adequate throughput when 16 time slots are used for scheduling. Therefore, the scheduler discussed in this thesis is designed for scheduling within the 16 subsequent time slots.

Before we can discuss the detailed design of each functional block, we should be clear in what format each functional block interfaces with the others, because it will affect the structure of the basic functional blocks.

#### • The Format of the Output Address

As stated above, to make a schedule for a cell, the schedule needs a copy of the output address of this cell. In what form should we use to describe this output address? Recall that one of the design objectives of this ATM switch is to support multicast. Multicast means a cell from an input may be switched to a number of outputs simultaneously. Therefore, we need an array of binary number that can select any number of outputs. Towards that end, for an ATM switch with 16 output ports, we need a 16-bit binary number to describe the output address. In this binary array, we use I to represent a selected output port and O to represent a port not selected. In order to minimise the pin count for the scheduler, this 16-bit array is shifted into the scheduler in series. Therefore, the scheduler should have 16 inputs for the output

addresses, each of the addresses coming from a different input port controller.

#### • The Format of the Priority Information

As we have discussed in the first chapter, for such a scheduler with 16 time slots for scheduling, we need a 16-bit array to describe the threshold value for priority. Note that we can also use a four-bit binary number to describe such a 16-bit array, and then the 4-bit binary number can be decoded into the 16-bit array. As will be shown in the later chapter, the scheduler should shift in and out the information at a very high speed, from a point of view of power saving it is advantageous to use the 4-bit addresses instead of 16-bit. Also, for this scheduler we assume that a cell to be multicast to the different outputs would have identical priority for all the outputs, because it would be very difficult to distinguish different priorities for different outputs of a multicast cell. Therefore, only one bit of priority information is required for any cell. Therefore, the scheduler has 16 inputs for priority information, and each one is connected to one input port controller.

#### The Format of the Input Address

We have mentioned that the scheduler should generate the input addresses for each selector slice in the switch matrix to set up the data path. As with the output address, a question may be raised regarding the format of this input address. Since in one time slot one output port can only handle one cell, we should use such an array that can select one input from sixteen inputs. In order to minimise the hardware of the scheduler, we use a 16-bit array with one asserted bit to select an input. The input

address is shifted out of the scheduler to the switch matrix in series.

#### • The Format of the Schedule

As we know, the scheduler should return a schedule for each input port controller as the result of request processing. This array of schedules informs the input port controller in which time slot the cell is to be scheduled. For the multicast case, a cell may be scheduled into a number of time slots to be switched out through different outputs. If this is the case, we have to use a 16-bit array to describe which time slots the cell is scheduled to. Therefore, the scheduler has 16 outputs for shifting the 16bit schedule array back to the input port controllers.

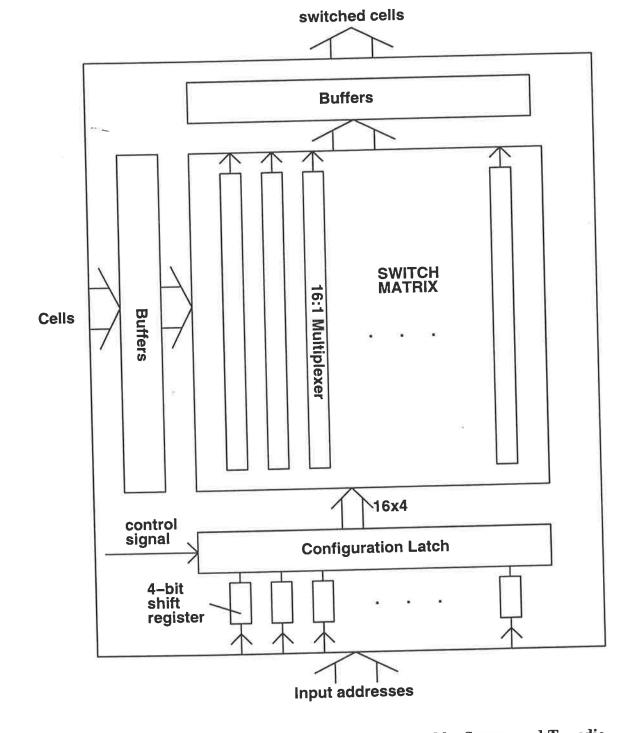

#### 2.2 Switch Matrix

As described above, the core of the ATM switch is a switch matrix, in which the data paths are developed between the input and output ports at the request of the cell. In the first chapter, we have reviewed some possible architectures. In this section, we will discuss the crosspoint switch architecture that meets the requirement of the particular scheduler discussed in this thesis. According to the above discussion, we note that the crosspoint switch suitable for this ATM switch should have the following characteristics:

- high speed;

- supporting multicast;

- interfaces perfectly with the other parts of the ATM switch.

Figure 8 Architecture of crosspoint switch used in this ATM switch

Figure 8 shows a crosspoint switch architecture, which employs a broadcast and select architecture. This crosspoint switch consists of 16 cell inputs, 16 cell outputs and 16 address inputs. The switch is comprised of 16 selector slices, each of which corresponds to an output. The incoming cells are driven by the buffers and broadcasted to all the selector slices. Each selector slice receives an input address that informs the selector to select one of the cell inputs and connect it to the output.

The structure of the selector slice is shown at the bottom of the figure 5. The selector includes four parts: a 16-bit shift register, a configuration latch, a 16:1 multiplexer and a buffer. The input address is shifted into the shift register in series. When all the addresses are ready, the configuration latch is turned on, and the input address is loaded into the multiplexer in parallel. The asserted bit in the address will select one of the cell inputs and send it to the buffers. The buffers drive cells to the output port controller.

On the one hand, the broadcast and select architecture ensures that the switch can support multicasting and the simple structure makes very-high-speed switching possible. On the other hand, each selector slice receives a particular input address for its corresponding output port simultaneously, which means that the switch need only set up once per time slot. It simplifies the external control significantly. Moreover, we employ a 16-bit shift register to receive the 16-bit input address generated from the output scheduler, to ensure that the switch matrix can interface with output scheduler perfectly. Currently, the GaAs crosspoint switch as described in the literature can offer the capability of up to 16 input and output ports at 10Gb/s for each [4], so the design of the scheduler and input port controller should be able to support such very-high-speed switch matrix.

#### 2.3 Design of the Input Port Controller

In the ATM switching system, the input port controllers which act as the interface between the switch matrix and the output scheduler play a significant role in the data flow control. Now let us look at how an input port controller works. The input port controllers should coordinate with the output scheduler and switching fabrics to provide not only the basic cell control capability but also the advanced functions such as multicast and variable threshold for priorities.

#### 2.3.1 Overview of the Input Port Controller

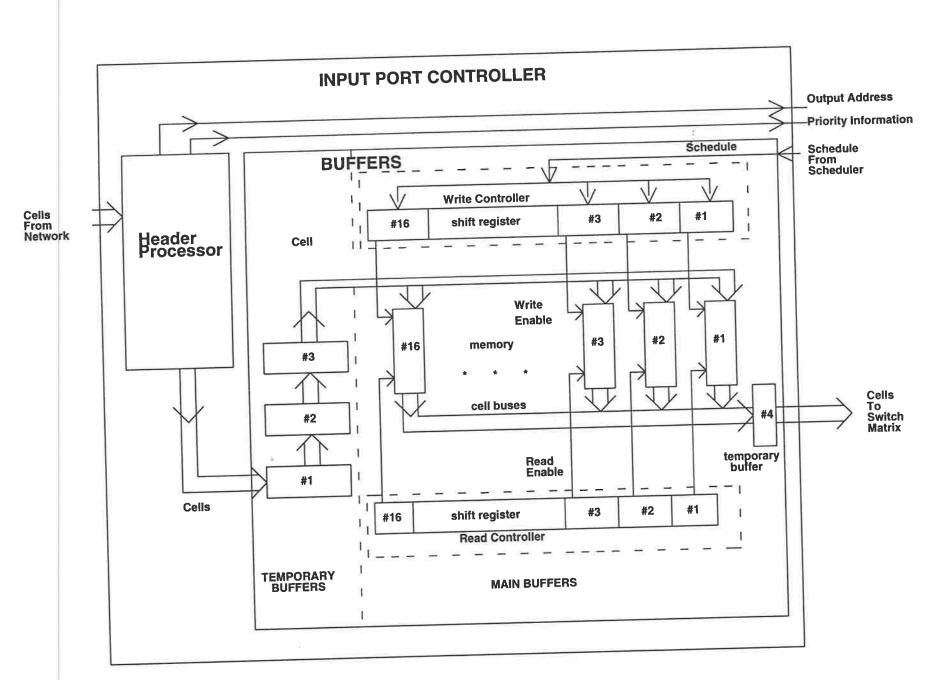

As we have discussed, the input port controller is the interface between the network and switch. On the one hand, the controller processes the cell header and deduces the necessary routing information for switching. On the other hand, the input port controller coordinates with the scheduler to manage the cell flow. To realise these two functions, the input port controller consists of two basic functional blocks: the header processor and the buffers. A diagram of the input port controller is shown in figure 9.

Figure 9 Diagram of input port controller

29

20 - 12 a -

#### 2.3.2 The Function of Header Processor

When a cell arrives at an input port controller, first of all, it goes through a header processor. Recall that in each ATM cell there is a header that consists of the properties and the routing information of the cell. The header processor analyses the header of the cell so as to determine the type of the cell. If the idle cell that is inserted by the physical layer and contains no user information is detected, this cell is discarded immediately. However, for the user cell the header processor generates the necessary information for switching the cell. The routing information is updated and the cell is passed to the buffers.

As we have discussed in the previous section, for this ATM switch the information required to switch a cell is the output address that indicates to which outputs the cell is to be switched, and the priority information that describes how many scheduling resources can be used by the cell. Recall that because of the need of multicast, the output address should be in the form of an array of 16-bit binary numbers. Each bit of this array corresponds to an output and an asserted bit represents an output for the cell to be switched out. The priority information should be a 4-bit binary number, which will be decoded to a 16-bit array in the scheduler. The header processor sends them to the output scheduler respectively.

#### 2.3.3 The Operation of the Buffers

The buffers in the input port controller not only store the cells but also control the cell flow. The diagram of the buffers is also shown in figure 9. From the diagram we

stored in the #1 buffer, the cell stored in the #1 buffer is forwarded into the #2 buffer. Similarly, at the beginning of the 3<sup>rd</sup> time slot, the cells in the #1 and #2 buffers are forwarded into the #2 and #3 buffers respectively and a new incoming cell is stored in the #1 buffer. At the end of the 3rd time slot, the schedule is received, and the cell in the #3 buffer is written into the main buffer under the guidance of the schedule result.

#### 2.3.3.2 The Structure of the Main Buffers

The block diagram of the main buffers is shown in figure 9. The main buffer consists of two basic blocks: one is the memory, the other is the read-write controller.

The memory is comprised of 16 memory units. Each unit can store a cell. The capability of the main buffer is determined by the scheduling capability of the output scheduler. Recall that this output scheduler is designed to be able to make a schedule within the subsequent 16 time slots. As we will see later, storing a cell into the main buffer is dependent on the schedule for it. If no schedule is made for a cell, this cell will not be written into the main buffer at all. The cell that fails to enter the main buffer will be discarded. Therefore, the number of the memory units in the main buffer is identical to the maximum number of the cells that can be scheduled. In addition to 16 memory units, there is a temporary buffer in the main buffers, which receives the cell from the cell buses and sends it to the switch matrix after one time slot. The necessity of this temporary buffer will become evident shortly.

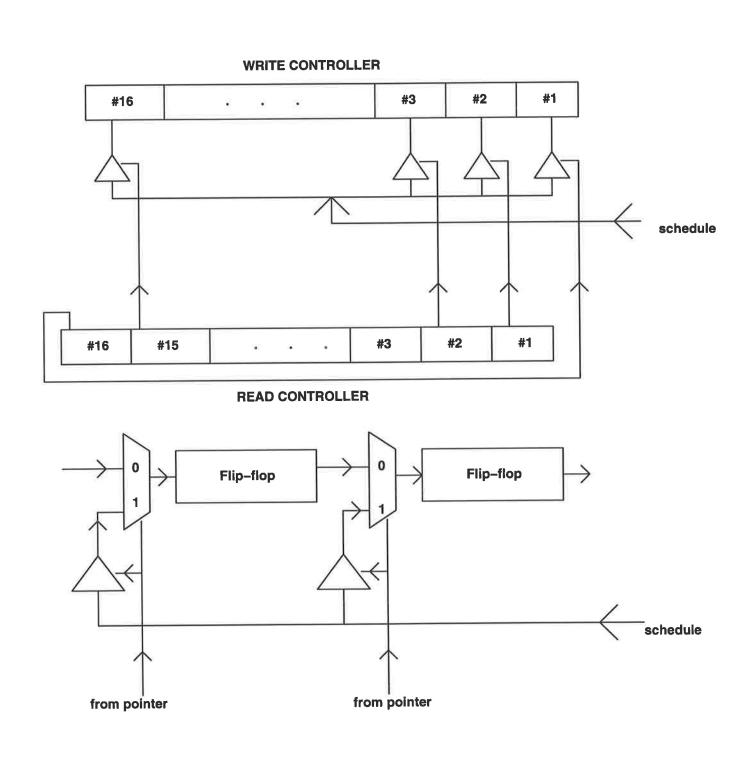

Associated with the memory, there are two shift registers, which are the write controller and read controller respectively (see figure 9). Each bit of the shift register is connected to a memory unit so as to control the write and read process.

#### 2.3.3.3 Operation of the Main buffer

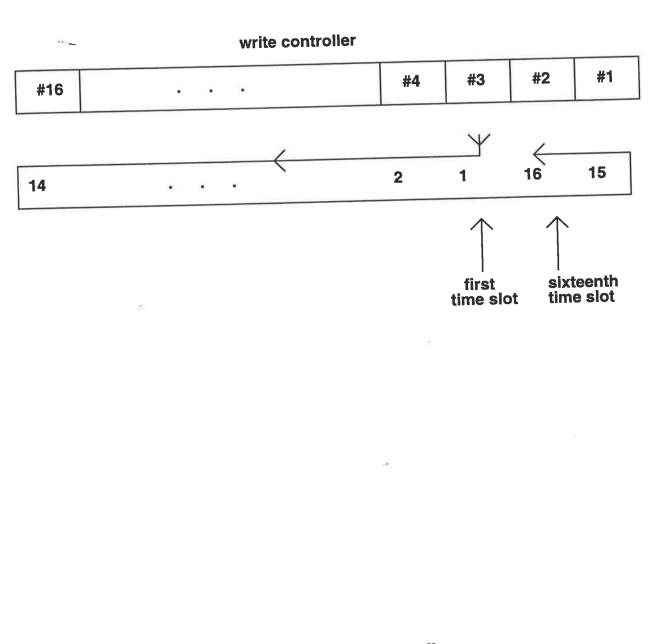

In the last subsection, we mentioned that the operation of the main buffer relies on the schedule results. Therefore, we can associate the position of the memory unit with the time slot. Specifically, each memory unit corresponds to a time slot. Thus, we can identify the memory address with the time slot.

We shall now discuss the operation of the main buffer. Similar to other memory devices, it includes two processes: read and write.

#### Reading Process

As we know, the cells are scheduled into the subsequent 16 time slots. When a cell is sent out, the subsequent cell becomes the leading cell in the new time slot. Therefore, when a cell is saved in a memory unit, the time slot to which this memory unit corresponds will change with the time. For example, at one moment, the #1 memory corresponds to the first time slot. The #2 memory corresponds to the second time slot (refer to figure 9). In the next time slot, the time slot that the #1 memory corresponds to becomes the current time slot and the cells in #1 memory is sent out. At the same time, the #2 memory corresponds to the 1<sup>st</sup> time slot and all the other groups now correspond to its subsequent time slot. After this time slot, the cell in the

#2 memory will be sent out and #3 memory will correspond to the 1<sup>st</sup> time slot. Therefore, we need a pointer that can indicate which memory corresponds to the current time slot and activates it to send the cell out.

In order to select the cell to be sent out, we need a read controller. Indeed, this controller is a circular 16-bit shift register with the input of the first bit connected to output of the last bit (see figure 9). Thus, the state of this shift register can be rotated around the register. Each bit of this 16-bit shift register is connected to the "read enable" input of a memory.

When the controller is initialised with an array of states such as "0000\_0000\_0000\_0001". The shift register is designed to shift the state in it in a counterclockwise direction, namely, the state in each bit is moved to the bit on its left and the left-most bit is shifted into the right-most bit. The shift register is driven by a signal that is asserted at the beginning of each time slot. Clearly, the state I will be moved around one bit per time slot. We can regard the state I in the shift register as a pointer.

As stated above, each memory unit corresponds to one of 16 subsequent time slots, so the memory unit that has just sent the cells out should correspond to the  $16^{th}$  time slot, a new time slot for scheduling. Therefore, we conclude that the pointer is always pointing to the memory unit that corresponds to the  $16^{th}$  time slot.

Since the pointer is always moved counterclockwise, the memory unit on the left of the pointed one should correspond to the 1<sup>st</sup> time slot. These properties are very important for the operation of write controller. We will come back to this point later.

If we have been clear about the properties of this pointer, it is very easy to understand the operation of the reading process. The pointer is moved around the register one bit per time slot. The memory pointed by a pointer will send the cell to temporary buffer #4 the cell buses (refer to figure 9). After one time slot, the cell in buffer #4 is forwarded into the switch matrix. Then a read process is finished. We will explain the reason of using this buffer #4 in a later section.

#### • Writing process

The write process is to save the cell held in the #3 temporary buffer into the main buffers. The memory in which the cell is written is controlled by the write controller. As shown in figure 9, the write controller is also a 16-bit shift register with the input of the first bit connected to the output of the last bit. The shift register receives the schedule in series and sends them out in parallel. Each bit of this shift register is connected to the "write enable" input of a memory unit. This shift register is somewhat different from a common series-in-parallel-out register. We note that the schedule input is directed to all the 16 bits of the register. That means any bit of the register can be selected as the entry-point for shifting in the schedule array, but only one is selected at any one moment. The entry-point of the register is decided by the pointer.

Contraction of the second

111

ŝ.

Figure 10 Structure of write controller

Part of this shift register is shown at the bottom of figure 10. Note that there is a 2:1 multiplexer between each flip-flop. The control signal of this multiplexer comes from the pointer. When the pointer is *1*, the input of the flip-flop is connected to the schedule, so the flip-flop pointed by the pointer becomes the entry-bit and the schedule shifts into the shift register. At the same time, the multiplexer blocks the signal from the preceding flip-flop. On the other hand, those flip-flops that are not pointed to by the pointer will receive the signal from its preceding stage, whose operation is identical to an ordinary shift register. The reason for using such a structure will become evident shortly.

Note that the output of the #3 temporary buffer is connected to the input of all the 16 memory units in the main buffer. That means the cell can be sent into any number of enabled memory units simultaneously. This is due to the need for multicast, in which the cell from one input may be scheduled to a number of different time slots. Since we associate the memory place with the time slot, it makes a good sense to save the cell into the memory unit that corresponds to the time slots scheduled by the cell. For example, if a multicast cell is scheduled into both the 1<sup>st</sup> and 2<sup>nd</sup> time slots, we should save the cell into the group that currently corresponds to the 1<sup>st</sup> and 2<sup>nd</sup> time slot. Clearly, due to this association relationship, we can use the schedule array to select the memory units and write the cell into them. Specifically, the asserted bits in the schedule array represent schedules. The asserted bits will turn on the "write enable" of certain memory units and the cell is written in.

If we use the schedule array as the write address of the main buffers, we have to make sure that each memory unit and its received schedule correspond to the same

a service and a service of the

ķ

time slot. The time slot to which each memory unit corresponds is always changing, which is under control of the pointer. Therefore, a write controller is necessary to select the entry-point of the schedule.

The write controller is a shift register with variable shift-in bit. Here we assume that the schedule array is always shifted into the register counterclockwise. For example, the schedule result in #2 bit register is shifted to #3 bit; the schedule result in #3 bit is shifted to #4 bit; the schedule result in #16 bit is shifted to the #1 bit. In addition, we assume that the most-significant bit of the schedule array is shifted into the register first, and the least-significant bit is shifted in last.

On the basis of the above assumption, we note that no matter from which bit the schedule array is shifted in, the final result will follow such regularity: the schedule result that corresponds to the first time slot (least-significant bit) is always stored in the entry-bit register; the schedule result that corresponds to the  $2^{nd}$  time slot is stored in the register to the left of the entry-bit; the schedule result corresponding to the  $16^{th}$  time slot (most-significant bit) is stored in the register to the left of the entry-bit; the schedule result corresponding to the  $16^{th}$  time slot (most-significant bit) is stored in the register to the right of the entry-bit. An example is shown in figure 10. The diagram shows the entry-point, shifting direction and the final result. For this example the entry-point is the #3 register. When all the bits are shifted in, the bit corresponding to the first time slot is in the left of the entry-point, #4 register, and the bit corresponding to the  $16^{th}$  time slot is in the right of the entry bit, #2 register.

ł

## Figure 11 Operation of the write controller

ł

We have concluded that the time slot to which a memory unit corresponds is decided by the pointer in the read controller. The memory unit referenced by the pointer always corresponds to the  $16^{th}$  time slot and its left one corresponds to the first time slot. Therefore, we can simply use the read controller to select the entry-point of the schedule in the write controller. A diagram is shown on the top of figure 10. We note that each output of the read control is connected to a tristate buffer. The tristate buffer that is turned on will develop a path for the schedule to the write controller and the register connected to this buffer will become an entry-point. We note that the #N bit of the read controller is connected to the #(N+1) bit of the write controller. In other words, when the pointer of the read controller is pointing to the #N bit, the #(N+1) bit in the write controller will be selected as the entry-point for the schedule.

The writing operation is very straightforward. The pointer in the read controller turns on a tristate buffer. The schedule is shifted into the write controller from the selected entry-point. At the end of the time slot, all the schedules are ready in the write controller and they are loaded into the memories. The cell from the temporary #3 buffer is written into the selected memory units. The write process is accomplished.

#### 2.4 The Design of the Output Scheduler

As discussed in the first chapter, the most advantageous features of this ATM switch are due to the time scheduling algorithm, and this algorithm is realised by the output scheduler.

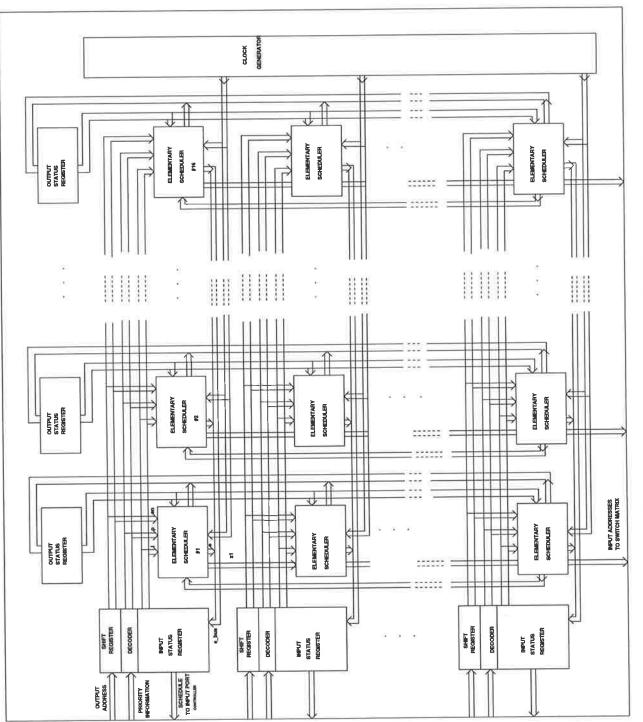

input address to switch matrix  $\uparrow$ 1 1 OUTPUT SCHEDULER Priority informatin from input port controller Ķ  $\langle =$ . 3÷. . Output address from Input port controller Schedule to input port controller  $\leftarrow$ 1-. . ٠ = 14  $\langle =$ . ٠ . 16 x 16 ELEMENTARY SCHEDULER ARRAY INPUT STATUS REGISTER . . . . elementary scheduler . 12. .  $\leftarrow$  $\wedge$ 介 REGISTER OUTPUT STATUS PULSE GENERATOR . .

Figure 12 Structure of output scheduler

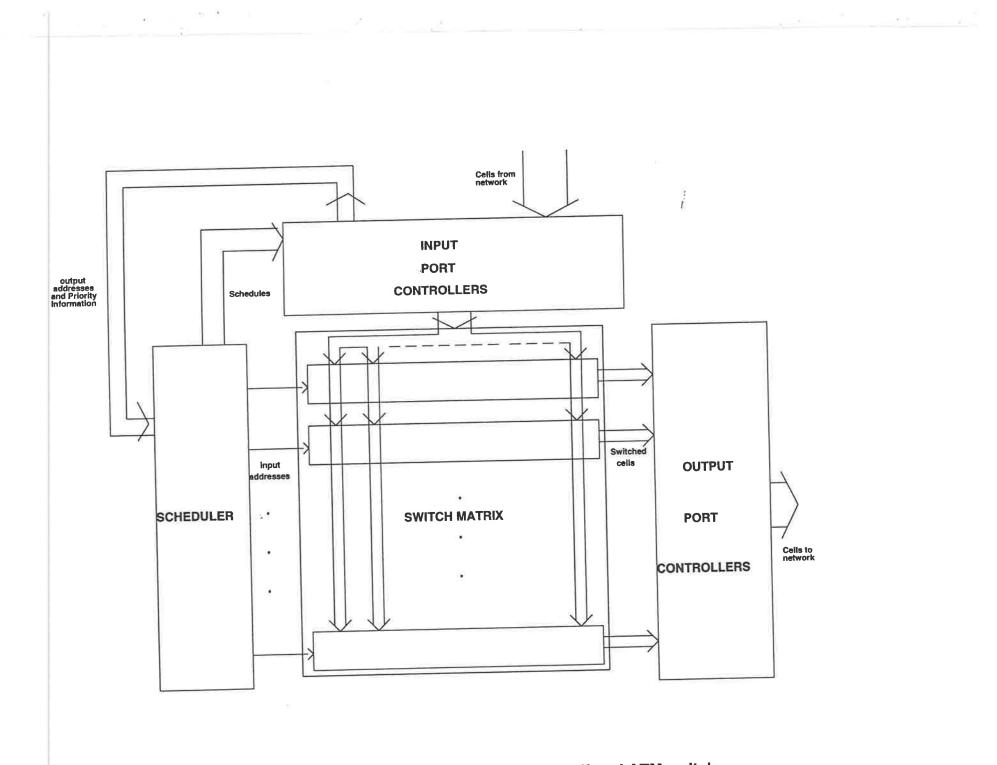

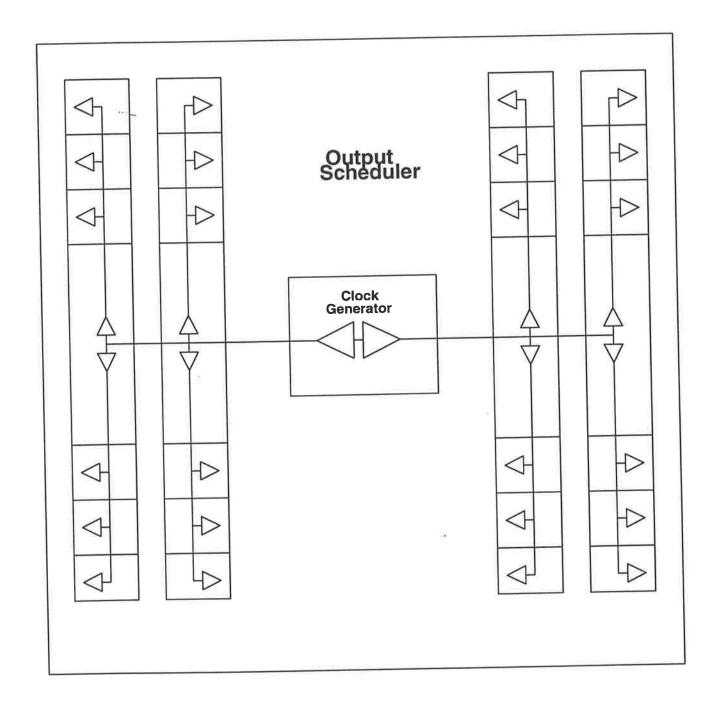

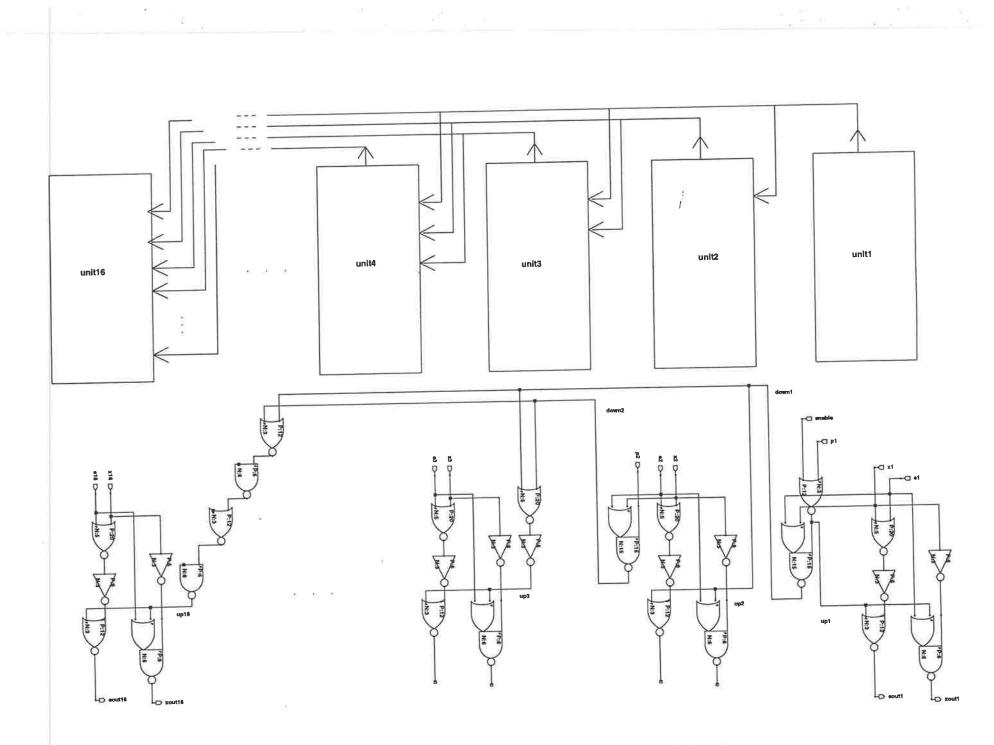

#### 2.4.1 The Structure of the Output Scheduler

A functional block diagram of the output scheduler is shown in figure 12. The example output scheduler shown in the diagram, has 32 input ports and 32 output ports. The inputs include 16 output addresses and 16 priority information codes. All of this input information comes from the input port controller. There are 16 output ports connected to the 16 input port controllers, which send the schedules to the controllers. The other 16 output ports are connected to the switch matrix. Each of these ports passes to the switch outputs, the input address to which the switch output is to be connected.

Basically, this output scheduler is composed of four main functional blocks: the elementary scheduler, the input status register, the output status register and the clock generator. As shown in the diagram, the scheduler consists of a 16x16 array of elementary schedulers. Each row of the elementary schedulers corresponds to an input, and each column of the elementary schedulers corresponds to an output. Each elementary scheduler corresponds to an input-output pair. The function of the elementary scheduler is to compare the input status array with the output status array.

To minimise the amount of information to be exchanged between the output scheduler and outside, we can simply maintain the input status array and output status array within the output scheduler. The input status array and output status arrays are stored in the input status register and output status register respectively (see figure 12). In addition to storing and updating the input status array, the input status register is in charge of sending the schedules out to the input port controller.

Moreover, a 4:16 decoder and a 16-bit address register are also integrated into the input status register, although they have a separate function. Another part of this output scheduler is a clock generator. This generator receives the clock signal from outside and it buffers and distributes it every clocked circuit on the chip. It also generates the assertion pulses which are needed both by the status register and the elementary schedulers.

#### 2.4.2 Operation of the Output Scheduler

A more detailed diagram of this output scheduler is given in figure 13, which shows dataflow among each functional block. The aim of this section is to illustrate how each functional block interfaces and coordinates with others. The detailed design within each functional block will be discussed in the next section.

#### 2.4.2.1 Data flow of the Output Scheduler

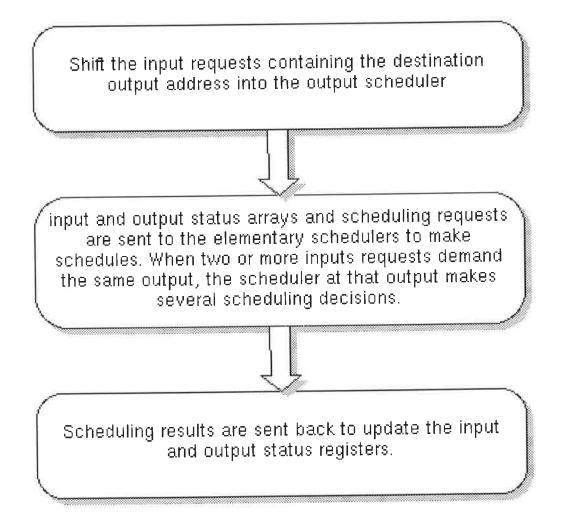

In this section we will discuss how the output scheduler works. Before we step into the detailed discussion of operation, a flow chart (see figure 14) can help us to understand the basic function of scheduler.

The operation of an output scheduler can be divided into three steps and each step takes one time slot. The first step is to import the request from the input status register; the second step is to compare the status arrays; the last step is to send the scheduling result out. Clearly, in order to achieve the best efficiency, shifting in the

Figure 13 Detailed structure of output scheduler

output addresses and priority information, comparing the status arrays and sending the input addresses and schedules out are all carried out in a pipelined manner.

### Figure14 Flow chart of operation of output scheduler

#### • Importing the Request

As mentioned above, the function of the output scheduler is to compare the input and output status arrays so as to find the first time slot available for both the requested input and output. The status arrays are compared within the elementary scheduler that corresponds to the requested input-output pair, so we need some information to find the particular elementary scheduler. Moreover, any schedule is made on the basis of the priority information, so some circuits must be provided in the output scheduler to handle this priority information.

Recall that each row of the elementary schedulers corresponds to an input and each elementary scheduler within this row corresponds to an output. Therefore, we can use an output address to select particular elementary schedulers and activate them to compare the status arrays. At the beginning of this chapter, we have stated that in order to support multicast (in which an input can select a number of outputs simultaneously), a 16-bit array is used to describe the output address. Referring to figure 13, in each row of the elementary schedulers, there is a 16-bit shift register that receives the output address from the input port controller in series and sends it to each elementary scheduler in this row in parallel. Each bit of this shift register is connected to the "enable" input of an elementary scheduler. The asserted bit in the address will activate the corresponding elementary scheduler to perform the comparison of the status array.

Let us study an example. If a cell requests to be switched to the outputs labelled #1 and #16 (see figure 13), its output address will be an array of bits such as

"1000\_0000\_0000\_0001". It takes one time slot to shift it into the shift register. At the beginning of the next time slot, the address is sent out in parallel. Each bit of this array is sent to the corresponding elementary scheduler. In this example, the elementary schedulers corresponding to the first and last output receive a logical I, so they are turned on and will compare the input and output status array. In contrast, the other elementary schedulers that receive 0 are turned off. In other words, when the status arrays flow through them they perform no operation and keep the status arrays intact.

Referring to figure 13, we note that we have provided a decoder with each row of the elementary schedulers. This decoder is utilised here to turn the 4-bit binary number that describes the priority information into a 16-bit array. As defined at the beginning of the chapter, we use a 4-bit array to describe the priority information, which is shifted into the output scheduler in series. This priority information describes the threshold value of the time slot that a cell can use. As shown in a later section, the elementary scheduler needs a 16-bit array to be used conveniently. Hence, we should turn this 4-bit binary number into a 16-bit array. This is done by the 4:16 decoder.

As we have discussed, in this output scheduler we assume that a cell to be multicast should possess the identical priority information. Therefore, we can simply send the decoded priority information for a multicast cell to all the 16 elementary schedulers in a row (see figure 13).

#### Comparing Status Arrays

When both the output addresses and priority information is available, the output scheduler is ready for the next step which is request processing. This step is the essential step for the operation of the output scheduler. We discuss its basic operation first, then we will analyse its drawbacks and improve it.

At the beginning of the next time slot, both the output address and the decoded priority information are sent to the elementary schedulers. Simultaneously, the input status registers load the status arrays into all the elementary schedulers in its corresponding row. The output status registers send the output status arrays to one of elementary schedulers in its column (refer to figure 13). The output status array will go through all the elementary scheduler in this column one by one and the output status array is compared with the input status array in the activated schedulers.

Note that the operation of each column of the elementary schedulers is identical, so let us study the operation of one column, which is sufficient to mirror the operation of the whole output scheduler. For simplicity, we assume that the output status array is loaded into the elementary scheduler in the first row. We will have a more general discussion on this topic in later section.

For example, if the first elementary scheduler in a column is activated, the output and input status is compared in it. If there is a schedule made, the elementary scheduler would update the output status array and send an updated copy of the output status array to its subsequent elementary scheduler, the one in the second row. In figure 13 the updated output status array is labelled *X1*. Simultaneously, the

elementary scheduler generates a schedule array (labelled e in the diagram) in which I represents a schedule and 0 means no schedule. This schedule array will coordinate with other schedule arrays generated by the other elementary schedulers in this row to produce a final schedule array for the input status register.

The updated output status array *XI* is sent to the elementary scheduler in the second row. If this elementary scheduler is also turned on, the output status array will be compared with the input status array that is stored there. Assume that in this comparison no schedule is made, so the output status array will be kept intact and go to the next elementary scheduler. At the same time, the elementary scheduler outputs a schedule array. Since no schedule is made, it is just an array of zeros.

Subsequently, assume that no other elementary schedulers in this column are turned on, then the output status array will flow through each of them and return to the output status register with a value that is identical to the value of X1. Since no schedule can be made in a disabled elementary scheduler, the schedule outputs of elementary schedulers are all arrays of zeros.

At the end of this time slot, the input status registers fetch the value from the  $e\_bus$ . Indeed, the value on the  $e\_bus$  is the logical OR of all the schedule results corresponding to the same time slot and different output. We will explain later why a logical OR should be used. The input status register uses the scheduling results to modify the input status arrays stored in them. On the other hand, the output status register stores the new output status array in it.

#### • Exporting the Scheduling Results

As we know, the input port controller needs the schedule array to place the cell into the buffer and the switch matrix needs the input address to switch the cell. We have discussed the generation of the schedule result. We will discuss the generation of the input address in a later section. The third step is to send them out. At the end of the  $3^{rd}$  time slot, the output scheduler processes a request.

#### 2.4.2.2 Structure Analysis

In the last section, we discussed how the output scheduler works. In this section, to gain insight into the operation of the switch, we will discuss why it is appropriate for the schedule to operate in this way..

One question may be why the input status array is sent to all the elementary schedulers in a row, while the output status arrays are fed to one scheduler and it ripples through the whole column.

As the name "output scheduler" implies, all the schedules made in this scheduler correspond to the output ports. In other words, what is scheduled is the operation of the output port. One output port can only handle one cell at one time slot, so it demands the output scheduler to schedule only one cell into a time slot. In the output scheduler, the output status arrays are employed to indicate the state of the output ports. If there were a schedule made the output status would be updated to I

immediately. The I in the output status array represents a time slot that has been scheduled out. Therefore, this I will give its subsequent elementary scheduler no chance to make further schedules into that time slot. Thus, this structure ensures that only one cell is scheduled to a time slot, in other words, no conflict may occur on the output port.

On the other hand, consider the input status arrays. As we know, this switch should provide the multicast function, so it is not surprising for one input port to send a cell to a few output ports simultaneously. In the section discussing the operation of the switch matrix, we have seen that in the crosspoint switch the inputs just broadcast the cells to all the outputs, and the output will select one of them according to the input address that comes from the output scheduler. This architecture implies that from the point of view of the input port of the switch matrix there is no difference between switching the cell to one output or to sixteen outputs. Therefore, we just send the input status array to all the elementary schedulers in a row simultaneously. Each elementary scheduler in this row will generate an array of schedule results. Therefore, we use a logical OR of all the corresponding bits of the 16 arrays as the final schedule result and send it to the input status register. This explains why the final schedule result should be the logical OR of all the individual results.

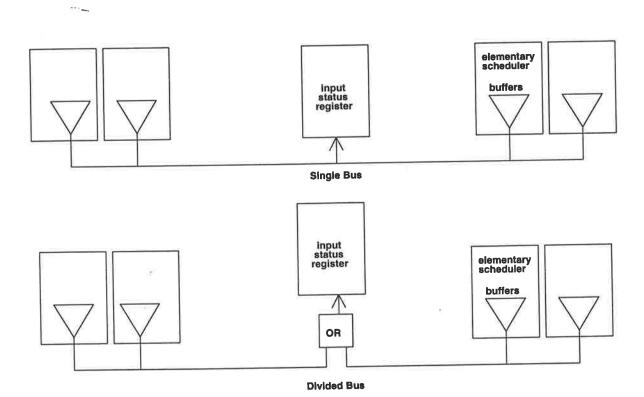

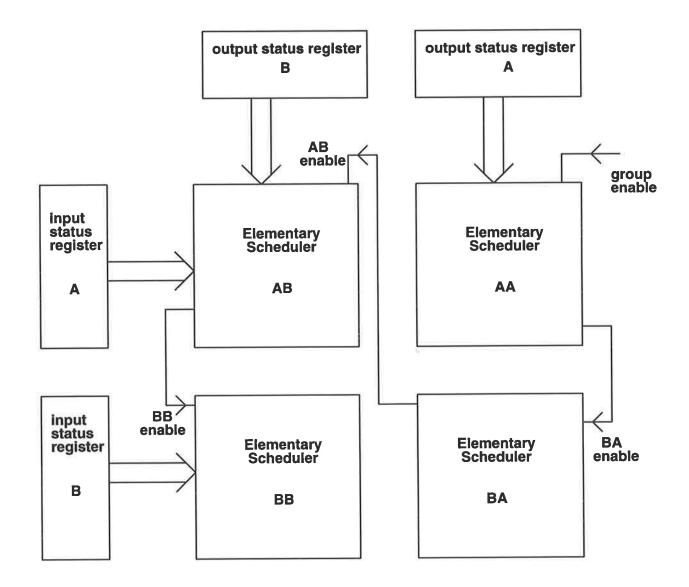

#### 2.4.2.3 Defeating Unfairness

Now we have understood the necessity of rippling the output status array through the column of elementary schedulers, another question related to it will appear: since each elementary scheduler can only receive the updated output status array from its

upper one, the upper elementary scheduler has a greater chance to make schedules as it receives the output array earlier. In other words, there is unfairness between each elementary scheduler in a column. In order to solve this problem, we have to change the entry-scheduler of the output status array frequently and regularly so that each elementary scheduler in a column has an equal opportunity on average to achieve the best service as well as the worst service.

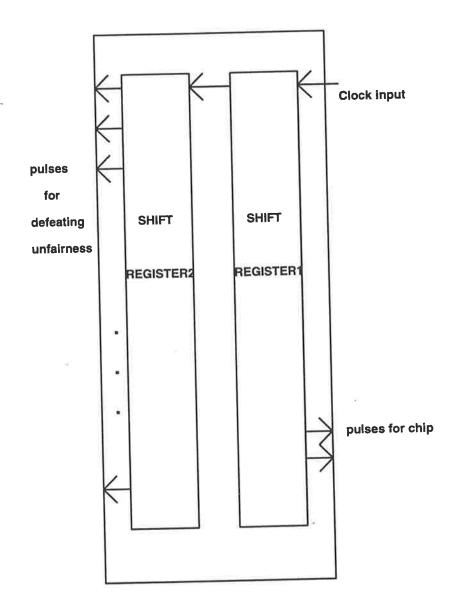

Towards that end, the scheduler is designed to be able to load the status array into any one of the elementary schedulers in one column and consequently, the updated output status array can be returned from any elementary scheduler (see figure 13). Clearly, in one time slot only one of them should be turned on to receive and return the status array. Therefore, we need a signal to select it. We employ a 16-bit shift register to act as a pointer in the signal generator. We have discussed the operation of a pointer in the previous section. Each bit of this register is connected to a row of elementary scheduler. When the pointer is pointing to a row, the row below the pointed row would be the entry scheduler of the output status arrays for this time slot. Thus, it receives the output status array from the output status register directly. The other ones will receive the status array from its upper scheduler. When the output status array goes through all the 16 elementary schedulers in a column, it is returned to the output status register through the scheduler in the row pointed to. The entry elementary scheduler is changed in each time slot, so that after 16 time slots, each elementary scheduler in a column achieves the identical average chance for service.

「「「「「「「」」」

ŝ, j

In this chapter, we discussed the operation of the ATM switch at the highest level. Four basic functional blocks are introduced and their coordination with each other is demonstrated. Then, we discussed the structure and operation of the input port controller. From the discussion of the input port controller, we understand how the controller generates the request and manages the cell flow according to the schedule results. Subsequently, we discussed the architectural design of the output scheduler, from which we understand the basic scheduling process. With a good understanding of the high-level operation, we will now investigate the detailed design in a lower level.

## **Chapter Three**

# Investigating Basic Functional Blocks of the Output Scheduler

Now that we have discussed the architecture of this output scheduler and studied how each module coordinates with others, we are ready to have a close look at the operation of each functional block.

#### **3.1 Elementary Scheduler**

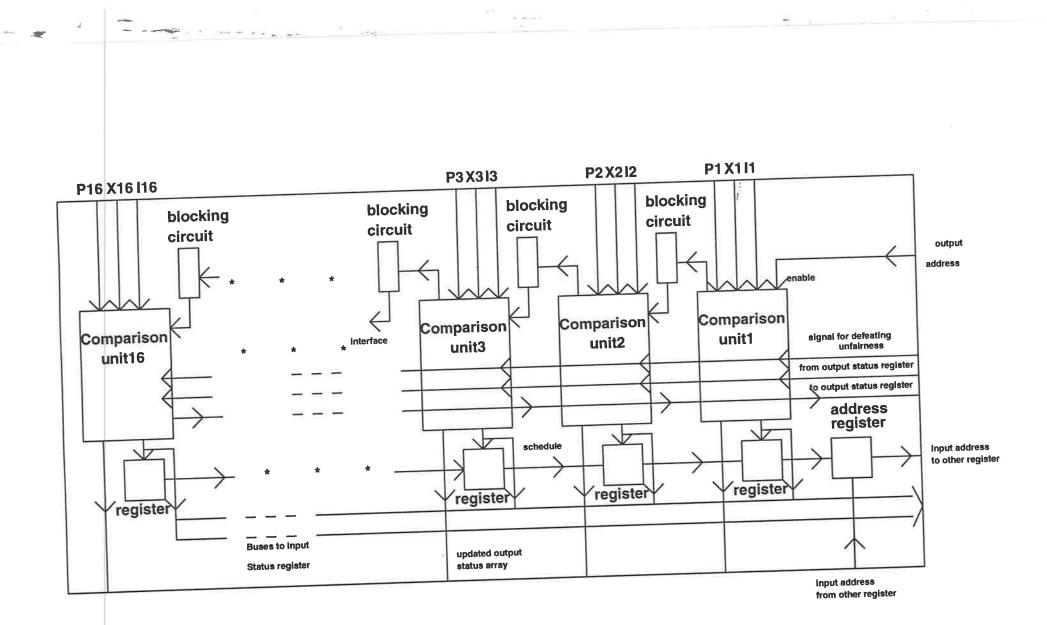

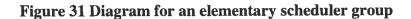

#### 3.1.1 Structure

strev A

and the second second second second

11

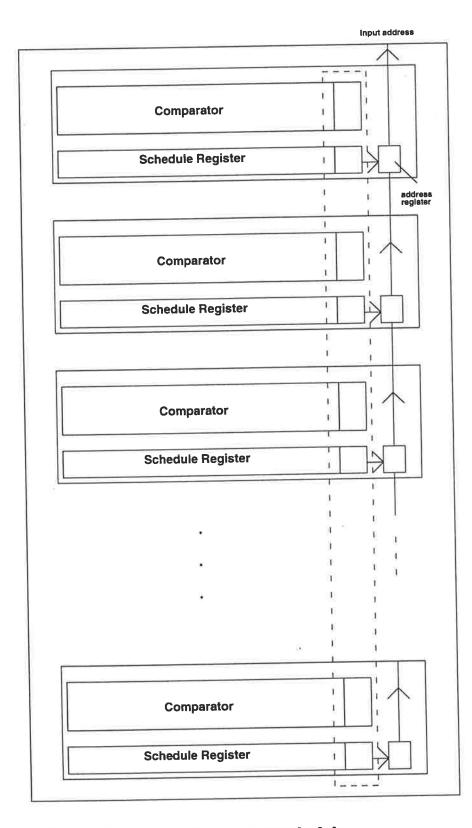

First of all, let us study the interface of an elementary scheduler with the outside world. The block diagram of an elementary scheduler is shown in figure 15. Since the basic function of an elementary scheduler is to compare the input status array and output status array, each elementary scheduler has two 16-bit inputs for the input and output status array respectively. As we have mentioned, the priority information also takes part in the comparison, so a 16-bit input for priority information that is decoded from a 4-bit binary number is needed. The elementary scheduler also needs an "enable" input which is controlled by the output address. In addition, in order to defeat unfairness, each elementary scheduler is designed to be able to receive the output status array directly, so a 16-bit input for the output status array and a pointer

input are necessary. Each elementary scheduler has a schedule array output and two output status array outputs one of which is connected to the subsequent elementary scheduler and the other is connected to the output status register. Moreover, each elementary scheduler has a one-bit input and a one-bit output for the input address.

Secondly, let us consider the internal structure of an elementary scheduler. The elementary scheduler consists of two main parts: the comparators and the schedule registers. As shown in figure 15, there are 16 comparison units and each unit corresponds to one time slot. For each unit, there are four inputs: input status, output status, priority information and the interfacing signal. Note that associated with each comparison unit there is a blocking circuit, which generates the interface signal to its subsequent unit. As we know, the scheduler is only concerned with the first time slot in which both input and output port are available. The blocking circuit is employed to keep other schedules from being reached once the first one is found. For the first unit, the interface signal comes from the output address, which determines whether to enable this elementary scheduler. In addition, each scheduler outputs a schedule array and an output status array. The schedule result has two branches of outputs, as shown in figure 15. One of them is sent back to the input status register. The other is fed into a 16-bit schedule register, whose function will be discussed later. Moreover, as shown in the diagram, there is a separate one-bit register, which is used for the generation of input addresses.

#### **3.1.2 Operation of the Comparison Units**

Whether an elementary scheduler will operate or not is decided by the "enable" signal, which is connected to one bit of the output address. If the output to which the elementary scheduler corresponds is not requested, a logical  $\theta$  will be sent to it. Then this signal is rippled down to each comparison unit through the blocking circuit and disables them. Alternatively, a logical l will activate this elementary scheduler. At the beginning of each time slot, the input status array and the priority information are sent to each elementary scheduler, while the output status register will not be available until it ripples to the elementary scheduler. When all these three sets of inputs appear on an elementary scheduler, the scheduler is activated. What we are interested in is the first time slot that is available for both input and output, so the comparison operation begins from the unit corresponding to the first time slot and passes along to the one corresponding to the last time slot. In other words, no decision can be reached for a comparison unit until it receives the interfacing signal from its preceding unit.

Now let us study a simple scheduling example without consideration of priority information. Assuming that an input status array,  $0000\_0000\_0111\_1101$ , and an output status array  $1111\_0000\_0000\_1111$  appears on the input of an activated elementary scheduler. Here we regard the least significant bit as the first time slot. The first bit of each array is *1* which means that in this time slot both input and output are busy. Then the first unit's blocking circuit sends a logical *0* to the following unit to inform it that no schedule is yet found. With this signal, the second comparison unit is activated and begins to compare the second bit of the arrays. However, there is still no schedule found, so similar to the first one it passes the

responsibility to its next unit. Thus, the comparison is carried out one by one until a schedule is found. For these two arrays, in the 8<sup>th</sup> time slot both arrays are 0 that means both input and output are available. The 8<sup>th</sup> comparison unit generates a logical I as the schedule result and updates the 8<sup>th</sup> bit of the output status array into I. Simultaneously, its blocking circuit sends a I to its subsequent unit and this signal will be passed through all its subsequent units. This signal prevents the subsequent units from making any schedules, although both ports are available in the 9<sup>th</sup> to 12<sup>th</sup> time slots.

#### 3.1.3 Modifications for Priority

From the last example we are clear about the basic operation of the comparator. Now let us look at how the priority information affects scheduling. In the last example, we did not consider the effect from the priority information. We can regard this situation as that each cell has high priority, in which case the cell can be scheduled into any one of the 16 time slots. In this case, the priority information should be "1000\_0000\_0000\_0000". As assumed above, the most significant bit corresponds to the 16<sup>th</sup> time slot, so this priority information means the cell can not use the time slots after the 16<sup>th</sup>. Thus all the 16 time slots are available for it.

A cell with a low priority can only use some of the time slots, which is decided by the threshold value set by the priority information. Let us still consider the two arrays in the last example to study how the priority information affects the scheduling results. For convenience, we write it here again, the input status array: 0000\_0000\_0111\_1101, and output status array: 1111\_0000\_0000\_1111. First, we

consider the priority information "0000\_1000\_0000\_0000". This array means the cell can use the first 12 time slots. As we have discussed above, the cell would be scheduled into the 8<sup>th</sup> time slot, so this cell obtains a schedule within the limit of resources. The priority information would have no affect on the schedule results. On the other hand, if the elementary scheduler receives such an array of priority information as "0000\_0000\_0100\_0000", the result will be different. This priority information limits the time slots available to the cell to the first seven, while there is no schedule for it until the 8<sup>th</sup> time slot. Thus, even though there are plenty of schedule resources are available from the 8<sup>th</sup> to 12<sup>th</sup> time slots, the cell is still going to be discarded because its low priority prevents it from using them.

#### 3.1.4 Operation of the Schedule Register

As mentioned above, the output scheduler should generate an input address for each output of the switch matrix to set up a data path for the cell. In order to generate the input address, we need a copy of schedules. Towards that end, one copy of the schedule results are sent to the input status register, which contributes to update the input status arrays stored in both the input status register and input port controller. The other copy of the schedule array is directed to a sixteen-bit schedule register. Each bit of the register corresponds to a time slot. Since each bit of this register obtains the schedule state from a comparison unit, the contents of this register unit should correspond to the same time slot as the comparison.

The schedule register is used here to record the schedule history of the elementary scheduler. In other words, it indicates which time slots have been scheduled by this

elementary scheduler. As we have mentioned, each elementary scheduler corresponds to one input-output pair. When a schedule is made in an elementary scheduler, it means that a cell is scheduled to be switched between this input-output pair. Indeed, the states in this schedule register indicate in which time slot this input-output pair will switch a cell.

Clearly, the schedule array is the accumulation of the results of the schedule array that come from the comparison units. We should use the schedule array to update the states in the schedule register. Towards that end, an OR gate is used. What is written into the schedule register is the logical OR of schedule array and the previous state in the schedule register. Since the new state always relies on its previous state, all the states in the schedule register should be set to 0 when the scheduler is powered up, which means no schedule has been made. When a new schedule, a logical 1, appears in the schedule array, it will modify the state in the corresponding bit of the register. If no schedule comes in, the states in the schedule register are kept intact.

Furthermore, as stated above, the shift register is adopted to indicate the scheduling history of the following 16 time slots, so the binary array stored in the register should be shifted one bit per time slot so that the state in the register can correspond to the proper time slot. Hence, the shift register is shifted one bit per time slot. The last bit which corresponds to the 16<sup>th</sup> time slot is loaded with a *0*, and the state stored in the first bit of the register is loaded into another shift register, as shown in figure 15. This register is also a parallel-in-series-out shift register, whose function is to shift the input address out of the output scheduler.

#### 3.1.5 Input Address Generation