#### University of Louisville

## ThinkIR: The University of Louisville's Institutional Repository

**Electronic Theses and Dissertations**

5-1983

# A master clock for the Speed School impulse clock system using **WWV** time information

John E. Pfeifer Jr. University of Louisville

Follow this and additional works at: https://ir.library.louisville.edu/etd

Part of the Electrical and Computer Engineering Commons

#### **Recommended Citation**

Pfeifer, John E. Jr., "A master clock for the Speed School impulse clock system using WWV time information" (1983). Electronic Theses and Dissertations. Paper 3669. https://doi.org/10.18297/etd/3669

This Master's Thesis is brought to you for free and open access by ThinkIR: The University of Louisville's Institutional Repository. It has been accepted for inclusion in Electronic Theses and Dissertations by an authorized administrator of ThinkIR: The University of Louisville's Institutional Repository. This title appears here courtesy of the author, who has retained all other copyrights. For more information, please contact thinkir@louisville.edu.

# A MASTER CLOCK FOR THE SPEED SCHOOL IMPULSE CLOCK SYSTEM USING WWV TIME INFORMATION

By.

John E. Pfeifer, Jr. B.S., University of Louisville, 1980

A Thesis

Submitted to the Faculty of the

University of Louisville

Speed Scientific School

as Partial Fulfillment of the Requirements

for the Professional Degree

MASTER OF ENGINEERING

Department of Electrical Engineering

May 1983

A MASTER CLOCK FOR THE SPEED SCHOOL IMPULSE CLOCK SYSTEM USING WWV TIME INFORMATION

Submitted by: John E. Pfeifer, Jr.

A Thesis Approved on

February 18, 1983

by the Following Reading and Examination Committee:

Willeam At Prince

Thesis Director, William H. Pierce

Barry/R. Horowitz

Robert L. Collins

#### ACKNOWLEDGEMENTS

The author would like to thank, in general, everyone that contributed to the completion of this thesis project and, in particular:

Dr. William H. Pierce for agreeing to serve as thesis director and for his technical guidance while serving as director.

Dr. Robert L. Collins and Dr. Barry R. Horowitz for serving as thesis committee members.

Mr. Thomas Bisch, Mr. William Hawkins, and Mr. Ernest

Williams of the Electronics Shop for their for their cheerful

and courteous assistance.

Mrs. Shirley Tomes for her typing "par excellence",

And last, but not least, his parents, Jack and Mary

Margaret Pfeifer, and his brothers and sisters, Marty, Julie,

Tom, and Sally for their more than ample encouragement and

support.

#### ABSTRACT

Since approximately February of 1979, the Speed School impulse clock system has not functioned due to a worn-out master clock that was never replaced because of a lack of funds. For this thesis project, a solid-state master clock that performs the same functions as the old mechanical master clock was built for less than \$200. The new clock features accuracy traceable to the National Bureau of Standards, automatic reset after a power-down and subsequent power-up, and a daylight savings time provision. A decoder that recovers time information broadcast by radio station WWV from Fort Collins, Colorado was built and interfaced to the master clock to provide the accuracy traceable to the National Bureau of Standards.

### TABLE OF CONTENTS

|         |                              |                                                                                                                                                                                                     |       |           | Dage                                                           |

|---------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------|----------------------------------------------------------------|

| APPROVA | AL PA                        | AGE                                                                                                                                                                                                 | • • • |           | Page<br>. ii                                                   |

| ACKNOWL | EDGE                         | EMENTS                                                                                                                                                                                              |       | • • • •   | . iii                                                          |

| ABSTRAC | т                            |                                                                                                                                                                                                     |       |           | . iv                                                           |

| TABLE C | F CC                         | ONTENTS                                                                                                                                                                                             |       |           | • v                                                            |

| LIST OF | TAE                          | BLES                                                                                                                                                                                                | ,     |           | • vii                                                          |

| LIST OF | FIC                          | GURES                                                                                                                                                                                               |       |           | • viii                                                         |

| I.      | INTE                         | RODUCTION                                                                                                                                                                                           |       |           | . 1                                                            |

| II.     | CLOC<br>A.<br>B.<br>C.<br>D. | Master Clock                                                                                                                                                                                        | • • • | • • • • • | 3<br>3<br>6                                                    |

| III.    | NEW<br>A.<br>B.              | MASTER CLOCK  General Function  Master Clock Hardware  1. MC6802 Microprocessor.  2. MM58167 Real-Time Clock  3. WWV Decoder  4. EST, EDT Switch  5. MC6821 PIA  6. 2716 EPROM  7. Address Decoding |       |           | 12<br>12<br>15<br>15<br>16<br>16<br>17<br>17                   |

|         | с.                           | 8. Clock Pulser                                                                                                                                                                                     |       |           | 21<br>22<br>22<br>22<br>22<br>23<br>23<br>23<br>25<br>25<br>25 |

|         |                              | <ol> <li>Hours Difference Routine.</li> </ol>                                                                                                                                                       |       |           | . 26                                                           |

|       |        |       |             |      |                  |         |      |         |          |     |       |       |       |       | Page  |

|-------|--------|-------|-------------|------|------------------|---------|------|---------|----------|-----|-------|-------|-------|-------|-------|

|       |        |       |             |      | Updat            | e Ro    | uti  | ne.     |          |     |       |       |       |       | . 26  |

|       |        |       |             | k.   | Add O            |         |      |         |          |     |       |       |       |       | 0.0   |

|       |        |       |             |      | Routi            |         |      |         |          |     |       |       |       |       |       |

|       |        |       |             | 1.   | Fifty            |         |      |         |          |     |       |       |       |       |       |

|       |        |       |             |      | Catch            |         |      |         |          |     |       |       |       |       |       |

|       |        |       |             | n.   | Short            | рет     | ay . | Rou     | CTHE     | • • | • • • | • • • |       | • • • | . 21  |

| ľ     | v.     | VWW   | DECC        | DER. |                  |         |      |         |          |     |       |       |       |       | . 28  |

|       |        |       |             |      | ind on           |         |      |         |          |     |       |       |       |       |       |

|       |        | В.    |             |      | Circ             |         |      |         |          |     |       |       |       |       |       |

|       |        |       |             |      |                  |         |      |         |          |     |       |       |       |       |       |

|       | V.     | CONC  | LUSI        | ONS  | AND R            | ECOM    | MEN  | DAT:    | LONE     |     | •••   | • • • | • • • | • • • | 39    |

| REF   | EREN   | CES.  |             |      |                  |         |      | • • • • |          |     |       |       |       |       | 40    |

| D 7 D |        |       |             |      |                  |         |      |         |          |     |       |       |       |       | 7.1   |

| BIB.  | LIOG   | KAPE  | 1Y          |      | • • • • •        | • • • • |      | • • • • |          | • • | • • • | • • • | • • • |       | 41    |

| APP   | ENDI   | хі    |             | MAST | ER CL            | оск     | OPE: | RAT:    | ION      | PR  | OCE   | DUR   | E     |       |       |

|       |        |       |             | AND  | MASTE            | R CL    | OCK  | ANI     | VW C     | VV  | DEC   | ODE   | R     |       |       |

|       |        |       |             | DISA | SSEMB            | LY G    | UID  | E       |          |     |       |       |       |       | 42    |

| APP   | ENDI   | X II  |             |      | 167 A            |         |      |         |          |     |       |       |       |       | 50    |

| APP:  | ENDI   | X II  | I           |      | EM SO            |         |      |         |          |     |       |       |       |       |       |

|       |        |       |             |      | FLOWC            |         |      |         |          |     |       |       |       |       | 61    |

| APP:  | ENDI   | X IV  | 7           | 7    | ED LAY           |         |      |         |          |     | -     |       |       |       |       |

|       |        |       |             |      | MASTE            |         |      |         |          |     |       |       | R     | • • • | , 87  |

| APP.  | ENDI   | ΧV    |             |      | RECEI            |         |      |         |          |     |       |       |       |       | 0.5   |

| 1 DD: | 7175 T |       |             |      | EMATIC           |         |      |         |          |     |       |       | • • • | • • • | , 95  |

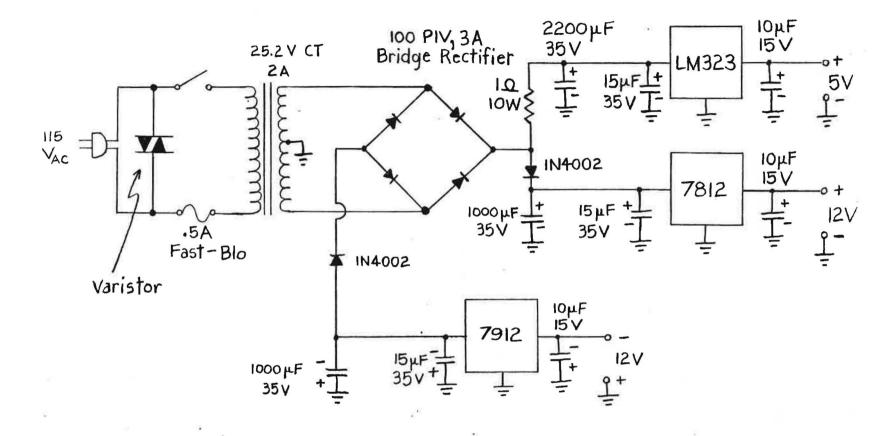

| APP.  | ENDI   | X VI  | L           |      | ER CL<br>ER SUP  |         |      |         |          |     |       |       |       |       | 0.8   |

| V D D | ENDI   | v 171 | т           |      | IR SUP<br>IBLESH |         |      |         |          |     |       |       |       |       |       |

| AFF.  | TUNT   | V AT  | L <b>.L</b> | TKOU | ם פימח כיו       | COLI    | MG , | GOTI    | ، د نارر | • • | • • • | • • • | • • • |       | , 102 |

|       | -      |       |             |      |                  |         |      |         |          |     |       |       |       |       | 105   |

#### LIST OF TABLES

| TABLE | I   | SPEED SCHOOL IMPULSE CLOCK SYSTEM | Page<br>11 |

|-------|-----|-----------------------------------|------------|

| TABLE | II  | MASTER CLOCK PRICE LIST           | 99         |

| TABLE | III | WWV DECODER PRICE LIST            | 100        |

| TABLE | IV  | POWER SUPPLY PRICE LIST           | 101        |

### LIST OF FIGURES

|        |    |                                 | Pag | _ |

|--------|----|---------------------------------|-----|---|

| FIGURE | 1  | Old Master Clock                | 4   | _ |

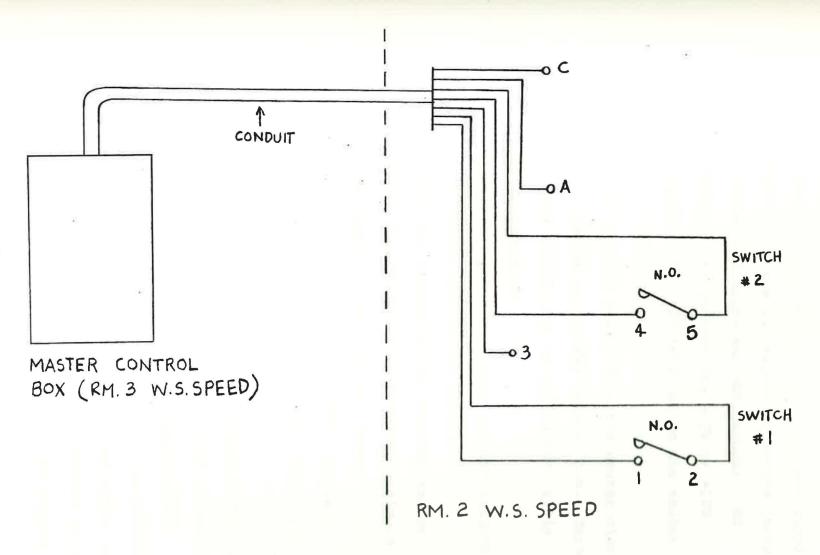

| FIGURE | 2  | Master Control Box              | 5   |   |

| FIGURE | 3  | Relay Box                       | 7   |   |

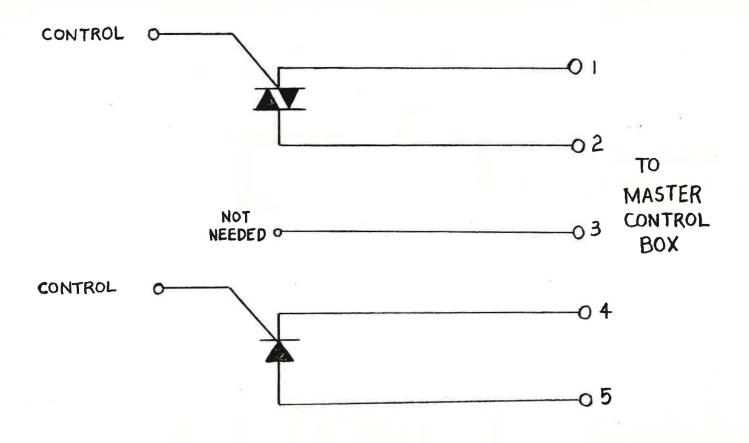

| FIGURE | 4  | Wall Clock Coil Connections     | 9   |   |

| FIGURE | 5  | New Master Clock                | 13  |   |

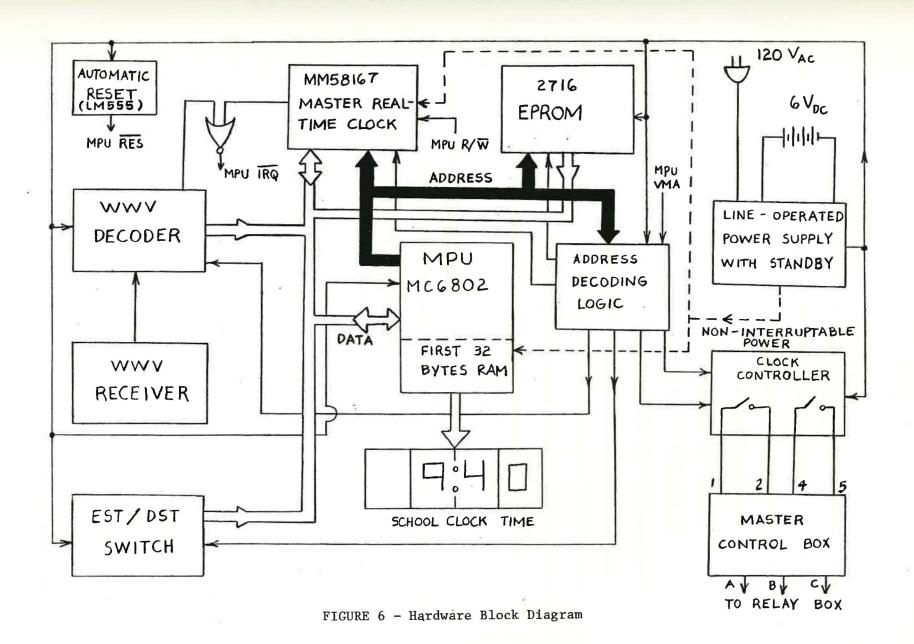

| FIGURE | 6  | Hardware Block Diagram          | 14  |   |

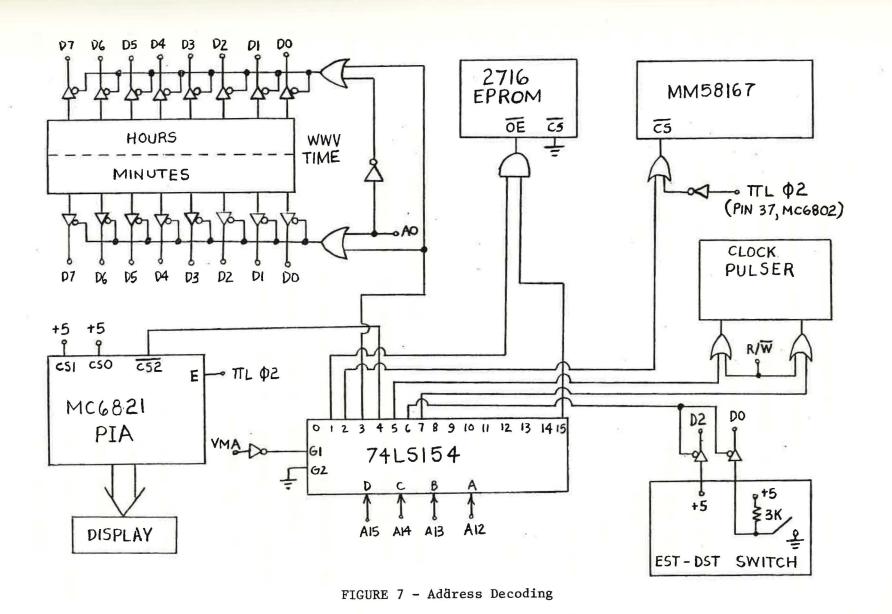

| FIGURE | 7  | Address Decoding                | 18  |   |

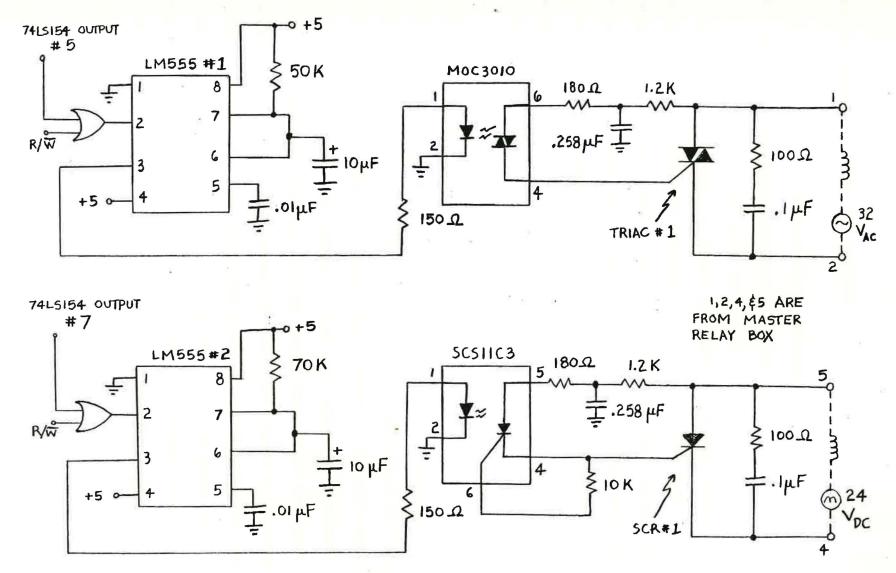

| FIGURE | 8  | Clock Pulser                    | 20  |   |

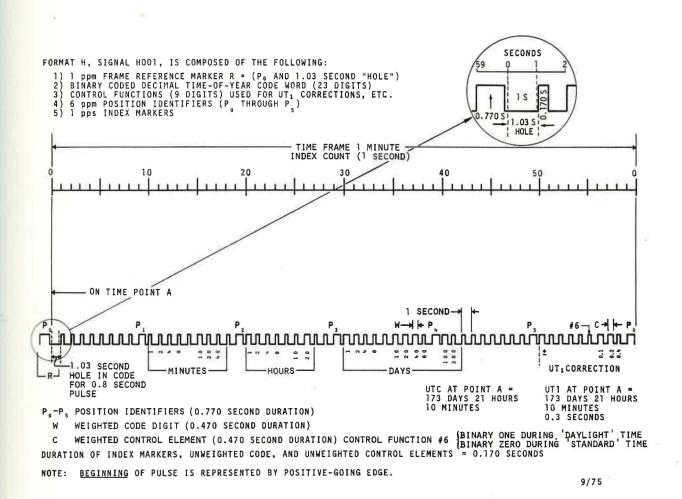

| FIGURE | 9  | WWV Broadcast Format            | 29  |   |

| FIGURE | 10 | WWV Guardband                   | 29  |   |

| FIGURE | 11 | WWV Time Code                   | 31  |   |

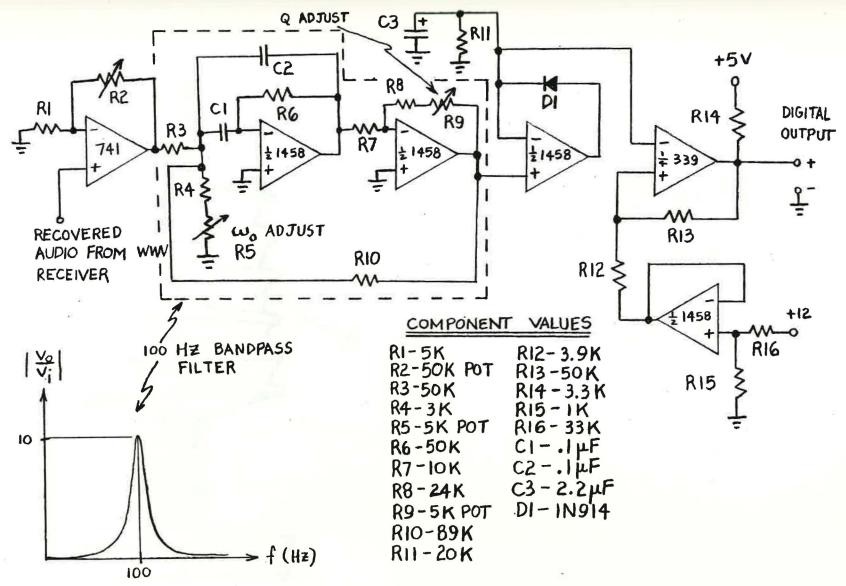

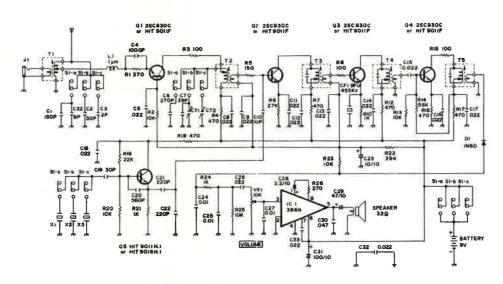

| FIGURE | 12 | Analog Decoding Circuitry       | 32  |   |

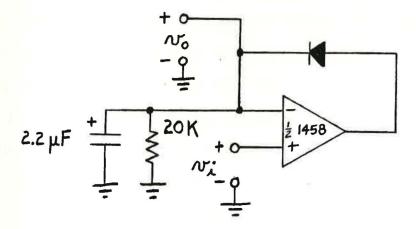

| FIGURE | 13 | Envelope Detector               | 33  |   |

| FIGURE | 14 | Schmitt Trigger Characteristics | 35  |   |

| FIGURE | 15 | Digital Decoding Block Diagram  | 36  |   |

| FIGURE | 16 | Timing Diagram                  | 38  |   |

| FIGURE | 17 | Clock Advancement Connections   | 41  |   |

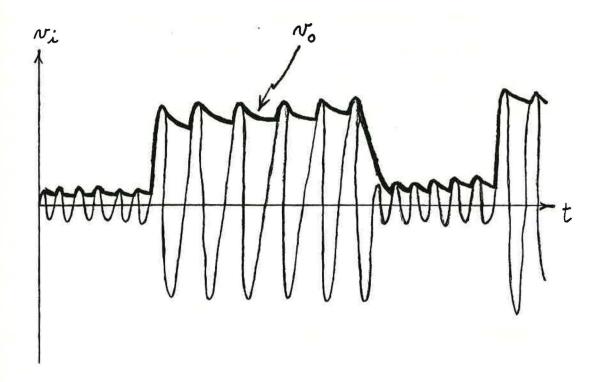

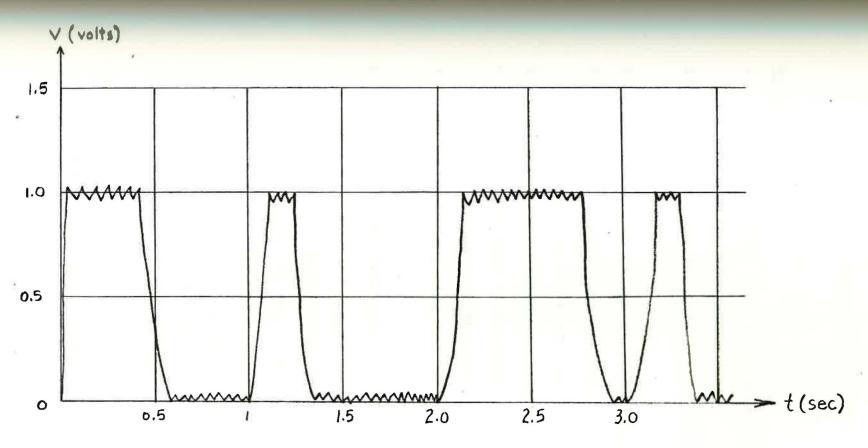

| FIGURE | 18 | Proper Decoder Waveform         | 47  |   |

#### I. INTRODUCTION

The Speed School impulse clock system has not been working since approximately February of 1979, when an old mechanical master clock that controlled the school clocks wore out. Shortly after the clocks stopped working, a bid of \$900 was submitted to make the clocks operational again. No funds were available at the time and the clocks were never repaired. The goal of this thesis project was to build another more advanced master clock that could be hooked up to the existing clock system, yet be all solid-state.

The new master clock was designed to have automatic reset capability after a power-down, a daylight-savings-time provision, and more accuracy than the old master clock. A microprocessor-based system was chosen for implementing the desired functions, since the cost of such systems has become very low, considering the flexibility that such a system provides. An MC6802 microprocessor was chosen since it has an internal clock-generating circuit and on-chip RAM that can be maintained during a power-down. Additional support devices included a microprocessor-compatible real-time clock, Erasable Programmable Read Only Memory (EPROM), and address decoding logic. Software for the master clock was developed with the Tektronix 8002A Development System.

In addition to this microcomputer unit, a separate WWV decoder was built to retrieve time information broadcast by radio station WWV. This decoder was then interfaced to the microcomputer to provide periodic updating of the real-time clock. In the following chapters, specifics of school clock operation, new master clock design, and WWV decoder design are presented.

#### II. CLOCK SYSTEM DESCRIPTION

The Speed School impulse clock system consists of a master clock, a master control box, two relay boxes, and the individual wall clocks. A brief description of each subsystem follows.

#### A. Master Clock

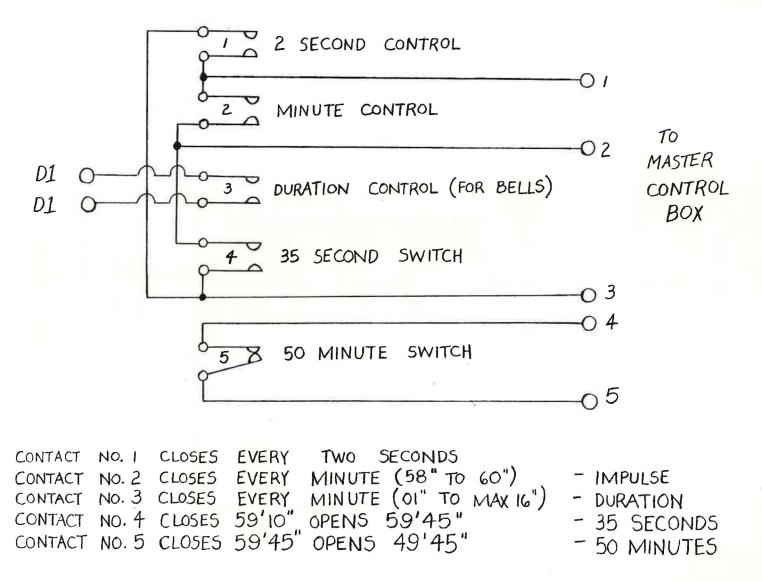

The old master clock, shown in FIGURE 1, consisted of a series of cam-actuated mechanical switches that opened and closed at different intervals. Switches one through four controlled an AC voltage, while switch five controlled a DC voltage. The time base for the master clock was a large pendulum connected to a series of gears that turned the switch cams. Originally located in Room 102 of W. S. Speed Hall, the master clock was connected to a master control box in Room 3 of W. S. Speed by seven wires in a section of conduit. In 1979, this mechanical clock apparently wore out and has never been replaced. The new master clock built for this thesis project will replace the old master clock.

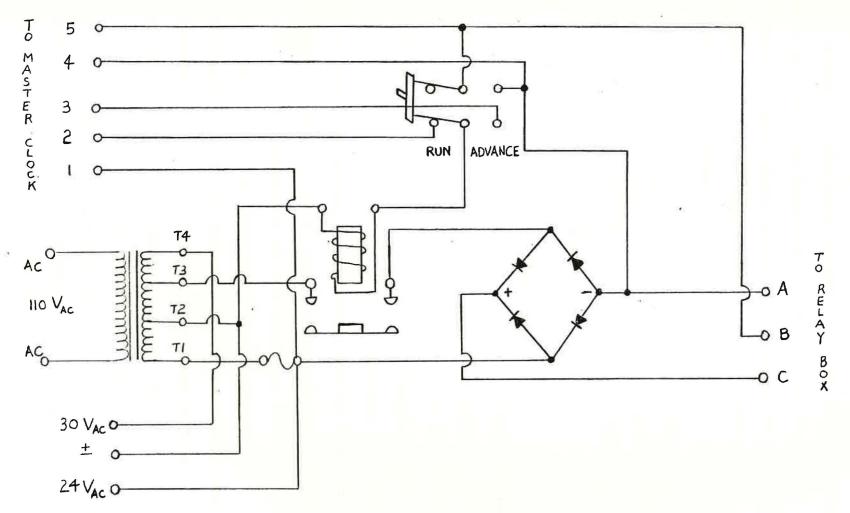

#### B. <u>Master Control Box</u>

The master control box, shown in FIGURE 2, contains an AC relay, a selenium rectifier, and an unconnected program unit that at one time controlled bells. The relay is energized when the proper switches in the master clock

FIGURE 1 - Old Master Clock

FIGURE 2 - Master Control Box

are closed (either #2 is closed or #1 and #4 are closed).

When the relay is energized, an AC voltage is applied to the rectifier input, which causes a DC voltage to appear across terminals A and C. The potential of terminal B is determined by switch #5 in the master clock. If the switch is closed, V = V , but if the switch is open, V = 0.

CB CA CB

These three output terminals are used as inputs to a relay box located immediately to the right of the master control box in Room 3 of W. S. Speed Hall.

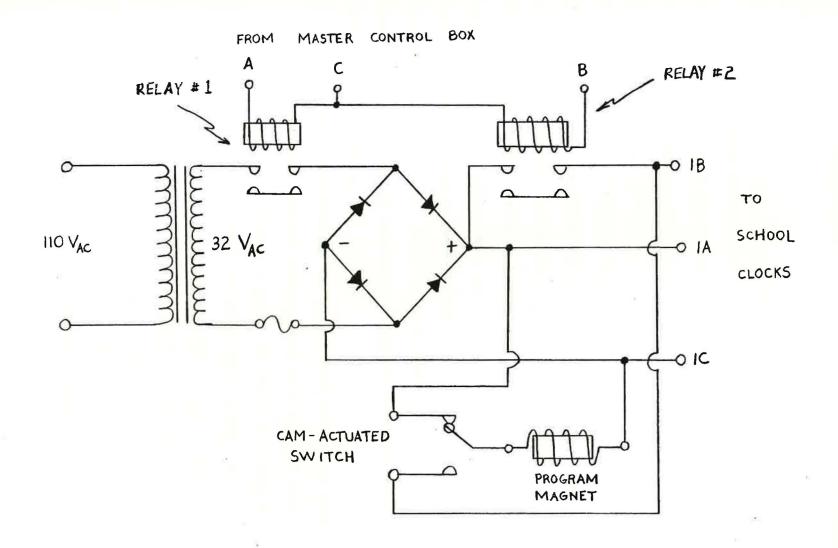

### C. Relay Box

The relay box, shown in FIGURE 3, receives inputs from the master control box. These three inputs control two relays that determine the status of outputs 1A, 1B, and 1C, which go to the school clocks in W. S. Speed Hall, J. B. Speed Hall, and Sackett Hall, and to another relay box in Ernst Hall. By having another relay box in Ernst Hall, the load on the unit in W. S. Speed is significantly reduced.

The program unit in the relay box in W. S. Speed

Hall controls all of the Speed School bells and is

programmed by breaking off tabs from metal strips and then

inserting the strips into a cylinder that rotates each time

the school clocks are incremented. At the programmed times,

a switch closes and rings the bells. If the toggle switches

at the bottom of the box are in the "off" position, the

bells are disabled. The program unit should still work with

the new master clock, but no attempt has been made to make

FIGURE 3 - Relay Box

the bells work again, since the desirability of bell-ringing is controversial.

#### D. School Wall Clocks

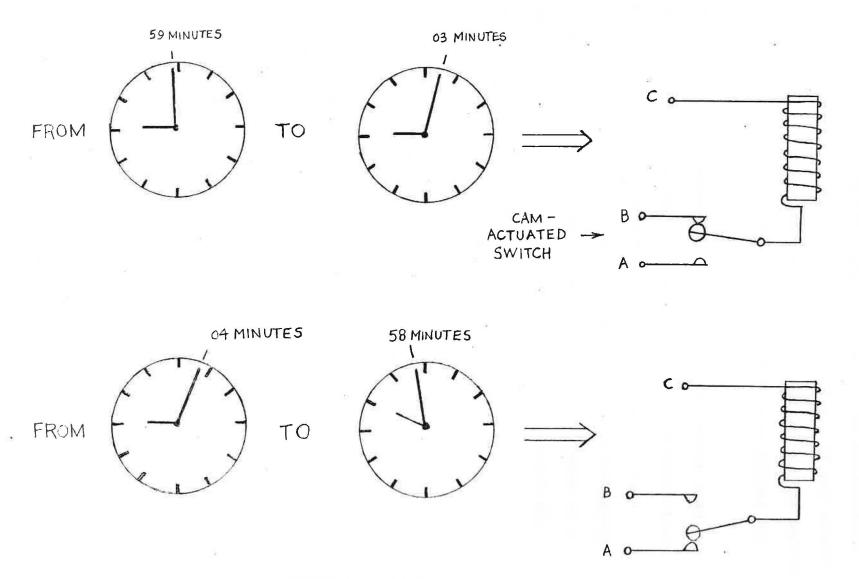

All Speed School clocks contain a 24-volt DC coil that when energized and subsequently de-energized, allows a ratchet mechanism to advance the clocks by one minute. Each clock has three wires (A, B, and C), one of which (wire C) is always connected to one terminal of the coil. The other coil terminal is switched between wires A and B by a cam-actuated switch inside the clock (see FIGURE 4). From four minutes after the hour until 58 minutes after the hour, the coil is connected from A to C. From one minute before the hour until three minutes after the hour, the coil is connected from B to C. With this arrangement, all clocks can be synchronized at one minute before the hour using the following procedure:

- From 00 minutes to 49 minutes after the hour,

24-volt pulses (duration = 0.5 second) are

applied between C and A as well as C and B.

- 2. From 50 minutes to 59 minutes after the hour, pulses are applied between C and A only. If any school clock is ahead of the master clock by ten minutes or less, then the school clock will stop advancing at 59 minutes after the hour and "wait" for the master clock to catch up.

FIGURE 4 - Wall Clock Coil Connections

3. At 59 minutes after the hour, ten consecutive pulses are sent between C and A. If any school clock is less than ten minutes behind the master clock, it will catch up when these pulses are sent.

Using the above procedure, any clocks that are at most ten minutes ahead of or one hour behind the master clock time will eventually be resynchronized to the master clock.

The power consumed by each clock is approximately equal to three watts, which at 24-volts corresponds to a current requirement of about 125 ma. TABLE I lists the locations of all Speed School impulse clocks.

#### TABLE I

#### SPEED SCHOOL IMPULSE CLOCK SYSTEM

Master Clock, Room 102, W. S. Speed Hall Program Machine Room 3, W. S. Speed Hall

### Secondary Clocks:

Sackett Hall, 3 Secondary Clocks: 1st floor hall, 2nd floor front hall, 2nd floor rear hall

Main Speed Building, 3 Secondary Clocks:

Basement Center hall, Room 201, Library

### W. S. Speed Hall, 9 Secondary Clocks:

Basement Laboratory, Basement Rear Hall, Basement Front Hall 1st floor Laboratory, 1st floor rear hall, 1st floor front hall 2nd floor Laboratory, 2nd floor rear hall, 2nd floor front hall

### ·R. C. Ernst Hall, 9 Secondary Clocks:

lst floor west hall, lst floor center hall, lst floor east hall

lst floor Departmental Office, lst floor Auditorium

2nd floor Central Hall (2 clocks), 3rd floor Central Hall (2 clocks)

Totals: 24 Secondary Clocks not including several that have been removed from both Sackett Hall and Main Speed Buildings when these buildings were remodeled from time to time.

#### III. NEW MASTER CLOCK

#### A. General Function

The hardware and software for the new master clock simply control two switches, and thus simulate the old master clock. A triac is used in place of switch #2 in the old master clock and an SCR is used in place of switch #5 (see FIGURE 5). Switches #1, #3, and #4 in the old master clock are not needed.

Whenever the school clocks are to be advanced or synchronized, the triac switch is closed. This energizes the relay in the master control box, which causes relay #1 in the relay box to close. A DC voltage now appears across output terminals Al and Cl, which go to the school clocks. If the SCR switch is not closed, terminal Bl of the relay box is floating and there is no current path between Bl and Cl. If the SCR switch is closed, a voltage appears across terminals B and C of the master control box. This energizes relay #2 in the relay box and now V = V since AlCl BlCl V = 0.

AlBI

### B. Master Clock Hardware

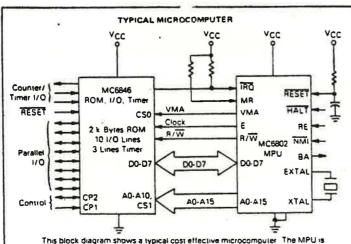

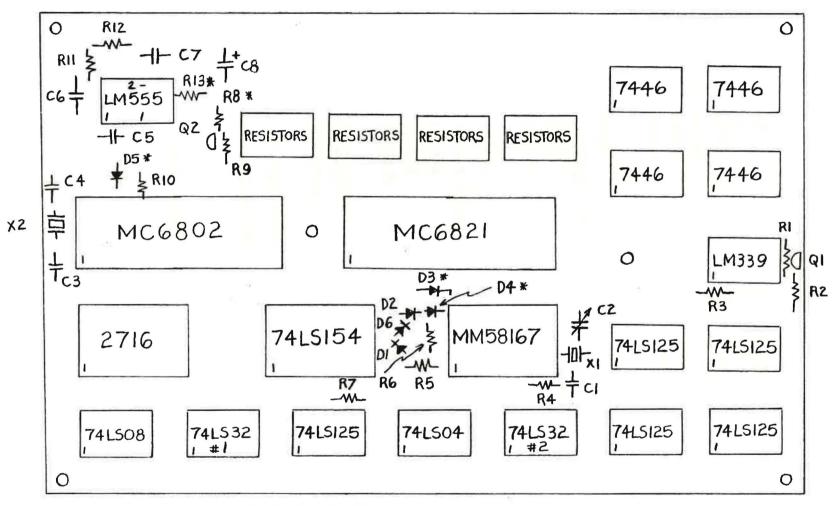

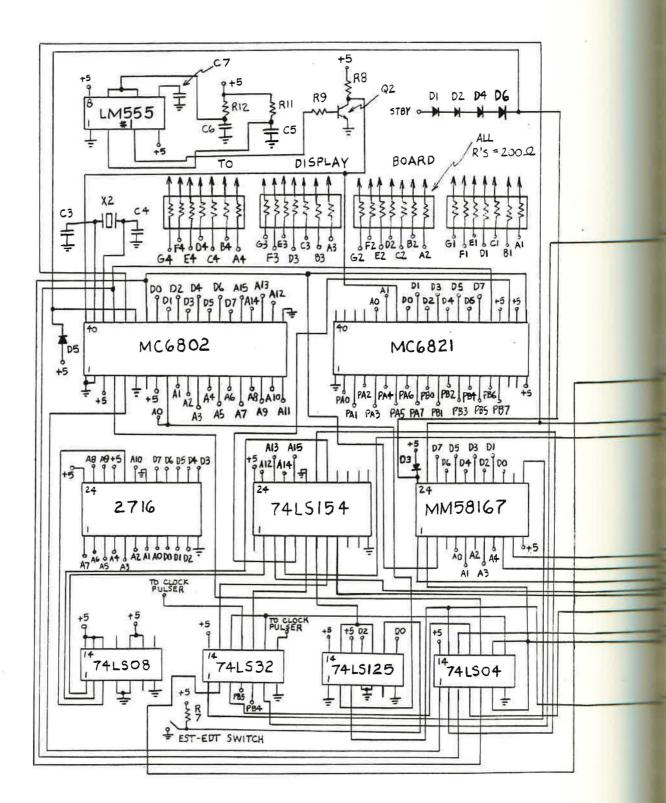

A block diagram of the system hardware is shown in FIGURE 6. A functional description of each block follows.

FIGURE 5 - New Master Clock

### 1. MC6802 Microprocessor

The microprocessor is the heart of the system, since it decides when to send pulses to the school clocks and how many to send. The 6802 is totally software compatible with the MC6800 microprocessor, but also features 128 bytes of on-chip RAM and an internal clock generating circuit.

During a power-down, the first 32 bytes of RAM can be maintained with very little power consumption from a standby source (batteries). This allows the school clock time to always be in RAM, so the microprocessor always "knows" the school clock time. For a more detailed description of the processor, the Motorola Microprocessor Manual should be consulted.

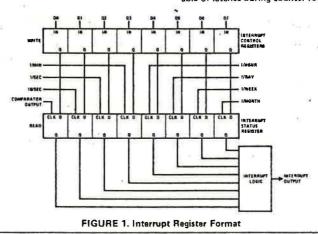

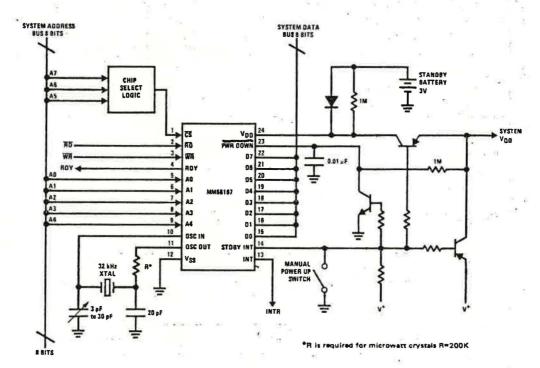

### 2. MM58167 Real-Time Clock

The MM58167 real-time clock can either be written to or read from by the microprocessor. A 32.768 KHz crystal is used as the clock's time base. The clock is microprocessor compatible and has eight data lines (the 6802 is an eight-bit processor) and five address lines to select among 24 internal registers. Time is kept in a BCD format, which is advantageous since WWV time frames are also given in a BCD format.

The 58167 also features a power-down mode that allows the chip to keep time even during a line-power failure, provided a standby power source is available. With the real time always available, and the school clock time always in RAM, the difference between the school clocks and

real-time clock can be computed when a power-down and subsequent power-up have occurred, and the school clocks can be updated. A full description of the MM58167 can be found in the data sheets in APPENDIX II.

#### 3. WWV Decoder

Operation of the WWV decoder is explained in Chapter IV of this thesis. The decoder is interfaced to the processor by four 74LS125 three-state buffers. The buffers are enabled by decoding logic when 3000H or 3001H is placed on the address bus. WWV time data can only be read by the microprocessor, whereas the real-time clock can be read from or written into. The end-of-frame 0.1 second pulse generated by the decoder is used as a hardware interrupt to the processor.

### 4. EST, EDT Switch

This feature allows the school clocks to adjust automatically to what amounts to a change in time zones every six months. This switch must be thrown manually once every six months to allow for the time change. WWV transmits UTC (Coordinated Universal Time), which is referenced to Greenwich, England. Data at the switch location (either four or five hours) is subtracted from the decoded time to obtain Eastern Daylight or Eastern Standard Time. In order for the clocks to adjust themselves, a valid WWV decode (see WWV routine in software section) must be received after the switch is thrown.

### 5. MC6821 PIA (Peripheral Interface Adapter)

The MC6821 PIA is used to latch and display the school clock time that is stored in RAM via four seven-segment displays. Since a BCD format requires 16 bits to represent a time and the PIA has 16 lines that can be configured as outputs, the 6821 is ideal for this application. The PIA output lines are used to drive four BCD to seven-segment decoders which, in turn, drive the four seven-segment displays.

### 6. 2716 EPROM (Erasable Programmable Read Only Memory)

The 2716 contains 2048 eight-bit-wide memory locations for storing the system software. A PROLOG programmer was used to program the EPROM. A single +5 volt power supply is required for operation of the EPROM.

### 7. Address Decoding

Since the microprocessor can only "communicate" with one external device at a time, address decoding is needed to assign each device a unique address. A 74LS154 four-to-sixteen-line decoder is used for this purpose. The four inputs to the chip are tied to the four most significant bits of the address bus (A12 - A15), which means that these four bits are completely decoded. If, for example, an address of 2000H is placed on the address bus, then output number two of the 74LS154 goes low (all outputs are active low), while all other outputs remain high and the real-time clock is addressed. A diagram of the address decoding scheme is shown in FIGURE 7.

### 8. Clock Pulser

The clock pulser hardware consists of two LM555's operating in the one-shot mode, an opto-isolator with an SCR output, an opto-isolator with a triac output, an SCR, and a triac. A diagram of the circuit is shown in FIGURE 8. When an address of 5000H is placed on the address bus, output #5 of a 74LS154 goes low and triggers 555 #1. When the output of the 555 is high, the LED in the opto-isolator turns the triac output on, which provides a path for gate current in triac #1. Triac #1 now allows current to flow through the inductive load, which is the relay coil in the master control box, thus closing the relay. The relay will remain closed for the time out period of the 555 (approximately 0.5 seconds). Under normal operation, location 5000H is addressed once each minute, but when the clocks are being advanced or synchronized, it is addressed once every two seconds.

Operation of the SCR circuit is almost identical to that of the triac circuit except that the SCR is only required to switch a DC voltage. The SCR switch is closed by addressing location 7000H and is closed from 00 - 49 minutes after the hour.

To protect the devices from false triggering due to line transients and inductive kickback, RC "snubber" networks are placed across the devices. These networks limit the rate of voltage rise (dV/dt) across the device and thus greatly reduce any C (dV/dt) charging current that

FIGURE 8 - Clock Pulser

might falsely trigger the device.

#### C. Master Clock Software

### 1. Addition and Subtraction of BCD Numbers

Since all times are represented in a BCD (binary coded decimal) format, a brief explanation of how these numbers are manipulated follows. Addition of two BCD numbers is accomplished by using the DAA (decimal adjust the A accumulator) instruction immediately after either the ABA (add A and B accumulators) or ADD A (add A accumulator to a memory location) instructions. BCD subtraction is performed using ten's complement addition. The ten's complement of the subtrahend is obtained by adding 66H (hexadecimal) to the subtrahend, complementing the result, and adding one. This result is added to the minuend to give the result of the subtraction. If there is an end carry generated by the ten's complement addition, then the minuend is greater than the subtrahend and the answer is the BCD difference between the two numbers. However, no end carry means that the true answer is the ten's complement of the result with a negative sign attached. If two equal BCD numbers are subtracted, the result is "positive zero" since an end carry is generated. The status of the carry bit in the microprocessor condition code register can therefore be used to test for a positive or negative result after a BCD subtraction.

### 2. Description of Software

The software for controlling the Speed School clocks is divided into 14 subprograms. A description of each subprogram follows.

- Initialization. The initialization program is a. executed every time a power-down and subsequent power-up occur. The first section of the program configures all 16 PIA lines as outputs and allows access to peripheral data registers A and B. The stack pointer is then initialized so that the processor will not get "lost" when jumping to and from the various subroutines. After initialization is completed, the processor determines if the power-up is the first by reading the first location in RAM. If the number in this location is 52H, then it is not the first power-up. If it is the first power-up, the MM58167 real-time clock and school clock RAM locations are set to 15:00, since this is the time that the school clocks are manually set to before the master clock is ever turned on. If the system has been working previously, then the "first power-up" sequence is skipped and, instead, the processor executes the reset subroutine.

- b. Reset Subroutine. During a power-down condition, standby power from batteries allows retention of the first 32 bytes of internal RAM in the 6802, where the school clock time is stored. The backup power also allows the MM58167 real-time clock to keep time during a line power failure. When power is restored, the reset routine will

calculate the difference between the school clocks and real-time clock, and send out the appropriate number of pulses to the school clocks to synchronize them with the real-time clock. Once the clocks are synchronized, the monitor routine is executed.

- waits for a change in the real-time clock minutes counter or a WWV decode. Both of these events will generate an interrupt to the processor. When the interrupt is generated, the processor will start executing an interrupt program at the address specified by the contents of memory locations FFF8H and FFF9H. When this program has been executed, the monitor routine will be returned to until another interrupt occurs.

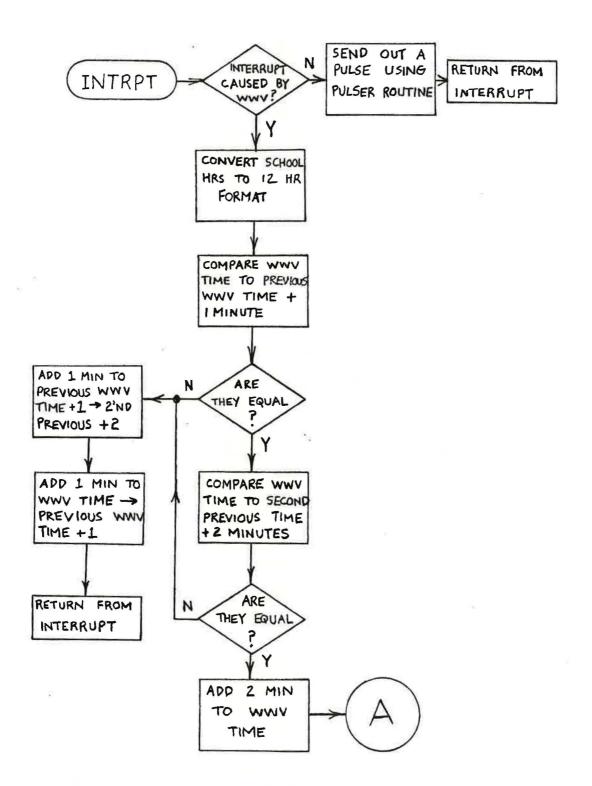

- d. Interrupt Program. At the end of each frame of WWV time code information, a 0.1 second pulse that is used as an interrupt pulse is generated by the decoding circuitry. Likewise, at the end of each minute, the real-time clock generates an interrupt signal. If a CLI (clear interrupt mask bit) instruction has been executed and an interrupt occurs, then the processor starts executing the interrupt program.

The interrupt program first determines if the real-time clock or the WWV decoder has generated the interrupt by reading the real-time clock interrupt status register. If bit three of the register is a "l", then the real-time clock has generated the interrupt. An interrupt

from the real-time clock instructs the processor to send out a pulse to the school clocks to advance them by one minute. Program control is then returned to the monitor routine. If, on the other hand, the WWV decoder generated the interrupt, then the WWV interrupt routine is serviced.

The WWV interrupt routine determines if the most recent decode is valid by comparing the time to the previous decode time plus one minute and then to the second previous decode time plus two minutes. If all three times are equal, then the most recent decoded time is assumed to be valid. If the three times are not equal, the frame is assumed to be invalid and one minute is added to the previous decode-time-plus-one-minute value, which is then stored in the second-previous-decode-plus-two location. Likewise, one minute is added to the most recent decode time and the result is stored in the previous decode-plus-one-minute location. The program is now set up for the next WWV interrupt.

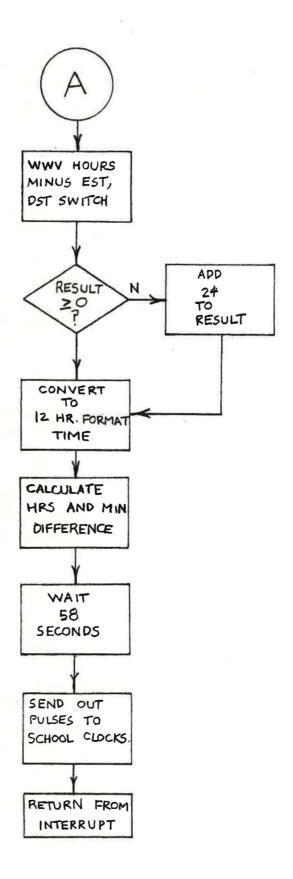

Due to the nature of the decoding circuitry and the WWV broadcast format, the actual local time when an interrupt occurs (assuming a valid decode) is the decoded time plus one minute, plus 1.15 seconds and minus four or five hours. These differences are accounted for by adding two minutes to a valid decode time and then subtracting four or five hours (depending on the position of the EST, EDT switch). This adjusted time is then used to determine the difference between the school clocks and the actual time. After this difference is determined, the program waits 58

seconds to send out the calculated number of pulses. When all pulses are sent, the school clock time is placed in the appropriate real-time clock locations and program control is returned to the monitor routine. This correction procedure assures that every time a valid WWV time is received, the real-time clock is reset accordingly.

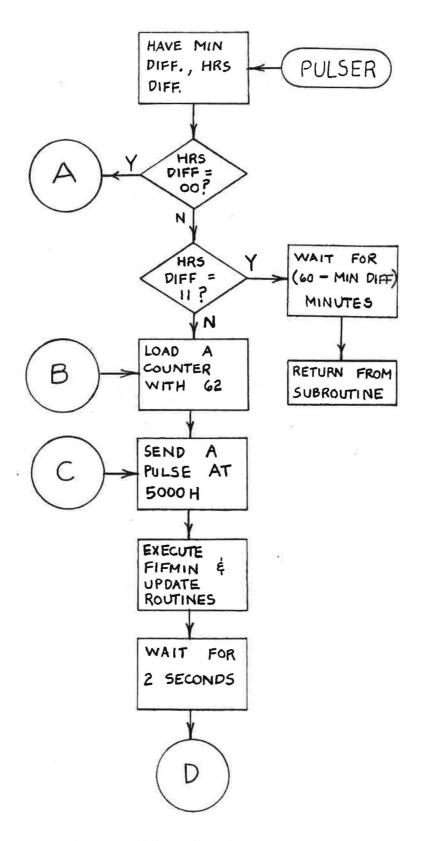

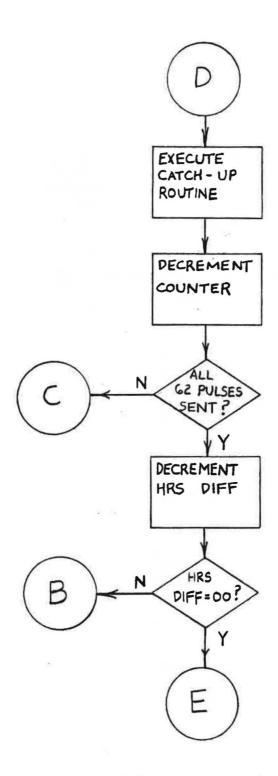

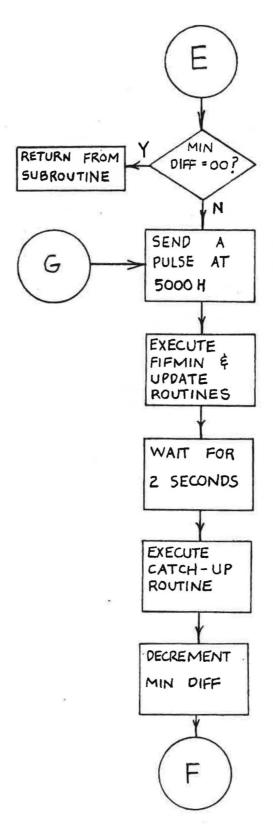

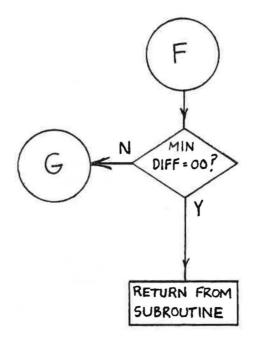

- e. <u>Pulser Routine</u>. The pulser routine sends out the number of pulses necessary to synchronize the school clocks with either WWV or the real-time clock at the rate of one pulse every two seconds. If the school clocks need to be advanced by more than eleven hours, the pulser routine will wait for the real-time clock or WWV to catch up. If the hours difference is less than eleven, 62 pulses are sent for each hour of difference. The extra pulses account for the two minute delay inherent in sending 60 pulses. The pulser routine also controls the self-correcting feature of the school clocks by executing the FIFMIN (fifty minute switch) and CATUP (catch-up) subroutines.

- f. <u>Second Delay Routine</u>. The second delay routine generates a time delay of approximately one second, since delays of integer multiples of one second are needed for various other subroutines.

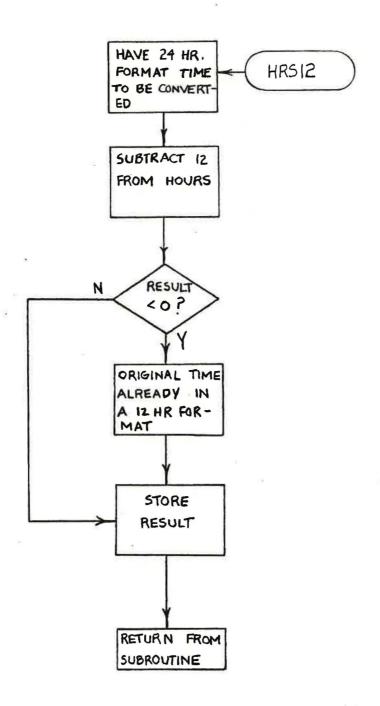

- g. Twelve-Hour Format Routine. The 12-hour format routine converts a 24-hour format time to a 12-hour format time by subtracting 12 hours from the 24-hour format time. If the result is positive, then the computed time is the correct 12-hour format time. If the result is negative,

then the original time was already in a 12-hour format.

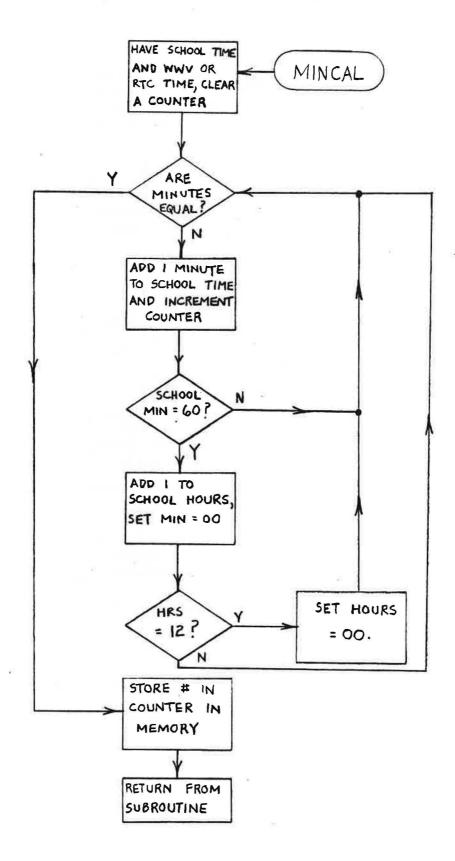

- h. Minutes Difference Routine. The minutes difference routine determines the number of minutes pulses that must be sent to the school clocks so that the school clock minutes and WWV or real-time clock minutes are the same. This is accomplished by counting the number of times the school clock minutes must be incremented to equal the WWV or real-time clock minutes. If the school clock minutes reach 60, then the school clock hours are incremented to prepare for the hours difference calculation, the minutes are set equal to zero, and the process continues. The result is a true binary number, not a BCD number.

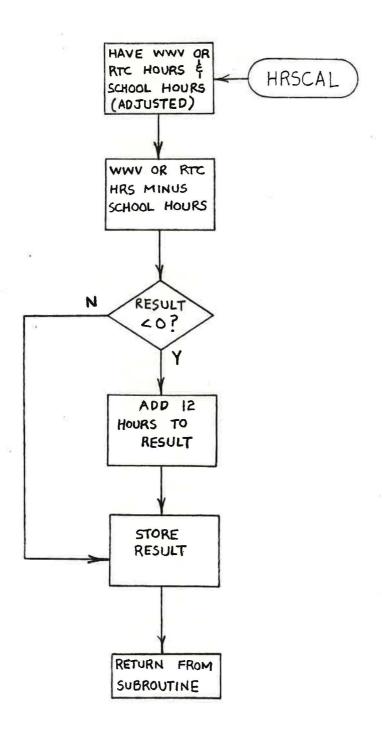

- i. Hours Difference Routine. This subroutine calculates the number of hours that the school clocks must be advanced to equal the WWV or real-time-clock time. This is done by subtracting the 12-hour format adjusted (refer to minutes difference routine) school-clock time from the 12-hour WWV or real-time clock time. If the result is positive, then the result is the hours difference, but if the result is negative, then the hours difference is the result plus 12.

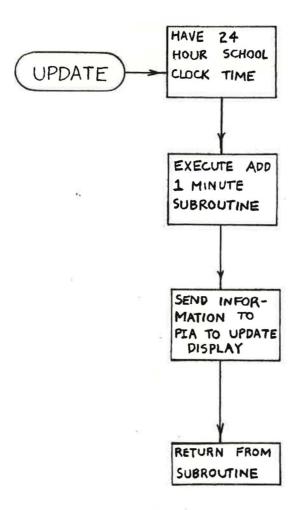

- j. <u>Update Routine</u>. The update routine adds one minute to the school-clock 24-hour format time and displays this time on the seven-segment displays by writing the time to the PIA. This routine is executed immediately after a pulse is sent to the school clocks.

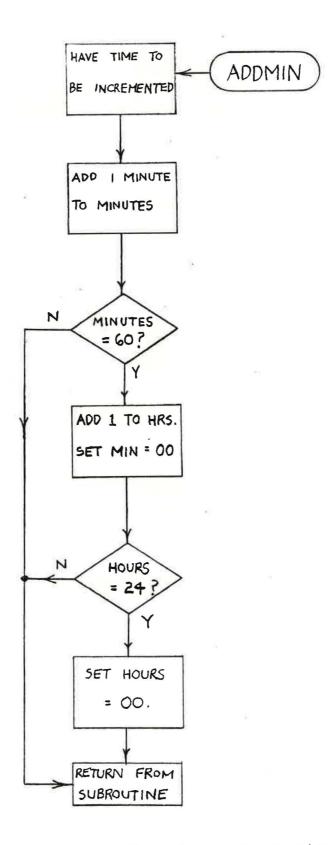

- k. Add One Minute to a Time Routine. This routine

adds one minute to a 24-hour format time. If the minutes are equal to 60 after addition of one minute, then the hours are incremented and the minutes are reset to zero. If the hours are equal to 24 after being incremented, they are reset to zero.

- 1. Fifty-Minute Switch Routine. This routine determines if the school-clock minutes are equal to 00 to 49 minutes. If they are, a switch is closed by writing to location 7000H.

- m. Catch-up Routine. The catch-up routine determines if the school-clock minutes are equal to 59. If they are, a switch at location 5000H is opened and closed ten times by writing to this location ten times at two second intervals.

- n. Short Delay Routine. This routine is used to provide a short delay between the time a switch at 5000H closes and the time a switch at 7000H closes.

#### IV. WWV DECODER

# A. Background On Time Services

Radio station WWV is operated by the National Bureau of Standards and broadcasts from Fort Collins, Colorado on carrier frequencies of 2.5, 5, 10, 15, and 20 MHz. Among the services offered by WWV are weather announcements, voice time announcements, standard time intervals, standard audio frequencies, and a BCD (binary coded decimal) time code. The entire WWV broadcast format is shown in FIGURE 9.

Of particular interest in this thesis is the BCD time code, which is continuously broadcast on a 100 Hz subcarrier with a modified version of the IRIG-H time code format. With the IRIG-H, a binary zero is represented as 20 cycles of 100 Hz amplitude modulation (0.2 seconds), a binary one is 50 cycles of 100 Hz amplitude modulation (0.5 seconds), and a position marker (used for synchronization purposes) is 80 cycles of 100 Hz amplitude modulation (0.8 seconds). However, WWV also transmits a five millisecond burst of 1000 Hz (which sounds like the tick of a clock) to mark the beginning of each second. burst has a guardband around it (see FIGURE 10) that deletes the first 30 milliseconds of the time code so, in this modified version, a binary zero is 17 cycles of 100 Hz AM, a binary one is 47 cycles of 100 Hz AM, and a position marker is 77 cycles of 100 Hz AM. If the 100 Hz subcarrier is

#### **WWV BROADCAST FORMAT** VIA TELEPHONE: (303) 499-7111 (NOT A TOLL-FREE NUMBER) STATION ID 440 Hz 1-HOUR MARK NBS RESERVED SPECIAL STORM INFORMATION SILENT EXCEPT TICK LOCATION UTC VOICE ANNOUNCEMENT 40'40'49.0"N; 105'02'27.0"W NO AUDIO 60 STANDARD BROADCAST FREQUENCIES TONE AND RADIATED POWER 2.5 MHz - 2.5 kW 10 MHz - 10 kW 5 MHz - 10 kW 600 Hz TONE 20 MHz - 2.5 kW UT 1 CORRECTIONS OMEGA FOR ADDITIONAL INFORMATION CONTACT REPORTS NBS RADIO STATION WWV 2000 EAST COUNTY RD 58 GEO ALERTS FT. COLLINS, CO 80524 (303) 484-2372 CODE ON 100 HE SUS BEGINNING OF EACH HOUR IS IDENTIFIED BY 0.8-SECOND LONG, 1500-Hz TONE. BEGINNING OF EACH MINUTE IS IDENTIFIED BY STATION ID-0.8-SECOND LONG, 1000-Hz TONE.

FIGURE 9 - WWV Broadcast Format (see Ref. 2)

THE 29th & 59th SECOND PULSE OF EACH MINUTE IS OMITTED.

FIGURE 10 - WWV Guardband (see Ref. 3)

demodulated, the rectangular pulse train shown in FIGURE 11 is obtained. The beginning of each one minute frame is denoted by a 1.03 second hole in the code during which no pulse is transmitted. The positive-going edges of consecutive pulses are spaced exactly one second apart, but are 30 milliseconds late with respect to the actual time due to the guardband around the five millisecond 1000 Hz burst. By decoding the proper sequence of pulses, hours, minutes, and day of year information can be recovered.

# B. Decoding Circuitry

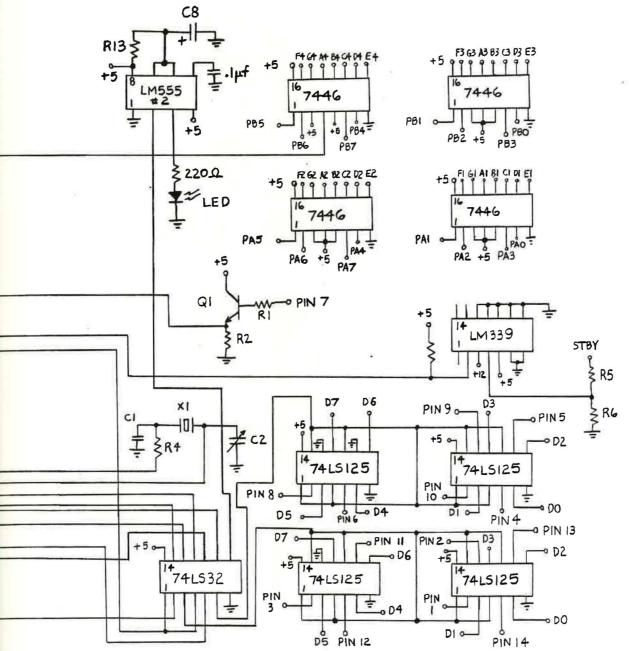

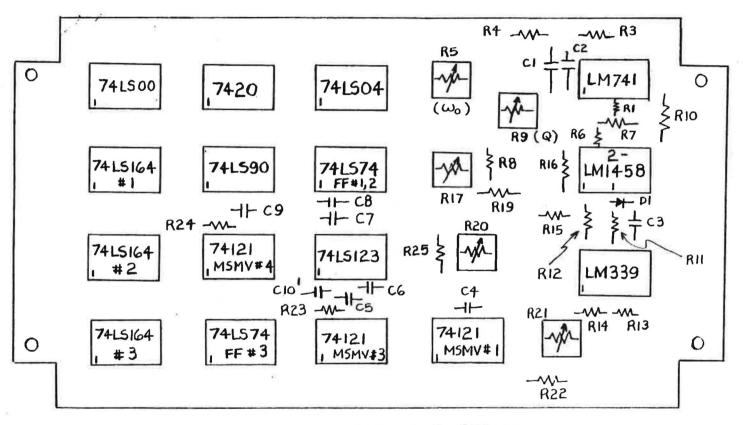

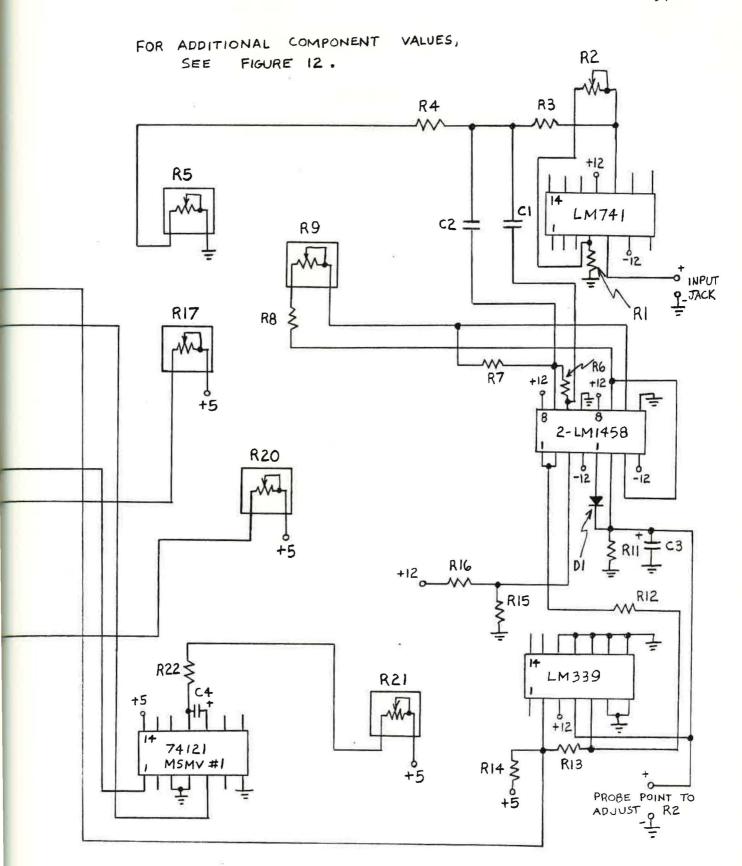

The circuitry used to reconstruct the rectangular pulse train from the 100 Hz subcarrier is shown in FIGURE Recovered audio (containing the 100 Hz code) at the output of the detector of the receiver being used is amplified and applied to the input of an active bandpass filter with a center frequency of 100 Hz and a Q of 10. This filter attenuates unwanted frequencies such as the 500 or 600 Hz audio tones and voice frequencies, but allows the 100 Hz subcarrier to be passed unattenuated. The center frequency ( $\omega_0$ ) of the filter is adjusted by varying potentiometer R5, while the Q is adjusted independently of  $\omega_{_{

m O}}$ by varying potentiometer R9. 4 The output of the bandpass filter is then applied to the input of an envelope detector that uses an operational amplifier to eliminate the forward voltage drop of the detector diode. 5 FIGURE 13 shows input and corresponding output waveforms for the envelope

FIGURE 11 - WWV Time Code (see Ref. 6)

FIGURE 12 - Analog Decoding Circuitry

A MANAGEMENT OF THE PROPERTY OF THE PROPERTY AND THE PROP

FIGURE 13 - Envelope Detector

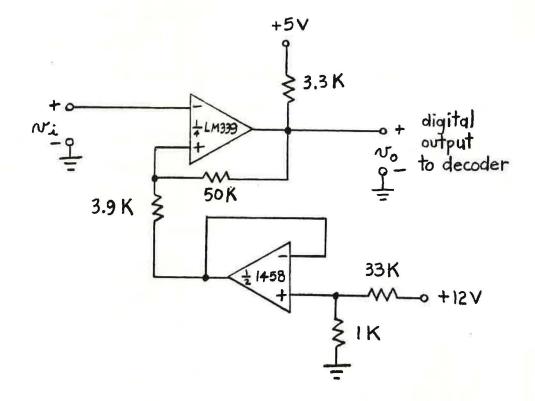

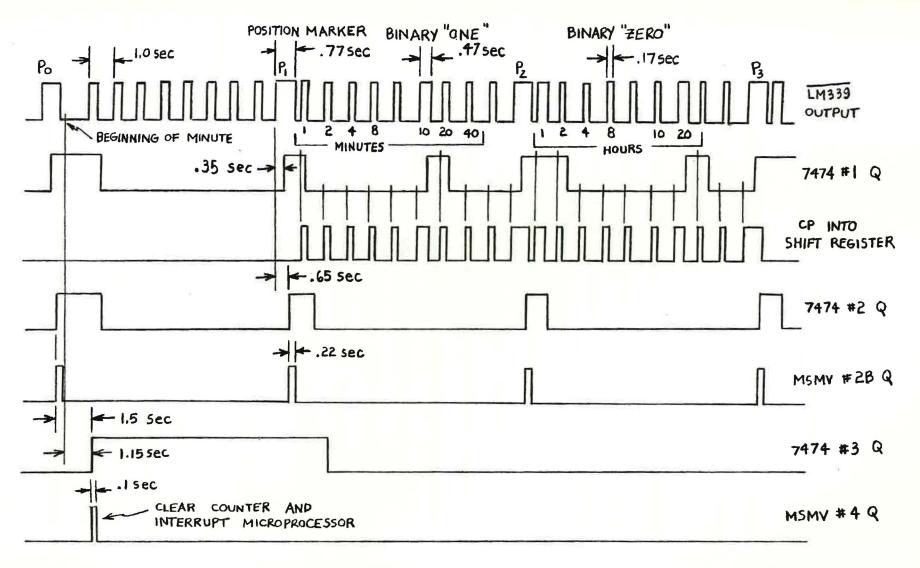

detector. The low-level output (approximately one volt) of the detector is then converted to standard TTL levels using a Schmitt trigger. FIGURE 14 shows the transfer characteristic of the Schmitt trigger. In order to get the proper level input to the Schmitt trigger, potentiometer R2 (see FIGURE 12) can be adjusted without affecting the rest of the circuit. The output of the Schmitt trigger is the logical complement of the BCD time code.

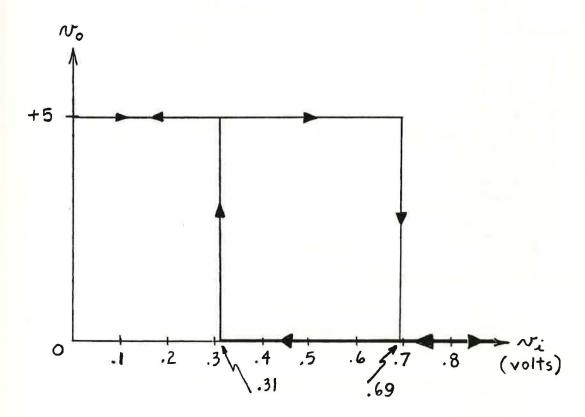

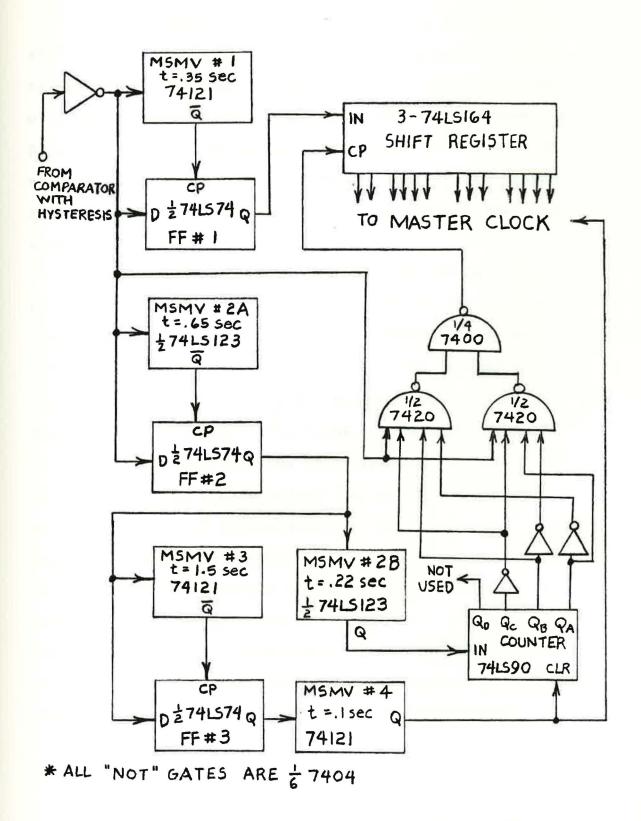

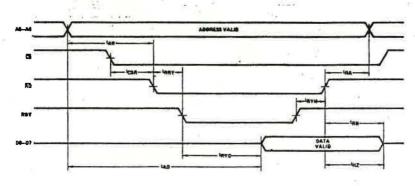

Decoding of the BCD time code is accomplished with the circuit shown in FIGURE 15. The Schmitt trigger output is inverted (to give the time code in its uncomplemented state) and applied to the inputs of positive edge triggered monostables and flip-flops. MSMV (monostable multivibrator) #1 and FF (flip-flop) #1 form a "1-0" detector, while MSMV #2A and FF #2 form a position marker detector. Upon a positive edge (corresponding to the beginning of each second), both monostables are triggered and time out. the end of each respective time out period (t = 0.35 sec. or 0.65 sec.), the  $\overline{Q}$  outputs of the monostables supply a positive edge to the clock inputs of the D flip-flops, which latch whatever is at the input at that instant. MSMV #3 and 4 and FF #3 are needed to detect the beginning of each minute, which is signified by a position marker followed by a 1.03 second period during which no pulse is transmitted. When this occurs, a pulse that resets the counter (74LS90) is generated.

FIGURE 14 - Schmitt Trigger Characteristics

FIGURE 15 - Digital Decoding Block Diagram

The counter is used to supply clock pulses to the shift register only during the interval between position markers Pl and P3 (see FIGURES 11 and 16) when hours and minutes information is transmitted. MSMV #2B reduces the pulse length into the counter from one or two seconds to .22 seconds, so that no bits of data are lost. Three 74LS164 shift registers are used to convert the serial input code to a parallel output.

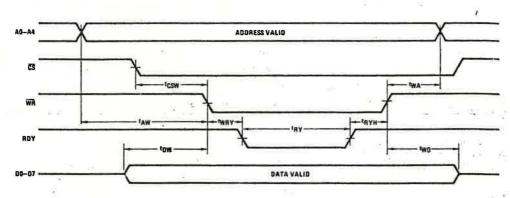

Due to the method of decoding and the WWV broadcast format, the decoded time will be behind the actual time. The reasons for this are most easily understood by examining FIGURES 11 and 16. From FIGURE 11, it can be seen that the time transmitted during the one minute frame is actually the time at the beginning of the frame. This means that the information latched into the shift register at the end of the minute is one minute behind the actual time. An additional error of approximately 1.15 seconds is incurred due to the method of decoding. As can be seen from FIGURE 16, the pulse that strobes the latches is generated 1.15 seconds after the beginning of the minute. Both of these sources of error are unimportant, since the decoder will be interfaced to a microprocessor that will easily account for such errors (see "Interrupt Routine" in CHAPTER III).

FIGURE 16 - Timing Diagram

#### V. CONCLUSIONS AND RECOMMENDATIONS

The new master clock and WWV decoder were built and worked as originally planned. There are, however, several areas for improvement that should be mentioned.

The WWV receiver uses a simple half-wave dipole antenna that is designed for reception of 15.0 MHz only. While it is felt that this arrangement provides adequate reception, a more broadband antenna would allow for better reception of the 5.0 and 10.0 MHz signals that the receiver is capable of receiving. To change the reception frequency, buttons on the presently installed receiver must be pushed manually. Receivers that automatically switch to the strongest carrier signal are commercially available and would be nice to have, but such a receiver might be too expensive to be practical. None of the above modifications would necessitate disabling the master clock at any time.

The real-time clock chip (MM58167) also contains a calendar that could be used for some specialized functions such as eliminating the EST/EDT switch or even ringing the bells on days and times that could be programmed into the EPROM now used to store the master clock software. The only disadvantage to undertaking such projects is that the master clock would have to be disabled while making any modifications.

#### REFERENCES

- 1. Ramshaw, R. S., <u>Power Electronics</u>, Chapman and Hall, London, 1973, pp. 37-39.

- 2. Howe, S. L., NBS Time and Frequency Dissemination

Services, NBS Special Publication 432, U. S. Government

Printing Office, Washington, DC, 1979, p. 2.

- 3. Ibid., p. 3.

- 4. Graeme, J. B., Operational Amplifiers, Design and Application, McGraw-Hill, 1971, pp. 293-295.

- 5. Schilling, D. L., Belove, C., Electronic Circuits, 2nd ed., McGraw-Hill, 1979, pp. 373-374.

- 6. Howe, S. L., p. 14.

### BIBLIOGRAPHY

- Graeme, J. G., Operational Amplifiers, Design and Applications, McGraw-Hill, 1971.

- Howe, S. L., NBS Time and Frequency Dissemination Services, NBS Special Publication 432, U. S. Government Printing Office, Washington, DC., 1979.

- Kamas, G., Howe, S. L., <u>Time and Frequency Users Manual</u>, NBS Special Publication 559, U. S. Government Printing Office, Washington, DC., 1979.

- Motorola, Inc., Microprocessor Data Manual, 1981.

- National Semiconductor Corp., MOS/LSI Data Book, 1980.

- Ramshaw, R. S., <u>Power Electronics</u>, Chapman and Hall, London, 1973.

- Schilling, D. L., Belove, C., Electronic Circuits, 2nd ed., McGraw-Hill, New York, 1979.

- Texas Instruments, Inc., The TTL Data Book for Design Engineers, 2nd ed., 1976.

# APPENDIX I

MASTER CLOCK OPERATION PROCEDURE AND MASTER CLOCK AND WWV DECODER DISASSEMBLY GUIDE

#### OPERATING PROCEDURE

# First Power-Up Procedure

This procedure must be performed any time the master clock display time and school clock time do not match. All clocks must read within ten minutes of 3:00. This is accomplished by connecting normally open switches from wire 1 to wire 2 (switch #1) and from wire 4 to wire 5 (switch #2) (see FIGURE 17). Switch #1 should be opened and closed 70 times (0.5 second closed, 1.5 seconds open each time) while switch #2 remains open. All clocks should now read one minute before the hour. To advance to the next hour, close switch #2 and open and close switch #1 six times (same duty cycle as before). Now open switch #2, and then open and close switch #1 70 times. The clocks should now read one minute before the hour. Keep advancing to the next hour until the clocks read 2:59. If any clocks read, say, 1:59 or 3:59 while the majority of the others read 2:59, the clocks with erroneous readings must be manually advanced to read 2:59.

# System Connections

When making connections, the power supply and WWV receiver should be OFF and UNPLUGGED.

Set the EST-DST switch on the master clock to the proper position.

FIGURE 17 - Clock Advancement Connections

- 2. Using banana leads, connect the power supply terminals to the corresponding banana jacks on the master clock and WWV decoder. BE CAREFUL not to connect the -12V or +12V supplies to the +5V terminal on the master clock.

- 3. Connect the DIP header from the master clock to the socket on the WWV decoder box. Turn the GAIN ADJUST knob on the decoder fully counterclockwise.

- 4. Connect the phone plug from the WWV receiver to the phone jack on the decoder.

- 5. Connect the labeled wires from the master control box to the corresponding terminals on the master clock terminal strip.

- 6. Connect the antenna to the WWV receiver.

- 7. Plug the line cord of the power supply into a wall outlet.

- 8. Turn the power supply on by flipping the switch on the supply to the "on" position at exactly 3:00 PM. The system is now operational.

- 9. Connect the negative terminal of the standby battery to the GND terminal on the power supply and then connect the positive terminal of the battery to the STBY terminal on the supply.

10. Turn on the shortwave receiver and tune it to WWV at 15 MHz. The volume setting is unimportant, since the input to the decoder is taken before the volume control. When a clear, non-fading signal is present, probe the terminal of the decoder adjacent to the input jack with an oscilloscope. The GAIN CONTROL knob on the decoder should be adjusted so that the signal at this point resembles FIGURE 18. No further adjustment should be necessary unless a different receiver is used in the future.

If something happens to the receiver or decoder, the decoder can be disconnected from the master clock at any time without affecting master clock operation.

The system is now fully operational and should not require any further servicing other than replacing the standby battery once a year. To replace the battery, reverse the procedure of step 9 to remove the old one and install the new battery (refer to step 9).

PULSE WIDTHS ≈ .2, .5, OR .8 SEC

ADJUST GAIN CONTROL FOR PULSE HEIGHT OF ≈ 1.0 VOLT

FIGURE 18 - Proper Decoder Waveform

### DISASSEMBLY GUIDE

# Master Clock

- The master clock must be disconnected from any power source during disassembly.

- Remove the six Phillips screws from the top panel of the master clock.

- 3. Remove the two screws that hold the display in place.

- 4. Remove the two screws that hold the EST-DST switch in place. The top cover may now be removed.

- 5. Remove the four banana jacks from the cabinet.

- 6. Unsolder the four wires going from the main board to the smaller board in the left rear of the cabinet.

- Remove the six screws that hold the main board in place.

- 8. Pull up on the left side of the board and, at the same time, feed the DIP jumper through the grommet enough to allow the board to be turned over, so that the solder connections are accessible.

- 9. To remove the smaller board, unsolder the four wires going to the triac and SCR, and then remove the two screws that hold the board in place.

- 10. To install the board(s), reverse the above procedure.

# WWV Decoder

The WWV decoder must be disconnected from any power source during disassembly.

- 2. Remove the four screws from the top of the decoder.

- 3. Remove the four banana jacks from the cabinet.

- 4. Remove the two screws that hold the socket on the side of the decoder in place and push the socket toward the inside of the cabinet.

- 5. Unscrew the input jack retainer and push the jack toward the center of the cabinet.

- 6. Remove the screw next to the input jack by unscrewing it from the cabinet.

- 7. Remove the five nuts from the bottom of the box and pull the board from the cabinet.

- 8. To reinstall the board, reverse the above procedure.

# APPENDIX II MM58167 AND MC6802 DATA SHEETS

\*MM58167 data sheets were taken from 1980 National Semiconductor MOS/LSI Databook.

\*\*MC6802 data sheets were taken from 1980 Motorola

Microprocessor Manual.

# **Electronic Data Processing**

# MM58167 Microprocessor Compatible Real Time Clock

# General Description

The MM58167 is a low threshold metal-gate CMOS circuit that functions as a real time clock calendar in bus-oriented microprocessor systems. The device includes an addressable counter, addressable latch for alarm-type functions, and 2 interrupt outputs. A power-down input allows the chip to be disabled from the outside world for standby low power operation. The time base is generated from a 32,768 Hz crystal-controlled oscillator.

#### **Features**

- Microprocessor compatible

- Thousandths of seconds, hundredths of seconds, tenths of seconds, seconds, minutes, hours, day of the week, day of the month, and month counters with corresponding latches for alarm-type functions

- Interrupt output (maskable) with 8 possible interrupt signals:

- Latch and counter comparison

- · Every tenth of a second

- Every second

- Every minute

- Every hourEvery day

- Every week

- Every month

- Power-down mode that disables all outputs except for an interrupt output that occurs on a counter latch comparison. This is not the same as the maskable interrupt output

- Don't care states in the latches

- Status bit to indicate clock rollover during a read

32,768 Hz crystal reference, with only the input

- tuning capacitor and load capacitor needed externally

- s Four year calendar

# **Functional Description**

The MM58167 is a microprocessor oriented real time clock. The circuit includes addressable real time counters and addressable latches, each for thousandths of seconds through months. The counter and latch are divided into bytes of 4 bits each. When addressed, 2 bytes will appear on the data I/O bus. The data, in binary coded decimal, can be transferred to and from the counters via the data I/O bus so that each set of 2 bytes (1 word) can be accessed independently as grouped in Table I.

If either of the bytes in the above 8-bit counter words do not legally reach 4-bit lengths (e.g., day of the week uses only the 3 least significant bits) the unused bits will be unrecognized during a write and held at VSS during a read. If any illegal data is entered into the counters during a write cycle, it may take up to 4 clocks (4 months in the case of the month counter) to restore legal BCD data to the counter during normal counting. The latches will read and write all 4 bits per byte. Each of the counter and latch words can be reset with the appropriate address and data inputs. The counter reset is a write function. The latches can be programmed to compare with the counters at all times by writing 1's into the 2 most significant bits of each latch, thus establishing a don't care state in the latch. The don't care state is programmable on the byte level, i.e., tens of hours can contain a don't care state, yet unit hours can contain a valid code necessary for a comparison.

### Connection Diagram

#### Dual-In-Line Package

Order Number MM58167N See Package 22

157.8

# **Absolute Maximum Ratings**

Voltage at All Inputs and Outputs Operating Temperature Storage Temperature V<sub>DD</sub> + 0.3 to V<sub>SS</sub> - 0.3 -25°C to +85°C, -65°C to +150°C

V<sub>DD</sub> - V<sub>SS</sub> Lead Temperature (Soldering, 10 seconds)

. 300°C

# Electrical Characteristics TA = -25°C to +85°C, VSS = 0V

| PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CONDITIONS                                        | MIN     | TYP     | MAX         | UNITS |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|---------|---------|-------------|-------|

| Supply Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                   |         |         |             |       |

| V <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Outputs Enabled                                   | 4.0     |         | 5.5         | ١     |

| V <sub>DD</sub> (Note 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Power Down Mode                                   | 2.0     | **      | 5.5         | . \   |

| Supply Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 100                                               |         |         | * * * * * * | 1     |

| IDD, Static                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Outputs TRI-STATE,                                |         |         | 10          | μ     |

| 194                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | f <sub>IN</sub> = DC, V <sub>DD</sub> = 5.5V      | 1 2     | 100 100 |             |       |

| IDD, Dynamic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Outputs TRI-STATE,                                |         | _       | 20          | ш     |

| Control of the contro | fin = 32 kHz, VDD = 5.5V,                         |         | - 2-    |             |       |

| ** En                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | VIH ≥ VDD - 0.3V, VIL ≤ VSS + 0.3V                |         | 10      |             | 46 40 |