$\odot$  Copyright by Chien-Wei Li, 2006

# ON EXTRACTING COARSE-GRAINED FUNCTION PARALLELISM FROM C PROGRAMS

#### BY

#### CHIEN-WEI LI

B.S., National Taiwan University, 1990 M.S., National Taiwan University, 1992

#### DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science in the Graduate College of the University of Illinois at Urbana-Champaign, 2006

Urbana, Illinois

To my family, my teachers, my friends, and people who helped me.

#### ACKNOWLEDGMENTS

I would like to thank my advisor Professor Wen-mei Hwu for giving me this opportunity to learn how to solve important problems. He teaches me to see the big picture, as well as to pay attention to the details. I appreciate his patience in correcting my errors in speaking, writing, and thinking. I feel grateful for his generosity in financial support. He has done everything a good teacher could do, however, I am not capable enough to fully carry out his vision. Efficiently mapping complex applications onto parallel machines is a fascinating problem to me. Hope that I can work on this for the rest of my life, based on what I've learned from him.

I would like to thank Professors David Padua, Vikram Adve and Mark Hesagawa-Johnson for their courtesy of being my thesis committee members. Their experiences, comments, and critics broaden my knowledge and make me understand the problem more deeply. I would like to thank Professors Nick Carter, Matt Frank, and Steve Lumetta for their feedback on my work.

Although they may not know me, I would still like to thank the professors who taught those interesting and helpful courses that I took at UIUC. Especially, I would like to thank Professor Benjamin Wah, visiting Professor Yao-Jen Chang, and late Professor Michael Faiman for their personal instruction and assistance when I first came to America. I would like to thank my M.S. thesis advisor Professor Jie-Yong Juang and my other teachers in Taiwan, from K to 18, who really make my life at UIUC much easier.

I would like to thank my officemates Hong-Seok Kim and Dan Burke. I learned a lot from Hong-Seok about pointer analysis and program analysis. Many ideas in my research are inspired during our discussion. I also obtained a lot of hardware knowledge from Dan. I would like to thank my colleagues, Ben-chung Cheng, Hong-Seok Kim, and Erik Nystrom for their pointer analysis work; Robert Kidd, Hong-Seok Kim, Tahir Mobashir, Erik Nystrom, James Player, Shane Ryoo, John Sias, and Ian Steiner for their Pcode enhancement work. Especially, Bob and John made a lot of effort in system administration and in perfecting the IMPACT compiler. I also appreciate the help of other IMPACT colleagues, Ron Barnes, Kevin Cernekee, Marie Conte, Hillery Hunter, Geoff Kent, Matt Merten, Chris Rodriguez, Andy Schuh, Chris Shannon, Sain Ueng, and Le-chun Wu. Especially, Le-chun and Ben-chung have been helping me since we met in Taiwan.

I would like to thank the staffs of the IMPACT group, Sabrina Hwu, Marie-Pierre Lassiva-Moulin and Xiaolin Liu, and the staffs of Coordinated Science Laboratory and Computer Science department. Especially, Marie-Pierre helps me a lot for the deposit of this dissertation. I really appreciate it.

I would like to thank the friends I made at Rockwell, Conexant and Mindspeed, especially my mentor Dr. Kumar Ganapathy, for their help and sharing experience.

This research is funded by the Semiconductor Research Corporation and by the Gigascale Systems Research Center.

Not to have an Acknowledgement longer than the other chapters, I'll just stop here. Finally, I would like to thank my other friends and my family for taking care of me.

## TABLE OF CONTENTS

|     |         | Tables                        | _        |

|-----|---------|-------------------------------|----------|

| Lis | St OI I | Figures                       | ix       |

| 1   | Intro   | oduction                      | 1        |

|     | 1.1     | Technology Trend              | 2        |

|     | 1.2     | Hardware Trend                | 4        |

|     | 1.3     | Application Trend             | 5        |

|     | 1.4     | Exploiting Parallelism        | 7        |

|     | 1.5     | Improving Design Productivity | 8        |

| 2   | Prev    | vious Work                    | 11       |

|     | 2.1     |                               | 11       |

|     |         |                               | 12       |

|     |         | O I                           | 12       |

|     |         | O I                           | <br>14   |

|     | 2.2     | - , , , , -                   | -<br>15  |

|     | 2.3     |                               | 17       |

| 3   | Thes    | sis Overview                  | 21       |

| •   | 3.1     |                               | 21       |

|     | 3.2     |                               | 26       |

|     | 3.3     | 0                             | -<br>29  |

|     | 0.0     | 0                             | -°<br>29 |

|     |         | 0                             | 31       |

|     |         | v O                           | 32       |

|     | 3.4     | e e                           | 39       |

|     |         |                               |          |

| 4   | Sym     |                               | 12       |

|     | 4.1     |                               | 12       |

|     | 4.2     | Induction Variable Detection  | 14       |

|     | 4.3     | SSA Extension                 | 46       |

| 5   | Prog    | gram Region Hierarchy         | 50       |

|     | 5.1     |                               | 50       |

|     | 5.2     |                               | 53       |

|     | 5.3     |                               | 56       |

|     | 5.4     |                               | 57       |

| 6  | $\operatorname{Exp}$ | osed Memory Access Summarization                 | 59  |

|----|----------------------|--------------------------------------------------|-----|

|    | 6.1                  | Memory Access Descriptor                         | 59  |

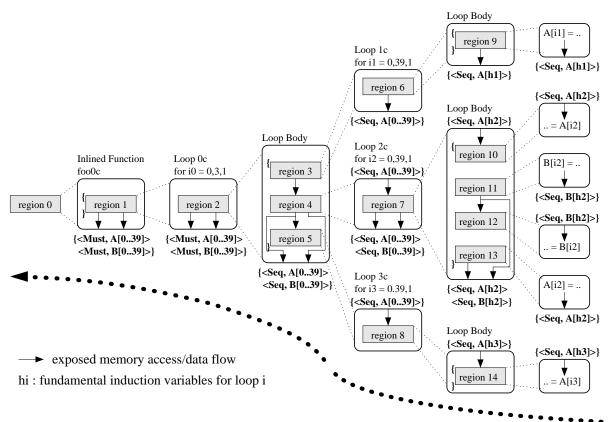

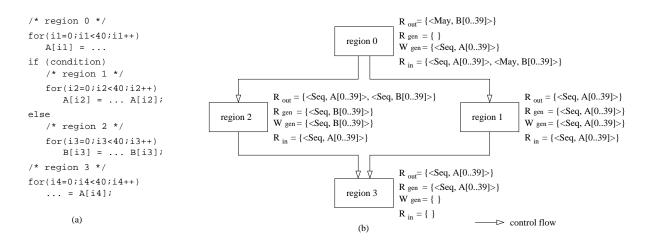

|    | 6.2                  | Bottom-up Summarization Process                  | 64  |

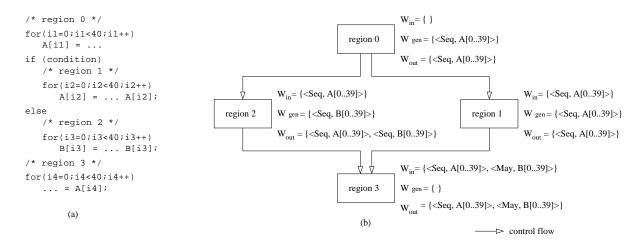

|    |                      | 6.2.1 An Example                                 | 67  |

|    |                      | 6.2.2 Finding Exposed Reads                      | 71  |

|    |                      | 6.2.3 Finding Exposed Writes                     | 76  |

|    |                      | 6.2.4 Memory Access Descriptor Operations        | 81  |

|    | 6.3                  | Related Work                                     | 100 |

| 7  | Proc                 | ducer-Consumer Relation Analysis                 | 105 |

|    | 7.1                  | Bottom-up Phase                                  | 105 |

|    | 7.2                  | Top-down Phase                                   | 107 |

|    | 7.3                  | Related Work                                     | 110 |

| 8  | Prot                 | totyping and Experiment Result                   | 111 |

|    | 8.1                  | Modification of Benchmark Programs               | 111 |

|    | 8.2                  | Verification and Visualization                   | 112 |

|    | 8.3                  | Efficiency                                       | 115 |

|    | 8.4                  | Effectiveness                                    | 116 |

| 9  | Con                  | clusion and Future Work                          | 129 |

|    | 9.1                  | Conclusion                                       | 129 |

|    | 9.2                  | Future Work                                      | 133 |

|    |                      | 9.2.1 Inter-procedural Memory Data-flow Analysis | 133 |

|    |                      | 9.2.2 Improving Versatility and Effectiveness    | 139 |

|    |                      | 9.2.3 Evaluation                                 | 140 |

| RI | EFER                 | RENCES                                           | 143 |

| ΔΙ | ТТНС                 | OR'S BIOGRAPHY                                   | 155 |

## LIST OF TABLES

| 8.1 | Breakdown of the execution time of the prototype memory data-flow analysis |     |  |

|-----|----------------------------------------------------------------------------|-----|--|

|     | system                                                                     | 114 |  |

| 8.2 | Breakdown of the type of MADs for exposed reads                            | 123 |  |

| 8.3 | Breakdown of the type of MADs for exposed writes                           | 123 |  |

| 8.4 | Breakdown of the percentages of the causes of May-type MAD                 | 124 |  |

| 8.5 | Breakdown of the percentages of the causes of <i>Doomed-type</i> MAD       | 126 |  |

## LIST OF FIGURES

| 1.1<br>1.2                              | The block diagram and data-flow of the post-filter of G.724 decoder The challenge of the design methodology community                                                                                                                                                               | 10                               |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 2.1                                     | A unified view of exploiting parallelism and boosting productivity                                                                                                                                                                                                                  | 20                               |

| 3.1<br>3.2<br>3.3<br>3.4                | The position of this work with in mapping applications onto multi-core architectures                                                                                                                                                                                                | 22<br>25<br>28<br>29             |

| 3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10 | Example coarse-grained functions of subroutine cans                                                                                                                                                                                                                                 | 30<br>33<br>34<br>37<br>39<br>41 |

| 4.1<br>4.2<br>4.3                       | Example SSA form nd value flow graph                                                                                                                                                                                                                                                | 43<br>46<br>47                   |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5         | Example program region hierarchy  Work-around of improper loop  Work-around of indirect function call  Work-around of recursive function call  A template describing the memory access behavior of fread                                                                            | 51<br>53<br>55<br>56<br>56       |

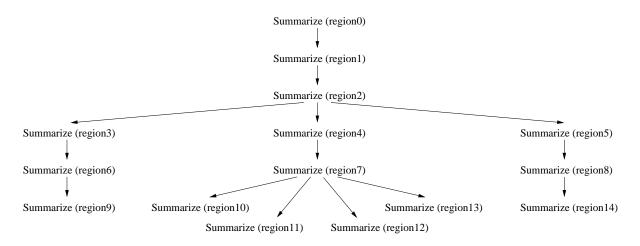

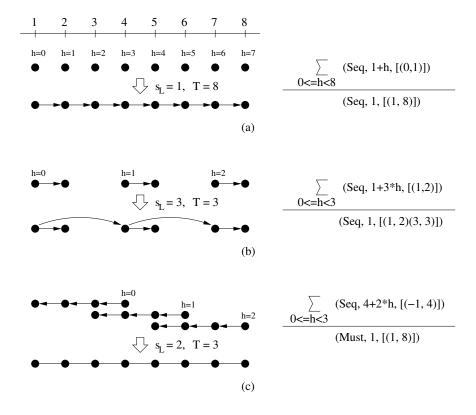

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6  | Example illustrating the displace field of the MAD data structure  Examples for illustrating different MAD structures  The pseudo-code of Summarize  Example recursive calls of Summarize  Illustration of the bottom-up summarization process  The pseudo-code of FindExposedReads | 60<br>61<br>65<br>67<br>67<br>72 |

| 6.7<br>6.8<br>6.9<br>6.10               | Example illustrating $FindExposedReads$                                                                                                                                                                                                                                             | 74<br>77<br>78<br>82             |

| 6.11<br>6.12                            | The pseudo-code of ConcatenateMAD                                                                                                                                                                                                                                                   | 83<br>84                         |

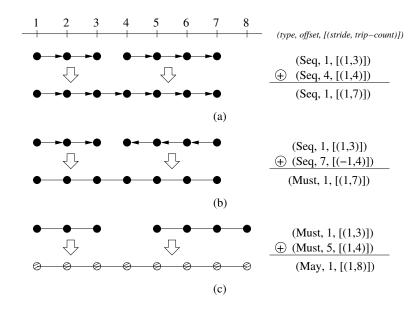

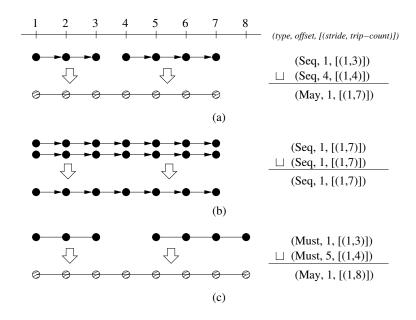

| 6.13 | Examples of concatenating two memory access patterns                             | 85  |

|------|----------------------------------------------------------------------------------|-----|

| 6.14 | The pseudo-code of CombineComponents                                             | 85  |

| 6.15 | The pseudo-code of $\mathbf{Merge} (\sqcup) \ldots \ldots \ldots \ldots \ldots$  | 87  |

| 6.16 | The pseudo-code of MergeMAD                                                      | 88  |

| 6.17 | The pseudo-code of MergePattern                                                  | 89  |

|      | Examples of merging two memory access patterns                                   | 90  |

|      | The pseudo-code of <b>Subtract</b> $(\ominus)$                                   | 90  |

|      | The pseudo-code of <b>SubtractMAD</b>                                            | 91  |

| 6.21 | The pseudo-code of Pattern_subtract                                              | 92  |

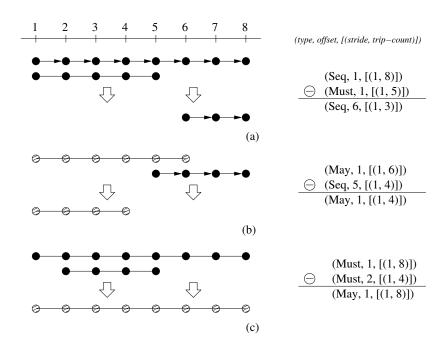

| 6.22 | Examples of subtracting two memory access patterns                               | 92  |

| 6.23 | The pseudo-code of IntersectPattern                                              | 93  |

| 6.24 | The pseudo-code of <b>PatternCovered</b>                                         | 93  |

| 6.25 | The pseudo-code of <b>Summation</b>                                              | 95  |

| 6.26 | The pseudo-code of <b>SummationMAD</b>                                           | 96  |

| 6.27 | The pseudo-code of <b>SummationMAD</b>                                           | 97  |

| 6.28 | Example illustrating <b>Summation</b> $(\sum)$                                   | 98  |

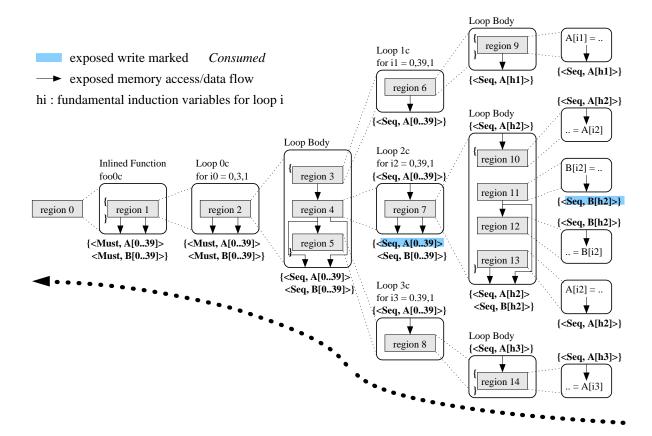

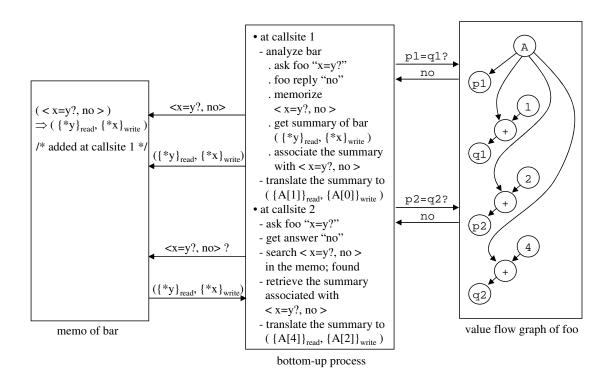

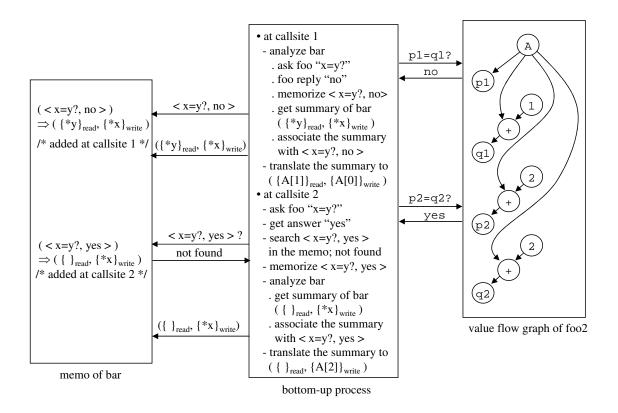

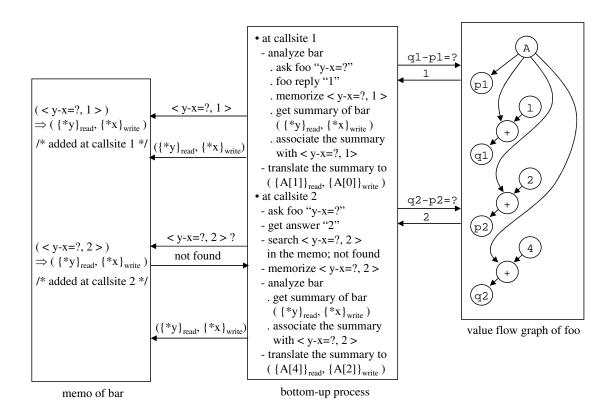

| 7.1  | Illustration of the bottom-up phase                                              | 106 |

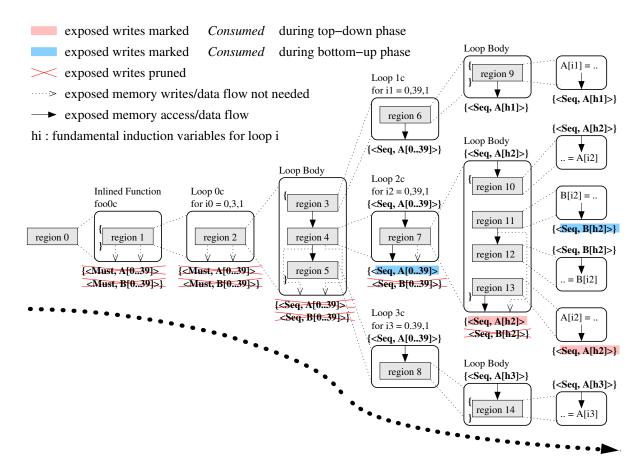

| 7.1  | * *                                                                              | 108 |

| 7.3  |                                                                                  | 100 |

| 1.0  | The pseudo-code of TruneExposed Wifees                                           | 103 |

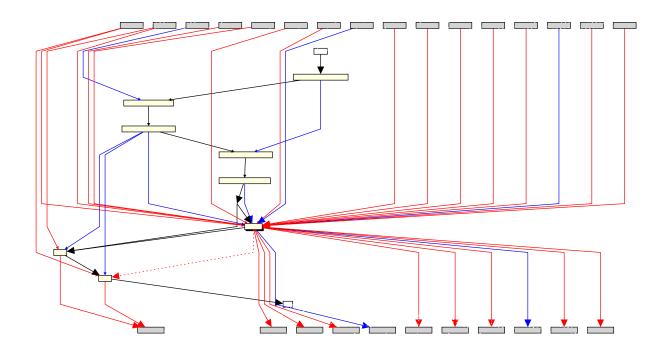

| 8.1  | Demonstration of the memory data-flow visualization system                       | 113 |

| 8.2  | Example for illustrating spurious data producers                                 | 116 |

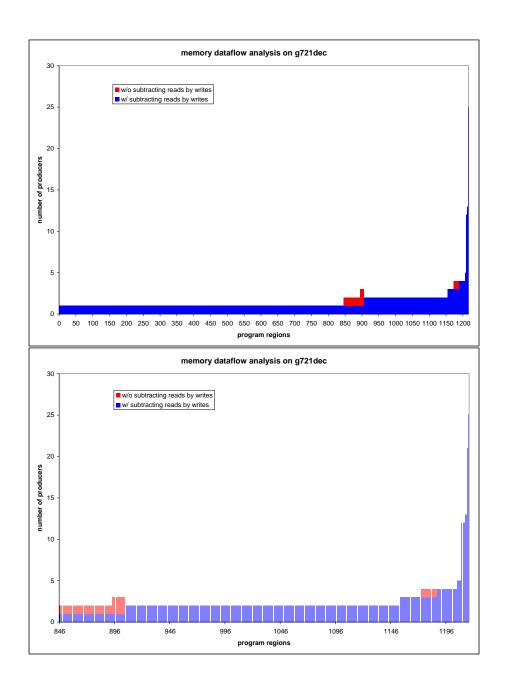

| 8.3  | Eliminated spurious data producers (false dependences) in g721dec                | 117 |

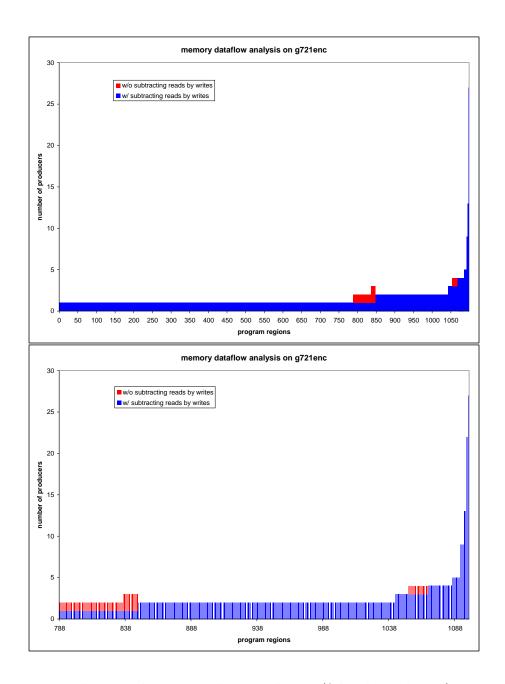

| 8.4  | Eliminated spurious data producers (false dependences) in g721enc                | 118 |

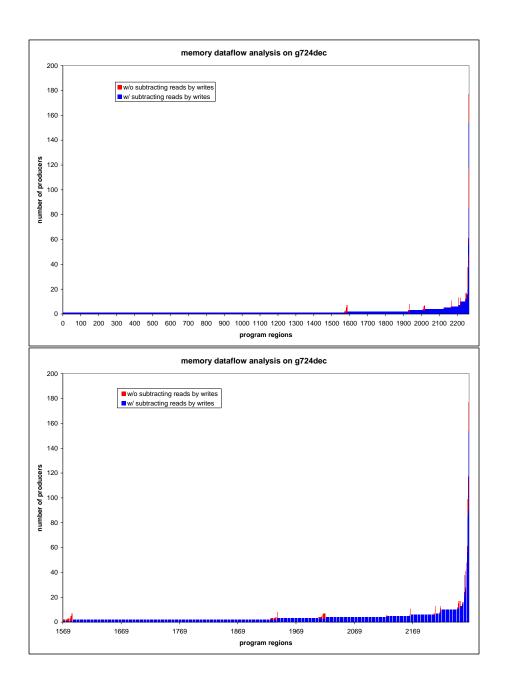

| 8.5  | Eliminated spurious data producers (false dependences) in g724dec                | 119 |

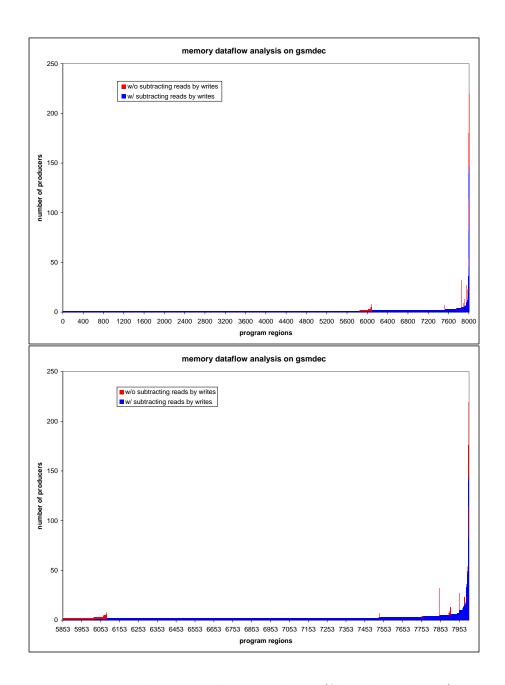

| 8.6  | Eliminated spurious data producers (false dependences) in gsmdec                 | 120 |

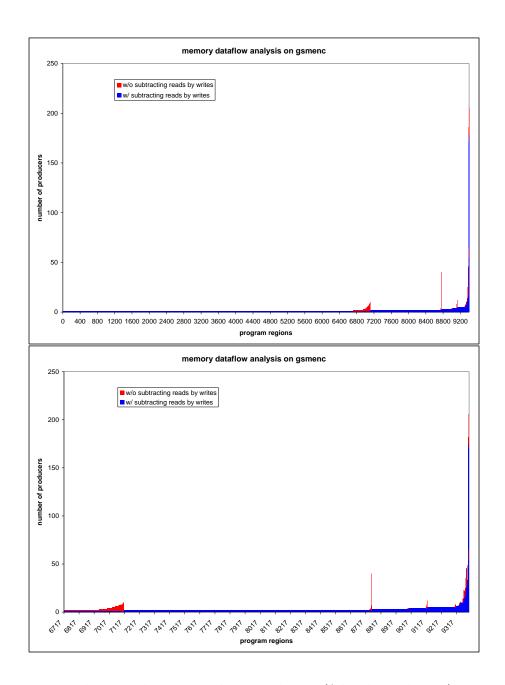

| 8.7  | Eliminated spurious data producers (false dependences) in gsmenc                 | 121 |

| 9.1  | Example of function with the same summary at two call-sites                      | 133 |

| 9.2  | Illustration of function calls with isomorphic memory data-flow analysis results |     |

| 9.3  | - · · · · · · · · · · · · · · · · · · ·                                          | 134 |

| 9.4  | Illustration of function calls without isomorphic memory data-flow analysis      | 100 |

| J.4  | - · · · · · · · · · · · · · · · · · · ·                                          | 136 |

| 9.5  |                                                                                  | 130 |

| J.J  | musuration of memerical queries to value now graph                               | TOI |

#### CHAPTER 1

#### Introduction

The progress of IT (Information Technology) industry is driven by the simultaneous advance of semiconductor manufacturing technology, hardware, application, and design methodology. More advanced manufacturing technology enables more powerful hardware, which in turn enables more advanced application. On the other hand, more advanced application motivates more powerful hardware, which in turn motivates more advanced manufacturing technology. Although less visible, design methodology plays a crucial role in meshing technology to hardware, and hardware to application, so that the whole IT industry is not out of gear.

To put the rest of this dissertation in perspective, this chapter will examine the trends on manufacturing technology, hardware, and application, and point out, among the many challenges faced by the current design methodology, which problem domain this dissertation is trying to make some small step contributions. Chapter 2 will review previous works to understand how the problems are approached by other researchers in different ways, and to identify the specific problem that this work will focus on. Chapter 3 will present the problem statement to set the goal of this work, and outline the steps to achieve the goal by decomposing the problem into sub-problems. Later chapters of this dissertation will discuss each of these sub-problems and the proposed solutions in

detail. Finally, this dissertation will conclude with the results and insights obtained from prototyping the proposed solutions, and propose some future works.

#### 1.1 Technology Trend

The rapid growth of the semiconductor industry is fundamentally driven by a trend observed by Gordon Moore in 1965, that is transistor density doubles every 18 months [1]. In this rate, a single chip will have a billion transistors on it in the near future, enough for the integration of a whole system [2]. However, to utilize this enormous amount of transistors, we need to solve many problems. Below is an incomplete list of the problems.

- The NRE (Non-Recurrent Engineering) cost is soaring. For example, the cost of mask set has risen from several hundred thousand dollars for 0.18-micron process to over 1 million dollars for 90-nm process, and 3 million dollars for 65-nm process [3] [4] [5]. Moreover, mask cost is only a fraction of the total NRE cost. The design and verification costs are also sky-rocketing as chip design is becoming more and more complex.

- Because of the shrinking of feature size, transistors can switch very fast, and are thus no longer the performance bottleneck. However, the RC delay of long wire does not scale down proportionally [6]. Signals can no longer propagate along long wires in one clock cycle [7]. One implication of this wire delay problem is that, because of clock skew, it is getting harder and harder to synchronize the whole chip at high clock frequency [8]. Even if technically possible, increasing clock frequency will no

longer be a feasible approach to achieve high performance, because of prohibitive power dissipation.

- Power dissipation has been a recurring problem since the early days of semiconductor industry. Integrating more transistors on a single chip will increase the power density, because more transistors switching simultaneously will cause more dynamic power dissipation. Moreover, in the deep sub-micron era, leakage power is no longer a second order effect. In the future, leakage power will even contribute more to total chip power dissipation than dynamic power [9] [10].

- Related to the power dissipation problem, energy efficiency is becoming a top design consideration for extending the operating period of small portable information appliances operating on batteries, and for reducing the utility cost of large data warehouses consisting of thousands of servers [9].

- Yet another everlasting problem is the memory bottleneck. While the density of DRAM quadruples in three years, even faster than the increase of logic density, the speed of memory cannot catch up the speed of logic. Putting more memory on chip does not necessarily solve the memory bottleneck problem, due to the wire problem and the limitation on the number of memory access ports.

The semiconductor industry will not stall building more powerful hardware because of these problems. Instead, people are developing innovative hardware architectures to more efficiently use the coming billion transistors [11].

#### 1.2 Hardware Trend

The state-of-the-art hardware systems are composed of ASICs (Application Specific Integrated Circuits) and/or programmable devices like digital signal processors and microprocessors. The goal of hardware design is to achieve a balance among performance, cost, and flexibility for the target applications. Technology trend profoundly affects how people build hardware systems to maintain this balance.

For example, traditional standard cell based ASIC design is being challenged as a costeffective approach to achieve low power and high performance, because of soaring NRE

cost, high design risk and constantly changing industry standards. For applications which

microprocessors and digital signal processors still cannot meet the performance, power,

and area requirements, people are seeking alternatives like structured ASIC, FPGAs

(Field Programmable Gate Arrays), and reconfigurable architectures, to replace standard

cell based ASICs. These alternatives promise lower cost and/or more flexibility, without

sacrificing too much performance [12] [13].

The technology trend is also challenging the conventional wisdom in microprocessor design. Because the centralized organization of current high-performance microprocessors does not scale well with the advance of semiconductor manufacturing technology, researchers are proposing alternative architectures like the M.I.T. RAW processor [14], the Stanford Stream processor [15] and Merrimac machine [16], and the U.T. Austin TRIPS processor [17], to address the issues faced by future billion transistor microprocessors [18].

For commercial microprocessors, the design objective now is not performance, but performance per Watt. Instead of increasing clock frequency, which will incur too much power dissipation, both Intel and AMD are shipping dual-core microprocessors and will resort to multi-core architectures to achieve high performance in the future [19] [20] [21]. The Cell processor developed by Sony, Toshiba and IBM also adopts multi-core architecture, consisting of one PowerPC Processing Unit and 8 Synergetic Processing Units for SIMD processing [22] [23].

Although microprocessors have been making significant progress in performance and will be more power efficient in the future, I believe general-purposed architecture alone is not the most efficient hardware platform. Future system on chip will consist of multiple general-purposed cores and application specific accelerators in order to power efficiently and cost effectively meet the requirements of emerging applications.

### 1.3 Application Trend

In the past, the growth of semiconductor industry is driven by PCs (Personal Computers) and desktop applications. As the analog world is gradually digitized, and more and more richer and richer digital contents are delivered through the Internet, (portable) telecommunication, multimedia, and gaming applications are replacing PC desk-top applications as the new driving applications.

These applications present much higher design challenges than traditional PC desktop applications because 1) they require much higher computing power for complicated

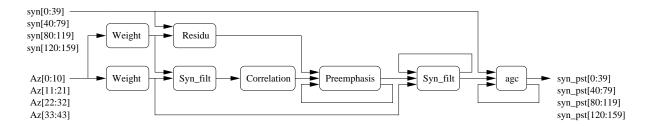

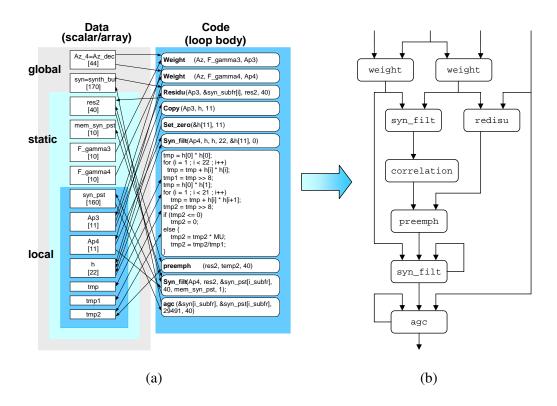

Figure 1.1 The block diagram and data-flow of the post-filter of G.724 decoder algorithms to, for example, analyze and synthesize audio and video streams; 2) they impose much tighter design constraints on form factor, cost, power dissipation and energy efficiency.

These applications usually consist of DSP (Digital Signal Processing) kernels, with inputs and outputs of sequences of frames. Usually an input frame is further divided into sub-frames or blocks, which are then individually processed by the DSP kernels. So potentially there is abundant parallelism in processing these sub-frames or blocks.

As a simple but concrete illustrating example, Figure 1.1 shows the components and data-flow of the post-filter used in the G.724 decoder [24]. The 160-bit input speech frame syn[0..159] is divided into four 40-bit sub-frames to be individually processed by the post-filter.

Parallelism also exists in each computation kernel. The **Weight** block is basically a vector multiplication, scaling its input signals by different weights. The **Residu** block is a FIR (Finite Impulse Response) filter and the **Syn\_filt** and **Preemphasis** blocks are IIR (Infinite Impulse Response) filters. The **Correlation** block computes two autocorrelations. The **agc** block for automatic gain control is a little more complicated, but the basic computations are still vector multiplication and accumulation.

To meet the, often conflicting, design requirements, it is necessary to exploit all the possible inherent parallelism in these applications.

## 1.4 Exploiting Parallelism

For the post-filter shown in Figure 1.1, potentially we can at least exploit the following parallelism.

- Frame level data parallelism. If there is no data dependence between the processing of consecutive frames, we could potentially duplicate the hardware to post-filter different frames in parallel.

- Sub-frame level data parallelism. If there is no data dependence between the processing of consecutive sub-frames, we could potentially duplicate the hardware to process each sub-frames in parallel.

- Sub-frame level function parallelism. Instead of duplicating hardware, we could pass the sub-frames through the DSP kernels in a pipelining or data-flow fashion to exploit the coarse-grained function parallelism among these kernels.

- Signal level data parallelism. For digital signal processing kernels, we could use techniques like Intel MMX/SSE [25] [26] to exploit fine-grained data parallelism.

- Instruction/operation level parallelism. We could implement these kernels using state-of-the-art high-performance digital signal processors or microprocessors, which exploit instruction level parallelism to speed up the execution. We could also

design ASIC to directly map the operations of these kernels to parallel arithmetic units.

In spite of its abundant parallelism, the post-filter contributes only about 50% of the total G.724 decoder execution time. According to Amdahl's law [27], the performance of the G.724 decoder cannot be significantly improved without speeding up the other 50% of its computation, which may exhibit different characteristics from the post-filter and thus require different approaches to improving performance.

It is no surprise that people build today's telecommunication and media applications using an array of hardware components, from ASIC and DSP (Digital Signal Processor) to micro-controller and microprocessor, exploiting coarse-grained and fine-grained, data and function parallelism to balance performance and cost.

Partitioning complex software into concurrent tasks, exploiting different forms of parallelism, mapping these tasks onto complex hardware and searching for a balance point between performance and cost is a daunting task. However, the current design practice mainly relies on designer's experience and instinct. With shorter time-to-market and product lifetime, the development of future applications needs more efficient and systematic design methodology.

#### 1.5 Improving Design Productivity

The exponential increase of transistor density is followed by the exponential increase of hardware and software complexities. However, we cannot exponentially improve our productivity using the same design methodology. To boost productivity, we shift to higher level design abstraction to hide complexity. In the past, software design moved from assembly language programming to high-level language programming; hardware design moved from gate-level design to RTL (Register Transfer Level) design. However, abstraction alone cannot achieve paradigm shift. We need the tools that can translate designs from higher level representation to lower level representation without sacrificing too much design quality. The success of the first high-level programming language Fortran is because of the accompanying good Fortran complier; the success of Verilog/VHDL is because of good RTL synthesis tools.

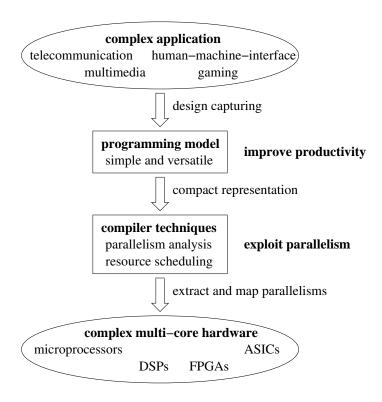

In summary, Figure 1.2 depicts the big picture of the problem domain that this dissertation is trying to make some small contributions. The problem is two-fold.

- What is the programming model for capturing complex emerging applications in a compact representation? To improve design productivity, the programming model must be simple. To cover wide range of applications, the programming model must be versatile.

- What are the compiler techniques to extract parallelism out of the compact representation, and to map concurrent tasks onto complex multi-core hardware? The complex hardware will consist of multiple general-purposed microprocessors, ASICs and even FPGAs.

Figure 1.2 The challenge of the design methodology community.

I realize that this is not a new research topic. Many researchers have made great contributions before. The next chapter will scan the previous works, trying to find an empty slot in the book shelf for this dissertation.

#### CHAPTER 2

#### **Previous Work**

Exploiting parallelism and boosting productivity are the recurring challenges of the IT industry, especially when the advance of technology accumulates enough momentum to make a hardware architecture leap, or to surpass the existing design methodology. This chapter will review the previous works on optimizing compilers, high-level synthesis, and concurrent languages. Although they take different approaches, or target different hardware platforms, all these three areas concern how to exploit parallelism and boost productivity.

## 2.1 Optimizing Compilers

Compiler optimization is an active and exciting research area. Researchers have been innovating new techniques to efficiently implement new programming language constructs and to effectively utilize new architecture features. We can roughly divide optimizing compilers into two categories, vectorizing/parallelizing compilers targeting supercomputers [28] [29] and optimizing compilers targeting super-scalar, VLIW (Very Long Instruction Word) or EPIC (Explicitly Parallel Instruction Computing) architectures [30] [31]. Great progresses have been made in these two areas.

#### 2.1.1 Vectorizing Compilers

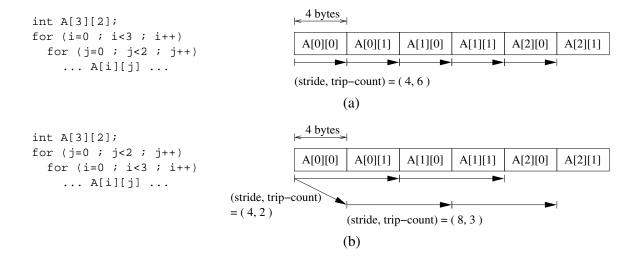

Early vectorizing compiler researches [32] [33] [34] [35] [36], most notably the Parafrase project at the University of Illinois [37] and the Parallel Fortran Converter project at Rice University [36], not only formalized fundamental notions like data dependence, dependence distance, dependence direction, and dependence level, but also pioneered dependence test techniques for automatically identifying the inherent parallelism in sequential programs. Furthermore, to enable more vectorization and to better utilize the underlying hardware features, these ground-breaking works also invented program restructuring techniques [38] [39] [40] [28], for example, loop interchanging [41] [42], loop skewing [43], scalar renaming [44], array renaming [36], strip-mining, and vector register allocation [45].

Although these early vectorizing compiler works focused on exploiting fine-grained data parallelism to speed up scientific computations on vector or SIMD (Single Instruction Multiple Data) machines, they also laid the foundation for the parallelizing compilers targeting MIMD (Multiple Instruction Multiple Data) machines, and more recently for the vectorizing compilers targeting instruction sets like the Intel MMX and SSE [26] for speeding up multimedia applications on microprocessors.

#### 2.1.2 Parallelizing Compilers

Because MIMD machines usually have high inter-processor communication cost, parallelizing compilers targeting MIMD machines must look beyond the inner-most loop to seek more coarse-grained parallelism in the outer loops [46] [47] [48] [49] [50] [51] [52].

To maximize parallelism and to increase locality, researchers have developed many program analysis and transformation techniques, for example, loop distribution [28], loop fusion [46] [53], loop tiling [54], unimodular transformation [55], array data-flow analysis [56] [57] [58] [59], and array privatization [60] [61] [60] [62] [63].

Because parallelizing compilers need to examine larger program regions for parallelism, many analyses need to cross the procedure boundaries to get more accurate analysis results. Because full program in-lining is too costly, researchers have developed many inter-procedural analysis techniques [64] [65] [66] [67] [68] [69] [70] [71].

Most of the parallelizing compiler works are based on the SPMD (Single Program Multiple Data) model to exploit coarse-grained data parallelism. This is suitable for scientific applications with data set much larger than the number of processors. However, researchers found that SPMD alone may not be the best way to parallelizing applications like many digital signal processing applications which have many kernels with small working set. For this kind of applications, it is better to exploit function (or task) parallelism in addition to data parallelism [72] [73].

In data parallelism, different processors (or functional units) execute the *same* program (or function) on different data at the same time. In function parallelism, different processors (or functional units) execute *different* programs (or functions) on different data at the same time. Researchers have developed techniques for task scheduling and resource allocation given the dependence or data-flow among the tasks [74] [75] [76].

Unlike parallelizing compilers targeting MIMD machines, which must exploit *coarse*grained data and/or function parallelism in order to avoid excessive costly inter-processor communication, optimizing compilers targeting high performance microprocessors exploit instruction level parallelism, which can be classified as *fine-grained* function parallelism.

#### 2.1.3 Superscalar/VLIW/EPIC Compilers

High performance microprocessors are capable of executing multiple instructions at the same time. People have made micro-architecture and compiler innovations to increase the number of instructions available for parallel execution.

For example, Tomasulo's algorithm [77], which is widely used in superscalar microprocessors, eliminates false dependencies among instructions by register renaming [78] [79]; branch prediction [80] [81] [82] [83], trace cache [84] [85], predication [86] [87] [88], speculation [89] [90] [91], and memory disambiguation [92] enable more parallel instruction execution by eliminating the synchronization barriers caused by spurious control dependencies and memory dependencies.

Often, the micro-architecture features for exploiting ILP (Instruction Level Parallelism) rely on compiler supports to achieve better utilization. For example, to expose and schedule more instructions for parallel execution, people have developed trace scheduling [93], superblock formation [94], software pipelining, modulo variable expansion and modulo scheduling [95] [96] [97]; to enable more effective predication, people have developed hyperblock formation and predication analysis [98] [99]; to support speculation, people have developed sentinel scheduling [100]; to obtain more accurate compile-time memory disambiguation, people have been improving the accuracy and efficiency of dependence tests [101] and pointer analysis [102] [103].

It is due to the micro-architecture and compiler innovations combined, and always being manufactured using the cutting-edge process technology, that microprocessors can make such impressive progress in performance and cost. However, general-purposed architecture still cannot meet the performance and cost requirements of many applications. Many products still rely on special hardware to achieve the required performance under strict cost and power constraints.

### 2.2 High-level Synthesis

Hardware designers have long been exploiting parallelism to improve the performance and efficiency of their products. However, designing hardware at circuit level or gate level is tedious and difficult. Designers must determine circuit topology, size transistors, optimize logic, synchronize signals with respect to clocks and perform circuit or logic simulations for functional verification and for timing analysis. As circuits become larger and larger, it is very time consuming to capture and verify the whole design at such low level.

To improve design productivity, people developed hardware description languages like Verilog and VHDL as well as RTL synthesis tools. The hardware description languages essentially abstract hardware as a hierarchy of concurrent processes following an event-driven execution model. Instead of drawing schematics, designers can now capture their designs using hardware description languages just like writing software programs, or more precisely concurrent programs. The RTL synthesis tool will then take the high-

level descriptions along with user specified design constraints, perform all the low level design activities, and finally generate a netlist ready for the place-and-route tool [104]. This enables designers to focus on RTL and architecture level design exploration and verification.

However, RTL designers still need to take care of details like circuit reset, clock synchronization and dividing critical timing path into several pipeline stages, as well as explicitly expressing fine-grained and/or coarse-grained, function and/or data, parallelism as a hierarchy of concurrent processes with bit-level or word-level interprocess communication signals. In other words, the designers still need to describe the design structurally, not behaviorally. As ASICs are getting more complex, RTL design is also becoming too time-consuming. We are again facing the productivity crisis.

Researchers are advocating moving to even higher design abstraction and high-level synthesis [105] [106] [107]. Starting from an abstraction like data flow graph [108], which describes the dependences between fine-grained or coarse-grained tasks, people have done extensive researches on how to optimize the mapping of concurrent tasks onto hardware building blocks.

There are already commercial tools that can take C programs and generate the corresponding RTL implementation [109] [110] [111] [112]. Although the users of these tools can describe their design behaviorally, in order to obtain better synthesis results, they still need to explicitly express parallelism, especially coarse-grained function parallelism, as well as the inter-process communication mechanism using compiler directives or concurrent language constructs.

### 2.3 Concurrent Programming Languages

In addition to the techniques that extract parallelism from sequential programs, vectorizing and parallelizing compiler researchers also developed compiler directives and language constructs to let programmers explicitly express parallelism. For example, Fortran-D [113] and High Performance Fortran (HPF) [114] extend the Fortran language with vector operations and data partitioning directives for explicit data parallelism on top of a shared memory model; the MPI standard [115] is proposed as a portable library for explicit inter-process communication under the message-passing paradigm. While it is natural to target shared-memory programs on shared-memory multiprocessors, and message-passing programs on distributed memory multicomputers, the memory model of a concurrent programming language is not tightly coupled to the memory organization of the underlying machines. It is up to the compiler and the run-time system to bridge the semantic gap.

In addition to vector, SIMD, shared-memory MIMD, and distributed-memory MIMD machines, researchers also experimented data-flow supercomputers [116] [117] [118] to exploit massive parallelism. In parallel with the development of data-flow machines, researchers also designed data-flow languages [119] [120] for explicitly expressing fine-grained function parallelism. Different from a program written in imperative languages, a program written in data-flow language is side-effect free and each of its variables has only single assignment.

Interestingly, researchers also developed compiler analyses and transformations that can translate an imperative program to a form with some data-flow properties. For example, there exists efficient algorithms to translate an imperative program into the SSA (Single Static Assignment) form [121], gated SSA form [122], or dependence web [123]. Researchers [124] even argued that it is not necessary to design data-flow languages for data-flow machines, because imperative programs can obtain the same performance on data-flow machines using advanced compiler techniques, and the compilers for both types of languages have similar complexities. Also, the von Neumann programming model of imperative languages could be more intuitive and result in more compact programs than the data-flow programming model for some applications, especially for applications with a lot of partial state changes in complex data structures.

Because of these and other reasons, in spite of their many creative concepts, dataflow languages did not become mainstream <sup>1</sup>. The dominating programming languages today are still imperative languages. Instead of for expressing massive parallelism in general applications, recent data-flow language researches are more for software engineering purpose [120] and for specific application domains.

For example, to model DSP applications, researchers have developed formal representations like synchronous data flow [125] and data-flow process networks [126]. In these models, a task or a process, which could be an imperative program, represents a DSP kernel which is repeatedly applied to its input signals. Also explicitly expressed in these

<sup>&</sup>lt;sup>1</sup>Neither did general purposed data-flow machines. Instead, it is the restricted data-flow model [78] that prevails in commercially successful high-performance microprocessors.

models are the signal flow among these tasks and the signal generating and consuming rates of each kernel. The motivation for these formalisms is to enable automatic synthesis and optimization of real systems from the models [127] [128] [129] [130] [131].

With similar motivation, and language semantics, researchers also developed streaming languages like StreamIt [132] and Brook [133] to ease the programming for machines like the MIT RAW machine [14], the Stanford Merrimac [16] or even graphics processors [134]. The fundamental concepts of these streaming languages are *stream* consisting of possibly infinite number of independent data, and *kernel* (or *filter*) operating on streams. Thus, a streaming program explicitly expresses the function parallelism among the execution of kernels, as well as the data parallelism among the processing of stream elements.

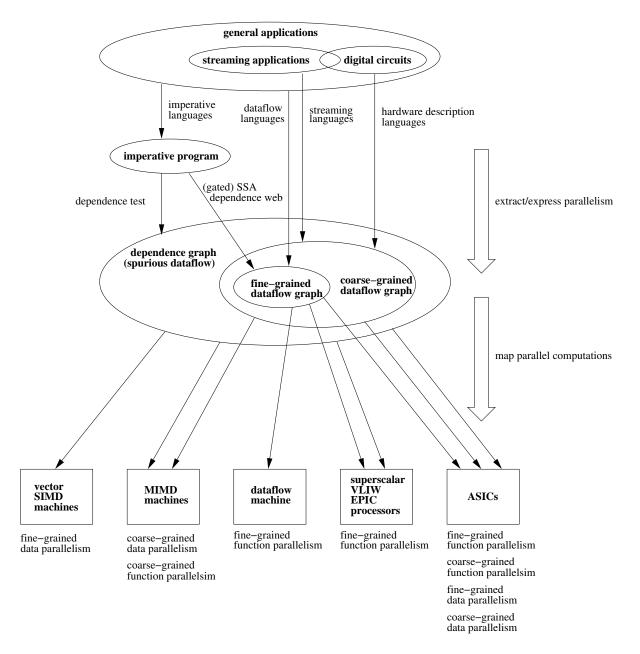

The previous works on exploiting parallelism and on boosting productivity are really tightly correlated, and we can unify them in a single picture, as shown in Figure 2.1. Figure 2.1 can be divided into two halves. The top half is extracting parallelism from the applications by compilers, or expressing parallelism in the applications by software programmers or hardware designers. The bottom half is mapping concurrent tasks onto hardwares exploiting various types of parallelism. Each edge in Figure 2.1 corresponds to the enormous amount of knowledge and techniques obtained in decades of compiler, high-level synthesis and programming language researches. The next chapter will discuss where my work will make a dent in this big picture, considering both the learned lessons and the projected trends.

Figure 2.1 A unified view of exploiting parallelism and boosting productivity

#### CHAPTER 3

#### Thesis Overview

This chapter will serve two purposes. First, it will establish the problem statement of my PhD research based on the reflection on the technology, hardware and application trends discussed in Chapter 1 and the previous works on exploiting parallelism discussed in Chapter 2. Second, it will discuss what sub-problems we need to solve and give an overview of the remaining chapters of this dissertation.

#### 3.1 Problem Statement

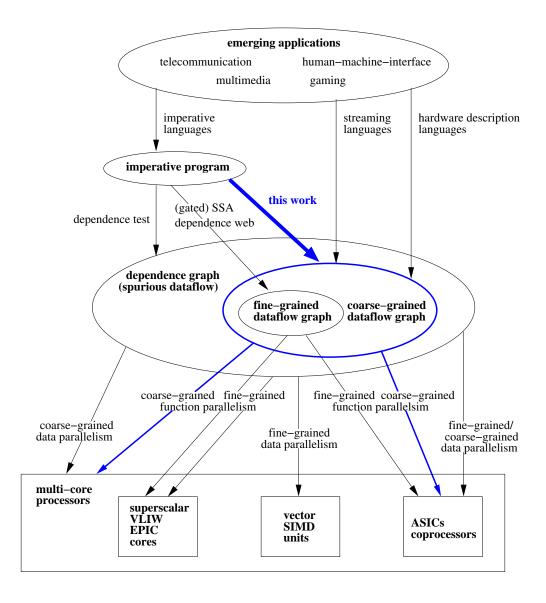

Figure 3.1 relates the previous works with the perceived multi-core architectures. Many of the works people have done for partitioning and distributing computations onto MIMD machines can be readily used for exploiting coarse-grained data and function parallelism for the multi-core architecture. For efficiently utilizing superscalar/VLIW/EPIC cores and SIMD/vector execution units, researchers have already developed a lot of techniques, and are keeping pushing the envelope. Very likely, the coming multi-core architecture will also include ASICs or coprocessors to efficiently accelerate applications [135]. The CAD community have been innovating more powerful tools to facilitate the development of these accelerators.

Figure 3.1 The position of this work with in mapping applications onto multi-core architectures

The works of mapping concurrent tasks onto multi-core architectures are all based on an abstraction, the dependence graph, which describes the partial order between the execution of computational tasks. Researchers have been pushing the accuracy of dependence test. There already exists exact data dependence test, the Omega test [101], which is very efficient for common cases. Because of the way they are constructed,

dependence graphs may contain many false dependences. While false dependences may not affect the effective accuracy of the dependence graph for compiler applications like vectorization, the removal of false dependences can improve the effectiveness of many other compiler optimizations [136].

Dependence graph without false dependences can be called data-flow graph, because it contains only the true data dependences, or data-flows, between computational tasks. A data-flow graph can be fine-grained, with each node corresponding to basic operations like addition, or it can be coarse-grained, with each node corresponding to more complicated computations like filters. Because they expose the maximum available parallelism, data-flow graphs are instrumental in high-level synthesis and in mapping tasks onto array of processors, and also the "programs" for the data-flow computation model.

It is indisputable that the data-flow model is ideal for building hardware, because of its localized memory access, neighboring communication, and maximum parallelism. Indeed it has been the model for designing high performance ASICs like DSP circuits [137]. For the perceived multi-core architecture, the data-flow model will also play an important role not only in building the accelerators, but also in core-to-core, core-to-accelerator, and accelerator-to-accelerator communications through the on-chip interconnection network.

However, as discussed in Chapter 2, there are two schools of thoughts about how to construct the data-flow graph. The first school of thought is to let the programmers write programs using data-flow or streaming languages. The second school of thought is to let the programmers write programs using conventional imperative languages, and

the compilers translate the imperative programs into data-flow graphs. This thesis work follows the second school of thought for the following reasons.

- There have already existed a huge code base written in imperative languages. As

time goes by, more and more important imperative programs will be developed.

These imperative programs will still need to run efficiently on future multi-core

processors.

- The von Neumann programming model of the imperative languages is widely applicable. Many complicated applications have been written in imperative languages based on the von Neumann programming model. On the other hand, the data-flow or streaming languages are still in the stage of proving concepts. If we could develop a program analysis system to extract data-flow from imperative programs, the need for developing new data-flow or streaming languages, as well as the associated tool chains, will be questionable.

Because there are already efficient algorithms to convert imperative programs to finegrained data-flow graphs [138] [123] [121] [139], and because exploiting coarse-grained parallelism will become more and more important for future multi-core processors, this thesis work will focus on extracting coarse-grained data-flows from imperative programs to facilitate the exploitation of coarse-grained function parallelism in multi-core processors, as indicated in Figure 3.1. More specifically, this thesis work will target programs written in the C language, partly because of the popularity of C and partly because of the

Figure 3.2 Illustration of the problem statement using the post-filter of G.724 decoder compiler infrastructure used for prototyping and experiments. However, the techniques developed in this work could also be applied to other imperative languages.

To specifically illustrate the problem that this work is to solve, Figure 3.2(a) shows the original C code and the corresponding memory accesses of the G.724 post-filter example presented in Figure 1.1. Note that the original program accesses both memory objects statically allocated in the global memory and memory objects dynamically allocated in the stack and the heap memory. These memory objects are often shared by different functions. The challenge is to sort out the memory data-flow as shown in Figure 3.2(b) from the complicated memory accesses as shown in Figure 3.2(a).

In summary, the problem statement of this research is as follows.

Problem statement: Building a program analysis system to extract coarse-grained data-flow from C programs for exploiting coarse-grained function parallelism.

This concludes the *philosophy* part, and start the *engineering* part, of this PhD dissertation.

# 3.2 Fine-grained Analogy

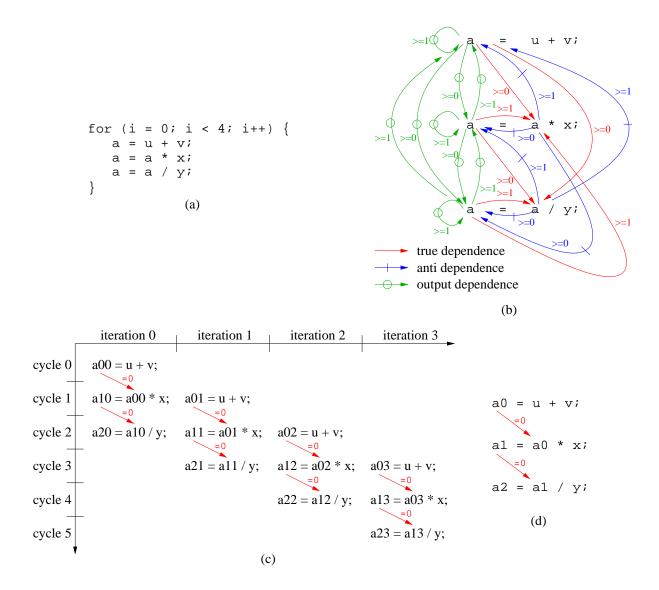

To obtain some insights on how to extract coarse-grained data-flow from imperative programs, this section will use Figure 3.3 to review how fine-grained data-flow is extracted from imperative programs to exploit fine-grained function parallelism.

By pairwise comparison of variable reads and variable writes in the code segment of Figure 3.3(a), we can construct the dependence graph shown in Figure 3.3(b). Each dependence is annotated with the corresponding dependence distance. Note that the dependence distance is an interval, not necessarily a single integer number [101]. For clarity, only the lower bound of the dependence distance is shown in Figure 3.3(b).

These dependences prevent the parallel execution of instructions in the same iteration and/or in different iterations. However, many of the dependences in Figure 3.3(b) are false dependences caused by writing to the same variable a. If each dynamic instruction writes to a different memory location, we can eliminate all the false dependences and obtain the maximum parallelism which is only constrained by the true dependences and hardware resources, as shown in Figure 3.3(c)  $^{1}$ .

<sup>&</sup>lt;sup>1</sup>Here we assume there are 1 adder, 1 multiplier, and 1 divider.

Superscalar processors achieve this by performing the architecture register to physical register renaming on the fly [79]. Renaming can also be done using compile-time techniques like SSA [121], which can easily convert the loop body in Figure 3.3(a) to the data-flow graph in Figure 3.3(d). To obtain better instruction scheduling results, software pipelining [95] or modulo scheduling [96] also perform register renaming using techniques like modulo variable expansion [95] to allocate different registers to instructions in different iterations.

The key to exploiting fine-grained function parallelism is really to extract the dataflow between instructions by eliminating false dependences through renaming. Essentially there are three issues in extracting data-flow for function parallelism.

- Defining function. For fine-grained function parallelism, a function is an instruction or an operation.

- Identifying the memory storages accessed by each function. For instructions operating on registers, the accessed memory storages can be identified using the specified register numbers for the source and the destination operands.

- Identifying the producer and consumer relation between functions. Superscalar processors use hardware structures like RAT (Register Alias Table) to establish the producer and consumer relation between instructions at run-time. Compilers identify the producer and consumer relation by performing data-flow analysis or by SSA construction.

Figure 3.3 Example illustrating extracting fine-grained data-flow

The next section will address these three issues in the context of extracting coarse-grained data-flow to exploit coarse-grained function parallelism.

```

1:

int A[40];

2:

3:

foo0 (...)

4:

for (i0 = 0 ; i0 \le 3 ; i0++) {

5:

6:

foo1 (A, ...);

7:

foo2 (... A, ...);

8:

foo3 (... A);

9:

10:

foo1 (short y[], ...)

11:

12:

for (i1 = 0 ; i1 \le 39 ; i1++)

13:

14:

y[i1] = ...

15:

16:

foo2 (..., short s[], ...)

17:

18:

for (i2 = 0 ; i2 >= 0 ; i2--)

s[i2] = s[i2] ...

19:

20:

21:

foo3 (... short x[])

22:

for (i3 = 0 ; i3 \le 39 ; i3++)

23:

24:

\dots = x[i3] \dots

25:

```

Figure 3.4 Example coarse-grained functions of subroutine calls

### 3.3 Coarse-grained Issues

This section will examine the issues in extracting coarse-grained data-flow from imperative programs to exploit coarse-grained function parallelism. The discussion will follow the three issues summarized in the previous section. As explained in the following sections, extracting coarse-grained data-flow is much more difficult than extracting fine-grained data-flow.

#### 3.3.1 Defining Coarse-Grained Function

To exploit coarse-grained function parallelism, we must first define what is *coarse-grained function*, then we can discuss how to execute *coarse-grained* functions in parallel.

```

1:

int A[40];

2:

3:

foo0a (...)

4:

5:

6:

* loop0a:

7:

for (i0 = 0; i0 \leq 3; i0++) {

8:

9:

* loop1a: write A[0..39]

10:

11:

for (i1 = 0 ; i1 <= 39 ; i1++)

12:

A[i1] = \dots

13:

14:

* loop2a: read A[39..0], write A[39..0]

15:

16:

for (i2 = 39 ; i2 >= 0 ; i2--)

17:

18:

A[i2] = A[i2] ...

19:

* loop3a: read A[0..39]

20:

21:

for (i3 = 0 ; i3 \le 39 ; i3++)

22:

23:

\dots = A[i3] \dots

24:

}

```

Figure 3.5 Example coarse-grained functions of loops

For the program segment in Figure 3.4, it is natural to consider the subroutine calls to foo1, foo2 and foo3 as coarse-grained functions. For the program segment in Figure 3.5, we may consider each inner loop as a coarse-grained function. Coarse-grained function is really not as well defined as fine-grained function. While subroutine calls and loops are natural candidates for program regions, there could be other ways to divide a program into regions, or coarse-grained functions.

Ideally we would like each program region, or coarse-grained function, is side-effect free and accesses most of its data in local memories. We would also like to partition a program in such a way that communication between program regions is localized in the memories only accessed by the two communicating program regions. Ideally we would like to partition a program into program regions in so that we could generalize the fine-

grained data-flow execution model to a coarse-grained data-flow execution model, and maximize the available coarse-grained function parallelism.

But this rarely happens in imperative programs which often use global variables for the communication between many program regions. To convert imperative programs into coarse-grained data-flow programs, a more practical approach is to sort out the producer and consumer relation between program regions and then convert global memory accesses to local memory accesses, as discussed in the next section.

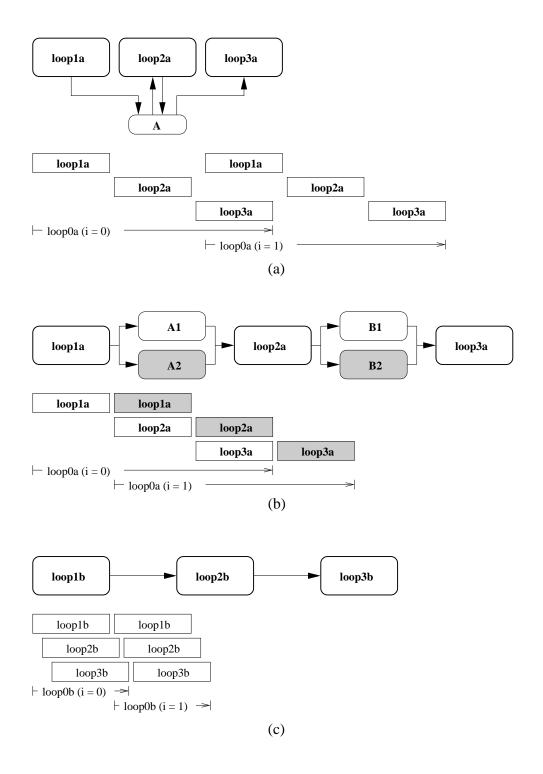

#### 3.3.2 Identifying Producer and Consumer Relation

Consider the example in Figure 3.5, which has three inner loops as coarse-grained functions, all accessing the same array A. As shown in Figure 3.6(a), we can speed up the execution of foo0a using three hardware accelerators for loop1a, loop2a, and loop3a, with a memory block for the communication between these three accelerators, just as the software implementation in the original program. This may speed up the execution of individual innder loop, but there is not too much overlap between the execution of accelerators as illustrated in Figure 3.6(a). Note that loop1a at outer loop iteration i can not start writing to A[0] until loop3a at outer loop iteration i-1 finishes reading the value of A[0] generated by loop2a at outer loop iteration i-1.

Similar to the example in Figure 3.3, the problem here is that both loop1a and loop2a write to the same array A. If we can use different buffers for loop1a and loop2a at different outer loop iterations, like renaming variables in Figure 3.3(c), we can increase

the overlapping between the execution of loop1a, loop2a, and loop3a at different outer loop iterations, as illustrated in Figure 3.6(b).

Basically, we can uncover more inherent coarse-grained function parallelism by separating the memory data-flow between loop1a and loop2a from the memory data-flow between loop2a and loop3a. However, this is possible only if we can prove the following.

- All the array A elements consumed by loop2a are produced by loop1a at the same outer loop iteration.

- All the array A elements consumed by loop3a are produced by loop2a at the same outer loop iteration.

The proof for this simple example is trivial. Note that the loop1a produces the set of array A elements  $\{A[i]|0 \le i \le 39\}$ , which is also the set of array A elements consumed by loop2a. Similarly, the same set of array A elements are produced and consumed by loop2a and loop3a respectively. However, in general it is not easy to identify the producer and consumer relation between coarse-grained functions, because determining the exact memory locations accessed in a coarse-grained program region is not as easy as in the fine-grained case.

# 3.3.3 Summarizing Coarse-grained Memory Accesses

Summarizing the accessed memory locations by a coarse-grained function is more difficult than summarizing the accessed memory locations by a fine-grained function. For the fine-grained case, the memory consists of registers (or scalar variables). The

${\bf Figure~3.6} \quad {\bf Illustration~of~the~producer-consumer~relations~between~coarse-grained~functions}$

```

1:

int A[40];

2:

3:

foo0b (...)

4:

5:

6:

* loop0b:

7:

for (i0 = 0 ; i0 <= 3 ; i0++) {

8:

9:

* loop 1b: write A[0..39]

10:

11:

for (i1 = 0 ; i1 <= 39 ; i1++)

12:

A[i1] = \dots

13:

14:

* loop 2b: read A[0..39], write A[0..39]

15:

16:

for (i2 = 0 ; i2 \le 39 ; i2--)

17:

18:

A[i2] = A[i2] ...

19:

* loop 3b: read A[0..39]

20:

21:

for (i3 = 0 ; i3 \le 39 ; i3++)

22:

s = A[i3] \dots

23:

24:

}

```

Figure 3.7 Producer and consumer program regions with the same memory access patterns

source and destination operands of an instruction unambiguously specify which registers are accessed. The set of accessed registers can be easily represented using a bit vector, with each bit corresponding to a register.

When performing data-flow analysis to identify the producer and consumer relation between instructions, we need to check whether two instructions may access the same registers. This checking can be easily done by applying bit-level operations on bit vectors.

On the other hand, a coarse-grained program region can access not only scalar variables, but also arrays and aggregates like structures or unions in the C programs. Using pointer to access dynamically allocated memories only makes the situation worse. In general, we cannot use bit vectors to represent the set of memory locations accessed by a coarse-grained function. Instead, we need to use complicated data structures to repre-

sent the accessed array elements, aggregates and dynamically allocated memories. If the array accesses are irregular, or we cannot figure out exactly which dynamically allocated memories are accessed, at best we can only have an inaccurate but conservatively correct representation.

This inevitably complicates the identification of producer and consumer relation between coarse-grained functions. When performing data-flow analysis, instead of applying bit-level operations on bit vectors, we need to apply complicated procedures on complicated data structures to check whether two coarse-grained functions may access some common memory locations.

There is another difference between accessing an array and accessing a scalar. The access order of array elements could be very useful information, as discussed in next section.

#### 3.3.3.1 Memory Access Order

Consider the program segment in Figure 3.7, which is essentially the same as the example in Figure 3.5 except that loop2a in Figure 3.5 accesses array A from element 39 to element 0, while loop2b in Figure 3.7 accesses array A from element 0 to element 39. Because of this reversal of the array accessing order, loop1b and loop2b in Figure 3.7 not only have a producer and consumer relationship but also have the same access pattern of array A. Similarly, loop2b and loop3b also have the same access pattern of array A. Because of this, the array elements produced by loop1b can be immediately consumed by loop2b, and the array elements produced by loop2b can be immediately consumed

by 100p3b, without the need to buffer the whole array A. This data streaming not only eliminates the buffering overhead but also increases the overlap between the execution of producer and consumer, as illustrated in Figure 3.6(c).

Note that, in Figure 3.4 and Figure 3.5, we use more memory for the communication between producer and consumer pairs to increase the available function parallelism. However, if the communication between producer and consumer can be in streaming fashion, like the one shown in Figure 3.6(c), we can increase the available coarse-grained function parallelism without using additional memory  $^2$ .

Strictly speaking, the data path in Figure 3.6(c) may not be correct, because the output of loop2b may be consumed by program regions outside loop0b. On the other hand, we are certain that the output of loop1b is only consumed by loop2b, because the writes of loop1b are "killed" by the writes of loop2b, and thus will not get exposed outside loop0b. Therefore, when we summarize the memory accesses of a program region, we only need to record the exposed memory accesses. The next section will elaborate on this.

#### 3.3.3.2 Summarizing Exposed Accesses

Consider the program segment in Figure 3.8, which is different from Figure 3.7 in that loop2c reads and writes both array A and array B. However, knowing that loop2c reads array B from element 0 to element 39 will not help find more producers for loop2c, because all the array B elements are produced from within the loop body of loop2c.

<sup>&</sup>lt;sup>2</sup>In this case, we even use less memory.

```

1:

int A[40];

int B[40];

2:

3:

4:

foo0c (...)

5:

6:

7:

* loopOc:

8:

9:

for (i0 = 0 ; i0 \le 3 ; i0++) {

10:

* loop 1c: write A[0..39]

11:

12:

*/

for (i1 = 0; i1 <= 39; i1++)

13:

14:

A[i1] = ...

15:

* loop 2c: read A[0..39], write A[0..39], write B[0..39]

16:

read B[0..39] (not exposed)

17:

18:

*/

for (i2 = 0 ; i2 \le 39 ; i2--) {

19:

B[i2] = A[i2] ...

20:

21:

A[i2] = ... B[i2] ...

22:

23:

* loop 3c: read A[0..39]

24:

25:

*/

26:

for (i3 = 0 ; i3 <= 39 ; i3++)

27:

s = A[i3] \dots

}

28:

```

Figure 3.8 Example illustrating summarization of exposed accesses.

In general, to find the producers and consumers of a program region, we only need to know its *exposed* memory accesses. The exposed memory reads of a program region are the memory reads that are not "covered" by any memory write *executed earlier* within the same program region. The exposed memory writes of a program region are the memory writes that are not "killed" by any memory write *executed later* within the program region.

An exposed read should have some producer *outside* its program region, unless it is an access of some implicitly initialized memory like look-up table. Otherwise the programmer may forget to initialize some memory. On the other hand, an exposed write may or may not have consumers *outside* its program region.

In general, to exactly summarize the *truly* exposed memory accesses of a coarsegrained function is difficult, partly because of the reason discussed at the beginning of Section 3.3.3, and partly because of the difficulty in calculating the addresses of accessed memories.

#### 3.3.3.3 Symbolic Scalar Variable Evaluation

The target language of this research work is the C language. C programs use pointers to reference memory extensively, which causes difficulty in summarizing the exposed memory accesses of program regions.

Take the program segment of foo2d in Figure 3.9 as example, which is simplified from the original source code of the pre-emphasis filter of G.724 decoder [24]. To determine the exposed memory reads of loop2d, we need to know the memory locations accessed by the pointer dereferences \*p and \*q in the loop body. Inter-procedural pointer analysis [140] [141] [142] [103] could tell us that both pointers p and q point to the memory object array A. However this information is not accurate enough for us to deduce that the reads by \*p and \*q at line 20 get their data from outside loop2d, not from the write \*p at line 20. To figure out this, we must know that the assignment statement at line 20 is equivalent to the assignment statement in the comment at line 21. Then we can use dependence test to confirm that there is no true data dependence between the write of \*p and the reads of \*p and \*q at line 20.

```

1:

short A[40];

2:

3:

foo0d ()

4:

5:

6:

foo2d (A, tmp2, 40);

7:

8:

9:

foo2d (short *s, short n, int L)

10:

11:

12:

short *p, *q, temp, i;

13:

p = s + L - 1;

14:

/* p = A + 39 */

15:

16:

/* q = A + 38 */

17:

temp = *p; /* A[39] */

loop2d: for (i = 0 ; i <= L - 2 ; i++) {

18:

19:

*p = *p - *q-- * n;

/* A[39-i] = A[39-i] - A[38-i] * n; */

20:

21:

22:

23:

24:

/* p = A + 0 */

25:

= *p - n * mem_pre;

/* A[0] = A[0] - n * mem_pre; */

26:

27:

mem_pre = temp;

}

28:

```

Figure 3.9 Example illustrating symbolic scalar variable evaluation.

We have discussed the sub-problems we need to solve to extract coarse-grained dataflow from C programs. The next section will outline the proposed program analysis system to solve these problems and the organization of the rest of this dissertation.

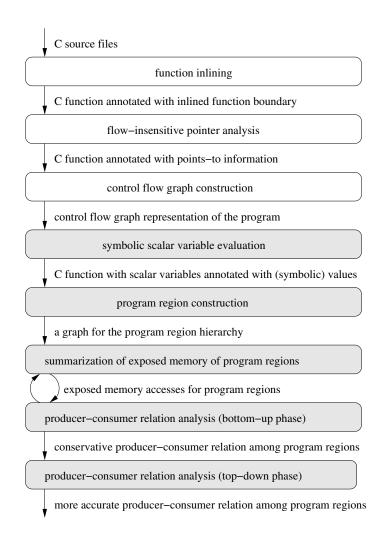

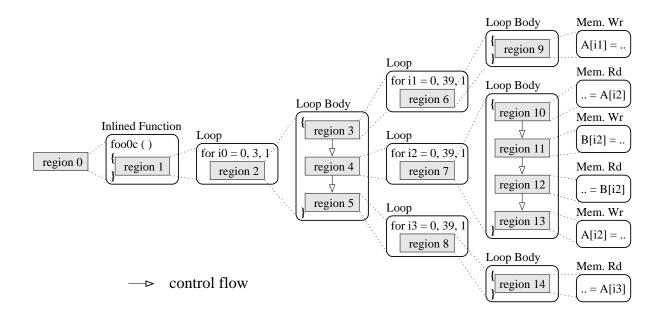

# 3.4 Thesis Organization

The proposed memory data-flow analysis system to extract coarse-grained data-flow from C programs for the exploitation of function parallelism is sketched in Figure 3.10, which shows the components of this program analysis system, as well as the information flow between them. The current implementation first does function in-lining to embed all C source code into the main function. Flow-insensitive pointer analysis [103] is then performed to obtain the set of objects that each pointer may points to. Next, control flow graph is constructed to facilitate the symbolic evaluation of scalar variables, as well as to obtain more accurate pointer information by taking control flow into consideration. The shaded components in Figure 3.10 constitute the main work of this research. The rest of this dissertation will present more detailed discussion on symbolic scalar variable evaluation (Chapter 4), program region construction (Chapter 5), exposed memory accesses summarization (Chapter 6), and producer-consumer relation analysis (Chapter 7). Chapter 8 will discuss the prototyping of the memory data-flow analysis system and the experiment results. Chapter 9 will conclude this dissertation with the obtained insights and some possible future research directions.

Figure 3.10 Components of the proposed memory data-flow analysis system

#### CHAPTER 4

# Symbolic Scalar Variable Evaluation

This chapter will explain how the proposed memory data-flow program analysis system evaluates the symbolic value of each scalar variable, based on SSA form [121] and induction variable detection [143]. The limitation of these algorithms is that they can not go beyond the procedure boundary. To work around this limitation, procedures are in-lined first, as indicated in Figure 3.10.

### 4.1 SSA-based Symbolic Evaluation

Use the program segment in Figure 3.9 as example. After in-lining, we can covert the function foo0d into the SSA form shown in Figure 4.1(a). Note that the variables in Figure 4.1(a) are annotated with different subscripts so that the value of each variable is generated by a single assignment statement. For straight-line code, the single assignment property can be easily obtained by renaming variables. However, in an arbitrary control flow graph, different values of the same variable can reach the same program point via different paths in the control flow graph. To preserve the single assignment property,  $\phi$ -functions are inserted at adequate confluence points in the control flow graph to represent all the possible reaching values using one dummy variable. For example, in Figure 4.1(a),

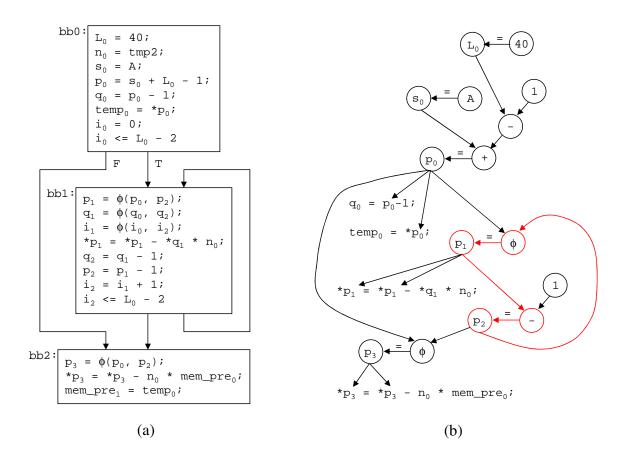

Figure 4.1 Example SSA form nd value flow graph

both values of the variable p,  $p_0$  and  $p_2$ , can reach the beginning of basic block bb1. Therefore, a  $\phi$ -function is inserted at the beginning of basic block bb1 to represent the two possible reaching values  $p_0$  and  $p_2$  using the dummy variable  $p_1$ .

Basically, SSA form is a sparse representation of the value flow between variables. By back-tracking the SSA link, we can do backward substitution to find the symbolic value of a variable. For example, in Figure 4.1(b), we can find the symbolic value of  $p_0$

as follows.

$$\mathbf{p}_0 = (\mathbf{s}_0 + \mathbf{L}_0) - 1$$

$$= (\mathbf{s}_0 + 40) - 1 \quad \text{, given } \mathbf{L}_0 = 40$$

$$= (\mathbf{A} + 40) - 1 \quad \text{, given } \mathbf{s}_0 = \mathbf{A}$$

$$= \mathbf{A} + 39$$

The problem with back-tracking the value flow through SSA links is that there may be cycles in the value flow graph, as the one highlighted in Figure 4.1(b) by red edges. Cycles in value flow graph are caused by reading and writing the same variables within loops. These variables are called induction variables. Induction variables must be handled carefully, otherwise, back-tracking the value flow graph may get trapped in infinite loop.

#### 4.2 Induction Variable Detection

For the detection of induction variables, we use the method invented in [144]. First, we identifies the SCCs (Strongly Connected Components) [145] in the value flow graph. Each SCC is corresponding to an induction variable. The nodes in SCC could be scalar variables, arithmetic operators, and  $\phi$ -functions. If the combination of the operators and  $\phi$ -functions in a SCC matches some predefined patterns, we can determine the symbolic value of each node in the SCC.

Take the SCC, marked with red edges, in Figure 4.1(b) as example. It has two operators: 1) a  $\phi$ -function at the loop header with an operand  $\mathbf{p}_0$  from outside the loop and another operand  $\mathbf{p}_2$  from within the loop; 2) a "—" operator with the second operand

being a constant 1. For this type of SCC, each node in the SCC will be an induction expression with symbolic value of the form d + (-1)h. Here h is called fundamental induction variable [144], which takes the values 0, 1, 2, 3, .... The coefficient of the fundamental induction variable is -1, which means the value of each induction expression in this SCC will decrement by 1 every iteration. Each induction expression in this SCC will have a different offset d, depending on its position in the SCC. Below are the symbolic values of the induction expressions  $p_1$  and  $p_2$ .

$$\begin{array}{lll} {\bf p}_1 & = & {\bf p}_0 + (-1){\bf h} & & , \mbox{ where } {\bf h} = 0, \, 1, \, 2, \, 3, \, \cdots \\ \\ {\bf p}_2 & = & {\bf p}_1 - 1 & & \\ & = & {\bf p}_0 + (-1){\bf h} - 1 & & \end{array}$$

We can further substitute the value of  $p_0$  into the symbolic values of  $p_1$  and  $p_2$  as follows.

$$\mathbf{p}_1 = \mathbf{A} + 39 + (-1)\mathbf{h}$$

, given  $\mathbf{p}_0 = \mathbf{A} + 39$

$$\mathbf{p}_2 = \mathbf{A} + 38 + (-1)\mathbf{h}$$

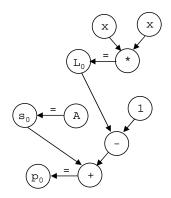

The technique presented in [144] can identify higher-order induction variables which can be represented as polynomials of the fundamental induction variable. For the current implementation, we only represent symbolic values as affine expressions of the form  $d+c\cdot h$ , where h is the fundamental induction variable, c is an integer constant, and d can be either an integer constant or a scalar variable. Back-tracking will proceed in the value flow graph until any non-affine term is encountered. For example, in Figure 4.2, back-

Figure 4.2 Example illustrating non-affine expressions

tracking will stop before  $L_0=x*x$ . The symbolic value of  $p_0$  will be represented as  $A+L_0-1$ , without further expanding  $L_0$  into x\*x.

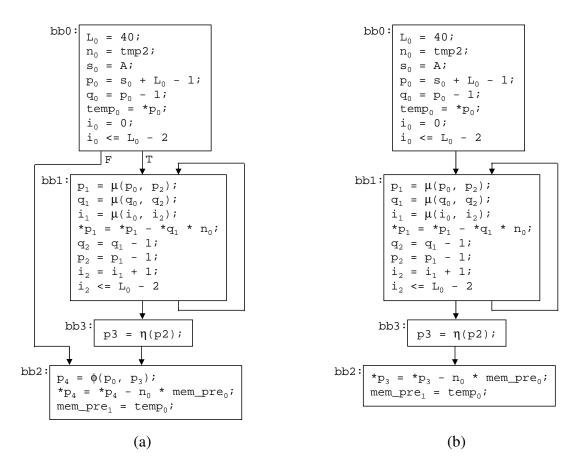

### 4.3 SSA Extension

Symbolic evaluation only based on SSA form has its limitation. For example, in Figure 4.1, the SSA form only tell us that the value of  $p_3$  can be either  $p_0$  or  $p_2$ . Note that the value of  $p_3$  could be  $p_0$  only if the branch at the end of the basic block bb0 is not taken. However, the branch at the end of the basic block bb0 is always taken, because its branch condition  $i_0 \le L_0 - 2$  is always true. (The value of  $i_0$  is 0, and the value of  $L_0$  is 40.) Therefore, the value of  $p_3$  is actually equal to  $p_2$ .

Furthermore,  $p_2$  is an induction variable, and thus can take more than one values.  $p_3$  should take the *last* value of  $p_2$  when the loop terminates, because  $p_3$  is outside the loop, while  $p_2$  is inside the loop. However, we can not figure out this using the SSA representation. The fundamental problem of SSA form is that it retains only data flow

Figure 4.3 Example gated SSA form and pruned control flow graph

information but no control flow information. The  $\phi$ -function contains no information to determine which of the reaching values it should take. To remedy this problem, people has extended SSA form to gated SSA form [123].

In gated SSA form,  $\phi$ -function is augmented with predicate for the selection of possible reaching values. Special  $\phi$ -functions called  $\mu$ -functions and  $\eta$ -functions are placed at loop entry and loop exits. A  $\mu$ -function has two operands. The output of a  $\mu$ -function will take the value of the first operand for the first loop iteration, and the value of the second operand for the remaining loop iterations. The value of a  $\eta$  function is the value of the

corresponding variable when control reaches the corresponding loop exit. Figure 4.3(a) shows the corresponding gated SSA form of Figure 4.1(a). For clarity, it does not show the predicates in  $\phi$ -functions,  $\mu$ -functions and  $\eta$ -functions. Note that a dummy basic block is inserted at the loop exit to facilitate the insertion of  $\eta$ -functions.

The implementation and interpretation of gated SSA form is complicated. For the symbolic evaluation of scalar variables in the prototype memory data-flow analysis system, we implemented a simplified version of gated SSA form. To ease the job of identifying induction variables and calculating their loop-exit values, we extended the SSA form with  $\mu$ -functions and  $\eta$ -functions, but without having predicates in  $\phi$ -functions,  $\mu$ -functions and  $\eta$ -functions. Without resorting to predicate evaluation, we can still prune the control flow graph by checking whether some branch conditions are always true or always false.

For the control flow graph in Figure 4.3(a), the false-branch at the end of basic block bb0 is never taken, so we can prune this edge and obtain the simplified control flow graph in Figure 4.3(b). After pruning the false-branch edge at the exit of basic block bb0, we can also prune the the  $\phi$ -function at the beginning of basic block bb2, because now the control can reach basic block bb2 only through bacic block bb3. This can be accomplished by re-constructing the SSA form using the pruned control flow graph  $^{1}$ .