#### University of Wisconsin Milwaukee

## **UWM Digital Commons**

Theses and Dissertations

May 2021

# Modular Multilevel Converters with Module-Level Energy Storage for Medium Voltage Applications

Bora Novakovic University of Wisconsin-Milwaukee

Follow this and additional works at: https://dc.uwm.edu/etd

Part of the Electrical and Electronics Commons

#### **Recommended Citation**

Novakovic, Bora, "Modular Multilevel Converters with Module-Level Energy Storage for Medium Voltage Applications" (2021). Theses and Dissertations. 2708. https://dc.uwm.edu/etd/2708

This Dissertation is brought to you for free and open access by UWM Digital Commons. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of UWM Digital Commons. For more information, please contact scholarlycommunicationteam-group@uwm.edu.

# MODULAR MULTILEVEL CONVERTERS WITH MODULE-LEVEL ENERGY STORAGE FOR MEDIUM VOLTAGE APPLICATIONS

by

Bora Novakovic

A Dissertation Submitted in

Partial Fulfillment of the

Requirements for the Degree of

Doctor of Philosophy

in Engineering

at

The University of Wisconsin - Milwaukee  ${\rm May}\ 2021$

#### ABSTRACT

# MODULAR MULTILEVEL CONVERTERS WITH MODULE-LEVEL ENERGY STORAGE FOR MEDIUM VOLTAGE APPLICATIONS

bv

#### Bora Novakovic

The University of Wisconsin-Milwaukee, 2021 Under the Supervision of Professor Adel Nasiri

This dissertation is on Modular Multilevel Converter (MMC) converter design and analysis and its integration with energy storage at the low voltage module-level. The developed converter concept and topology can be used in various applications especially for the support of intermittent renewable energy resources. The general converter structure is analyzed and extended to include integrated energy storage suitable but not limited to medium voltage applications. The behavior of the idealized structure is analyzed to obtain equations that govern general converter behavior and identify possible control loops. Detail mathematical switching model is developed for the MMC converter with generalized module structure. The switching model is averaged to obtain a large signal model and then reduced to obtain lower order models suitable for sizing and optimization. Open and compensated closed loop current control is proposed and extended to include feedback loops needed for full control of integrated energy storage. General sizing procedure with the optimization aspects is then proposed and used on the example system to obtain the converter structure parameters. The example system models are then used to fine tune the control and structure parameters and investigate the converter behavior.

©Copyright by Bora Novakovic, 2021 All Rights Reserved

# TABLE OF CONTENTS

| 1 | Intr            | oduction                                   | 1    |

|---|-----------------|--------------------------------------------|------|

|   | 1.1             | Problem Statement                          | . 1  |

|   | 1.2             | Motivation                                 | . 2  |

|   |                 | 1.2.1 Large Wind Energy Systems            | . 2  |

|   |                 | 1.2.2 Renewable Energy and Storage Systems | . 4  |

|   |                 | 1.2.3 Medium Voltage Wind Energy Systems   | . 6  |

|   |                 | 1.2.4 Multilevel Converters and MMC        | . 8  |

| 2 | $\mathbf{Lite}$ | rature background                          | 10   |

|   | 2.1             | MMC Background                             | . 11 |

|   | 2.2             | MMC Applications and Modifications         | . 18 |

|   |                 | 2.2.1 Grid Support Applications            | . 19 |

|   |                 | 2.2.2 Grid Inter-tie Applications          | . 19 |

|   |                 | 2.2.3 HVDC Applications                    | . 21 |

|   |                 | 2.2.4 Medium Voltage Drives                | . 26 |

|   |                 | 2.2.5 DC to DC Conversion Systems          | . 30 |

|   |                 | 2.2.6 Applications Solar PV Systems        | . 32 |

|   |                 | 2.2.7 Converters for Wind Energy Systems   | . 34 |

|   |     | 2.2.8 Energy storage applications                   | 35 |

|---|-----|-----------------------------------------------------|----|

|   | 2.3 | Renewable Energy, Energy Storage and Grid Tie Codes | 40 |

|   |     | 2.3.1 Renewable Energy and Grid Connection Code     | 40 |

|   |     | 2.3.2 Energy Storage and Grid Connection Codes      | 43 |

|   | 2.4 | Wind Energy Systems and Energy Storage              | 44 |

|   | 2.5 | Conclusion of Background                            | 48 |

| 3 | Ter | minology                                            | 48 |

|   | 3.1 | Naming Rules                                        | 50 |

| 4 | Bas | ic Equations for MMC Converter Leg                  | 54 |

|   | 4.1 | Modulation Index Definition                         | 58 |

|   | 4.2 | Circuit Equations                                   | 63 |

|   | 4.3 | Arm Voltage References                              | 68 |

|   | 4.4 | Power Flow                                          | 70 |

|   |     | 4.4.1 General Equations                             | 70 |

|   |     | 4.4.2 Converter Arm Power Balance                   | 75 |

|   | 4.5 | Low Switching Frequency Considerations              | 82 |

| 5 | Con | nverter Model                                       | 83 |

|   | 5.1 | Converter Module Equations                          | 85 |

|   |     | 5.1.1 Implementation #1 Module Equations            | 86 |

|   |     | 5.1.2 Implementation #2 Module Equations            | 87 |

|   |     | 5.1.3 Implementation #3 Module Equations            | 89 |

|   | 5.2 | Converter Arm Equations                          | 90  |

|---|-----|--------------------------------------------------|-----|

|   | 5.3 | Integrated Switching Model                       | 97  |

|   | 5.4 | Large Signal Model                               | 102 |

|   |     | 5.4.1 MMC Modulation Aspects                     | 103 |

|   |     | 5.4.2 Linear Ripple Approximation Generalization | 107 |

|   |     | 5.4.3 Large Signal System Model Matrices         | 115 |

|   |     | 5.4.4 Large Signal State Space Equation          | 122 |

|   |     | 5.4.5 Modulation Index Average                   | 125 |

|   | 5.5 | Reduced Average Model                            | 127 |

| 6 | Con | ntrol                                            | 133 |

|   | 6.1 | Control Model Equations                          | 134 |

|   | 6.2 | dq Frame of Reference and Transformations        | 136 |

|   | 6.3 | Control Model Equations in DQ frame              | 141 |

|   | 6.4 | Open Loop Control                                | 151 |

|   | 6.5 | Closed Loop Control                              | 165 |

|   | 6.6 | Modulation Index References                      | 174 |

|   | 6.7 | Balancing                                        | 174 |

|   |     | 6.7.1 Module Balancing                           | 175 |

|   |     | 6.7.2 Arm Balancing                              | 178 |

|   | 6.8 | Poly-phase System Considerations                 | 179 |

| 7 | Con | nverter Sizing                                   | 181 |

|   | 7 1 | General System Parameters                        | 181 |

| 7.2 | Exam   | ple System Parameters                        | 18  |

|-----|--------|----------------------------------------------|-----|

| 7.3 | Design | n constraints                                | 187 |

|     | 7.3.1  | Voltage Reach of the Converter Arm           | 188 |

|     | 7.3.2  | Module DC Voltage                            | 190 |

|     | 7.3.3  | Storage Power Rating                         | 190 |

|     | 7.3.4  | Storage Energy Rating                        | 191 |

|     | 7.3.5  | Energy Storage Current                       | 191 |

|     | 7.3.6  | THD and Ripple                               | 192 |

|     | 7.3.7  | Constrain and Variable Summary               | 193 |

| 7.4 | Conve  | rter Sizing - Approximation Approach         | 193 |

|     | 7.4.1  | Example System Results                       | 194 |

| 7.5 | Conve  | erter Sizing - Optimization                  | 194 |

|     | 7.5.1  | Example System Results                       | 196 |

| 7.6 | Modu   | le Filter - Approximation Design             | 198 |

|     | 7.6.1  | Example System Approximation Results         | 206 |

| 7.7 | Modu   | le Filter - Model Based Optimization Design  | 207 |

|     | 7.7.1  | Example System Optimization Approach Results | 212 |

| 7.8 | Arm I  | nductors                                     | 216 |

|     | 7.8.1  | Ripple Based Approximation Limits            | 218 |

|     | 7.8.2  | Example System Arm Inductance                | 220 |

| Sim | ulatio | n Results and Related Considerations         | 221 |

|     |        |                                              |     |

| 8 1 | Arm I  | Balance Verification and Tuning              | 229 |

8

|                  | 8.2              | Module Balance Verification and Tuning              | 226 |

|------------------|------------------|-----------------------------------------------------|-----|

|                  | 8.3              | Switching Model Simulation Results                  | 232 |

|                  | 8.4              | Module Stability Considerations                     | 246 |

|                  | 8.5              | Low Voltage Ride Through and Reactive Power Support | 250 |

| 9                | Con              | clusion                                             | 258 |

| $\mathbf{R}_{0}$ | eferences        |                                                     | 260 |

| Cı               | Curriculum Vitae |                                                     | 280 |

# LIST OF FIGURES

| 1 | Power conversion system arrangement inside the common low-voltage high-              |    |

|---|--------------------------------------------------------------------------------------|----|

|   | power wind turbine. To achieve desired power level, the power electronics            |    |

|   | converters are usually paralleled                                                    | 7  |

| 2 | Power conversion system arrangement inside the proposed medium voltage               |    |

|   | high power wind turbine. To achieve desired power and voltage levels, Mod-           |    |

|   | ular Multilevel Converter (MMC) converter modules are connected in series.           | 10 |

| 3 | Multilevel structure proposed by Hammond for the use in medium voltage               |    |

|   | drives [1]. In this case proposed output voltage is 2400V and the cells operate      |    |

|   | at standard 480V                                                                     | 13 |

| 4 | Cascade multilevel structure first proposed by Peng et al. (a) - Module struc-       |    |

|   | ture. (b) - Y-connected converter configuration. (c) - $\Delta$ -connected converter |    |

|   | configuration.                                                                       | 14 |

| 5 | Back-to-back structure implemented with MMC converters with the DC bus               |    |

|   | proposed by Marquardt et al. and named Modular MultiLevel Converter                  |    |

|   | $(M^2LC)$ by the authors. (a) - Half bridge module (cell) structure. (b) - MMC       |    |

|   | back to back structure showing the substructures commonly called "converter          |    |

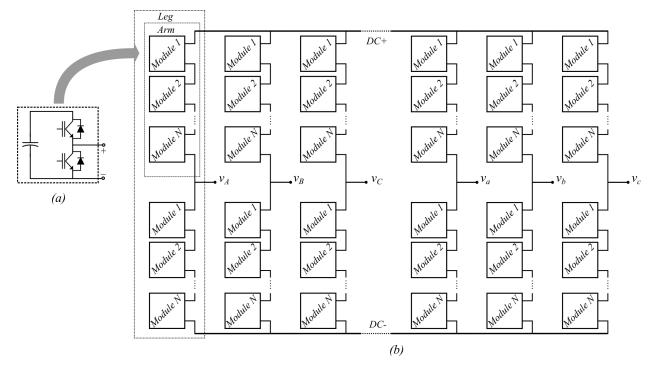

|   | arm" and "converter leg" in MMC terminology.                                         | 16 |

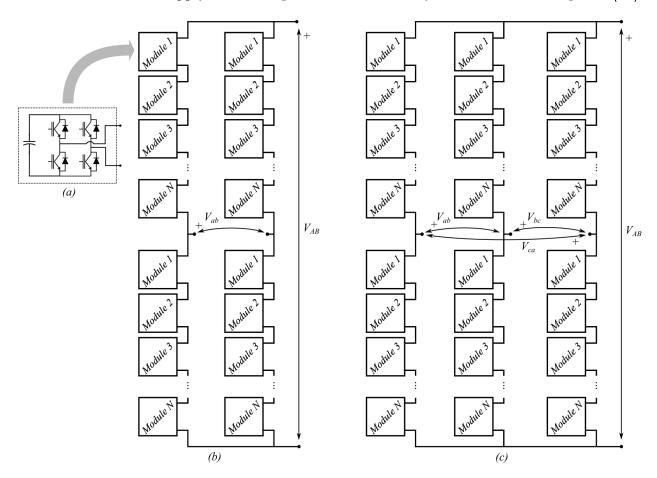

| 6  | Structure of the AC to AC MMC topology without the DC bus proposed by                  |    |

|----|----------------------------------------------------------------------------------------|----|

|    | Glinka and Marquardt.(a) - Module (cell) structure. (b) - Single phase AC to           |    |

|    | AC converter. (c) - MMC 3-phase AC to AC structure                                     | 20 |

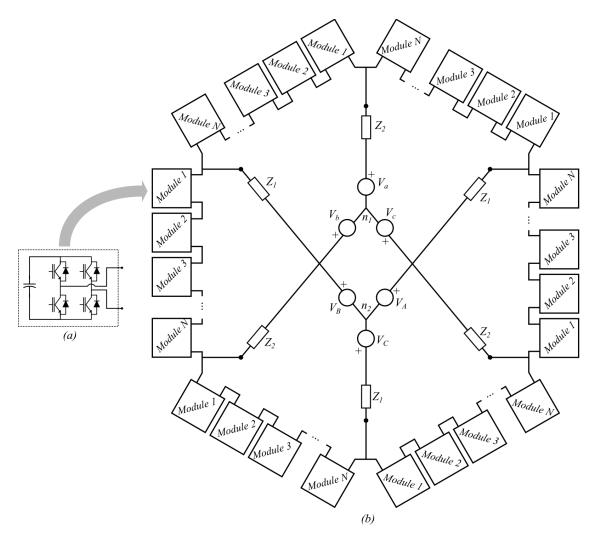

| 7  | MMC based 3-phase AC to AC converter structure known as Hexverter [2]                  | 22 |

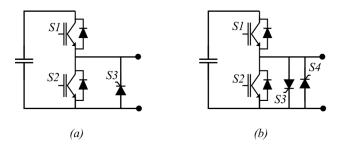

| 8  | Simple fault capable modules. (a) - Half bridge module with the fault bypass           |    |

|    | thyristor. (b) - Fast fault recovery module modification proposed by Li et al. [3]     | 25 |

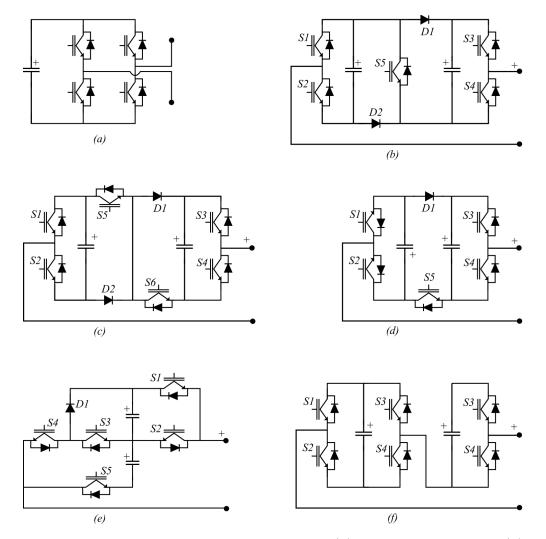

| 9  | Some of the fault tolerant module topologies: (a) - Full-bridge module. (b)            |    |

|    | - Clamp-double module. (c) - Three-level module. (d) - Series connected                |    |

|    | double module. (e) - T-Type module. (f) - Mixed module                                 | 27 |

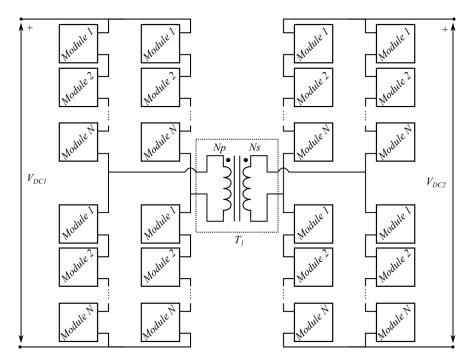

| 10 | Isolated dual active bridge DC to DC converter implemented with MMC struc-             |    |

|    | tures                                                                                  | 31 |

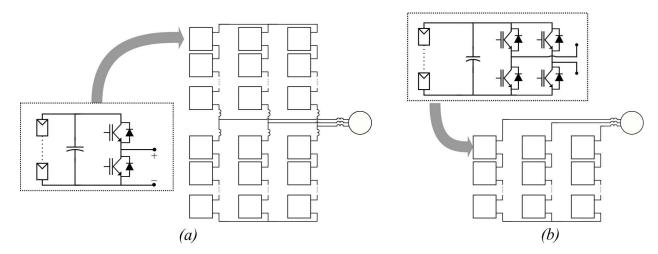

| 11 | (a) - Integration of solar panels directly in the DC bus of the MMC module.            |    |

|    | (b) - Integration of the solar panels into the modules of Cascaded H-Bridge            |    |

|    | (CHB) converter                                                                        | 33 |

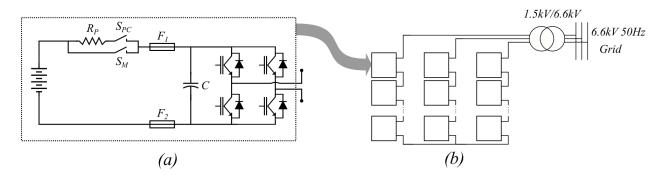

| 12 | CHB based energy storage system proposed by Kawakami et al. [4]. (a) -                 |    |

|    | Integration of battery energy storage directly in the DC bus of the MMC                |    |

|    | module. $R_p$ , $S_{PC}$ and $S_M$ make the module DC bus precharge circuit. $F_1$ and |    |

|    | $F_2$ are standard low voltage DC fuses. (b) - Overall system topology named           |    |

|    | Modular Multilevel Cascaded Converter (MMCC) by the authors                            | 37 |

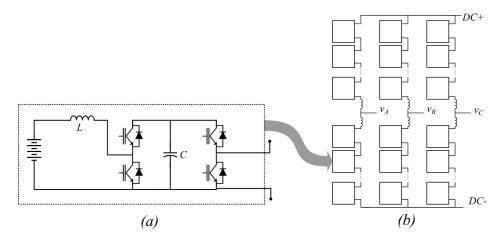

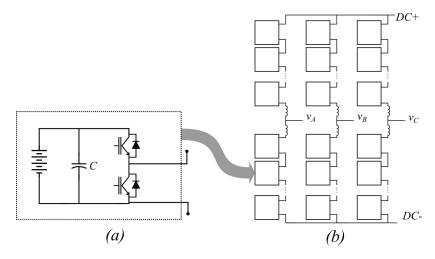

| 13 | $M^2LC$ based energy storage system with the energy storage integrated into            |    |

|    | the module CD bus through a DC to DC converter. (a) - Integration of battery           |    |

|    | energy storage in the DC bus of the converter module. (b) - Overall system             |    |

|    | topology (3-phase case)                                                                | 38 |

| 14 | $M^2LC$ based energy storage system with the energy storage integrated directly  |    |

|----|----------------------------------------------------------------------------------|----|

|    | into the module DC bus. (a) - Integration of battery energy storage in the       |    |

|    | DC bus of the converter module. (b) - Overall system topology (3-phase case).    | 38 |

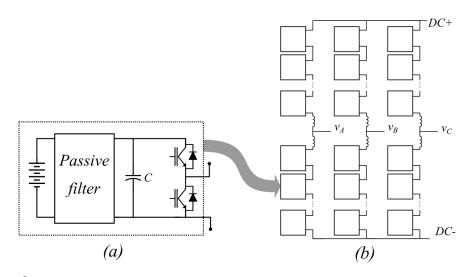

| 15 | $M^2LC$ based energy storage system with the energy storage integrated into      |    |

|    | the module DC bus through a passive filter. (a) - Integration of battery energy  |    |

|    | storage in the DC bus of the converter module. (b) - Overall system topology     |    |

|    | (3-phase case)                                                                   | 39 |

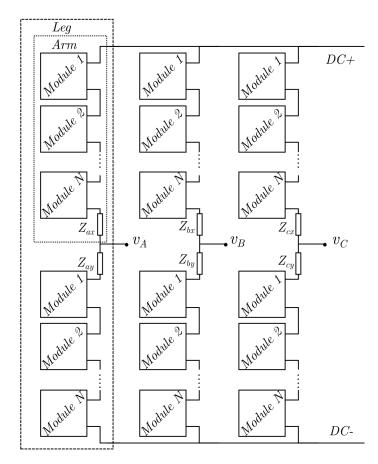

| 16 | High level representation of the three phase MMC structure with DC bus           |    |

|    | showing the main building blocks of the converter: legs, arms and modules .      | 49 |

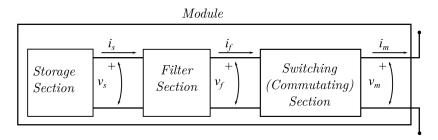

| 17 | Generalized structure of the MMC module and its building blocks: switching       |    |

|    | section, filter section and optional storage section                             | 50 |

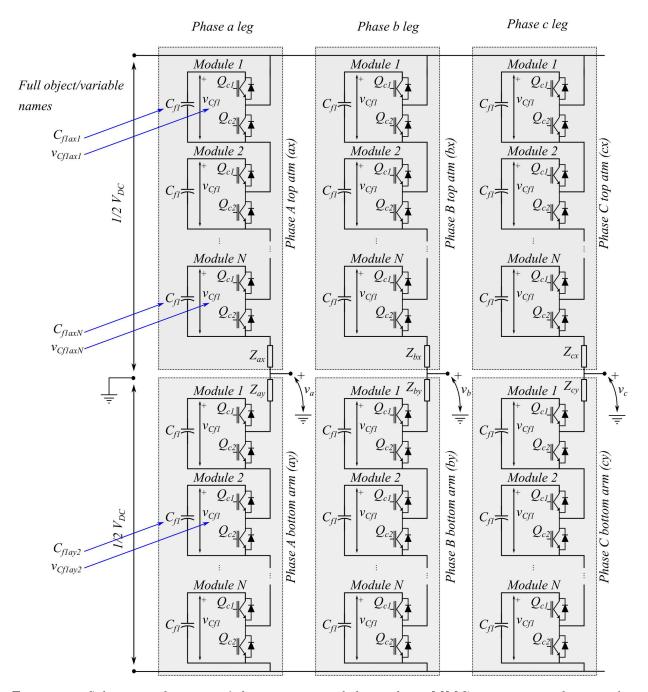

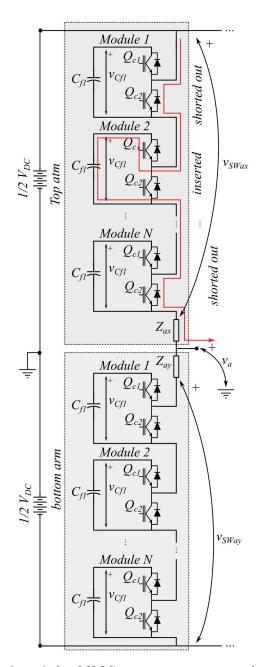

| 18 | Schematic diagram of the conventional three-phase MMC converter with ex-         |    |

|    | amples of the abbreviated and full names used for the components and vari-       |    |

|    | ables in equations.                                                              | 53 |

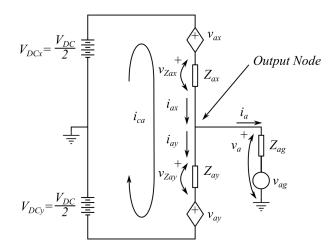

| 19 | Single phase leg of the MMC converter connected to the infinite DC bus           | 55 |

| 20 | Simplified model of the idealized phase leg of the MMC converter                 | 58 |

| 21 | Phasor diagrams for the leg currents and its output and circulating current      |    |

|    | representations for the fundamental frequency. (a) - For the circulating current |    |

|    | with arbitrary phase. (b) - For the circulating current in phase with output     |    |

|    | current                                                                          | 64 |

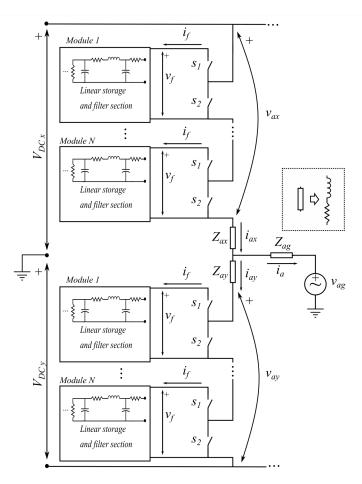

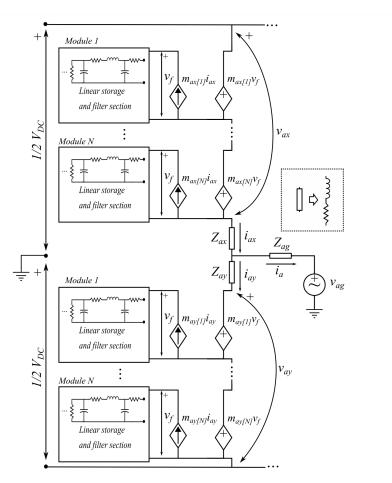

| 22 | General structure of the MMC converter leg. Module structure is arbitrary        |    |

|    | as long as it gives well filtered filter section output $v_f$                    | 84 |

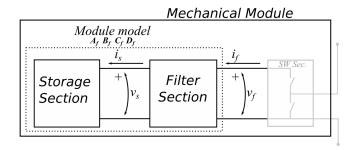

| 23 | General structure of the MMC converter module. The switching section is         |      |

|----|---------------------------------------------------------------------------------|------|

|    | modeled within the converter arm equations, as a result, the module is illus-   |      |

|    | trated with switching section grayed out                                        | 85   |

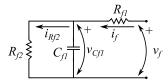

| 24 | Circuit diagram of a generic MMC module. Resistance model internal resis-       |      |

|    | tance of the capacitor bank and leakage/balancing circuit                       | 86   |

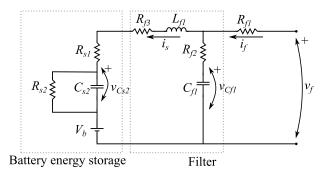

| 25 | Circuit diagram of the module with integrated battery energy storage. Battery   |      |

|    | energy storage is modeled                                                       | 88   |

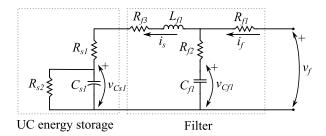

| 26 | Circuit diagram of the module with integrated ultra-capacitor energy storage.   | 89   |

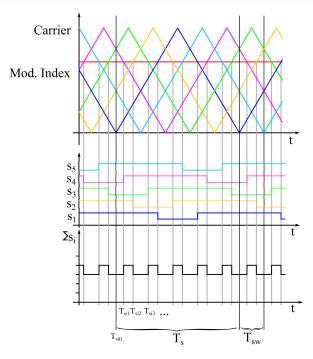

| 27 | Ideal phase-shifted Pulse Width Modulation (PWM). The graphs illustrate:        |      |

|    | carrier, approximately constant modulation index, individual module PWM         |      |

|    | and aggregate output PWM for 5 level modulator. The color of the signals        |      |

|    | show correlation between carrier and module PWM                                 | 105  |

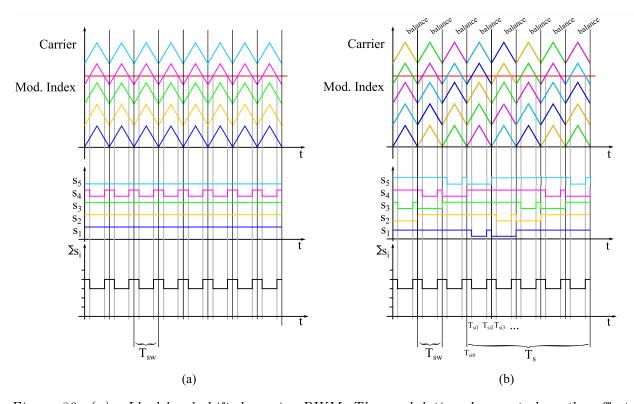

| 28 | (a) - Ideal level-shifted carrier PWM. The modulation does not show the ef-     |      |

|    | fects of balancing algorithm. (b) - Level-shifted carrier modulation. The color |      |

|    | of the signals show correlation between carrier and module PWM. Modula-         |      |

|    | tion index is shown constant which is approximately true for high switching     |      |

|    | frequencies.                                                                    | 106  |

| 29 | The circuit diagram for the averaged MMC model given in Equation 149            | 123  |

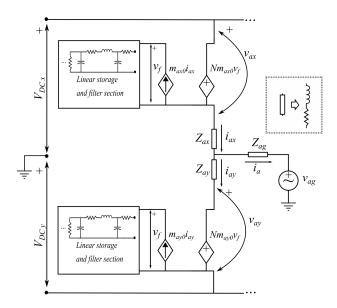

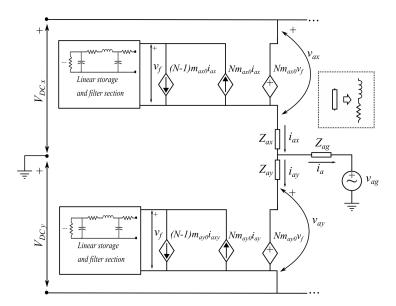

| 30 | Circuit representation of the reduced linearized model given in Equation (169)  | .133 |

| 31 | Alternate circuit representation of the reduced linearized model given in Equa- |      |

|    | tion (169). The extra current source models the remaining N-1 modules. All      |      |

|    | modules heheve the same                                                         | 13/  |

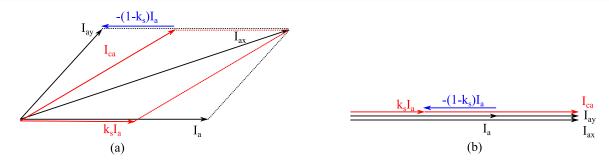

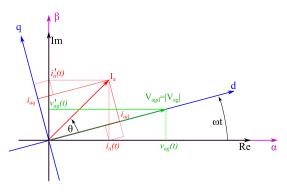

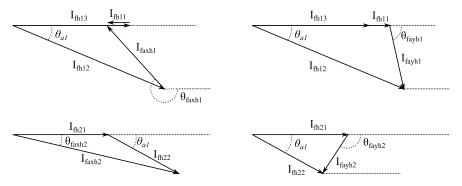

| 32 | ad frame of reference and its relation to the voltage and current phasor. Sim-        |      |

|----|---------------------------------------------------------------------------------------|------|

|    | ilar triangles used to obtain the transformation matrix in (181) are outlined         |      |

|    | as well                                                                               | 138  |

| 33 | Open loop current controller for the MMC converter leg described in equations         |      |

|    | (229) and (221). White blocks are matrix multiplications and grey blocks are          |      |

|    | subsystems. Wide connection strips represent vectors and line represent scalars       | .158 |

| 34 | Simulink model of the simplified converter leg. The controller CTRL structure         |      |

|    | is shown in Figure 33                                                                 | 159  |

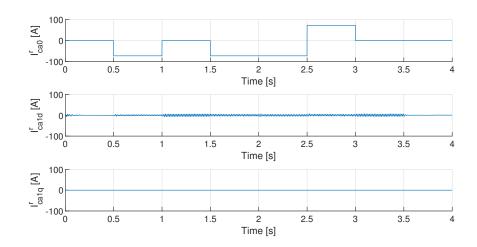

| 35 | References given to the open loop controller. From top to bottom plot the             |      |

|    | references are: circulating current DC component, circulating current funda-          |      |

|    | mental d component, circulating current fundamental q component, output               |      |

|    | current fundamental d component, output current fundamental q component.              |      |

|    | Note that the $v_{ag0}$ is omitted in this and all other figures to save space. It is |      |

|    | set to be constant zero in in reference and feedback vectors                          | 160  |

| 36 | Measured outputs of the converter model in dq frame of reference. From top to         |      |

|    | bottom the measurements are: circulating current DC component, circulating            |      |

|    | current fundamental d component, circulating current fundamental q compo-             |      |

|    | nent, output current fundamental d component, output current fundamental              |      |

|    | q component                                                                           | 161  |

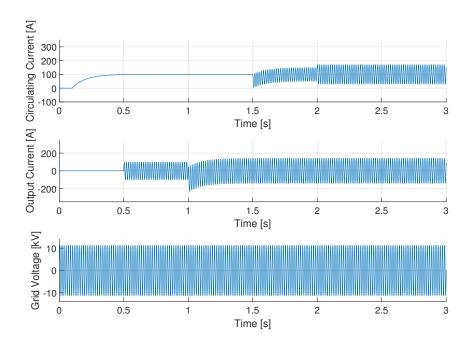

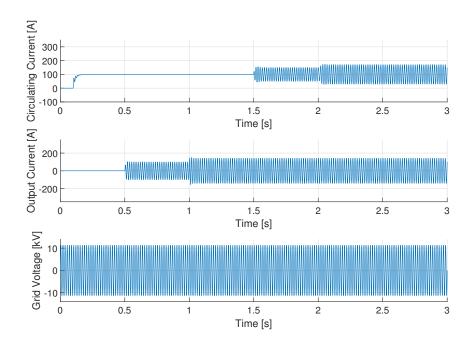

| 37 | Measured outputs of the converter model. First plot is the circulating current,       |      |

|    | second is output current and third is the grid emf                                    | 162  |

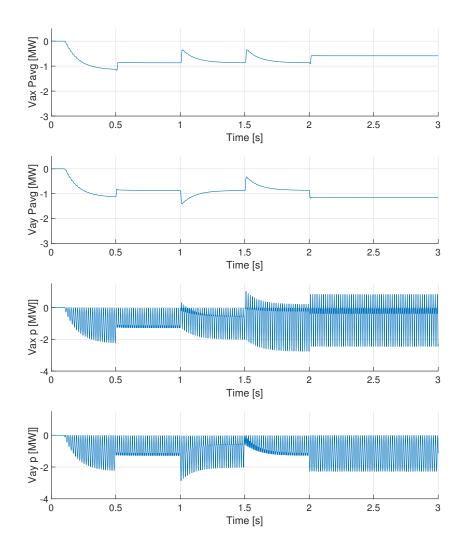

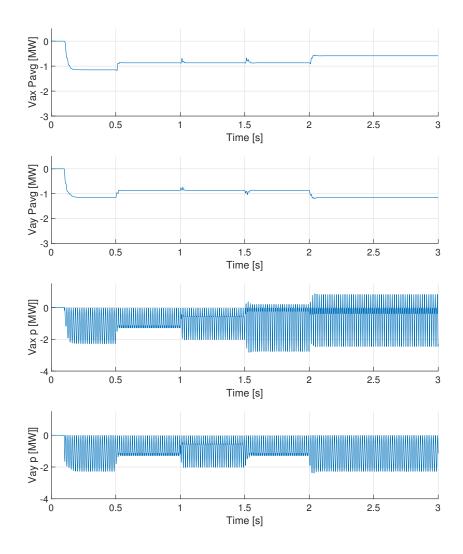

| 38 | Output power of the arm generators. From top to bottom the plots are: av-                |     |

|----|------------------------------------------------------------------------------------------|-----|

|    | erage power of the upper arm generator $v_{ax}$ , average power of the lower arm         |     |

|    | generator $v_{ay}$ , instantaneous power of the upper arm generator $v_{ax}$ , instanta- |     |

|    | neous power of the lower arm generator $v_{ay}$                                          | 163 |

| 39 | Active and reactive power flowing from the converter to the grid                         | 164 |

| 40 | Upper and lower arm voltage references in $\alpha\beta$ time domain                      | 165 |

| 41 | Block diagram for the closed loop controller. The controller includes feed               |     |

|    | forward control and closed loop feedback compensator $K_{fb}$ for appropriate            |     |

|    | pole placement                                                                           | 167 |

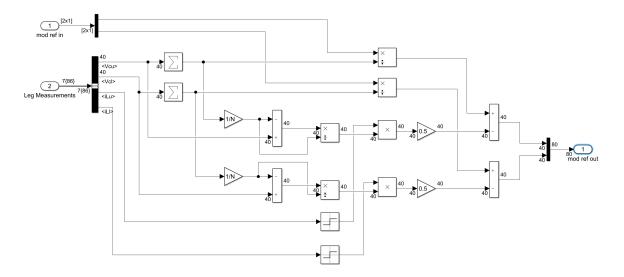

| 42 | Simulink model of the closed loop controller shown in Figure 41 and used to              |     |

|    | control the model shown in Figure 34                                                     | 168 |

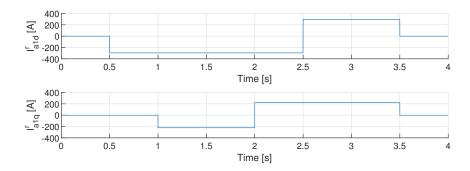

| 43 | Current reference vector components on dq frame of reference for the close               |     |

|    | loop control simulation. For more information look at the corresponding open             |     |

|    | loop control references given in Figure 35                                               | 169 |

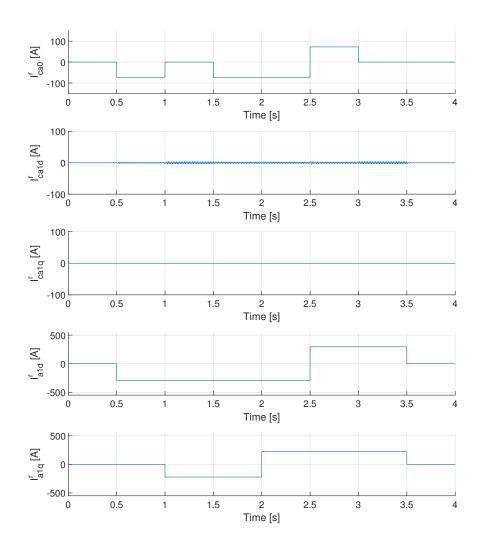

| 44 | Current measurement vector components in dq frame of reference. For more                 |     |

|    | information and comparison look at the corresponding open loop current mea-              |     |

|    | surements given in Figure 36                                                             | 170 |

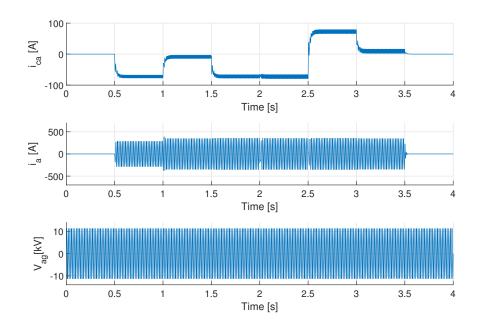

| 45 | Circulating current, output current and grid voltage measurements in natural             |     |

|    | $\alpha\beta$ frame of reference. For more information and comparison look at the        |     |

|    | corresponding open loop measurements given in Figure 37                                  | 171 |

| 46 | Output power of the arm generators. For more information and comparison                  |     |

|    | look at the corresponding open loop measurements given in Figure 38                      | 172 |

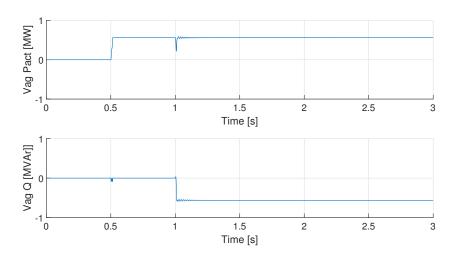

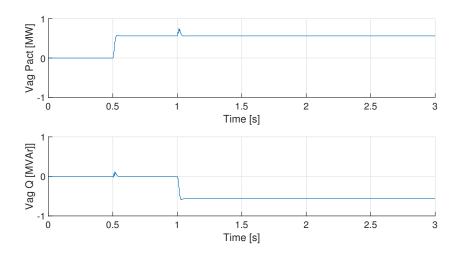

| 47 | Active and reactive power flowing from the converter to the grid. For com-          |     |

|----|-------------------------------------------------------------------------------------|-----|

|    | parison with open loop behavior look at Figure 39                                   | 173 |

| 48 | Upper and lower arm voltage references in $\alpha\beta$ time domain. For comparison |     |

|    | with open loop behavior look at Figure 40                                           | 173 |

| 49 | Block diagram for module state of charge balancing and generation of normal-        |     |

|    | ized modulation indexes. Wide lines represent vectors of width N and thin           |     |

|    | lines are scalars                                                                   | 178 |

| 50 | Block diagram for the balancing of arm state of charges within one leg of the       |     |

|    | converter                                                                           | 179 |

| 51 | (a) - Fault Ride Through requirements for large wind energy system meeting          |     |

|    | all the requirements listed in [5]. (b) - Assumed power delivery profile. Energy    |     |

|    | storage rating can be obtained bu calculating the red shaded surface area           | 186 |

| 52 | Module filter section inputs and outputs                                            | 198 |

| 53 | Phasor diagrams for fundamental and first harmonic components of the filter         |     |

|    | input current $i_f$                                                                 | 204 |

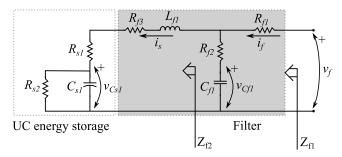

| 54 | Module model for the Example System from Table 3 and Table 7. The filter            |     |

|    | section is shaded                                                                   | 205 |

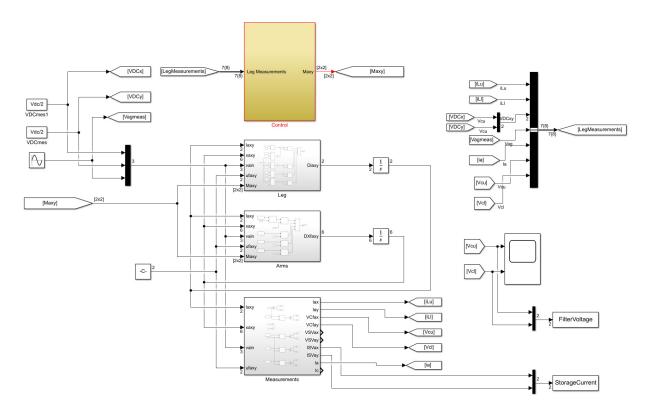

| 55 | Reduced order model top level                                                       | 209 |

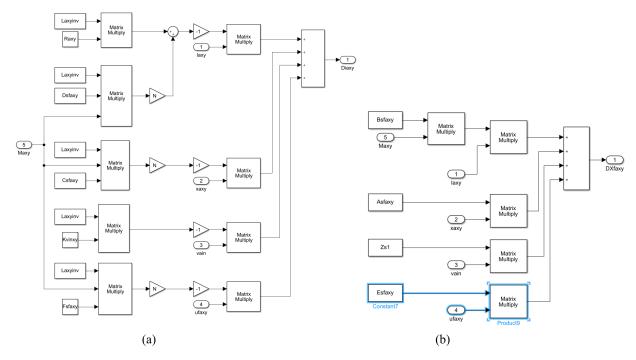

| 56 | (a) - Structure of the Leg block. (b) - Structure of the Arm block                  | 210 |

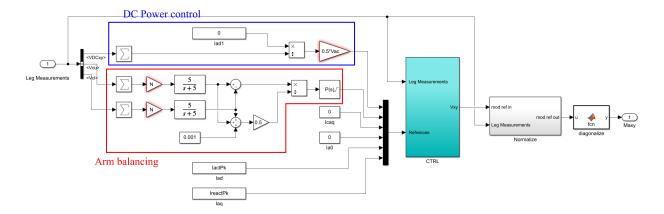

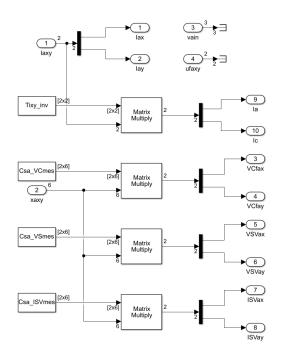

| 57 | Control block structure                                                             | 211 |

| 58 | Measurement block structure                                                         | 211 |

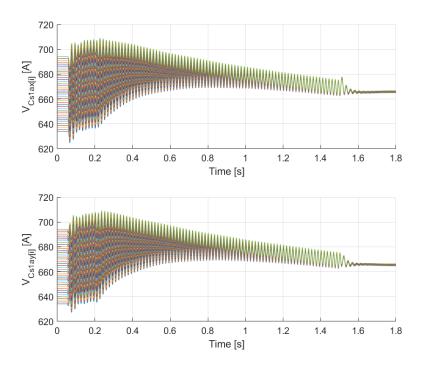

| 59 | Simplified model simulation results - Control references                            | 213 |

| 60 | Simplified model simulation results - Output currents and grid voltage              | 214 |

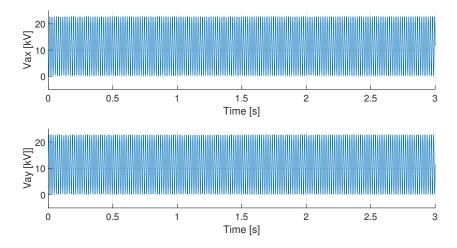

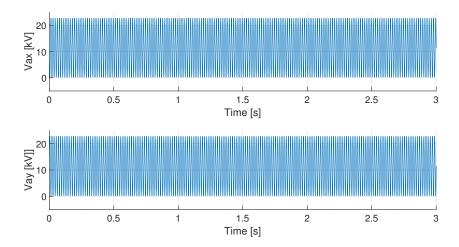

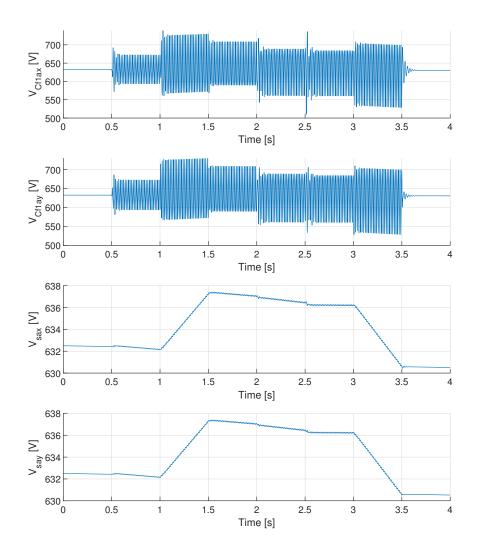

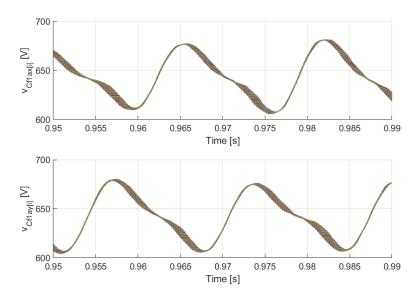

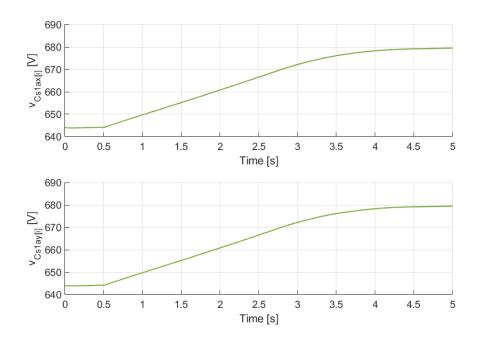

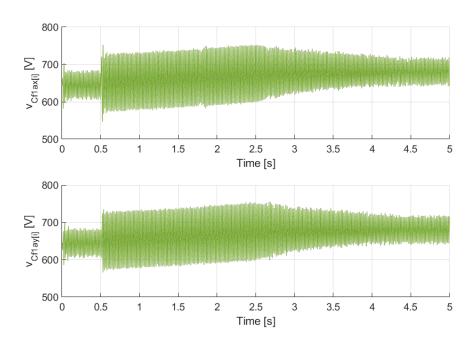

| 61 | Voltage of the module filter section for upper and lower arm and module       |     |

|----|-------------------------------------------------------------------------------|-----|

|    | module storage systems of upper and lower arm                                 | 215 |

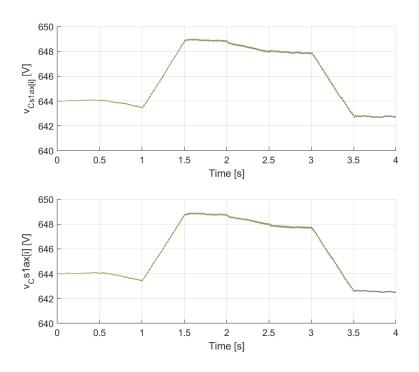

| 62 | RMS currents for the storage system current for upper and lower arm and       |     |

|    | waveforms of the storage system currents for upper and lower arms             | 216 |

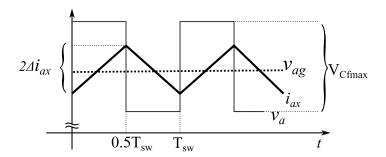

| 63 | Arm current ripple illustration                                               | 218 |

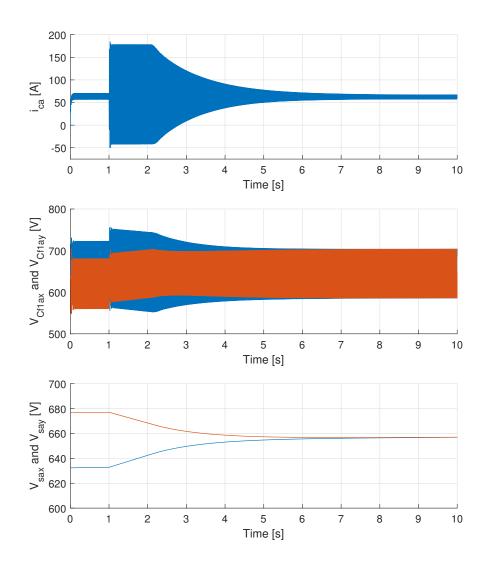

| 64 | From top to bottom: circulating current and upper and lower arm module        |     |

|    | filter voltages and upper and lower arm storage voltages. AC/DC power         |     |

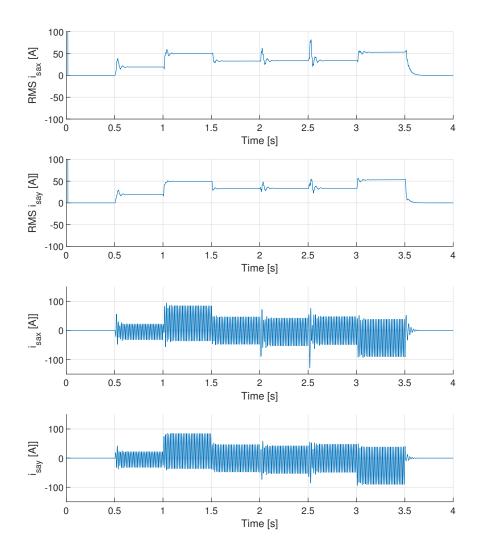

|    | balance is maintained                                                         | 223 |

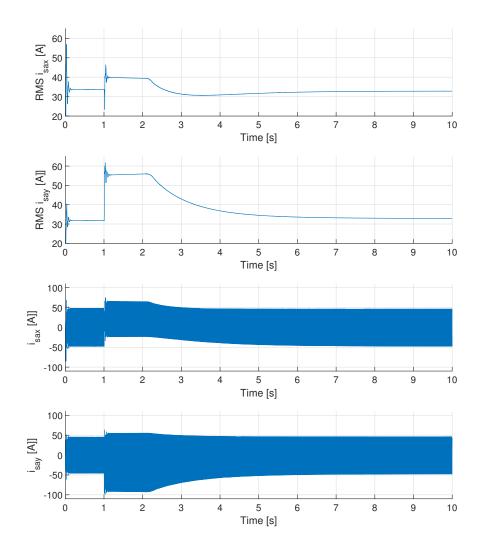

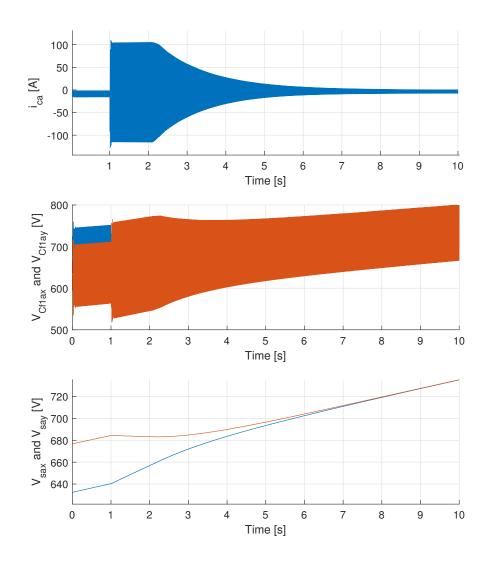

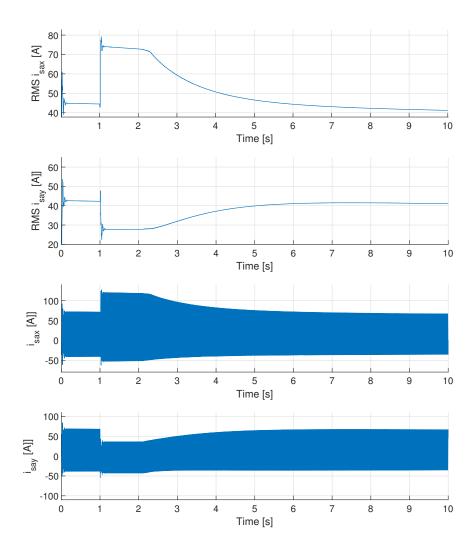

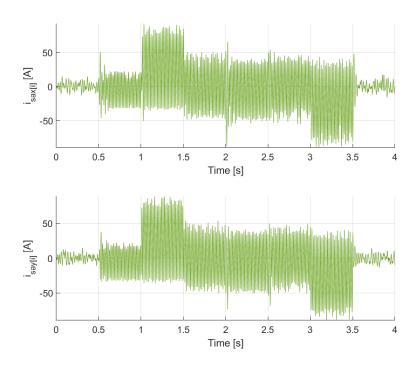

| 65 | Storage current RMS are shown in upper two plots and waveforms on the         |     |

|    | lower two plots. AC/DC power balance is maintained                            | 224 |

| 66 | From top to bottom: circulating current and upper and lower arm module        |     |

|    | filter voltages and upper and lower arm storage voltages. The power balance   |     |

|    | is not maintained. Storage is being charged                                   | 225 |

| 67 | Storage current RMS are shown in upper two plots and waveforms on the lower   |     |

|    | two plots. The power balance is not maintained. Storage is being charged      | 226 |

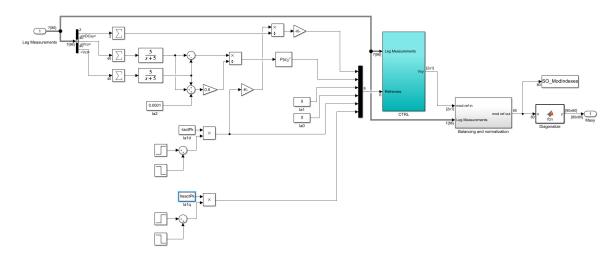

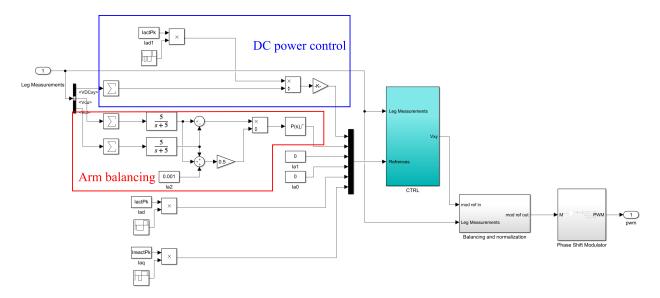

| 68 | Control section for the averaged converter model (shaded Control block struc- |     |

|    | ture from Figure 68)                                                          | 228 |

| 69 | Balancing and normalization block structure implementation in Simulink        | 228 |

| 70 | Circulating current during the module balancing sequence in the upper plot    |     |

|    | and the output current in the lower plot                                      | 230 |

| 71 | Module filter output voltage during the balancing simulation sequence         | 230 |

| 72 | Circulating current during the module balancing sequence in the upper plot    |     |

|    | and the output current in the lower plot                                      | 231 |

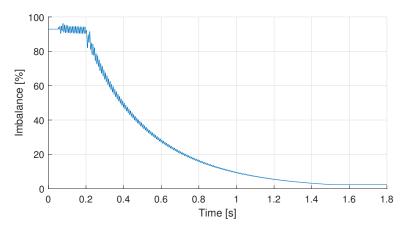

| 13 | impalance measurements as defined in (278) during the balancing sequence        |     |

|----|---------------------------------------------------------------------------------|-----|

|    | simulation run.                                                                 | 231 |

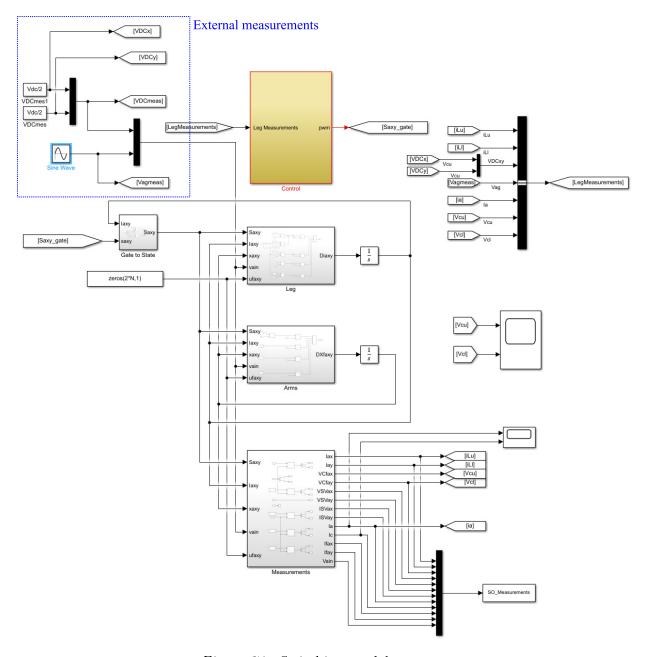

| 74 | Switching model structure                                                       | 233 |

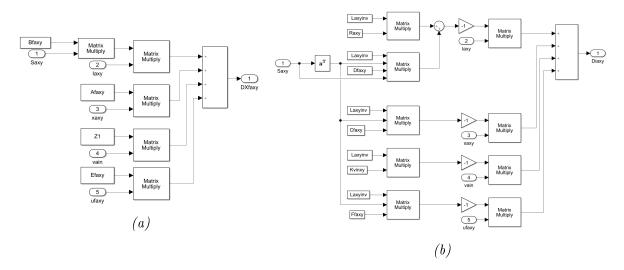

| 75 | (a) - Arms block structure and (b) - Leg block structure for switching model.   | 234 |

| 76 | Switching model Control block structure                                         | 235 |

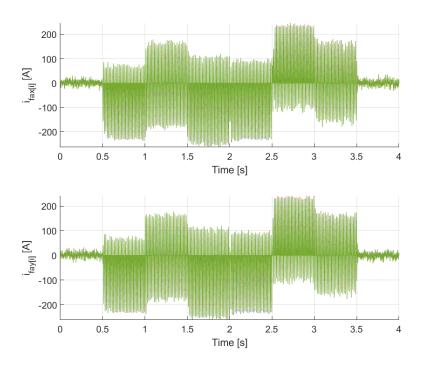

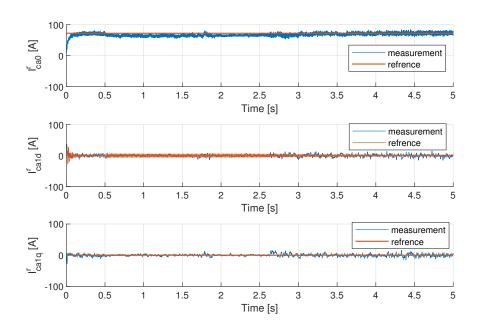

| 77 | References for the circulating current for the switching model simulation       | 236 |

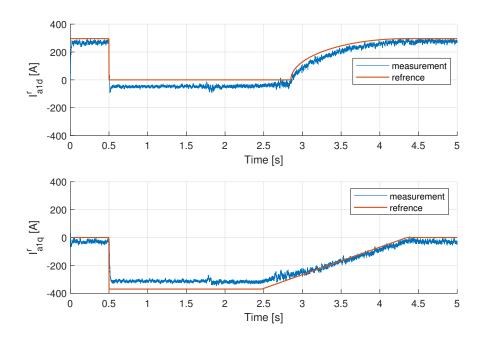

| 78 | References for the output current for the switching model simulation            | 237 |

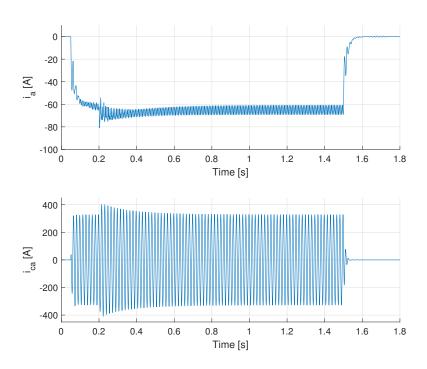

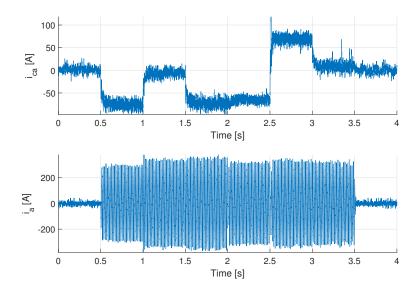

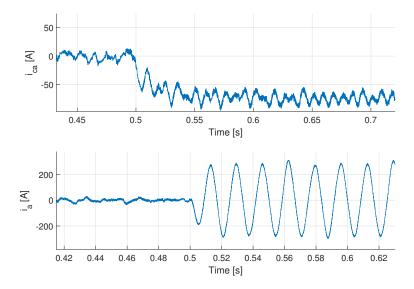

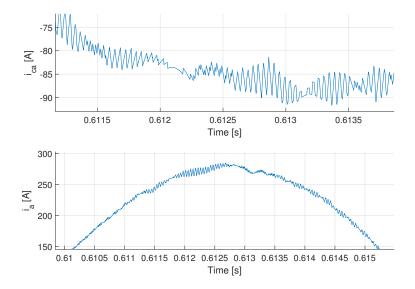

| 79 | Circulating current and output current simulation results for the switching     |     |

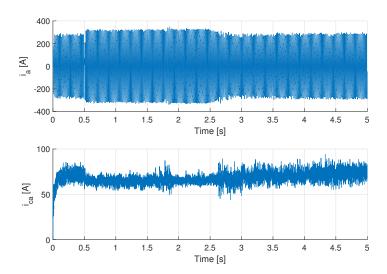

|    | model                                                                           | 238 |

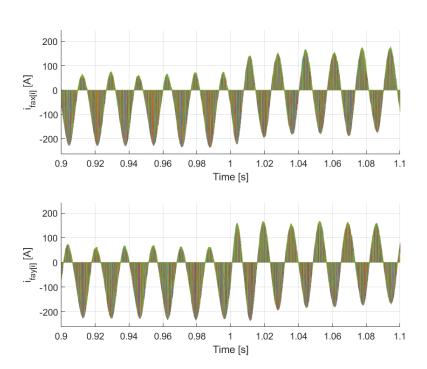

| 80 | Circulating current and output current transient at $t=0.5s$ from Figure 79     | 239 |

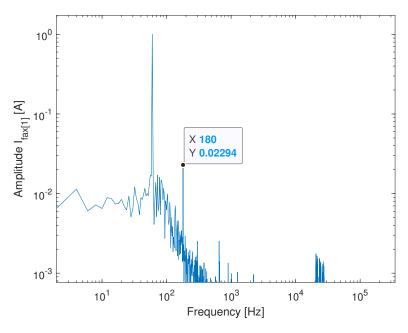

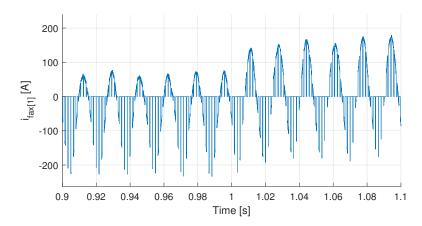

| 81 | Output and circulating current ripple                                           | 240 |

| 82 | Normalized output current spectrum                                              | 241 |

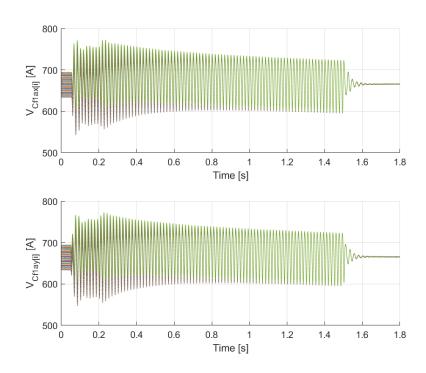

| 83 | Module filter output voltages for top and bottom arms                           | 241 |

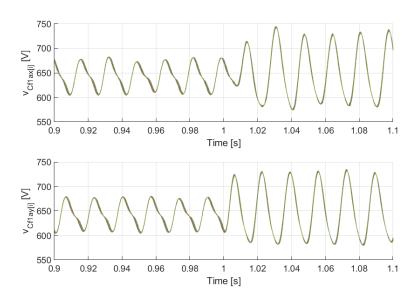

| 84 | Module filter output voltages for top and bottom arms. Zoomed during tran-      |     |

|    | sient at t=1s to illustrate waveform shapes for different operating conditions. | 242 |

| 85 | Module filter output voltages for top and bottom arms. Zoomed section during    |     |

|    | transient at t=1s                                                               | 242 |

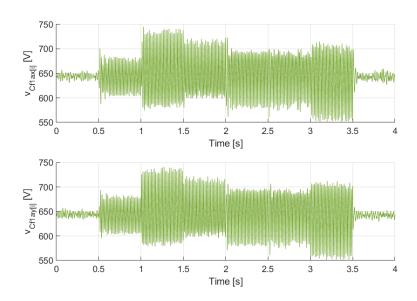

| 86 | Module storage system voltage for top and bottom arms                           | 243 |

| 87 | Module storage currents                                                         | 243 |

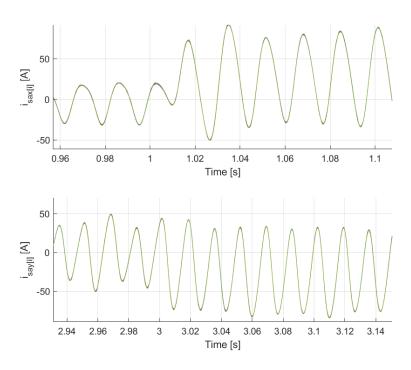

| 88 | Module storage current waveforms. for two different points near the start and   |     |

|    | near the end of the simulation run                                              | 244 |

| 89 | Filter input currents for upper and lower arm modules                           | 244 |

| 90 | Zoomed section of filter input currents for upper and lower arm modules         | 245 |

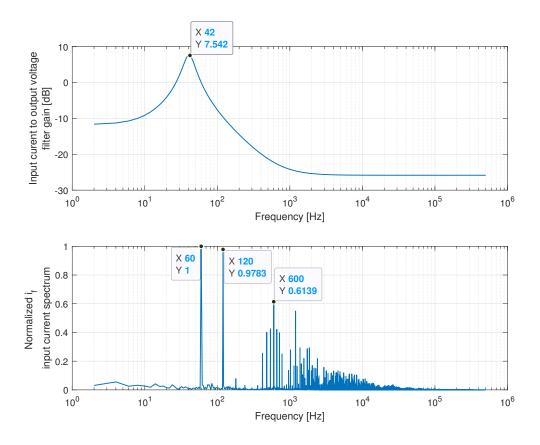

| 91  | Zoomed section of filter input currents for one first module in the upper arm. | 247 |

|-----|--------------------------------------------------------------------------------|-----|

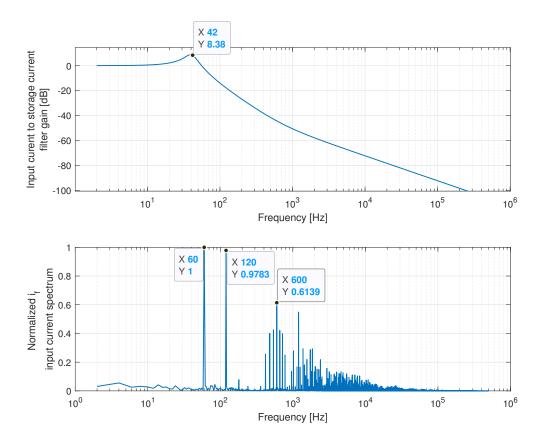

| 92  | Magnitude Bode plot of the transfer function from the input current to the     |     |

|     | filter output voltage and normalized spectrum of the input current             | 248 |

| 93  | Magnitude Bode plot of the transfer function from the input current to the     |     |

|     | storage current and normalized spectrum of the input current                   | 249 |

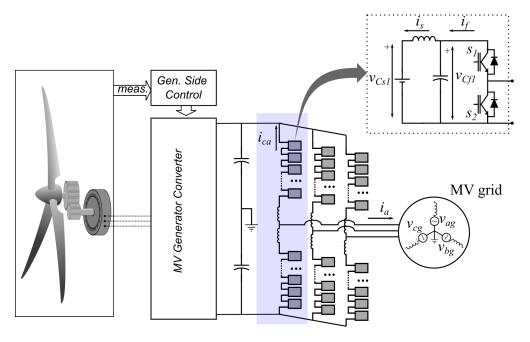

| 94  | Application of the MMC converter within wind energy system with the rep-       |     |

|     | resentative leg highlighted                                                    | 250 |

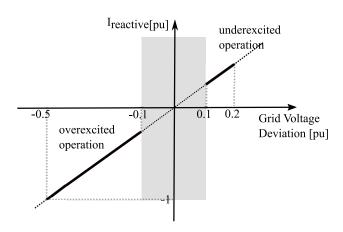

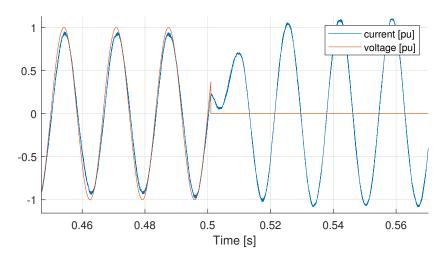

| 95  | Reactive support requirement according to E-ON standard [5]                    | 251 |

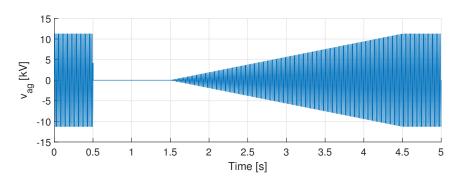

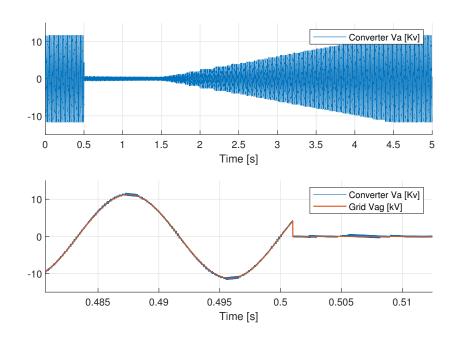

| 96  | Grid voltage for the Low Voltage Ride Through (LVRT) simulation run            | 251 |

| 97  | DC and circulating current fundamental references in dq frame during the       |     |

|     | LVRT event                                                                     | 252 |

| 98  | AC output current references and measurements in dq frame during the LVRT      |     |

|     | event                                                                          | 253 |

| 99  | DC and AC side current waveforms of the converter leg during the LVRT event.   | 254 |

| 100 | Active power, reactive current support and control performance illustration    |     |

|     | during the LVRT event.                                                         | 255 |

| 101 | Storage system voltage within the modules of upper and lower arm of the        |     |

|     | converter leg during the LVRT event                                            | 256 |

| 102 | Filter voltages of modules within upper and lower arm of the converter leg     |     |

|     | during the LVRT event.                                                         | 257 |

| 103 | Converter output voltage and zoomed section of the converter output voltage    |     |

|     | compared to the grid back emf voltage just at the start of the LVRT sequence.  | 257 |

# LIST OF TABLES

| 1  | Power carrying waveforms                                | 76  |

|----|---------------------------------------------------------|-----|

| 2  | Base System Parameters                                  | 158 |

| 3  | Sizing requirements and operating conditions            | 187 |

| 4  | Energy Storage Cell Parameters [6]                      | 187 |

| 5  | Sizing Variables and Affected Constraints               | 193 |

| 6  | Design Solution Parameters - Arm parameters, estimate   | 195 |

| 7  | Design Solution Parameters - Arm parameters, optimal    | 197 |

| 8  | Estimated Module Filter Parameters                      | 206 |

| 9  | Estimated Module Filter Parameters - Model Based Design | 212 |

| 10 | Estimated arm inductance and related parameters         | 221 |

| 11 | Gates to switching states conversion table              | 234 |

#### **GLOSSARY**

$M^2LC$  Modular MultiLevel Converter.

**CHB** Cascaded H-Bridge.

**DAB** Dual Active Bridge.

**FACTS** Flexible AC Transmission Systems.

FERC Federal Energy Regulatory Commission.

**HVDC** High Voltage Direct Current.

**IGBT** Insulated Gate Bipolar Transistor.

KVL Kirchhoff's Voltage Law.

LVRT Low Voltage Ride Through.

MMC Modular Multilevel Converter.

MMCC Modular Multilevel Cascaded Converter.

MVDC Medium Voltage Direct Current.

**PFR** Primary Frequency Response.

**PLL** Phase Locked Loop.

PV Photovoltaic.

**PWM** Pulse Width Modulation.

SCADA Supervisory Control and Data Acquisition.

**STATCOM** Static Synchronous Compensator.

**THD** Total Harmonic Distortion.

WECSS Wind Energy Conversion and Storage System.

### 1 Introduction

#### 1.1 Problem Statement

The trend for power electronics systems is to move to higher power voltages and control utility grid power and energy. Various power converter topologies have been proposed and developed for medium voltage and high power systems. One major issue is that energy storage systems are typically developed and operated at low voltage and an efficient means for integration with medium voltage systems is required. The focus of this research is the analysis of Modular Multilevel Converter (MMC) converter topology and integration of energy storage to create power and energy flexibility. The main purpose of this analysis is to investigate the modifications to the MMC topology and necessary control that will facilitate the possibility of energy storage integration. This will make the converter suitable for the high power medium voltage systems that require higher level of decoupling between the input and output power flows. The decoupling between the input and output power flows is commonly associated with modern renewable energy systems grid tie converters, especially for wind and solar. While it is not limited to the renewable energy systems applications, this converter topology aims to solve the same set of challenges commonly associated with converters used in modern wind turbines and large solar fields. To put the problem in more practical framework the challenges and the solutions will be treated from a wind energy system standpoint. The energy storage and the converter will therefore be designed to assist with the power by the new grid connection codes for renewable energy.

#### 1.2 Motivation

There is a need for integration of energy storage systems at various levels of power conversion systems to improve reliability, flexibility, and stability. MMC topology enables medium voltage power conversion using widely available low-voltage power switching devices. In the same manner, low-voltage energy storage systems can be conceptually integrated with MMC converter to offer energy storage and energy conversion in a single converter. MMC topology is a complex converter in regard to hardware and control. Adding energy storage adds flexibility to converter but increases complexity. This dissertation performs detail analysis, formulation, control, and simulation of the new concept. The developed converter can help with better control of energy from renewable resources and ultimately increase their penetration.

#### 1.2.1 Large Wind Energy Systems

The percentage of renewable energy systems in the total world power generation is constantly increasing [7], [8]. With the increase in number of large offshore wind farms, the size of the individual wind turbine is increasing as well. At the end of 2016 the average power rating of a single wind turbine was about 2MW [8]. Individual offshore wind turbines of 8MW are available and power levels of 10MW-20MW are being researched [9], [10], [11]. The increase in the power conversion system size introduces new technical challenges into electrical, mechanical and control subsystems design. For wind energy systems these challenges can be summarized in several groups:

1. Intermittent and unpredictable nature of the wind energy can affect the power system

stability in a negative manner on many levels. Large power production fluctuations can change the grid frequency, voltage or even destabilize the entire power system. This is especially true in cases when wind accounts for a large percentage of the power production in a utility grid. Such utility grids usually do not have enough conventional generators that would provide a sufficient amount of inertia and counteract sudden changes in power delivery from the wind. Problem of intermittency and unpredictability is common for wind and solar power systems. As a consequence, utility companies with high percentage of renewables impose strict power quality codes for such systems [12], [13].

- 2. Fault ride through capabilities are required by the new grid connection codes for all renewable energy systems. Fault ride through requirements dictate the behavior of a grid connected power converter during the short term grid faults. Fault ride through behavior is an important aspect of any grid connected system, specially the power generating systems. To maintain power grid stability and to prevent the sudden loss of large amount of power production, it is important to keep the power generating system on line during short faults and low voltage conditions [5]. The fulfillment of these requirements can be challenging for the systems that rely on sensitive power electronic converters like modern wind turbines and Photovoltaic (PV) systems.

- 3. Ancillary support requirements for reactive power and grid frequency are also included in the most new grid connection codes for renewable energy systems [5]. Implementation of these requirements requires that the system always has power and energy reserve in order to be able to support the grid in cases of low voltage or low frequency

conditions. This requirement conflicts the intermittent nature of wind and PV systems.

- 4. Steady increases in wind turbine size and power created a number of design challenges for the electrical subsystem. These challenges are mostly related to high current ratings and the efficiency of the power conversion system. For wind turbines this is additionally complicated due to the limited space in the nacelle. High power wind turbines nowadays have full back-to-back conversion systems in excess of 5 MW but they still operate on 690V in most cases. To achieve power levels so high, power converters have to be paralleled. Paralleling and high current ratings negatively affect efficiency, size and economical aspects of the system [14].

- 5. The power conversion system of wind turbine is usually in the nacelle, high off the ground. Furthermore, offshore wind farms are usually far from the shore and are not easily accessible for repair. Difficult access to the system in conjunction with projected lifetime of a common the wind turbine, which is about 20 years, makes the reliability and fault tolerance specially important issue for the wind energy systems.

#### 1.2.2 Renewable Energy and Storage Systems

If properly integrated with the power converter, energy storage system can provide a level of power decoupling between the power exported to the grid and the power coming from the renewable energy resource. This power decoupling can be helpful for solving the problems associated with fault ride through, ancillary support requirements and intermittency. As a consequence, wind and solar energy systems and energy storage systems complement each other very well [13], [15], [16].

Fault ride through challenges are easier to solve if the energy storage system is integrated into a renewable energy system. This is specially true for the wind energy. Power decoupling provided by the integrated energy storage can be used to isolate and protect the mechanical system of the wind turbine from the grid faults [17].

Energy storage can be used to provide extra power needed to emulate inertia or support the grid frequency [18]. Without the energy storage, renewable energy systems have to be moved off their optimal operating points to maintain power production margin needed for ancillary services. This is known as power curtailing in the available literature.

Power curtailment is also used when for some reason energy coming from the renewable resource cannot be exported to the grid. This condition can be encountered in cases of low power demand or lack of transmission capacity.

As it forces the system off its optimal point, power curtailment decreases the overall efficiency and the affordability of renewable energy. With the use of energy storage, the power flow from the renewable resource to the grid become decoupled, which can reduce or completely mitigate the need for power curtailment [19], [20]. Furthermore, with the properly designed energy storage the excess energy can be stored and used when needed.

When talking about wind turbines and energy storage systems one can notice two parallel trends, the size and the investment into individual wind turbines is continuously going up while the price of energy storage technologies goes down. Furthermore, energy storage systems are becoming more reliable, more affordable and more widespread. As a consequence, joining the wind energy systems and energy storage systems in various ways became more attractive research area [17], [21].

Integrated wind energy system and energy storage system is known as Wind Energy

Conversion and Storage System (WECSS) in the available literature [22]. While somewhat covered in the literature, integrated wind energy and energy storage systems are still not common in industry. However, one can argue that the technology will eventually come to a point when the benefits from the integration of the energy storage within a wind turbine will overcome the drawbacks of the increased price and complexity of the system.

#### 1.2.3 Medium Voltage Wind Energy Systems

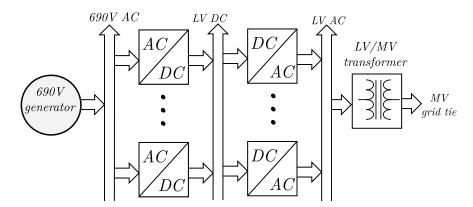

While the individual wind turbines power rating have increased steadily over the years, the majority of generators and power converters inside individual wind turbine remains at low-voltage levels, below 1kV. For the systems above 0.75MW low-voltage power converters are usually paralleled to achieve the appropriate current rating as shown in Figure 1 [14].

Parallel arrangement of low-voltage power converters is used in many commercial high power wind turbines as most commercially effective solution. However, for the wind turbines above 3MW this arrangement is affecting efficiency and reliability of the power conversion system. As an example, a 3MW wind turbine requires a number of converters connected in parallel to handle 2500A of the output current per phase. High current levels dissipate relatively high amount of heat in the converter semiconductors and conductors of the generator and the step-up transformer. This creates a cooling problem in the narrow space of the wind turbine nacelle. One way to solve the dissipation problem is to move to medium voltage levels to reduce the current ratings of the conversion system.

Although medium voltage technology is mature for motor drives, it is still not common for wind energy systems [14]. As a result, some manufacturers are trying to migrate their wind energy systems to medium voltage levels of up to several kV. The use of medium

Figure 1: Power conversion system arrangement inside the common low-voltage high-power wind turbine. To achieve desired power level, the power electronics converters are usually paralleled.

voltage generators and power converters improves the system efficiency as it allows the use of a single power converter and eliminates the need for low-voltage converter paralleling but it also introduces new design issues.

One of the major problems with medium voltage converters is silicon semiconductor device breakdown voltage. To overcome this issue multilevel converter topologies are used for medium voltage power electronics systems. For these topologies, the voltage stress on the semiconductor device usually reduces proportionally to the number of levels. As a result, each semiconductor device switches only a fraction of the total DC bus voltage. Multilevel converter topology solves the semiconductor breakdown problem but increases the complexity of the system and sometimes reduces the reliability with the larger number of active components that can fail.

In general, medium voltage power conversion systems are more challenging to design because of the more severe requirements for the insulation system and higher voltage stress on the active components. Increase of the insulation system complexity and voltage stress on the components affects all parts of the conversion system from the generator to the control system. Protection circuits, data-acquisition circuits, gate-driving circuits, DC bus capacitor banks and power supplies are harder to implement for medium voltage than for the low-voltage converters. It should be noted however, that all additional engineering and design efforts become more justified as the power level increases due to the increase in the system cost and size.

It seems that the wind industry has reached the power levels where the use of medium voltage conversion systems becomes justified and more commercially viable [14], [23].

#### 1.2.4 Multilevel Converters and MMC

For traditional two-level power converters the maximum DC bus and maximum input voltage are limited by the breakdown voltage limitation of the semiconductor switching devices. For conventional two level typologies each switch has to withstand the full DC bus voltage. To overcome the breakdown limitations of the semiconductor switching devices and to increase the output waveform quality, most medium voltage power electronic converters use some sort of multilevel topology. For multilevel topologies the DC bus voltage is evenly spread among the switches that generate the individual voltage levels, the more the levels the higher the total DC bus voltage can go with the same semiconductor switches. The trade-off is of course the use of additional switching and accompanying components.

Most traditional multilevel topologies have quadratic dependence between the number of levels and the component count (i.e. number of diodes in the diode clamped multilevel converters or capacitors in capacitor clamped multilevel converters is proportional to the square of the number of levels) [24]. High component count increases cost and complexity and decreases the converter efficiency. This makes conventional multilevel converter topologies

with number of levels greater than five somewhat unattractive in the industry unless they are necessary.

One of the converter families that allow linear increase of converter complexity with the increase of levels is MMC. One of the most important properties of the MMC family of converters is their modular nature. The number of converter levels is increased by simply adding identical modules, which are completely identical and interchangeable. As a result, this converter topology has become very interesting for medium and high voltage systems that require higher number of levels [25], [26].

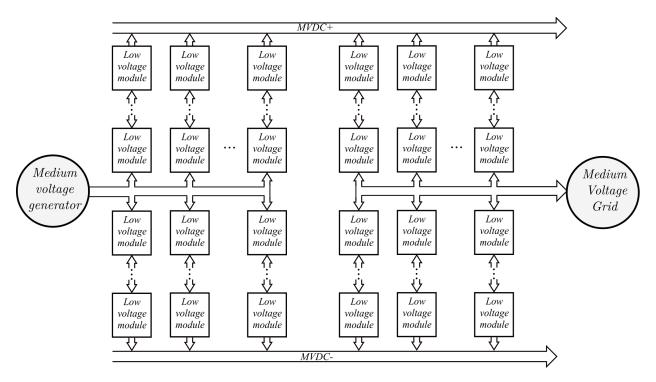

If used in high-power wind-energy systems, the desired power level is achieved by increasing the number of modules connected in series as illustrated in Figure 2. This may be viewed as dual approach to the parallel connection of converters given in Figure 1. In this way the operating voltage of the system is increased while keeping the current at relatively low levels, which in some cases increases the efficiency of the system. If the system is operated at medium voltage levels that are high enough, the same voltage can be used for the power transmission and the grid connection transformer from Figure 1 can also be avoided. This makes the overall system lighter and potentially more efficient.

Due to its modular nature the MMC topology can be varied and augmented in many ways. For this study the modification of interest changes the structure of the basic module of the converter to include an energy storage system. Although the MMC topology has been mentioned in the literature for the use with the energy storage systems and wind energy systems separately, as will be shown later in the text, it has not been investigated for the use in Wind Energy Conversion and Storage Systems (WECSS).

Figure 2: Power conversion system arrangement inside the proposed medium voltage high power wind turbine. To achieve desired power and voltage levels, MMC converter modules are connected in series.

## 2 Literature background

This section will focus on the research publications related to the MMC converter topology or rather a family of converters that are usually referred under the name MMC. In order to provide the base for the proposed topology modification, an attempt will be made to outline the main branches of this family of converters and show their distinct characteristic and most suitable application.

Attention will also be given to the renewable energy systems, energy storage uses and the applicable grid codes in order to provide the background for the proposed topology modification and its potential usefulness and feasibility.

#### 2.1 MMC Background

Growing demand for high and medium voltage grid tied power electronic conversion systems and medium voltage motor drives in the 1990's and early 2000's inspired an entire family of very similar multilevel converter topologies. The main characteristic of these converter topologies is their modular nature, which allows expanded voltage and power range and overcomes the limitations imposed by the semiconductor switching element breakdown voltage. The modularity in this case refers to the series connection of identical cells or modules that create multiple converter levels. Converters that belong to this family of topologies can be easily recognized in the literature as they usually have label "modular", "stacked" or "cascaded" together with "multilevel" in their names. Although the term MMC appeared later, some researchers classify all these similar modular converter topologies and their variations under this name [27].

The main advantage of the modular multilevel converters compared to the non-modular multilevel topologies like diode or capacitor clamped voltage source converters, is slower increase of power carrying components per additional converter level. Modular topologies usually have linear increase in the component count per level compared to the quadratic increase for non-modular topologies. Besides the number of power components per level, for large number of levels, modular topologies tend to be less complicated and in some cases more efficient.

Although modular topologies have definitive advantages for multilevel converters with high number of levels, they have a disadvantage for the applications that can be implemented with simpler multilevel topologies with low number of levels. For the low level count, modular topologies tend to require more components per level than non modular. As a result, these topologies are still rarely considered for the applications that operate at low voltage and lower range of medium voltage.

The point where the component count advantage tilts to the modular topologies is usually when the number of levels reach seven or more. This point depends on the particular type and implementation of the stacked or modular multilevel converter and can be significantly higher for some variants. As a result, they are suitable for systems that operate at high voltage and upper range of medium voltage levels where the maximum reverse blocking voltage of available semiconductor devices dictates the requirement for relatively high number of levels.

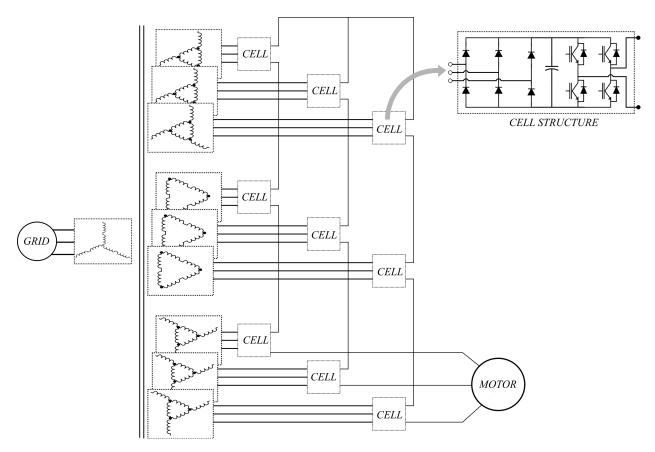

One of the first modular multilevel converter structures was proposed by Hammond in 1995 [1], [28], [29]. This topology finds its inspiration in medium voltage drives and is commonly referred to as Cascaded H-Bridge (CHB) topology. The proposed multilevel voltage source converter was aimed to be cheaper and better performing than the current source topologies commonly used in medium voltage drives at that time. The topology uses isolated outputs of a multiple winding transformer to supply individual converter cells. A cell of the converter is implemented as low voltage full-bridge inverter supplied by a 3-phase diode bridge rectifier. The full-bridge cell outputs are connected in series to form multilevel phase legs. Phase legs are then Y-connected to supply the motor as shown in Figure 3.

Using this approach, medium voltage drive can be implemented using standard, low voltage semiconductors making the entire power switch and gate driver circuit cheaper. In fact, the drive described in the original publications uses low voltage 480V rated 3-phase supplied full-bridge converters as cells and then uses three cells in series to generate 2.3kV voltage supply for the medium voltage motor [1].

Figure 3: Multilevel structure proposed by Hammond for the use in medium voltage drives [1]. In this case proposed output voltage is 2400V and the cells operate at standard 480V.

The main drawback of the Cascaded H-Bridge converter is the expensive and rather complicated multiple output 3-phase transformer. The system implemented using this topology also cannot operate in all four quadrants, i.e. if the motor enters a generating mode, the active power cannot be delivered to the grid.

One can also argue that this topology is not completely modular in nature. Adding more levels requires not just adding more identical modules in series but also requires modification of the multiple winding transformer, which is an integral part of the converter. For this reason the cells were not marked as modules in Figure 3.

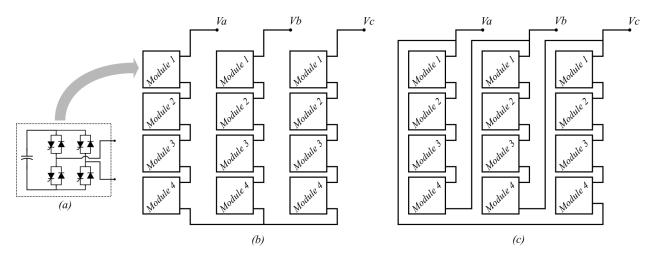

The idea of the modular multilevel topology was pushed a bit further with the "Multilevel Cascade Inverter" proposed in 1995 by Peng et al. for Flexible AC Transmission Systems

(FACTS) applications, specifically for the VAr generation [30]. This topology is composed of completely identical modules and the number of levels can be extended by just adding more modules in series. The topology uses stacked full-bridge converters as modules and needs one full-bridge converter for additional level. As a result, N-level inverter can be implemented using 4N diodes and 4N semiconductor switches. In the original paper the inverter was proposed in two different configurations: Y-connected configuration shown in Figure 4 - (b) and  $\Delta$ -connected shown in Figure 4 - (c).

Figure 4: Cascade multilevel structure first proposed by Peng et al. (a) - Module structure. (b) - Y-connected converter configuration. (c) -  $\Delta$ -connected converter configuration.

Although this inverter seems very attractive for the medium voltage applications that could benefit from a large number of levels and high quality output waveform, the topology has one interesting drawback - it does not have a DC bus in the classical sense. Instead, the DC bus is divided among converter modules. Furthermore, each module DC bus has to be isolated from the rest of the modules. As a result, inverter supply implementation is somewhat challenging. In fact, if we use multiple winding transformer to supply the modules of the Y-connected configuration shown in Figure 4 - (a) we will end up with the converter

topology very similar to the one proposed by Hammond.

In a number of follow-up papers related to the Cascade Multilevel Converter Topology authors argue that the topology can be used for the applications:

- Where individual DC bus voltage can be maintained through the full-bridge output.

These applications include phase shifting, reactive power support Static Var Generators (SVG) and harmonic filtering [31], [32].

- Where the isolation between DC sources naturally exists. Examples of such systems are PV and fuel cell grid tie converters [30], [33].

The idea that finally introduced a truly modular multilevel AC to DC and DC to AC converter topology was proposed in 2002 by Marquardt et al. and is illustrated in Figure 5 [34]. The topology was proposed in an effort to create network inter-tie system suitable for FACTS applications and high power, high or medium voltage power transmission and distribution systems. An obvious trend up to this point was to reduce the module complexity and increase modularity of the topology by utilizing symmetries available in the standard three-phase grid supply. The arrangement in Figure 5 seems to have reached the optimum in this regard. The members of the MMC family of converters that were proposed after usually represent a combination, rearrangement or the adaptation to a new application of the previous three ideas. Although usually considered as the origin for most of the multilevel converters that belong to MMC family, topology in Figure 5 can also be seen as the successor of the previously mentioned topologies illustrated in Figure 3 and Figure 4.

As with the previous converters the main benefit of the  $M^2LC$  topology is its modular nature and the linear increase in the component count with the increase in the number

Figure 5: Back-to-back structure implemented with MMC converters with the DC bus proposed by Marquardt et al. and named Modular MultiLevel Converter  $(M^2LC)$  by the authors. (a) - Half bridge module (cell) structure. (b) - MMC back to back structure showing the substructures commonly called "converter arm" and "converter leg" in MMC terminology.

of levels. Although the idea seems very similar to the previously mentioned Cascaded H-Bridge converter and Multilevel Cascade Inverter given in figures 3 and 4, it has a number of important differences:

- $M^2LC$  topology allows the simplest module topology (half-bridge + capacitor)

- $M^2LC$  topology has single, common high-voltage DC bus.

- $M^2LC$  topology uses half bridge modules instead of H-bridge modules common for most stacked or cascaded converters.

- $M^2LC$  does not have a DC bus supply for individual modules, but can be supplied through the high voltage DC bus.

•  $M^2LC$  topology was the first modular topology of its kind to be suitable for high and medium voltage back to back conversion systems and operation in all four PQ quadrants without the use of transformer of any kind.

Since the early 2000s acronym MMC has become the common term in the literature for many variations of the modular multilevel topology including  $M^2LC$  and cascade modular multilevel converter mentioned above [27], [35]. It may be argued that there is a level of confusion regarding the topology names and naming conventions in the literature dealing with this topic. Different topologies sometimes share the same name and same or very similar configurations have been referred under different names. For example, same or very similar configurations can be found in the literature under different names like:  $M^2LC$ , double star MMC configuration, M2C, MMC configuration with a DC bus, Chainlink, etc. [25], [27], [36], [37].

The line between MMC and CHB seems to be particularly vague as well. For example, many authors consider converter from Figure 4 and similar structures a part of MMC family if they do not have external supplies to the DC bus of the modules. If every module DC bus has external power supply, it is usually considered to be a CHB converter. The converter from Figure 5 is considered MMC even if the modules have independent external supplies. Classification and naming convention attempt was given in a publication by Akagi [38]. In this publication the author classified most of the mentioned topologies under the name - Modular Multilevel Cascaded Converter (MMCC).

Over the years the topic known as MMC has become very broad and includes dozens of various multilevel topologies with different practical importance and field of application. Furthermore, the converter itself has become integrated with the higher level system to such extent that it cannot be treated or analyzed on its own. Excellent example of this can be found in wind and solar applications of the MMC topology. The following sections will attempt to outline at least some of the directions the above mentioned converters have evolved to.

## 2.2 MMC Applications and Modifications

MMC topology and its variations have been investigated in the literature for many applications mostly for high power, medium and high voltage systems. Applications can be divided into several groups where each group introduces a distinctive characteristic and some modification to the MMC topology. MMC applications can therefore be classified as:

- Grid support applications including various Static Synchronous Compensator (STAT-COM) systems

- Grid inter-tie applications

- HVDC applications

- Medium voltage motor drive applications

- DC/DC conversion systems

- Converters solar PV systems

- Converters for wind energy systems

- Energy storage applications

#### • Other applications

#### 2.2.1 Grid Support Applications

The idea of using the MMC topology for grid support device and STATCOM applications has been extensively analyzed in the available literature. One of the earliest modular topologies was proposed by Peng et al. for the use in a medium voltage static VAr generation system as mentioned in previous section [30]. Akagy et al. pointed out early on that the MMC topology allows design of medium and high voltage STATCOMs without the use of a step-up transformers. This makes high power medium voltage systems of this kind lighter, smaller, cheaper and more efficient in most cases [39]. Ota et al. further extended the research of the STATCOM applied MMCs with the control system analysis, different modulation techniques and balancing algorithms that allow improved current Total Harmonic Distortion (THD), current control and capacitor voltage balancing [40], [41].

The application of the MMC converter topology for grid support inverters, STATCOMs and similar applications usually does not require an external supply, but only internal storage. As a consequence, most of these systems do not have DC bus and have similar structure as the converters shown in Figure 4.

## 2.2.2 Grid Inter-tie Applications

The flexibility of the MMC structure allowed AC to AC conversion systems and grid intertie converters to evolve in a couple of directions. One line of converters uses back-to-back MMC structure with the common DC bus and the other uses AC to AC MMC arrangement converter without the DC bus.

The original converter structure with the DC bus, introduced by Marquardt et al. and shown in Figure 5, was proposed for a three-phase to three-phase grid inter-tie system [34]. Similar system with more levels was later analyzed by Lesnicar and Marquardt for a three-phase to single-phase grid inter-tie [25]. This configuration with the DC bus can easily be extended to link two multi-phase systems with arbitrary number of phases.

Glinka and Marquardt also showed that the same MMC structure (or  $M^2LC$  as these authors call it) can be used for the AC to AC power conversion if the DC terminals are connected to the AC supply eliminating the DC bus in the system as shown in Figure 6 [26].

Figure 6: Structure of the AC to AC MMC topology without the DC bus proposed by Glinka and Marquardt.(a) - Module (cell) structure. (b) - Single phase AC to AC converter. (c) - MMC 3-phase AC to AC structure.

MMC converters without the DC bus proposed by Glinka and Marquardt shown in Figure 6 allows connections between single-phase and multi-phase systems but not between two multi-phase systems. Compared to the structure in Figure 5 for the same application they have significantly less modules but are more difficult to analyze and control. Furthermore, this AC to AC topology requires full-bridge switching arrangement in each module which could make the total semiconductor switch count equal or even higher for the same number of levels.

Structure that allows connection between two three-phase systems is shown in Figure 7 and was introduced much later in 2011 by Baruschka and Mertens as a "Hexverter" topology [2]. This converter has half of the module count compared to the three-phase back-to-back structure illustrated in Figure 5 with the same number of levels. While the capacitor and module count is half of the converter in Figure 5, Hexverter still requires full bridge modules making the equivalent semiconductor count equal.

#### 2.2.3 HVDC Applications

Modular nature and series connection of modules makes the MMC topology suitable for high voltage power conversion systems commonly found in High Voltage Direct Current (HVDC) transmission applications. Besides bulk power transmission over long distances for conventional power grid and power production, HVDC systems also found their application in modern renewable energy power production system like large off-shore wind farms and remote solar fields.

First commercial HVDC transmission systems appeared in 1950s as a result of advancements in power electronics and increasing demand for electric power and long distance trans-

Figure 7: MMC based 3-phase AC to AC converter structure known as Hexverter [2].

mission systems. These early HVDC systems were supplied by high power high voltage two level converters implemented with mercury-arc vacuum tubes. To achieve the voltage rating mercury-arc tubes were usually connected in series to create HVDC switches, or valves as they were called at the time that could operate at voltages of hundreds of kilo-Volts. With the introduction of semiconductor switches and the invention of thyristors in 1970s, mercury-arc tubes in the HVDC converter valves were replaced by a rather complicated series-parallel connection of large number of thyristors [42]. To facilitate proper high voltage operation of the entire switching structure thyristors had to be protected and balanced by the special

snubber circuits [43], [44]. Finally in 2010 HVDC valves were replaced by MMC converter arms, implemented with Insulated Gate Bipolar Transistor (IGBT) semiconductor switches. In this way the two-level converter topology was replaced with the multilevel MMC structure shown in Figure 5 [45].

MMC topology offers better power quality and higher HVDC conversion efficiency than conventional two level converters as demonstrated in a paper by Allebrod *et al.* [46]. Furthermore, high number of switches in a two level HVDC converters makes the MMC approach comparable in complexity and cost. As a result, relatively expensive and complicated MMC topology found its first commercial implementation in the area of HVDC power transmission systems. The first large commercial MMC system and the first MMC based HVDC transmission systems was commissioned in the Bay of San Francisco, between San Francisco and Pittsburgh CA in 2010. The system is rated at 400MVA with 216 + 16 modules (cells) per arm and DC transmission voltage of  $\pm 200kV$  [27], [47], [45].

HVDC transmission systems usually carry significant power to or from the local power systems. As a result, outages can have serous negatively effects on economy and grid stability. In general, when it comes to large power transmission systems besides efficiency and power quality, reliability is among the most important aspects of the system. Fault management and fault ride through is therefore a highly important topic in the field of MMC based HVDC transmission systems and has inspired a great number of publications and MMC topology modifications.

MMC topology with the DC bus given of Figure 5-(b) is vulnerable to the DC faults if used with the modules shown in Figure 5-(a). In case of the DC fault, series connection of the anti-parallel diodes will rectify the AC input and will feed the DC fault arc until

the entire converter is disconnected from the AC side supply or until the diodes fail. To avoid over sizing of the anti-parallel diodes, high current rating bypass thyristor shown as S3 in Figure 8-(a) is usually added to each module. This high current thyristor protects the converter from damage until the AC side circuit breakers act and disconnects the entire system from the supply [48]. If the system has to be disconnected from the grid and powered down, each fault can cause a significant downtime. As a result, this kind of MMC converters systems are not suitable for overhead DC transmission systems where faults may be frequent and intermittent.

A solution that makes the MMC converters more suitable for overhead transmission was proposed by Li et al. [3]. The authors proposed a minimal modification to the module topology shown in Figure 8-(b) that allows quick recovery from non-permanent DC faults. Added thyristors S3 and S4 protect the converter switches from high fault currents, shunt the DC bus and allow the fault arc to extinguish. If the fault persists, the converter and the system still need to be disconnected from the AC grid supply.

Another solution that makes the MMC converter shown in Figure 5-(b) and the HVDC transmission system completely fault tolerant and fault ride through capable is analyzed by Kontos et al. [49]. In this case authors used full-bridge modules as shown in Figure 9-(a) instead of half bridge modules given in Figure 5-(a). full-bridge module facilitates the control over AC and DC side currents and makes the MMC converter AC and DC fault tolerant. The price is highly reduced efficiency as the current path contains twice as many semiconductor switches.

To mitigate the problem of decreased efficiency a number of module variations were proposed over the last decade. The guiding idea behind most of these modifications was to

Figure 8: Simple fault capable modules. (a) - Half bridge module with the fault bypass thyristor. (b) - Fast fault recovery module modification proposed by Li et al. [3]

combine multiple modules into one and eliminate the redundant switches while maintaining the fault tolerant capability. This reduces the losses caused by the increased number of switches in the current path and effectively creates fault tolerant multilevel modules for the MMC topology.

One of the first such modules was proposed by Marquardt and was named clamp-double module. This module combines two half bridge modules into one. Compared to the equivalent connection of half-bridge modules, the losses are increased by one additional switch per two modules shown as S5 in Figure 9-(b) [50]. Switch S5 is normally ON and is turned OFF only during the fault handling situations. When the S5 is OFF, the current path is not symmetric during the positive and negative half cycle of the current, which means that the blocking voltages is not symmetric during fault handling. The module can block full DC bus amplitude for negative half cycle of the input current and only half for the positive [51].

Module topology in Figure 9-(c) was proposed by Li  $et\ al.$  and can block full DC voltage for positive and negative current half cycle. The module has one additional switch S6 and higher losses than clamp-double module. Switches S5 and S6 are always ON in normal operation [52].

Topology in Figure 9-(d) was proposed by Zhang and Zhao and can also block the full

DC bus voltage on the input but requires switch S5 and diode D1 with doubled voltage ratings [53]. For this module, switch S5 is always ON in normal operation.

Module in Figure 9-(e) was named T-Type and was proposed by Zhao et al. as an efficiency improvement to the clamp-double module topology given in Figure 9-(b) [54]. As can be seen from figures 9-(b) and 9-(e), T-Type module topology has one diode less than the clamp-double module but suffers from the same asymmetric blocking voltage for positive and negative half cycle.

A number of other arrangements were also proposed that were based on combining a number of full bridge and half bridge modules into one. These modules are sometimes called mixed modules. The simplest one is shown in Figure 9-(f) and covered in a publication by Adam et al. [55].

Other more complicated module topologies are also possible and were proposed in the available literature but they usually do not bring any significant advantage compared to using full bridge modules for the MMC converter structure shown in Figure 5-(b). A survey of some of the fault tolerant MMC module topologies that were proposed up to 2015 can be found in a publication by Nami *et al.* [56].

#### 2.2.4 Medium Voltage Drives

One of the predecessors of the MMC topology, mentioned in Section 2.1 and shown in Figure 3, was proposed by Hammond for medium voltage drives [1]. For this converter each individual module has its own supply, which is the main feature that separates this converter from the MMC family of converters. Without a supply for each module, DC bus voltage must be maintained by the module internal capacitance. As the current flowing through the

Figure 9: Some of the fault tolerant module topologies: (a) - Full-bridge module. (b) - Clampdouble module. (c) - Three-level module. (d) - Series connected double module. (e) - T-Type module. (f) - Mixed module.

module capacitors have strong first and second harmonics for the MMC converter topologies, maintaining DC bus voltage relatively constant at lower operating frequencies requires higher capacitance in each module.

Frequency dependent capacitance requirement for module DC bus creates a number of challenges for the application of MMC converters in variable speed drives. Capacitor voltage stability at low speed and standstill operation and consequently the stability of the entire converter operation is a serious issue that was initially described by Antonopoulos *et al.* back

in 2009 [57]. Year later in a publication by Hagiwara *et al.* it was pointed out that stable operation of the MMC drive requires capacitor sizing for the worst case of the particular application and torque limiting control at lower operating frequencies in order to avoid module overvoltage problems, especially during the machine startup [58].

One of the first control system based solutions that allows stable operation of the MMC drive through the entire range of frequencies was proposed by Antonopoulos et al. in 2010 [59]. The proposed control algorithm adjusts output reference voltages for the converter arms in order to control the total energy stored in the converter leg and to balance the energy between upper and lower arm. As a consequence, DC bus voltage in each module is maintained within limits. The trade-off of this approach is the introduction of, so called, circulating currents in order to move the power between arms of the converter leg. Circulating currents flowing between converter leg and the DC bus or between two converter legs are unwanted in normal operation as they introduce additional losses and do not contribute to the converter output. In fact, a significant number of publications are dedicated to the suppression controllers for circulating currents in HVDC and grid connected MMC converters [60], [61], [62]. The circulating current control for MMC based drives helps with capacitor voltage imbalances but it reduces the output power capability of the drive and torque production at start-up an low frequencies. As a consequence, instead of capacitor banks the semiconductors have to be over-sized.

Circulating current control has been covered extensively in the literature. For example, the circulating current control has been extended for the  $\alpha\beta0$  frame of reference and described in more detail by Kolb *et al.* [63]. The same concept was used by Baruschka *et al.* to help balance the module voltages for the drives application of the MMC based AC to AC Hexverter

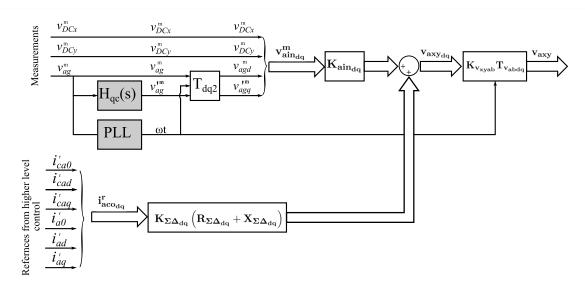

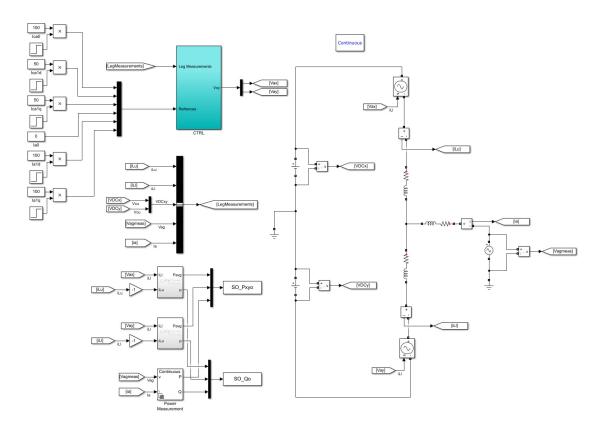

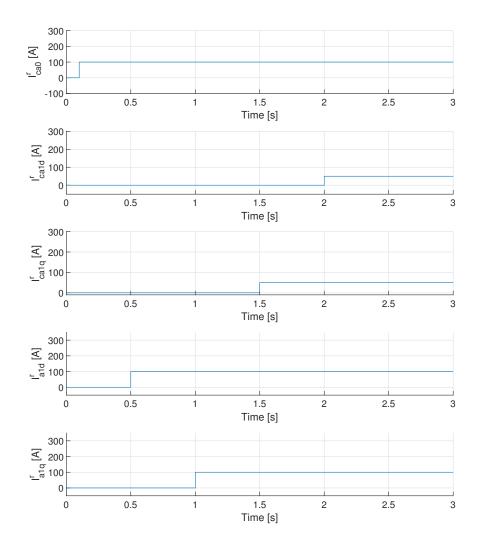

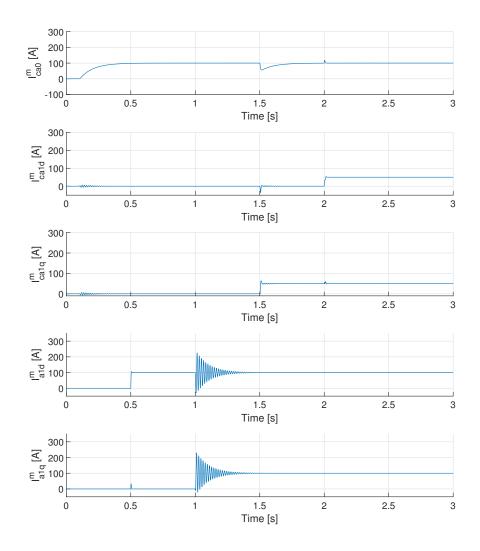

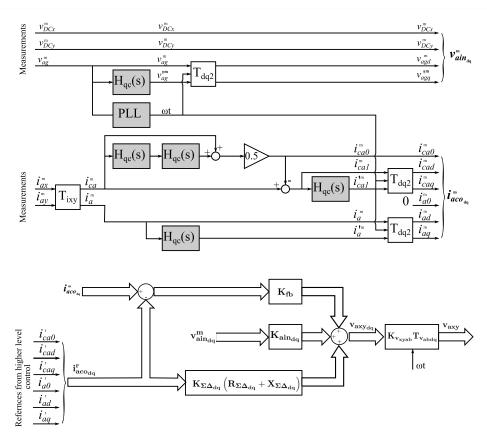

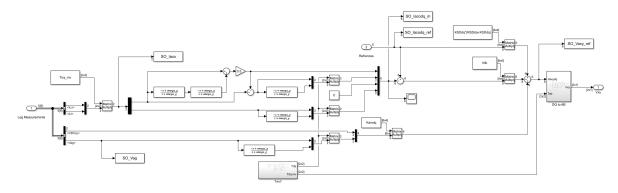

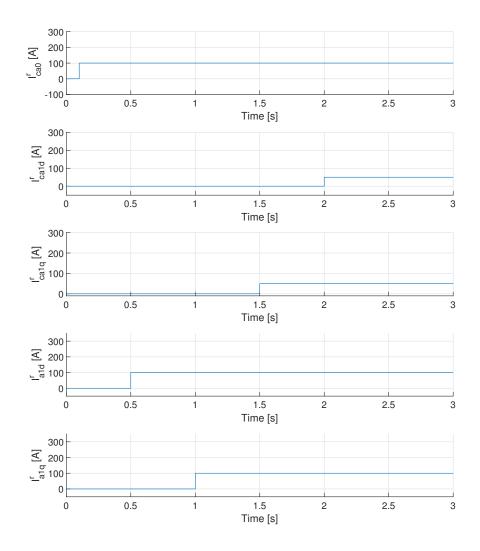

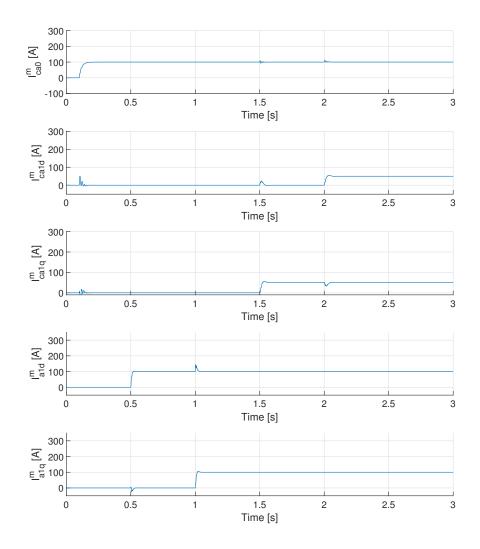

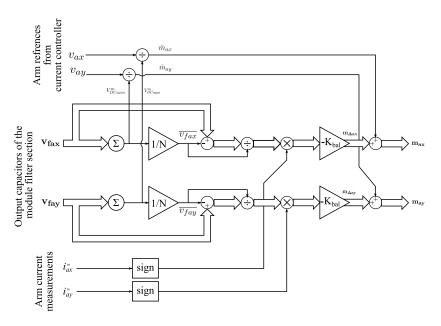

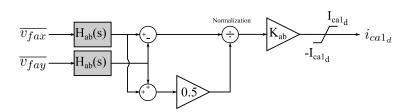

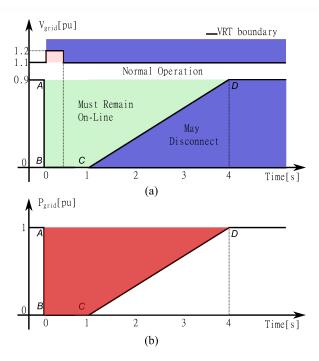

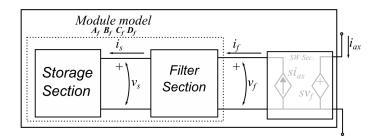

topology mentioned in previous section and illustrated in Figure 7 [64]. The application of the circulating current control in conjunction with space vector modulation for the MMC based drive was described by Brando *et al.* [65].