# AN ALL-DIGITAL CHARGE TO DIGITAL CONVERTER

Yuqing Xu

A Thesis Submitted for the Degree of Doctor of Philosophy at Newcastle University School of Electrical and Electronic Engineering Faculty of Science, Agriculture and Engineering December 2018

Yuqing Xu: An All-Digital Charge to Digital Converter ©2018

I hereby declare that this thesis is my own work and effort and that it has not been submitted anywhere for any award. Where other sources of information have been used, they have been acknowledged.

Newcastle upon Tyne September 2018

Yuqing Xu

CERTIFICATE OF APPROVAL

I confirm that, to the best of my knowledge, this thesis is from the student's own work and effort, and all other sources of information used have been acknowledged. This thesis has been submitted with my approval.

ALEX YAKOVLEV

To the soul of my wonderful Wife, and my lovely family. — Yuqing

#### ACKNOWLEDGEMENTS

I would like to express my deep gratitude to my supervisors Prof. Alex Yakovlev, Dr. Delong Shang and Dr. Fei Xia for their support and guidance through my PhD journey. They have always been a source of motivation and my inspirational model as a researcher.

I would like also to express my gratefulness and appreciation to my colleagues and friends in the School of Electrical and Electronic Engineering, especially those in Microelectronic Systems research (MSD) group, at Newcastle University for their guidance and assistance through my study. Especially, I appreciate the support of my wonderful colleagues Kaiyuan Gao, Danhui Li, Dr. Junwen Luo, Dr. Hubin Zhao and Vladimir Dubikhin for their productive suggestions, fruitful discussions, and subjective criticism.

I would like to offer my special regards to all the staff of the school of Electrical and Electronic Engineering in Newcastle university

last but not least, I would like to thank my wonderful family for their continuous support and motivation throughout my PhD journey. During the last two decades, the topic of the Internet of Things (IoT) has become very popular. It provides an idea that everything in the real world should be connected with the internet in the future. Integrating sensors into small wireless networked nodes is a huge challenge due to the low power/energy budget in wireless sensor systems. An integrated sensor normally consumes significant power and has complex design which increases the cost. The core part of the sensor is the sensor interface which consumes major power especially for a capacitor-based sensor.

Capacitive sensors and voltage sensors are two frequently used sensor types in the wireless sensor family. Capacitive sensors, that transform capacitance values into digital outputs, can be used in areas such as biomedical, environmental, and mobile applications. Voltage sensors are also widely used in many modern areas such as Energy Harvesting (EH) systems. Both of these sensors may make use of sensor interfaces to transform a measured analogue signal into a frequency output or a digital code for use in a digital system. Existing sensor interfaces normally use complex analog-to-digital converter (ADC) techniques that consume high power and suffers from slow sensing response.

This thesis proposes a smart all-digital dual-use capacitorbased sensor interface called charge to digital converter (QDC). This QDC is capable of not only sensing capacitance but also sensing voltages by using fully digital solutions based on iterative delay chain discharge. Unlike the conventional methods that only treats the sensed capacitance only as the input signal, this thesis proposes a method that can directly use the stored energy from the sensed capacitance as well to power parts of the circuit, which simplifies the design and saves power. By playing with the capacitance and input voltage, it can be used as a capacitance-to-digital converter (CDC) to sense capacitance under fixed input voltage and it also can be used as a capacitorbased voltage sensor interface to measure voltage level under fixed capacitance. The new method achieves the same accuracy with less than half the circuit size, and 25% and 33% savings on power and energy consumption compared with the state of art benchmark. The method has been validated by experimenting with a chip fabricated in 350nm process, in addition to extensive simulation analysis.

## CONTENTS

| I | Τŀ  | nesis ( | Chapte     | rs                              | 1  |

|---|-----|---------|------------|---------------------------------|----|

| 1 | INT | RODUC   | TION       |                                 | 2  |

|   | 1.1 | Motiv   | ation      |                                 | 2  |

|   | 1.2 | Thesis  | s Contrib  | ution                           | 5  |

|   | 1.3 | Public  | cations .  |                                 | 6  |

|   | 1.4 | Orgar   | nization c | of Thesis                       | 6  |

| 2 | BAC | KGROU   | JND ANI    | D LITERATURE REVIEW             | 10 |

|   | 2.1 | Introc  | luction .  |                                 | 10 |

|   | 2.2 | Capac   | citive Sen | sing                            | 11 |

|   |     | 2.2.1   | Capacit    | ors                             | 11 |

|   |     | 2.2.2   | Capacit    | ive Sensors                     | 11 |

|   | 2.3 | Capac   | citance to | Digital Converter               | 13 |

|   |     | 2.3.1   | ADC-re     | lated CDC                       | 15 |

|   |     | 2.3.2   | Frequer    | ncy/Time-based CDC              | 17 |

|   |     |         | 2.3.2.1    | Period Modulation-based CDC     | 17 |

|   |     |         | 2.3.2.2    | Pulse width Modulation-based    |    |

|   |     |         |            | CDC                             | 19 |

|   |     |         | 2.3.2.3    | Frequency modulation-based CDC  | 21 |

|   |     |         | 2.3.2.4    | Iterative Delay-Chain Discharge |    |

|   |     |         |            | based CDC                       | 22 |

|   |     | 2.3.3   | Summa      | ry of existing CDC techniques   | 27 |

|   | 2.4 | Voltag  | ge Sensin  | g                               | 27 |

|   |     | 2.4.1   | Referen    | ce-based Voltage Sensing        | 29 |

|   |     | 2.4.2   | Referen    | ce-free Voltage Sensing         | 30 |

|   |     | 2.4.3  | Summary of existing voltage sensing tech- |    |

|---|-----|--------|-------------------------------------------|----|

|   |     |        | niques                                    | 32 |

|   | 2.5 | Charg  | ge to Digital Converter                   | 34 |

|   | 2.6 | Ring o | oscillator                                | 35 |

|   | 2.7 | Metas  | stability Filter                          | 39 |

|   |     | 2.7.1  | Definition of Metastability               | 39 |

|   |     | 2.7.2  | Mutual Exclusion                          | 42 |

|   | 2.8 | Summ   | nary                                      | 43 |

| 3 | GEN | IERAL  | THEORY AND ALGORITHM                      | 45 |

| J | 3.1 |        |                                           |    |

|   | 3.1 |        |                                           | 45 |

|   |     | 3.1.1  |                                           | 45 |

|   |     | 3.1.2  |                                           | 48 |

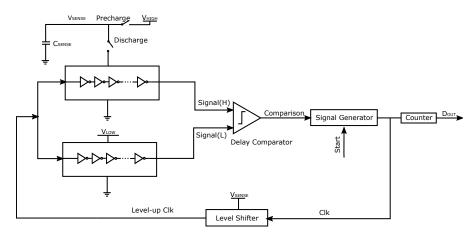

|   |     | 3.1.3  | Ring oscillator load QDC                  | 51 |

|   |     |        | 3.1.3.1 Sensing Capacitance               | 53 |

|   |     |        | 3.1.3.2 Sensing Voltage                   | 57 |

|   |     | 3.1.4  | Replacing $V_{LOW}$ in QDC                | 57 |

|   |     | 3.1.5  | The proposed design                       | 59 |

|   | 3.2 | Summ   | nary                                      | 60 |

| 4 | DES | IGN AI | ND IMPLEMENTATION                         | 63 |

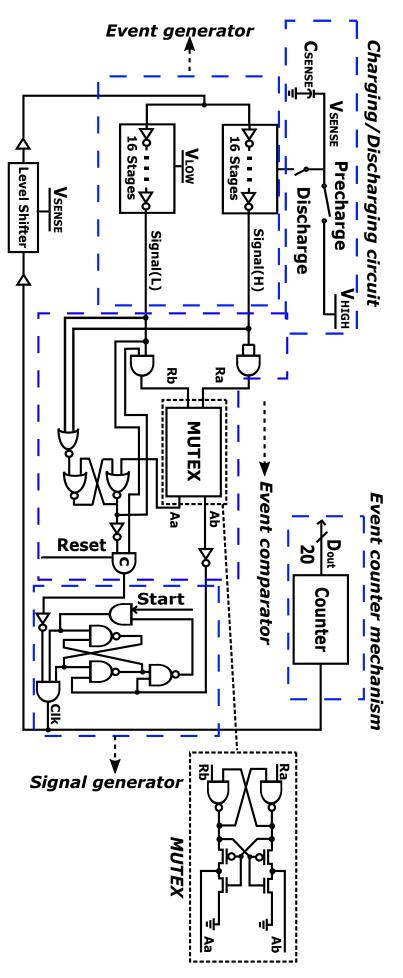

| • | 4.1 | Propo  | osed Solution                             | 63 |

|   | ·   | 4.1.1  |                                           | 63 |

|   | 4.2 | Detail |                                           | 64 |

|   | ·   | 4.2.1  | Charging/Discharging Circuit              | 64 |

|   |     | 4.2.2  | Signal Generator                          | 66 |

|   |     | 4.2.3  | Event Generator                           | 69 |

|   |     | 4.2.4  | Event Comparator                          | 71 |

|   |     | 4.2.5  | Level shifter                             | 74 |

|   |     | 4.2.6  | Event counter mechanism                   | 77 |

|   | 4.3 | Physic | cal Implementation                        | 81 |

|   |     |        |                                           |    |

|     | 4.4  | Sumn    | nary                                      | 81  |

|-----|------|---------|-------------------------------------------|-----|

| 5   | EXP  | ERIME   | NTAL RESULTS AND VALIDATIONS              | 84  |

|     | 5.1  | Simul   | lation Results                            | 84  |

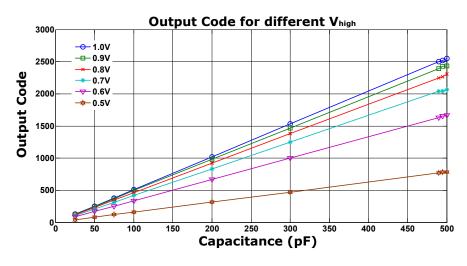

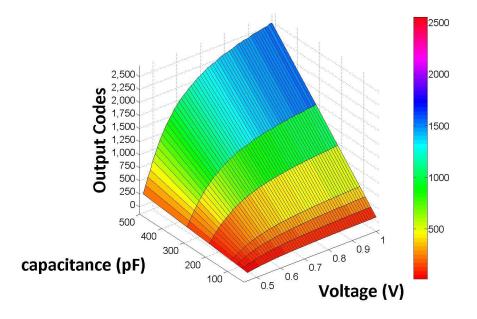

|     |      | 5.1.1   | Output codes for sensing capacitance      | 85  |

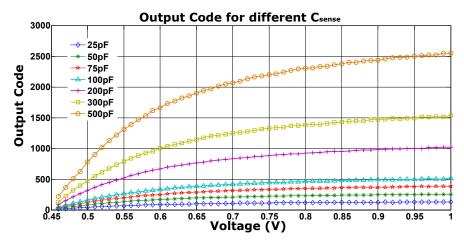

|     |      | 5.1.2   | Output codes for sensing voltage          | 86  |

|     |      | 5.1.3   | Overall performance for charge-to-digital |     |

|     |      |         | converter (QDC)                           | 87  |

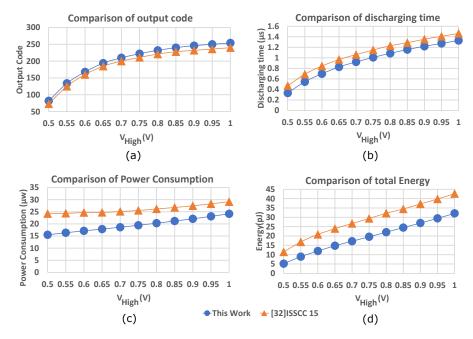

|     |      | 5.1.4   | Performance comparison                    | 88  |

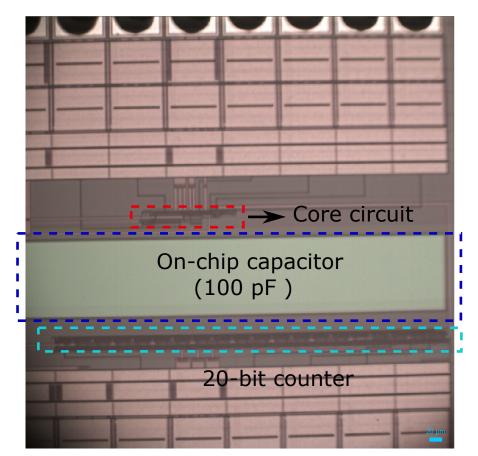

|     | 5.2  | Chip    | Results                                   | 91  |

|     |      | 5.2.1   | Test Setup                                | 91  |

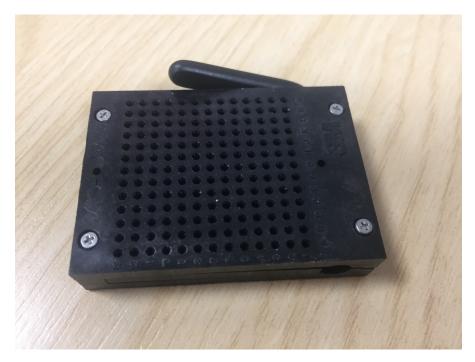

|     |      |         | 5.2.1.1 Fabricated chip                   | 91  |

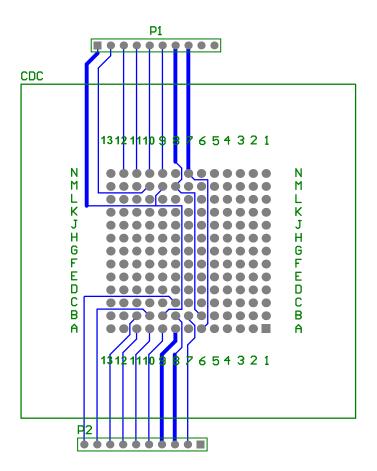

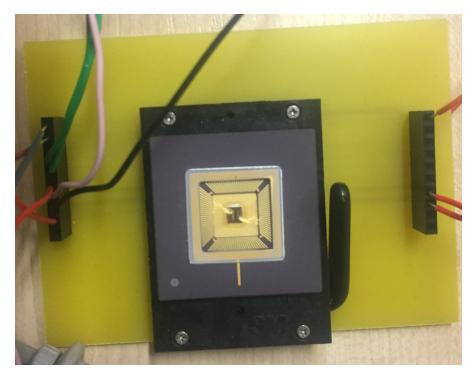

|     |      |         | 5.2.1.2 Printed Circuit Board and PGA     |     |

|     |      |         | sockets                                   | 92  |

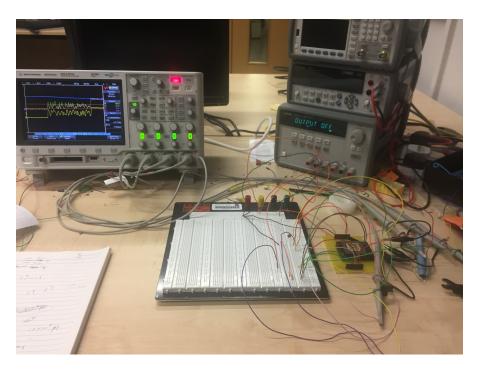

|     |      |         | 5.2.1.3 Equipment                         | 94  |

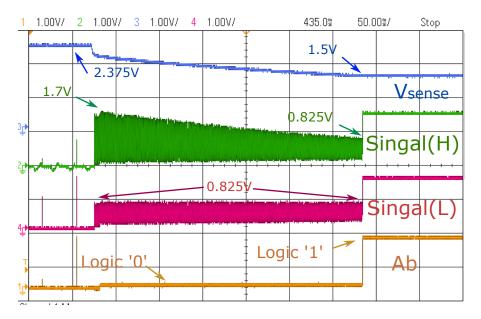

|     |      | 5.2.2   | Test Result                               | 94  |

|     | 5.3  | Sumn    | nary                                      | 98  |

| 6   | CON  | ICLUSI  | IONS AND FUTURE WORK                      | 100 |

|     | 6.1  | Summ    | nary and Conclusion                       | 100 |

|     | 6.2  | Futur   | e work                                    | 101 |

| 11  | Τł   | nesis / | Appendices                                | 104 |

| Α   | SCH  | EMATI   | IC OF THE DESIGNS                         | 105 |

| 111 | I TI | nesis   | Bibliography                              | 109 |

| BI  | BLIO | GRAPH   | IY                                        | 110 |

# LIST OF FIGURES

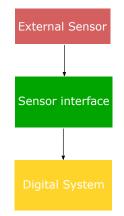

| Figure 1.1  | Basic sensing system                                          | 4  |

|-------------|---------------------------------------------------------------|----|

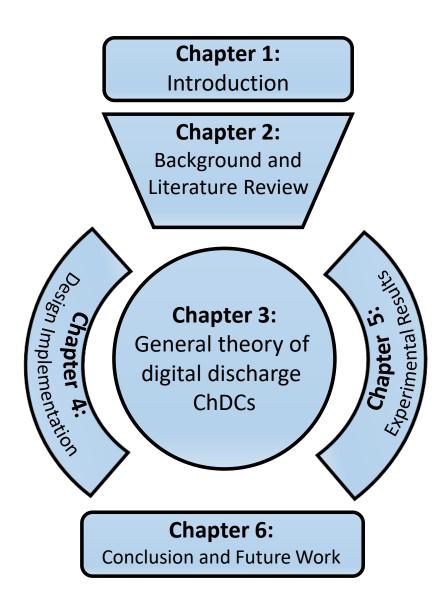

| Figure 1.2  | Thesis orginization                                           | 9  |

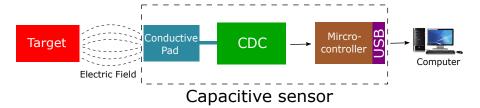

| Figure 2.1  | CDC-based Capacitive sensing system                           | 13 |

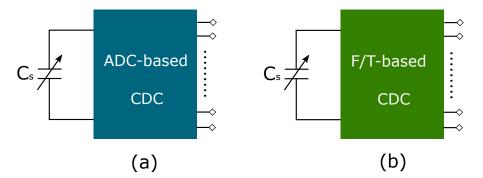

| Figure 2.2  | Two different types of CDCs (a) CDC                           |    |

|             | based on ADC modulation; (b) CDC based                        |    |

|             | on frequency/time modulation                                  | 15 |

| Figure 2.3  | ADC-based CDC                                                 | 16 |

| Figure 2.4  | Digital waveform                                              | 17 |

| Figure 2.5  | Period modulation:(a) $\phi_1$ on, $\phi_2$ off; (b) $\phi_2$ |    |

|             | on, $\varphi_1$ off [73]                                      | 18 |

| Figure 2.6  | Period modulation associated waveforms                        | 19 |

| Figure 2.7  | Structure of PW [2]                                           | 20 |

| Figure 2.8  | Frequency based CDC [22]                                      | 21 |

| Figure 2.9  | Structure of Iterative Delay-Chain Dis-                       |    |

|             | charge based CDC [32]                                         | 22 |

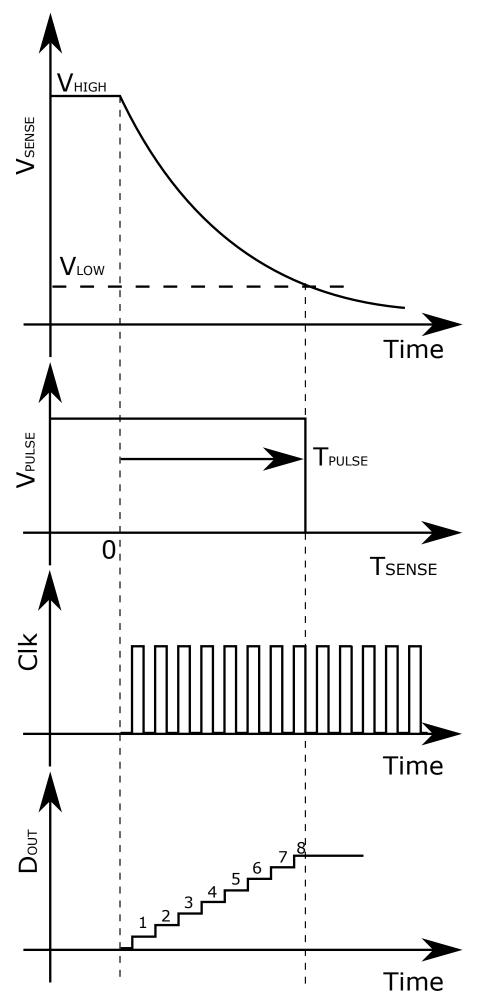

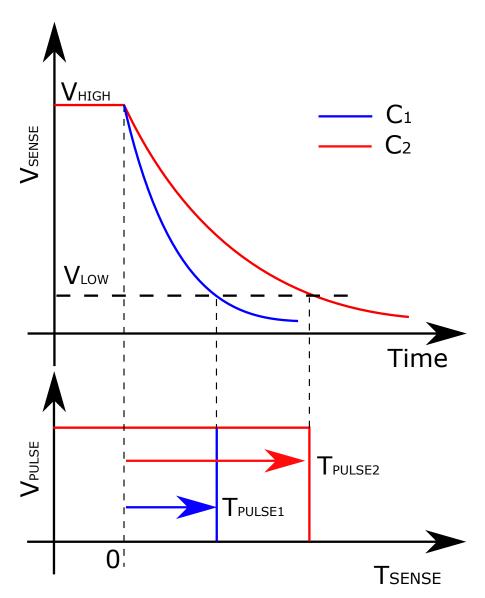

| Figure 2.10 | Iterative Delay-Chain Discharge based                         |    |

|             | CDC [32]                                                      | 23 |

| Figure 2.11 | Waveform of Iterative Delay-Chain Dis-                        |    |

|             | charge based CDC [32]                                         | 25 |

| Figure 2.12 | Three scenarios [66]                                          | 26 |

| Figure 2.13 | Single slope ADC [51]                                         | 29 |

| Figure 2.14 | Reference-free voltage sensing mechanism                      |    |

|             | [24]                                                          | 30 |

| Figure 2.15 | Voltage tracking [24]                                         | 31 |

| Figure 2.16 | Charge-to-Digital Conversion: (a) Charg-                      |    |

|             | ing process; (b) Discharging process[60]                      | 32 |

| Figure 2.17 | Ring oscillator powered by capacitor[59] . | 35 |

|-------------|--------------------------------------------|----|

| Figure 2.18 | Ring oscillator discharging                | 35 |

| Figure 2.19 | Schematic of inverters                     | 36 |

| Figure 2.20 | Transistor switching                       | 37 |

| Figure 2.21 | The operation of the ring oscillator[82]   | 37 |

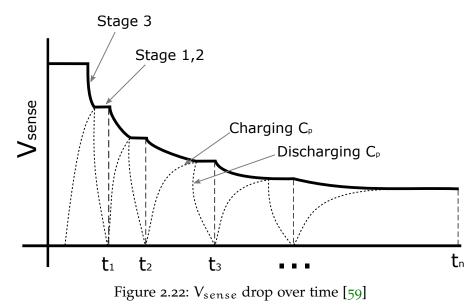

| Figure 2.22 | V <sub>sense</sub> drop over time [59]     | 38 |

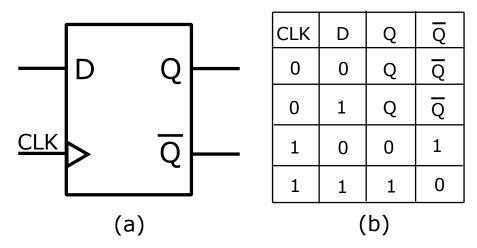

| Figure 2.23 | D flip-flop and the truth table            | 40 |

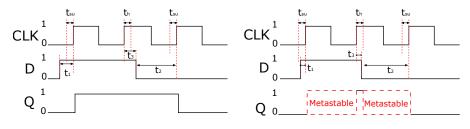

| Figure 2.24 | Timing diagram of D flip-flop (a) Normal   |    |

|             | state; (b) Metastable state                | 40 |

| Figure 2.25 | Detailed timing diagram of metastable      |    |

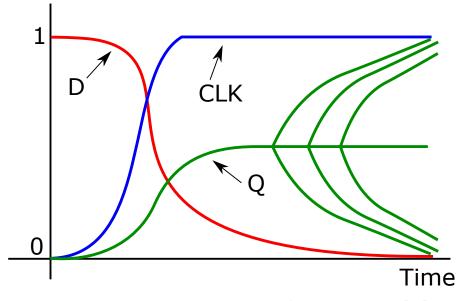

|             | state [47]                                 | 41 |

| Figure 2.26 | The mutual exclusion element [69]          | 42 |

| Figure 3.1  | A simple RC discharging circuit            | 45 |

| Figure 3.2  | RC discharging time                        | 48 |

| Figure 3.3  | RC load QDC                                | 49 |

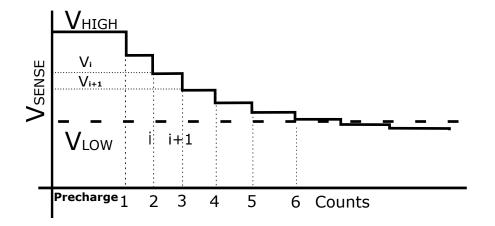

| Figure 3.4  | Signal performance during the discharging  |    |

|             | process [32]                               | 50 |

| Figure 3.5  | Signal performance during the discharging  |    |

|             | process [32]                               | 52 |

| Figure 3.6  | RC load replaced by ring oscillator [32]   | 52 |

| Figure 3.7  | Signal performance during the discharging  |    |

|             | process [32]                               | 54 |

| Figure 3.8  | Discharge process                          | 55 |

| Figure 3.9  | Fast capacitance-to-digital converter with |    |

|             | internal reference [25]                    | 58 |

| Figure 3.10 | Time reference using inverter chain        | 59 |

| Figure 3.11 | The proposed QDC                           | 60 |

| Figure 3.12 | Iterative delay chain discharge method     | 60 |

| Figure 4.1  | Asynchronous Implementation                | 63 |

| Figure 4.2  | Charging/Discharging Circuit               | 65 |

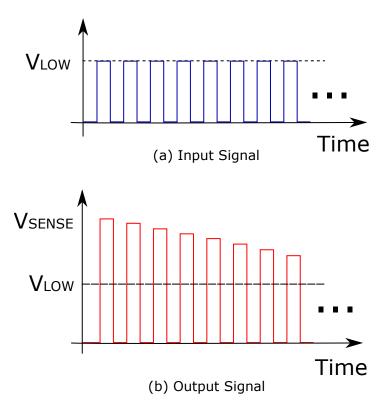

| Figure 4.3  | Operation of capacitor charging and dis-                 |            |

|-------------|----------------------------------------------------------|------------|

|             | charging 6                                               | 5          |

| Figure 4.4  | Schematic of the signal generator 6                      | 6          |

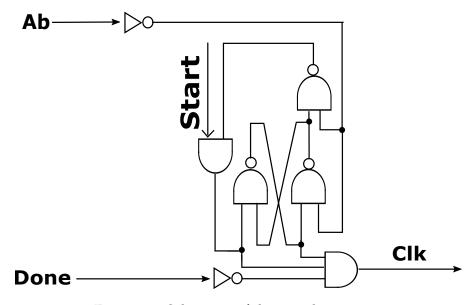

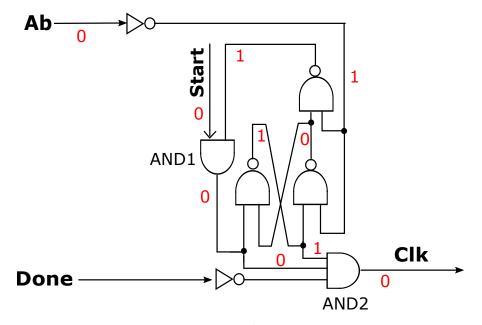

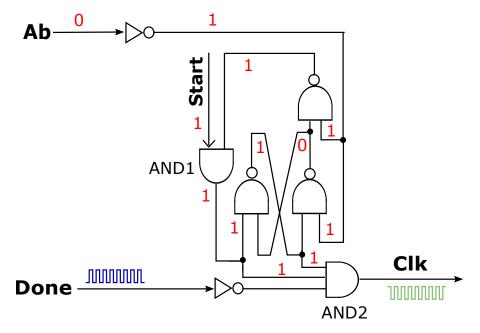

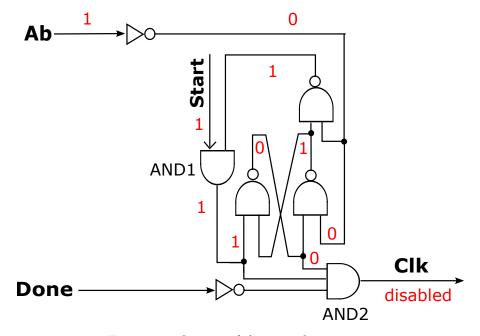

| Figure 4.5  | Initial state of the signal generator 6                  | 7          |

| Figure 4.6  | State 2 of the signal generator 6                        | 68         |

| Figure 4.7  | State 3 of the signal generator 6                        | 68         |

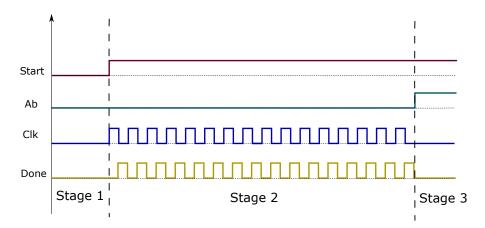

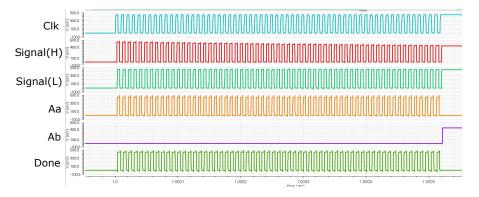

| Figure 4.8  | Timing diagram of the signal generator 6                 | 9          |

| Figure 4.9  | Event Generator                                          | 70         |

| Figure 4.10 | Output of event generator                                | 70         |

| Figure 4.11 | Schematic of event comparator 7                          | 71         |

| Figure 4.12 | Timing diagram of event comparator 7                     | 73         |

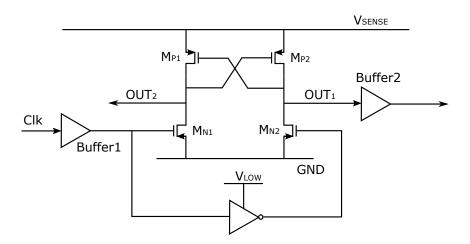

| Figure 4.13 | Schematic of the level shifter                           | <b>'</b> 5 |

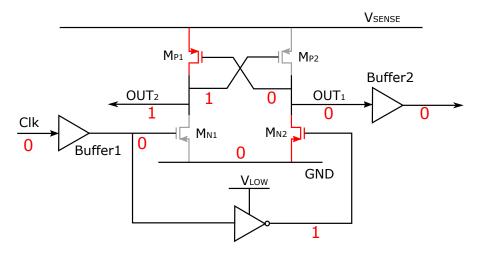

| Figure 4.14 | When $Clk$ signal is at logic 'o'                        | <b>'</b> 5 |

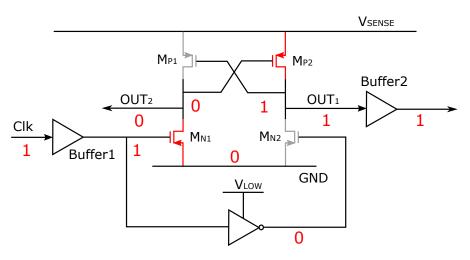

| Figure 4.15 | When <i>Clk</i> signal is at logic $'1' \ldots \cdots 7$ | 76         |

| Figure 4.16 | The operation of the level shifter 7                     | 76         |

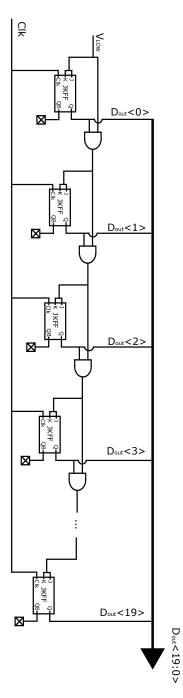

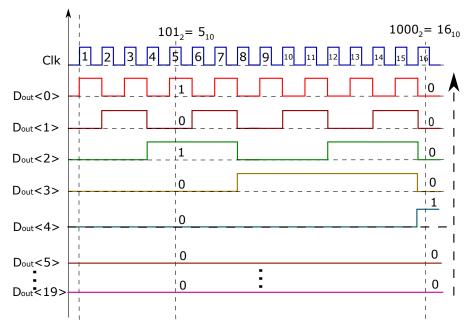

| Figure 4.17 | schematic of the counter                                 | 78         |

| Figure 4.18 | Timing diagram of the counter 7                          | '9         |

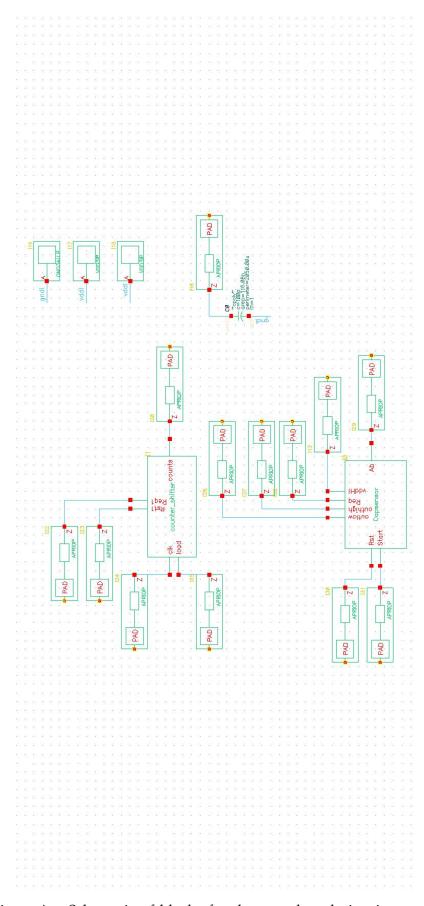

| Figure 4.19 | complete design                                          | 80         |

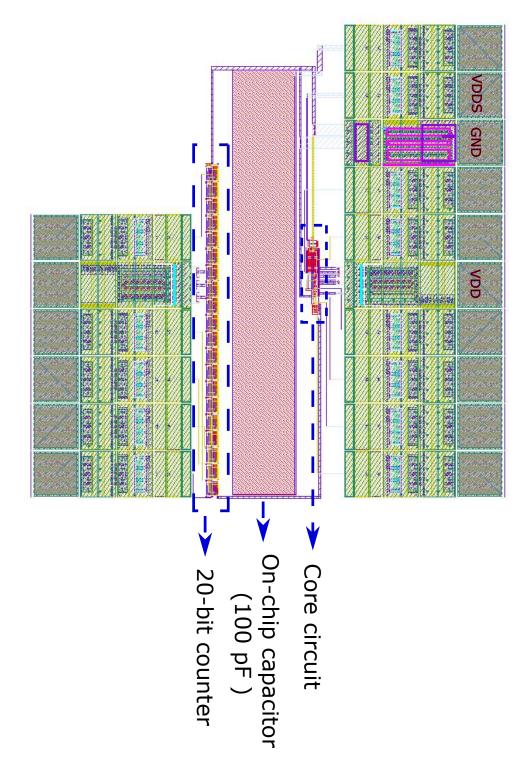

| Figure 4.20 | complete design. The design is imple-                    |            |

|             | mented in a 350nm process and covers an                  |            |

|             | area of 1000µm by 996.45µm. The QDC                      |            |

|             | consists of the charging/discharging cir-                |            |

|             | cuit, event generator, event comparator,                 |            |

|             | signal generator and level shifter 8                     | 32         |

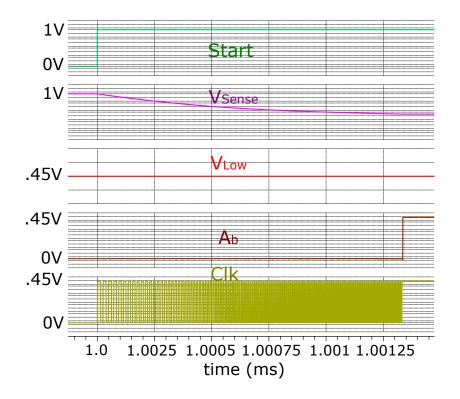

| Figure 5.1  | Simulation Results                                       | 5          |

| Figure 5.2  | Simulation Results                                       | 5          |

| Figure 5.3  | Simulation Results                                       | 37         |

| Figure 5.4  | Overall Performance                                      | 88         |

| Figure 5.5  | Simulation Results                                       | 89         |

| Figure 5.6  | Implementation size comparison 9                         | )0         |

| Figure 5.7  | Test Chip Micrograph91                                      |

|-------------|-------------------------------------------------------------|

| Figure 5.8  | Test PCB layout         92                                  |

| Figure 5.9  | 169 Contacts PGA Socket 93                                  |

| Figure 5.10 | final chip                                                  |

| Figure 5.11 | Picture of the test setup 94                                |

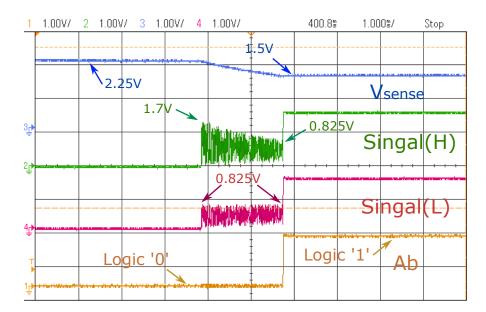

| Figure 5.12 | Chip performance with a 10 $\mu$ F capacitor . 95           |

| Figure 5.13 | Chip performance with a 100nF capacitor . 95                |

| Figure 5.14 | Zoom-in signals when $V_{SENSE}$ drops to                   |

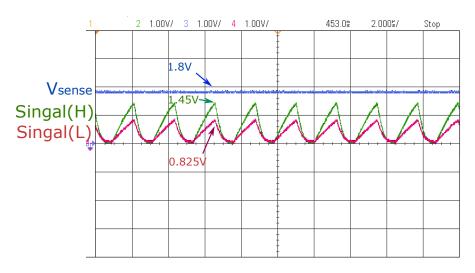

|             | 1.8V                                                        |

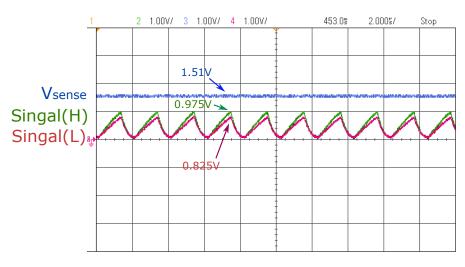

| Figure 5.15 | Zoom-in signals when $V_{\text{SENSE}}$ drops to 1.51V $96$ |

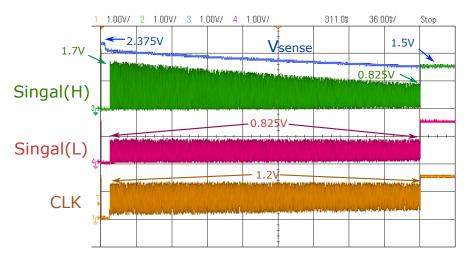

| Figure 5.16 | Chip performance with the 'CLK' signal . 97                 |

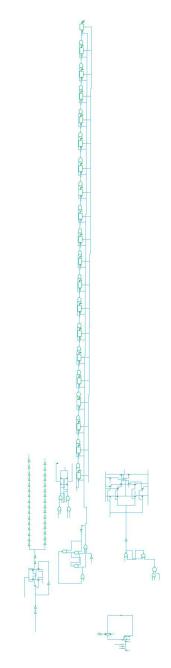

| Figure A.1  | Schematic of QDC design in 90nm tech-                       |

|             | nology                                                      |

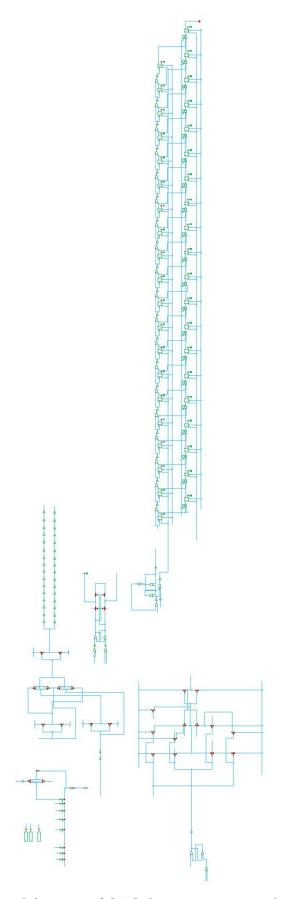

| Figure A.2  | Schematic of QDC design in 350nm tech-                      |

|             | nology                                                      |

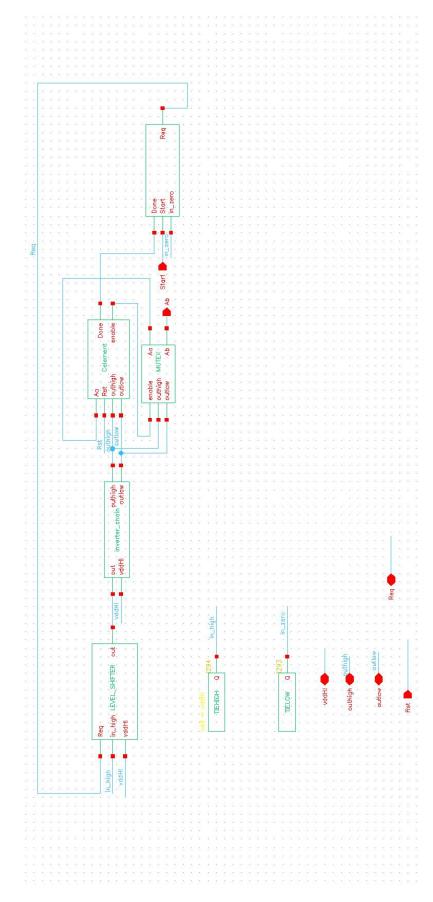

| Figure A.3  | Schematic of blocks for the core circuit in                 |

|             | 350nm technology 107                                        |

| Figure A.4  | Schematic of blocks for the complete de-                    |

|             | sign in 350nm technology                                    |

# LIST OF TABLES

| Table 2.1 | Applications of capacitive sensors          | 14 |

|-----------|---------------------------------------------|----|

| Table 2.2 | Truth table of Multiplexer [43]             | 22 |

| Table 2.3 | Overview of different capacitance-to-       |    |

|           | digital converter (CDC) techniques          | 28 |

| Table 2.4 | Overview of different voltage sensing tech- |    |

|           | niques                                      | 33 |

| Table 4.1 | Truth table of C-element [69]     | 73 |

|-----------|-----------------------------------|----|

| Table 4.2 | Truth table of the 20 bit counter | 79 |

#### ACRONYMS

- QDC charge-to-digital converter

- CDC capacitance-to-digital converter

- ADC analog-to-digital converter

- PCB printed circuit board

- **CVC** capacitance-to-voltage converter

- SAR successive approximation

CDAC capacitive digital-to-analog converter

- TDC time-to-digital converter

- TDCs time-to-digital converters

- **RO** ring oscillator

VPwC voltage-to-pulse width converter

- EH energy harvesting

- **VCO** voltage controlled oscillators

- PMOS p-type metal-oxide-semiconductor

- NMOS n-type metal-oxide-semiconductor

- **MUTEX** mutual exclusion

- LVS Layout verse schematic

- DRC Design Rule Check

- PGA pin grid array

- PCB printed circuit board

- MUTEX mutual exclusion

- IoT Internet of Things

- WSN wireless sensor network

# Part I

# **Thesis Chapters**

# 1

### INTRODUCTION

#### 1.1 MOTIVATION

The term Internet of Things (IoT) was initially proposed by Kevin Ashton in 1999 [5]. The basic concept of IoT is that every object in the real world can be connected together with the internet [72]. Many people believe that building a smart world is the goal for the near future, where the world itself will be covered by sensing and actuation [70]. During the last two decades, the research on IoT has been developed tremendously [80, 31, 56]. The dream of a smart world is becoming closer. Nowadays, for instance, home automation develops fast to provides a more convenient life style for people than before [26]; Many buildings have sensors to save power [11, 83, 70]; Mobile phones with sensors help people achieve things that was not possible before [14]; Wearable devices in healthcare monitor people's body conditions in real time [45, 44]. However, all of these are still at early stages of development and are not qualified enough to build a smart world [70]. One important issue is the degree of the density of sensing coverage. In the world of IoT, the density of sensing coverage should be way higher than today [70].

The wireless sensor network (WSN) is one of the foundational technology for IoT [80]. The wireless sensor plays a vital role as a bridge connecting the physical world and the information world [72]. The increasing density of sensing for IoT means more power

consumption and cost on WSN in total. Integrating sensors into small wireless networked nodes thus becomes a huge challenge due to the low power/energy budget in wireless sensor systems [32]. The integrated sensor normally consumes significant power and has complex design which increases the cost.

Sensors, as a key part of the WSN, are hot topics in industrial and research fields [36, 3, 41, 13]. A sensor is a device which can detect a physical parameter (e.g., humidity, temperature, pressure, voltage, etc.) from a target and then output a digital or other desired signal corresponding to and representing this parameter to fulfil requirements such as data transmission, processing, storage, recording and controlling [6].

The capacitive sensor is one of the widely used types in the sensor family [17, 75]. Capacitive sensors are a solution of sensing and measuring many different types of quantities [6] because a large number of physical quantities can be made to charge a capacitor so that this charge reflects the value of the parameter [81]. Unlike other sensors, capacitive sensors can detect both conductive and non-conductive materials [58, 74]. Moreover, capacitive sensors tend to consume lower power compared to others so the battery life for small portable products may last for a very long time [6].

The voltage sensor is also a very important type of sensors in many applications [84, 76, 68]. A voltage sensor can detect and/or measure voltages and transform them into efficient output signals in order to monitor or control the voltage of an equipment or a system. For example, in Energy Harvesting systems, voltage levels are monitored during energy accumulation. Based on the different voltage levels, different tuning mecha-

Figure 1.1: Basic sensing system

nism are used to achieve greater energy accumulation efficiency [81].

Both of the above types of sensors may need sensor interfaces [39, 46]. Fig. 1.1 shows a simple basic sensing system. A sensor interface is used to transform a measured analogue signal (e.g., capacitance, voltage level) from an external sensor into a frequency output or a digital code [85] for use in a digital system e.g., a microcontroller. Typically, sensor interface requires complex analogue circuits, e.g., amplifiers and analog-to-digital converter (ADC), which increase design complexities and often require additional power consumption [32, 81]. An all-digital converter will significantly reduce the power consumption comparing with the conventional converters. The development of the digital converter will be shown in the literature review below.

The sensor interface in a capacitive sensor is typically realized with a capacitance-to-digital converter (CDC), which converts a sensed capacitance value to a digital code. A CDC can be implemented with a charge-to-digital converter (QDC), which converts the amount of charge on a capacitor to a digital code. On the other hand, a QDC can also be used in other sensing applications unrelated to capacitance sensing where it does not serve as a CDC , and a CDC can also be implemented with other non-QDC methods. The distinction between CDC and QDC is an important concept throughout this thesis.

#### **1.2 THESIS CONTRIBUTION**

The aim of this thesis is to present a power efficient QDC that can be used in both capacitive sensing and voltage sensing systems. The following contributions are made as a result of this research work.

- An all-digital capacitor-based QDC is proposed. This QDC is capable of not only sensing capacitance but also sensing voltages by using fully digital solutions based on iterative delay chain discharge. Unlike the conventional methods that only treats the sensed capacitance only as the input signal, this thesis proposes a method that can also directly use the stored energy from the sensed capacitance to power parts of the circuit, which simplifies the design and saves power. By playing with the capacitance and input voltage, it can be used as a CDC to sense capacitance under fixed input voltage and also can be used as a capacitor-based voltage sensor to measure voltage level under fixed capacitance. The all-digital design results in low power, low energy consumption, fast response time, high resolution and low system complexity compared to other CDCs and QDCs.

- A test chip consisting of the all-digital QDC was fabricated and used in experimental tests for validation purposes, in addition to extensive simulation analysis.

#### **1.3 PUBLICATIONS**

The published paper can be seen as following:

- Y. Xu, D. Shang, F. Xia and A. Yakovlev, A smart all-digital charge to digital converter, 2016 IEEE International Conference on Electronics, Circuits and Systems (ICECS), Monte Carlo, 2016, pp. 668-671. doi: 10.1109/ICECS.2016.7841290

- D. Shang, Y. Xu, K. Gao, F. Xia and A. Yakovlev, *Low power voltage sensing through capacitance to digital conversion*, 2016 IEEE 19th International Symposium on Design and Diagnostics of Electronic Circuits and Systems (DDECS), Kosice, 2016, pp. 1-6. doi: 10.1109/DDECS.2016.7482476

- K. Gao, Y. Xu, D. Shang, F. Xia and A. Yakovlev, Wideband dynamic voltage sensing mechanism for EH systems, 2015 25th International Workshop on Power and Timing Modeling, Optimization and Simulation (PATMOS), Salvador, 2015, pp. 185-192. doi: 10.1109/PATMOS.2015.7347605

- 4. D. Shang, O. Benafa, F. Xia, Y. Xu and A. Yakovlev, An elastic timer for wide dynamic working range, 2015 IEEE 13th International New Circuits and Systems Conference (NEWCAS), Grenoble, 2015, pp. 1-4. doi: 10.1109/NEW-CAS.2015.7182004

#### 1.4 ORGANIZATION OF THESIS

This thesis is organized into six chapters, as shown in Fig. 1.2. Their contents are described as followed:

Chapter 1 "Introduction": introduce the motivations, contributions, publications and organization of this thesis. Chapter 2 "Background and Literature Review": This chapter provides a background knowledge of capacitive sensors and their applications. subsequently, it presents a coherent overview of existing approaches for sensor interfaces including ADC-based CDC, and Frequency/time-based CDC. Moreover, it shows the existing voltage sensing technologies. It also studies the operation of capacitor discharging through a ring oscillator. In addition, the characteristic of metastability and its solution is introduced. In the end, it discusses the existing QDC with their advantages and disadvantages.

Chapter 3 "General theory of Digital Discharge QDC": This chapter presents the design process from a simple RC discharging circuit to an iterative delay chain discharge method which can form the foundation for QDC. The mechanism and algorithm behind these methodologies are explained. It also studies the capacitance to digital discharge progress. The mathematical theory shows that the proposed design can not only sense capacitance under fixed input voltage but also can sense voltage under fixed input capacitor.

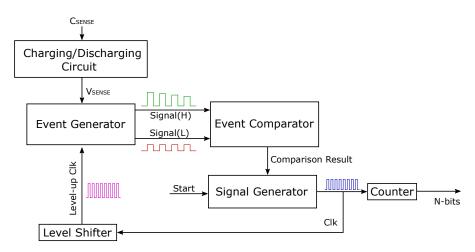

Chapter 4 "Design and Implementation": In this chapter, a detailed QDC design which contains six blocks is provided. Firstly, it presents the asynchronous implementation of the design. Then the functions of each block are explained with the circuit designs and timing diagrams in detail.

Chapter 5 "Experimental Results and Validations": This chapter firstly presents the simulation results in terms of power consumption, total energy, response time, output codes. A summary of the measured results of the QDC will be presented in a table and compared to the state of art benchmark. Then the fabricated chip and its test platform is showed. Finally, the chip performance is discussed based on the tested results.

Chapter 6 "Conclusions and Future Work": This chapter summarizes the contributions of the thesis and includes a critical review of this research as well as the prospective future work.

Figure 1.2: Thesis orginization.

## BACKGROUND AND LITERATURE REVIEW

#### 2.1 INTRODUCTION

Section 2.2 will show an overview of capacitive sensing including the characteristics of capacitors and applications of capacitive sensors. The capacitance-to-digital converter (CDC) will thereafter be presented in section 2.3. This section will start by introducing how a CDC is used in a capacitive sensing system as well as the main types of the CDC. After that, the detailed methodologies of modern CDCs will be presented with their advantages and disadvantages discussed. In section 2.4, the principle of voltage sensing will be presented by giving some examples of the existing voltage sensing techniques. Section 2.5 will introduce the principles of the charge-to-digital conversion system. In section 2.6, the principle of capacitor discharging through a ring oscillator will be presented. The final section of this chapter, section 2.7 will explore the definition of metastability and the mutual exclusion (MUTEX) element.

#### 2.2 CAPACITIVE SENSING

#### 2.2.1 Capacitors

The capacitance of a capacitor can be calculated as [74, 10]:

$$C = \varepsilon_r \frac{\varepsilon_0 A}{d} \tag{2.1}$$

where,

c is the capacitance in farads (F),

$\epsilon_r\,$  is a dielectric constant of the material between the two plates,

$\epsilon_0\,$  is permittivity of free space and is equal to  $8.85\times 10^{12}$  F/m,

A is the area of each plate in  $m^2$  and

d is the distance between two plates.

According to the Eq. 2.1, except  $\varepsilon_0$  which is a constant, the rest three parameters:  $\varepsilon_r$ , *A* and *d* become the factors that change the characteristics of a capacitor. In other word, the functions of different capacitive sensors are determined by varying any of these three parameters.

#### 2.2.2 Capacitive Sensors

A large number of capacitive sensors with different functions have been developed [4, 18, 16, 34, 55]. Some typical applications of capacitive sensors are shown below:

*Proximity Sensor*: A capacitive proximity sensor is a type of sensors that can provide non-contact detection of nearby ob-

jects. Unlike inductive proximity sensors which can only detect metal objectives, capacitive proximity sensors can detect not only electrically conductive, but also non-conductive objects such as glass, plastics, paper and so on [58, 74]. The key parts of a typical capacitive proximity sensor is a capacitive probe, an oscillator and a controller unit. When a target gets near the capacitive probe, the electric field around the capacitor changes. This results in a change of the oscillator frequency. It is then detected and sent to controller unit [58, 74]. Because there is no direct contact between a capacitive proximity sensor and a sensed object, it is very reliable and has long functional life [74].

*Humidity Sensor*: Humidity plays an important role in many areas such as manufacture industry, agriculture, comfortability of daily life and so on [71]. For a capacitive humidity sensor, the dielectric constant of material  $\varepsilon_r$ , in this case, air, is influenced by humidity. According to Eq. 2.1, the value of a capacitance is in direct proportion of  $\varepsilon_r$ [74]. Basically, when temperature goes higher, the air holds more moisture. The dielectric between two plates in the capacitor then collects more moisture, which causes the change of  $\varepsilon_r$  and results in the change of capacitance [85].

*Liquid level sensor*: Liquid level sensors are widely used to monitor the liquid volume in industry and medical field [27]. In a capacitance, the dielectric constant changes when the device occupies different levels of liquid because the relative permittivity of liquid and air are different. When the plates start to fill with liquid, more and more space, in other words, the dielectric, between the two plates will be filled by liquid as well. The capacitance will then increase because liquid has more ability to hold electric charge than air [74, 20].

Figure 2.1: CDC-based Capacitive sensing system

Table 2.1 shows a case study of how capacitive sensors are used in our daily life in terms of its working environment, description and sensor type, and receptively.

#### 2.3 CAPACITANCE TO DIGITAL CONVERTER

In the modern capacitive sensor interface technologies, standardized and easy to read output are two main goals leading the research direction [50]. In capacitive sensor design, a CDC is commonly used as a sensor interface.

Fig. 2.1 shows a typical CDC-based capacitive sensing system. Mainly, it includes three different sections. These are a conductive pad, a CDC section and a data transmission section. The conductive pad normally can be either a simple piece of metal, or a conductive trace on a printed circuit board (PCB). The CDC section includes a capacitance to digital converter. The data transmission section contains an interface such as a USB and is managed by a microcontroller.

Let us take a proximity sensor as an example. When the object is at a detectable distance from the conductive pad, it produces a capacitance and refers to CDC. The CDC then converts the capacitance to digital output. Then the output signal from CDC transmits to microcontroller to process the digital data. At last, these data are sent to computer through USB. When the target moves towards or away from the capacitive pad within an

|                          | ladle 2.1: Appi                 | Table 2.1: Applications of capacitive sensors.                                                                                                                                                                                                                                          |           |

|--------------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Sensor type              | Scenarios                       | Description Re                                                                                                                                                                                                                                                                          | Reference |

| Proximity sen-<br>sor    | In most smart phones us-<br>age | To detect whether the user is listening to the [64] call with or without the loudspeaker. When a user answers a call without the loudspeaker and his/her ear is near the phone, the sensor implemented in the mobile phone detects this and turns off the screen light to save battery. | 54]       |

| Humidity Sen-<br>sor     | In production of noodles        | Humidity sensors are widely used in noodle pro-<br>duction such as flour moisture control, noodle<br>drying, swear stage humidity monitoring and<br>so on.                                                                                                                              | 57]       |

| Liquid level sen-<br>sor | Rain gauge                      | Liquid level sensors are often used as rain [27] gauges to monitor the level of rainfall, which is an important parameter for weather station to analyse the climate.                                                                                                                   | 27]       |

| Displacement<br>sensor   | Thickness Measurement           | Measuring if the thickness of rolled steel sheets [33] is uniform, if the thickness of laminated glass achieves the standard, etc.                                                                                                                                                      | 33]       |

| Tilt sensor              | Anti-theft system in car        | Prevent a vehicle from being stolen. When the [77] vehicle is being lifted by a car jack, the tilt sensor will detect the attempt of removing the wheels.                                                                                                                               | 77]       |

Table 2.1: Applications of capacitive sensors.

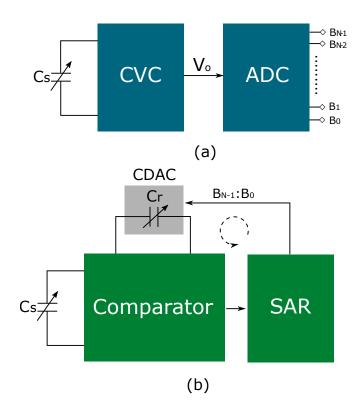

Figure 2.2: Two different types of CDCs (a) CDC based on ADC modulation; (b) CDC based on frequency/time modulation

effective range, the capacitance changes because electric fields between the target and conductive pad changes. Then the capacitive sensor repeats the above steps and generates new output data.

Fig. 2.2 shows two general types of CDCs based on different modulations. Conventional CDCs are based on an analog-todigital converter (ADC), which contains ADC-related techniques, as shown in Fig. 2.2(a). They convert capacitance to electrical signals and measured with ADCs. The other type of CDCs uses Frequence/Time modulations, as shown in Fig. 2.2(b). They transform capacitance into frequencies or periods and often measure with time-to-digital converters (TDCs).

#### 2.3.1 ADC-related CDC

The ADC-baesd CDC technique is unrelated to the proposed design in this thesis. Hence, only a short review are presented.

Fig. 2.3(a) shows a ADC-based CDC that transform the sensor capacitance  $C_s$  into a output analog voltage  $V_o$  by using a capacitance-to-voltage converter (CVC).  $V_o$  then is digitized via an ADC [23, 79].

Figure 2.3: ADC-based CDC

Another ADC-related CDC is called a successive-approximation CDC [54, 30], which is shown in Fig. 2.3(b).  $C_s$  represents sensor capacitance.  $C_r$  is a reference capacitance implemented in a capacitive digital-to-analog converter (CDAC). The comparator compares the capacitance values  $C_s$  and  $C_r$ . A successive approximation (SAR) is a commonly used technique in an ADC, which can also implements in an CDC. According to the results of the comparison, the SAR keeps sending different digital outputs to CDAC to get different  $C_r$  until the values of  $C_s$  and  $C_r$  matches with each other.

There are some advantages of ADC-based CDCs. ADC techniques are very mature with several modulations such as Discrete-Time  $\Delta\Sigma$  modulation [52], Continuous-Time  $\Delta\Sigma$  modulation [48], SAR modulation [54], etc. It is very convenient to design CDCs with these existing modulations. However, the ADC

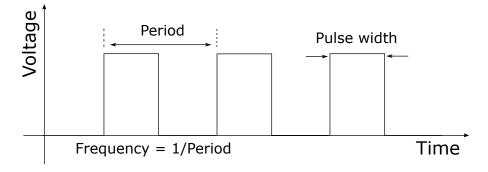

Figure 2.4: Digital waveform

consumes external power and increases the complexity which may lead to high power consumption, slow response time.

#### 2.3.2 Frequency/Time-based CDC

This section introduces some examples of frequency/time based CDCs. Fig. 2.4 shows some basic definition in a digital waveform which is related to the work below. The period refers to the duration time taken to complete one cycle in a repeating event. The frequency is the number of repeating cycles in a unit of time, which can be expressed as 1/period. The pulse width is the duration time for a pulse to maintain it's maximum amplitude [9]. The CDCs shown in this section are all based on the theory that the sensed capacitors are in a relation of these factors.

#### 2.3.2.1 Period Modulation-based CDC

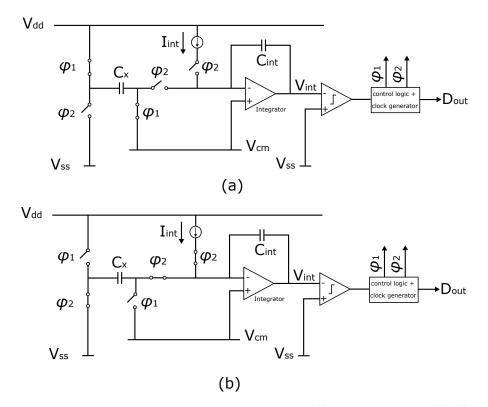

Fig. 2.5 shows a typical period modulation based CDC. It uses relaxation oscillators [78] that converts the sensed capacitance to a period time. First,  $\varphi_1$  sets to on and  $\varphi_2$  sets to off, , as is shown in Fig 2.5(a). The sensed capacitance  $C_x$  is charged because it is connected between  $V_{dd}$  and a mid-supply common-mode reference  $V_{cm}$ . Then  $\varphi_1$  sets to off and  $\varphi_2$  sets to on, ,as is shown

Figure 2.5: Period modulation:(a)  $\varphi_1$  on, $\varphi_2$  off; (b)  $\varphi_2$  on, $\varphi_1$  off [73]

in Fig 2.5(b).  $C_x$  is connected between  $V_{ss}$  and the virtual ground of an active integrator. The charge from  $C_x$ , which is  $C_x \times V_{dd}$ , is then transferred to an integrated capacitor  $C_{int}$ . This causes a step up for the output of the integrator  $V_{int}$ . The charge from  $C_{int}$  is then removed by a constant integration current  $I_{int}$  until  $V_{int}$  returns to its original level. This is detected by a comparator at the output of the integrator. The time interval  $T_{msm}$  in Fig 2.6, which is the time difference from the start of phase  $\varphi_2$  until  $V_{int}$ crosses the threshold of the comparator, is then proportional to  $C_x$  [73, 28]:

$$T_{msm} = \frac{V_{dd}}{I_{int}} C_x$$

(2.2)

This means  $T_{msm}$  can be used to measure  $C_x$ . And by counting the number of cycles of a faster reference clock during this

Figure 2.6: Period modulation associated waveforms

period by a digital counter or microcontroller, an output code is then obtained [73, 28].

The advantage of this design is that it is operated asynchronously which means it does not need a clock signal. The input capacitance range can also be very large with high resolution [73]. However, it needs a high quality amplifier to act as an integrator and the constant current source design is a very costly approach which makes the design more complicated.

#### 2.3.2.2 Pulse width Modulation-based CDC

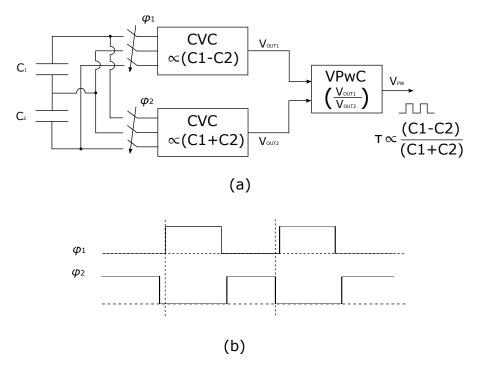

Fig. 2.7 shows the block diagram of a pulse width modulation [86, 67] based CDC. As can be seen from Fig. 2.7(a), it includes two CVCs and one voltage-to-pulse width converter (VPwC). The sensed capacitors  $C_1$  and  $C_2$  are from a differential capacitive

Figure 2.7: Structure of PW [2]

microsensor.  $\varphi_1$  and  $\varphi_2$  in Fig. 2.7(b) are two non-overlapping clock phases which act as switches of the corresponding CVCs. The top CVC generates an output voltage  $V_{OUT1}$  which is proportional to the difference between C<sub>1</sub> and C<sub>2</sub> (i.e. C<sub>1</sub>-C<sub>2</sub>), while the bottom CVC generates an output voltage  $V_{OUT2}$  which is proportional to the sum of C<sub>1</sub> and C<sub>2</sub> (i.e. C<sub>1</sub>+C<sub>2</sub>). The VPwC provides a pulse width which is proportional to the ratio of  $V_{OUT1}$  and  $V_{OUT2}$  (i.e.  $V_{OUT1}/V_{OUT2}$ ). This means by replacing the value of  $V_{OUT1}$  and  $V_{OUT2}$  with C<sub>1</sub> and C<sub>2</sub>, the output pulse width is proportional to the ratio of the difference to the sum of C<sub>1</sub> and C<sub>2</sub>, which is shown below [2]:

$$\tau \propto \frac{C_1 - C_2}{C_1 + C_2}$$

(2.3)

The pulse width based CDC may minimize the sensitivity to parasitic capacitances [12, 49, 2] with low power consumptions.

Figure 2.8: Frequency based CDC [22]

However, the performance is affected by the stability of clock signals which may affect the linearity.

## 2.3.2.3 Frequency modulation-based CDC

Fig. 2.8 shows a block digram of capacitance-to-frequency based [8] CDC. The sensed capacitance  $C_s$  is charged and discharged with two constant current sources  $I_c$ . The output voltage  $V_{OUT}$  decides the action of the switch. The hysteresis comparator is designed with two comparators COMP1 and COMP2 with different threshold voltages  $V_{tr+}$  and  $V_{tr-}$ , which transform the triangle voltage  $V_s$  on  $C_s$  into a square wave. The outputs of COMP1 and COMP2 are then sent to a multiplexer MUX [43], which has two inputs and a one output fed back to the strobe terminal. Table 2.2 shows the truth table of the multiplexer. If S=0, the output voltage  $V_{OUT}$  only depends on the state of input voltage  $V_{COMP2}$  and if S=1, the output voltage  $V_{OUT}$  only depends on the state of the input voltage  $V_{COMP1}$ . In other words, for  $V_s$  increasing, the output of the multiplexer is decided by  $V_{COMP2}$  and for  $V_s$  decreasing, it is decided by  $V_{COMP1}$  [22].

The constant current sources are controlled by a bias voltage  $V_b$ .  $C_s$  is charging when  $V_{OUT}$  is low. On the other hand, it

Table 2.2: Truth table of Multiplexer [43]

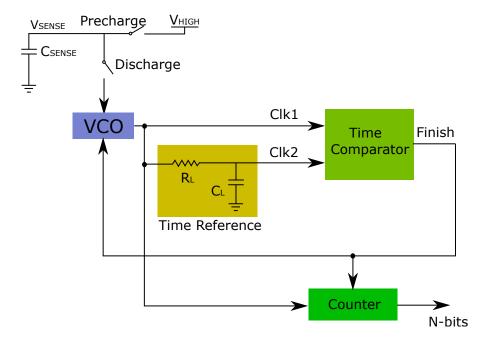

Figure 2.9: Structure of Iterative Delay-Chain Discharge based CDC [32]

is discharging when which charges when  $V_{OUT}$  is high. As a result, the frequency of  $V_{OUT}$  is a function of  $C_s$ . The output frequency can be converted by digital codes with a time-to-digital converter (TDC) and thus can be used as a CDC [22].

This design is suitable for low-voltage low-power capacitance sensor application. However, it suffers from the stability of the oscillator signal [1] and the design of constant current source complicates the design.

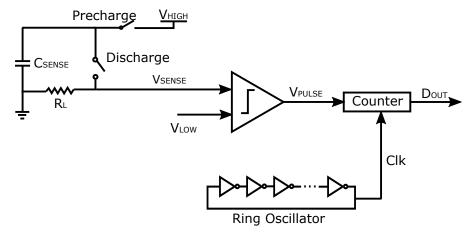

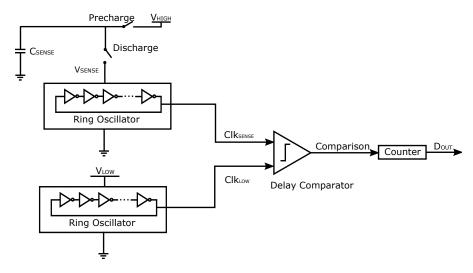

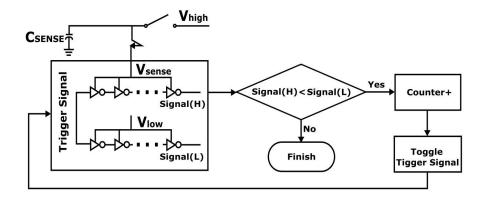

### 2.3.2.4 Iterative Delay-Chain Discharge based CDC

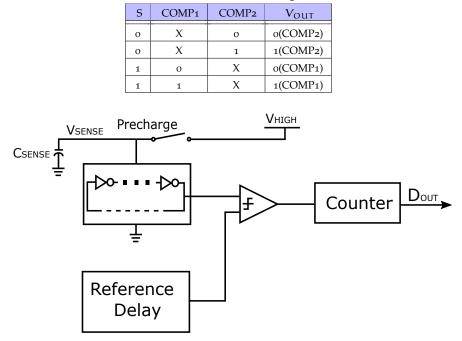

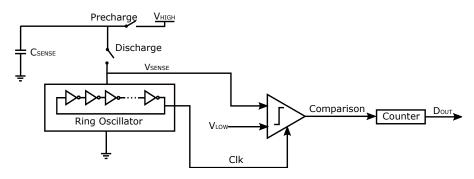

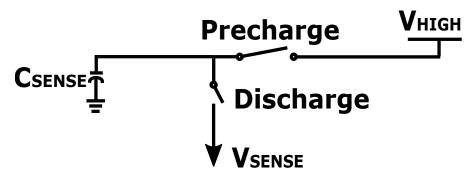

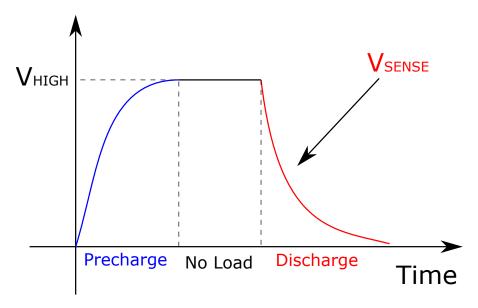

Fig. 2.9 shows a basic structure of iterative Delay-Chain Discharge based CDC that uses ring oscillators to transform sensor capacitance into digital outputs. It is based on the theory that when a ring oscillator (RO) [42] uses a charged capacitance as a power supply, the number of RO cycles required to discharge the

Figure 2.10: Iterative Delay-Chain Discharge based CDC [32]

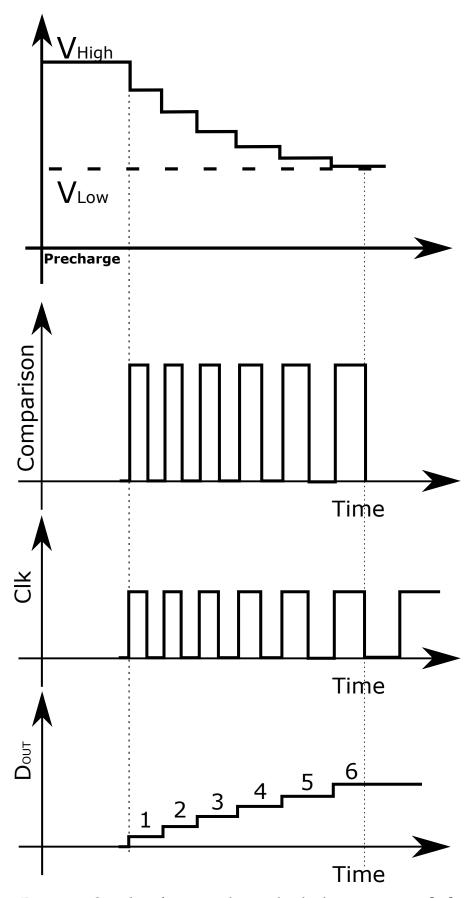

capacitance to a fixed voltage varies linearly with the capacitance value. This structure basically consists five parts: a capacitance charging/discharging block, a ring oscillator, a reference delay block, a delay comparator and a counter. The sensed capacitor  $C_{SENSE}$  is charged to  $V_{HIGH}$  by turning the *Precharge* switch on. After  $C_{SENSE}$  is fully charged, the *Precharge* switch turns off. The ring oscillator powered by  $V_{SENSE}$  then starts oscillating. During the oscillation, the RO draws some charge from  $C_{SENSE}$  and gradually lowering  $V_{SENSE}$ . As a result, the propagation delay of RO increases gradually. The comparator compares its delay with the reference delay. The counter counts the pulse number of the RO until the propagation delay of RO become longer than the reference delay and outputs the code  $D_{OUT}$  [32].

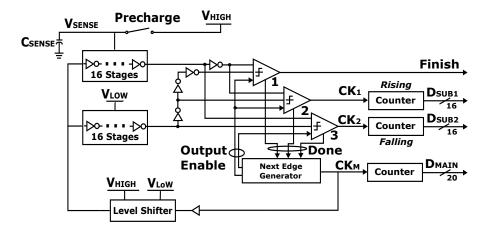

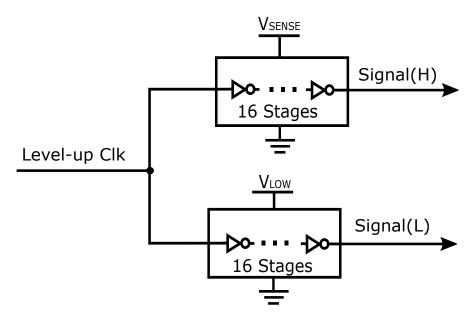

Fig. 2.10 shows the detailed architecture of this CDC. The CDC is built by two 16-stage inverter chains, three comparators, a clock generator, a level shifter and three counters. The circuit is powered by  $V_{LOW}$  to save power, except the upper inverter chain. In the first step, the precharge switch is on,  $V_{HIGH}$  charges the capacitor. After  $C_{SENSE}$  is fully charged, the precharge switch turns off and the second step starts. The two inverter chains which are supplied by  $V_{SENSE}$  and  $V_{LOW}$  respectively compare their

propagation delay in three comparators. The middle comparator compares their rising edges and the bottom comparator compares their falling edges. After each comparison, the next edge generator triggers the next discharge and delay comparison. The level shifter converts  $V_{LOW}$  to  $V_{HIGH}$  [32].

As the upper inverter chain is powered by  $V_{SENSE}$  from a charged capacitor, which is not an unlimited power source,  $V_{SENSE}$  keeps decreasing because the oscillation in the upper inverter chain drains the charge from  $C_{SENSE}$ . The top comparator, which takes a slightly delayed version of the reference delay, decides when to pulse a *Finish* signal to stop the overall conversion. The conversion stops when  $V_{SENSE}$  becomes lower than  $V_{LOW}$  by some margin. The middle and bottom comparators output pulses once only when the propagation delay of the top inverter chain is longer than the bottom inverter chain. The top two counters counts the number of pulses from comparators and output digital codes  $D_{SUB1}$  and  $D_{SUB2}$ . The bottom counter counts the main oscillation triggering signal and output digital codes  $D_{main}$  [32].

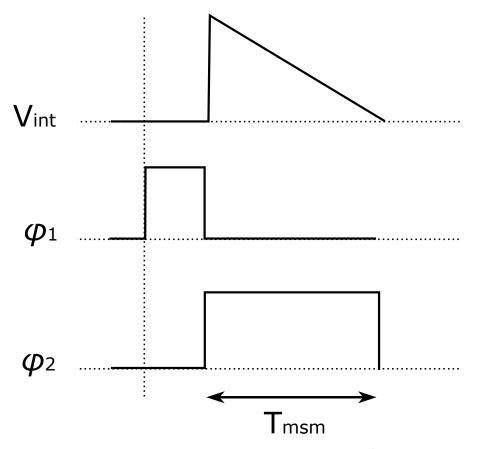

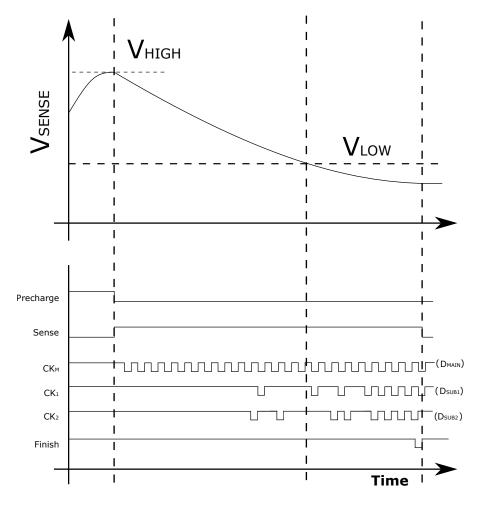

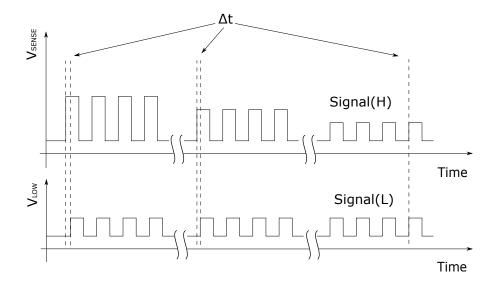

Fig. 2.11 shows the waveform of this design. After the capacitance precharge finishes, the *Sense* signal goes high to trigger the oscillation. Before  $V_{SENSE}$  falls some margin below the level of  $V_{LOW}$ , the next edge generator keeps outputting pulses  $CK_M$ . The clock signals  $CK_1$  and  $CK_2$  from the bottom two comparators pulse sporadically, due to noise, and more frequently as  $V_{SENSE}$  goes across  $V_{LOW}$ . After the *Finish* from the top com-

Figure 2.11: Waveform of Iterative Delay-Chain Discharge based CDC [32]

parator pulses, the oscillation stops. The final output code of comparator outputs D<sub>OUT</sub> is then calculated as [32]:

$$D_{OUT} = 2 \times D_{MAIN} - (D_{SUB1} + D_{SUB2})$$

(2.4)

The reason for using three comparators is to increase the accuracy by averaging noise over many comparisons when  $V_{SENSE}$ is closed to  $V_{LOW}$ . The number of comparisons is doubled by comparing both rising and falling edges. By extending the oscillation to where  $V_{SENSE}$  is lower than  $V_{LOW}$  by some margin, comparisons are performed through the whole noise region

Figure 2.12: Three scenarios [66]

around  $V_{LOW}$ . Hence, the false " $V_{SENSE} < V_{LOW}$ " decisions above  $V_{LOW}$  and false " $V_{SENSE} > V_{LOW}$ " decisions below  $V_{LOW}$  are compensated stochastically. By using the calculation method in Eq. 2.4, the output code  $D_{OUT}$  becomes centred at the number of exact counts from  $V_{HIGH}$  to  $V_{LOW}$ . Thus, the performance of linearity is improved [32].

This design is fully digital, and transforms the sensed capacitance directly into digital codes, which means it does not need complex circuits, such as amplifiers and ADCs. Comparing to conventional CDCs, it consumes less power. As the RO draws sensor capacitance directly from  $C_{\text{SENSE}}$  without a CVC, the input capacitance range is only limited by the counter size. However, there are still some disadvantages existed as following [66]:

*Problem 1: Extra power/Energy for correction.* There are three comparators implemented in this design to improve the linearity performance of output code corresponding to the sensor capacitance by using Eq. 2.4 for correction. This results in extra computation and more power/Energy consumption [66].

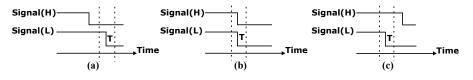

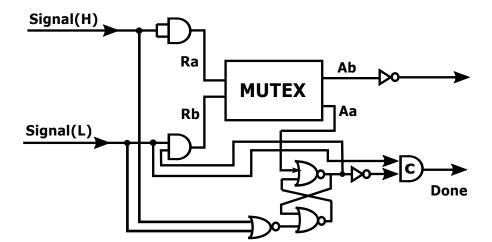

*Problem 2: Accuracy.* The errors may happen in the final results. In theory, only one comparator and one counter are needed for detecting the propagation delay when  $V_{SENSE}$  goes from  $V_{High}$  down to  $V_{LOW}$  and count the number of discharging iterations. However, instead of stopping comparison immediately the moment  $V_{SENSE}$  becomes lower than  $V_{LOW}$ , it uses a complicated method to introduce extra delays to let the comparison stop after  $V_{SENSE}$  becomes lower than  $V_{LOW}$  by some margin to minimize the error. One reason for this design is because of the three scenarios shown in Fig. 2.12 when  $V_{SENSE}$  discharges to and close to  $V_{LOW}$ . Signal(H) is the output signal of the top inverter chain and Signal(L) is the output signal of the bottom inverter chain in Fig. 2.10. Fig. 2.12(a) represents the state when Signal(H) comes earlier than Signal(L); Fig. 2.12(b) represents the state when Signal(H) and Signal(L) comes very closely; Fig. 2.12(c) represents the state when Signal(H) comes later than Signal(L) [66].

However, even with three comparators and counters, and the correction equation in Eq. 2.4, the signal in the comparator may not be triggered if metastability (This will be explained in section 2.7) happens in the scenario Fig. 2.12(b), which could causes the missing of counts and affects the accuracy of the final result [66].

### 2.3.3 Summary of existing CDC techniques

The above section discussed some existing CDC techniques. Each technique has its own advantages and disadvantages in terms of the trade-off among power consumption, resolution, capacitance range, etc. Table. 2.3 concludes an overview of different CDC techniques in terms of power consumption, capacitance range, resolution, etc. based on other researchers' review on the existing CDC techniques.

#### 2.4 VOLTAGE SENSING

Voltage sensing is also a very important technique for many applications [59, 24]. It transforms a sensed analog dc voltage

|                                    | Table 2.3: Overview of different CDC techniques                                     | erent CDC techniques                                                                                                                                                                                           |

|------------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Type                               | Advantages                                                                          | Disadvantages                                                                                                                                                                                                  |

| CVC+ADC                            | Relatively high resolution                                                          | Mostly power hungry [23];<br>Require complex signal conditioning circuits<br>[23];<br>Require large die area [23]                                                                                              |

| SAR                                | Relatively low power con-<br>sumption [38];<br>Excellent energy efficiency<br>[53]. | Limited capacitance range [40].<br>Medium resolution [62].                                                                                                                                                     |

| ΔΣ modulation                      | Very high resolution by virtue of oversampling and noise shaping [53].              | Power hungry [40];<br>Limited in dynamic range due to the fast over-<br>sampling clock frequency used [23]                                                                                                     |

| Dual-slope                         | Simplicity [62].                                                                    | Low energy efficient [62].                                                                                                                                                                                     |

| Period /Pulse width<br>modulation  | High resolution [48];<br>Large input capacitance<br>range [73];                     | Large measurement time[48];<br>High-resolution time reference decreases the en-<br>ergy efficiency[48];<br>Time-to-digital converter circuits (TDCs) are re-<br>quired which dissipate significant power [23]. |

| Iterative Delay-Chain<br>Discharge | High capacitor range;<br>Relatively low power con-<br>sumption [62].                | Need extra correction limited resolution [66];<br>Not suitable for sensing small capacitors despite<br>its wide sensing range [62].                                                                            |

Table 2.3: Overview of different CDC techniques

Figure 2.13: Single slope ADC [51]

into digital signals. This section introduces two techniques for the voltage sensing.

## 2.4.1 Reference-based Voltage Sensing

The most commonly used voltage sensing technique is the ADC. The ADC compares the input voltage  $V_{in}$  with a known reference voltage  $V_{ref}$  and generates a digital code corresponding to the  $V_{in}$  [37, 19, 51, 24].

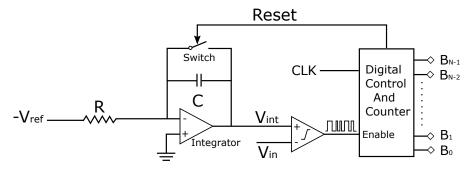

Fig. 2.13 shows a typical single slope ADC also known as an integrating ADC. The integration starts when  $V_{ref}$  inputs to the integrator and outputs the integrated voltage  $V_{int}$ .  $V_{int}$  is then compared against  $V_{in}$  by the comparator until  $V_{int}$  equals to  $V_{in}$ . The time it takes during the comparison is then encoded. The time encoded pulse then inputs to the counter as an enable signal which triggers the counter to count to a digital value which representing the time information. A digital control block controls the operation of the ADC. It resets the integrator after a set number of clock cycles elapse to make sure that there is enough conversion time for the counter to count the highest value which representing the full-scaled input voltage [51].

The disadvantage of the single slope ADC is that the accuracy is dependent on the integrator. The accuracy of the integrator is

also affected by the value of C and R. Even a slightly change of these parameters will completely affect the results [51].

# 2.4.2 Reference-free Voltage Sensing

In the energy harvesting (EH) system, the harvested energy may provide a low and unstable power supply. The introduced dynamic voltage sensing mechanism can sense the unstable voltage without a reference voltage [24].

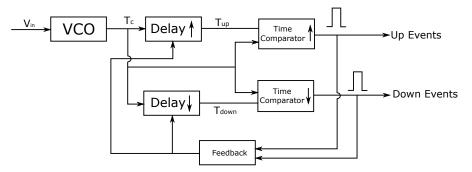

Fig. 2.14 shows the block diagram of the wideband dynamic voltage sensing mechanism. The voltage controlled oscillators (VCO) transform the input voltage  $V_{in}$  into the time domain, which is the frequency  $T_c$ . The top delay block generates a delayed frequency  $T_{up}$  to compare against  $T_c$  with the top time comparator to detect the voltage rising and generate an up event when the voltage increases by a sensing resolution  $\Delta v$ . If sensing starts at  $V_0$ , the voltage in the i<sup>th</sup> step of an up event can be calculated as  $V_0 + i\Delta v$ , if there is no down events happened [24],

The same thing happens in the bottom delay block and time comparator. The only deference is that it detects the voltage falling by comparing the delayed frequency  $T_{down}$  against  $T_c$  and generates the down events [24].

Figure 2.14: Reference-free voltage sensing mechanism [24]

Figure 2.15: Voltage tracking [24]

Either an up event or a down event triggers the next round of sensing by the feedback block until the system powers off, which can be seen in Fig. 2.15. The input voltage  $V_{in}$  thus can be calculated by counting the number of the events [24].

This voltage sensing technique can track or sense unstable voltage without a reference voltage. However, there is a trade-off between the resolution and power consumption. The resolution depends on the value of  $\Delta v$ . For higher resolution, a smaller  $\Delta v$  is needed, which increases the number of events. This means more comparison are required and it consumes more power in a result. If you want to decrease the power consumption, then the resolution are sacrificed.

Figure 2.16: Charge-to-Digital Conversion: (a) Charging process; (b) Discharging process[60]

## 2.4.3 Summary of existing voltage sensing techniques

The above section introduced the reference-based/reference-free voltage sensing techniques. Table. 2.4 concludes an overview of different voltage sensing techniques in terms of power consumption, voltage range, etc. based on other researchers' review on the existing voltage sensing techniques.

Table 2.4: Overview of different voltage sensing techniques

|                                                    | Table 2.4. Overview of different votage serious rectundues                                                                                                                                                                                                                         | mig recumidaes                                                                                             |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| Type                                               | Advantages                                                                                                                                                                                                                                                                         | Disadvantages                                                                                              |

| ADC                                                | Most widely used to convert voltage to<br>digital outputs<br>Relatively high power consumption [51].                                                                                                                                                                               | Requires a stable reference voltage which consumes more energy;<br>Relatively high power consumption [51]. |

| Power-on set                                       | May not need a stable reference voltageinherent references highly rely on circuitbut can be created from inherent properties of CMOS technologies which resultsinherent references highly rely on circuitties of CMOS technologies which resultsin low power consumption [24, 65]. | inherent references highly rely on circuit<br>structures [24].                                             |

| Charging and discharg-<br>ing a sampling capacitor | Fully digital;<br>Low power consumption [24].                                                                                                                                                                                                                                      | relatively long response time [24].                                                                        |

| SRAM+inverter chain                                | Reference free; Detect huge range of sup-<br>ply voltage [35]; High accuracy [24]; Fast may increase power consumption [24].<br>response time [24].                                                                                                                                | the circuit area is relatively large which<br>may increase power consumption [24].                         |

|                                                    |                                                                                                                                                                                                                                                                                    |                                                                                                            |

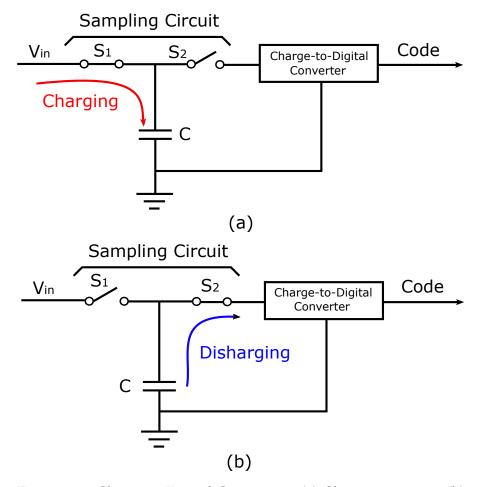

#### 2.5 CHARGE TO DIGITAL CONVERTER

A charge-to-digital converter (QDC) is used to convert the amount of charge stored in a capacitor to a binary output code. Fig. 2.16 shows a system overview of a charge-to-digital conversion. A capacitor is used to transform an input voltage  $V_{in}$  into a certain amount of energy contained in the form of a charge stored on this capacitor. A QDC provides reliable conversion of the stored energy to a binary code on the output [60]. This is realized in two steps. Fig. 2.16(a) shows a first step, which is the capacitor charging process. The sampling circuit turns the switch S<sub>1</sub> on and switch S<sub>2</sub> off. The capacitor will then be charged to  $V_{in}$ . In the second step shown in 2.16(b), after the capacitor is fully charged, the switch S<sub>1</sub> turns off and switch S<sub>1</sub> turns on. This results in a capacitor discharging process. The energy stored in the capacitor will then be converted to a binary code by a QDC [60].

The code number depends on the charge stored in the capacitance. As can be seen in Eq. 2.5 below [74, 10], different values of C and V affect the amount of charge Q, in other words, changes the output code. Hence a QDC can either be used as a CDC to sense capacitance under a fixed input voltage, or be used as a voltage sensor to sense voltage under a fixed input capacitance. The detailed explanation will be found in chapter 3.1.

$$Q = C \times V \tag{2.5}$$

Where,

Q is the stored charge in coulomb(C),

c is the capacitance in farads(F),

v is the voltage cross the capacitor in volts(V).

Unlike a conventional CDC which needs an external power supply to sense the capacitance, in a QDC system, the stored energy from the capacitance is not wasted and can be used to power the circuit, which simplifies the design and saves power.

#### 2.6 RING OSCILLATOR

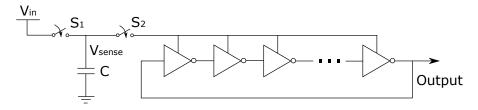

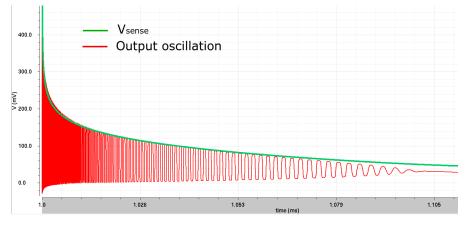

Figure 2.17: Ring oscillator powered by capacitor[59]

Figure 2.18: Ring oscillator discharging

Fig .2.17 shows a capacitor discharging through a ring oscillator. The ring oscillator is made of an odd number of inverters to produce the oscillation [42]. In step one, the switch  $S_1$  is on and  $S_2$  is off. The capacitor C is then be charged to the input voltage  $V_{in}$ . After the capacitor is fully charged, the second step begins. The switch  $S_1$  turns off and  $S_2$  turns on. The voltage  $V_{sense}$  on the capacitance starts to power the ring oscillator. The ring oscillator powered by higher voltage produces higher oscillation frequency. Thus, the oscillation frequency is high in the beginning when  $V_{sense}$  is high. Then, every step of oscillation draws some energy from the capacitor. As a result,  $V_{sense}$  becomes lower. Thus, oscillation frequency becomes lower. The simulation results of the output oscillation is shown in Fig. 2.18. It clearly shows that the oscillation draws the energy from the capacitance, which decreases  $V_{sense}$ . In return,  $V_{sense}$  keeps decreasing and slowing the oscillation. In the end, the energy runs out and the oscillation stops [59].

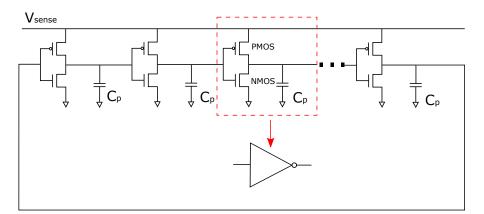

Figure 2.19: Schematic of inverters

Fig. 2.19 shows the schematic of inverters in the ring oscillator. An inverter includes a p-type metal-oxide-semiconductor (PMOS) transistor, a n-type metal-oxide-semiconductor (NMOS) transistor and a parasitic capacitor  $C_p$ . Fig. 2.20 shows the simplification of charging and discharging process in an inverter. When the input is low (i.e. logic 'o'), the PMOS is on and NMOS is off. The output becomes high (i.e. logic '1') and  $V_{sense}$  charges  $C_p$  through PMOS. In contrast, when the input is high (i.e. logic 'o'), the PMOS turns off and NMOS turns on. The output becomes low (i.e. logic 'o') and  $C_p$  is discharged through NMOS [59].

Figure 2.21: The operation of the ring oscillator[82]

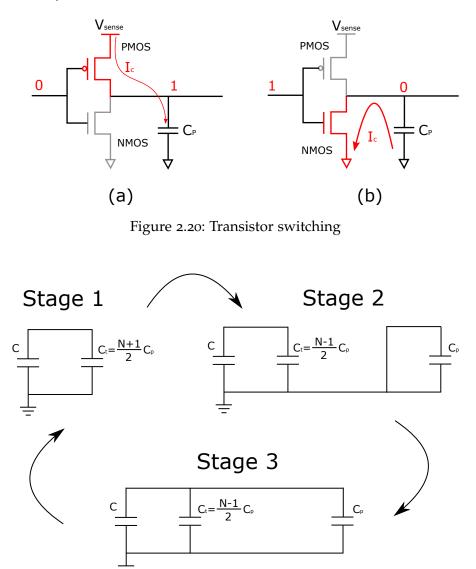

The operation of the ring oscillator with N inverters can be explained in three stages shown in Fig.2.21. Stage 1 represents the situation when C is just connected to the ring oscillator. In this state, no switching action has been fired. In other words, no charging or discharging action takes place. In this initial state, the output of each odd numbered inverter is at logic '1', which means (N+1)/2 of C<sub>p</sub> are charged to the voltage level equal to

that of C. The output of rest inverters is at logic 'o' and their corresponding  $C_p$  are empty. Stage 2 represents the state that a switching occurs. The output of one of the odd numbered inverter is supposed to switch from 1 to o. Its corresponding  $C_p$  is gradually discharged. The state of the remaining inverters stays the same as in stage 1. No energy transfers from C in this stage. In stage 3, the discharged  $C_p$  associated with the next inverter which is supposed to switch from 0 to 1 begins to receive charge from C. This is the only state that draws energy from C [59]. These three stages keep repeating until the energy in C is empty.

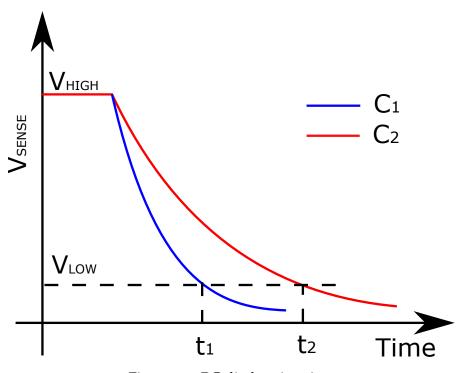

Fig. 2.22 shows the process of  $V_{sense}$  dropping over time.  $V_{sense}$  represents the voltage across C. Hence, as explained before,  $V_{sense}$  drops only in stage 3 and  $t_n$  is a function of  $V_{sense}$ .

## 2.7 METASTABILITY FILTER

## 2.7.1 Definition of Metastability

In a digital circuit system, the digital signals should be either logic 'o' or '1' within certain voltage to operate the circuit correctly. In certain situations, it is possible for a signal to have an equilibrium point with a voltage which is somewhere in between those corresponding to logic 'o' and logic '1'. For instance, if logic 'o' corresponds to oV and logic '1' corresponds to 1V, a circuit may have an equilibrium at around 0.5V. The state of a signal being in such an equilibrium point is known as metastability because such equilibriums are not stable. The metastability may cause loss of data. In the worst case scenario, if a metastable output is continuously interpreted as random 'o' or '1' by different subsequent logic stages, it may cause system failure [47, 69, 15].

The metastability mostly happens in a flip flop or latch. When the active edge of the clock and the transition of data signal arrive at the same time (or sufficiently close) [7], the time difference between them becomes smaller than the clock setup time  $t_{su}$  or hold time  $t_h$  of the signal. [15, 69]. The latching circuit may fall into a non-logic 'o' and non-logic '1' equilibrium, which although unstable, would persist for an non-determinant amount of time.

Take the operation of a D flip-flop as an example. Fig. 2.23 shows the symbol of a D flip-flop and the corresponding truth table. The D flip-flop has two inputs which are signal 'D' and the clock 'CLK'. If the rising edge of 'CLK' is not triggered, the

Figure 2.23: D flip-flop and the truth table

output Q remains its previous state; If 'CLK' becomes logic '1', then 'Q' becomes the same logic as input 'D' [8].

Figure 2.24: Timing diagram of D flip-flop (a) Normal state; (b) Metastable state

Fig. 2.24(a) shows the time diagram of a D flip-flop in a normal state. Before the 'CLK' rises, a certain time is needed that the input 'D' can not change. That time is called setup time,  $t_{su}$ . The same, after 'CLK' rises, another certain time is needed during which the input 'D' need to be stable as well. That time is called hold time,  $t_h$ . In this case,  $t_{su} < t_1$  and  $t_2$ ;  $t_h < t_3$ . This makes sure that the D flip-flop can operate correctly and outputs a stable 'Q'. However, Fig. 2.24(b) shows a metastable state. In this scenario, sometimes the two inputs 'CLK' and 'D' are triggered almost at the same time, where  $t_{su} > t_1$  and  $t_h > t_3$ . The metastable state then may happen during transition. The consequence is that the D flip-flop does not have enough

time to stabilize the signal. The output 'Q' becomes unstable, which means random 'o' and '1' will be triggered.

Figure 2.25: Detailed timing diagram of metastable state [47]

Fig. 2.25 shows the metastable state happened in 2.24(b) in detail. Assuming that 'Q' is set to logic 'o' initially and 'D' just becomes logic '1'. When 'CLK' is triggered and at the same time, 'D' is becoming 'o' again. 'Q' should start rising but may get stuck in the middle of logic levels because it detects the falling of 'D'. Should 'Q' keep rising to '1' or falling to 'o'? In fact, either decision is correct. However, in this case, the D flip-flop becomes unstable. During this time, 'Q' may persist in the metastable equilibrium of 'o.5' for an non-determinant amount of time before settling randomly either to 'o' or '1'. The time it takes 'Q' to become a valid logic value is theoretically unbounded. In this metastable state, 'Q' inputs to the different subsequent logic stages and may be interpreted as random 'o' or '1'. This could cause operation errors of the circuit and eventually cause system failure [47].

#### 2.7.2 Mutual Exclusion

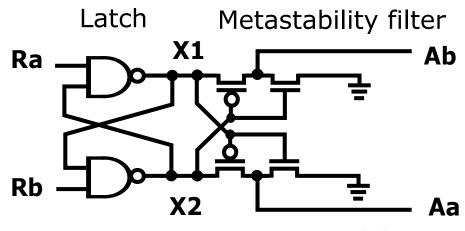

Figure 2.26: The mutual exclusion element [69]

Metastability is an obvious problem with MUTEX elements because these are designed for arbitrating asynchronously arriving signals, for which 'conflicting signals arriving at the same time' is a standard operation state. A MUTEX element therefore must contain methods of resolving metastability. One way of doing this is to add a metastability resolver or filter to a standard SR latch, in the scheme shown in Fig. 2.26. 'Ra' and Rb' are input signals with independent timing. 'Aa' and 'Ab' are the outputs of the MUTEX. The NAND gate latch enables one input to block the other. The task of the MUTEX is to pass 'Ra' and Rb' to their corresponding outputs 'Aa' and 'Ab' in such a way that at most one output is active at any given time. If one input arrives well earlier than the other, the corresponding output is then granted and the latter input signal is blocked until the first arrived signal is de-asserted. When the two inputs arrive at the same time, the circuit may fail to immediately resolve which one comes first, leading to metastability. In this scenario, both 'X1' and 'X2' have voltages about half way between those of V<sub>dd</sub> and ground. The metastability filter prevents these undefined values to propagate

to the outputs. 'Aa' and 'Ab' are both kept low until 'X1' and 'X2' differ by more than a transistor threshold voltage in the metastability filter [69]. Hence, the metastable state does not propagate outside the MUTEX when it is happening and the output only moves after metastability has settled.

#### 2.8 SUMMARY

This chapter provides a background and literature review of capacitive and voltage sensing techniques. Capacitive sensors are widely used in modern life. In a capacitive sensing system, the CDCs are commonly used in capacitive sensing systems as sensor interfaces. The ADC-based CDCs are reviewed briefly. These CDCs require complex analogue circuits which increase design complexities and power consumption. Several Frequency/Timebased CDCs based on different methods including period modulation, pulse width modulation, frequency modulation and iterative delay-chain discharge method are then summarized. These CDCs are semi-digital or fully digital, which often consume less power but the measurement time usually needs to be improved. Moreover, the voltage sensing systems with/without reference voltages are presented. The principles of the charge-todigital conversion system is summarized as well. The QDC does not need external power supply and can be implemented as either a capacitive sensor interface or a voltage sensor interface. In addition, the operation of capacitor discharging through a ring oscillator are explained. The process is in fact charging and discharging the parasitic capacitors in the oscillator. Finally, the issue of metastability is discussed. The metastability mostly happens in a flip flop or latch and may cause system failure. A

MUTEX element within a metastability filter inside makes sure the metastable state does not propagate outside the MUTEX and the output only moves after metastability has settled.

# GENERAL THEORY AND ALGORITHM

#### 3.1 MATHEMATICAL THEORY

This section shows the steps of improvement and simplification from a RC discharging circuit to a fully digital QDC.

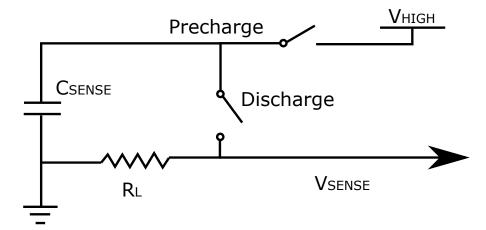

# 3.1.1 RC discharging circuit

Figure 3.1: A simple RC discharging circuit

Fig. 3.1 shows a simple RC discharging circuit. It contains a power source  $V_{\text{HIGH}}$ , a sensed capacitor  $C_{\text{SENSE}}$ , a load resistor  $R_{\text{L}}$  and two switches which control the charging and discharging of  $C_{\text{SENSE}}$ . First, the switch 'Precharge' turns on while the switch 'Discharge' is off.  $C_{\text{SENSE}}$  is then charged gradually to the level of  $V_{\text{HIGH}}$ . Once it is fully charged, the switch 'Precharge' turns off and the switch 'Discharge' turns on.  $C_{\text{SENSE}}$  is then discharged

gradually through  $R_L$ . The discharging equation is shown below according to [9, 21]:

Firstly, we have:

$$I = -\frac{dQ}{dt}$$

(3.1)

As we know:

$$V = IR, Q = CV \tag{3.2}$$

By replacing I and Q in Eq. 3.1, we can have:

$$\frac{V}{R} = -C\frac{dV}{dt}$$

(3.3)

After rearranging, we can get:

$$\frac{\mathrm{d}V}{\mathrm{V}} = -\frac{1}{\mathrm{RC}}\mathrm{dt} \tag{3.4}$$

By integrating Eq. 3.4, we have:

$$\int \frac{\mathrm{d}V}{\mathrm{V}} = -\int \frac{1}{\mathrm{RC}} \mathrm{d}t \tag{3.5}$$

Then:

$$\ln V = -\frac{t}{RC} + A \tag{3.6}$$

$$V = e^{-\frac{t}{RC} + A} \tag{3.7}$$

$$V = e^{-\frac{t}{RC}} \cdot e^{A} \tag{3.8}$$